Clock synchronous device and system for Field Programmable Gate Array (FPGA) prototype test plate piling

A prototype verification and clock synchronization technology, applied in the field of FPGA prototype verification, can solve the problems of unguaranteed quality and difficulty in flexible change of the number of synchronization clocks, to simplify the circuit design structure, improve the clock synchronization efficiency, improve the clock synchronization efficiency and The effect of precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0030] On the contrary, the invention covers any alternatives, modifications, equivalent methods and schemes within the spirit and scope of the invention as defined by the claims. Further, in order to make the public have a better understanding of the present invention, some specific details are described in detail in the detailed description of the present invention below. The present invention can be fully understood by those skilled in the art without the description of these detailed parts.

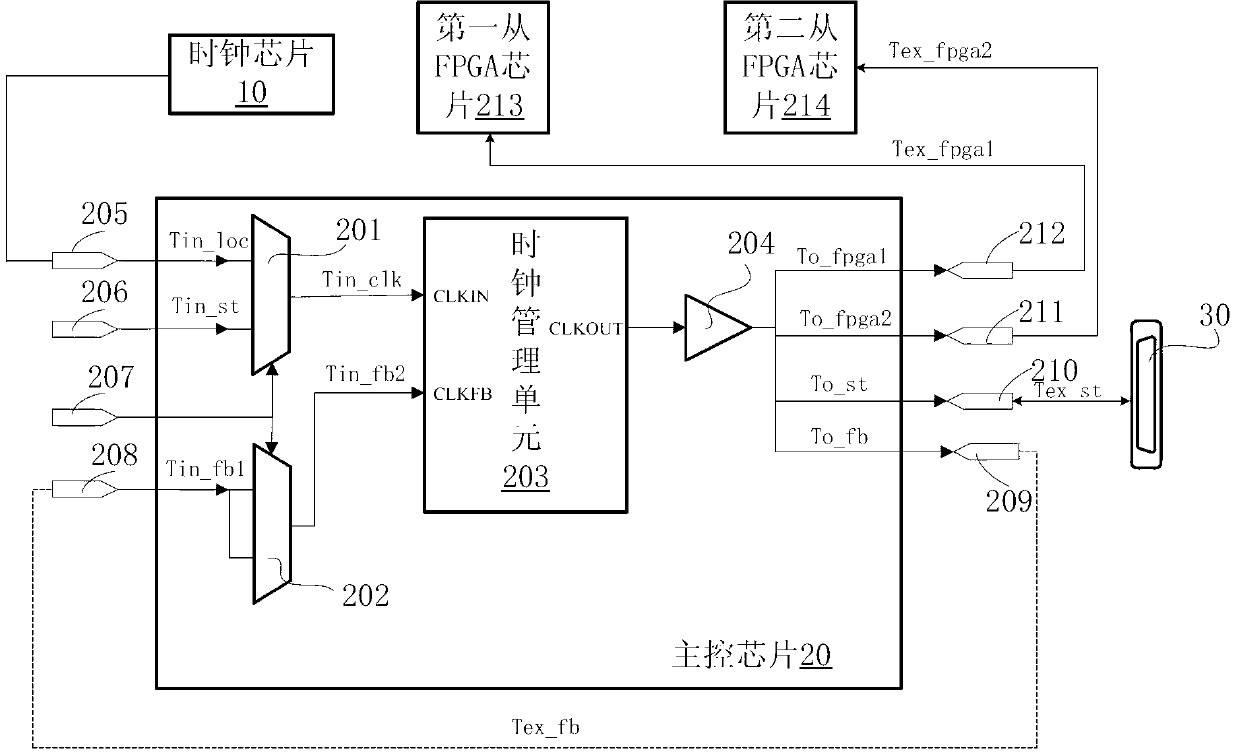

[0031] refer to figure 1 , which shows the principle structure diagram of the clock synchronization d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More