Patents

Literature

103 results about "Clock management unit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

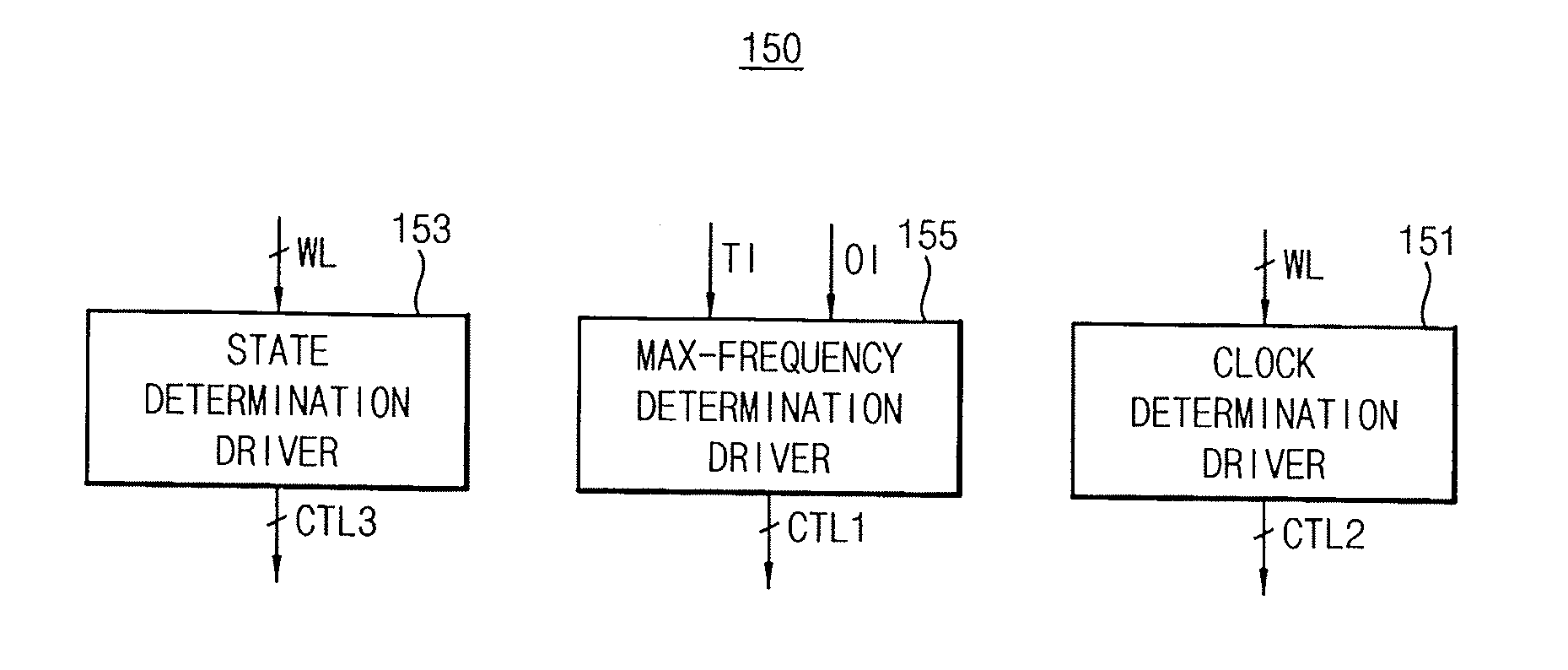

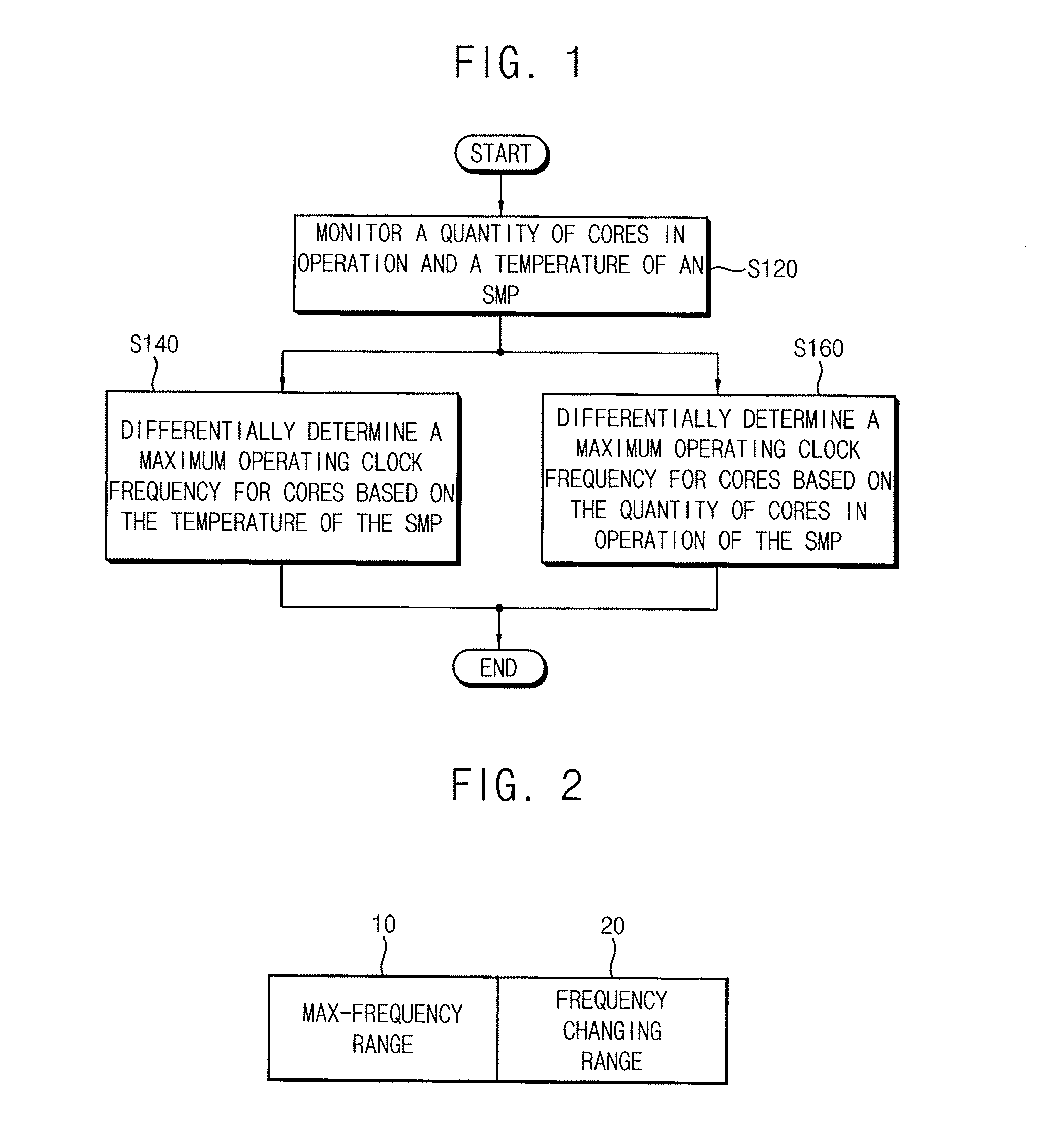

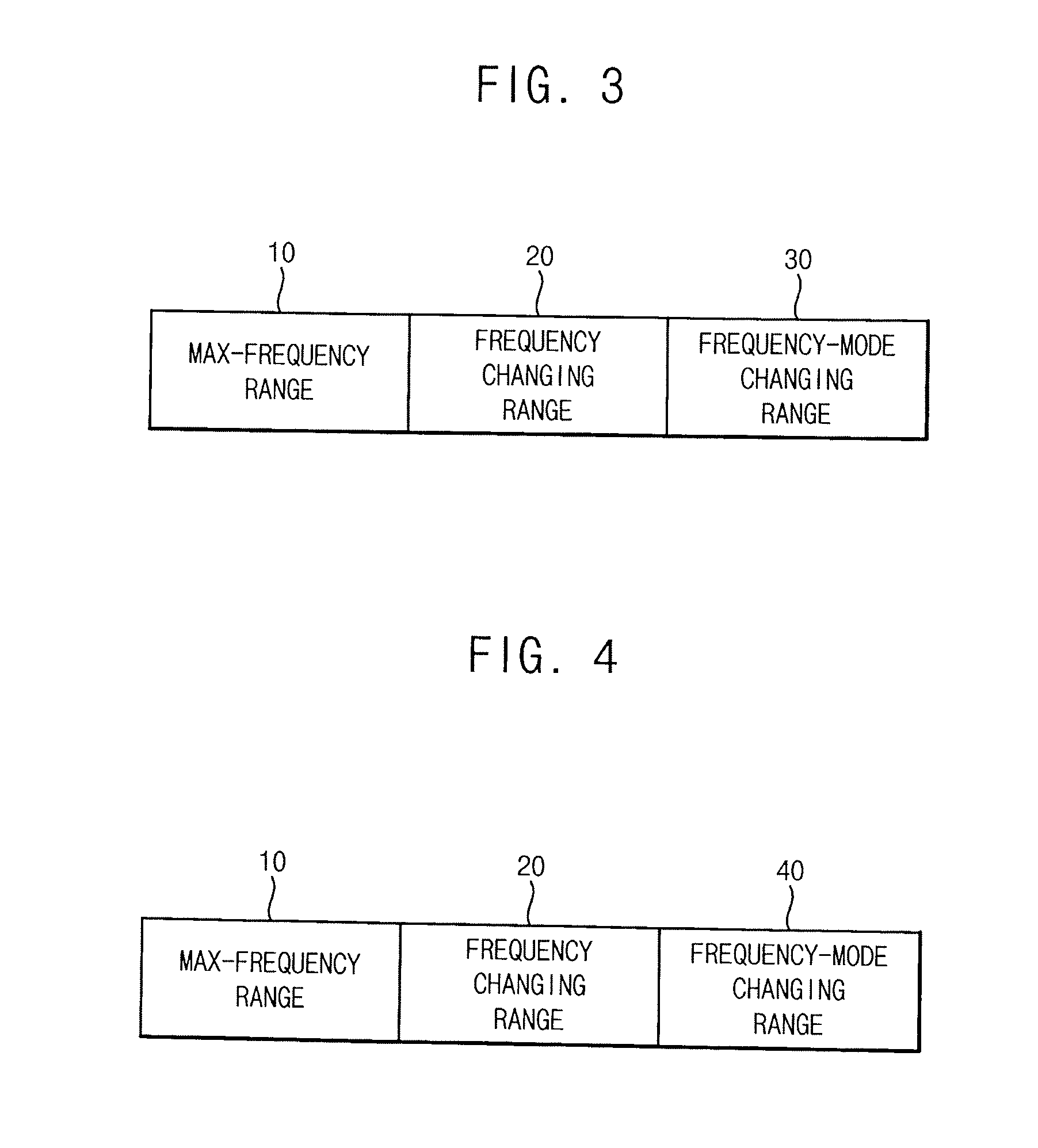

System-on-chip having a symmetric multi-processor and method of determining a maximum operating clock frequency for the same

ActiveUS20150134995A1Reduce heatReduce power consumptionVolume/mass flow measurementHardware monitoringManagement unitMulti processor

A system-on-chip includes a symmetric multi-processor including a plurality of cores, each configured to operate in a high performance operating mode and a low performance operating mode. The system-on-chip further includes a clock management unit configured to provide an operating clock signal to the symmetric multi-processor, a state management unit configured to monitor operating states of the cores, a temperature management unit configured to monitor a temperature of the symmetric multi-processor, and a symmetric multi-processor control unit configured to determine the operating clock signal and the operating states of the cores based on a workload of the symmetric multi-processor. The symmetric multi-processor control unit is further configured to differentially determine a maximum operating clock frequency for the cores based on the temperature and the operating states of the cores, which indicate a quantity of cores that are currently in operation.

Owner:SAMSUNG ELECTRONICS CO LTD

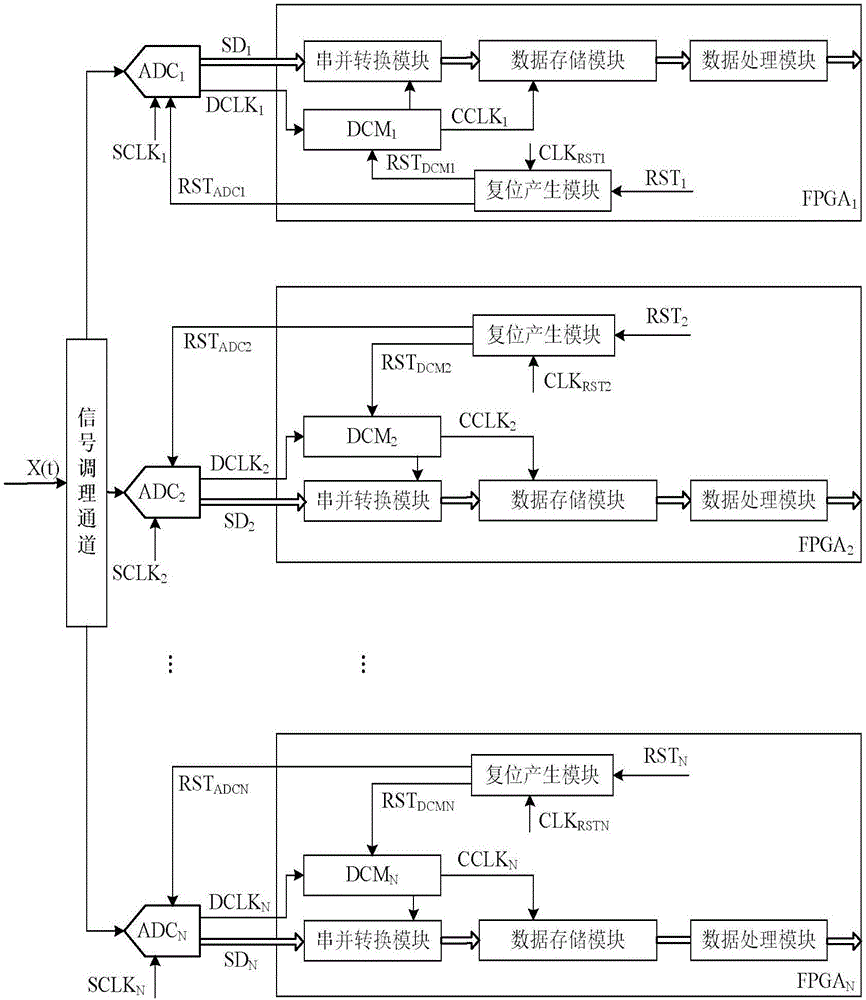

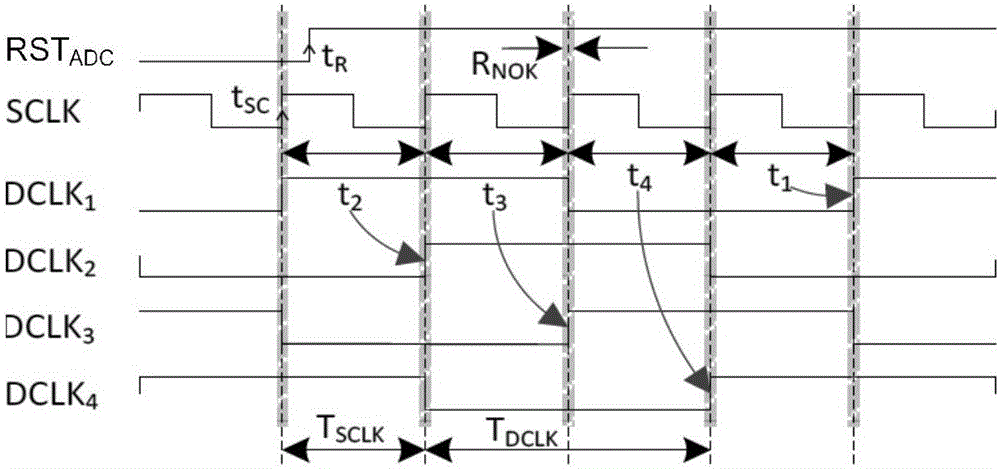

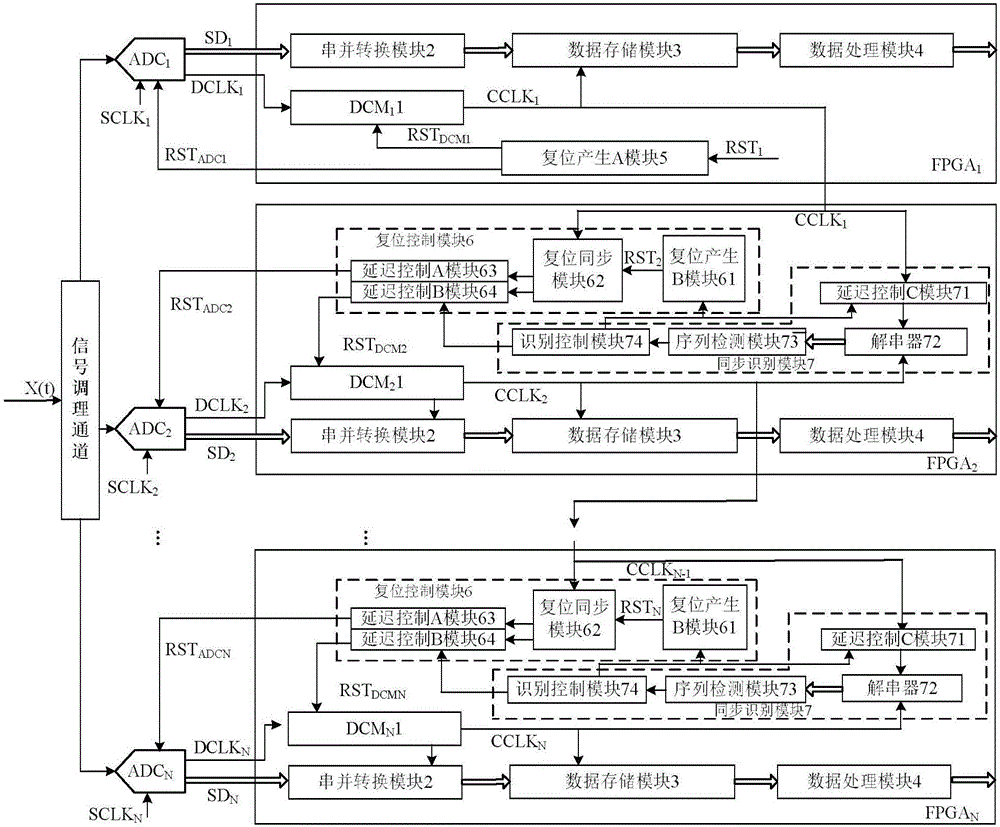

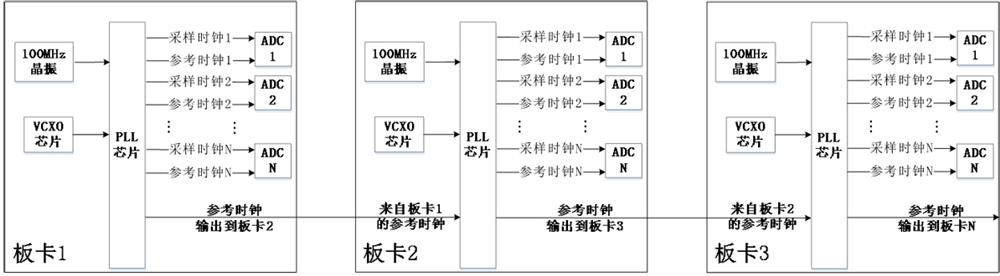

Multichannel parallel acquisition system with multi-device asynchronous reset recognition correction function

ActiveCN106253902AGuaranteed accuracyAnalogue/digital conversion calibration/testingComputer modulePhase relation

The invention discloses a multichannel parallel acquisition system with a multi-device asynchronous reset recognition correction function. In N ADC and FPGA modules of the multi-channel parallel acquisition system, the first FPGA module sends a reset signal according to a system reset start command to complete the reset operation of the ADC and the DCM, thereby generating a stable data work clock CCLK1 in the FPGA; each of the second to the N-th FPGA modules contains a synchronous recognition module and a reset control module; the synchronous recognition module is used for adjusting a delay value of the data work clock of the former FPGA module, and synchronously recognizing the data work clocks of the current FPGA and the former FPGA through the adoption of a de-serializer and a sequence detection module, using the delay value in synchronization as the time interval, and then adjusting the delay value from the reset signal to the corresponding ADC and the clock management unit according to the time interval, thereby completing the multi-device asynchronous reset recognition correction. Through the adoption of the system disclosed by the invention, the reset accuracy can be guaranteed; therefore, the phase relation of the multi-channel data work clock after each synchronous resetting is determined.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

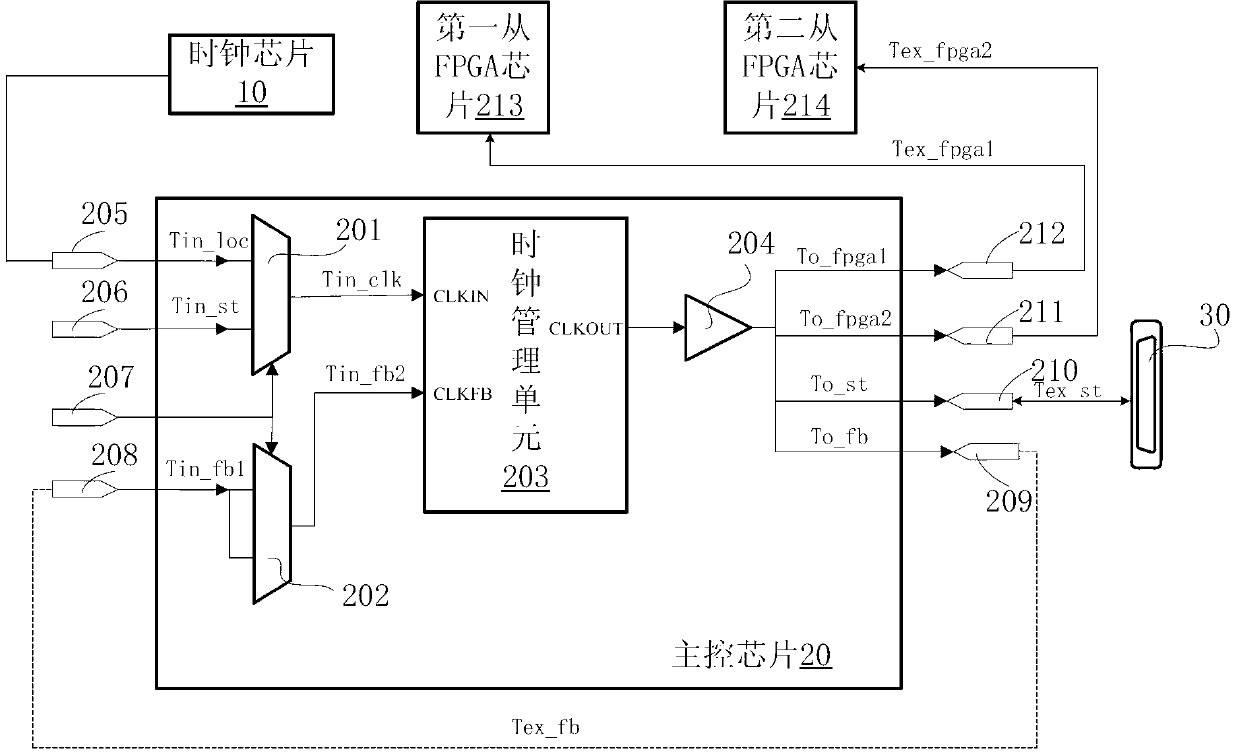

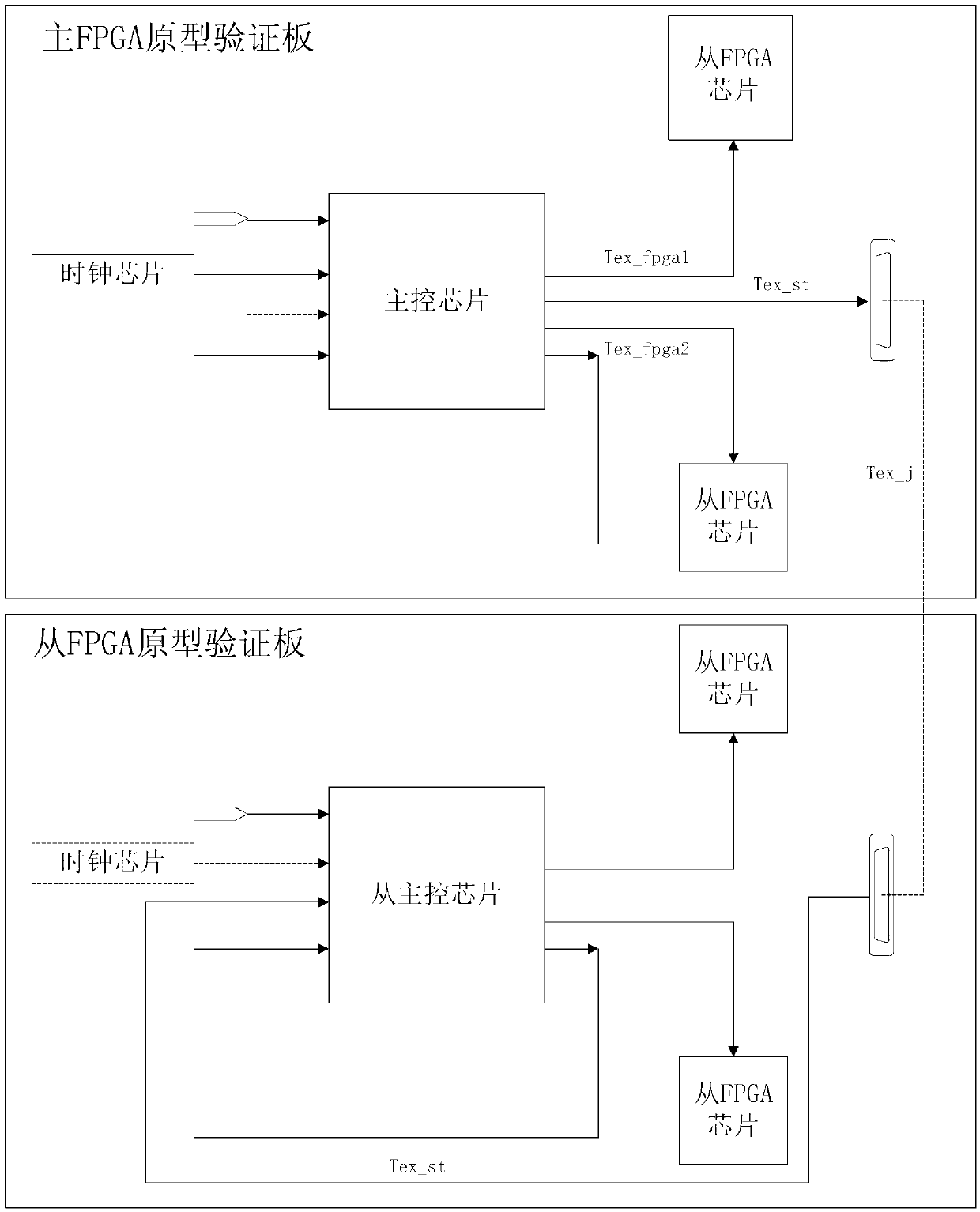

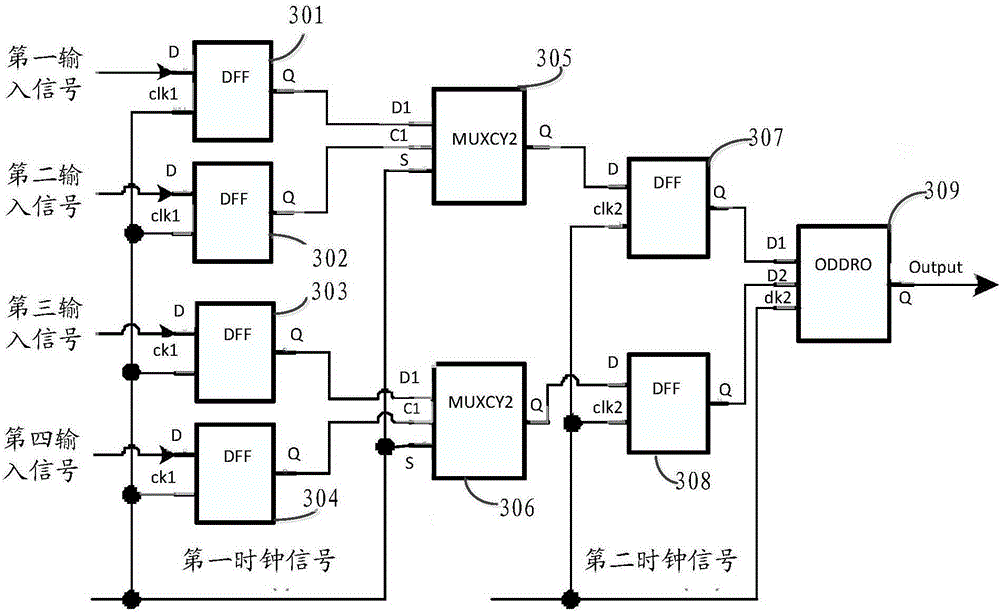

Clock synchronous device and system for Field Programmable Gate Array (FPGA) prototype test plate piling

ActiveCN103105889ASimple designImprove clock synchronization efficiencyFunctional testingGenerating/distributing signalsTime delaysMultiplexer

The invention discloses a clock synchronous device and a system for Field Programmable Gate Array (FPGA) prototype test plate piling, wherein the clock synchronous device for FPGA prototype test plate piling comprises a clock chip, a master control chip, at least one slave FPGA chip and at least one high-speed connector, wherein the main control chip further comprises a first data selector, a second data selector, a clock management unit and a global clock buffer. The master chip comprises a local clock input pin, a piling clock input pin, a selective signal input pin, a selective signal input pin, a feedback clock input pin, a slave FPGA clock synchronization clock signal output pin, a feedback clock synchronization clock signal output pin and a high-speed connector synchronization clock signal output pin. The clock synchronous device and the system for FPGA prototype test plate piling utilize a master control chip inner lock phrase loop to feed back, the time delay of a master control chip inner routing is equal to the corresponding routing time delay of an outer PCB plate, and the clocks which are output to all slave FPGA chip are enabled to achieve synchronization.

Owner:杭州乔微电子科技有限公司

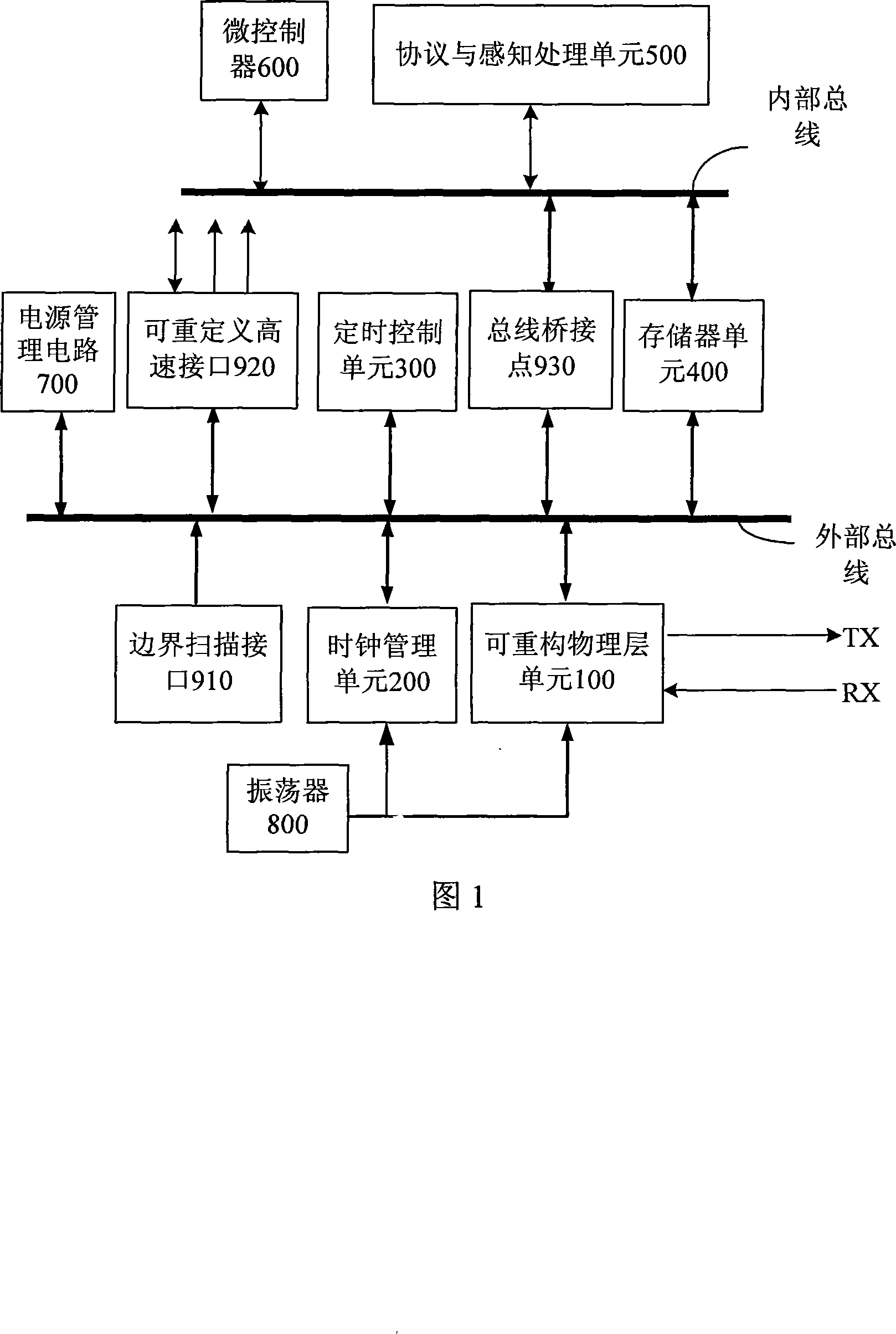

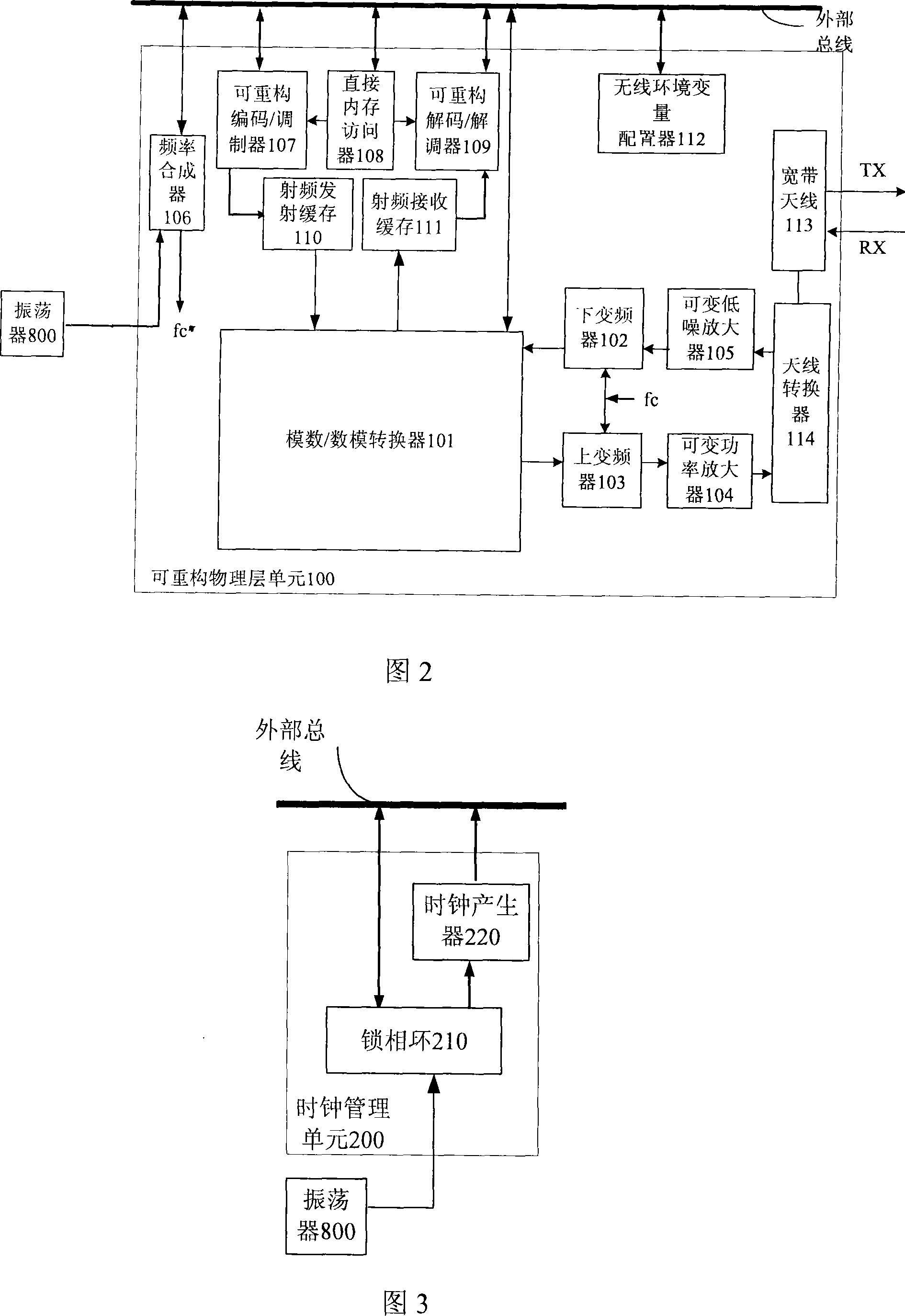

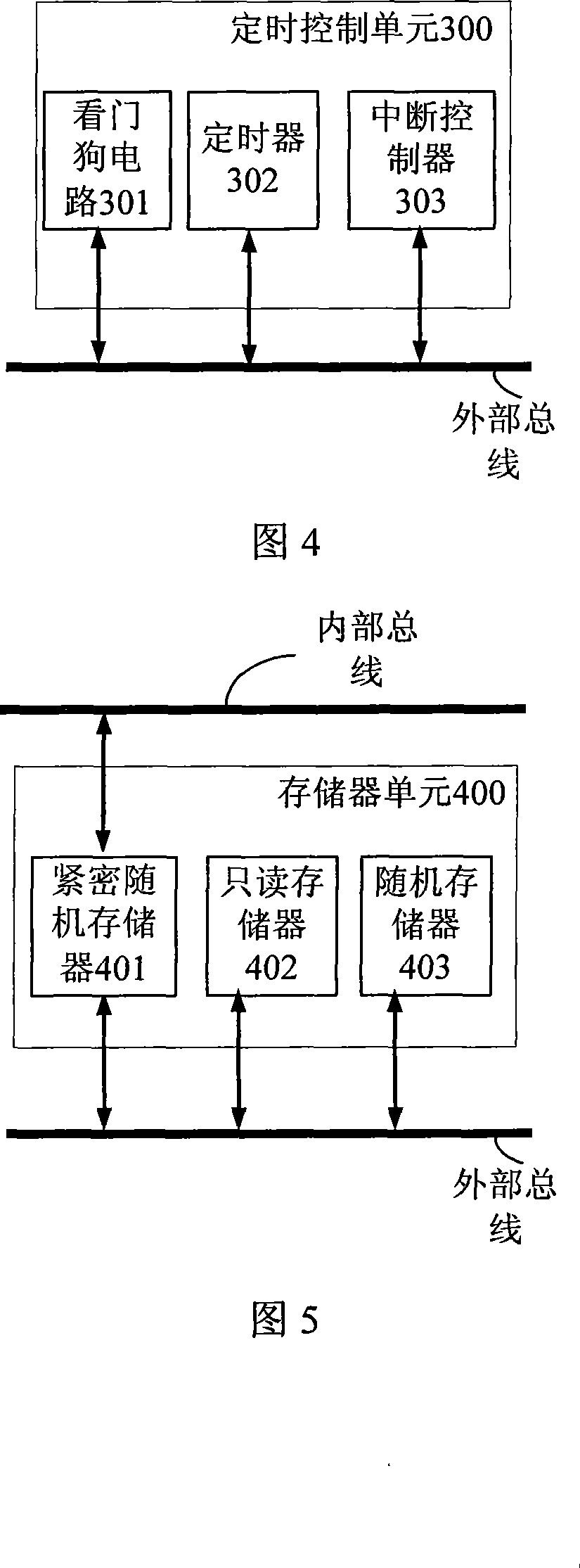

Environment perception restructurable mobile terminal communication processor

The invention discloses a mobile terminal communication processor with environment perception and reconfigurable ability, comprising a reconfigurable physical layer unit, a clock manager, a time control unit, a microcontroller, a storage unit, a protocol and perception processing unit, a bus bridge contact, a boundary scan interface, an oscillator, a power management circuit, a high-speed interface for multiple architectures and a bus bridge contact. Datum from exterior are received and self-adaptive transceived by the reconfigurable physical layer unit based on oscillation frequency providedby the oscillator and delivered to the external bus after modulated. The processed datum are delivered to the external bus and sent out from the unit. The invention has the advantages that external environment can be sensed and self-adaptive adjustment of a modulation and demodulation technique and a radio frequency amplifier can be realized; the communication between a non heterogeneous and a heterogeneous network is supported; seamless communication with chips of other protocols in a wide area network can be carried out, and the cost of realization is reduced on basis of improved integral performance of the processor.

Owner:WUHAN SYNTEK CO LTD

Method for transmitting image data of multi-channel high-speed line-frequency-variable linear array CCD (charge coupled device)

ActiveCN103024306ASolve the difficult problem of digital transmissionIncrease transfer rateTelevision system detailsColor television detailsAviationCcd camera

The invention discloses a method for transmitting image data of a multi-channel high-speed line-frequency-variable linear array CCD (charge coupled device), and relates to the field of transmission of image data of aerospace and aviation CCD cameras. The method includes steps that a digital phase-locked loop clock management unit creates a relation between frequency of a pixel transfer clock and frequency of a TLK2711 transmission clock according to the quantity of transmission channels of the CCD, the pixel transfer clock and the quantity of transmission channels of TLK2711 devices; the TLK2711 devices create a reliable and stable transmission link for transmitting and receiving the image data; and multi-channel image data fusion transmission and line signal and image data fusion transmission units start to fuse the multi-channel data into one channel of data and transmit the channel of data to the TLK2711 devices after the transmission link is stable, and the TLK2711 deserializer transmits the channel of data to a receiving FPGA (field programmable gate array) processor. The method has the advantage that cables of an aerospace and aviation remote-sensing camera data transmission system are greatly reduced.

Owner:长光驰宇科技(长春)有限公司

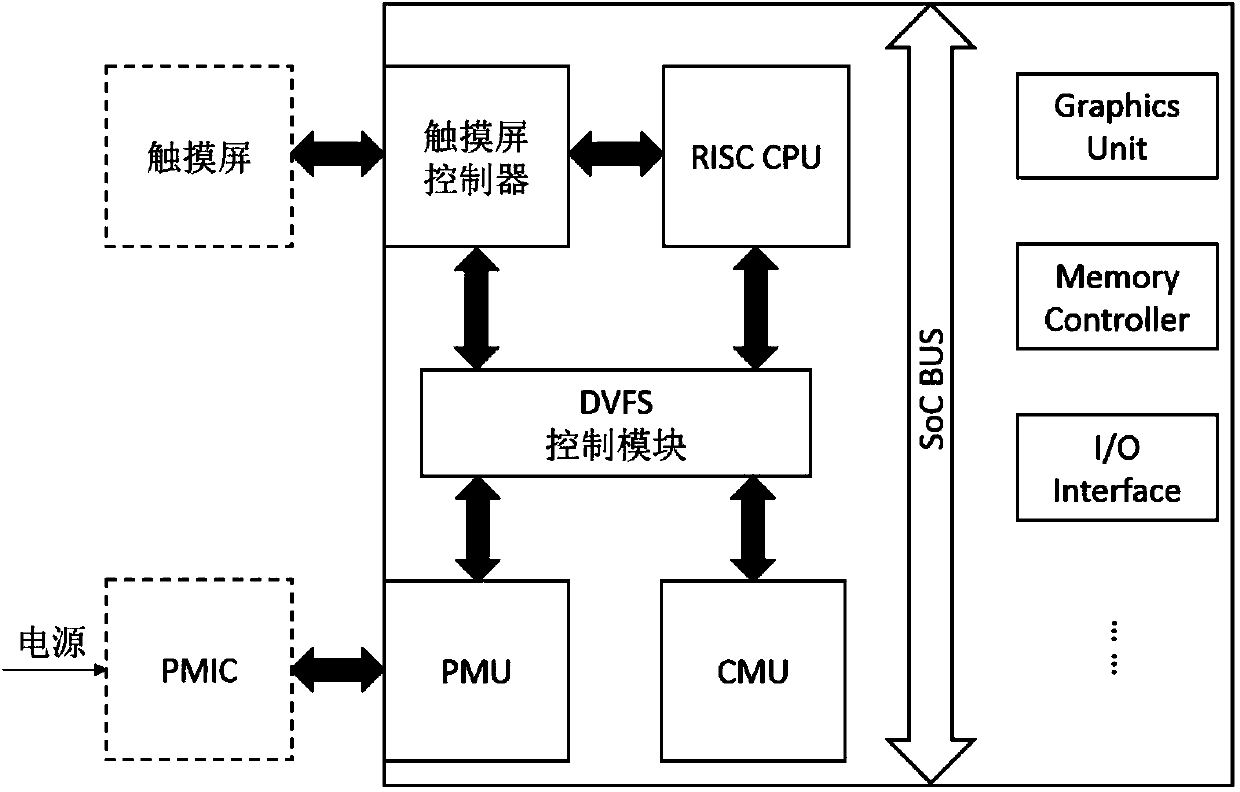

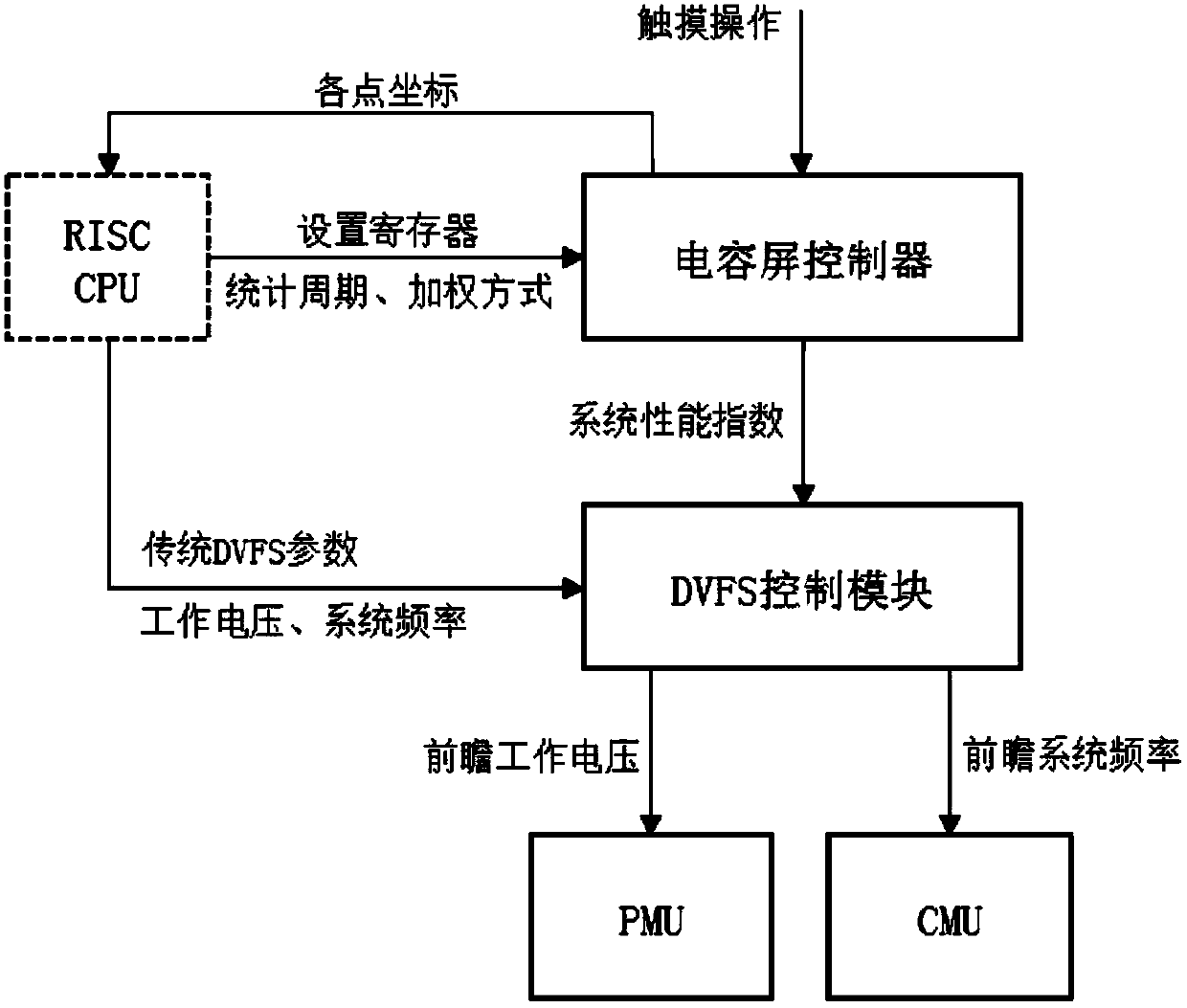

SoC (system on chip) dynamic voltage frequency scaling method with foresight

InactiveCN104216502AImprove system performance indexIncrease system frequencyPower supply for data processingComputer modulePower Management Unit

The invention discloses a SoC (system on chip) dynamic voltage frequency scaling method with foresight and belongs to the field of chip design and application. The invention aims to solves the delay problem of dynamic voltage frequency scaling in a master control chip of a mobile device, realize the reduction of power consumption whiling guaranteeing the CPU (central processing unit) performance and improve the user experience. Compared with a traditional scaling method, the CPU dynamic voltage frequency scaling of a SoC is with foresight and is realized on the basis of the following principle: a capacitive screen controller is integrated to the SoC; the capacitive screen controller adopts the digital-analog mixed signal design, not only has the functions of digital-analog conversion, coordinate output and multipoint touch control of a traditional capacitive screen controller, but also has the functions of touch strength detection, touch frequency statistical and touch length statistical; then a DVFS (dynamic voltage frequency scaling) module outputs a CPU voltage and frequency with foresight through judgment according to the parameters and the load situation of the operating system, and the CPU voltage and frequency are also output to a power management unit and a clock management unit of the SoC for appropriate scaling.

Owner:SOUTH CHINA UNIV OF TECH

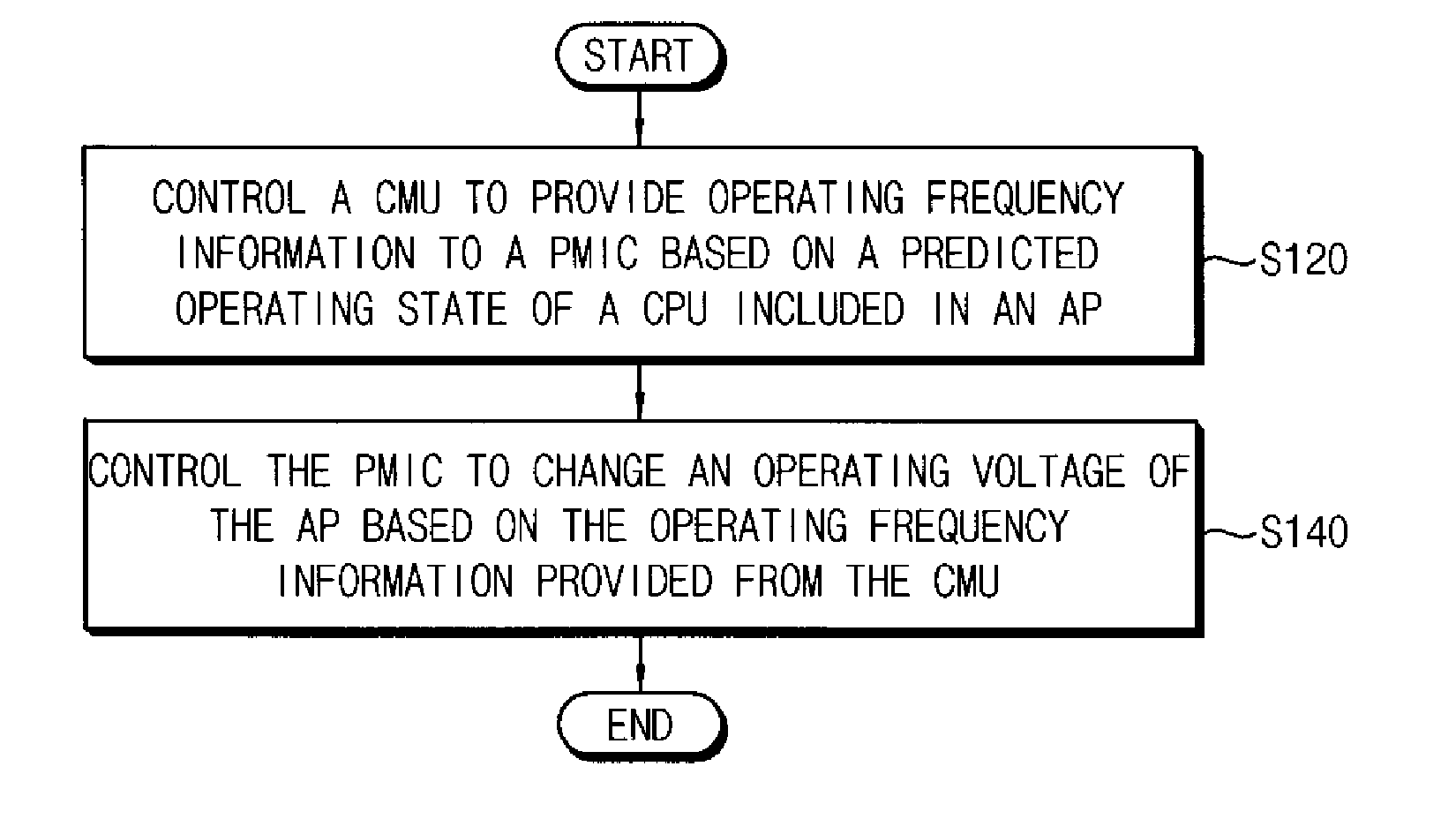

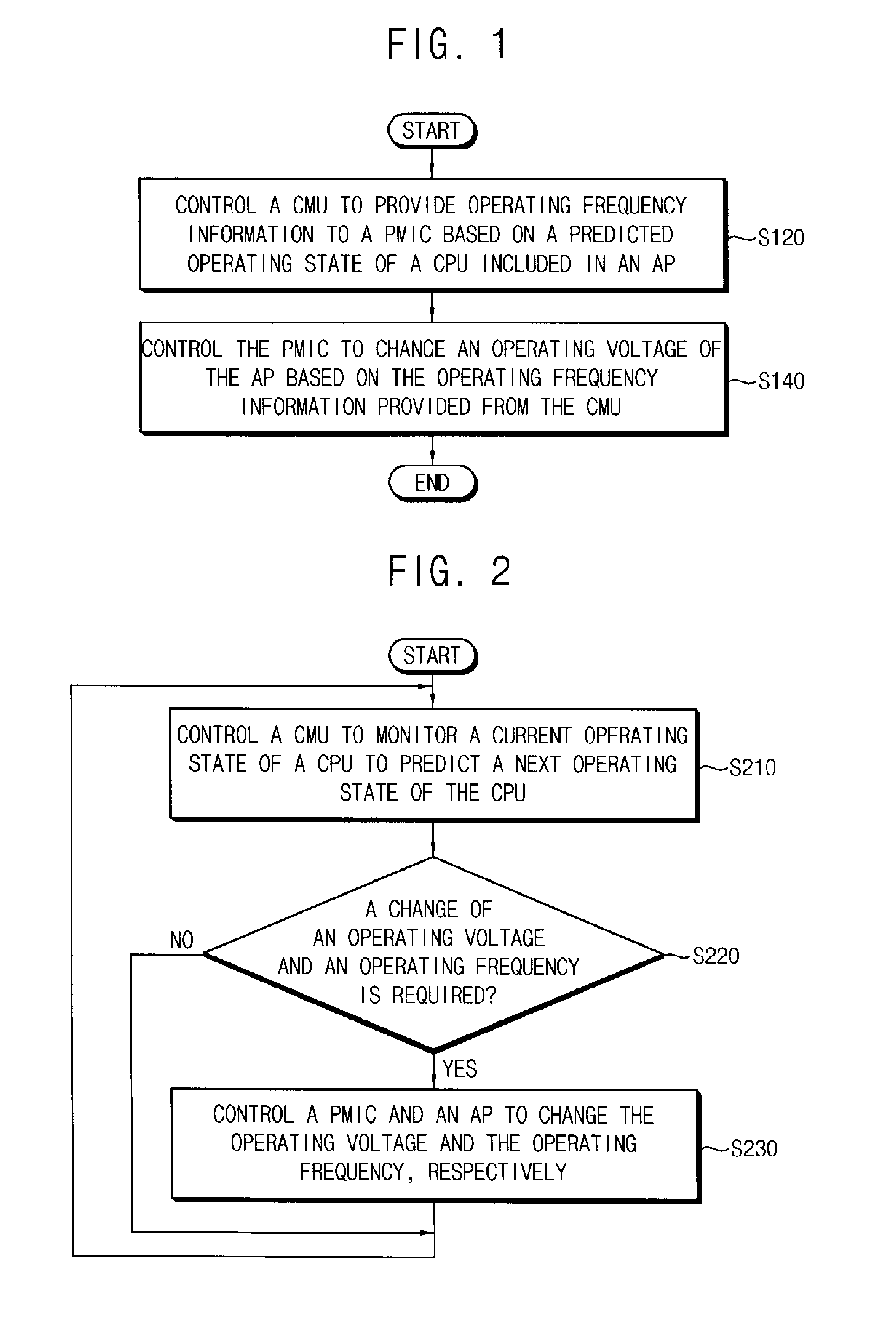

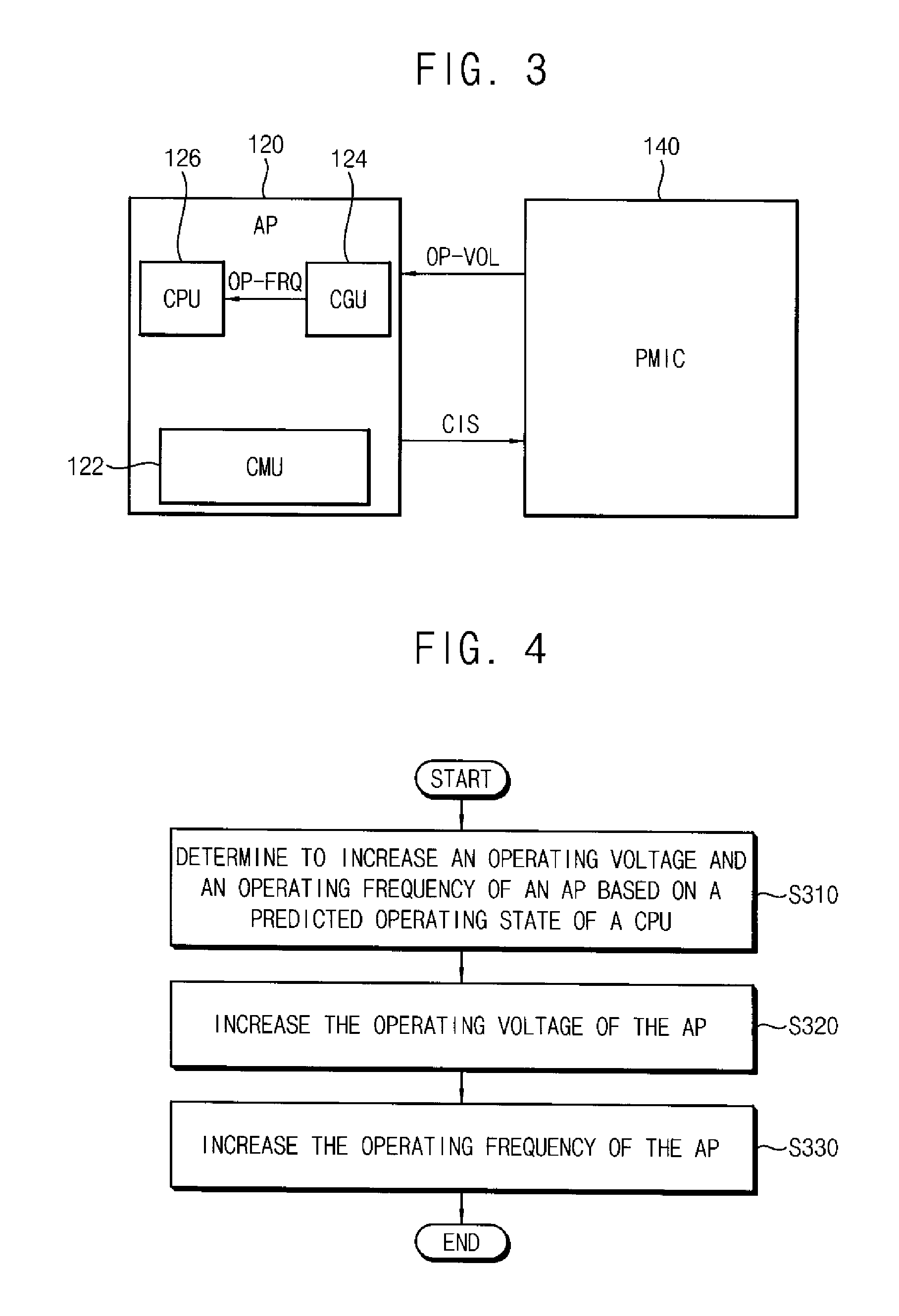

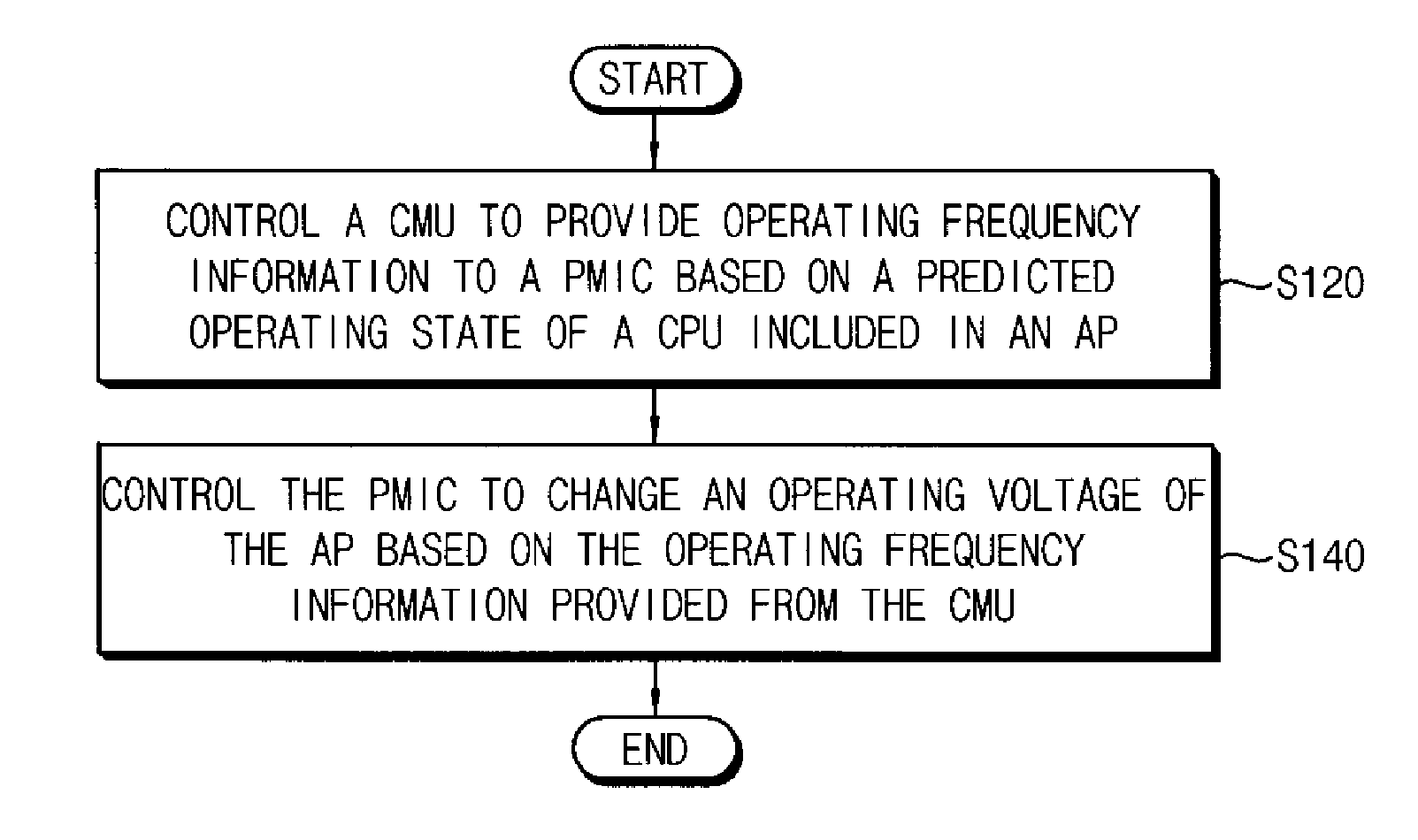

Method of performing dynamic voltage and frequency scaling operation, application processor performing method, and mobile device comprising application processor

ActiveUS20140075224A1Prevent unnecessary power consumptionPower supply for data processingGenerating/distributing signalsProcessing elementMobile device

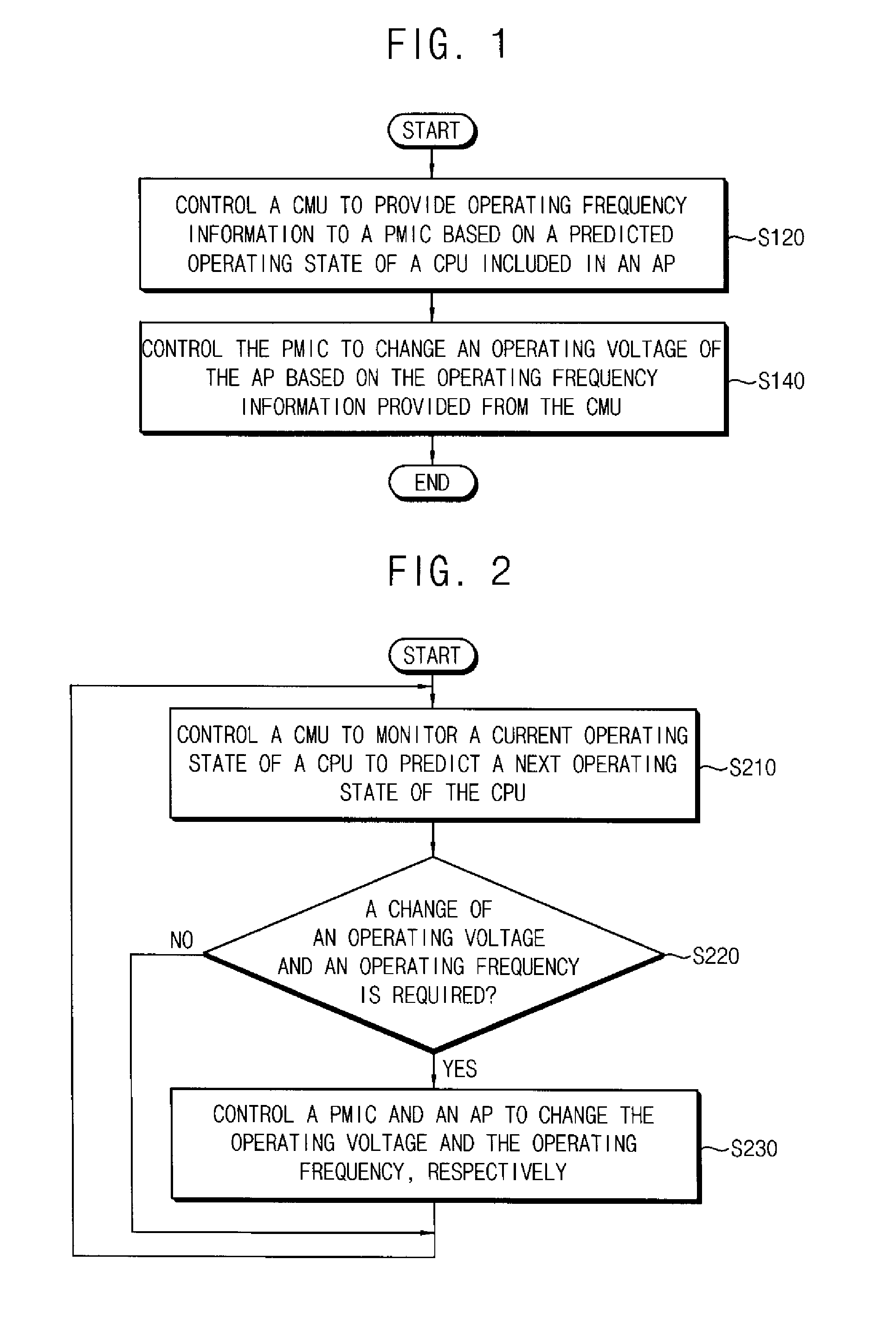

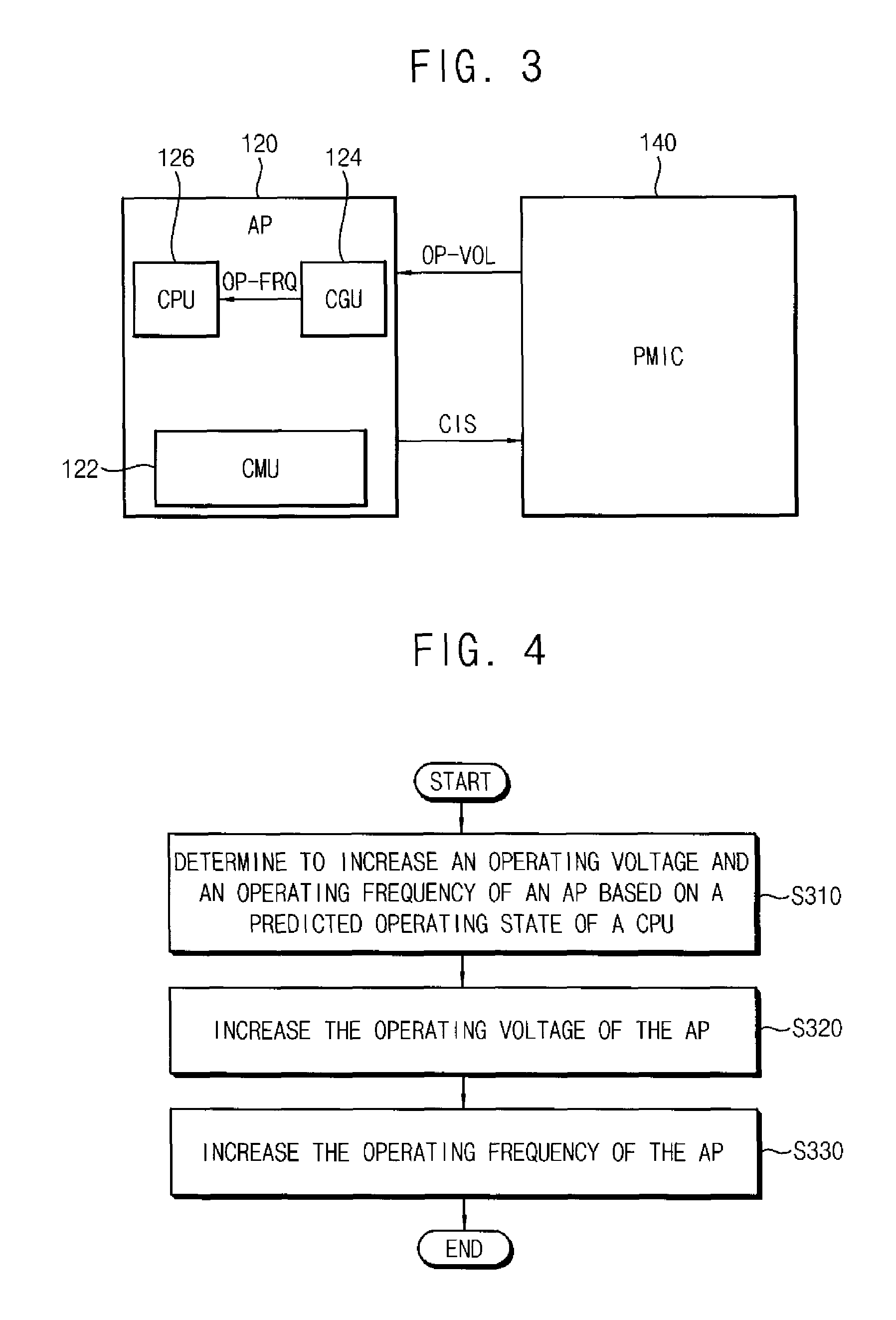

A method of performing a dynamic voltage and frequency scaling operation comprises controlling a clock management unit (CMU) to predict an operating state of a central processing unit (CPU) and to provide operating frequency information to a power management integrated circuit (PMIC) based on the predicted operating state of the CPU, the operating frequency information indicating a change of an operating frequency of an application processor, and controlling the PMIC to change an operating voltage of the application processor based on the operating frequency information provided from the clock management unit.

Owner:SAMSUNG ELECTRONICS CO LTD

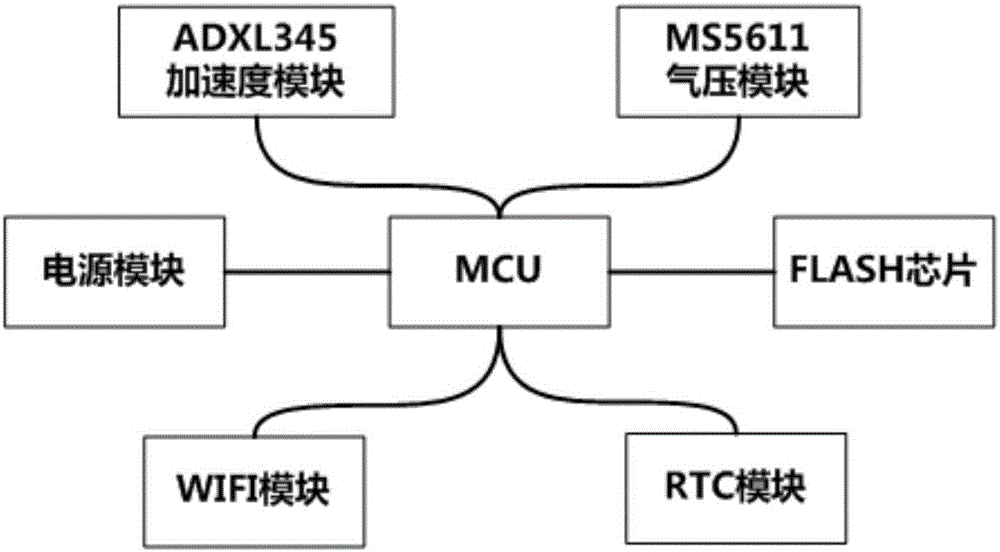

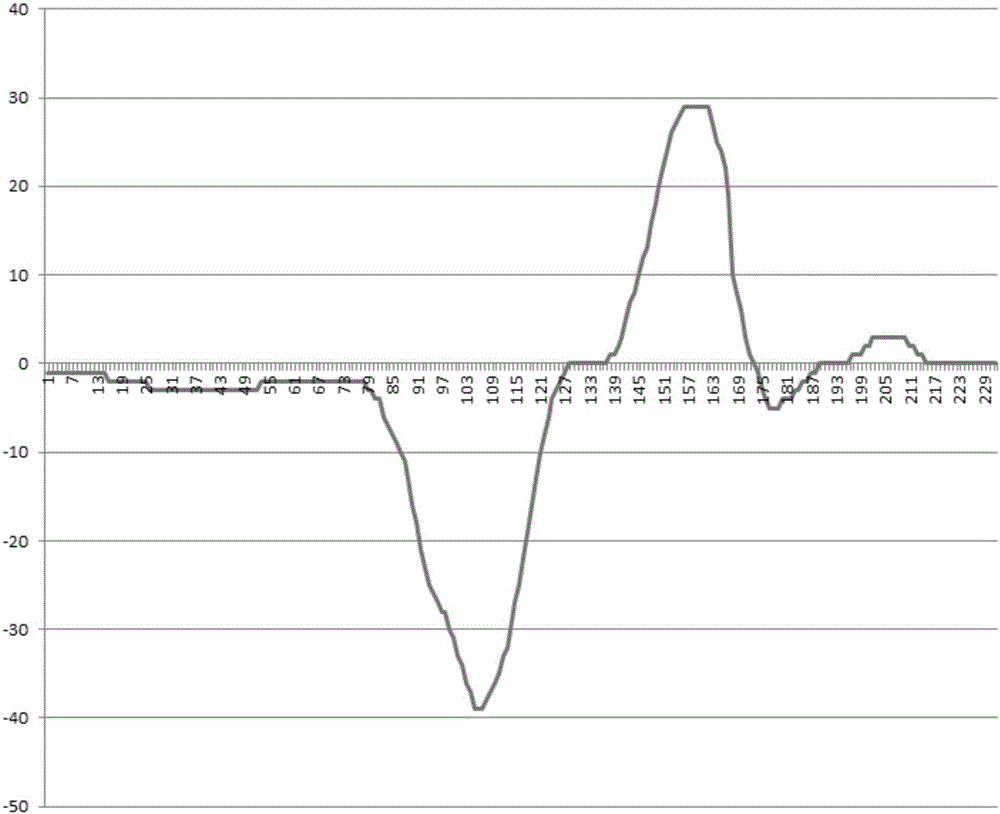

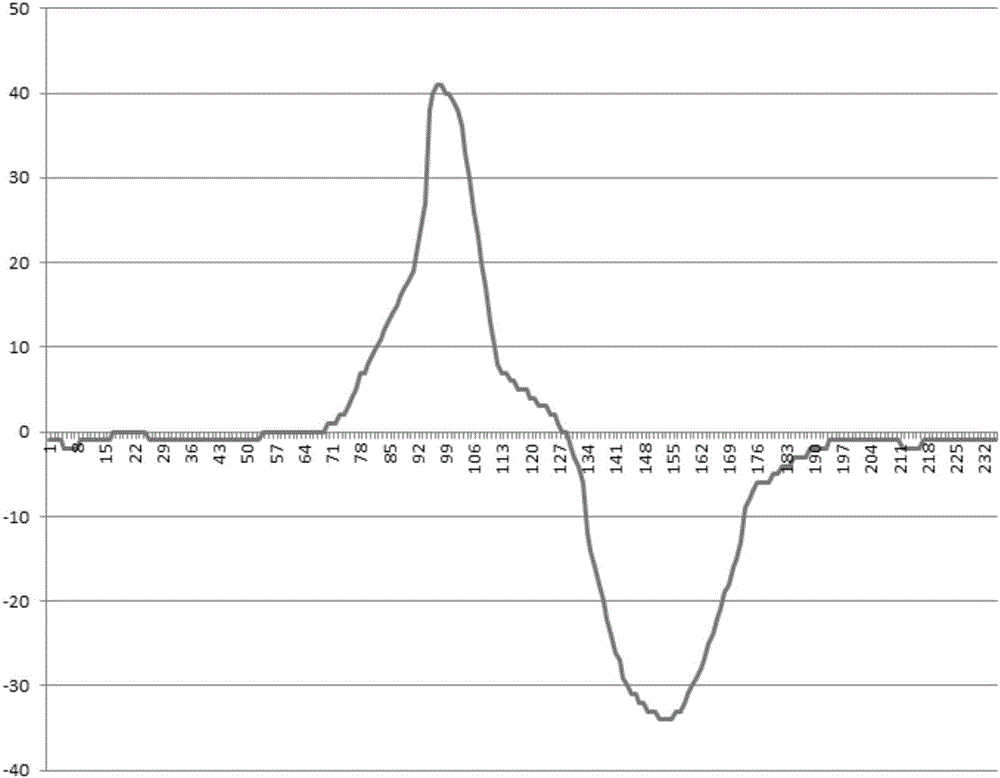

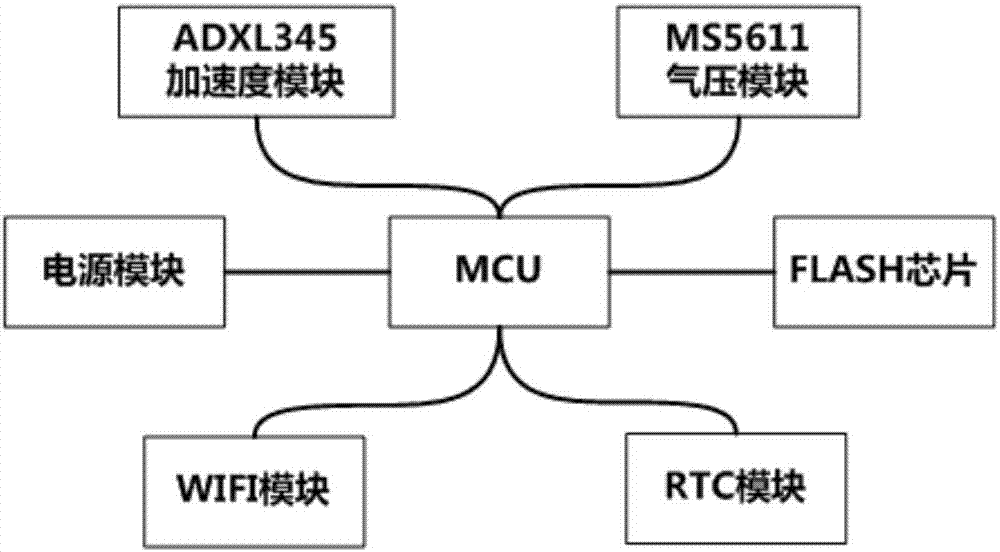

System for acquiring opening and closing information of elevator cage door

The invention discloses a system for acquiring opening and closing information of an elevator cage door. The system comprises an acceleration module which is connected with a single-chip MCU through data and is used for acquiring acceleration information of the cage door, completing acquisition of original data once within certain time and carrying out sum averaging on data of a set number of points to obtain a sum average serving as a sampling point; a Flash chip which is connected with the single-chip MCU through data and is used for storing statistical data of an elevator, a real-time clock management unit which is connected with the single-chip MCU through data and is used for supplying a clock interface for the system, and the single-chip MCU for analyzing opening and closing information of the elevator cage door according to the acceleration information, including: opening (closing) the door: when a negative (positive) directional amplitude value of the sampling point exceeds a door opening (closing) threshed value, calibrating the sampling point as negative (positive) directional acceleration gradual increase, then judging whether the positive (negative) directional amplitude value of the sampling point exceeds the door opening (closing) threshed value, and if the positive (negative) directional amplitude value of the sampling point exceeds the door opening (closing) threshed value, judging that the cage door is in a door opening (closing) state.

Owner:DALIAN ALLRUN ELECTRONICS

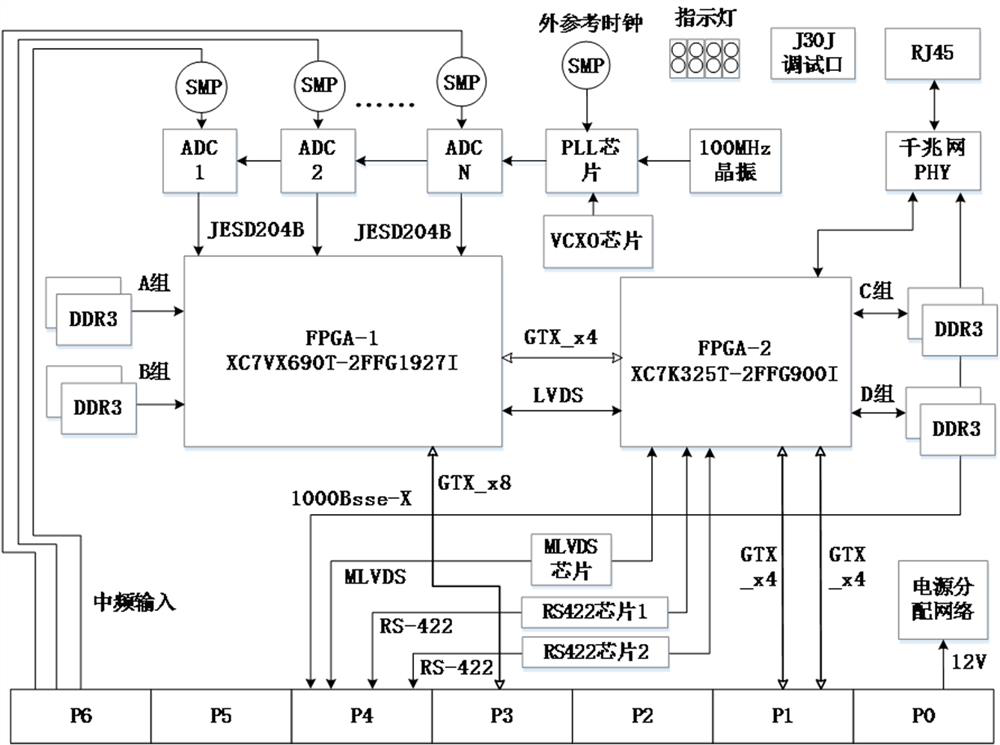

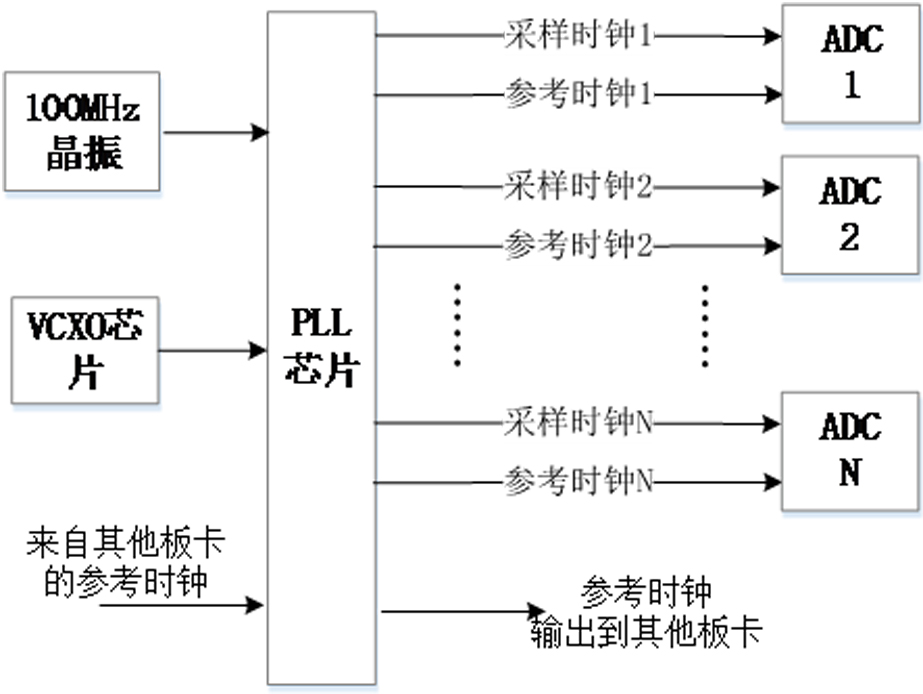

Synchronous acquisition processing card system based on multi-channel ADC and FPGA

InactiveCN111736517AMulti-sample rateA large amountProgramme controlComputer controlComputer hardwareIntermediate frequency

The invention discloses a synchronous acquisition processing card system based on a multi-channel ADC and an FPGA. The synchronous acquisition processing card system comprises a clock management unit,a plurality of ADC chips, two FPGA chips, a plurality of groups of DDR3 chips and a power distribution network. The clock management unit generates multiple paths of synchronous sampling clocks and reference clocks, and the ADC chips are used for collecting and converting intermediate frequency signals accessed by an SMP. In the present invention, the invention relates to the technical field of ultra-high-speed data acquisition and processing. The sampling clock management unit provides sampling clocks and reference clocks required by synchronous sampling of multiple ADCs, it is convenient for expansion of ADC channel numbers. ADC+FPGA+DDR3 construction is adopted to complete data acquisition, processing, and caching, so that the synchronous acquisition processing card system has the advantages of being large in synchronous acquisition channel number, large in data storage capacity, high in processing capacity, wide in data transmission bandwidth and the like, and the market requirement of array signal processing for multi-channel synchronous data acquisition can be met.

Owner:CHENGDU SIMATE SCI & TECH

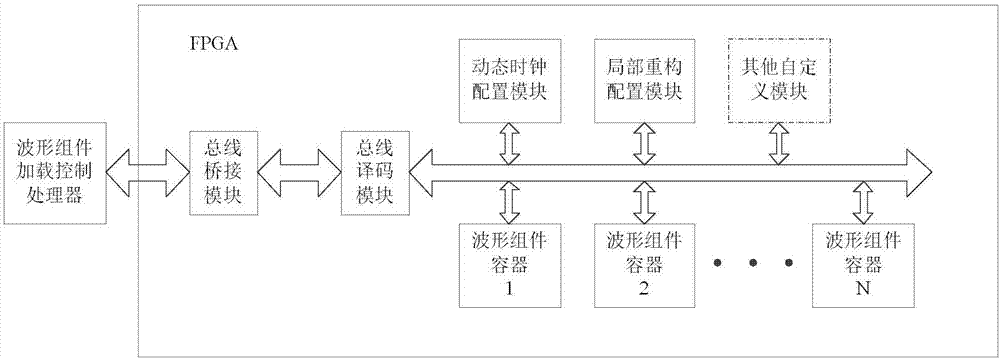

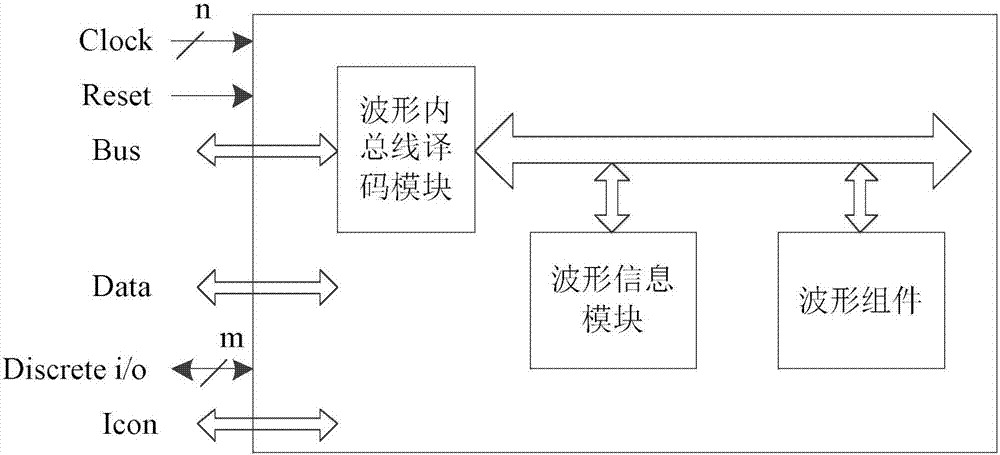

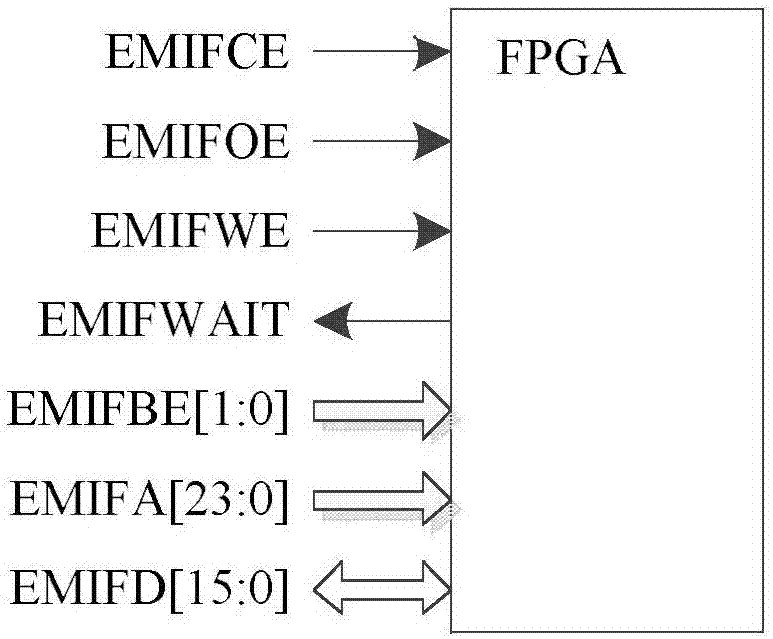

Local dynamic reconfigurable system for multi-waveform operation

InactiveCN106886505AReduce complexitySimplified volumeCAD circuit designArchitecture with single central processing unitComponent LoadCommunications system

The invention discloses a local dynamic reconfigurable system for multi-waveform operation and aims to provide the local dynamic reconfigurable system capable of lowering the power consumption, complexity and size of an integrated communication system. According to the technical scheme, a bus bridging module and a bus decoding module connected with each other through an FPGA internal bus are set in an FPGA, and a waveform component loading control processor writes waveform component container data needing to be loaded into a local reconfiguration configuration module mounted on an FPGA internal bus mounting interface through the bus bridging module and the bus decoding module; and the bus decoding module is connected with a clock management unit CMT generating different work clocks and netlist files containing all waveform component containers of waveform components through mounting interfaces, integrated software provided by the Xilinx company is adopted to integrate all the netlist files to generate a code stream file, the code stream file is converted into binary data, and therefore waveform component data used for dynamic loading is obtained.

Owner:10TH RES INST OF CETC

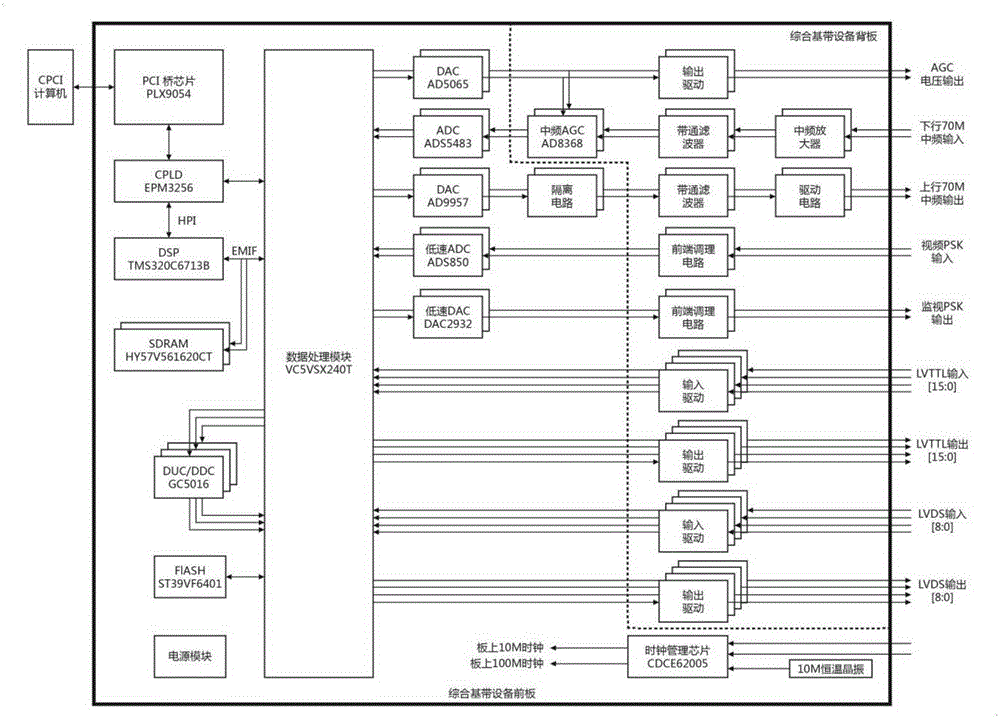

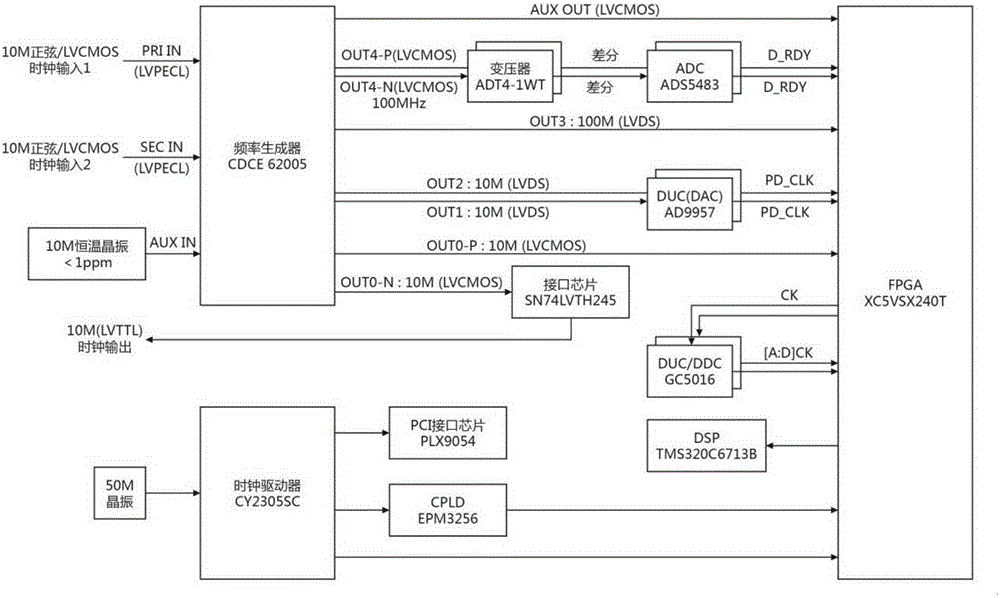

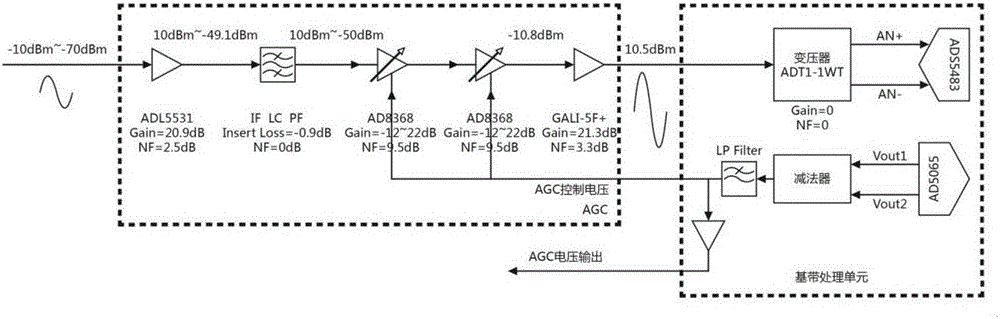

Base-band device based on software radio

InactiveCN105278404AIncrease opennessIncrease flexibilityProgramme controlComputer controlMulti bandMulti protocol

The purpose of the invention is to provide a base-band device based on software radio. The technical scheme of the invention includes two paths of 70M uplink sending channels, two paths of 70M downlink reception channels, two paths of PSK reception channels, two paths of PSK sending channels, LVTTL level input and output interfaces for test, a clock management unit, a data processing module, a PCI interface module, a CPLD logic module, an expanding RAM module, digital up conversion / down conversion modules, a FLASH module and a power supply module. The base-band device is connected to a CPCI computer through an PCI interface chip. A PCI bus protocol is converted to a local bus protocol. Address decoding is carried out on local bus signals output by the PCI interface chip through CPLD. A PCI bus finishes accessing the interface through the CPLD, and finishes downloading programs, so that the computer can update firmware programs through the PCI interface. The multifunctional communication of multi-band frequency, multi-mode, multi-channel, multi-speed, and multi-protocol is realized, and thus a good and flexible software radio system platform is constructed.

Owner:广州北航新兴产业技术研究院

System for collecting motion information of lift car

The invention discloses a system for collecting the motion information of a lift car. The system for collecting the motion information of the lift car comprises an acceleration module, a Flash chip, a real-time clock management unit and a single-chip microcomputer MCU, wherein the acceleration module completes collection of original data once within a certain time and sum and average the data of a specified number of points, and the average is used as a sample point; the Flash chip stores the statistics data of a lift; the real-time clock management unit provides a clock interface for the system; and the single-chip microcomputer MCU analyzes the motion information of the lift car according to acceleration information. According to analysis of the single-chip microcomputer MCU, during upward (downward) movement, when the negative (positive) amplitude value of the sample point exceeds the upward (downward) movement threshold, negative (positive) acceleration gradual increase is determined, and the lift moves upwards (downwards) and accelerates at the moment; then, whether the negative (positive) amplitude value of the sample point exceeds the upward (downward) movement threshold or not is judged, if yes, positive (negative) acceleration gradual change is determined, and the lift moves upward (downward) and decelerates at the moment; and finally, whether the lift meets a stopping condition or not is judged, and if yes, one upward (downward) movement process is ended.

Owner:DALIAN ALLRUN ELECTRONICS +1

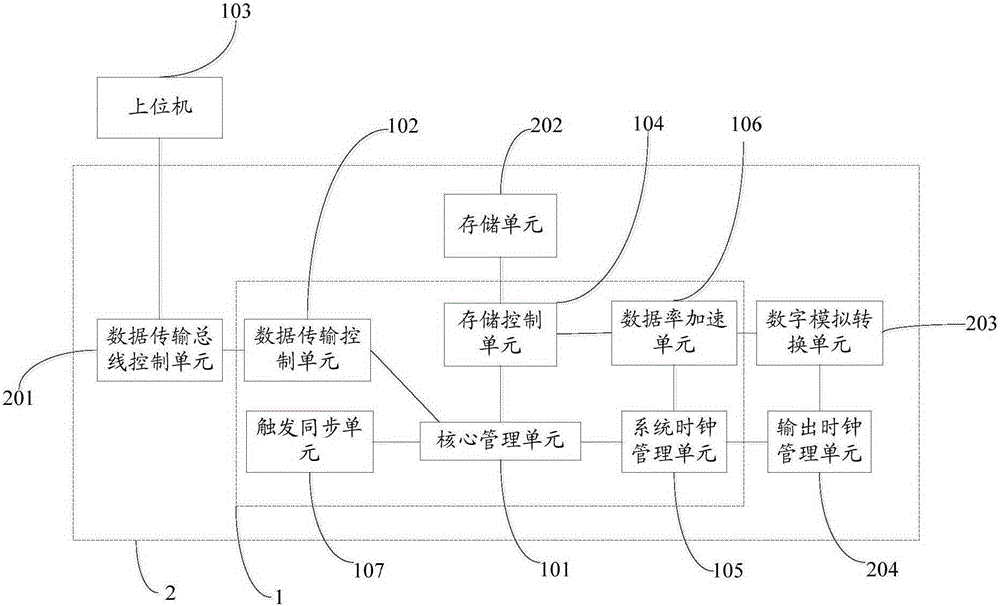

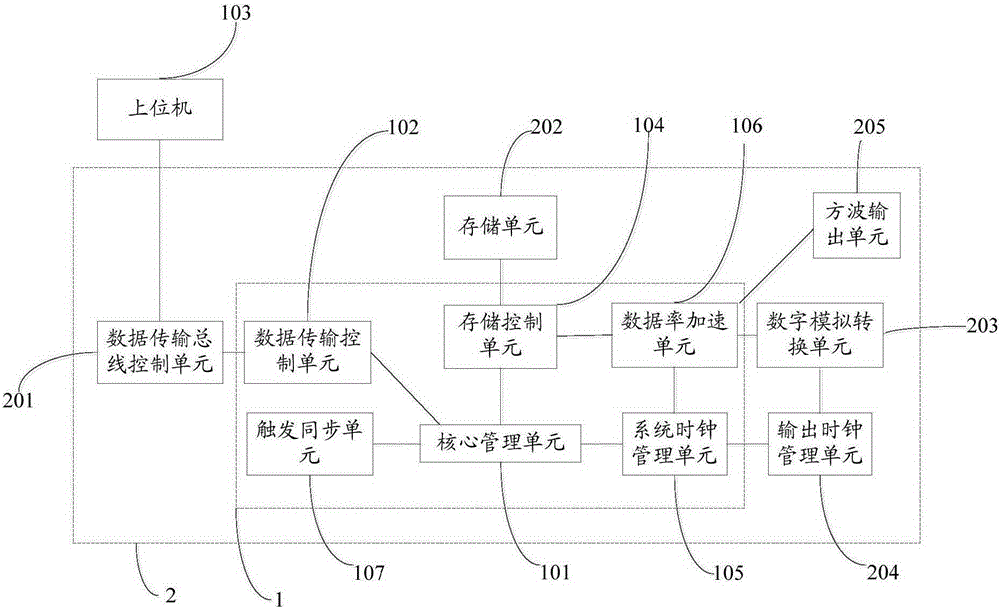

Waveform generating device and method

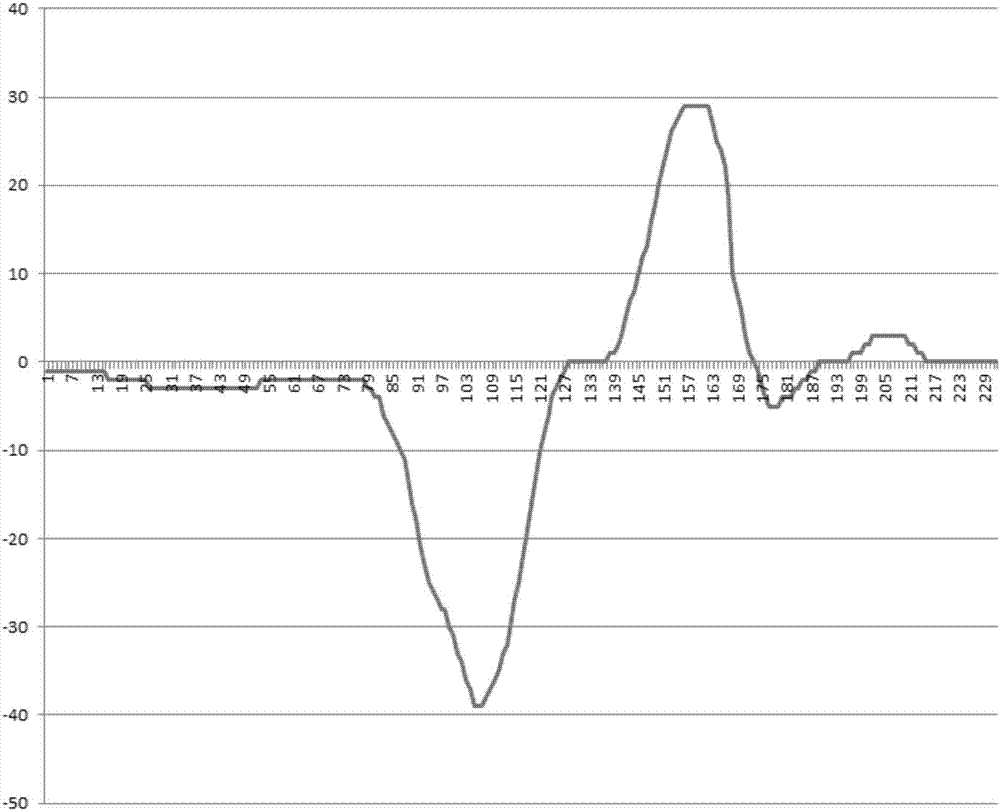

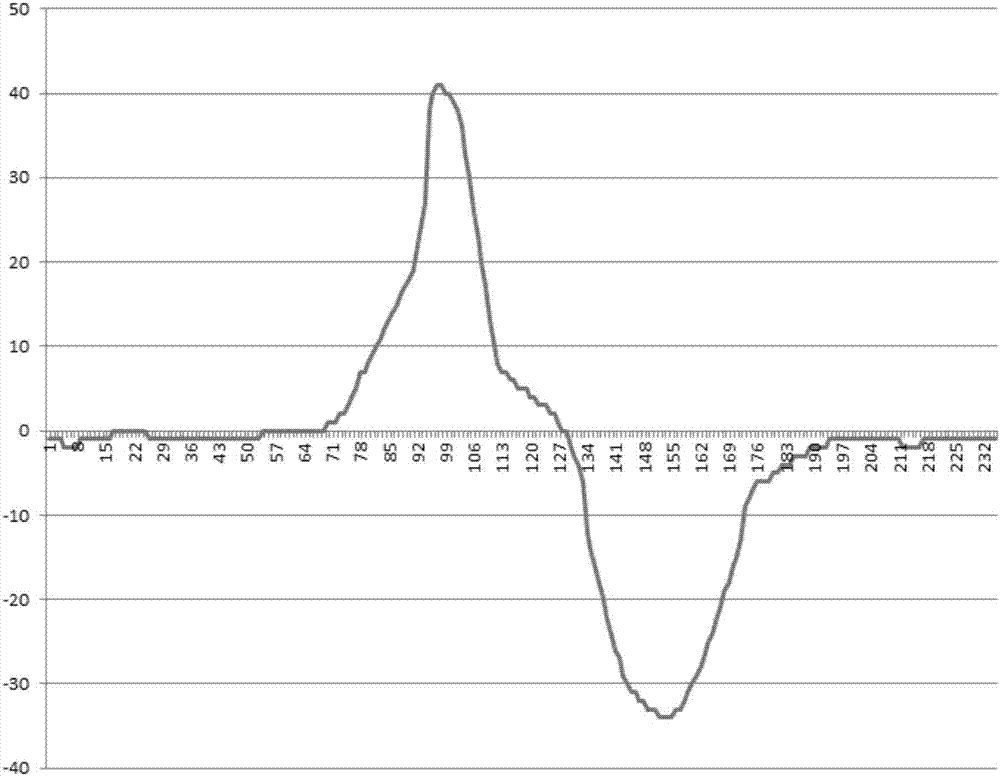

ActiveCN105162437AIncrease flexibilityHigh Speed Digital Waveform GenerationElectric pulse generator circuitsDigital function generatorsManagement unitData rate

The application discloses a waveform generating device and method. The waveform generating device comprises a waveform generating management module based on a FPGA (Field Programmable Gate Array) and a peripheral circuit expansion module. The waveform generating management module comprises a core management unit, a data transmission control unit, a storage control unit, a system clock management unit and a data rate acceleration unit, wherein the data transmission control unit is connected to the core management unit; the storage control unit is connected to the core management unit; the system clock management unit is connected to the core management unit; and the data rate acceleration unit is used for outputting waveform data at an accelerated output rate. The peripheral circuit expansion module comprises a data transmission bus control unit, a storage unit, a digital-analog conversion unit and an output clock management unit. The invention is high in flexibility and can achieve a high-speed digital waveform generation and control function.

Owner:UNIV OF SCI & TECH OF CHINA

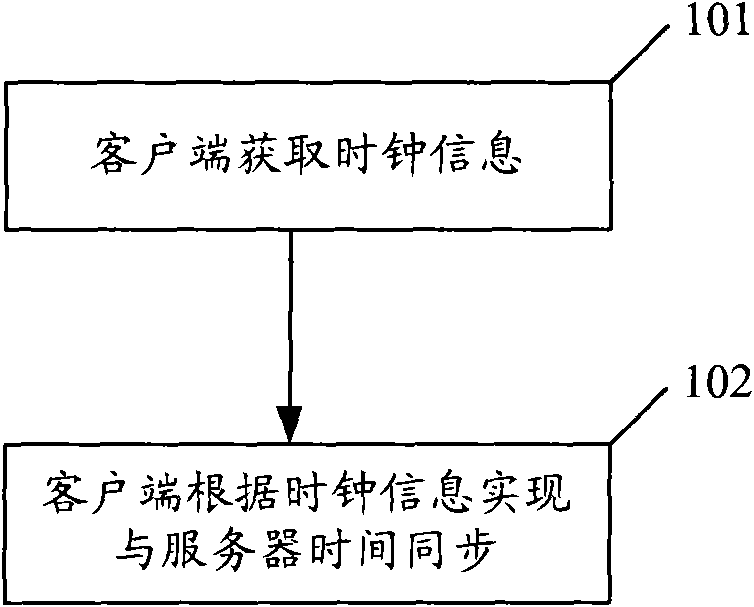

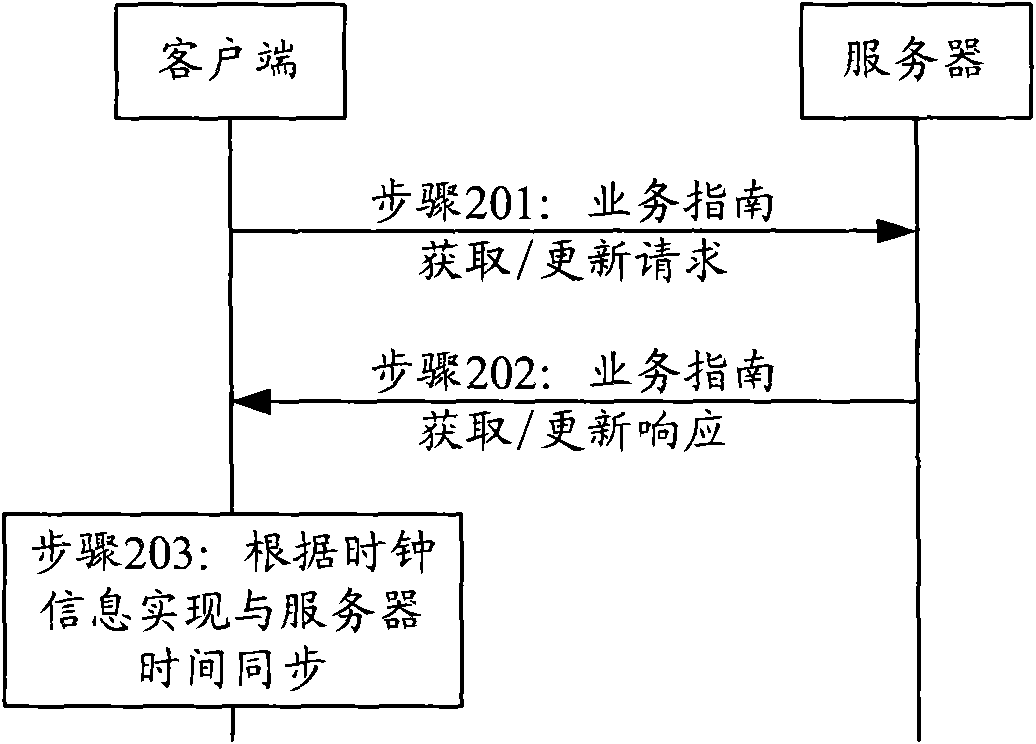

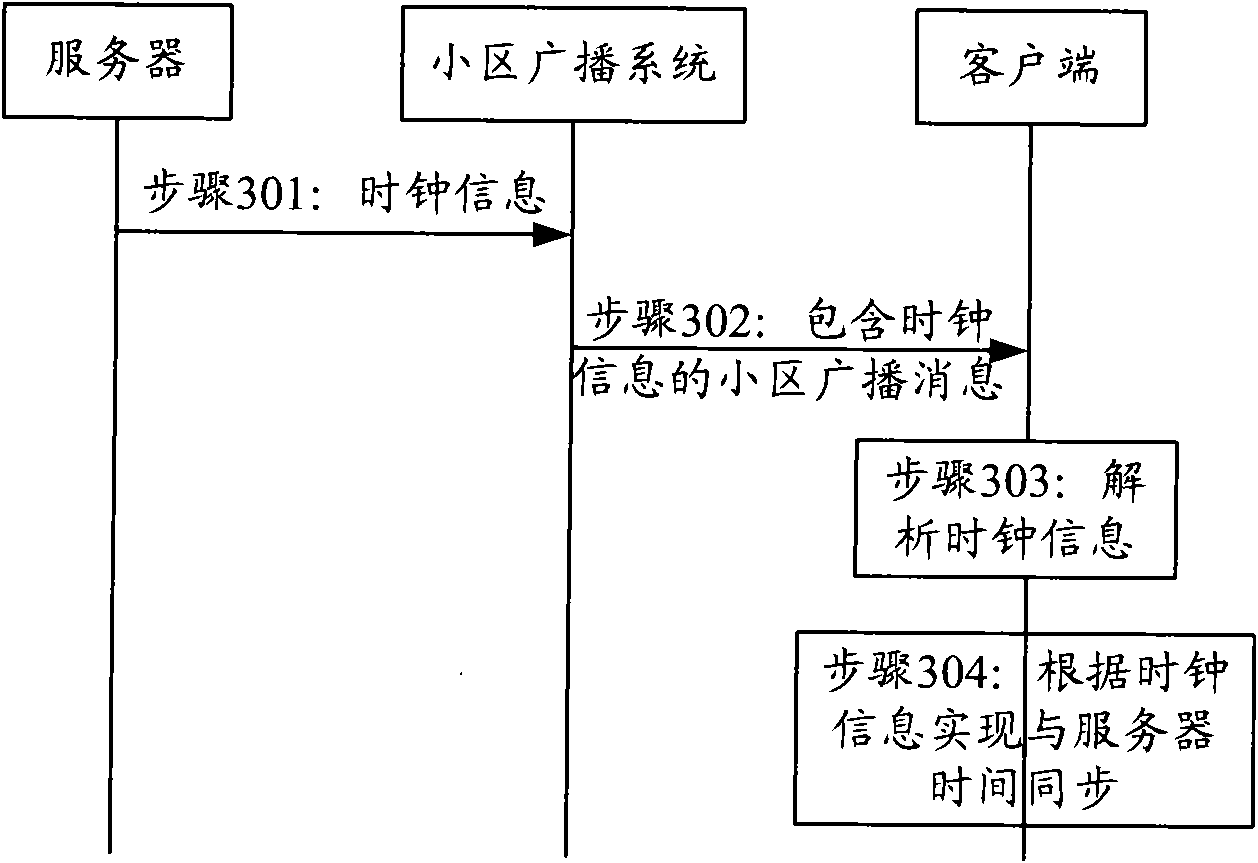

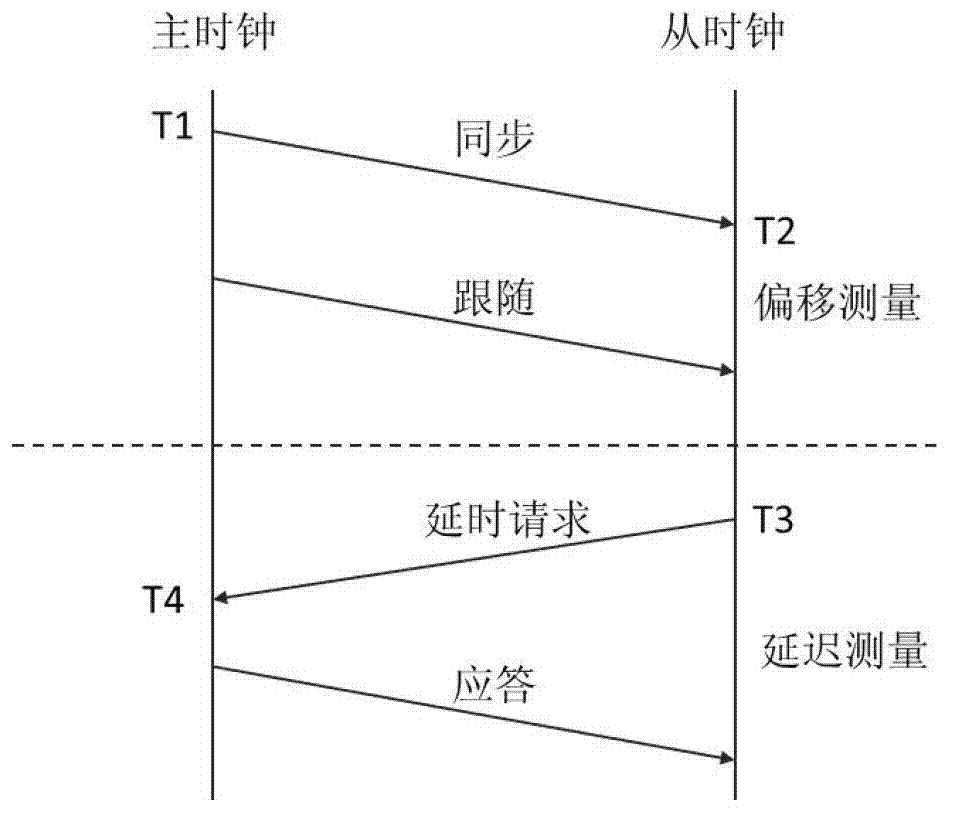

Time synchronization method, time synchronization device and time synchronization system

InactiveCN101656606ATime synchronizationImprove experienceSpecific information broadcast systemsTime-division multiplexData synchronizationClient-side

The embodiment of the invention discloses a time synchronization method, a time synchronization device and a time synchronization system. The time synchronization method comprises the following stepsthat: a client acquires clock information; and the client realizes time synchronization with a server according to the clock information. The client comprises a clock information acquisition unit anda clock management unit, wherein the clock information acquisition unit is used for acquiring the clock information, and the clock management unit is used for realizing the time synchronization with the server according to the clock information acquired by the clock information acquisition unit. In the embodiment of the invention, the client acquires the clock information and realizes the time synchronization with the server according to the clock information, so the time of the client and the time of the server can be kept synchronous so as to keep the time of a user and the time of the server synchronous and further strengthen the experience of the user.

Owner:HUAWEI TECH CO LTD

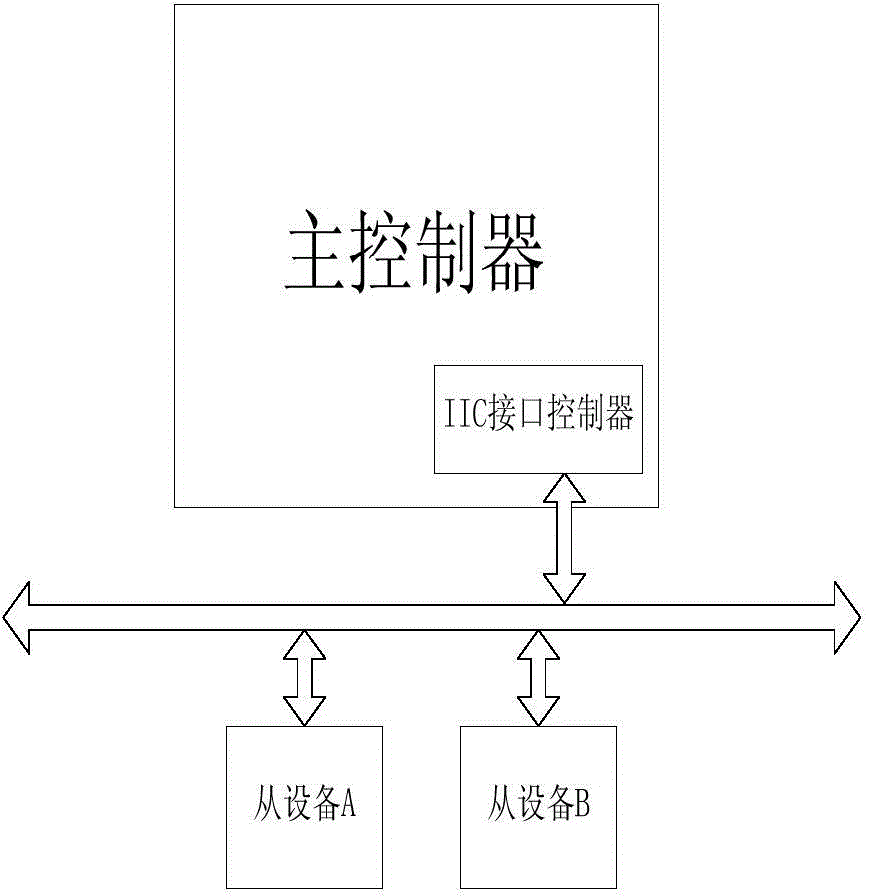

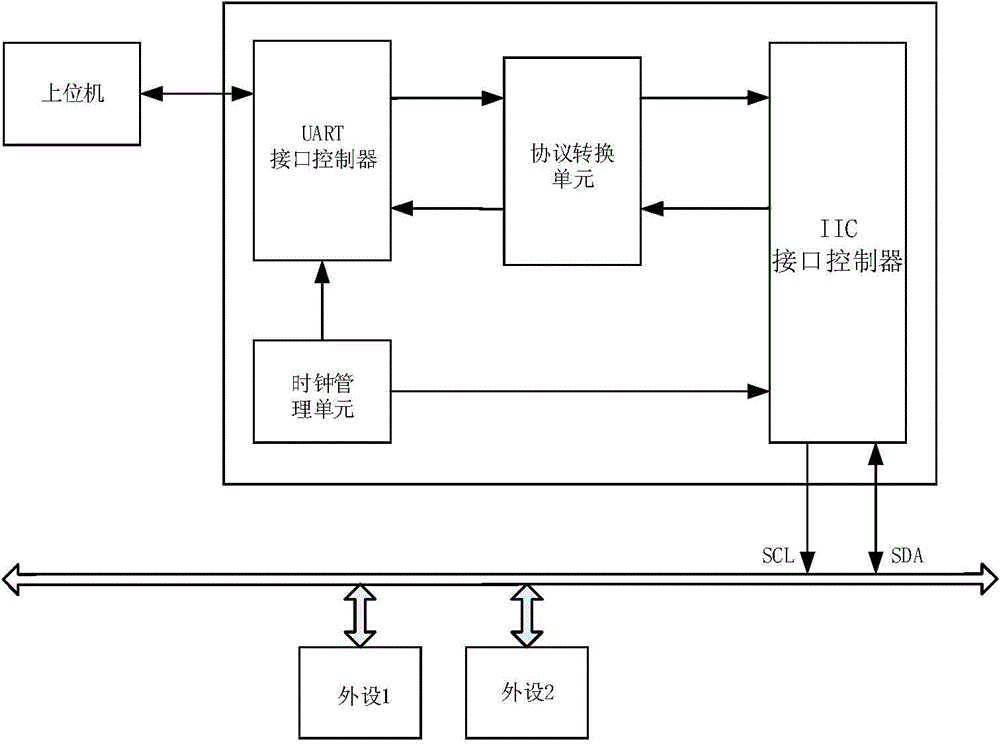

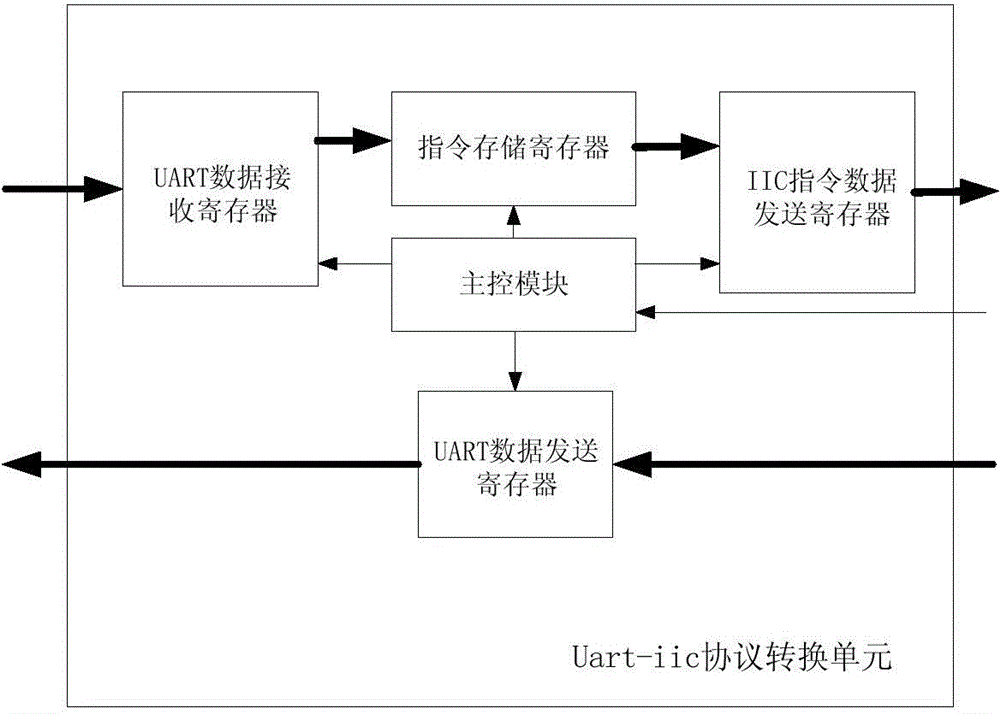

IIC bus experimental facility debugged by serial port

InactiveCN104407956ASave resourcesSimple operation instructionsError detection/correctionProcessor registerBus interface

Owner:TIANJIN UNIV

Method of performing dynamic voltage and frequency scaling operation, application processor performing method, and mobile device comprising application processor

ActiveUS9541992B2Prevent unnecessary power consumptionEnergy efficient ICTPower supply for data processingProcessing elementMobile device

A method of performing a dynamic voltage and frequency scaling operation comprises controlling a clock management unit (CMU) to predict an operating state of a central processing unit (CPU) and to provide operating frequency information to a power management integrated circuit (PMIC) based on the predicted operating state of the CPU, the operating frequency information indicating a change of an operating frequency of an application processor, and controlling the PMIC to change an operating voltage of the application processor based on the operating frequency information provided from the clock management unit.

Owner:SAMSUNG ELECTRONICS CO LTD

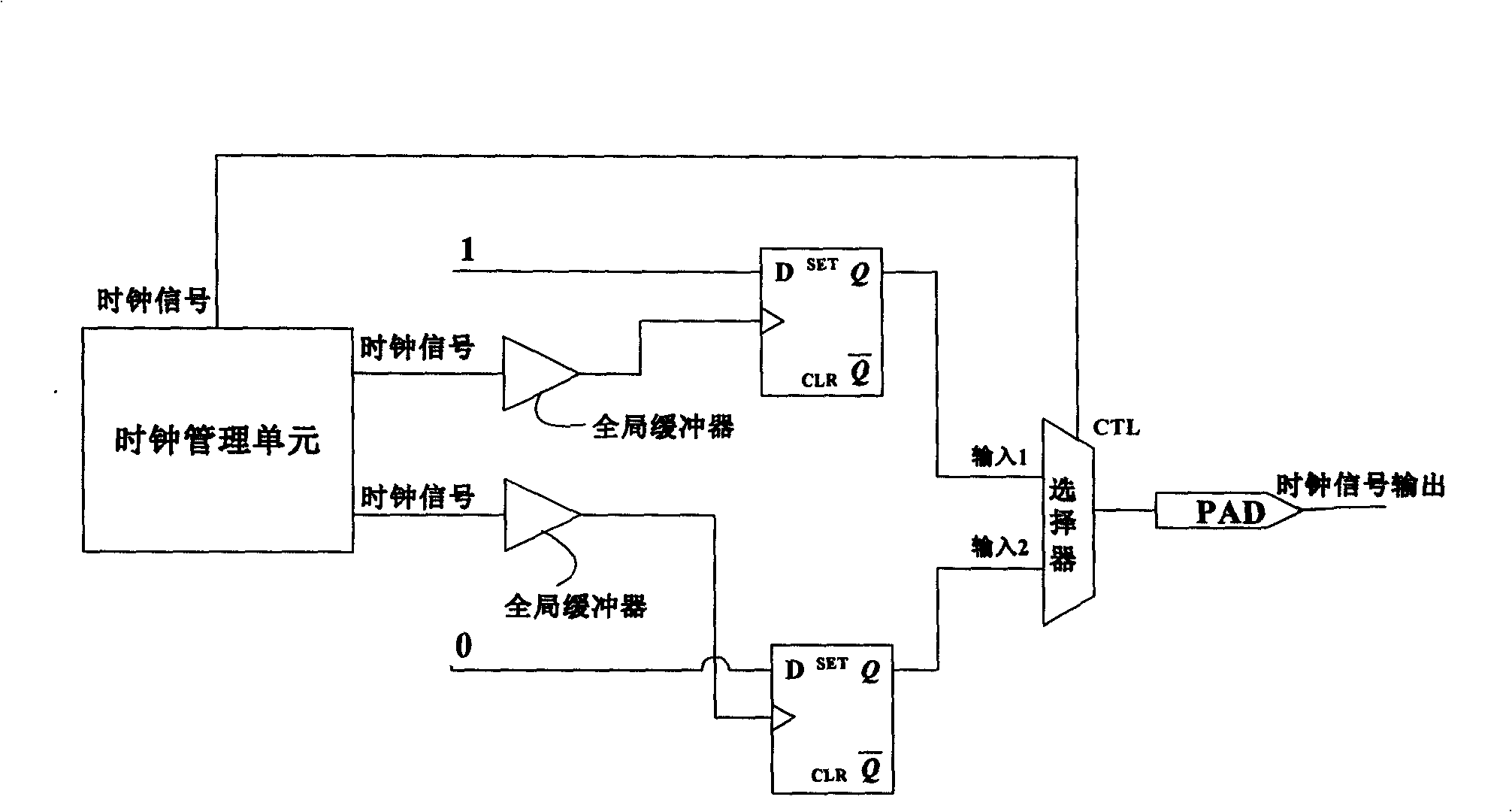

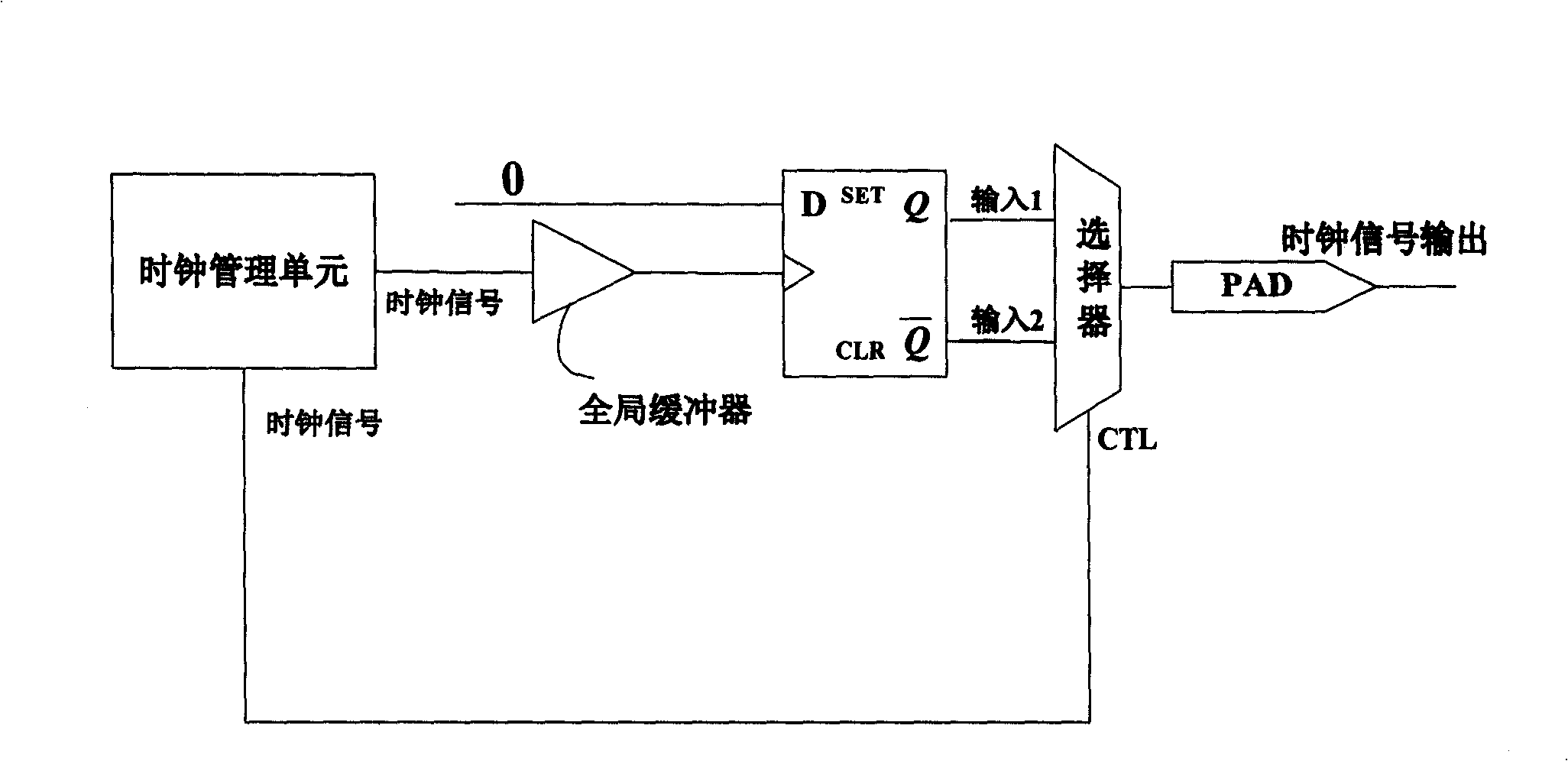

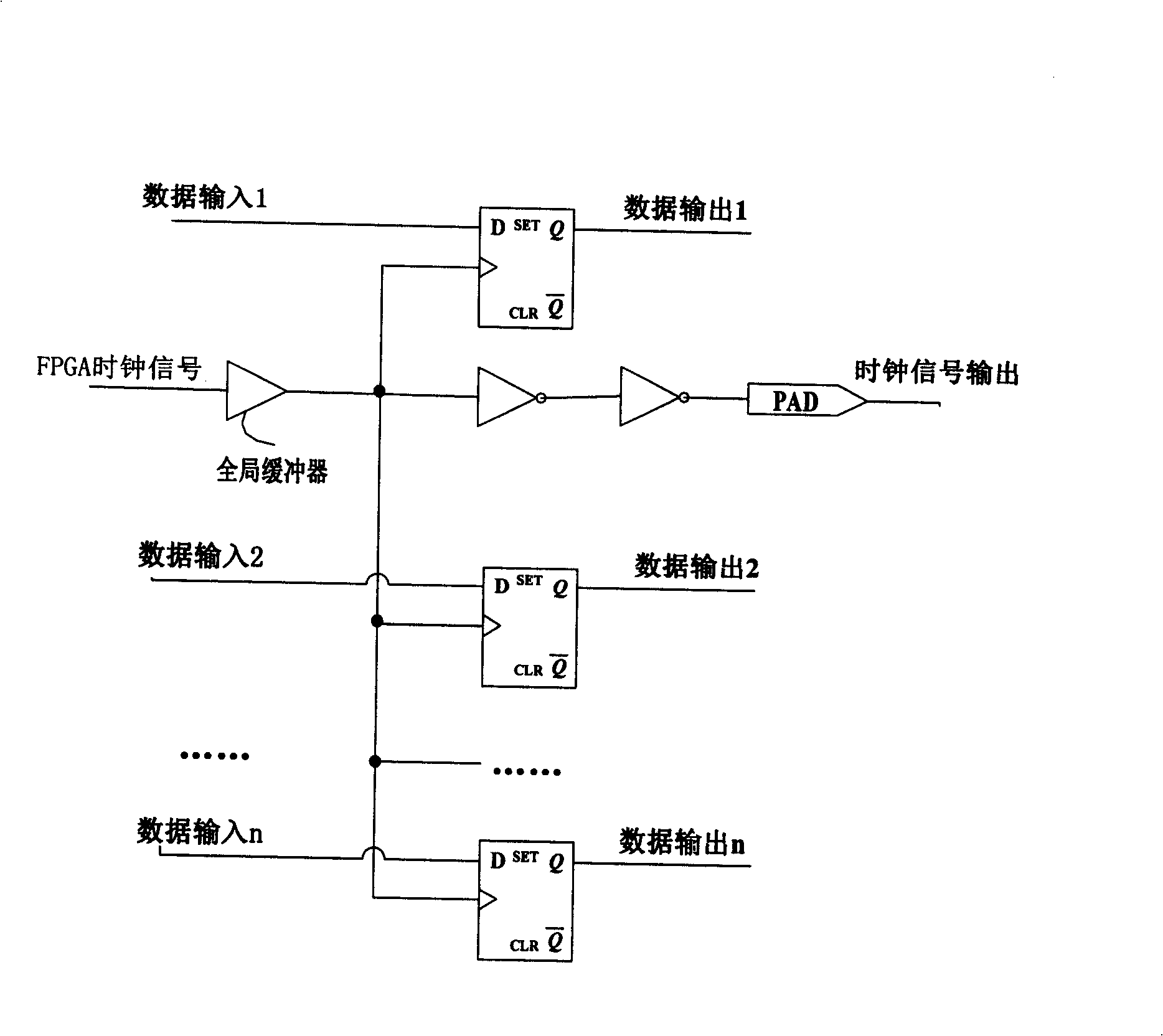

Output circuit for FPGA clock signal and processing method thereof

InactiveCN101355359AReduce the impactWon't collapseLogic circuits using elementary logic circuit componentsControl signalClock tree

The invention discloses an FPGA clock signal output circuit, comprising a clock management unit and a global buffer, wherein a clock signal generated by the clock management unit is distributed by the global buffer; moreover, the FPGA clock signal output circuit also comprises a trigger unit and a selector, the end of the clock signal of the trigger unit is connected with the output end of the global buffer, a data input signal of the trigger unit is a constant logic signal, the trigger unit provides a positive output signal and a negative output signal to the end of the input signal of the selector, the control input end of the selector is connected with the end of the clock signal outputted by the clock management unit, and the selector outputs the clock signal to an output pin of the FPGA. The FPGA clock signal outputted by the circuit reduces the delay, and lowers the negative influence of the external load on an internal clock tree of the FPGA.

Owner:VIMICRO CORP

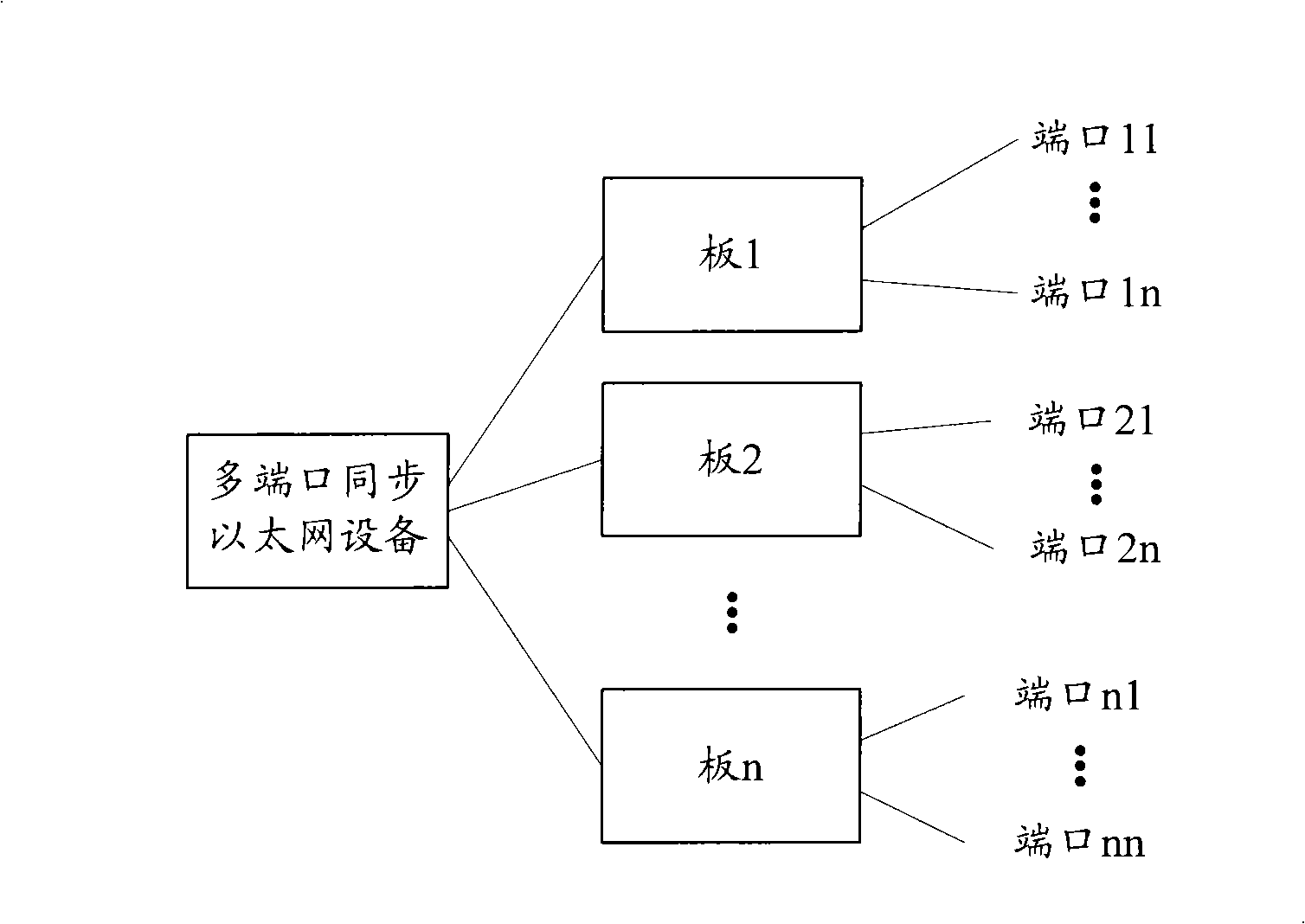

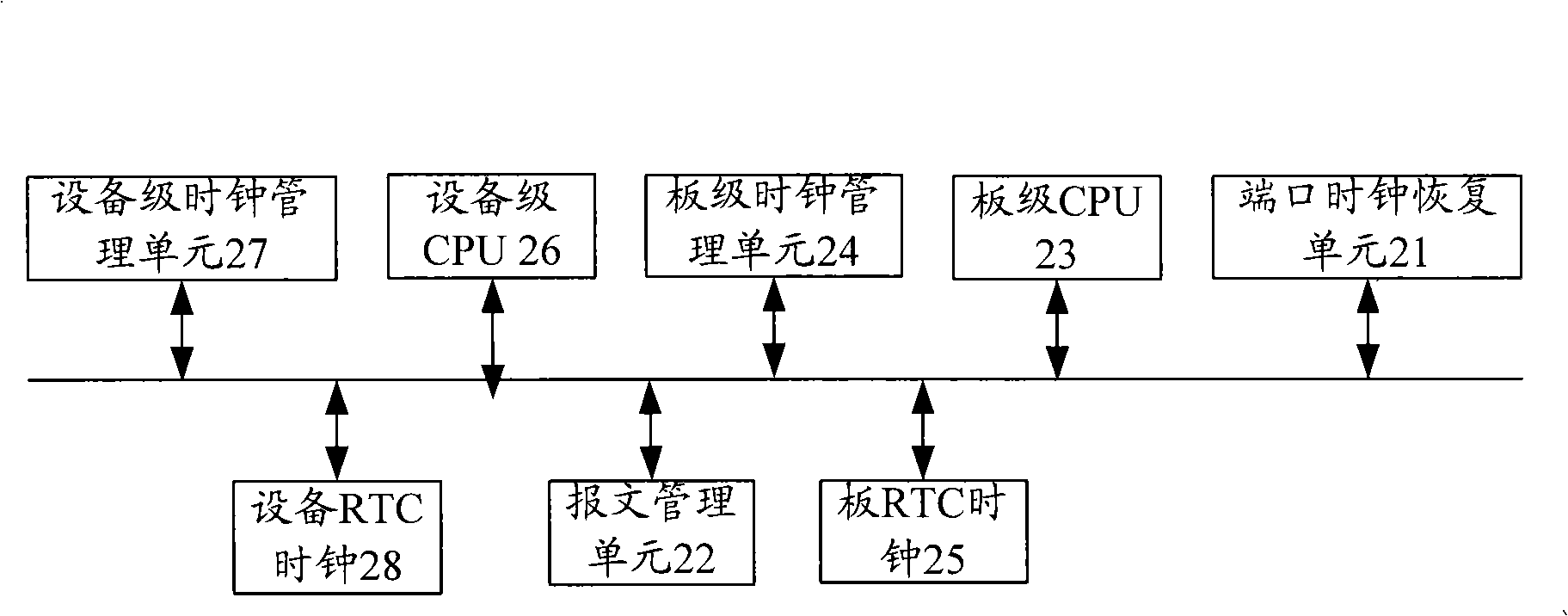

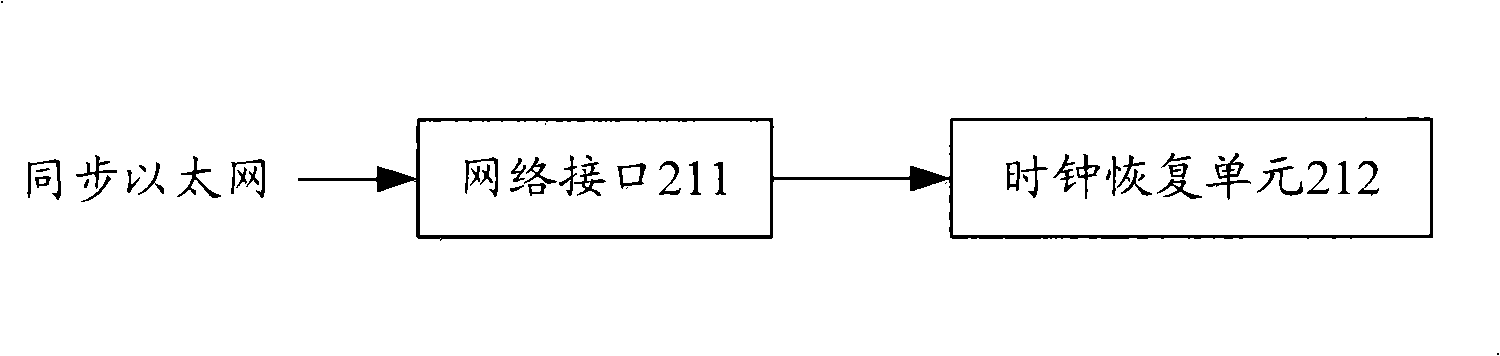

Clock synchronization method and system of multiport synchronization Ethernet equipment

ActiveCN101296070AHigh precisionThe precision level determines that the clock precision is highData switching by path configurationSynchronising arrangementReal-time clockEthernet

The invention discloses a clock synchronization method for a multiport synchronization Ethernet device, which comprises the following steps: slave ports and master ports are determined according to the clock resumed from each port and real time clock (RTC) of boards is used for synchronizing the RTC of each master port on the boards after using the clock of the slave ports to synchronize the clock of the boards; slave boards and master boards are determined according to the RTC of each board and the clock of the slave boards is used for synchronizing the RTC of the device and the RTC of the device is transmitted to the boards; the boards synchronize the RTC of the boards according to the RTC of the device and the RTC of the boards after the synchronization is used for synchronizing the clock of each port on the boards. Meanwhile, the invention discloses a clock synchronization system of the multiport synchronization Ethernet device, which comprises a port clock resuming unit, a board level CPU, a board level clock management unit, a device level CPU and a device level clock management unit. The utilization of the invention can realize the synchronization of all clocks of the multiport synchronization Ethernet device.

Owner:ZTE CORP

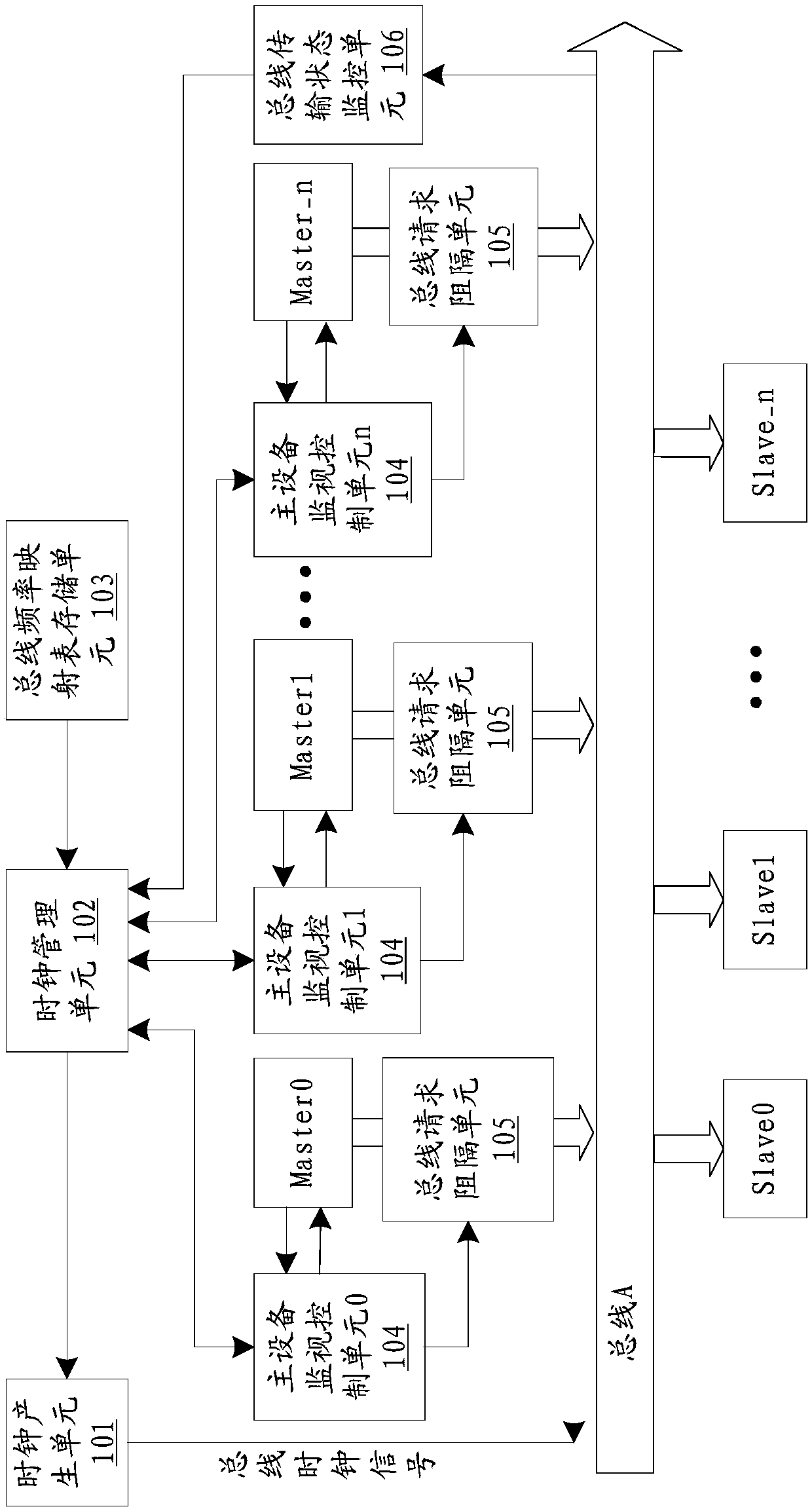

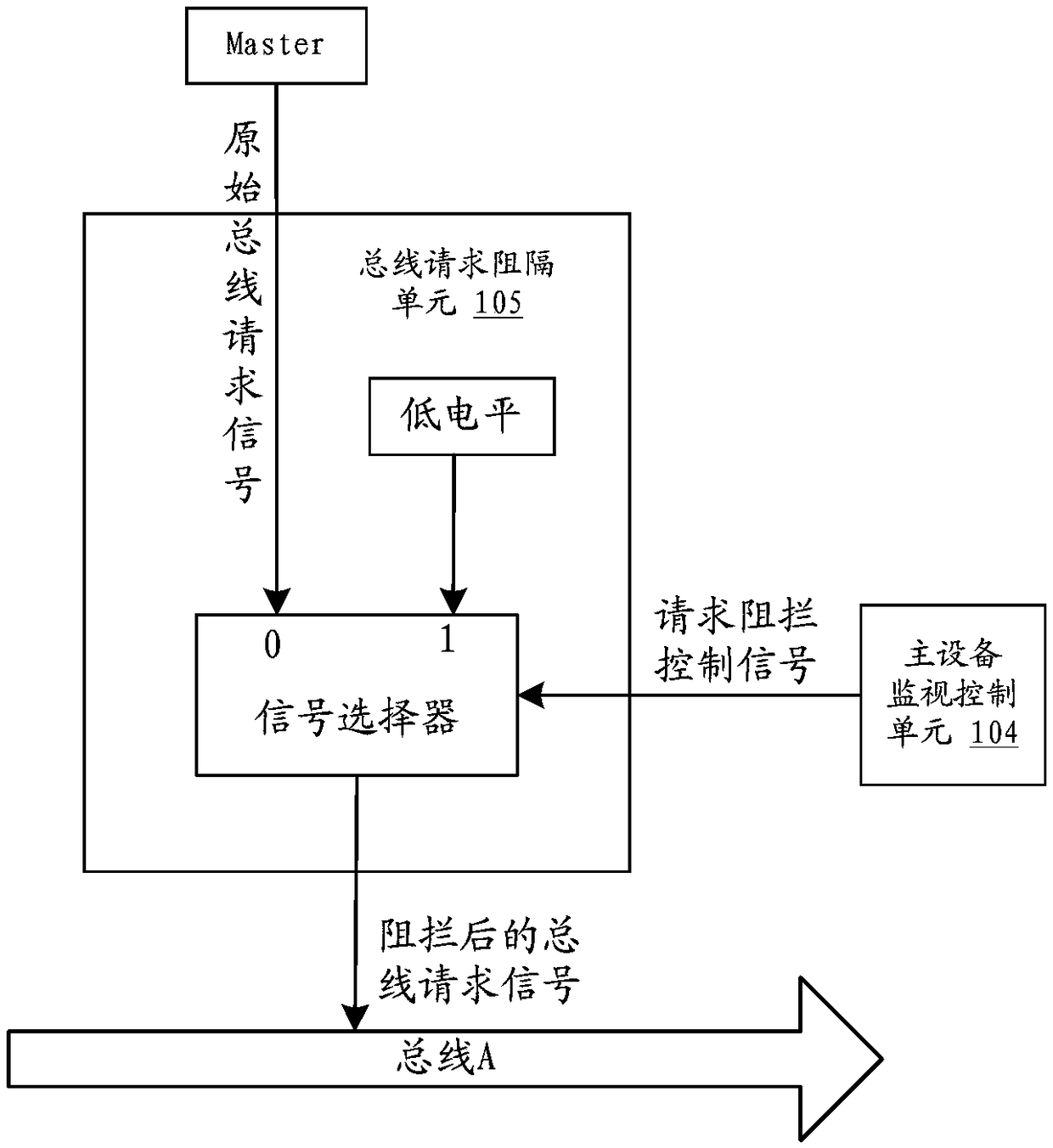

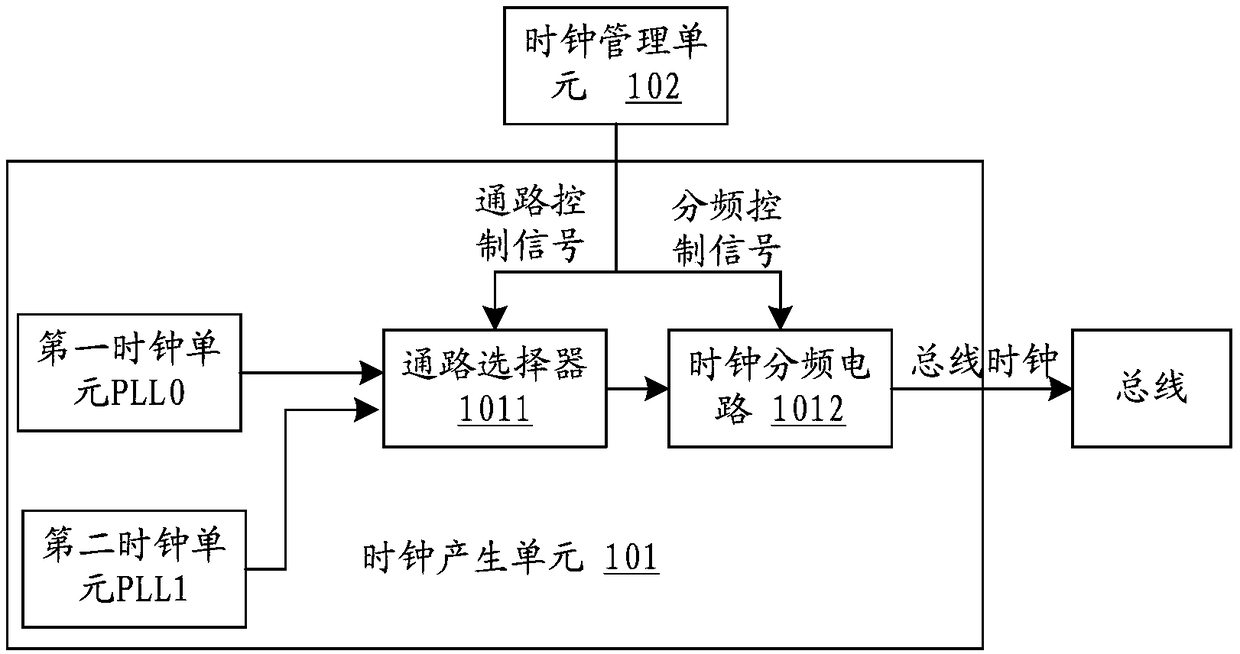

SOC chip bus dynamic multi-level frequency adjustment circuit and method

ActiveCN108845911AControl frequencyMonitor load in real timeHardware monitoringArchitecture with single central processing unitBusiness efficiencyFrequency conversion

The invention provides a SOC chip bus dynamic multi-level frequency adjustment circuit and method. The circuit comprises a clock generation unit, a clock management unit, a bus frequency mapping tablestorage unit, master device monitoring control units, bus request blocking units and a bus transmission state monitoring unit. The bus frequency mapping table storage unit stores a multi-level bus frequency mapping table which presets the bus frequency corresponding to working scenes of the master devices. The clock management unit receives a working state of each master device sent from each master device monitoring control unit and an idle state of the entire bus sent from the bus transmission state monitoring unit, and controls relevant units such as the clock generation unit to complete abus dynamic frequency conversion process according to the working state of the master device, or controls the clock generation unit to turn off the clock of the entire bus according to the idle stateof the entire bus. Thus, the frequency of the bus can be adjusted dynamically in time to adapt to the current bus load, and the best energy efficiency ratio can be obtained.

Owner:FUZHOU ROCKCHIP SEMICON

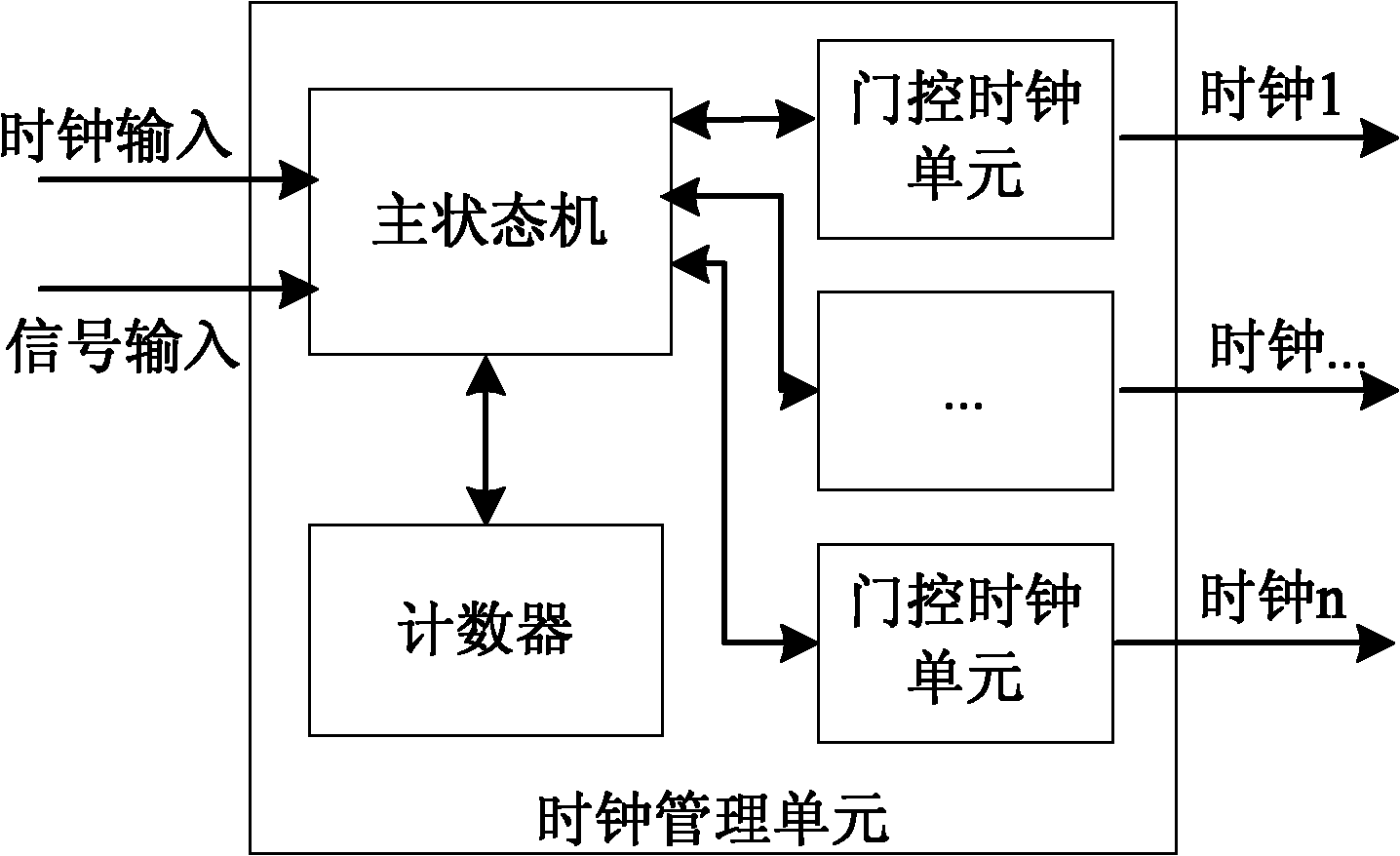

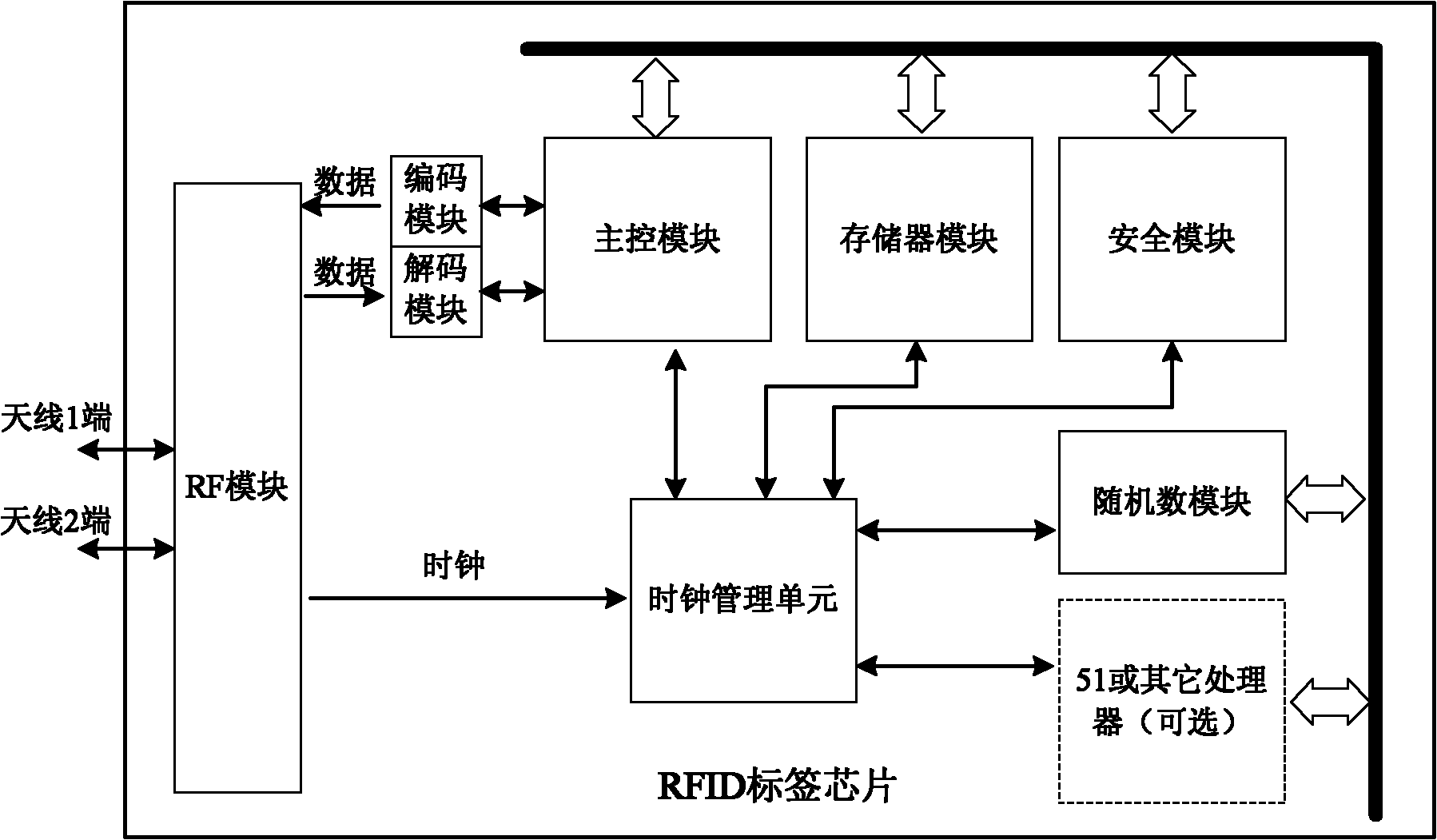

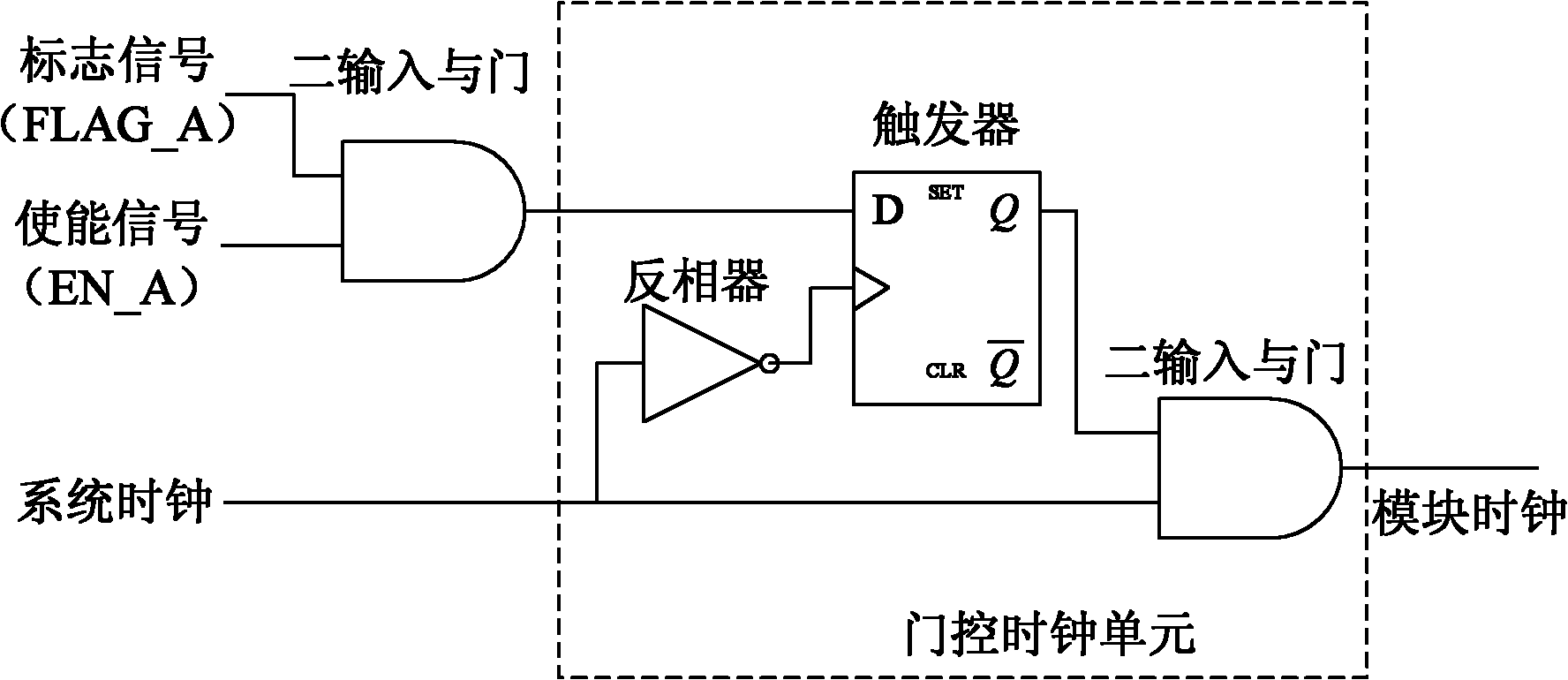

Clock management unit of RFID tag chip

InactiveCN102156899AClose in timeEffectively staggeredRecord carriers used with machinesManagement unitProcessor register

The invention discloses a clock management unit of a RFID (radio frequency identification) tag chip which can reduce power consumption and peak power consumption of the RFID tag chip. The clock management unit of the RFID tag chip comprises a main state machine, a counter and a plurality of gating clock units, wherein the main state machine analyzes the state of each functional unit of the tag chip, judges moments when a plurality of functional units are woken at the same time and a plurality of operations are executed at the same time, and further judges which functional units are still unnecessary, sets a clock enable signal of the functional units which can be stopped to zero, and separates the operations of the plurality of functional units which are independent to each other and enable registers to turn over synchronously; the counter is used for helping control on the input signal, and helping the main state machine to move up some operations of the functional units which are independent to each other and enable registers to turn over synchronously for several clocks and delay some operations of the same for several clocks; the gating clock units are used for instantiating the enable signals and system clock signals of each functional unit, and taking the instantiated output clock as a control clock for controlling the action of each functional unit.

Owner:SHENZHEN ZHENGDONGYUAN TECH CO LTD

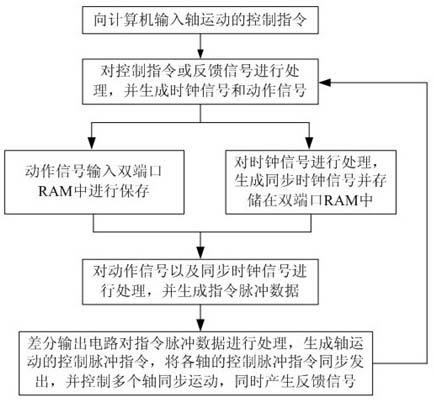

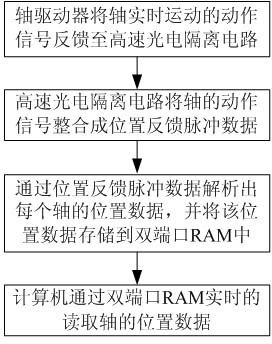

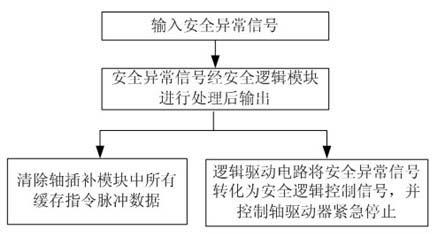

Multi-axis movement control method of industrial robot

ActiveCN102615647AControl Synchronized MotionRealize synchronized motionProgramme-controlled manipulatorEngineeringMovement control

The invention discloses a multi-axis movement control method of an industrial robot, and the method is characterized by comprising the following steps of: (1) obtaining current data of each axis of the industrial robot by a computer and utilizing the current data to generate a clock signal and a movement signal for controlling the next step of the movement of each axis of the industrial robot; (2) utilizing a clock managing unit to treat the clock signal to generate a synchronous clock signal for controlling synchronous movement of each axis; (3) processing the synchronous clock signal and the movement signal through an interpolation module to generate a control pulse instruction for controlling the movement of each axis of the industrial robot; and (4) synchronously sending the control pulse instruction to a driver of each axis of the industrial robot to realize the synchronous movement of all the axes. According to the multi-axis movement control method disclosed by the invention, a plurality of axes of the industrial robot can be controlled for synchronous movement and instruction data for controlling the axial movement is corrected, so that the precision of the multi-axis synchronous movement can be better guaranteed; and therefore, the multi-axis movement control method is applicable to popularization and application.

Owner:CHENGDU CRP ROBOT TECH CO LTD

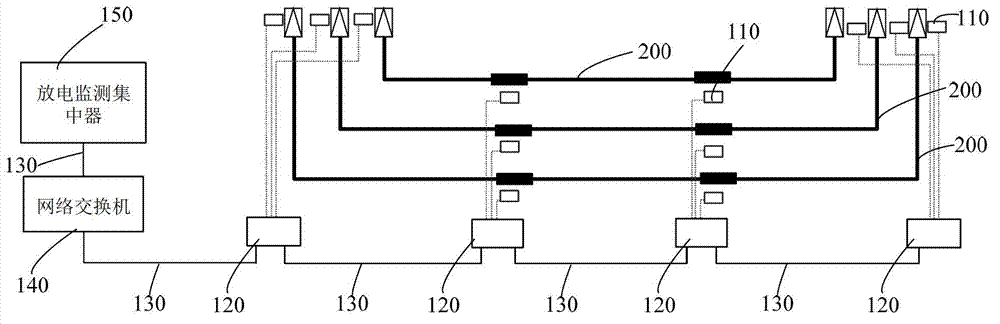

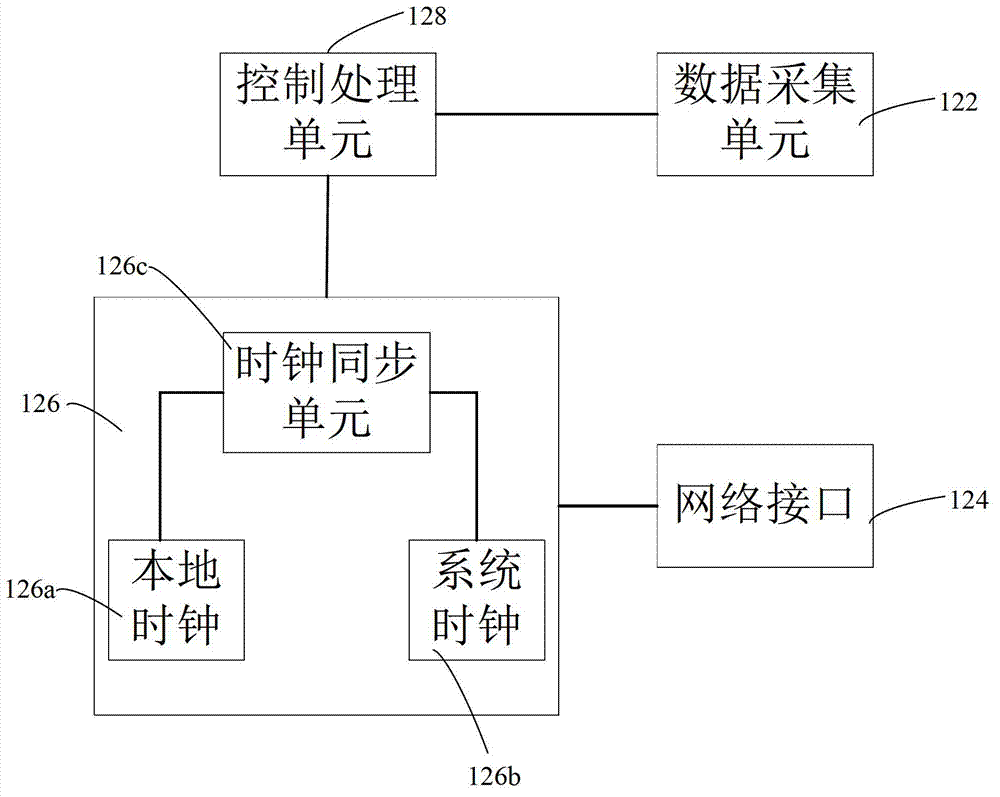

Online monitoring and positioning system for local discharge of high-voltage cable

The invention provides an online monitoring and positioning system for local discharge of a high-voltage cable. The online monitoring and positioning system comprises a plurality of sensors used for collecting discharge signals in different positions of the high-voltage cable, a plurality of monitoring terminals connected with the sensors, a network switch connected with the monitoring terminals and a discharge monitoring concentrator connected with the network switch. The monitoring terminals comprise a data acquisition unit connected with the sensors, a clock management unit, a plurality of network interfaces connected with the clock management unit, and a control processing unit connected with the data acquisition unit and the clock management unit. The control processing unit is connected with the network switch, and the monitoring terminals are connected via the network interfaces. The control processing unit is used for controlling the clock management unit by synchronizing a clock of the connected monitoring terminals via high-precision clock synchronization based on the IEEE 1588 protocol on a hardware time stamp. Therefore, the precision of synchronization of the clock of the connected monitoring terminals is high. By adopting the online monitoring and positioning system for local discharge of the high-voltage cable, the precision of finally obtained discharge source location data is high.

Owner:SUZHOU GUANGGE EQUIP

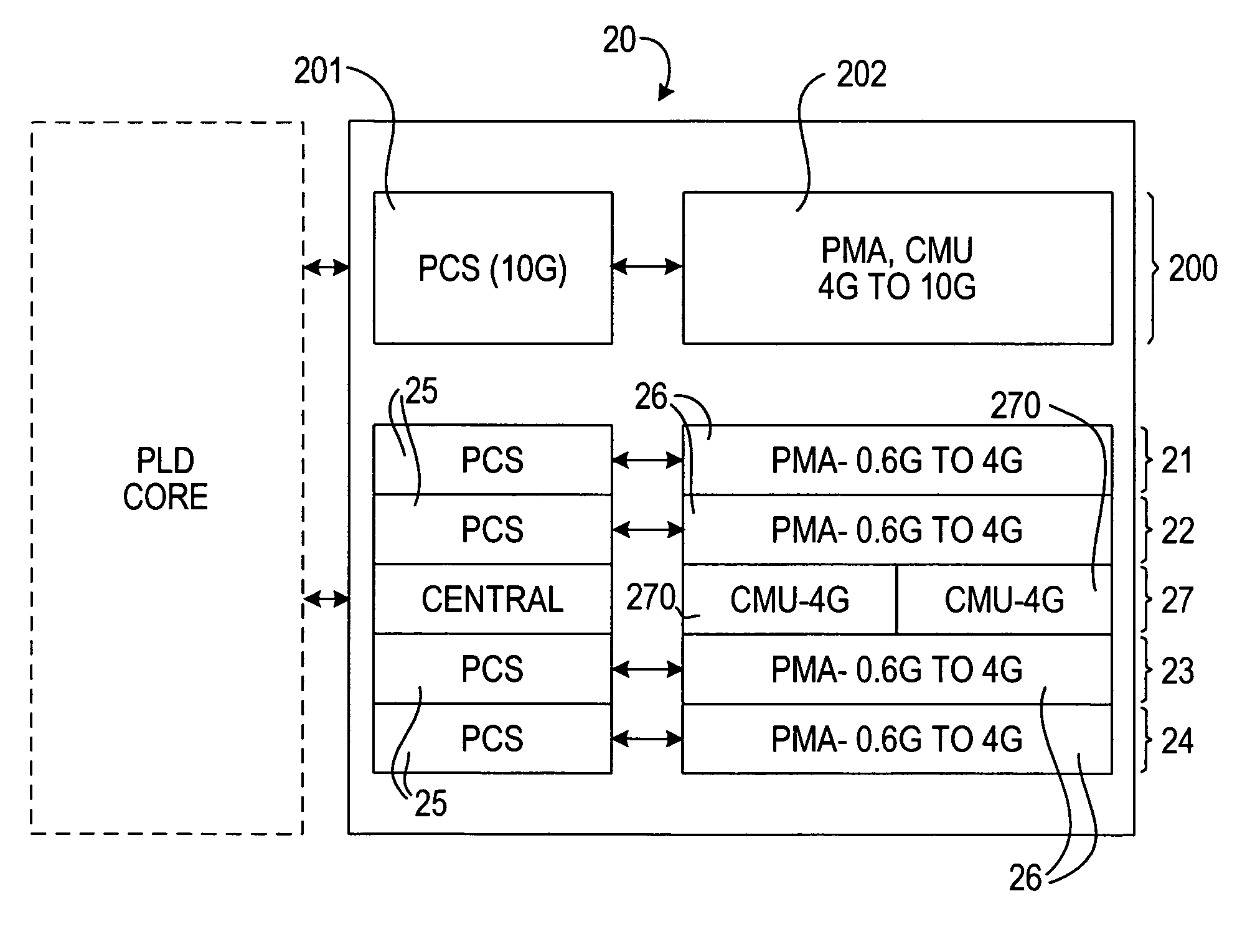

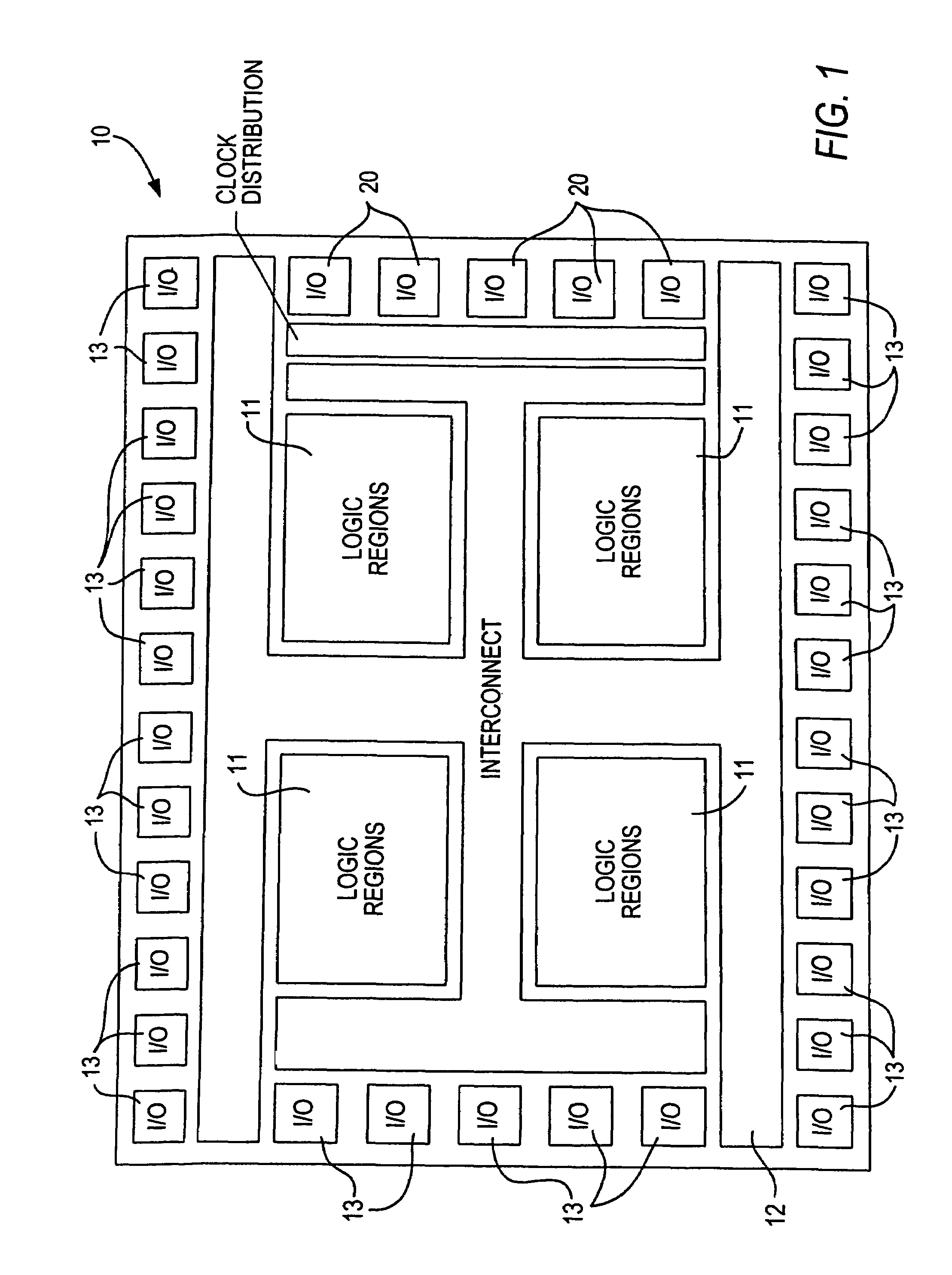

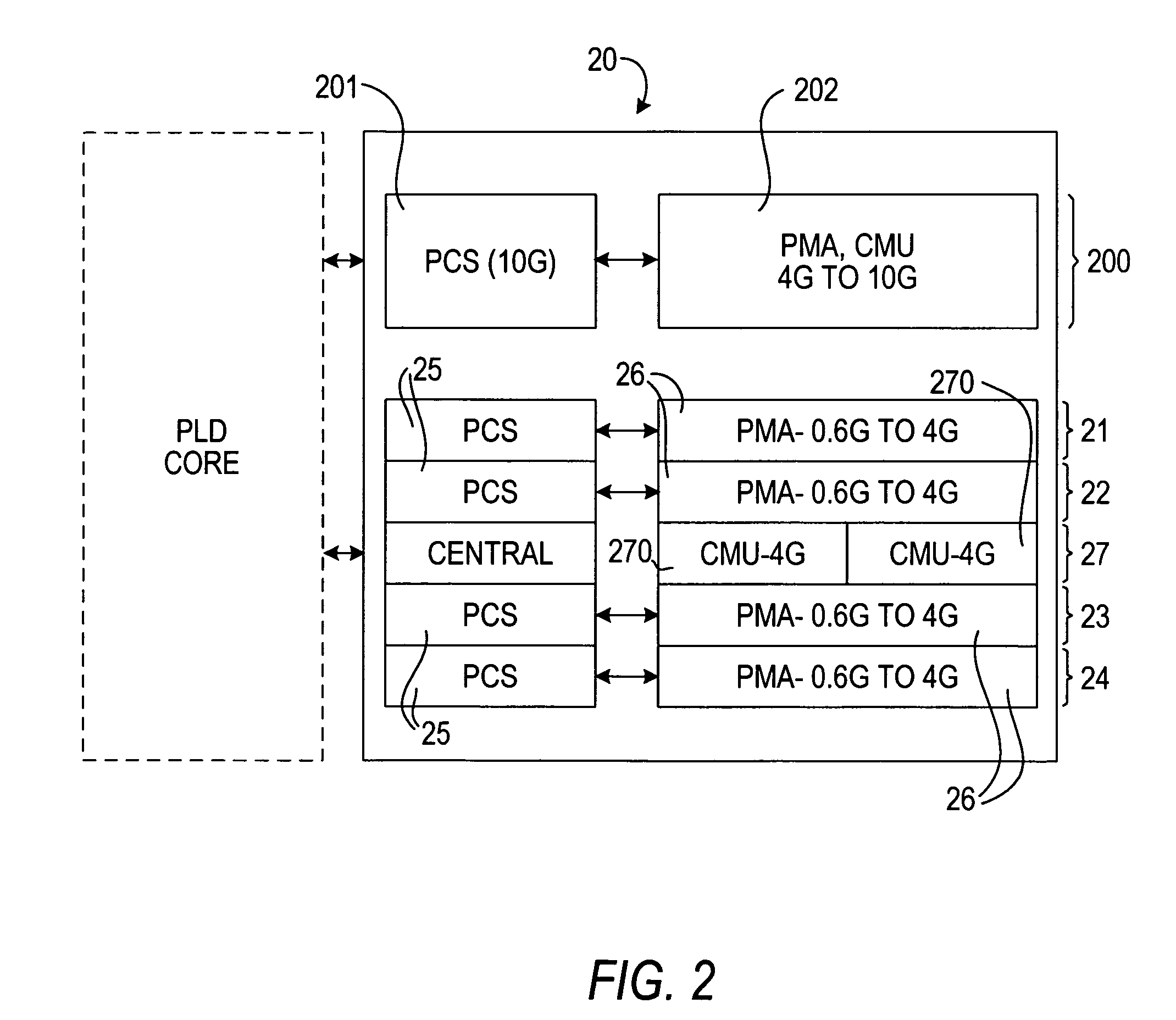

Multiple data rates in integrated circuit device serial interface

InactiveUS7698482B2Run at high speedReduce in quantityInput/output processes for data processingLogic circuitsLow speedProgrammable logic device

A serial interface for a programmable logic device supports a wide range of data rates by providing a first number of channels supporting a first range of data rates and a second number of channels supporting a second range of data rates. The first range of data rates is preferably lower than the second range of data rates and preferably the first number of channels is higher than the second number of channels which preferably is 1. For backward compatibility with existing devices, the first number of channels in each interface preferably is four. Each channel preferably includes a physical medium attachment module and a physical coding sublayer module. Each of the higher-speed channels in the second number of channels preferably also includes a clock management unit, while the lower-speed channels in the first number of channels preferably share one or more clock management units.

Owner:ALTERA CORP

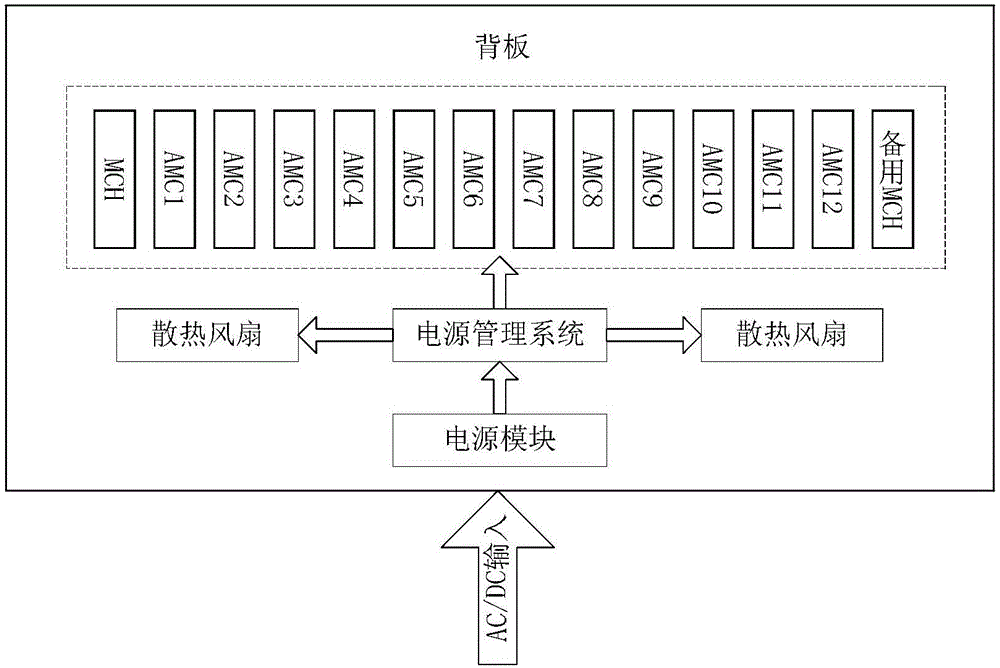

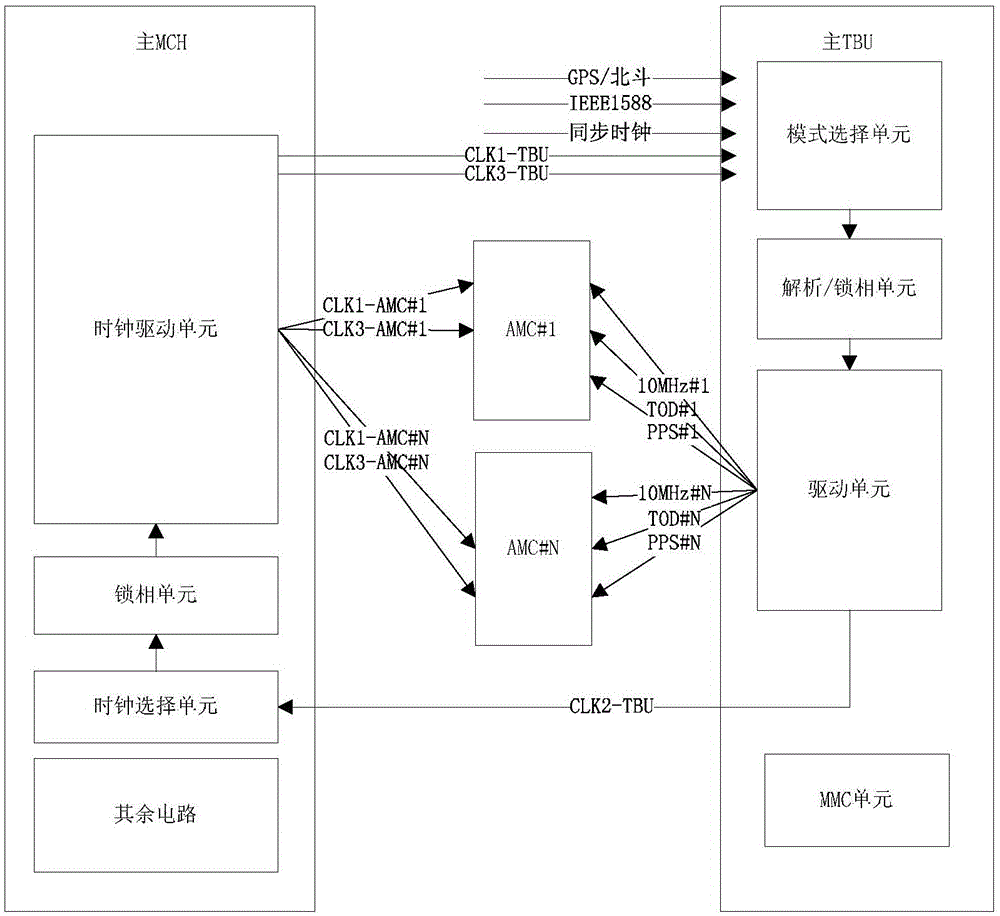

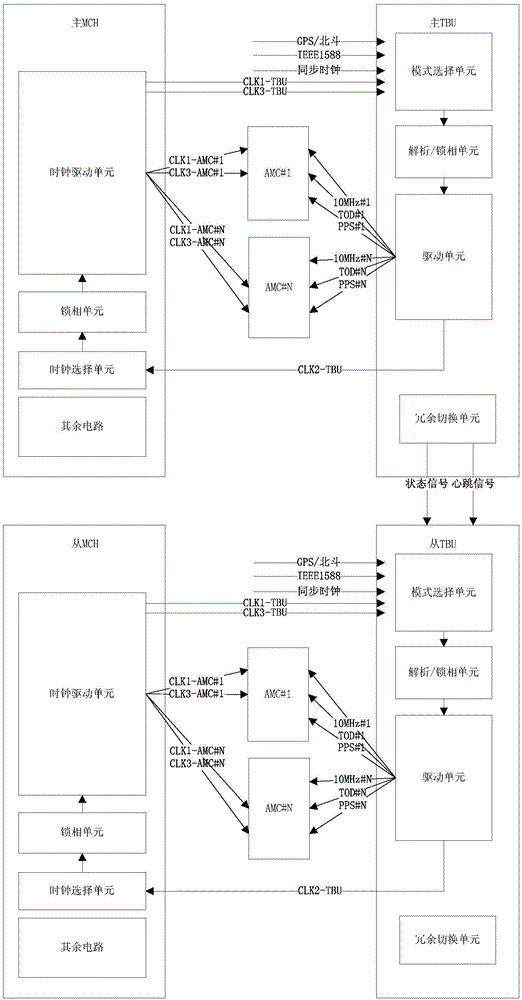

Multi-standard clock MicroTCA system and clock management method

ActiveCN105119703AImprove reuse rateImprove reliabilitySynchronising arrangementDifferential lineReusability

The invention discloses a MicroTCA system and a clock synchronization method and solves the problem that the introduction of a clock source is limited in the prior art. The MicroTCA system at least includes an MCH and a plurality of AMC cards connected with the MCH through a back board. The MCH includes a clock unit which is used for outputting a system synchronized clock to a predetermined clock input port of an AMC card through a predetermined output port, and at least one clock card connected with the MCH through a back board. The clock card is provided with an extra clock output end, an extra clock input end is arranged on the AMC card, the extra clock output end of the clock card outputs an extra clock to the extra clock input end of the AMC card through an extra differential line on the back board, and the AMC card is provided with a clock management unit which selectively uses the predetermined clock output by the MCH and / or the extra clock output by the AMC clock card. A special clock distribution board card is arranged inside a cabinet to support the multi-standard system clock synchronization to be suitable for a multi-standard combined scene, and a switching board MCH and an AMC board card are not needed to be redesigned. Therefore, the reusability of hardware is improved, the product development period is shortened, and the cost is reduced. Clock configuration double redundancy is allowed to improve the system reliability.

Owner:南京中科晶上通信技术有限公司

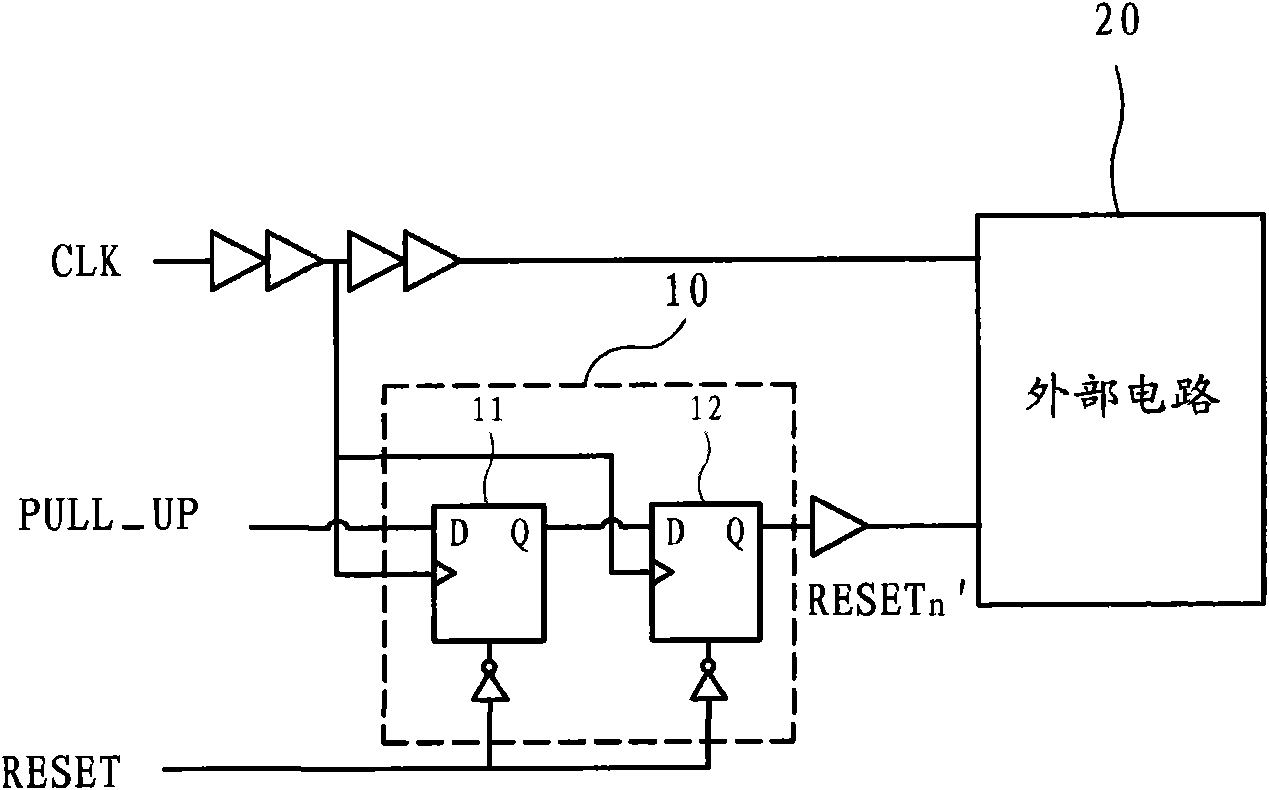

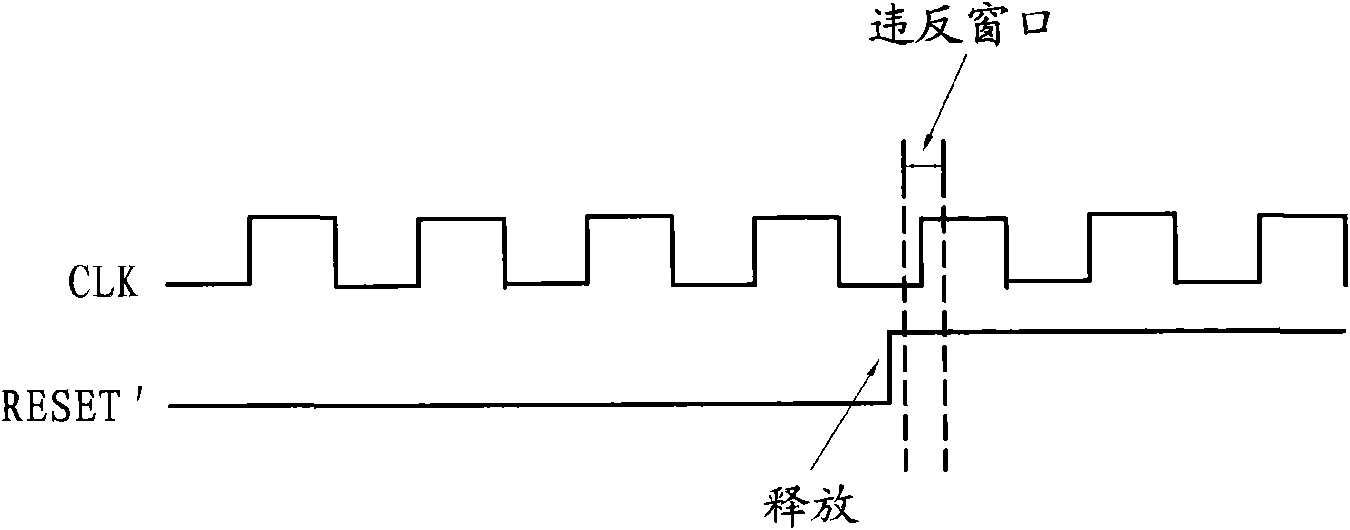

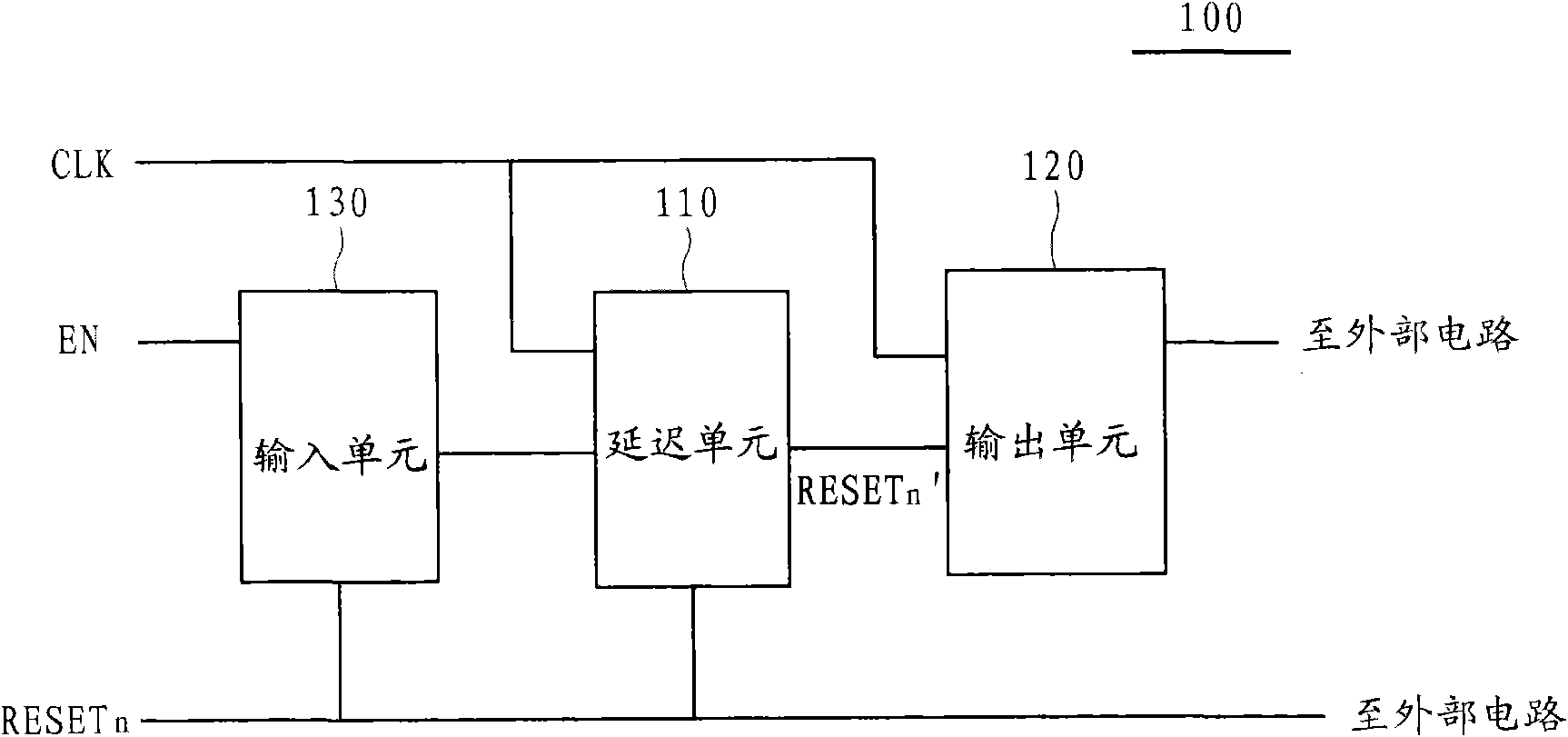

Clock management unit

InactiveCN102402242APrevent timing violationsSimplified backend designGenerating/distributing signalsExternal circuitClock management unit

The invention provides a clock management unit, which comprises a first trigger, a second trigger, a clock gate and an AND gate, wherein the first trigger comprises a first D terminal for receiving reset signals, a first clock terminal for receiving clock signals, and a first output terminal connected to a second D terminal of the second trigger; the second trigger comprises a second D terminal connected to a first output terminal of the first trigger, a second clock terminal for receiving clock signals and a second output terminal connected to an enable terminal of the clock gate; the clock gate comprises the enable terminal, a clock terminal for receiving clock signals, and an effective clock terminal connected to an external circuit; the clock gate provides the clock signals for the external circuit through the effective block terminal according to the output of the second output terminal of the second trigger; and the AND gate provides the reset signals for the first D terminal of the first trigger according to enable signals. Therefore, in at least two periods of the clock signals after the external circuit receives the reset signals, no clock signals are provided for the external circuit.

Owner:SAMSUNG SEMICON CHINA RES & DEV +1

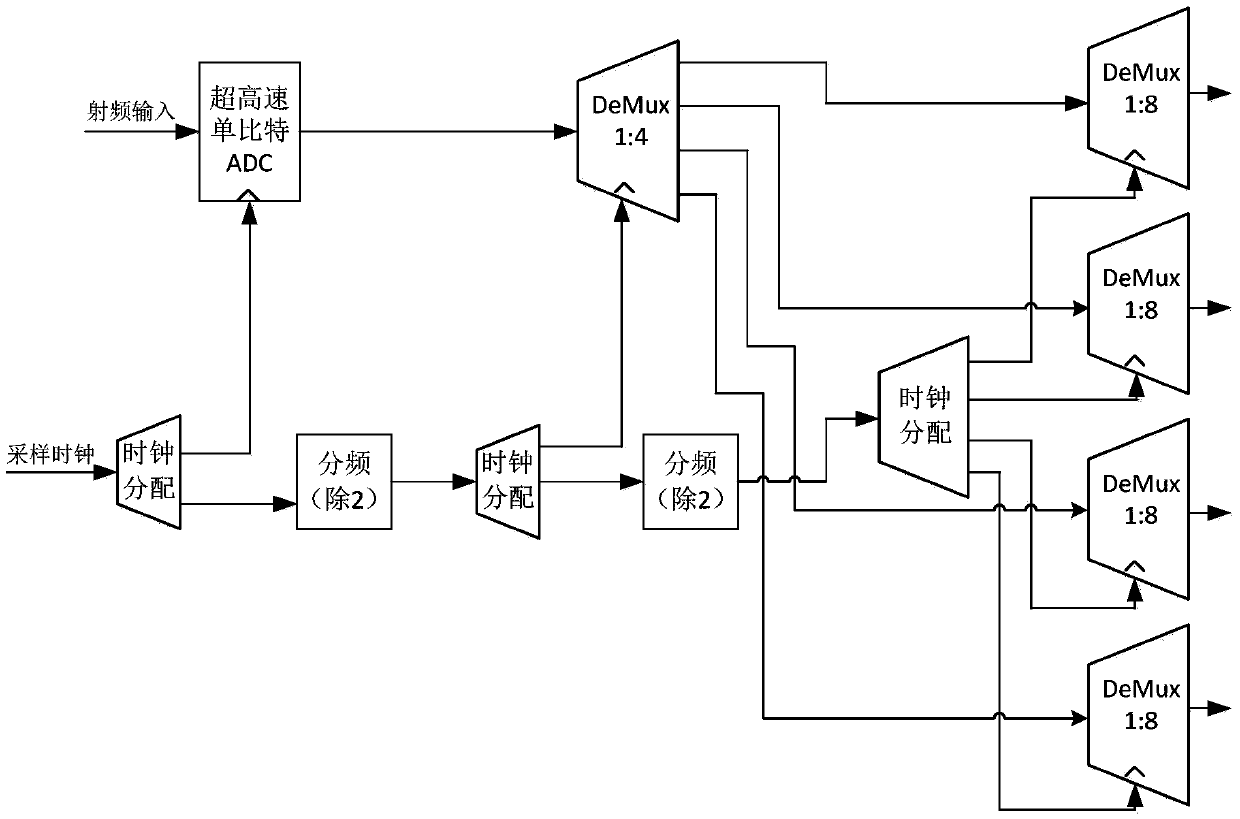

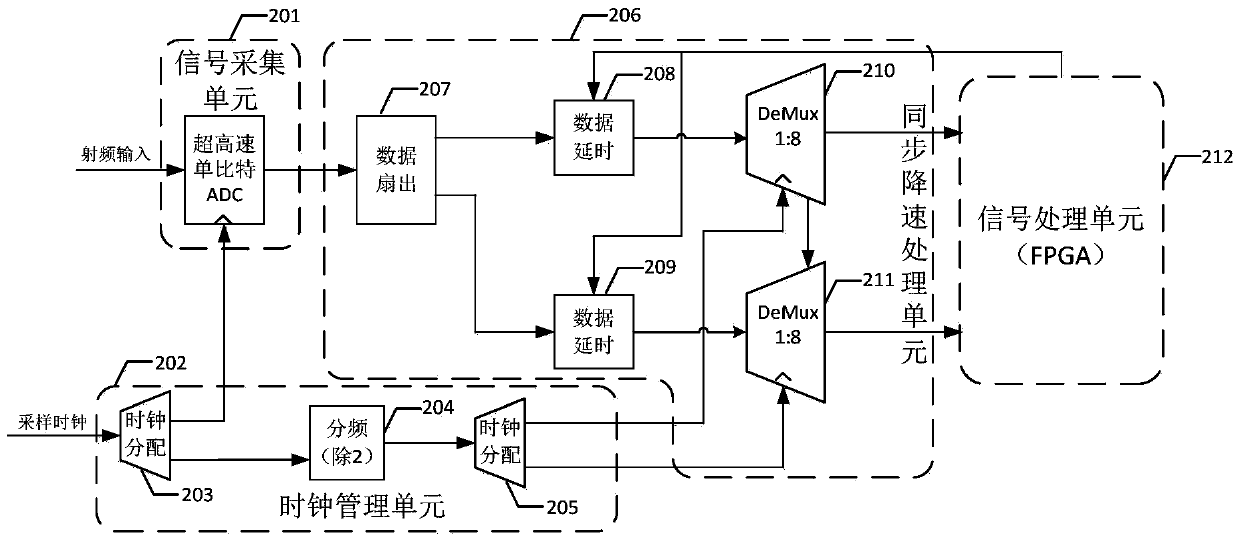

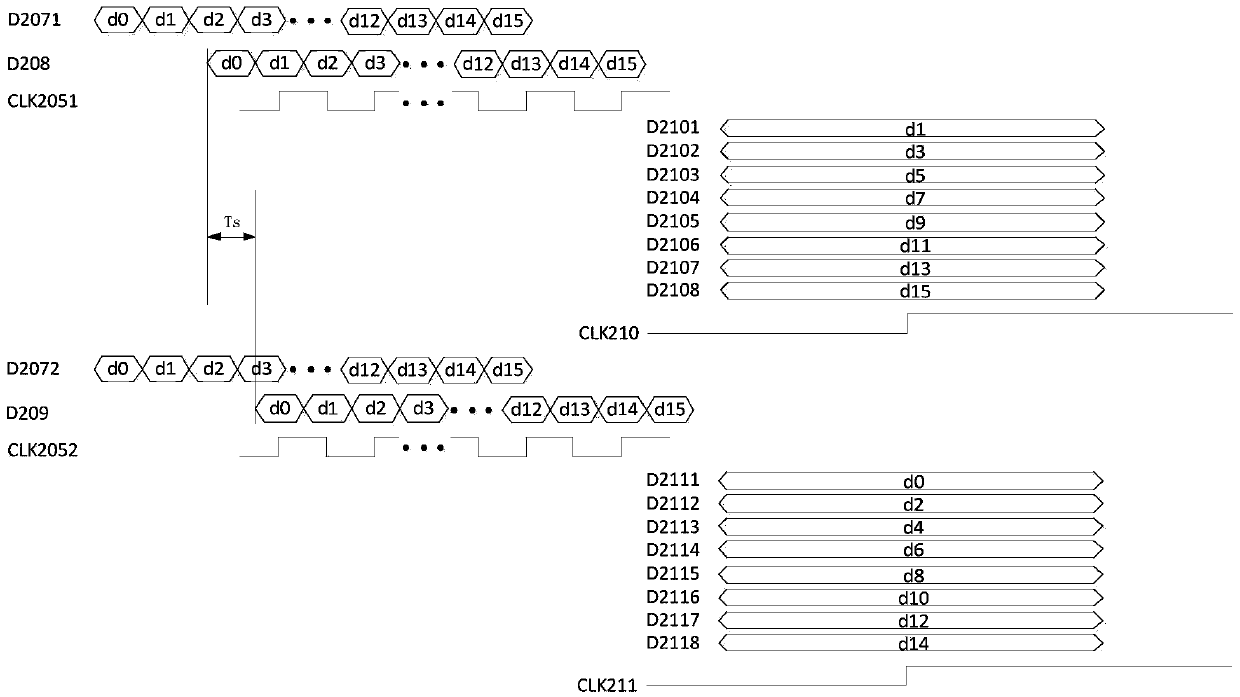

Digital receiver module, signal processing method thereof, and radio frequency card wiring method

The invention discloses a digital receiver module, a signal processing method thereof, and a radio frequency card wiring method. The digital receiver module comprises a signal collection unit, a clock management unit, a synchronous speed reduction processing unit, and a signal processing unit. The clock management unit supplies a superspeed sampling clock for the signal collection unit, and provides a synchronous speed reduction processing clock for the synchronous speed reduction processing unit, wherein the synchronous speed reduction processing clock is coherent with the sampling clock. The signal collection unit achieves the sampling and single-bit quantification of a radio-frequency input signal, and outputs superspeed single-bit collection data. The synchronous speed reduction processing unit enables one-path superspeed serial data to be converted into 16-path high-speed parallel data through first level speed reduction processing. The signal processing unit provides an on-line adjustable time delay code value in the synchronous speed reduction processing unit, and completes the real-time processing of high-speed parallel data. The invention also discloses the signal processing module for the digital receiver module, and the radio frequency card wiring method for the digital receiver module.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

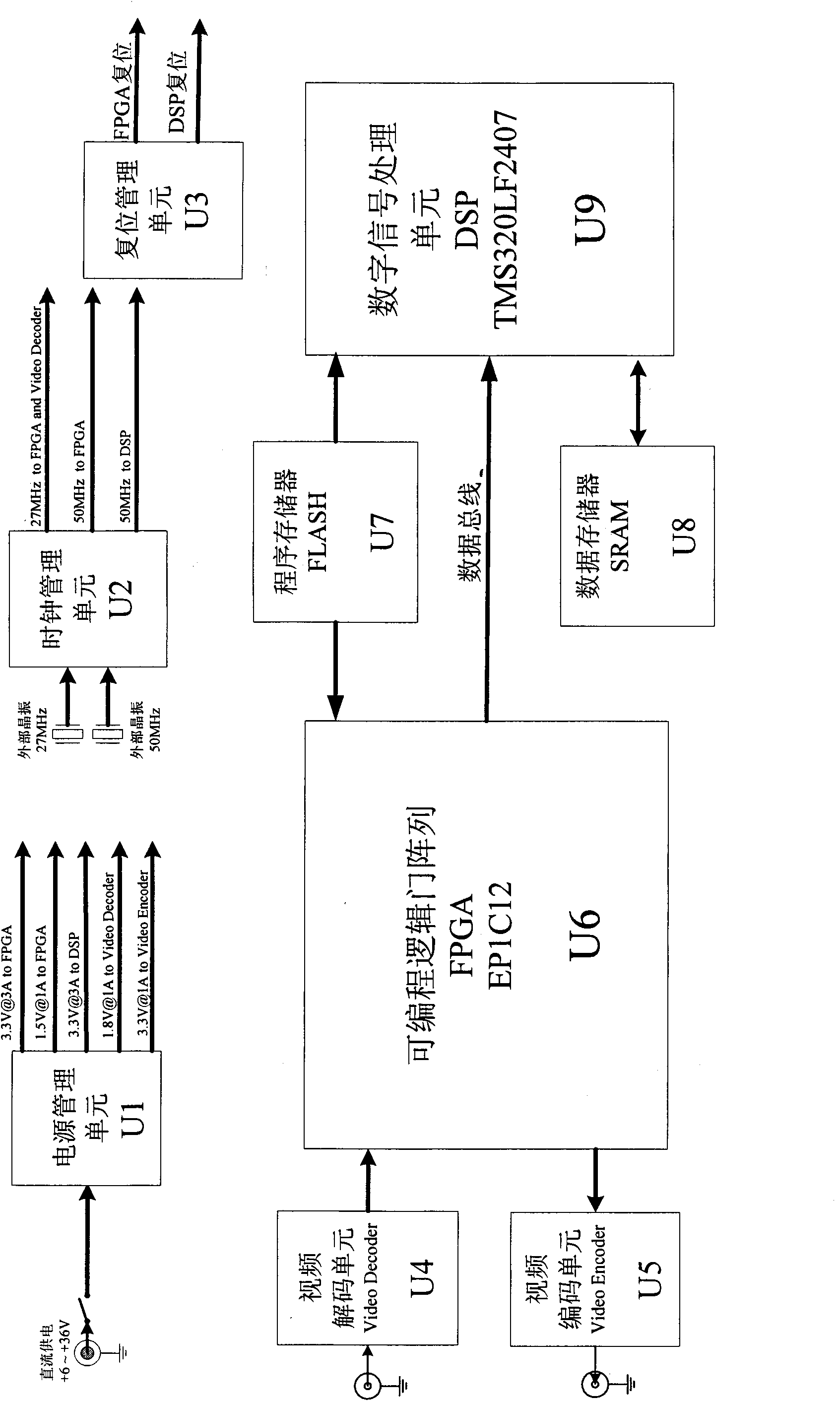

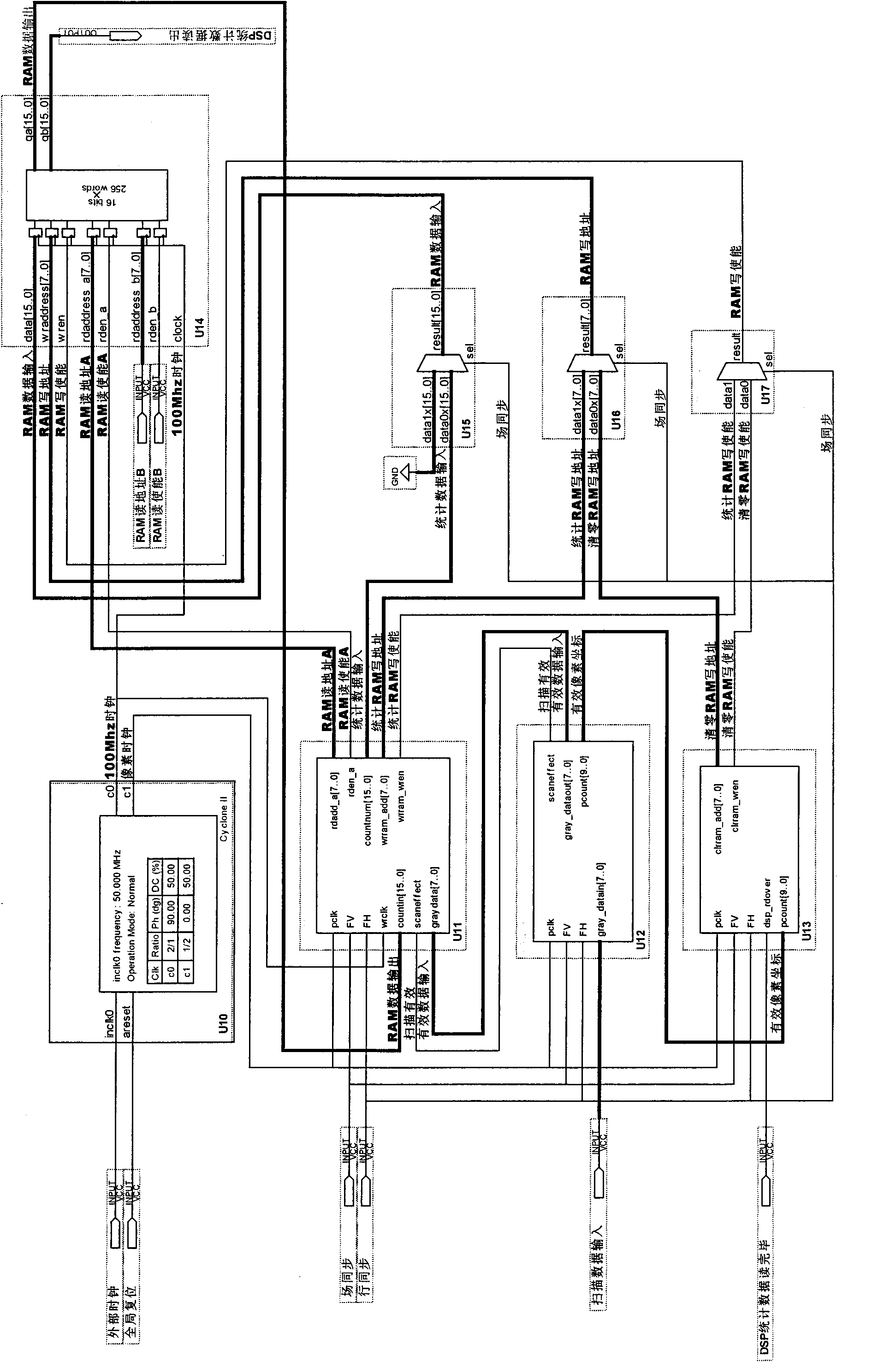

Device for real-time image statistics with histogram and method for implementing same

InactiveCN101674473AAchieve statisticsReduce complexityTelevision systemsDigital video signal modificationManagement unitSupply management

The invention relates to a device for real-time image statistics with a histogram and a method for implementing the same. The device comprises a video decoding unit, a programmable logic gate array, aprogram storage, a clock management unit, a resetting management unit and a power supply management unit, wherein the video decoding unit receives, filters, amplifies and digitalizes an original image signal to generate video data; the programmable logic gate array receives video data output by the video decoding unit and performs the statistics of the video data with the histogram; the program storage stores the application programs of the programmable logic gate array; the clock management unit provides required clocks for the programmable logic gate array and the video decoding unit; the resetting management unit provides a resetting signal for the programmable logic gate array; and the power supply management unit provides required power supply for the programmable logic gate array and units. The method comprises that: the video decoding unit receives, filters, amplifies and digitalizes the original image signal to generate the video data; and the programmable logic gate array performs the statistics of the video data with the histogram to obtain a result. The device and the method have the advantages of quickness, high integration level, low cost, and the like.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

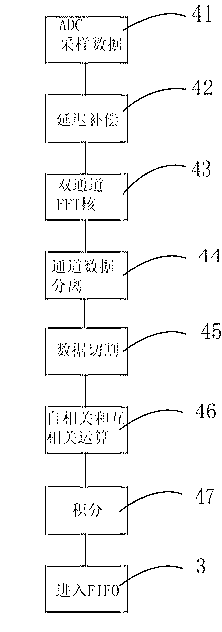

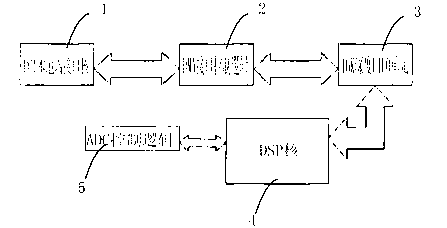

Realization method of double-passage real-time relevance machine

InactiveCN102778611AAvoid the convolution processSave resourcesAntenna radiation diagramsFast Fourier transformComputer architecture

The invention relates to a realization method of a double-passage real-time relevance machine on an FPGA (field programmable gate array) chip. According to the realization method, a PCI (peripheral component interconnect) local end interface core, a DMA (direct memory access) interface control logic unit, a 16K depth FIFO (first in first out) unit, a DSP (digital signal processor) core, an ADC (analog to digital converter) control logic unit and a clock management unit are adopted, wherein the DSP core comprises the following processing flow processes that ADC sampling data enters a double-passage FFT (fast fourier transform) core after delay compensation and enters a self relevance and mutual relevance operation unit through passage data separation and data cutting, and finally, the ADC sampling data enters an integrator for integration and enters the FIFO unit. Therefore, the signal to noise ratio of the mutual relevance can be improved, meanwhile, much chip resource space is saved, and the high-speed operation is realized.

Owner:SHANGHAI ASTRONOMICAL OBSERVATORY CHINESE ACAD OF SCI

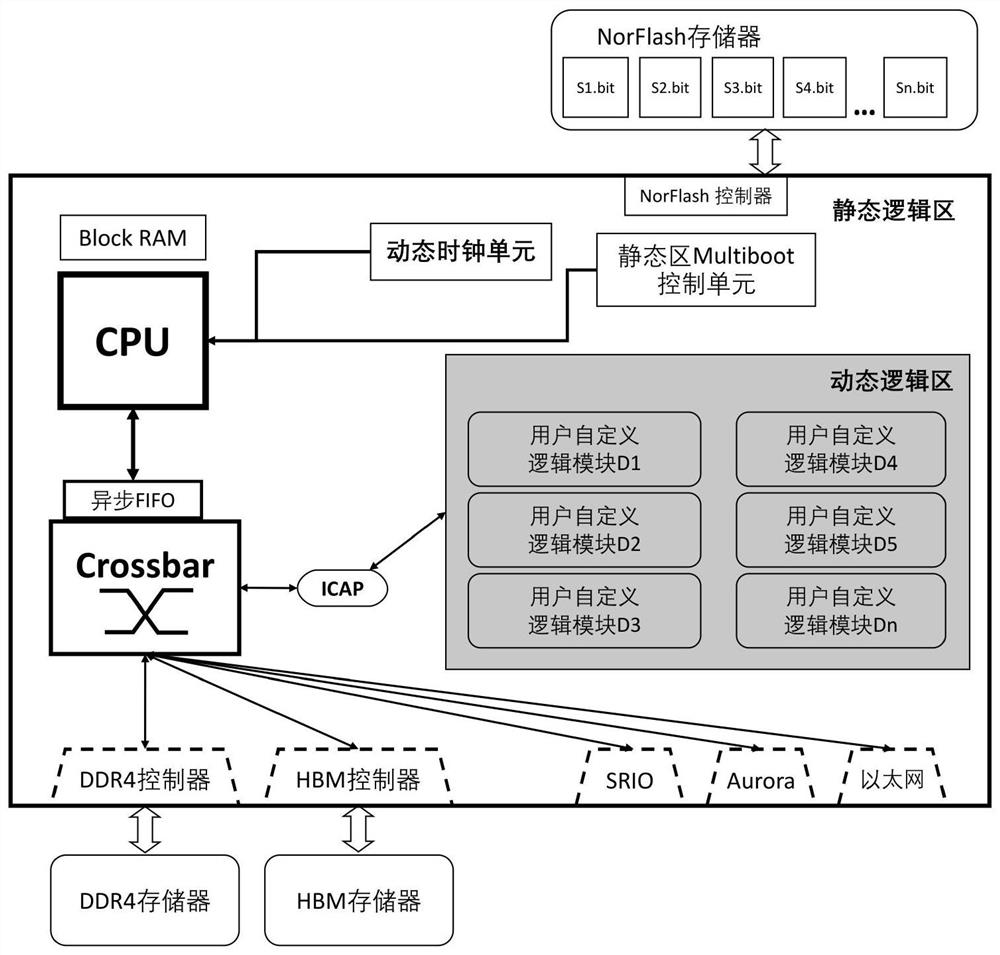

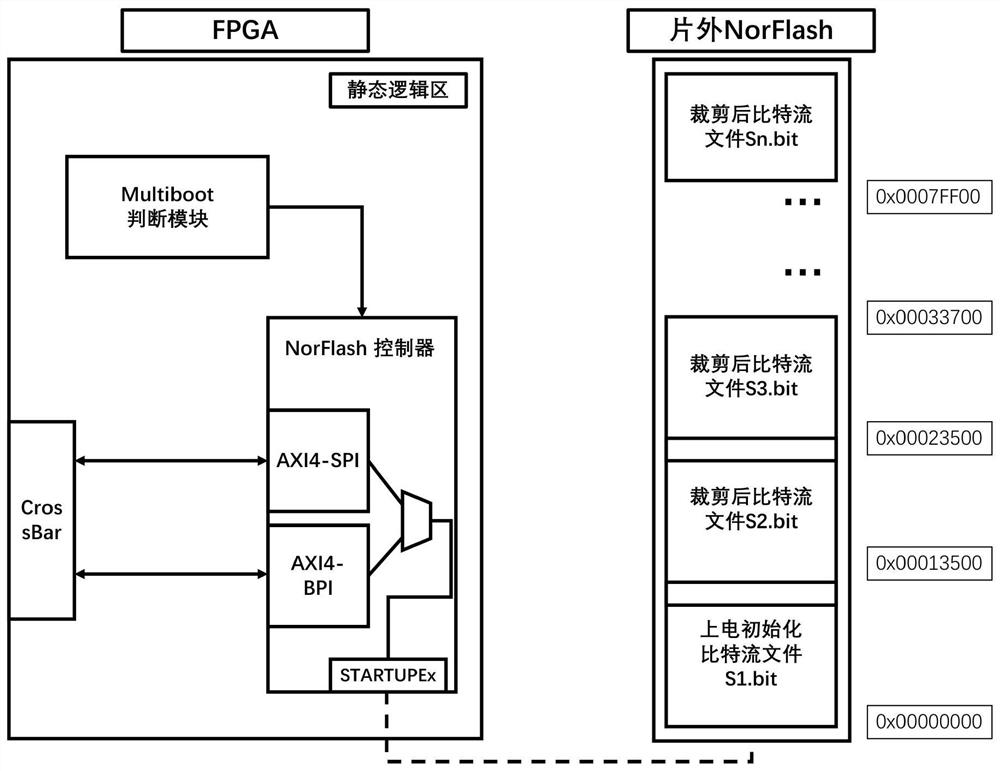

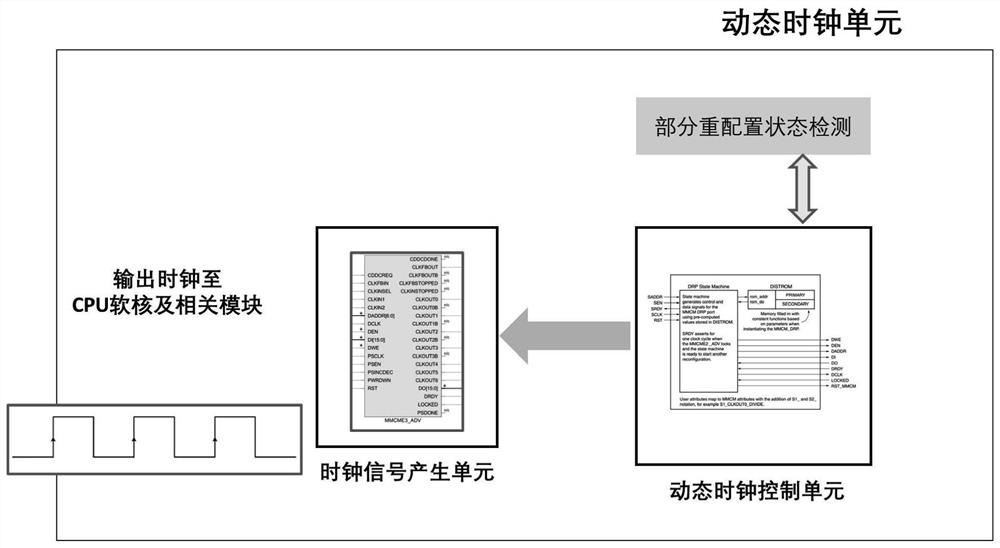

Low-power-consumption FPGA (Field Programmable Gate Array) partially reconfigurable method and low-power-consumption FPGA partially reconfigurable device

PendingCN112597096AReduce ineffective power consumptionAvoid heat dissipationDigital data processing detailsArchitecture with single central processing unitComputer architectureClock rate

The invention provides a low-power-consumption FPGA (Field Programmable Gate Array) partially reconfigurable method and a low-power-consumption FPGA partially reconfigurable device. According to the method and device provided by the scheme of the invention, the invalid power consumption of the FPGA static logic region is effectively reduced by combining the logic cutting and reconstruction switching technology of the FPGA static logic region and the clock frequency real-time adjustment mechanism of the memory control interface dormancy and dynamic clock management unit; and meanwhile, the problems of heat dissipation and stability caused by long-term working of the static logic region in a high-frequency state are further avoided.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Heterogeneous multi-core processor power consumption control device and method

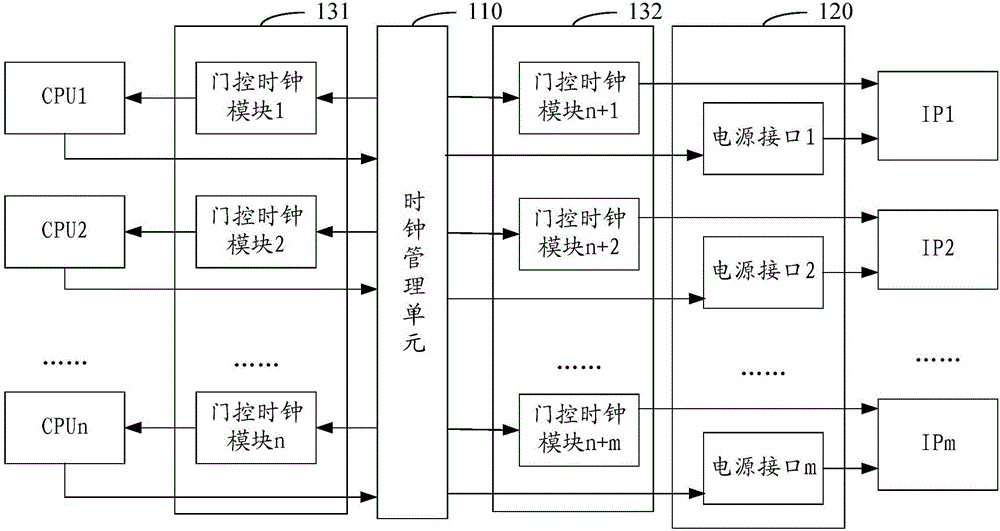

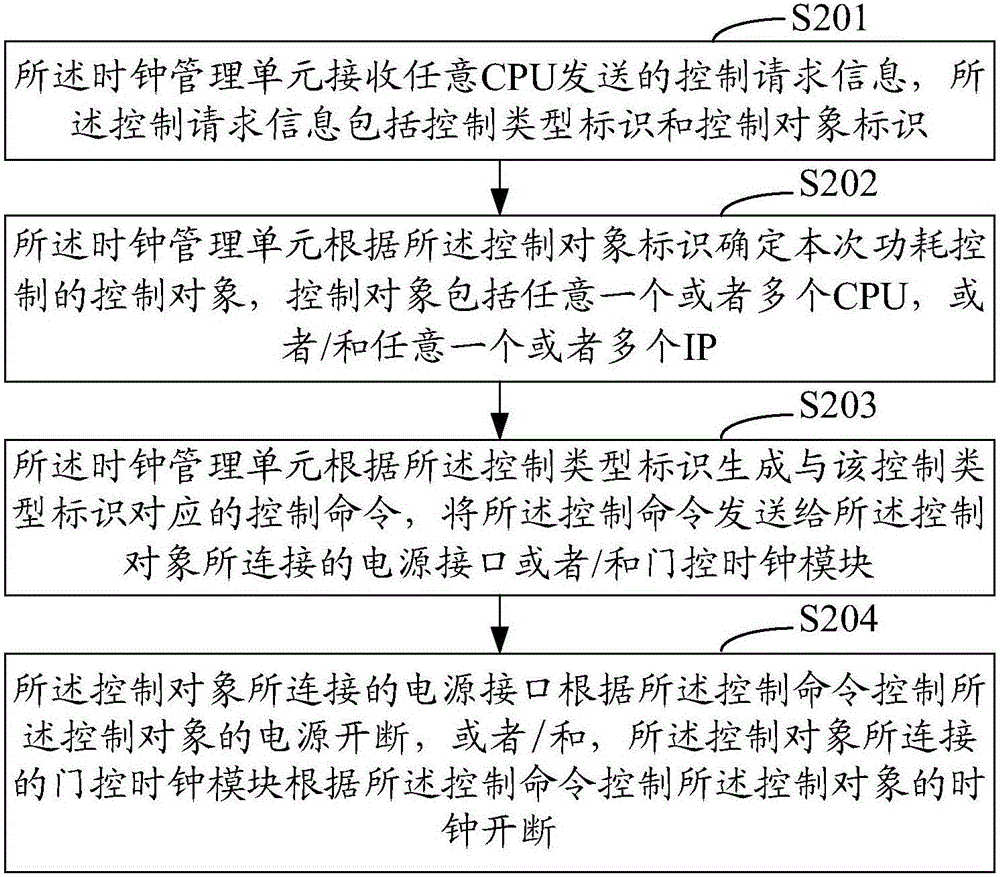

ActiveCN106681472AReduce power consumptionDigital computer detailsPower supply for data processingControl powerManagement unit

The invention relates to a heterogeneous multi-core processor power consumption control device and method. The device comprises n CPUs and m IPs, and further comprises a clock management unit, a power source management unit and a clock control unit, wherein n and m are integers larger than 1. The power source management unit comprises m power source interfaces which control power sources of the connected IPs to be switched on or off respectively according to control commands of the clock management unit. The clock control unit comprises n+m clock gating modules, and each clock gating module is connected with one CPU or one IP, and the clock gating modules control clocks of the connected CPUs or the IPs to be switched on or off respectively according to control commands of the clock management unit. Each CPU can control the clock management unit to send the control commands to any power source interface or any clock gating clock module. By means of the scheme, power consumption of a chip and design difficulty of the chip can be reduced.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD