Multichannel parallel acquisition system with multi-device asynchronous reset recognition correction function

An acquisition system and synchronous correction technology, applied in electrical components, analog/digital conversion calibration/test, code conversion, etc., can solve problems such as cumbersome debugging process, complex hardware, and increased risk of reset uncertainty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

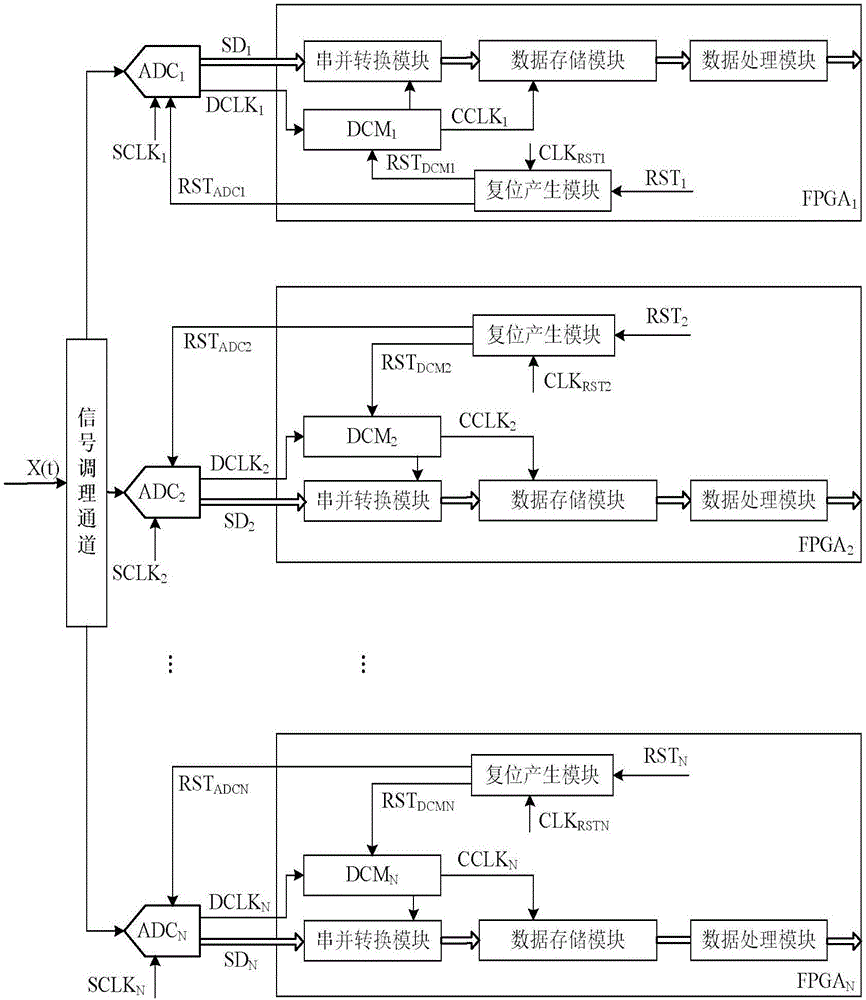

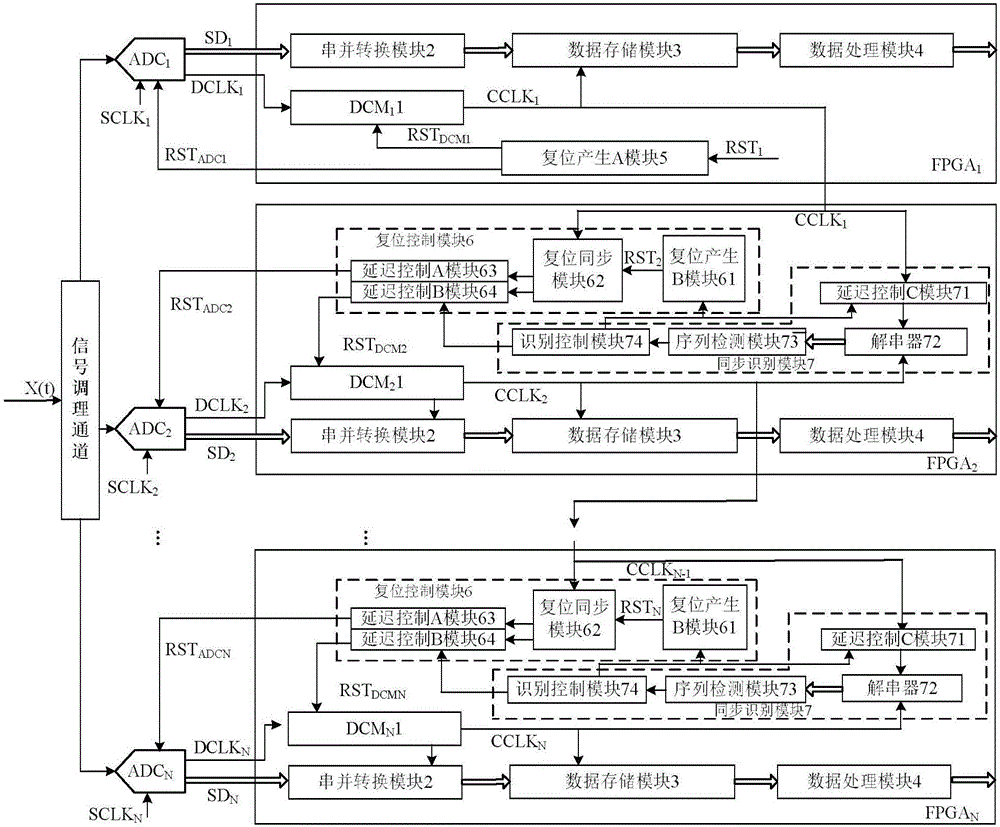

[0027] image 3 It is a structural diagram of a specific embodiment of a multi-channel parallel acquisition system with multi-device synchronous reset, identification and correction functions of the present invention. Such as image 3 As shown, the multi-channel parallel acquisition system with multi-device synchronous reset identification and correction function of the present invention includes N sets of ADC and FPGA modules, and the value range of N is N≥2.

[0028] The ADC module collects the analog signal in the conditioning channel, and sends the collected data to the serial-to-parallel conversion module 2 of the corresponding FPGA module.

[0029] The FPGA module includes a clock management unit (DCM) 1, a serial-to-parallel conversion module 2, a data storage module 3 and a data processing module 4. The specific descriptions of each module are as follows:

[0030] The clock management unit 1 receives the data synchronous clock signal DCLK (frequency division clock of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More