Patents

Literature

31results about How to "Prevent unnecessary power consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

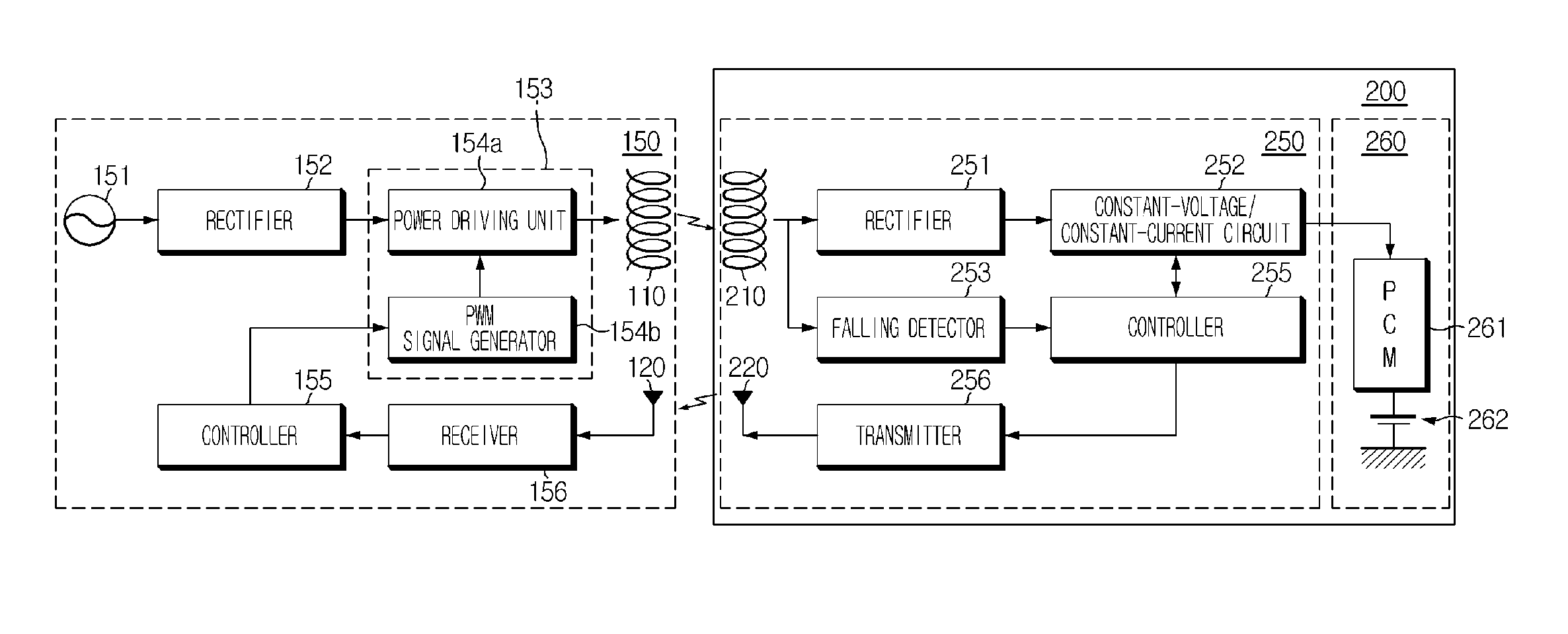

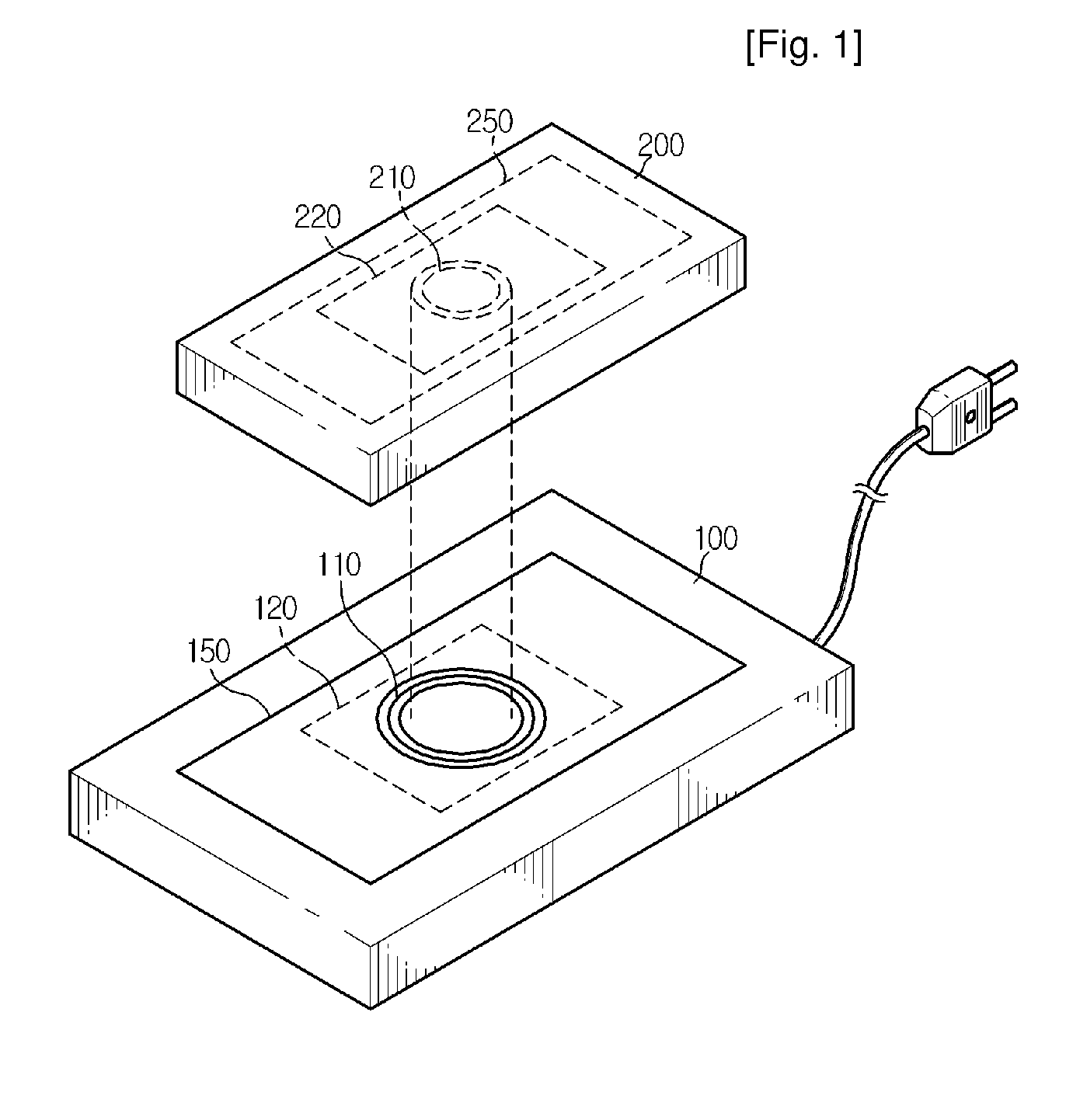

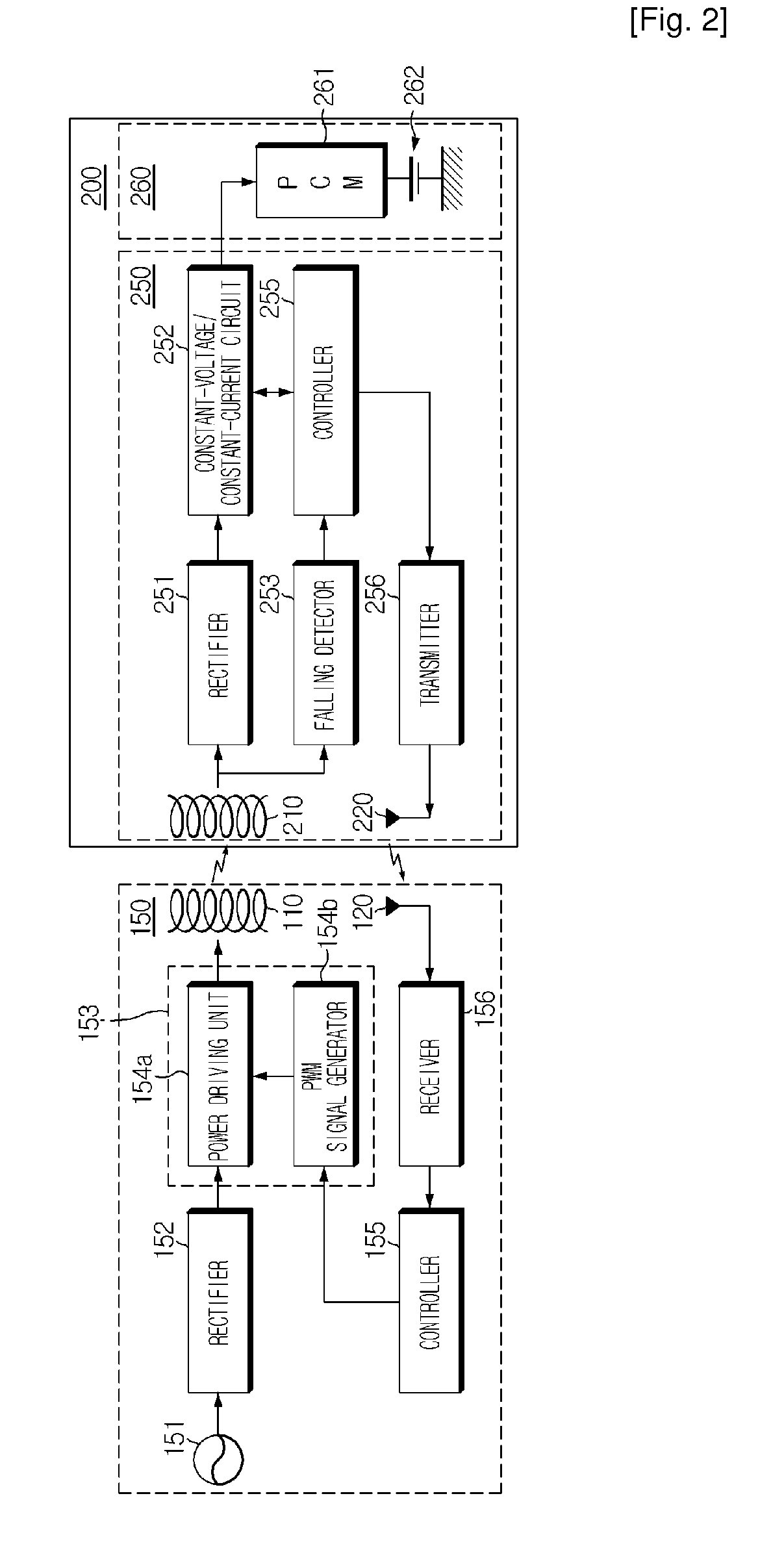

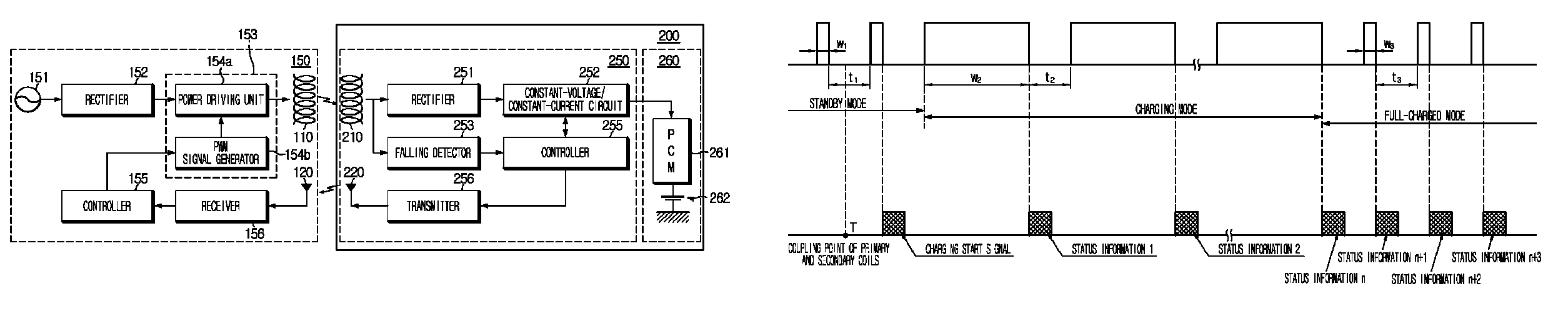

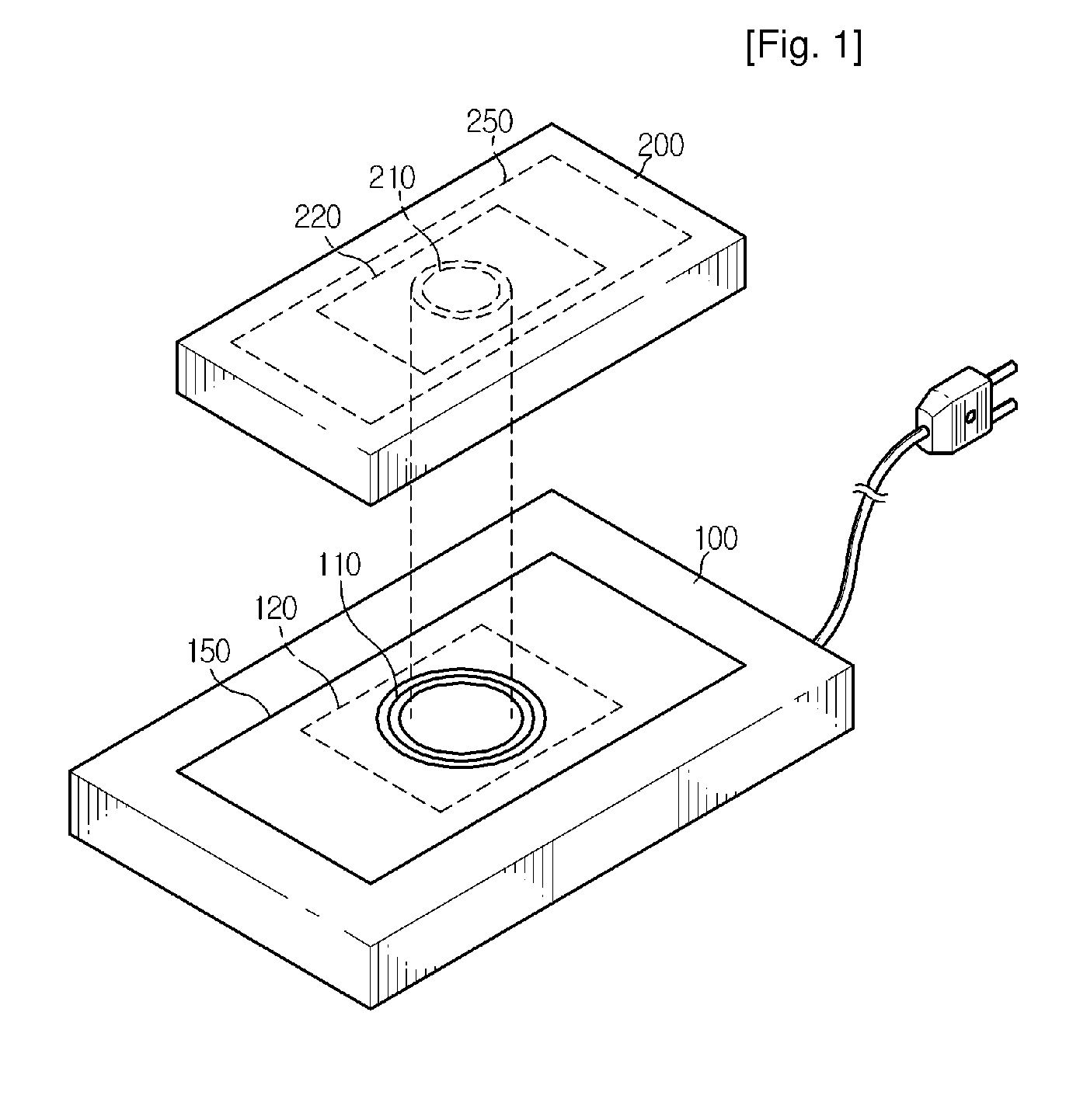

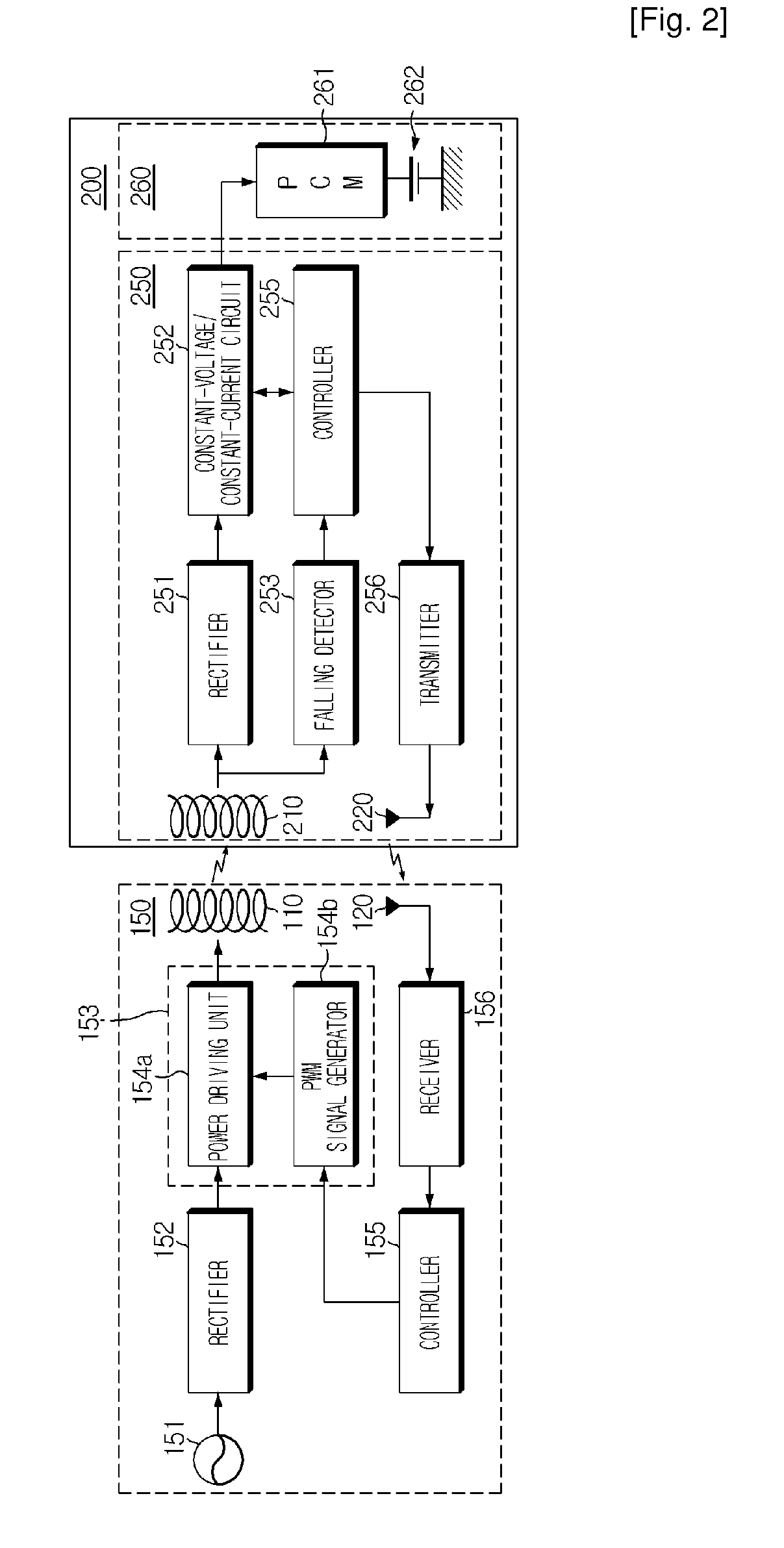

Rechargeable Power Supply, Battery Device, Contactless Charger System And Method For Charging Rechargeable Battery Cell

ActiveUS20080211455A1Prevent unnecessary power consumptionNear-field transmissionCircuit monitoring/indicationBattery chargeRechargeable cell

A system, method and apparatus for contact-less charging of battery operated devices is presented. There is a host charger with a power converter and resonant tank circuit and a portable device where the battery is located, with a battery charging control IC. The method obviates the need for a voltage controller in each of both the host and the portable stages, thus decreasing complexity and increasing efficiency. The charging of the battery in the portable device is controlled by a charging controller therein, which is in continual electric communication with the host, whose output power the control IC dynamically monitors and controls. Two embodiments for the charging circuitry in the portable device are presented. In one embodiment component count is minimized but battery charging is not optimized when the battery voltage is very low. In the other embodiment charging efficiency is maximized regardless of the output voltage of the battery, but additional components are utilized.

Owner:LS CABLE & SYST LTD

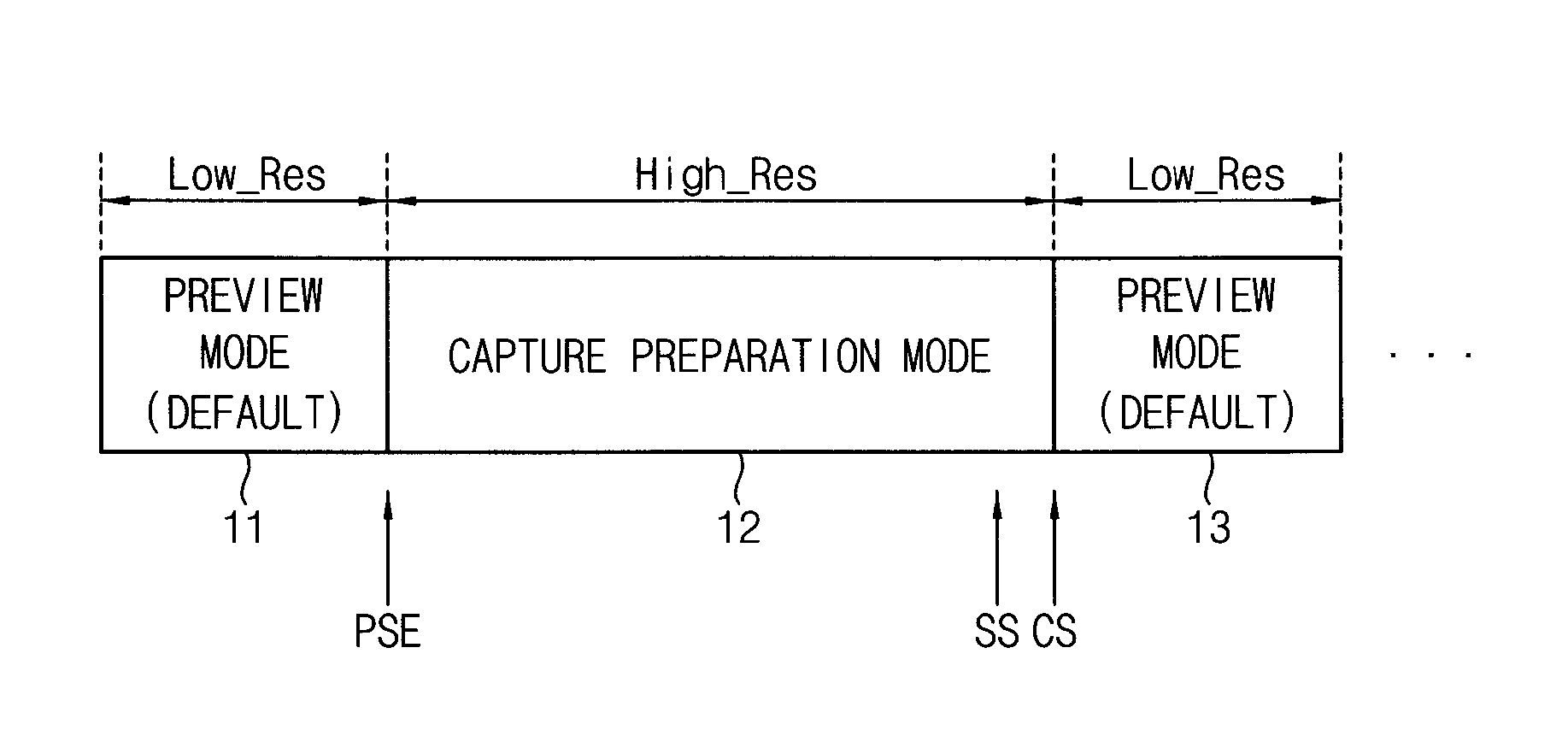

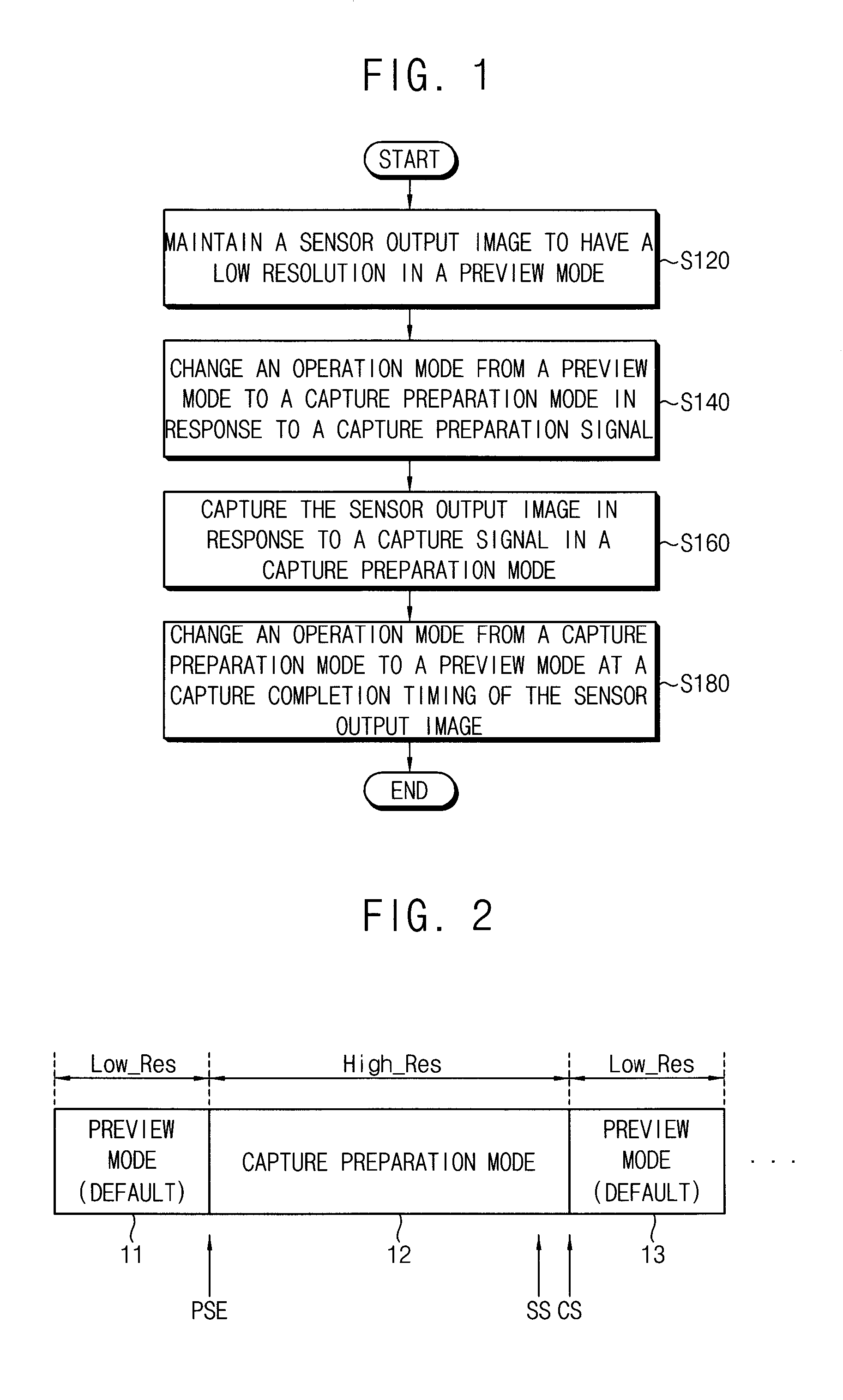

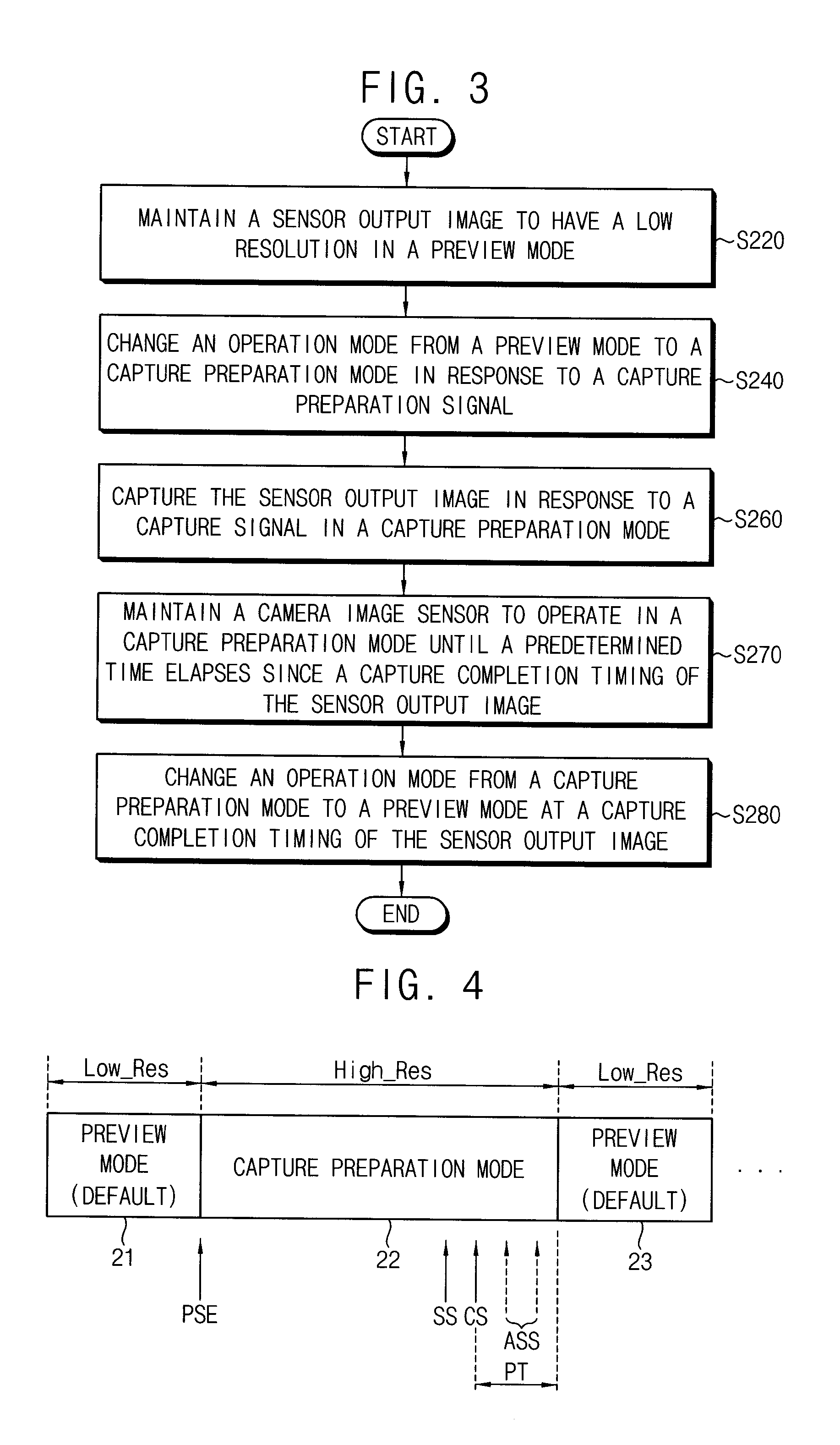

Method of eliminating a shutter-lag, camera module, and mobile device having the same

ActiveUS20130135499A1Prevent unnecessary power consumptionHigh resolutionTelevision system detailsColor television detailsImage resolutionImage sensor

A method of reducing shutter-lag in a camera image sensor may include maintaining a sensor output image to have a low resolution in a preview mode of a camera image sensor; changing a resolution of the sensor output image from a low resolution to a high resolution in response to a capture preparation signal to change an operation mode of the camera image sensor from a preview mode to a capture preparation mode, the low resolution being a resolution equal to or below a reference resolution, the high resolution being a resolution above the reference resolution; and capturing the sensor output image in response to a capture signal in the capture preparation mode of the camera image sensor.

Owner:SAMSUNG ELECTRONICS CO LTD

Contactless charging method for charging battery

ActiveUS8129942B2Prevent unnecessary power consumptionNear-field transmissionCircuit monitoring/indicationBattery chargeEngineering

A system, method and apparatus for contact-less charging of battery operated devices is presented. There is a host charger with a power converter and resonant tank circuit and a portable device where the battery is located, with a battery charging control IC. The method obviates the need for a voltage controller in each of both the host and the portable stages, thus decreasing complexity and increasing efficiency. The charging of the battery in the portable device is controlled by a charging controller therein, which is in continual electric communication with the host, whose output power the control IC dynamically monitors and controls. Two embodiments for the charging circuitry in the portable device are presented. In one embodiment component count is minimized but battery charging is not optimized when the battery voltage is very low. In the other embodiment charging efficiency is maximized regardless of the output voltage of the battery, but additional components are utilized.

Owner:LS CABLE & SYST LTD

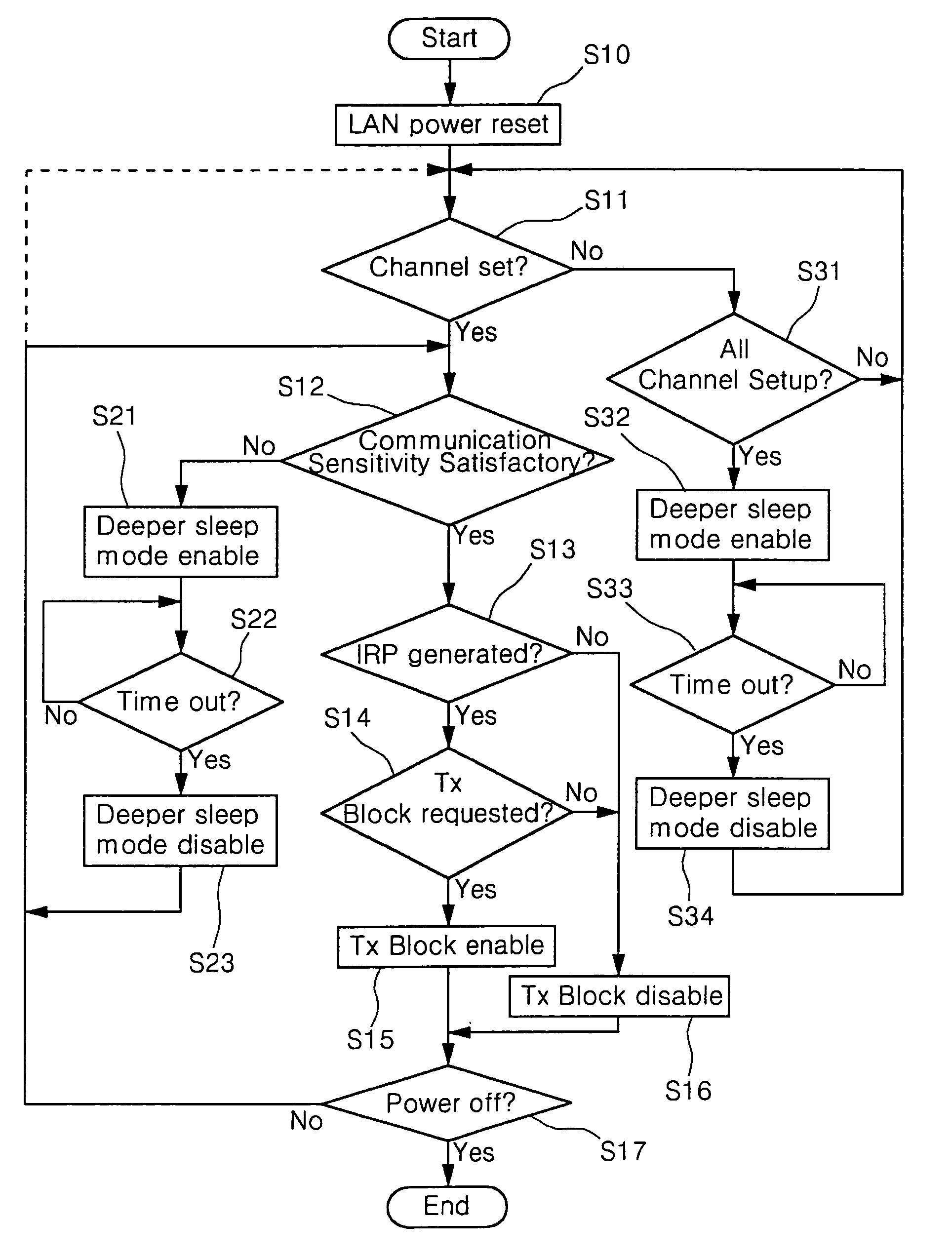

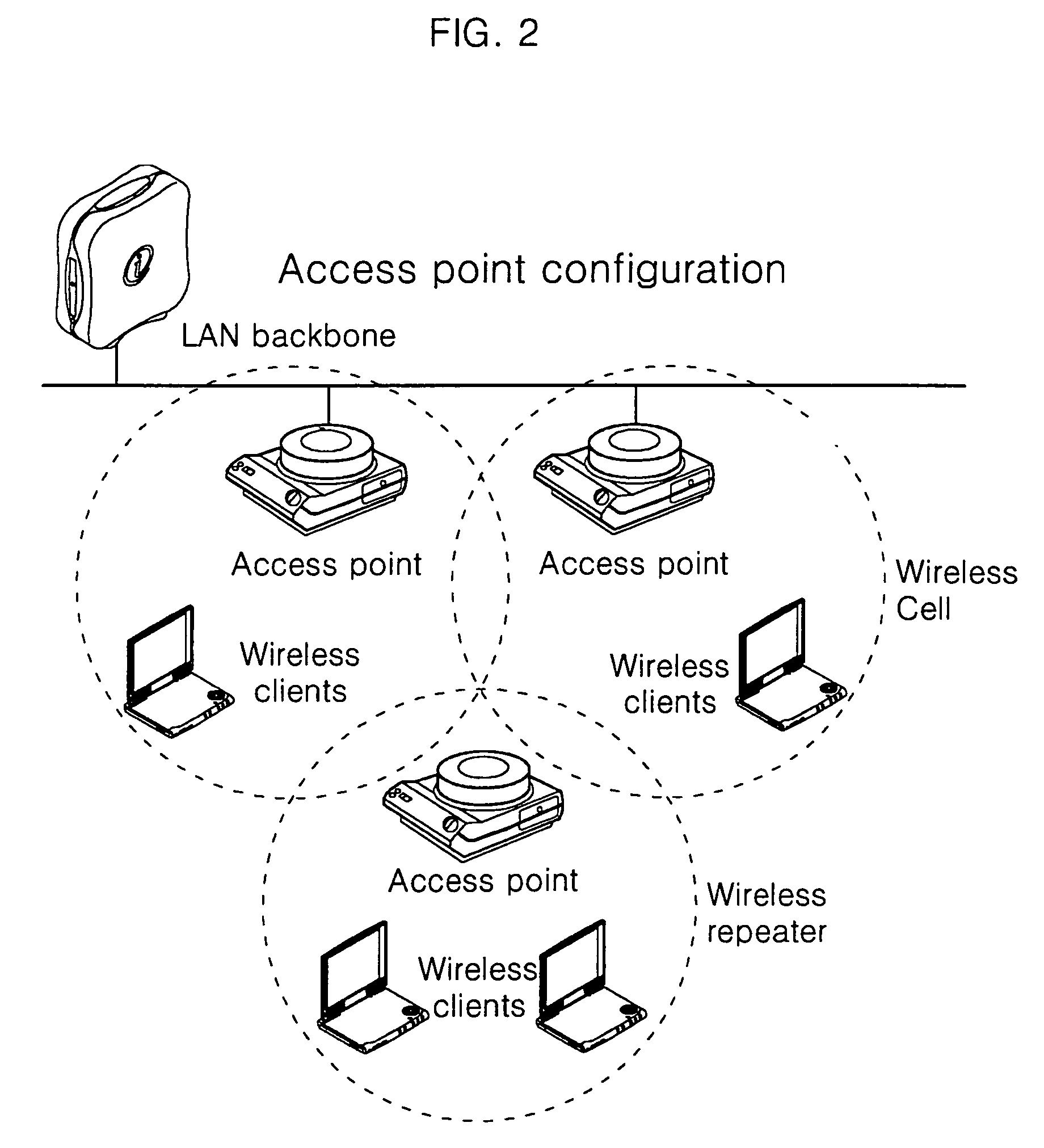

Power management method and apparatus of wireless local area network module in computer system

ActiveUS7321787B2Prevent unnecessary power consumptionReduce system loadPower managementEnergy efficient ICTData needsNormal mode

A power management method and apparatus for a wireless LAN module in a computer system may include a communication sensitivity checking unit for checking a communication sensitivity of a wireless communications channel. If a communications sensitivity is lower than a desired value, a power mode of the wireless LAN module is changed into a sleep mode for a predetermined period of time. After the delay period expires, the wireless LAN module is switched back into a normal mode, and the communications sensitivity is checked again. If the communications sensitivity is acceptable, a data checking unit checks to determine whether there is data to be transmitted / received by the wireless LAN module. If no data needs to be sent, at least the transmission block of the wireless LAN module can be set to the power down mode. Also, if an attempt to set up a communications channel is unsuccessful, the device can be set to the power down mode for a predetermined delay period. After the delay period expires, the wireless LAN module is returned to the normal mode for another setup attempt.

Owner:LG ELECTRONICS INC

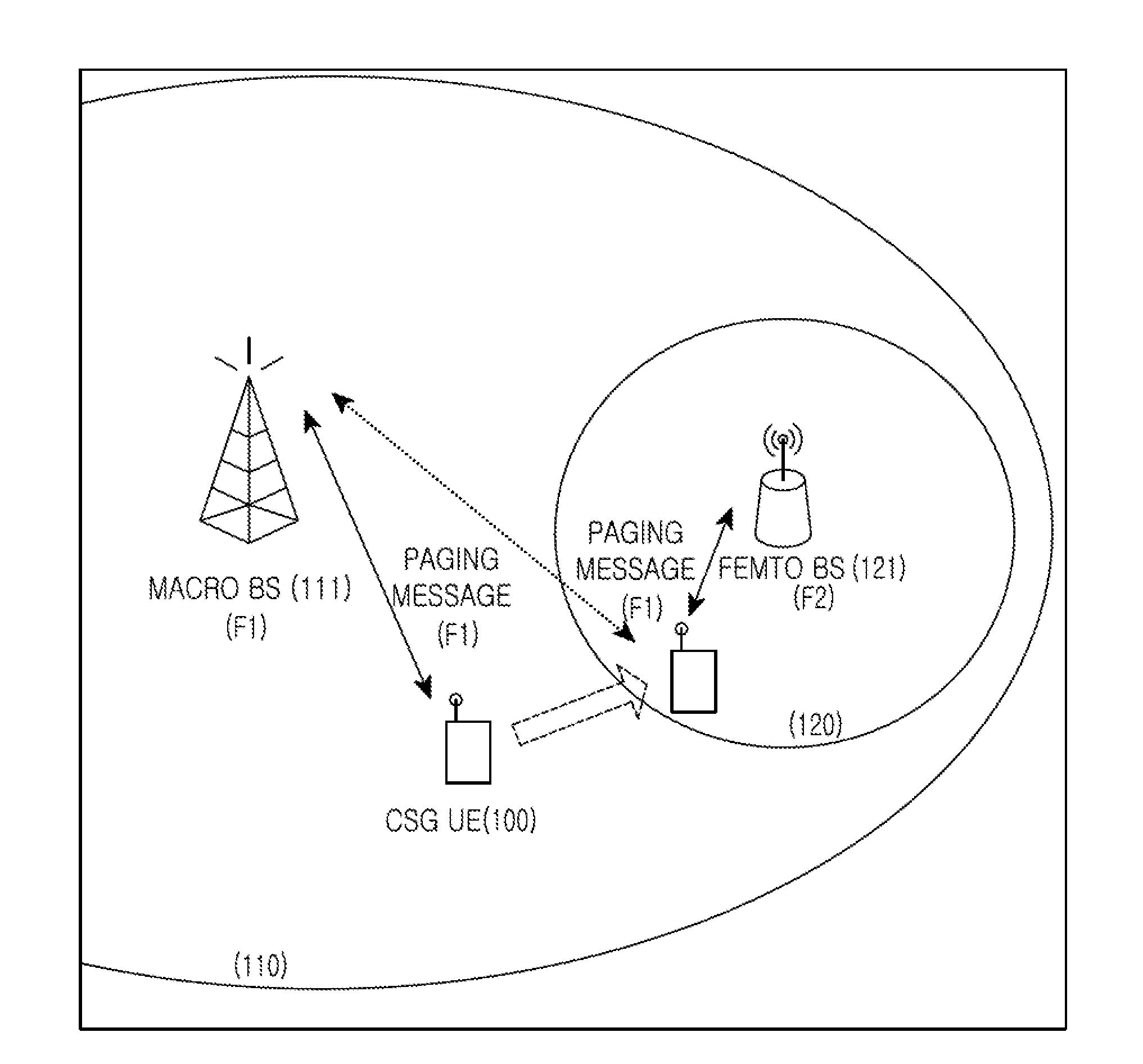

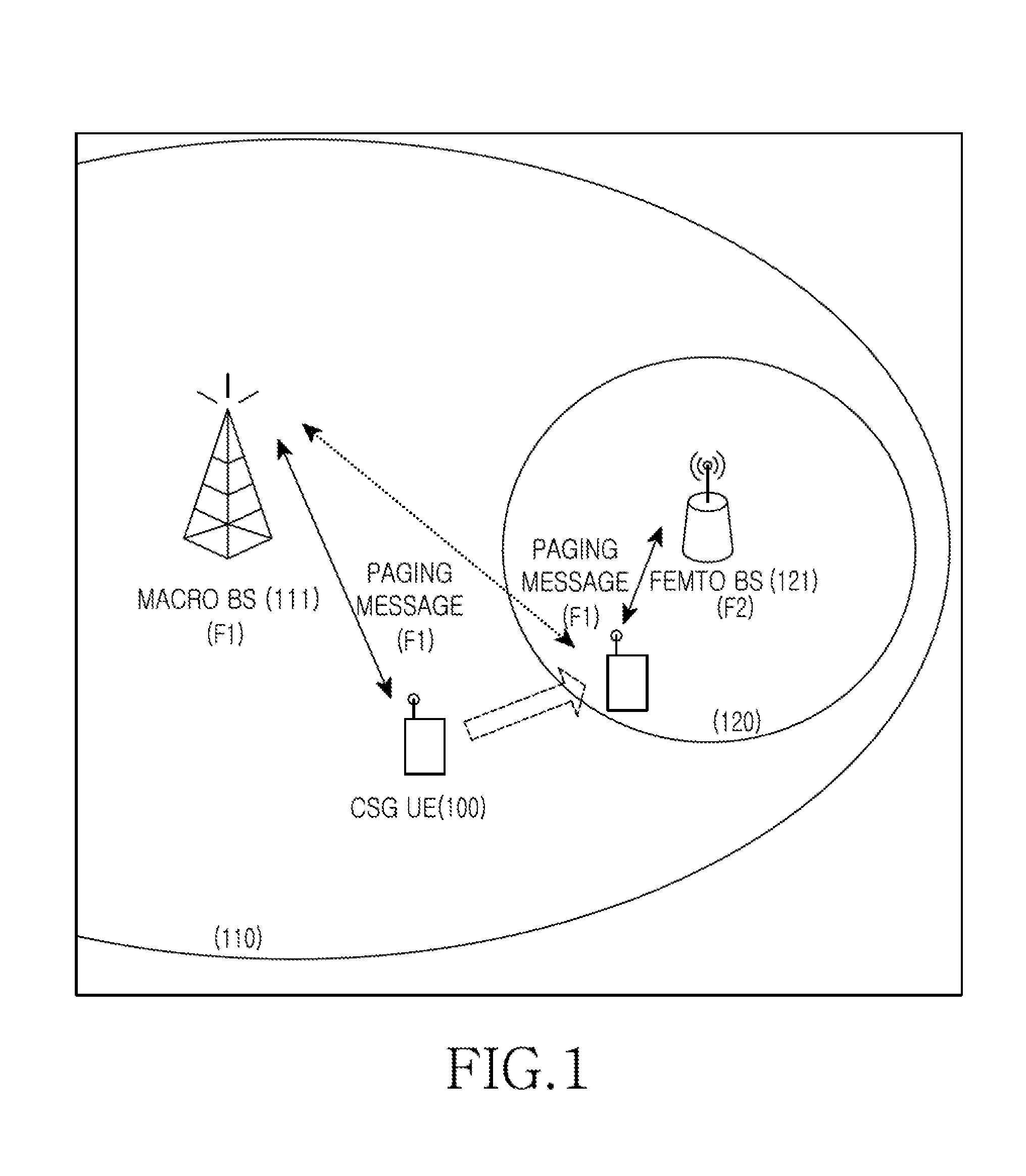

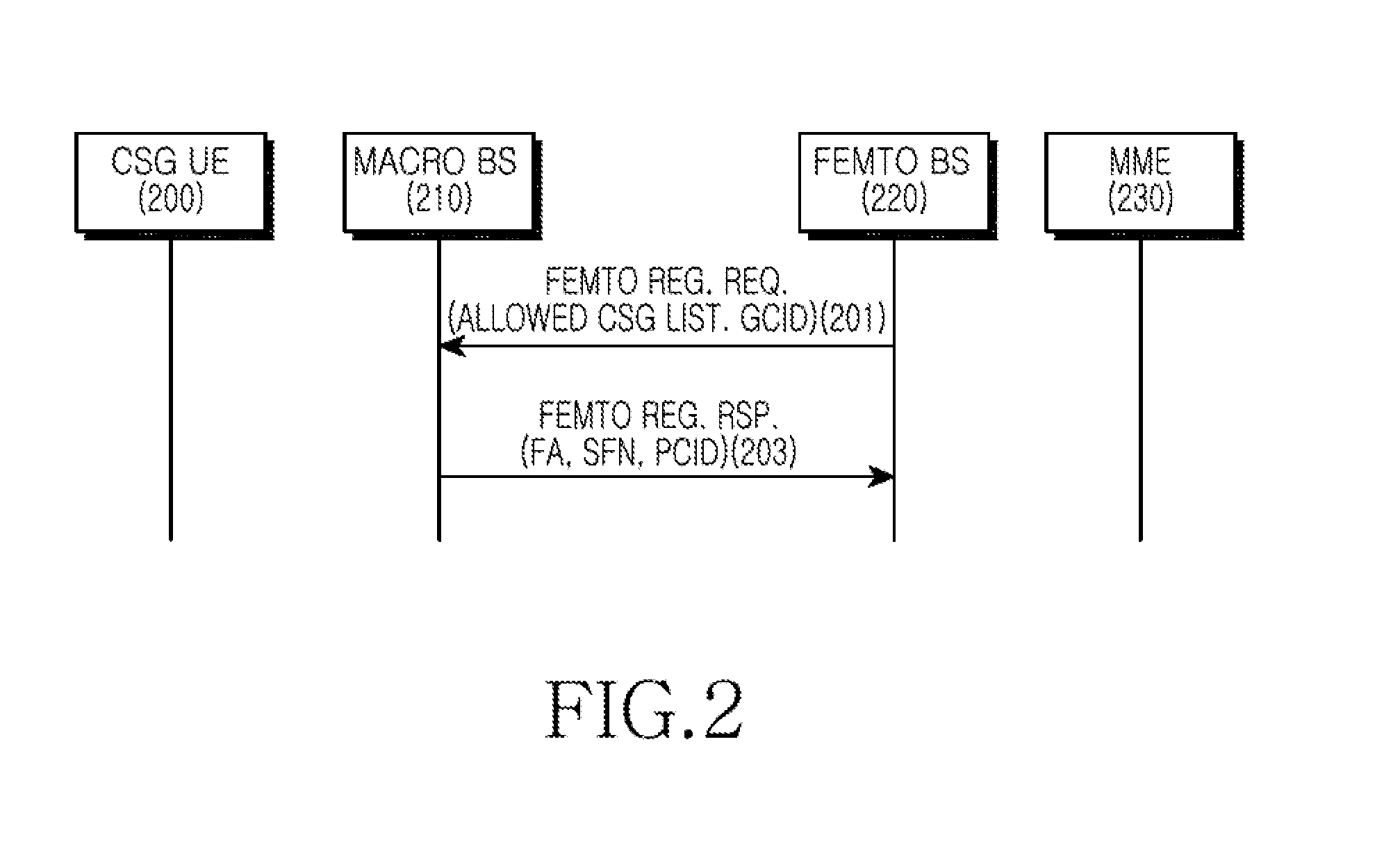

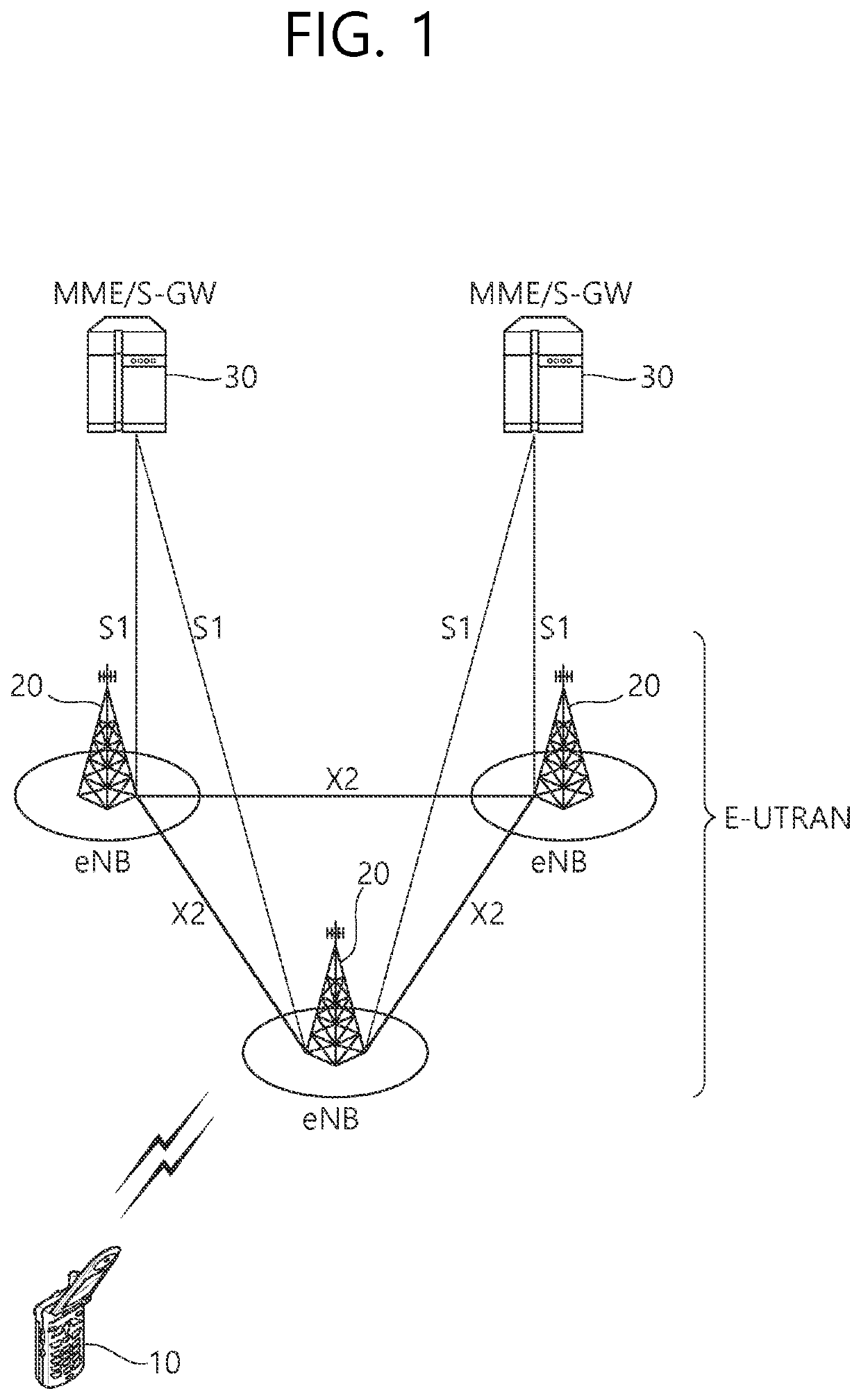

Apparatus and method for measuring a femto base station of user equipment registered to femto base station in mobile communication system

ActiveUS20110076960A1Performance degradation be diminishPrevent unnecessary power consumptionPower managementNetwork topologiesFemto-Service coverage

An apparatus and a method for measuring a signal from a femto Base Station (BS) of a User Equipment (UE) registered to the femto BS in a mobile communication system are provided. An operating method of a femto BS for measuring the signal from the femto BS of a UE registered to the femto BS in a mobile communication system where the femto BS and a macro BS coexist, includes, when the UE registered to the femto BS is located in a service coverage area of the macro BS, generating a paging message informing of the existence of the femto BS, and sending the generated paging message to the UE. The UE measures the signal from the femto BS based on the paging message, generates a measurement report message including a measurement result, and sends the generated measurement report message to the macro BS.

Owner:NOKIA TECHNOLOGLES OY

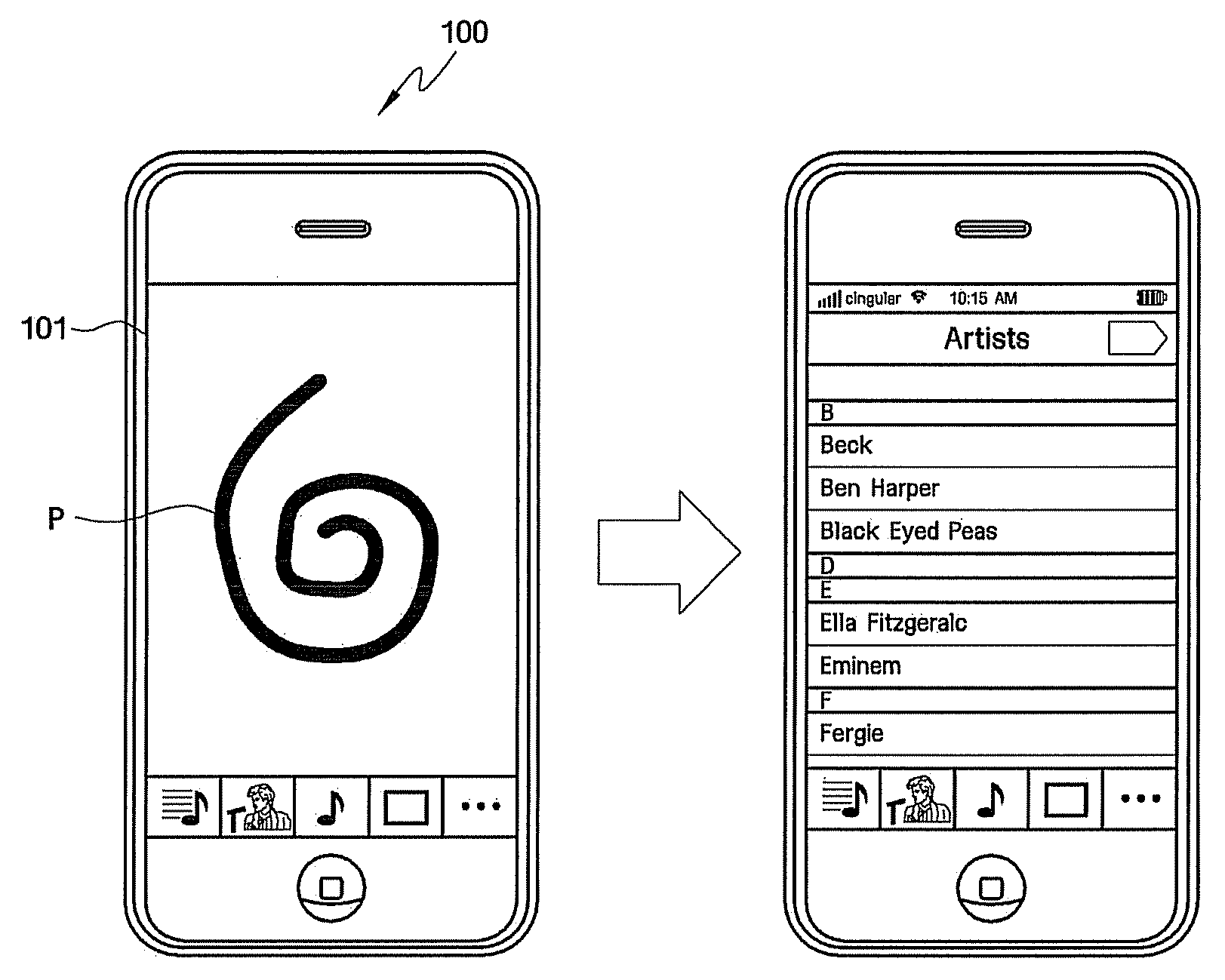

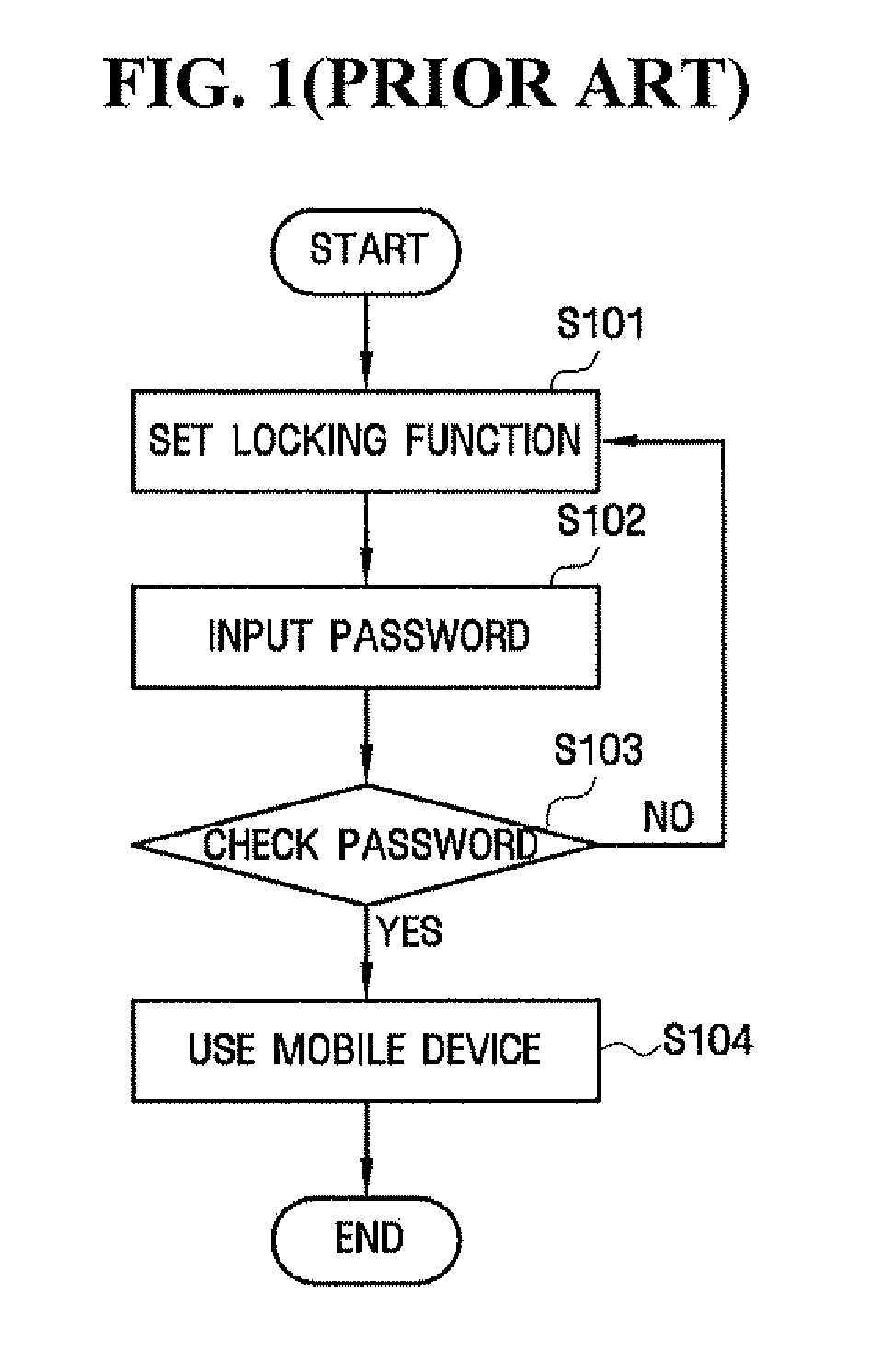

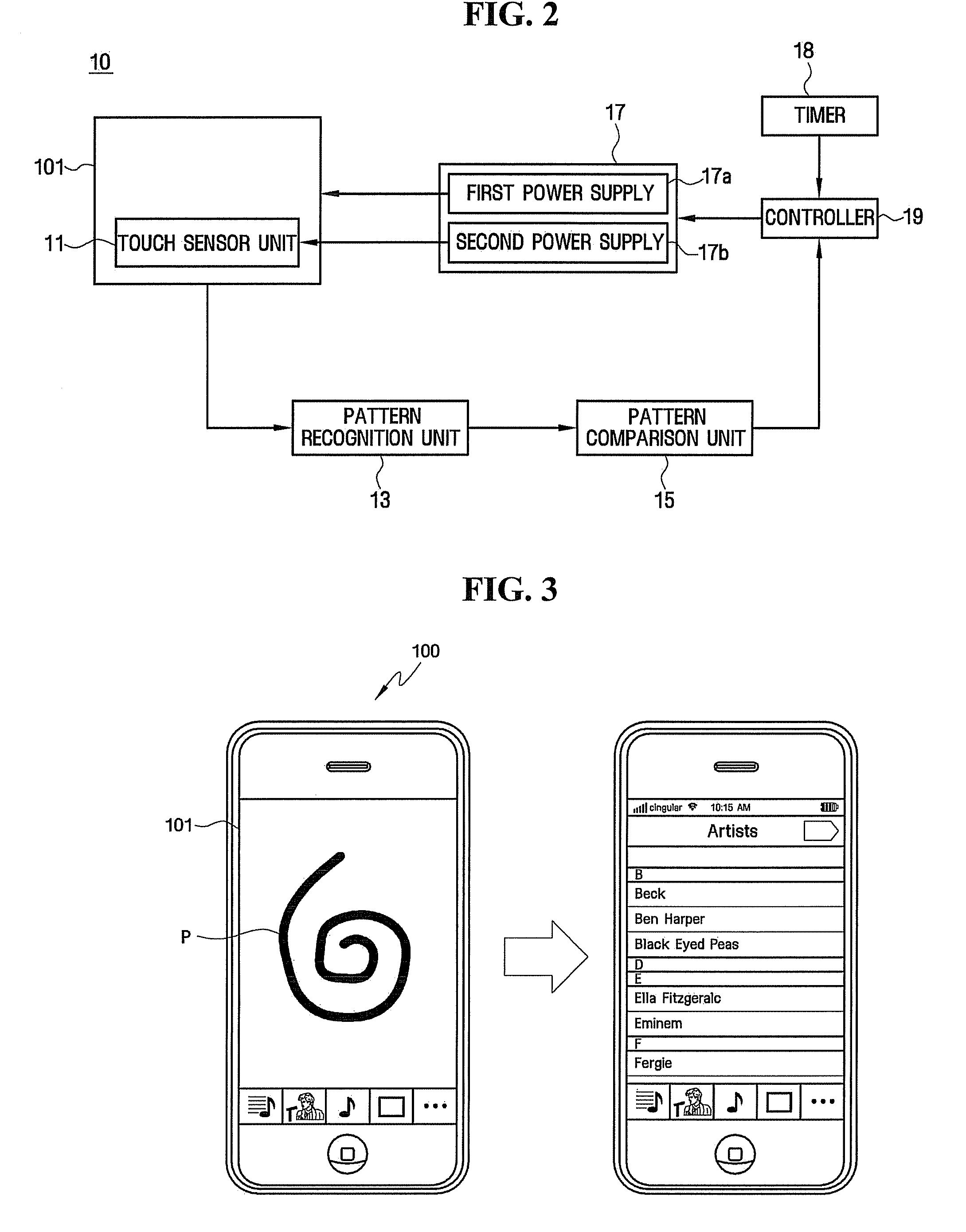

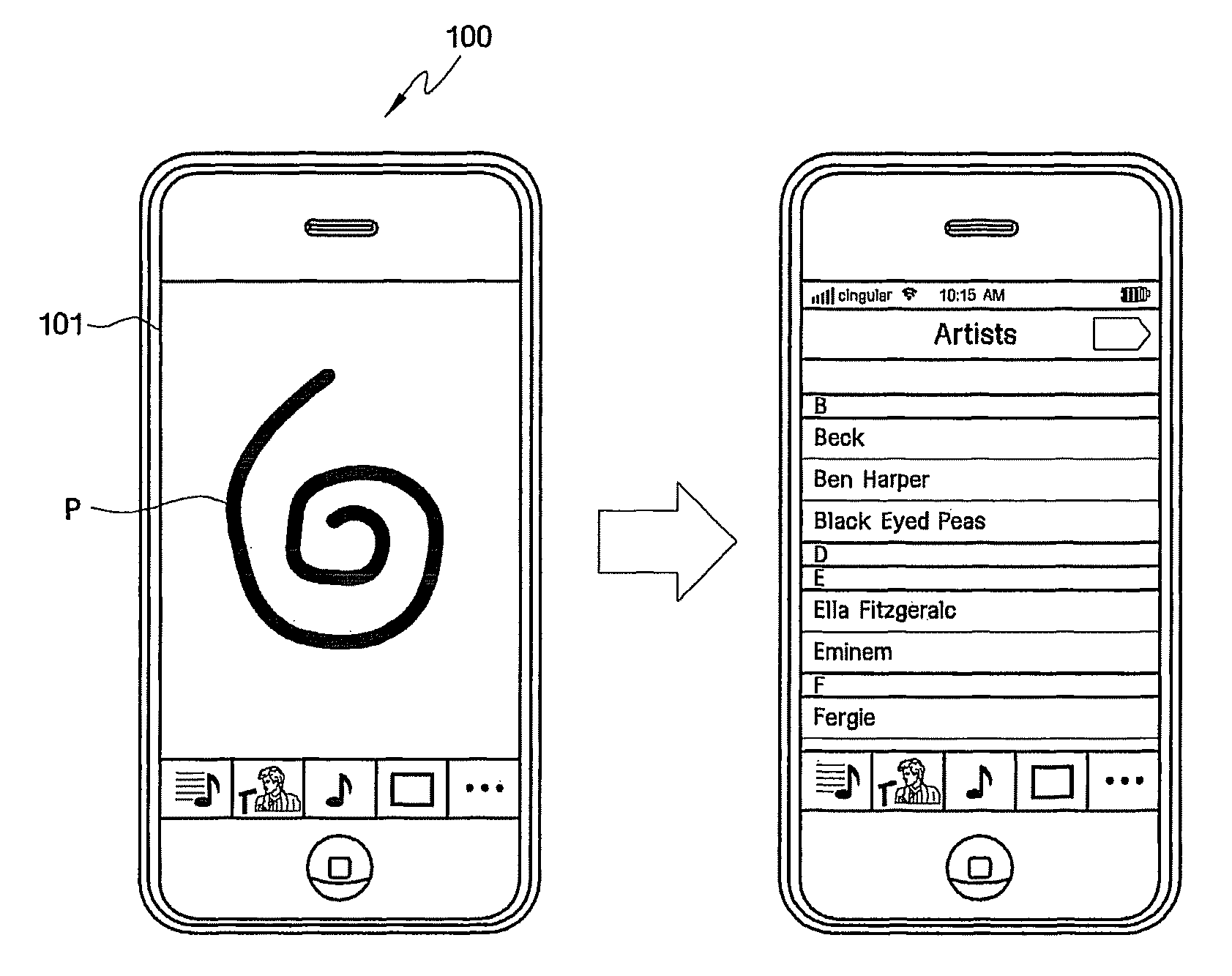

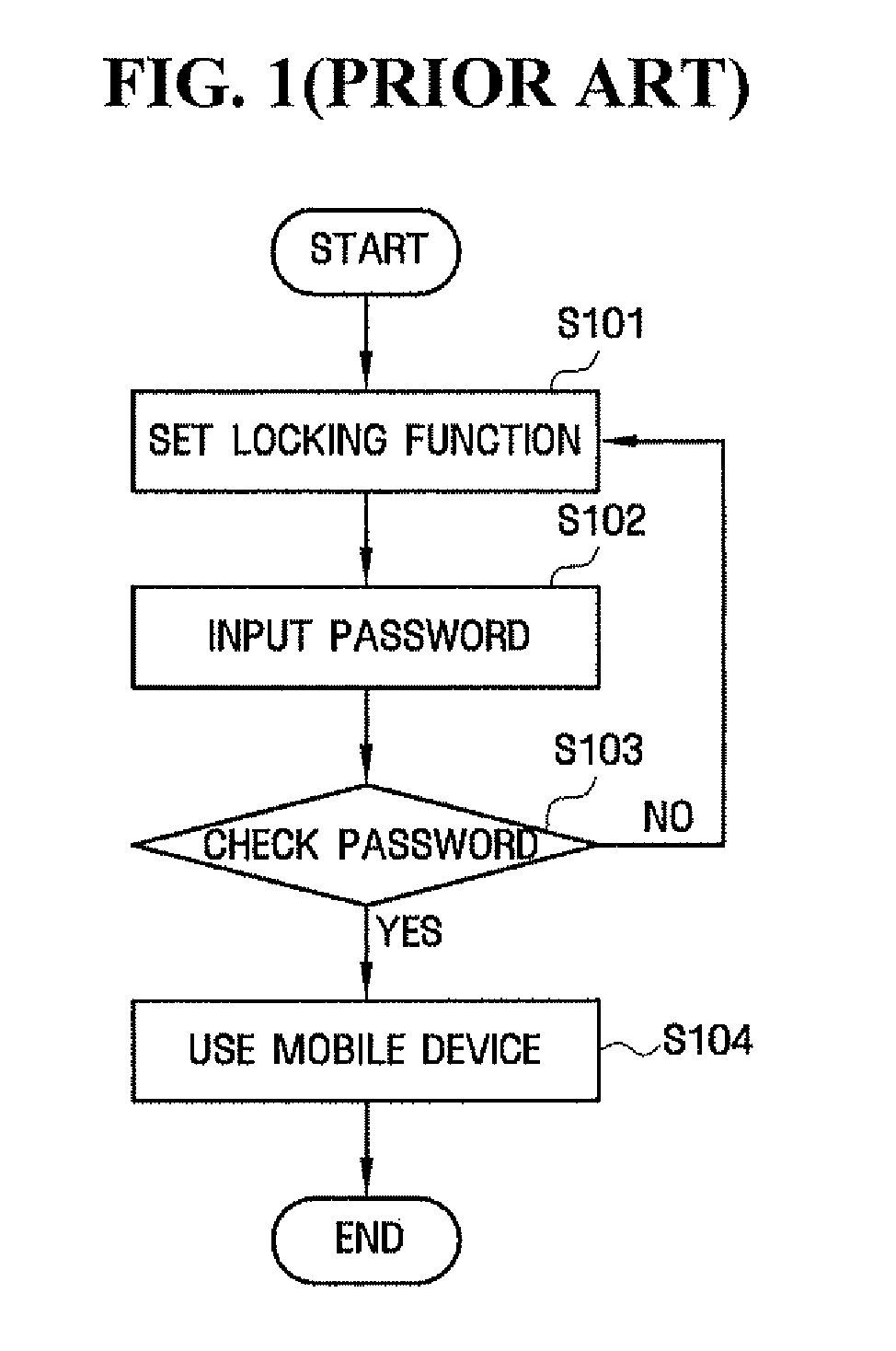

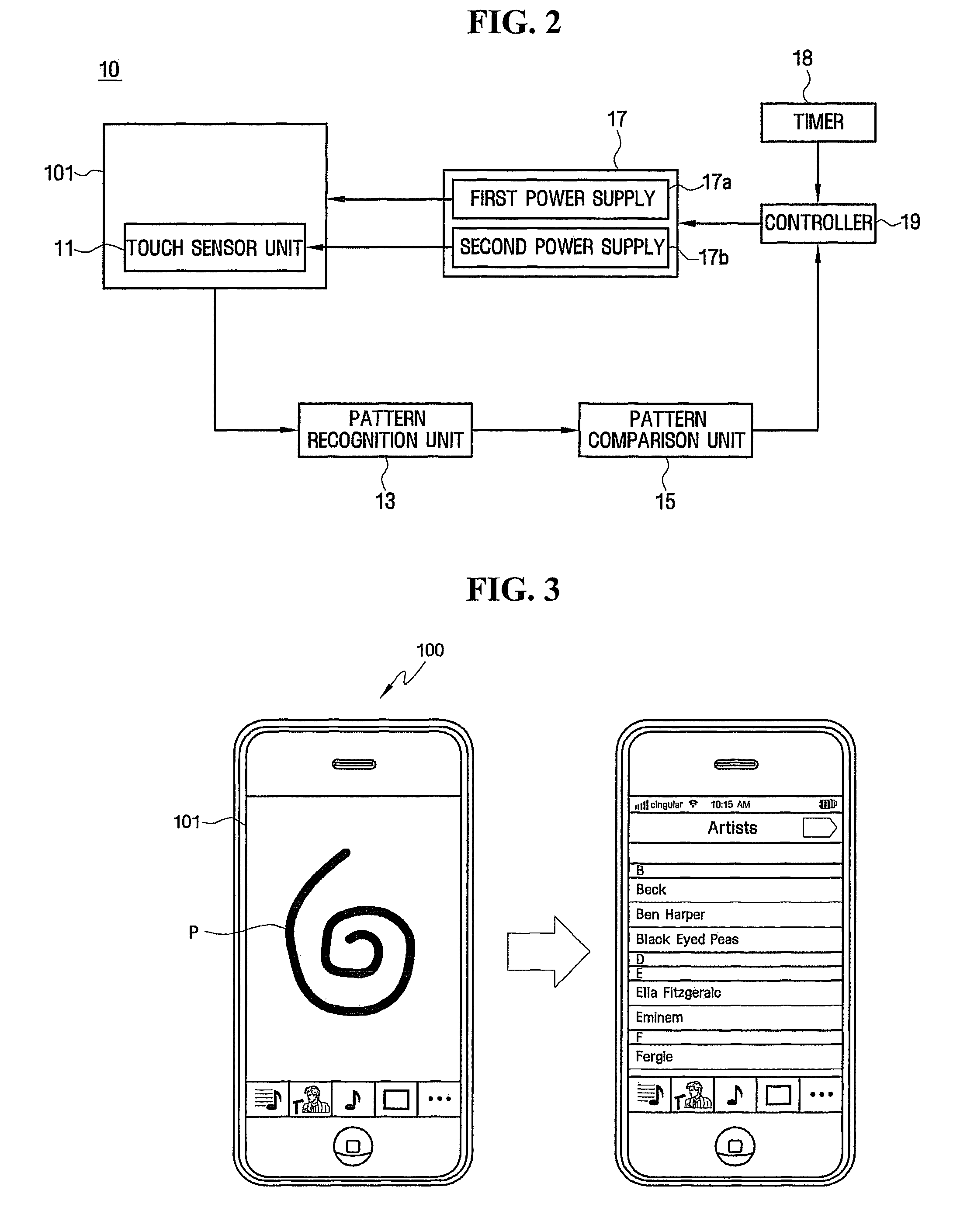

Apparatus for unlocking mobile device using pattern recognition and method thereof

ActiveUS20090149156A1Improve user convenienceEnsure security improvementElectric signal transmission systemsUnauthorised/fraudulent call preventionPattern recognitionLiquid-crystal display

An apparatus and method for unlocking a mobile device using pattern recognition are provided. The apparatus includes a touch sensor unit sensing a predetermined pattern touch-input to a liquid crystal display (LCD) unit, a pattern recognition unit recognizing information about the input pattern sensed by the touch sensor unit, a pattern comparison unit comparing information about the input pattern recognized by the pattern recognition unit with information about a predetermined pattern set by a user, and a controller controlling supply of power to the LCD unit to enable the user to use the mobile device if the input pattern and the predetermined pattern are equal to each other as compared by the pattern comparison unit.

Owner:SAMSUNG ELECTRONICS CO LTD

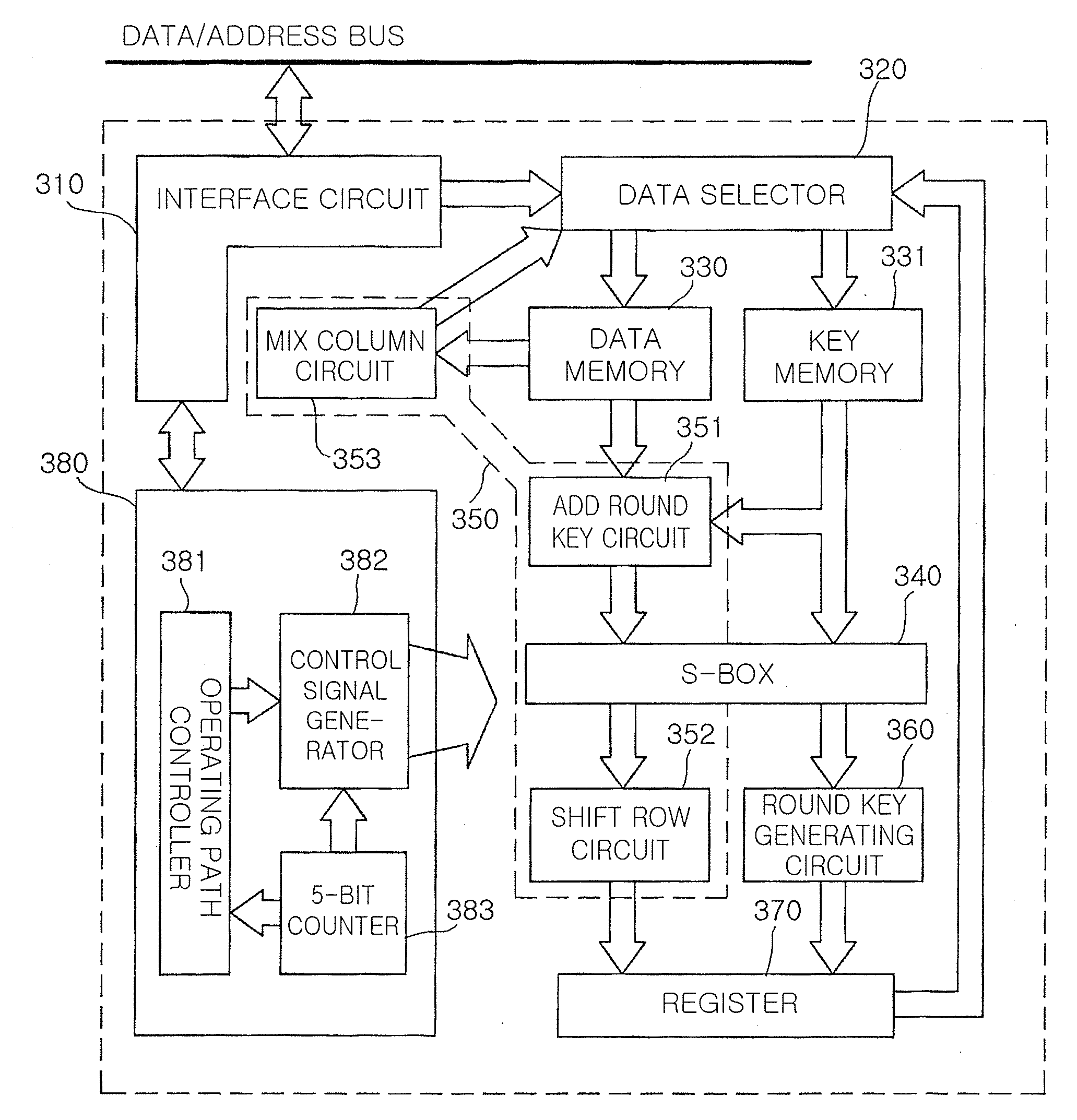

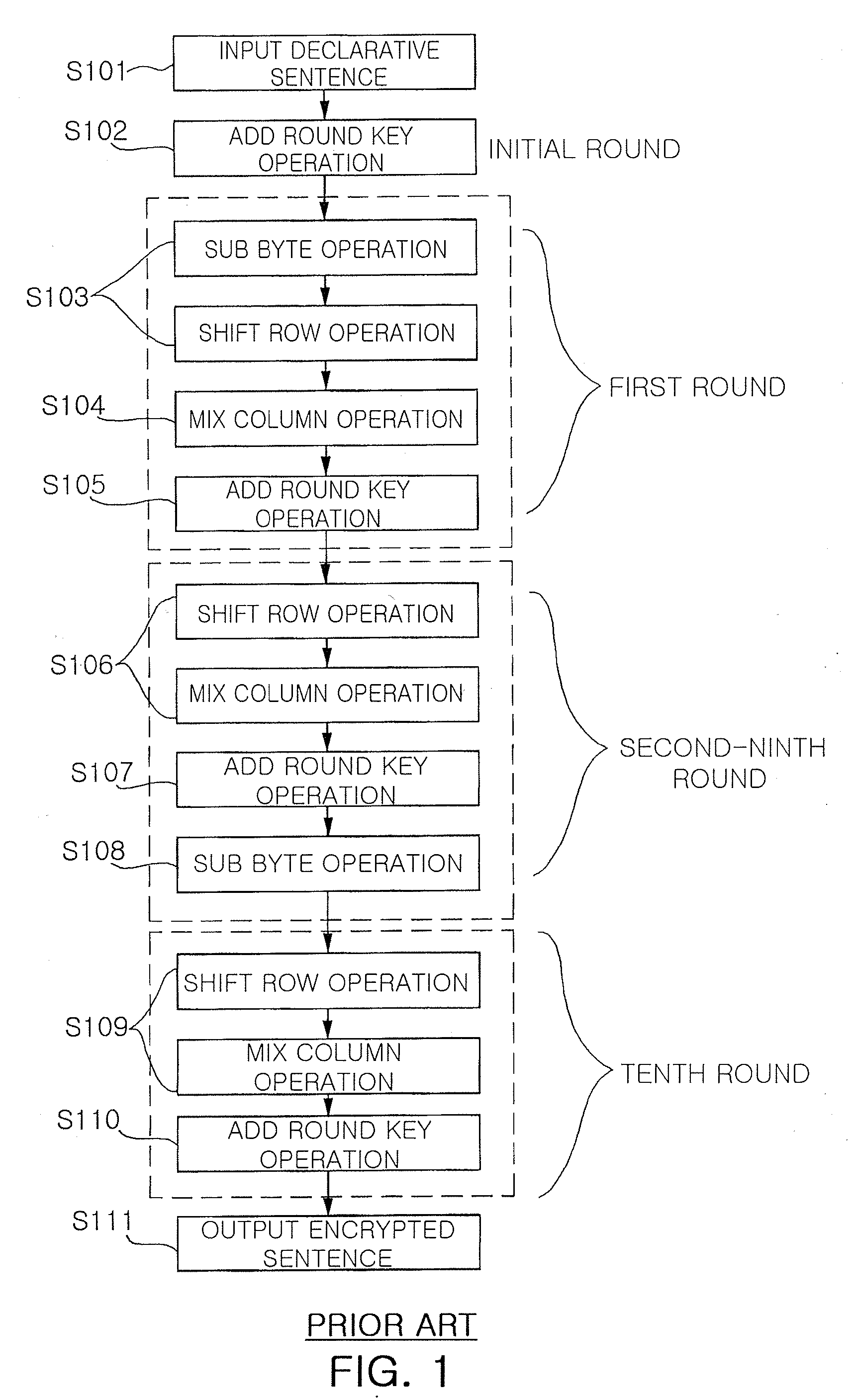

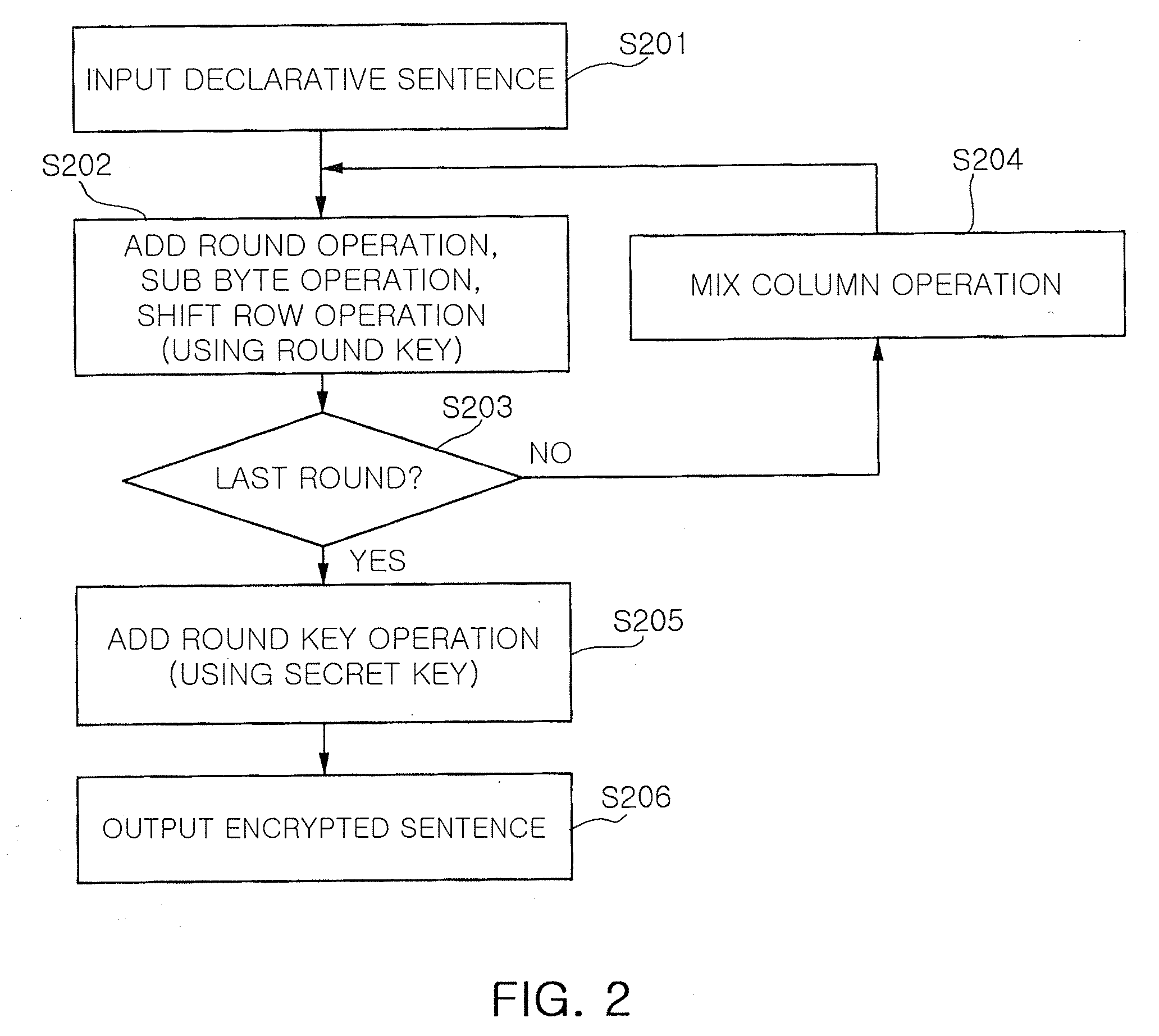

Apparatus and method for low power AES cryptographic circuit for embedded system

InactiveUS20080019524A1Reduce power consumptionPrevent unnecessary power consumptionSecuring communicationByte8-bit

Provided are an apparatus and a method for a low power AES cryptographic circuit for an embedded system. The apparatus and method allows each round operation to be performed in an order of an add round operation, a sub byte operation, a shift row operation, and a mix column operation in order to realize a small circuit area by making maximum reuse of designed element modules. When data is input, on the first place, operations are repeated in the above order from a first round to a round right before a last round. During a last round, only an add round key operation and a sub byte operation, and a shift row operation are performed, and then an add round key operation using a secret key is performed. At this point, each operation is performed on data by a 8-bit unit.

Owner:ELECTRONICS & TELECOMM RES INST

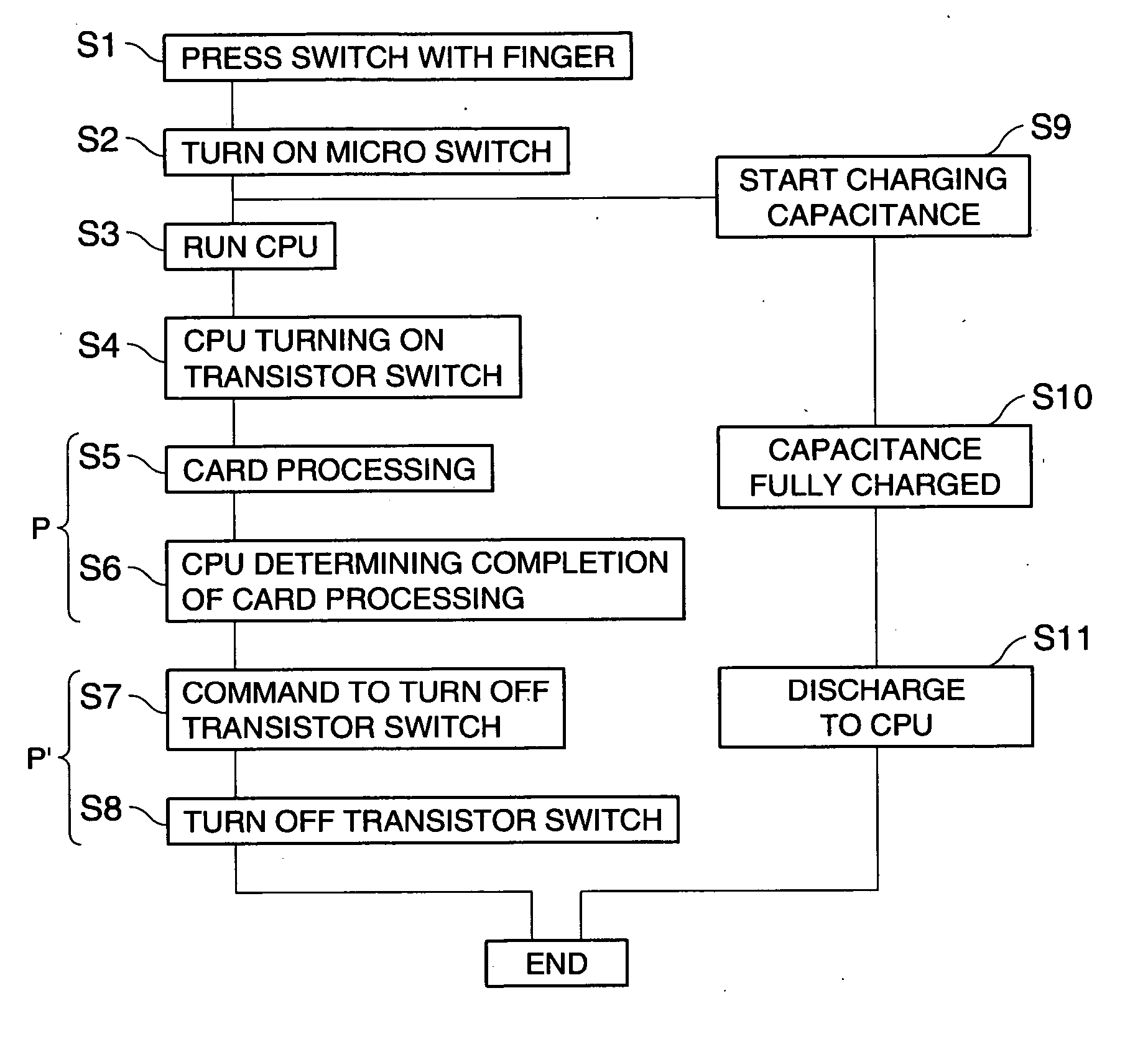

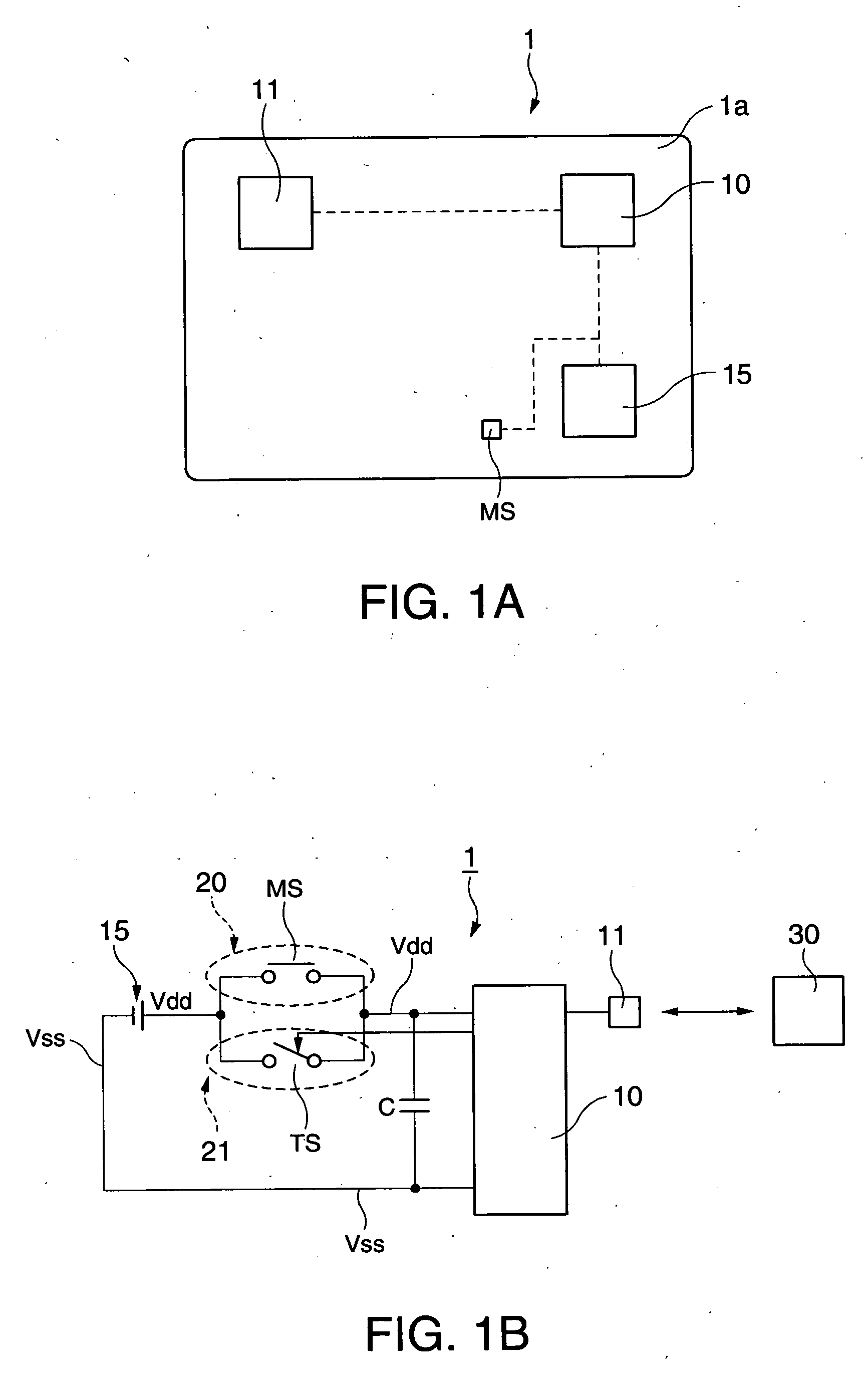

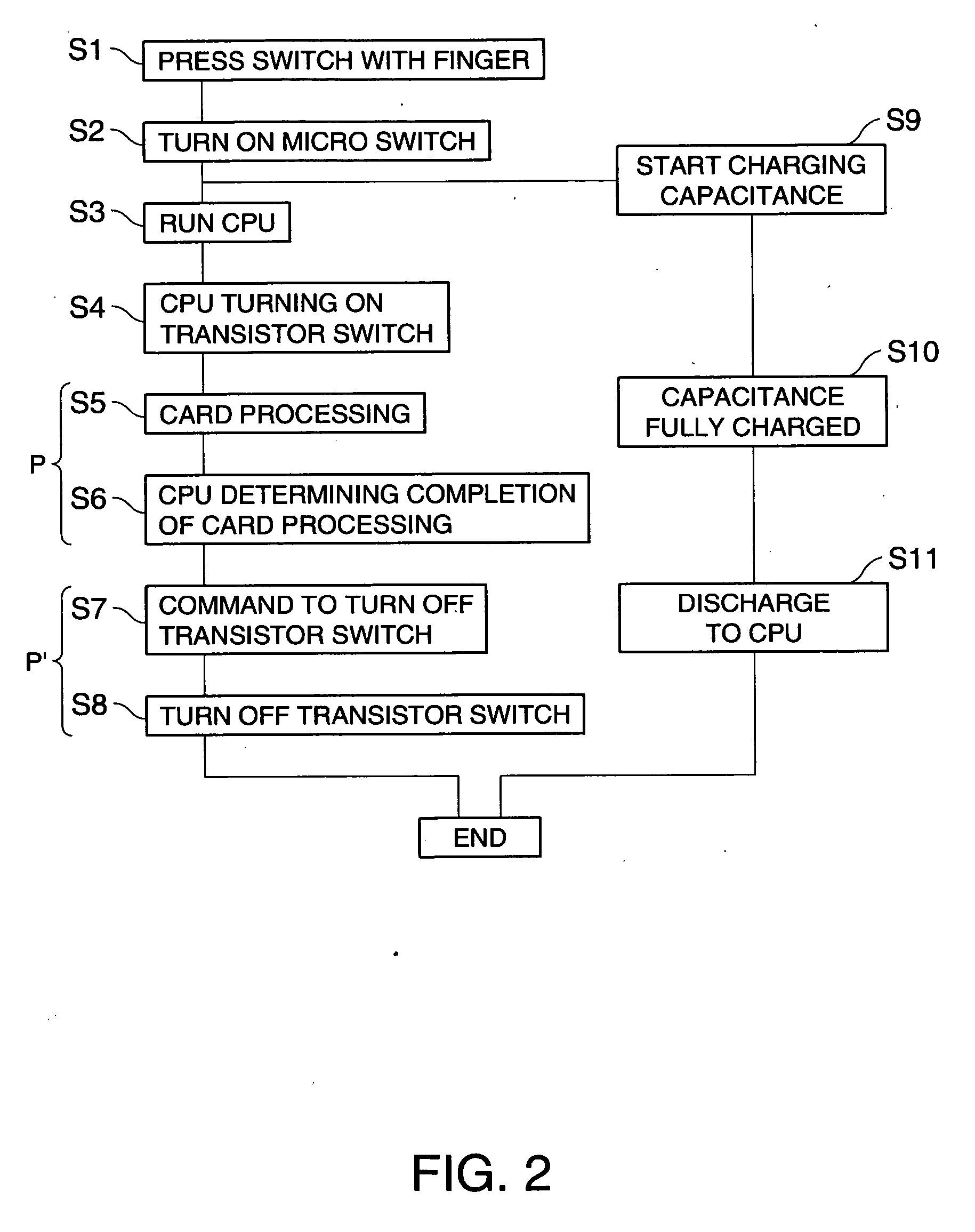

Portable information device

InactiveUS20060190737A1Keep for a long timeEfficiently use powerAcutation objectsComputer security arrangementsControl systemInformation device

A portable information device having a central processing unit and a power source coupled to the central processing unit and driving the central processing unit, comprises: an external control system circuit provided between the power source and the central processing unit, and providing power supply from the power source to the central processing unit by an external input; and an autonomous control system circuit providing power supply from the power source to the central processing unit under control of the central processing unit; the external control system circuit and the autonomous control system circuit being coupled in parallel with each other, the external control system circuit including a mechanical switch turned on and off by an external input, and the autonomous control system circuit including a transistor switch turned on and off under control of the central processing unit.

Owner:SEIKO EPSON CORP

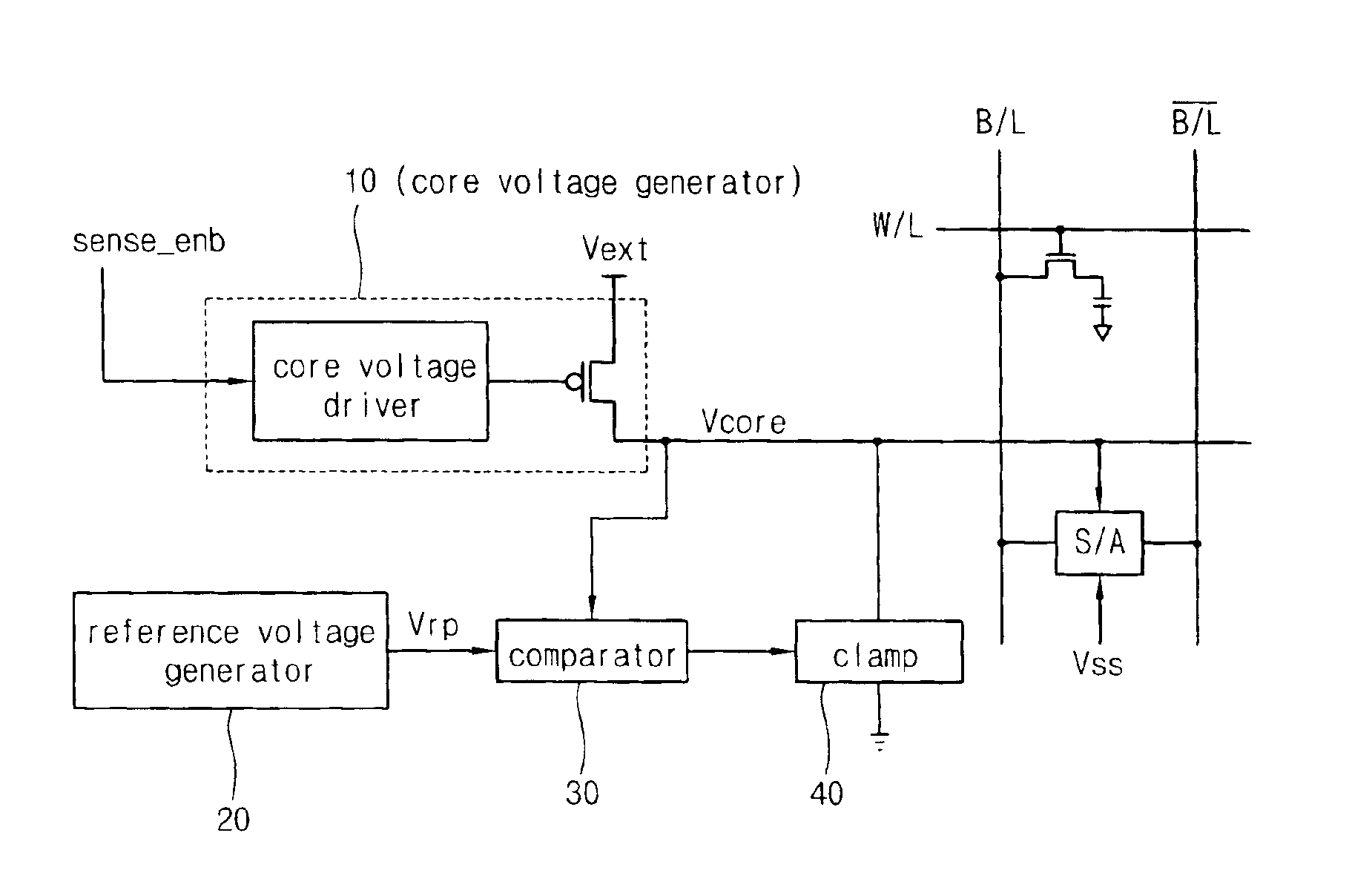

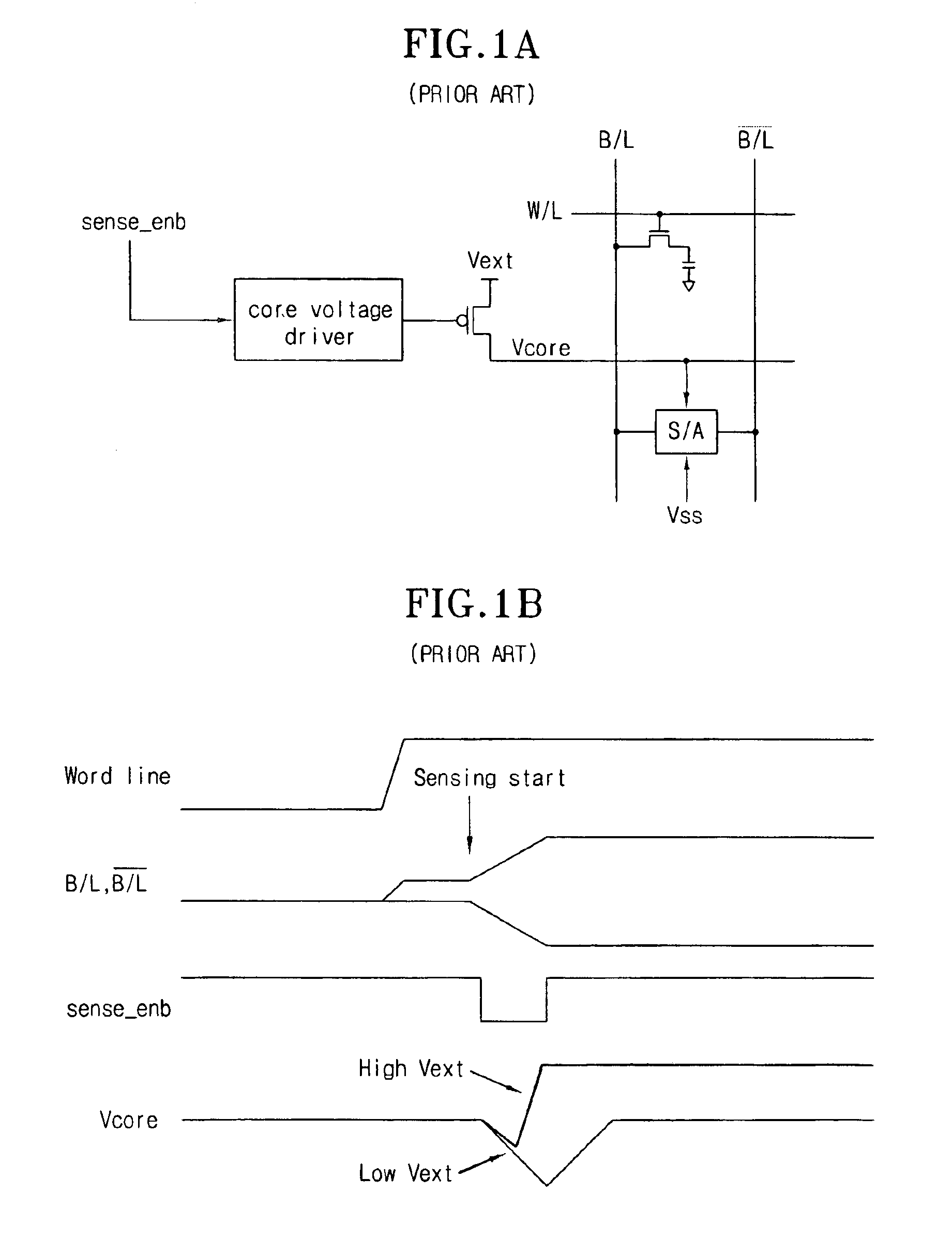

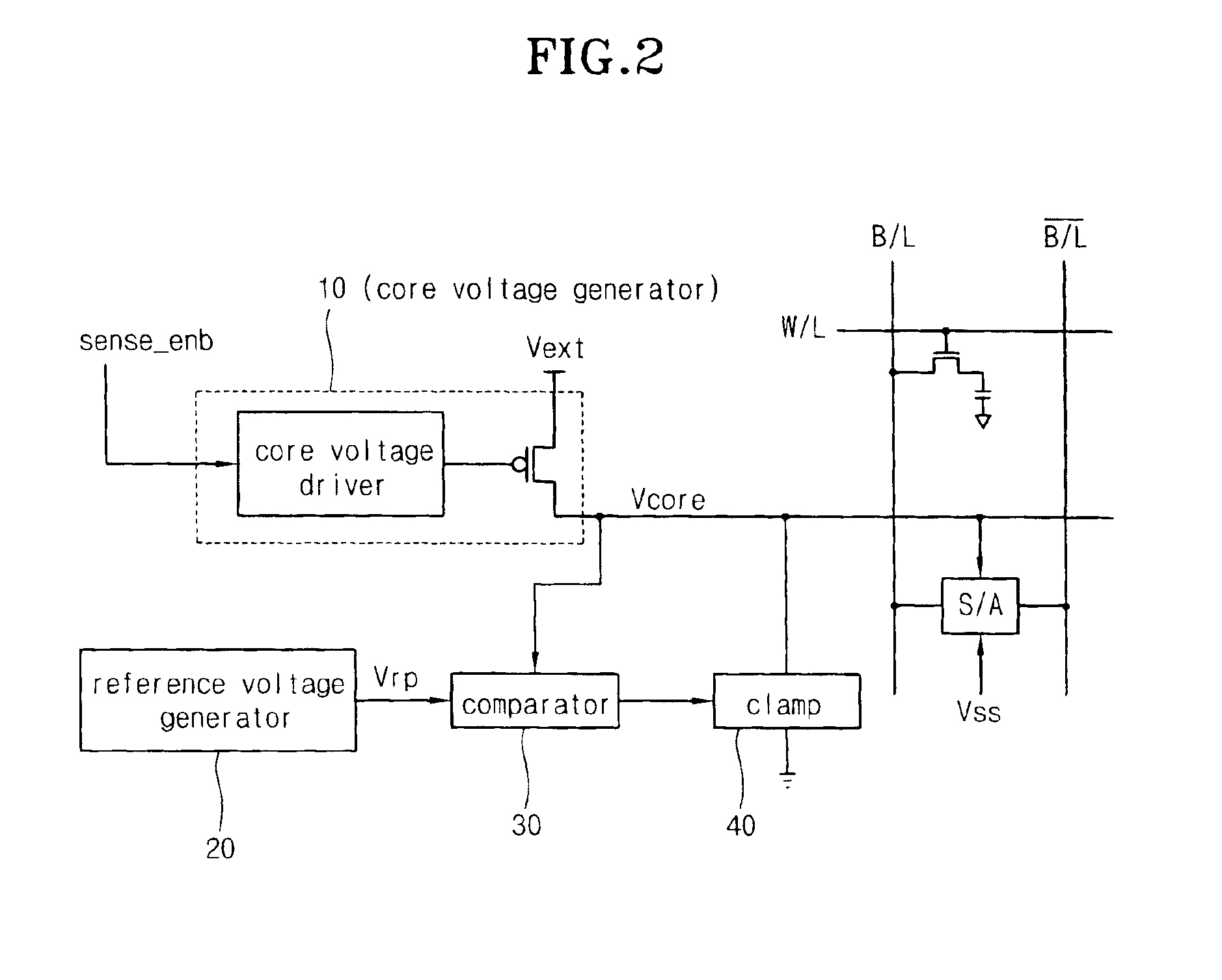

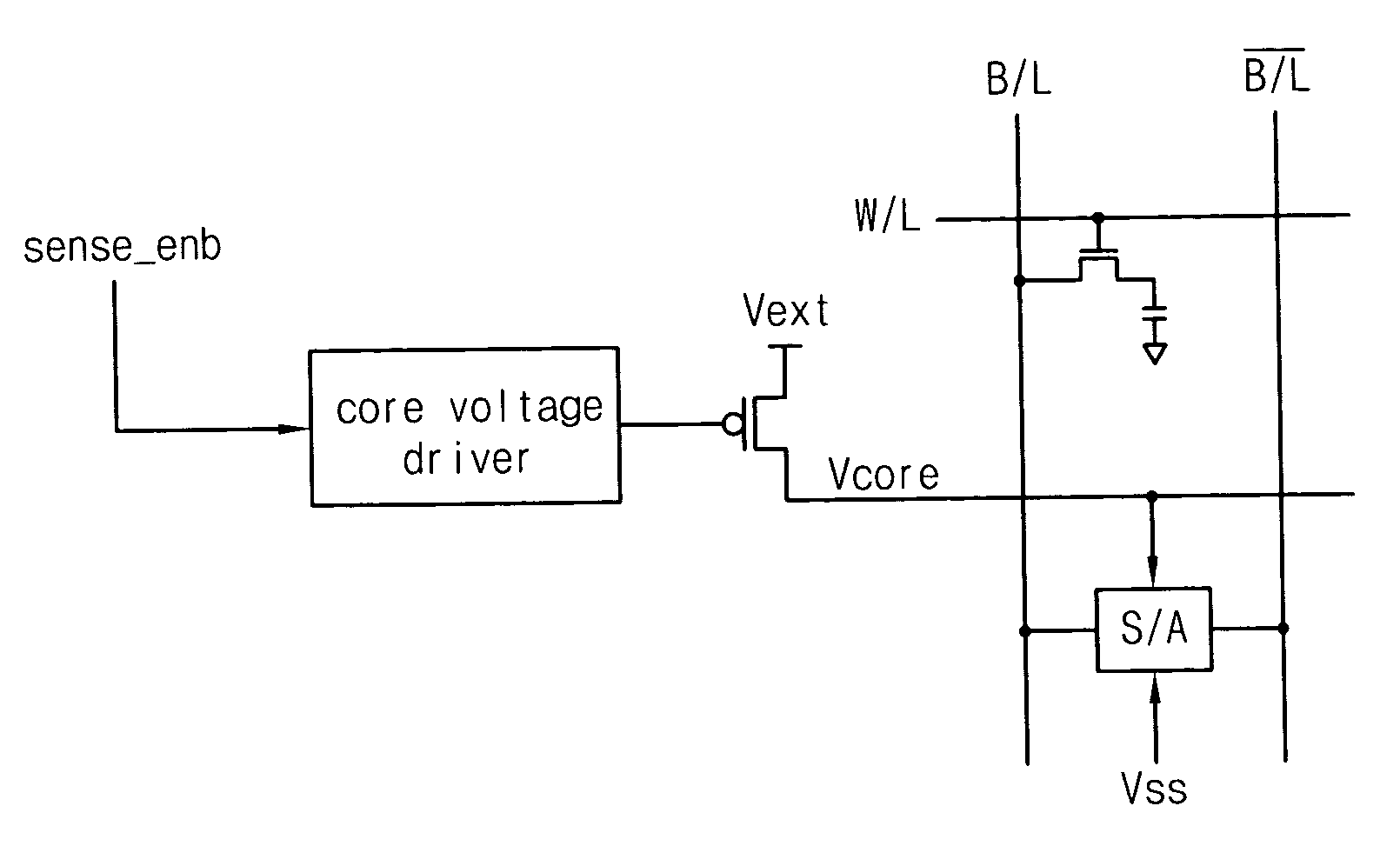

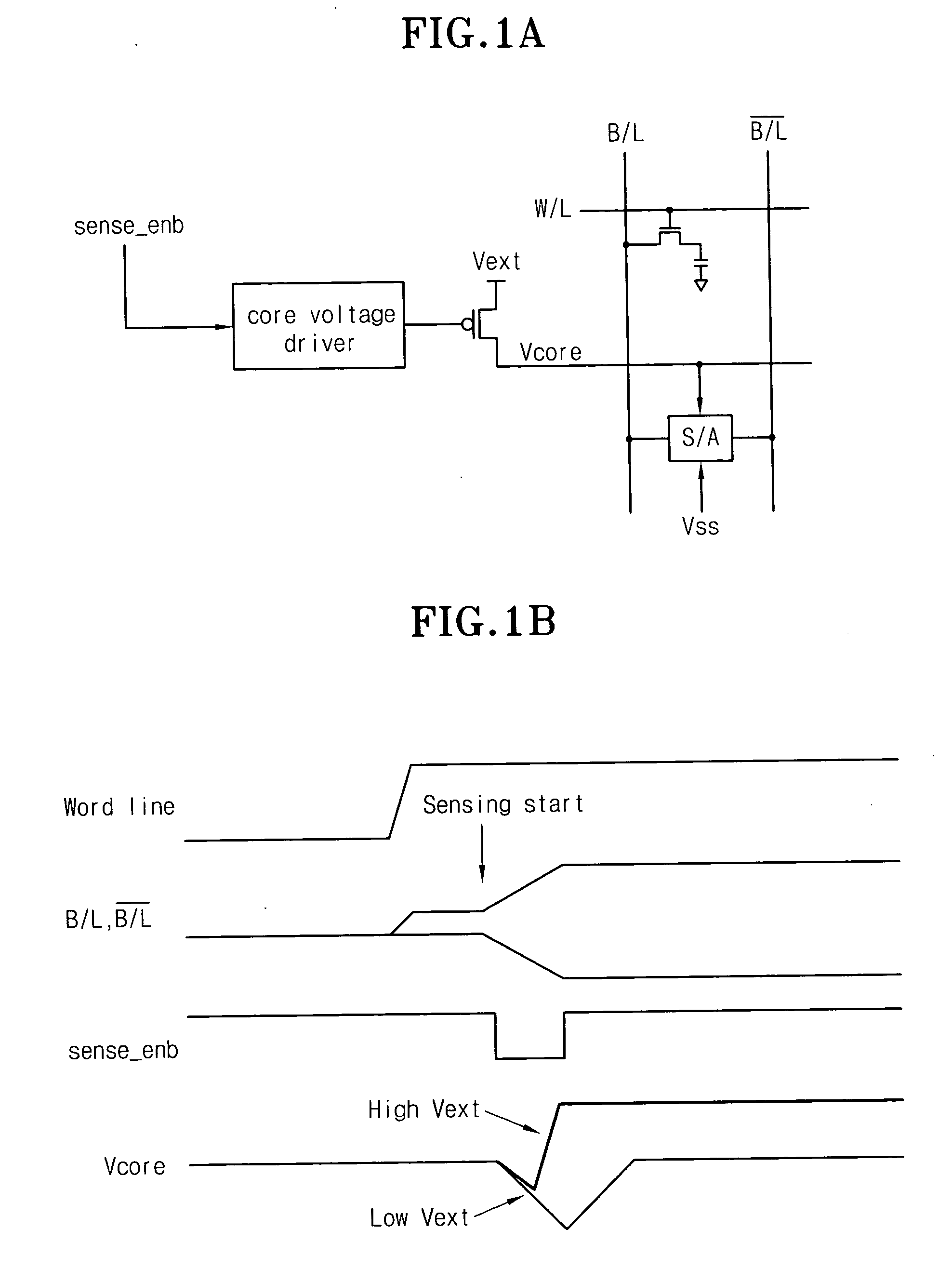

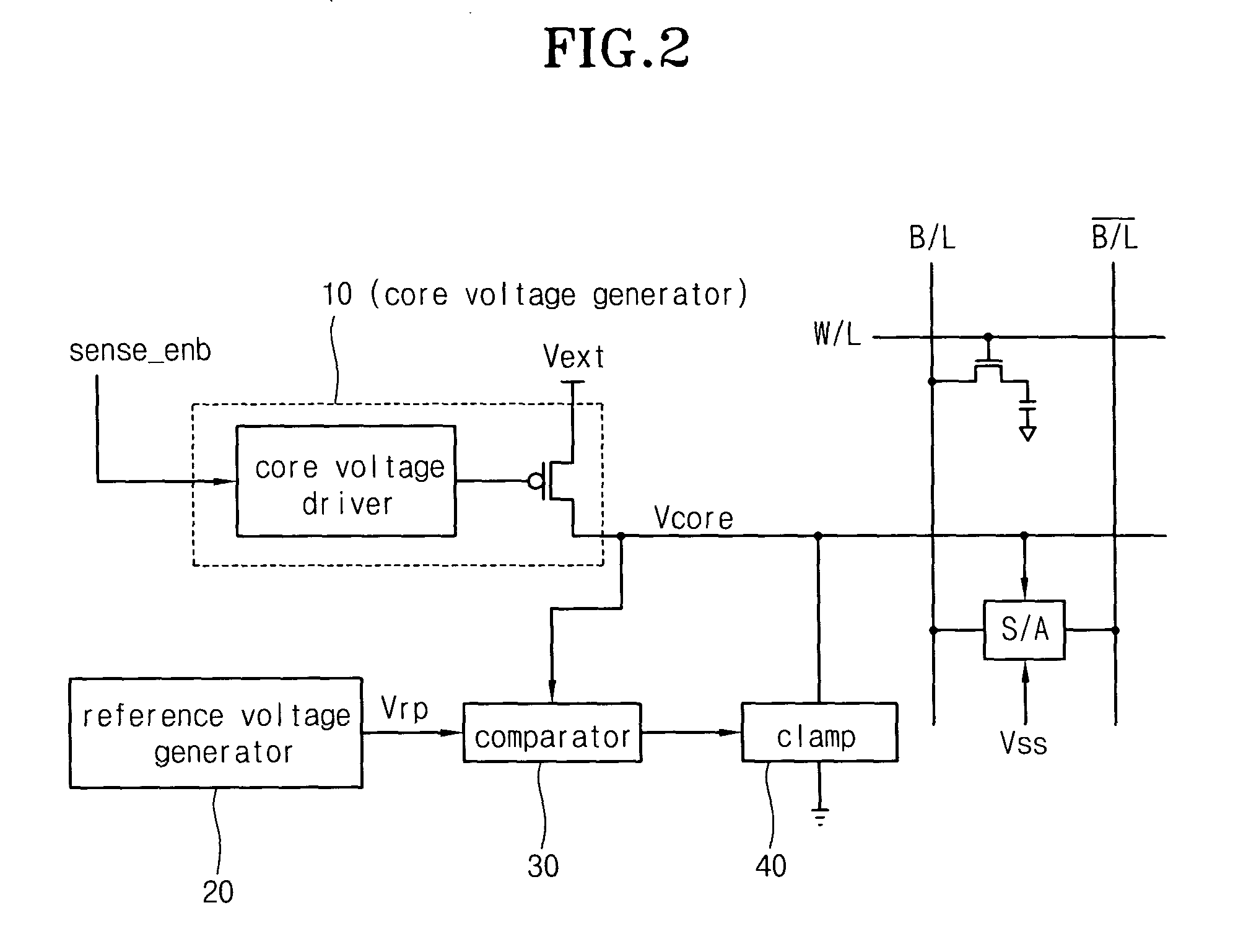

Driving voltage controller of sense amplifiers for memory device

InactiveUS6891773B2Prevent unnecessary power consumptionStable voltageDigital storageVoltage generatorAudio power amplifier

Disclosed is a driving voltage controller of sense amplifiers for a memory device which prevents the sense amplifier from being over-driven when an external power voltage is used for an internal driving voltage of the sense amplifier. Reference voltage generator generates a reference voltage. Core voltage generator generates a core voltage to be used for driving voltage of sense amplifier. Comparator compares the core voltage generated by core voltage generator with the reference voltage generated by reference voltage generator. Clamp adjusts a level of the core voltage generated by the core voltage generator based on an output signal of comparator. In the case where an external power used for a driving voltage of the sense amplifier is excessively high, the comparator compares the external power voltage with the reference voltage. When the driving voltage of sense amplifier exceeds the reference voltage, the clamp drops the driving voltage of sense amplifier. Thus, the core voltage can be stably supplied.

Owner:SK HYNIX INC

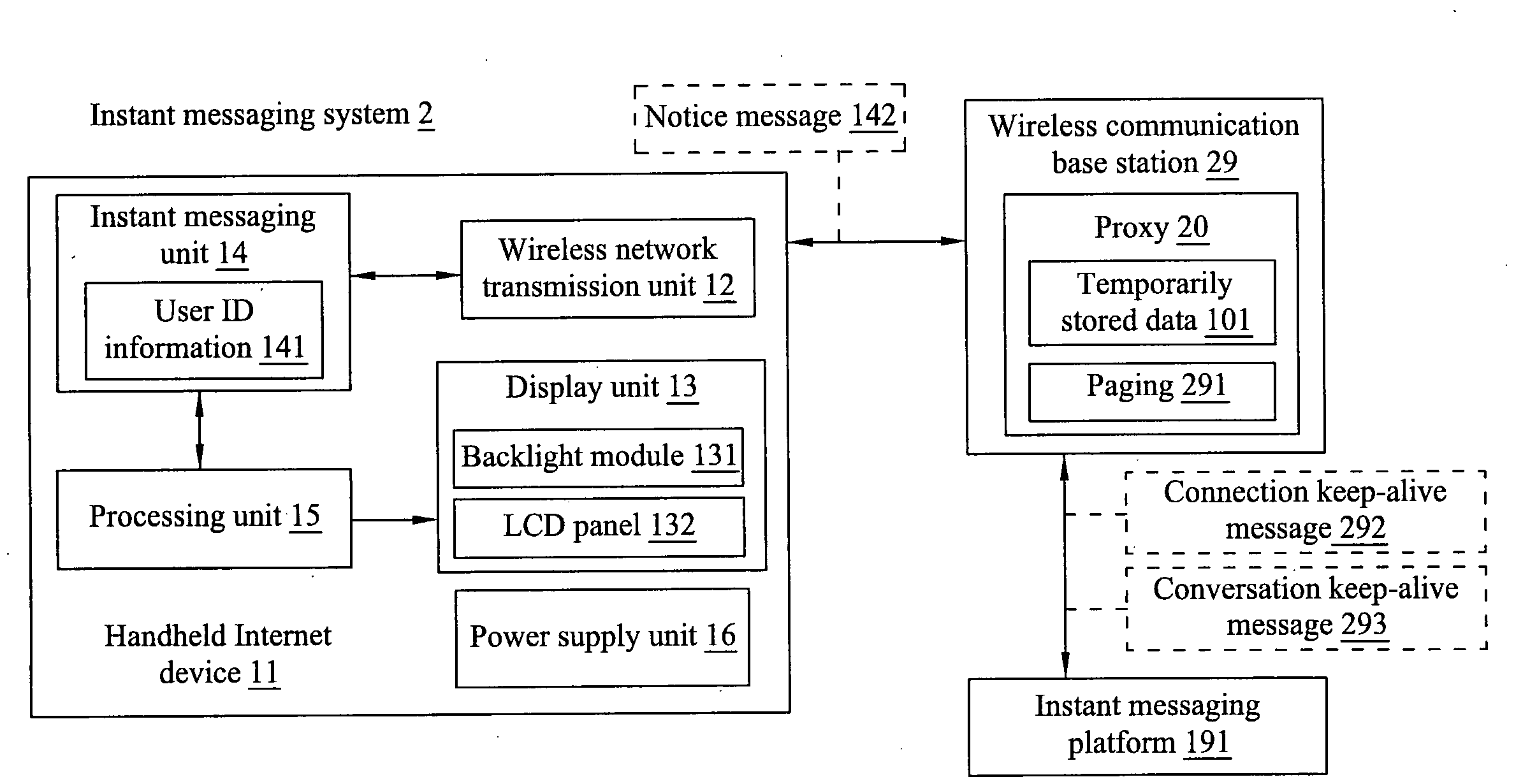

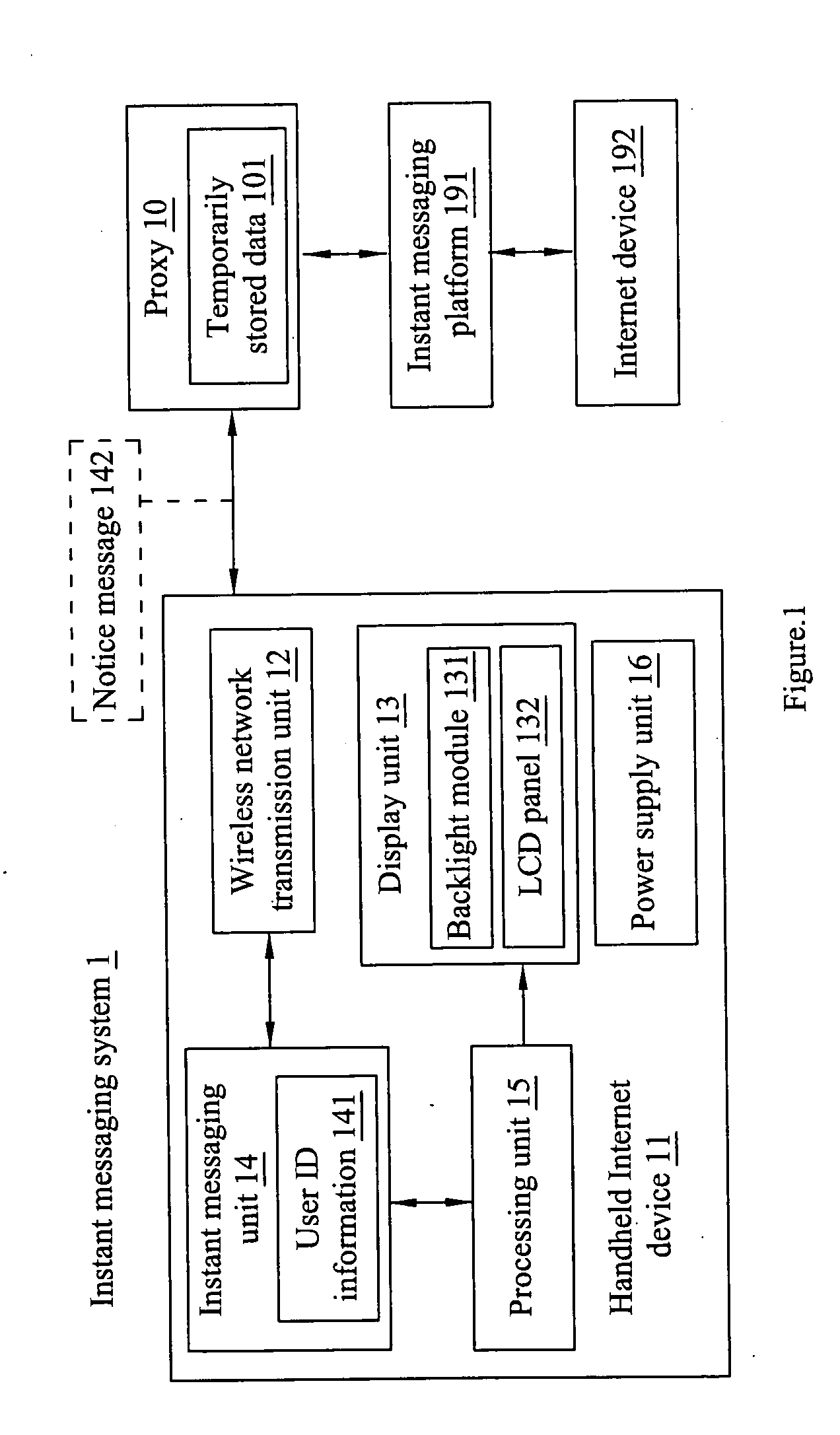

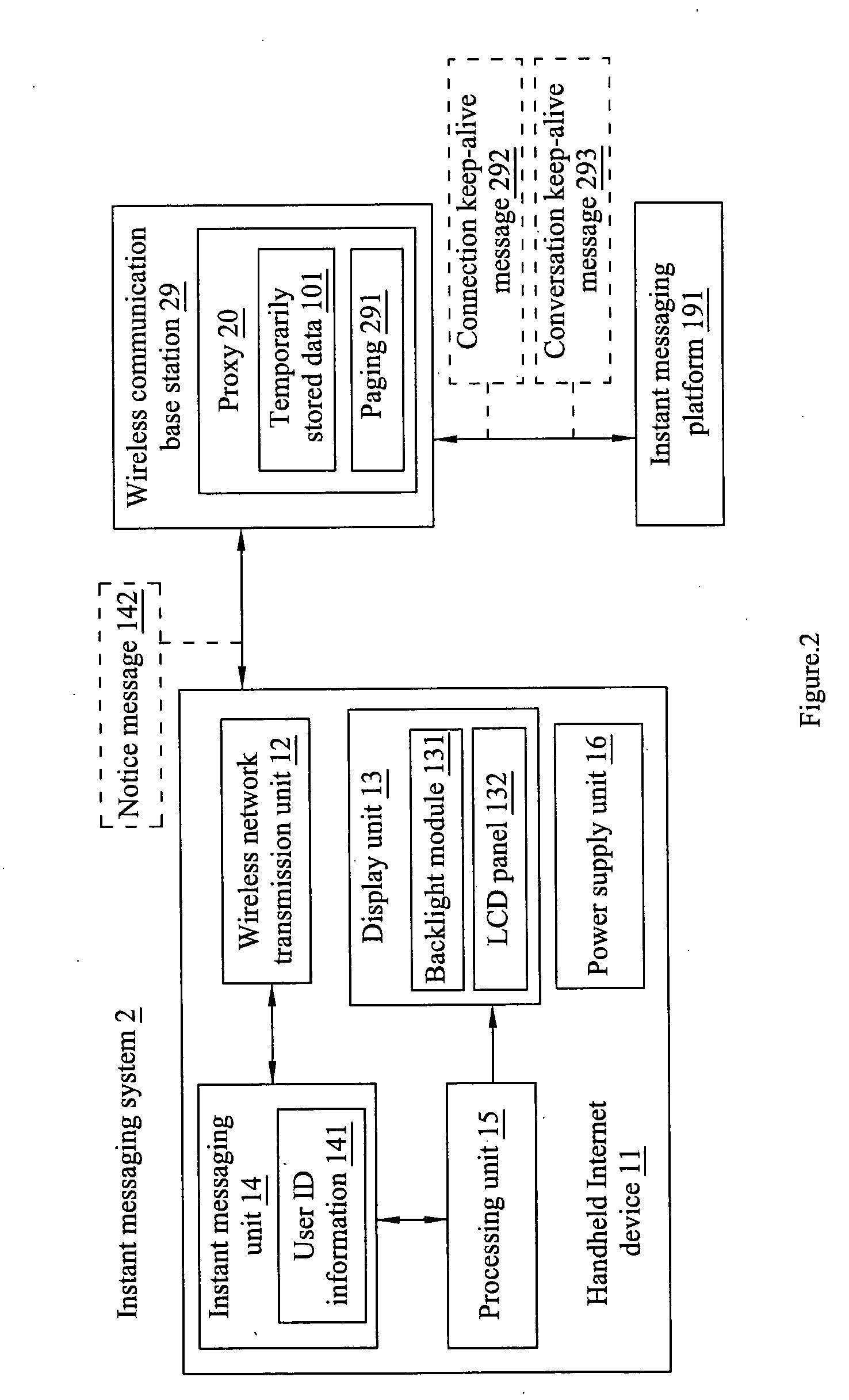

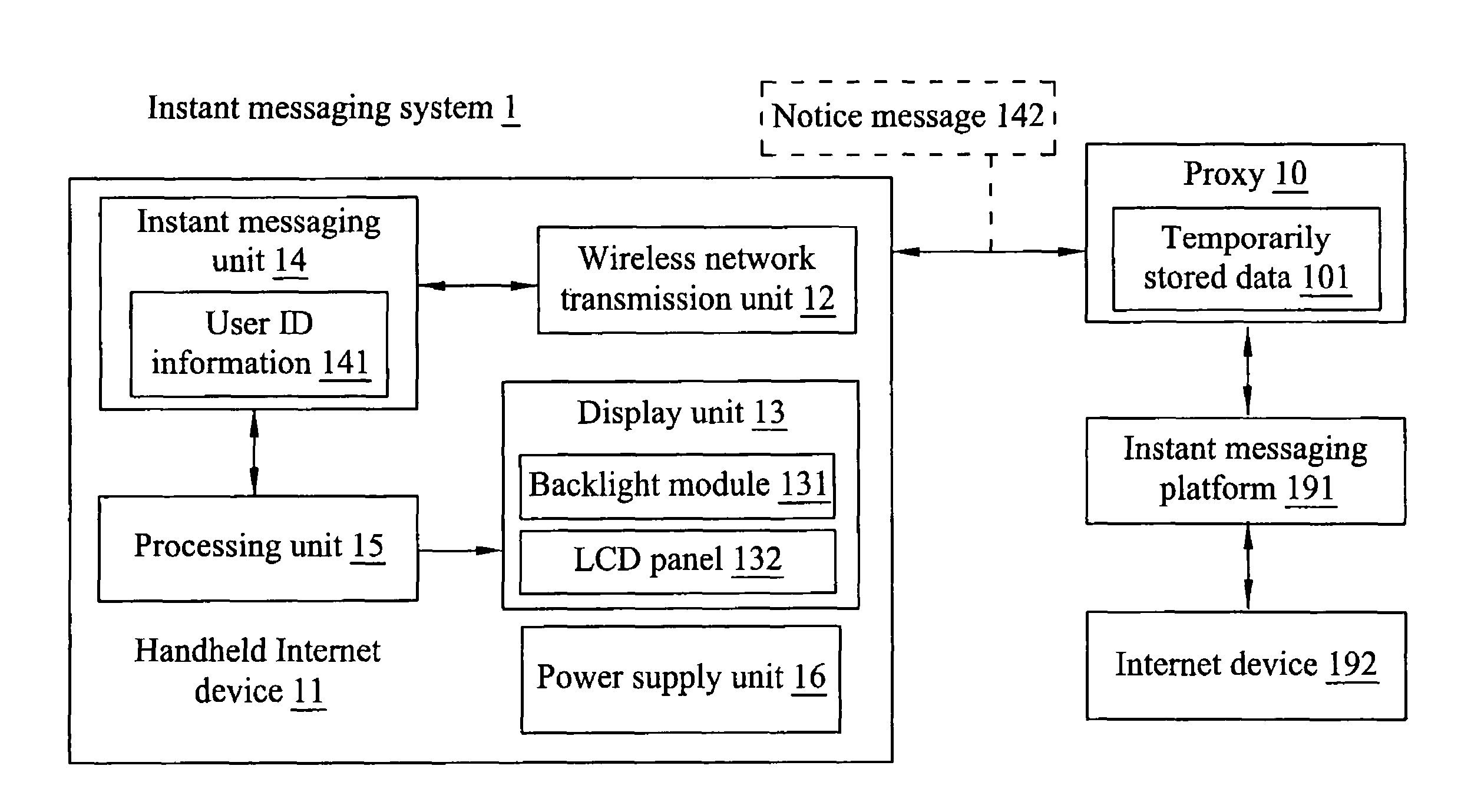

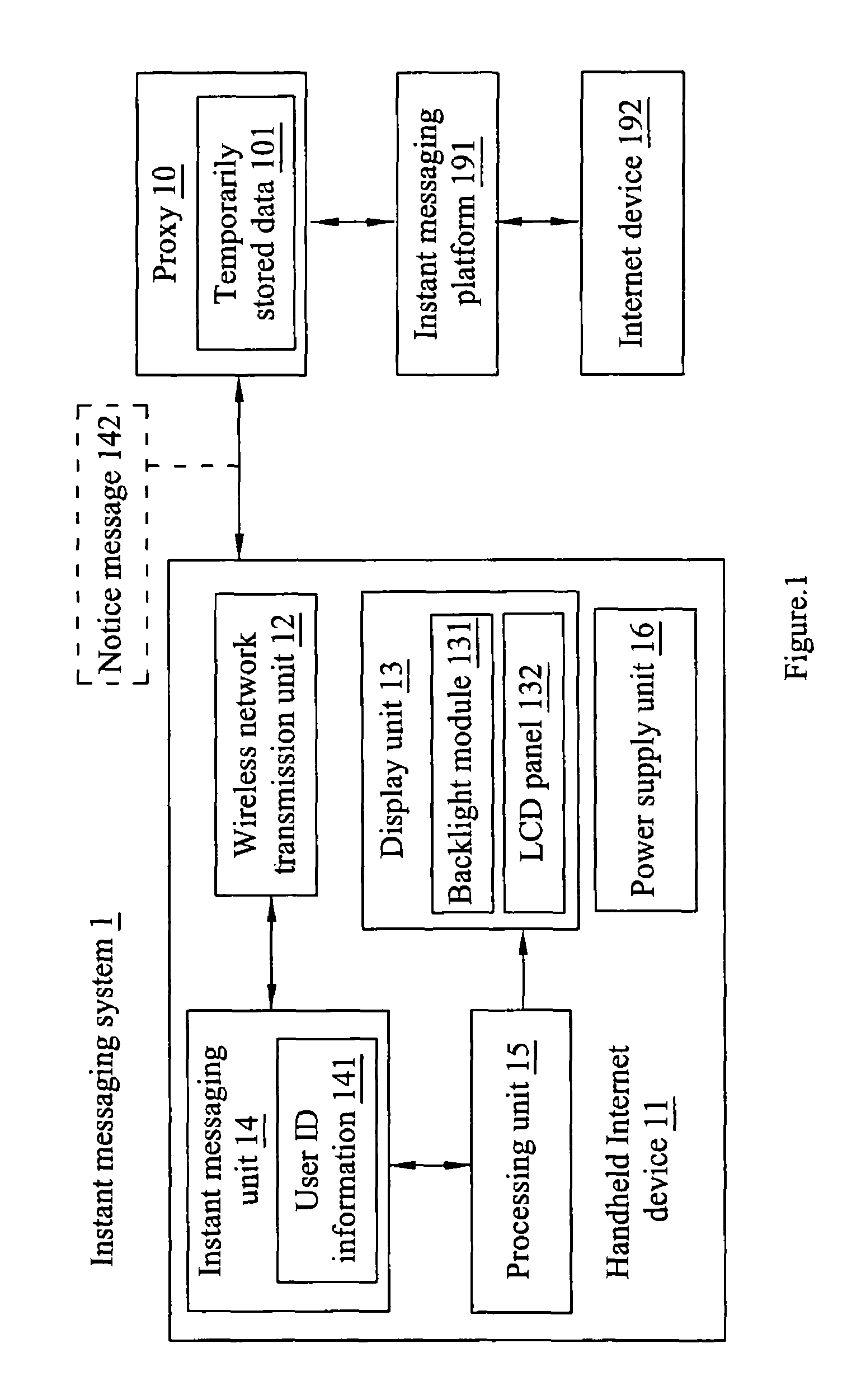

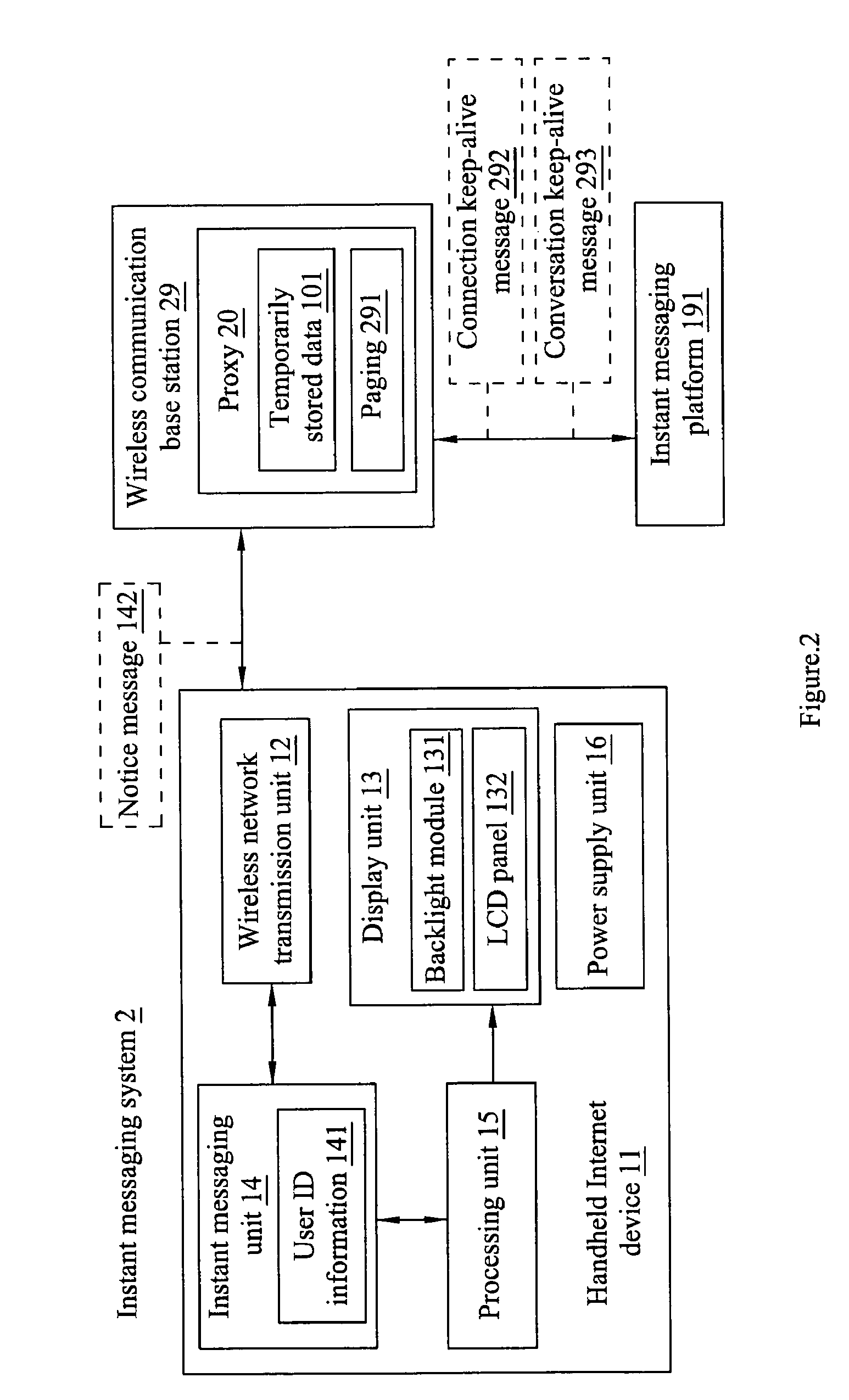

Power saving method of portable internet device and portable internet device thereof, and instant messaging system using the same

ActiveUS20100042856A1Reduce power consumptionPrevent unnecessary power consumptionPower managementEnergy efficient ICTEmbedded systemPower saving

The present invention discloses a power saving method of a portable Internet device, the portable Internet device and its instant messaging system. If a screen of the portable Internet device is in non-view state, for example, both backlight module and LCD panel are turned off, it means that a user is not viewing the screen, and thus the message update frequency of the instant messaging program is lowered to prevent unnecessary transmission and receiving of wireless signals, so as to reduce power comsumption of the portable Internet device.

Owner:ACER INC

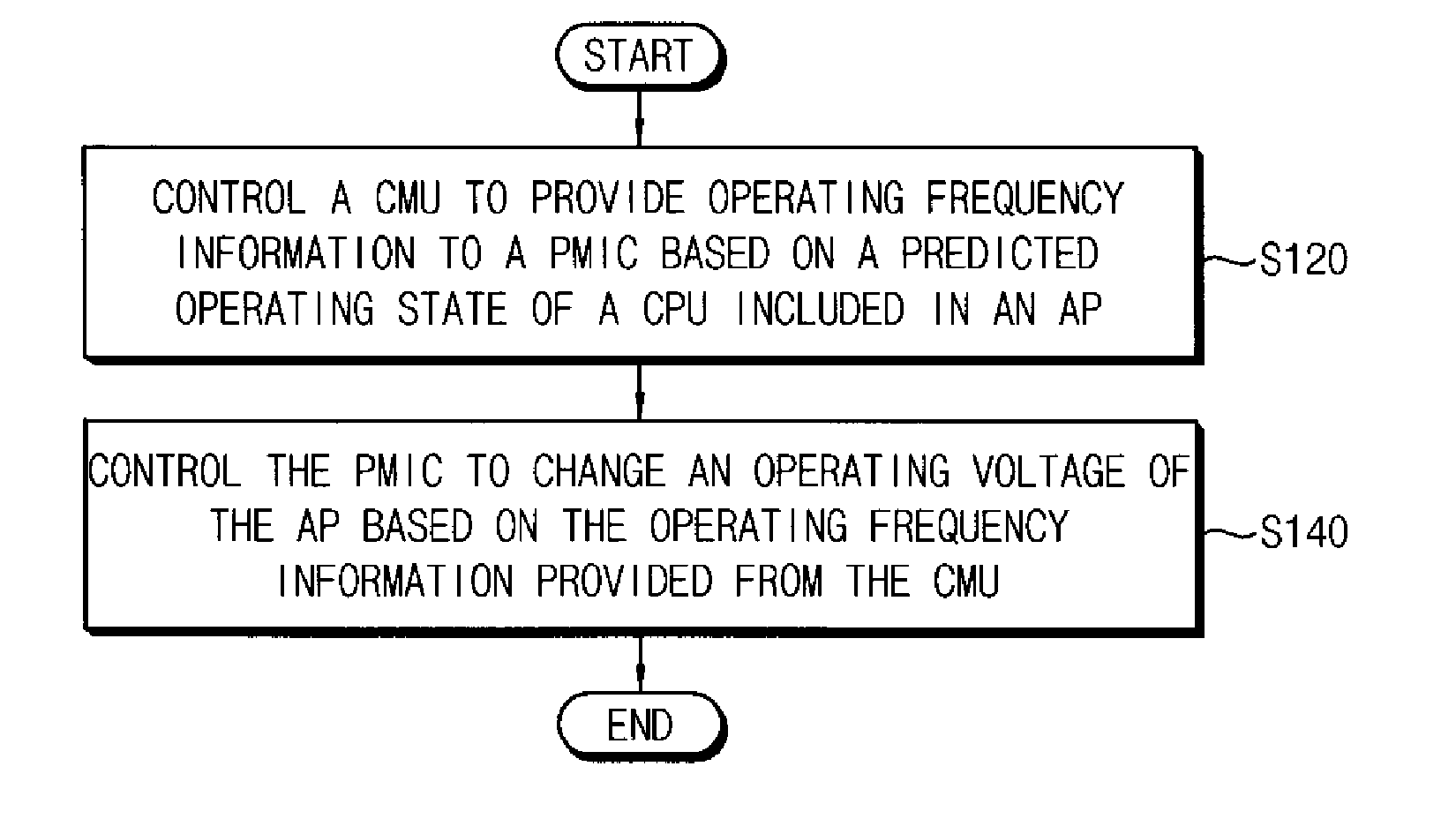

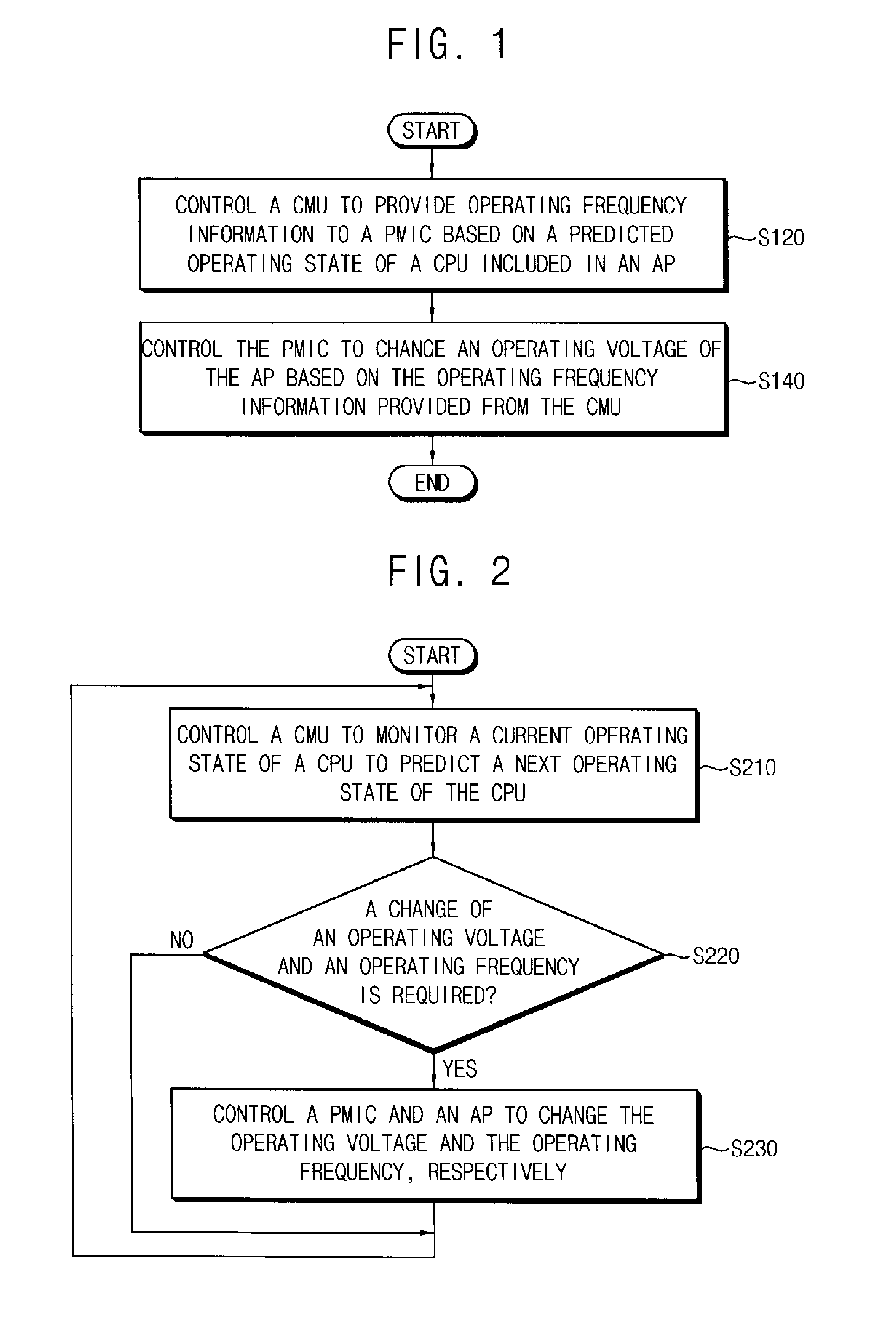

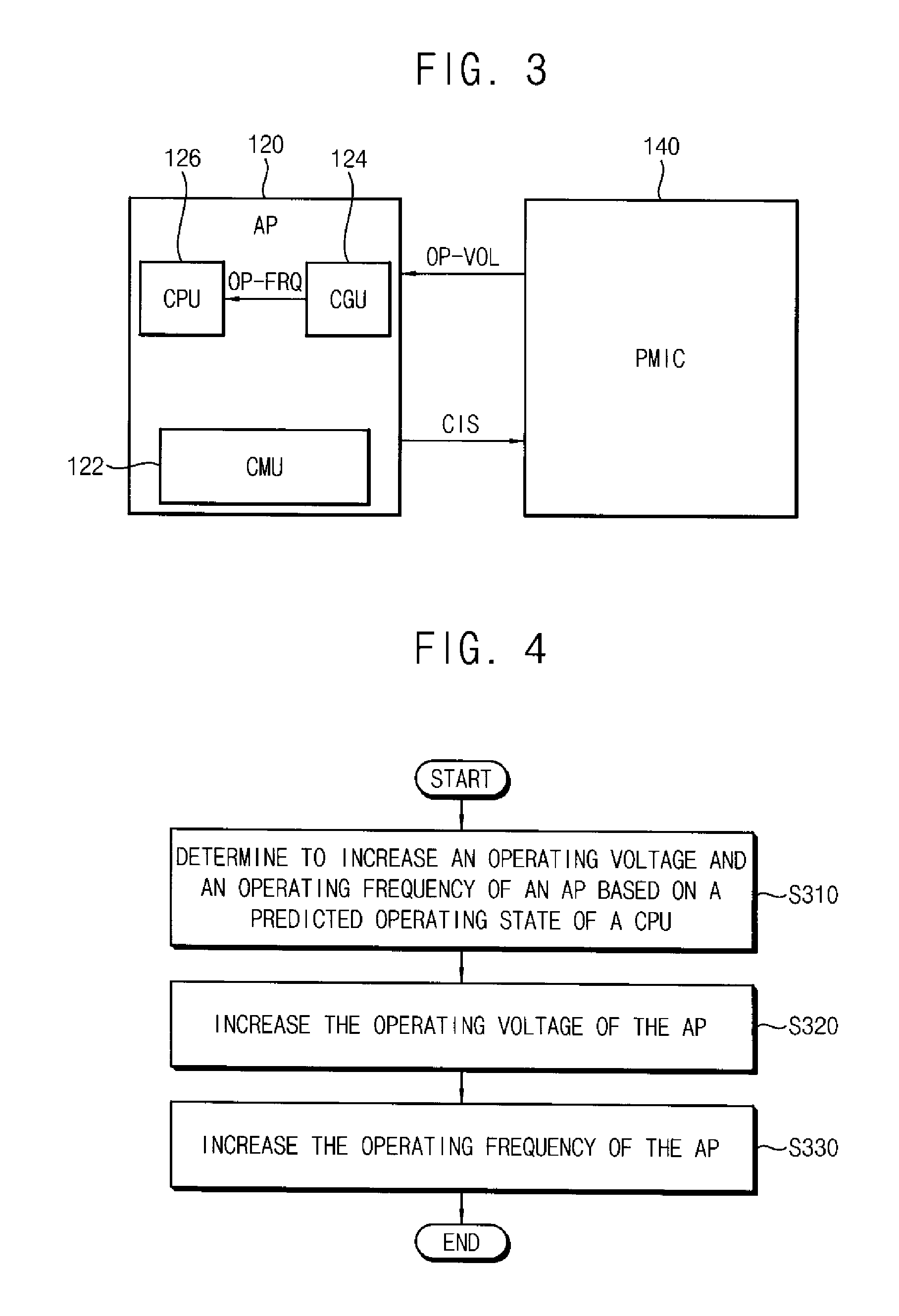

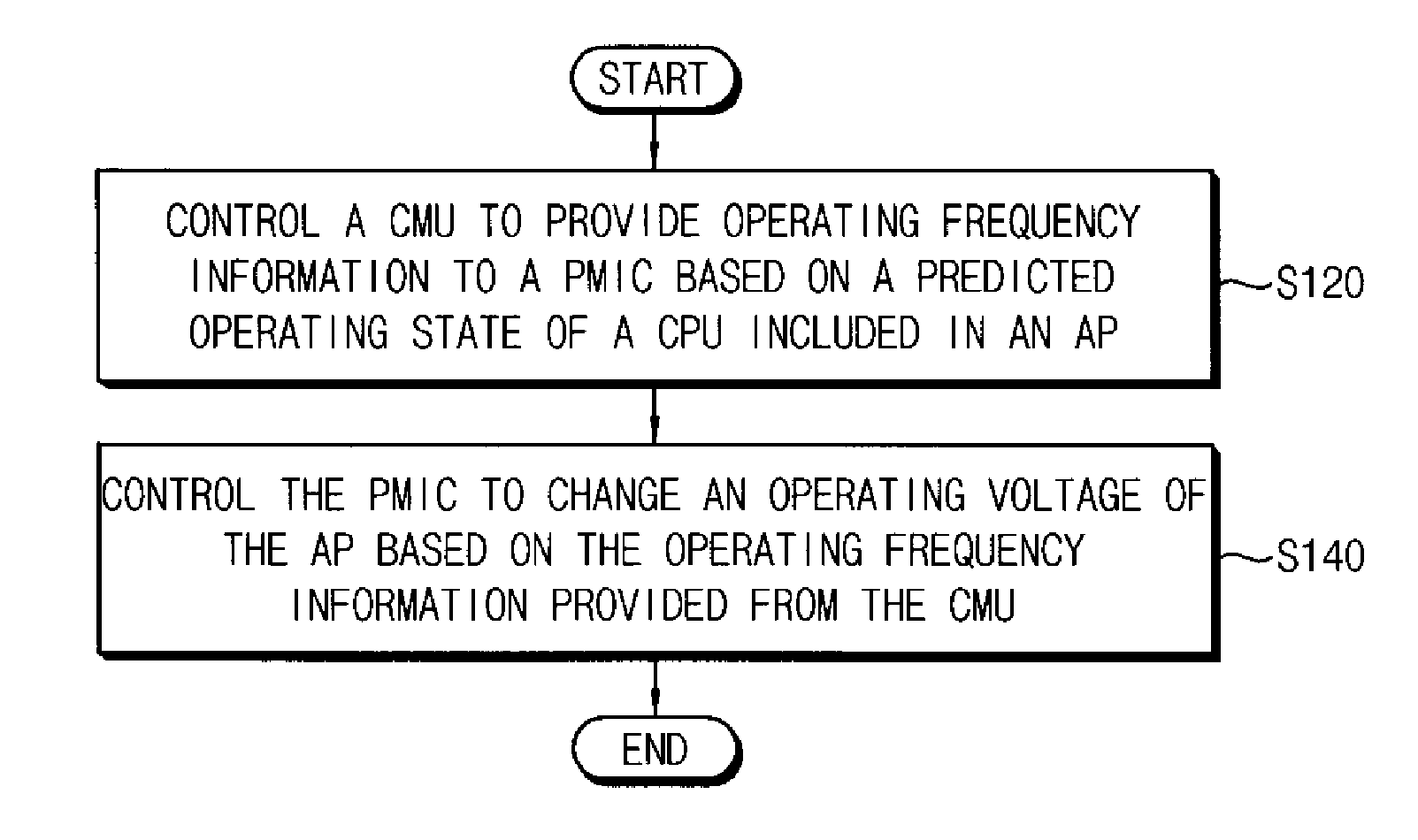

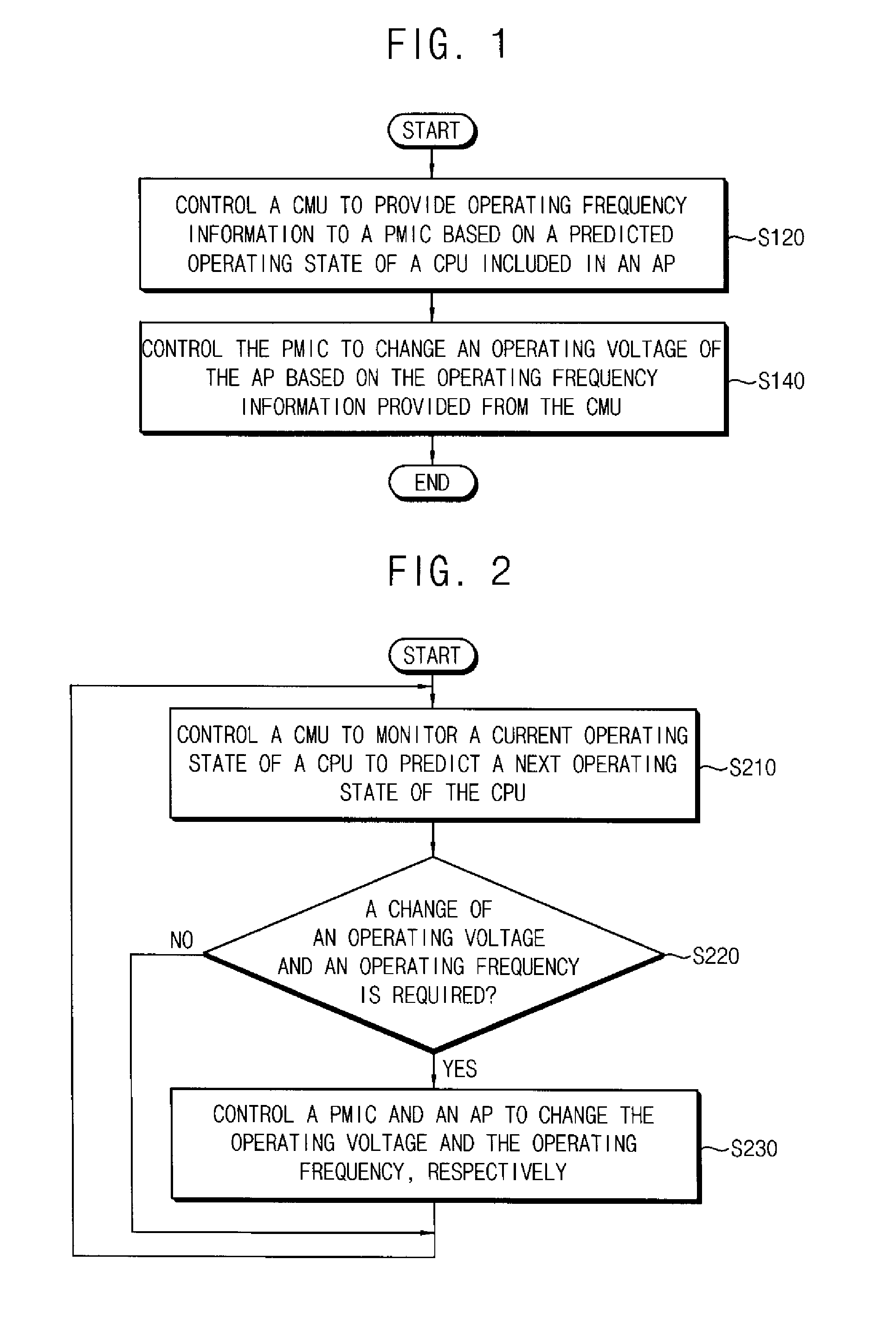

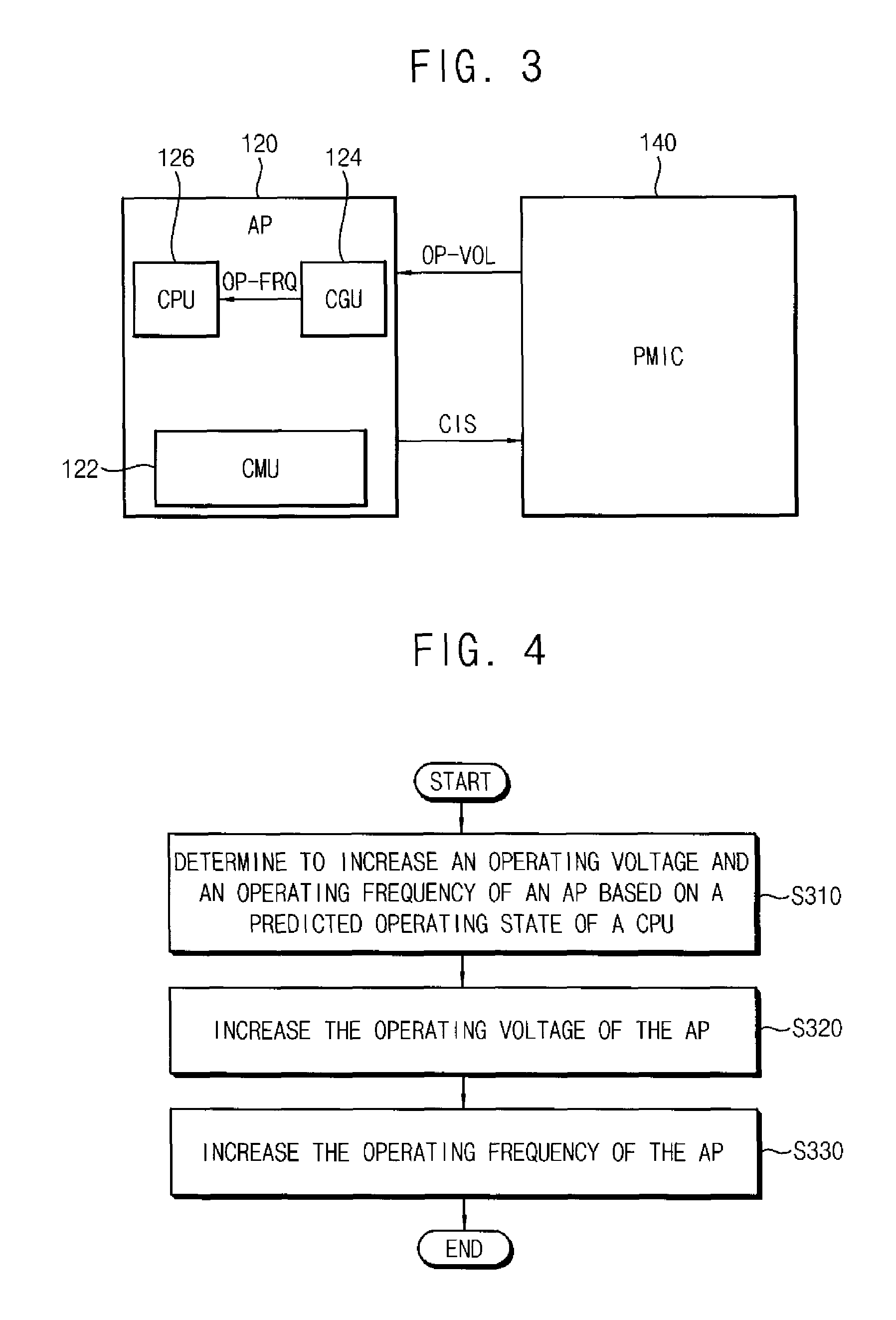

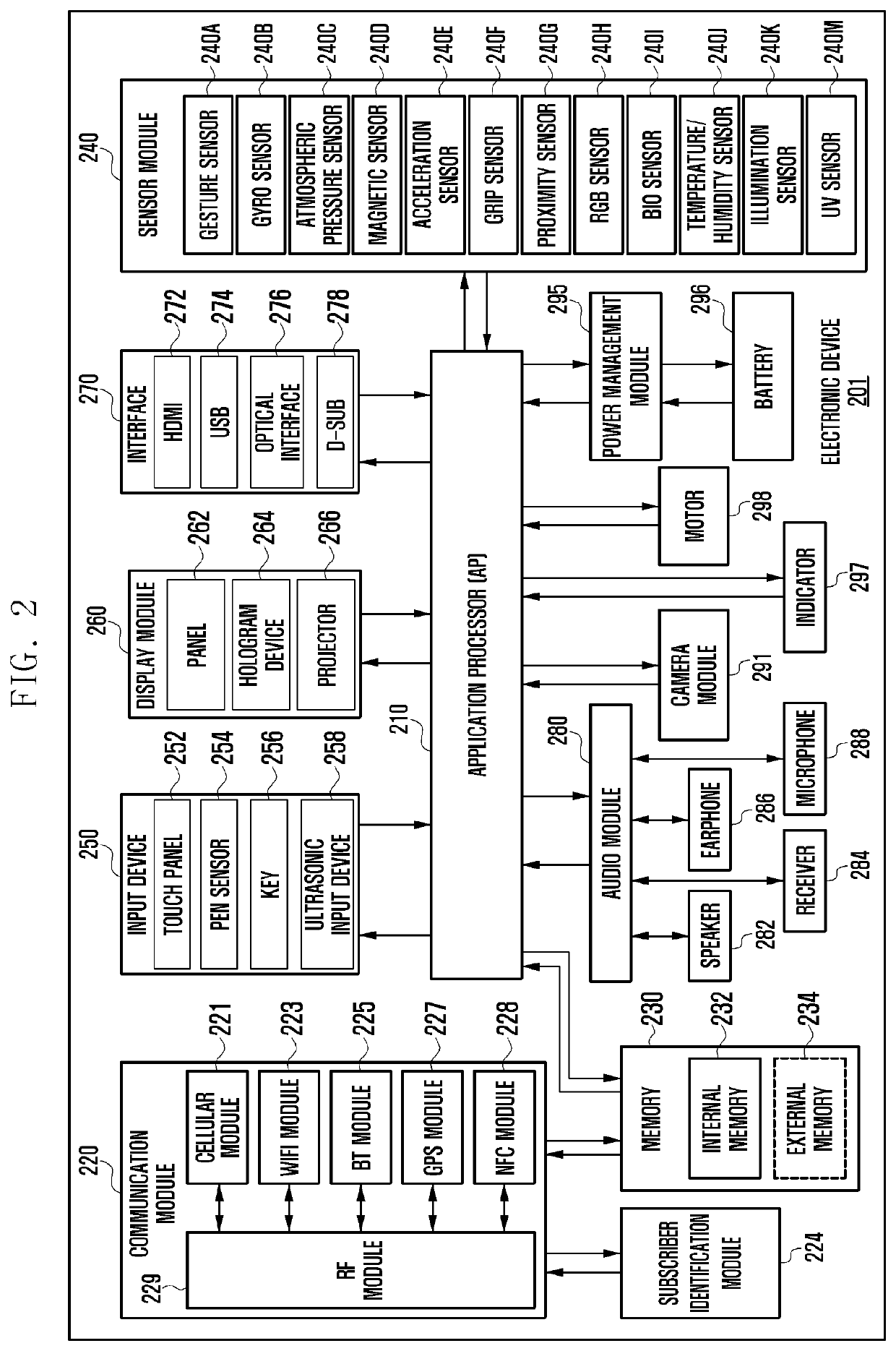

Method of performing dynamic voltage and frequency scaling operation, application processor performing method, and mobile device comprising application processor

ActiveUS20140075224A1Prevent unnecessary power consumptionPower supply for data processingGenerating/distributing signalsProcessing elementMobile device

A method of performing a dynamic voltage and frequency scaling operation comprises controlling a clock management unit (CMU) to predict an operating state of a central processing unit (CPU) and to provide operating frequency information to a power management integrated circuit (PMIC) based on the predicted operating state of the CPU, the operating frequency information indicating a change of an operating frequency of an application processor, and controlling the PMIC to change an operating voltage of the application processor based on the operating frequency information provided from the clock management unit.

Owner:SAMSUNG ELECTRONICS CO LTD

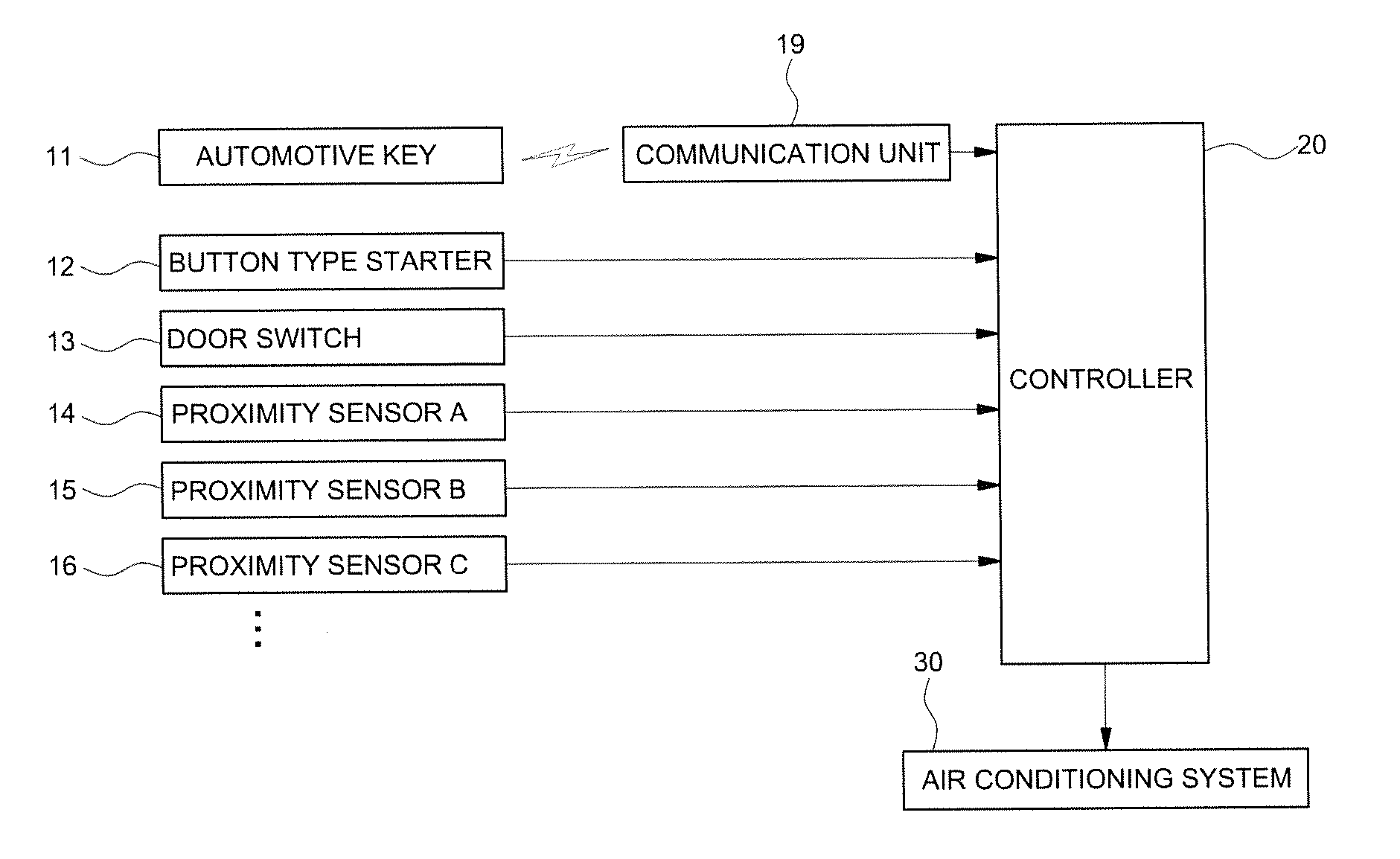

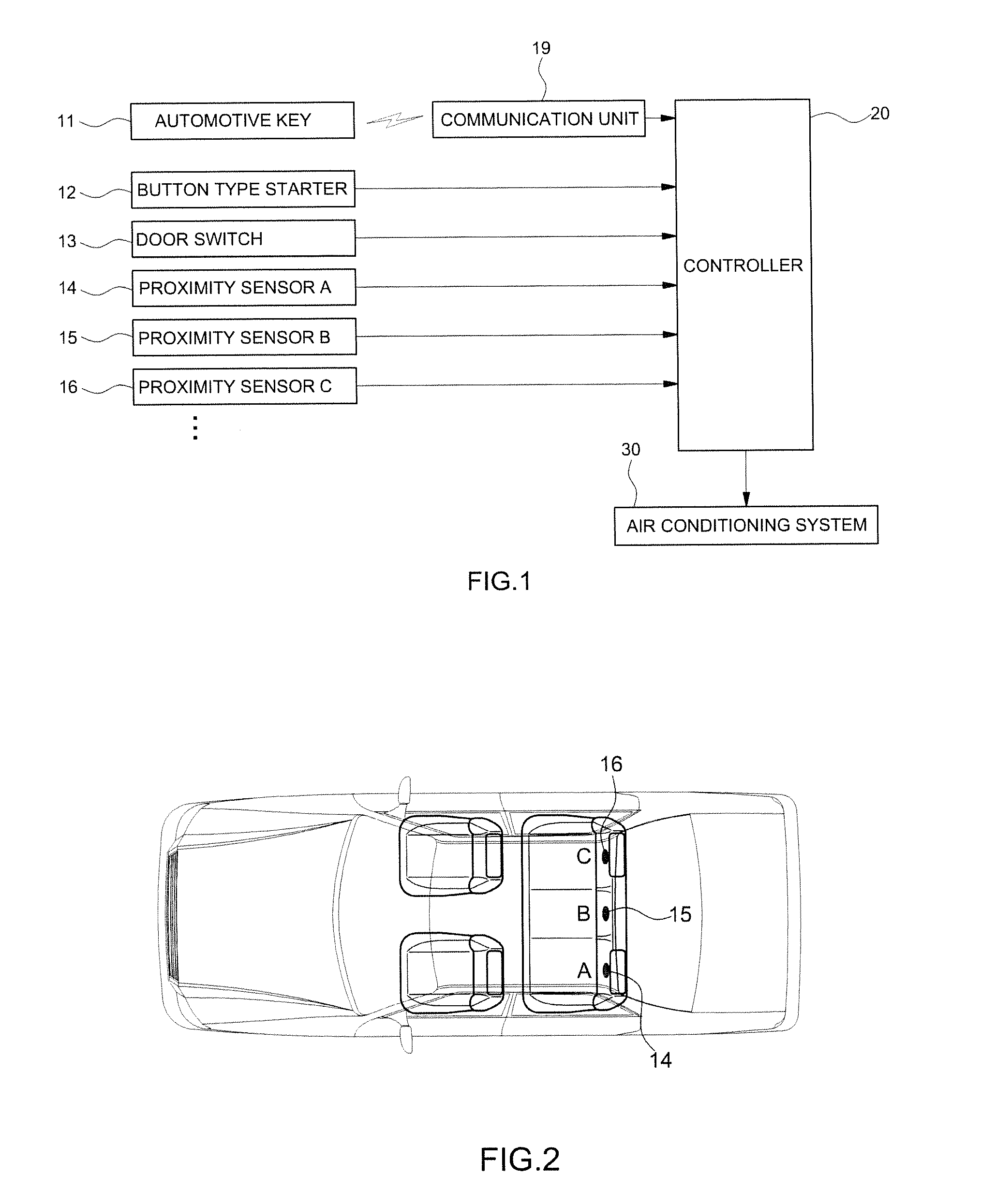

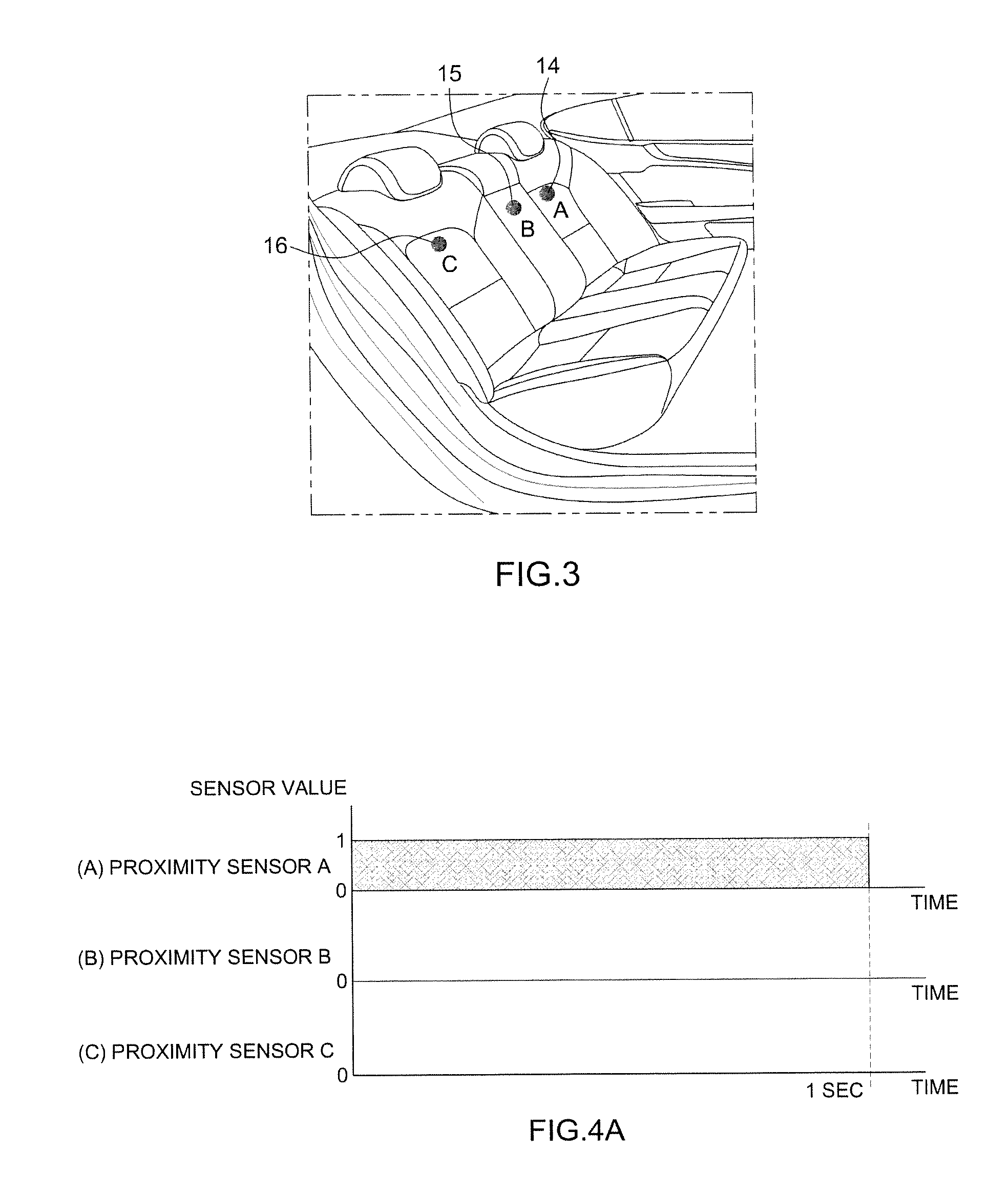

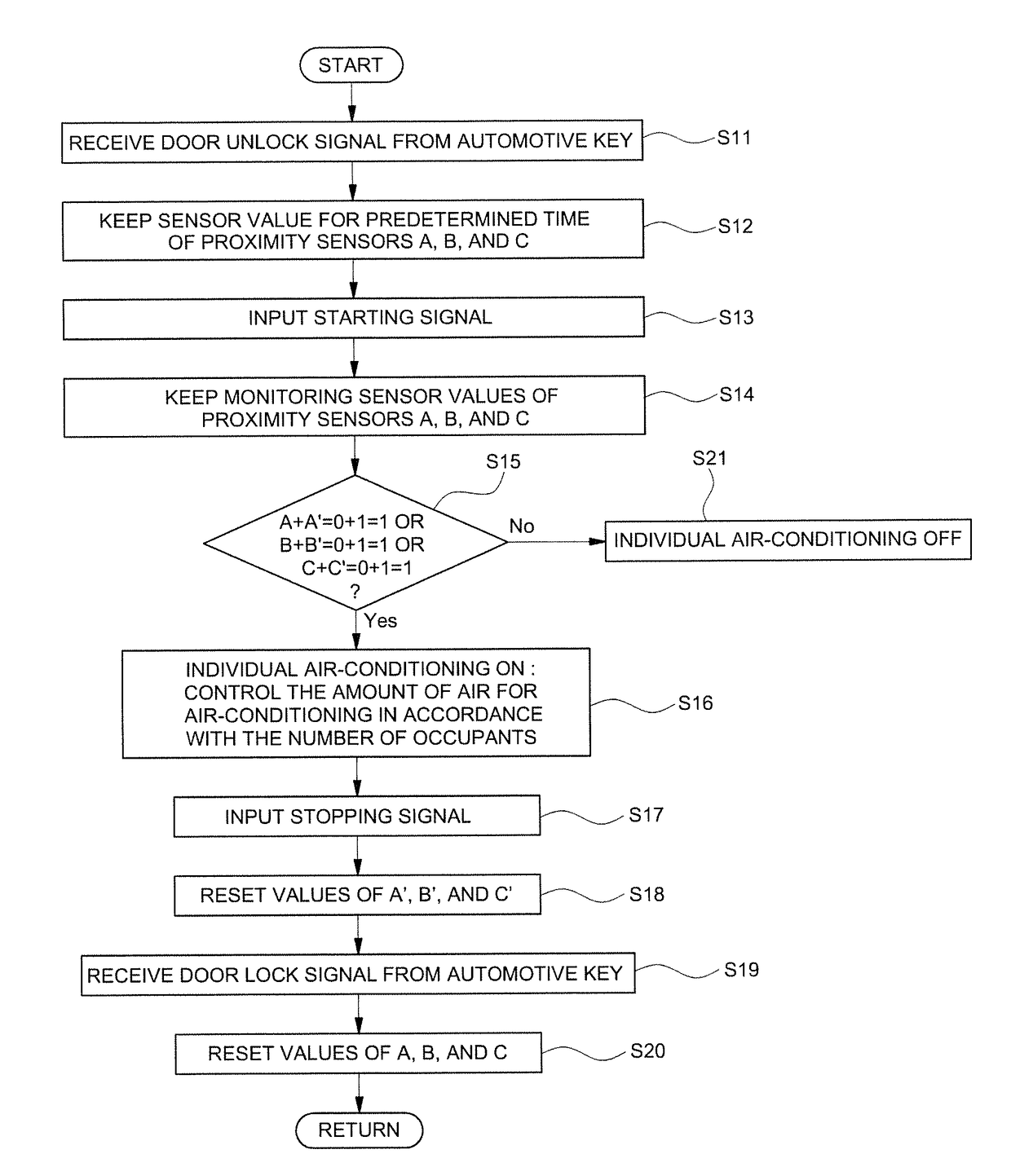

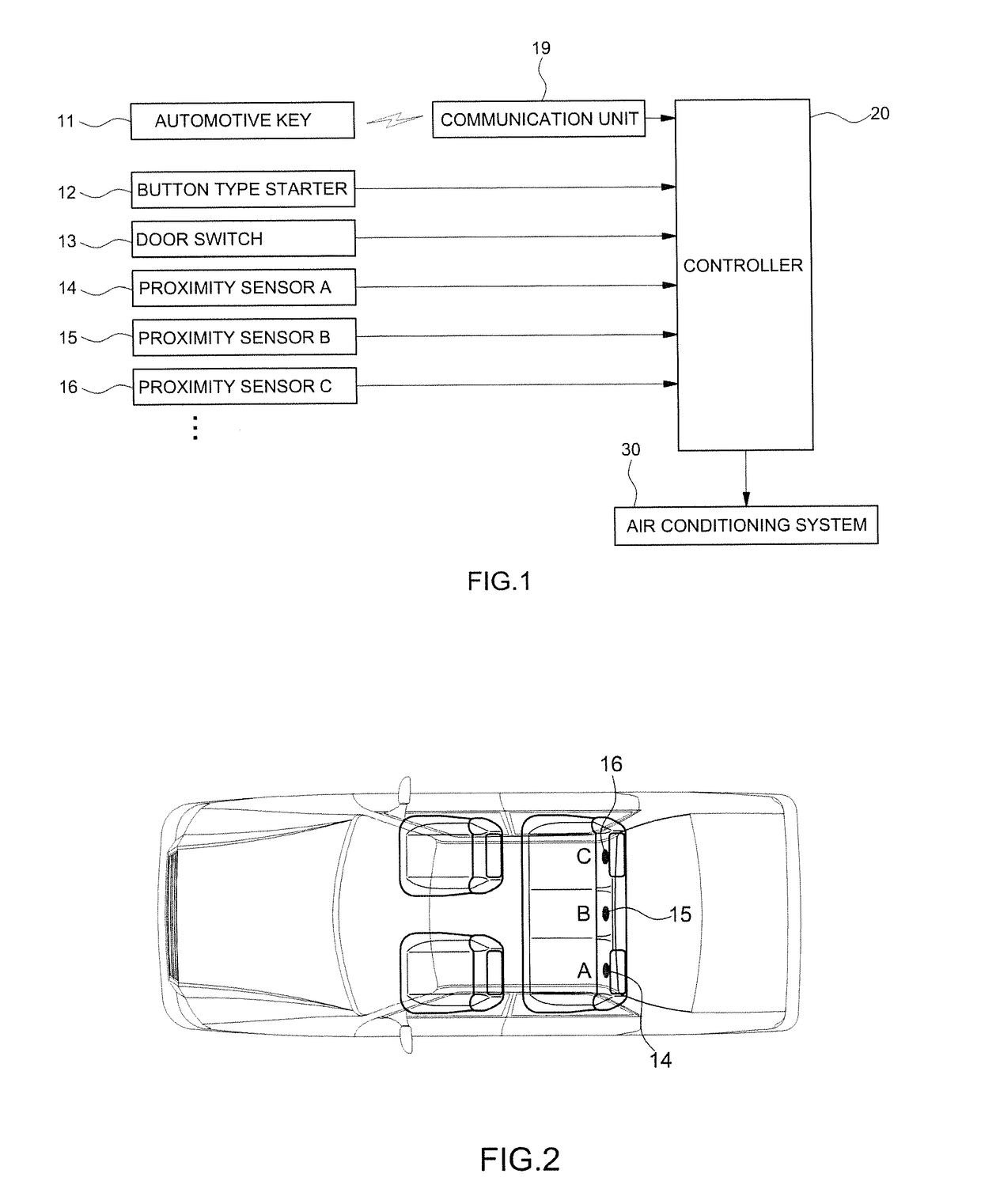

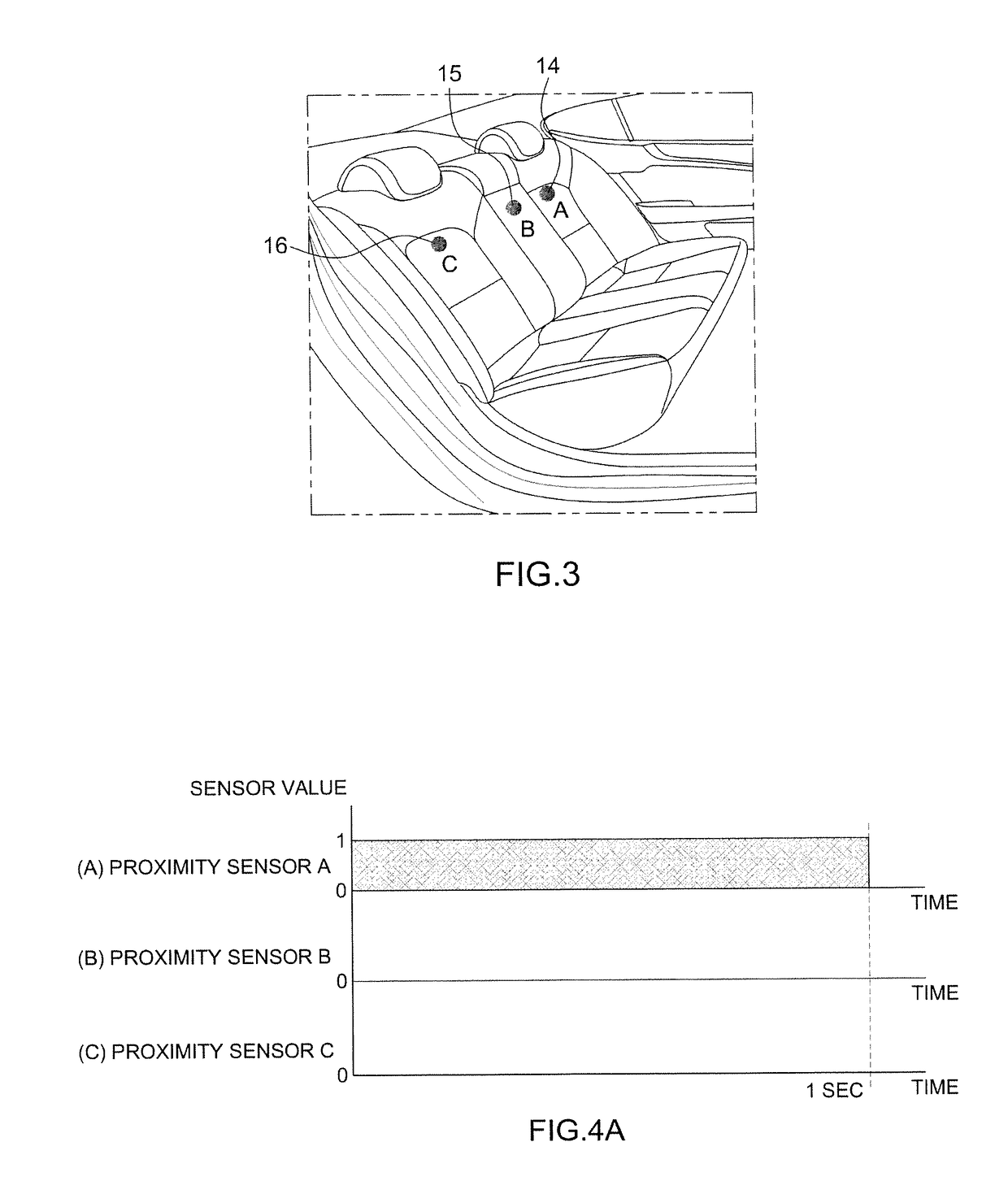

System for detecting occupant in vehicle and method for controlling air conditioning using the same

ActiveUS20160114650A1Low costReduce weightVehicle seatsMechanical apparatusProximity sensorIn vehicle

A system for detecting an occupant in a vehicle includes a proximity sensor installed at a back of a seat and detecting an object. An automotive key locks and unlocks a door. A starter starts and stops an engine of the vehicle. A controller is configured to determine whether the occupant is in the seat based sensor values of the proximity sensor, a door unlock signal from the automotive key, and a starting signal from the starter.

Owner:HYUNDAI MOTOR CO LTD

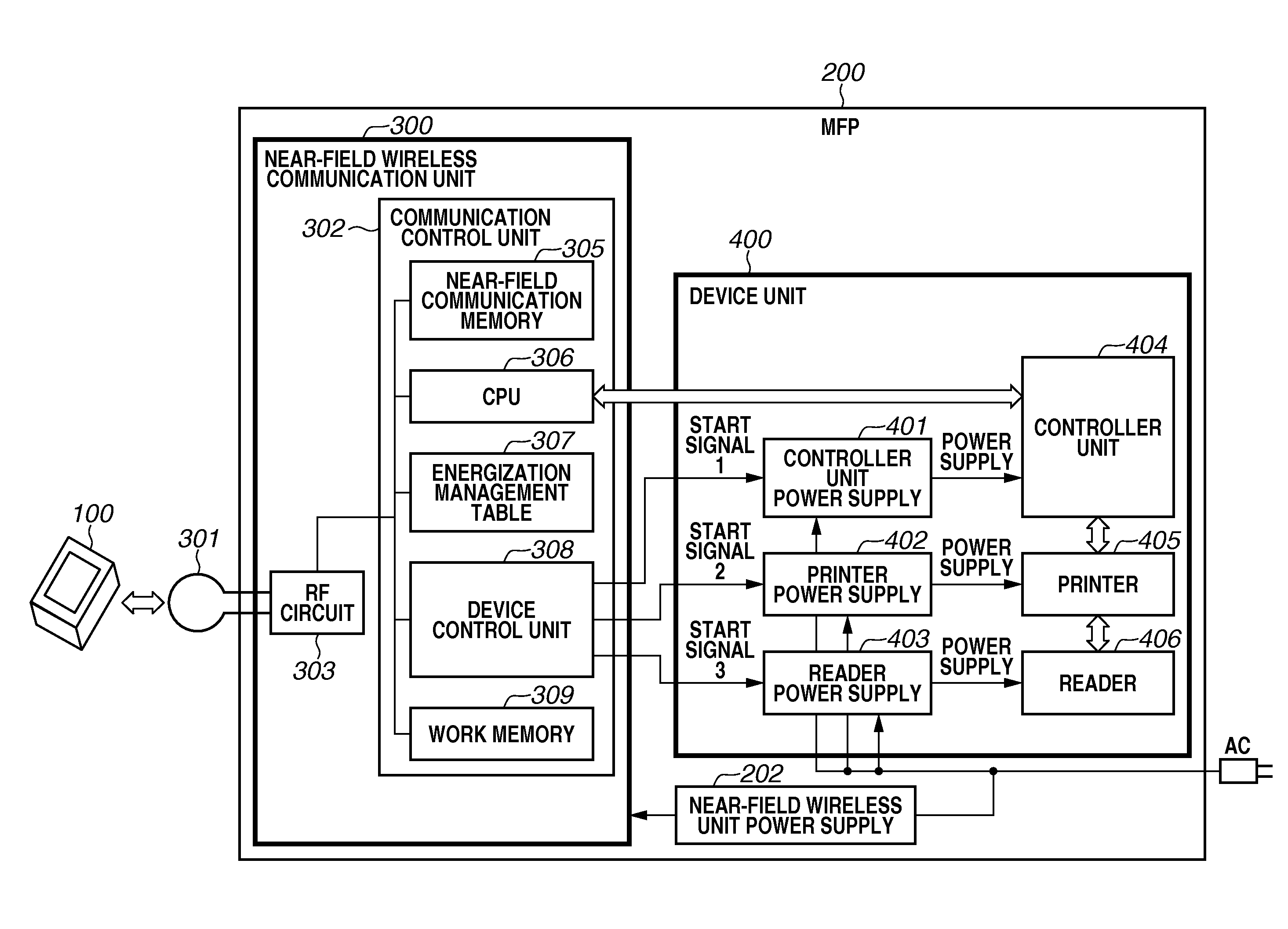

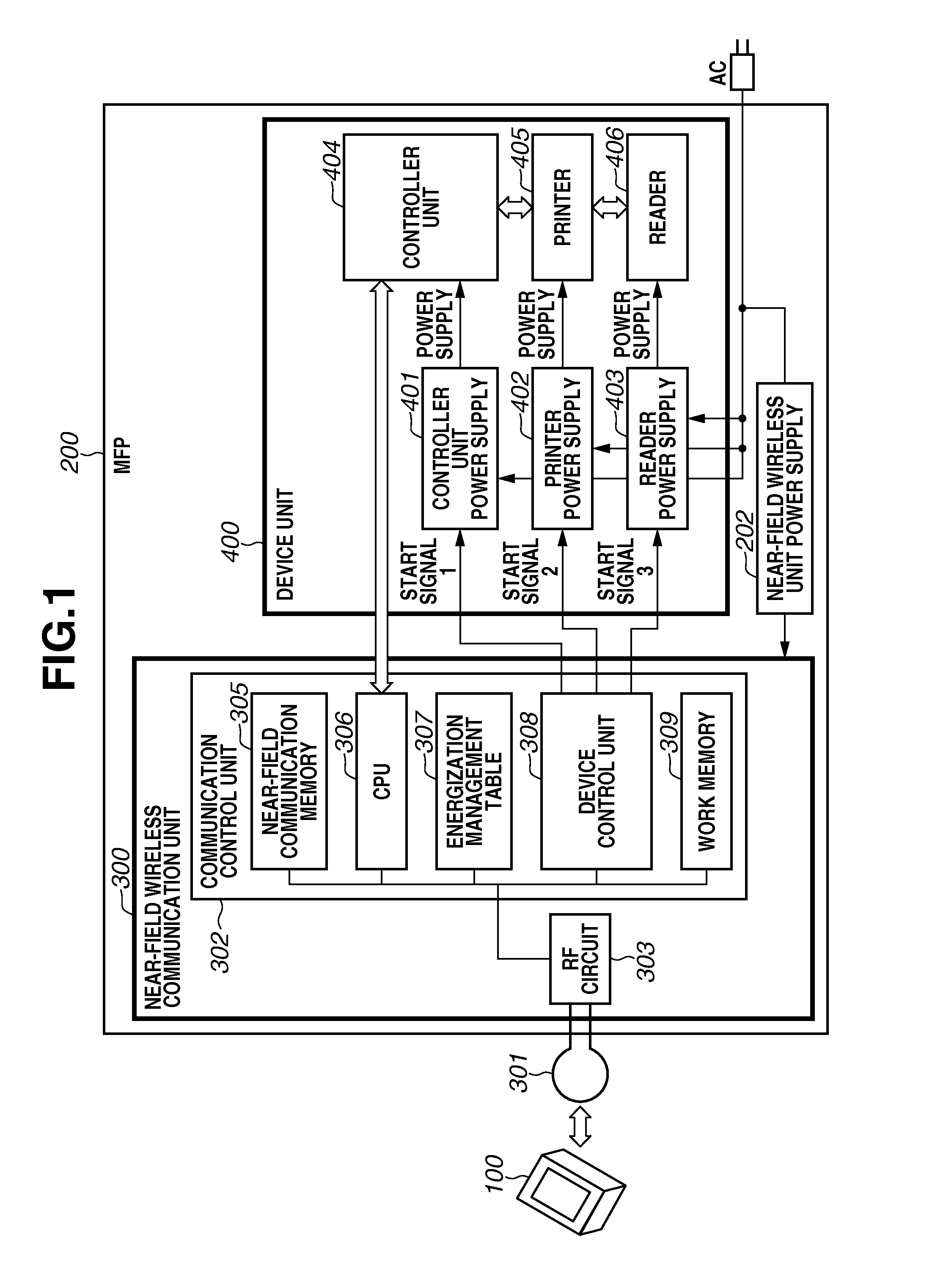

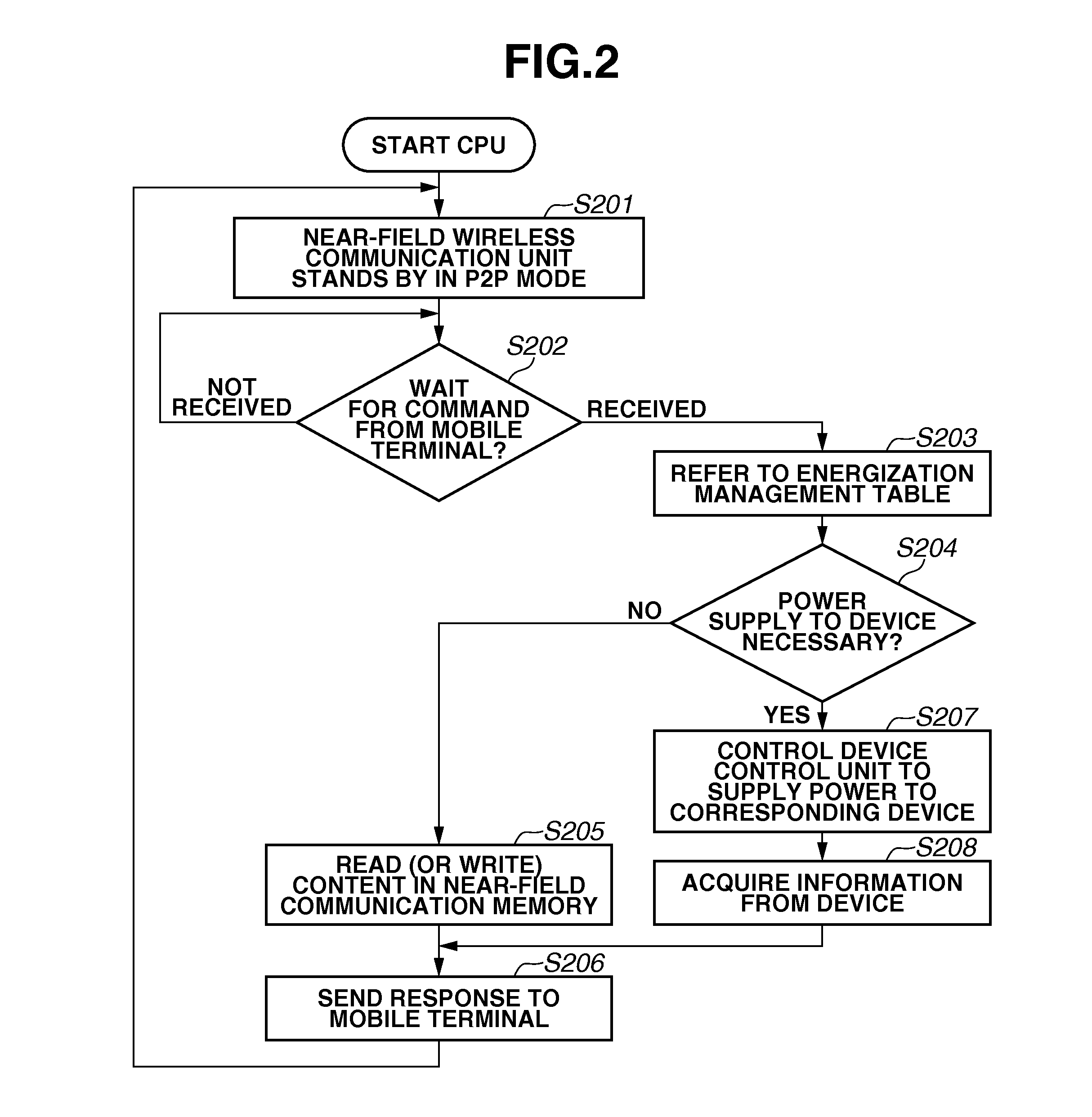

Information processing apparatus, method for controlling information processing apparatus, and storage medium

InactiveUS20150173020A1Enhance convenience of operator and power saving capabilityPrevent unnecessary power consumptionPower managementNear-field transmissionRadio waveEngineering

An information processing apparatus operable in a first power state and in a second power state in which power consumption is lower than that in the first power state includes a near-field wireless communication unit configured to be driven by electric power induced by a radio wave from a mobile terminal, and communicate with the mobile terminal when the information processing apparatus is in the second power state. The near-field wireless communication unit sends, if a command received from the mobile terminal in the second power state is a command of a first type, a response corresponding to the command to the mobile terminal in the second power state, and if the received command is a command of a second type, performs control so as to supply electric power to a portion necessary for sending a response corresponding to the command to the mobile terminal.

Owner:CANON KK

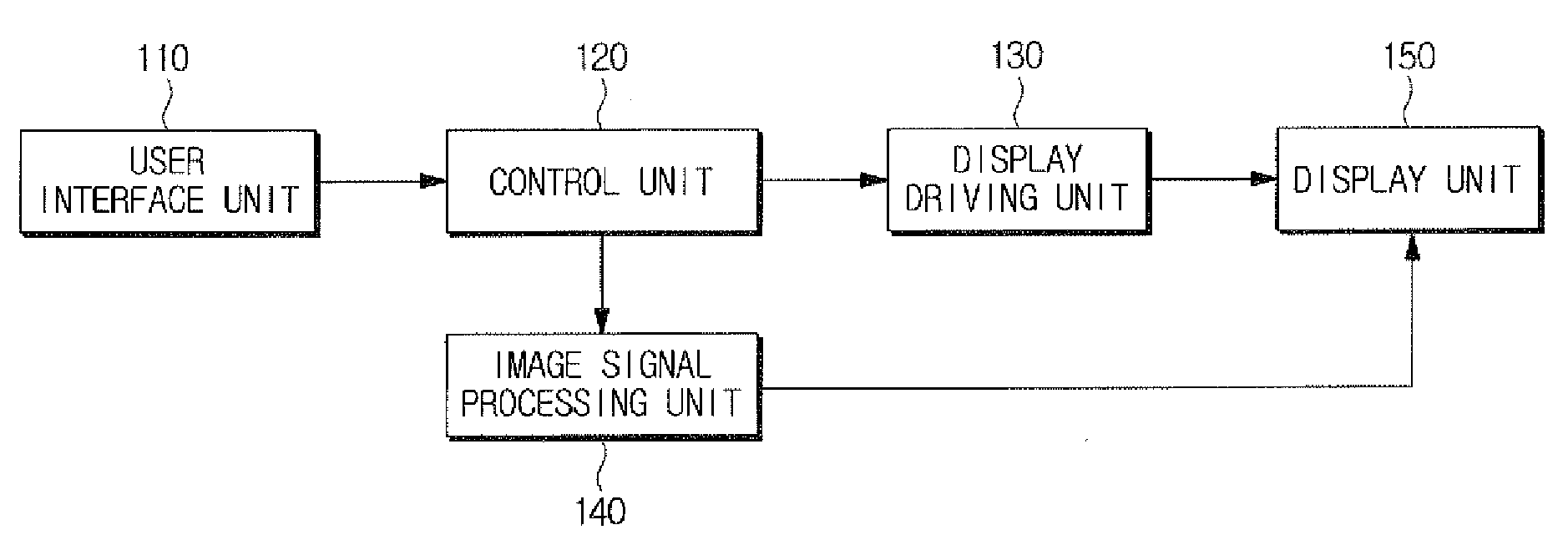

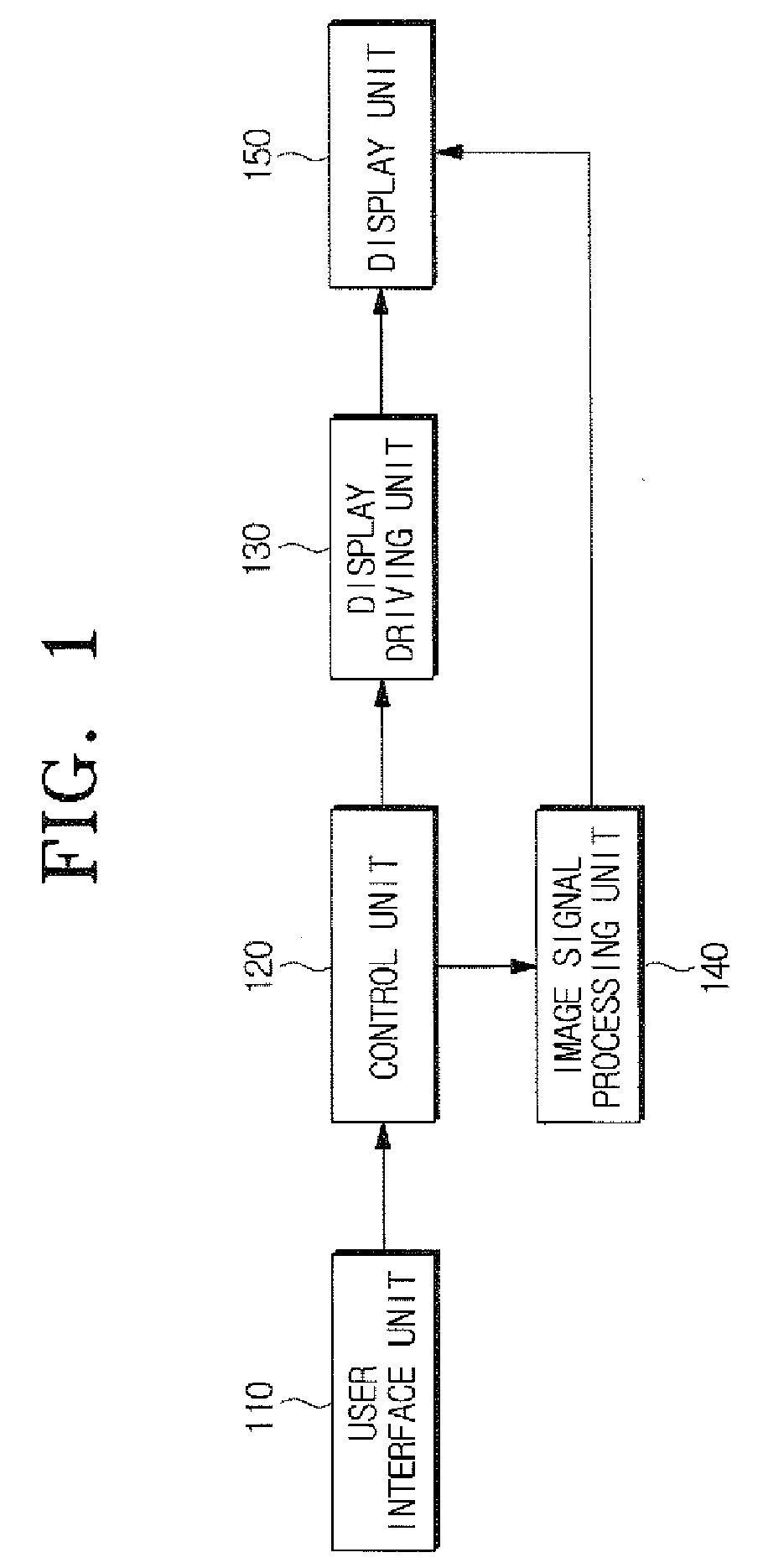

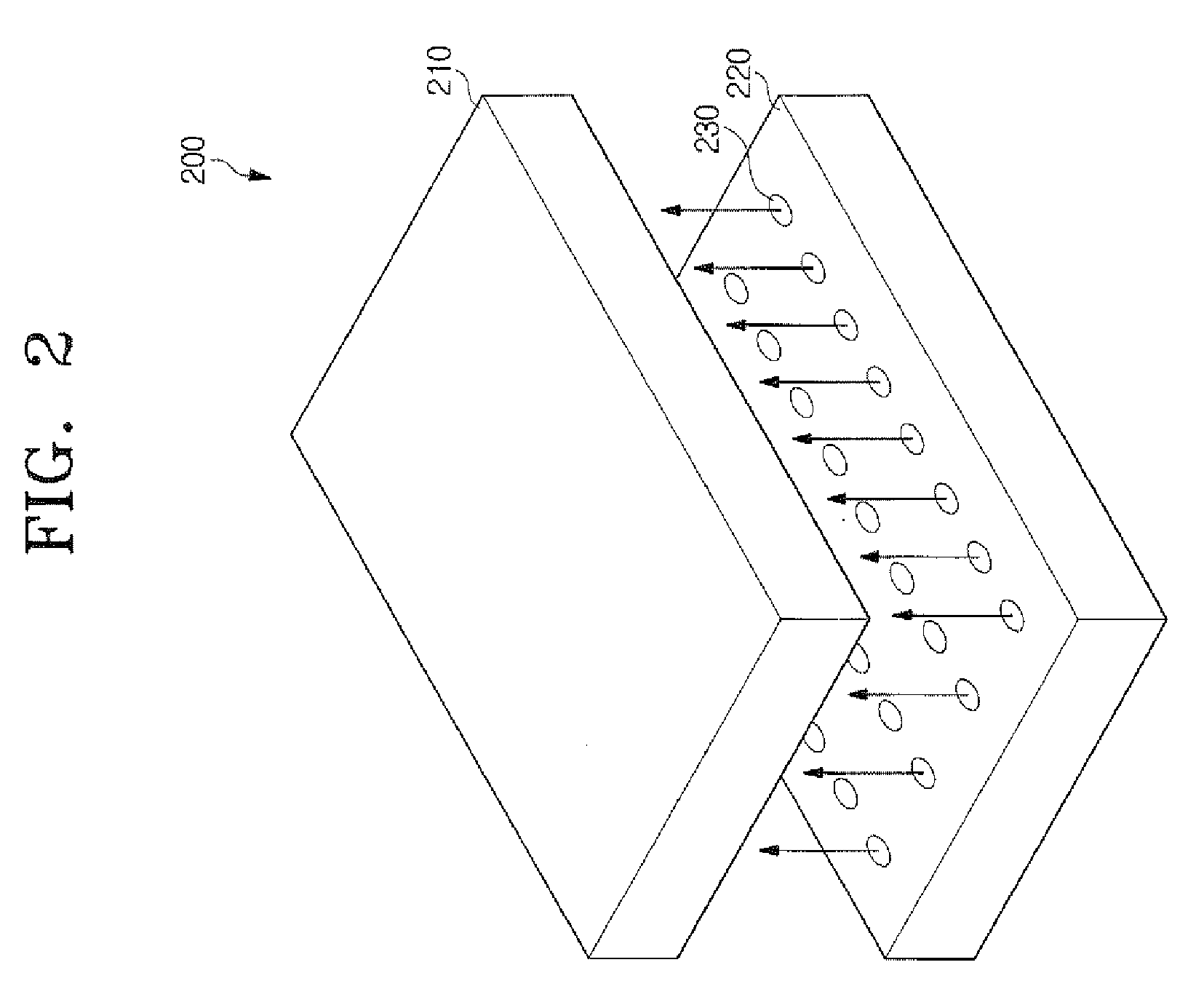

Image display device for displaying small-sized image and method thereof

InactiveUS20080155466A1Avoid unnecessary power consumptionImprove user convenienceInput/output for user-computer interactionCathode-ray tube indicatorsComputer graphics (images)Image conversion

An image display device capable of displaying a small-sized image and a method thereof are provided. The image display device includes a display unit, a display driving unit which controls an operation state of the display unit, a user interface unit which receives an input of a user's selection command, an image signal processing unit which receives an image signal and converting the received image signal into a designated size in accordance with the user's selection command, and a control unit which controls the display driving unit to display the converted image signal by activating a designated region on the display unit and inactivating the remaining region in accordance with the user's selection command. The image display device can be implemented by an LCD device or a PDP device. Accordingly, a small-sized image can be displayed in accordance with a user's selection, and power consumption can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

System for detecting occupant in vehicle and method for controlling air conditioning using the same

ActiveUS9827825B2Prevent unnecessary power consumptionVehicle seatsMechanical apparatusProximity sensorIn vehicle

A system for detecting an occupant in a vehicle includes a proximity sensor installed at a back of a seat and detecting an object. An automotive key locks and unlocks a door. A starter starts and stops an engine of the vehicle. A controller is configured to determine whether the occupant is in the seat based sensor values of the proximity sensor, a door unlock signal from the automotive key, and a starting signal from the starter.

Owner:HYUNDAI MOTOR CO LTD

Method of performing dynamic voltage and frequency scaling operation, application processor performing method, and mobile device comprising application processor

ActiveUS9541992B2Prevent unnecessary power consumptionEnergy efficient ICTPower supply for data processingProcessing elementMobile device

A method of performing a dynamic voltage and frequency scaling operation comprises controlling a clock management unit (CMU) to predict an operating state of a central processing unit (CPU) and to provide operating frequency information to a power management integrated circuit (PMIC) based on the predicted operating state of the CPU, the operating frequency information indicating a change of an operating frequency of an application processor, and controlling the PMIC to change an operating voltage of the application processor based on the operating frequency information provided from the clock management unit.

Owner:SAMSUNG ELECTRONICS CO LTD

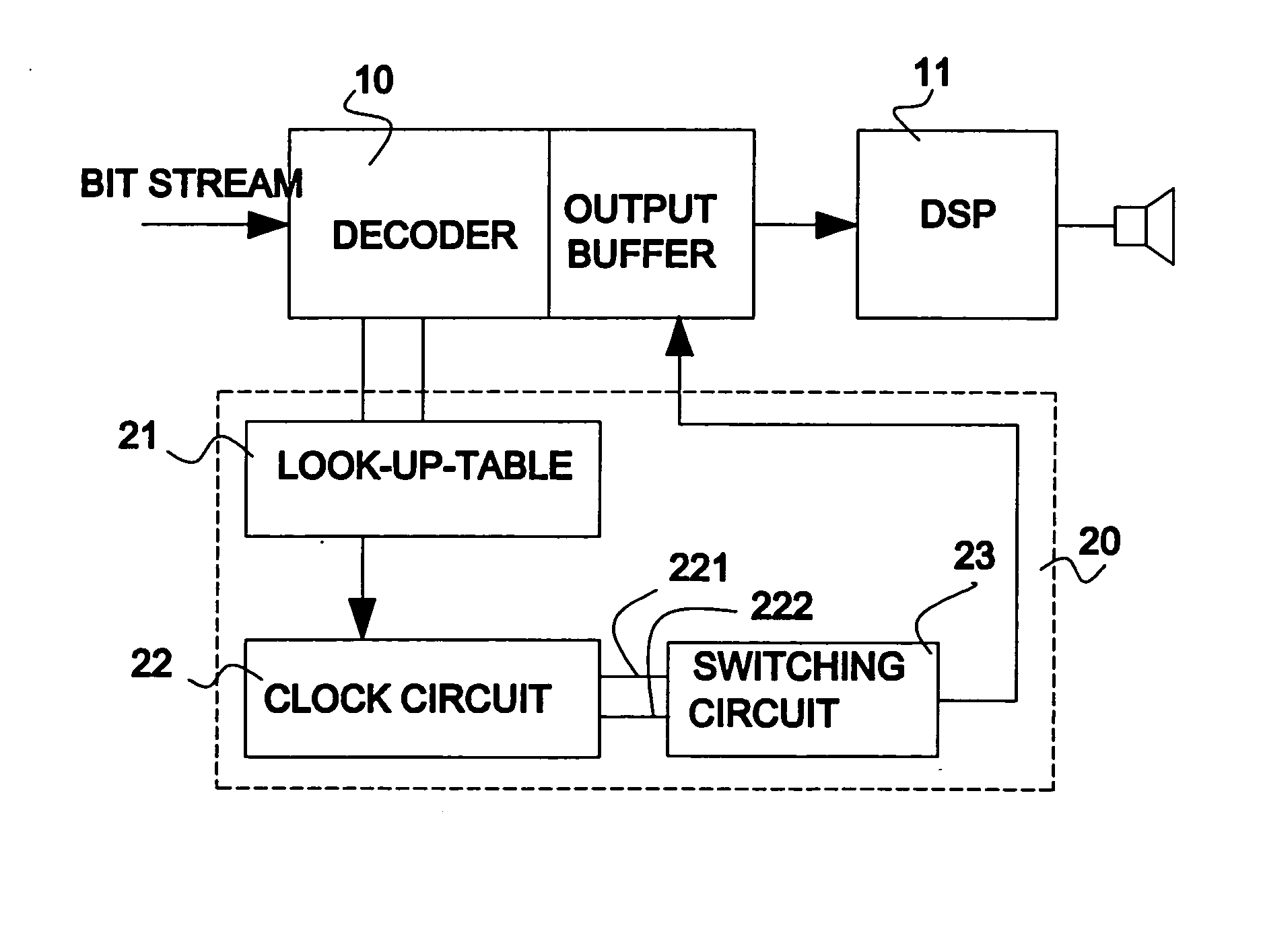

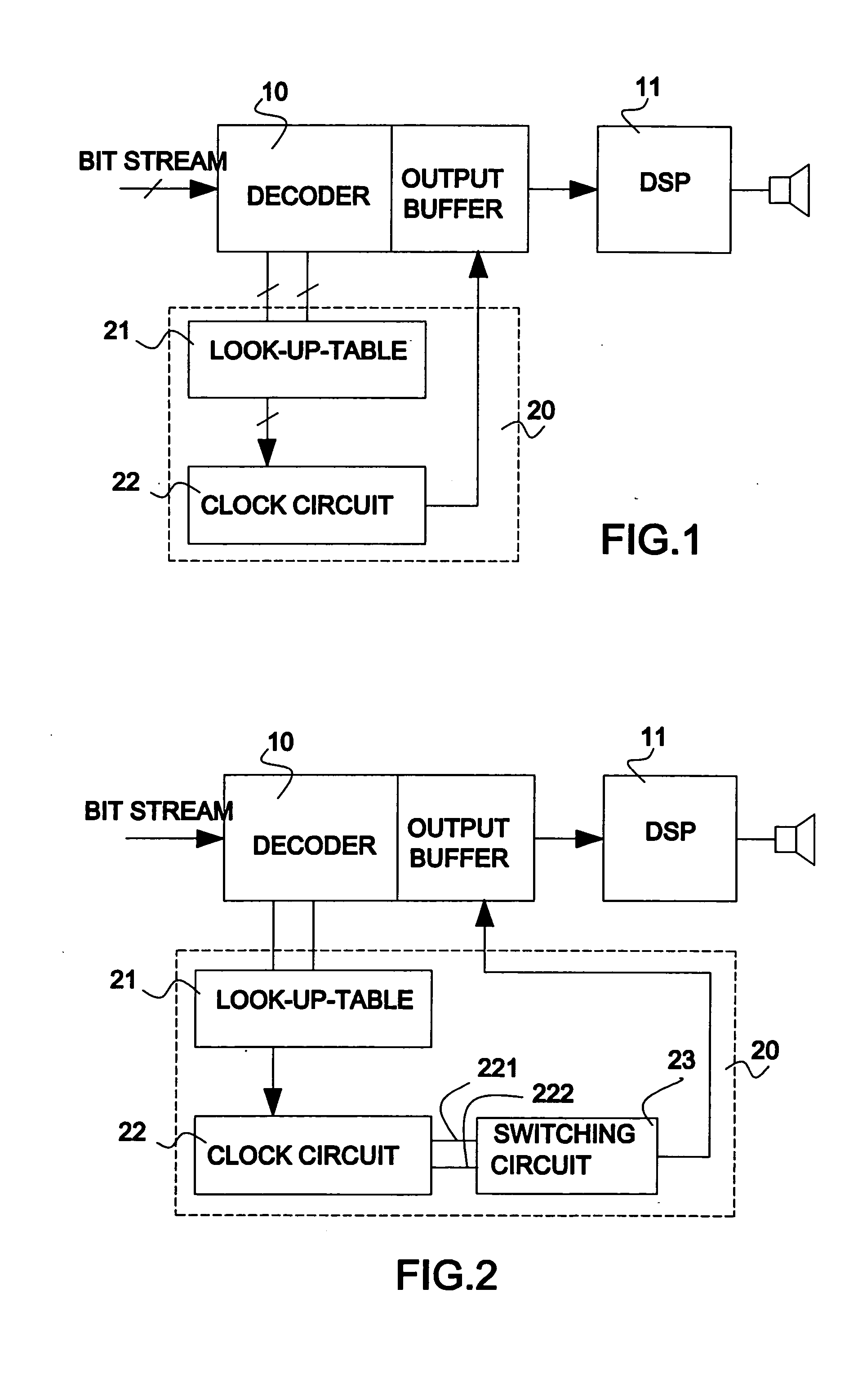

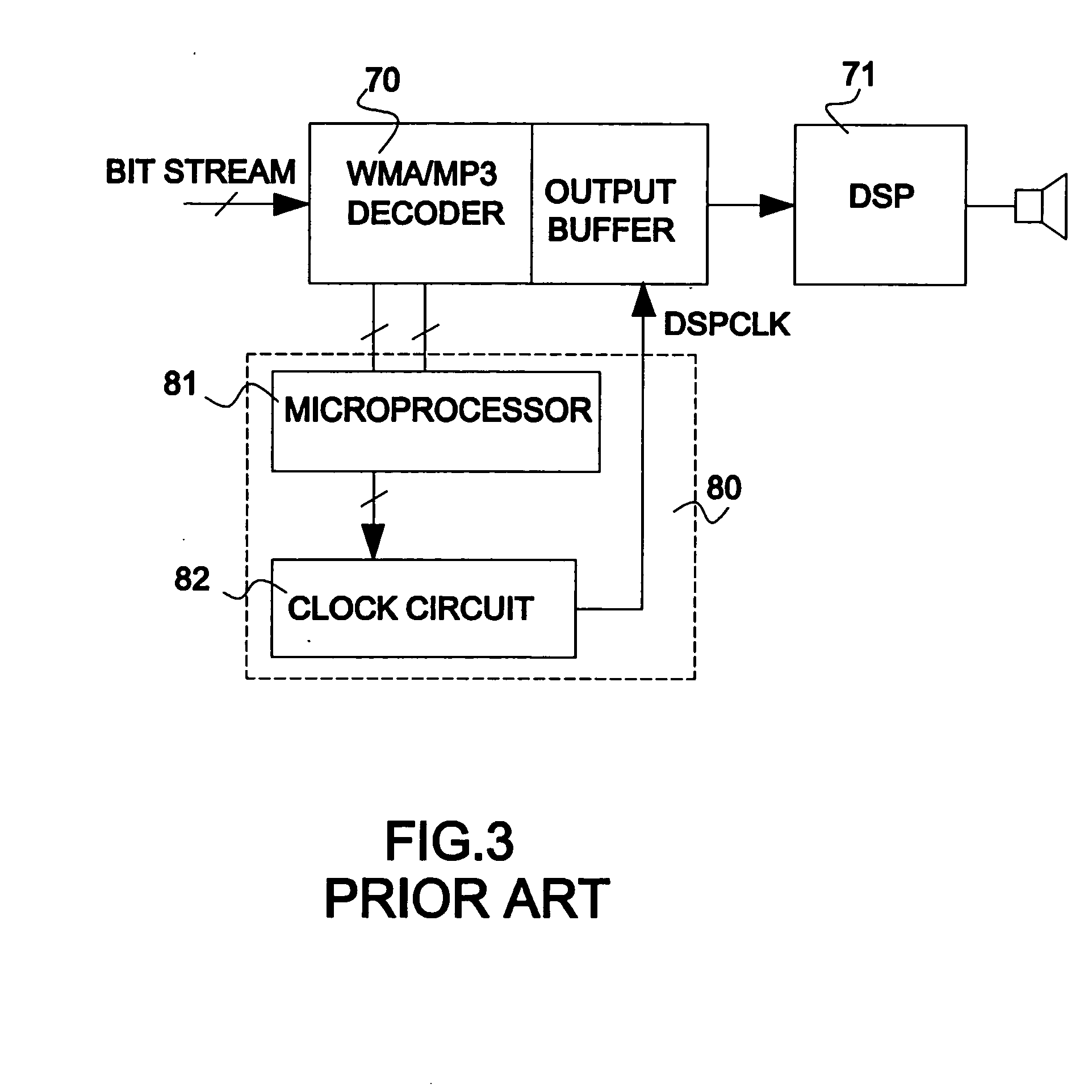

Variable frequency decoding apparatus for efficient power management in a portable audio device

InactiveUS20050091052A1Extend operation timePrevent unnecessary power consumptionSpeech analysisColor television detailsAudio equipmentClock generator

A variable frequency decoding apparatus operable in a portable audio device that can improve the power management is disclosed. The above apparatus has a decoder and a clock generator that provides the system clock for the decoder. When a bit stream representing audio compressed data is received, the decoder simultaneously provides the audio information embedded in the audio compressed data such as the bit rate and the sampling frequency of the data frame to the clock generator, and then the clock generator adjusts the clock signals; which are used by the decoder to restore to the original PCM format, to match the audio information embedded in the data frame. This audio signal compression technique can prevent possible output delay and reduce power consumption as compared with the conventional way that used a fixed sys clock.

Owner:G DESIGN TECH

Apparatus for unlocking mobile device using pattern recognition and method thereof

ActiveUS8554177B2Improve user convenienceImprove securityElectric signal transmission systemsUnauthorised/fraudulent call preventionPattern recognitionLiquid-crystal display

An apparatus and method for unlocking a mobile device using pattern recognition are provided. The apparatus includes a touch sensor unit sensing a predetermined pattern touch-input to a liquid crystal display (LCD) unit, a pattern recognition unit recognizing information about the input pattern sensed by the touch sensor unit, a pattern comparison unit comparing information about the input pattern recognized by the pattern recognition unit with information about a predetermined pattern set by a user, and a controller controlling supply of power to the LCD unit to enable the user to use the mobile device if the input pattern and the predetermined pattern are equal to each other as compared by the pattern comparison unit.

Owner:SAMSUNG ELECTRONICS CO LTD

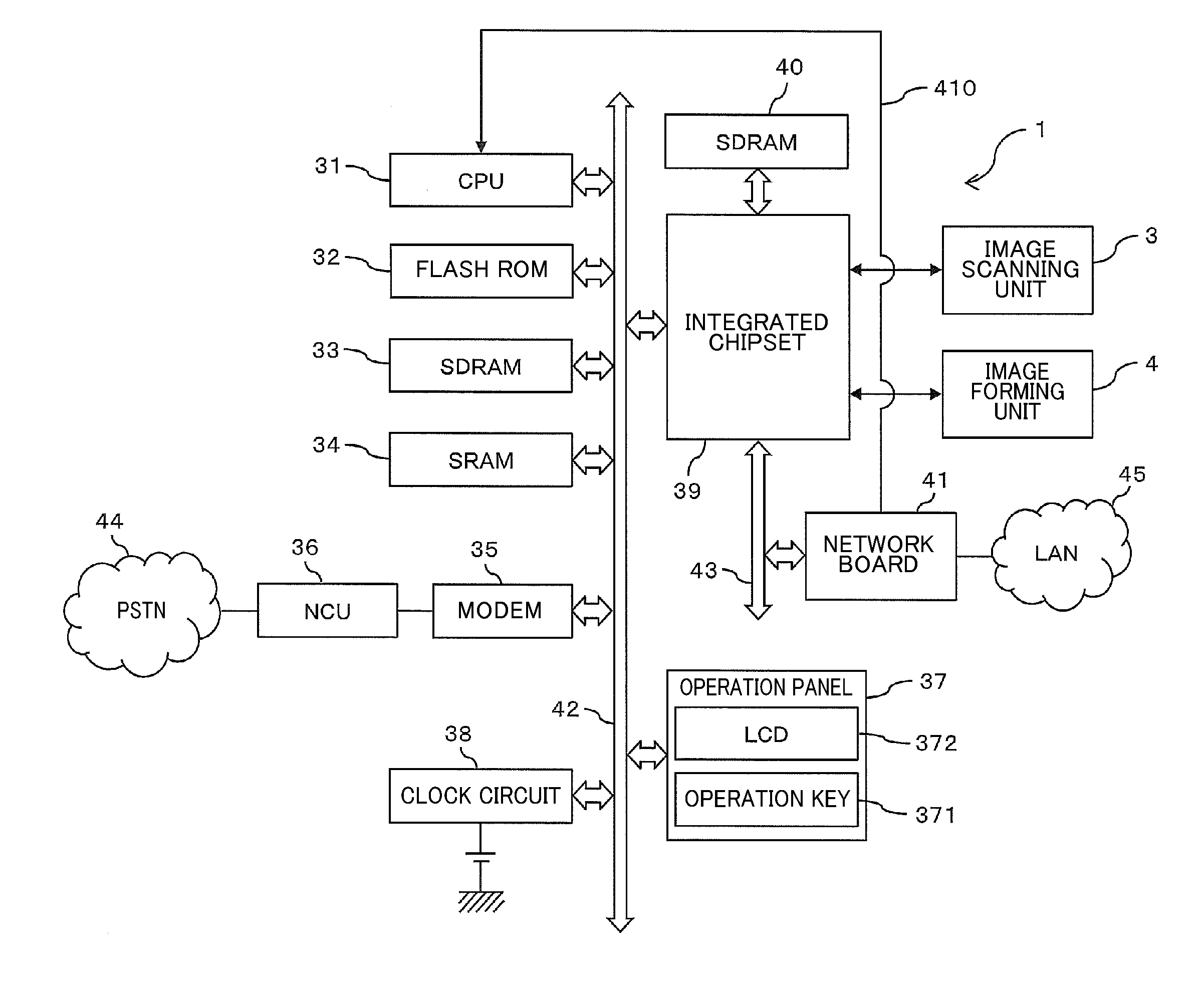

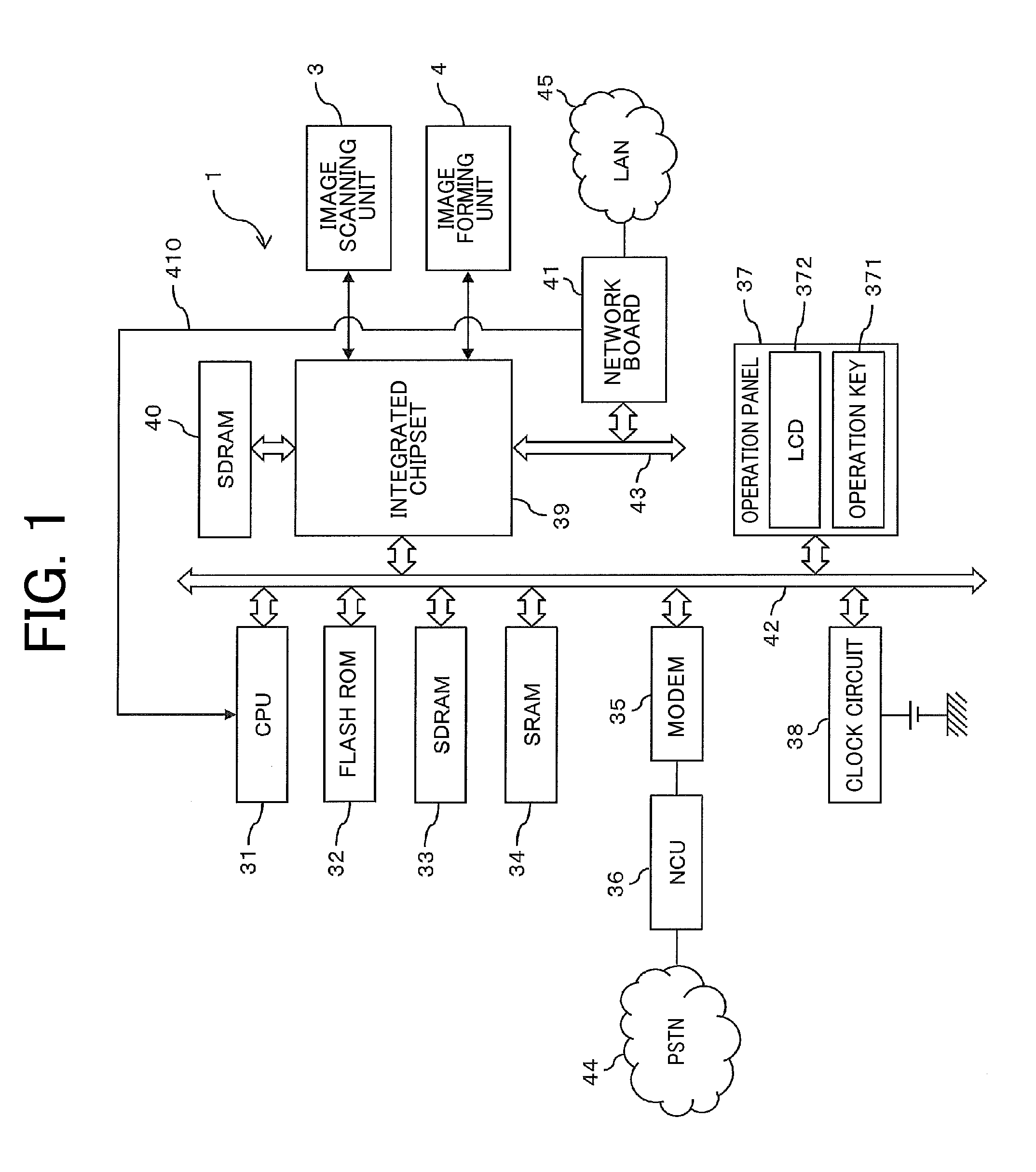

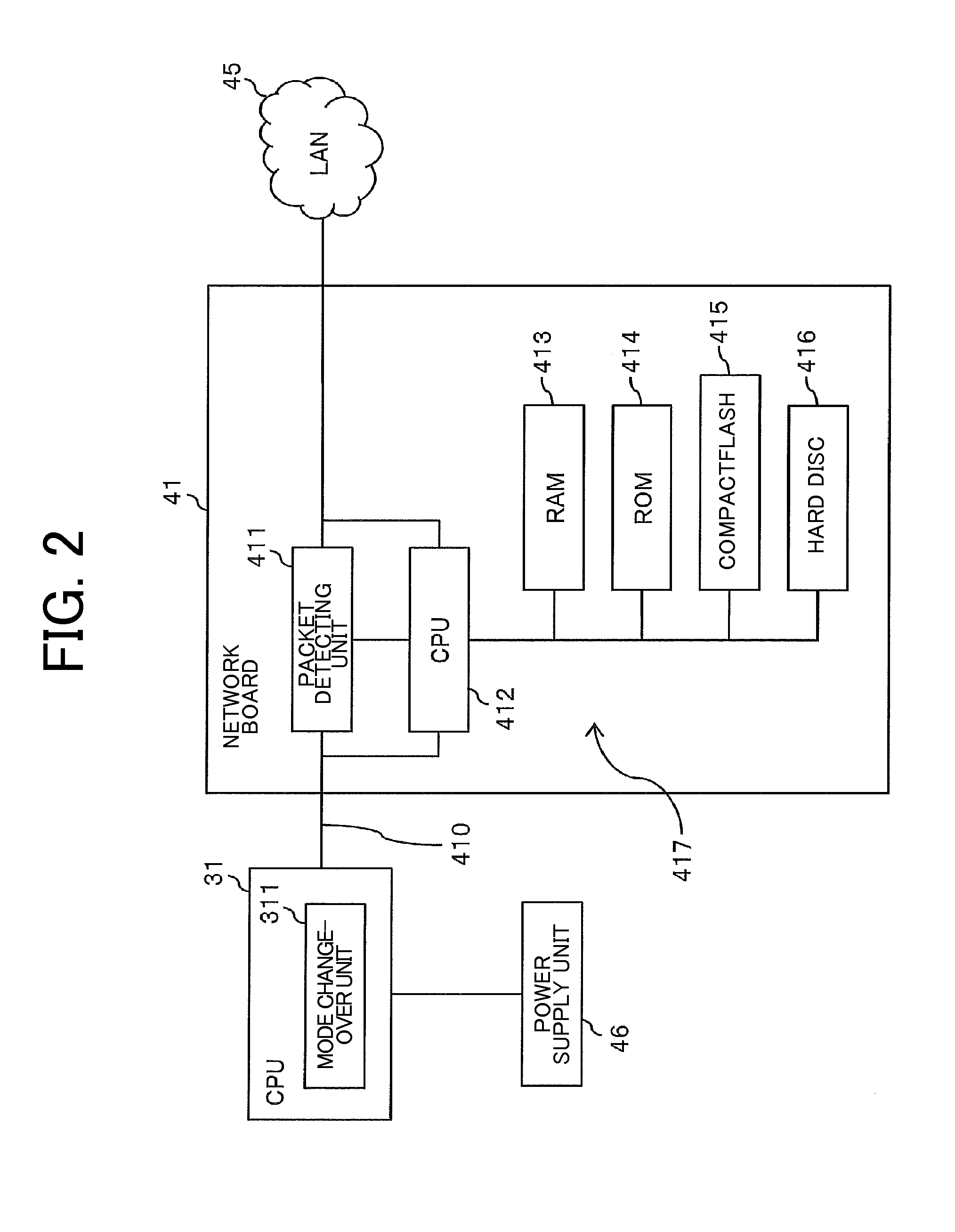

Image processing apparatus and power-saving method of image processing apparatus

InactiveUS20130050727A1Prevent unnecessary power consumptionOperation is complicatedPower supply for data processingPictoral communicationPower savingMode control

An apparatus includes a packet detecting unit; a packet analyzing unit; an image processing unit processing images using image data from the packet; a power supply unit supplying power to the packet detecting, packet analyzing, and image processing units; a stand-by mode controlling unit controlling the packet detecting unit, the packet analyzing unit, and the image processing unit to be operable in a stand-by mode; a first controlling unit controlling, in a first mode, the packet detecting and packet analyzing units to be operable while the image processing unit is inoperable; a second controlling unit controlling, in a second mode, the packet detecting unit to be operable while the packet analyzing and image processing units are inoperable; and a first mode-changeover unit changing a power supply mode from the second mode to the first mode when the packet detecting unit detects a predetermined packet in the second mode.

Owner:MURATA MASCH LTD

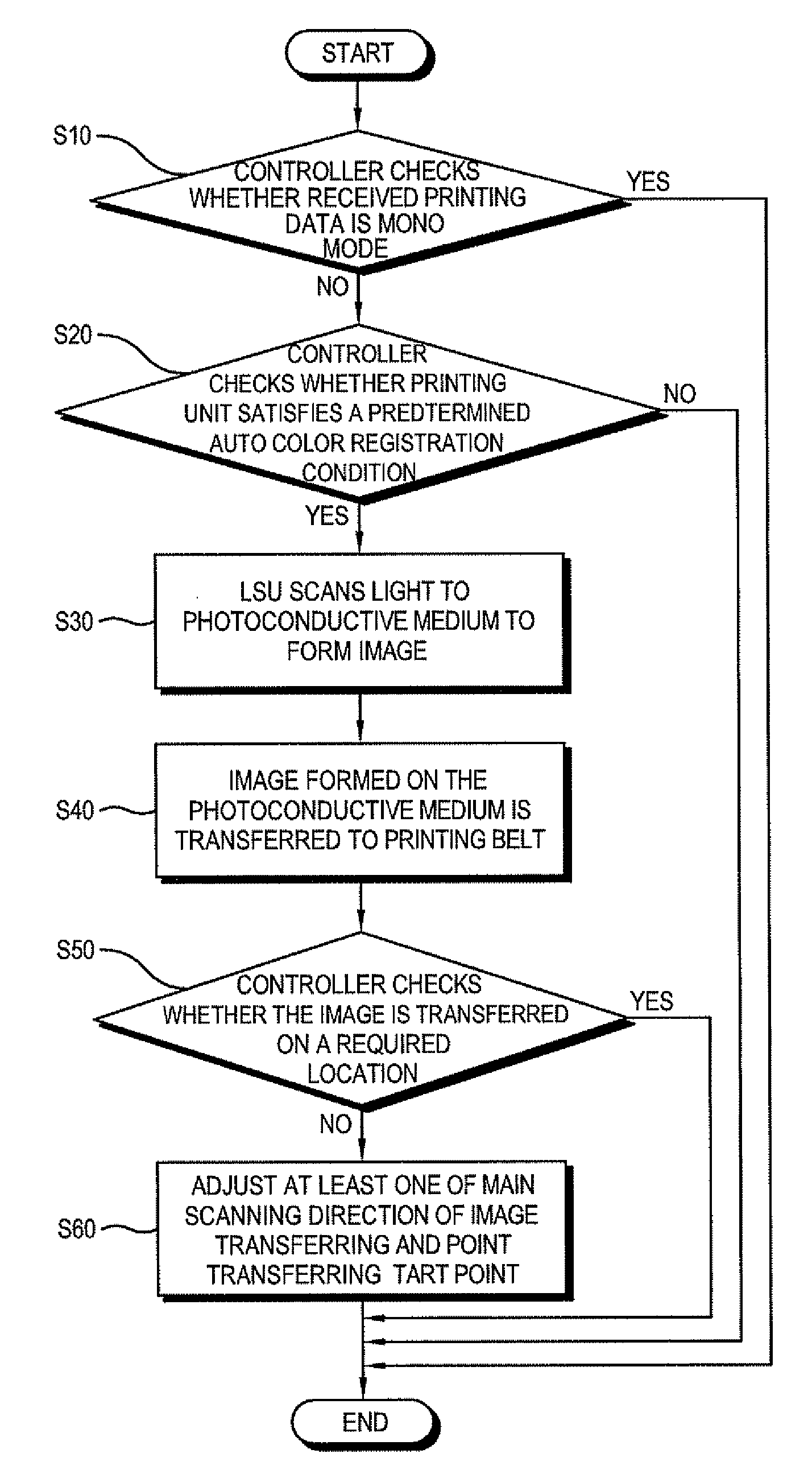

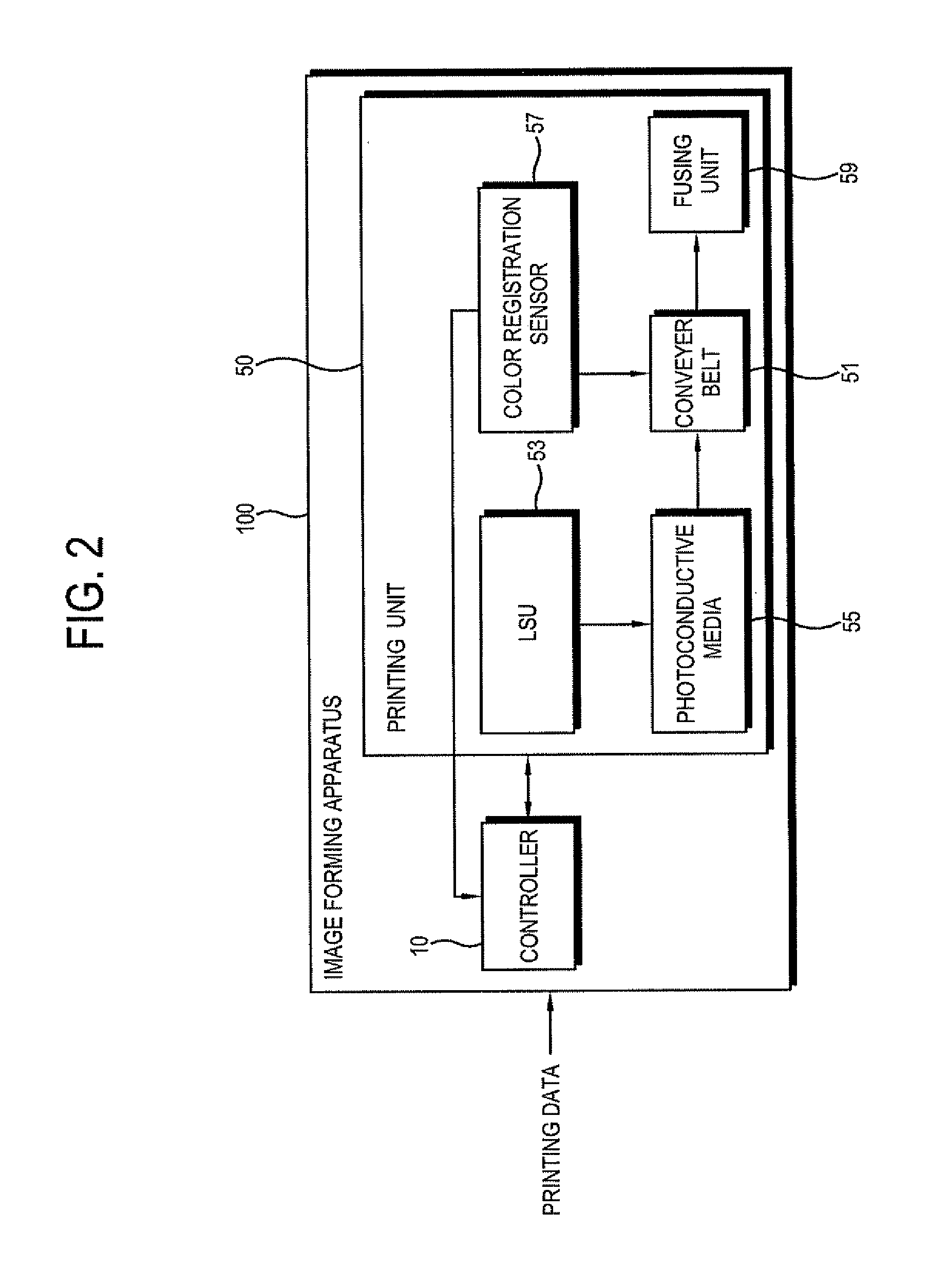

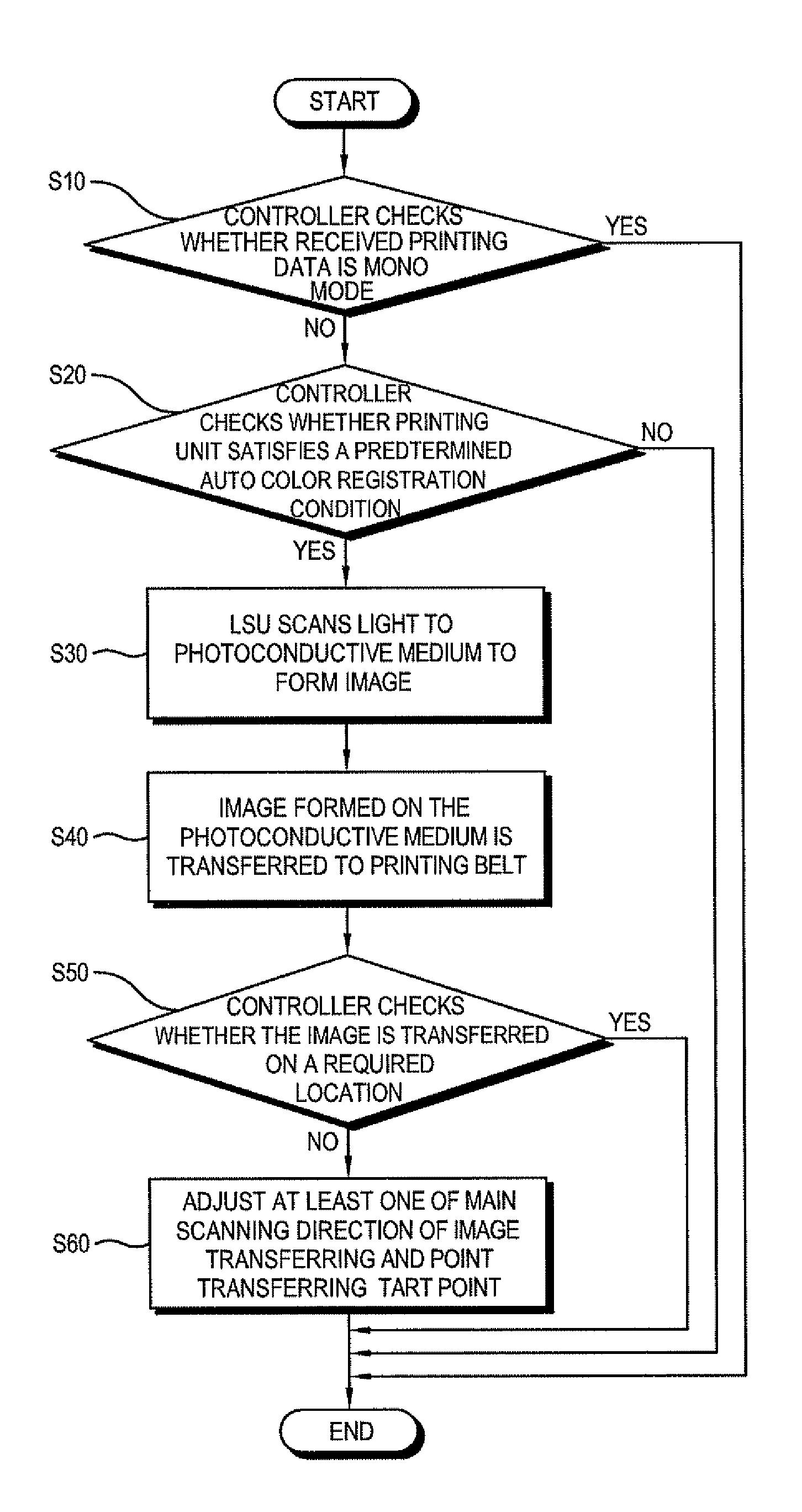

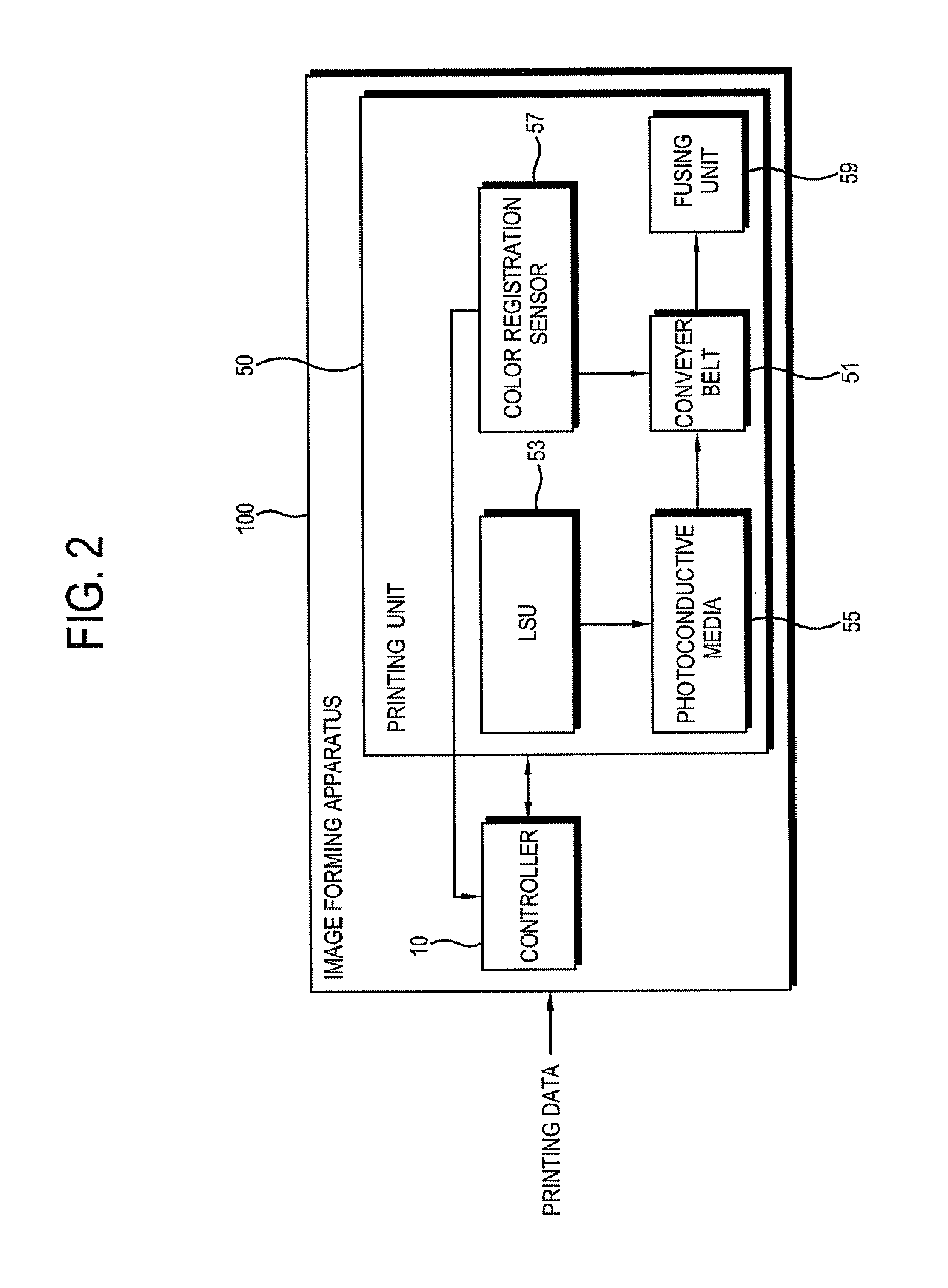

Image forming apparatus and control method thereof

ActiveUS20080137117A1ConserveAvoid unnecessary power consumptionRecording apparatusDigitally marking record carriersColor imageImage formation

Owner:HEWLETT PACKARD DEV CO LP

Power saving method of portable internet device and portable internet device thereof, and instant messaging system using the same

ActiveUS8060768B2Prevent unnecessary power consumptionReduce frequencyEnergy efficient ICTPower managementThe InternetInternet appliance

The present invention discloses a power saving method of a portable Internet device, the portable Internet device and its instant messaging system. If a screen of the portable Internet device is in non-view state, for example, both backlight module and LCD panel are turned off, it means that a user is not viewing the screen, and thus the message update frequency of the instant messaging program is lowered to prevent unnecessary transmission and receiving of wireless signals, so as to reduce power comsumption of the portable Internet device.

Owner:ACER INC

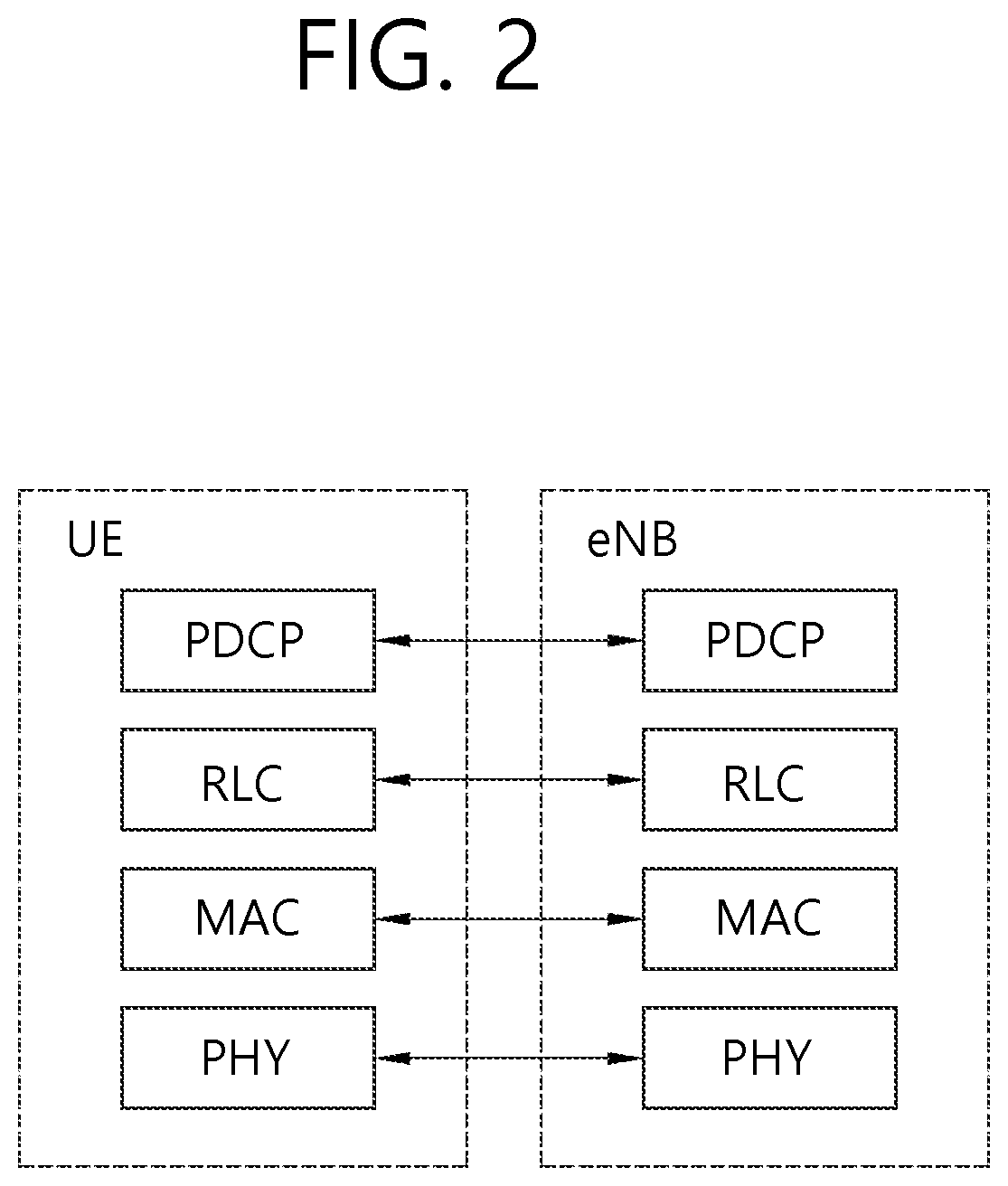

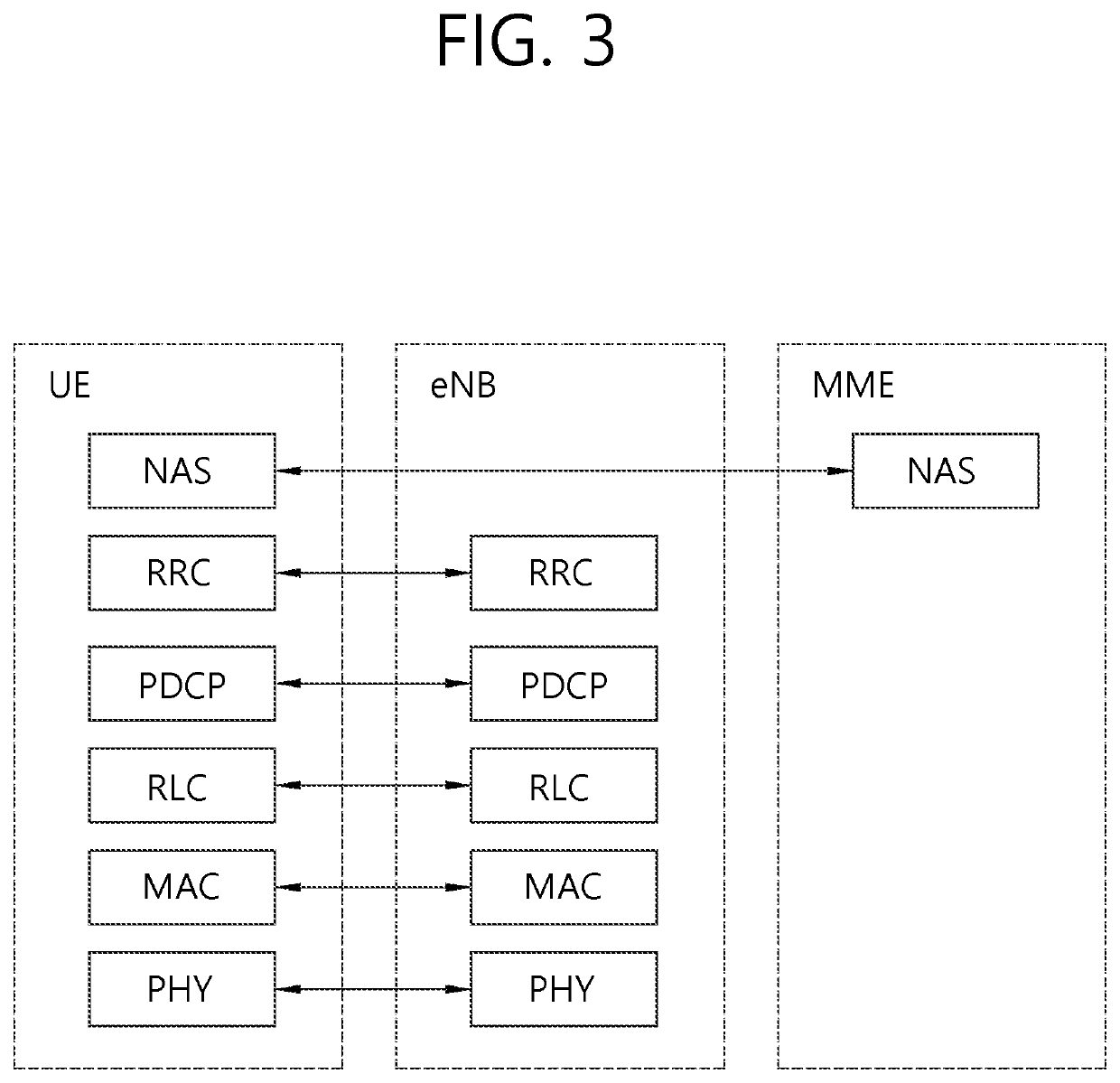

Method for reducing complexity in downlink control channel for saving power in wireless communication system, and terminal using same method

ActiveUS20210185651A1Prevent unnecessary power consumptionReduce controlPower managementError preventionTarget rangeReal-time computing

The present disclosure relates to a method for performing monitoring, performed by user equipment (UE), in a wireless communication system, the method comprising: receiving information related to monitoring from a network; and performing monitoring on the basis of the information related to monitoring, wherein the information related to monitoring is information related to reduction of a range of a target which the UE will monitor.

Owner:LG ELECTRONICS INC

Driving voltage controller of sense amplifiers for memory device

InactiveUS20040213063A1Prevent unnecessary power consumptionStable voltageDigital storageVoltage generatorAudio power amplifier

Disclosed is a driving voltage controller of sense amplifiers for a memory device which prevents the sense amplifier from being over-driven when an external power voltage is used for an internal driving voltage of the sense amplifier. Reference voltage generator generates a reference voltage. Core voltage generator generates a core voltage to be used for driving voltage of sense amplifier. Comparator compares the core voltage generated by core voltage generator with the reference voltage generated by reference voltage generator. Clamp adjusts a level of the core voltage generated by the core voltage generator based on an output signal of comparator. In the case where an external power used for a driving voltage of the sense amplifier is excessively high, the comparator compares the external power voltage with the reference voltage. When the driving voltage of sense amplifier exceeds the reference voltage, the clamp drops the driving voltage of sense amplifier. Thus, the core voltage can be stably supplied.

Owner:SK HYNIX INC

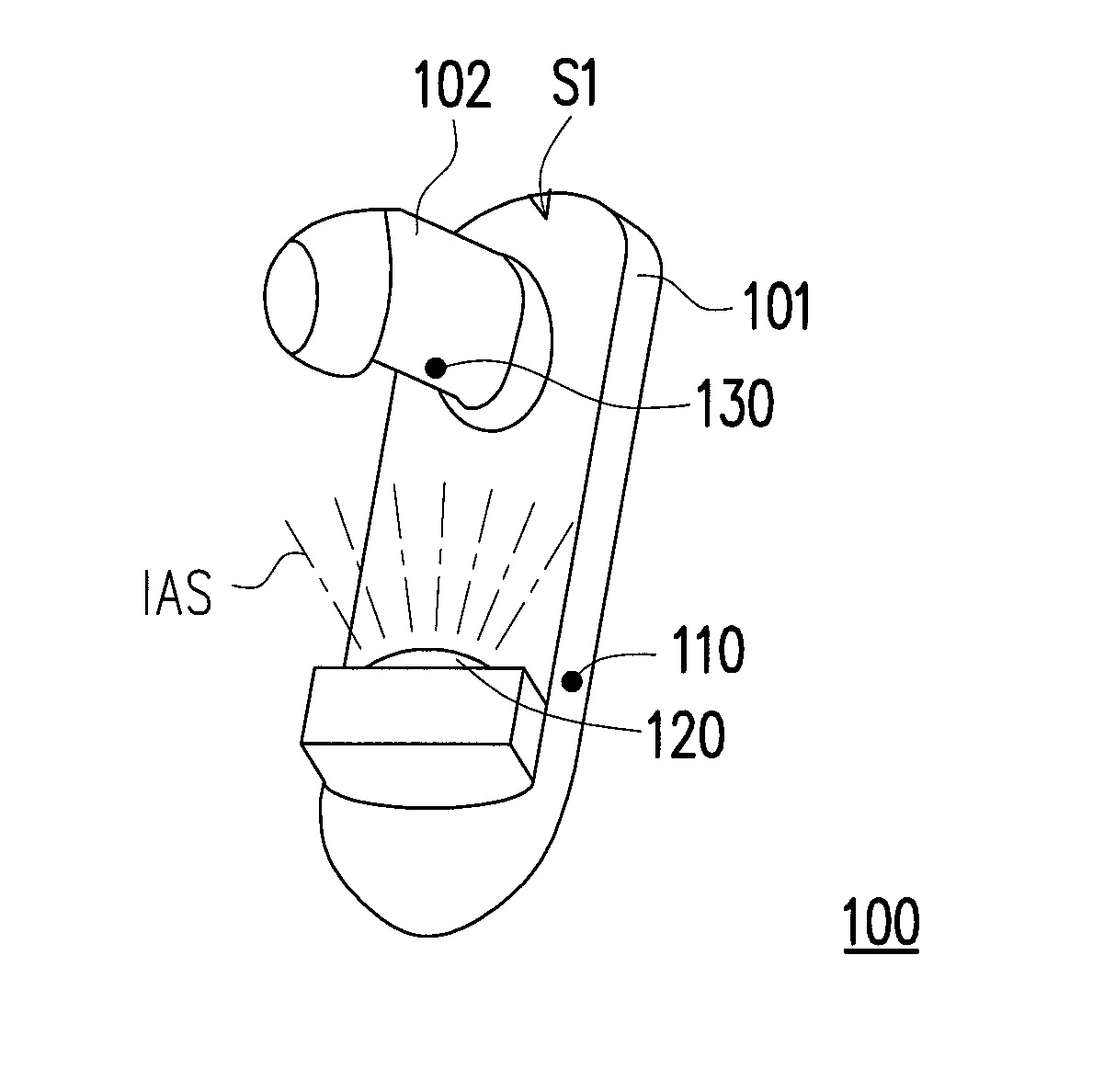

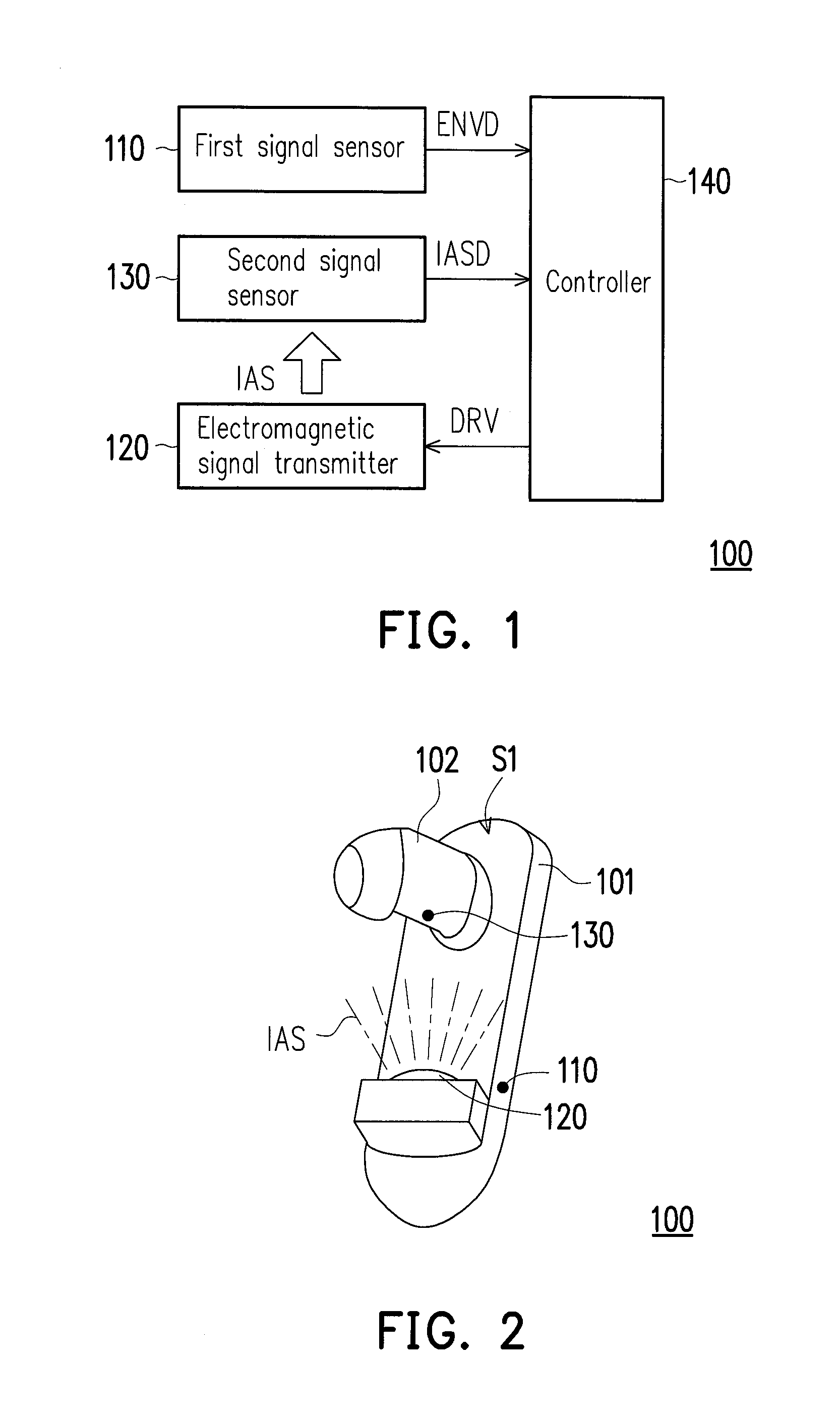

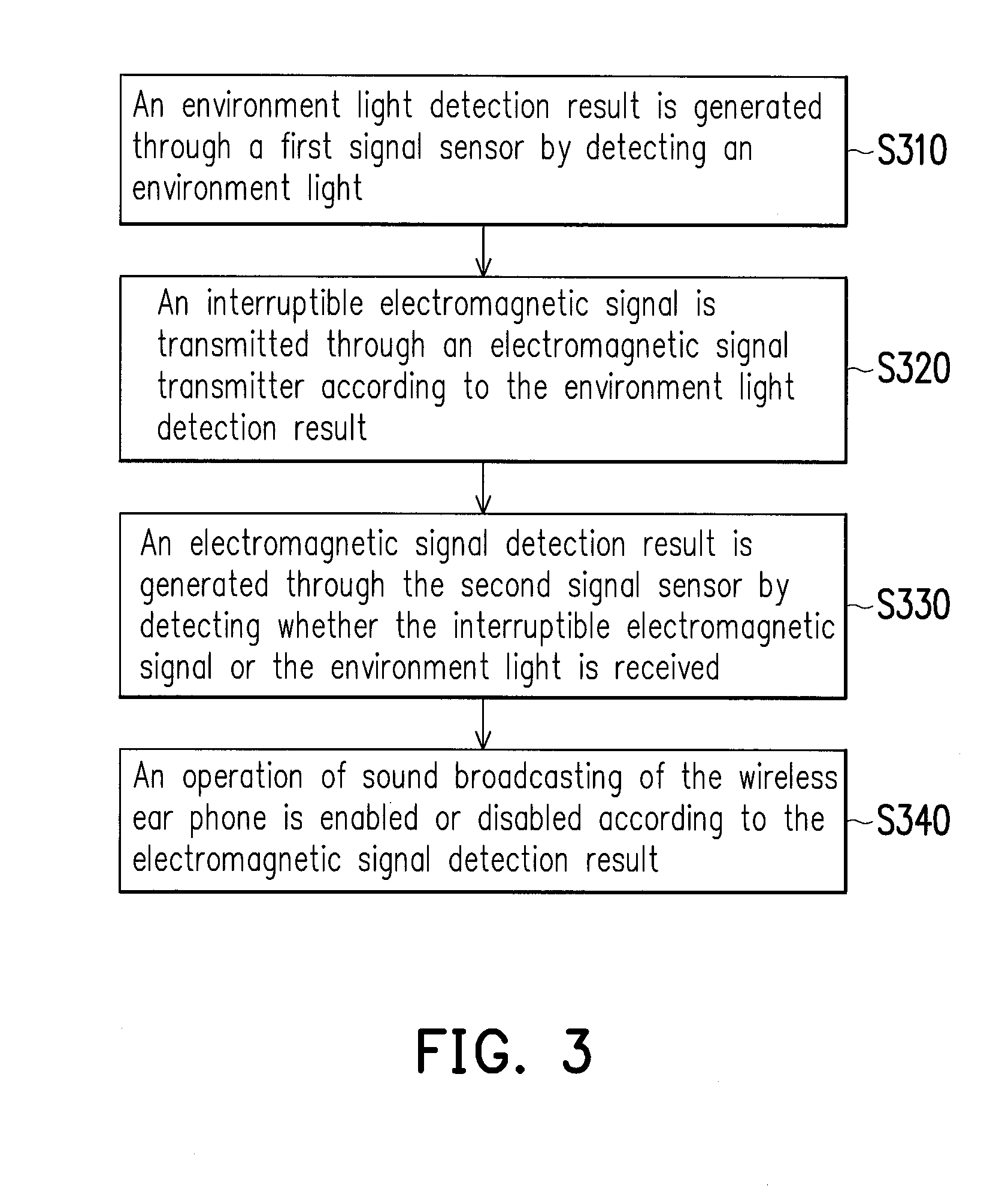

Wireless ear phone and sound broadcasting method thereof

ActiveUS20150080062A1Conserve power requirementSave powerSubstation speech amplifiersDevices with sensorEngineeringHeadphones

A wireless ear phone and a sound broadcasting method thereof are provided. The wireless ear phone includes a first signal sensor, an electromagnetic signal transmitter, a second signal sensor and a controller. The first signal sensor generates an environment light detection result by detecting an environment light. The electromagnetic signal transmitter transmits an interruptible electromagnetic signal. The second signal sensor is disposed on a transmission path of the interruptible electromagnetic signal, and the second signal sensor generates an electromagnetic signal detection result by detecting whether the interruptible electromagnetic signal or the environment light is received. The controller enables or disables an operation of sound broadcasting of the wireless ear phone according to the electromagnetic signal detection result. When the wireless ear phone is put into an ear of a user, the transmission path is cut-off by the ear of the user.

Owner:WISTRON CORP

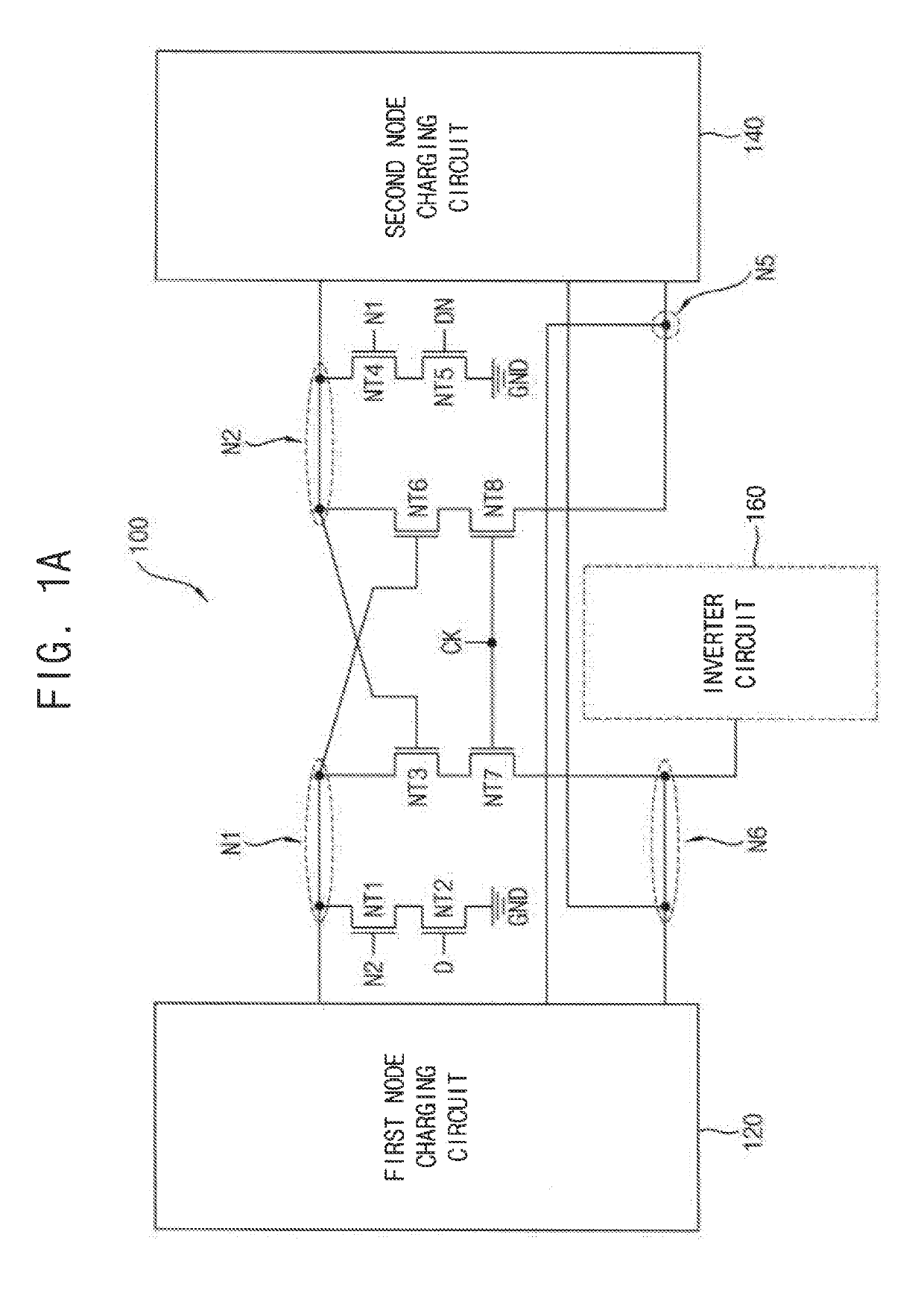

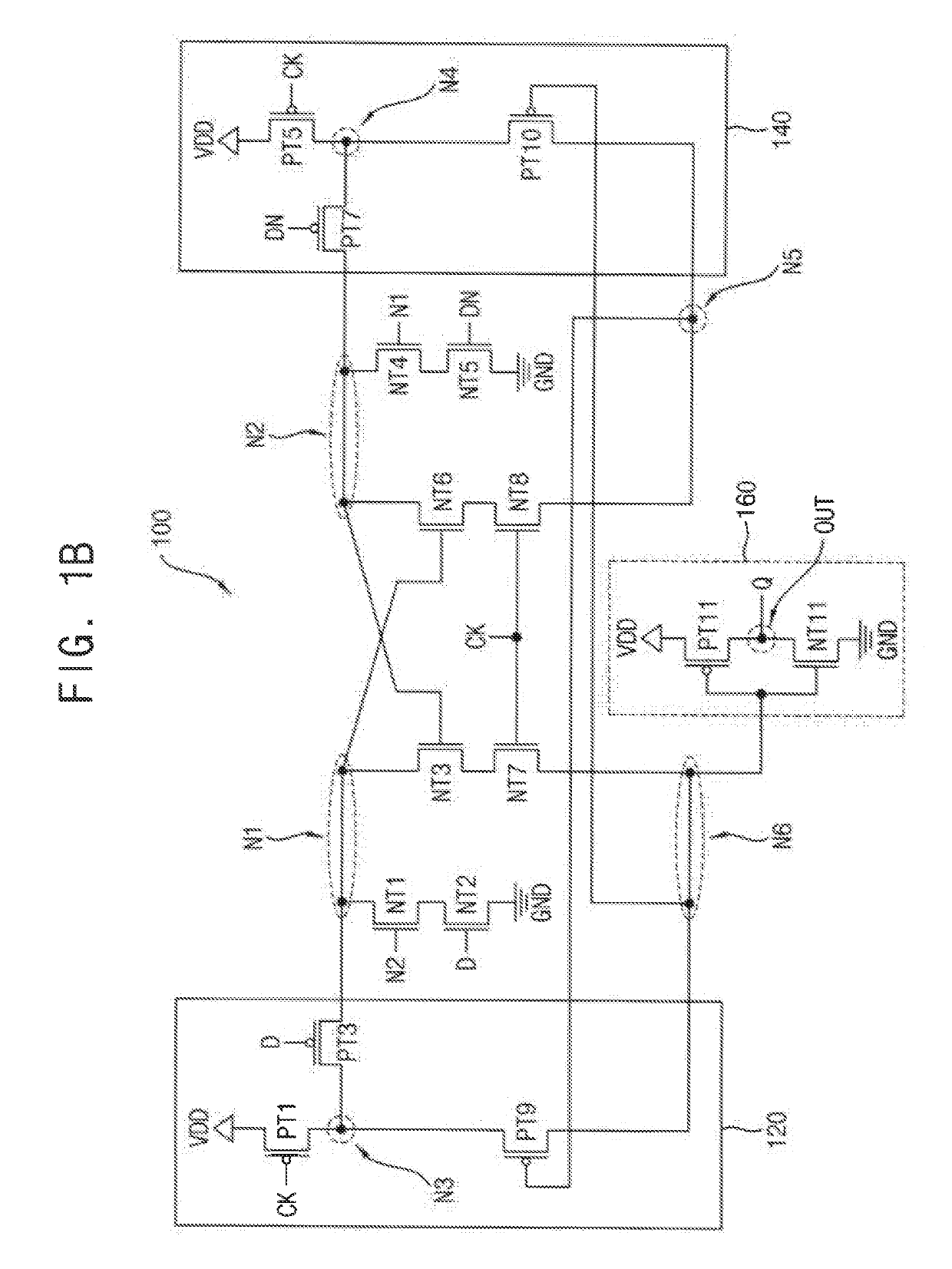

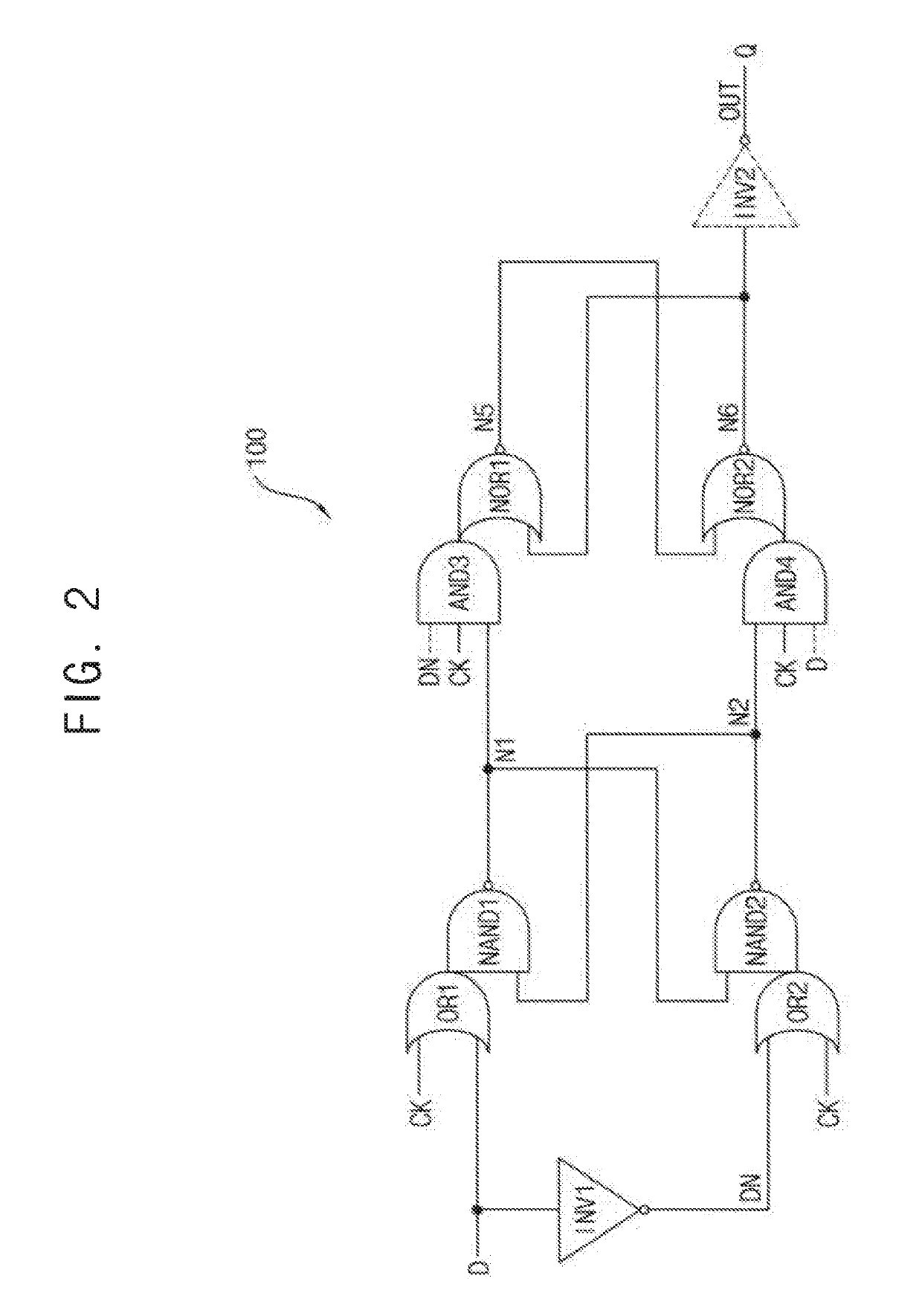

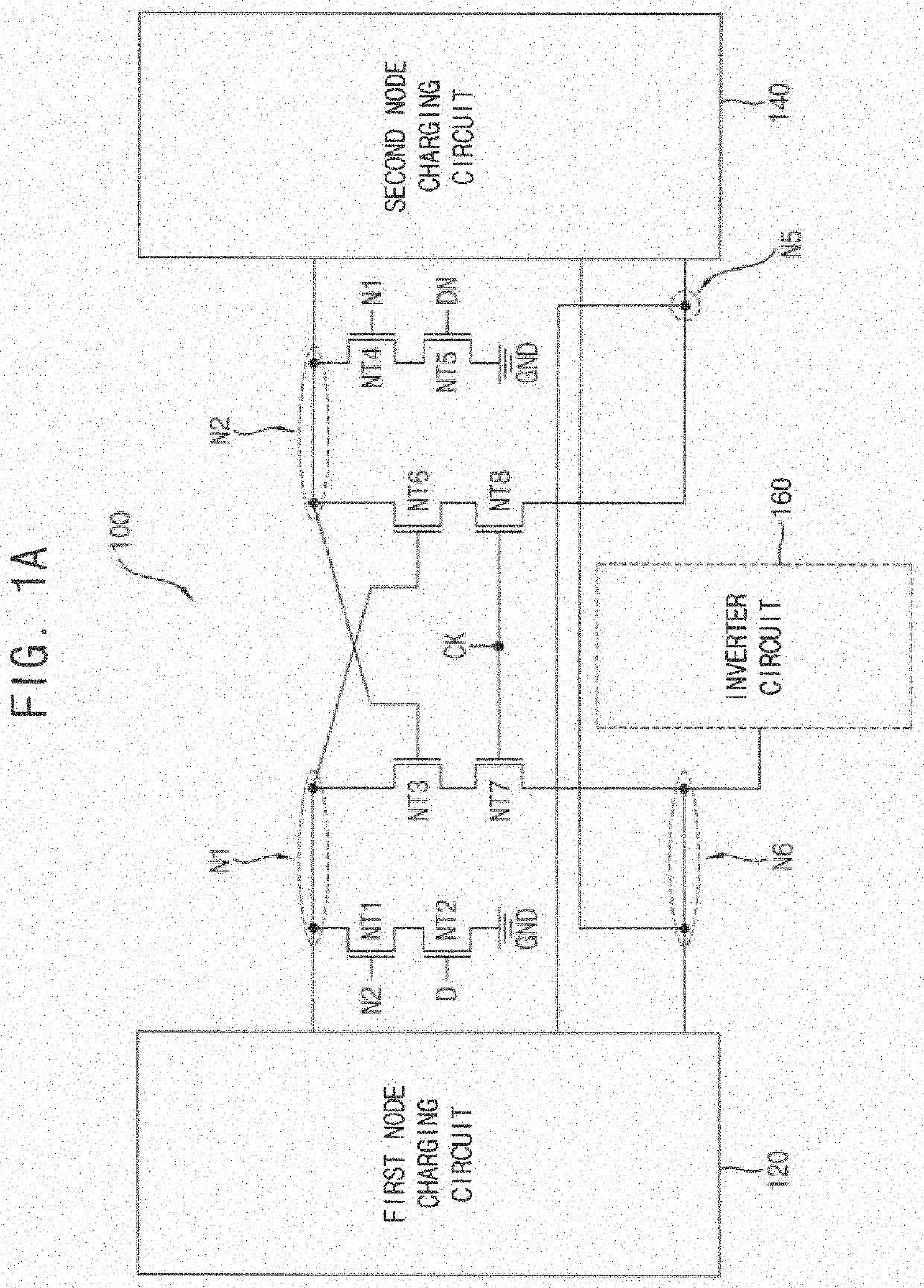

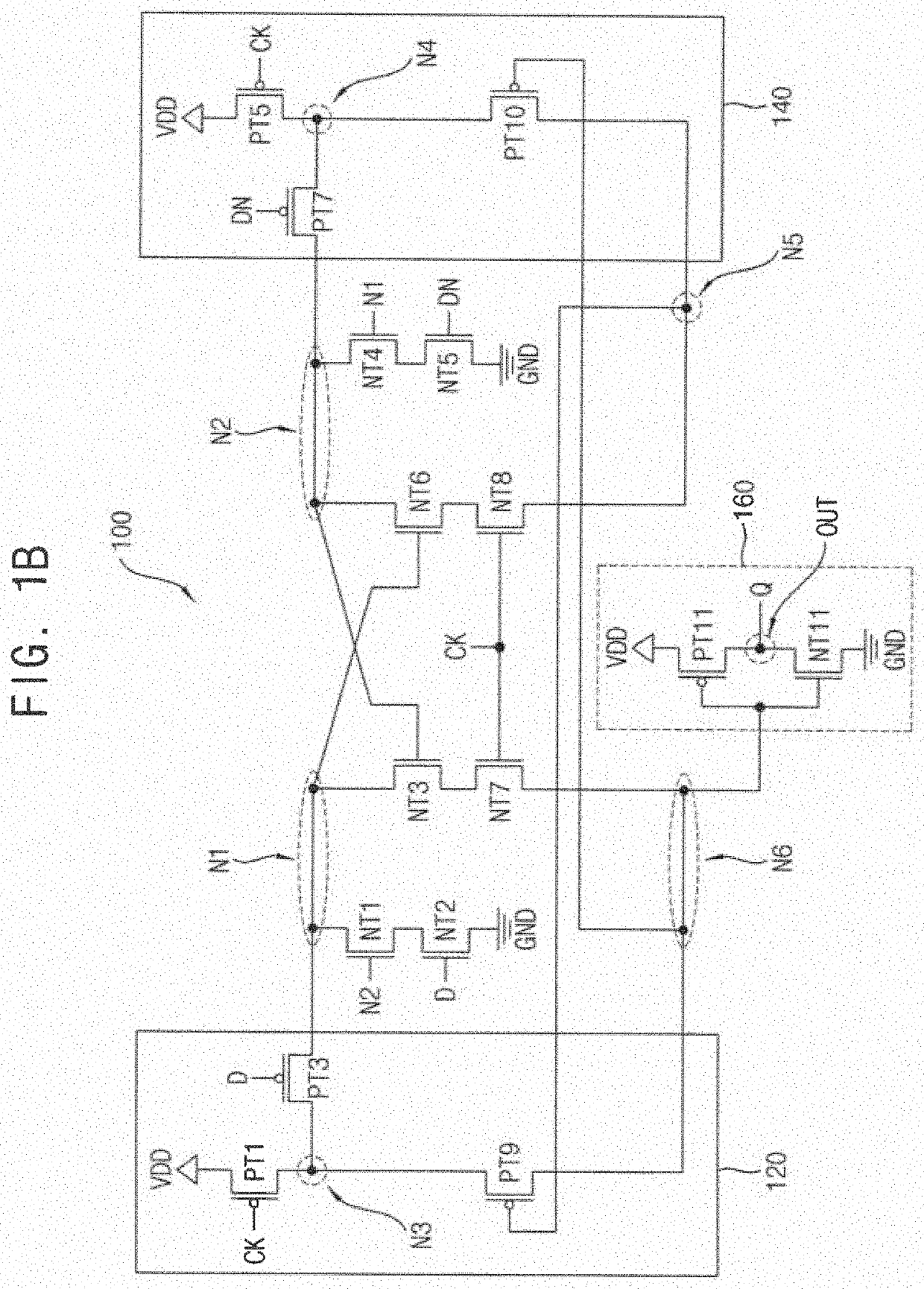

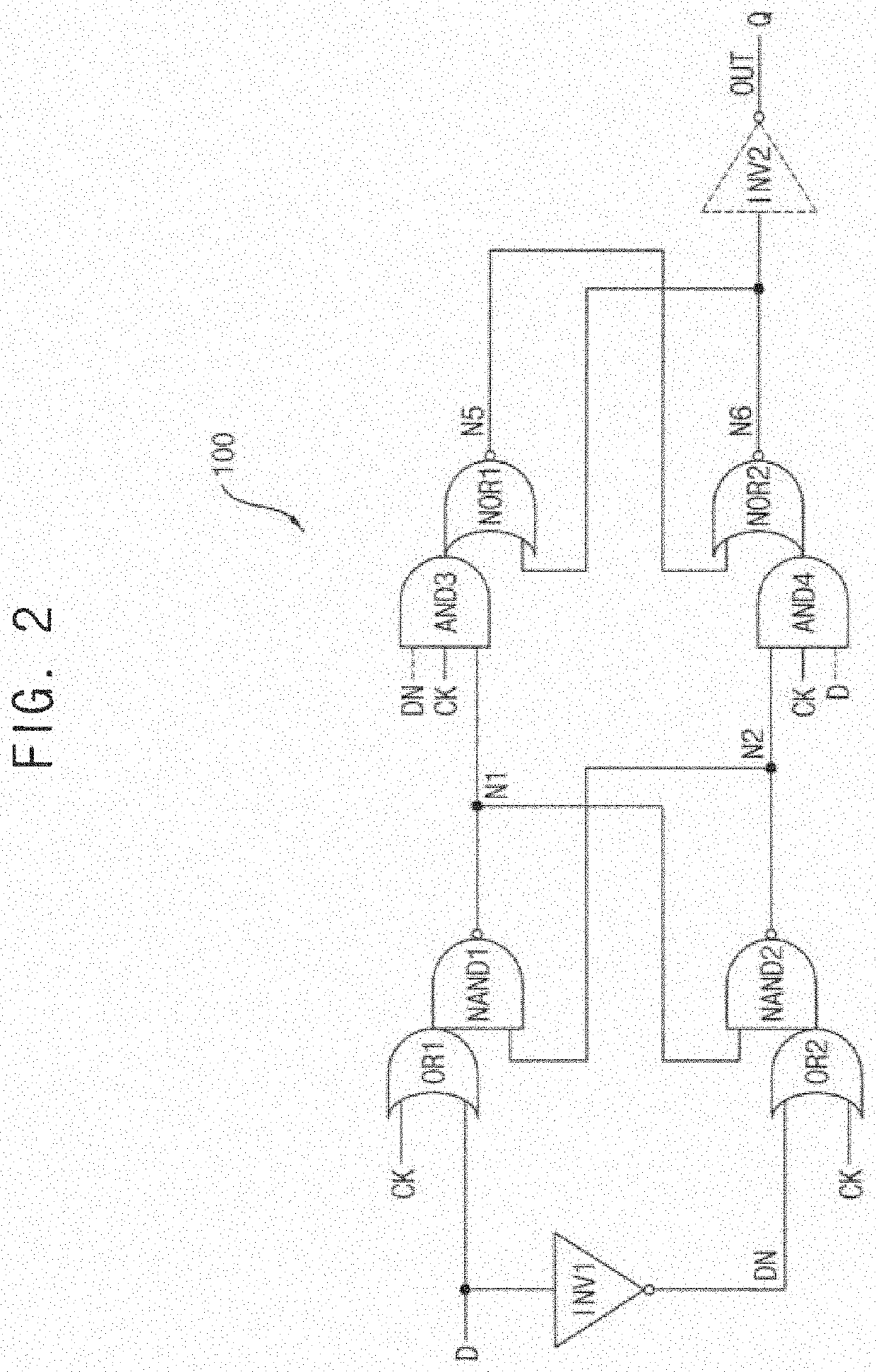

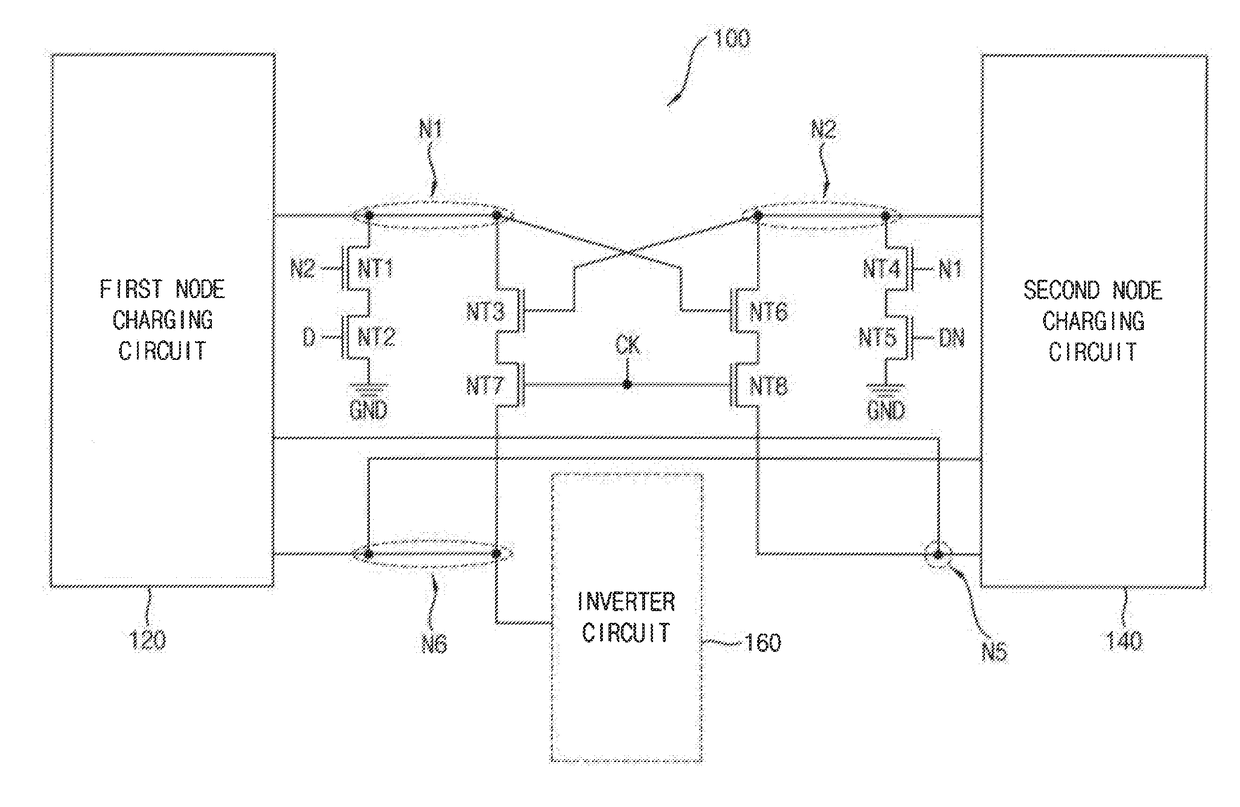

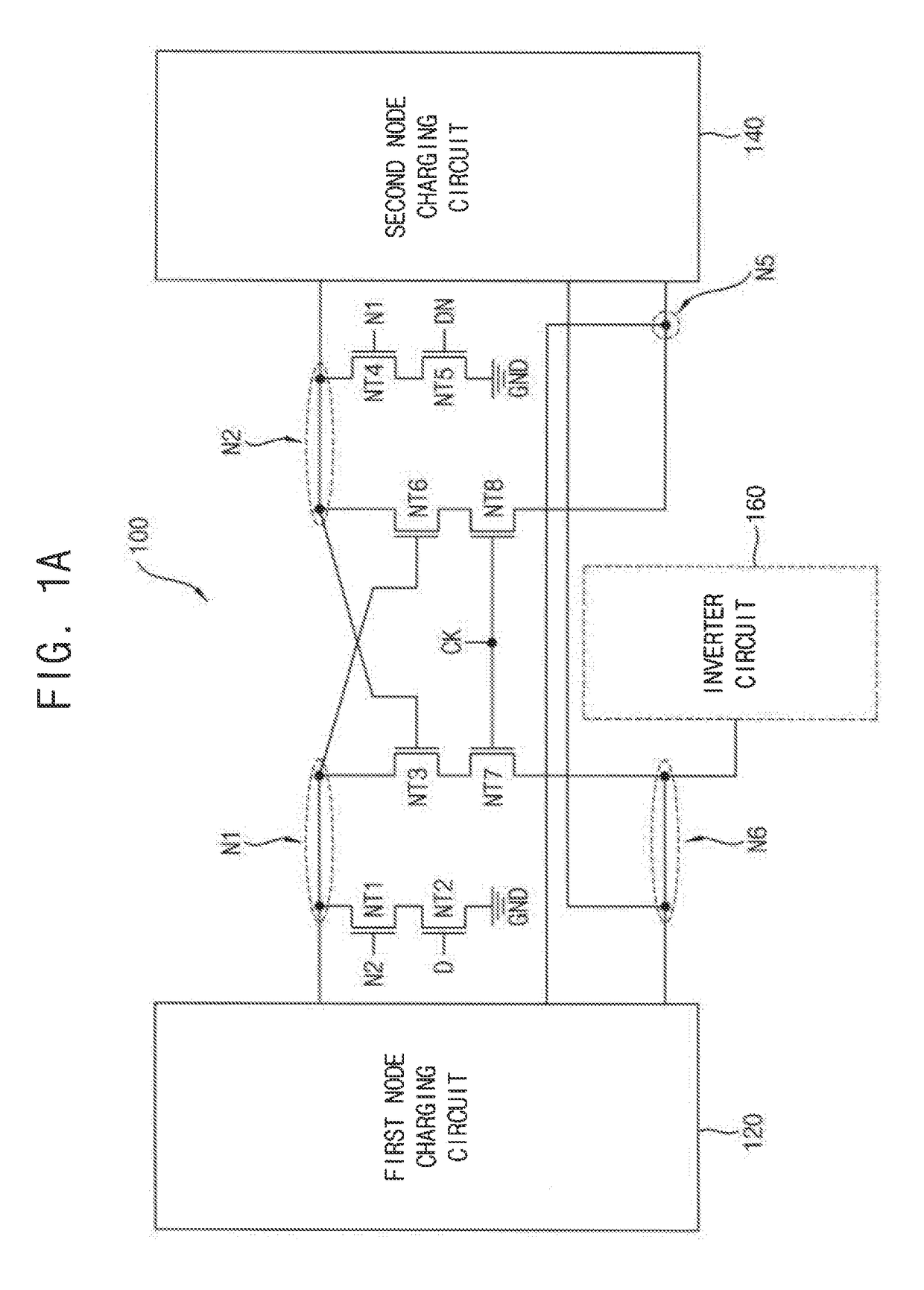

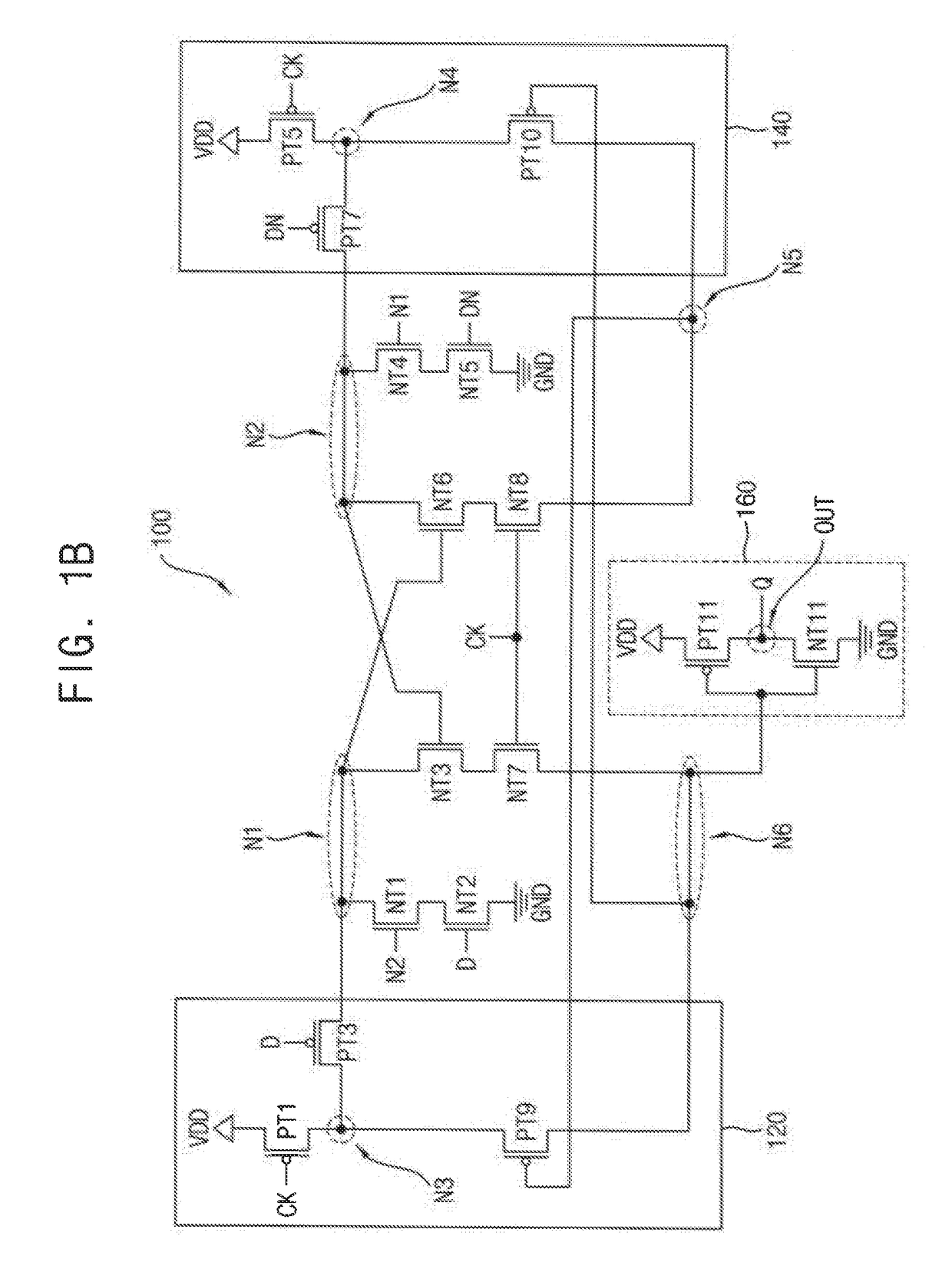

Flip-flop

ActiveUS10396761B2Prevent unnecessary power consumptionLow powerPulse generation by active elementsVoltage/current interference eliminationSoftware engineeringFlip-flop

A flip-flop includes a first node charging circuit configured to charge a first node with inverted input data generated by inverting input data, a second node charging circuit configured to charge a second node with the input data, and first through eighth NMOS transistors. The flip-flop is configured to latch the input data at rising edges of a clock signal and output latched input data as output data. The flip-flop includes an internal circuit configured to charge a sixth node with inverted input data generated by inverting the latched input data.

Owner:SAMSUNG ELECTRONICS CO LTD

Flip-flop

ActiveUS20190379361A1Prevent unnecessary power consumptionLow powerPulse generation by active elementsVoltage/current interference eliminationTransistorClock signal

A flip-flop includes a first node charging circuit configured to charge a first node with inverted input data generated by inverting input data, a second node charging circuit configured to charge a second node with the input data, and first through eighth NMOS transistors. The flip-flop is configured to latch the input data at rising edges of a clock signal and output latched input data as output data. The flip-flop includes an internal circuit configured to charge a sixth node with inverted input data generated by inverting the latched input data.

Owner:SAMSUNG ELECTRONICS CO LTD

Flip-flop

ActiveUS20180145661A1Prevent unnecessary power consumptionLow powerPulse generation by active elementsVoltage/current interference eliminationEngineeringTransistor

A flip-flop includes a first node charging circuit configured to charge a first node with inverted input data generated by inverting input data, a second node charging circuit configured to charge a second node with the input data, and first through eighth NMOS transistors. The flip-flop is configured to latch the input data at rising edges of a clock signal and output latched input data as output data. The flip-flop includes an internal circuit configured to charge a sixth node with inverted input data generated by inverting the latched input data.

Owner:SAMSUNG ELECTRONICS CO LTD

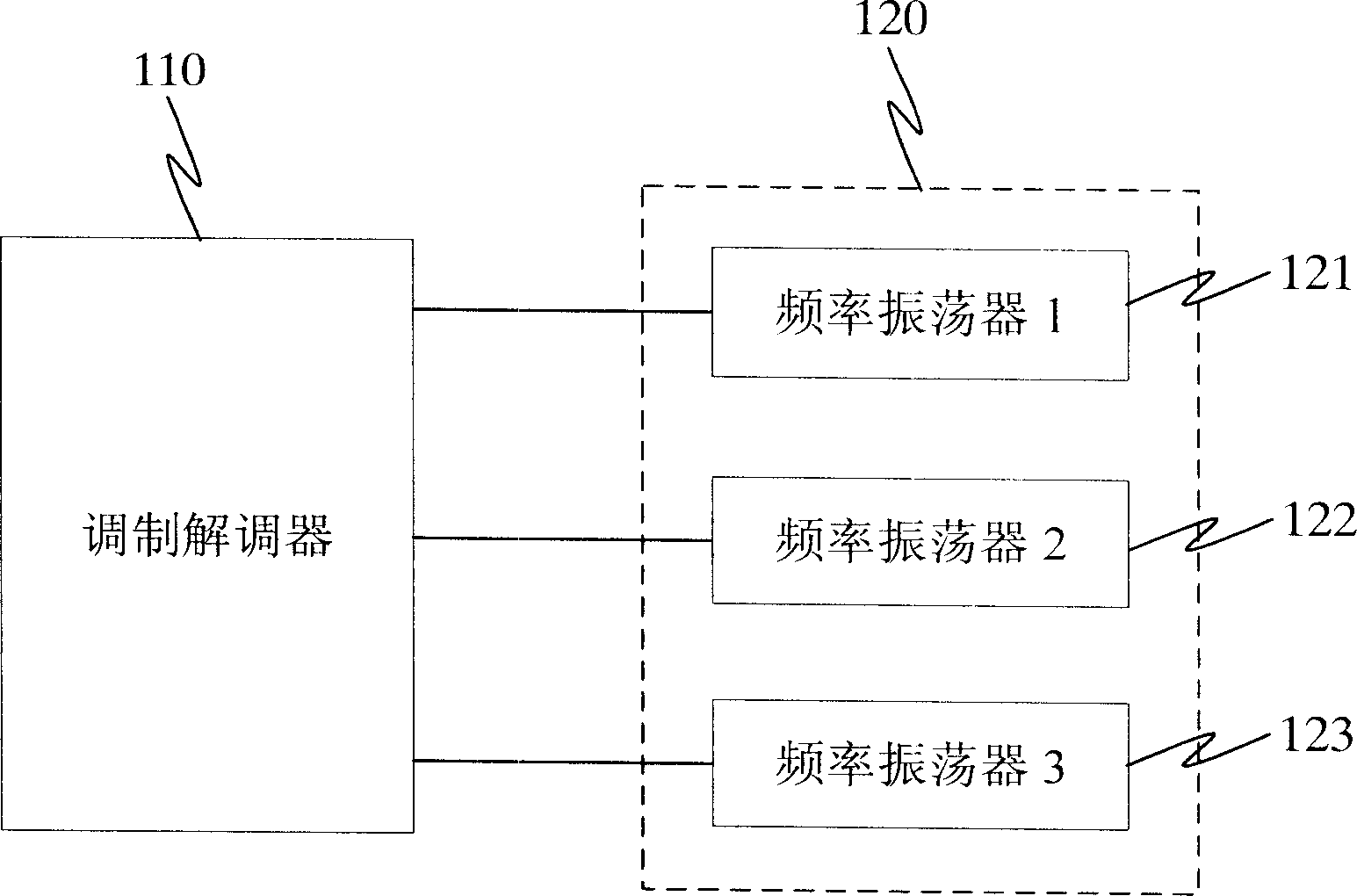

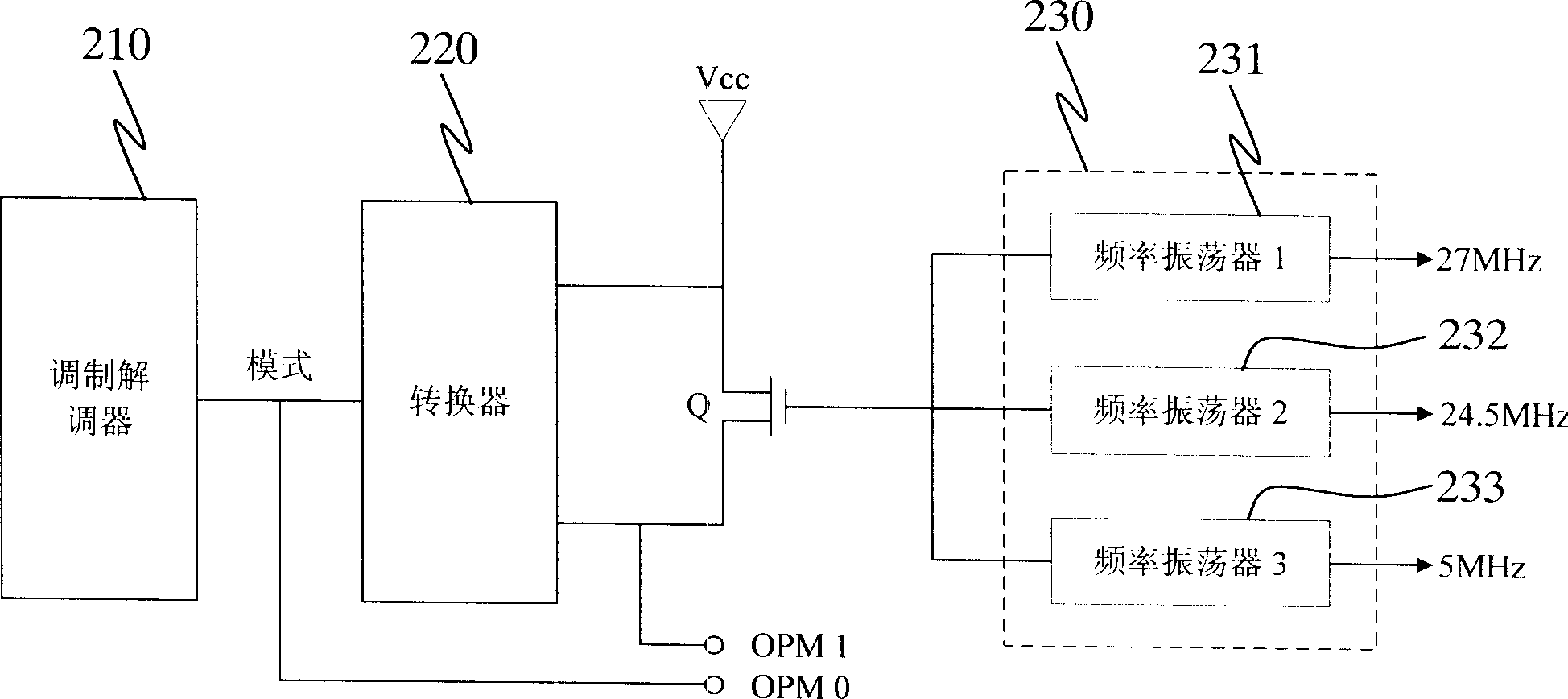

Terminal for digital multimedia broadcast and its control method

InactiveCN1878009APrevent unnecessary power consumptionPrevent electricity consumptionTelevision system detailsColor television detailsField-effect transistorCurrent consumption

A DMB(Digital Multimedia Broadcasting) terminal and a control method thereof is provided to prevent unnecessary current consumption in a DMB receiving system. A DMB(Digital Multimedia Broadcasting) terminal comprises an inverter and an FET(Field Effect Transistor,Q). The inverter converts a mode signal offered from an MSM(Mobile Station Modem) into a DMB receipt mode signal. The FET(Field Effect Transistor,Q) activates an operation of a DMB SOC(System On Chip) only in case of going into a DMB mode according to an output signal of the inverter. The inverter inverts a mode signal offered from the MSM.

Owner:LG ELECTRONICS (CHINA) R&D CENT CO LTD

Image forming apparatus to selectively perform auto color registration and control method thereof

ActiveUS8284412B2Prevent unnecessary power consumptionSave materialRecording apparatusDigitally marking record carriersColor imageImage formation

Owner:HEWLETT PACKARD DEV CO LP

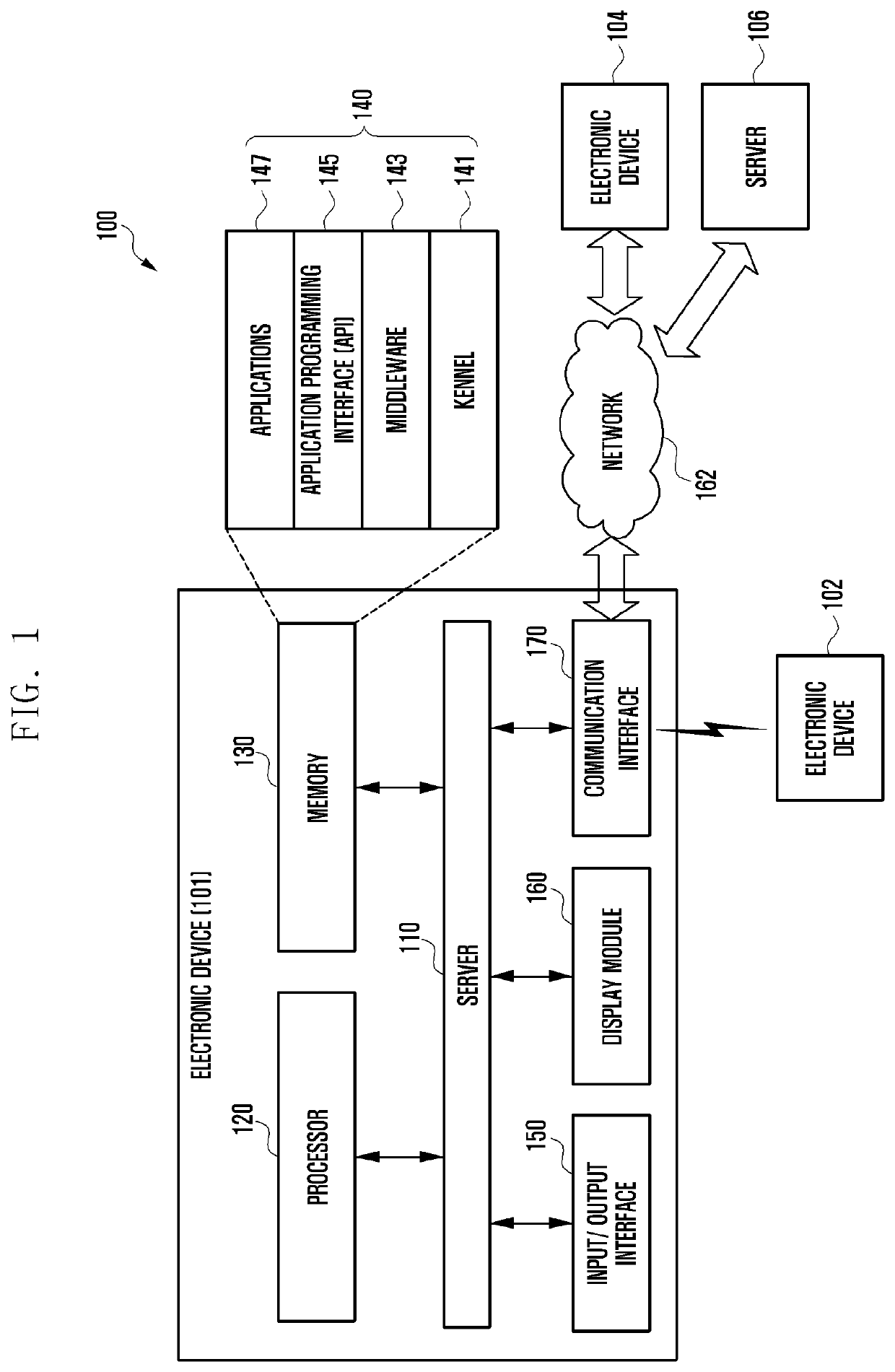

Electronic device and method for managing articles thereby

InactiveUS20200302772A1Avoid lostPrevent unnecessary power consumptionDatabase updatingParticular environment based servicesDisplay deviceEngineering

An electronic device according to various embodiments of the present invention comprises: a display; a communication module supporting short-range communication; a processor electrically connected to the display and the communication module; and a memory electrically connected to the processor, wherein the memory may store instructions that, when executed, cause the processor to: determine whether at least one predetermined article management condition has occurred; when it is determined that the article management condition has occurred, search for a signal, transmitted by at least one signal transmission apparatus, by controlling the communication module; receive the searched signal from the at least one signal transmission apparatus which transmits the signal; configure a list of articles corresponding to the article management condition on the basis of a database which includes data on articles and is stored in at least one of the memory and at least one external electronic device; and store, in the memory and the at least one external electronic device, the configured list of the articles corresponding to the article management condition. In addition, various embodiments are possible.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com