Output circuit for FPGA clock signal and processing method thereof

A clock signal output, clock signal technology, applied in logic circuits using specific components, logic circuits using basic logic circuit components, etc., can solve problems such as amplitude changes, other signal phase shifts, FPGA clock tree collapse, etc. achieve the effect of reducing lag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

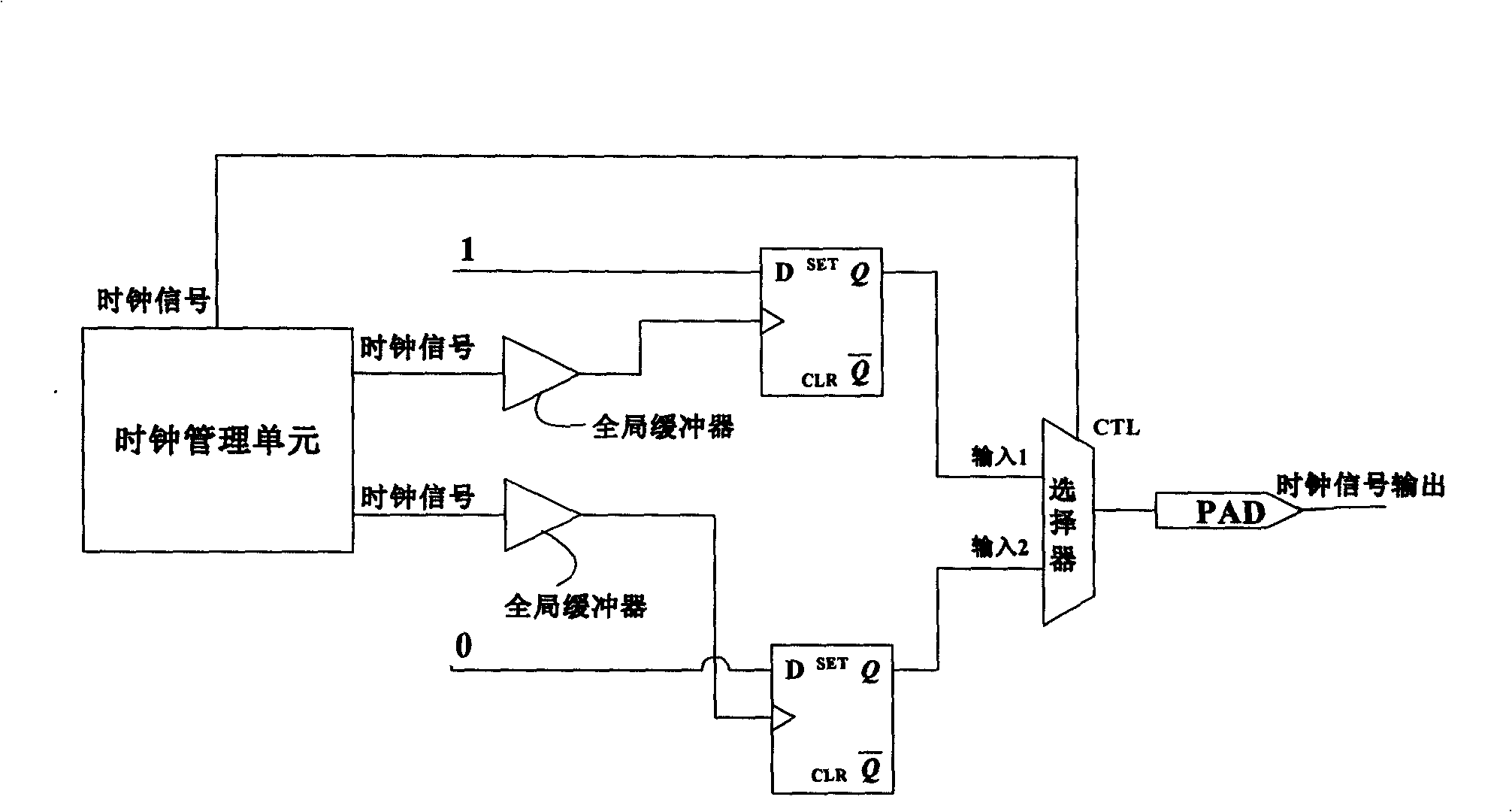

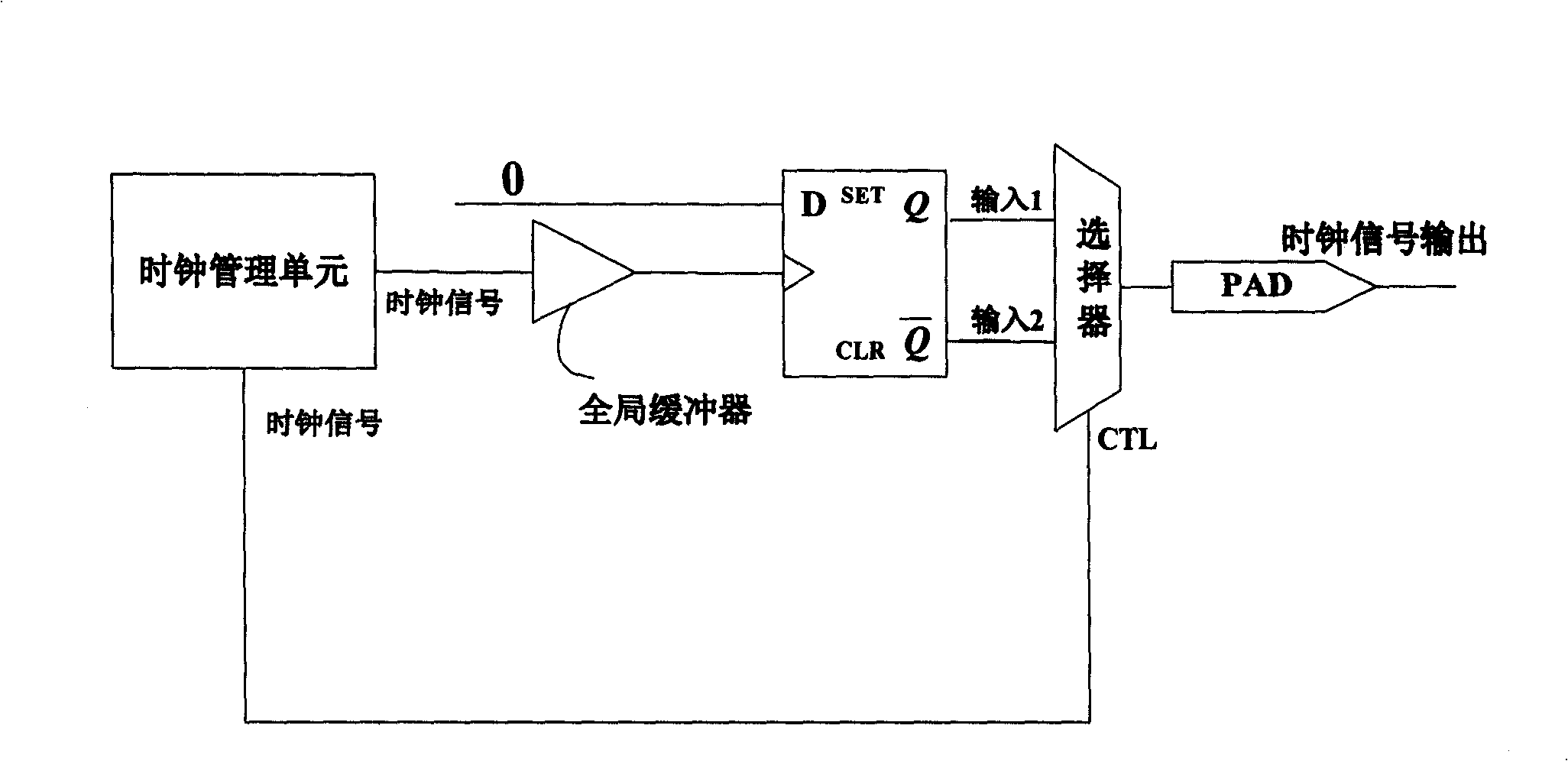

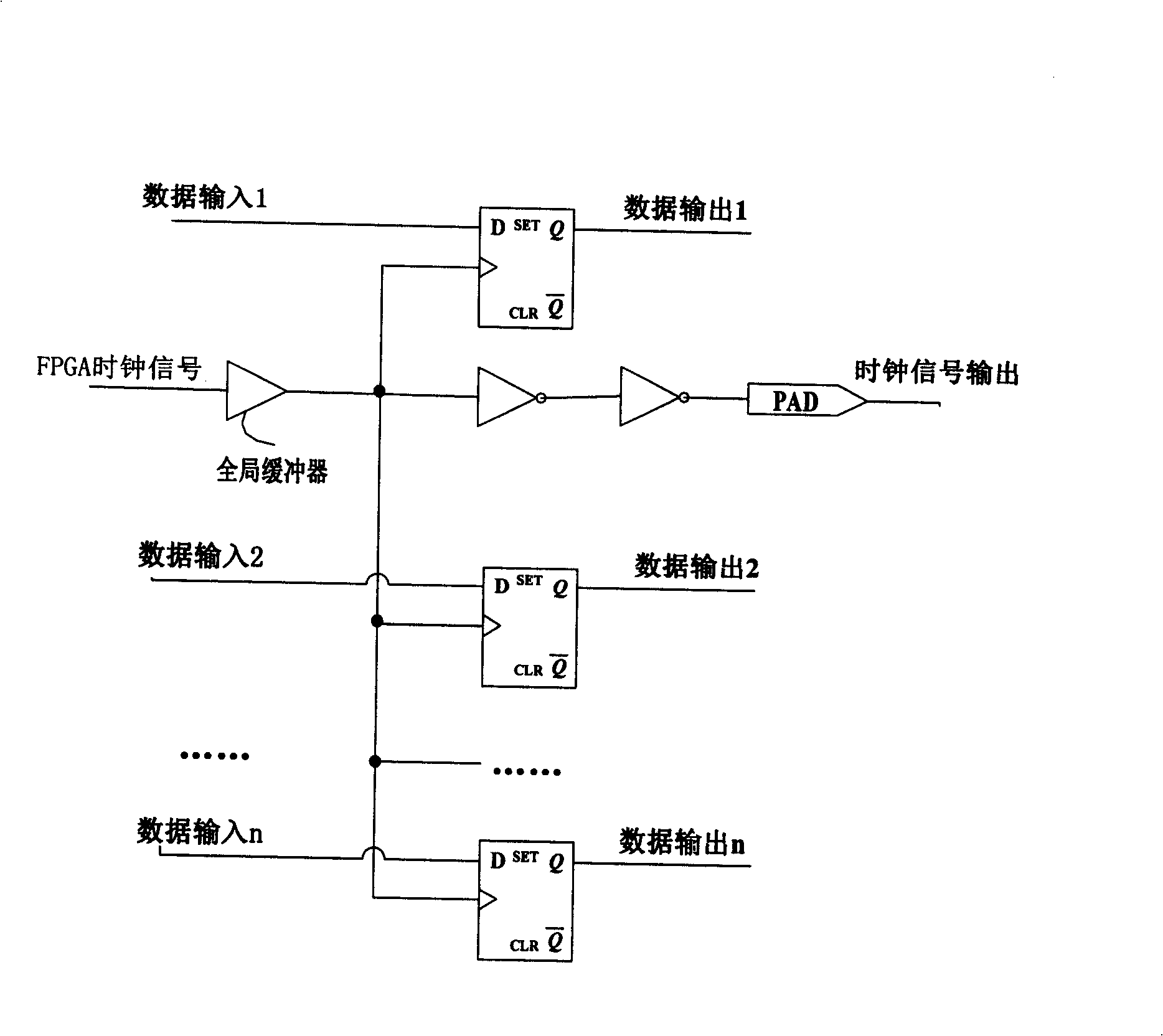

[0021] figure 1 It is the FPGA clock non-phase output circuit diagram using two flip-flops of the present invention. As shown in the figure, in this kind of circuit, the flip-flop unit is composed of two D flip-flops in parallel.

[0022] The clock management unit of the FPGA generates and outputs a clock signal, which enters the clock terminals of the two D flip-flops through the global buffer BUFG. Since the clock signal output by the FPGA needs to be in phase with its internal clock signal, that is, the so-called positive phase output, the input signal of a D flip-flop is connected to logic "1", and its output terminal is connected to the first input signal terminal of the selector; The input signal of a D flip-flop is connected to logic "0", and its output terminal is connected to the second input signal terminal of the selector.

[0023] The control signal of the selector is the clock signal output by the clock management unit. When it is "1", the first input signal ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More