SOC chip bus dynamic multi-level frequency adjustment circuit and method

A technology of bus frequency and chip bus, which is applied in the field of SOC chip bus frequency adjustment circuit, can solve the problems of slow response, difficult clock control of software, and inaccurate and timely detection of software, so as to achieve the effect of good energy efficiency ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

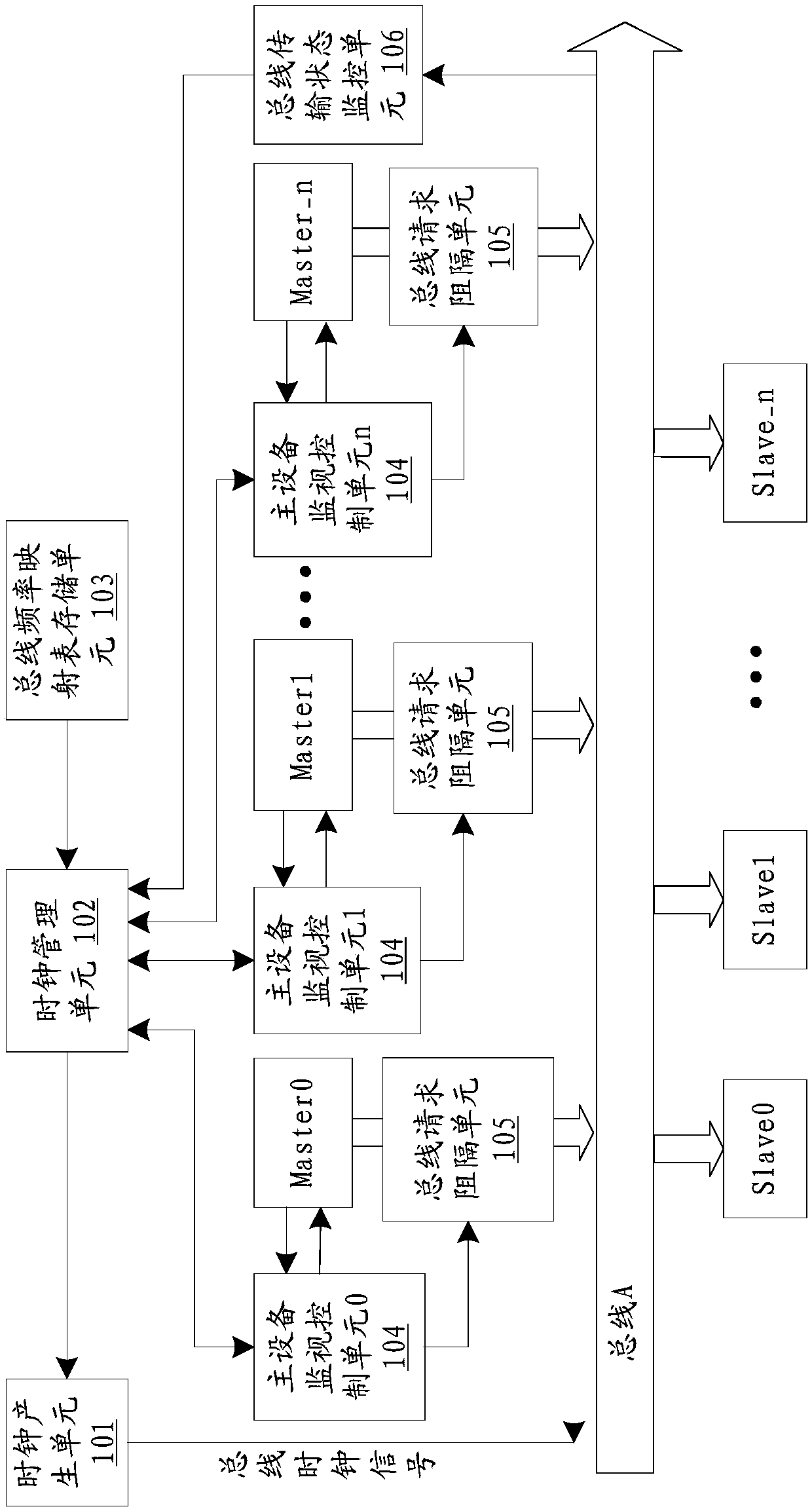

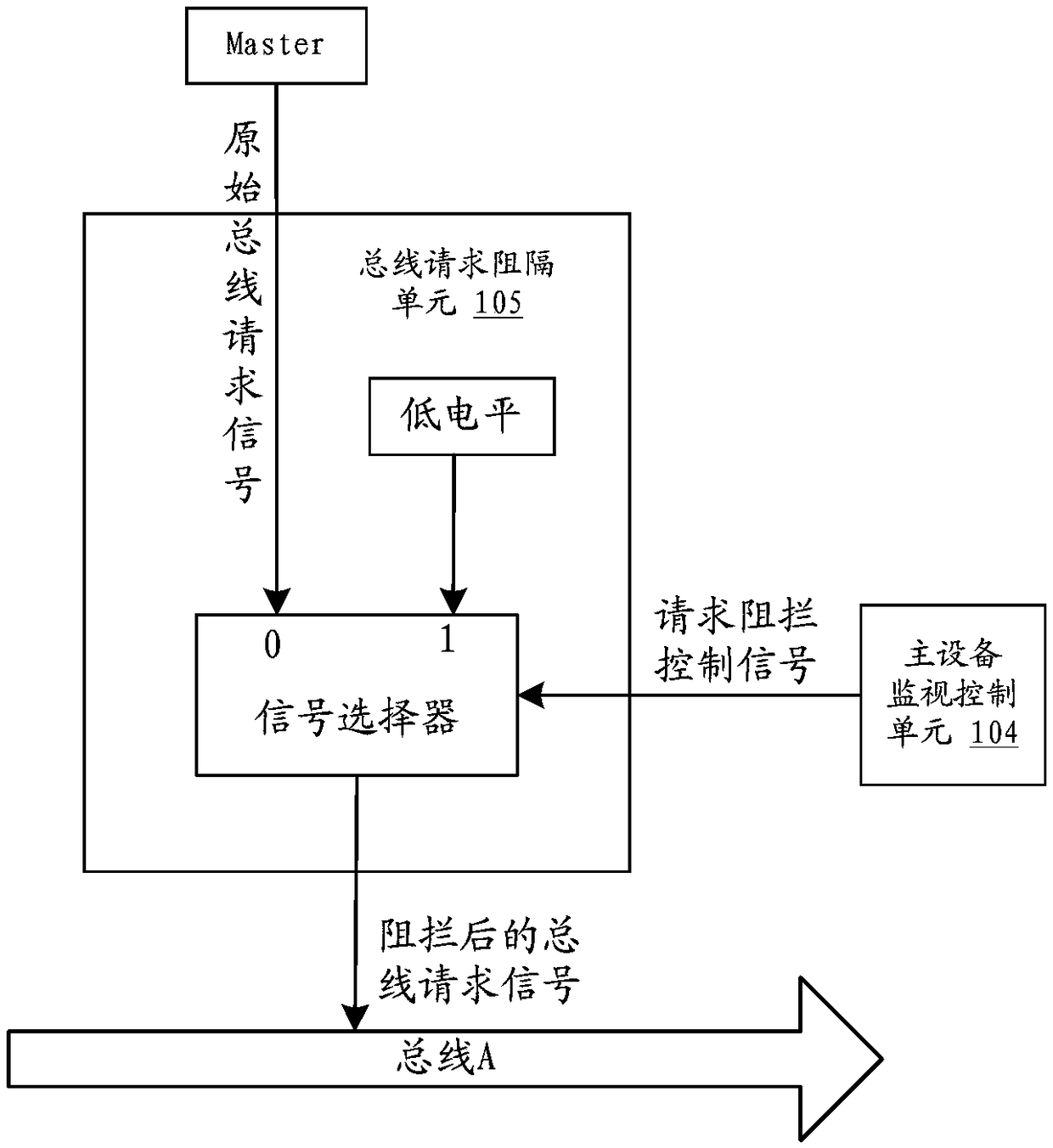

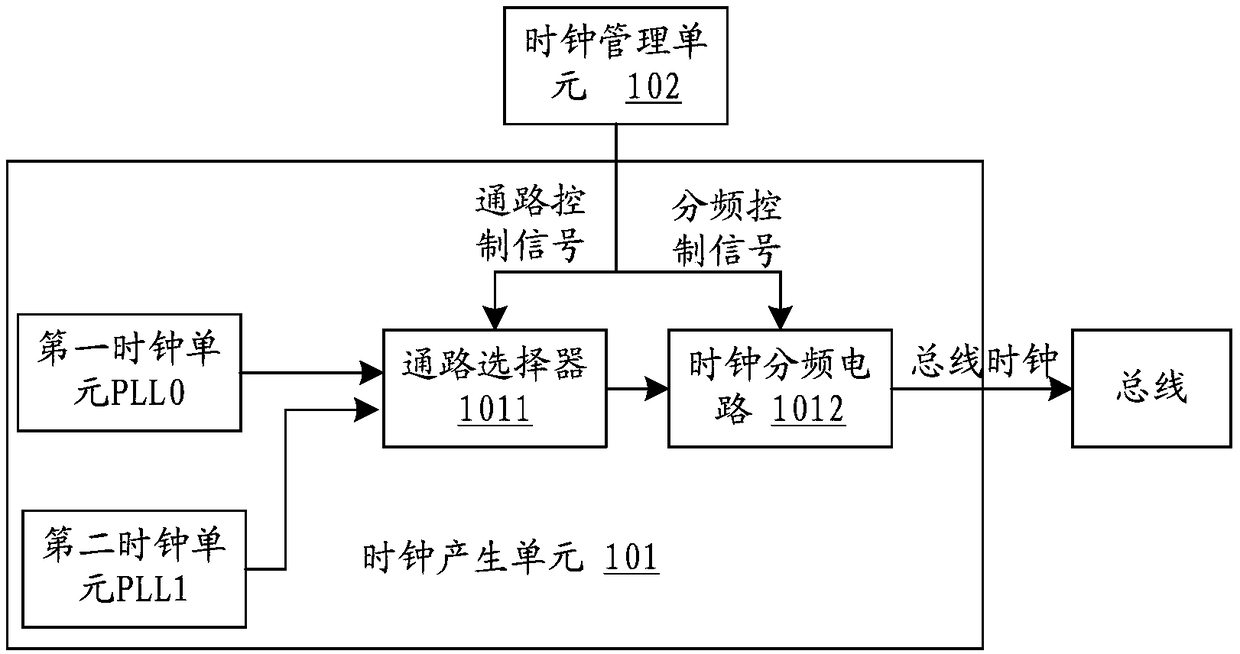

[0042] see Figure 1 to Figure 3 As shown, the present invention provides a SOC chip bus dynamic multi-stage frequency adjustment circuit and a SOC chip bus dynamic multi-stage frequency adjustment method based on the circuit, the SOC chip bus dynamic multi-stage frequency adjustment circuit includes a clock generation unit 101, a clock management Unit 102, bus frequency mapping table storage unit 103, master device monitoring control unit 104, bus request blocking unit 105 and bus transmission state monitoring unit 106; wherein, said master device monitoring control unit 104 and said bus request blocking unit 105 are respectively One-to-one corresponding settings with the master device (represented as Master0, Master1, ..., Master_n in the figure),

[0043]The clock management unit 102 is respectively connected to the bus frequency mapping table storage unit 103 and the master monitoring control unit 104; the master monitoring control unit 104 is also connected to the master ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More