A shared on-line debugging method based on FPGA prototype verification system

A technology of prototype verification and debugging methods, applied in functional inspection, detection of faulty computer hardware, etc., can solve the problems of slow simulation speed, inability to achieve performance, lengthy simulation speed, etc., to avoid errors, improve simulation speed, The effect of increasing usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific embodiments.

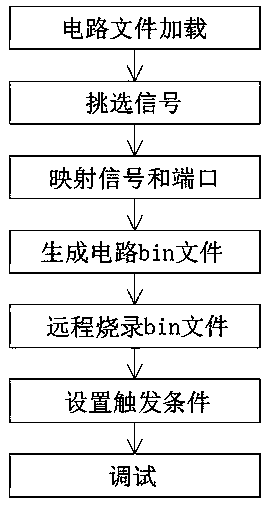

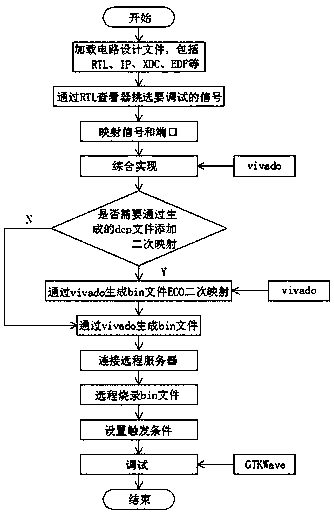

[0029] see Figure 1 to Figure 3 , the present invention provides a kind of technical scheme: a kind of shared type online debugging method based on FPGA prototype verification system, described debugging method comprises the following steps:

[0030] Step 1: Load the circuit file; open the client and load the circuit file that needs to be debugged and verified. The circuit file includes RTL, IP, XDC, EDF, etc.;

[0031] Step 2: Select the signal; select the signal you want to debug through the RTL code viewer;

[0032] Step 3: Map signals and ports; map the selected debug signals with the 32 predetermined Probes on the FPGA prototype verification board, and then call vivado;

[0033] Step 4: Generate the circuit bin file; judge whether it is ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More