Field programmable gate array (FPGA) prototype verification device and method

A technology for prototype verification and signal selection, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of short signal length, time-consuming more than ten to twenty hours, low positioning error efficiency, etc. Improve operability, increase signal types, and save time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

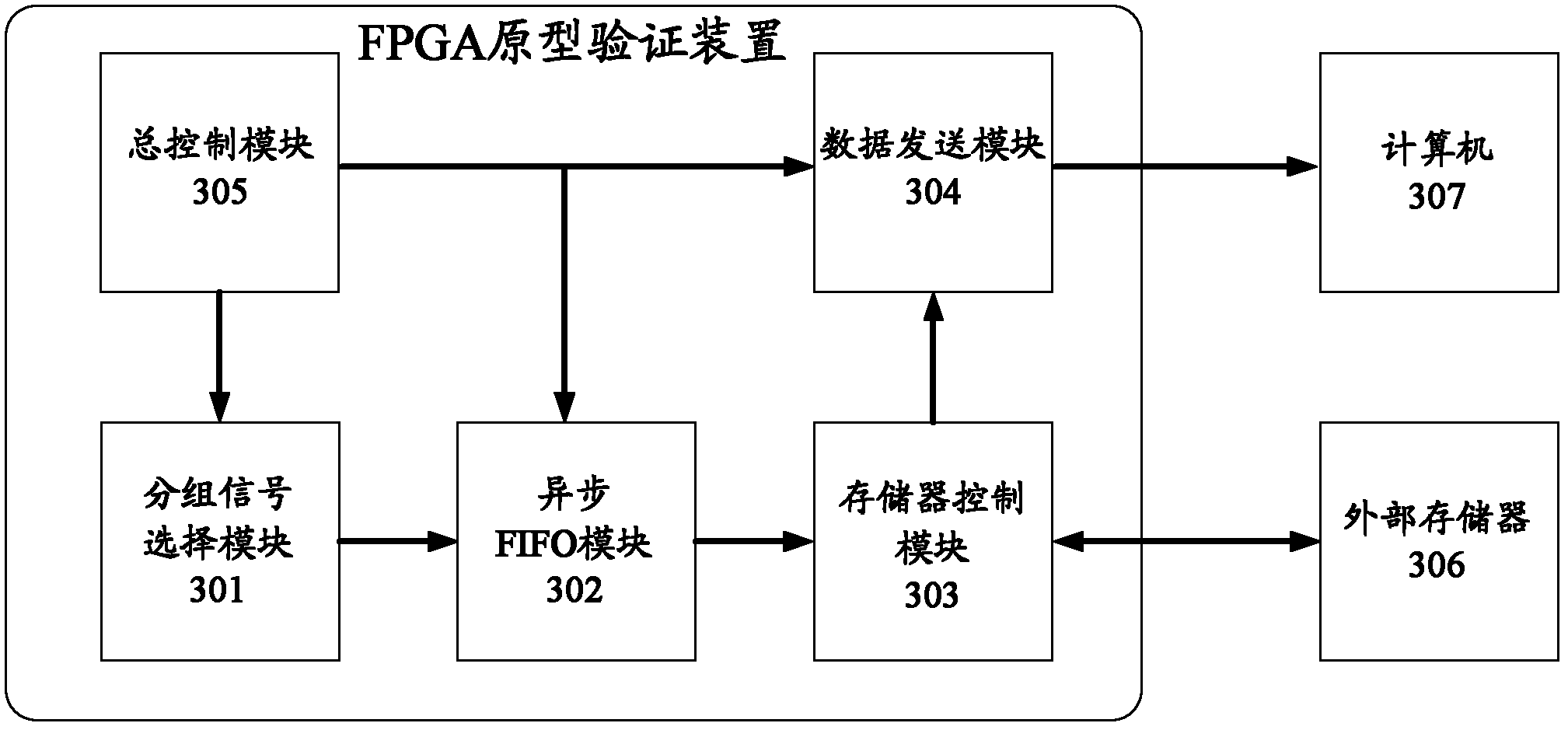

[0063] image 3 It is a structural block diagram of an embodiment of the FPGA prototype verification device of the present invention. see image 3 , the device includes: a packet signal selection module 301 , an asynchronous FIFO module 302 , a memory control module 303 , a data sending module 304 and a general control module 305 .

[0064] The grouping signal selection module 301 has more than one input terminal and one output terminal, and its input terminal is connected to at least one group of grouping signals of the FPGA prototype, and one group of grouping signals is input to one input terminal in parallel, and the grouping signal selection module 301 selects according to the selected The instruction selects one of the grouped signals at its input as a monitored signal and outputs the monitored signal at its output.

[0065] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More