Patents

Literature

78 results about "Multibus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Multibus is a computer bus standard used in industrial systems. It was developed by Intel Corporation and was adopted as the IEEE 796 bus. The Multibus specification was important because it was a robust, well-thought out industry standard with a relatively large form factor, so complex devices could be designed on it. Because it was a well-defined and well-documented industry standard, it allowed a Multibus-compatible industry to grow around it, with many companies making card cages and enclosures for it. Many others made CPU, memory, and other peripheral boards. In 1982 there were over 100 Multibus board and systems manufacturers. This allowed complex systems to be built from commercial off-the-shelf hardware, and also allowed companies to innovate by designing a proprietary Multibus board and then integrating it with other vendors' hardware to create a system. A good example of this was Sun Microsystems with their Sun-1 and Sun-2 workstations. Sun built custom-designed CPU, memory, SCSI, and video display boards, and then added 3Com Ethernet networking boards, Xylogics SMD disk controllers, Ciprico Tapemaster 1/2 inch tape controllers, Sky Floating Point Processor, and Systech 16-port Terminal Interfaces in order to configure the system as a workstation or a file server. Other workstation vendors who used Multibus-based designs included HP/Apollo and Silicon Graphics.

Transmission power control method and transmission power control apparatus in mobile communication system

InactiveUS6963753B1Keep the quality constantConstantPower managementSite diversityControl objectiveMobile station

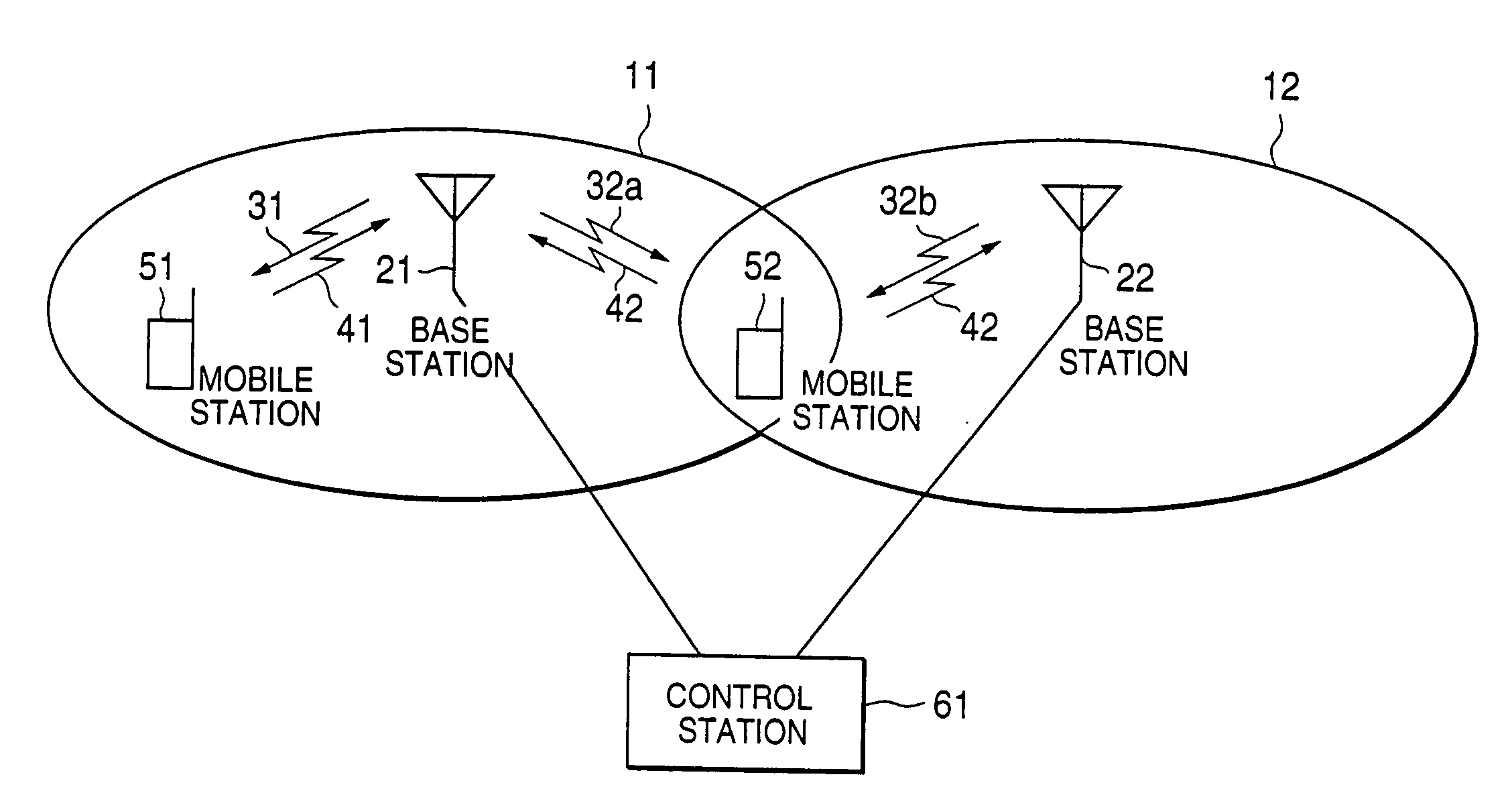

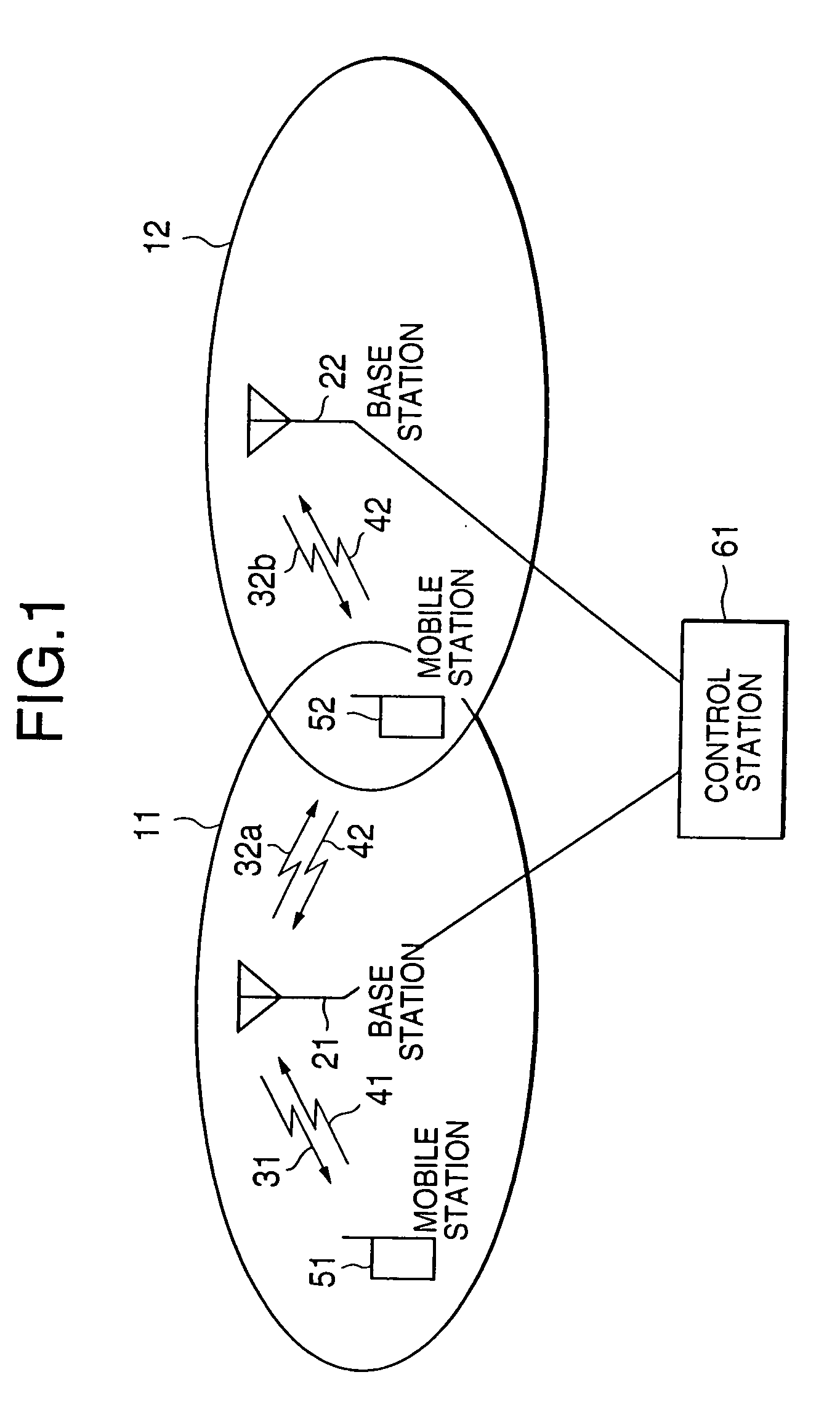

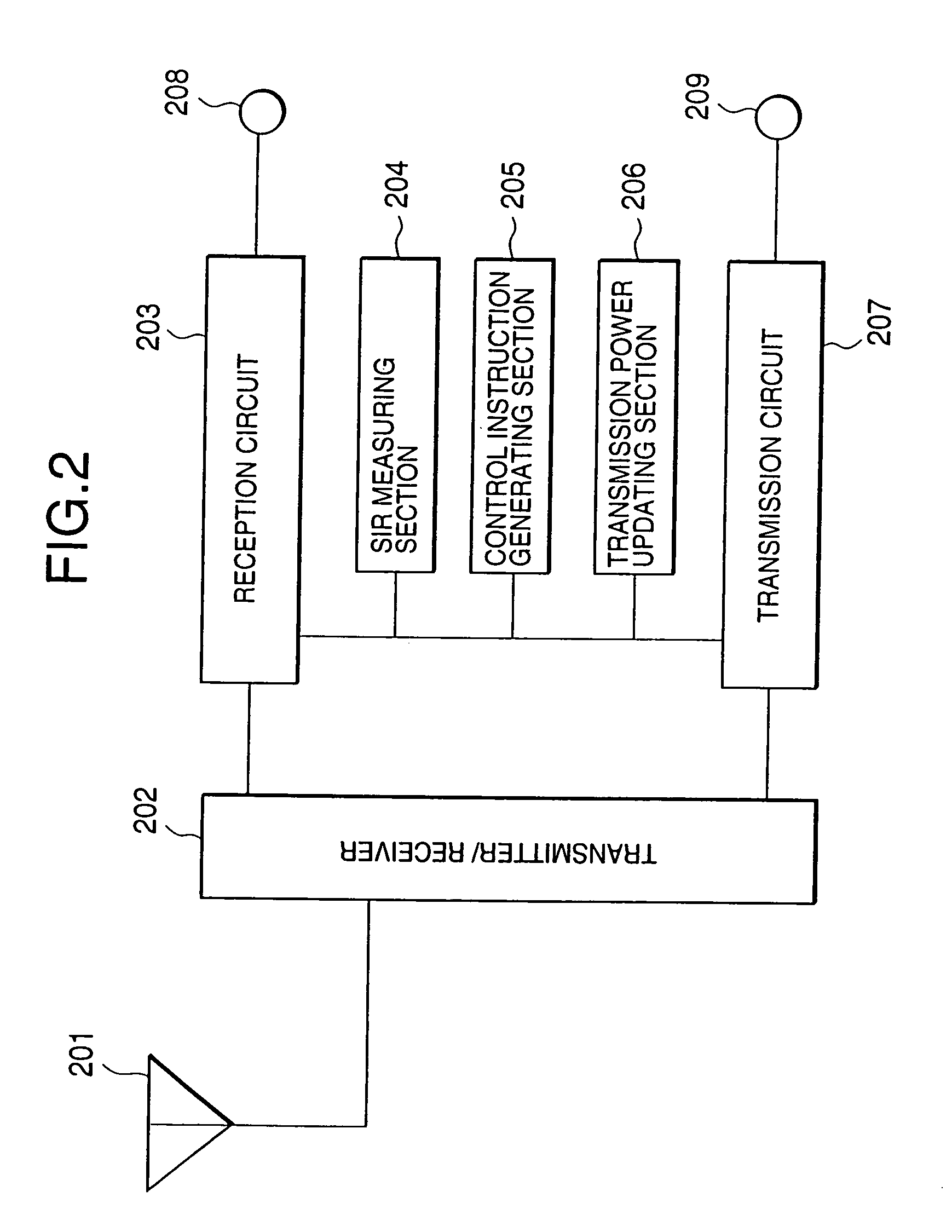

This invention relates to a transmission power control method and transmission power control apparatus in a mobile communication system. The reception quality of a signal (31, 32a, 32b, 41, or 42) transmitted from another mobile station (51 or 52) or base station (21 or 22) is compared with a predetermined control target value such as a signal-to-interference ratio. The comparison result is used for transmission power control on a remote station. If a frame error is detected in a transmitted signal, the control target value is increased by SIRinc. If no frame error is detected, the control target value is decreased by SIRdec. As SIRdec, the product of a target value of a frame error rate and SIRinc is set. With this operation, when a propagation environment such as multibus or moving speed changes, the control target value for transmission power control is changed within a short period of time, and channel quality is maintained constant, thus realizing desired channel quality.

Owner:NEC CORP

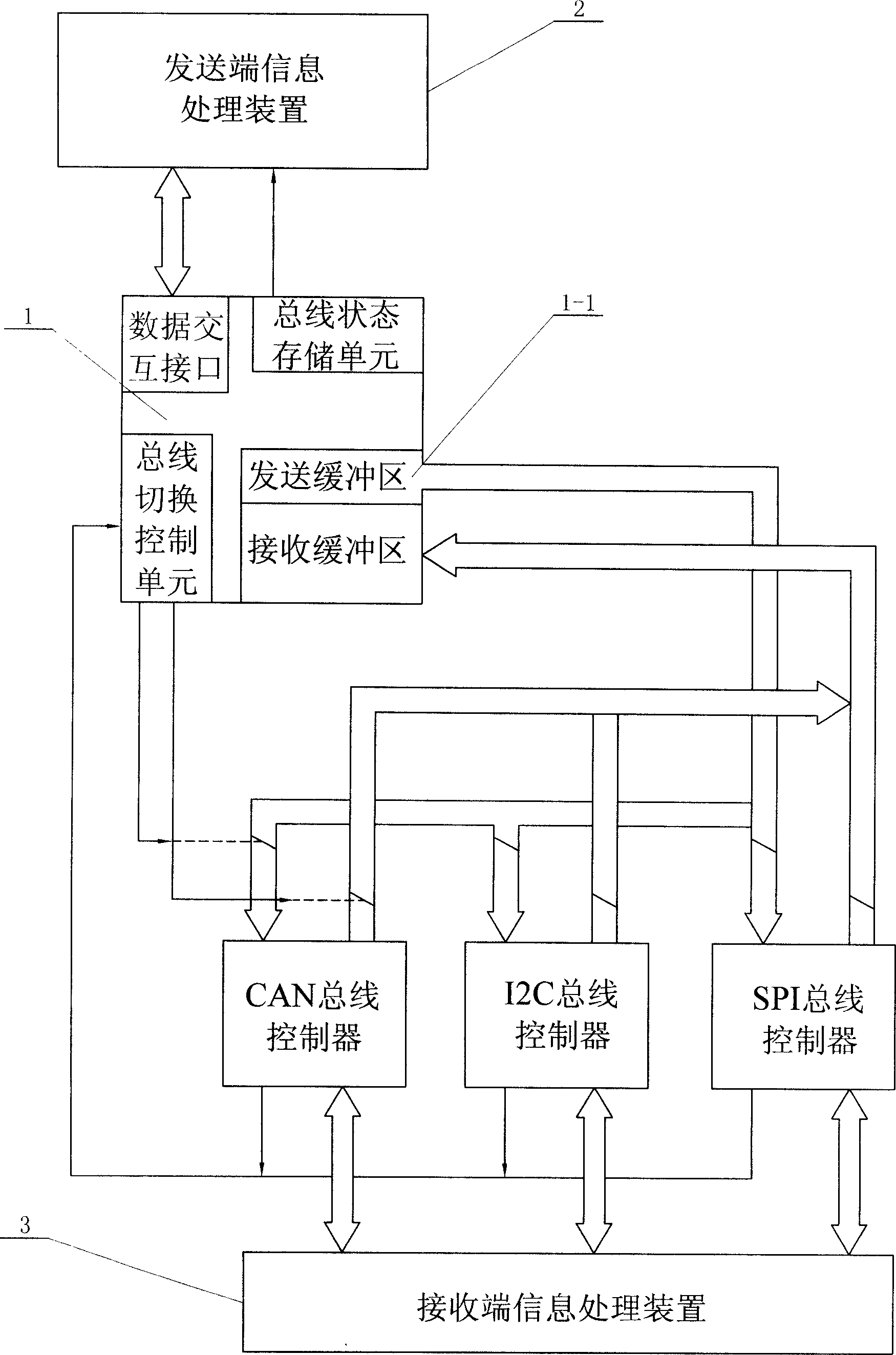

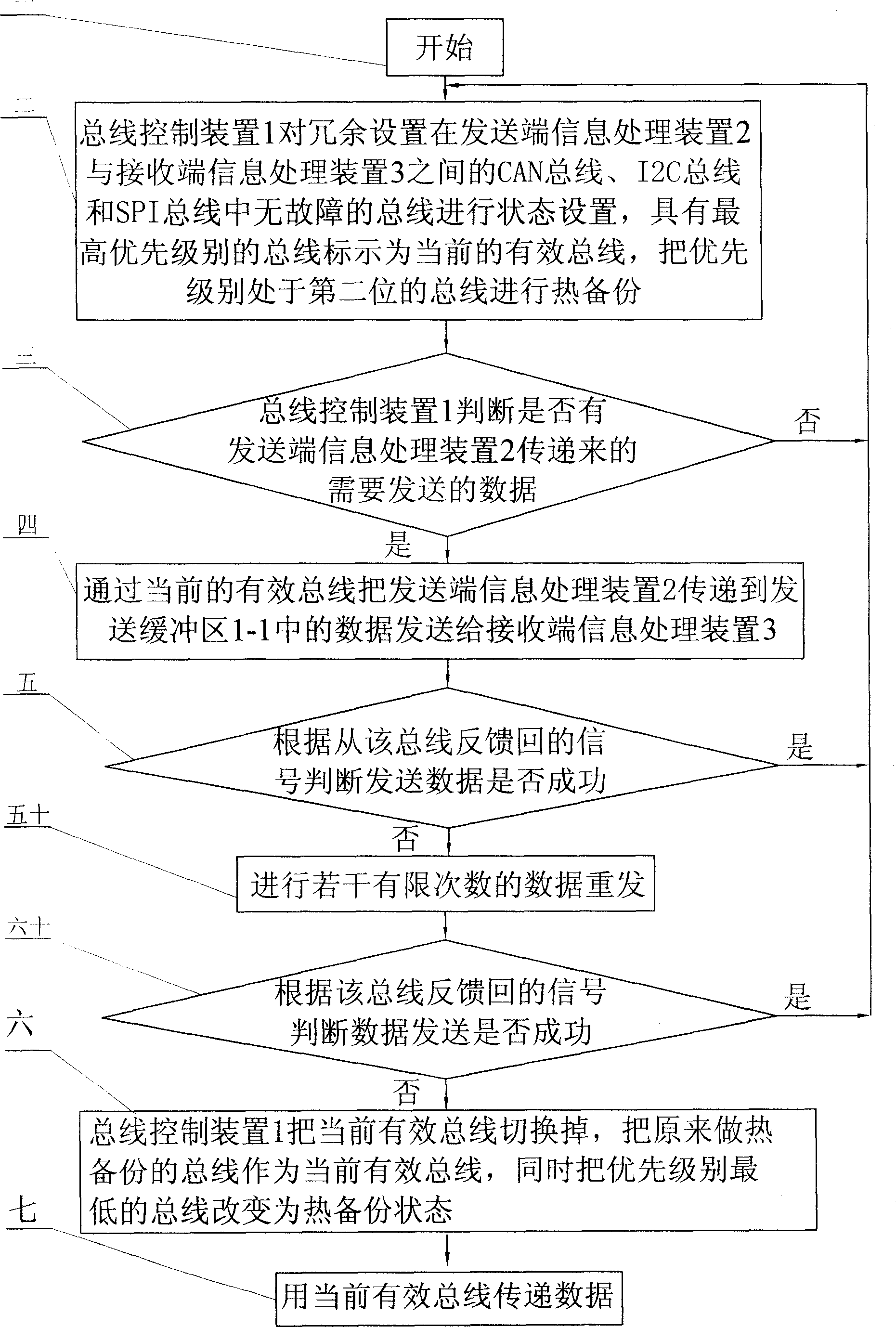

Heterogeneous multi-bus data transmission method between information processing device

InactiveCN1758622AOvercoming the defect of low reliabilityAvoid failureBus networksInformation processingBus mastering

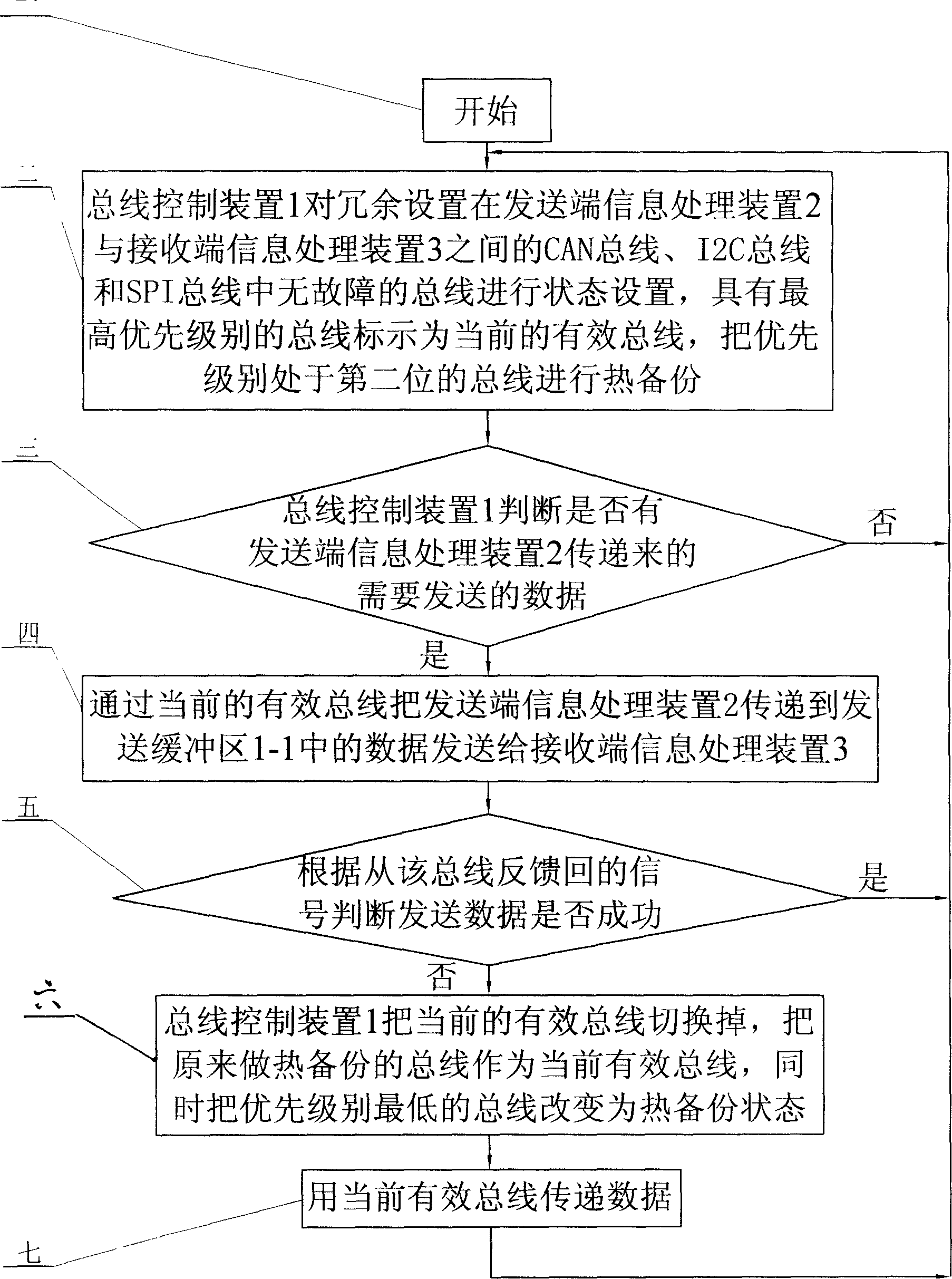

A method for transmitting data with heterostructure multibus between information processing units includes dividing CAN, I 2C and SPI bus to be three different transmission priorities, using only bus with high transmission priority to transmit data in system at the same time and using one bus as hot standby for undertaking data transmission at any time when current effective bus is failure, closing current effective bus and start up bus with next priority to transmit data by utilizing bus control device to judge out fault and to issue switching over command if data transmission fault is occurred on current effective bus.

Owner:HARBIN INST OF TECH

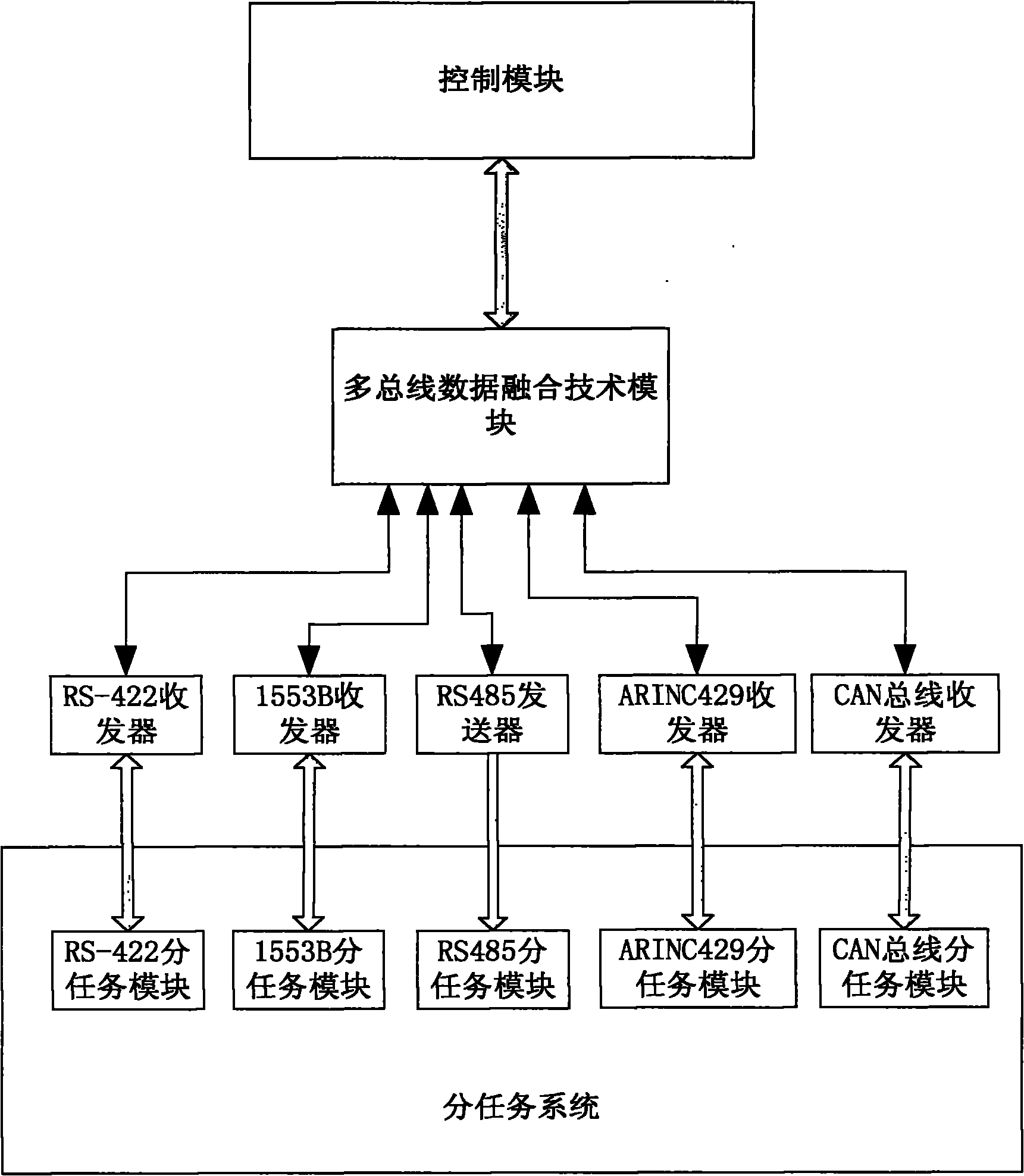

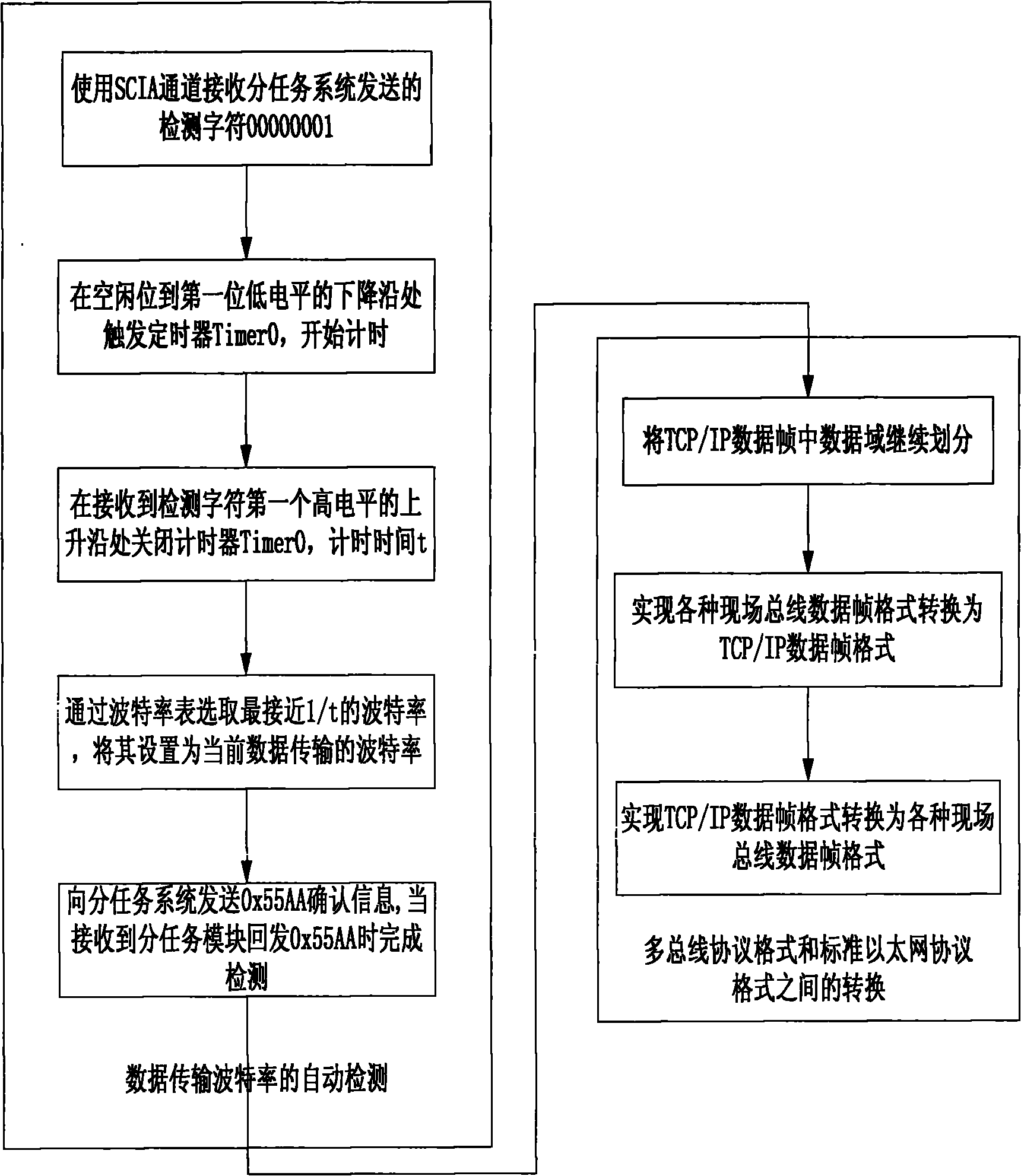

Self-adaptive multibus fusion method

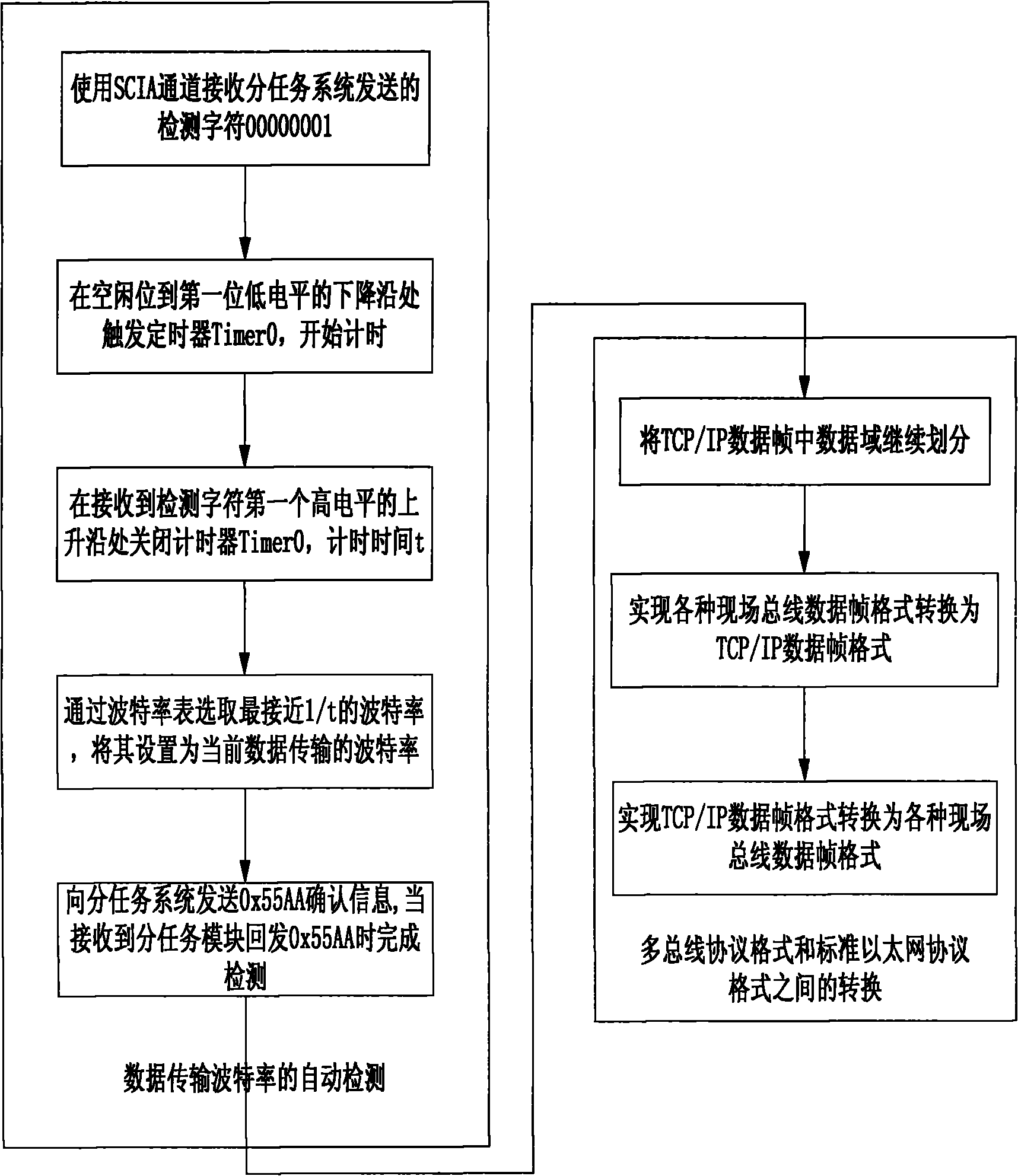

The invention discloses a self-adaptive multibus fusion method which mainly solves the problem that the traditional multibus fusion requires developing special gateway or OPC (OLE (Object Linking and Embedding) for Process Control) server. The method comprises the following steps of: controlling the on and off of a timer 0 according to the level fluctuation of a detection character 00000001 received by an SCIA (Smart Card Industry Association) channel to obtain count time, and realizing the automatic detection of data transmission baud rate; dividing the data domain of a TCP / IP (Transmission Control Protocol / Internet Protocol) data frame into various bus subdata domains, extracting the data bit of each bus through packet disassembly for different bus data frames, and adding the data bit to the subdata domain of the corresponding TCP / IP data frame to realize the conversion from different bus data frame formats into the TCP / IP data frame format; and extracting the data of each subdata domain through packet disassembly for the TCP / IP data frame, and adding the data to the corresponding bus data frame format through packet assembly to realize the conversion from TCP / IP data frame format into the different bus data frame formats. The invention can realize multibus fusion under the condition of not developing special gateway or OPC server, and can be used for realizing the data transmission of various field buses.

Owner:XIDIAN UNIV

Bus control device for field-programmable gate array (FPGA) prototype verification system

ActiveCN102306131AConvenient verificationLow costElectric digital data processingData streamMode control

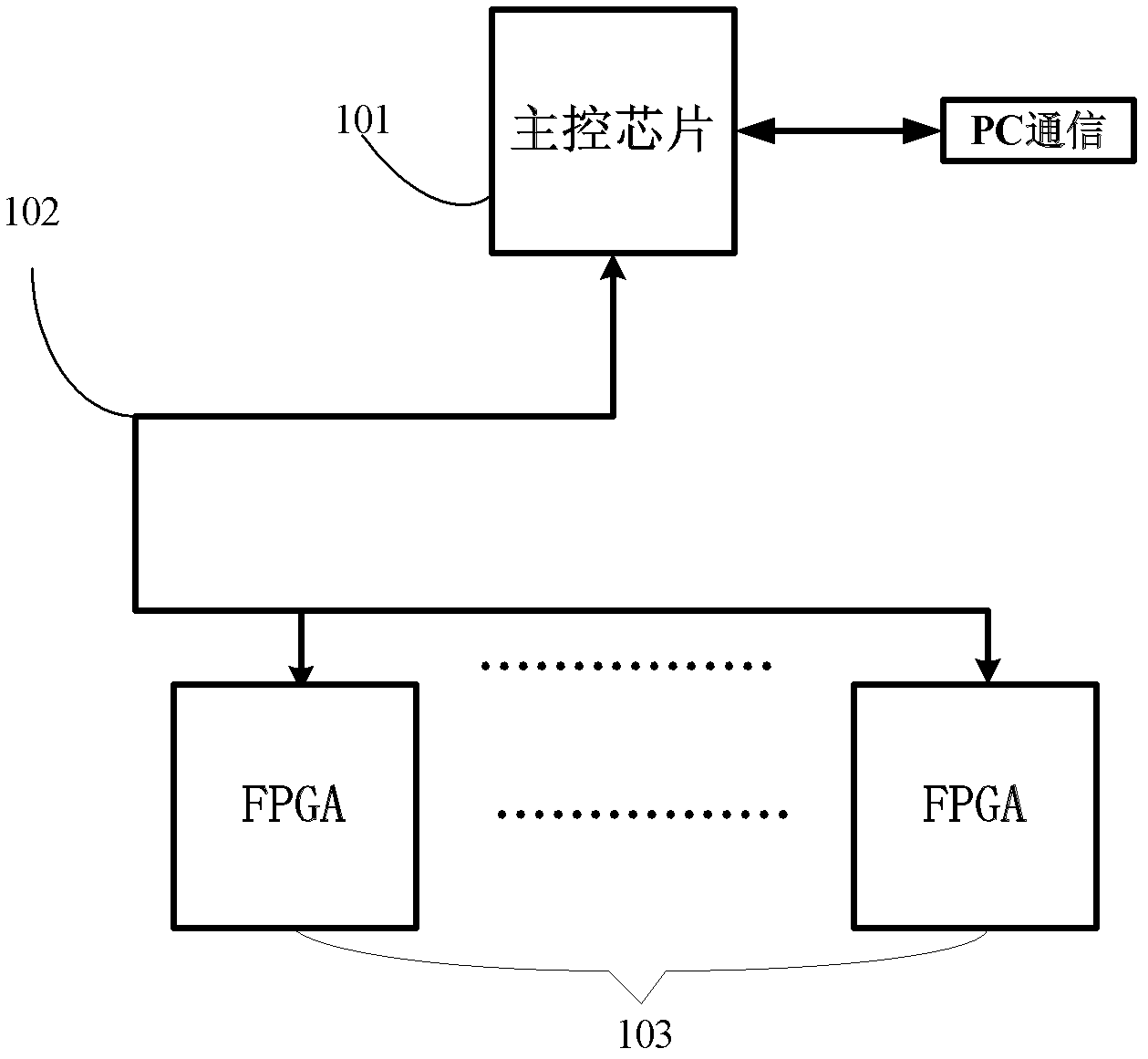

The invention provides a bus control device for a field-programmable gate array (FPGA) prototype verification system, and relates to the field of FPGA prototype verification. The device comprises a master control chip, a HyperBus and a plurality of slave FPGA chips, wherein the master control chip is connected with the plurality of slave FPGA chips through the HyperBus; the HyperBus comprises a mode control line; the master control chip comprises a master mode control module, a master data transceiving module and a master data stream monitoring module; and each slave FPGA chip comprises a slave mode control module and a slave data transceiving module. In the device, the master control chip is connected with the HyperBus (HyperSilicon Bus), adjusts the state of the mode control line according to a mode control instruction, or sets the working mode of a system bus by manually setting the state of the mode control line in an initial state, so that a multibus working mode is operated in the same system, great convenience is brought to the FPGA prototype verification, cost is reduced, and the HyperBus provides a good system communication and control path particularly for HyperBus-based secondary development.

Owner:无锡亚科鸿禹电子有限公司

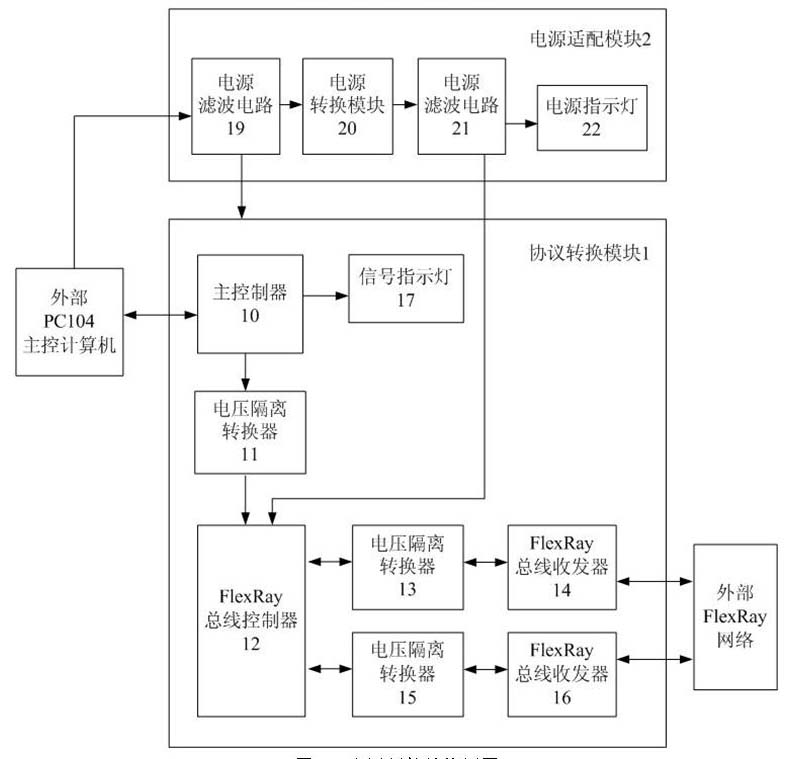

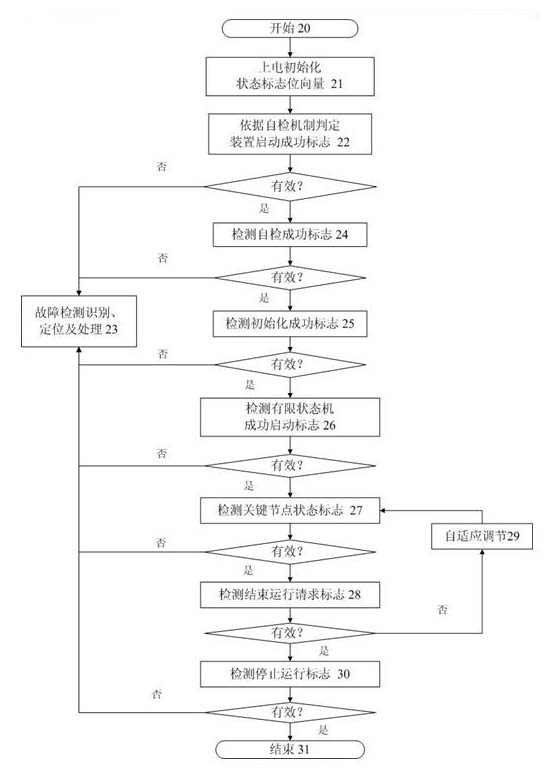

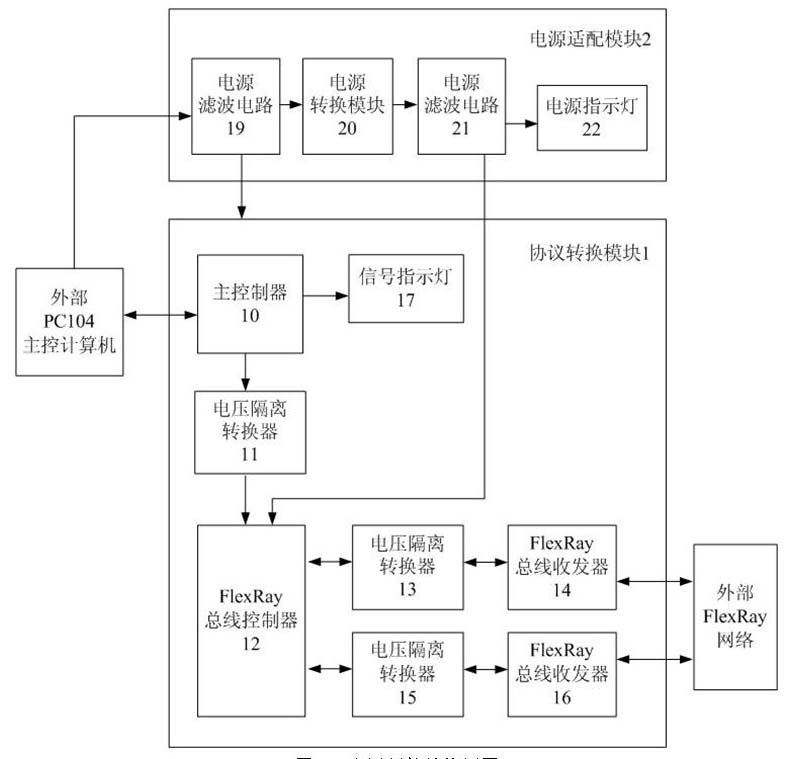

Protocol converter for FlexRay bus and PC104 bus

InactiveCN101969393AOptimize redundant communication logicImprove interchangeabilityBus networksControl systemFinite-state machine

The invention provides a protocol converter for a FlexRay bus and a PC104 bus. The converter comprises base hardware and support software, wherein the base hardware comprises a power supply adapting module and a protocol conversion module, and the support software is a finite state machine implemented based on state query and response mechanism. The protocol converter can efficiently and reliably realize bidirectional communication between nodes of the FlexRay bus and the PC104 bus in real time, meanwhile, positions, identifies, analyzes, tracks and detects the bus communication fault, solves the problems of signal interfaces and data exchange between the FlexRay bus and the PC104 bus, and has the advantages of low network time delay, reasonable dynamic distribution of data frames, accurate and quick fault positioning and convenience for quick and effective integration of a multi-bus control system.

Owner:MIANYANG WEIBO ELECTRONICS

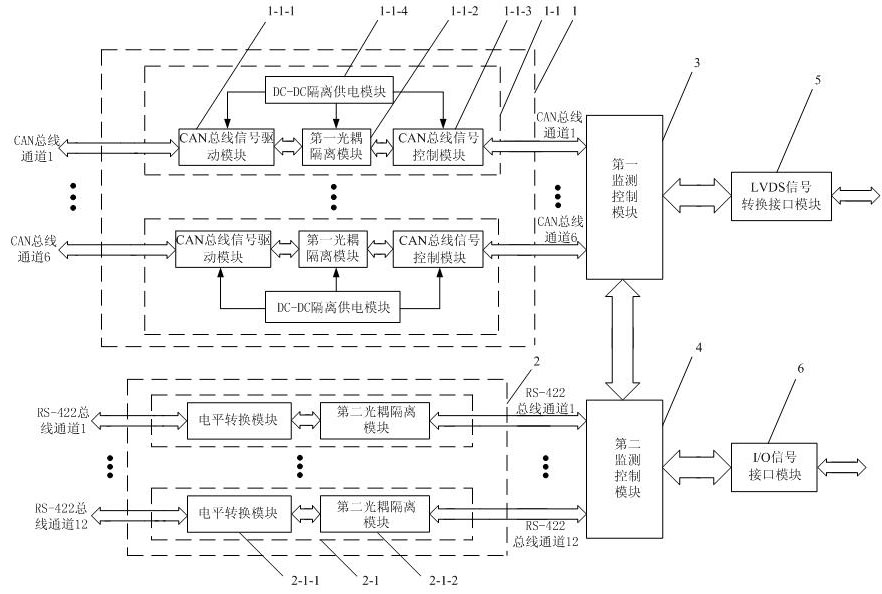

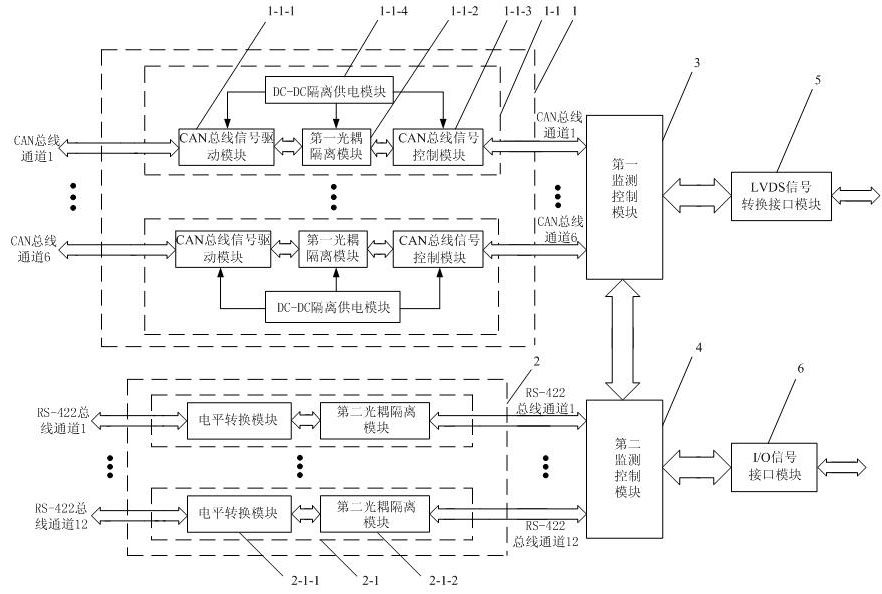

Moonlet multi-bus multi-passage communication monitoring device and monitoring method thereof

The invention provides a moonlet multi-bus multi-passage communication monitoring device and a monitoring method thereof, which relate to a communication monitoring device and a monitoring method thereof. The invention is provided by aiming at solving the problems that the monitoring device can only monitor the bus modes of the same type, in addition, the monitored passages are few. The data signal output end and the data signal input end of an interface module of each path of CAN bus respectively correspond to the signal input end and the signal output end of one path of CAN bus of a first monitoring control module, the interface module of each path of CAN bus respectively receives a path of CAN bus signals from an external bus, the data signal output end and the data signal input end of an interface module of each path of RS-422 bus respectively correspond to the signal input end and the signal output end of one path of RS-422 bus of a second monitoring control module, and the interface module of each path of RS-422 bus respectively receives one path of RS-422 bus signals. The invention can monitor two kinds of buses, can simultaneously monitor multi-passage data, and can be widely applied to various occasions needing simultaneous monitoring of multi-passage data.

Owner:HARBIN INST OF TECH

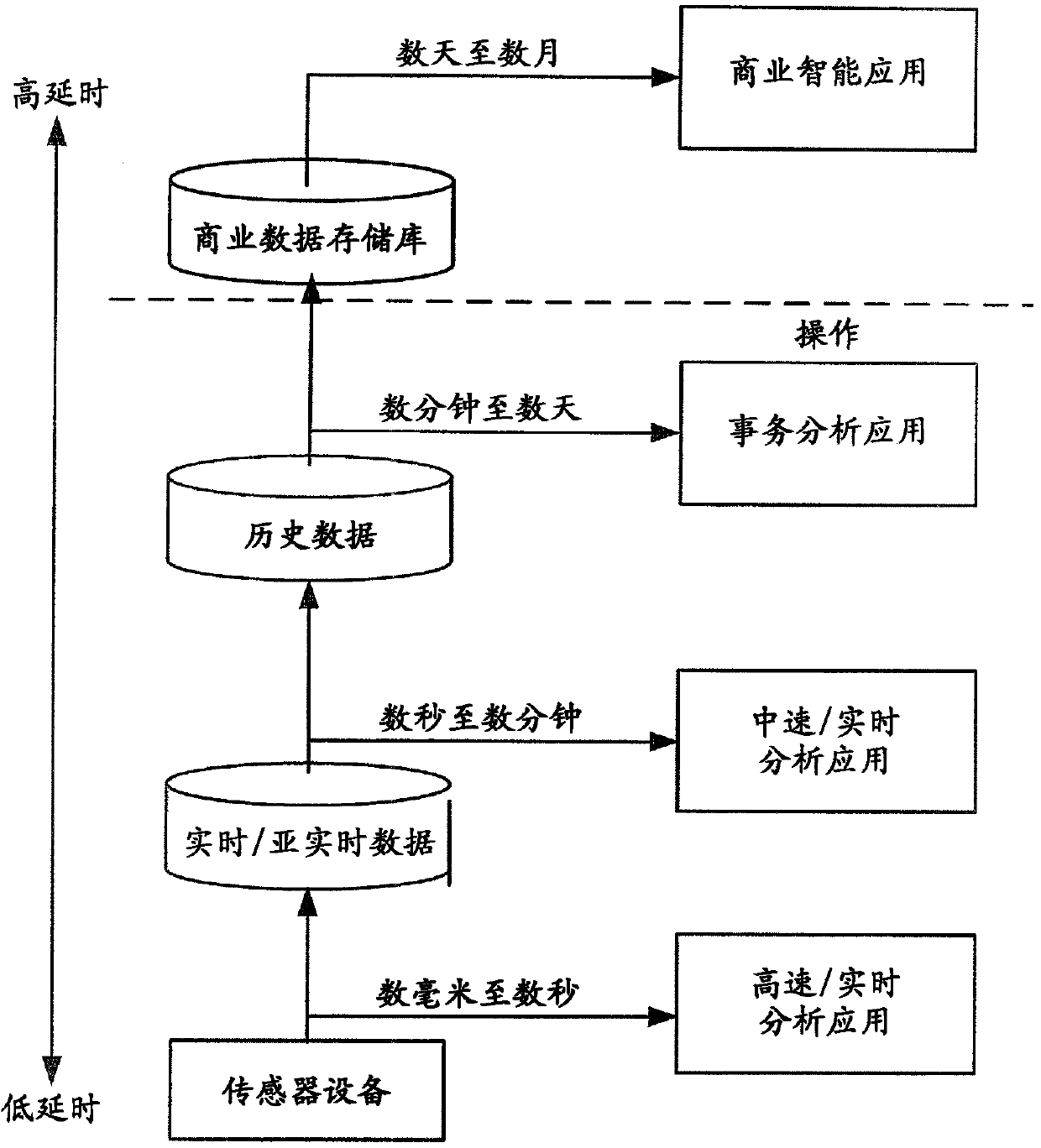

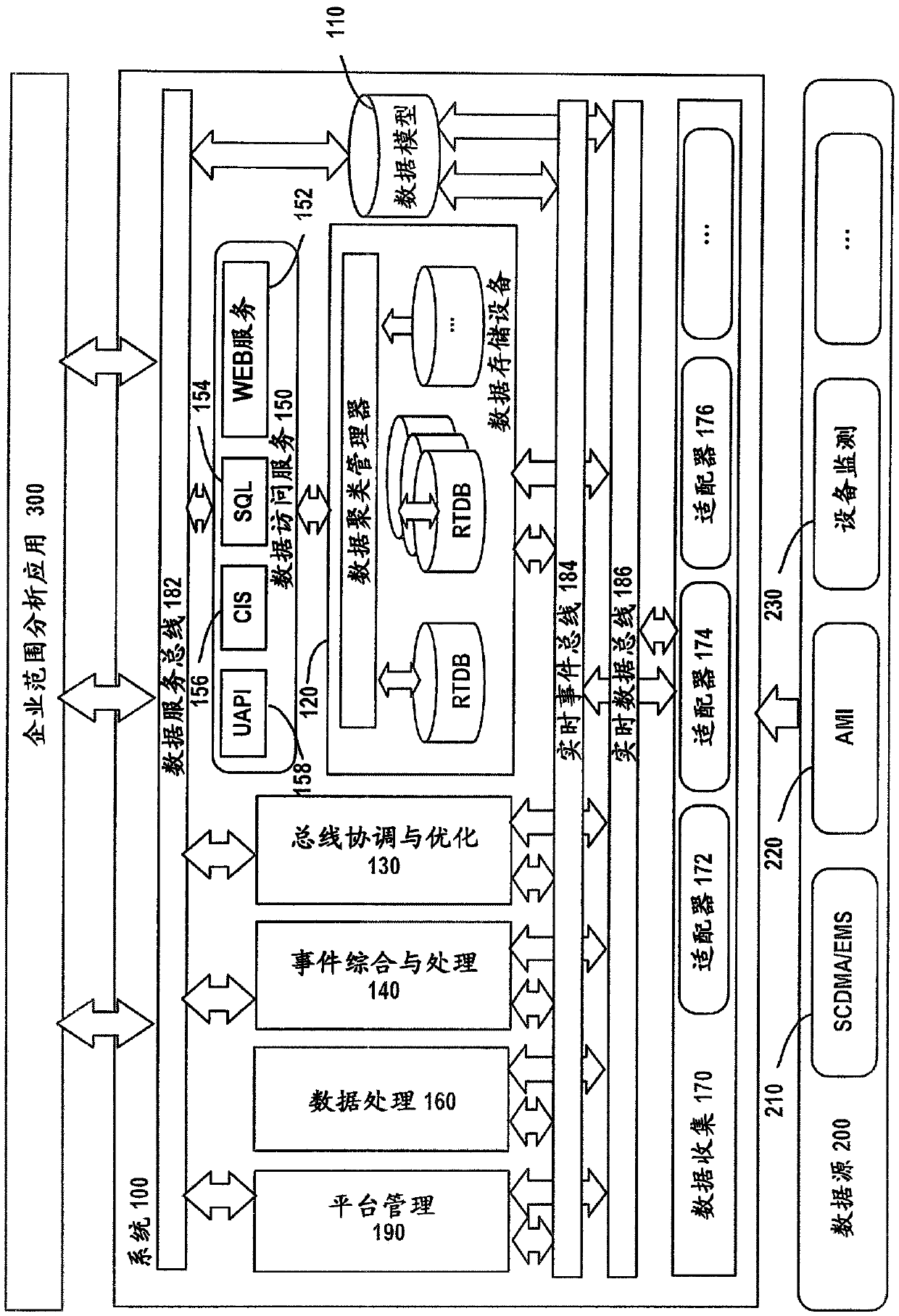

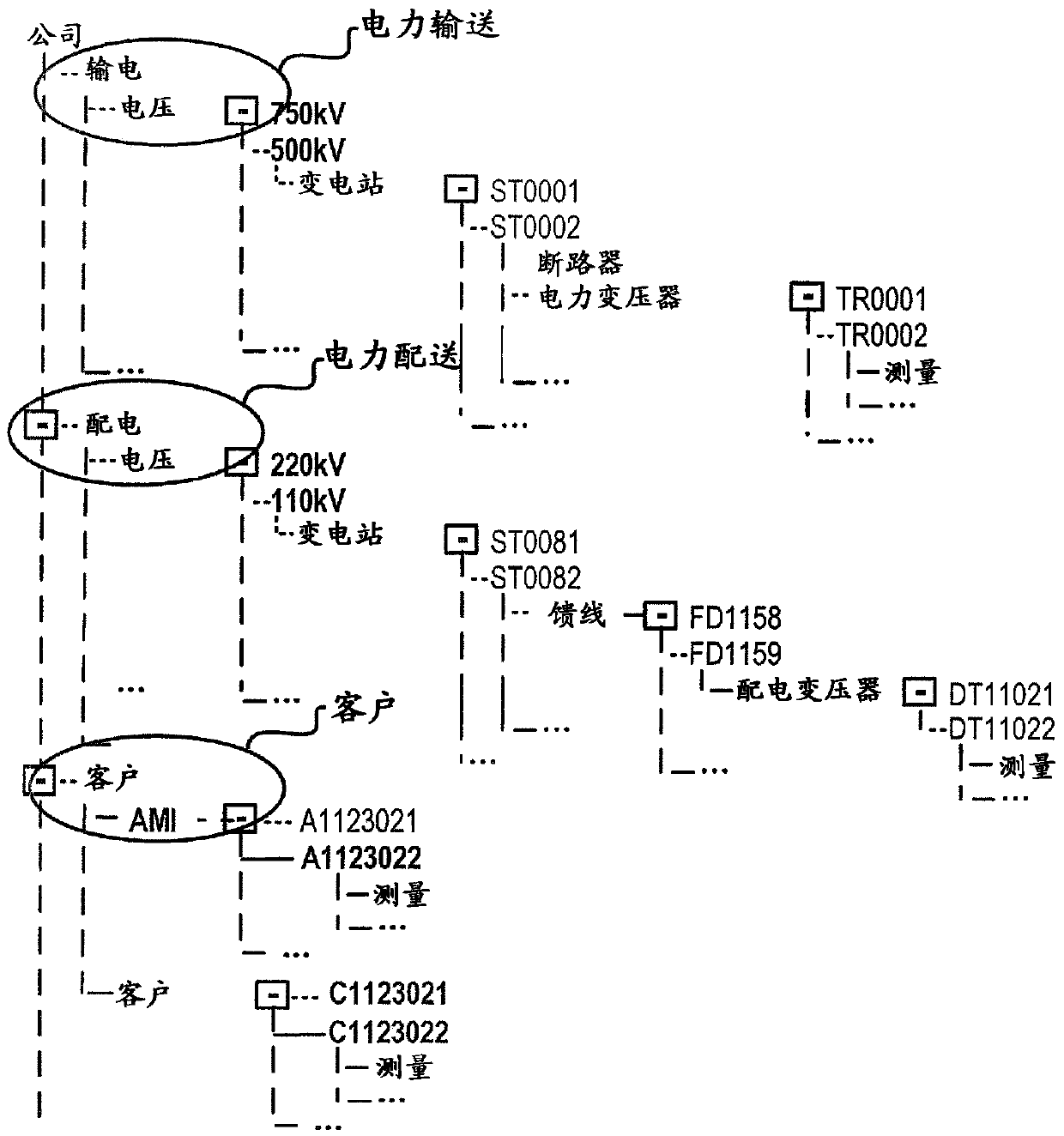

Real-time data management for a power grid

ActiveCN104769582AEfficient managementExpandable and flexibleError detection/correctionDigital data processing detailsClustered dataComplex event processing

The present disclosure relates to real-time data management for a power grid and presents a real-time data management system, a system, method, apparatus and tangible computer readable medium for accessing data in a power grid, a system, method, apparatus and tangible computer readable medium for controlling a transmission delay of real-time data delivered via a real-time bus, and a system, method, apparatus and tangible computer readable medium for delivering real-time data in a power grid. In the real-time data management system of the present disclosure, a unified data model covering various organizations and various data resource is designed and a management scheme for clustered data is used to provide a transparent and high speed data access. Besides, multi-bus collaboration and bus performance optimization approaches are utilized to improve efficiency and performance of the buses. The real-time data management system may also include an event integration and complex event process component to provide a credible prediction on status of the power grid. With embodiments of the present disclosure, it may efficiently manage the high volume of real-time data and events, provide data transmission with a low latency, provide flexible extension of both the number of data clusters and the number of databases to ensure high volume data storage, and achieve a high speed and transparent data access, Additionally, it also enable the rapid design and development of analytical applications, and support the near real-time enterprise decision-making business.

Owner:ACCENTURE GLOBAL SERVICES LTD

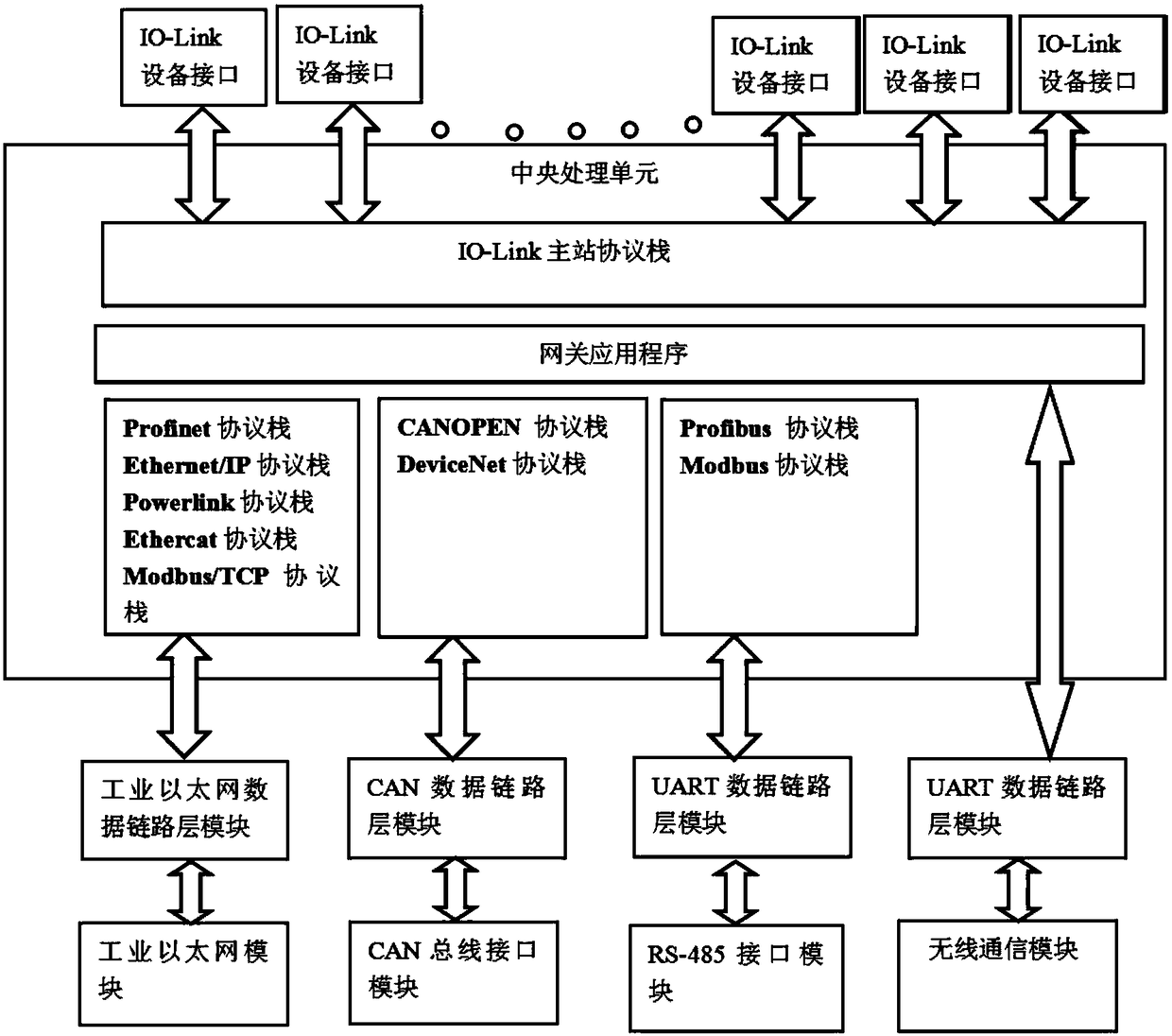

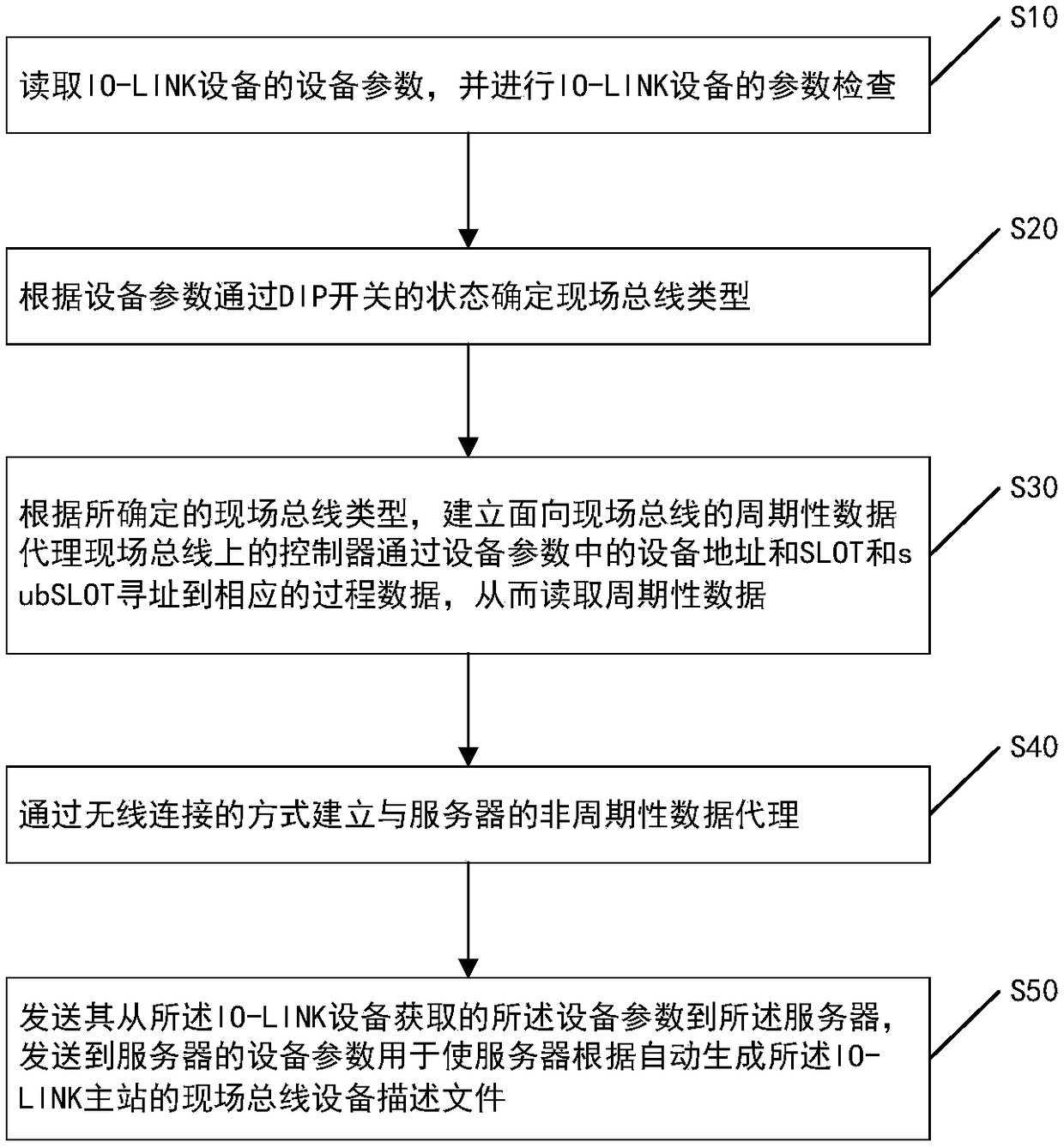

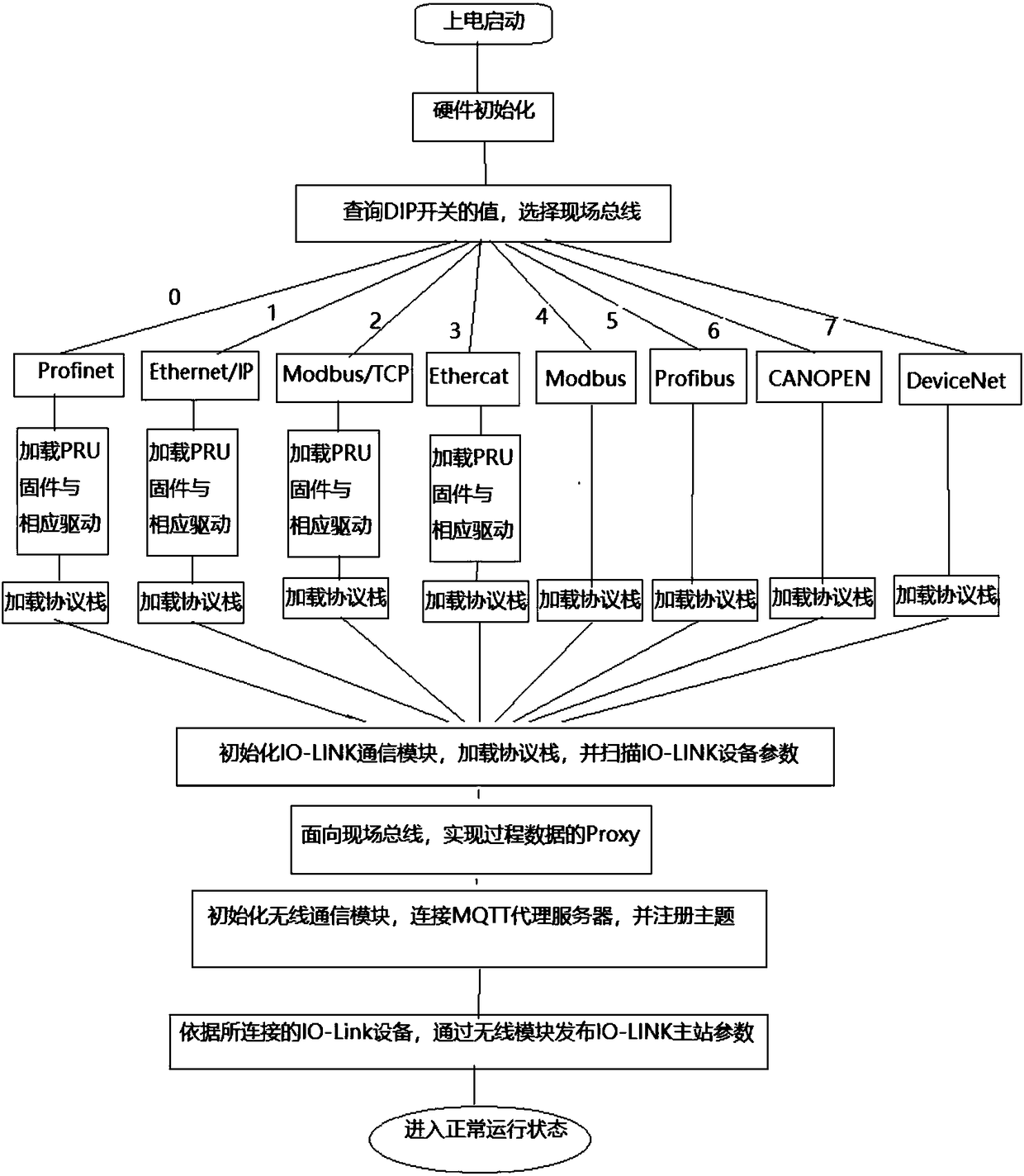

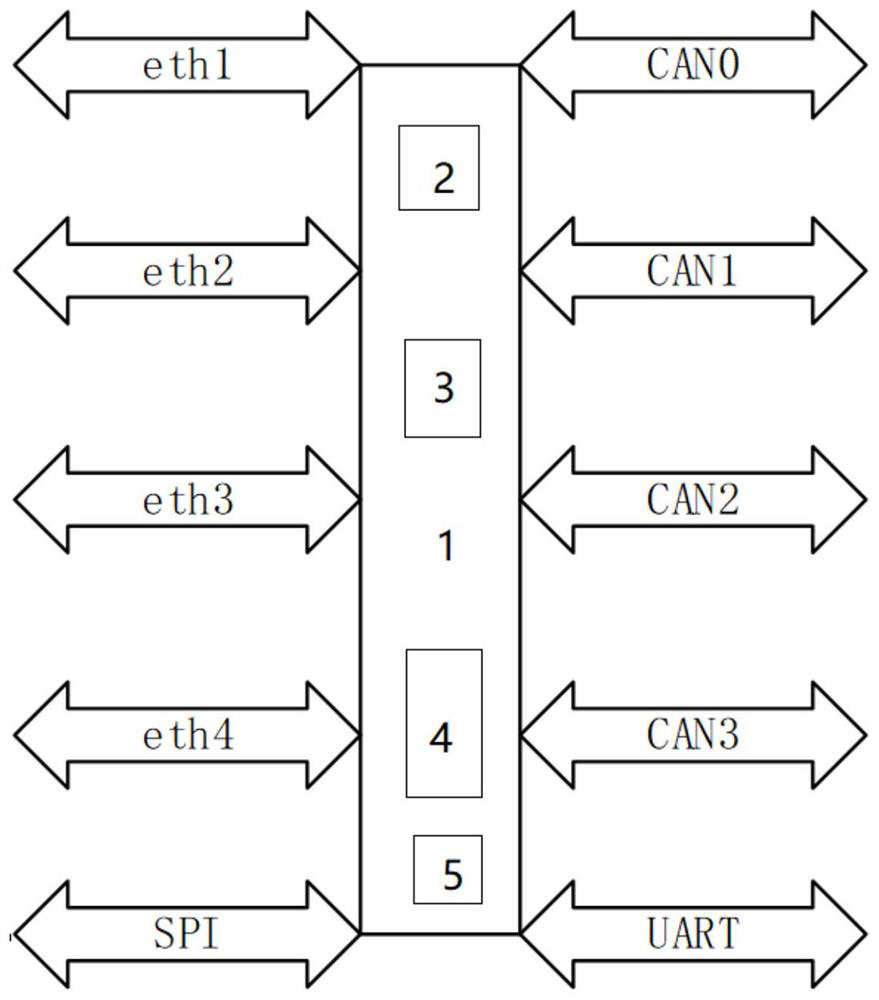

Multibus IO-LINK master station supporting device and method

PendingCN108449250AEasy to operateBus networksTotal factory controlIndustrial EthernetHardware architecture

The embodiment of the invention discloses a multibus IO-LINK master station supporting device. The device comprises an industrial Ethernet module, a CAN bus interface module, an RS485 communication module, an IO-LINK master station physical layer communication module, a central processing module and a wireless communication module. The industrial Ethernet module is connected with the central processing module in an MII interface mode. The CAN bus interface module is connected with the central processing module through a UART interface. The RS485 communication module is connected with the central processing module through the UART interface. The wireless communication module is connected with the central processing module through the UART interface. Periodic data and aperiodic data are processed separately. Under the condition of not changing existing upper computer control hardware architecture, IO layer devices are smoothly upgraded as IO-LINK devices. Moreover, most advantages of anIO-LINK technology are reserved.

Owner:SANMING UNIV

Method for designing multibus test platform based on VPX

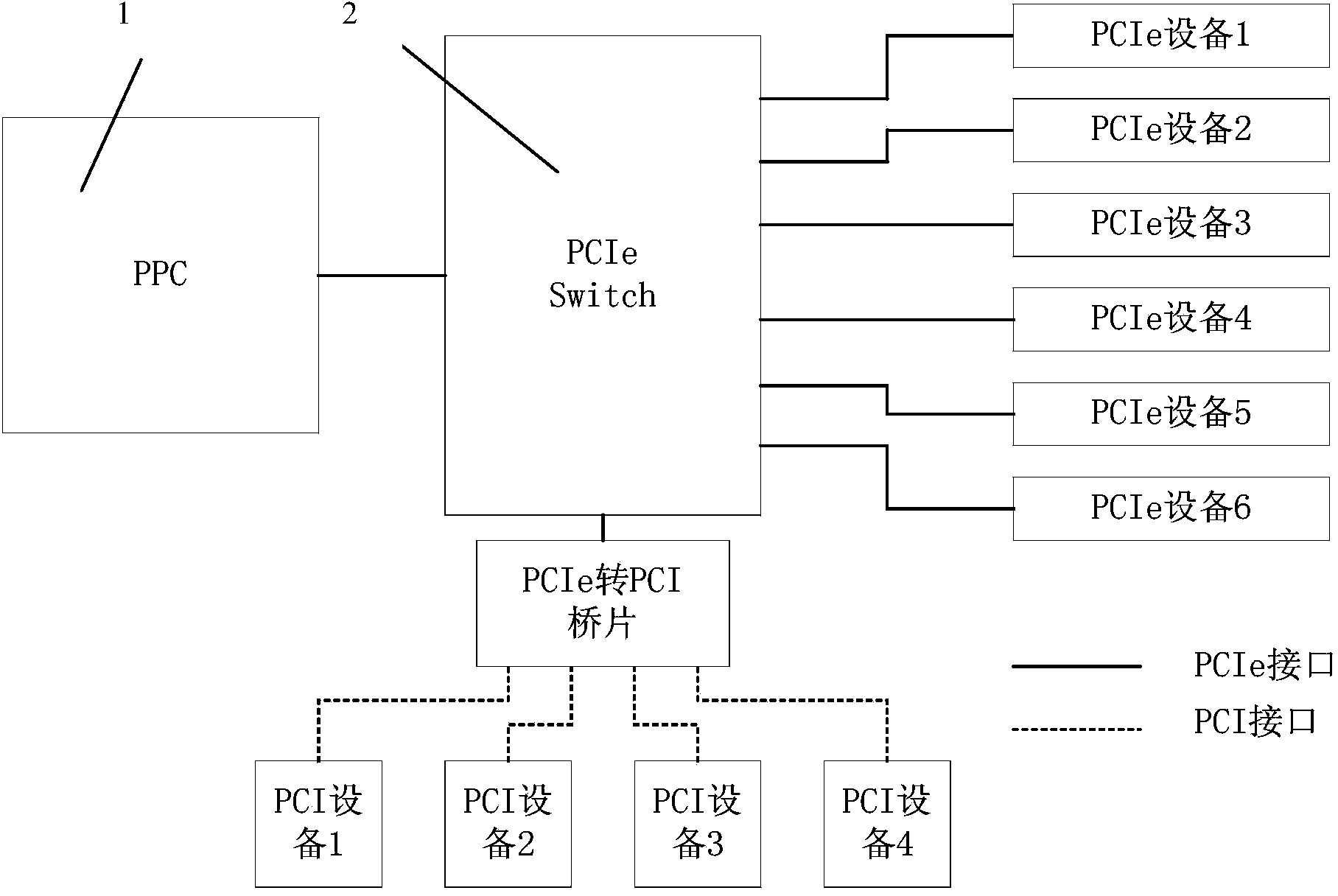

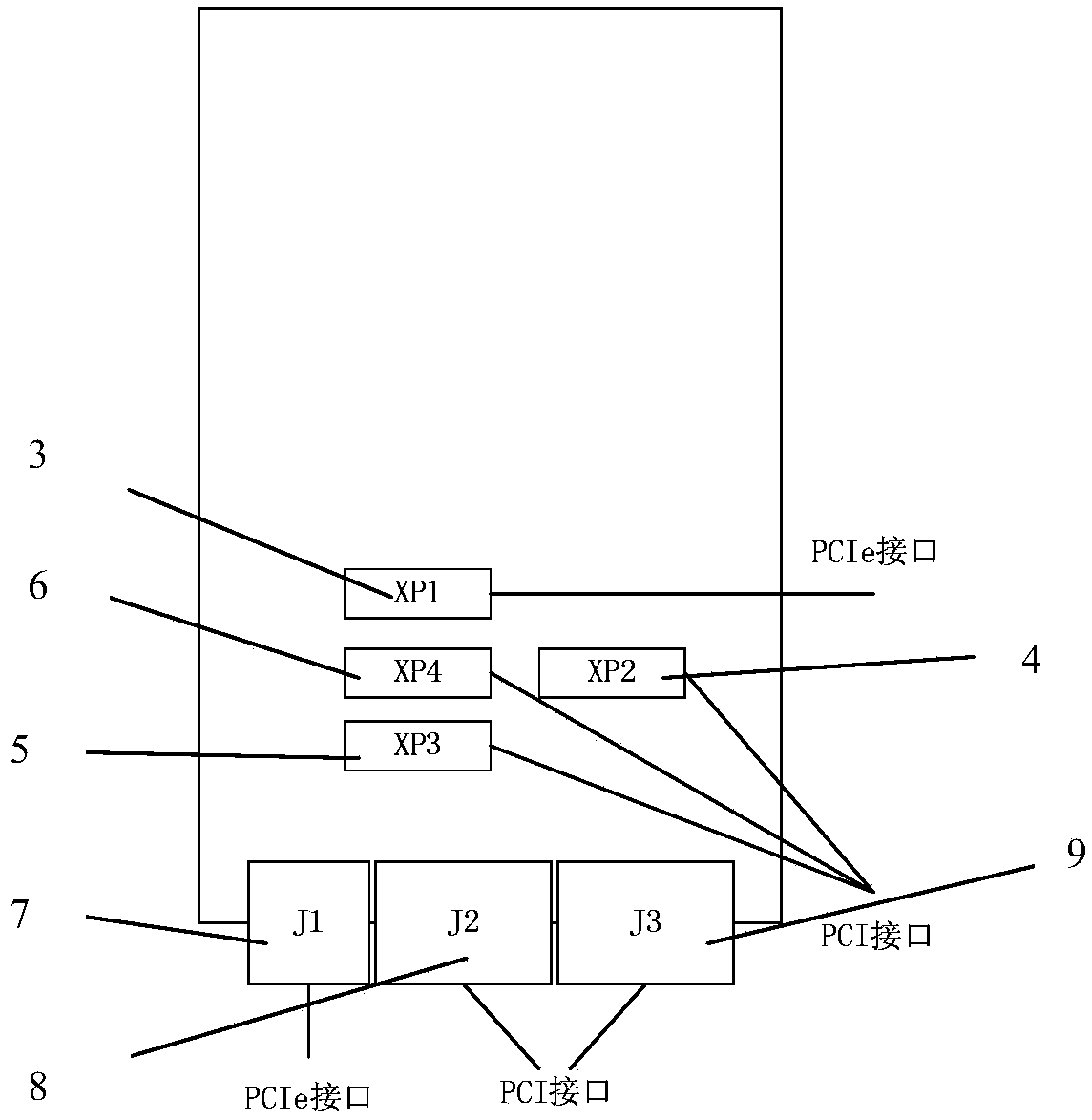

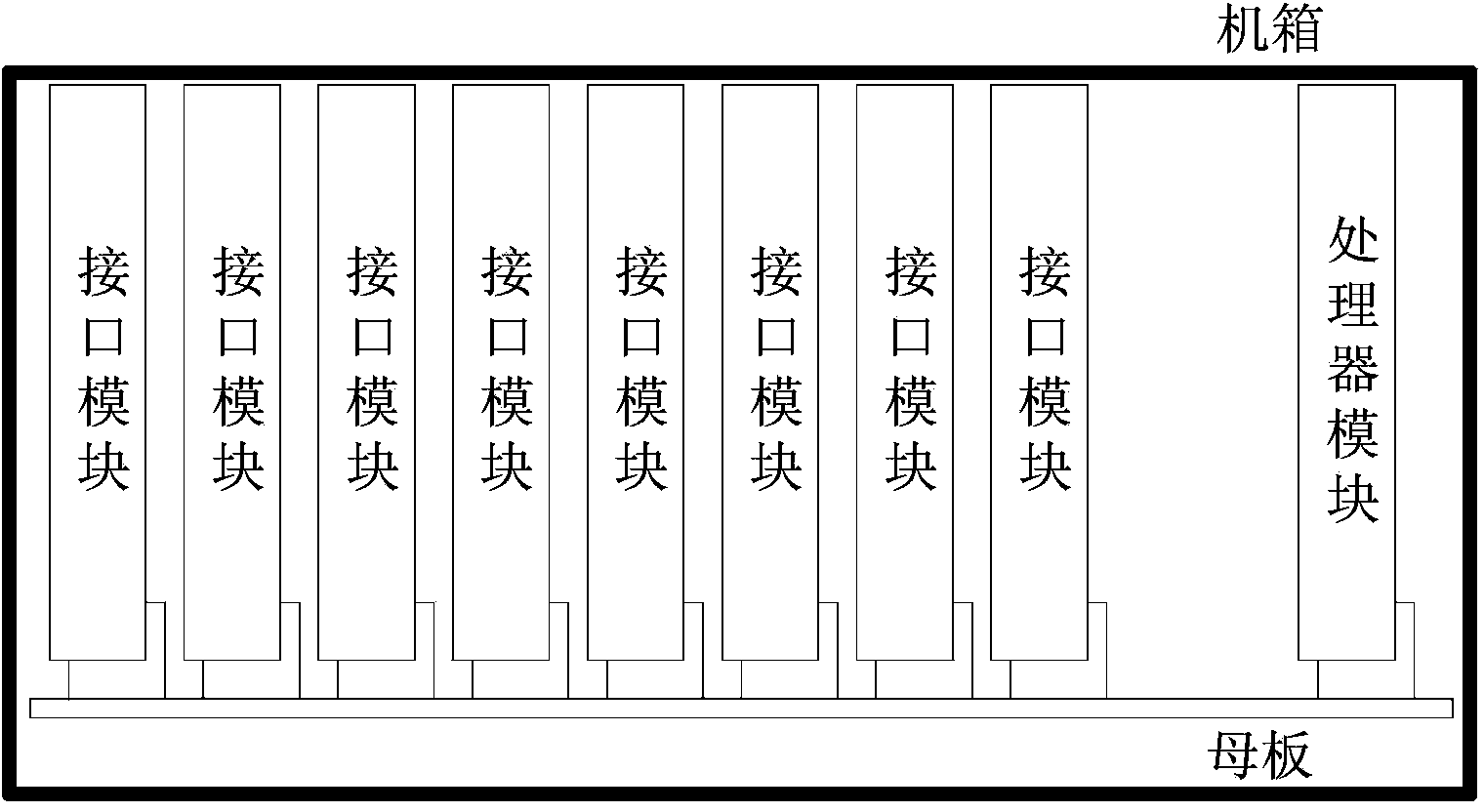

The invention relates to a multibus test platform system based on a VPX. The multibus test platform system based on the VPX comprises a mother board, a processor connected with the mother board and an adapter plate set. The mother board comprises a PCIE interface connected with the processor. The multibus test platform system is a one-to-many standard and integrated multibus test platform system.

Owner:AVIC NO 631 RES INST

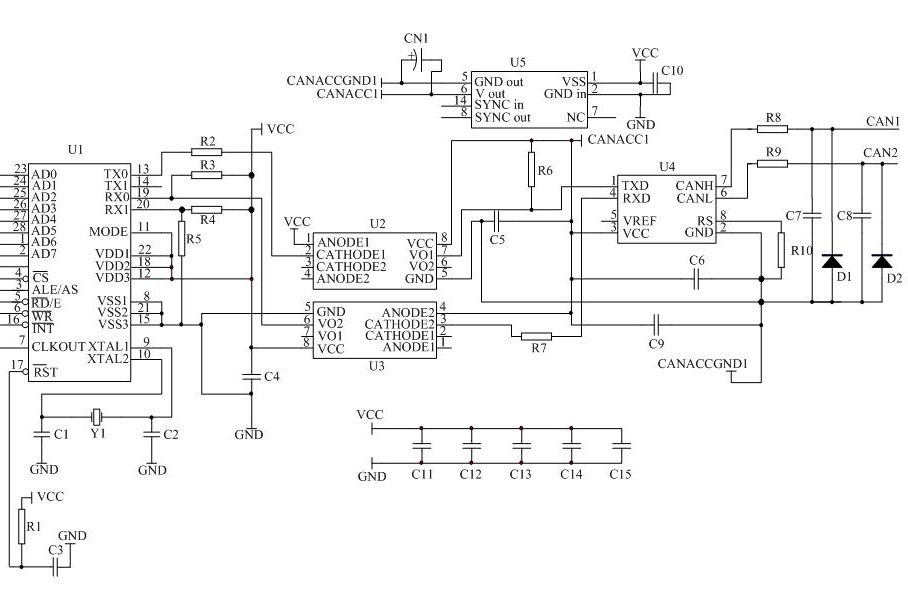

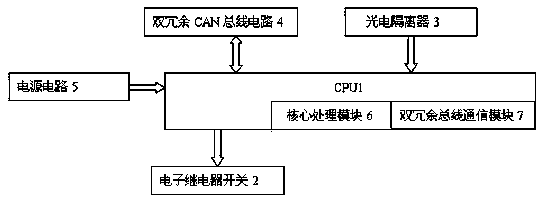

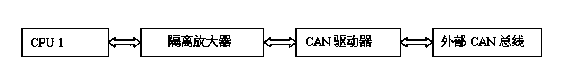

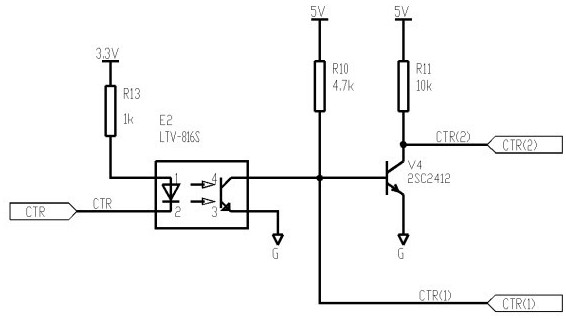

Gateway controller with multi-channel CAN bus communication function

InactiveCN104270306ALow reliabilityReduce functionNetwork connectionsBus networksIsolatorData acquisition

The invention discloses a gateway controller with a multi-channel CAN bus communication function. The gateway controller comprises a CPU (1), a power circuit (5), a dual-redundancy CAN bus circuit (4), a core processing module (6), a dual-redundancy bus communication module (7), an electronic relay switch (2) and an optoelectronic isolator (3). According to the gateway controller, data exchange with multi-CAN subnet control equipment is realized through the dual-redundancy CAN bus circuit (4); switching value signals in various forms are collected through the optoelectronic isolator (3), and the core processing module (6) conducts data collection, logical operation and diagnostic analysis to obtain control requirements; control over controlled equipment is realized through the electronic relay switch (2). The controller is key equipment for multi-CAN-bus subnet system networking for outdoor equipment such as automobiles, special vehicles and engineering machines, each group of CAN network uses two CAN buses to realize dual-redundancy communication, and the problems that a general gateway controller is poor in reliability and single in function are solved.

Owner:BEIJING MECHANICAL EQUIP INST

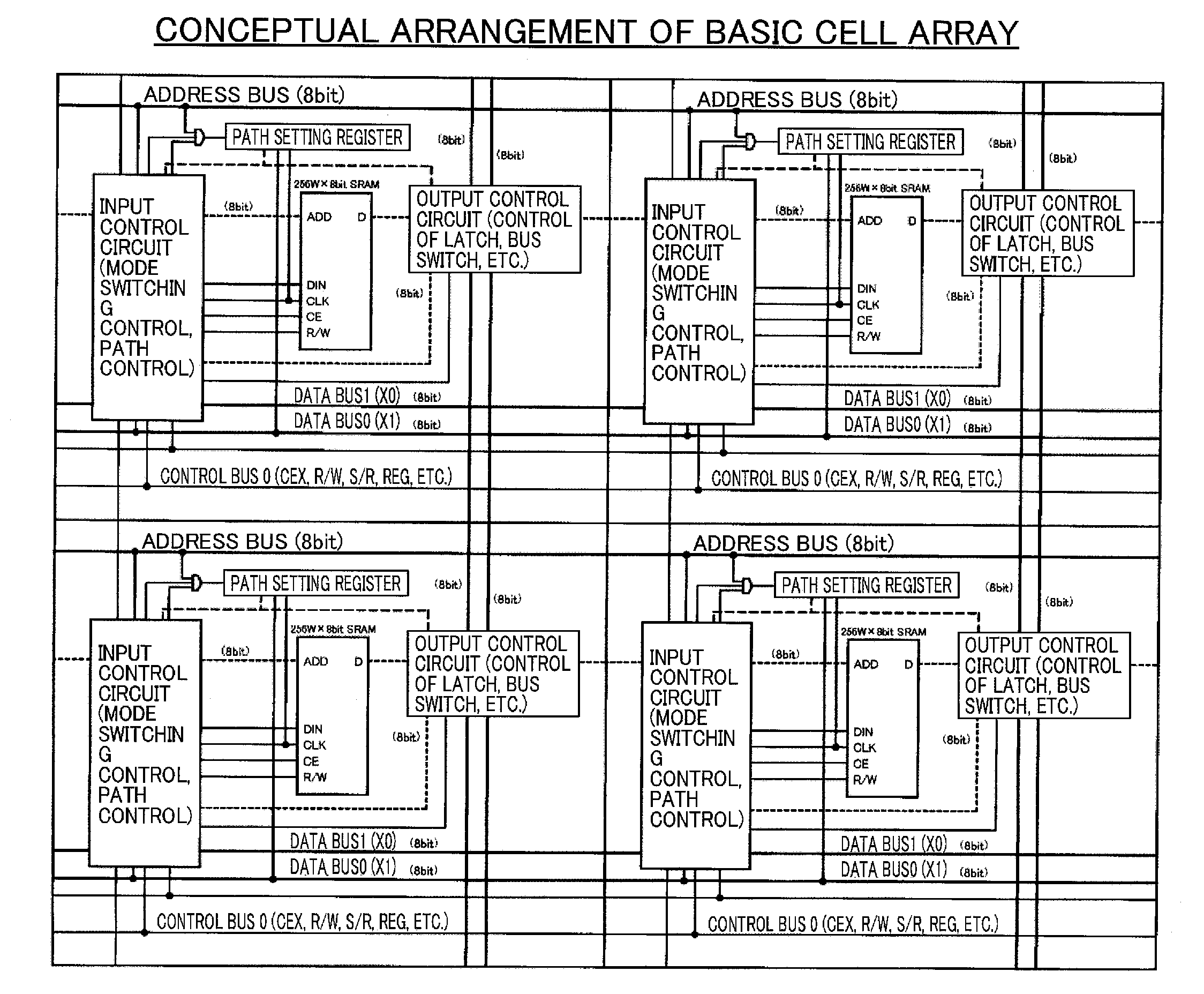

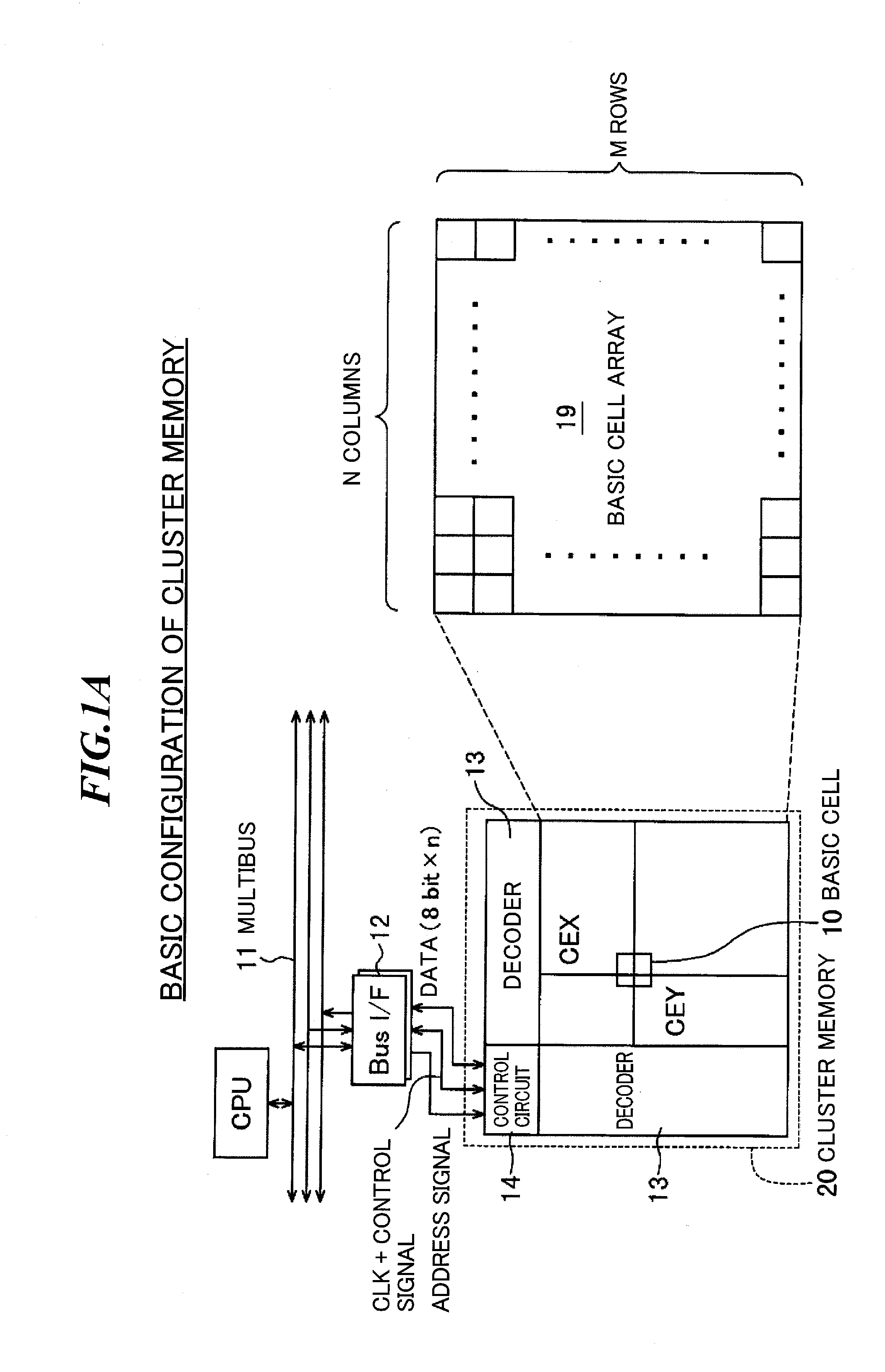

Memory/logic conjugate system

InactiveUS20110255323A1Reduce system costImprove performanceDigital storageElectric digital data processingElectricityMemory chip

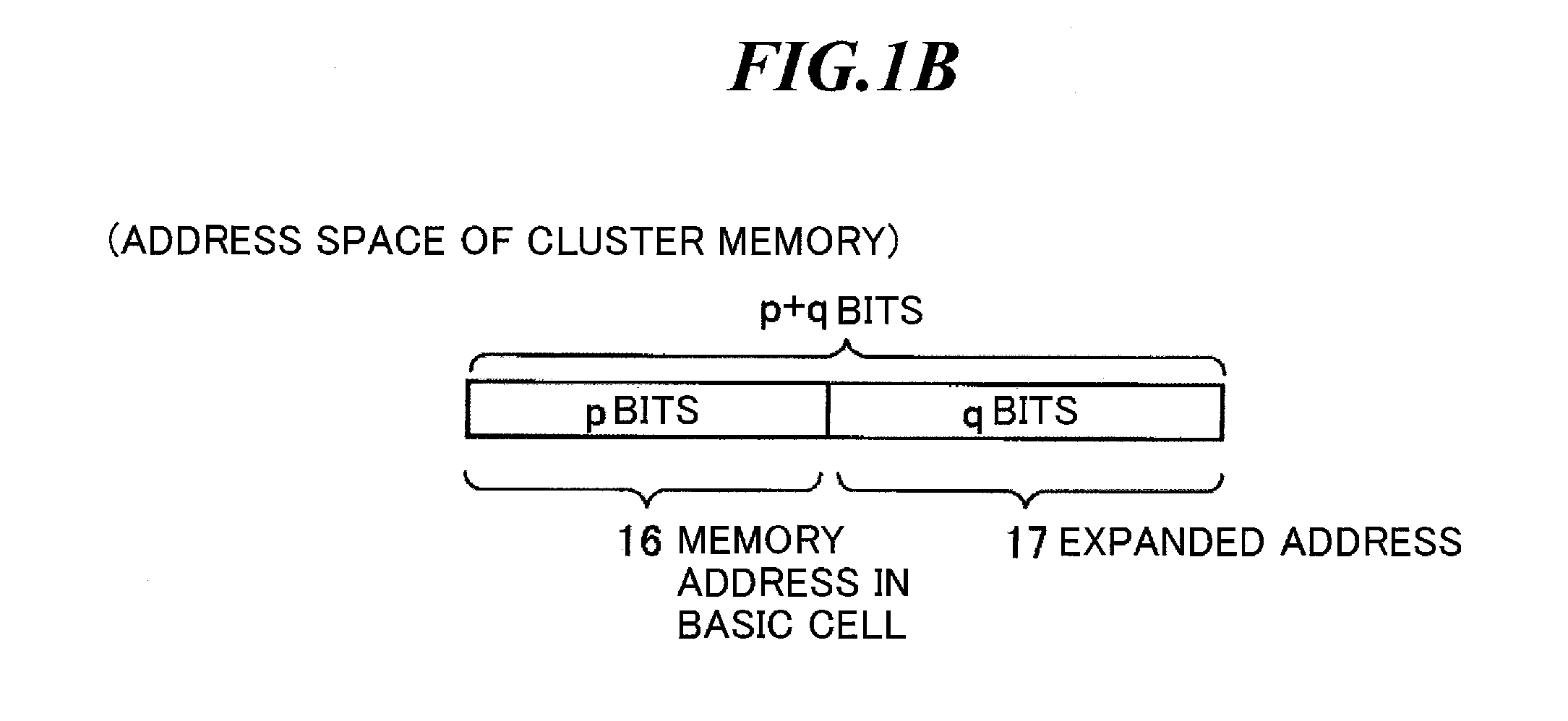

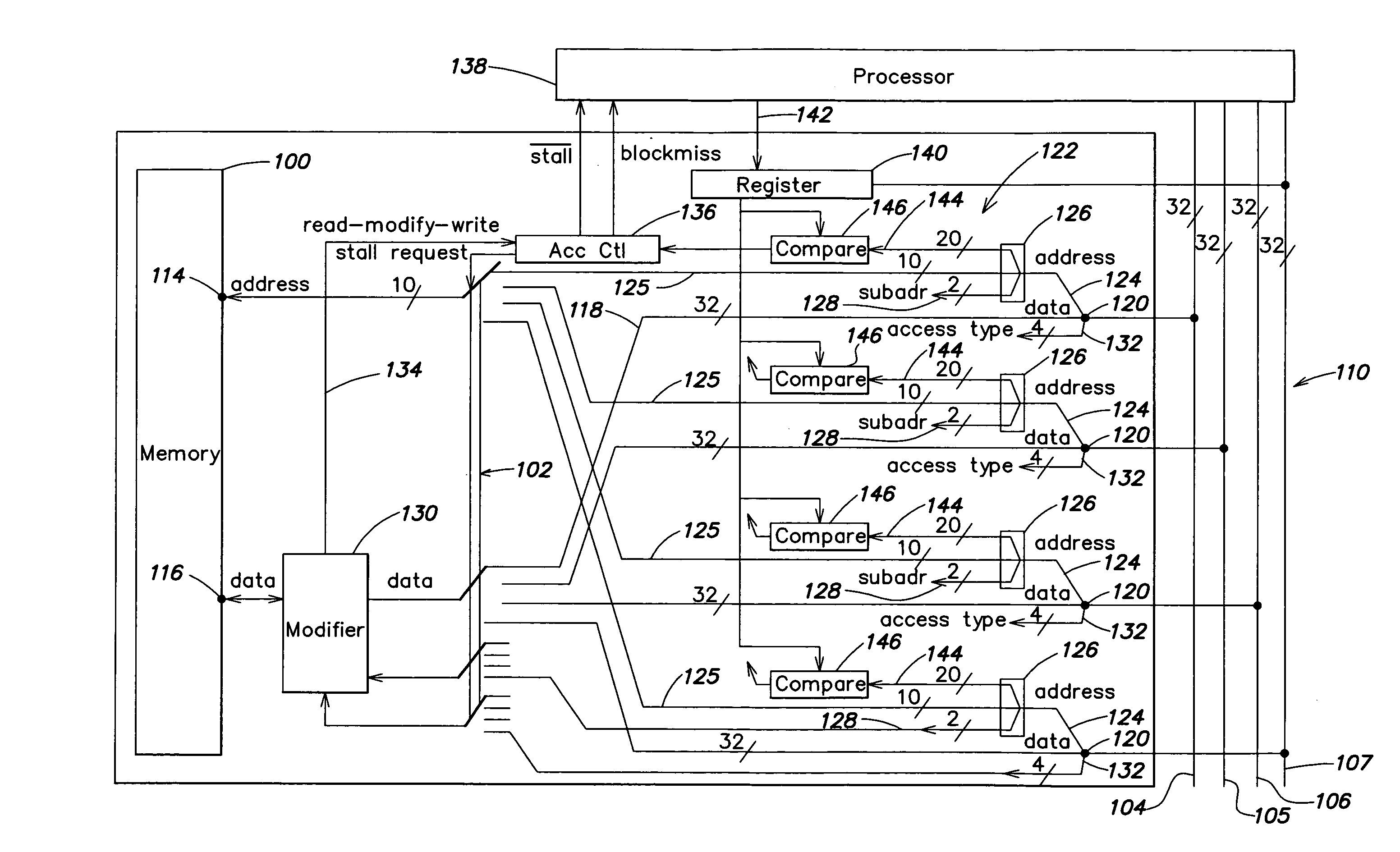

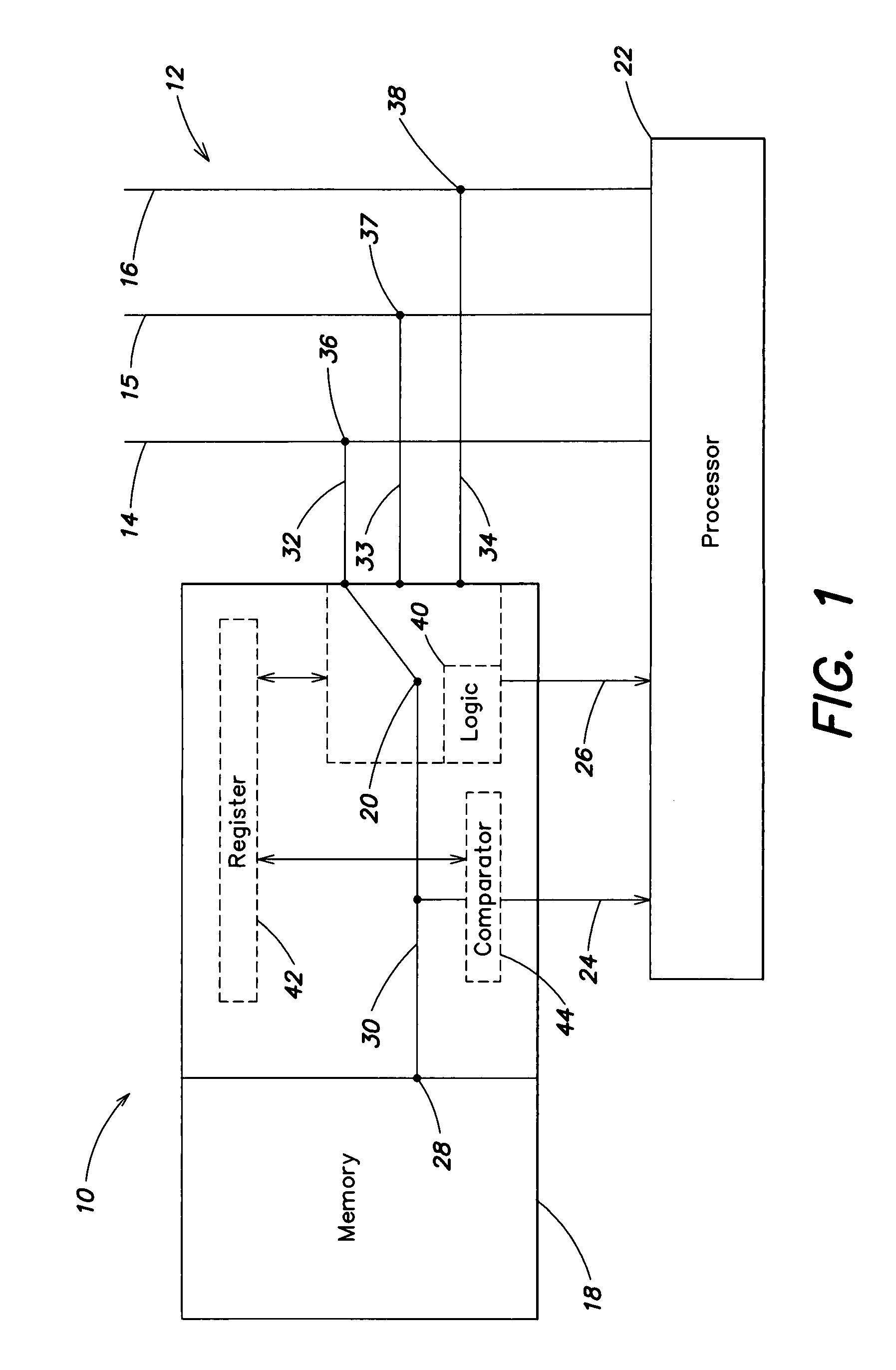

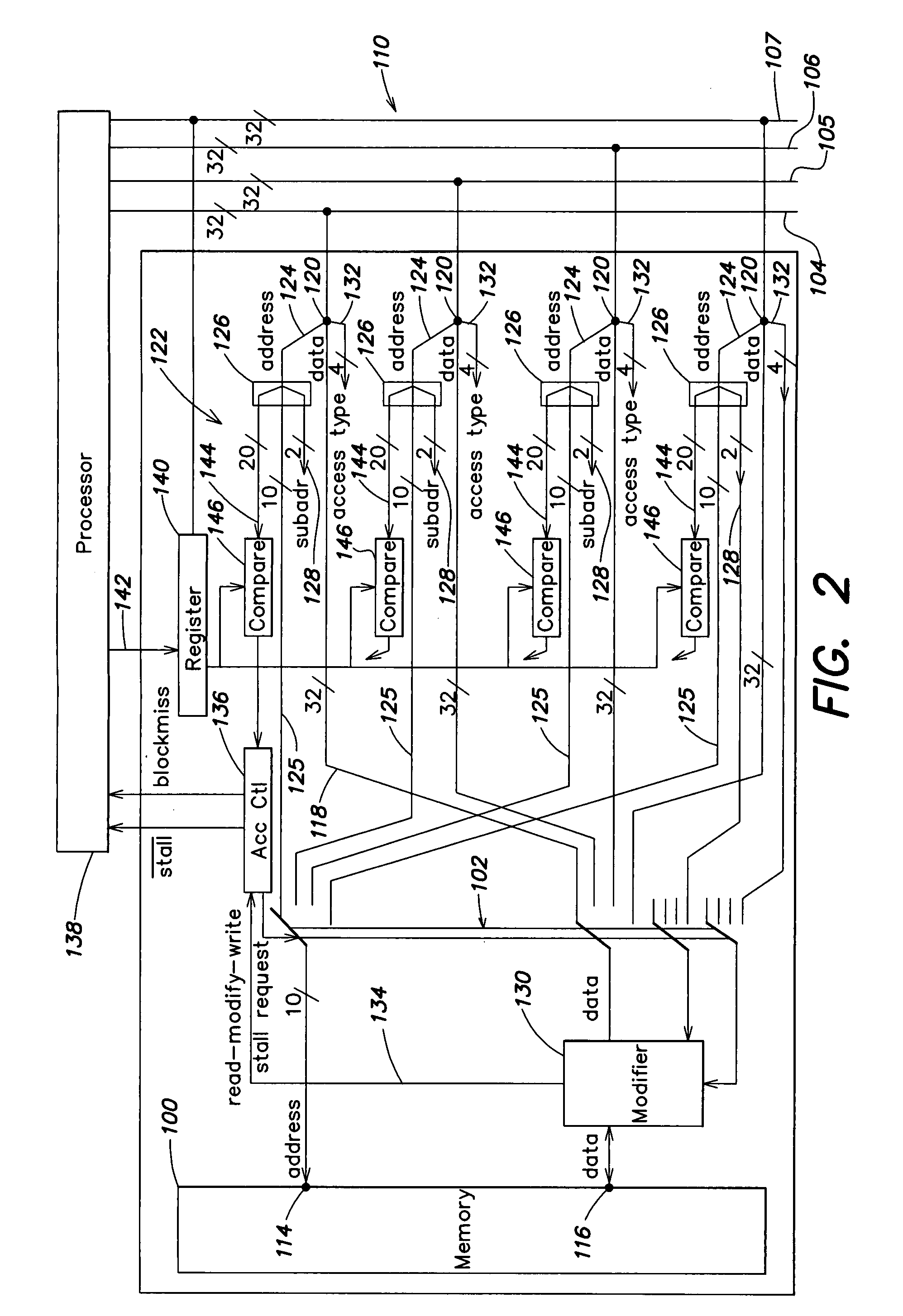

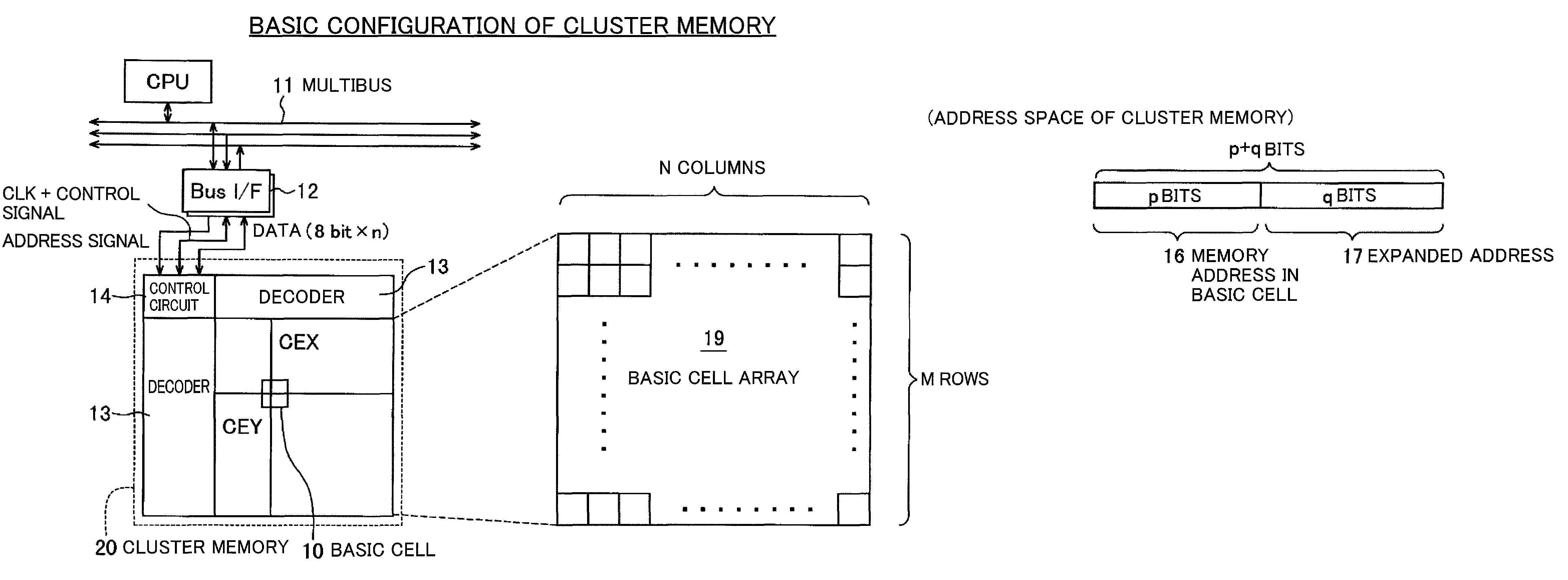

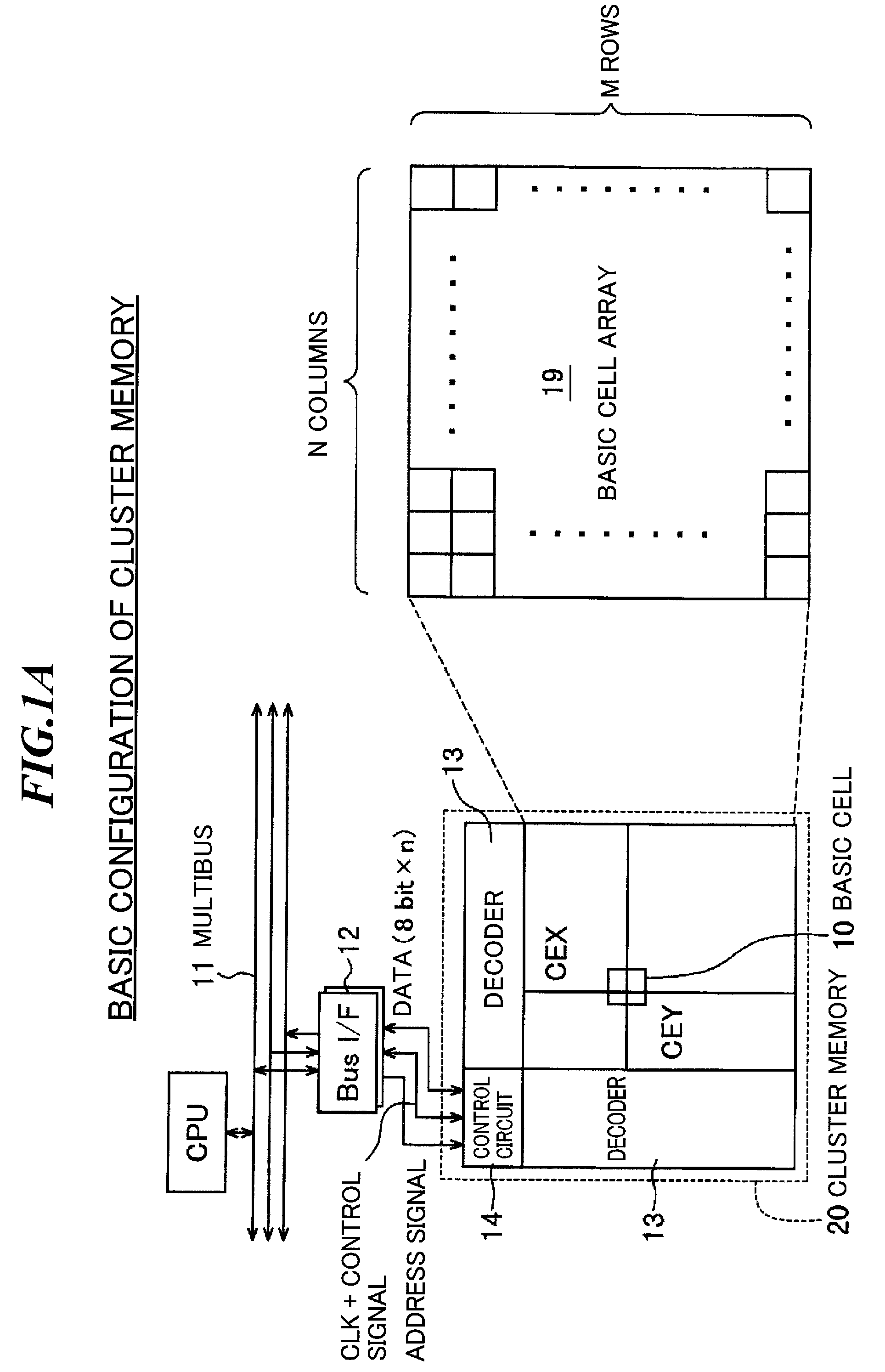

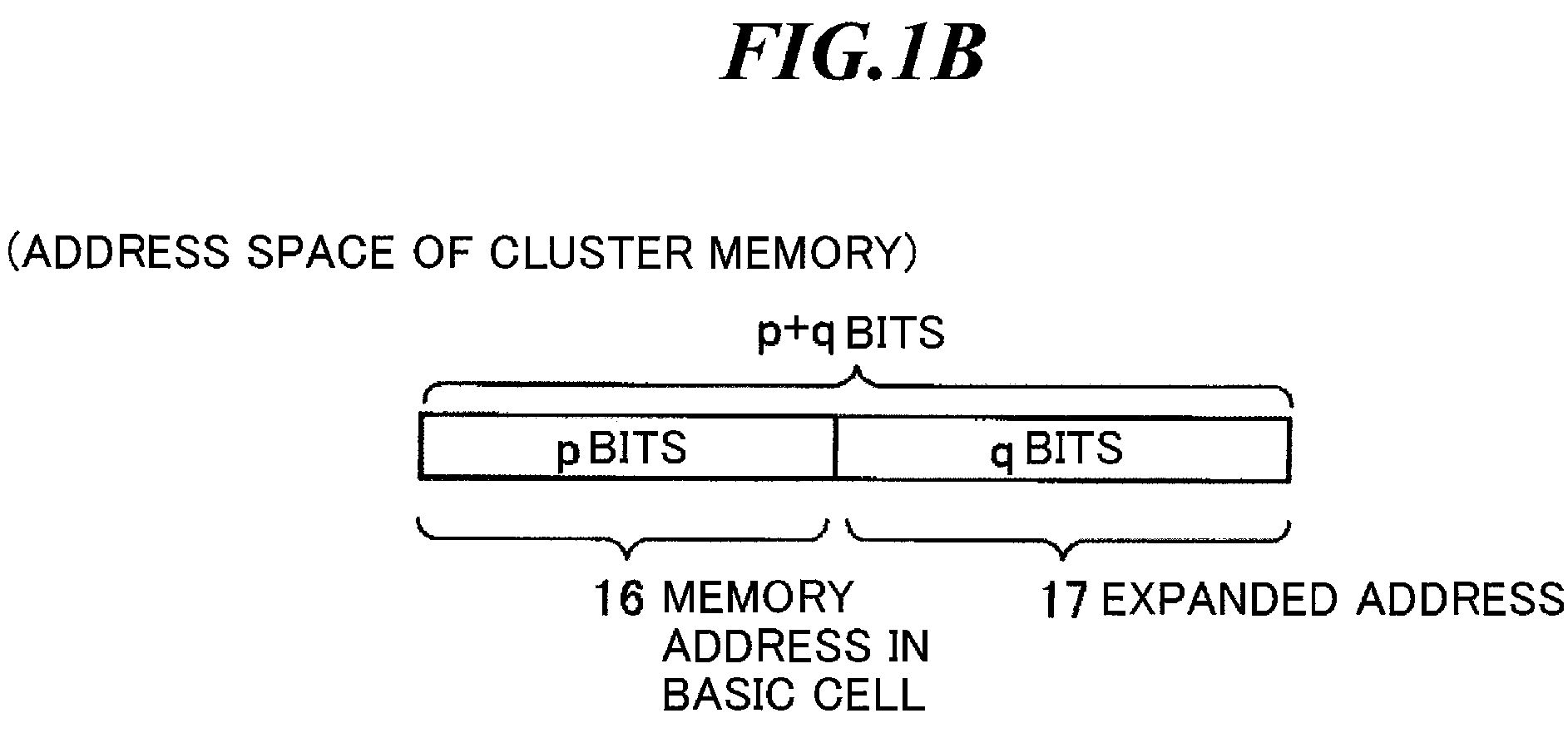

There is a problem that a bandwidth bottleneck occurs because a crossbar switch is used to cope with an increase in scale. In an example of a memory / logic conjugate system according to the present invention, a plurality of cluster memory chips each including a plurality of cluster memories 20 including basic cells 10 arranged in a cluster, the basic cell 10 including a memory circuit, and a controller chip that controls the plurality of cluster memories are three-dimensionally stacked, the plurality of cluster memories 20 located along the stacking direction of the plurality of cluster memory chips and the controller chip are electrically coupled to the controller chip via a multibus 11 including a through-via, an arbitrary one of the basic cells 10 is directly accessed through the multibus 11 from the controller chip so that truth value data is written therein, and whereby the arbitrary basic cell 10 is switched to a logic circuit as conjugate.

Owner:OTSUKA KANJI +7

Storage device for a multibus architecture

InactiveUS7287110B2Reduce expensesAvoid lostMemory adressing/allocation/relocationDigital storageControl memoryMultibus

A storage device for a multibus architecture includes at least one memory to store data, information, and / or addresses, along with a memory connection having a port to connect the memory to one of the buses of the multibus architecture. The memory connection, the port, and the bus have data lines to transmit data along with address lines to transmit addresses, and / or control information to control the memory and other devices connected to each specific bus within the multibus architecture. A switching device selectively connects the memory connection to one of the buses to enable a memory access to transmit data, addresses, and / or control information to or from the selected one of these buses.

Owner:MICRONAS

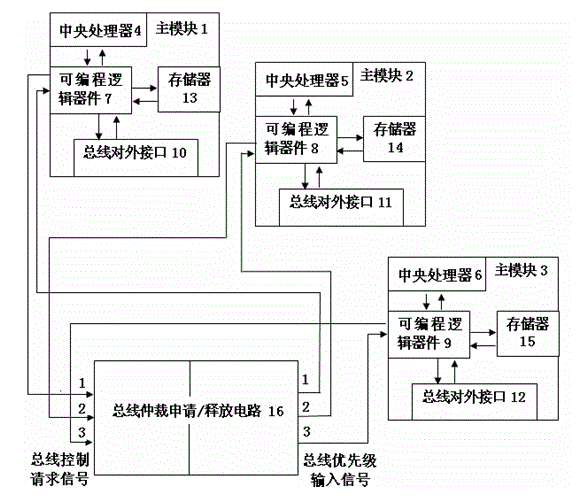

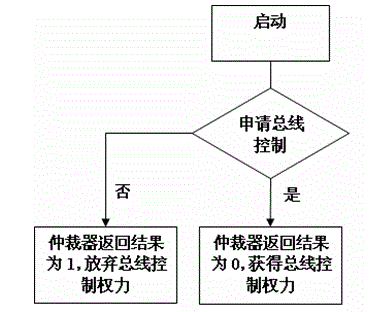

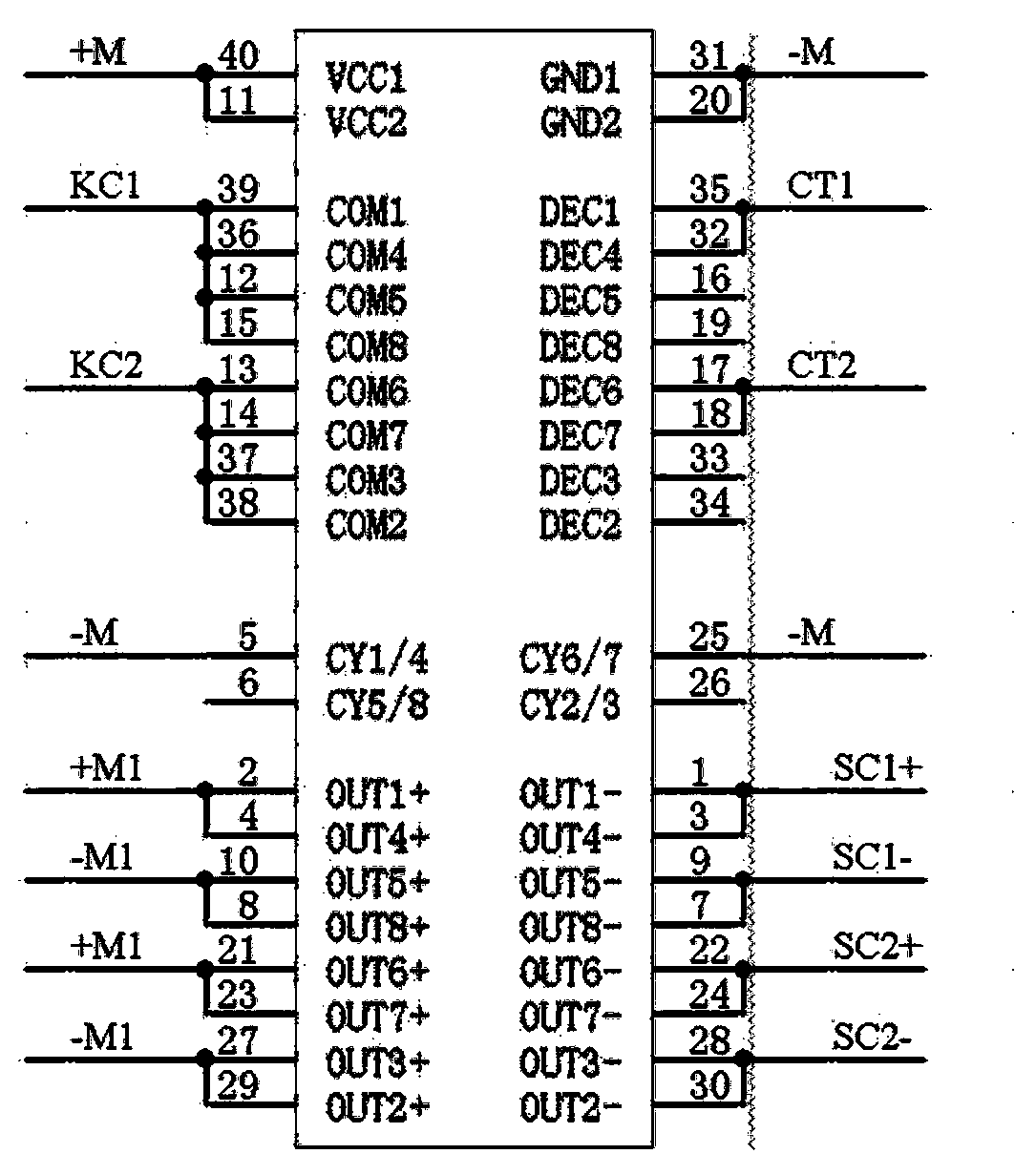

16-bit multibus circuit in 2 in 3 or 2 in 2 control system

ActiveCN102722466AIncrease flexibilityAvoid sendingElectric digital data processingElectricityControl system

The invention discloses a 16-bit multibus circuit in a 2 in 3 or 2 in 2 control system. The 16-bit multibus circuit in the 2 in 3 or 2 in 2 control system is characterized in that the system comprises three master modules and a bus arbitration application / release circuit. Each master module comprises a central processor, a programmable logic apparatus, a memory and a bus external interface which are independent. The program logic apparatus in each master module is electrically connected with the central processor, the memory and the bus external interface in the master module respectively. The program logic apparatuses in the three master modules are electrically with the bus arbitration application / release circuit respectively. Under a condition of same-level processor and due to the 16-bit multibus circuit in the 2 in 3 or 2 in 2 control system provided by the invention, the work efficiency and the operating speed of the system are improved, the device loss is reduced, the service life of the device is prolonged and the sending of incorrect commands is effectively prevented.

Owner:TIANJIN EMBEDTEC

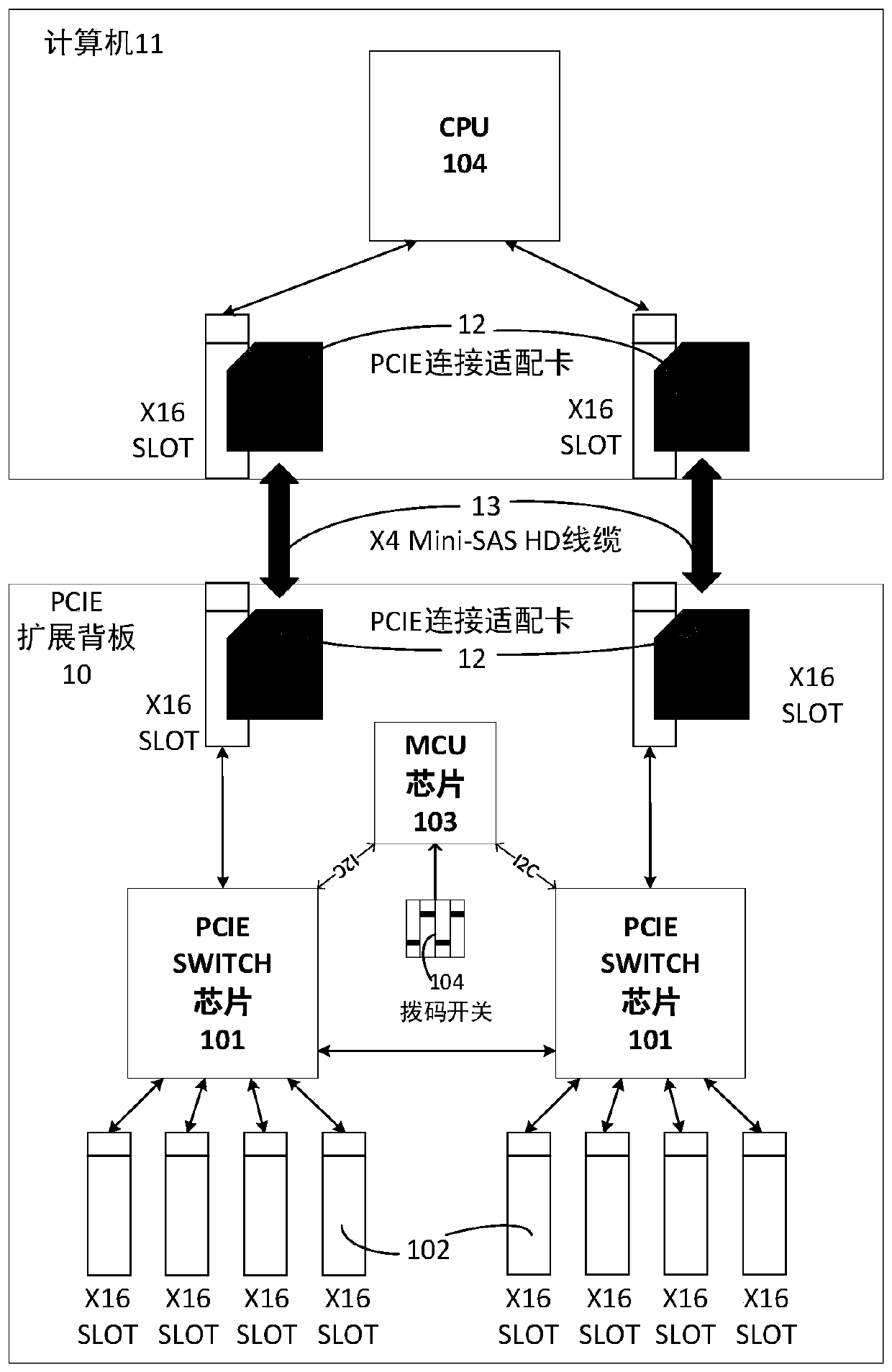

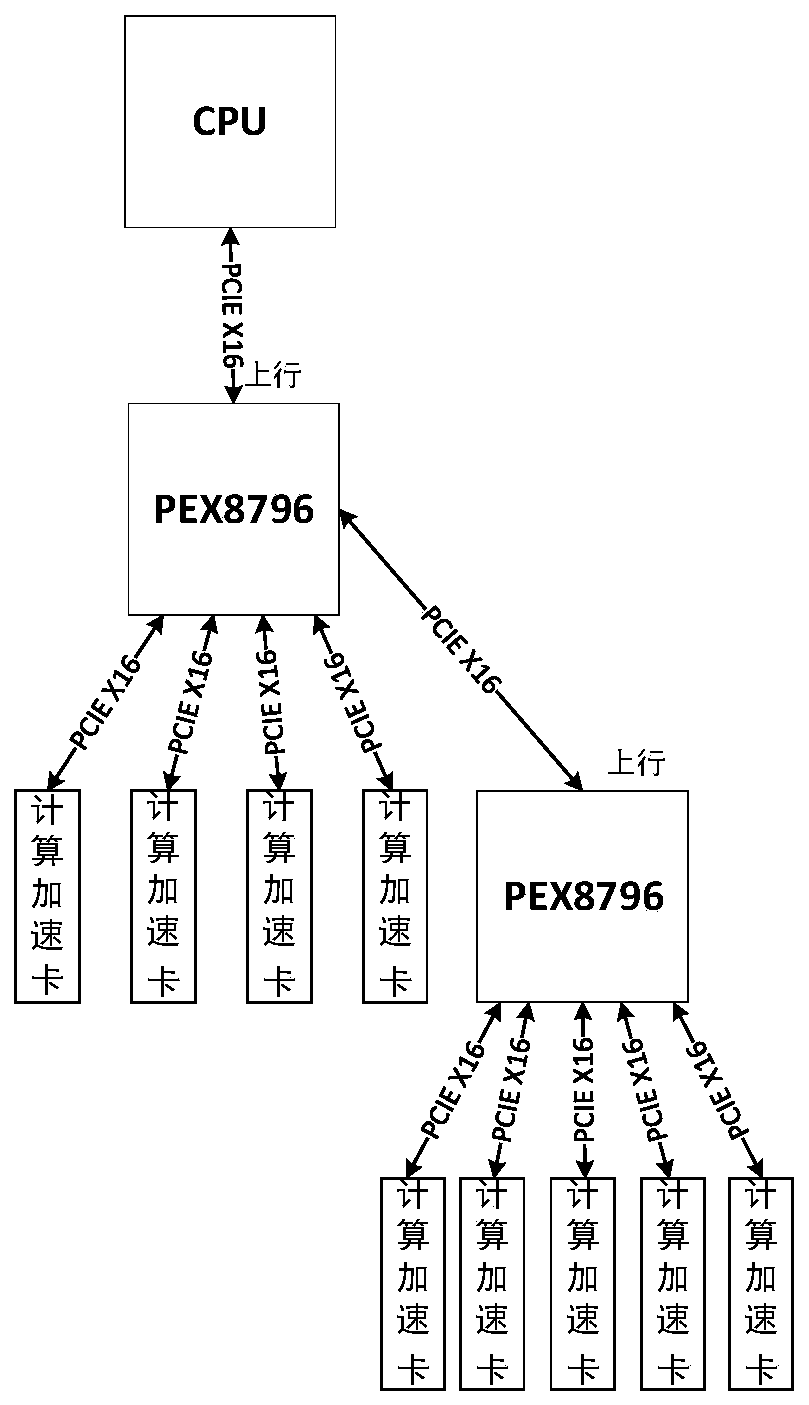

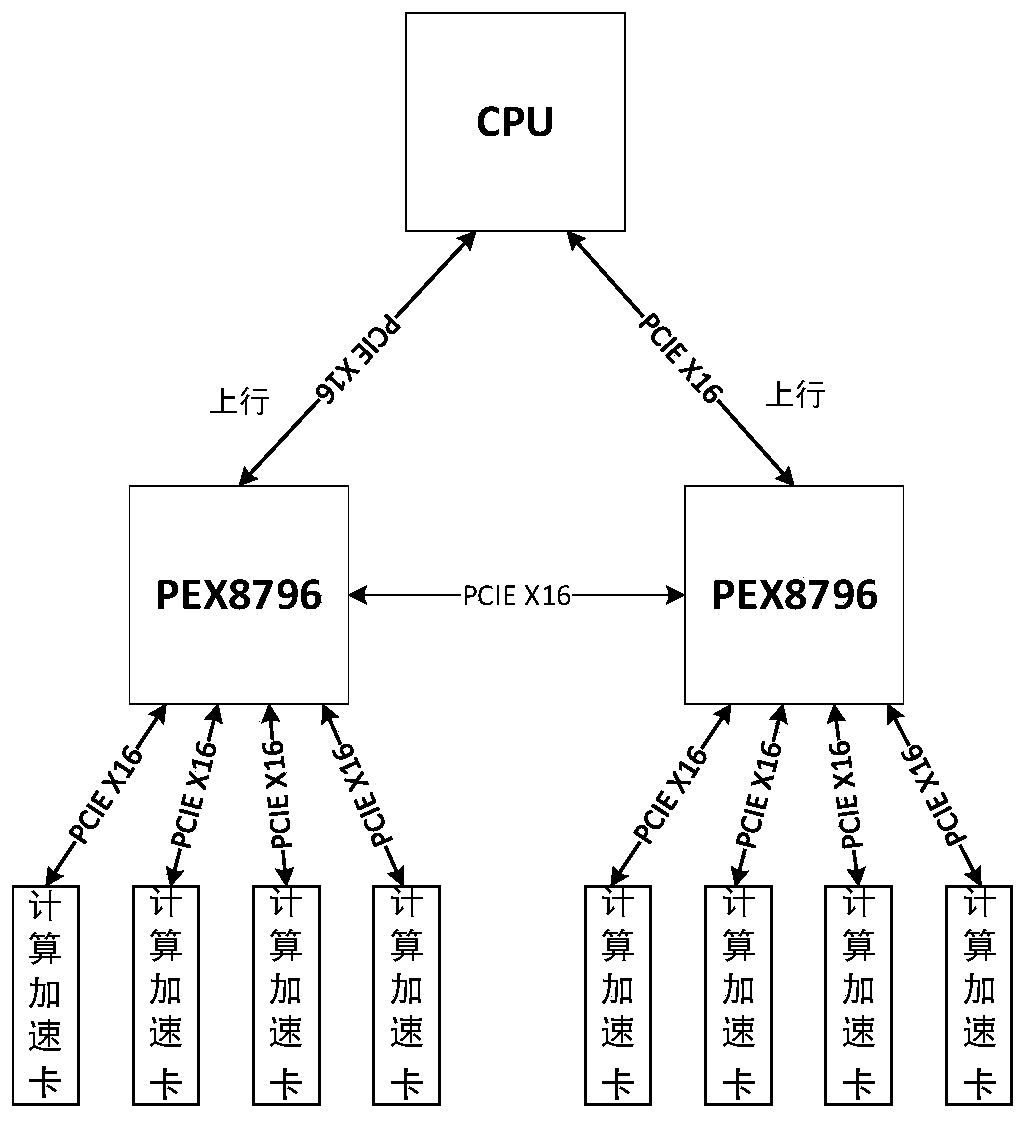

PCIE bus extension system and method

InactiveCN111538693ARich IO pinsIncrease flexibilityElectric digital data processingControl cellBus interface

The invention belongs to the technical field of data transmission, aims at solving the problem that PCIE interfaces are insufficient when multiple acceleration cards are used in the same computer, andprovides a PCIE bus extension system. The system comprises a CPU and a PCIE extension backboard in communication connection with the CPU. The PCIE expansion backboard comprises a micro-control unit,a dial switch and an exchange chip. The dial switch and the exchange chip are in signal connection with the micro-control unit; the micro-control unit can set the working mode of the switching chip based on the working state of the dial switch. The system has the beneficial effects that through the at least two PCIE switching chips arranged in the system, a plurality of PCIE X16 slots can be connected in an extended manner, two different connection relationships can be realized between the system and the CPU, and one or two groups of PCIE X16 signal connection between the system and the CPU isrealized; the system can be flexibly set according to application scenarios requiring higher data bandwidth or more PCIE bus interfaces, and two different topology schemes are realized by adopting one set of system.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI +1

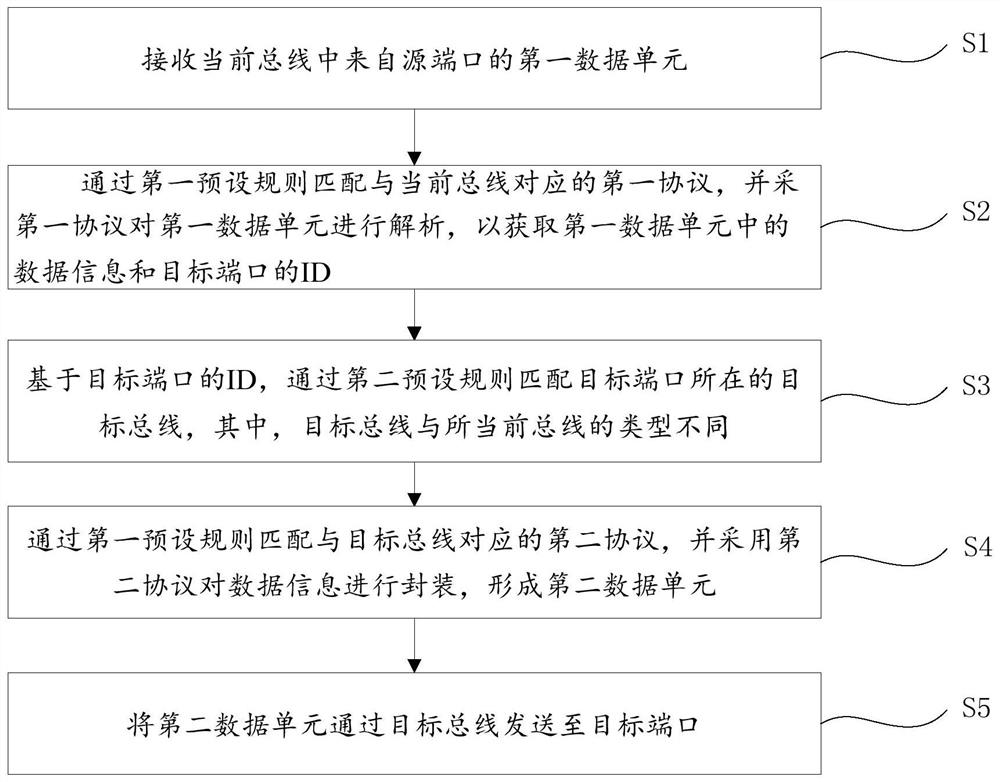

Multi-bus hybrid routing method and gateway device

ActiveCN111901215AImprove exchange efficiencyImprove transmission efficiencyNetwork connectionsBus networksHybrid routingEngineering

The invention discloses a multi-bus hybrid routing method and a gateway device. The method comprises the following steps of: receiving a first data unit from a source port in a current bus; matching afirst protocol corresponding to the current bus through a first preset rule, and analyzing the first data unit by adopting the first protocol to obtain data information in the first data unit and anID of a target port; based on the ID of the target port, matching a target bus where the target port is located through a second preset rule, the type of the target bus being different from that of the current bus; matching a second protocol corresponding to the target bus through the first preset rule, and packaging the data information by adopting the second protocol to form a second data unit;and sending the second data unit to the target port through the target bus. Routing of data unit transmission between different buses is achieved, and the data exchange and transmission efficiency isimproved.

Owner:ZHICHEAUTO TECH BEIJING

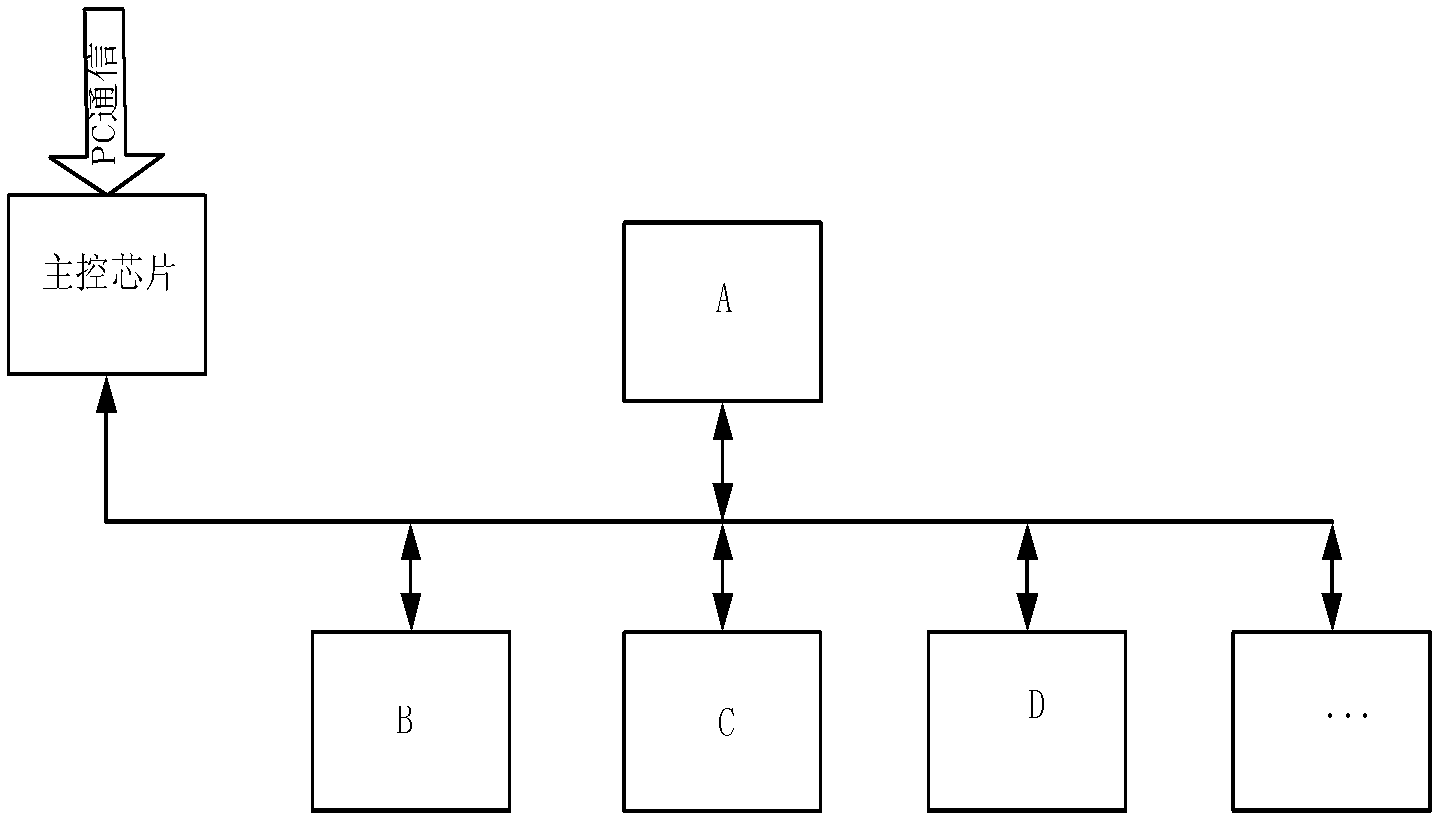

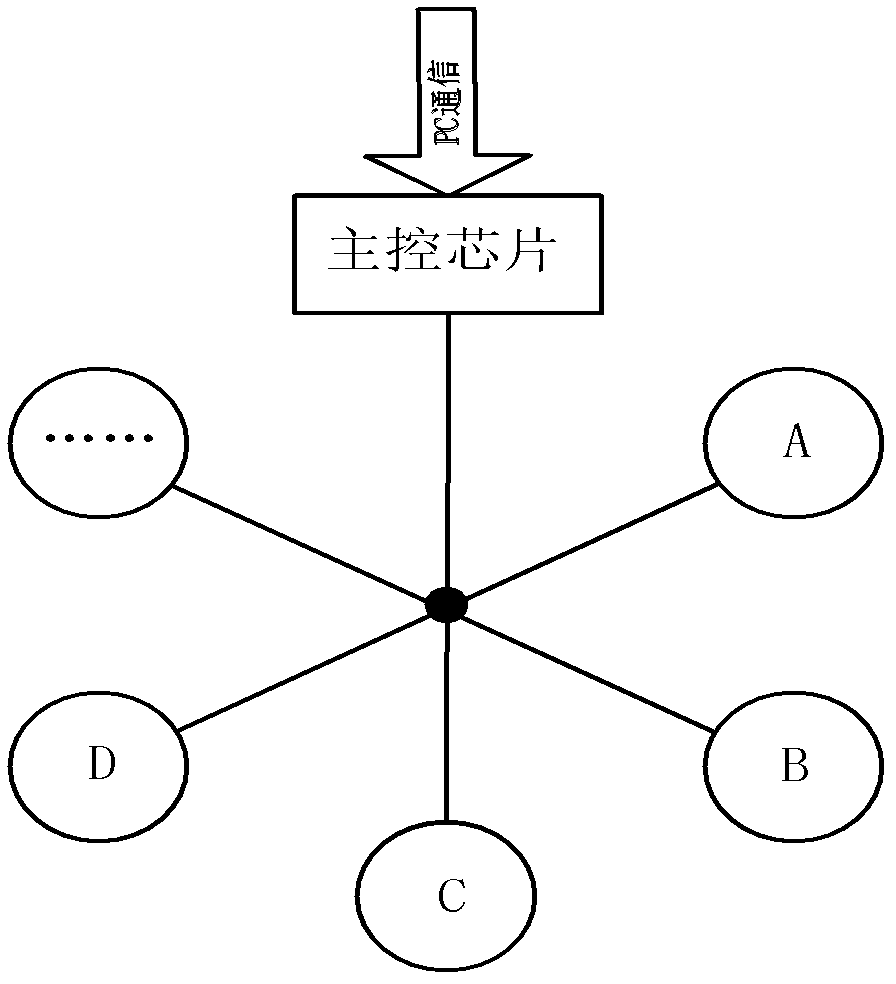

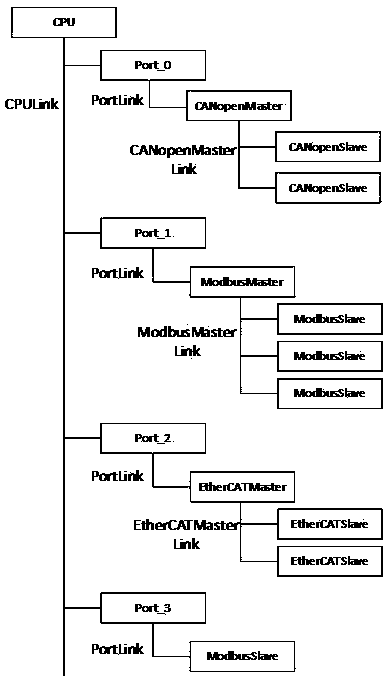

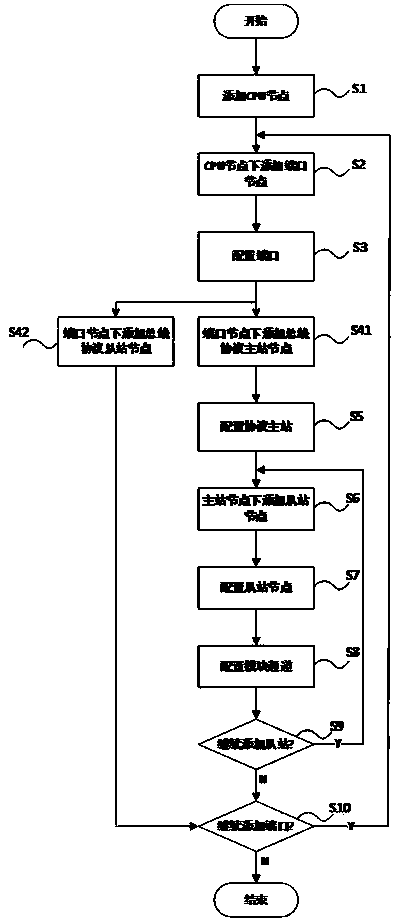

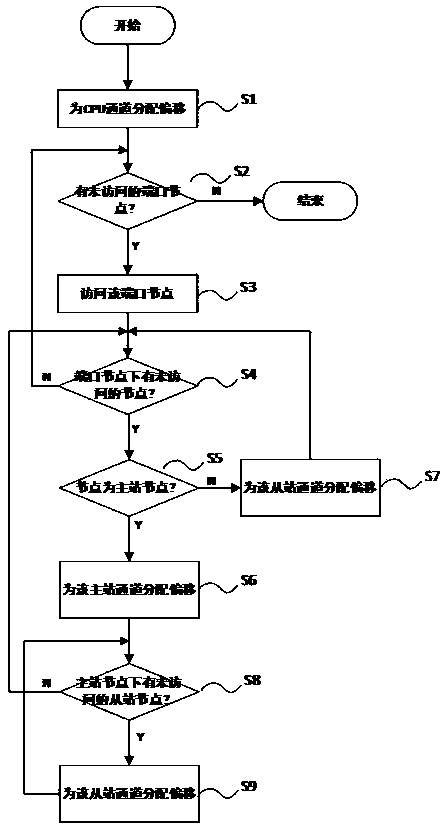

Unified module configuration strategy for multiple buses

The invention discloses a unified module configuration strategy for multiple buses. The strategy comprises a tree-shaped module configuration structure for various bus protocols, a multi-bus protocolconfiguration method for the structure, a module channel offset allocation algorithm for the structure, and a protocol library logic organization method for realizing the structure. The device tree structure is composed of nodes and links, CPU nodes are used as root nodes, port nodes are used as child nodes of the CPU nodes, bus protocol nodes are used as child nodes of the port nodes, protocol slave nodes are used as child nodes of a protocol master node, and all the nodes are connected through the links to form a configuration tree. Aiming at the tree structure, the invention provides a multi-bus unified configuration method which comprises the steps of CPU node addition and configuration, port node addition and bus master-slave node addition and configuration. Meanwhile, a module channel offset allocation algorithm is provided for the tree-shaped equipment structure, and the algorithm is based on depth-first traversal and offset accumulation. In order to realize the structure, an infrastructure definition library and a configuration library of each bus need to be realized. The structure and the implementation method can conveniently support the configuration of various bus protocols, facilitate the addition and deletion of new protocols, and reduce the research and development cost and the error rate.

Owner:中电智能科技有限公司

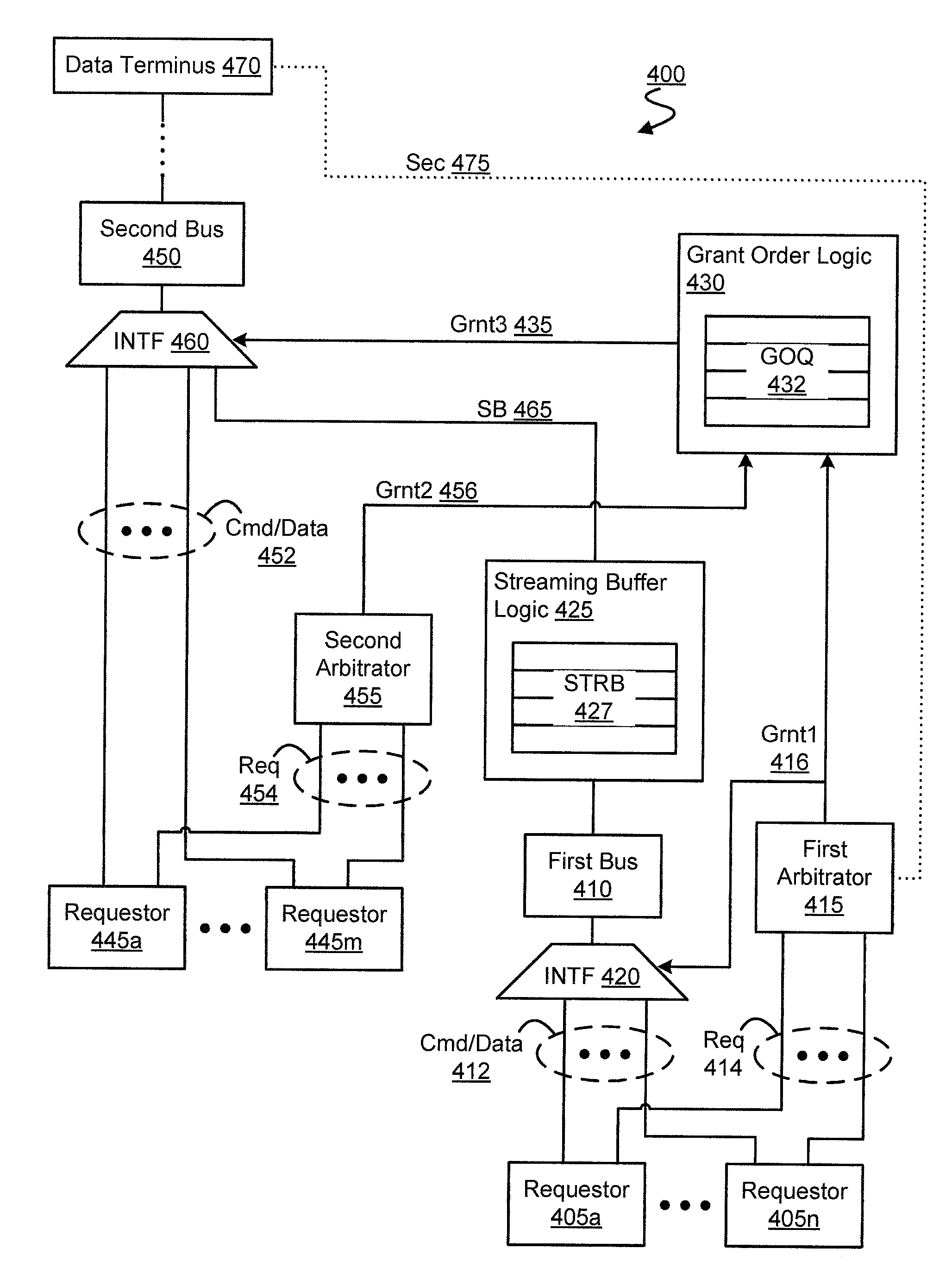

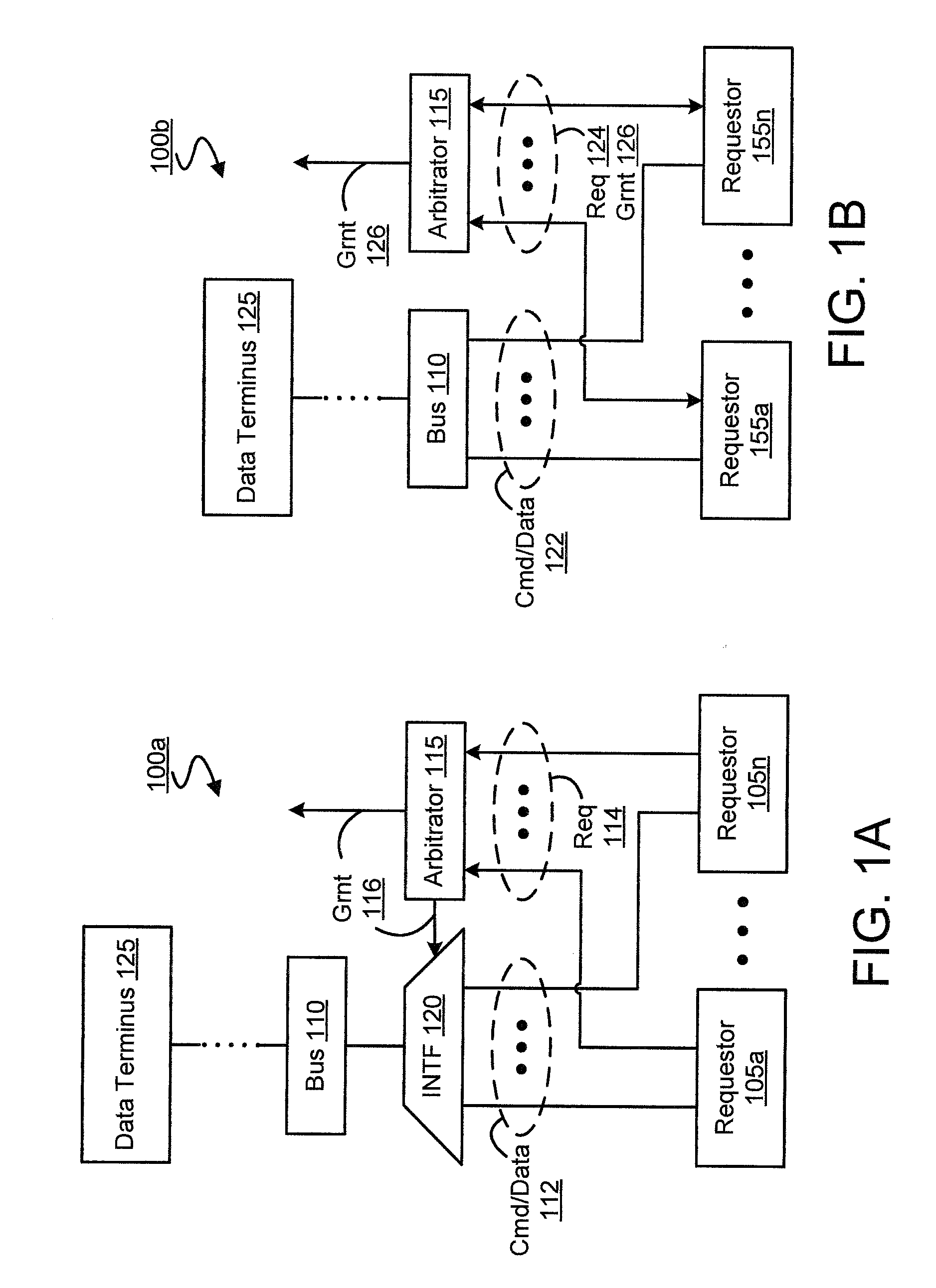

Method, apparatus and system for maintaining transaction coherecy in a multiple data bus platform

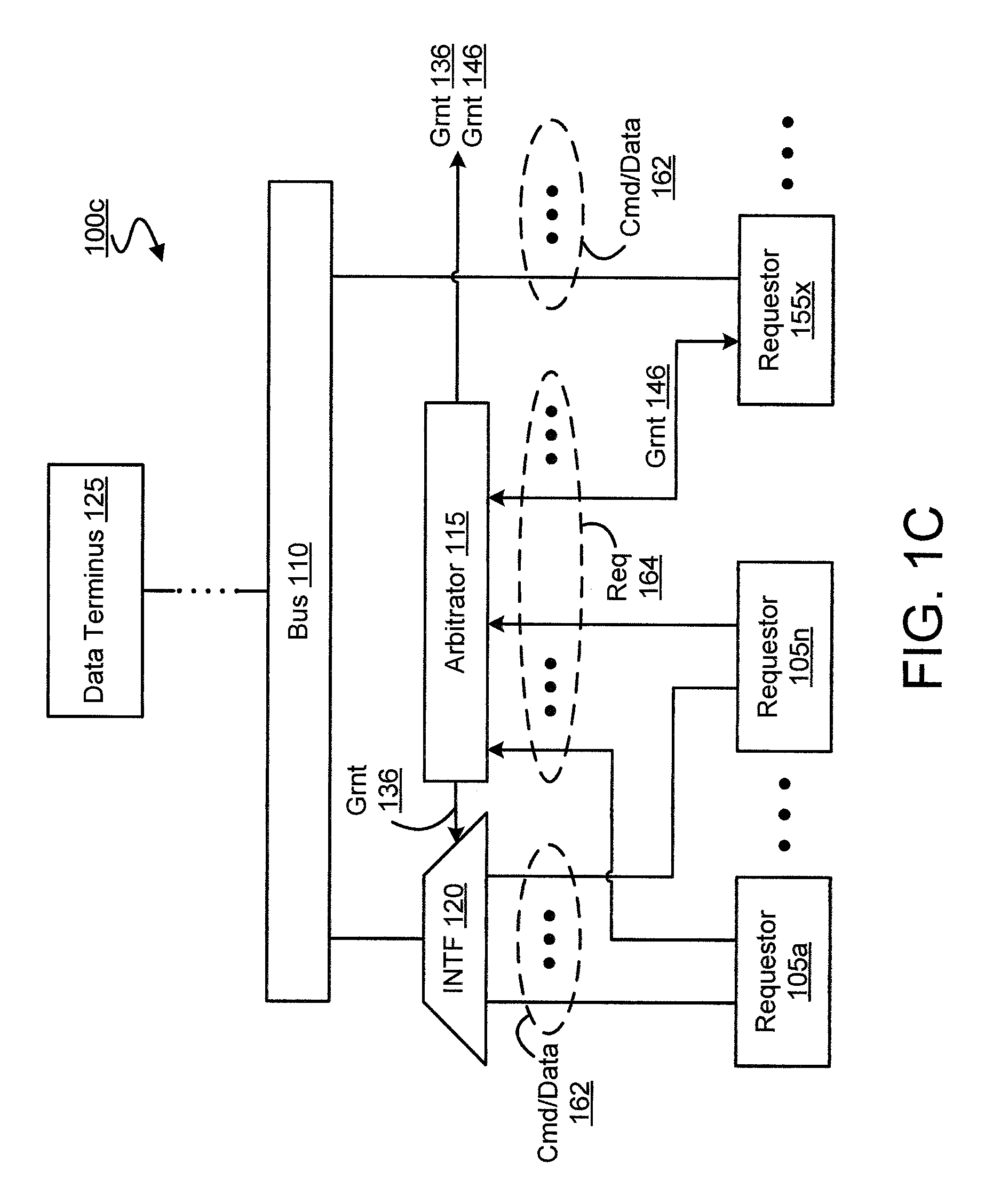

Techniques for maintaining an order of transactions in a multi-bus computer architecture. In an embodiment, an arbitrator receives access requests from a plurality of requestors, each access request requesting a respective access to a bus. Based on an arbitration between the access requests—e.g. between those requestors providing the access requests—the arbitrator may generate a grant message which triggers a carrying of a first message on the first bus. In certain embodiments, the grant message further triggers another carrying of the first message on the second bus.

Owner:INTEL CORP

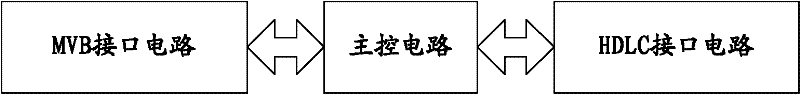

CANOPEN-HDLC gateway based on ARM 7

InactiveCN102223320AInnovative designEasy to installNetwork connectionsBus networksLight railEngineering

The invention discloses a CANOPEN-HDLC gateway based on ARM 7. The CANOPEN-HDLC gateway comprises a backboard, a CANOPEN interface board, an HDLC interface board, a main control board, an RS232_USB interface board and a power board providing working voltage for the above boards, wherein the above boards are connected through the backboard. The CANOPEN interface board is responsible for input and output of CANOPEN data. The HDLC board is responsible for input and output of HDLC data. The main control board is responsible for coding and decoding of CANOPEN protocol, coding and decoding of HDLC protocol, protocol function transition, and function and data processing of CANOPEN bus master and HDLC bus master. The gateway in the invention is accord with SO11898, CIADS-301Ver.4.02 and ISO13239-2002 standards. Interface problems among buses of subway and light rail are solved. The gateway provided in the invention has strong versatility and strong reliability.

Owner:华车(北京)交通装备有限公司 +1

Multi-bus network cross-network communication method, device, system and equipment and storage medium

ActiveCN112803998AAvoid Data Transmission ConflictsRealize interconnection communicationElectromagnetic transmissionBus networksCommunications systemNetwork communication

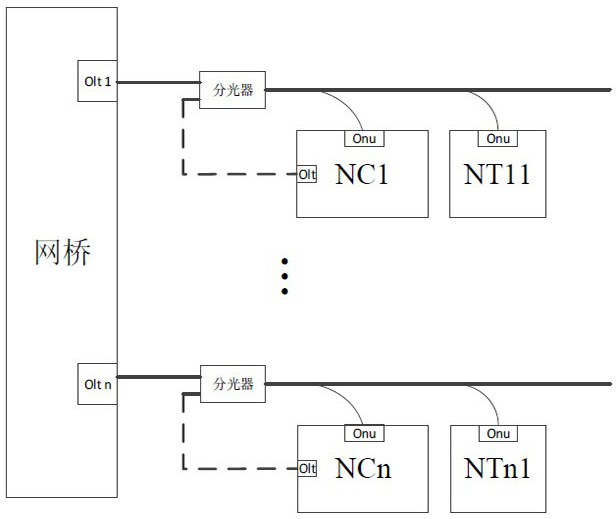

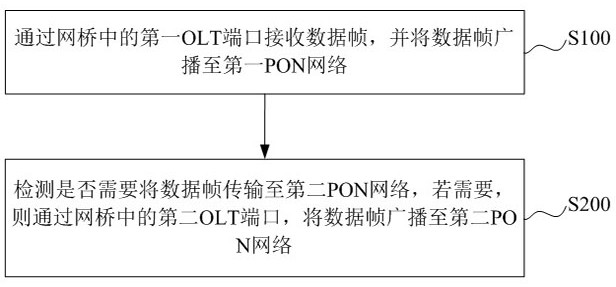

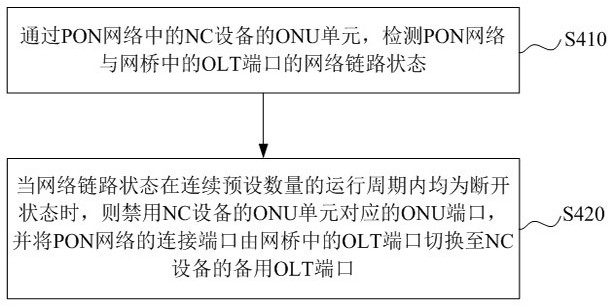

The invention relates to a multi-bus network cross-network communication method, device and system, computer equipment and a storage medium. The method is applied to a multi-bus network cross-network communication system. The system comprises a network bridge and PON networks; the network bridge comprises OLT ports; the OLT ports comprise a first OLT port and a second OLT port, the PON networks comprise a first PON network and a second PON network, the first PON network corresponds to the first OLT port, and the second PON network corresponds to the second OLT port. The method comprises the following steps: receiving a data frame through a first OLT port in a network bridge, and broadcasting the data frame to a first PON network; and detecting whether the data frame needs to be transmitted to a second PON network, and if so, broadcasting the data frame to the second PON network through a second OLT port in the network bridge. Therefore, data transmission conflicts among the networks can be avoided, and interconnection communication of a plurality of PON networks is realized.

Owner:北京国科天迅科技股份有限公司

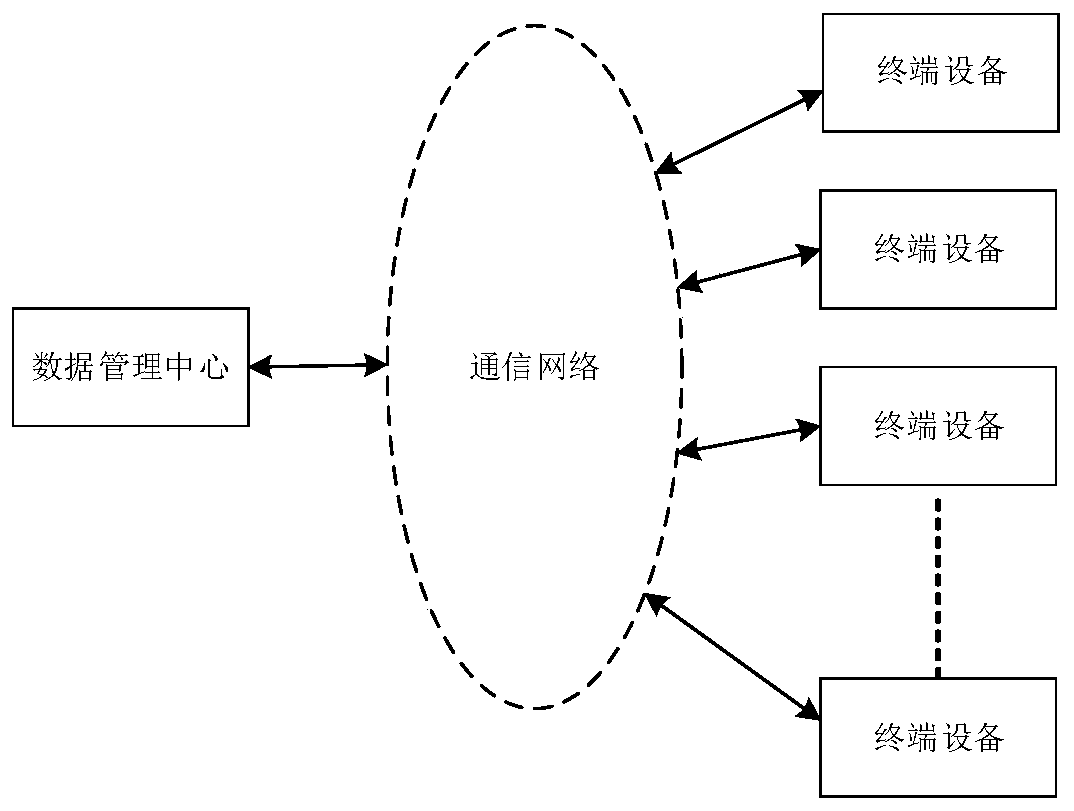

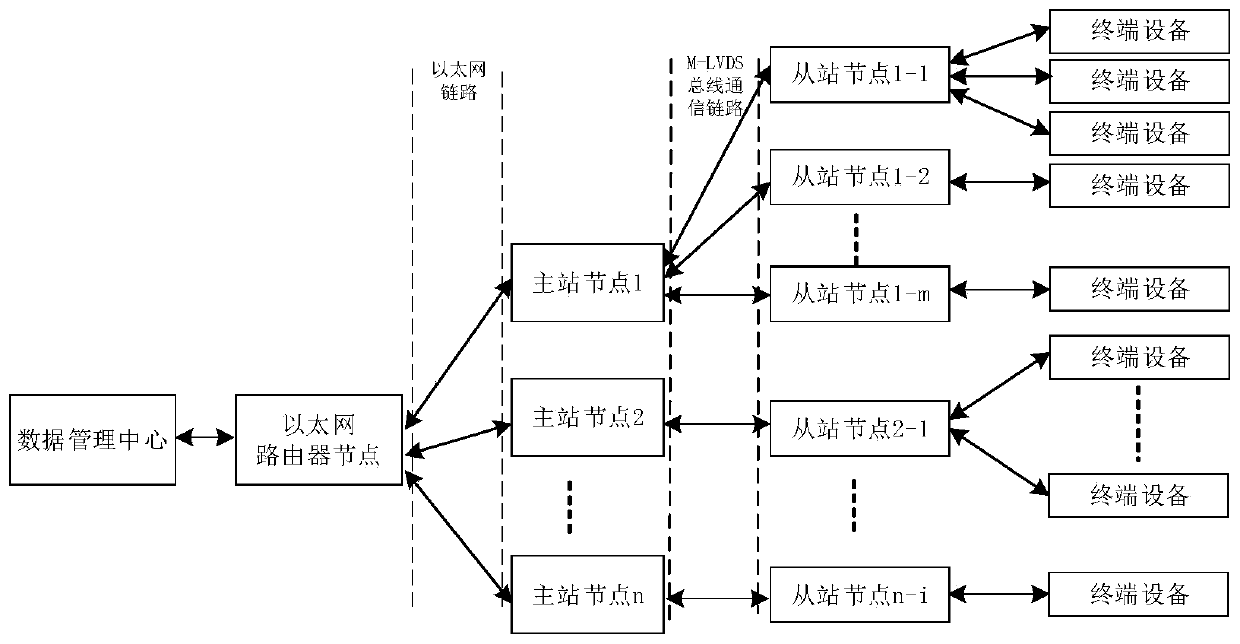

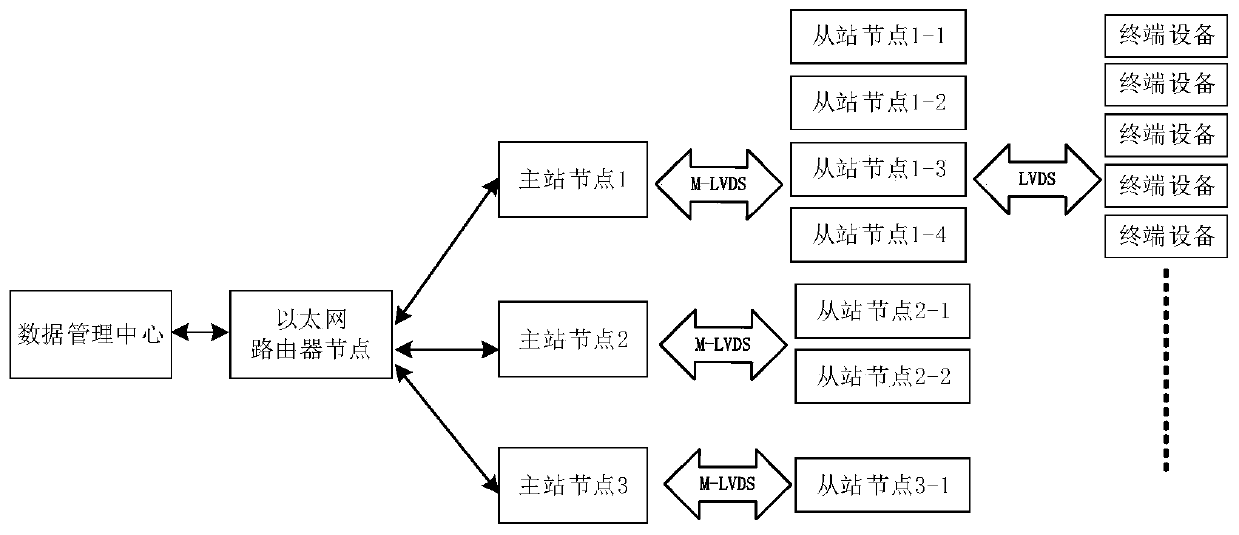

Multi-bus network communication architecture

PendingCN111464466ASolve the problem of low bandwidth utilizationAvoid Quantity LimitsBaseband system detailsBus networksNetwork deploymentTerminal equipment

The invention relates to a multi-bus network communication architecture. The architecture includes an Ethernet router node, a master station node and slave station nodes. The Ethernet router node is in bridge connection with a data management center and the master station node, the master station node is connected with the slave station nodes through an M-LVDS bus, the slave station nodes communicate with terminal devices, and a network structure formed by cascading the data management center, the Ethernet router node, the master station node, the slave station nodes and the terminal devices is achieved. According to the multi-bus network communication architecture, the communication bandwidth utilization efficiency of a bus communication link can be improved; the network deployment mode can be optimized by configuring the number of the nodes and the node connection relationship, and the access capability can be provided for different types of terminal devices by configuring the slavestation nodes, so that the limitation of the terminal devices in the aspects of access mode, number, bus type and the like can be avoided, flexible network scale expansion is realized, and the multi-bus network communication architecture is suitable for more application environments.

Owner:NAT UNIV OF DEFENSE TECH

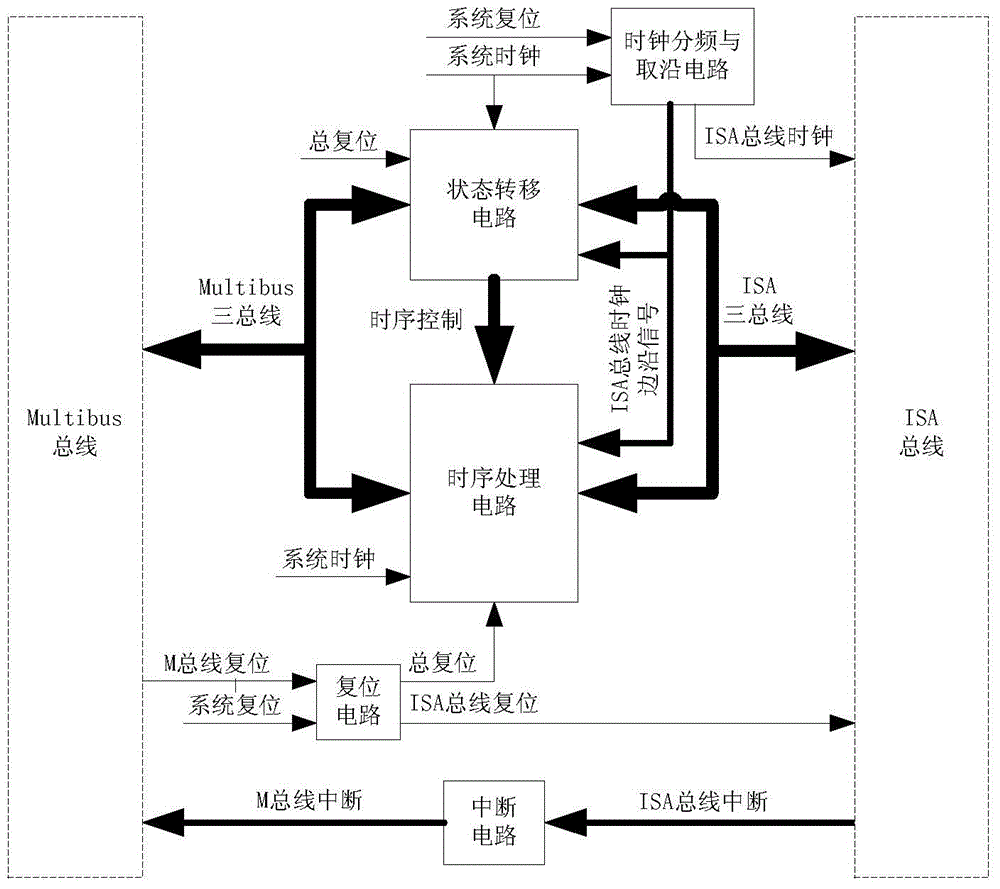

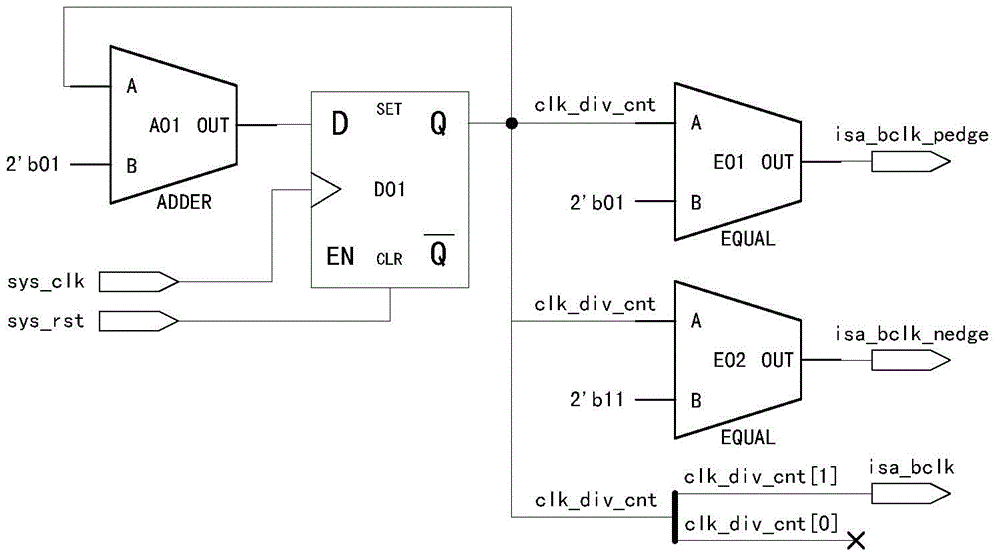

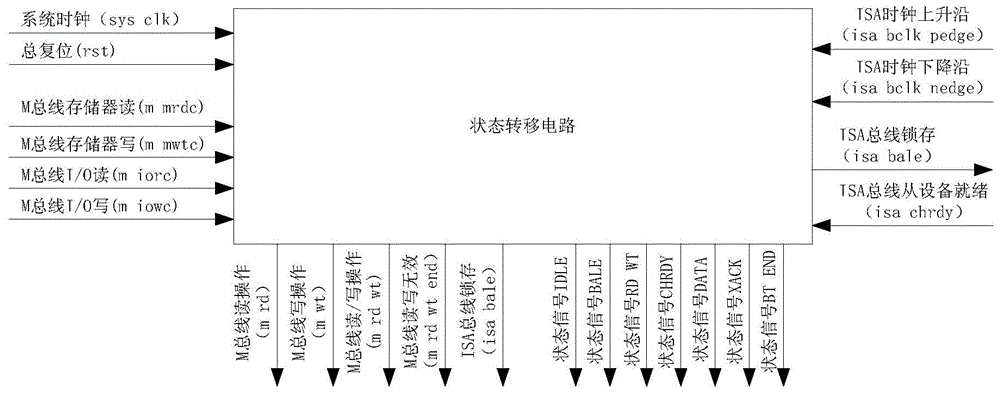

Multibus bus-to-ISA bus read-write operation switching circuit

ActiveCN104572559ASimple structureImprove conversion efficiencyElectric digital data processingComputer system design16-bit

The invention discloses a Multibus bus-to-ISA bus read-write operation switching circuit. The Multibus bus-to-ISA bus read-write operation switching circuit switches the asynchronous read-write operation of the Multibus bus into the synchronous read-write operation of the ISA bus to realize the read-write operation of Multibus bus main equipment for ISA bus slave equipment. The Multibus bus-to-ISA bus read-write operation switching circuit is simple in structure and supports 8-bit and 16-bit data width, an address wire can be extended according to user requirements, and the address wire can be used for designing a hybrid bus computer system. The Multibus bus-to-ISA bus read-write operation switching circuit realizes mixed insertion and compatibility for configuring ISA bus slave equipment on a Multibus bus case and has broad application in the hybrid bus reinforced computer design field, computer bus board card test diagnosis field and the like.

Owner:716TH RES INST OF CHINA SHIPBUILDING INDAL CORP +1

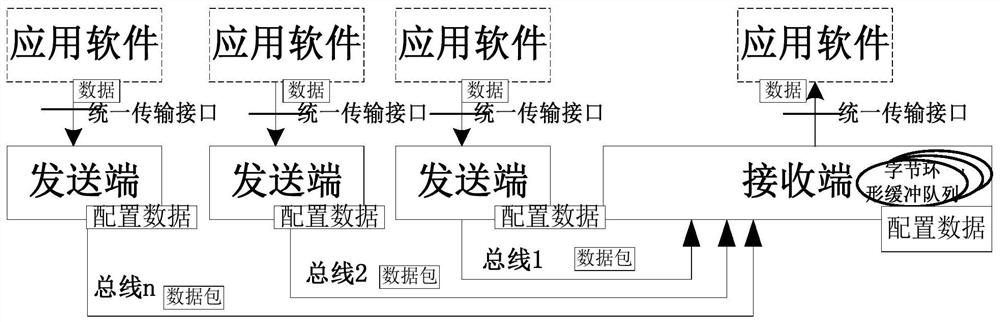

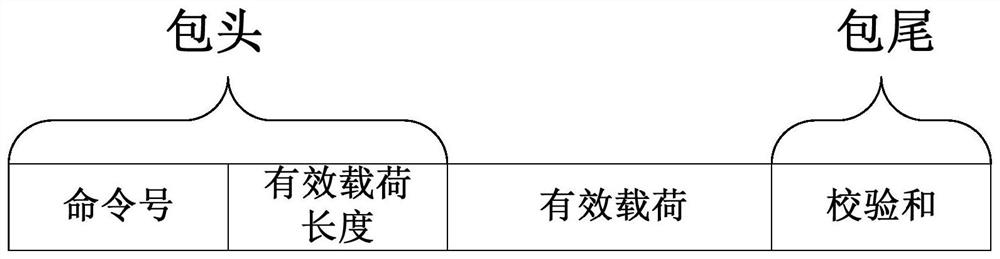

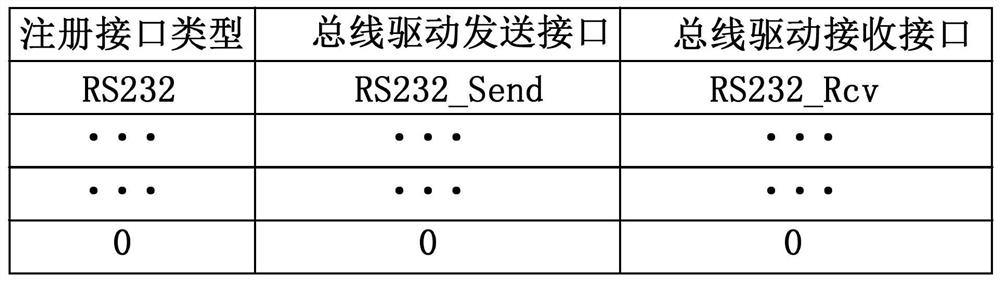

High-security configurable real-time data transmission framework supporting heterogeneous bus

ActiveCN112433707ASolve the real-time problem of transmissionEasy to controlProgramming languages/paradigmsProgram loading/initiatingData packSource Data Verification

The invention discloses a high-security configurable real-time data transmission framework supporting a heterogeneous bus, which is a constructed unified transmission framework and comprises a transmission module, a unified transmission interface, configuration data and a packet format, wherein the unified transmission framework supports and can configure a heterogeneous bus, specifically supportsa programming interface registration bus based on application software and supports a unified transmission interface; the method has high security and configurable capability, specifically supports the configuration and filtering of data packets in different electromechanical application modes, and supports the transmission start and end positioning and data verification based on a state machine.And the system has the functions of receiving multi-bus data in real time and configuring the multi-bus data. According to the embodiment of the invention, the problems of multiple bus types and non-uniform interfaces are solved, the problems that load data transmission in an electromagnetic environment is easy to cause errors and messages cannot be distinguished due to continuous arrival of thedata are solved, and the problem of transmission real-time performance is solved.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

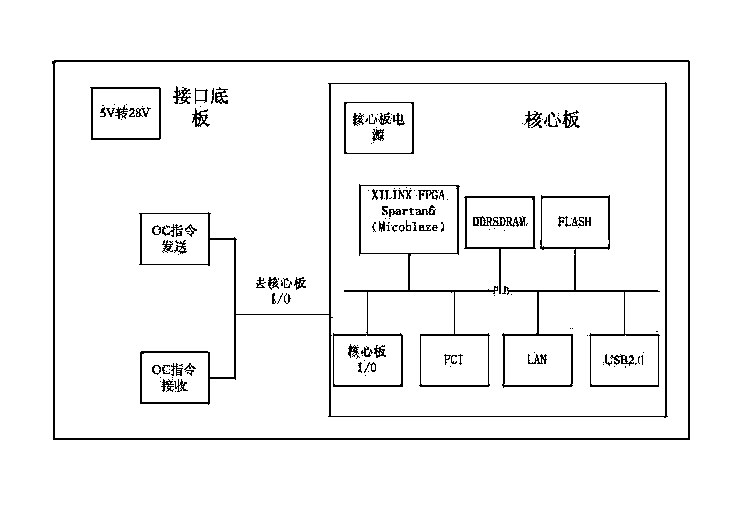

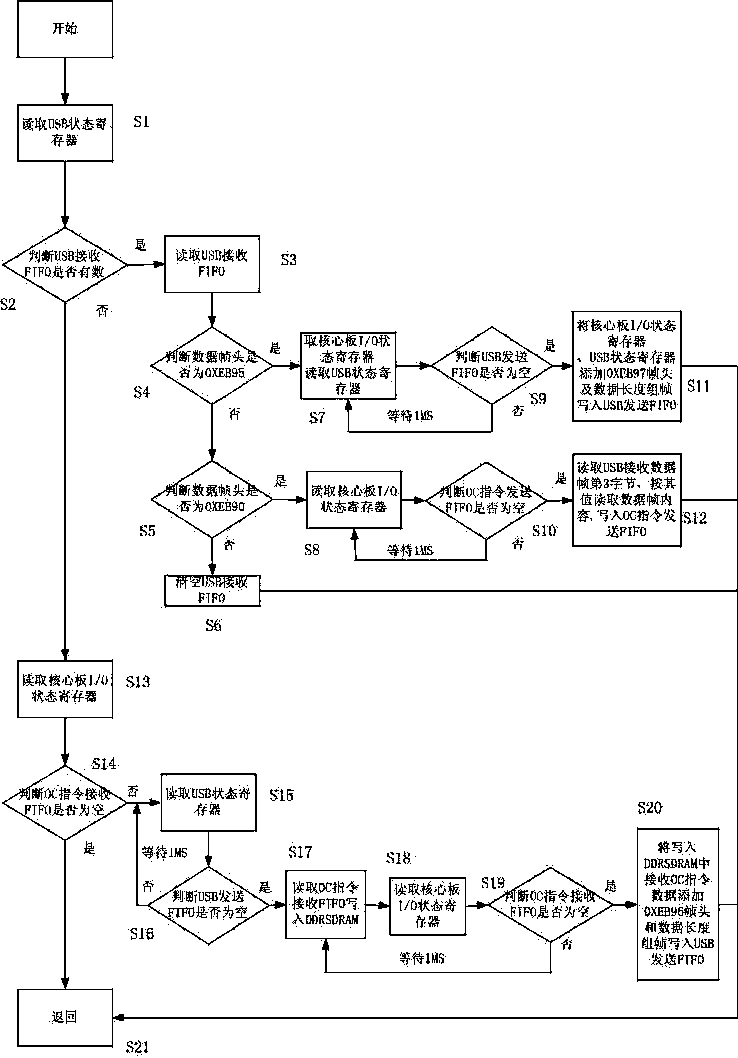

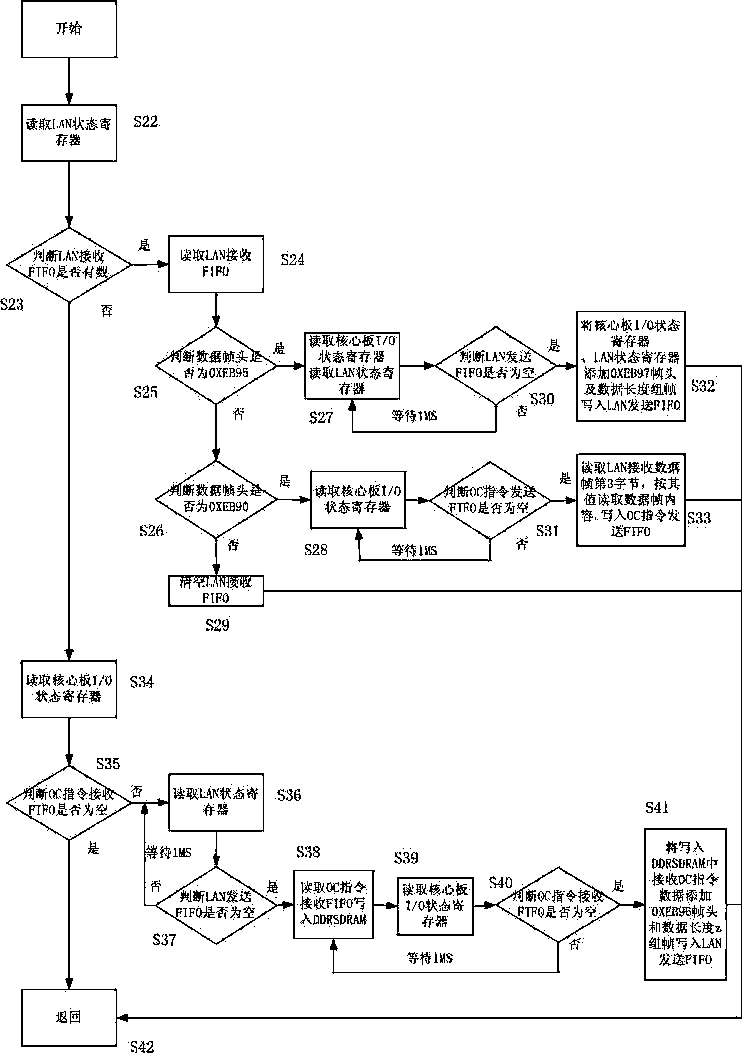

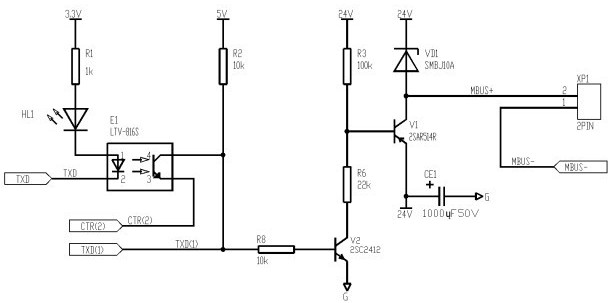

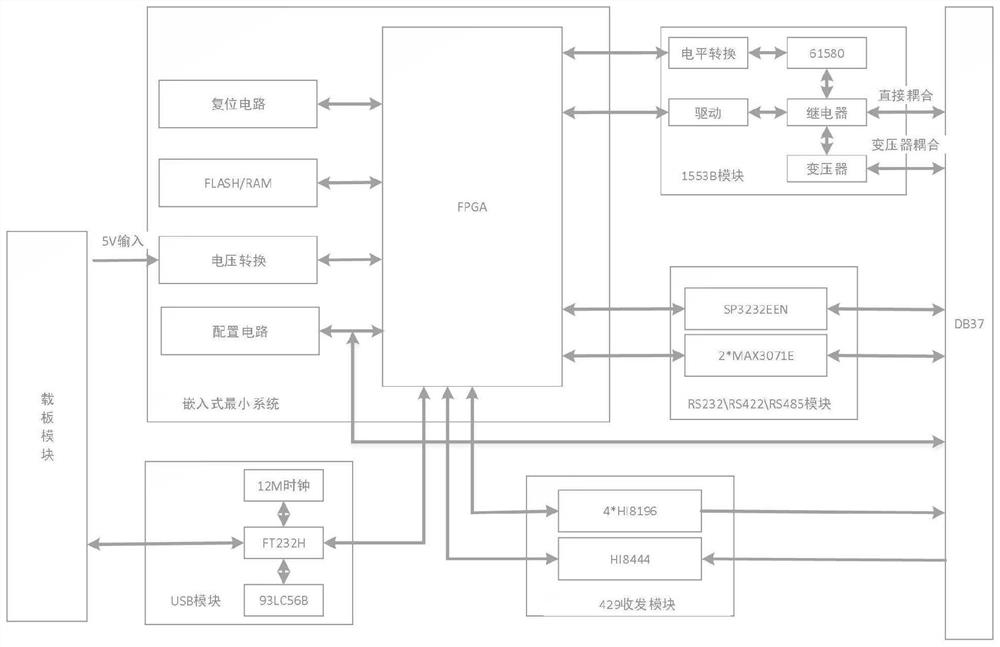

USB/PCI/LAN OC instruction satellite ground detection module

ActiveCN104021061AShorten the development cycleReduce development costsProgramme controlComputer controlUSBMultibus

The invention relates to a USB / PCI / LAN OC instruction satellite ground detection module. A corresponding integrated ground detection device is developed according to specific functions of each satellite, and the defects including large interface number, long development period and the like exist. The USB / PCI / LAN OC instruction satellite ground detection module is formed by combining a USB / PCI / LAN multi-bus core board and an OC instruction universal detection interface base plate. The USB / PCI / LAN multi-bus core board comprises an FPGA device, a DDRSDRAM device, an FLASH device, a PCI device, an LAN device, a USB device, a core board power supply circuit and a core board I / O. The OC instruction universal detection interface base plate comprises a 5V-28V circuit, an OC instruction sending circuit and an OC instruction receiving circuit. An OC instruction logic of the interface base plate is hung to a PLB bus of an FPGA embedded soft core Microblaze to finish control and data communication. USB, PCI, LAN standard industrial interfaces are designed on one core board, and satellite ground detection device quick integration based on three types of standard industrial interfaces can be achieved.

Owner:XIAN SPACE STAR TECH IND GRP

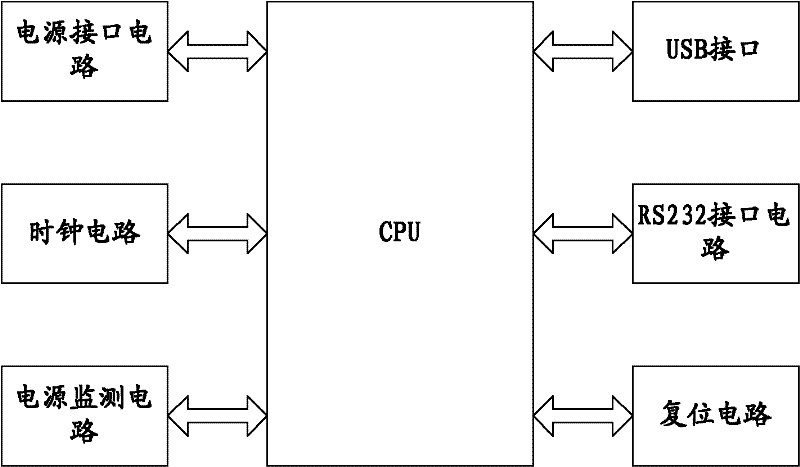

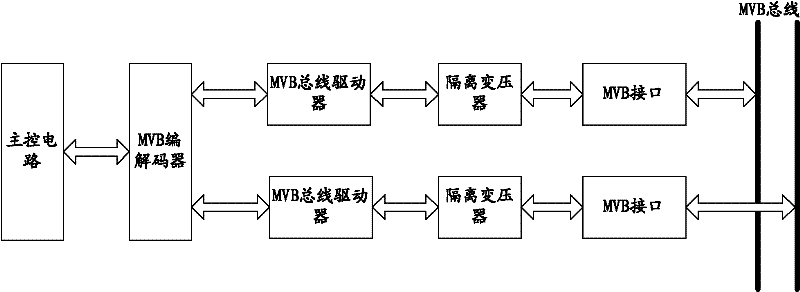

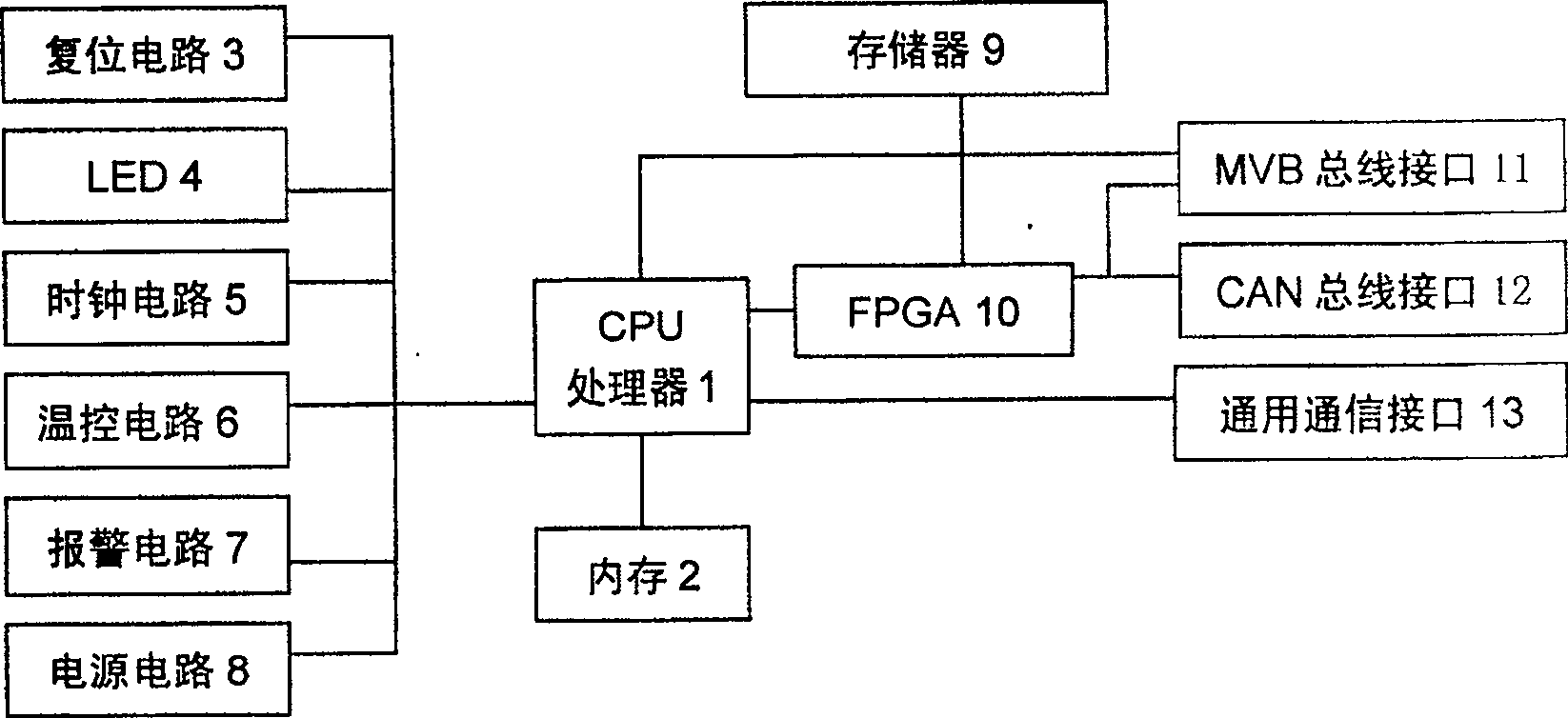

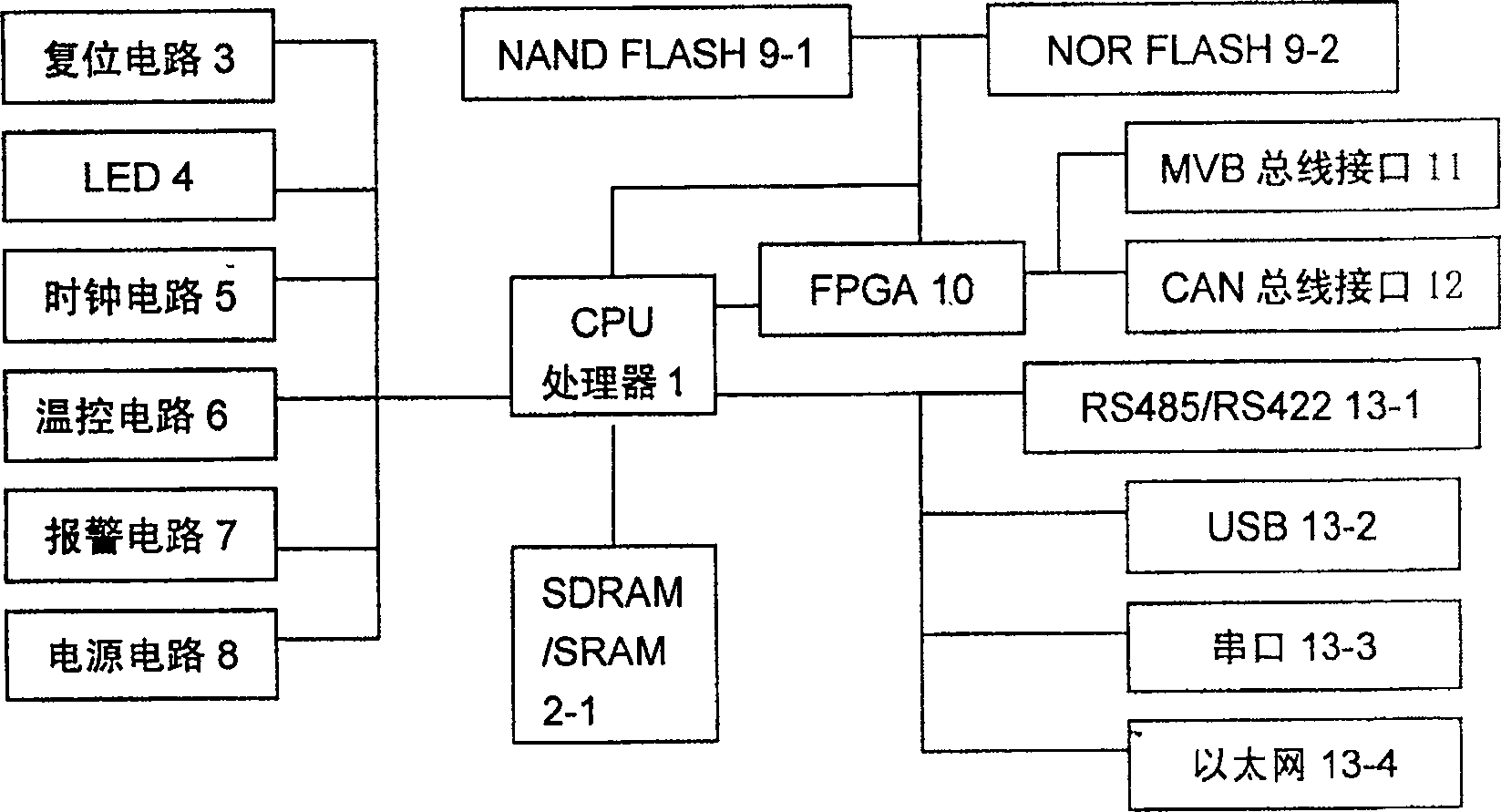

Multi-bus automobile communication control module based on TCN

ActiveCN100469035CEasy programmingImplement graphics programmingRailway signalling and safetyBus networksInternal memoryTemperature control

A vehicle communication control module of multibus based on TCN consists of CPU processor, internal memory, reset circuit, LED, clock circuit, temperature control circuit, alarm circuit and power supply circuit. It is featured as connecting CPU processor to FPGA being connected with storage and CAN bus interface as well as MVB bus interface, connecting MVB bus interface to CPU processor through buffer and connecting CPU processor to universal communication interface.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

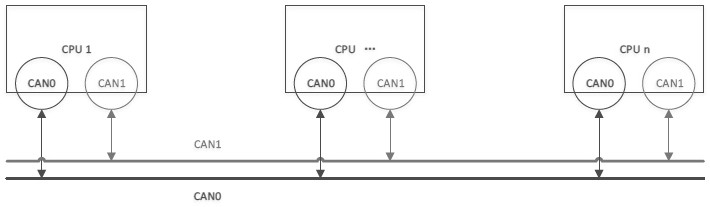

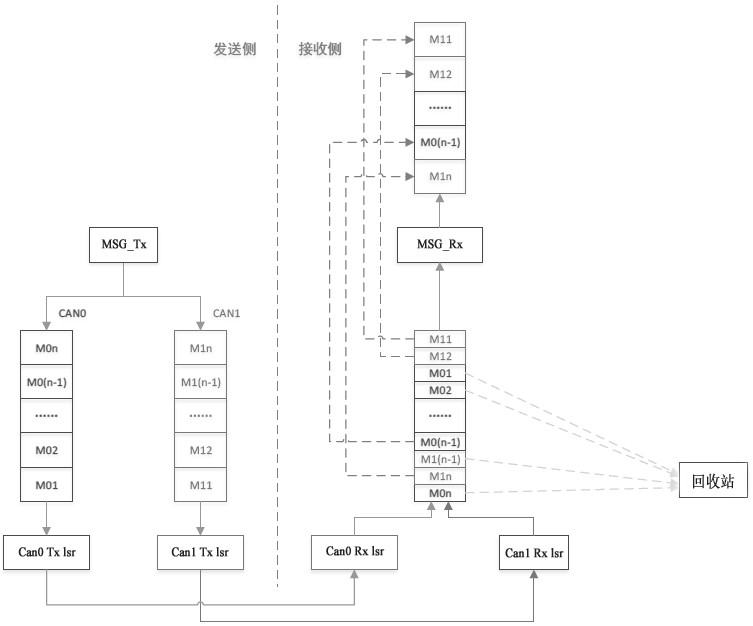

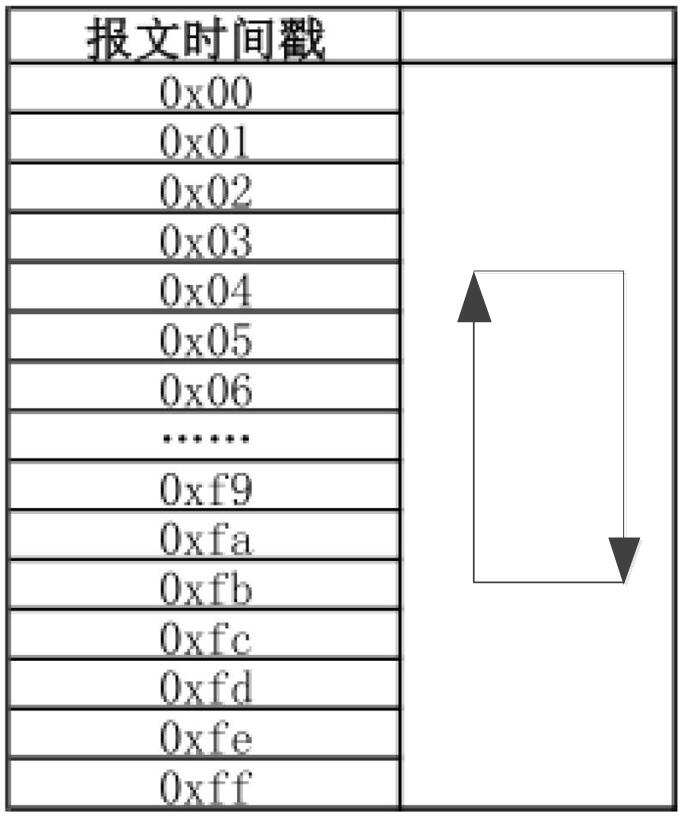

Redundant communication method for seamless switching of multiple communication buses

The invention discloses a redundant communication method for seamless switching of multiple communication buses. The number of the communication buses is at least two, each communication terminal is connected with each communication bus, and the redundant communication method comprises the following steps that S1, when a sender sends a message each time, the messages with the same content are pressed into a message sending queue of each communication bus at the same time; S2, each communication bus takes data from the message sending queue of the communication bus and sends the data; and S3, the receiver puts the messages received through each communication bus into the same queue, and for a plurality of mutually redundant messages with the same content, the system uses the first arrived message and discards the later arrived redundant message. During multi-bus switching, bus communication message 'zero' loss, continuous communication data, no data loss and no data repetition can be achieved, so that multi-communication bus seamless switching is realized, and the safety, reliability and availability of a traffic control system are improved.

Owner:CHENGDU YUNDA TECH CO LTD

Data management method and system based on soft PLC

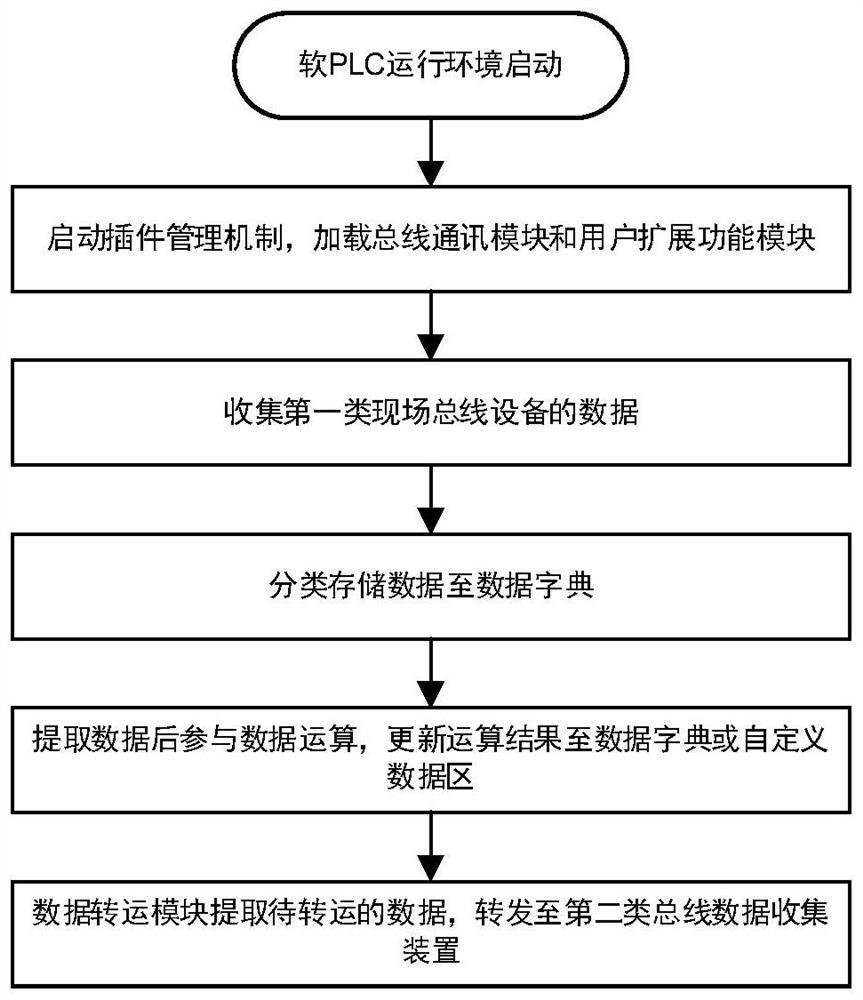

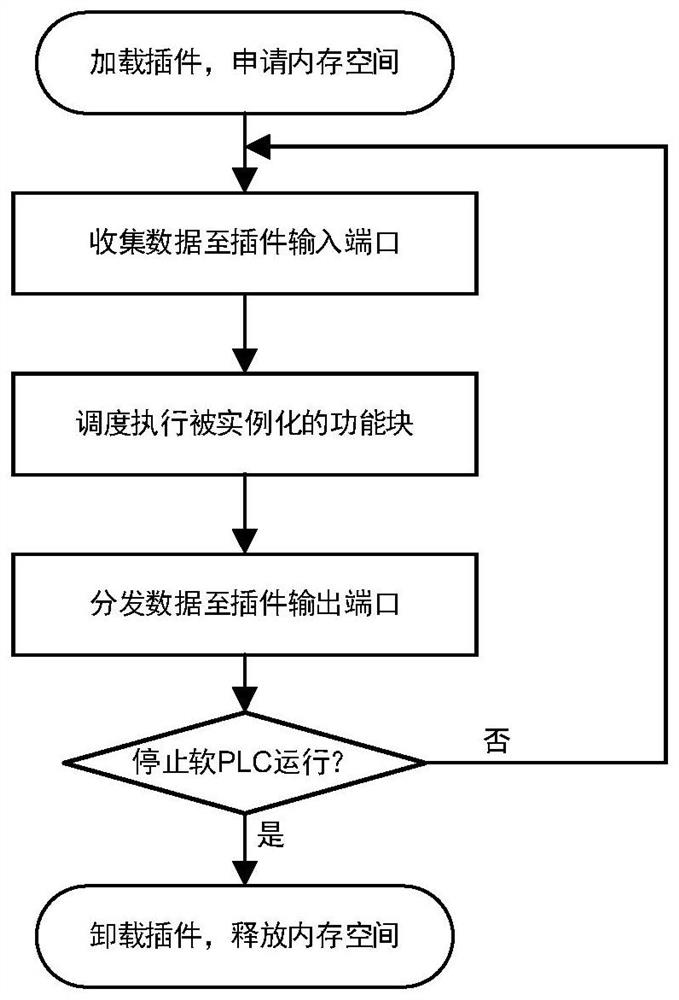

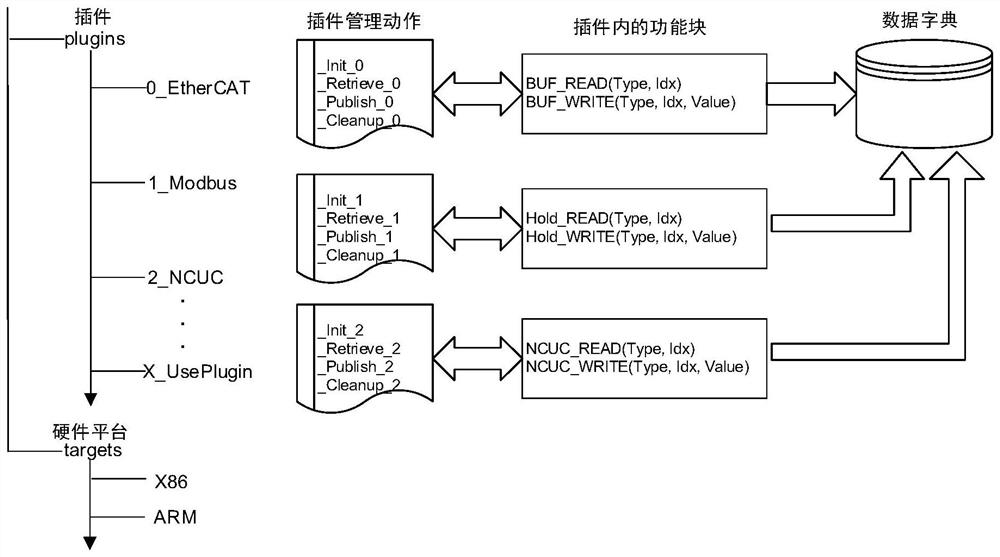

PendingCN114721736AIncrease flexibilityOvercome the disadvantage of poor flexibilityProgram initiation/switchingResource allocationData acquisitionOperability

The invention discloses a data management method and system based on a soft PLC, and the method comprises the steps: enabling the soft PLC to be embedded with a plug-in management mechanism, and loading a communication module of a plurality of bus types and a user extension function module; collecting data of the first type of field bus equipment, and storing the data in a data dictionary in a classified manner; data to be processed is extracted from the data dictionary, after a data processing function is executed, an operation result is updated to the data dictionary or a self-defined global data storage area according to the attribute of the data operation result, and then the operation result is forwarded to a second-class bus data collection device or localized storage; and repeating the steps, acquiring the first type of bus data, processing and transferring a processing result to the second type of bus data collection device or storing the processing result in a local file. According to the method, expandability and operability of multi-bus data management are considered, and through a plug-in management mechanism and in combination with the programmable characteristics of a data dictionary and a soft PLC, the method better meets the full-process requirements of data acquisition, processing and distribution.

Owner:HUAZHONG UNIV OF SCI & TECH

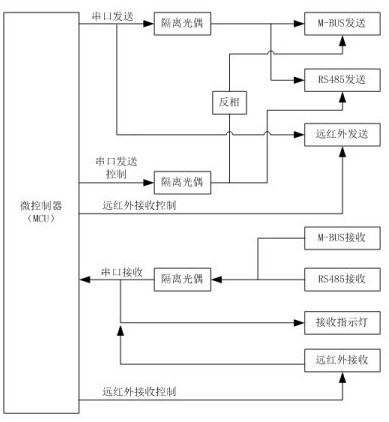

Multi-bus and multi-channel interface realized in single serial port multiplexing mode

The invention discloses a multi-bus and multi-channel interface realized in a single serial port multiplexing mode and relates to the technical field of communication interface circuits of data acquisition terminals. The multi-bus and multi-channel interface comprises a data acquisition terminal communication interface circuit for M_BUS, RS485 bus and far infrared communication. The M_BUS and RS485 multi-bus data acquisition interface is realized in the single serial port multiplexing mode, and meanwhile, an integrated design of a far infrared communication interface is realized in the singleserial port multiplexing mode, and communication with handheld far infrared communication equipment is realized; only one serial communication interface of a microcontroller is used for realizing theinterface circuit, and therefore, the circuit is simple, the number of peripheral devices is small, the cost is low; under the control of the interface control circuit, when the M_BUS, the RS485 bus and far infrared communication channels work, the data sending state and the data receiving state are independent of each other and do not interfere with each other, communication is stable and reliable, and full verification is achieved in data collection engineering.

Owner:湖南慧明谦信息技术有限公司

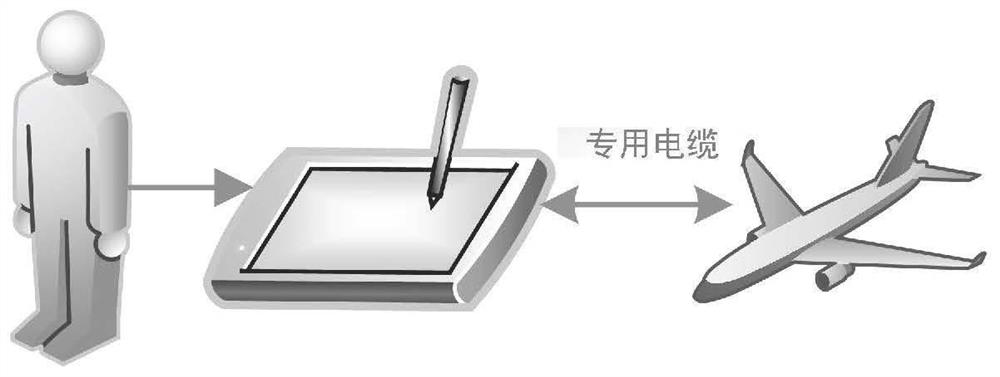

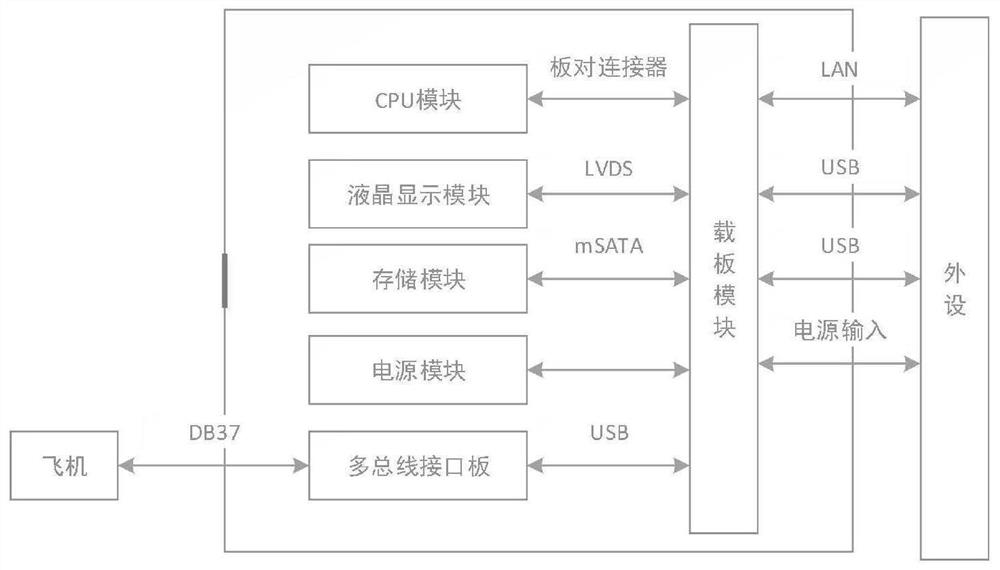

Portable multi-bus test equipment

The invention relates to the field of aircraft test equipment, in particular to portable multi-bus test equipment, which comprises a CPU (central processing unit) module and further comprises: a reinforced tablet personal computer serving as an upper computer for achieving data input of a user; and a multi-bus interface board which is communicated with the reinforced tablet computer through a USB (Universal Serial Bus), serves as a lower computer for achieving equipment functions, and is used for achieving protocol processing of various buses, controlling the various buses connected with the multi-bus interface board, completing interaction with an upper computer and controlling protocol analysis.According to the invention, an infield can be used for bus-related tests; the test equipment is miniaturized, modularized and universalized, the cost is reduced, a good test platform is provided for an airplane, the multi-bus board can serve as an interface board for bus test, the cost performance is high, the system integration degree is high, the mode of the built-in interface board based on the USB bus is adopted, and the advantages of portability and integration degree are both considered.

Owner:国营芜湖机械厂

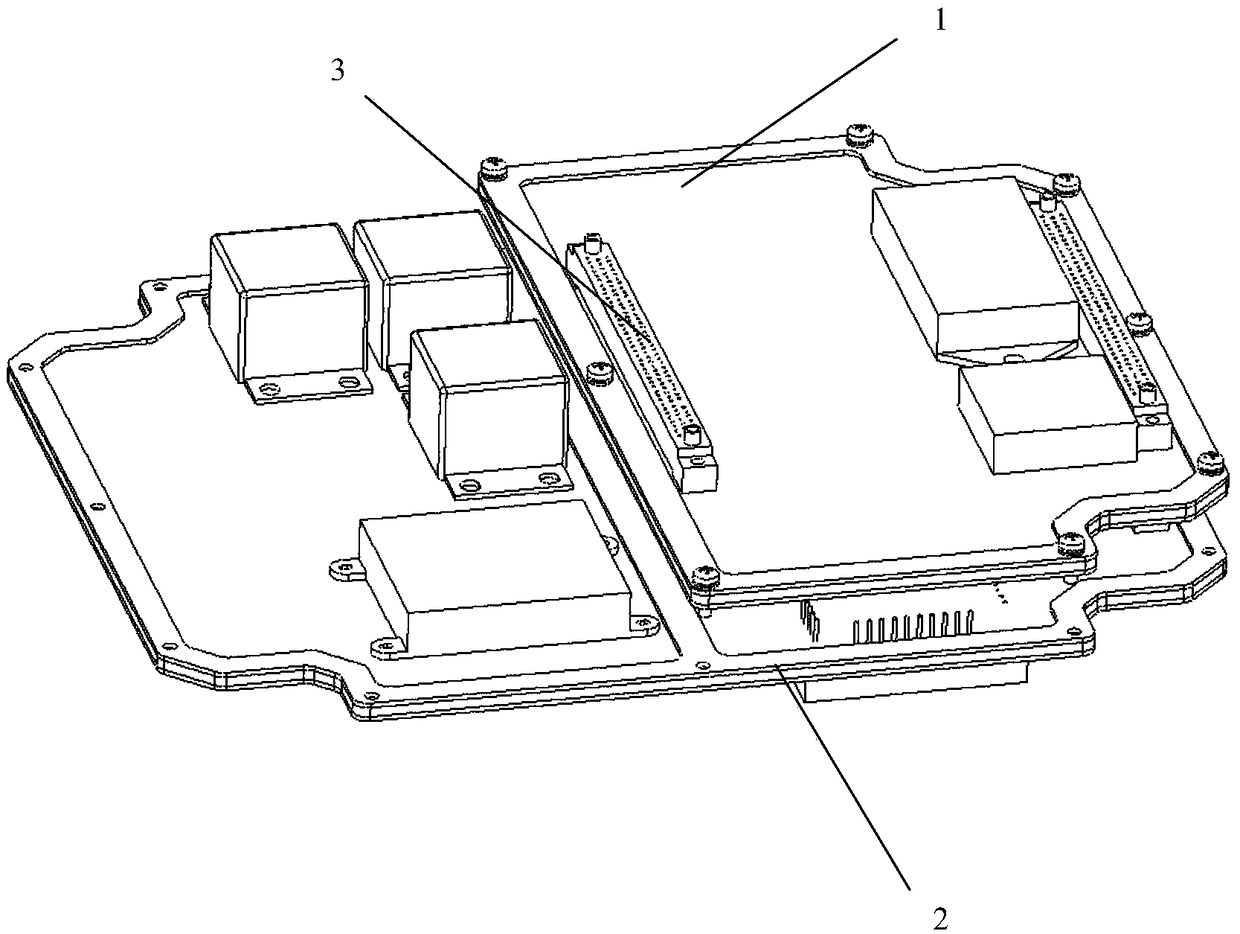

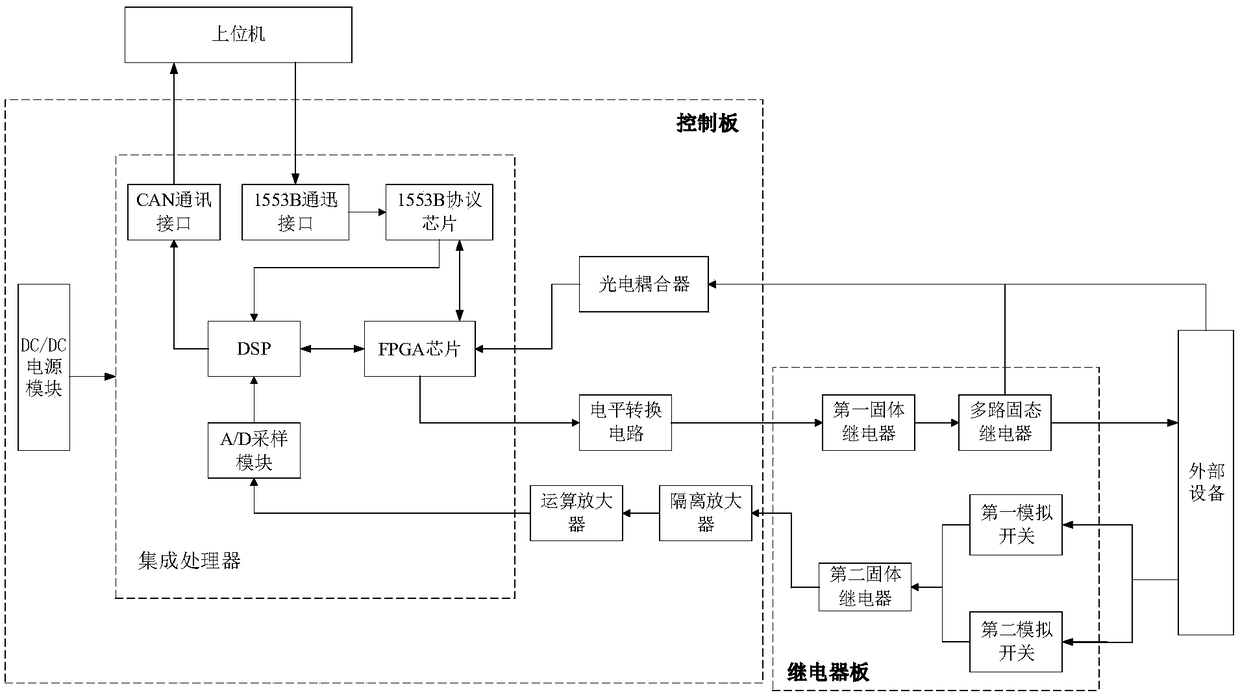

Small universal multi-bus control device

ActiveCN108710327AHighly integratedImprove use reliabilityProgramme controlComputer controlTransmission channelEngineering

The invention discloses a small universal multi-bus control device. The small universal multi-bus control device includes a control board and a relay board; the control board and the relay board adopta vertical stacking structure, and the board layers are connected by a connector; the relay board comprises a first solid state relay, a multi-channel solid state relay, a second solid state relay, and at least one analog switch; a first end of the first solid state relay is connected to an output end of the control board, and a second end of the first solid state relay is connected to an input end of the multi-channel solid state relay; a first output end of the multi-channel solid state relay serves as a first external device interface of the relay board, and a second output end of the multi-channel solid state relay is connected to an input end of the control board; a first end of the second solid state relay is connected to a sampling end of the control board, and a second end of thesecond solid state relay is connected to an output end of the analog switch; and an input end of the analog switch serves as a second external device interface of the relay board. The invention increases the communication type and the number of signal transmission channels under the premise of reducing the size of the device, so that the device has versatility, the device utilization rate is improved, and the cost is saved.

Owner:HUBEI SANJIANG AEROSPACE WANFENG TECH DEV

Memory/logic conjugate system

InactiveUS8305789B2Reduce system costImprove performanceDigital storageElectric digital data processingElectricityCrossbar switch

A bandwidth bottleneck occurs because a crossbar switch is used to cope with an increase in scale. A memory / logic conjugate system according to the present invention, a plurality of cluster memory chips each including a plurality of cluster memories 20 including basic cells 10 arranged in a cluster, the basic cell 10 including a memory circuit, and a controller chip that controls the plurality of cluster memories are three-dimensionally stacked, the plurality of cluster memories 20 located along the stacking direction of the plurality of cluster memory chips and the controller chip are electrically coupled to the controller chip via a multibus 11 including a through-via, an arbitrary one of the basic cells 10 is directly accessed through the multibus 11 from the controller chip so that truth value data is written therein, and whereby the arbitrary basic cell 10 is switched to a logic circuit as conjugate.

Owner:OTSUKA KANJI +7