Fast generating method of user-customizable PLD (programmable logic device) layouts

A programming logic and user-customized technology, applied in the direction of instruments, special data processing applications, electrical digital data processing, etc., can solve problems such as low layout efficiency, insufficient FPGA IP cores to meet resource requirements, and long time required to generate layouts, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

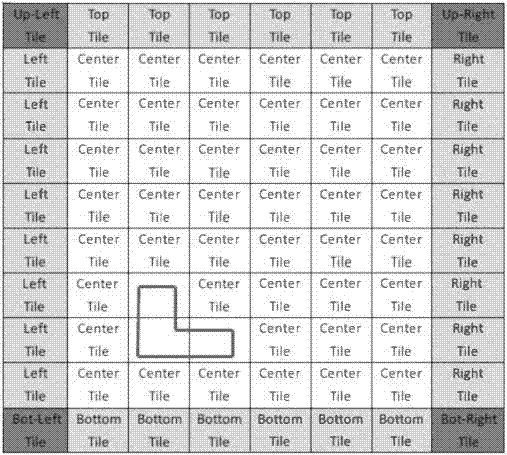

[0083] Since the layout of commercial FPGA chips is not public, we cannot obtain its layout files. Therefore, the present invention selects the cell layout of the FDP3P7 series FPGA chips developed by Fudan University ASIC and State Key Laboratory of Systems as an example, and illustrates how to utilize the method proposed by the present invention to generate a 16 x 20 array-scale FPGA that is set by a user territory.

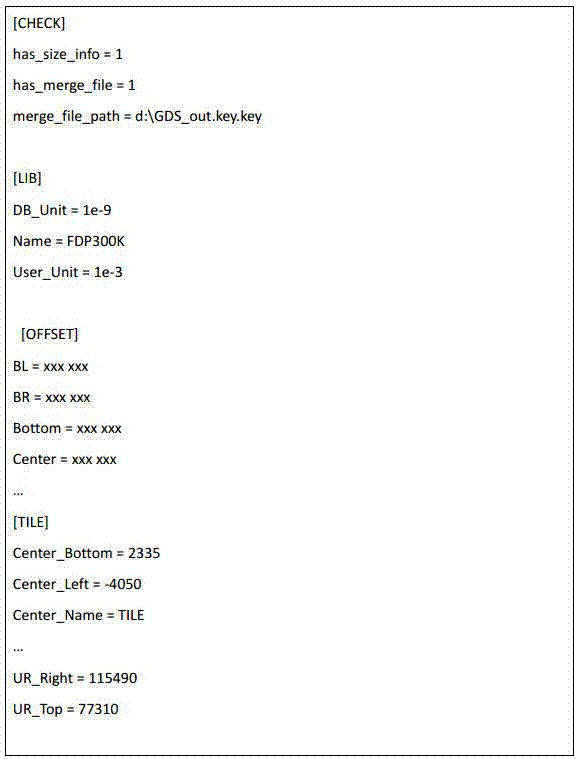

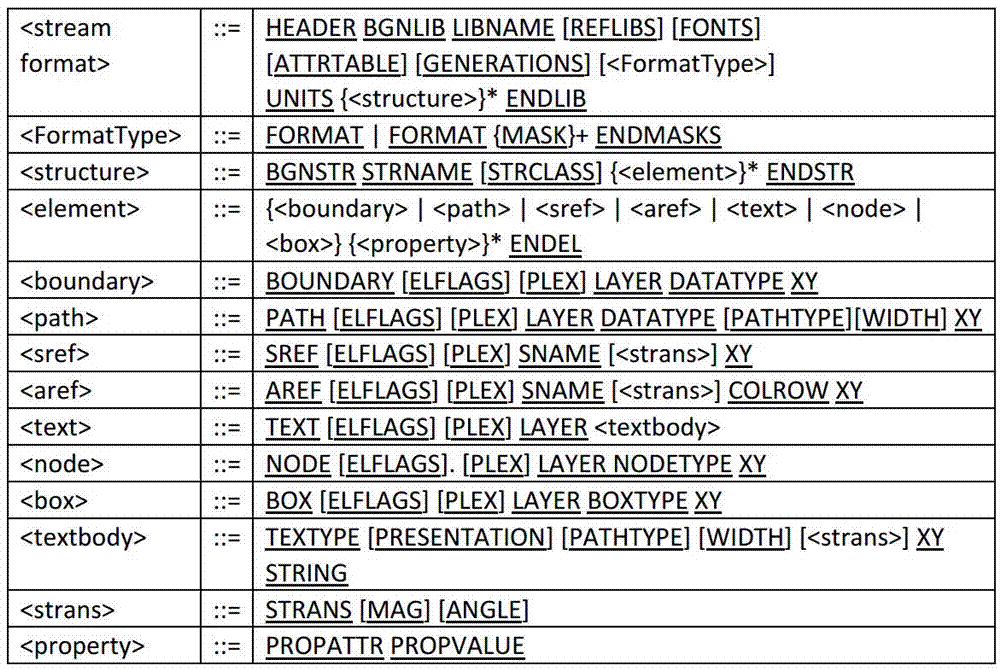

[0084] First, create a chip configuration file for the FDP3P7 FPGA chip, manually measure the position offset between each TILE, record it in the configuration file, and complete the recording of the [OFFSET] part, see figure 2 ;By recording the storage path of the 9 sub-layout files and recording them in the [TILE] section, the size of the 9 sub-layouts will be automatically calculated and saved to the configuration file when the program is running, so as to avoid repeated calculations next time and speed up the generation speed; The information in other par...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More