High-voltage electronic static discharge (ESD) protection device with positive-negative (PN) junction auxiliary trigger silicon controlled rectifier-laterally diffused metal oxide semiconductor (SCR-LDMOS) structure

A SCR-LDMOS, ESD protection technology, applied in the field of electronics, can solve problems such as latch-up, achieve the effect of avoiding the latch-up effect, improving ESD protection capability, and improving ESD robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

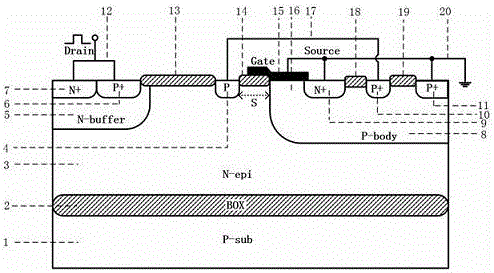

[0016] Below in conjunction with accompanying drawing, technical scheme of the present invention is described in further detail:

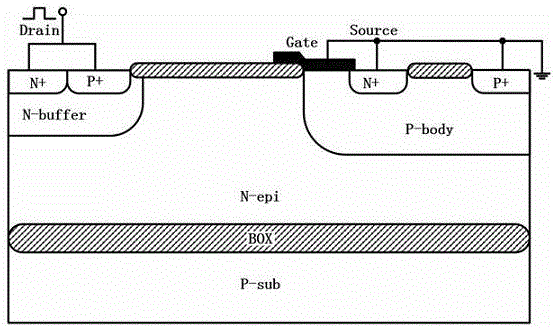

[0017] as attached figure 2 Shown is a high-voltage ESD protection device with a PN junction-assisted trigger SCR-LDMOS structure, including a P-type silicon substrate 1, a buried oxide layer 2 is provided on the P-type silicon substrate, and a drift region 3 is provided on the buried oxide layer. An N-buffer region 5, a P region 4, and a P-body region 8 are sequentially provided above the drift region from left to right; the N-buffer region 5 is sequentially provided with a first drain heavily doped N+ region 7 and the first drain heavily doped P+ region 6; the P-body region 8 is provided with a second source heavily doped N+ region 9 and a second source heavily doped P+ region 10 in sequence from left to right and the third source heavily doped P+ region 11; a first thin oxide layer 13 is provided between the first drain heavily doped P+ region...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More