Integrated power device on silicon on insulator (SOI) layer for negative supply voltage

A technology of negative power supply voltage and integrated power, which is applied in the field of semiconductor power devices, can solve the problems that cannot meet the requirements of the negative power supply voltage working environment, etc., and achieve the effects of low power consumption, reduced process difficulty and cost, and excellent performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

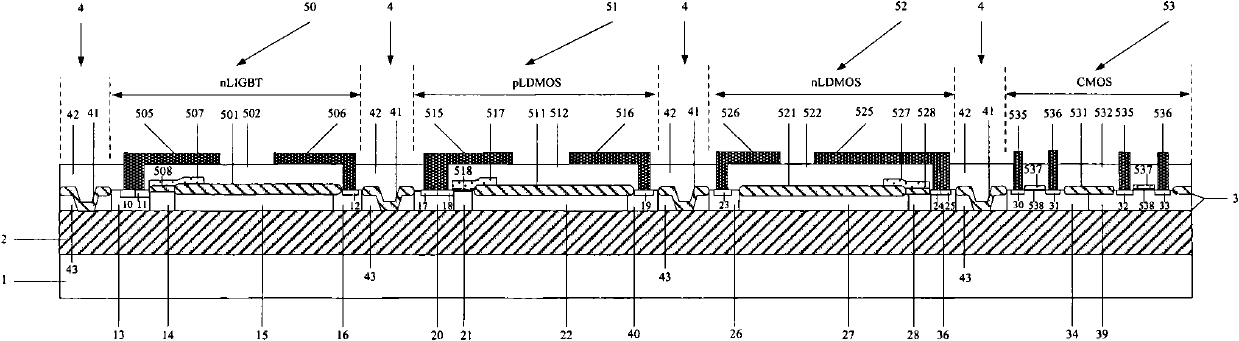

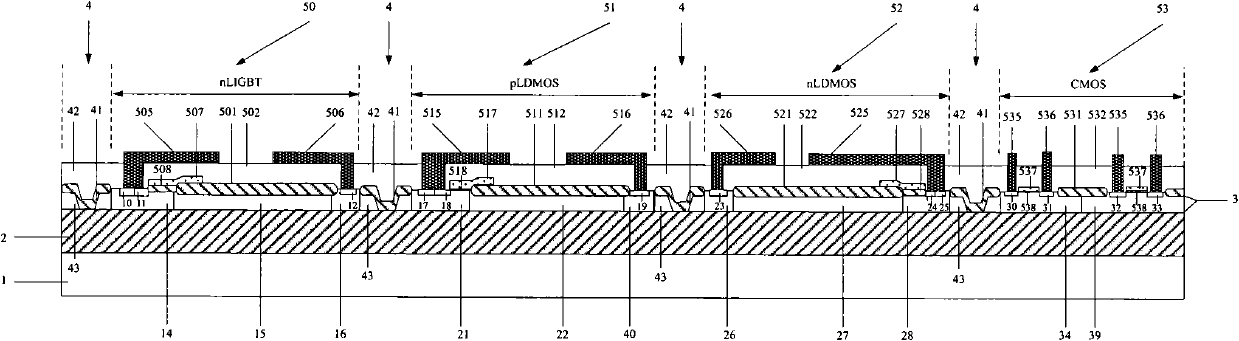

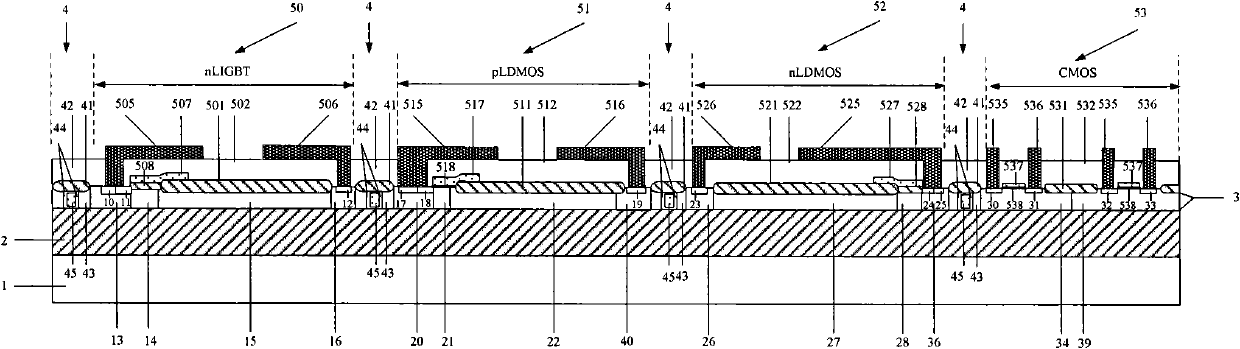

[0022] A thin-layer SOI integrated power device for negative supply voltages, such as Figure 1 to Figure 3 As shown, it includes substrate 1 , buried oxide layer 2 and SOI layer 3 . The buried oxide layer 2 is located between the substrate 1 and the SOI layer 3, and the SOI3 layer is a thin-layer semiconductor with a thickness of 0.5-3 μm. The SOI layer 3 is at least integrated with a high-voltage nLIGBT device (n-channel Lateral Insulated Gate Bipolar Transistors) 50, a high-voltage pLDMOS device (p-channel Lateral Double-diffused MOSFET) 51 and a high-voltage nLDMOS device (n-channel Lateral Double-diffused MOSFET) Two or three devices in MOSFET) 52. Different high-voltage devices are completely isolated by the buried oxide layer 2 and the dielectric isolation region 4 built on the buried oxide layer 2; Slot isolation technology is implemented.

[0023] The SOI layer of the high-voltage nLIGBT device 50 consists of a p-type body region 14, an n-type drift region 15, a p-t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Electric field strength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More