Anti-latch circuit and integrated circuit

A latching circuit, power supply voltage technology, applied in circuits, electrical components, electronic switches, etc., can solve problems such as burnout and circuit failure to work properly, and achieve the effect of preventing latchup effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0024] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

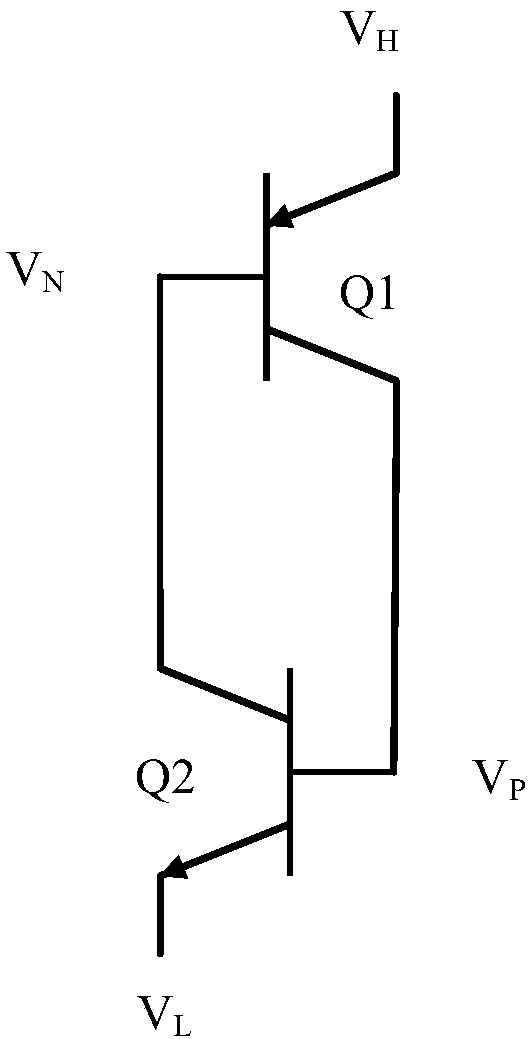

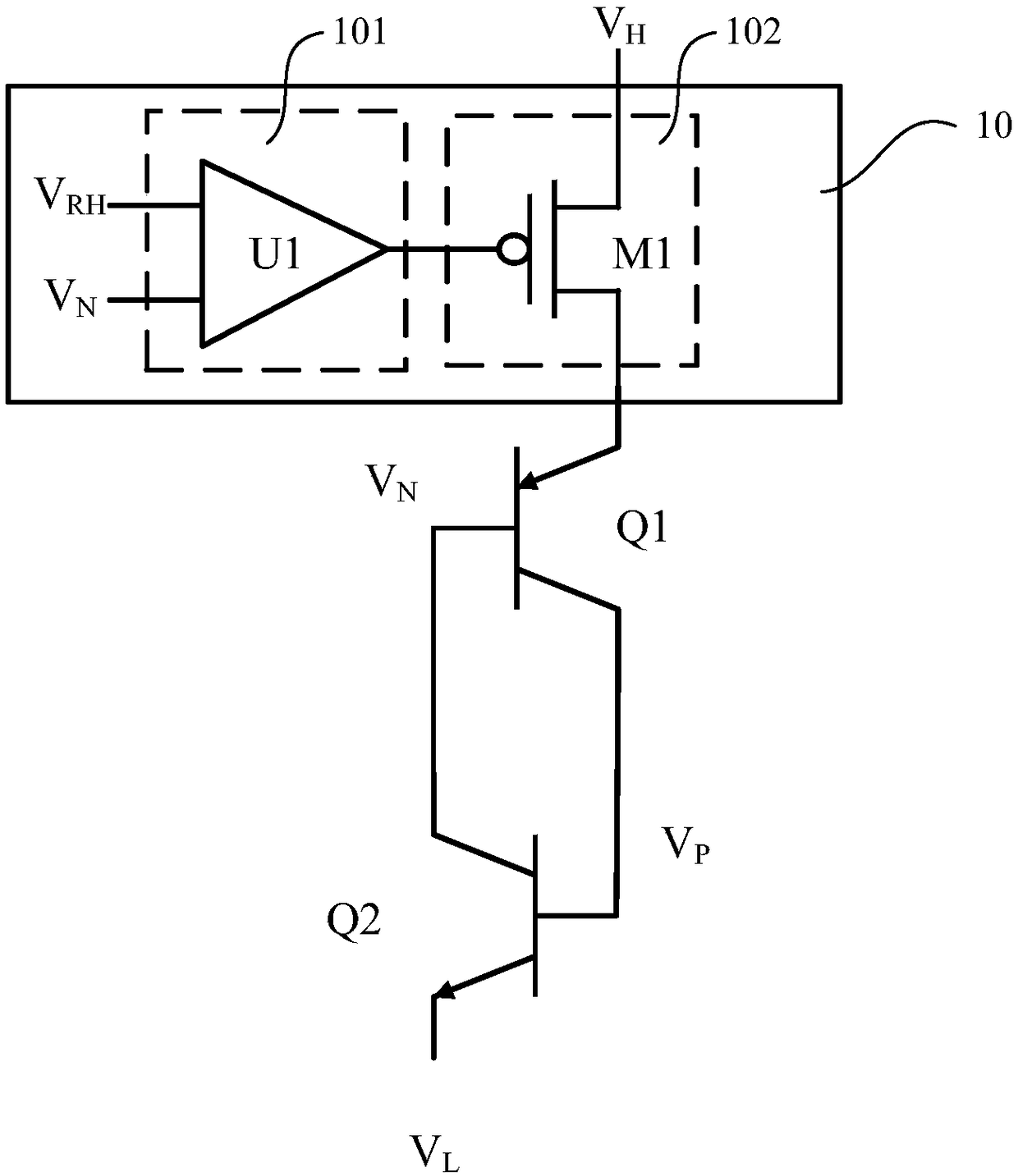

[0025] image 3 A circuit diagram of the anti-latch circuit provided by the first embodiment of the present invention is shown. Such as figure 1 As shown, the anti-latch circuit includes a first transistor Q1 and a second transistor Q2 and a control circuit 10 .

[0026] The first transistor Q1 has a control terminal, a first terminal and a second terminal, and the control terminal receives the first control voltage V N , the first terminal receives the first supply voltage V H .

[0027] Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More