Patents

Literature

300 results about "Impact ionization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Impact ionization is the process in a material by which one energetic charge carrier can lose energy by the creation of other charge carriers. For example, in semiconductors, an electron (or hole) with enough kinetic energy can knock a bound electron out of its bound state (in the valence band) and promote it to a state in the conduction band, creating an electron-hole pair. For carriers to have sufficient kinetic energy a sufficiently large electric field must be applied, in essence requiring a sufficiently large voltage but not necessarily a large current.

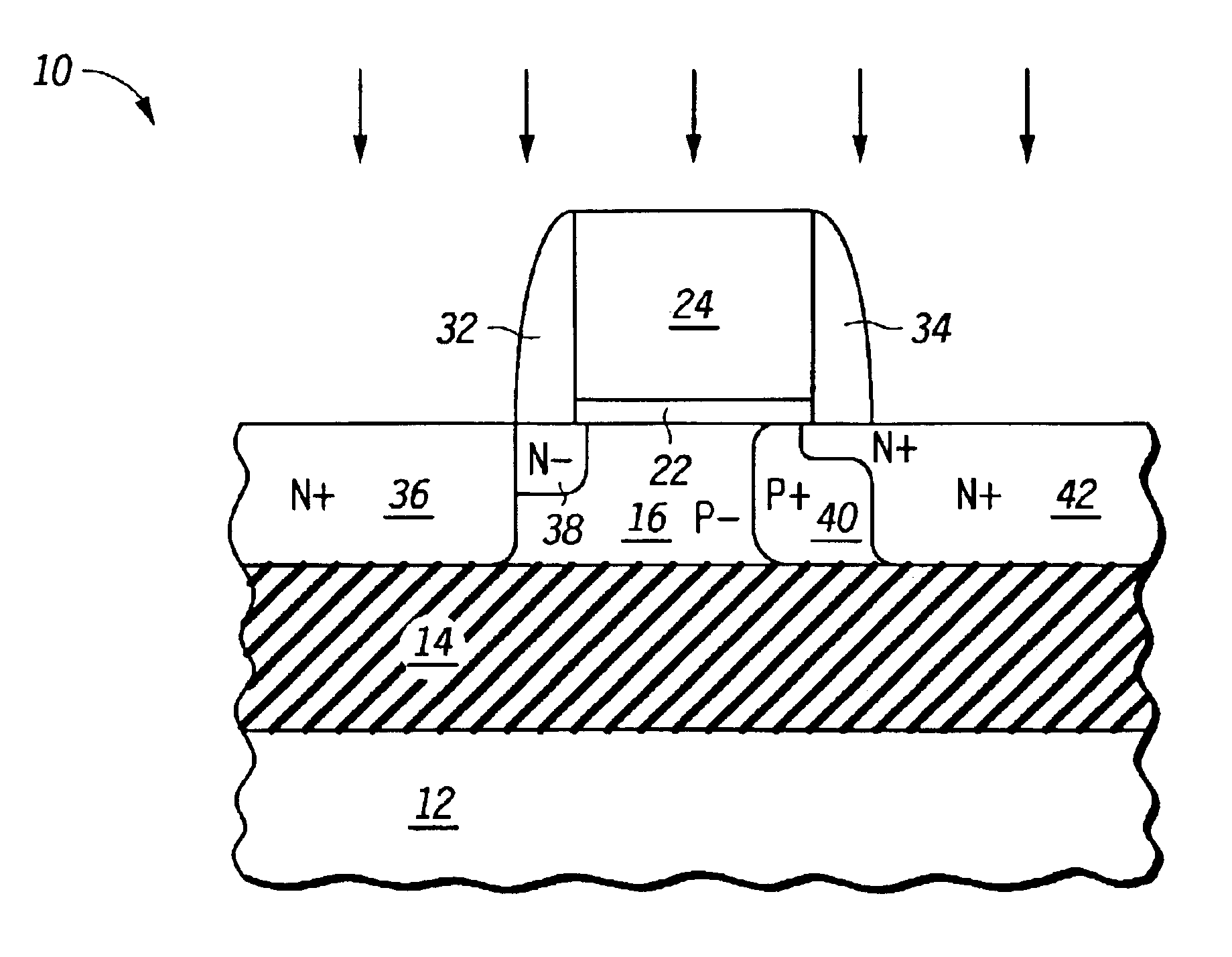

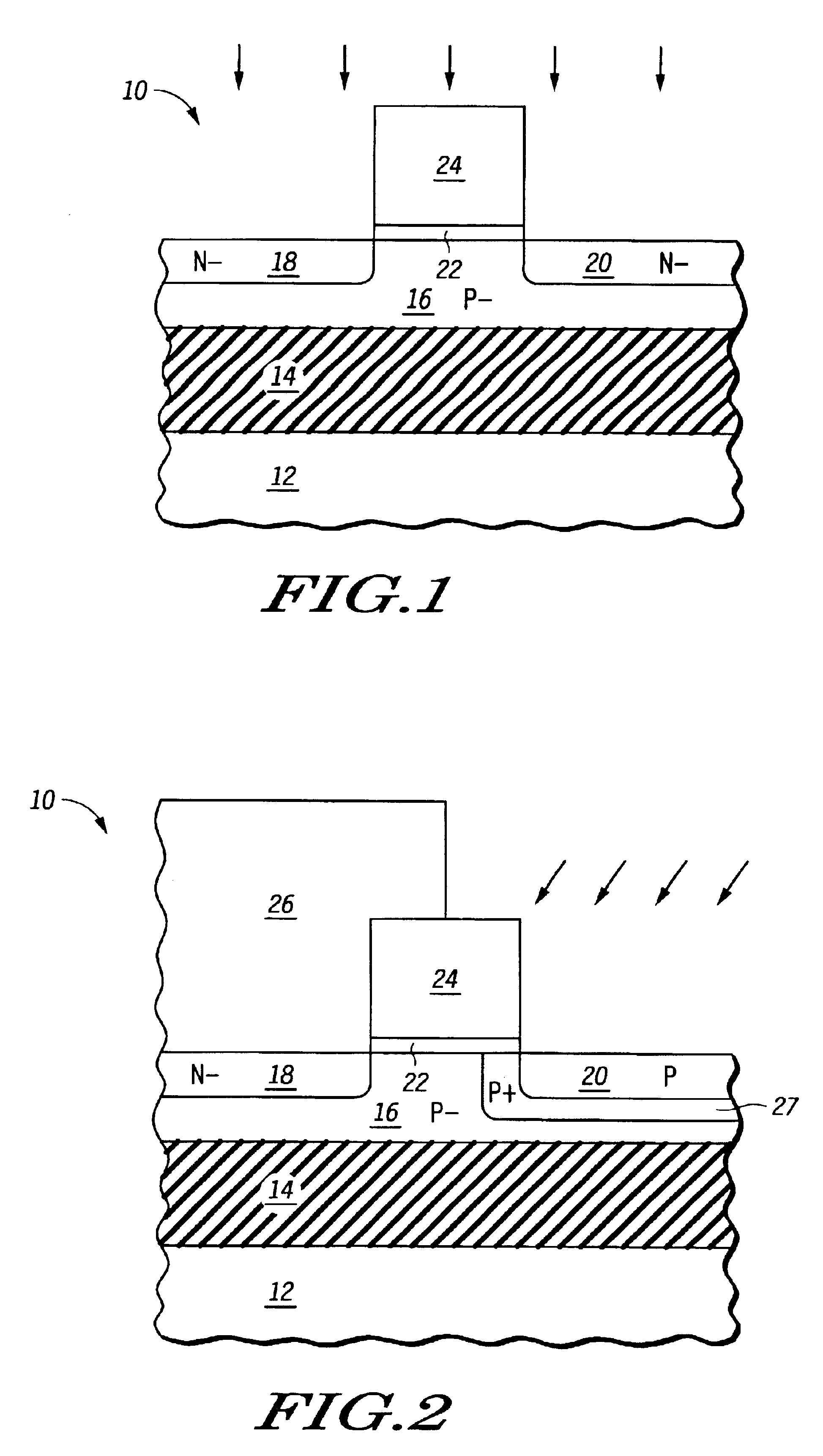

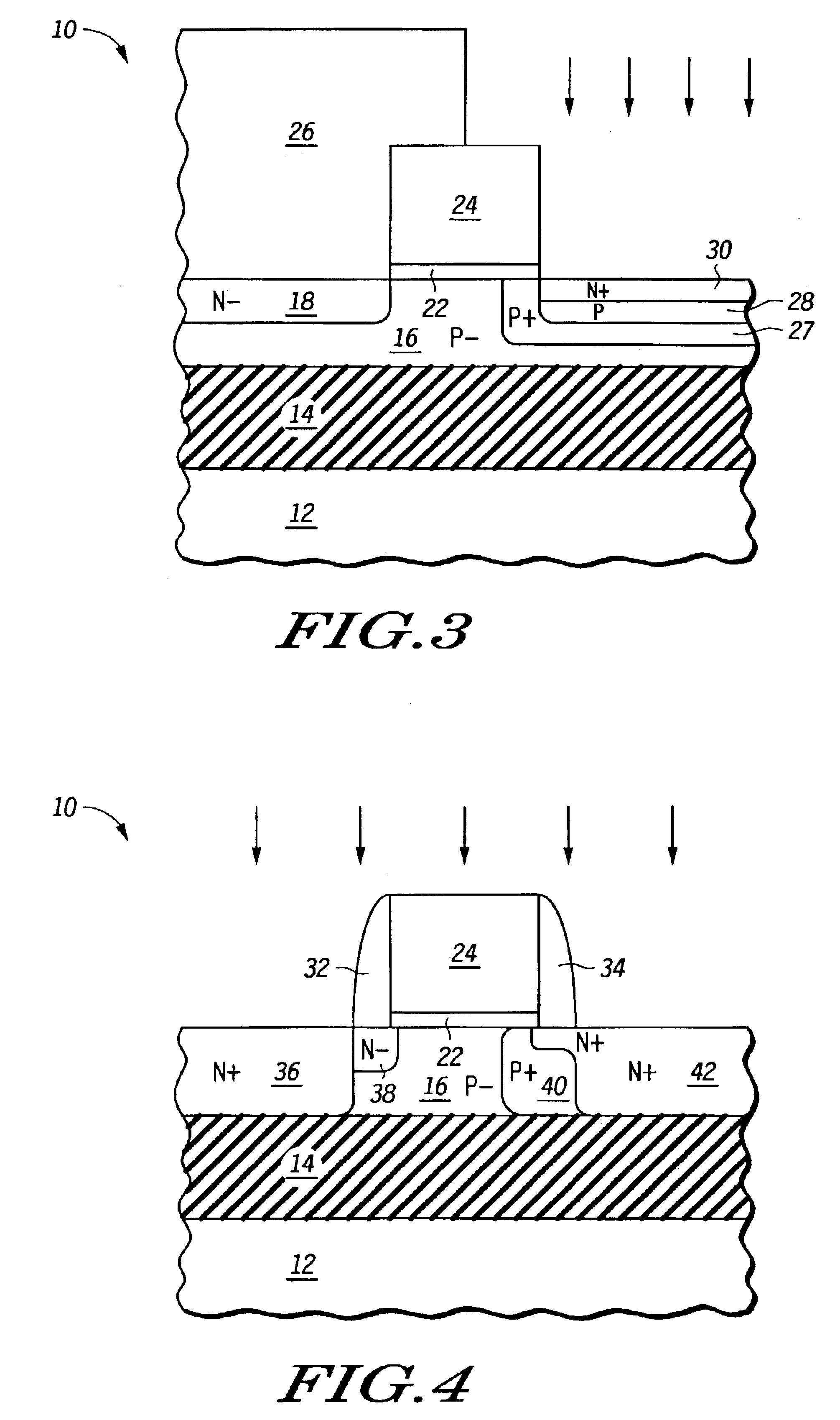

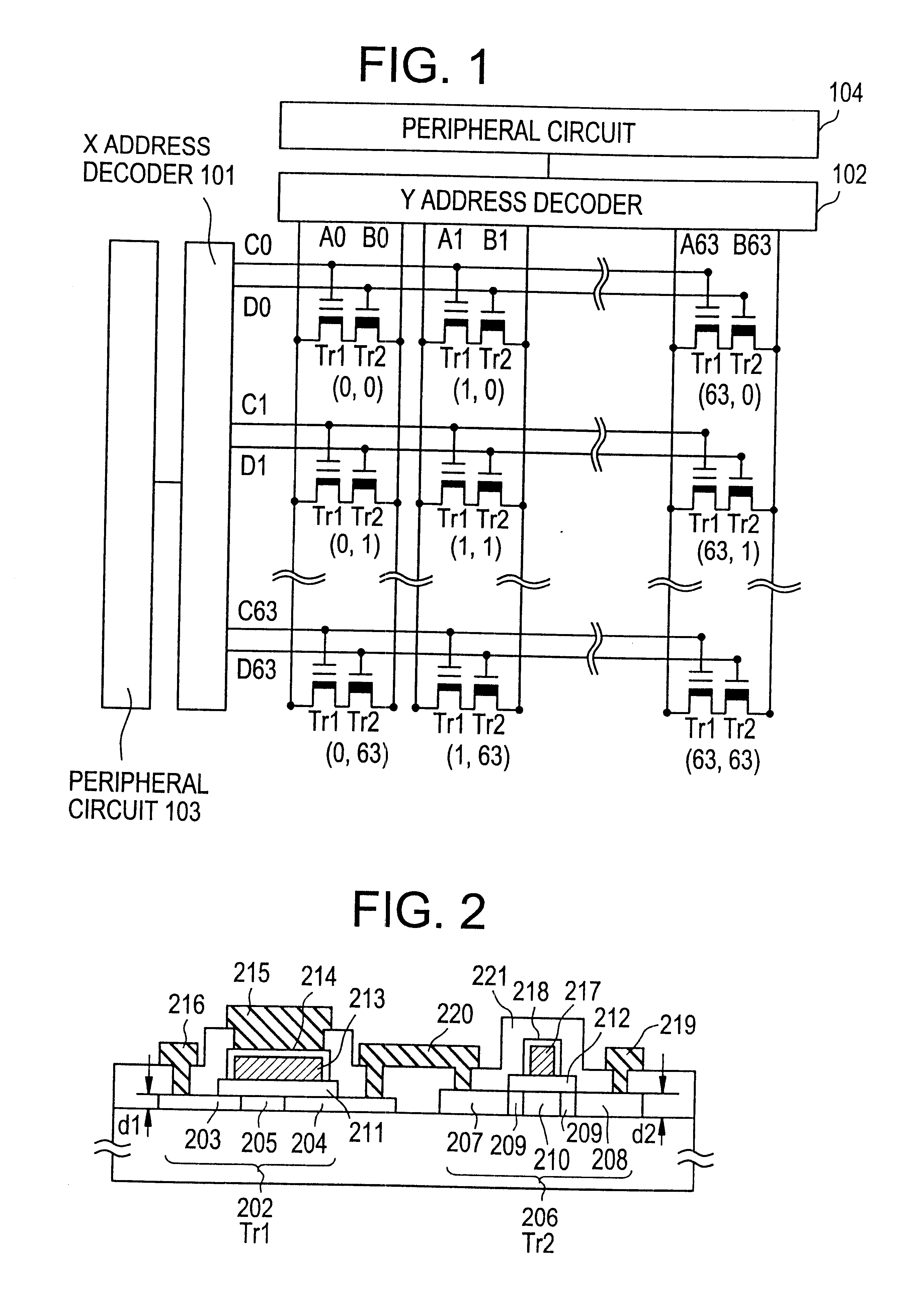

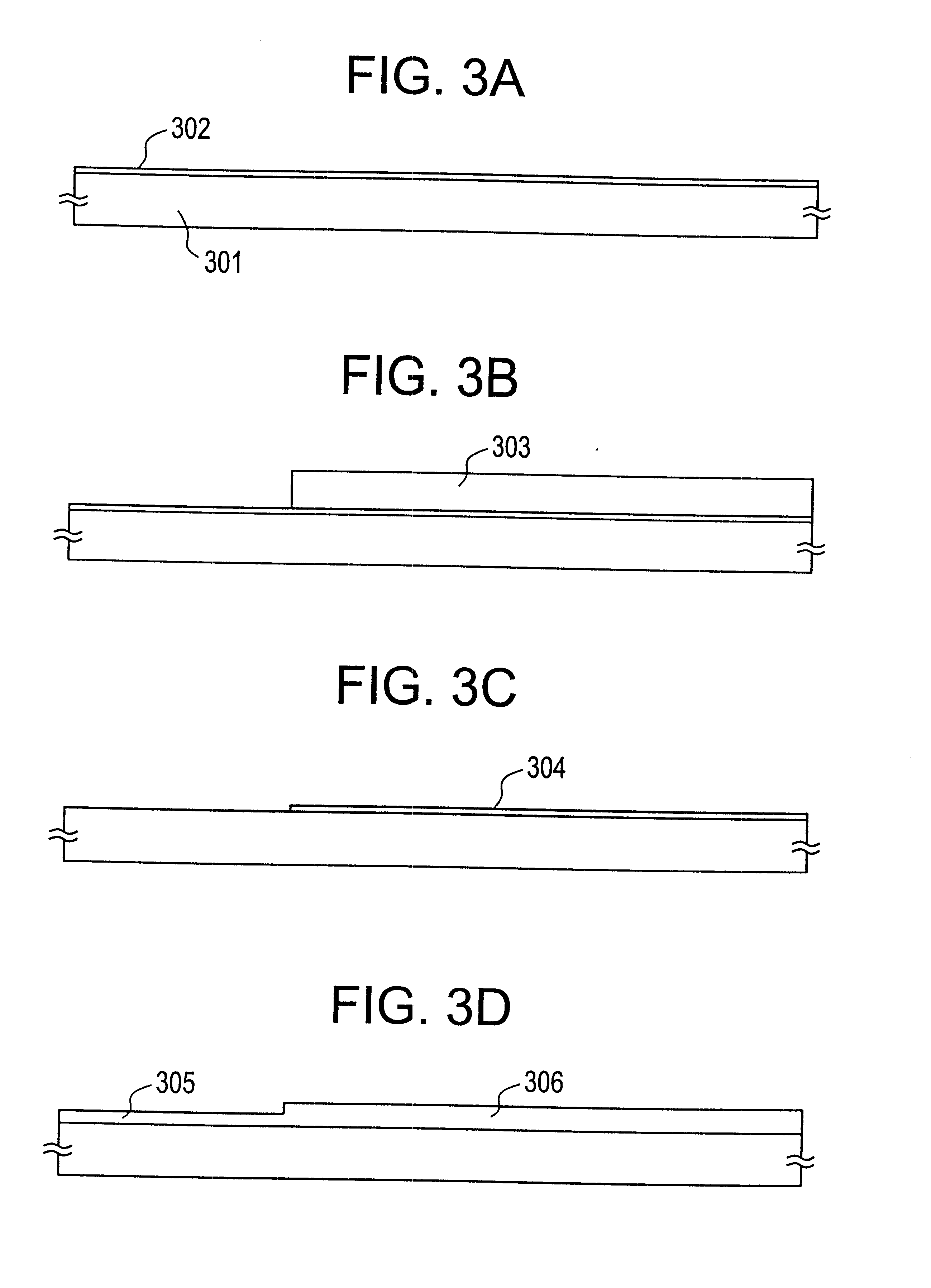

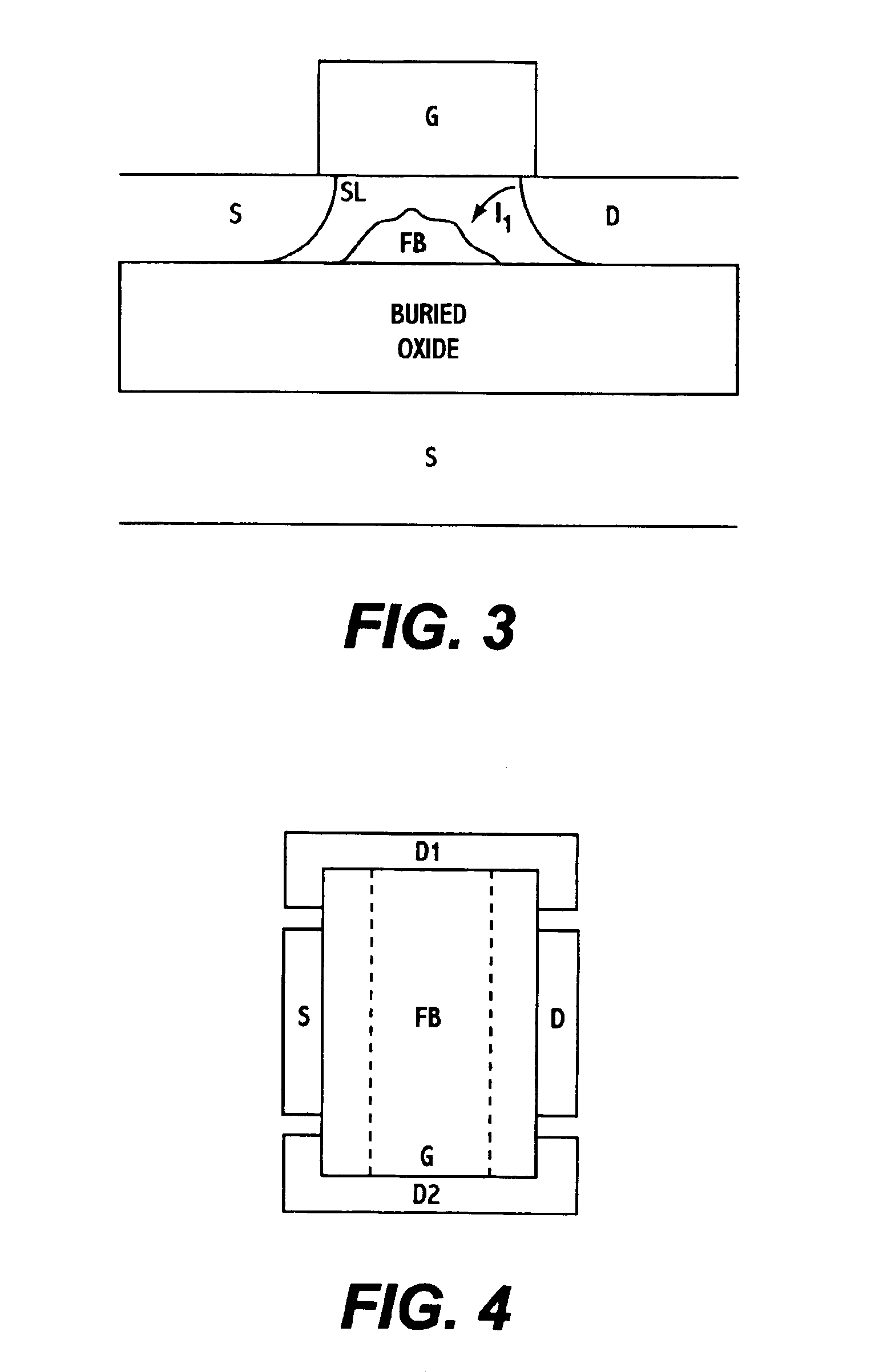

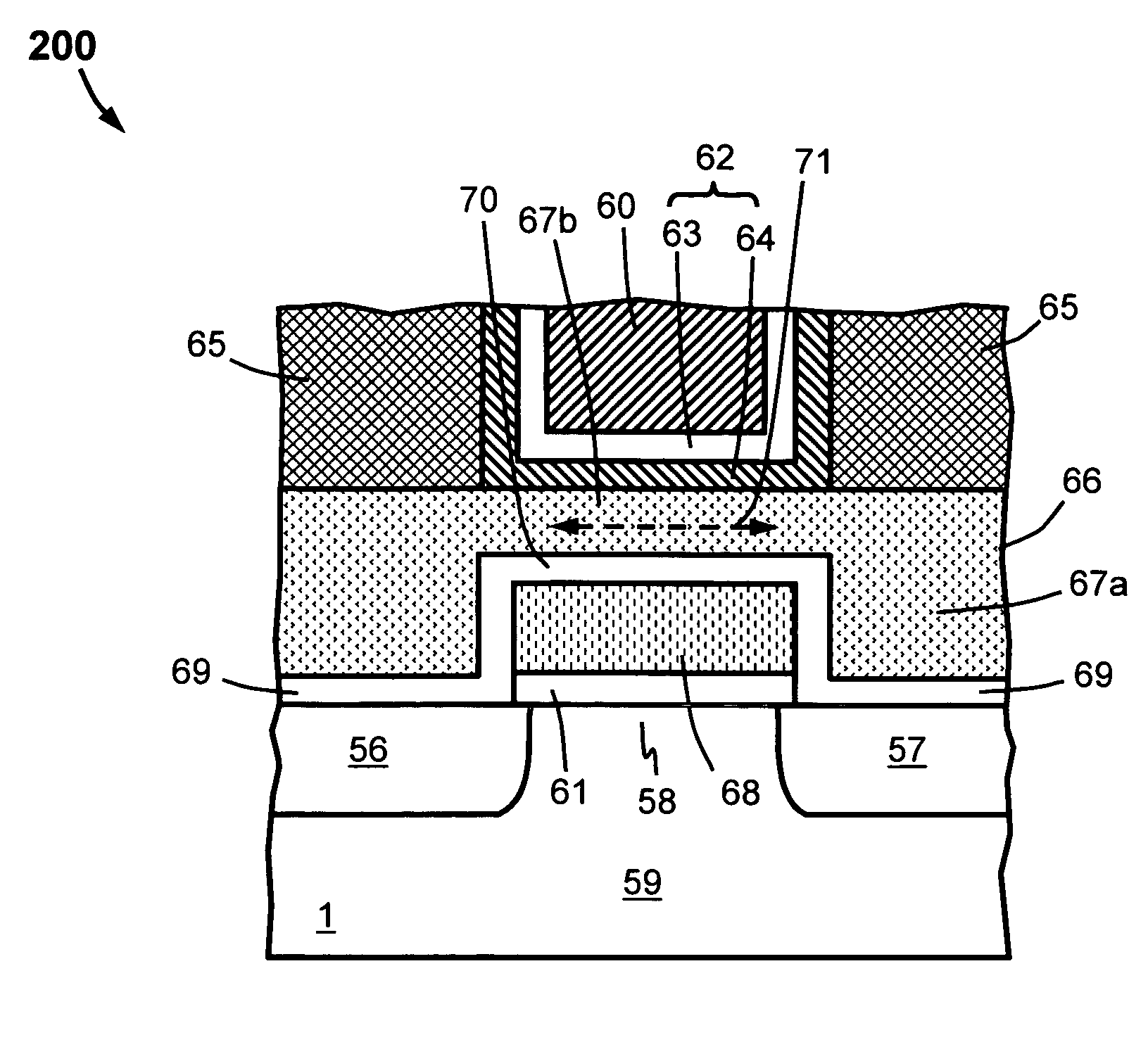

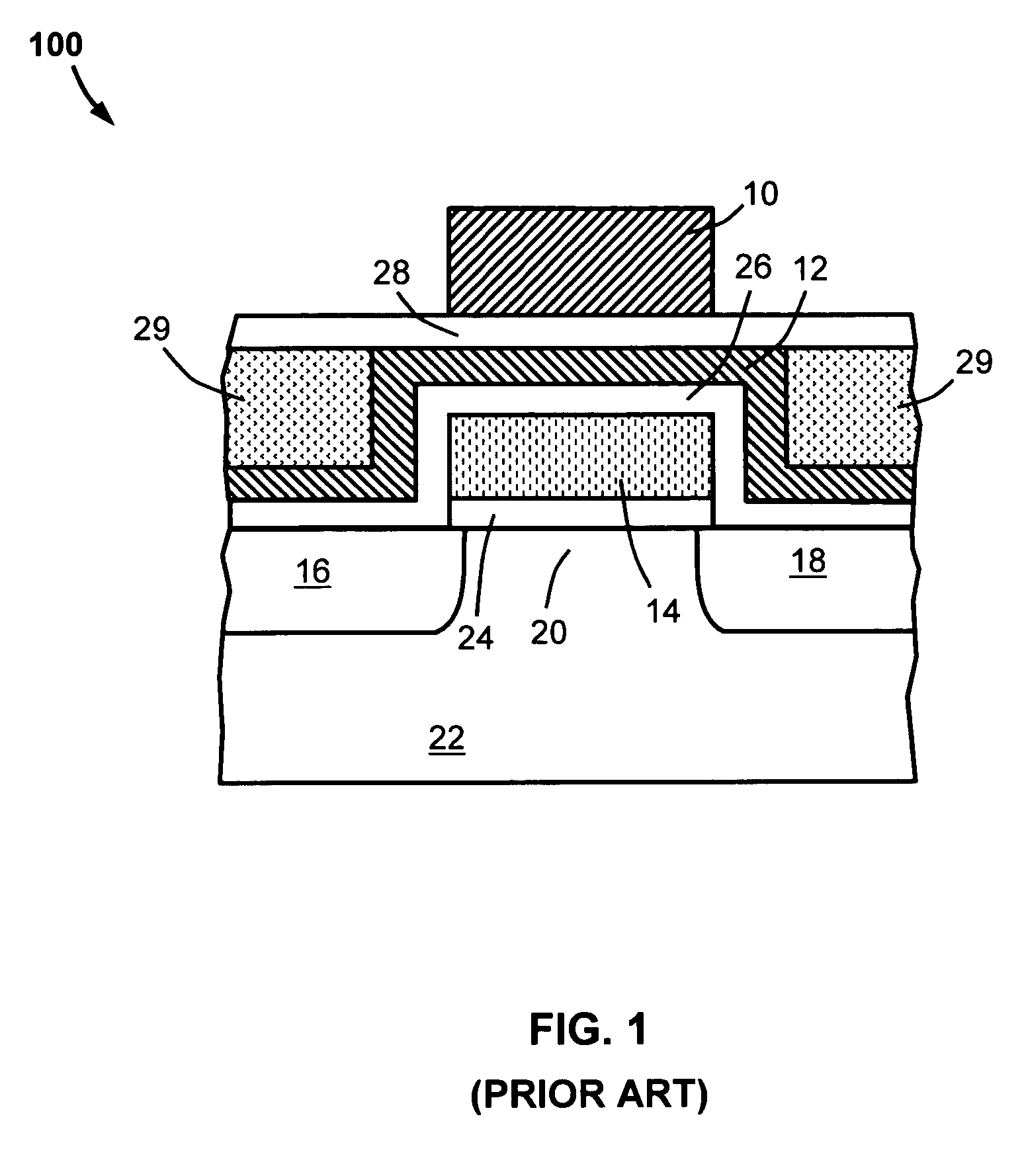

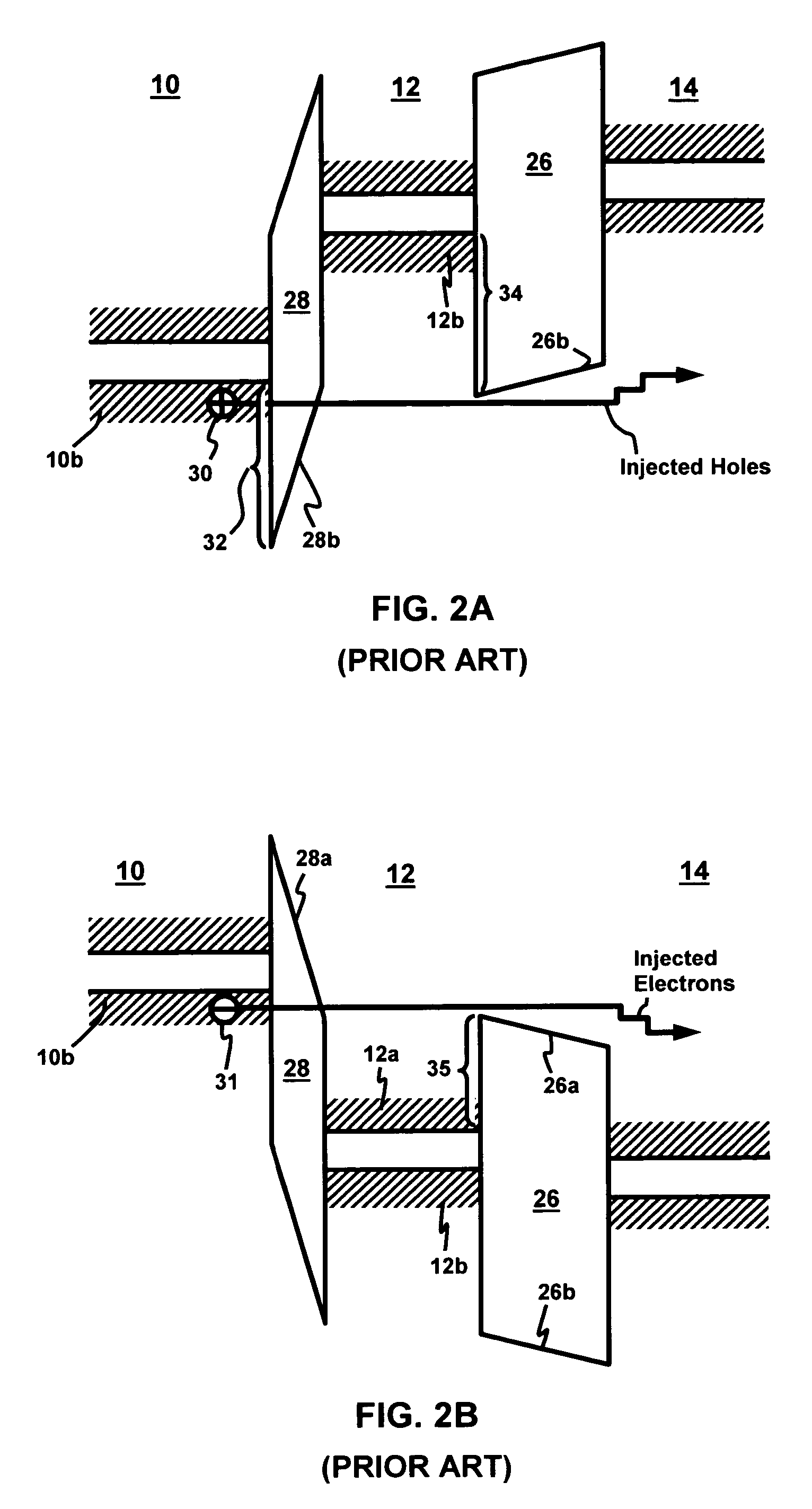

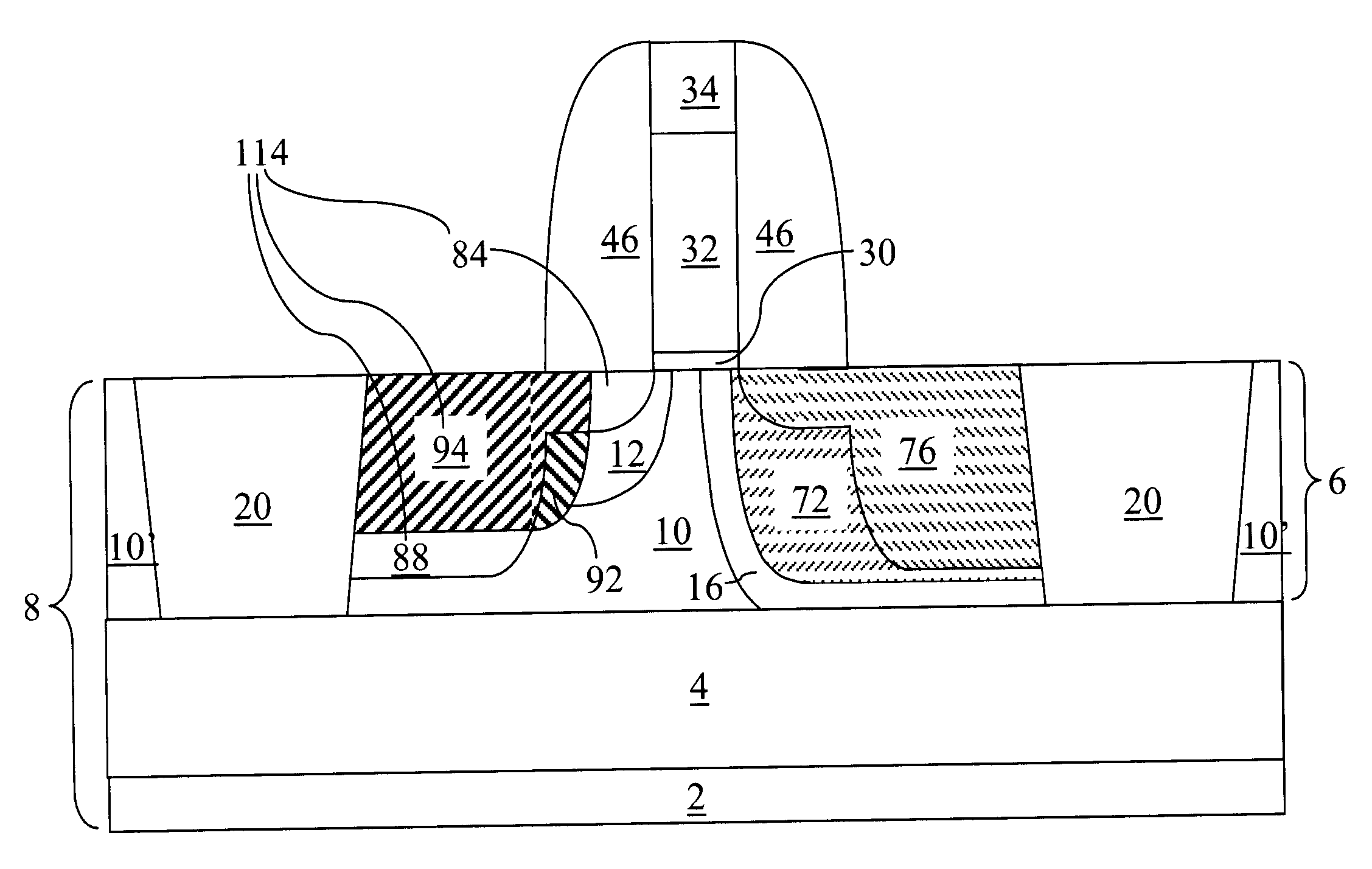

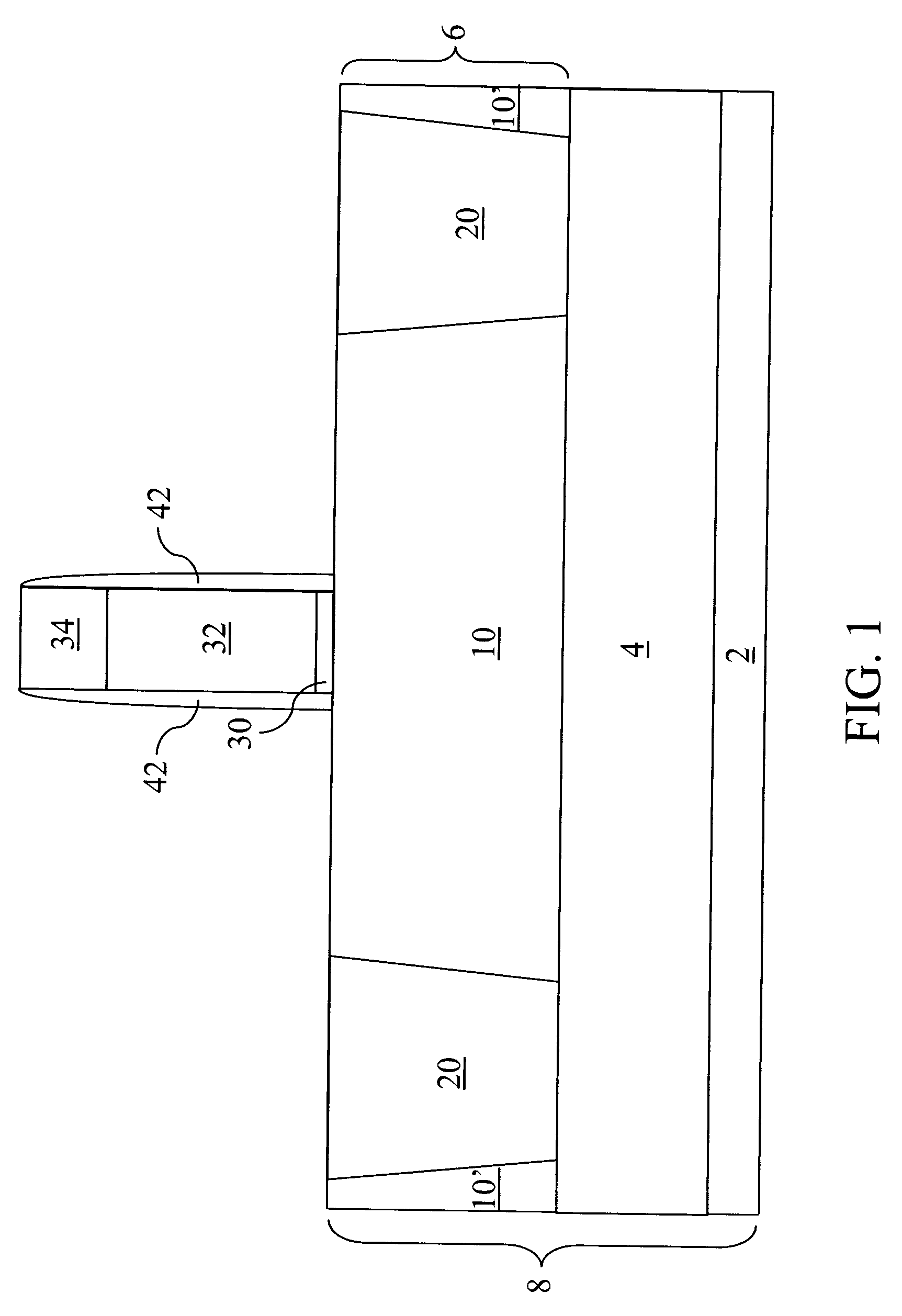

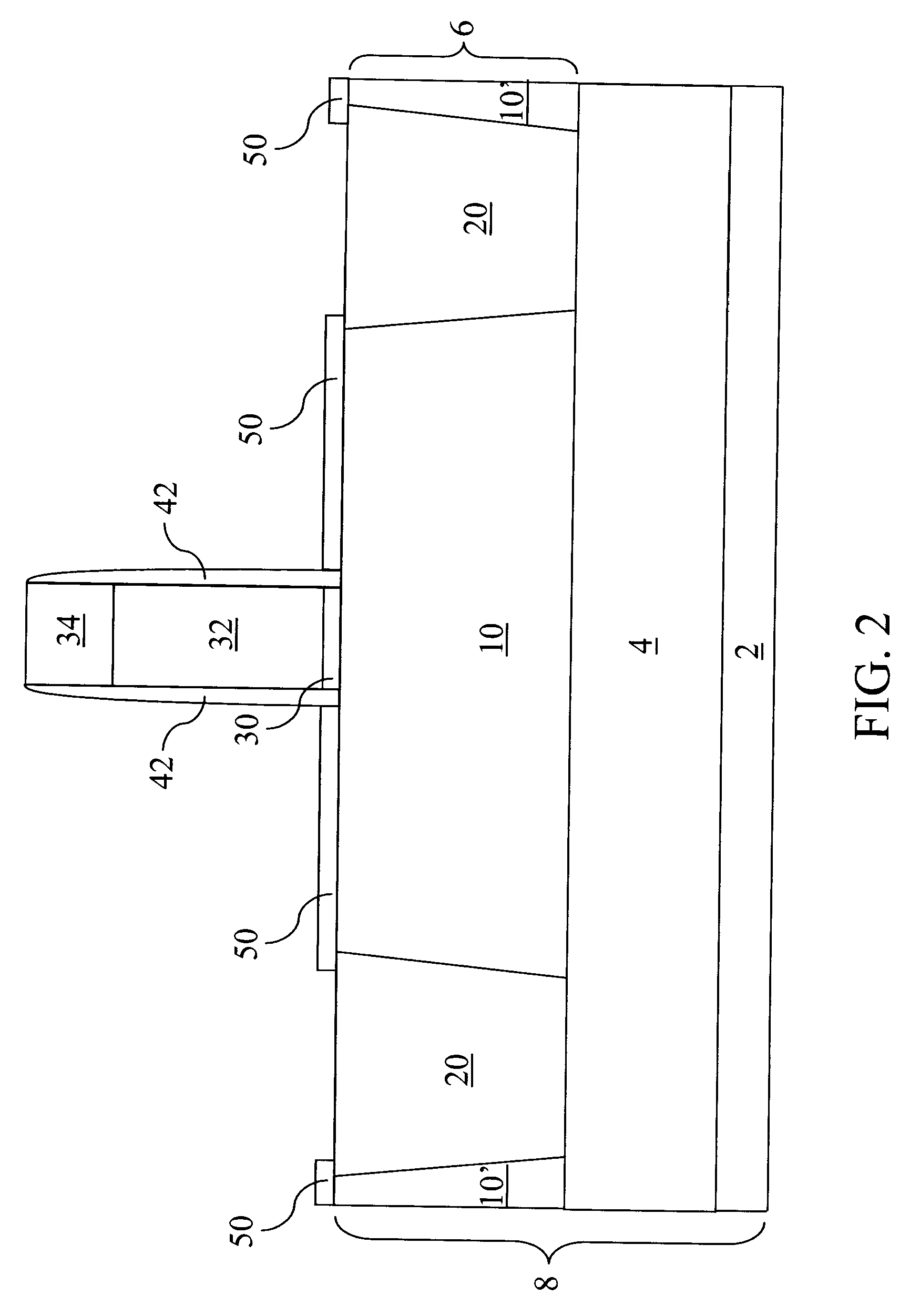

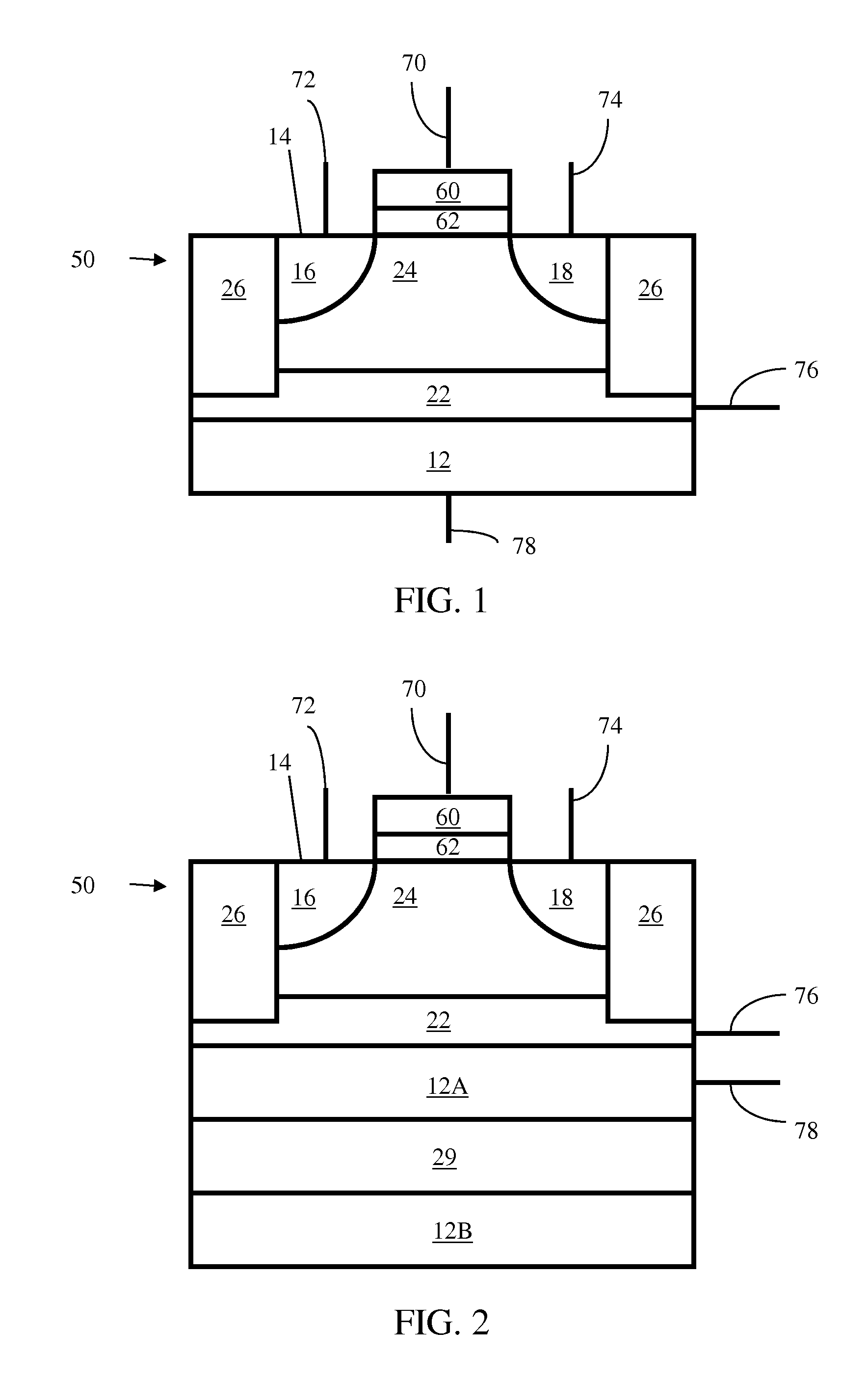

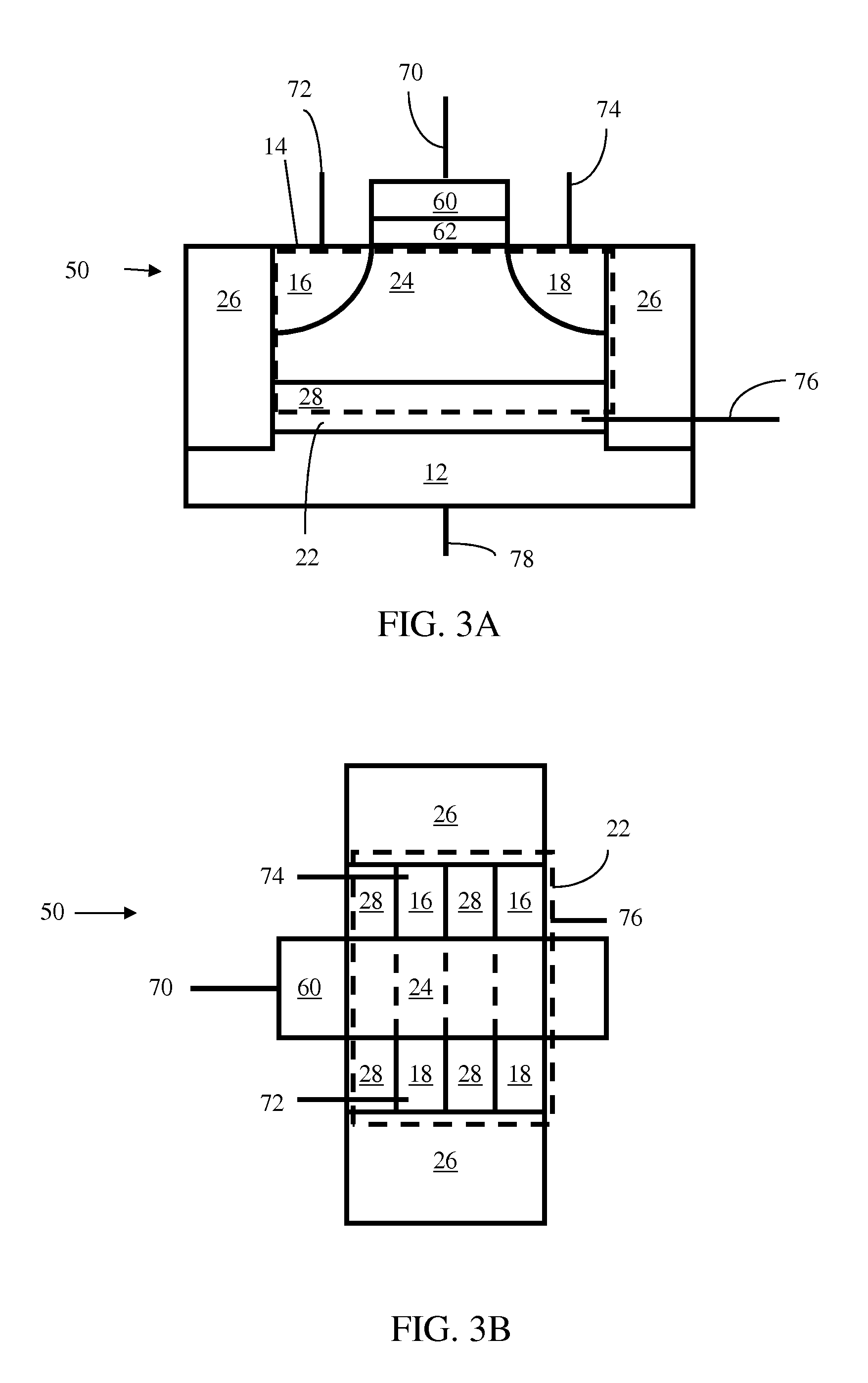

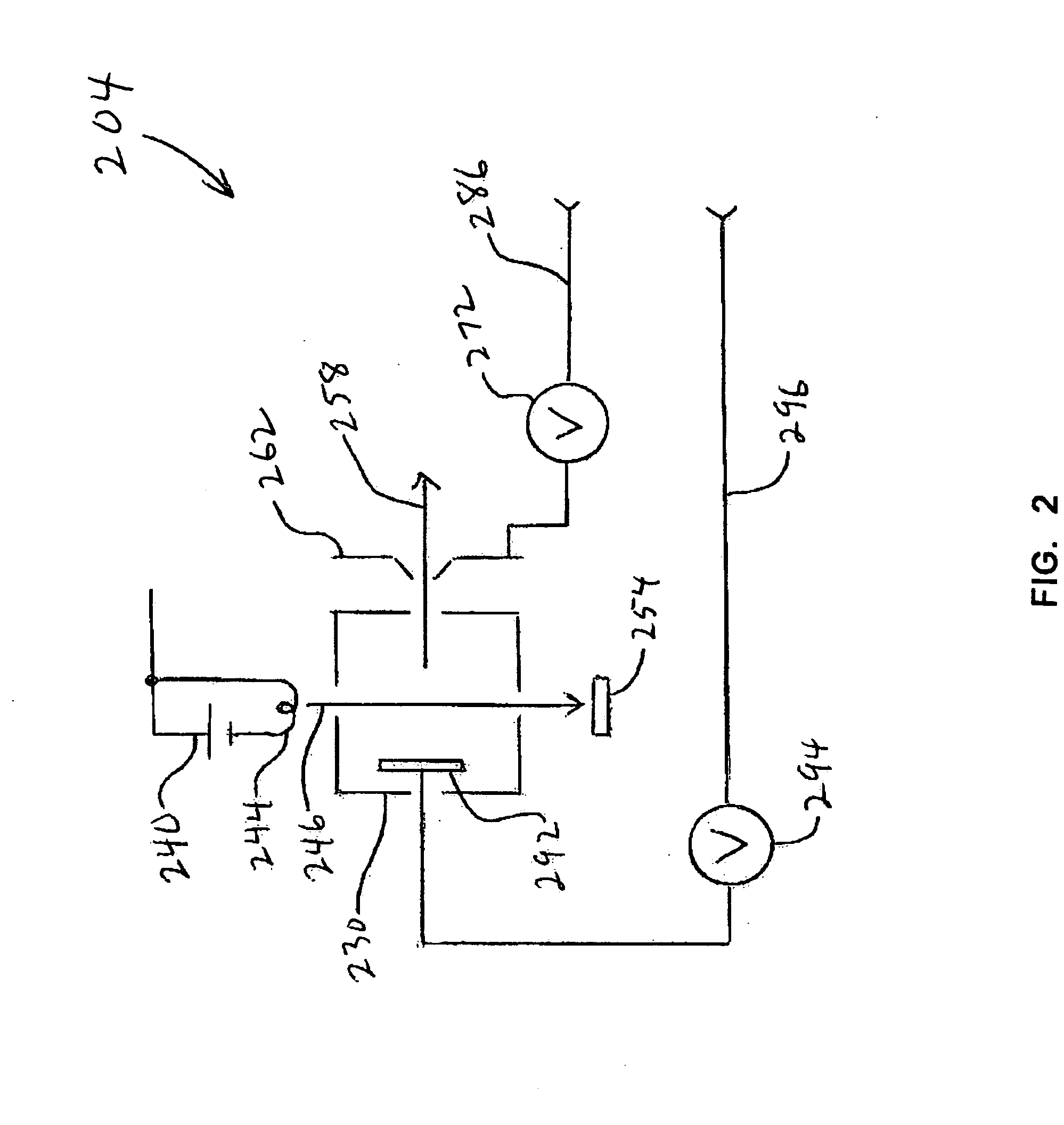

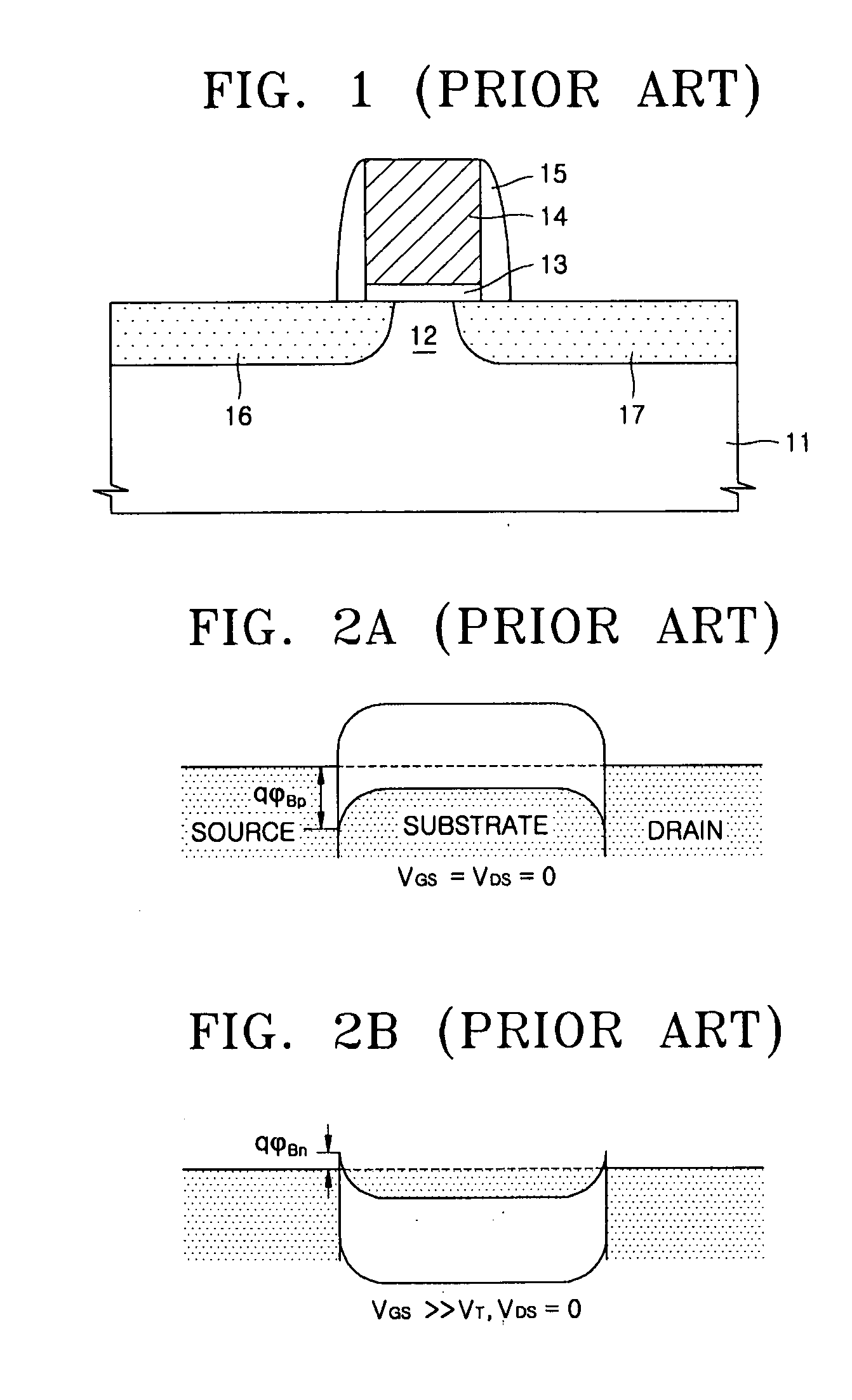

One transistor DRAM cell structure and method for forming

A single transistor DRAM cell is formed in a SOI substrate so that the DRAM cells are formed in bodies that are electrically isolated from each other. Each cell has doped regions that act as source and drain contacts. Between the drain contact and the body is a region, which aids in impact ionization and thus electron / hole formation during programming that is the same conductivity type as the body but of a higher concentration than the body. Adjacent to the source contact and to the body is a region, which aids in diode current during erase, that is the same conductivity type as the source contact but of a lower concentration than the source contact.

Owner:III HLDG 12 LLC

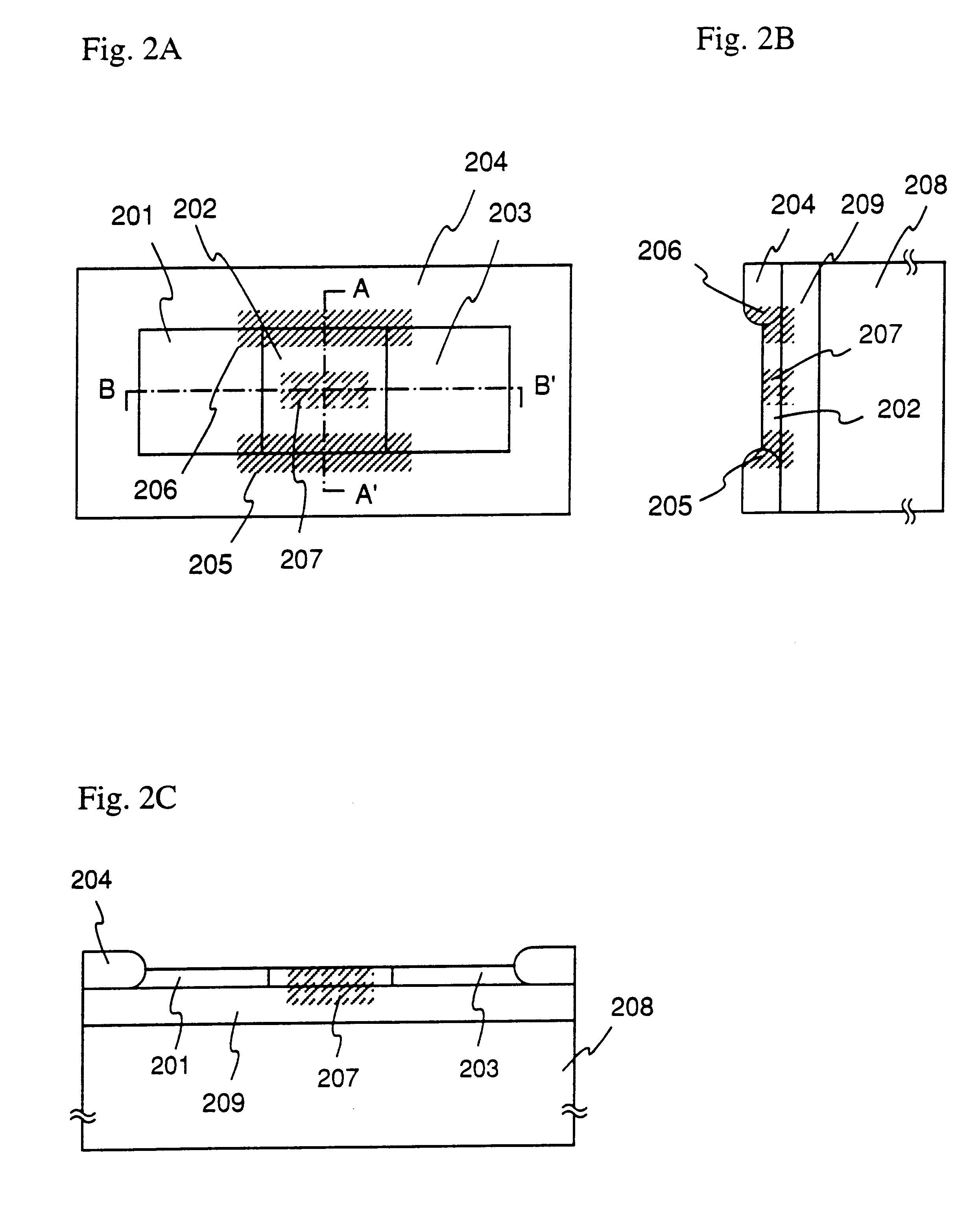

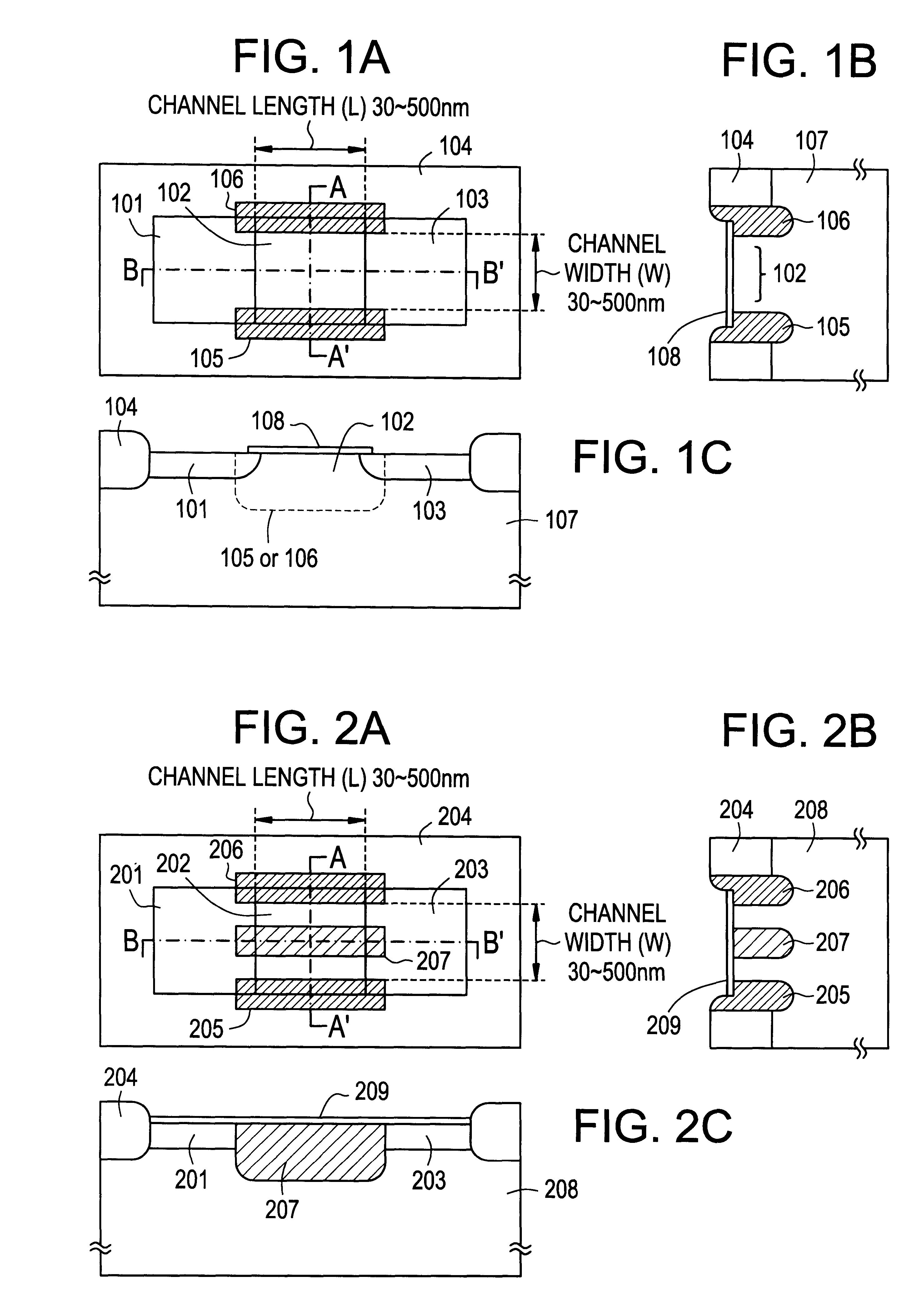

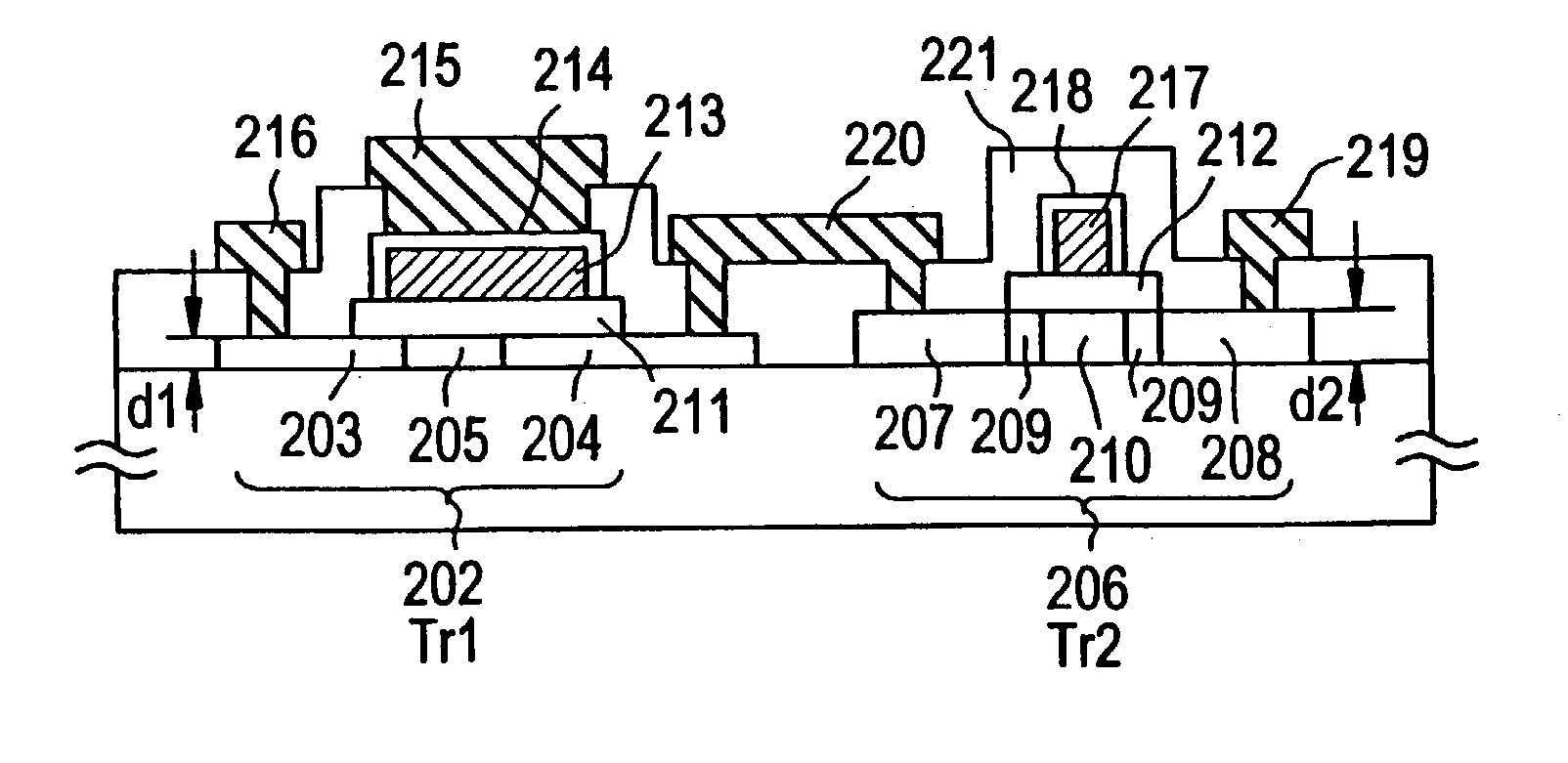

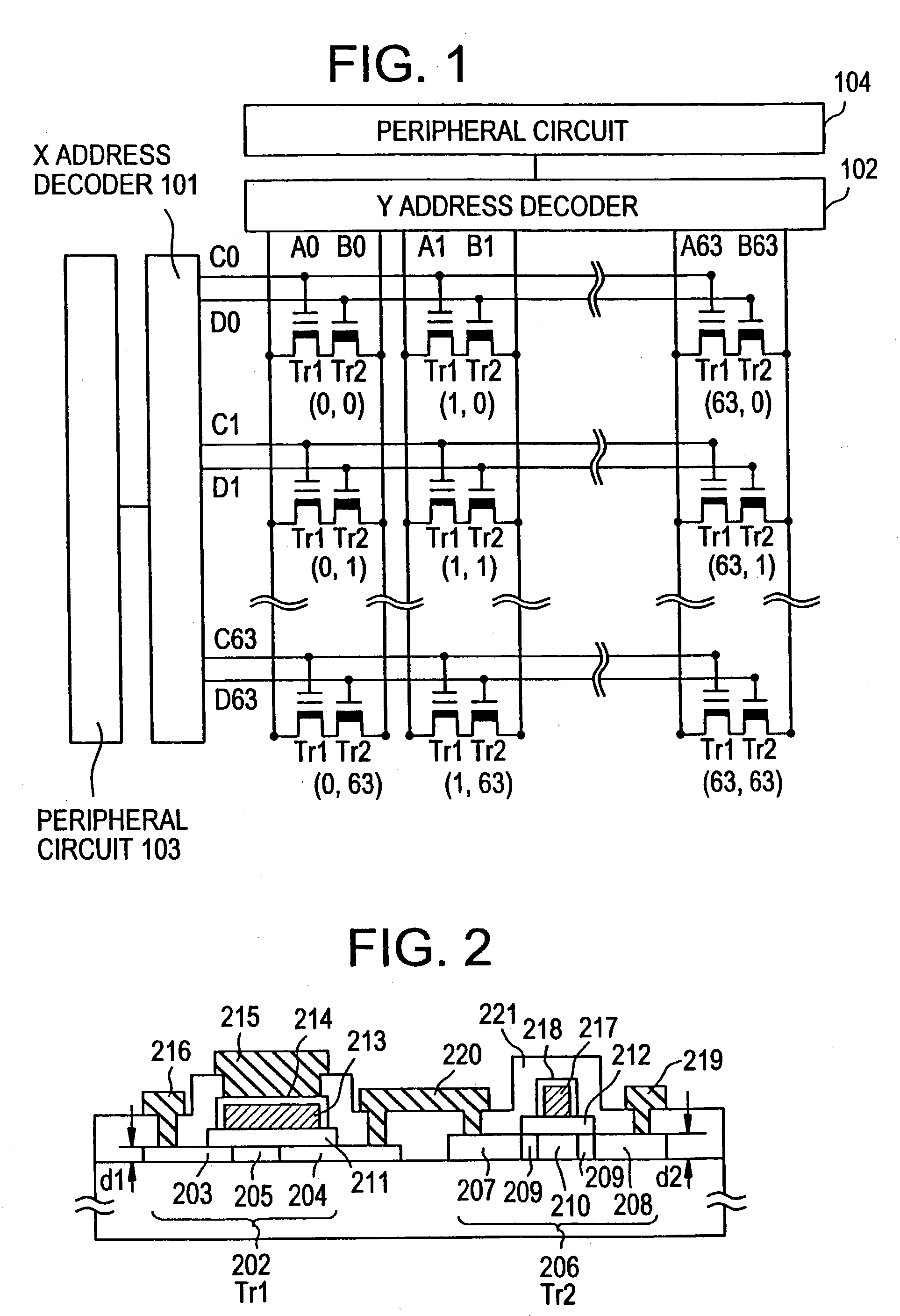

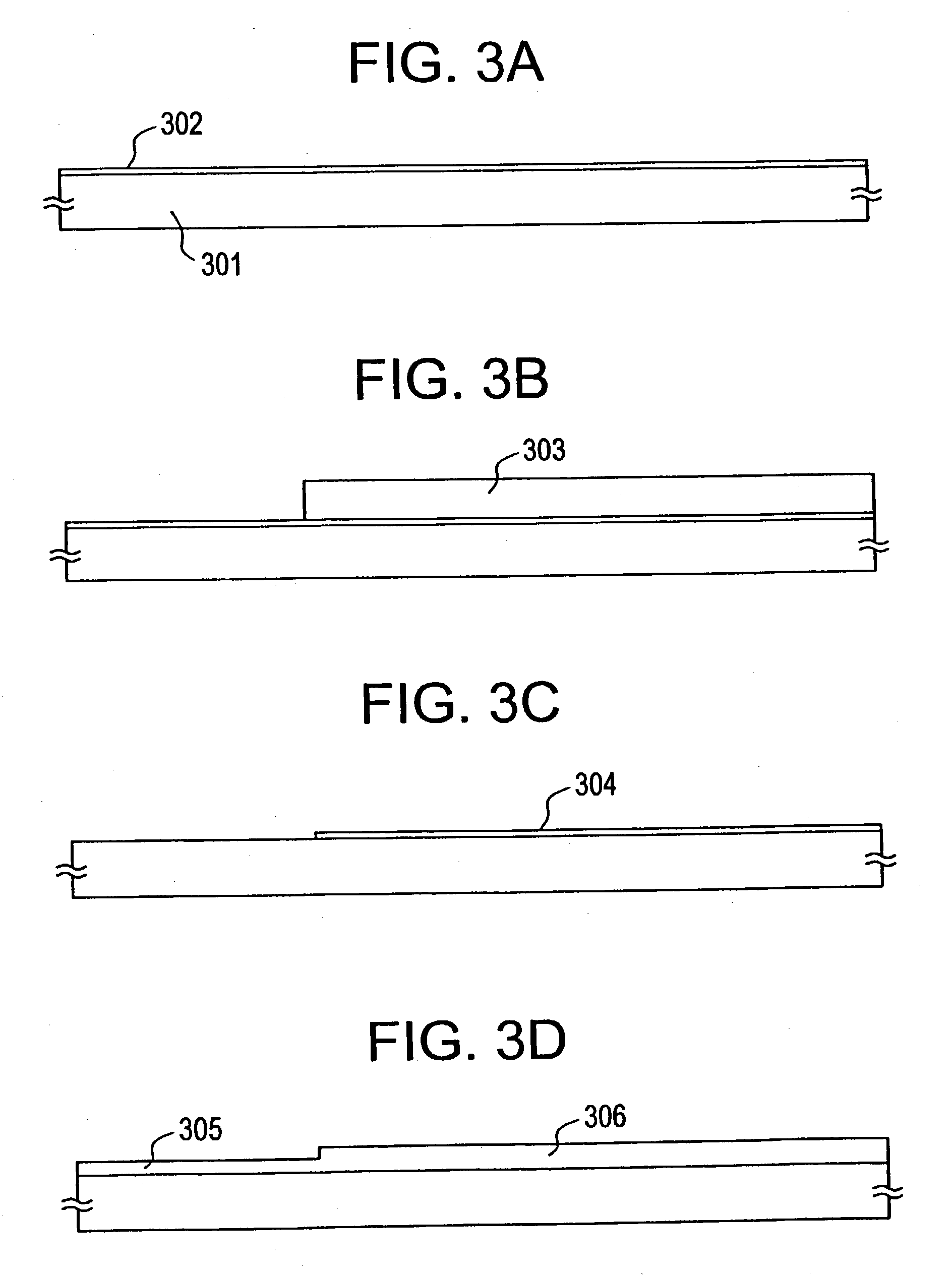

Nonvolatile memory and manufacturing method thereof

InactiveUS6472684B1Impact ionization occurs more easilyEasy to produceTransistorSemiconductor/solid-state device detailsLow voltageMiniaturization

Memory elements, switching elements, and peripheral circuits to constitute a nonvolatile memory are integrally formed on a substrate by using TFTs. Since semiconductor active layers of memory element TFTs are thinner than those of other TFTs, impact ionization easily occurs in channel regions of the memory element TFTs. This enables low-voltage write / erase operations to be performed on the memory elements, and hence the memory elements are less prone to deteriorate. Therefore, a nonvolatile memory capable of miniaturization can be provided.

Owner:SEMICON ENERGY LAB CO LTD

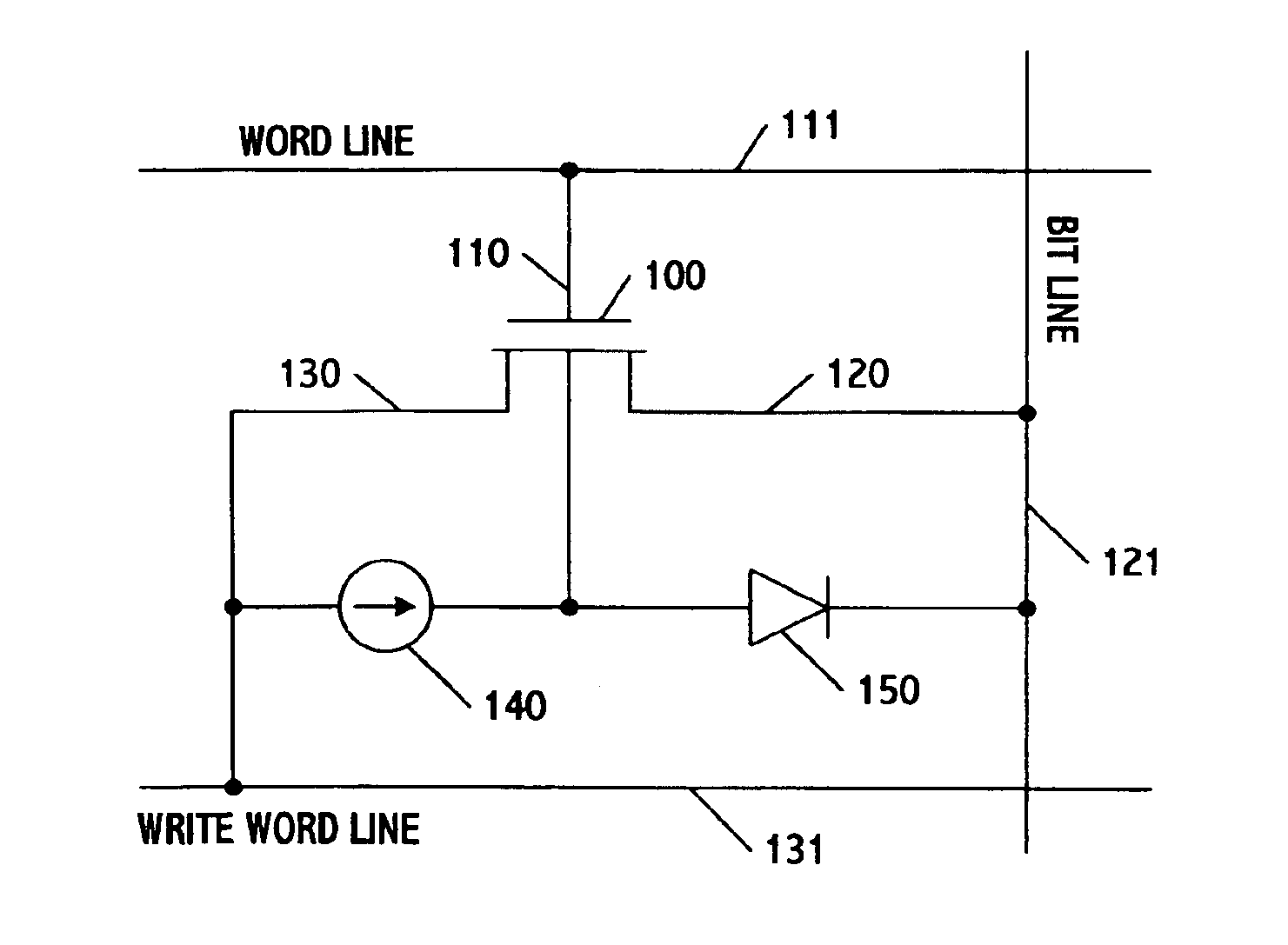

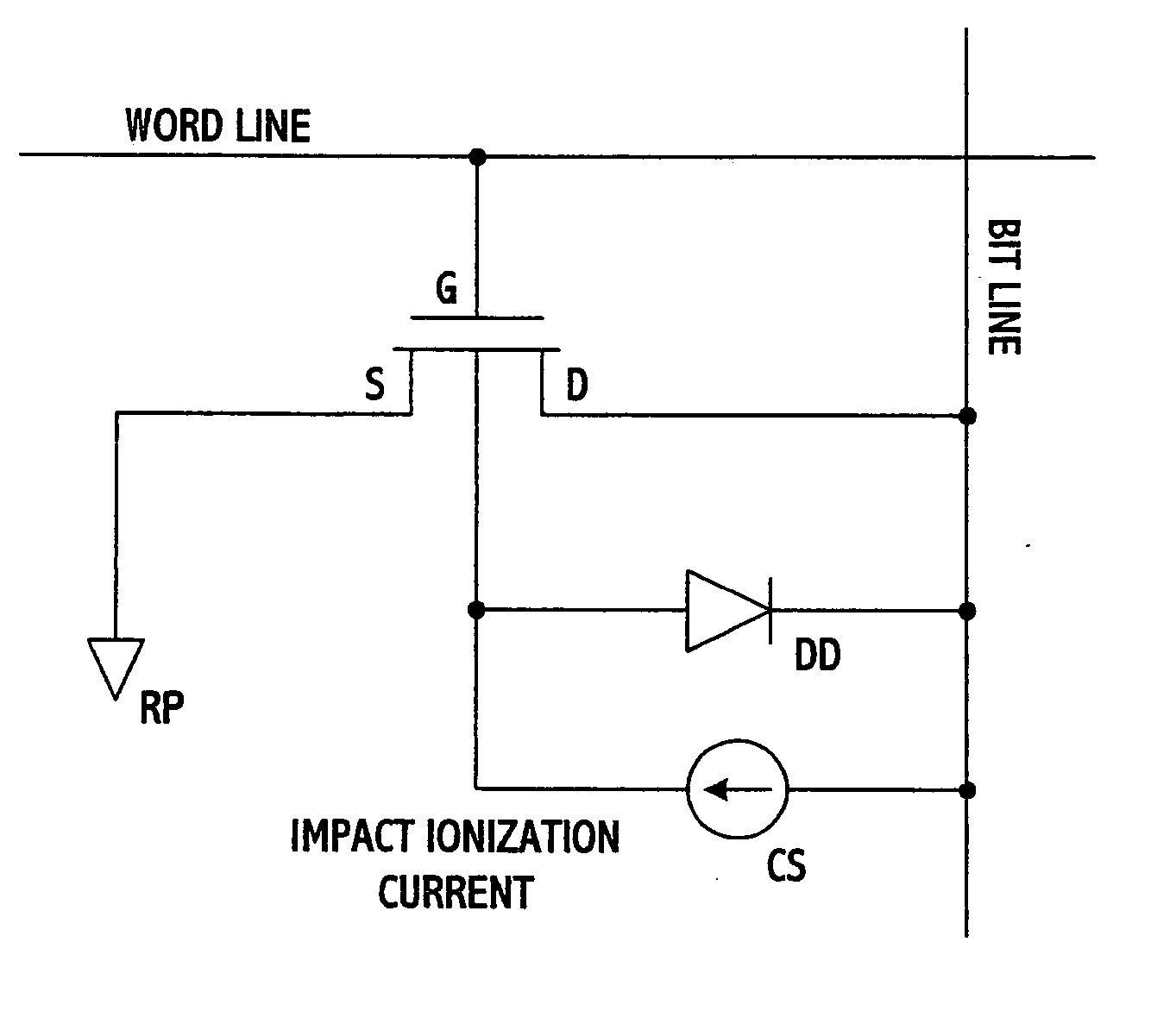

Floating-body DRAM using write word line for increased retention time

A DRAM memory cell uses a single transistor to perform the data storage and switching functions of a conventional cell. The transistor has a floating channel body which stores a potential that corresponds to one of two digital data values. The transistor further includes a gate connected to a first word line, a drain connected to a second word line, and a source connected to a bit line. By setting the word and bit lines to specific voltage states, the channel body stores a digital one potential as a result of impact ionization and a digital zero value as a result of forward bias of body-to-source junction.

Owner:INTEL CORP

Method and apparatus for nonvolatile memory

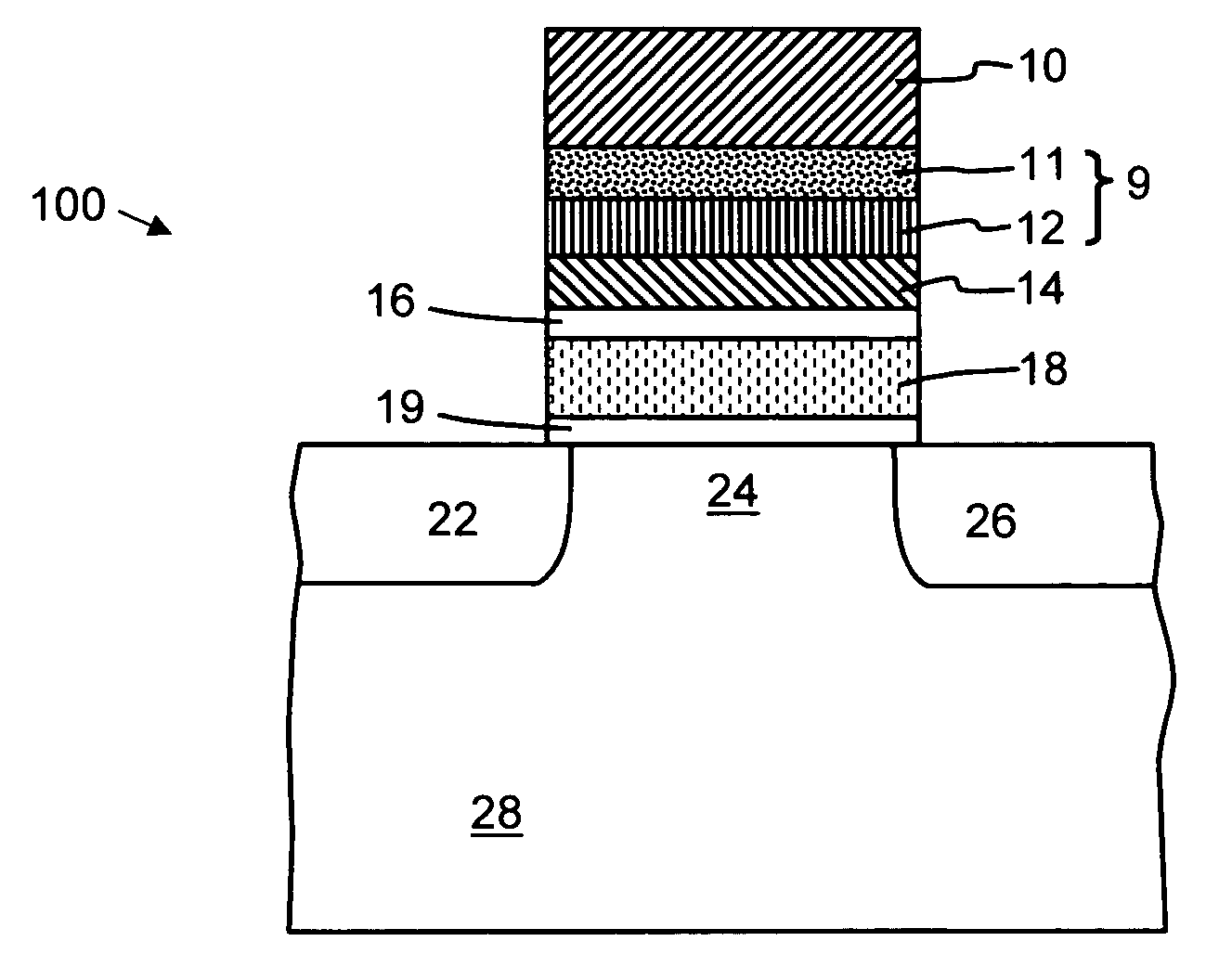

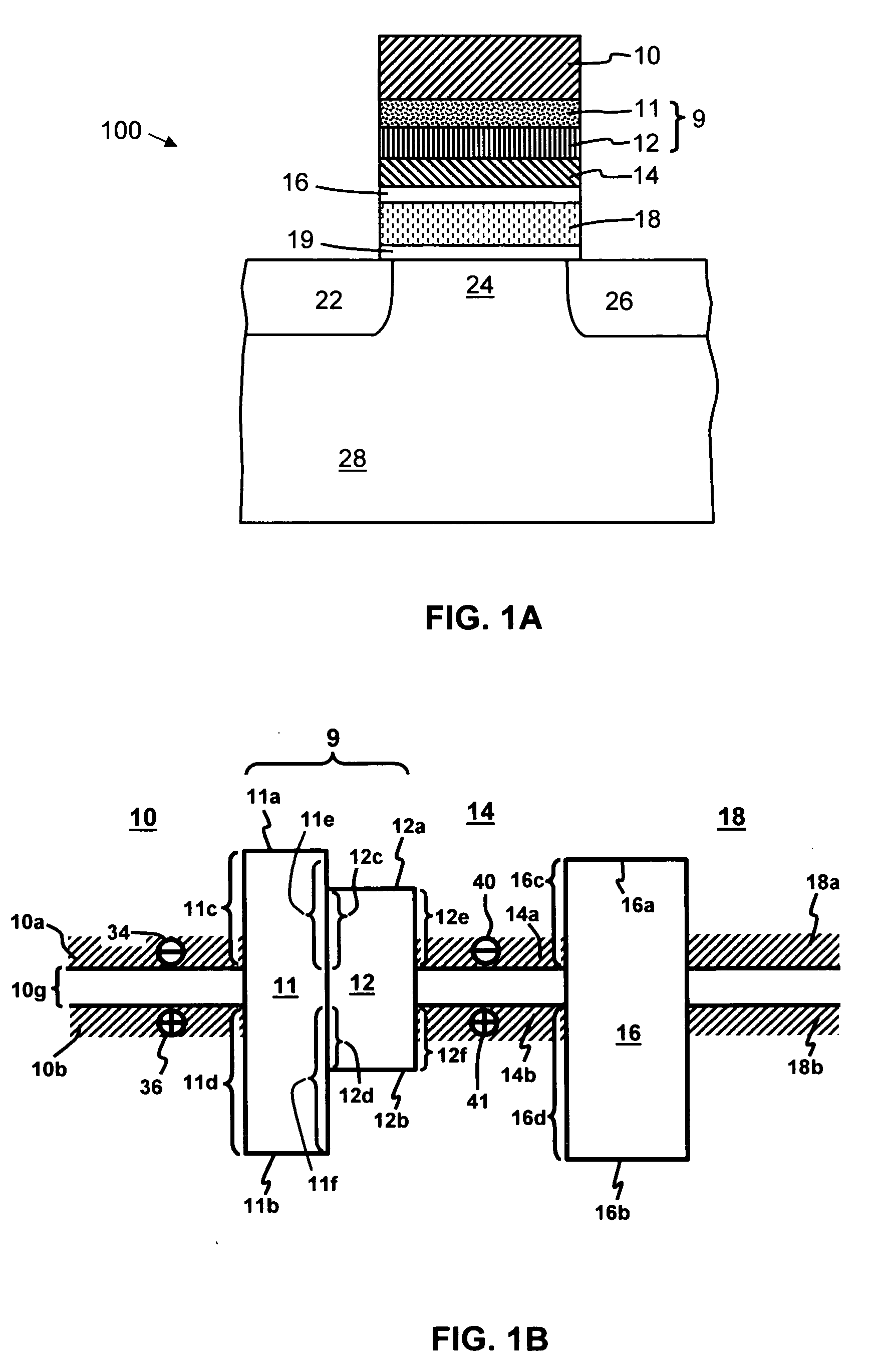

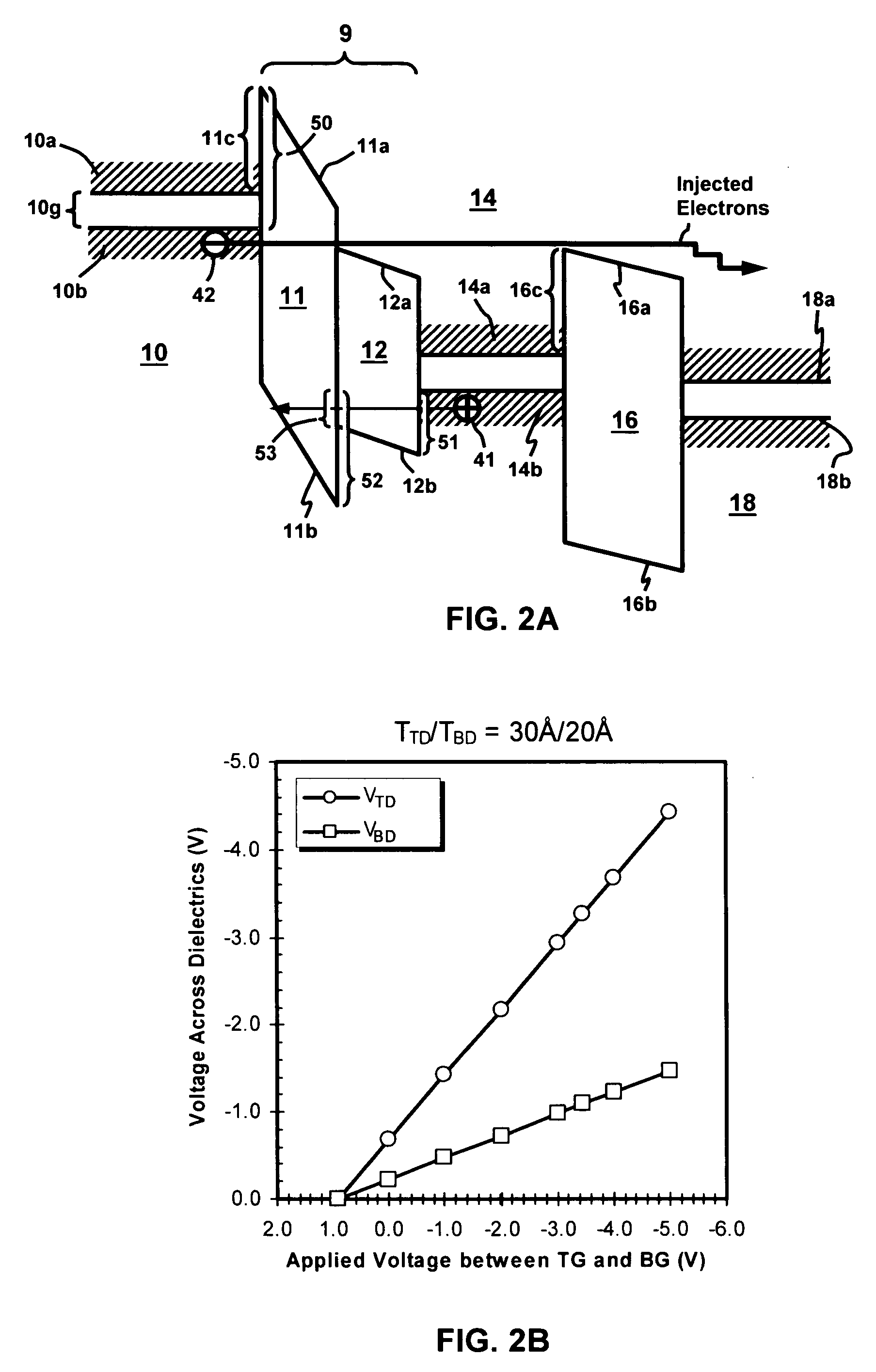

Method and apparatus on charges injection using piezo-ballistic-charges injection mechanism are provided for nonvolatile memory device. The device has a strain source, an injection filter, a tunneling gate, a ballistic gate, a charge storage region, a source, and a drain with a channel defined between the source and drain. The strain source permits piezo-effect in ballistic charges transport to enable the piezo-ballistic-charges injection mechanism. The injection filter permits transporting of charge carriers of one polarity type from the tunneling gate through the blocking material and the ballistic gate to the charge storage region while blocking the transport of charge carriers of an opposite polarity from the ballistic gate to the tunneling gate. The present invention further provides an energy band engineering method permitting the memory device be operated without suffering from disturbs, from dielectric breakdown, from impact ionization, and from undesirable RC effects.

Owner:MARVELL ASIA PTE LTD

Semiconductor device

There is provided a semiconductor device having a new structure which allows a high reliability and a high field effect mobility to be realized in the same time. In an insulated gate transistor having an SOI structure utilizing a mono-crystal semiconductor thin film on an insulating layer, pinning regions are formed at edge portions of a channel forming region. The pinning regions suppress a depletion layer from spreading from the drain side and prevent a short-channel effect. In the same time, they also function as a path for drawing out minority carriers generated by impact ionization to the outside and prevent a substrate floating effect from occurring.

Owner:SEMICON ENERGY LAB CO LTD

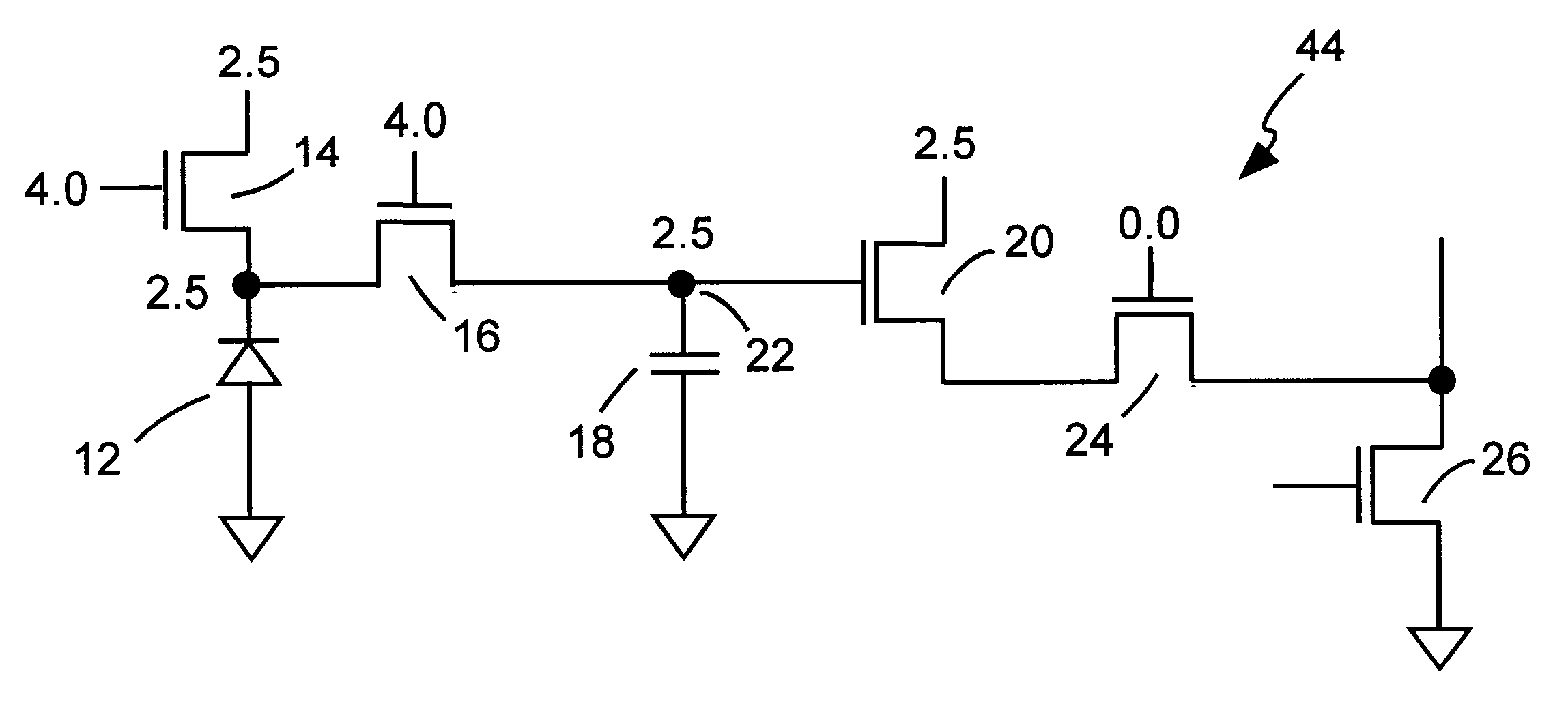

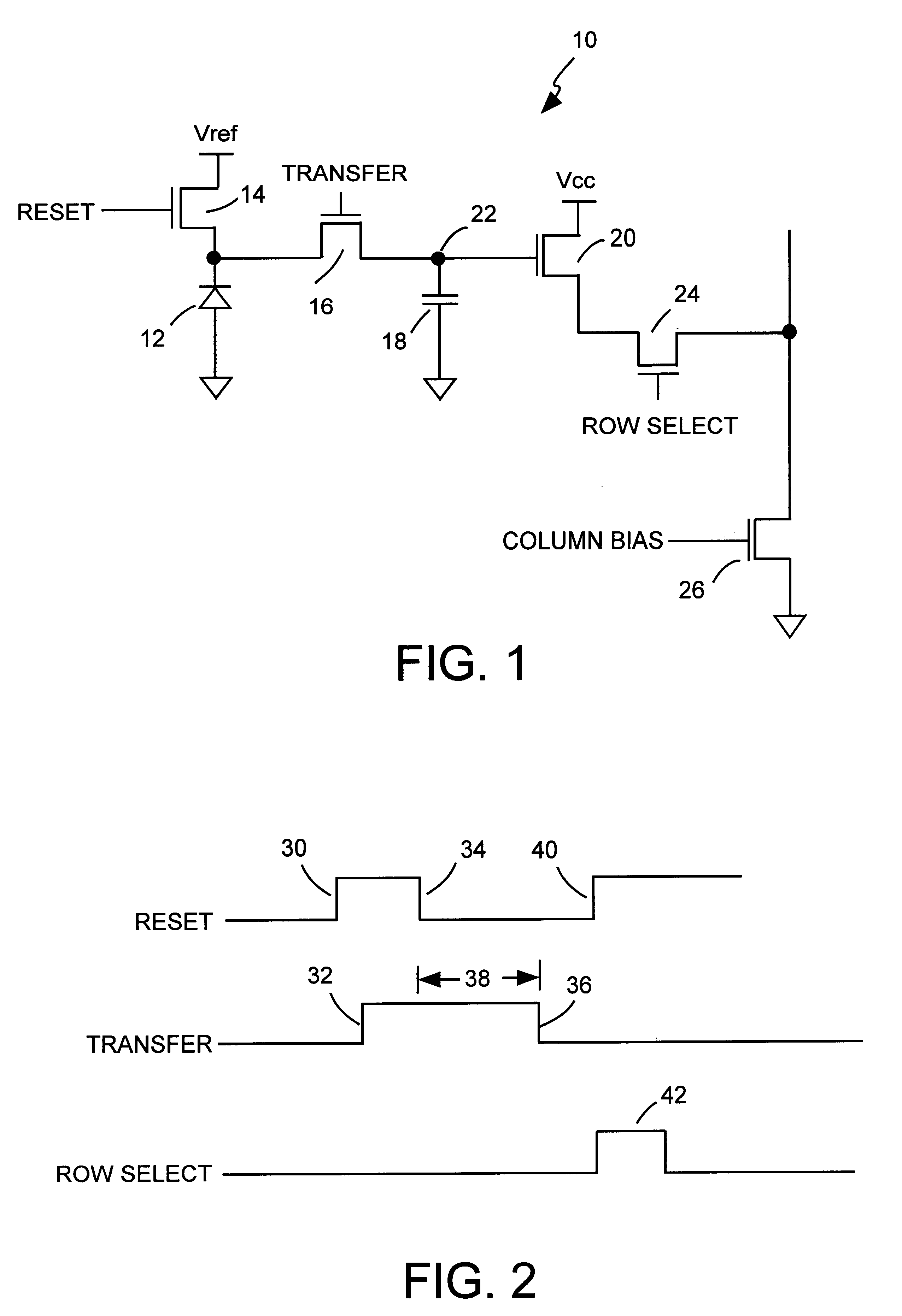

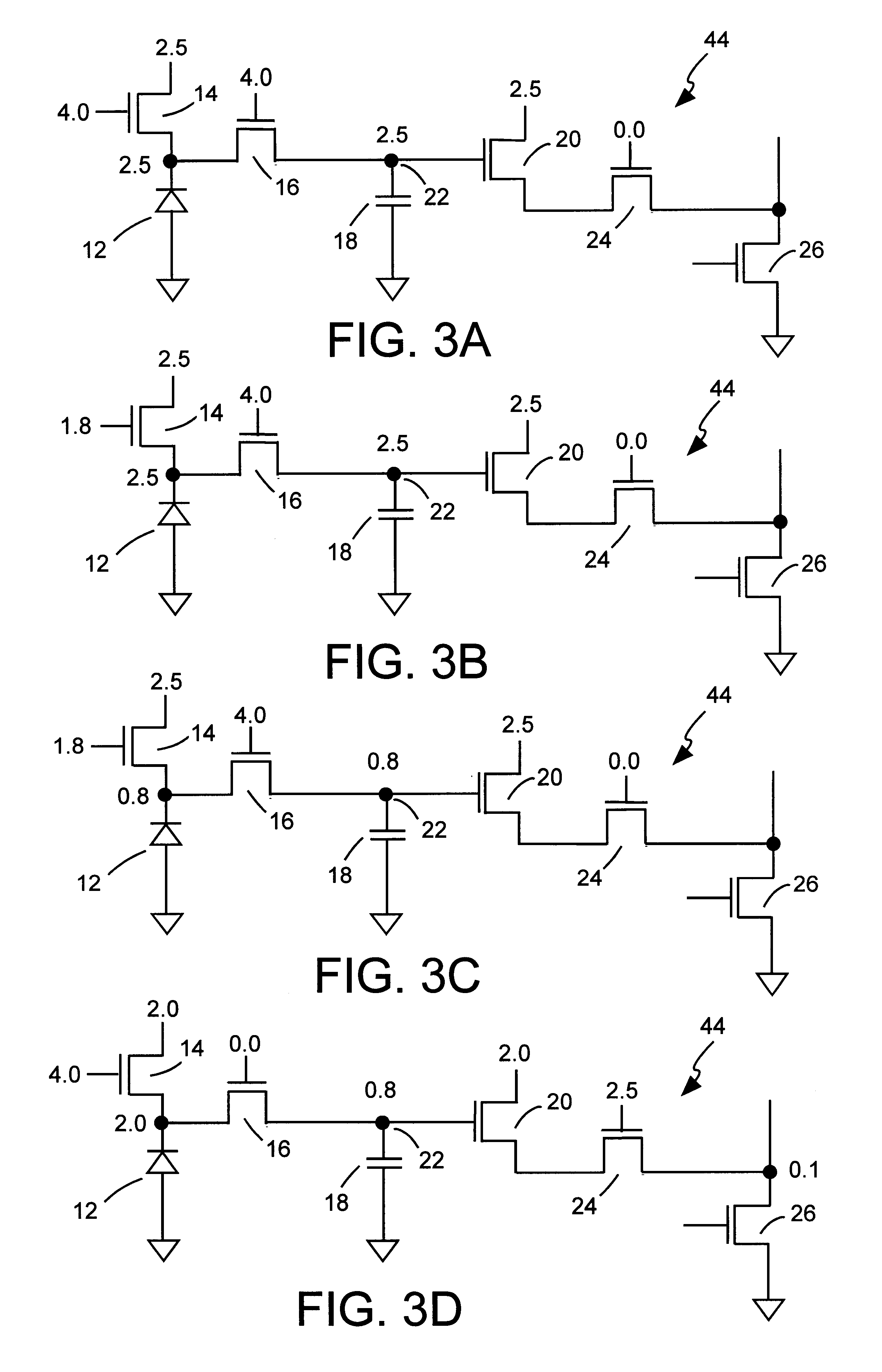

Method and apparatus for biasing a CMOS active pixel sensor above the nominal voltage maximums for an IC process

An active pixel sensor is operated with voltages that exceed the nominal operating voltages for a particular integrated circuit process. Voltages that exceed the nominal operating voltages are employed during the reset, integration and readout periods in the operating cycle of the active pixel sensor. The lower limit of the voltage representing the capture of photocharge in the active pixel sensor is fixed by setting the voltage applied to the gate of a reset transistor in the active pixel sensor to a level during integration which prevents the voltage across the dielectric of a transfer transistor from exceeding a preselected value. Read disturb caused by impact ionization current from a readout transistor to a storage node is reduced by lowering the voltage applied to the drain of a readout transistor to reduce the Vds of the readout transistor at the start of a readout period.

Owner:FOVEON

Field effect transistor containing a wide band gap semiconductor material in a drain

InactiveUS20090121258A1Suppress impact ionizationLarge band gapTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsGate dielectric

A field effect transistor comprising a silicon containing body is provided. After formation of a gate dielectric, gate electrode, and a first gate spacer, a drain side trench is formed and filled with a wide band gap semiconductor material. Optionally, a source side trench may be formed and filled with a silicon germanium alloy to enhance an on-current of the field effect transistor. Halo implantation and source and drain ion implantation are performed to form various doped regions. Since the wide band gap semiconductor material as a wider band gap than that of silicon, impact ionization is reduced due to the use of the wide band gap semiconductor material in the drain, and consequently, a breakdown voltage of the field effect transistor is increased compared to transistors employing silicon in the drain region.

Owner:GLOBALFOUNDRIES INC

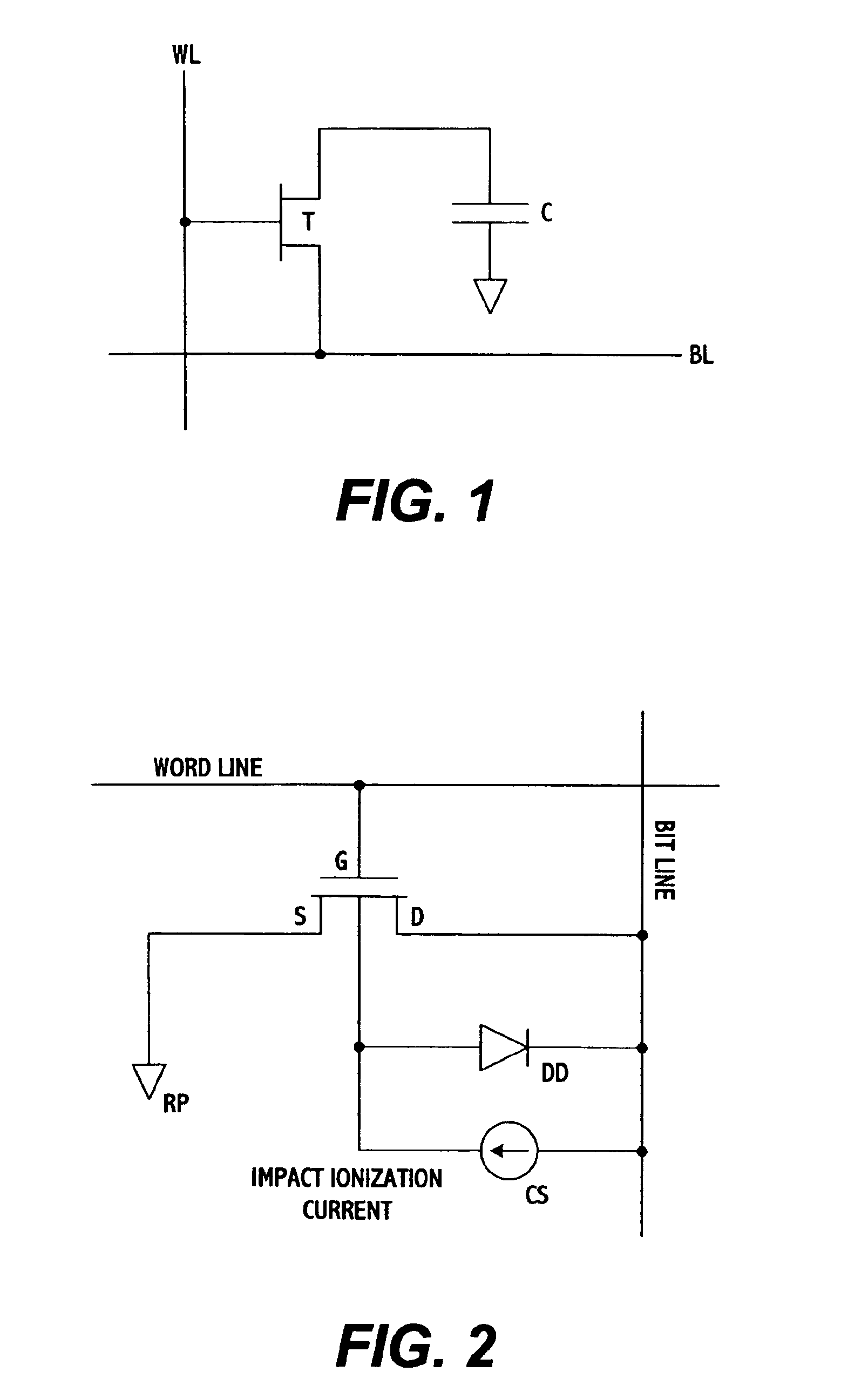

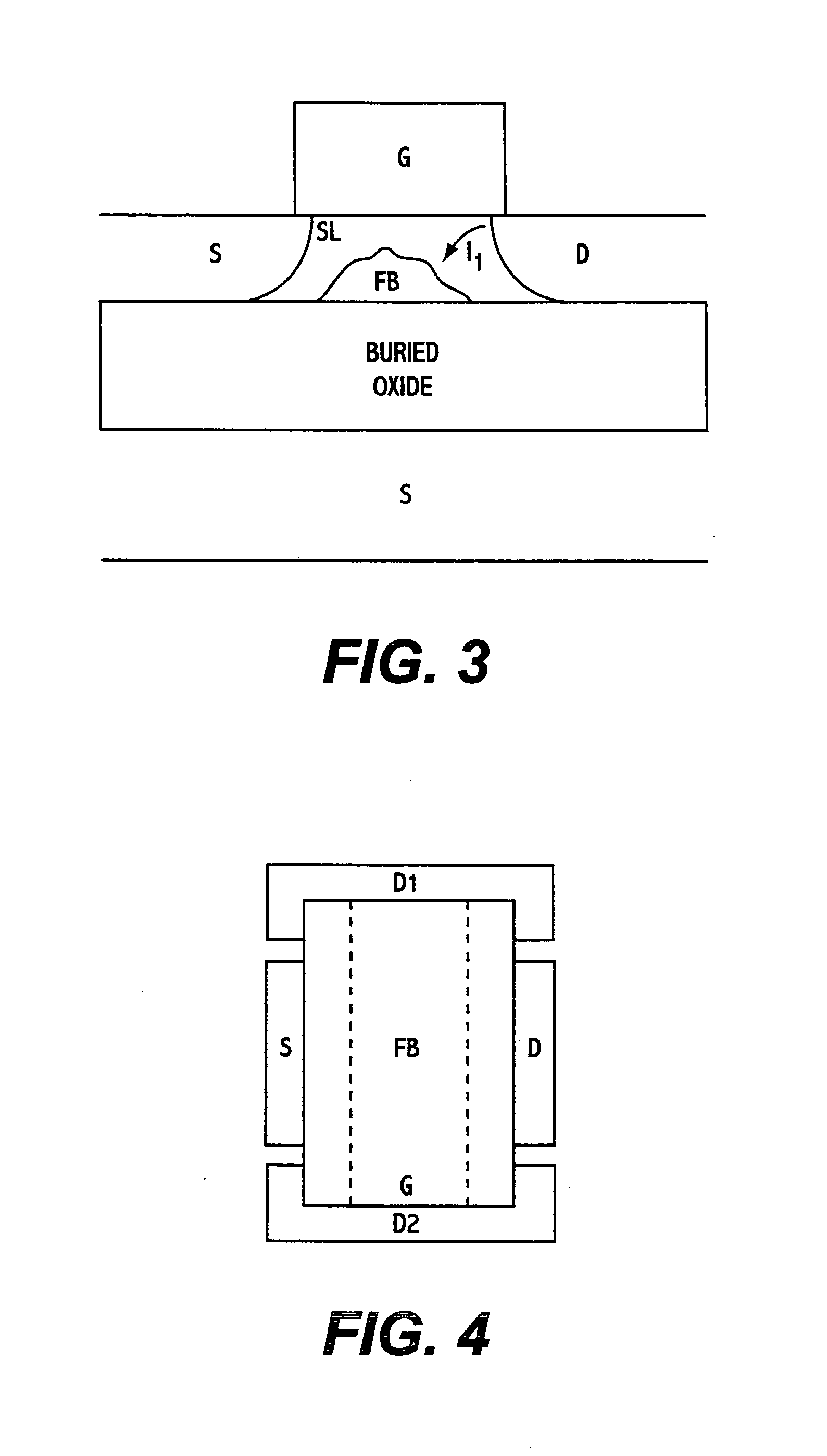

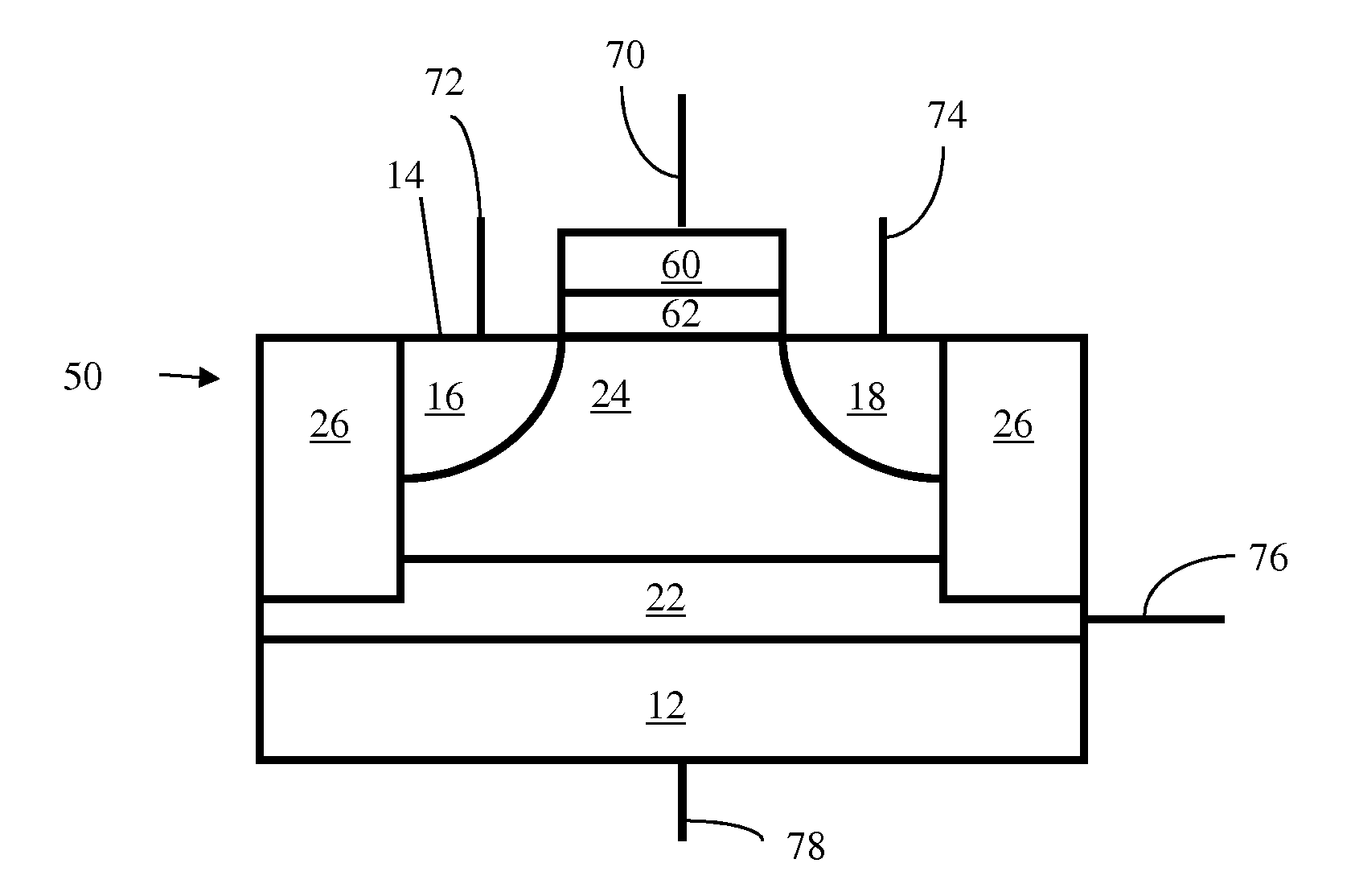

Memory Device Having Electrically Floating Body Transistor

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell selected from at least first and second states. A first region of the memory cell is in electrical contact with the floating body region. A second region of the memory cell is spaced apart from the first region and is also in electrical contact with the floating body region. A gate is positioned between the first and second regions. A back-bias region is configured to generate impact ionization when the memory cell is in one of the first and second states, and the back-bias region is configured so as not to generate impact ionization when the memory cell is in the other of the first and second states.

Owner:ZENO SEMICON

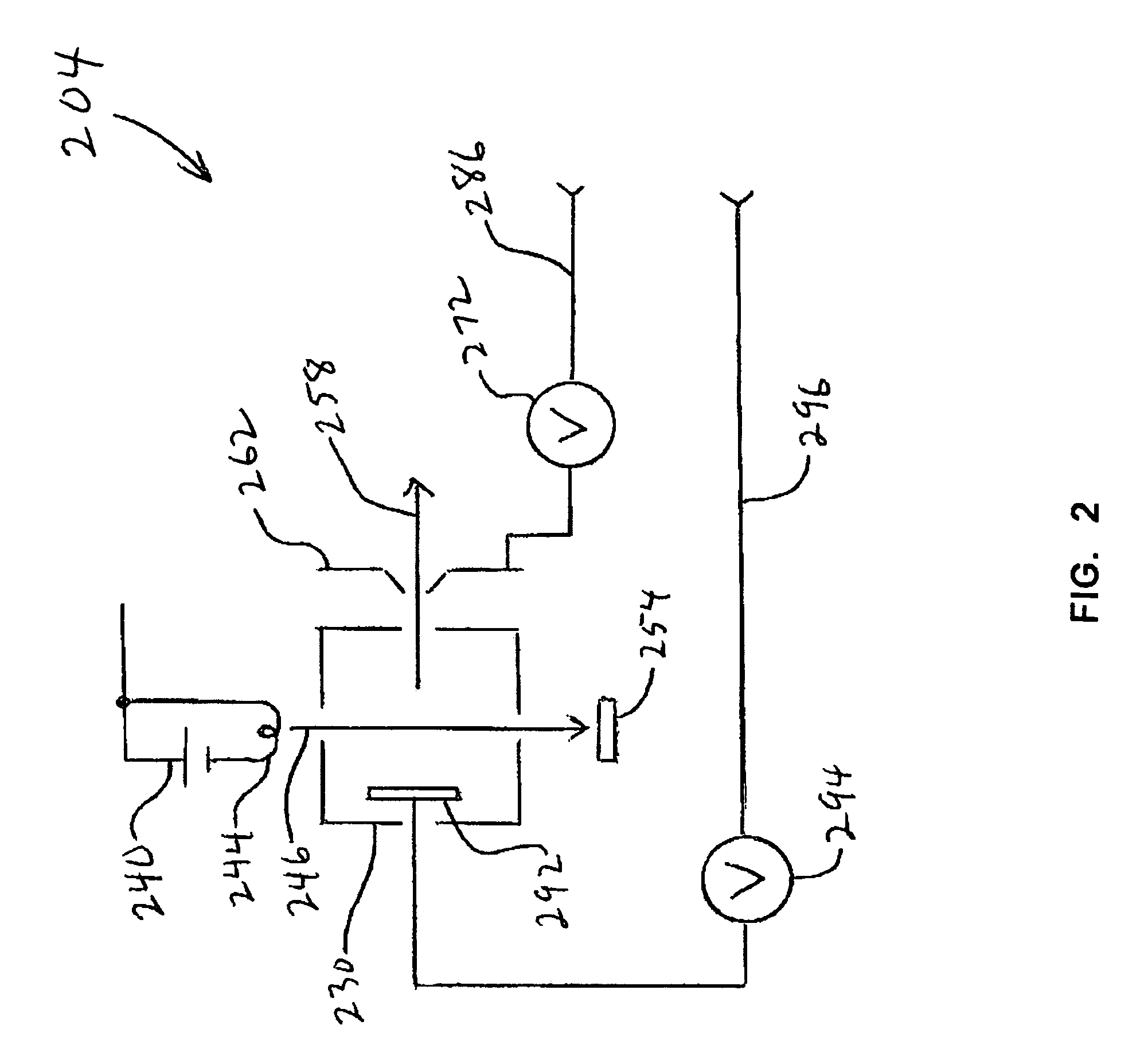

Method for controlling space charge-driven ion instabilities in electron impact ion sources

ActiveUS20060237641A1Inhibition effectMaterial analysis by optical meansIon sources/gunsVoltage pulseElectron collision

In a method for inhibiting space charge-related effects in an ion source, an electron beam is directed into a chamber to produce ions from sample material in the chamber. A voltage pulse is applied to the chamber to perturb an electron space charge present in the chamber. The ion source may be an electron impact ionization (EI) apparatus. The ion source may operated in conjunction with a mass spectrometry system.

Owner:BRUKER DALTONIK GMBH & CO KG

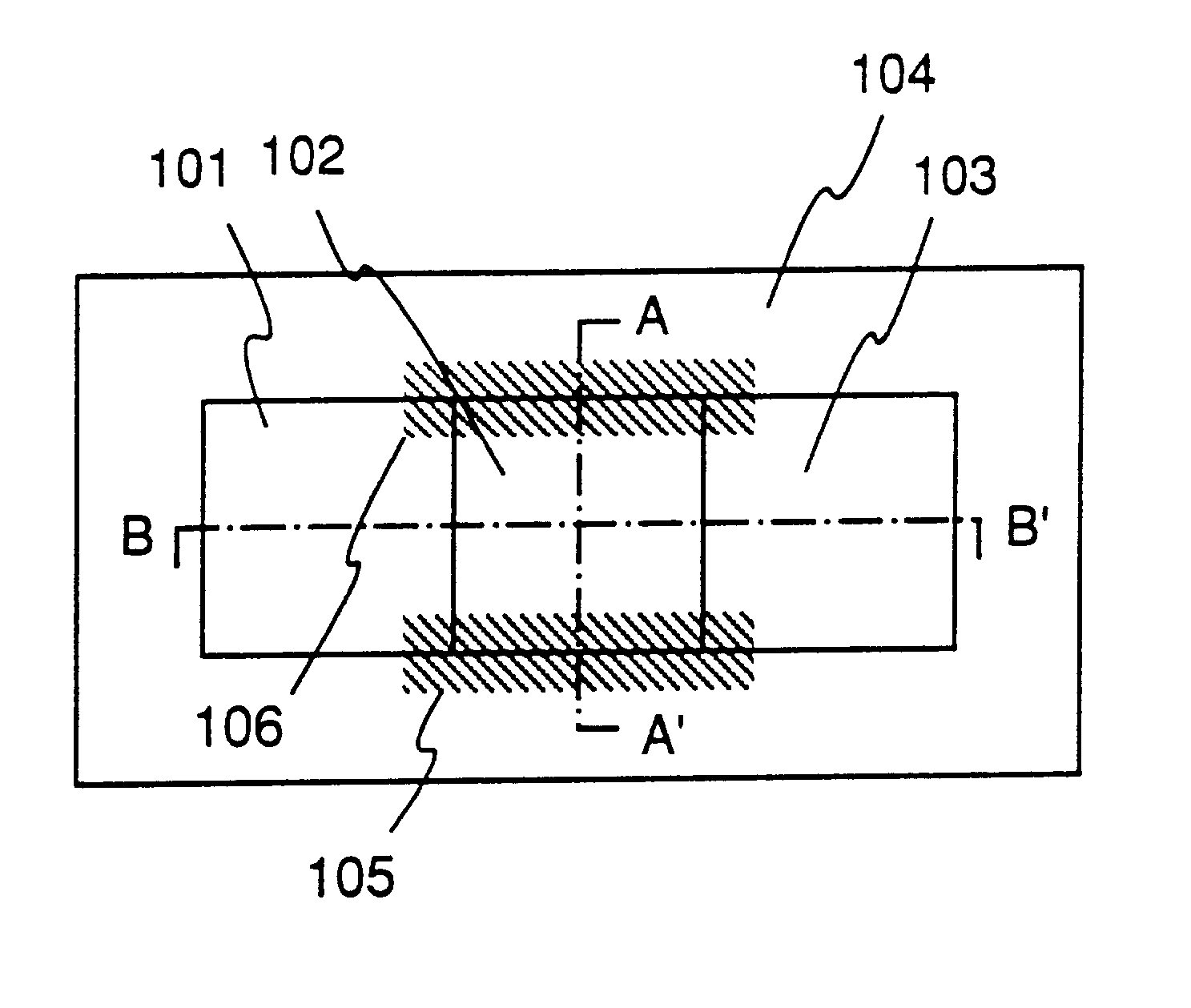

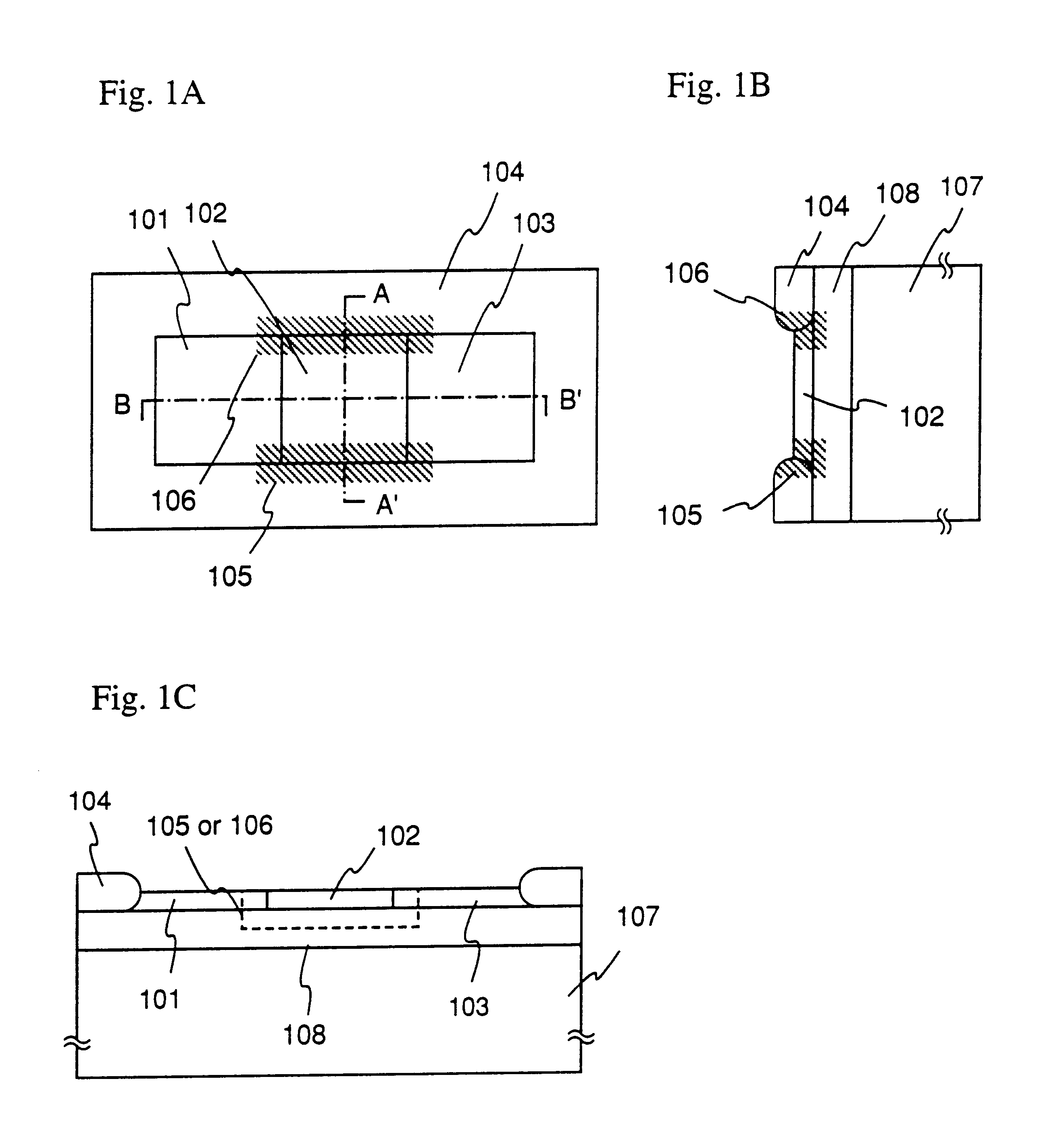

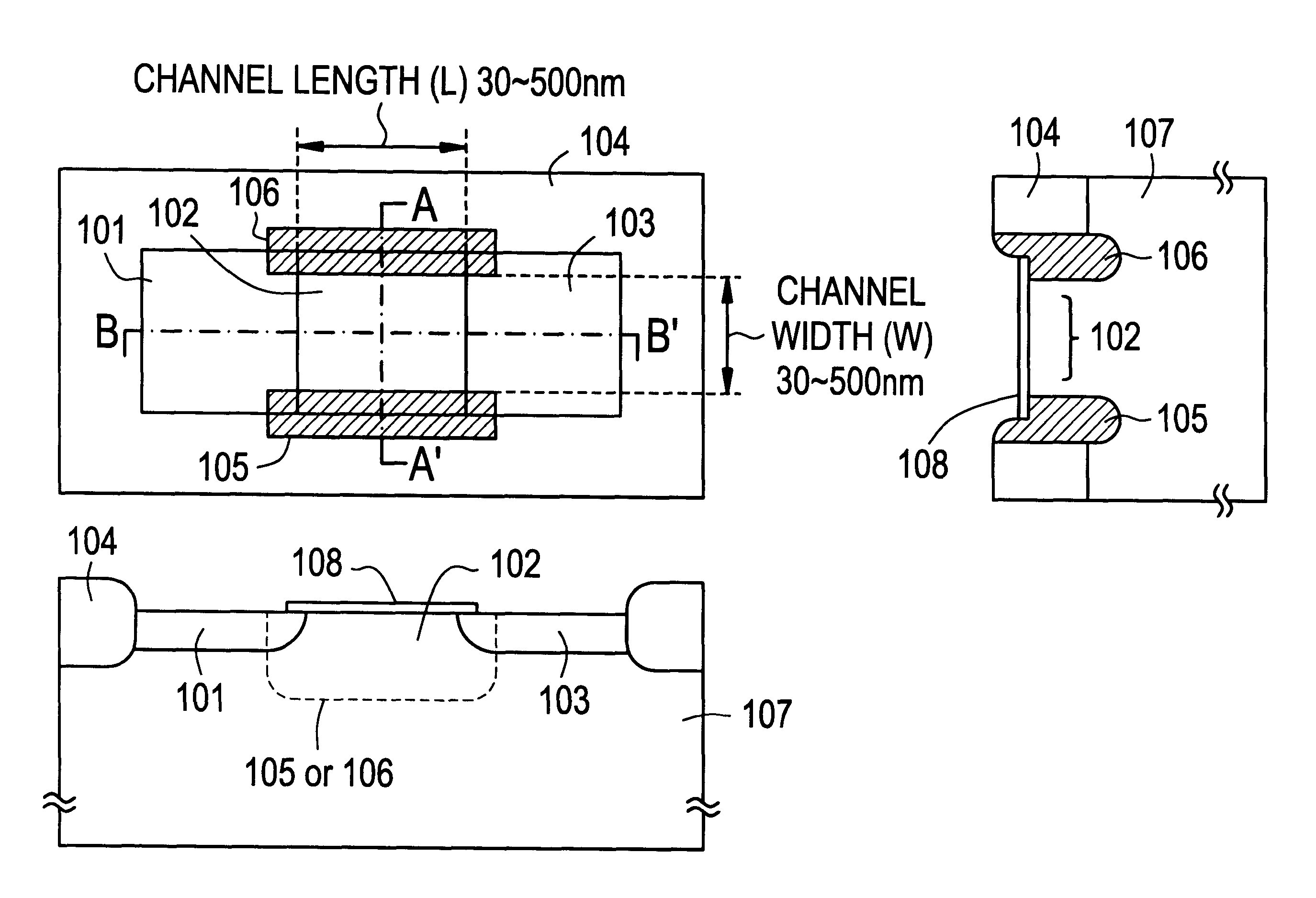

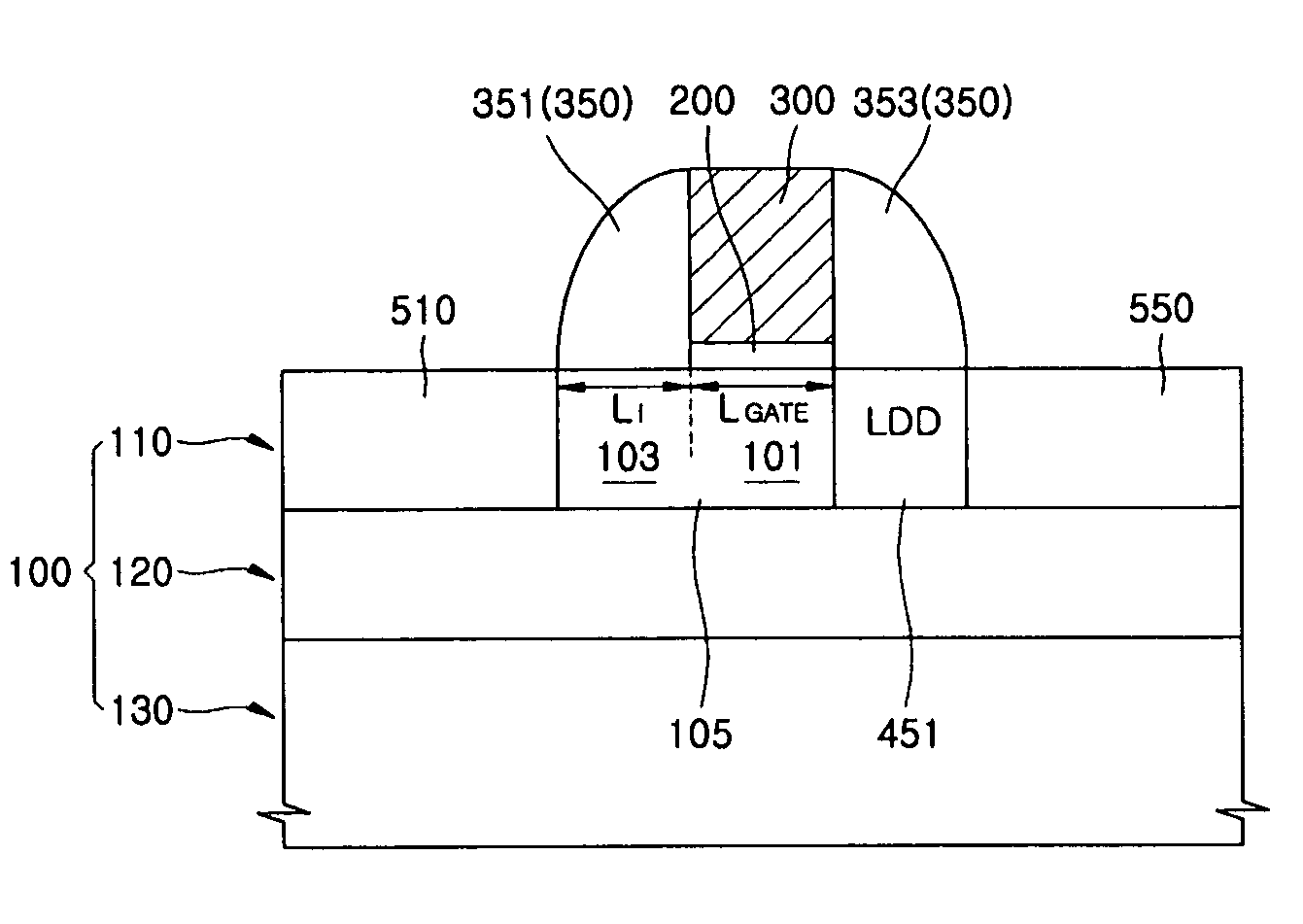

Semiconductor device having impurity region locally at an end of channel formation region

InactiveUS6232642B1Suppresses and prevents short channel effectLow mobilityTransistorSemiconductor/solid-state device detailsBreakdown phenomenonCharge carrier

There is provided a semiconductor device having a novel structure in which high reliability and high field effect mobility can be simultaneously achieved. In an insulated gate transistor formed on a single crystal silicon substrate, pinning regions 105 and 106 are formed at the ends of a channel formation region 102. The pinning regions 105 and 106 suppress the expansion of a depletion layer from the drain side to prevent a short channel effect. In addition, they also serve as a path for extracting minority carriers generated as a result of impact ionization to prevent breakdown phenomena induced by carrier implantation.

Owner:SEMICON ENERGY LAB CO LTD

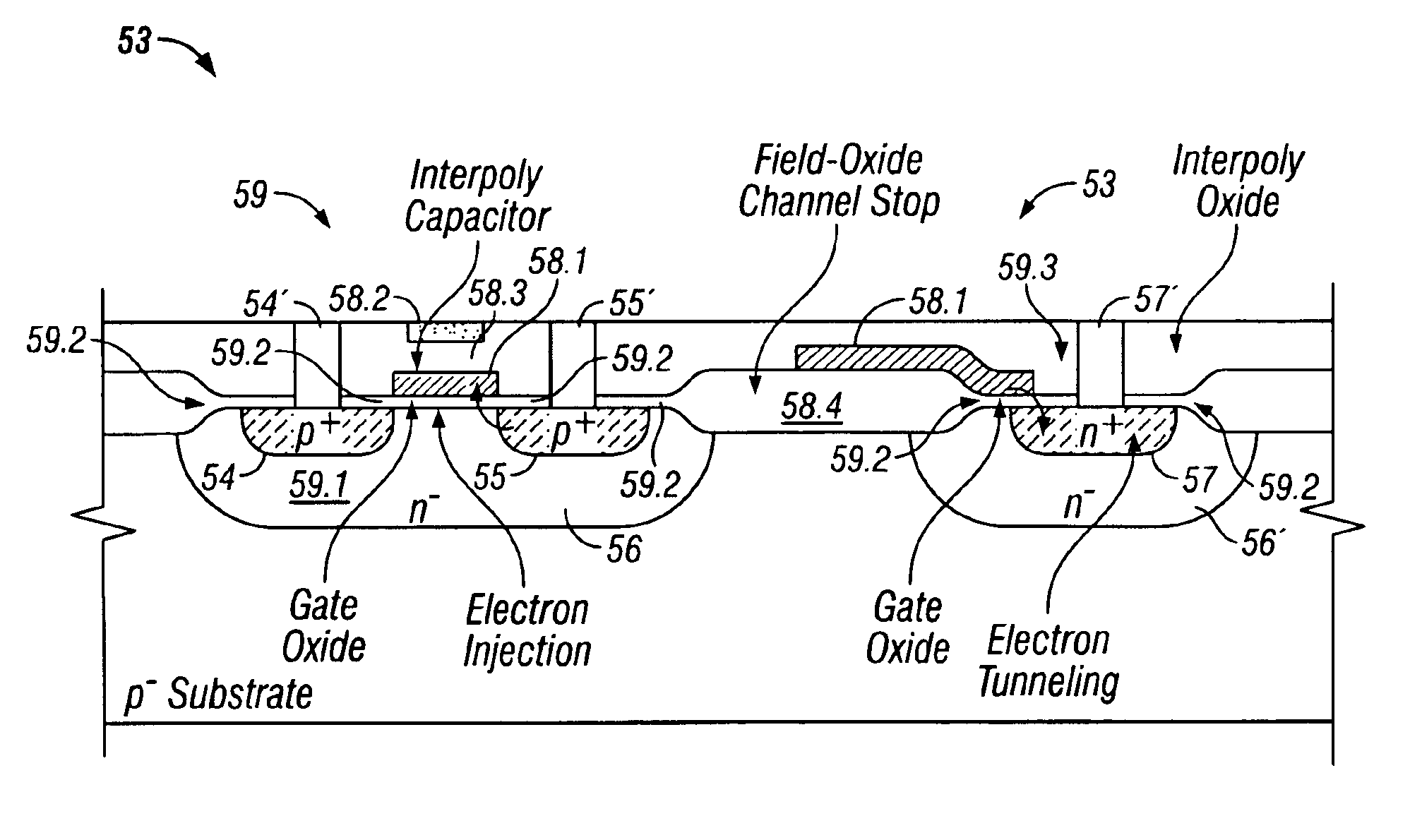

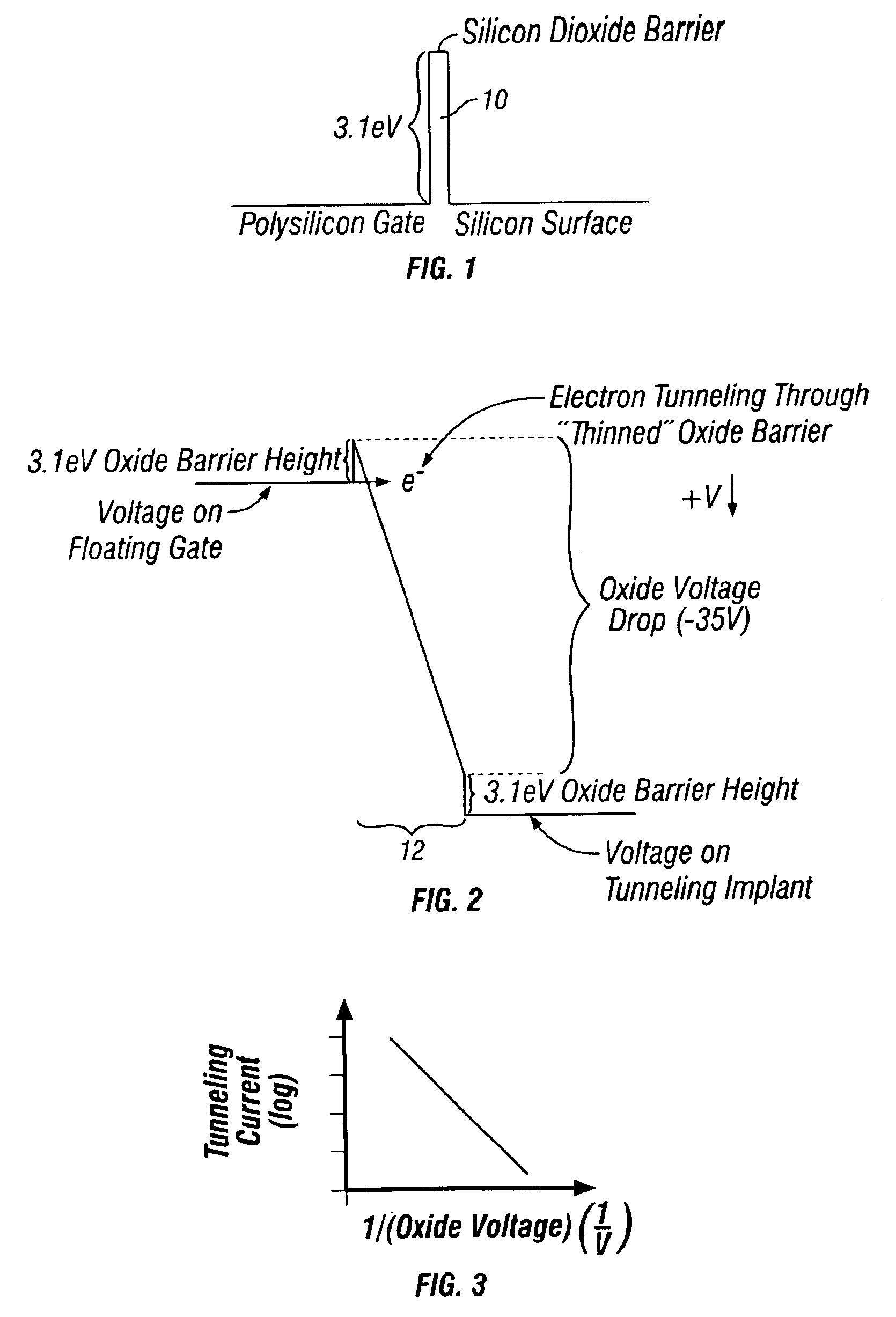

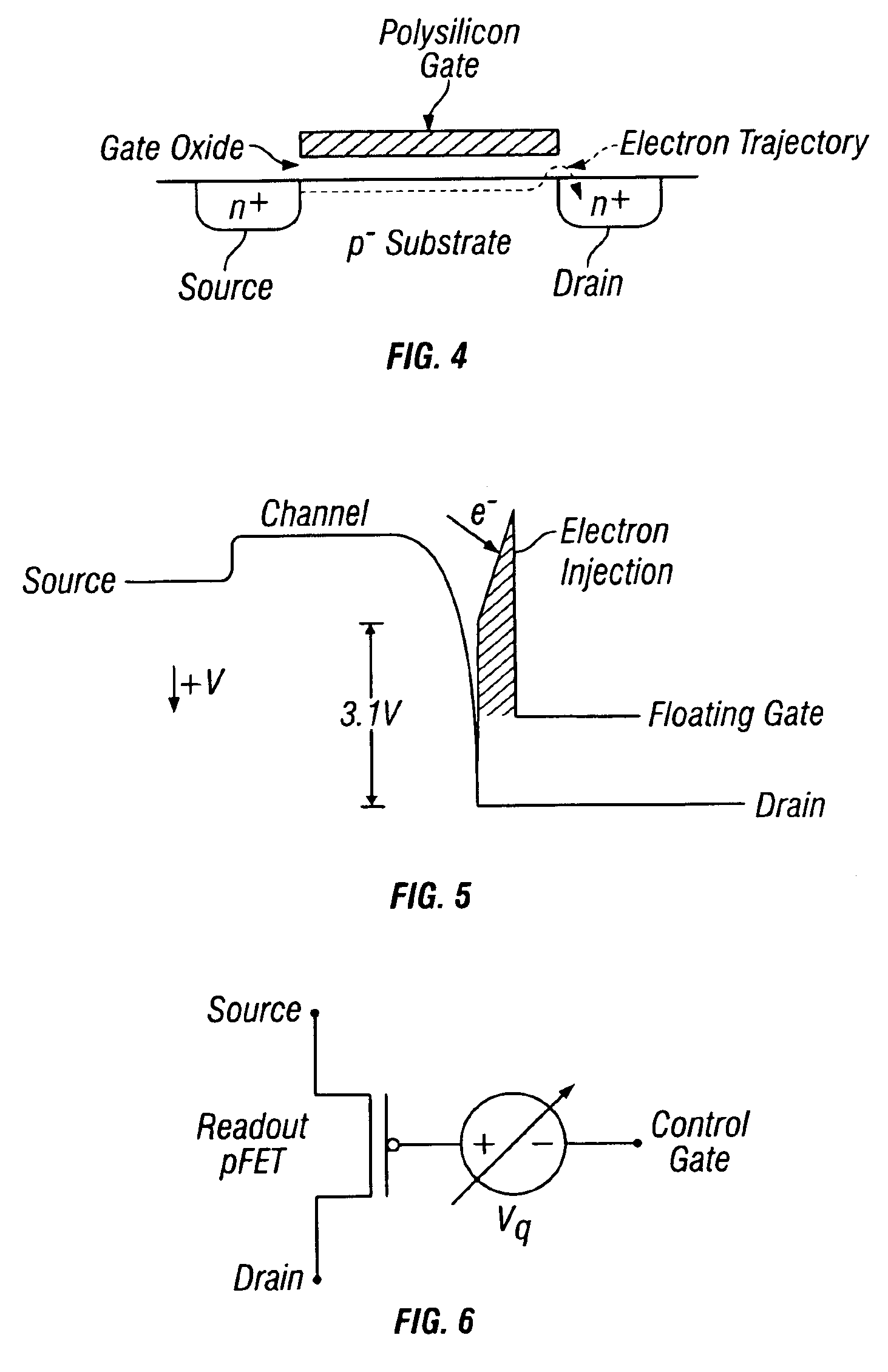

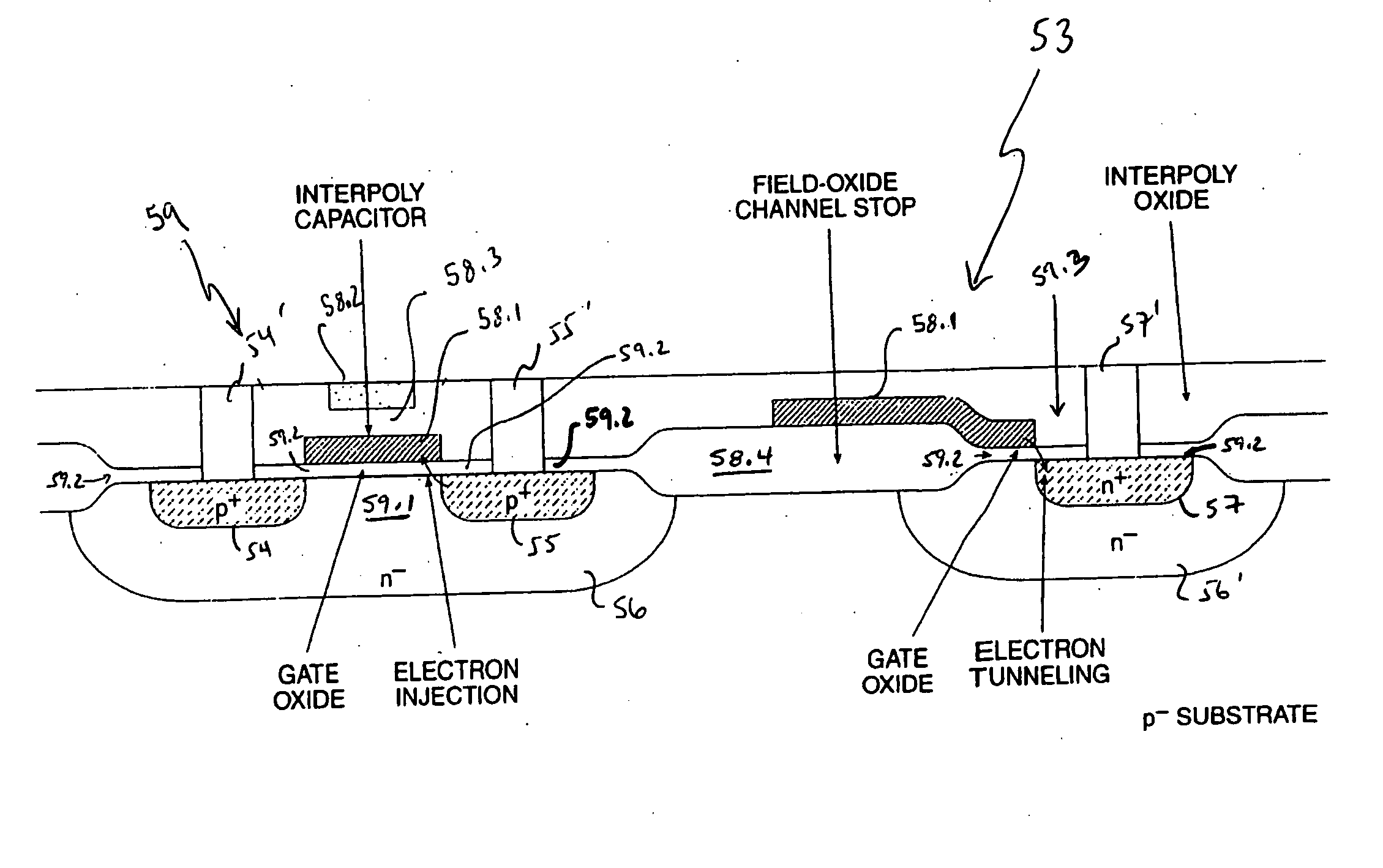

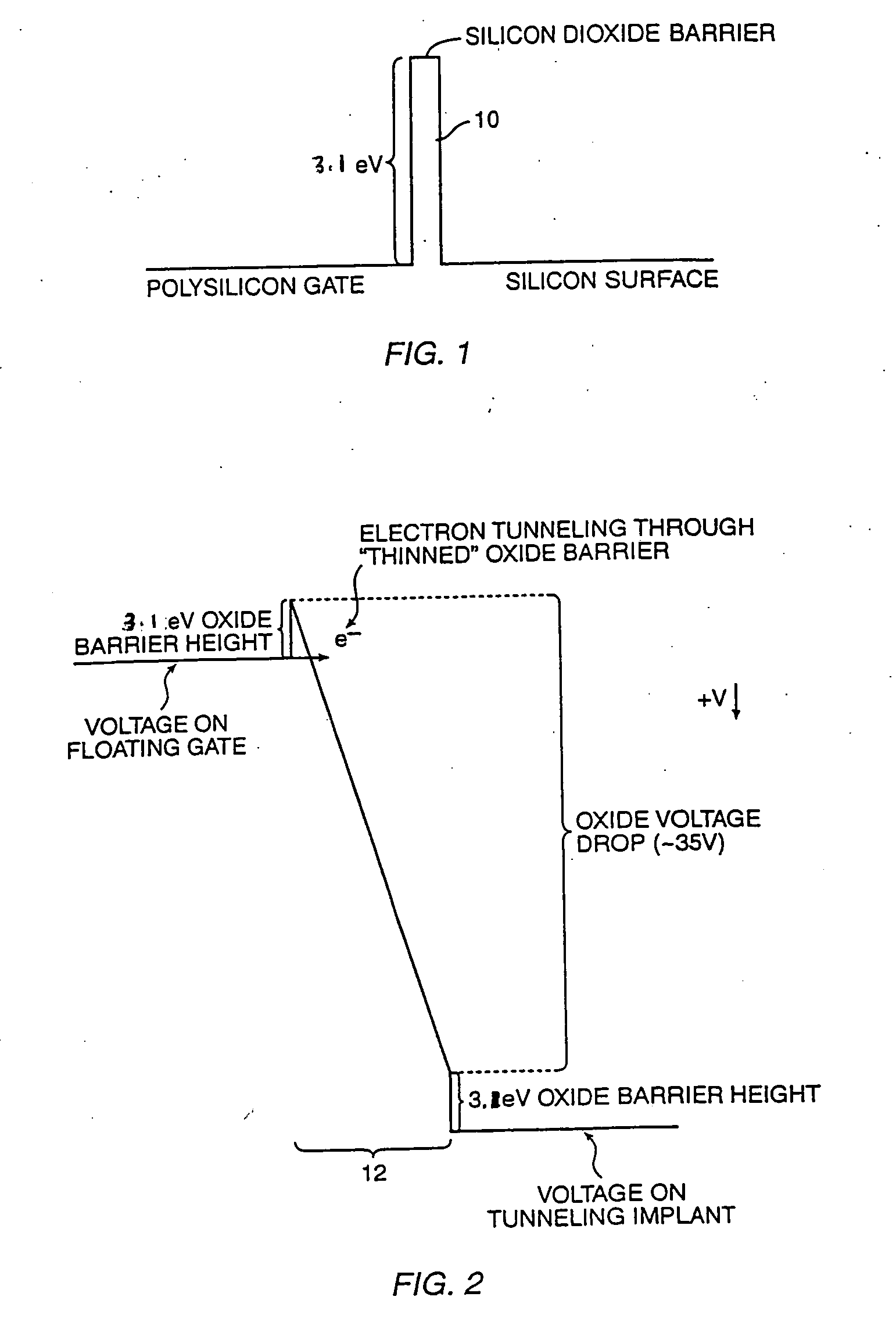

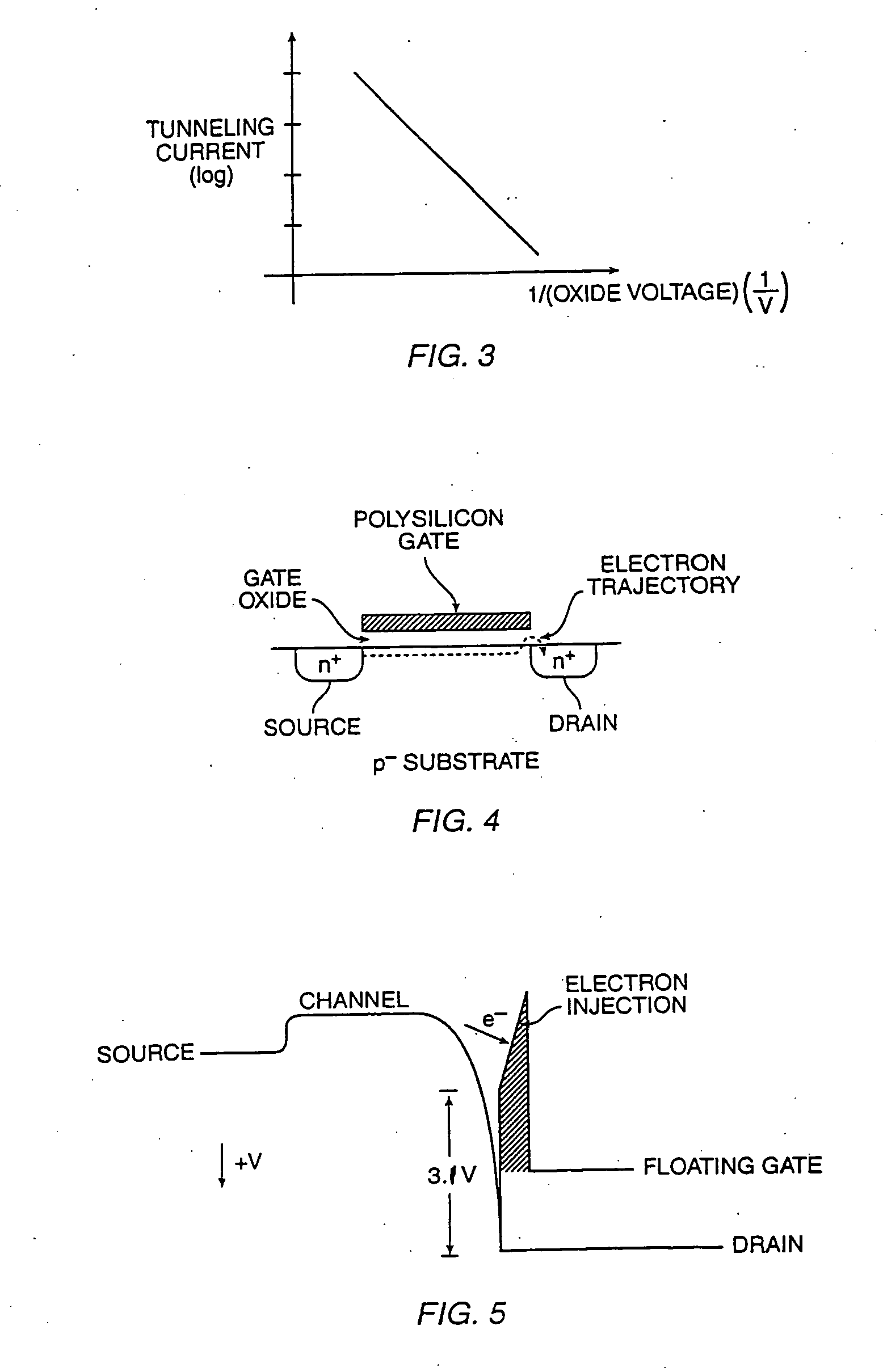

Floating-gate semiconductor structures

Hot-electron injection driven by hole impact ionization in the channel-to-drain junction of a p-channel MOSFET provides a new mechanism for writing a floating-gate memory. Various pFET floating-gate structures use a combination of this mechanism and electron tunneling to implement nonvolatile analog memory, nonvolatile digital memory, or on-line learning in silicon. The memory is nonvolatile because the devices use electrically isolated floating gates to store electronic charge. The devices enable on-line learning because the electron injection and tunneling mechanisms that write the memory can occur during normal device operation. The memory updates and learning are bidirectional because the injection and tunneling mechanisms add and remove electrons from the floating gate, respectively. Because the memory updates depend on both the stored memory and the pFETs terminal voltages, and because they are bidirectional, the devices can implement on-line learning functions.

Owner:SYNOPSYS INC +1

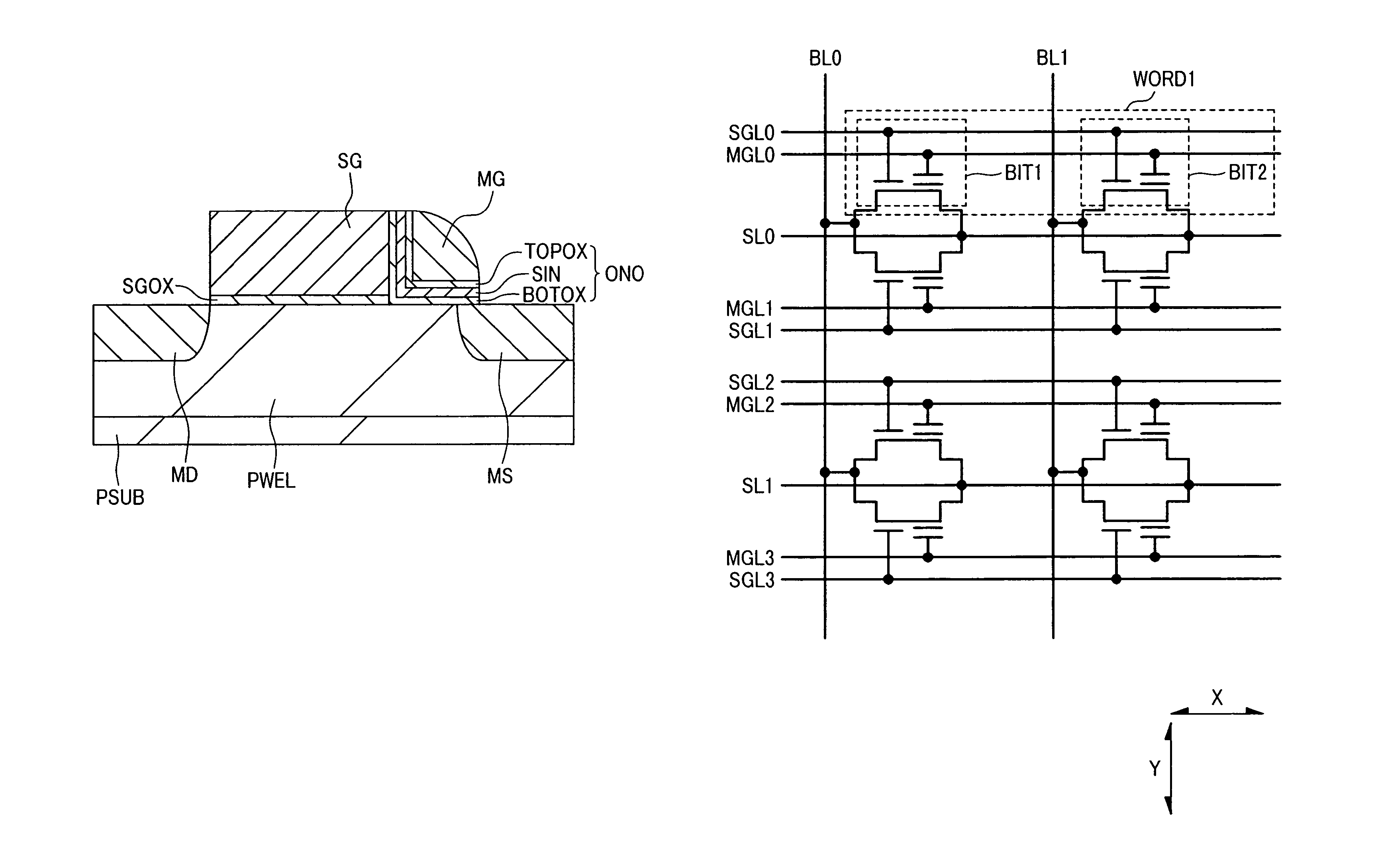

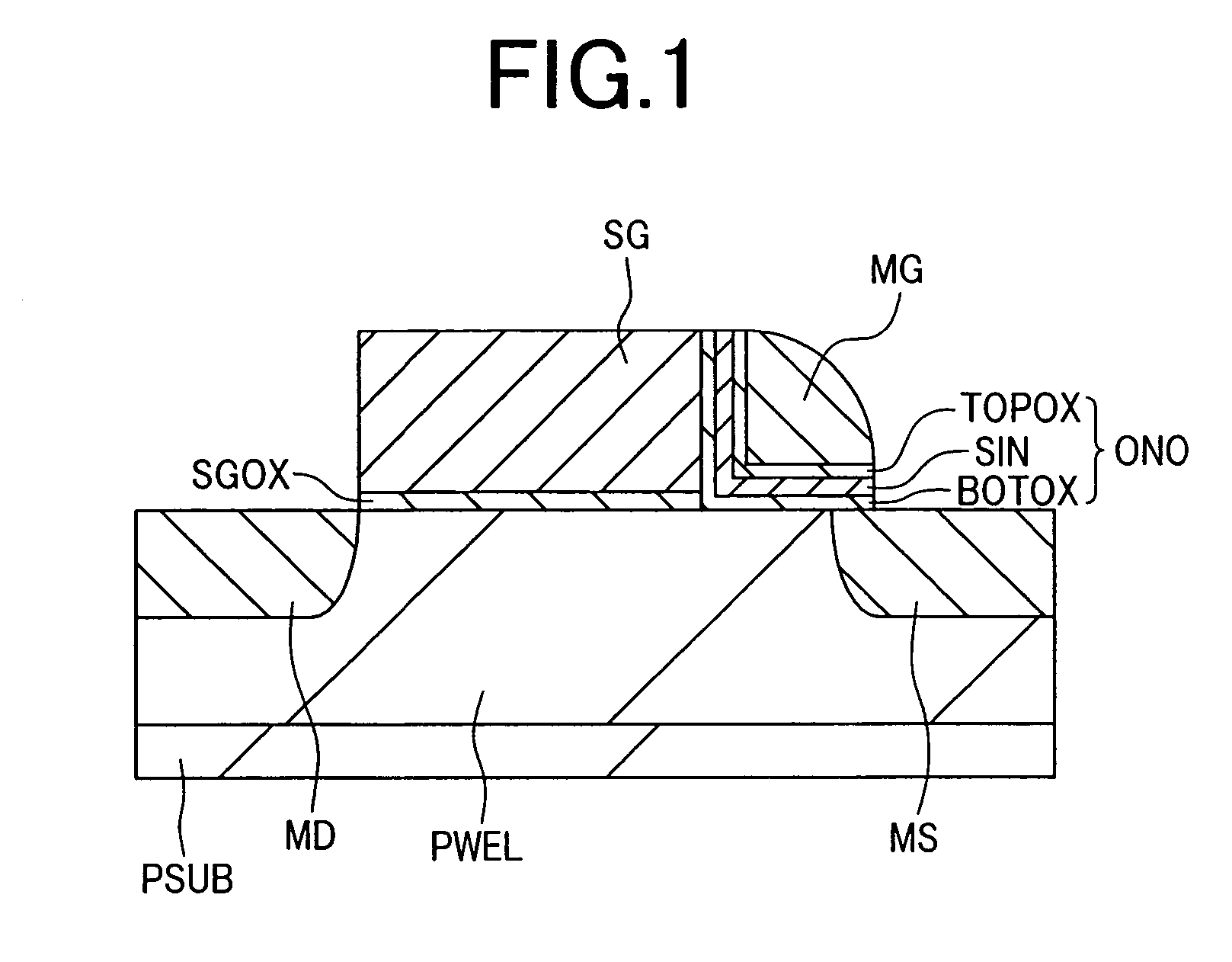

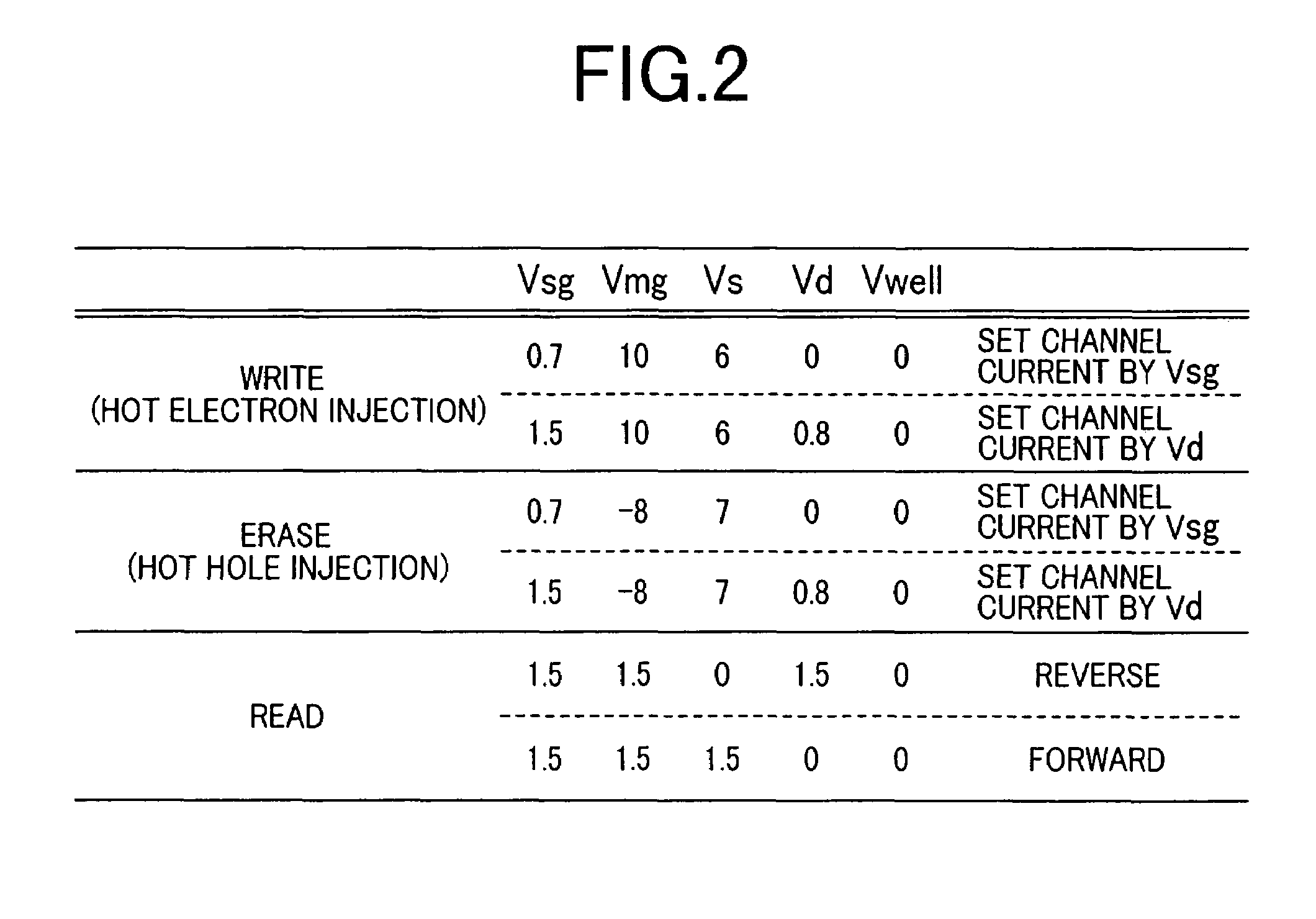

Nonvolatile semiconductor memory device

ActiveUS6972997B2Improve performanceImprove reliabilityTransistorSolid-state devicesElectron flowImpact ionization

Characteristics of a nonvolatile semiconductor memory device are improved. The memory cell comprises: an ONO film constituted by a silicon nitride film SIN for accumulating charge and by oxide films BOTOX and TOPOX disposed thereon and thereunder; a memory gate electrode MG disposed at an upper portion thereof; a select gate electrode SG disposed at a side portion thereof through the ONO film; a gate oxide film SGOX disposed thereunder. By applying a potential to a select gate electrode SG of a memory cell having a source region MS and a drain region MD and to the source region MS and by accelerating electrons flowing in a channel through a high electric field produced between a channel end of the select transistor and an end of an n-type doped region ME disposed under the memory gate electrode MG, hot holes are generated by impact ionization, and the hot holes are injected into a silicon nitride film SIN by a negative potential applied to the memory gate electrode MG, and thereby an erase operation is performed.

Owner:TESSERA ADVANCED TECH

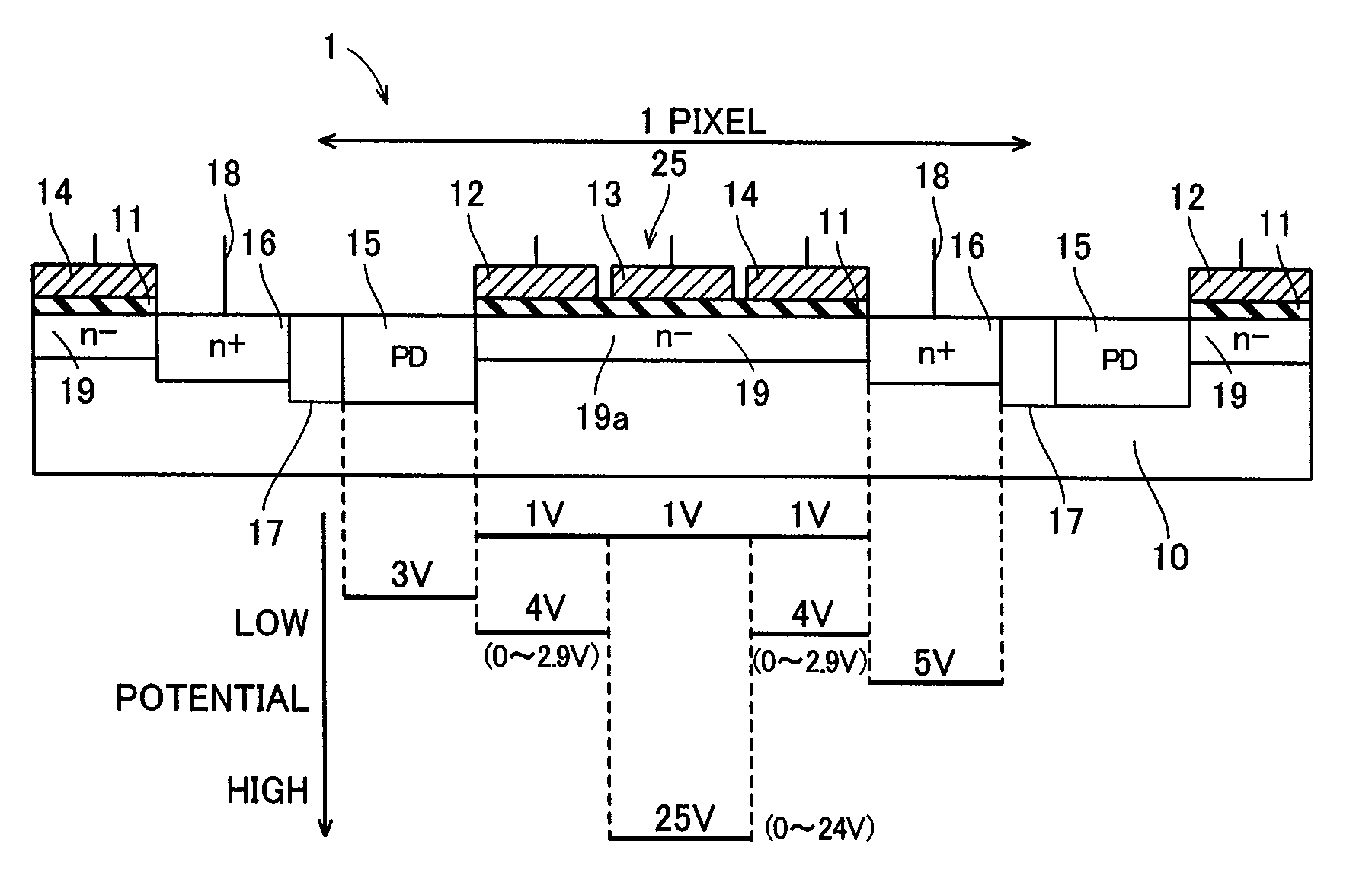

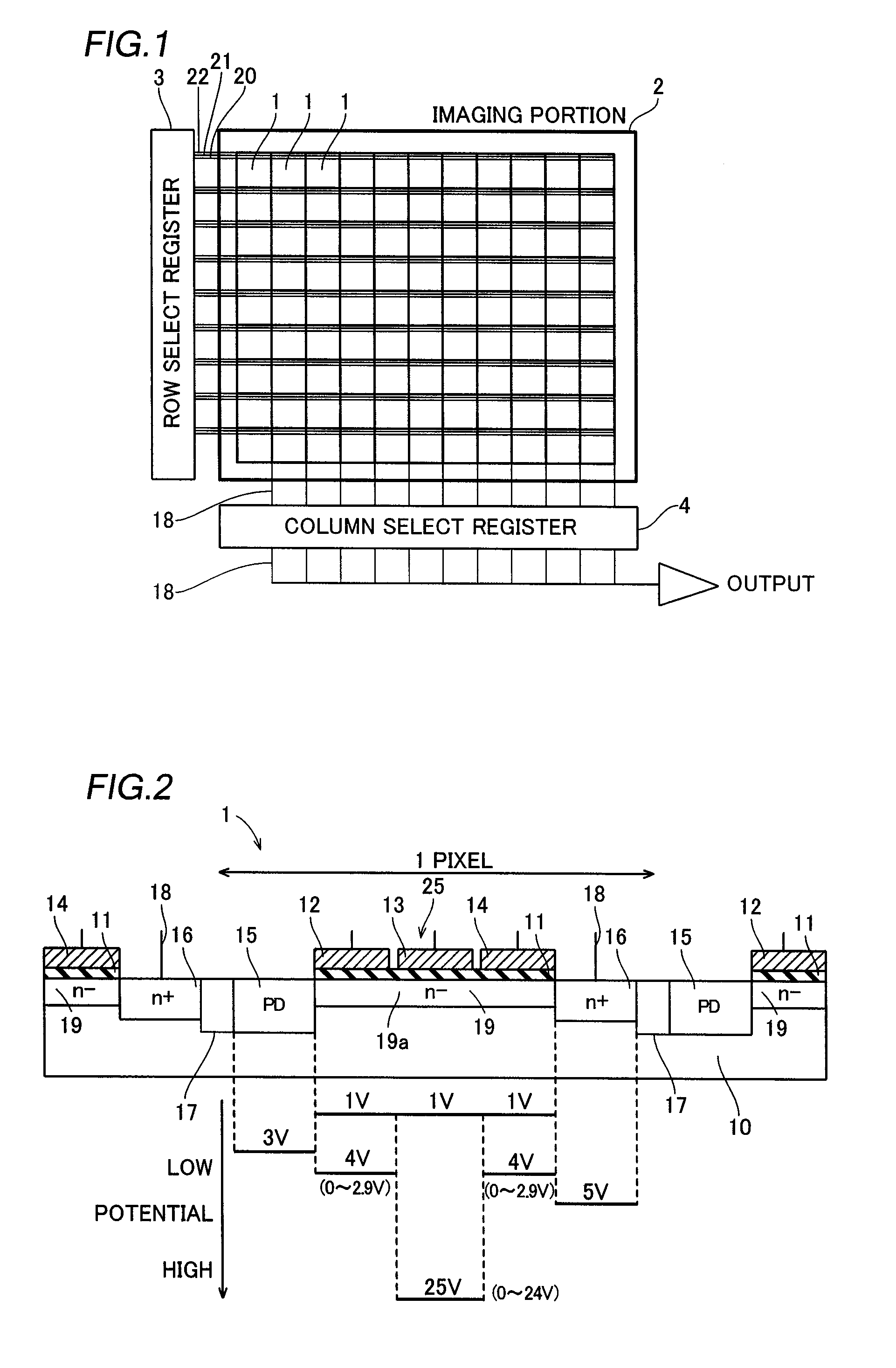

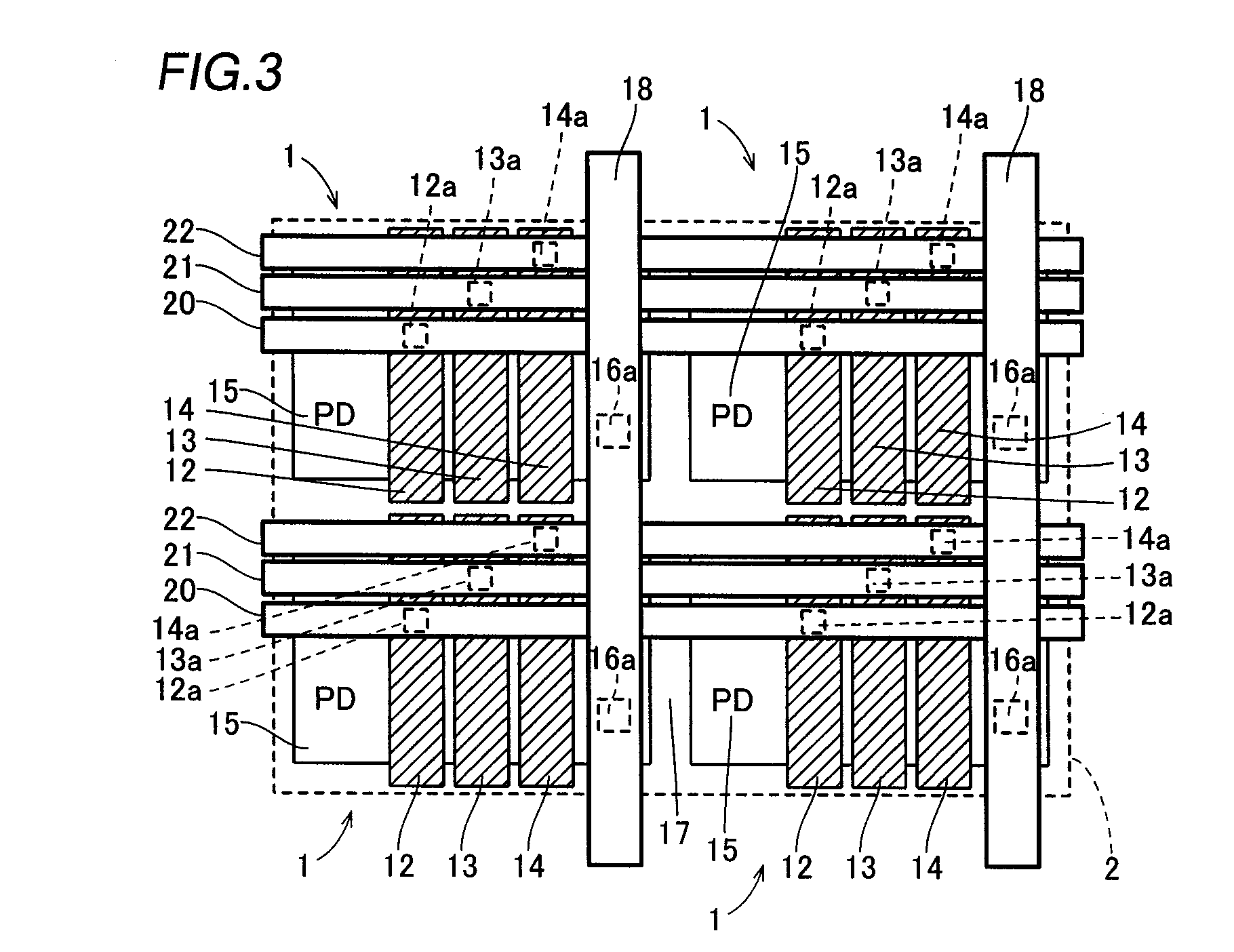

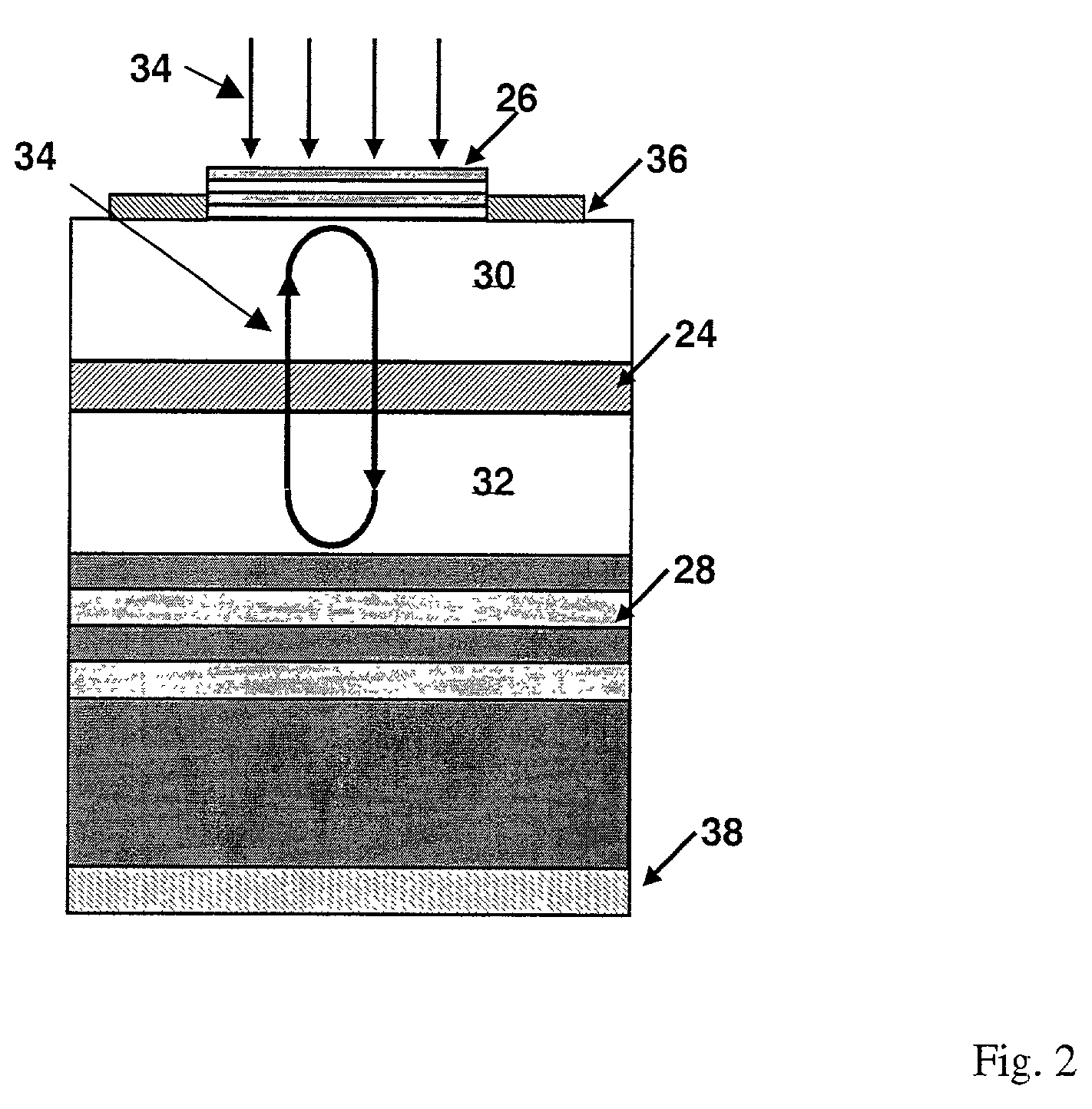

Imaging device

InactiveUS20070176213A1Television system detailsTelevision system scanning detailsCarrier signalMiniaturization

An imaging device capable of multiplying carriers and miniaturizing the device is obtained. The imaging device includes a carrier storage portion for storing carriers generated by photoelectric conversion, having a photoelectric conversion function, a multiplier section including a multiplier electrode applying an electric field for multiplying carriers due to impact ionization by an electric field, one first transfer electrode so provided between the carrier storage portion and the multiplier electrode as to be adjacent to the carrier storage portion and the multiplier electrode.

Owner:SANYO ELECTRIC CO LTD

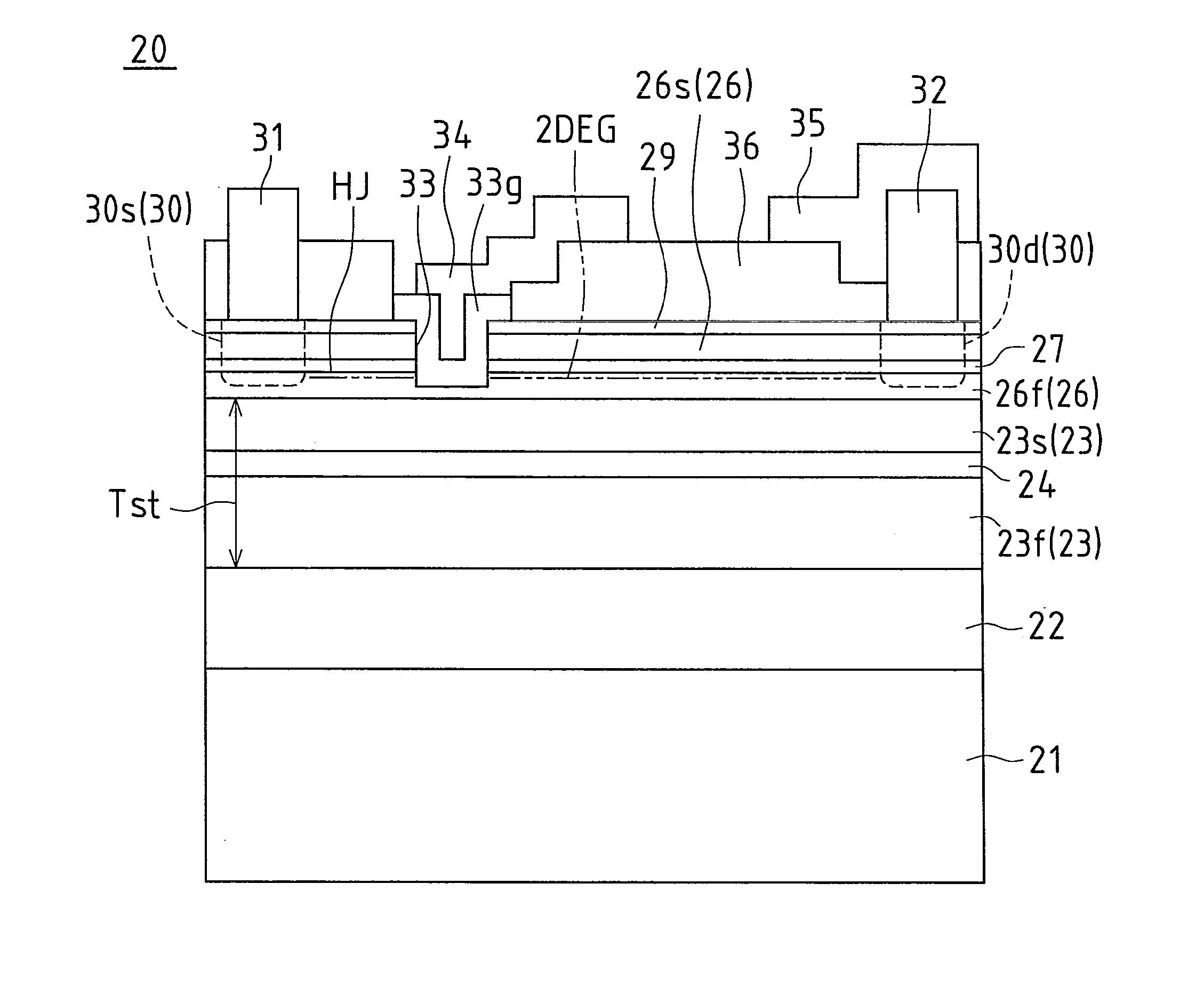

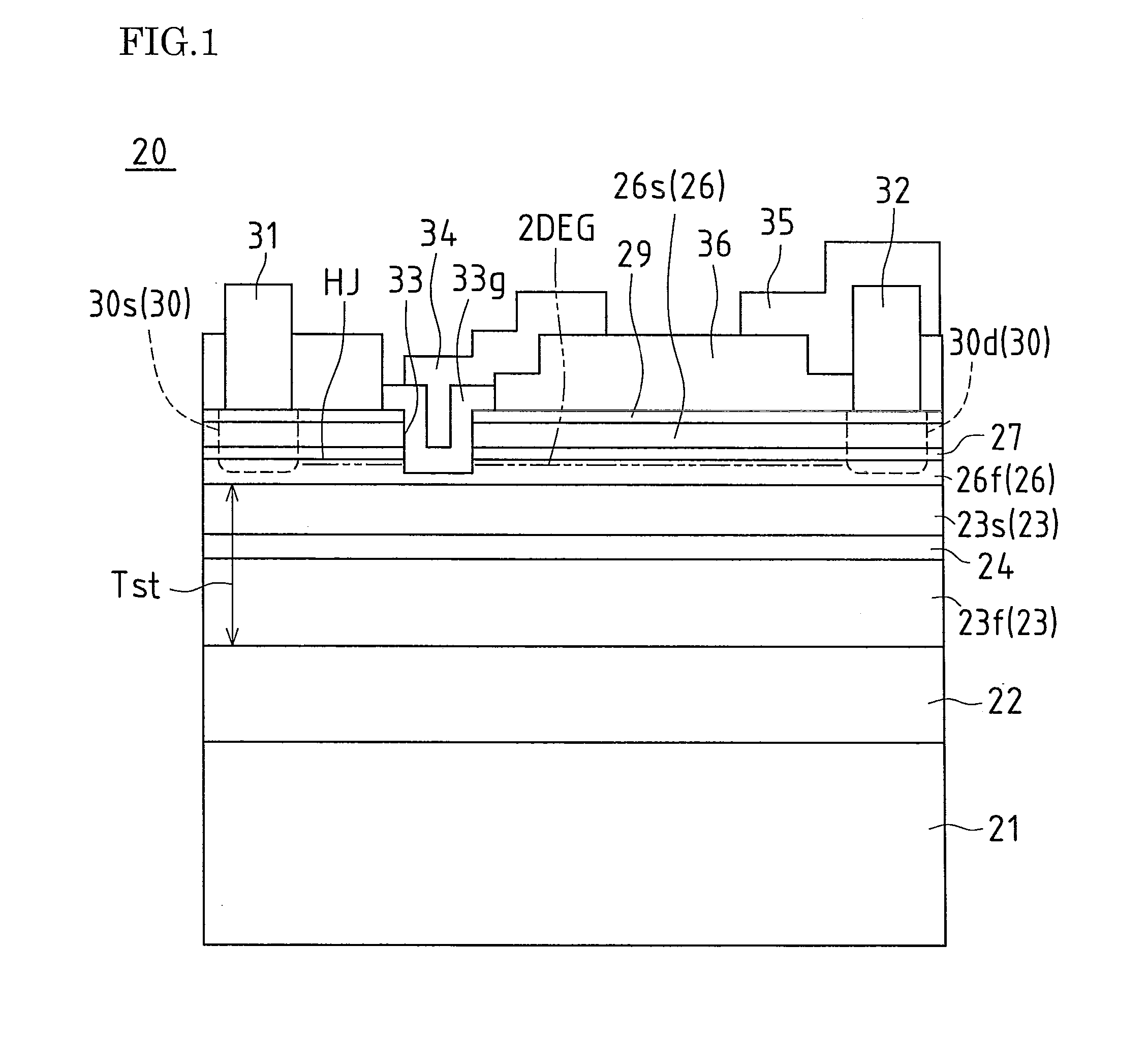

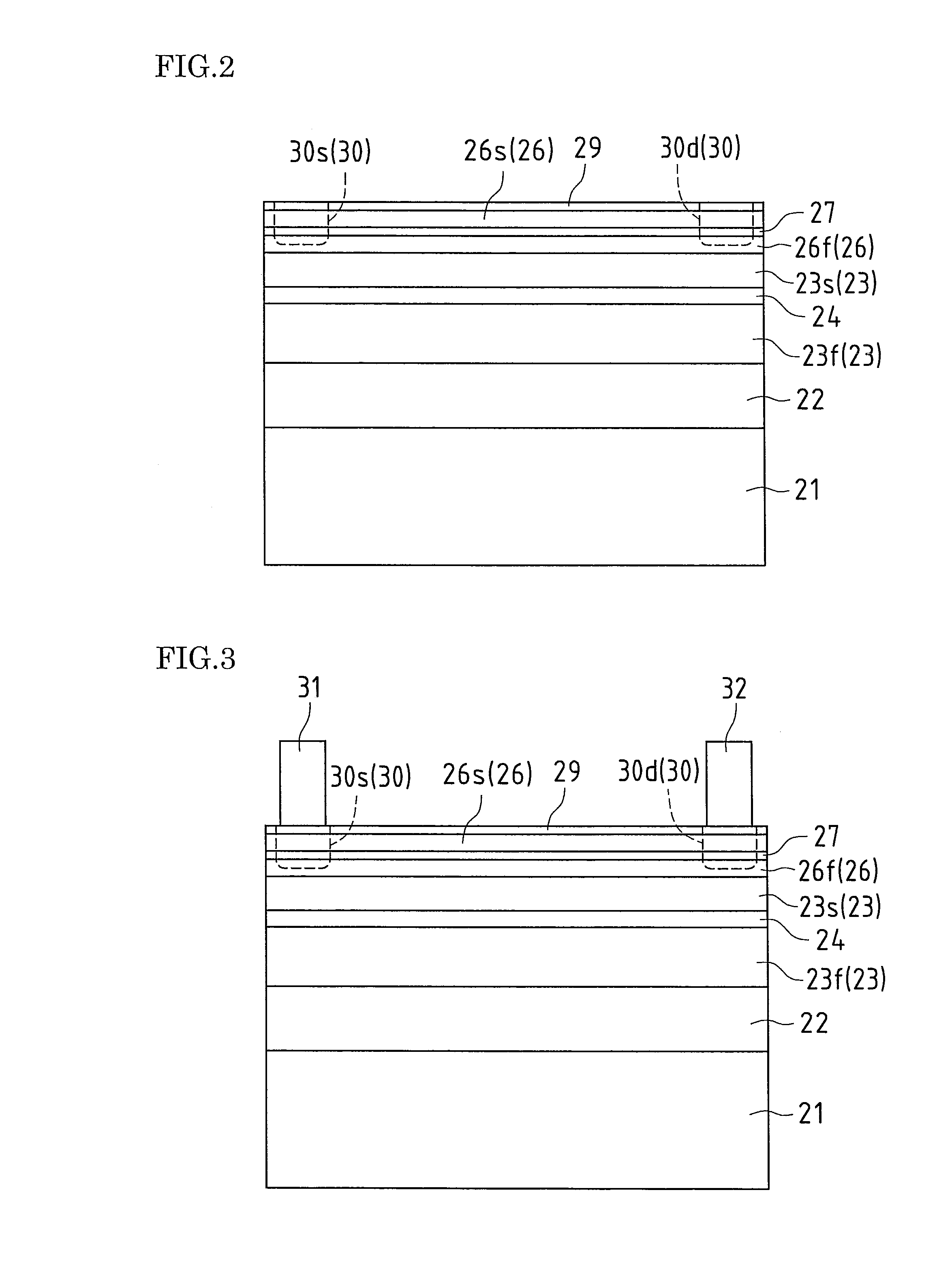

Semiconductor device

InactiveUS20100314663A1Effective absorptionImprove accuracySemiconductor devicesControl layerImpact ionization

One embodiment of a semiconductor device according to the present invention includes a substrate, a base compound semiconductor layer layered on the substrate to form a base, a channel defining compound semiconductor layer layered on the base compound semiconductor layer to define a channel, and an impact ionization control layer that is layered within a layering range of the base compound semiconductor layer and controls the location of impact ionization, wherein the base compound semiconductor layer is formed of a first compound semiconductor, the channel defining compound semiconductor layer is formed of a second compound semiconductor, and the impact ionization control layer is formed of a third compound semiconductor that has a smaller band gap than the first compound semiconductor.

Owner:SHARP KK

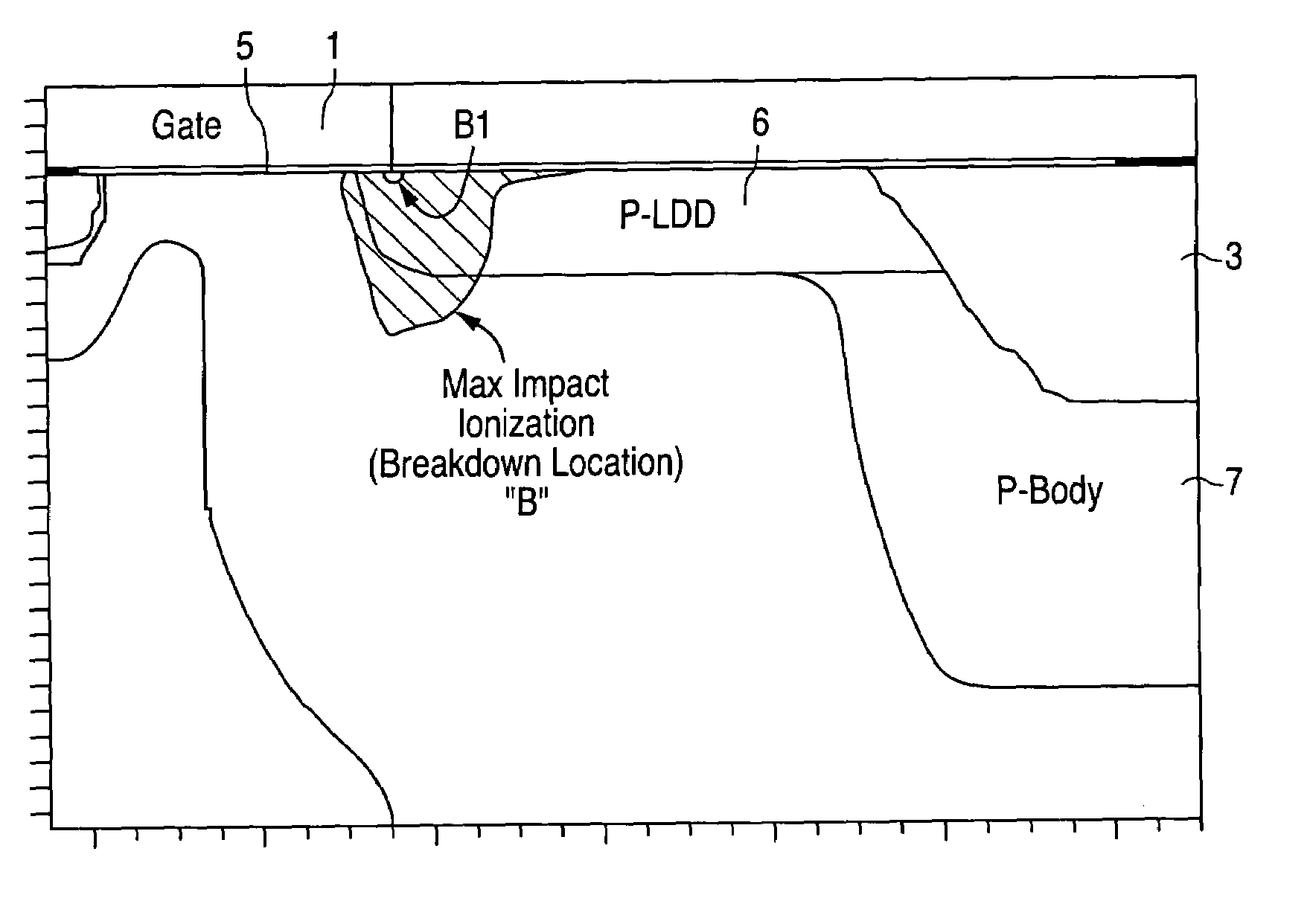

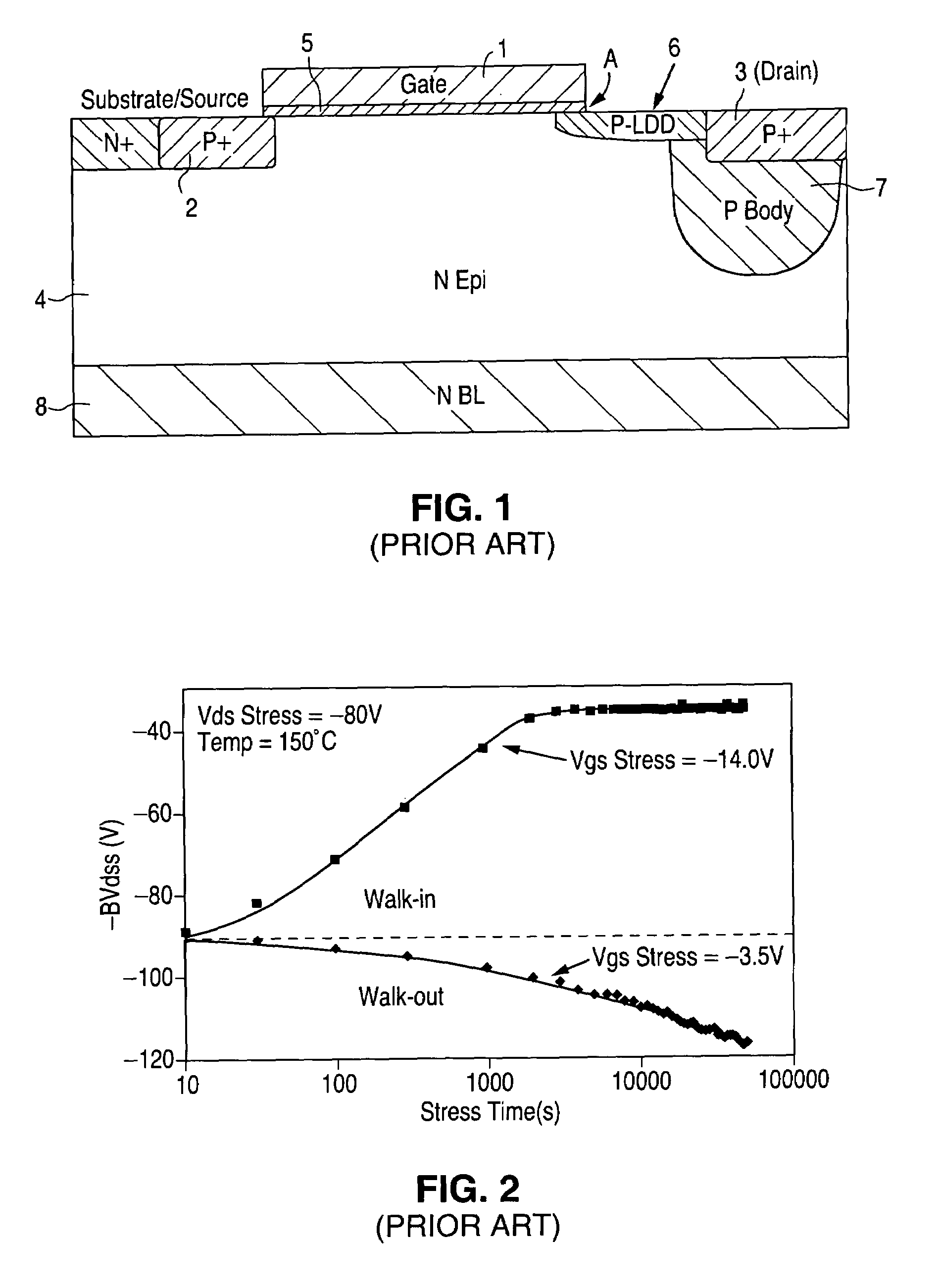

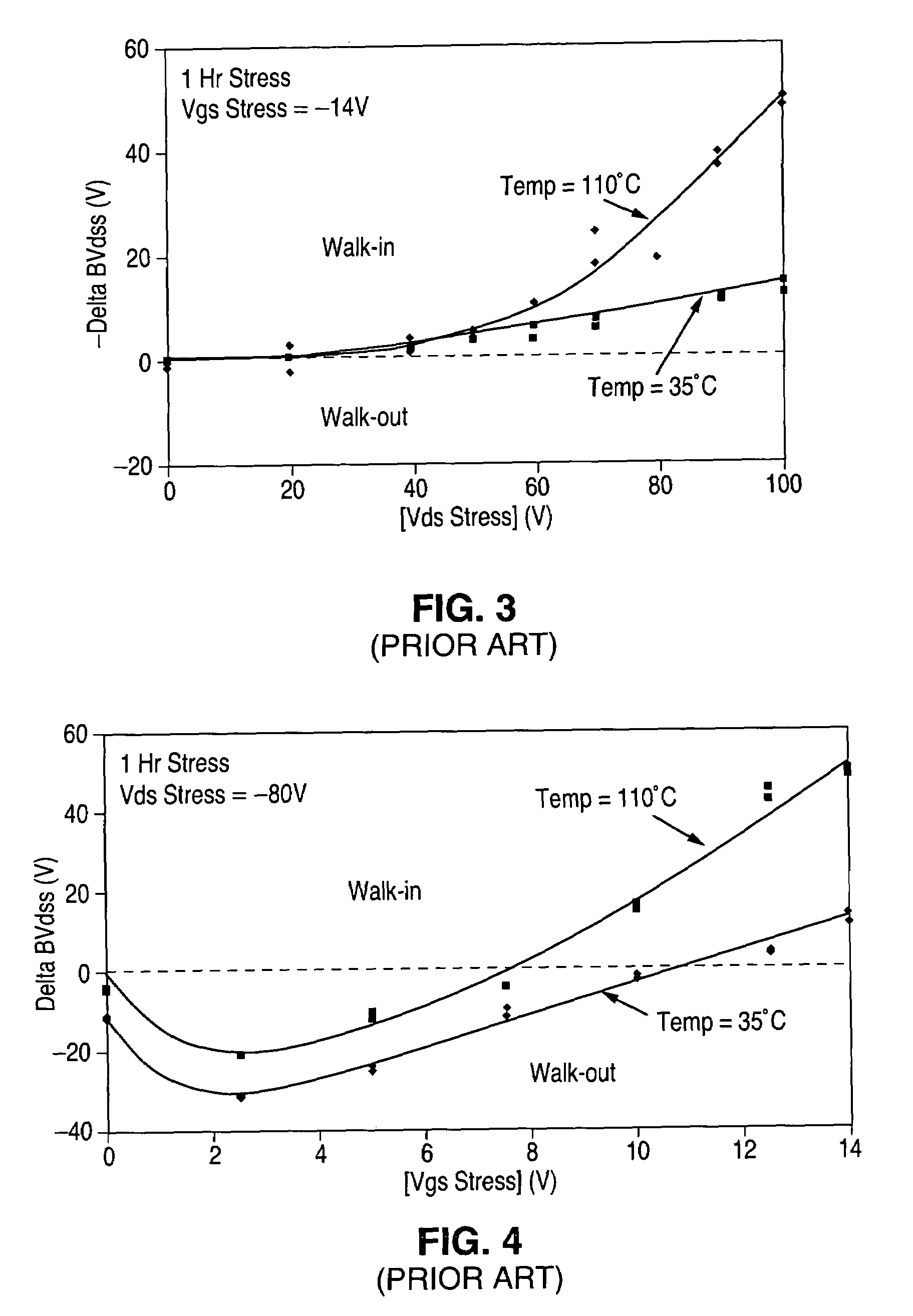

PMOS device with drain junction breakdown point located for reduced drain breakdown voltage walk-in and method for designing and manufacturing such device

ActiveUS7180140B1Semiconductor/solid-state device detailsSolid-state devicesImpact ionizationHigh pressure

A PMOS device can be designed and manufactured in accordance with the invention to locate its drain junction breakdown point and maximum impact ionization point to reduce or eliminate drain breakdown voltage walk-in. In some embodiments, the drain junction breakdown point and maximum impact ionization point are located sufficiently far from the gate that the device exhibits no significant drain breakdown voltage walk-in. The device can be a high voltage power transistor having an extended drain region including a P-type lightly doped drain (P-LDD) implant, with drain junction breakdown and maximum impact ionization points appropriately located by controlling the implant dose employed to produce the P-LDD implant. Other aspects of the invention are methods for designing a PMOS device including by determining relative locations of the gate and at least one of the drain junction breakdown and maximum impact ionization points to reduce drain breakdown voltage walk-in, and methods for manufacturing integrated circuits including any embodiment of the PMOS device of the invention.

Owner:NAT SEMICON CORP

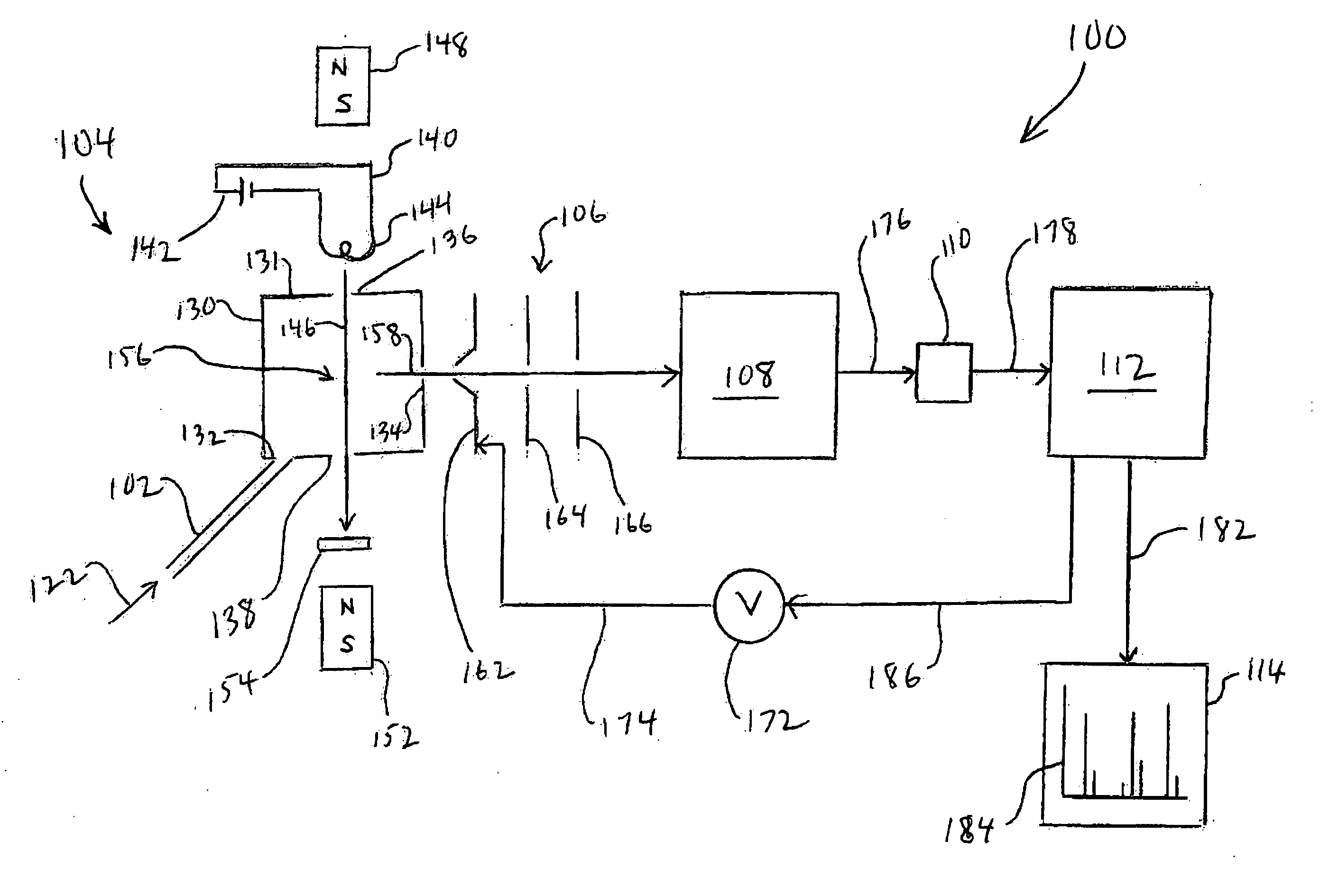

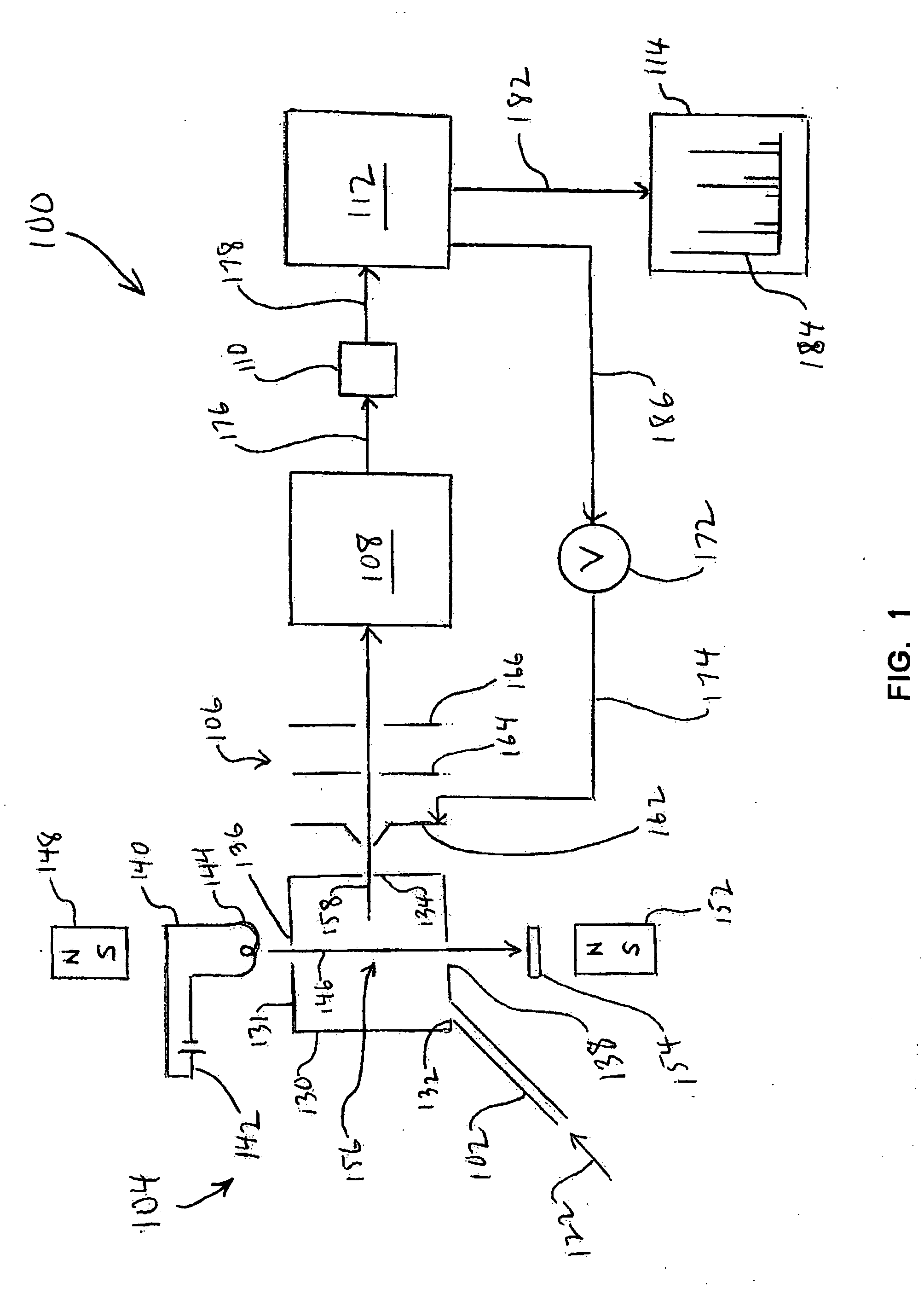

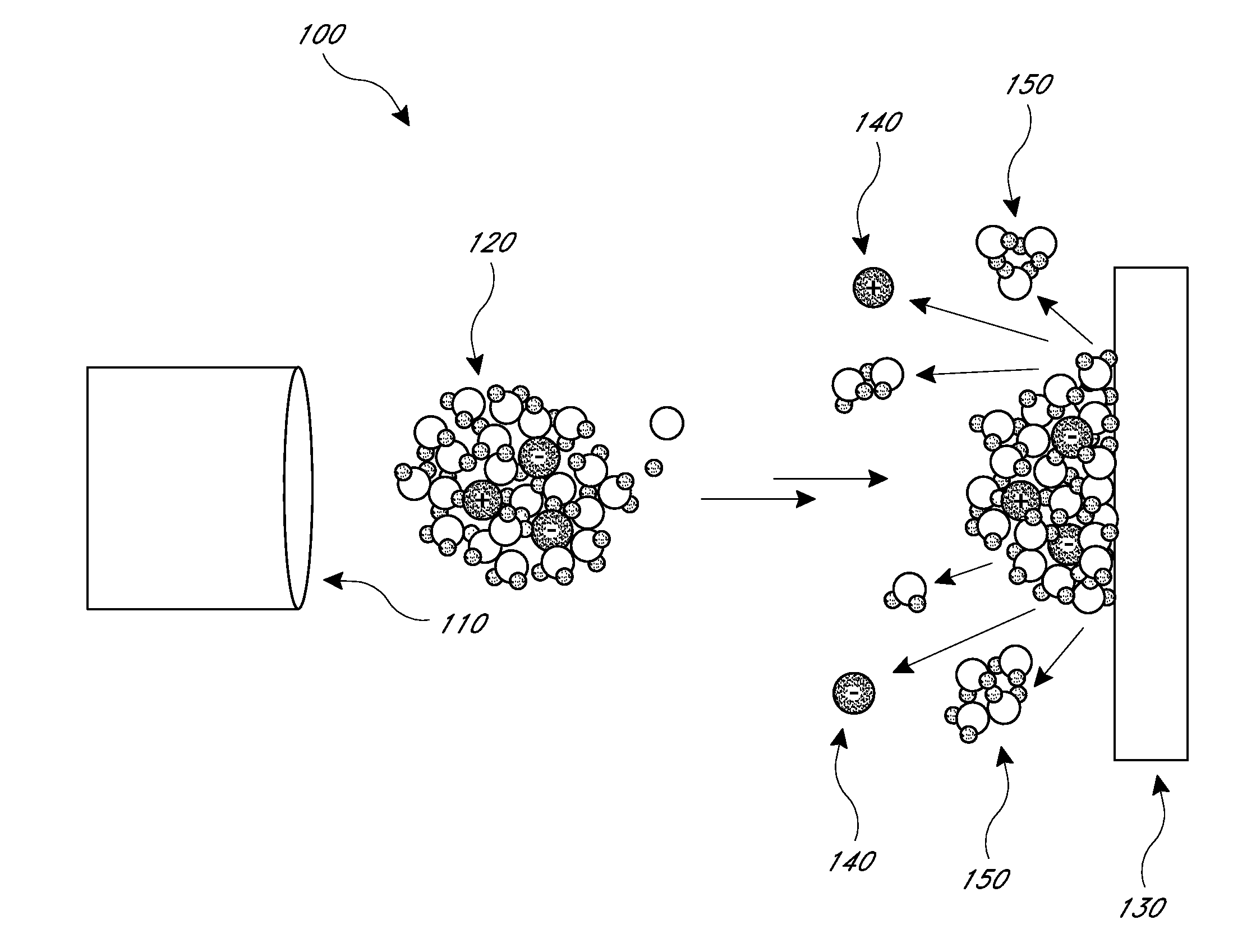

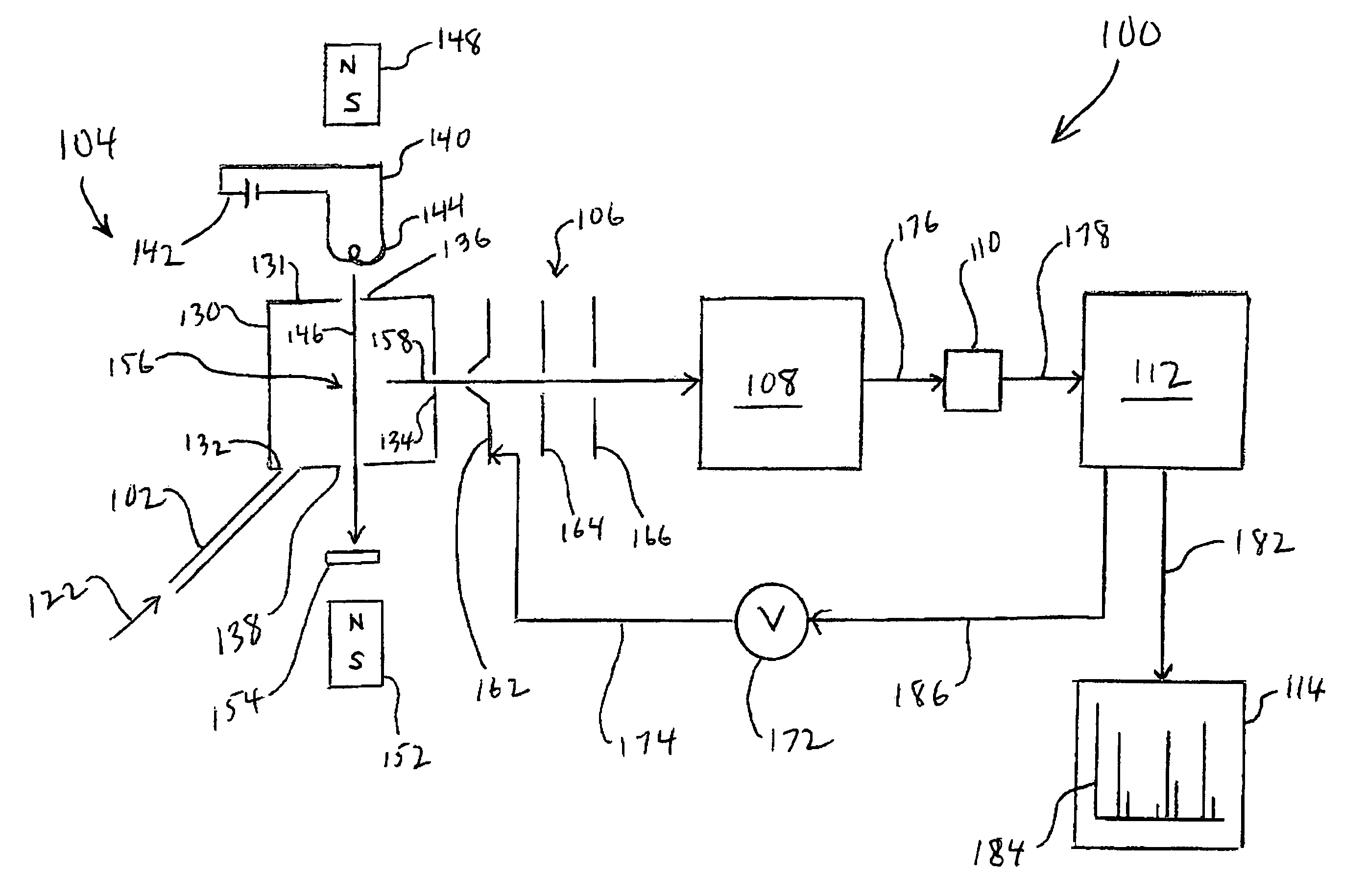

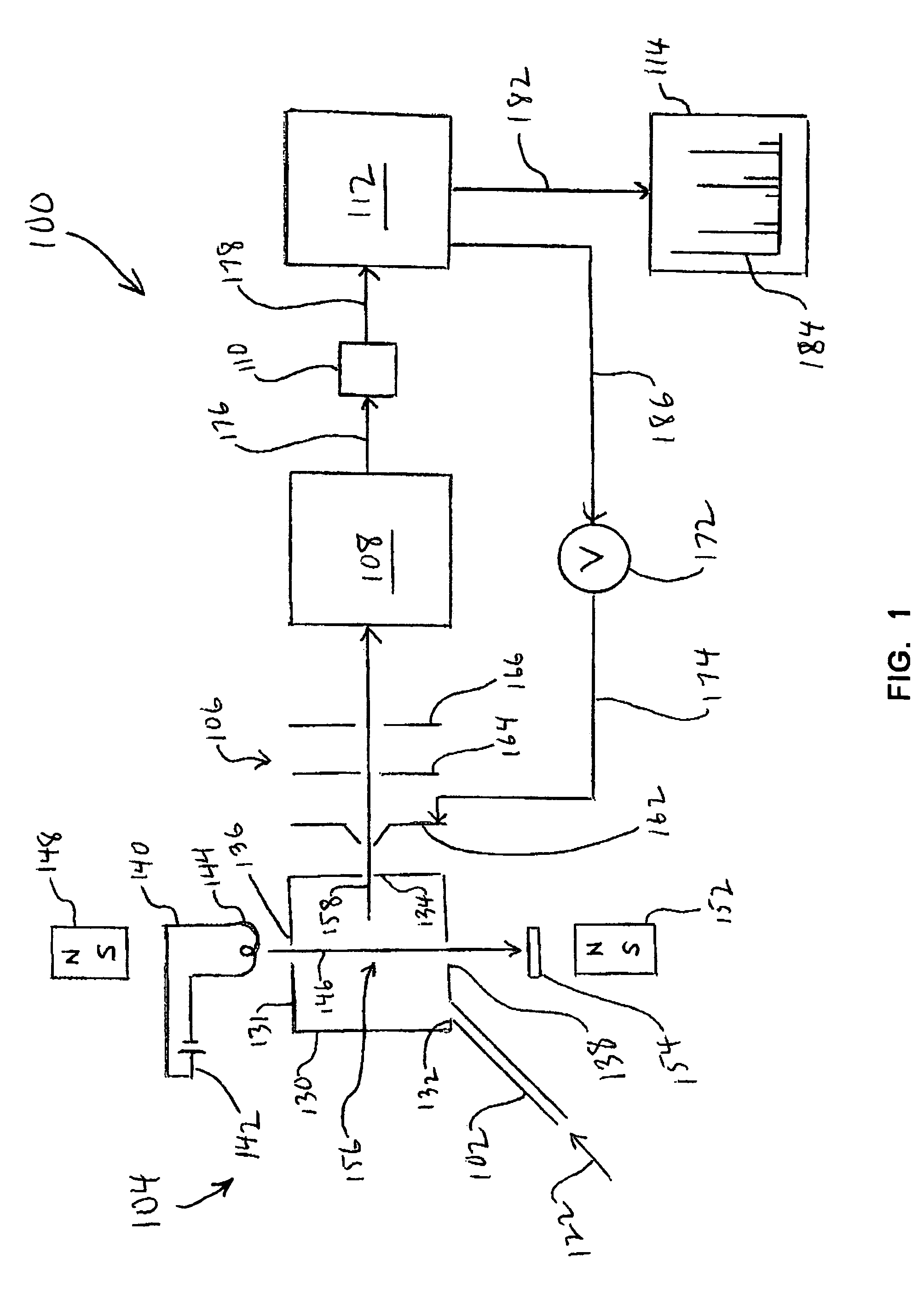

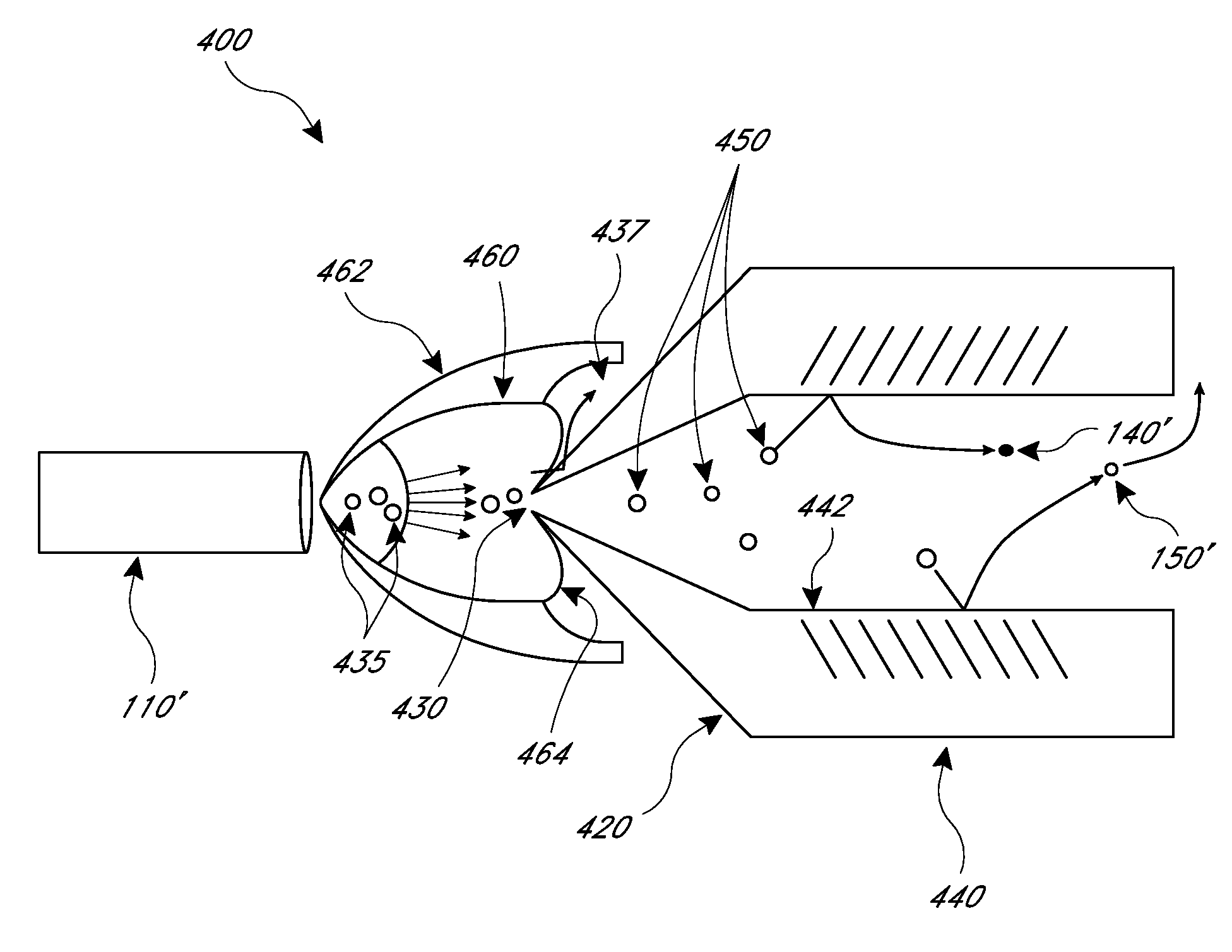

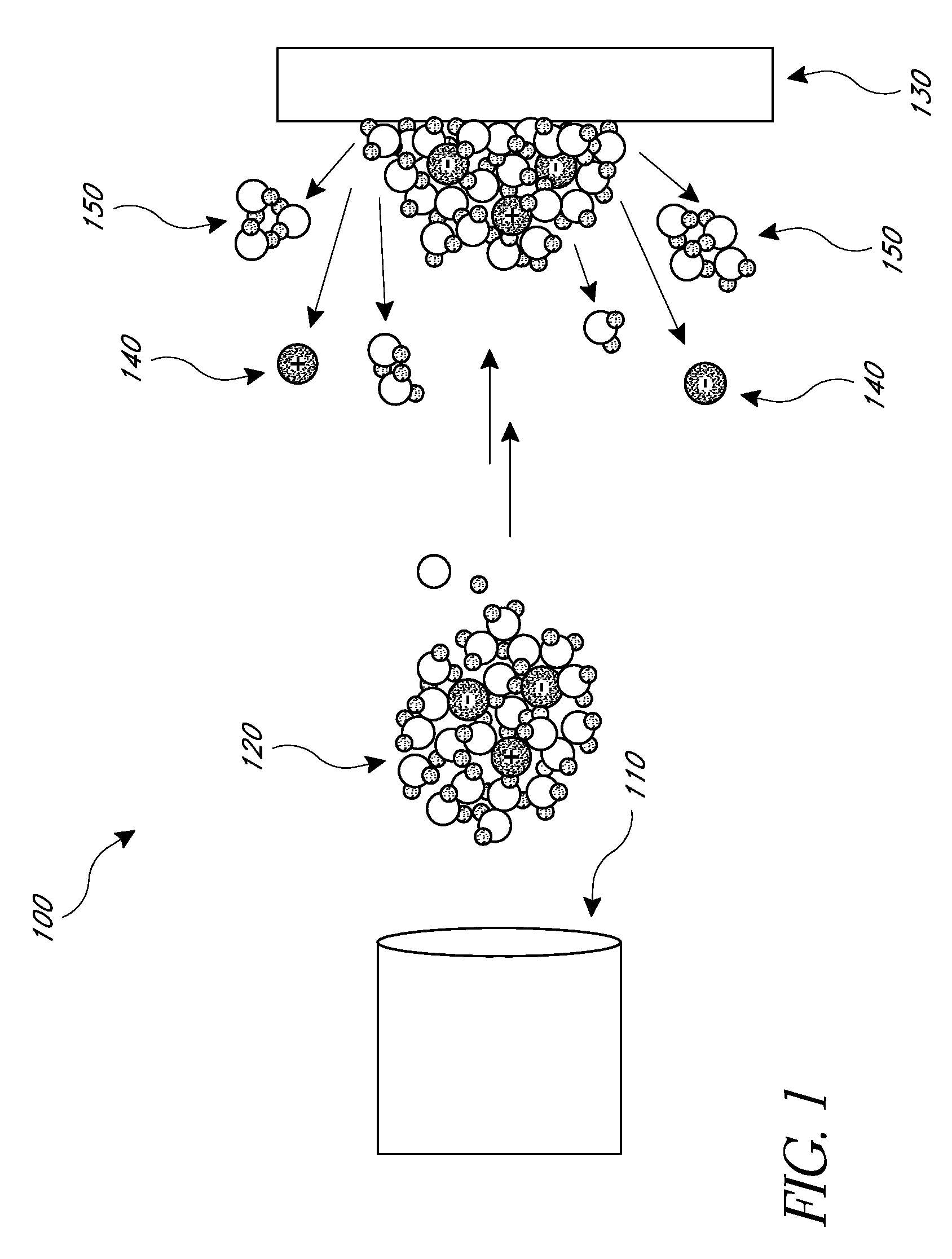

Collision ion generator and separator

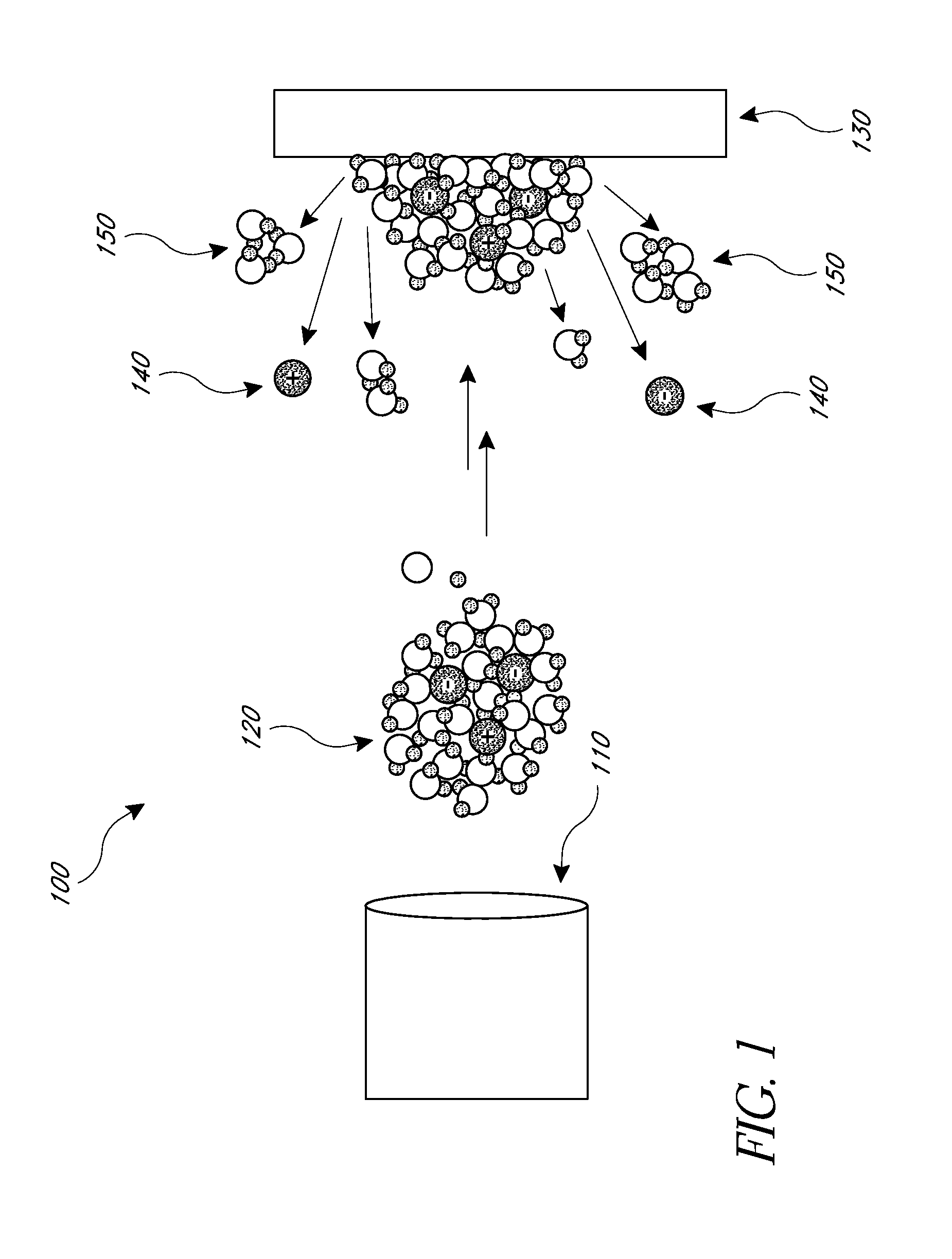

ActiveUS20140353489A1Provide informationSamples introduction/extractionMaterial analysis by electric/magnetic meansImpact ionizationComputational chemistry

According to some embodiments, systems and methods for surface impact ionization of liquid phase and aerosol samples are provided. The method includes accelerating a liquid or aerosol sample, colliding the sample with a solid collision surface thereby disintegrating the sample into both molecular ionic species (e.g., gaseous molecular ions) and molecular neutral species (e.g., gaseous sample), and transporting the disintegrated sample to an ion analyzer. Some embodiments of the method further comprise discarding the molecular neutral species. Such embodiments transport substantially only the molecular ionic species to the ion analyzer.

Owner:MEDIMASS +1

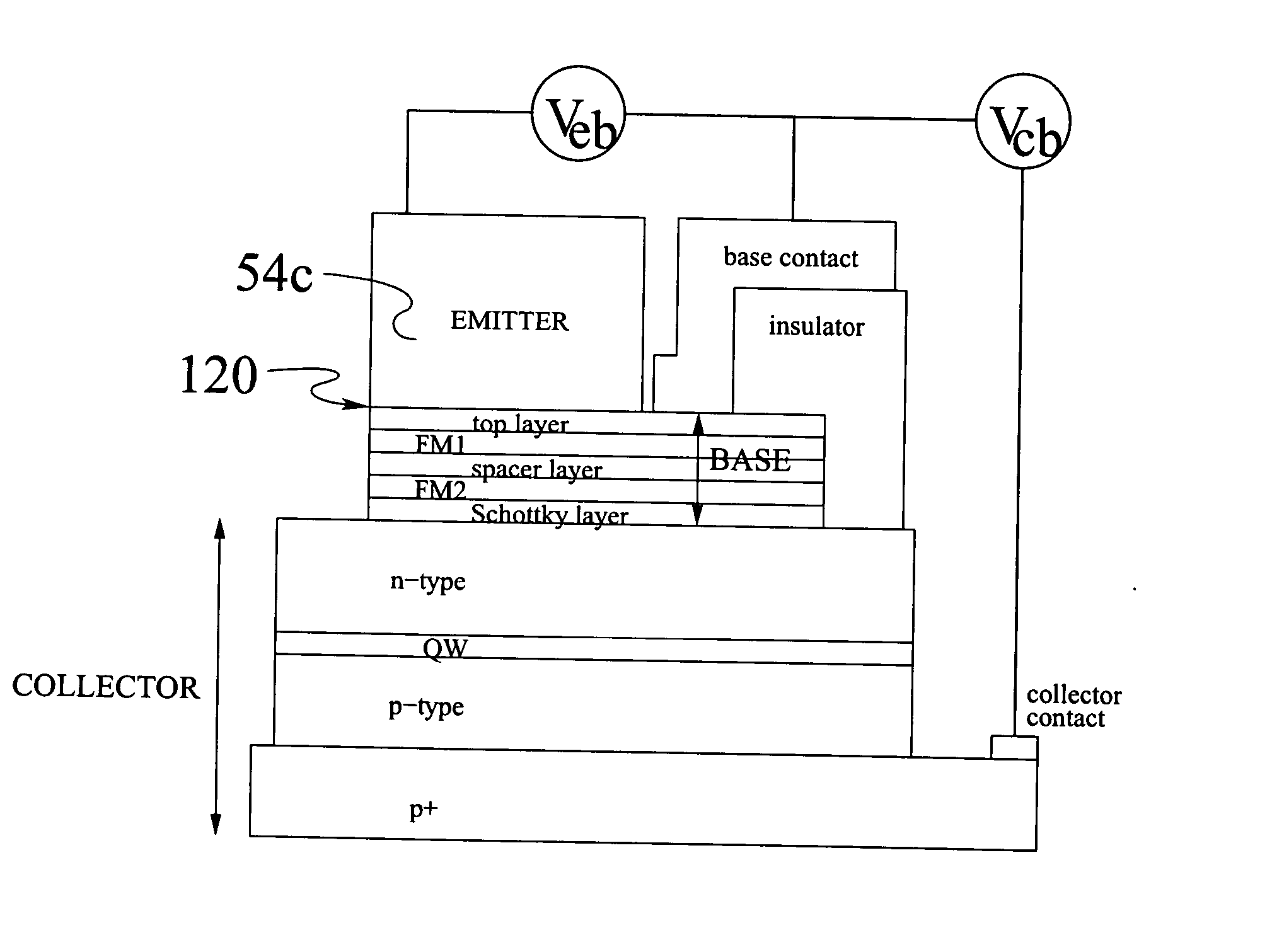

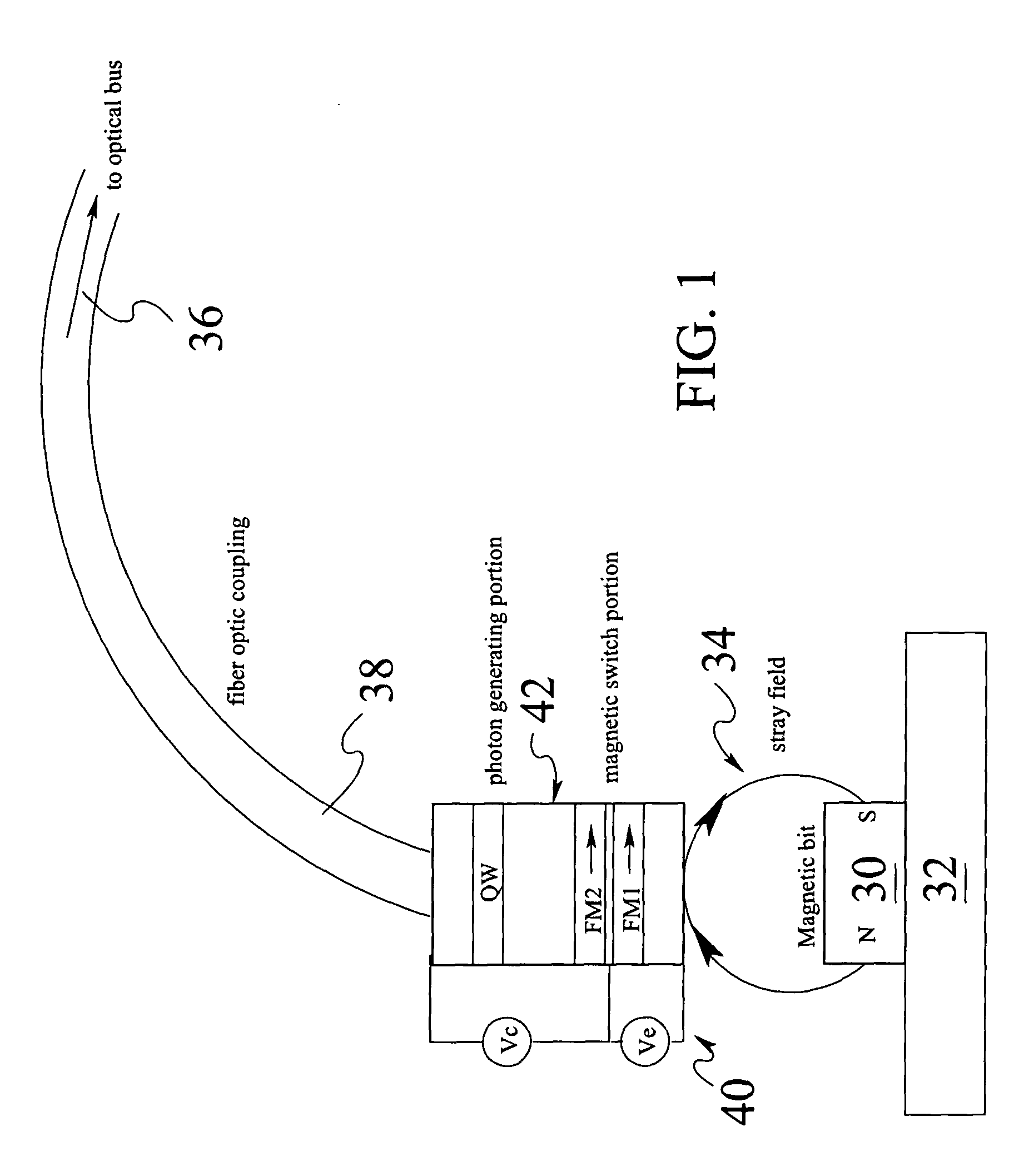

Magneto-luminescent transducer

InactiveUS20050007323A1Without burdenFacilitate emission of lightNanotechStatic indicating devicesMagnetic storageDisplay device

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Method for controlling space charge-driven ion instabilities in electron impact ion sources

In a method for inhibiting space charge-related effects in an ion source, an electron beam is directed into a chamber to produce ions from sample material in the chamber. A voltage pulse is applied to the chamber to perturb an electron space charge present in the chamber. The ion source may be an electron impact ionization (EI) apparatus. The ion source may operated in conjunction with a mass spectrometry system.

Owner:BRUKER DALTONIK GMBH & CO KG

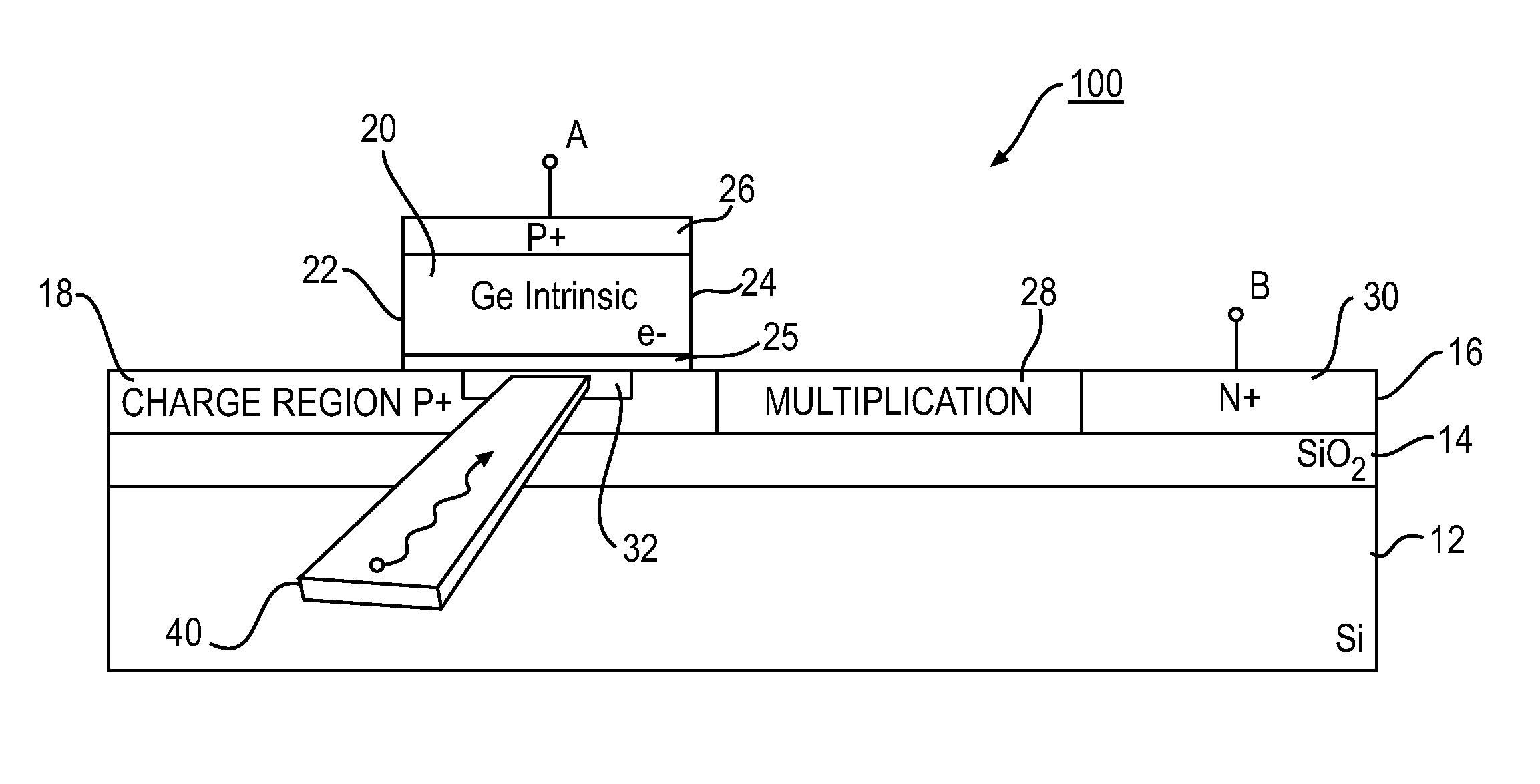

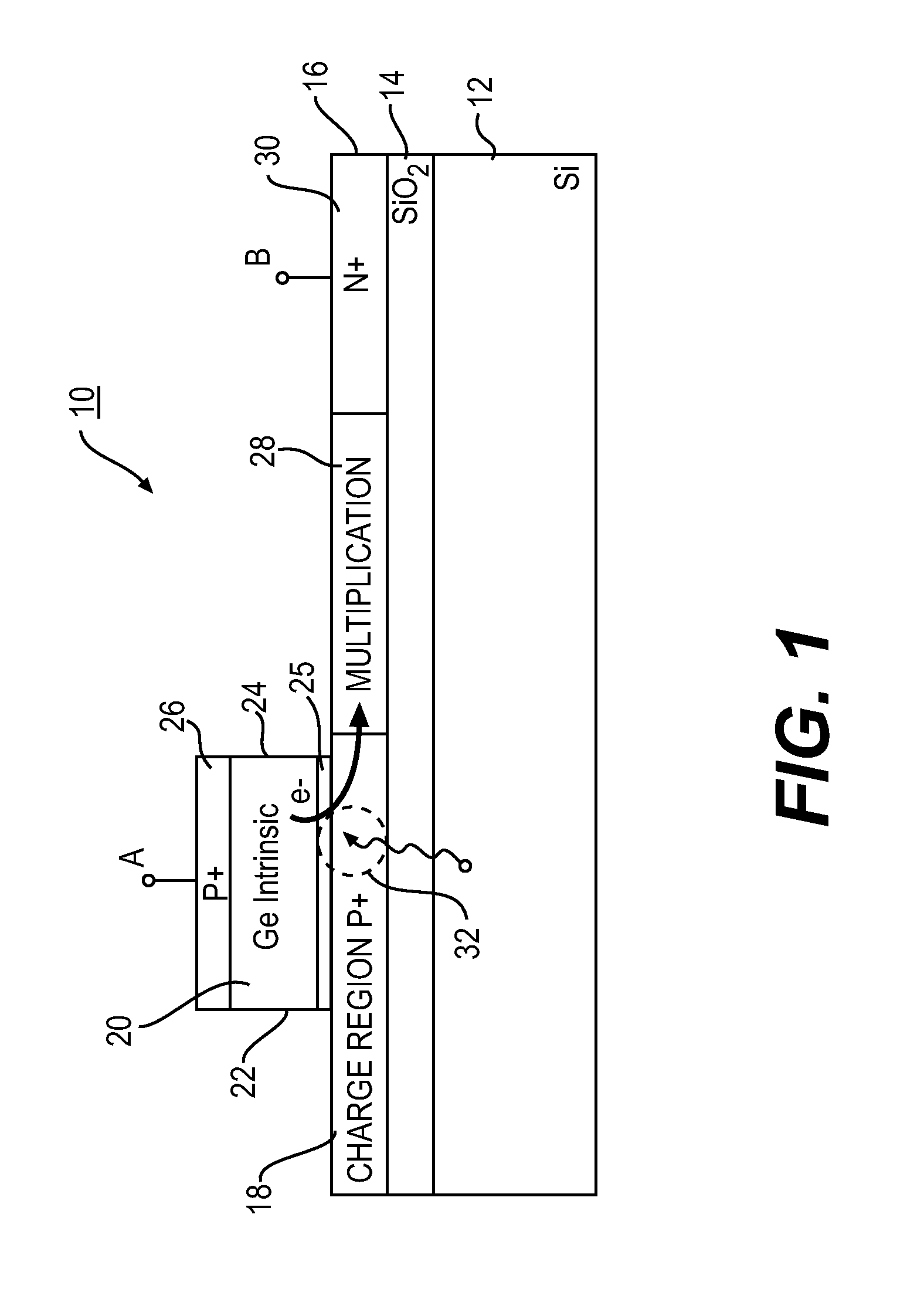

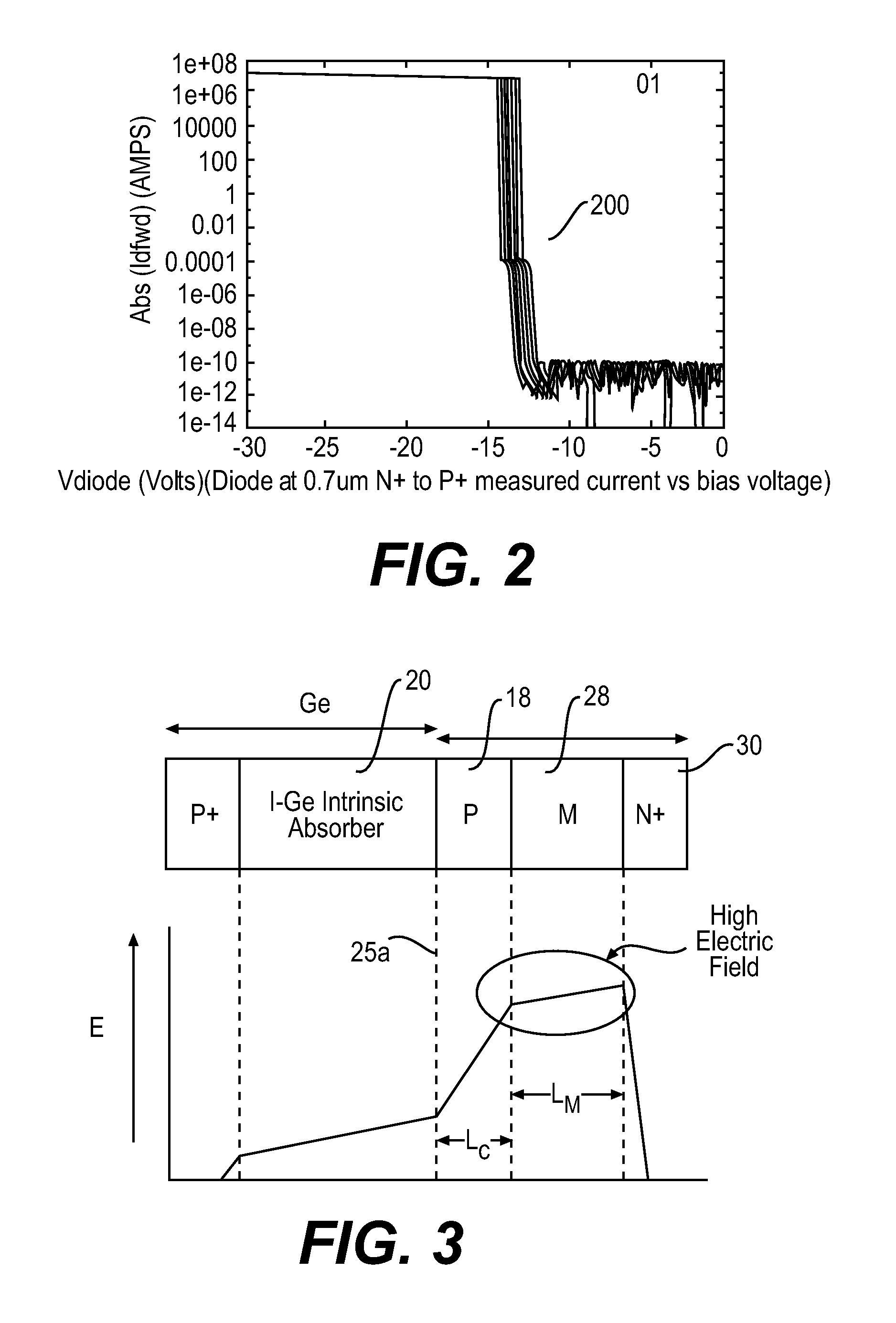

Two-dimensional APDs and SPADs and related methods

ActiveUS9391225B1Great amplificationEasy to measureCladded optical fibreCoupling light guidesImpact ionizationPhoton

Avalanche photodiodes (APDs) and single photon avalanche detectors (SPADs) are provided with a lateral multiplication region that provides improved amplification through increased impact ionization.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

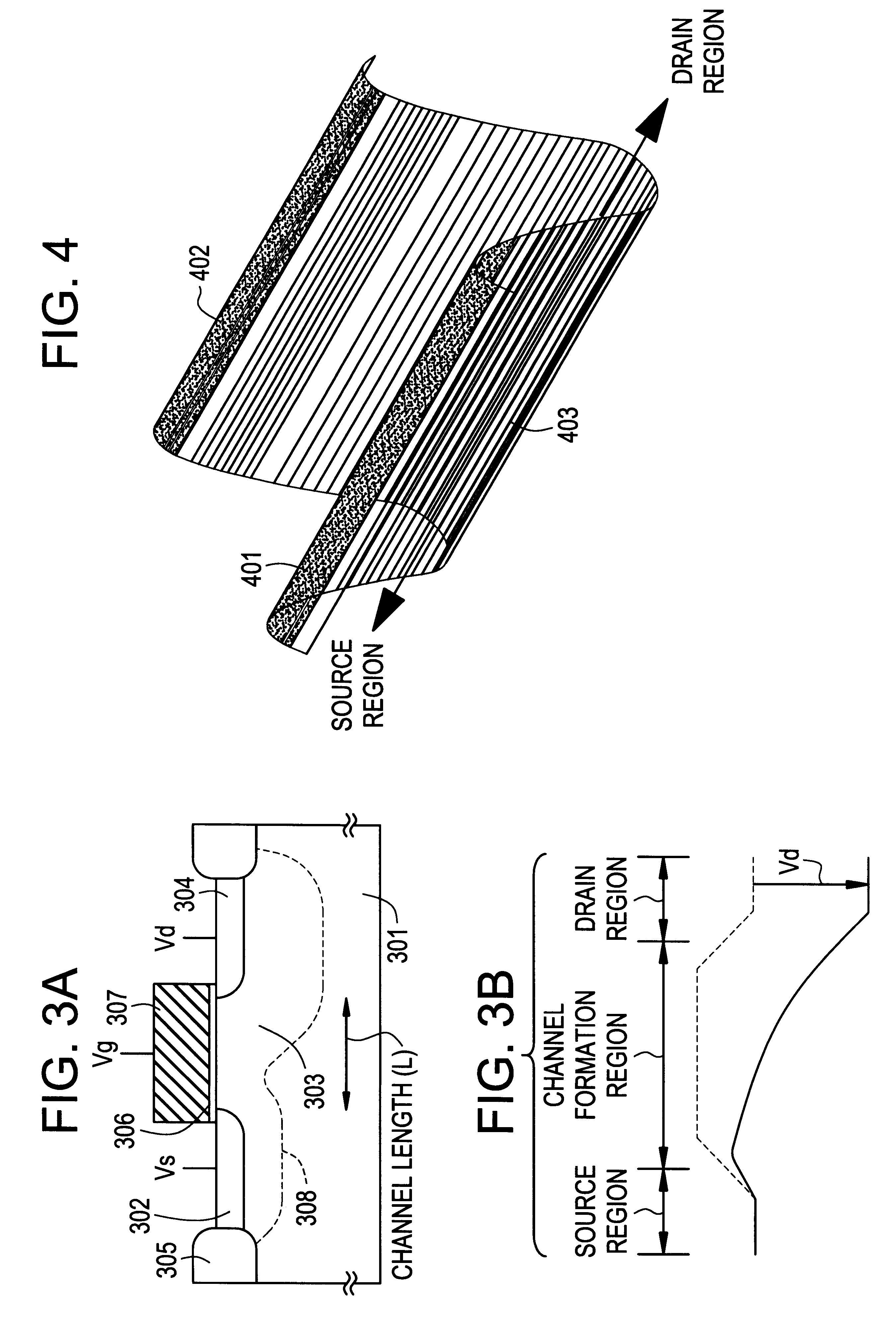

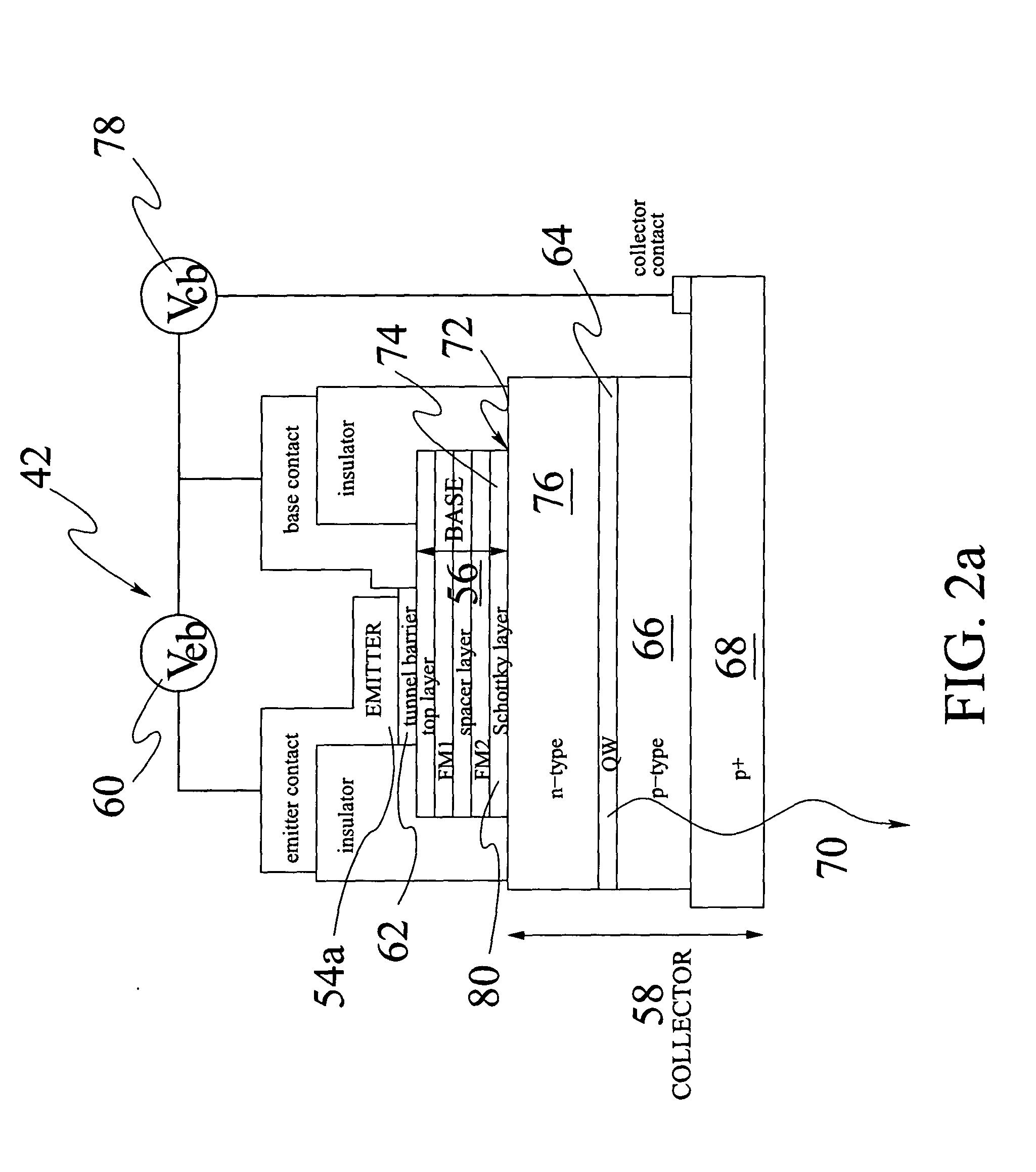

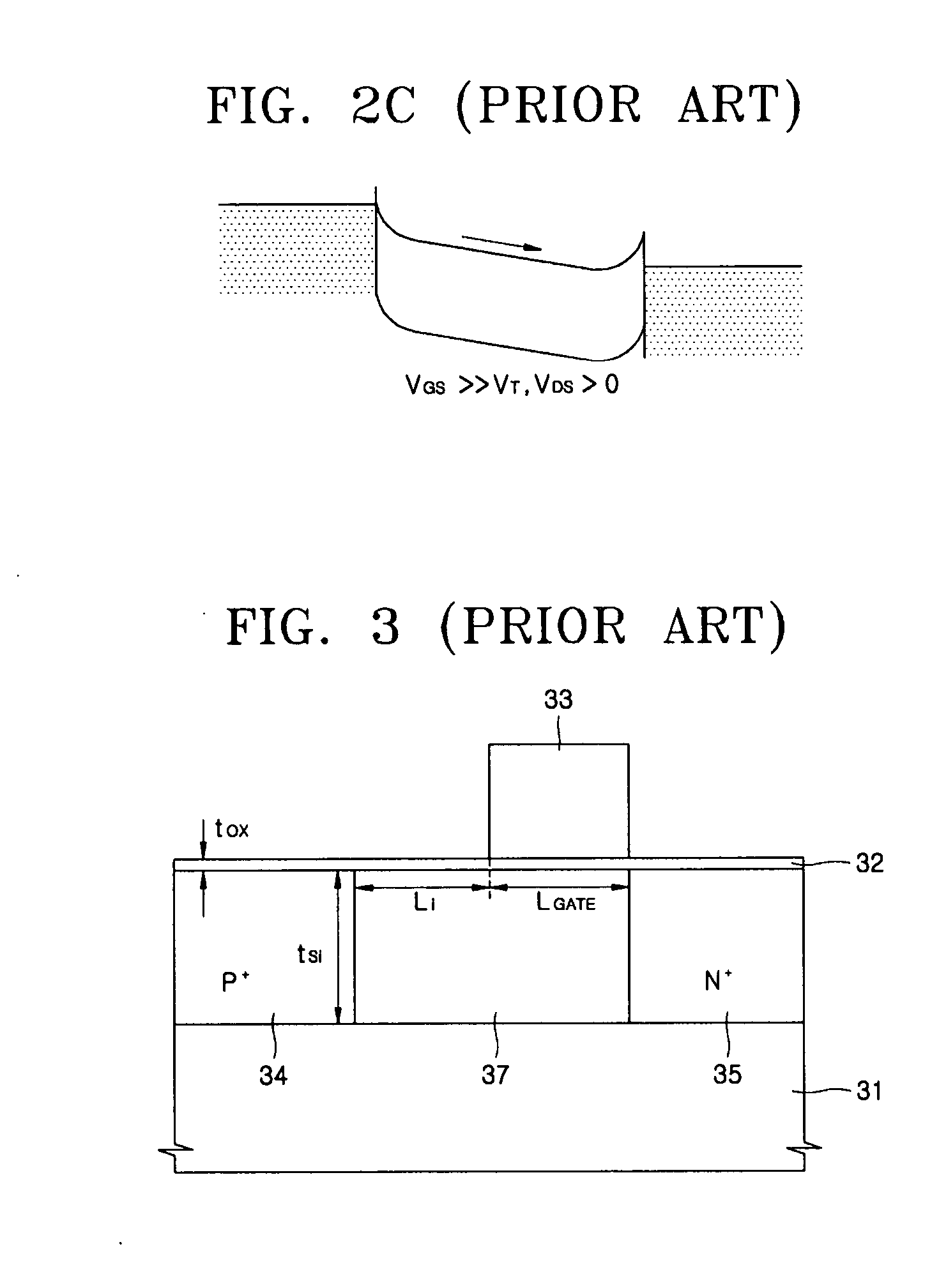

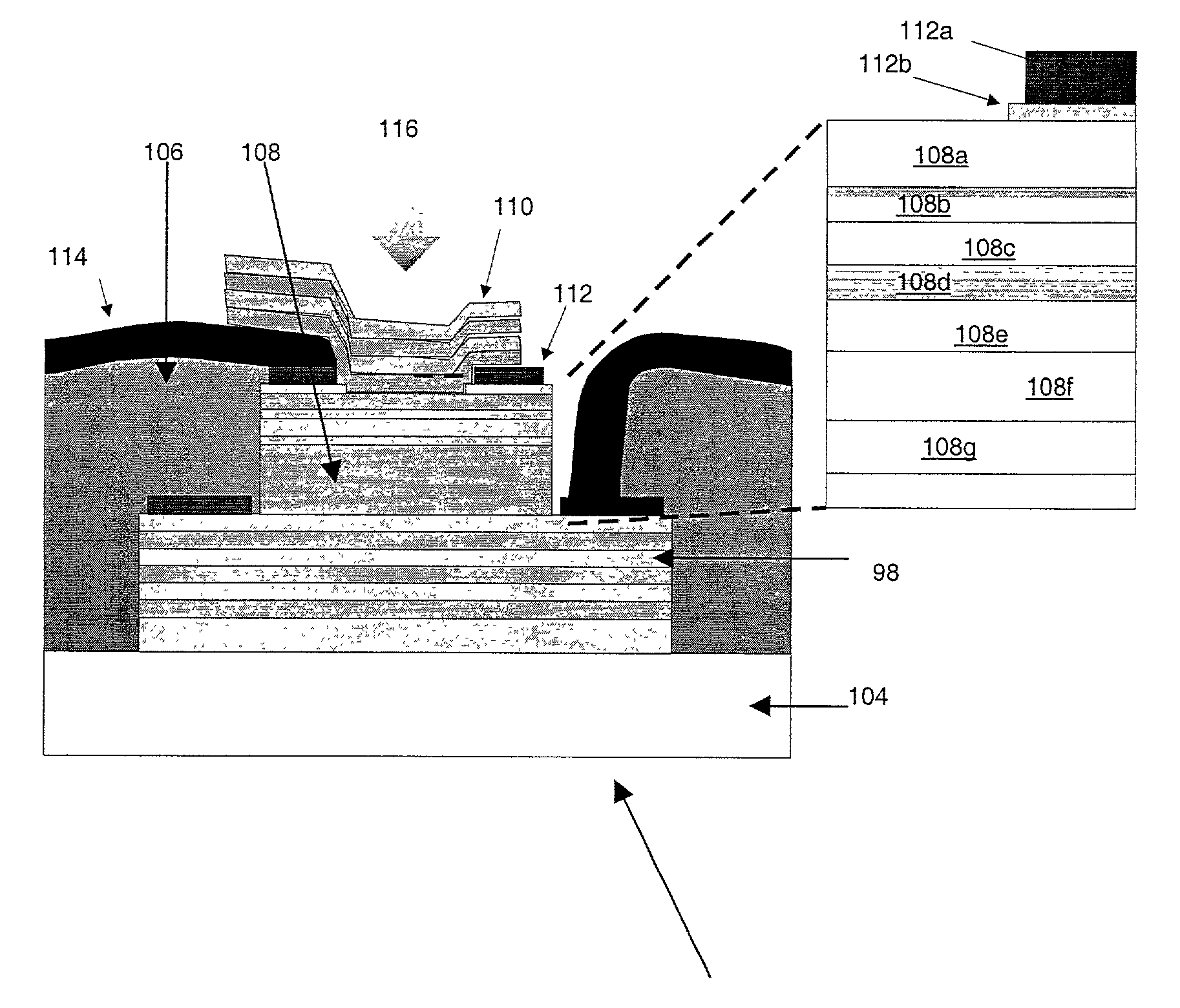

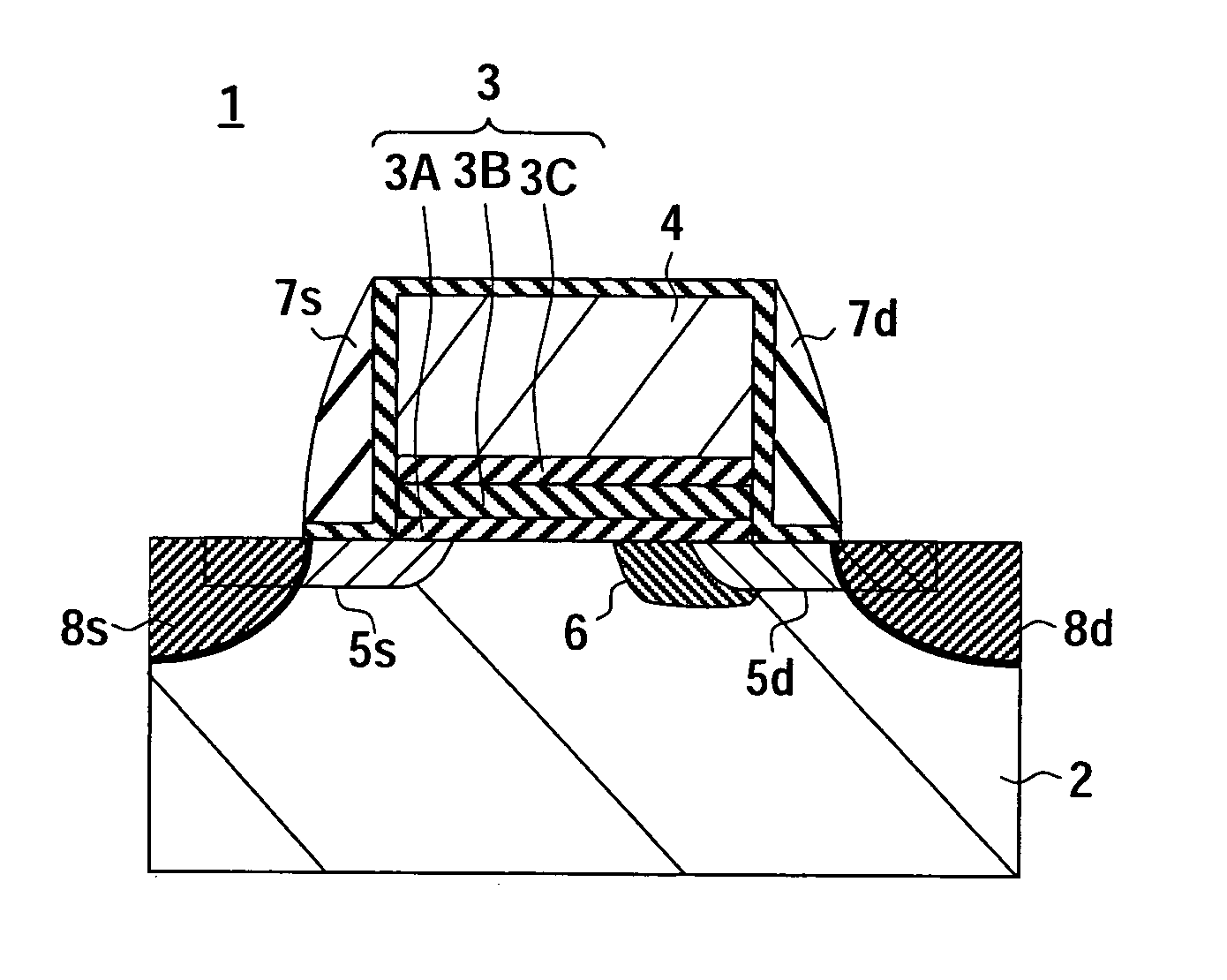

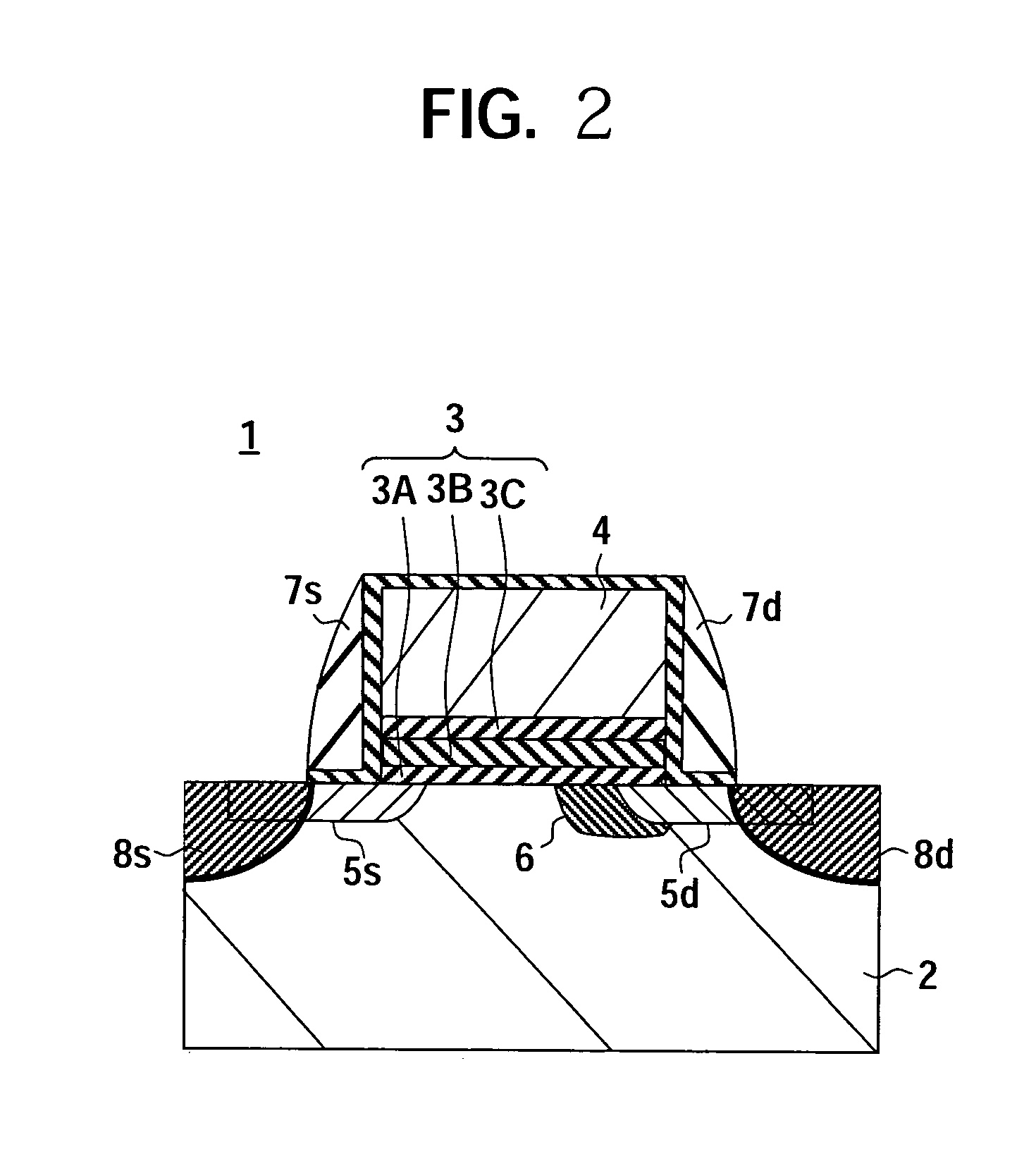

Transistor using impact ionization and method of manufacturing the same

InactiveUS20060125041A1TransistorSemiconductor/solid-state device manufacturingGate dielectricOhmic contact

A transistor using impact ionization and a method of manufacturing the same are provided. A gate dielectric layer, a gate, and first and second spacers are formed on a semiconductor substrate. A first impurity layer is formed spaced from the first spacer and a second impurity layer is formed expanding and overlapping with the second spacer therebelow, by performing slant ion-implantation on the semiconductor substrate using the gate and the first and second spacers as a mask. A source and a drain are formed on the semiconductor substrate to be self-aligned with the first and second spacers, respectively, thereby defining an ionization region between the source and the drain in the semiconductor substrate. The source includes a first silicide layer to form a schottky junction with the ionization region. The drain includes a portion of the second impurity layer overlapping with the second spacer and a second silicide layer which is aligned with the second spacer to form an ohmic contact with the second impurity layer.

Owner:ELECTRONICS & TELECOMM RES INST

Collision ion generator and separator

ActiveUS9287100B2Samples introduction/extractionMaterial analysis by electric/magnetic meansImpact ionizationComputational chemistry

According to some embodiments, systems and methods for surface impact ionization of liquid phase and aerosol samples are provided. The method includes accelerating a liquid or aerosol sample, colliding the sample with a solid collision surface thereby disintegrating the sample into both molecular ionic species (e.g., gaseous molecular ions) and molecular neutral species (e.g., gaseous sample), and transporting the disintegrated sample to an ion analyzer. Some embodiments of the method further comprise discarding the molecular neutral species. Such embodiments transport substantially only the molecular ionic species to the ion analyzer.

Owner:MEDIMASS +1

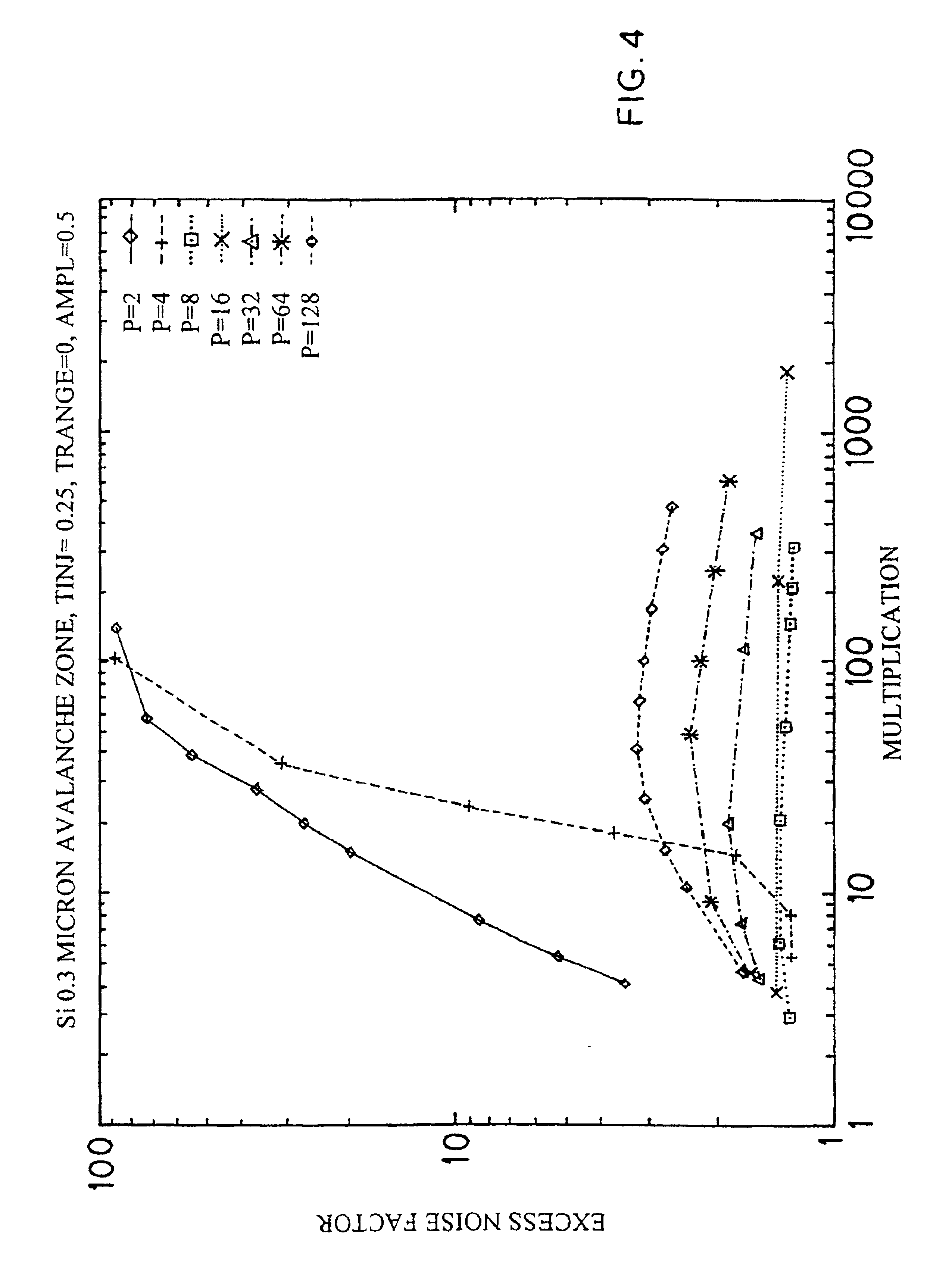

Avalanche photodiodes with an impact-ionization-engineered multiplication region

InactiveUS7045833B2Reduction in avalanche noiseDecreasing multiplication region thicknessSolid-state devicesSemiconductor/solid-state device manufacturingCharge carrierElectron avalanche

An avalanche photodiode including a multiplication layer is provided. The multiplication layer may include a well region and a barrier region. The well region may include a material having a higher carrier ionization probability than a material used to form the barrier region.

Owner:INTELLECTUAL VENTURES HLDG 40

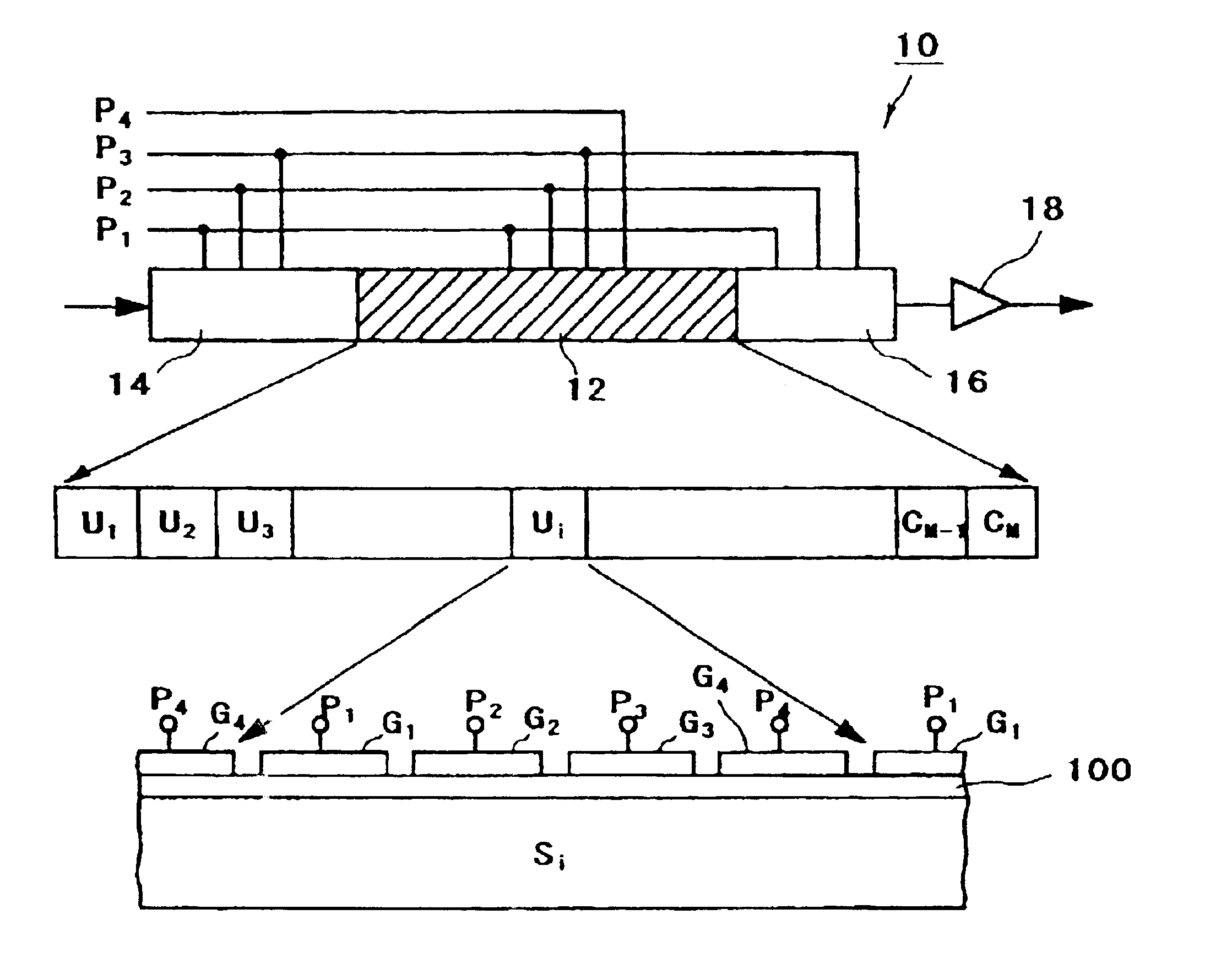

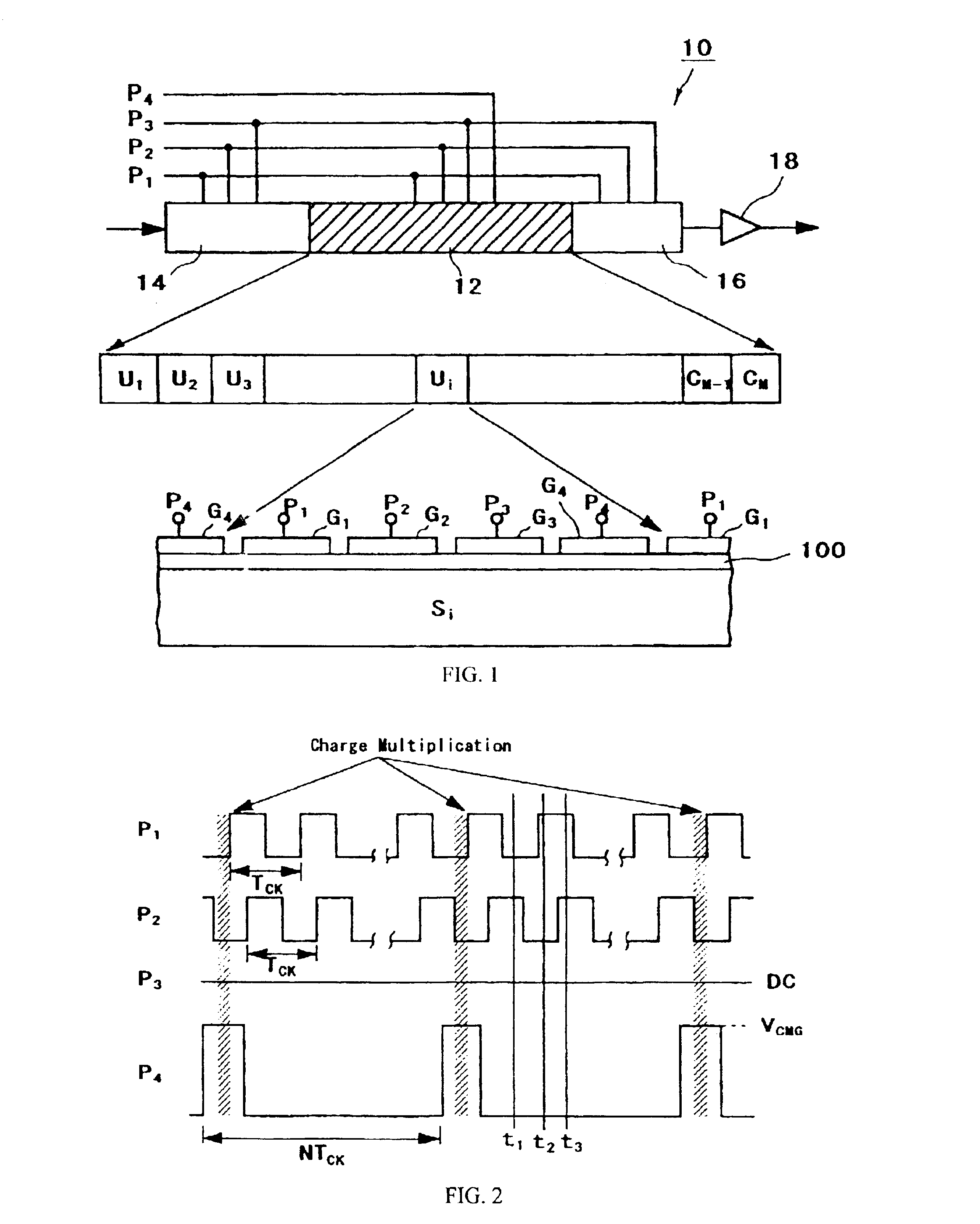

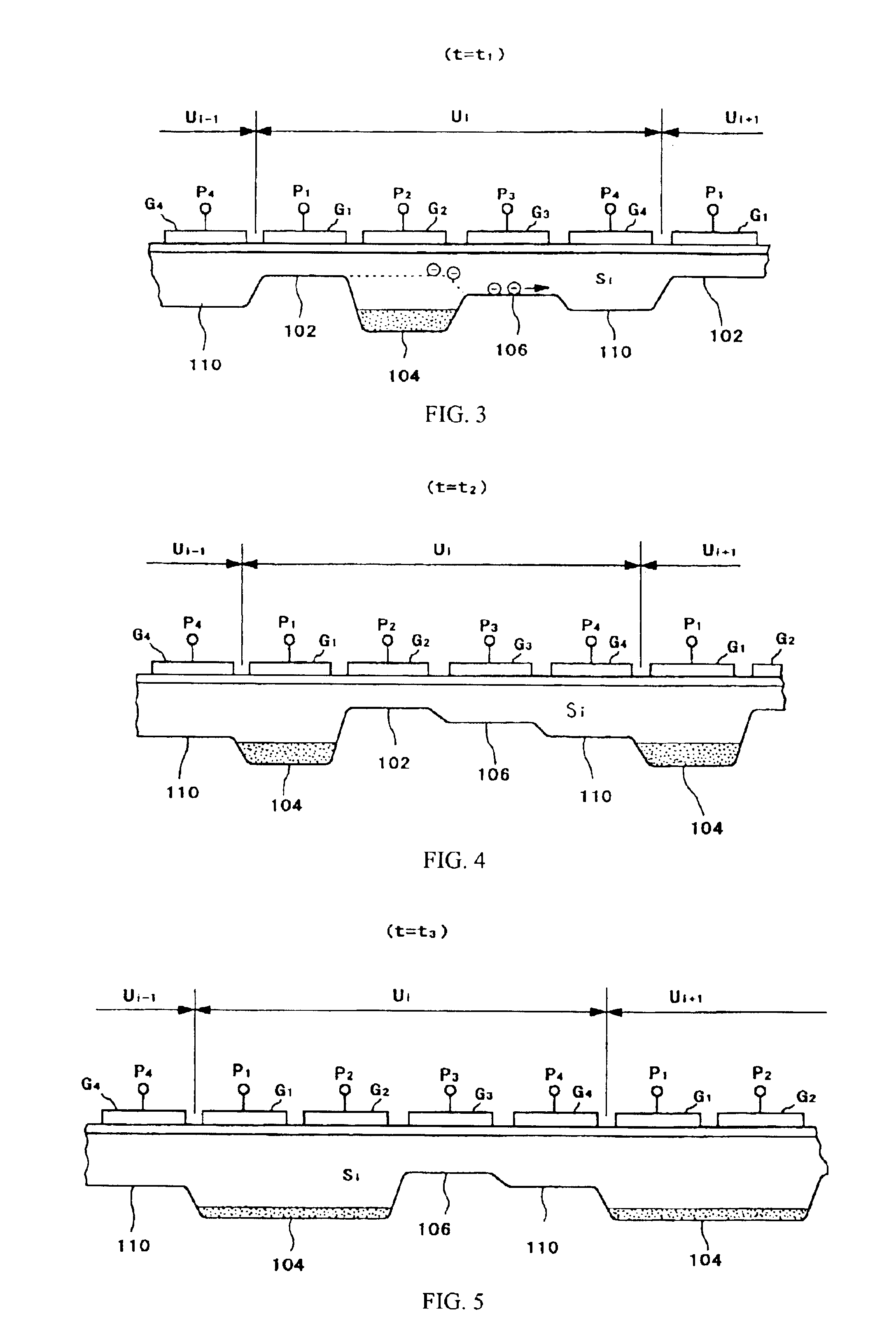

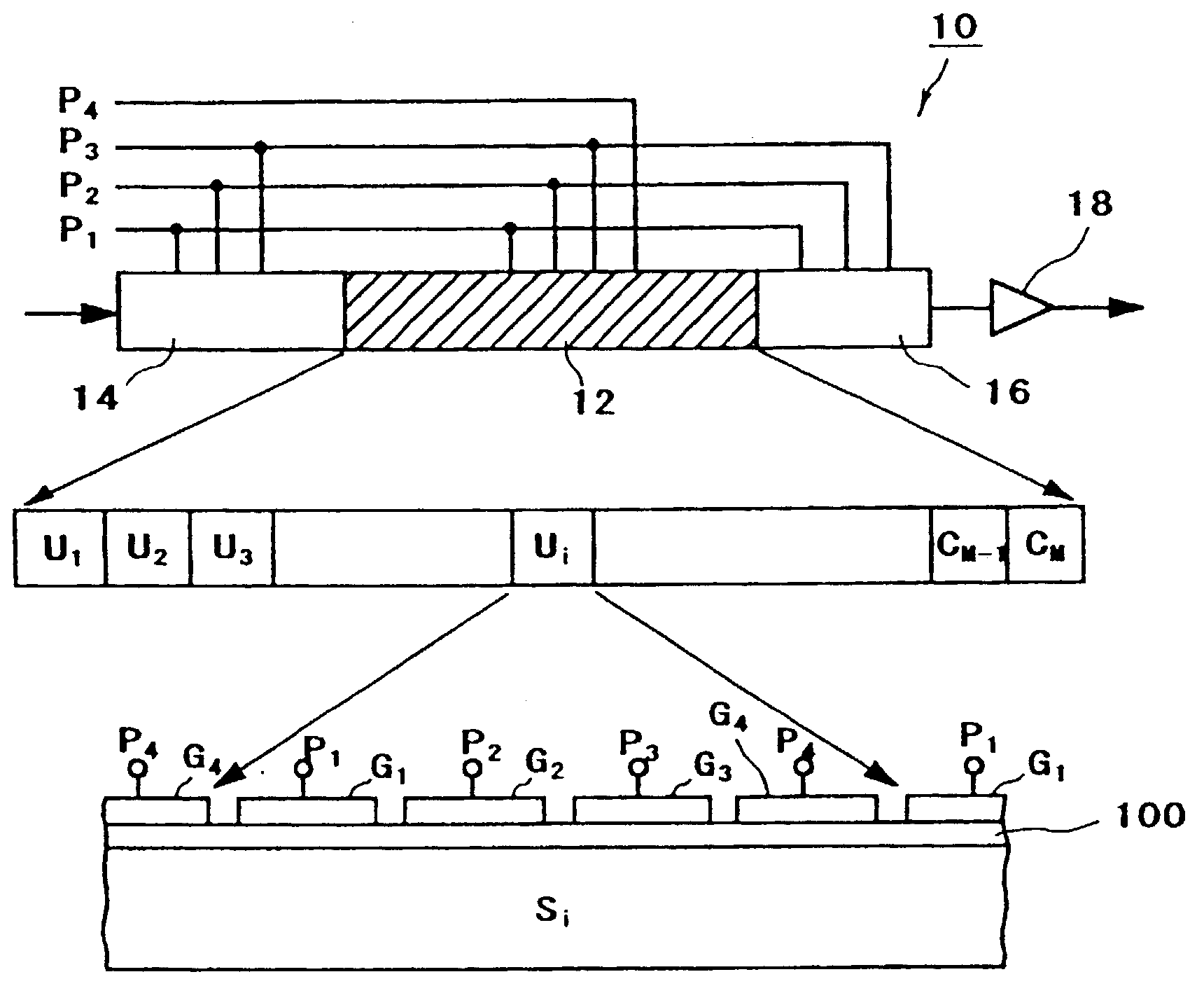

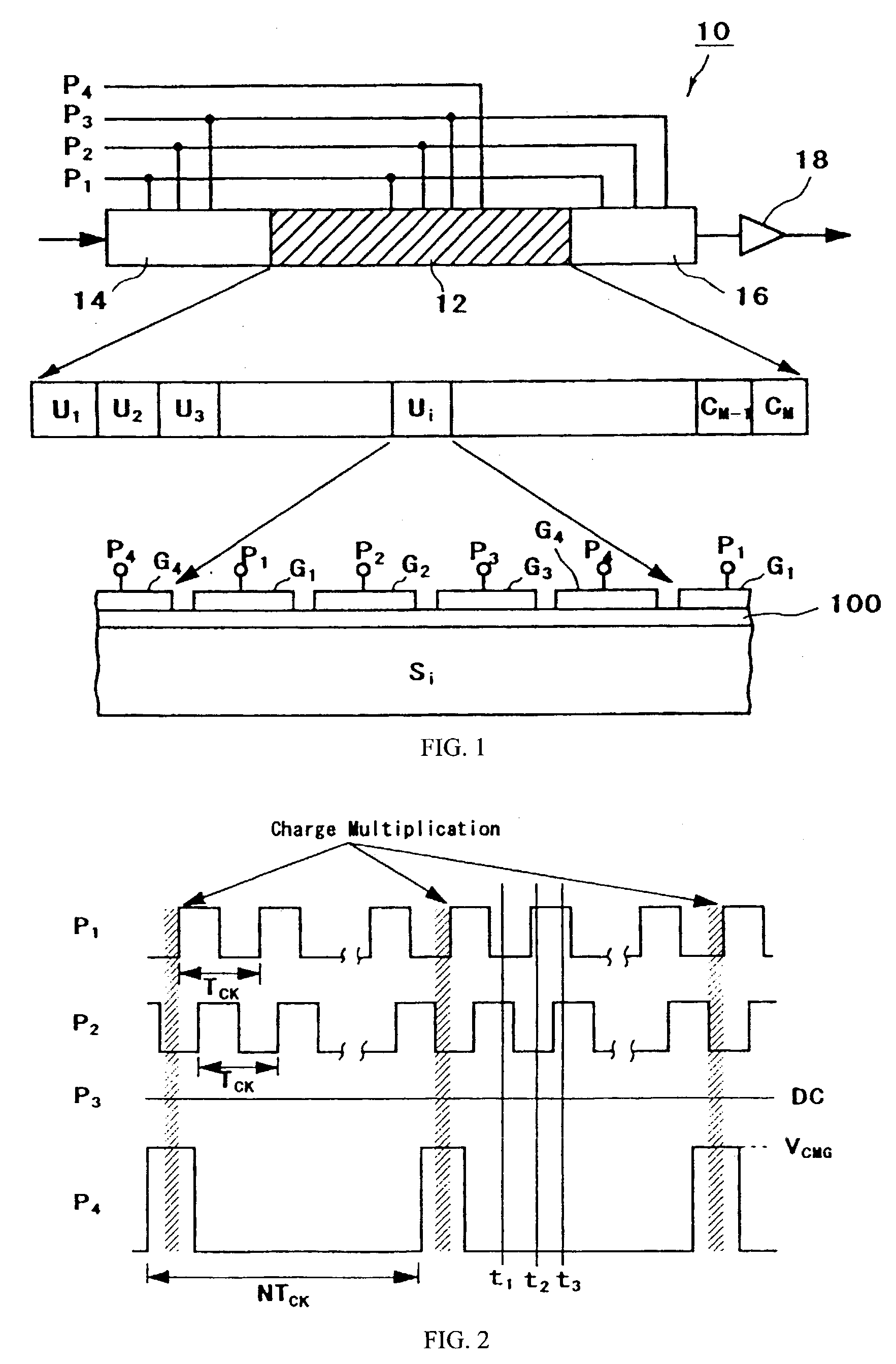

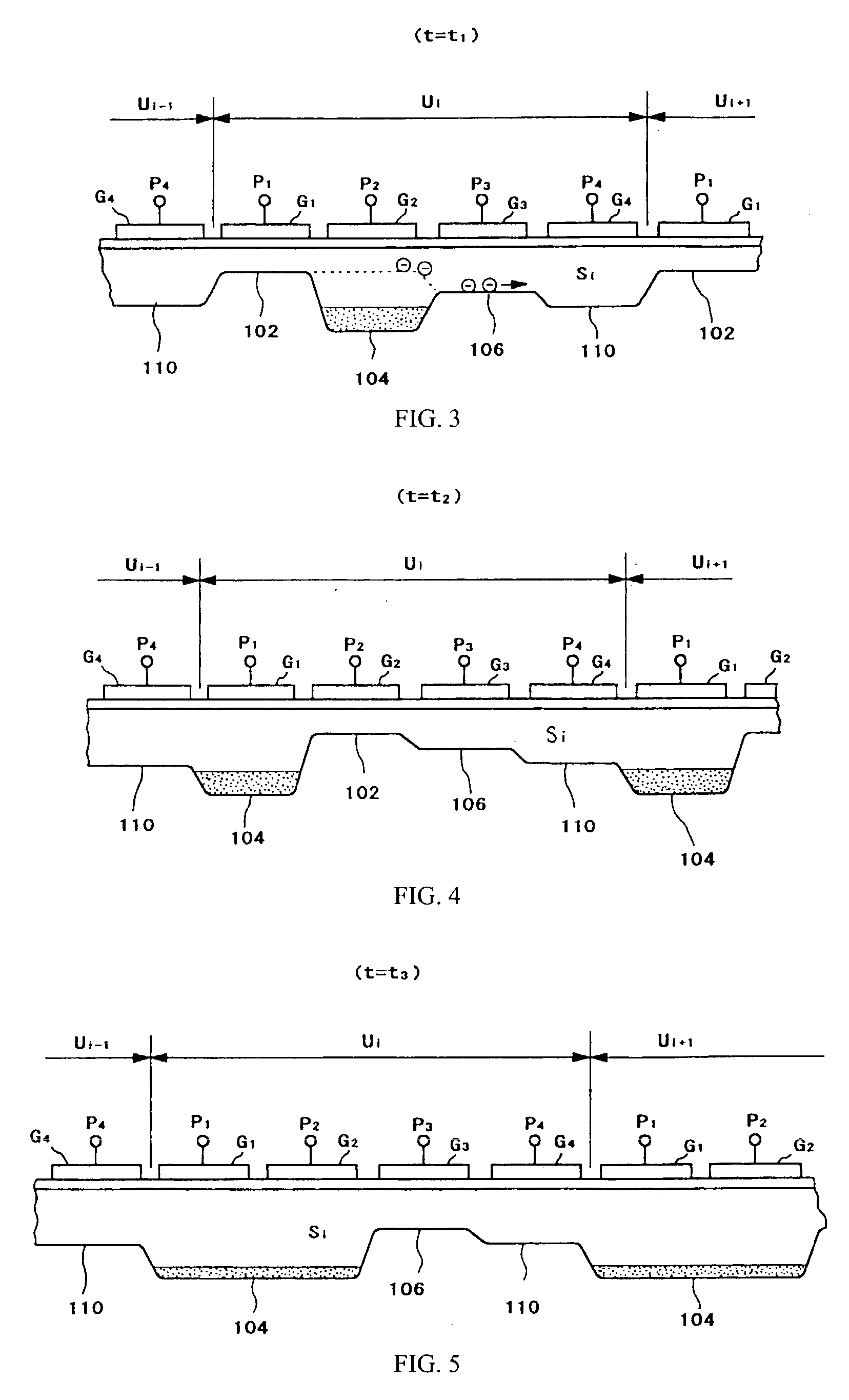

CMD and CMD-carrying CCD device

InactiveUS6862333B2Uniform rateTelevision system detailsCounting chain synchronous pulse countersControl signalSilicon oxide

This invention controls the signal amplification rate in a simple way with high precision in a CMD or CMD-carrying CCD device. CMD 12 has plural sections, such as M sections (U1-UM), each of which is a CMD unit U that can perform a charge multiplication operation, set in series. Each section of CMD unit Ui has plural (such as 4) electrodes G1, G2, G3, G4 set in a row via an insulating film, such as silicon oxide film 100, on a silicon insulating film. Among driving voltages P1, P2, P3, P4 applied on the electrodes G1, G2, G3 and G4, P1 and P2 are applied in the same cycle as the transfer clock, P4 for impact ionization is applied in intermittent cycles with respect to P1 and P2, and P3 is applied as a DC voltage at a prescribed level.

Owner:TEXAS INSTR INC

CMD and CMD-carrying CCD device

InactiveUS20030223531A1Uniform rateTelevision system detailsCounting chain synchronous pulse countersControl signalSilicon oxide

This invention controls the signal amplification rate in a simple way with high precision in a CMD or CMD-carrying CCD device. CMD 12 has plural sections, such as M sections (U1-UM), each of which is a CMD unit U that can perform a charge multiplication operation, set in series. Each section of CMD unit Ui has plural (such as 4) electrodes G1, G2, G3, G4 set in a row via an insulating film, such as silicon oxide film 100, on a silicon insulating film. Among driving voltages P1, P2, P3, P4 applied on the electrodes G1, G2, G3 and G4, P1 and P2 are applied in the same cycle as the transfer clock, P4 for impact ionization is applied in intermittent cycles with respect to P1 and P2, and P3 is applied as a DC voltage at a prescribed level.

Owner:TEXAS INSTR INC

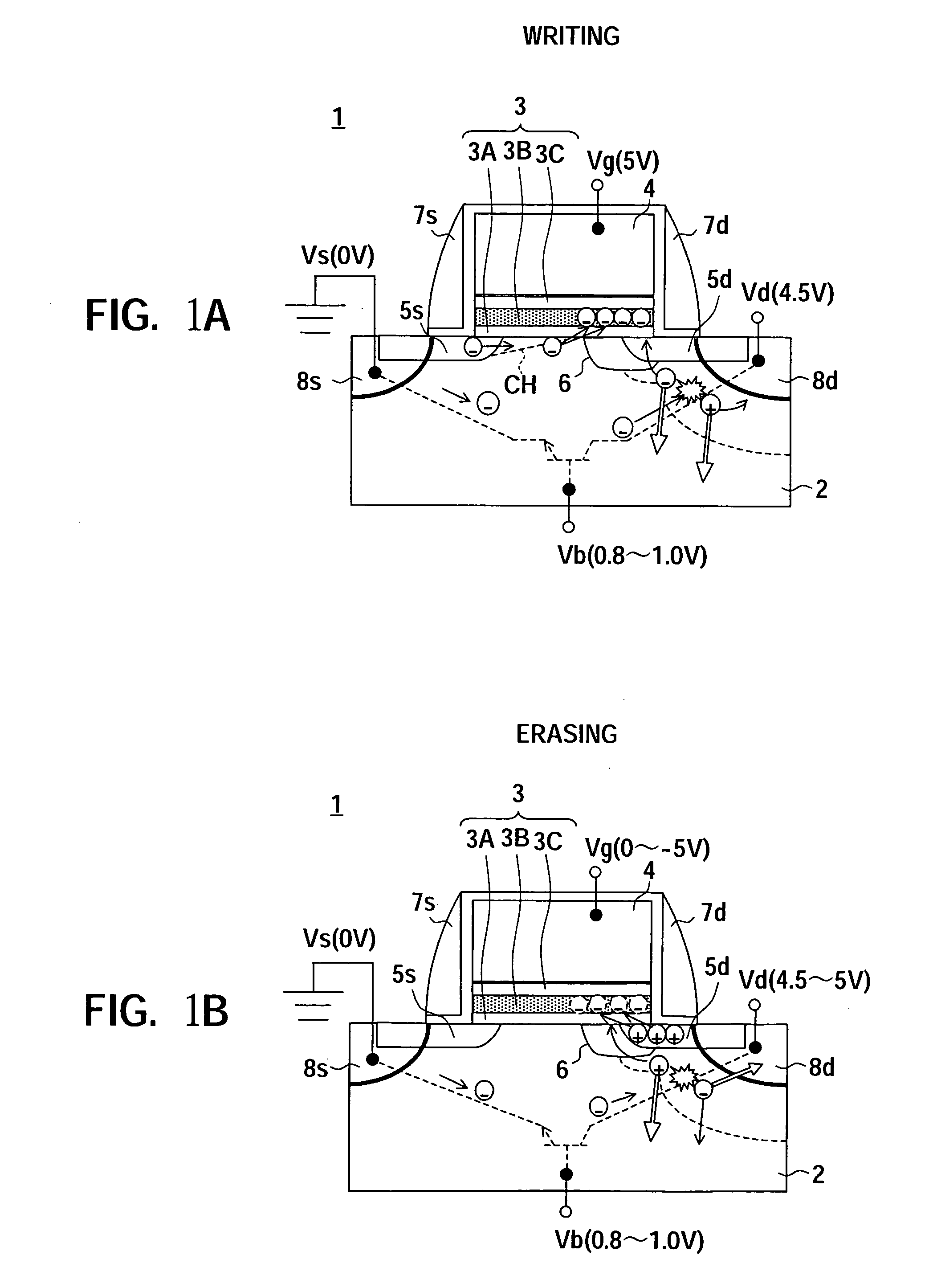

Nonvolatile semiconductor memory device, charge injection method thereof and electronic apparatus

InactiveUS20050194633A1High data re-writing speedLow ON voltage operationTransistorSolid-state devicesCharge injectionParasitic bipolar transistor

A charge injection method for improve efficiency of generating hot carrier, wherein, for example, electrons are injected at writing and holes are injected at erasing to a charge storage layer of a memory transistor. A positive voltage is applied to the drain region by using a voltage of the source region as a reference, and a voltage having a polarity in accordance with charges to be injected is applied to a gate electrode. A voltage having a voltage value between a source voltage and a drain voltage for turning on a diode made by an N-type source region and a P-type body region is applied to the body region. Then a parasitic bipolar transistor turns on, consequently, impact ionization arises on the drain side and an injection charge amount increases.

Owner:SONY CORP

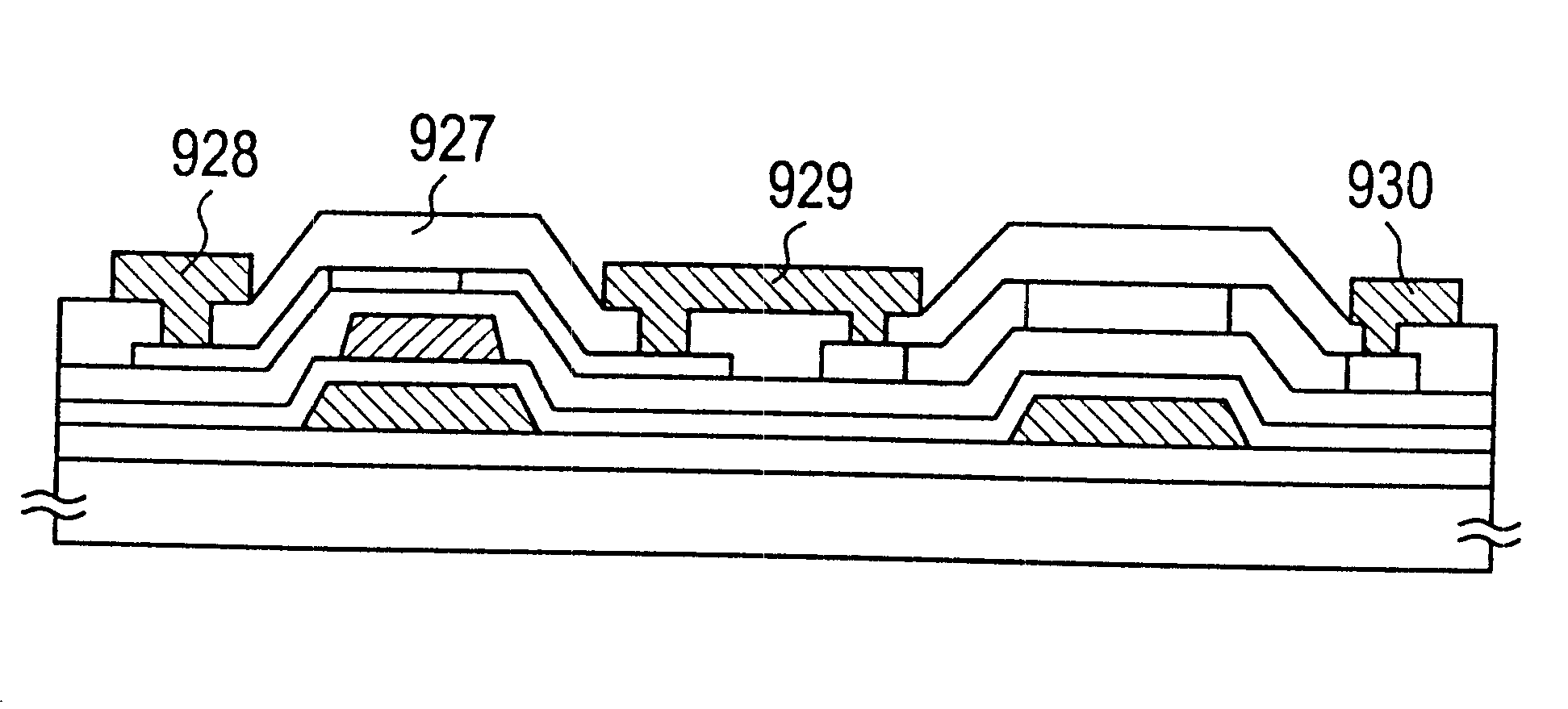

Nonvolatile memory and manufacturing method thereof

InactiveUS20030107077A1Impact ionization occurs more easilyEasy to produceTransistorSolid-state devicesLow voltageMiniaturization

Memory elements, switching elements, and peripheral circuits to constitute a nonvolatile memory are integrally formed on a substrate by using TFTs. Since semiconductor active layers of memory element TFTs are thinner than those of other TFTs, impact ionization easily occurs in channel regions of the memory element TFTs. This enables low-voltage write / erase operations to be performed on the memory elements, and hence the memory elements are less prone to deteriorate. Therefore, a nonvolatile memory capable of miniaturization can be provided.

Owner:SEMICON ENERGY LAB CO LTD

Electrically alterable memory cell

InactiveUS20060006454A1Suppresses large C effectEliminate requirementsTransistorCharge carrierEngineering

A nonvolatile memory cell is provided. The cell has a charge filter, a tunneling gate, a ballistic gate, a charge storage layer, a source, and a drain with a channel defined between the source and drain. The charge filter permits transporting of charge carriers of one polarity type from the tunneling gate through the blocking material and the ballistic gate to the charge storage layer while blocking the transport of charge carriers of an opposite polarity from the ballistic gate to the tunneling gate. Further embodiments of the present invention provide a cell having a charge filter, a supplier gate, a tunneling gate, a ballistic gate, a source, a drain, a channel, and a charge storage layer. The present invention further provides an energy band engineering method permitting the memory cell be operated without suffering from disturbs, from dielectric breakdown, from impact ionization, and from undesirable RC effects.

Owner:MARVELL ASIA PTE LTD

Floating-gate semiconductor structures

Hot-electron injection driven by hole impact ionization in the channel-to-drain junction of a p-channel MOSFET provides a new mechanism for writing a floating-gate memory. Various pFET floating-gate structures use a combination of this mechanism and electron tunneling to implement nonvolatile analog memory, nonvolatile digital memory, or on-line learning in silicon. The memory is nonvolatile because the devices use electrically isolated floating gates to store electronic charge. The devices enable on-line learning because the electron injection and tunneling mechanisms that write the memory can occur during normal device operation. The memory updates and learning are bidirectional because the injection and tunneling mechanisms add and remove electrons from the floating gate, respectively. Because the memory updates depend on both the stored memory and the pFETs terminal voltages, and because they are bidirectional, the devices can implement on-line learning functions.

Owner:CALIFORNIA INST OF TECH

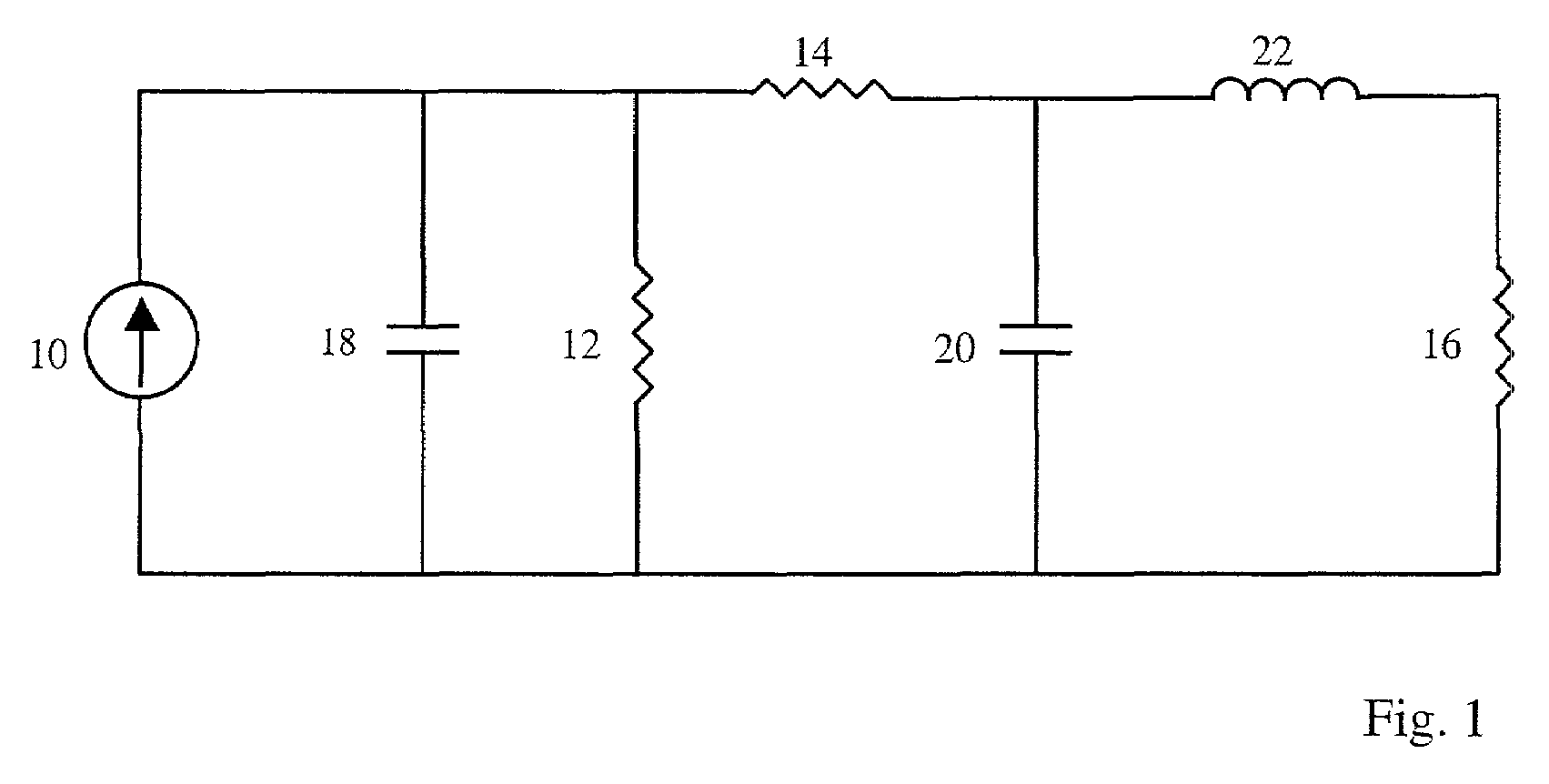

IMPATT diodes

InactiveUS6774460B1Improve predictabilityReduce noiseSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueImpact ionization

The present invention relates to an impact ionisation avalanche transit time (IMPATT) diode device comprising an avalanche region and a drift region, wherein at least one narrow bandgap region, with a bandgap narrower than the bandgap in the avalanche region, is located adjacent to or within the avalanche region in order to generate within the narrow bandgap region a tunnel current which is injected into the avalanche region. This improves the predictability with which a current can be injected into the avalanche region and enables a relatively narrow pulse of current to be injected into the avalanche region in order to enable a relatively noise free avalanche multiplication. The narrow bandgap region may be located between a heavily doped contact region and the avalanche region and is preferably arranged to generate a tunnel current at the peak reverse bias applied to the diode.

Owner:CHEMTRON RES