Method of accelerating hot carrier injection investigating

A test method and hot carrier technology, applied in the direction of single semiconductor device testing, semiconductor/solid-state device testing/measurement, etc., can solve the problems of delaying data analysis time, taking a long time for MOS field effect device testing, speeding up speed limitations, etc. , to save time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described below with reference to the accompanying drawings and specific embodiments.

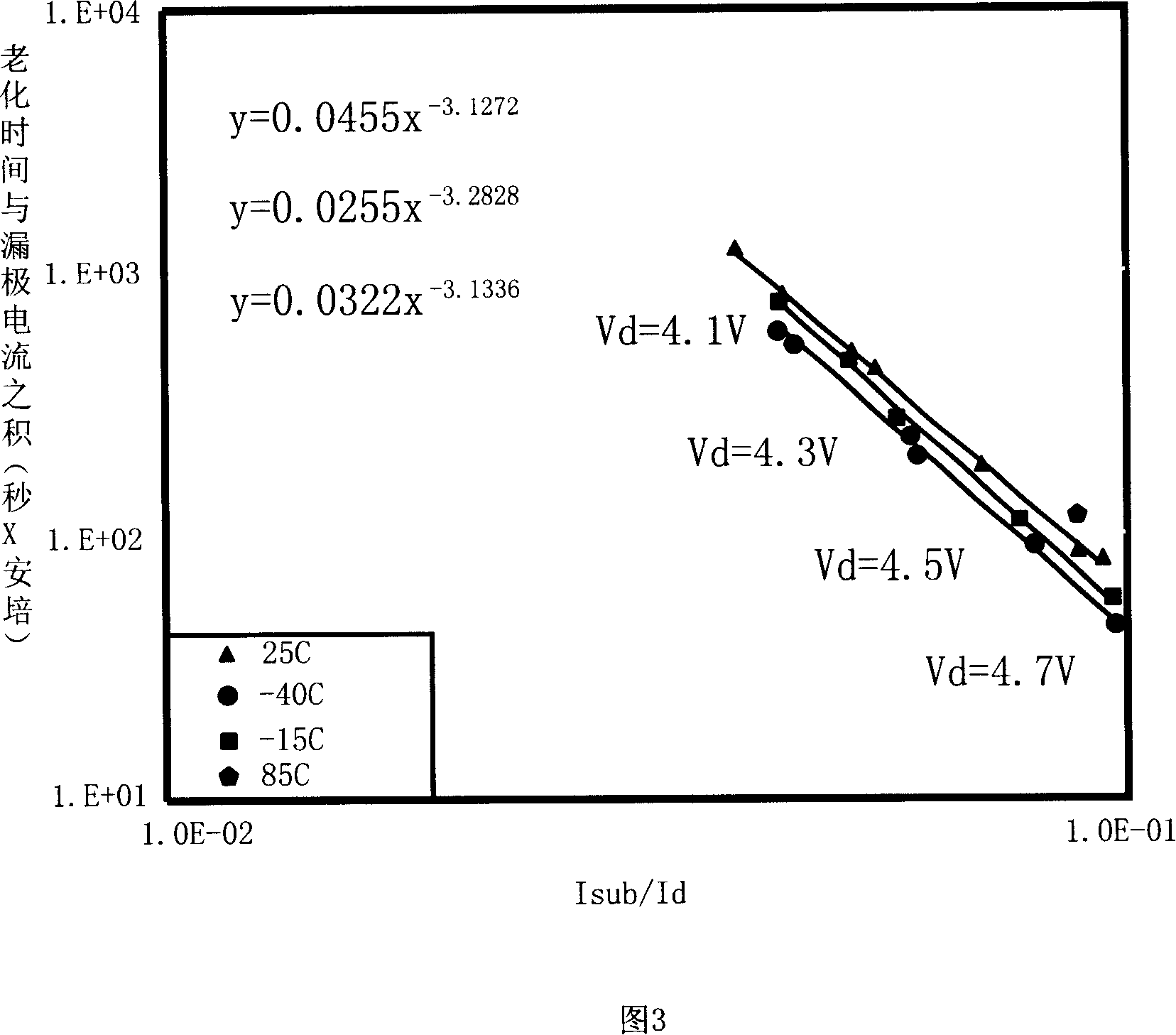

[0019] In one embodiment of the present invention, the present invention is briefly explained by taking an NMOS transistor as an example. First, measure the MOS hot carrier injection data at different temperatures according to the traditional method. During this process, measure the drain current Id and the substrate current Isub at different drain-source voltage Vds and gate-source voltage Vgs (maximum Isub bias) corresponding stress time. And set the 10% drain saturation current Idsat decay as the standard to get the stress time called failure time.

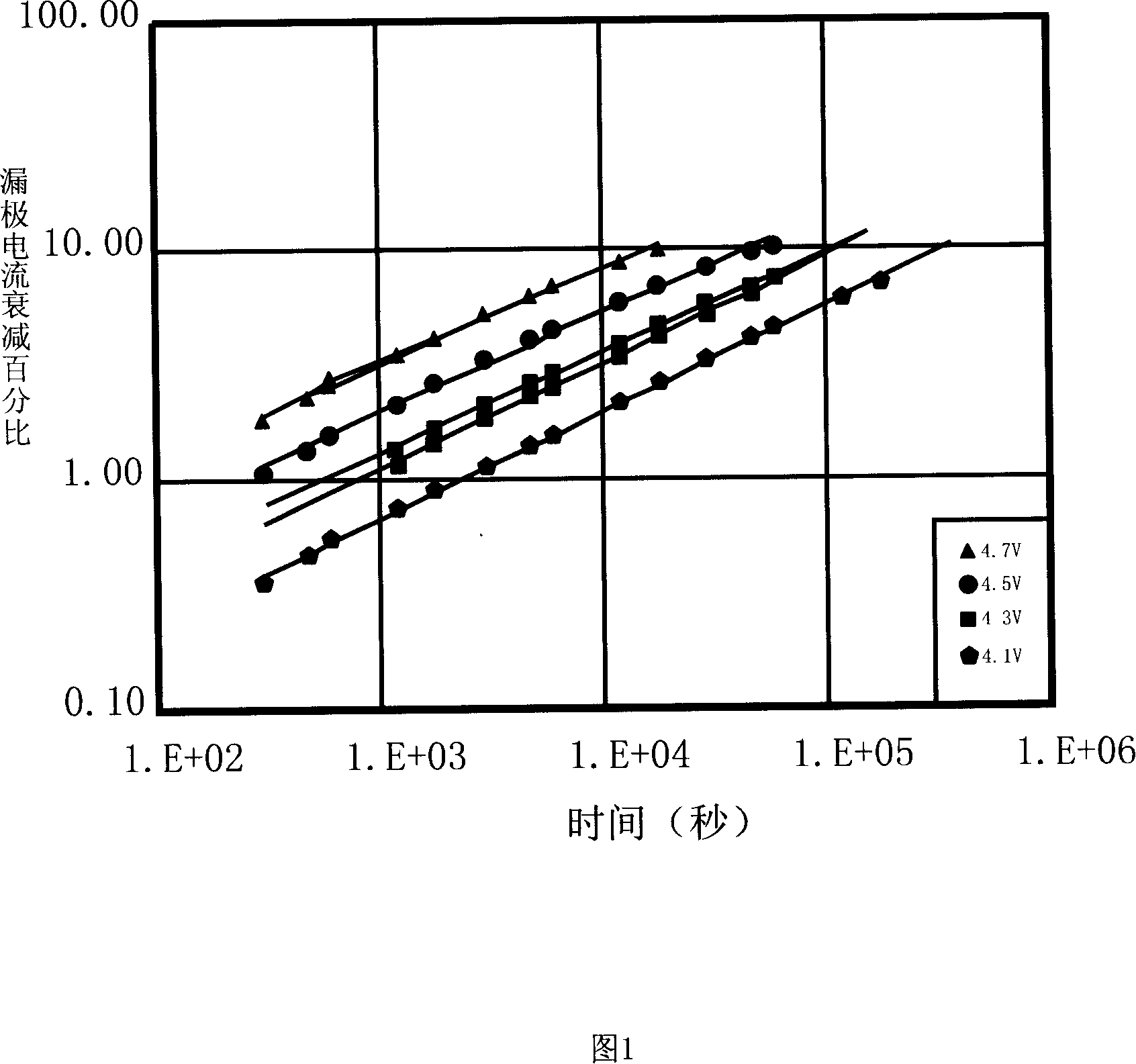

[0020] Please refer to FIG. 1 . FIG. 1 is a graph showing the relationship between drain saturation current decay and time for the NMOS transistor of the present invention at room temperature for different drain-source voltages. A typical device is used in this embodiment with a width to length ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More