High-voltage low-on-resistance LDMOS device and manufacturing method thereof

A low on-resistance, high-voltage technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increased chip cost, high process requirements, poor compatibility, etc., to reduce on-resistance, reduce manufacturing Cost, effect of improving electric field distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

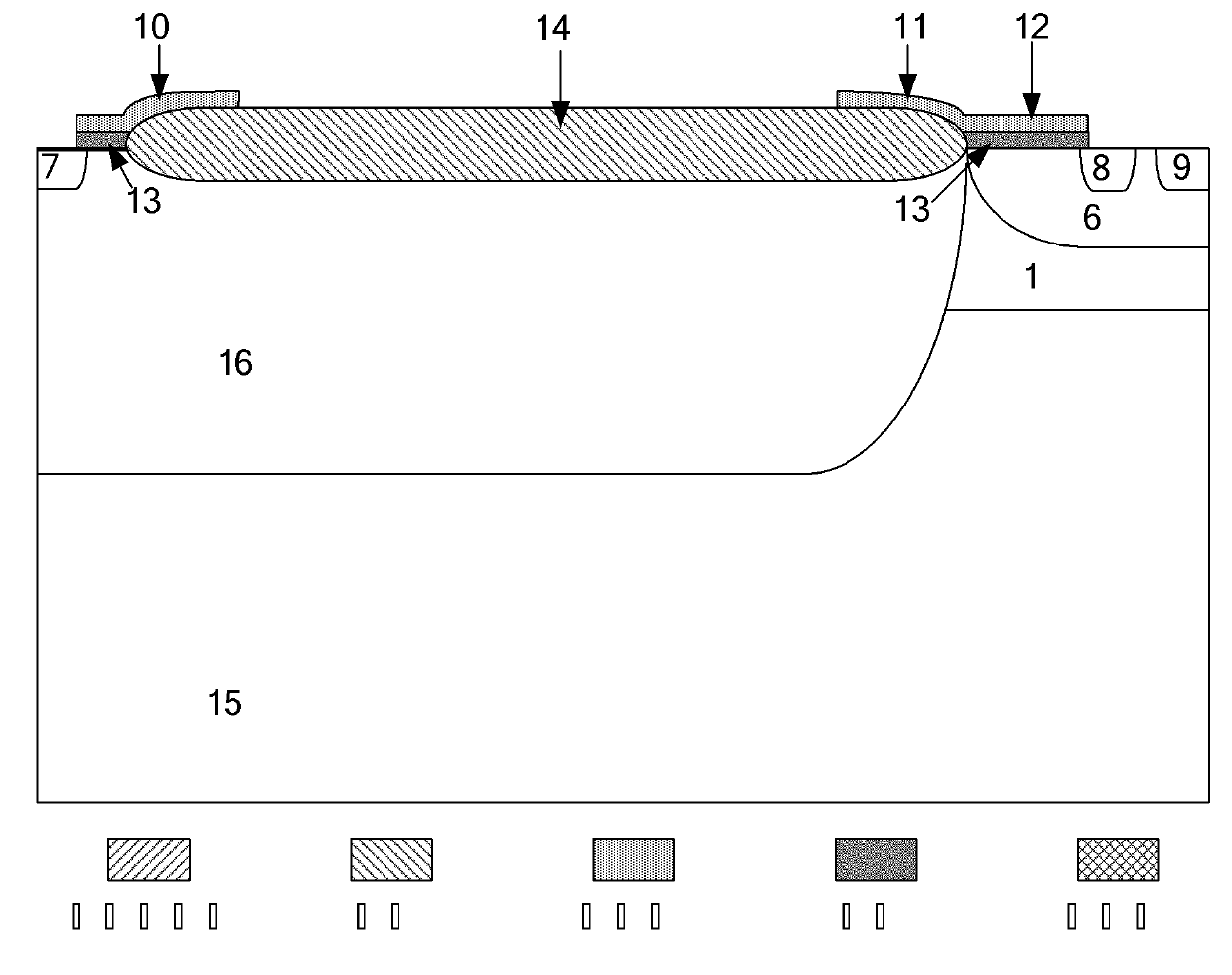

[0055] Embodiment 1: as image 3 As shown, a 700V low on-resistance LDMOS, including P epitaxy 1, P well region 6, N + Anode 7, N + Cathode 8, P + Cathode terminal 9, anode polycrystalline field plate 10, cathode polycrystalline field plate 11, gate polycrystalline 12, gate oxide layer 13, field oxygen layer 14, P substrate 15, N well region 16, P epitaxy 1 and N well The region 16 is located on the P substrate 15, the P well region 6 is located on the P epitaxy 1, and the N + Cathode 8 and P + The cathode terminal 9 is located on the P well region 6, and the N + The anode 7 is positioned on the top of one end of the N well region 16, the field oxide layer 14 is positioned on the N well region 16, and the gate oxide layer 13 at the anode end is positioned on the N well region 16 and is connected with the N well region 16 respectively. + The anode 7 is adjacent to the field oxide layer 14, and the gate oxide layer 13 at the cathode end is located on the P well region 6 an...

Embodiment 2

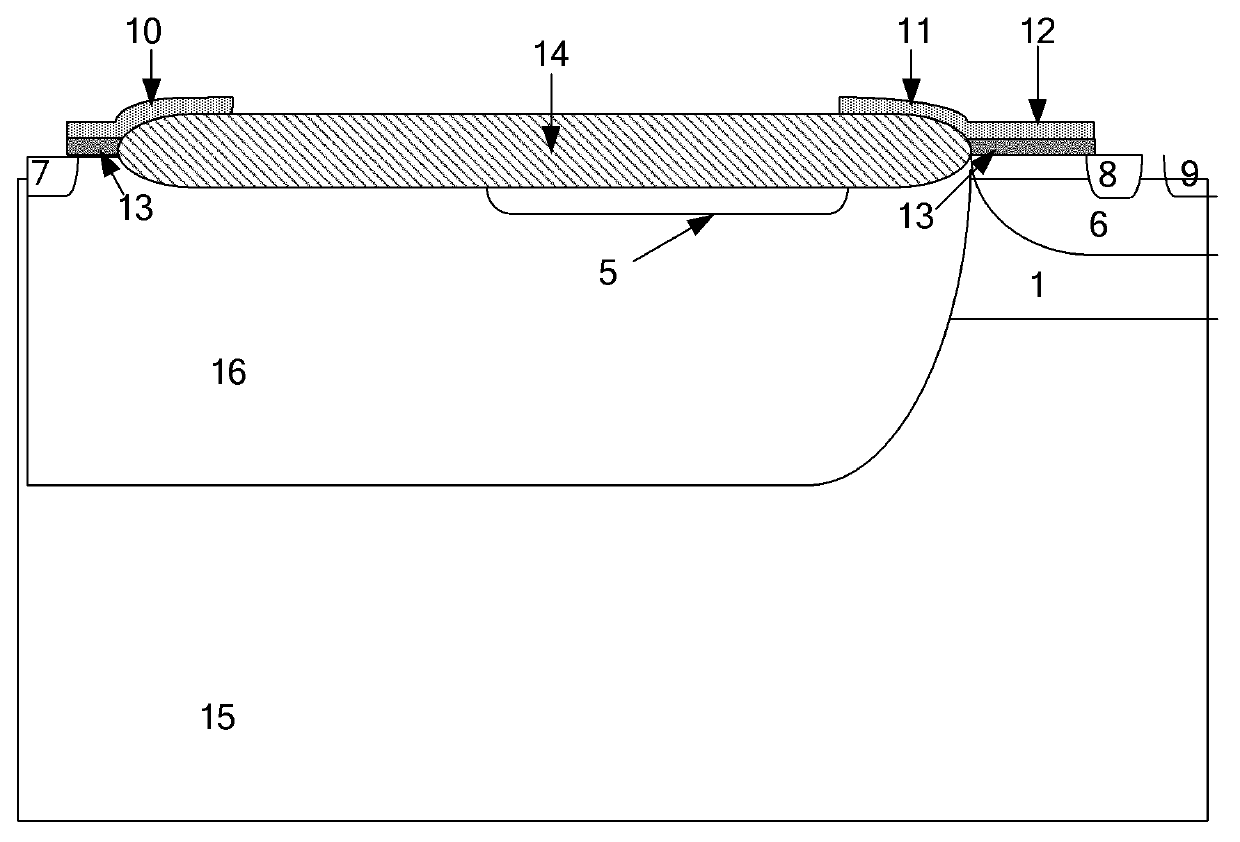

[0079] Embodiment 2: as Figure 4 As shown, the difference between this embodiment and embodiment 1 is that the P buried layer 2 has an N-type conductive channel near the anode, and the rest of the structure is the same as that of embodiment 1, so it will not be repeated here.

[0080] In the forward conduction process of this embodiment, a high potential is applied to the gate polycrystal 12, and an inversion layer is formed on the surface of the cathode end of the gate polycrystal 12, which is located on the surface N of the second N well region 3. + The anode 7 is the drain end of the high voltage LDMOS, and the N in the P well region 6 at the cathode end + The cathode 8 is the source terminal of the structure, and the drain and source terminals are biased with electron flow from N + The cathode 8 is N welled by the inversion layer channel and the second N well region 3 and the first N well region 4 + The anode 7 is collected, and the P-type region 5 is isolated from the ...

Embodiment 3

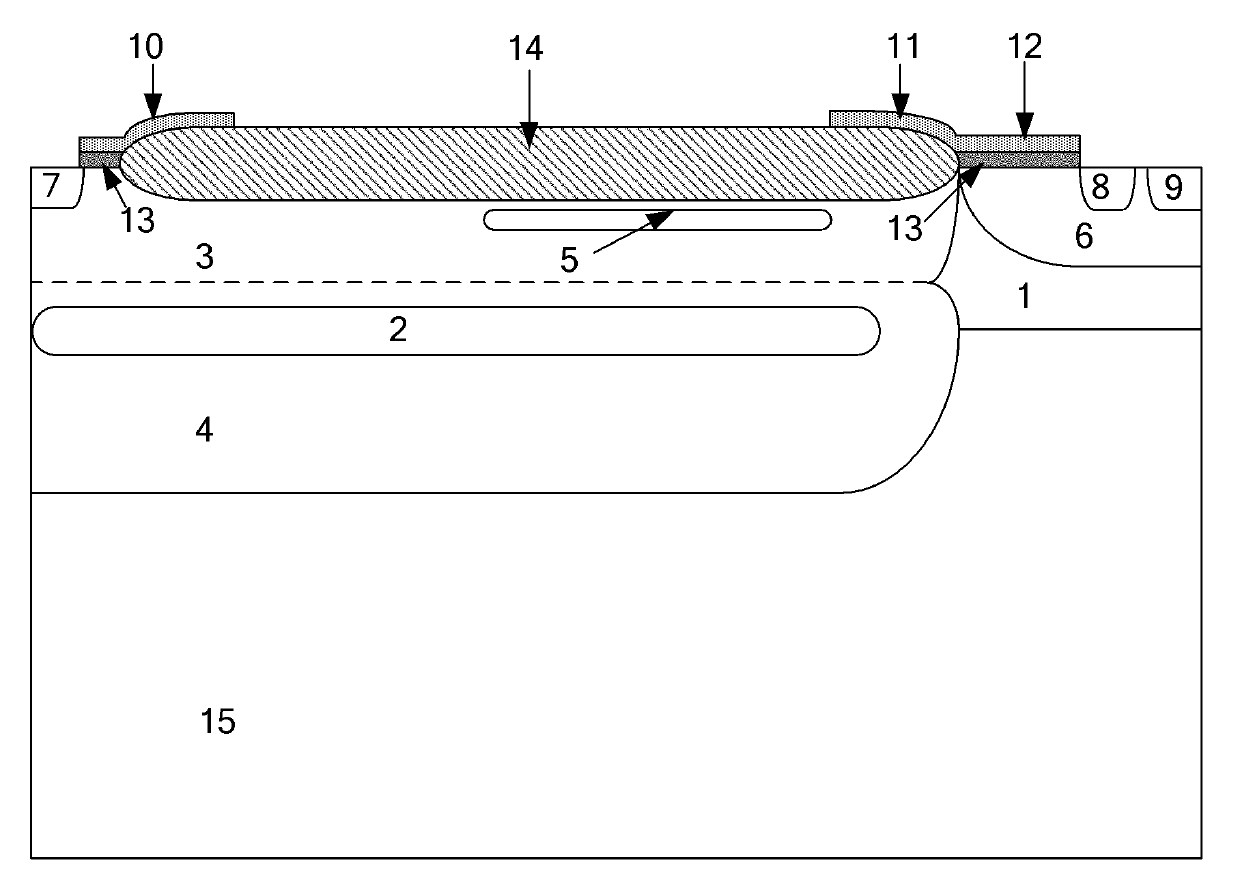

[0085] Embodiment 3: as Figure 5 As shown, the difference between this embodiment and Embodiment 1 is that the P buried layer 2 is a series of isolated islands, the lateral size of each island and the distance between each other are variable, and the P-type region 5 is a series of isolated islands, and each island The lateral dimensions and the distance between them are variable, and the rest of the structure is the same as that of Embodiment 1, so it will not be repeated here.

[0086] In the forward conduction process of this embodiment, a high potential is applied to the gate polycrystal 12, and an inversion layer is formed on the surface of the cathode end of the gate polycrystal 12, which is located on the surface N of the second N well region 3. + The anode 7 is the drain end of the high voltage LDMOS, and the N in the P well region 6 at the cathode end + The cathode 8 is the source terminal of the structure, and the drain and source terminals are biased with electron ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More