Manufacturing method of vertical double diffused metal oxide semiconductor field effect transistor

An oxide semiconductor and vertical double-diffusion technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of VDMOS device electrical parameter changes, waste of manpower and material resources, and VDMOS device drain-source soft breakdown. Achieve the effect of solving the drain-source soft breakdown and avoiding waste

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The technical solution of the present invention will be described in further detail below through specific embodiments and accompanying drawings.

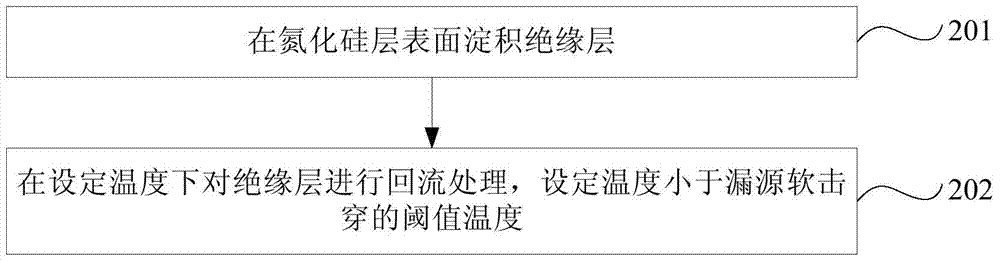

[0026] figure 2 A schematic flowchart of an embodiment of a method for manufacturing a vertical double-diffused metal-oxide-semiconductor field effect transistor provided by the present invention. Such as figure 2 As shown, the method may specifically include:

[0027] S201, depositing an insulating layer on the surface of the silicon nitride layer.

[0028] S202, performing reflow treatment on the insulating layer at a set temperature, where the set temperature is lower than a threshold temperature of drain-source soft breakdown.

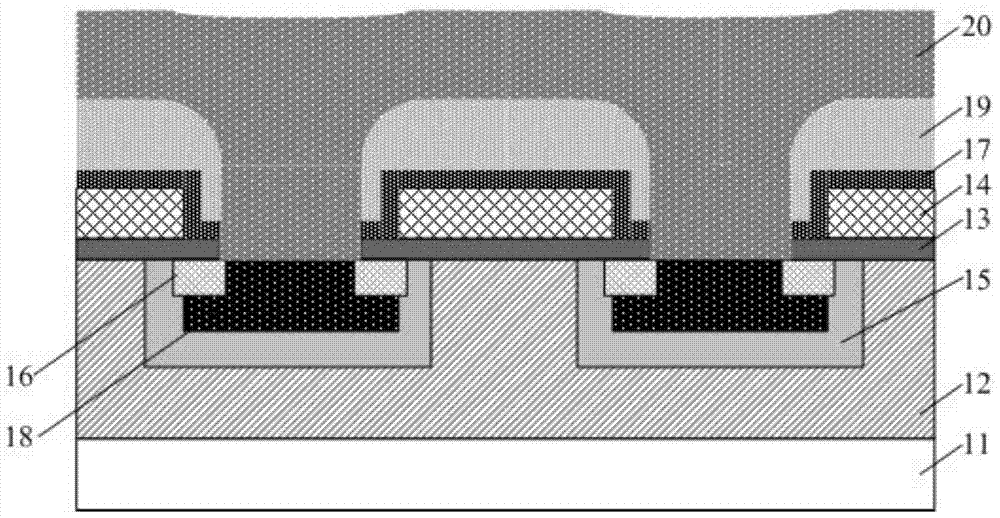

[0029] refer to figure 1 Those skilled in the art can understand that before step S201, the following steps are also included: sequentially forming an epitaxial layer 12, a gate oxide layer 13, a polysilicon layer 14, a body region 15, a source region 16, and a silicon nitride layer on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More