Patents

Literature

226 results about "Electric stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The dielectric or insulation has an electric field, equal to applied voltage, which causes a stress in it , described as volts / unit thickness. If this stress goes beyond its bearing capacity, there will be insulation breakdown or failure .

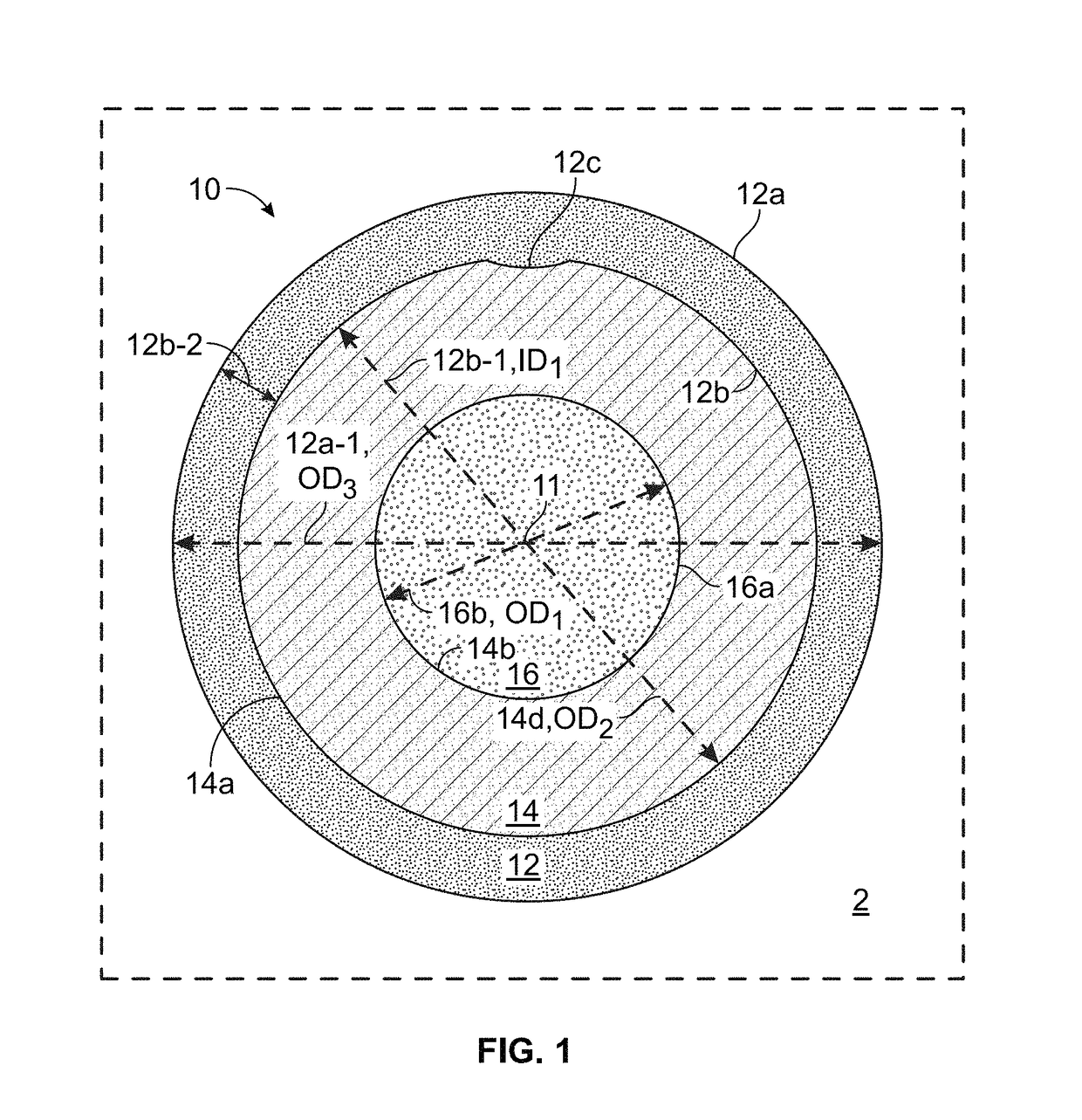

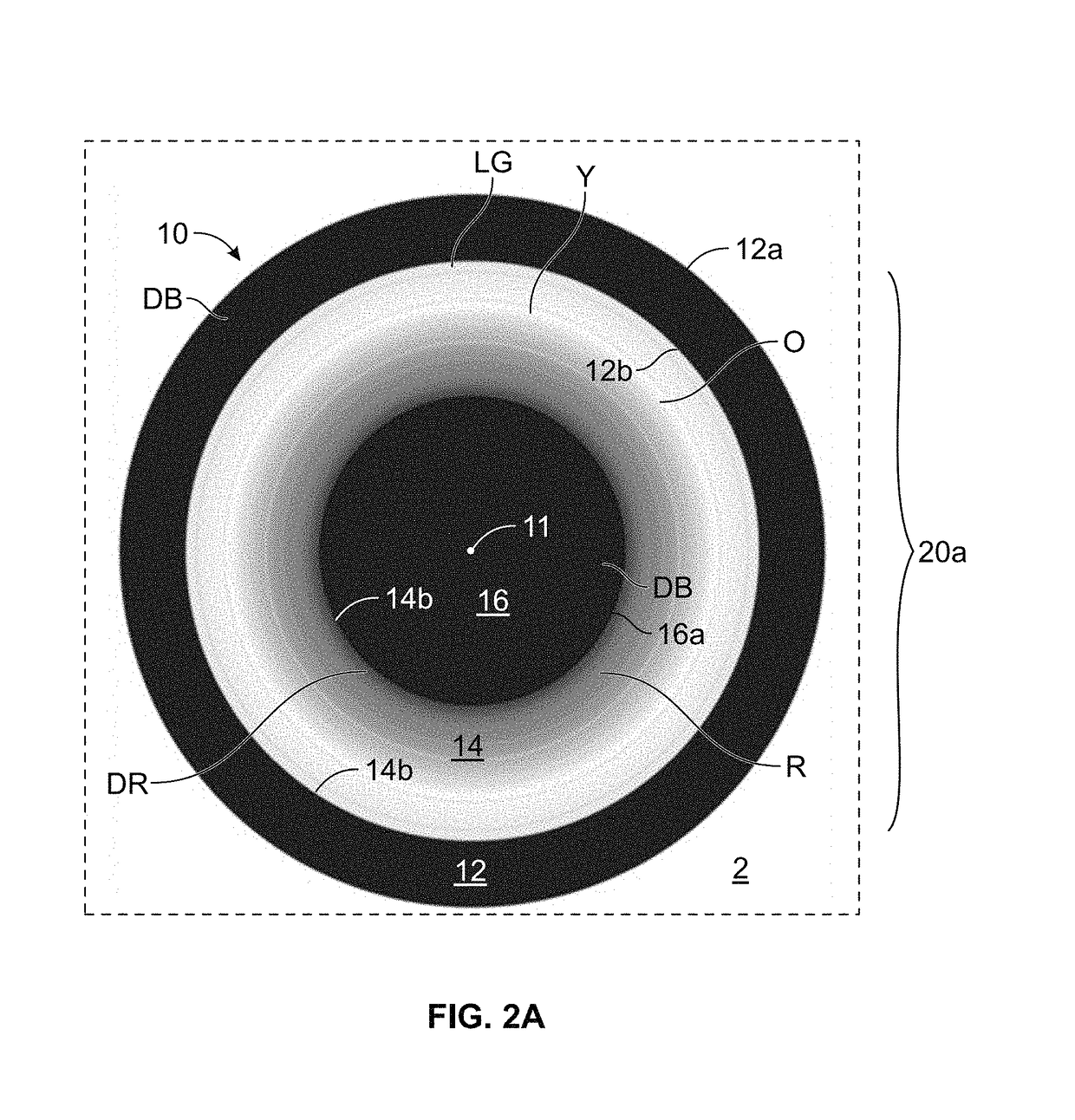

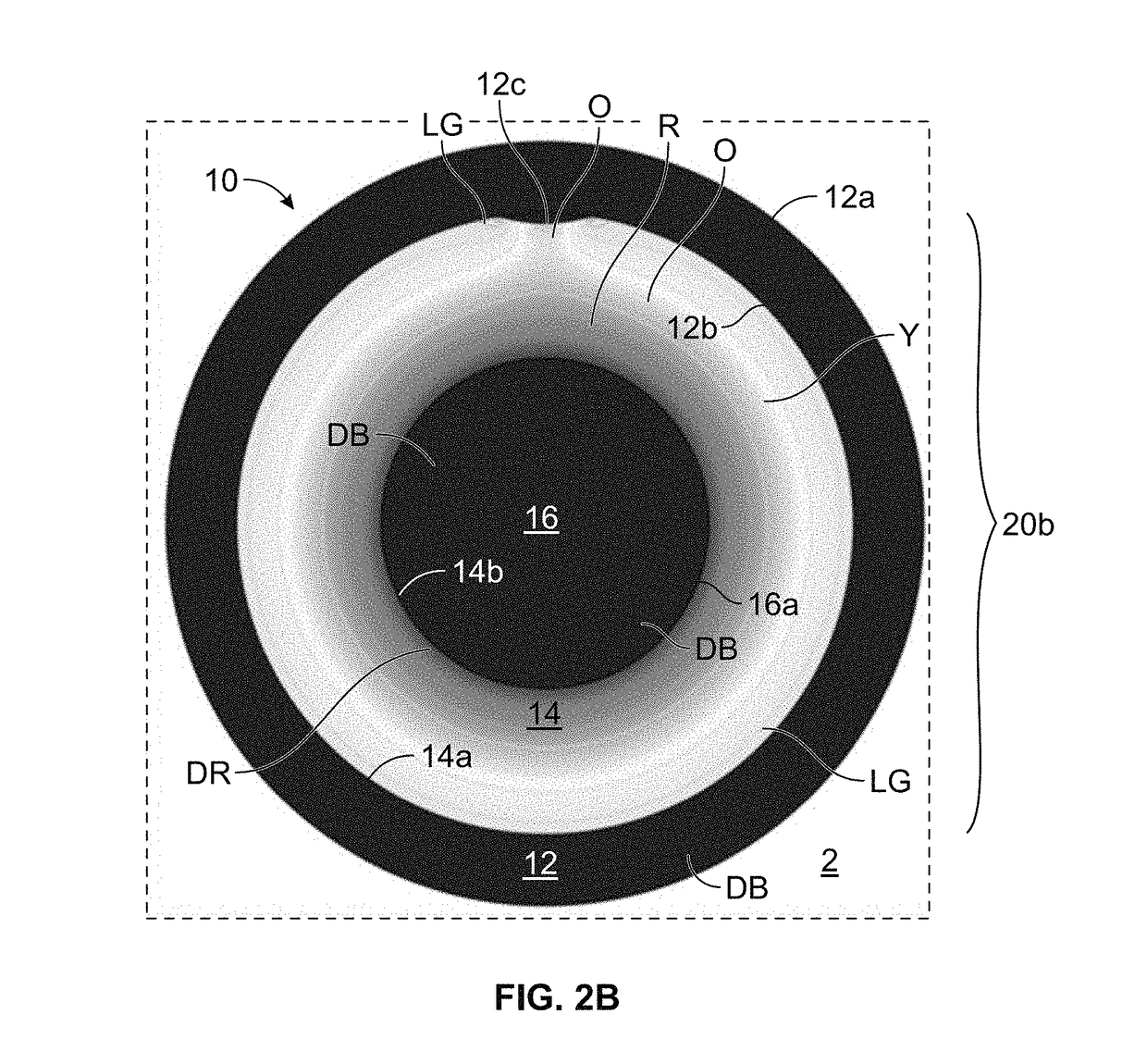

Stress control cones for downhole electrical power system tubing encapsulated power cables

ActiveUS20190089143A1Reduce electrical stressElectrically conductive connectionsDrilling rodsInsulation layerPower cable

A stress cone for reducing electrical stresses is disclosed for use on terminated ends of tubing encapsulated power cable used in surface applications in a subsurface well power system employing electric submersible pumps (ESPs). The stress cone comprises an annular section about a longitudinal axis for receiving a terminated end of the TEPC in its first end and for abutting the terminated metal TEPC end against a metal shoulder at its second end therein, and an insulation chamber axially aligned with and connected to the annular section. The chamber comprises a metal interior surface symmetrical about the axis. The insulated TEPC core (without outer metal sheath) passes through the insulation chamber along the axis and then exits. The ID of the TEPC metal sheath and the inside metal surface of the chamber form a smooth ground plane transition surface. Insulation material surrounds the TEPC insulation layer within the insulation chamber.

Owner:ARTIFICIAL ELEVATOR

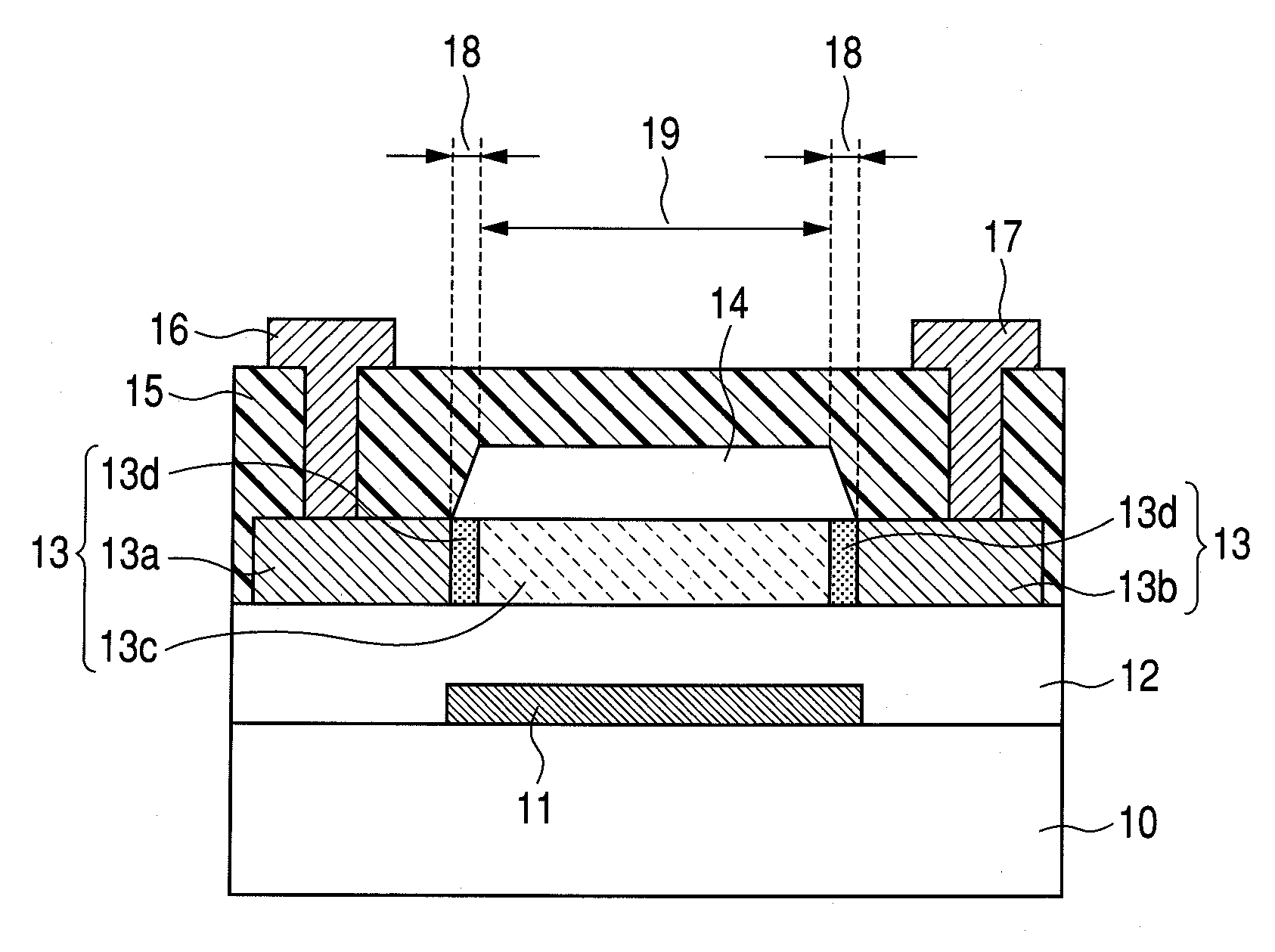

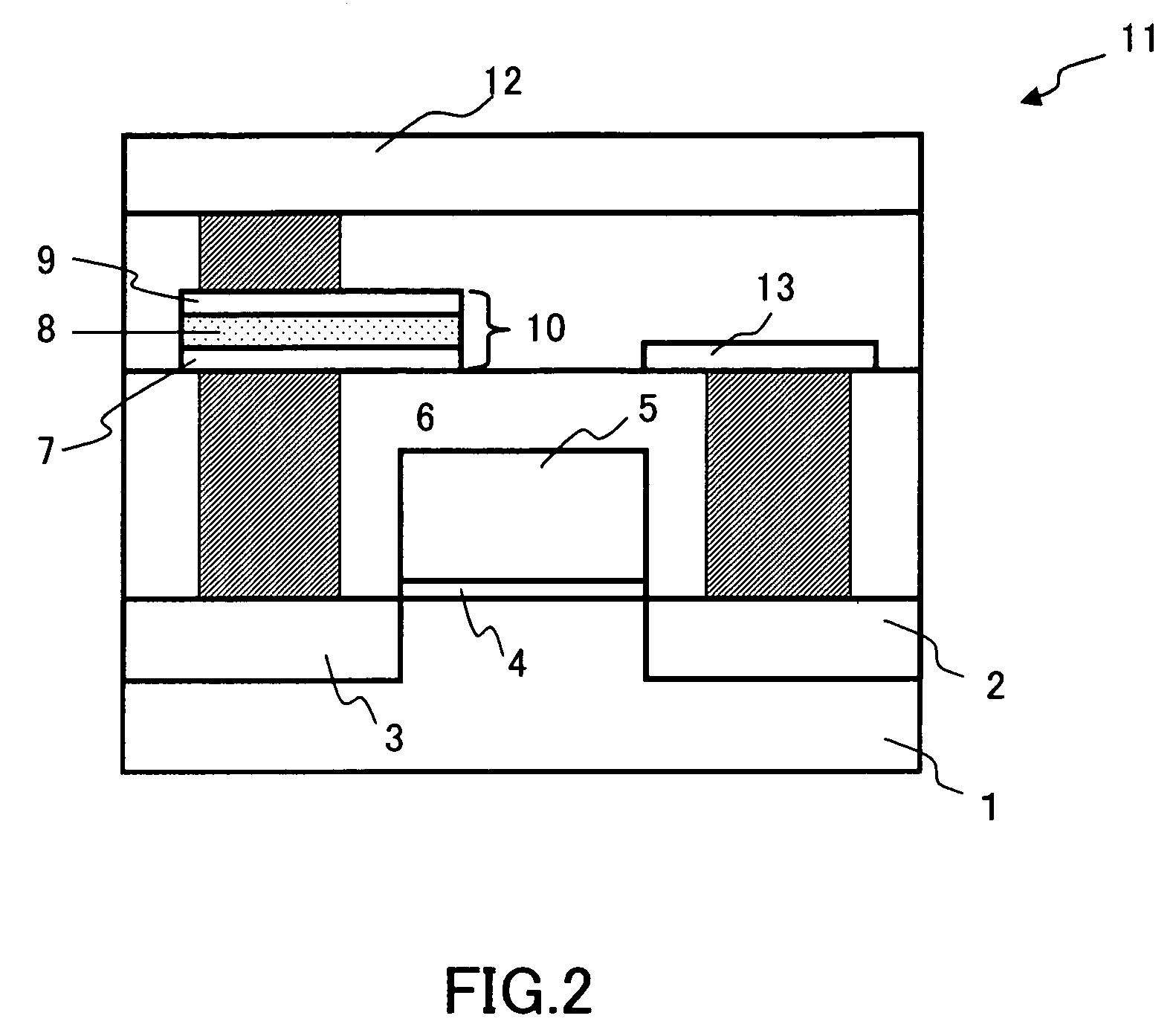

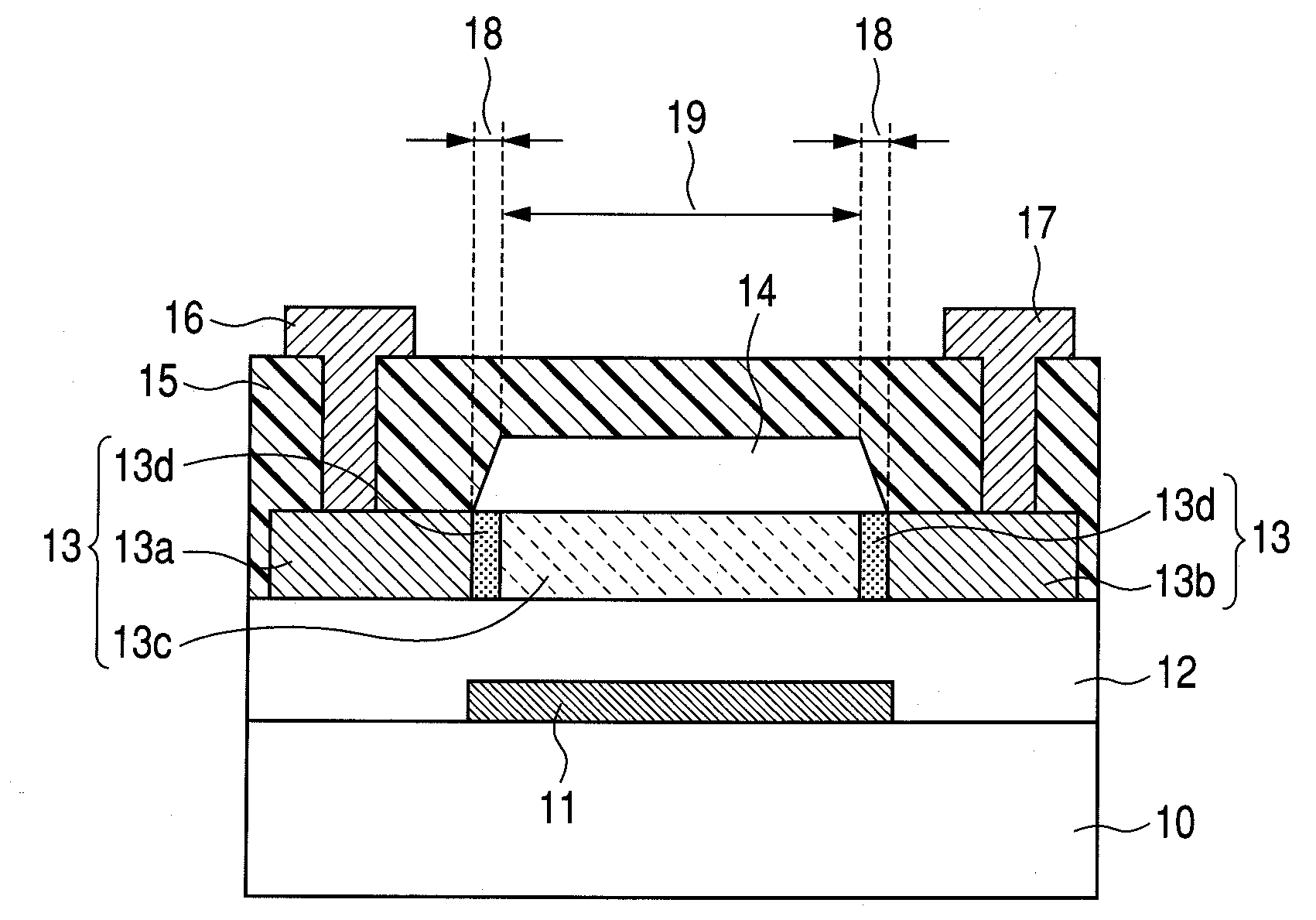

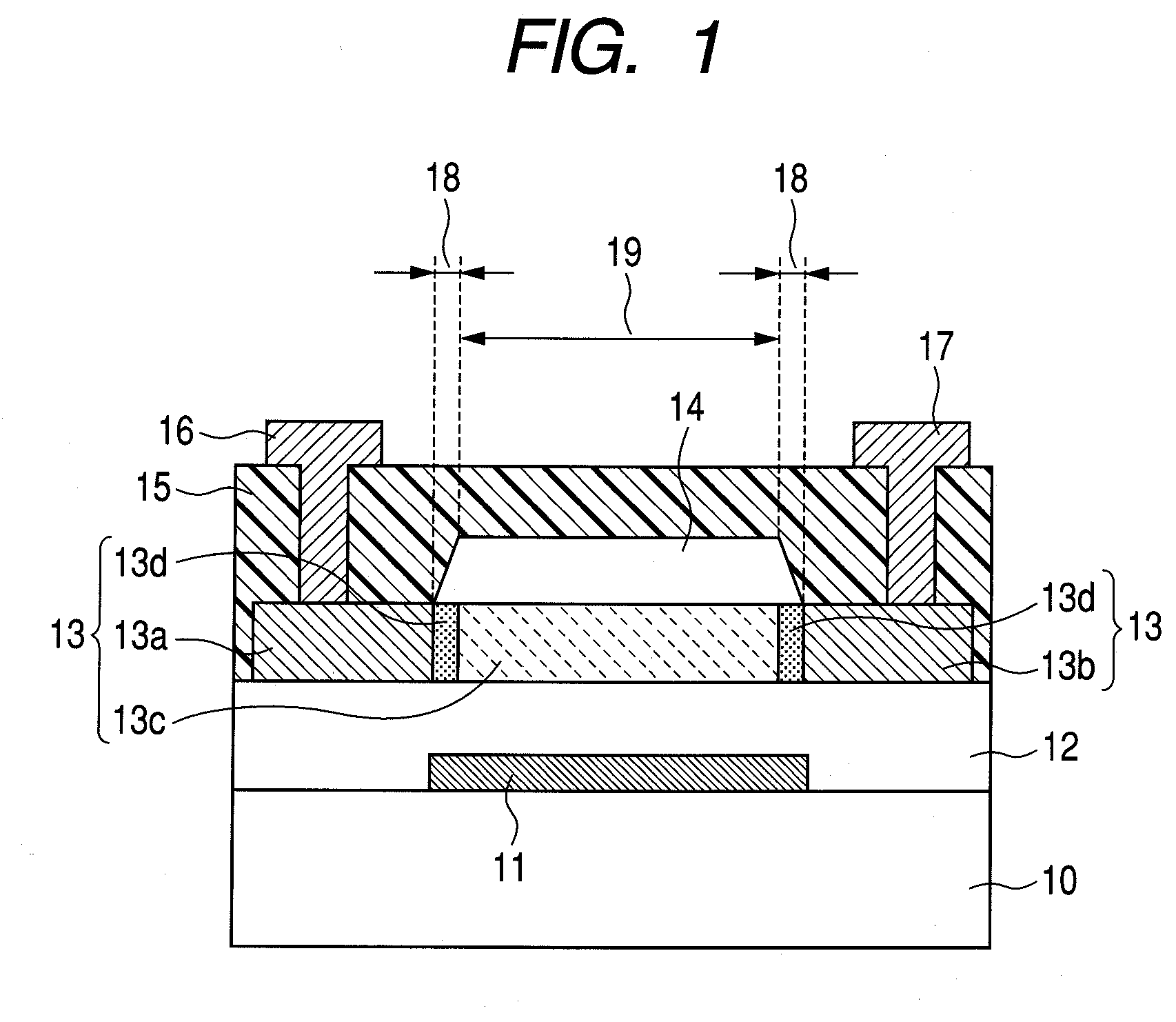

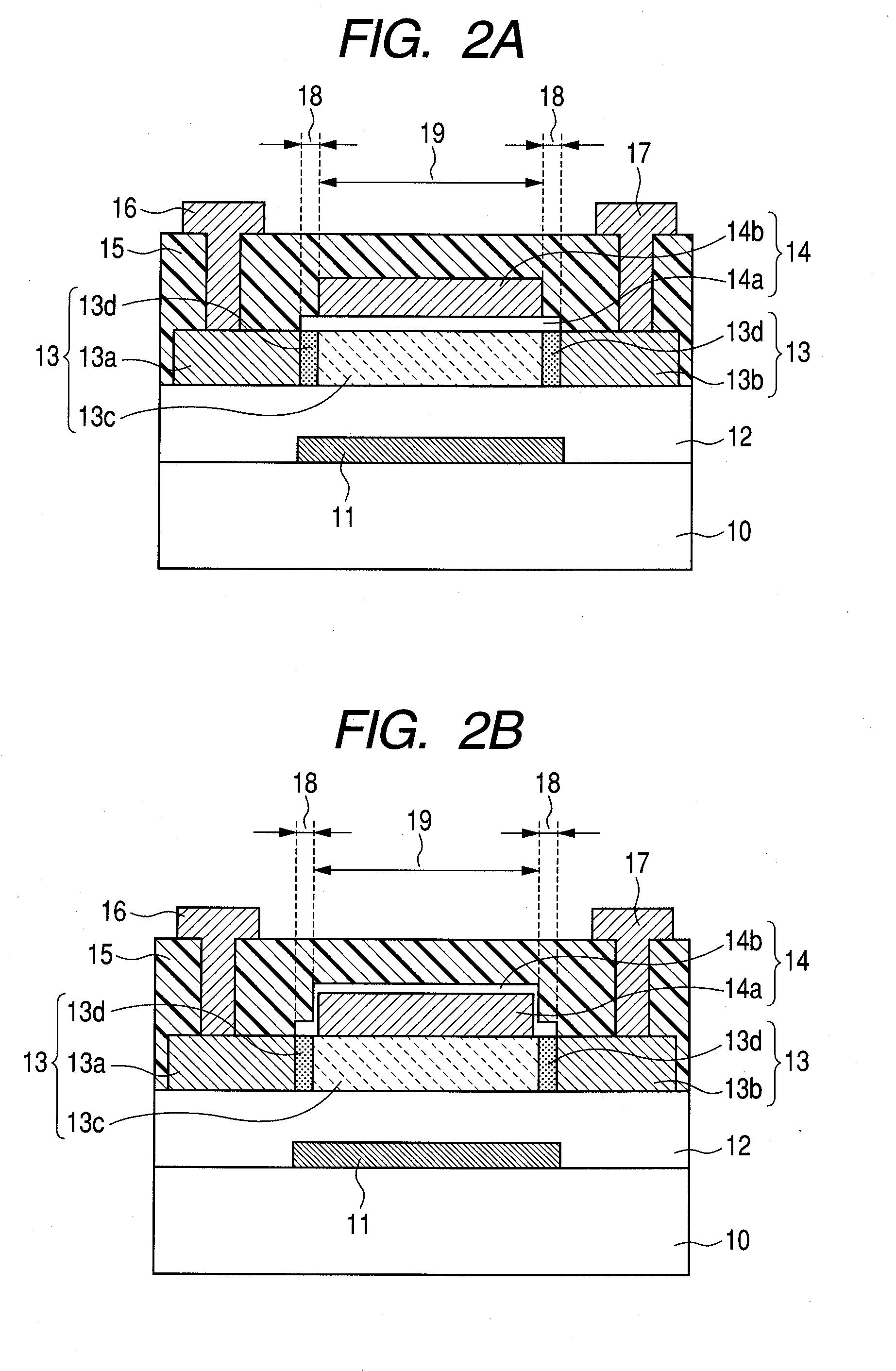

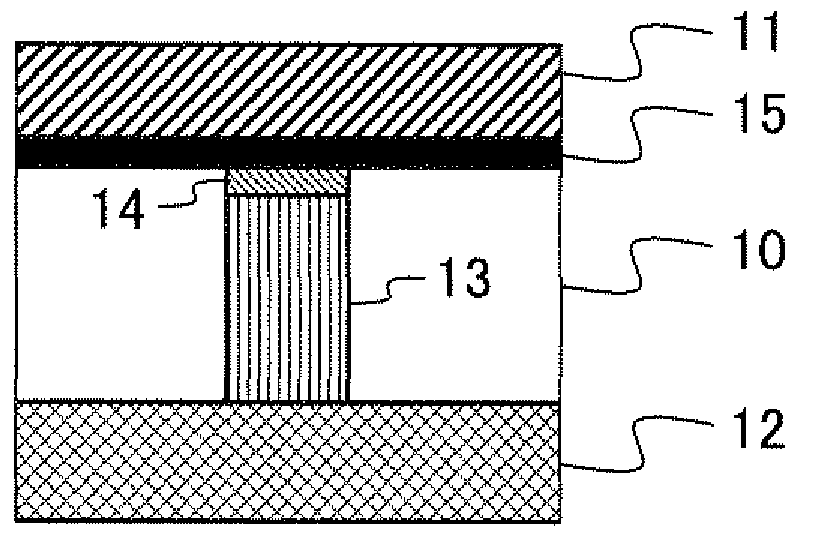

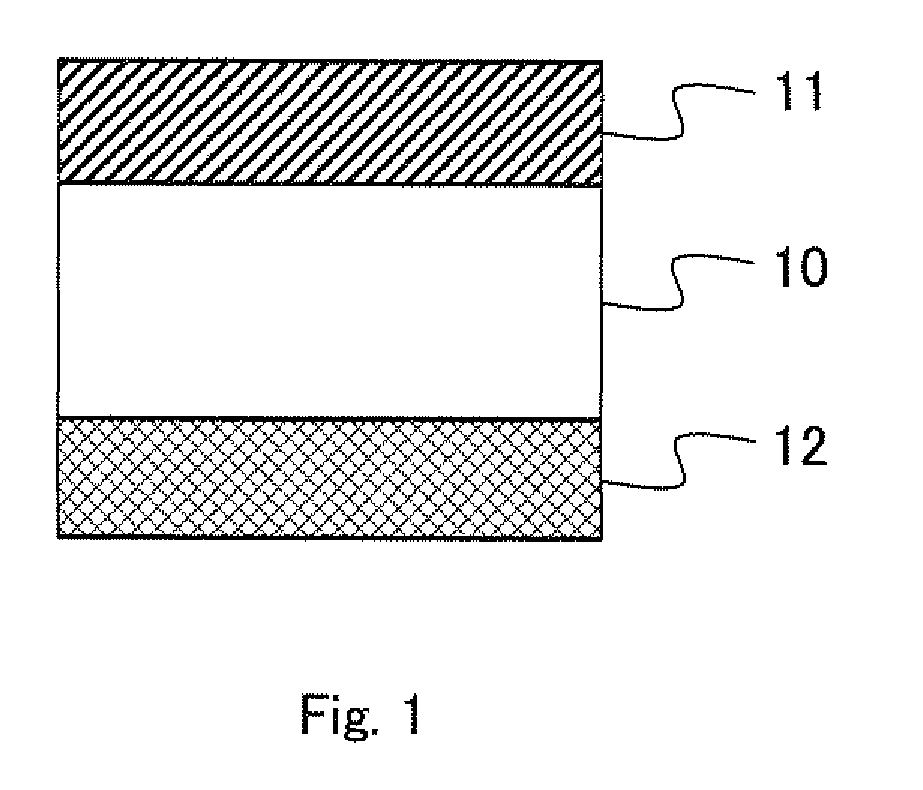

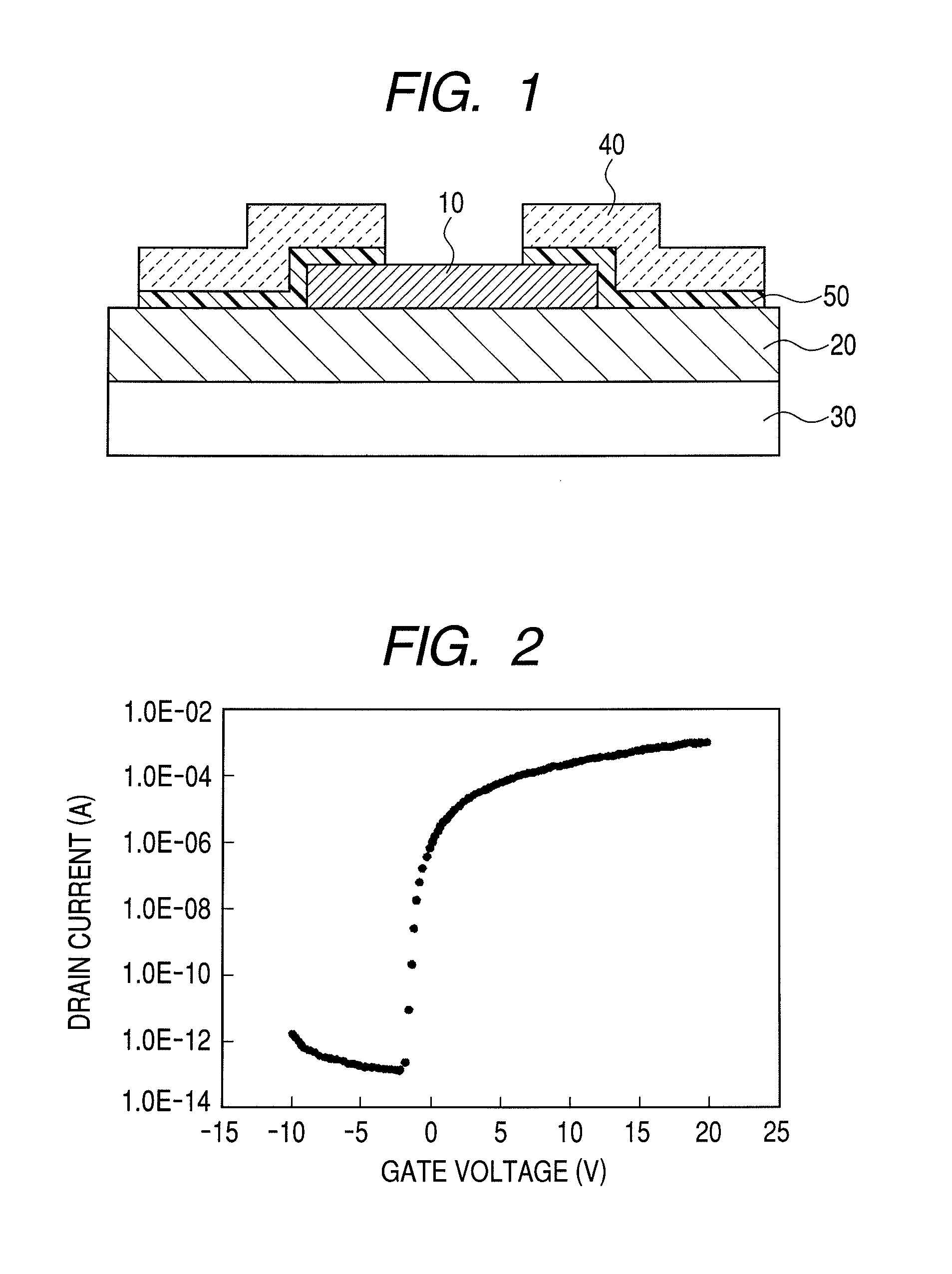

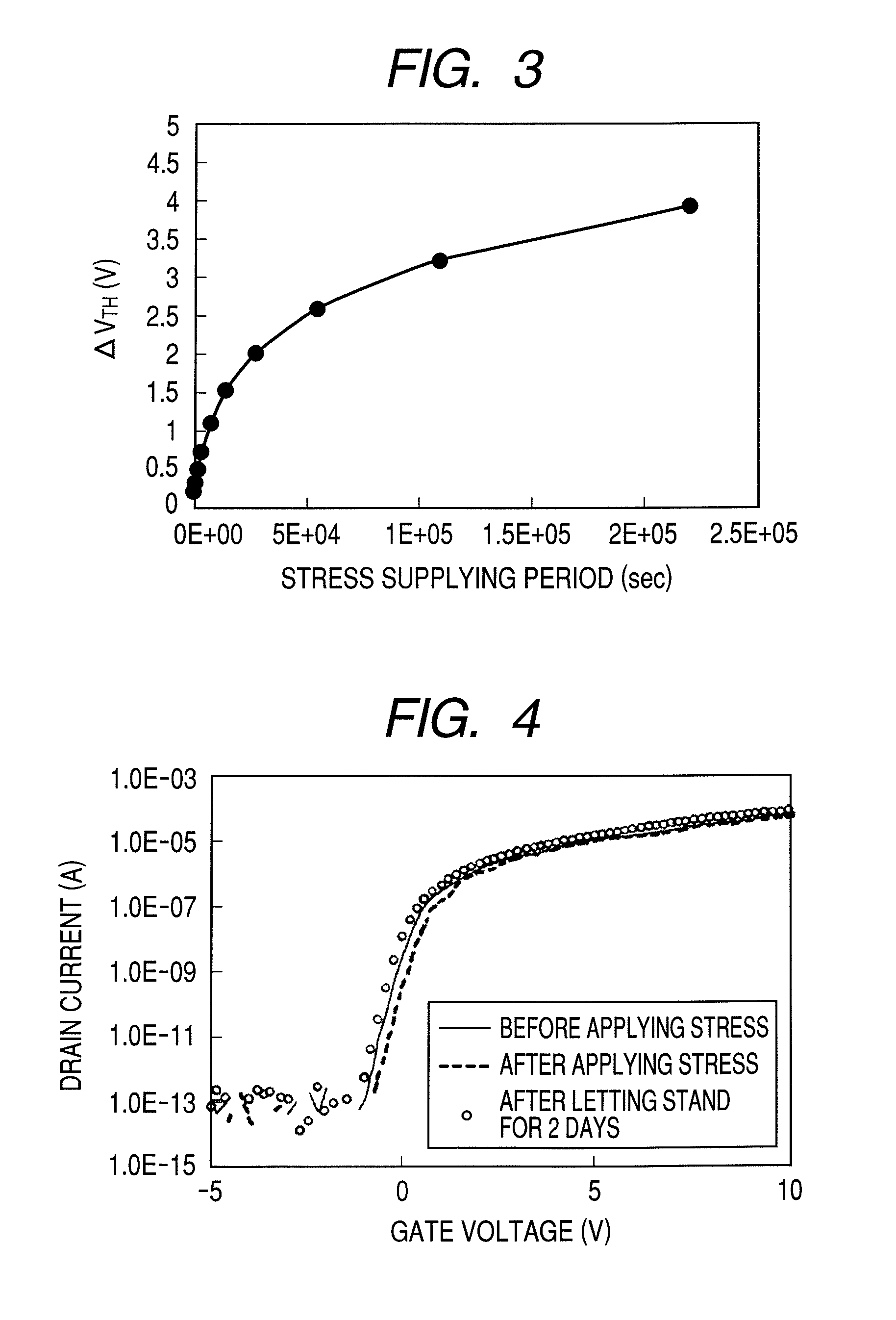

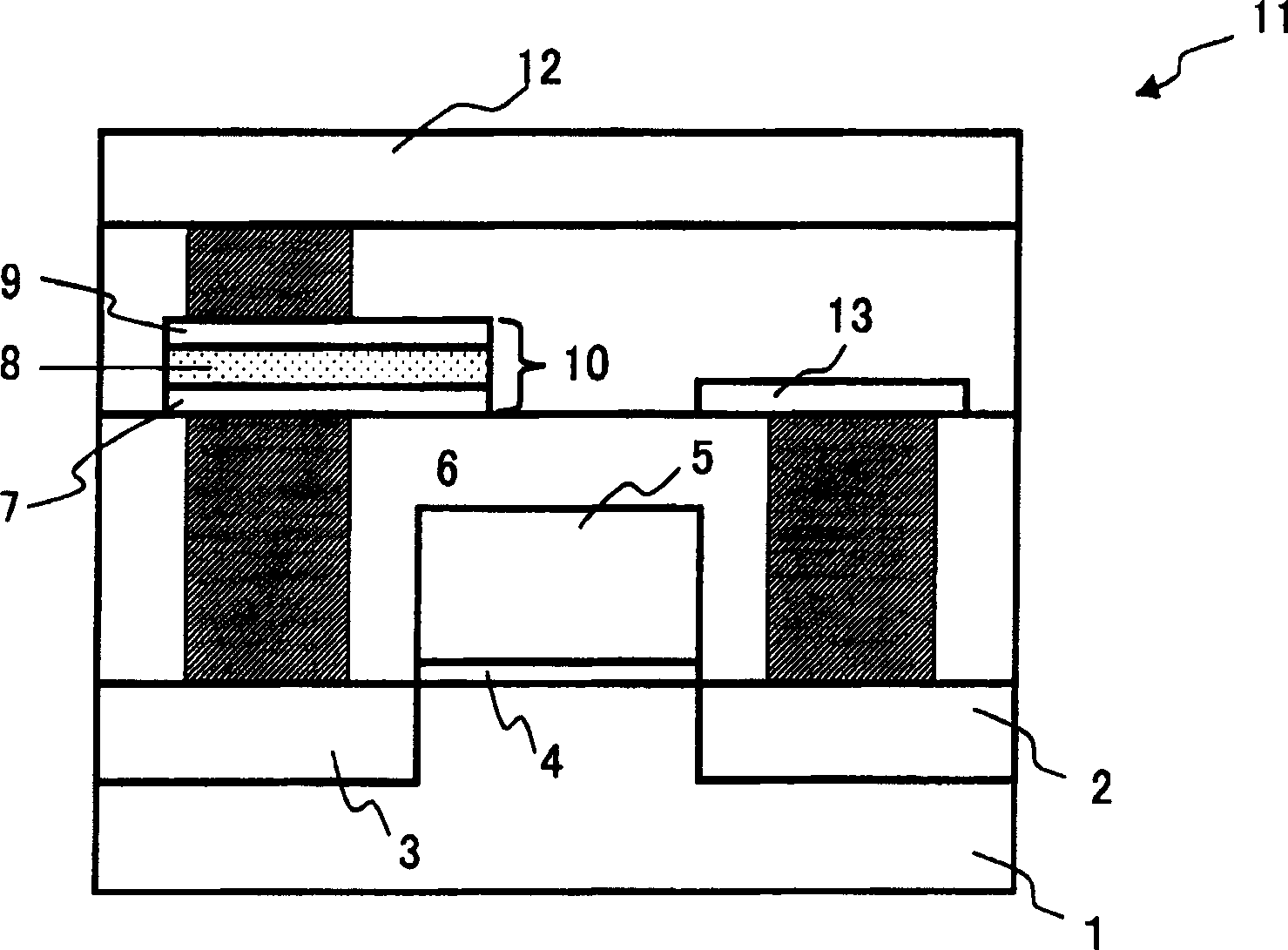

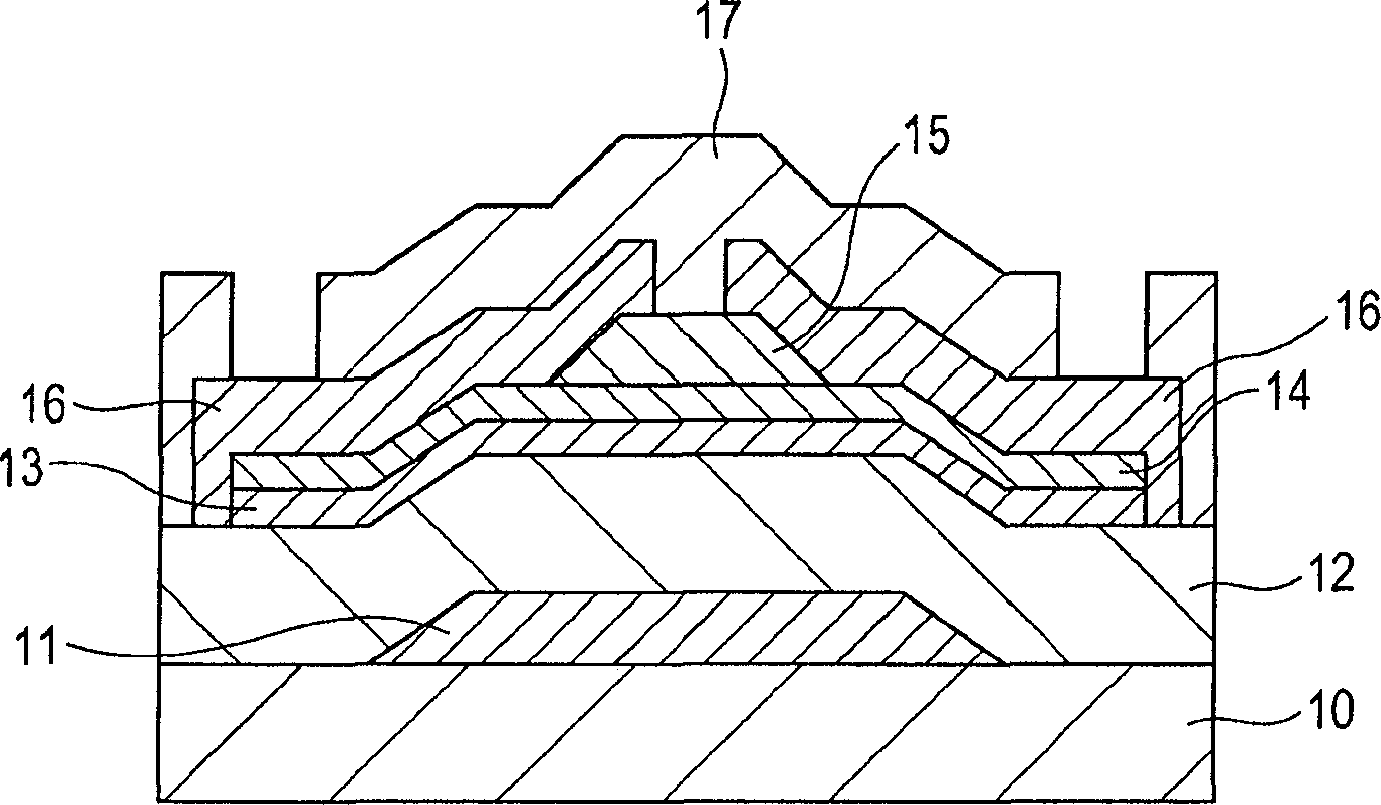

Thin film transistor and method of manufacturing the same

ActiveUS8445902B2Parasitic resistanceAvoid controlSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenEngineering

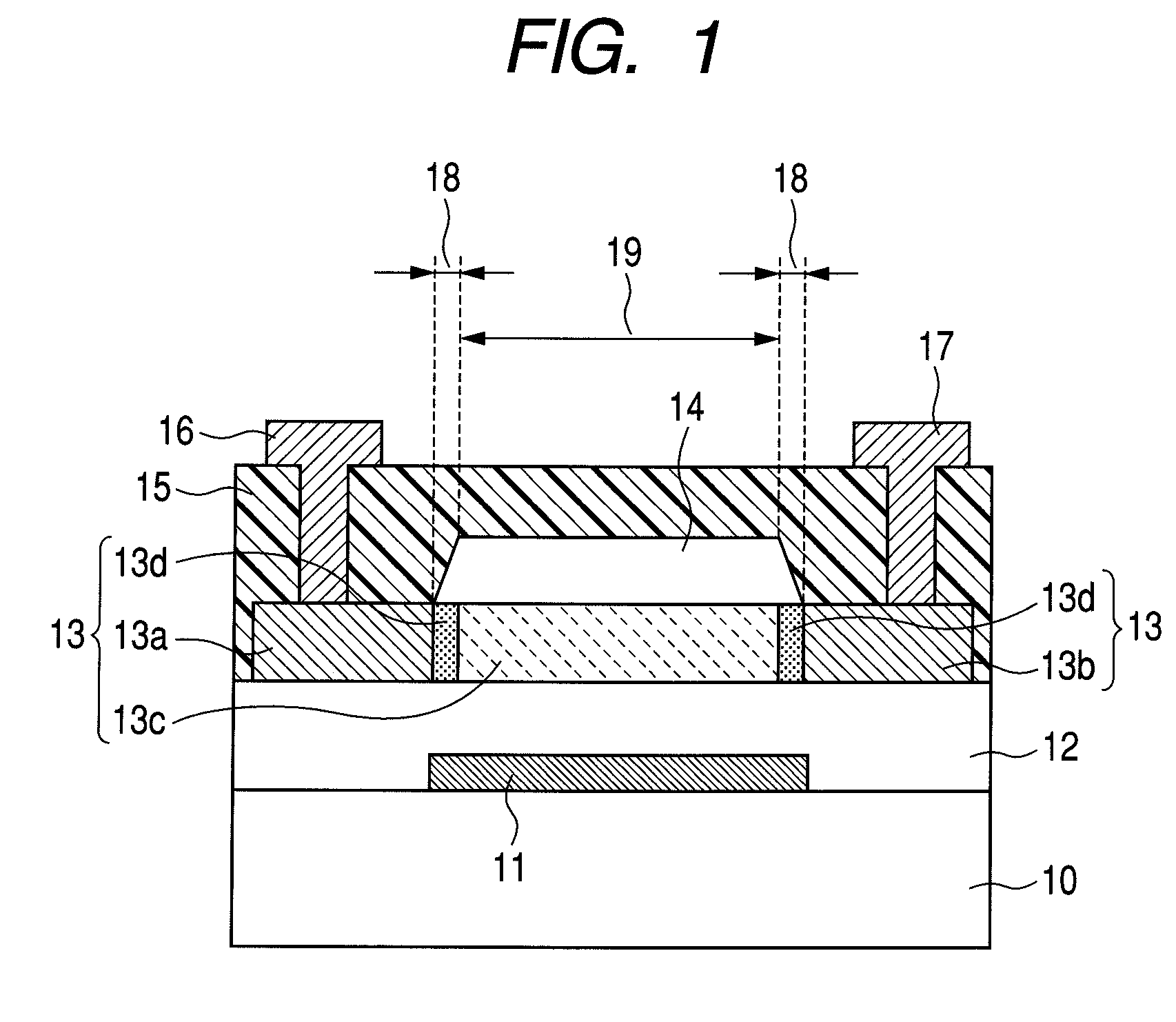

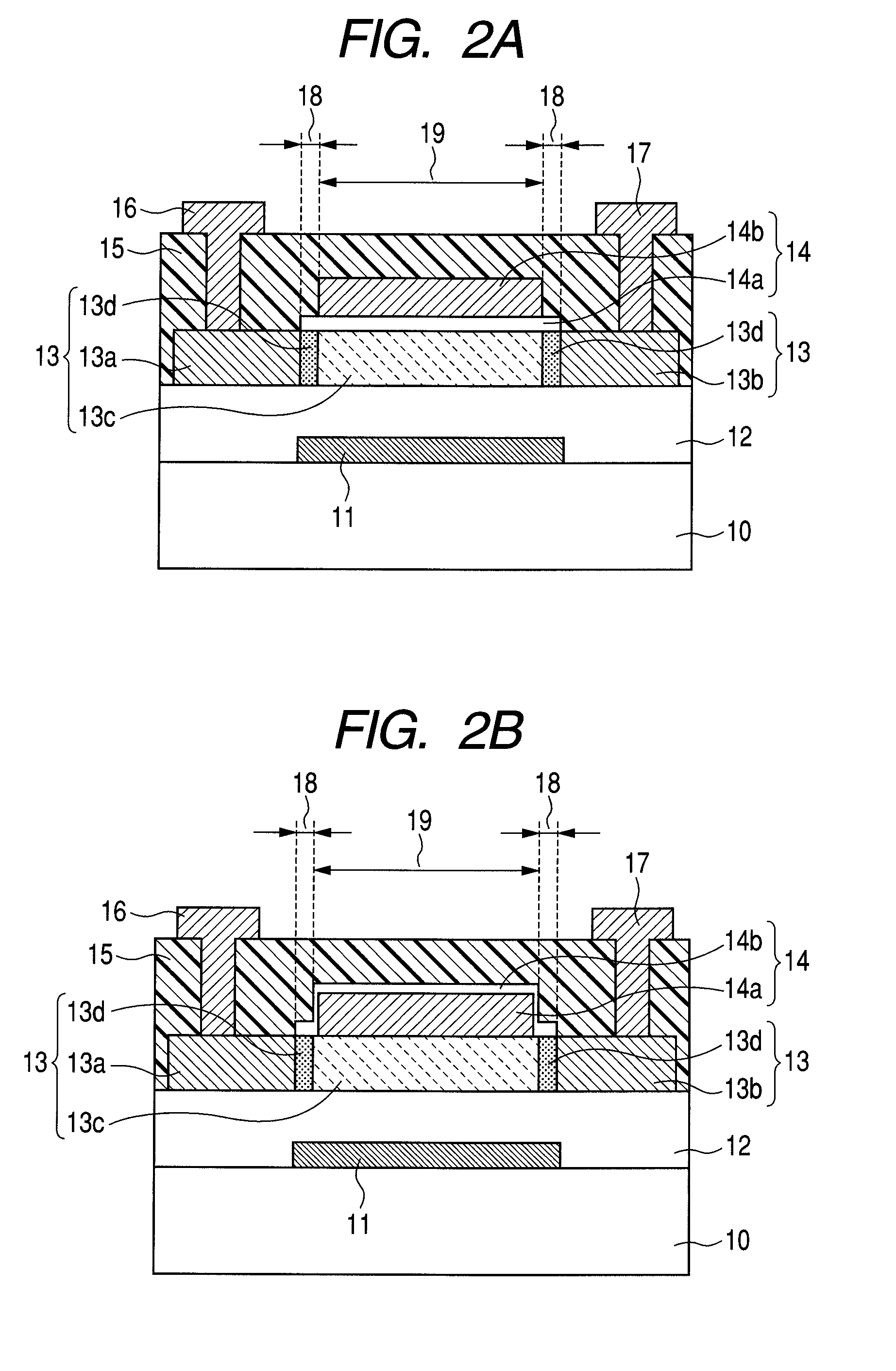

Provided are a coplanar structure thin film transistor that allows a threshold voltage to change only a little under electric stress, and a method of manufacturing the same. The thin film transistor includes on a substrate at least: a gate electrode; a gate insulating layer; an oxide semiconductor layer including a source electrode, a drain electrode, and a channel region; a channel protection layer; and an interlayer insulating layer. The channel protection layer includes one or more layers, the layer in contact with the oxide semiconductor layer among the one or more layers being made of an insulating material containing oxygen, ends of the channel protection layer are thinner than a central part of the channel protection layer, the interlayer insulating layer contains hydrogen, and regions of the oxide semiconductor layer that are in direct contact with the interlayer insulating layer form the source electrode and the drain electrode.

Owner:CANON KK

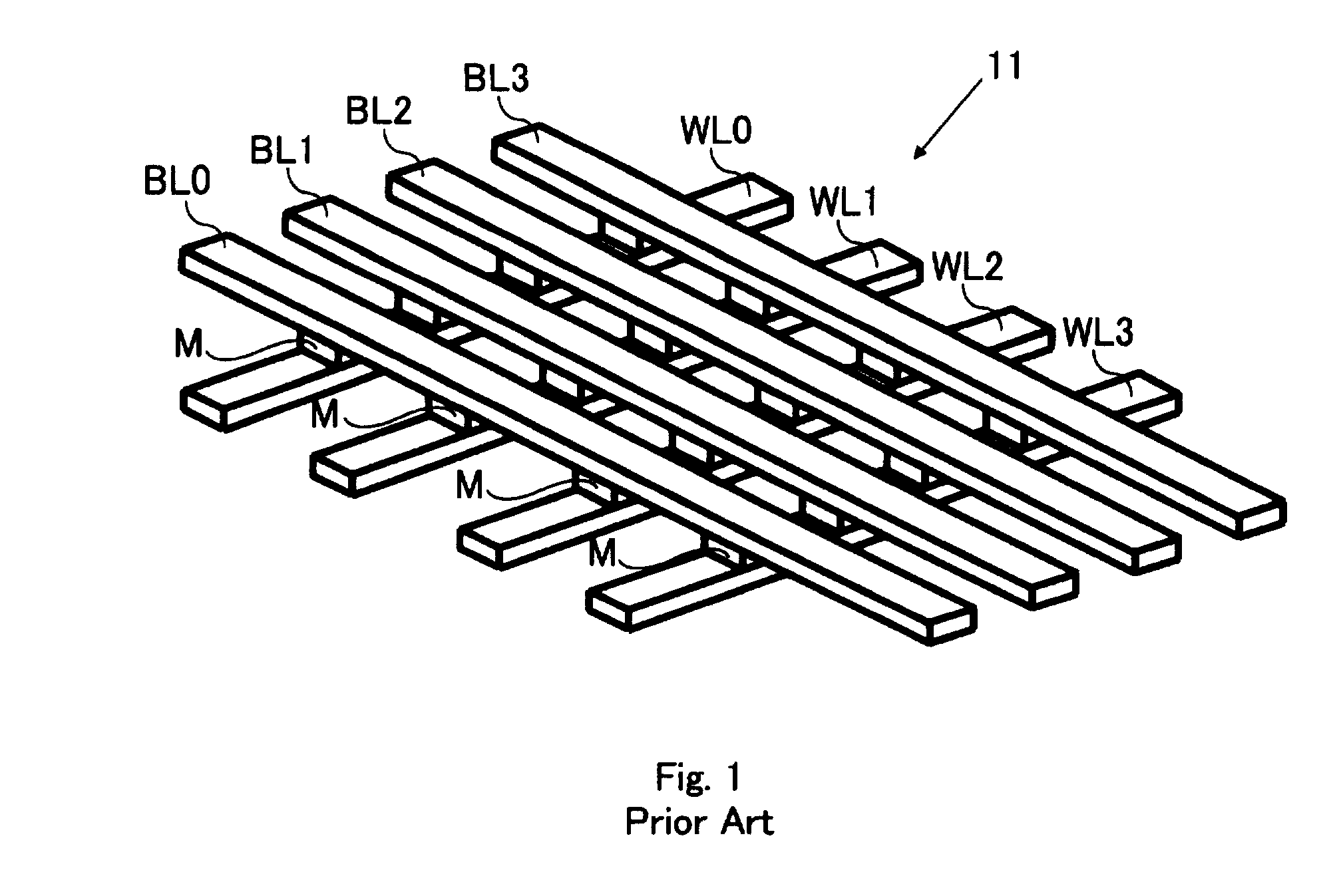

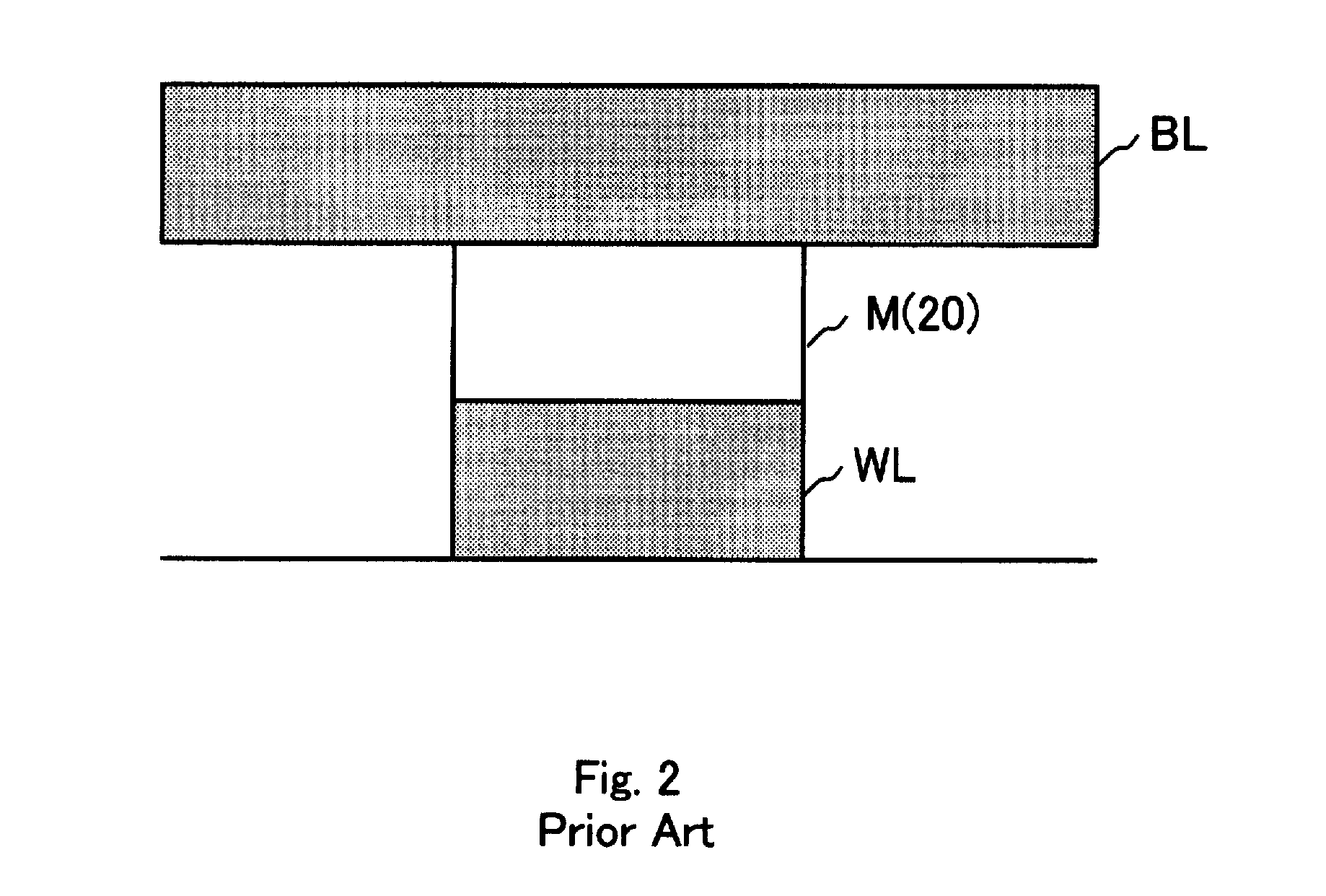

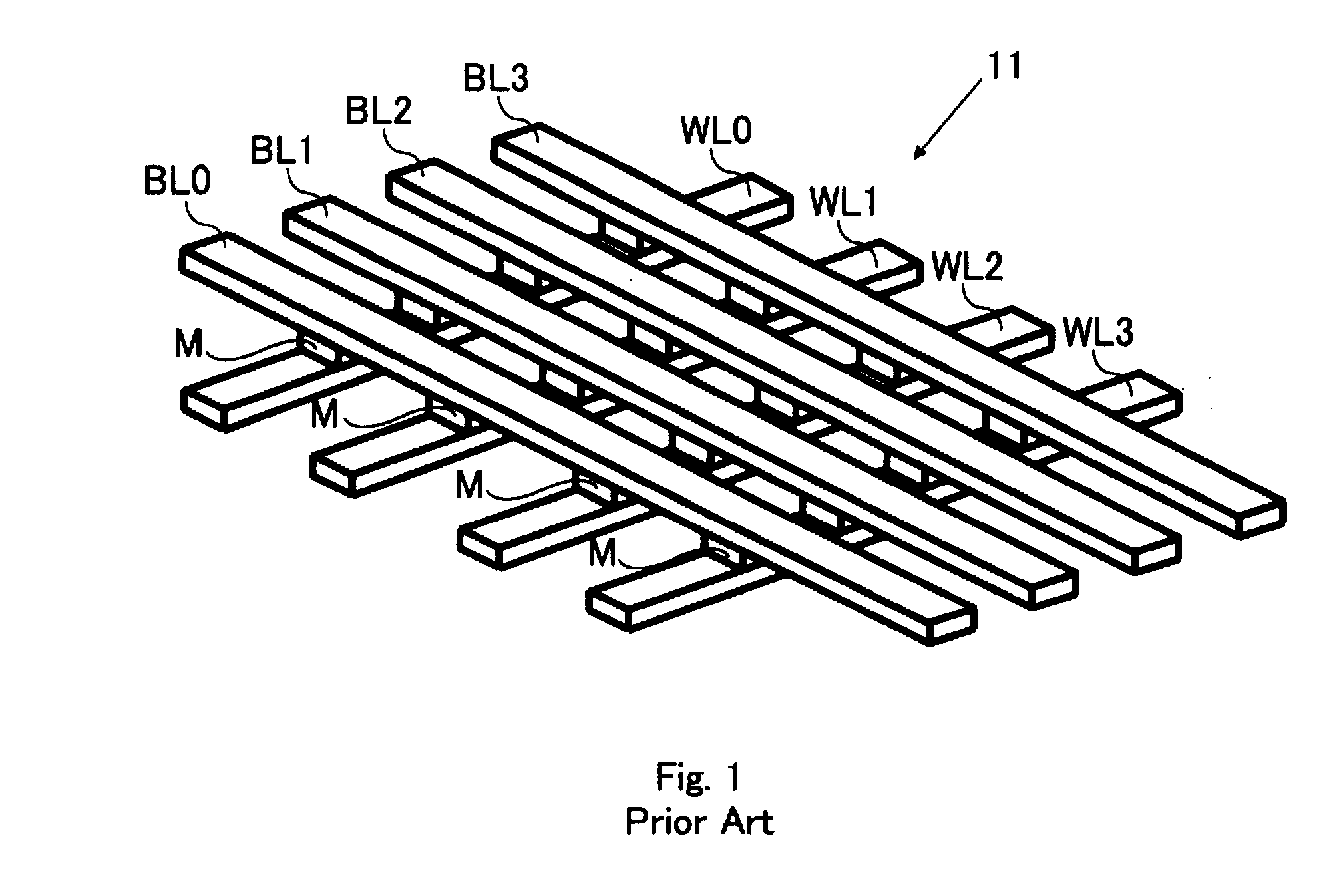

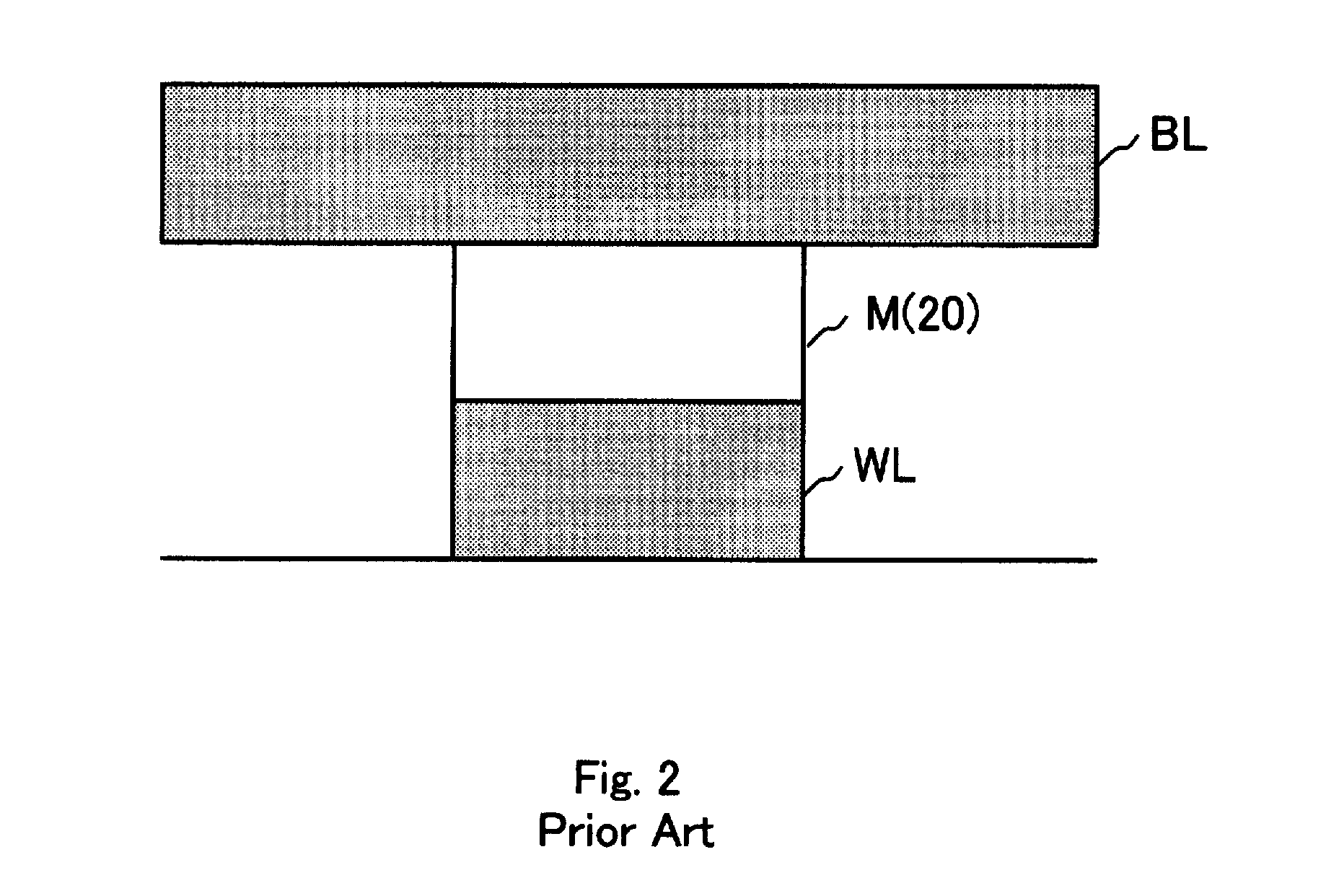

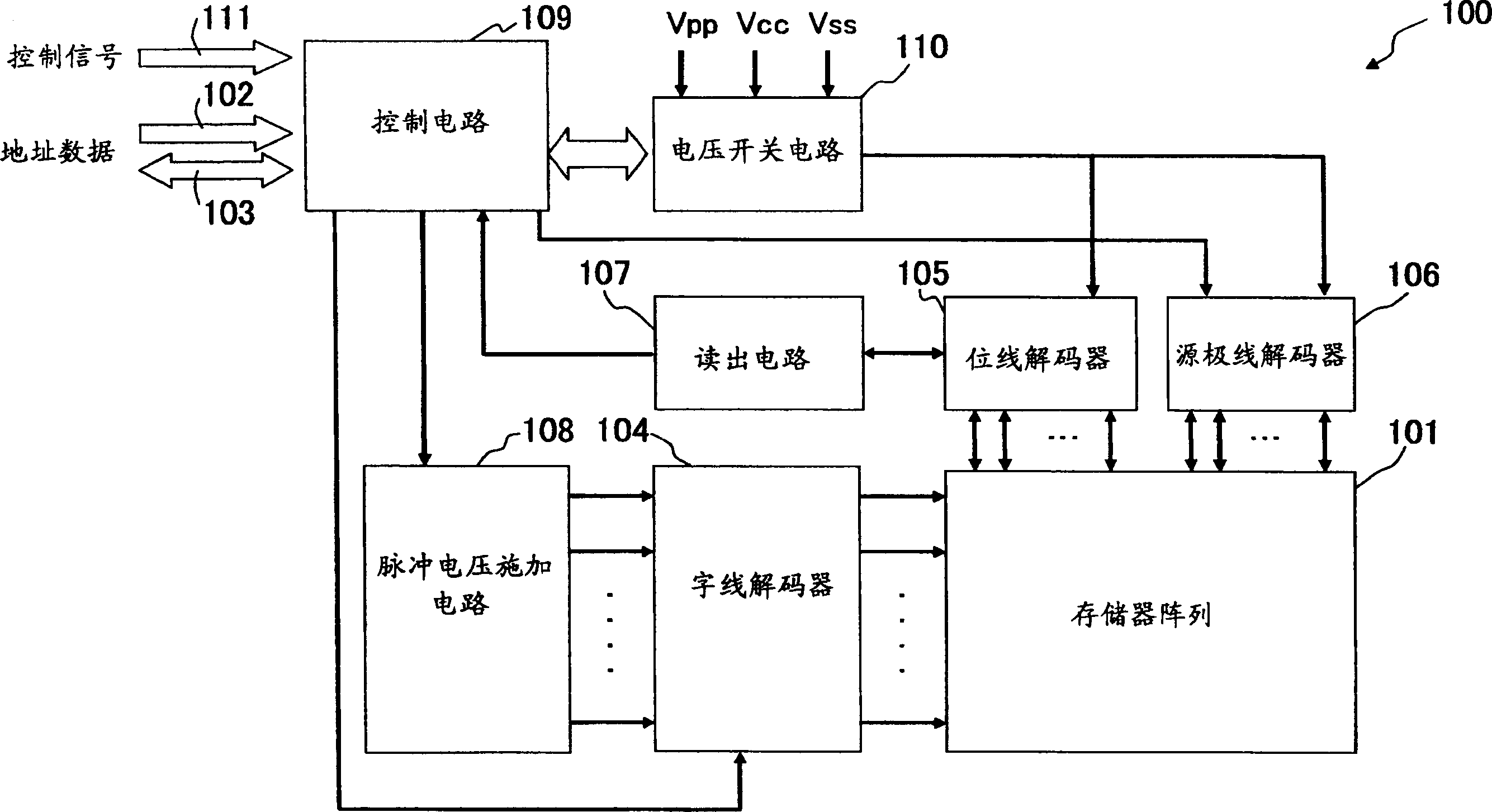

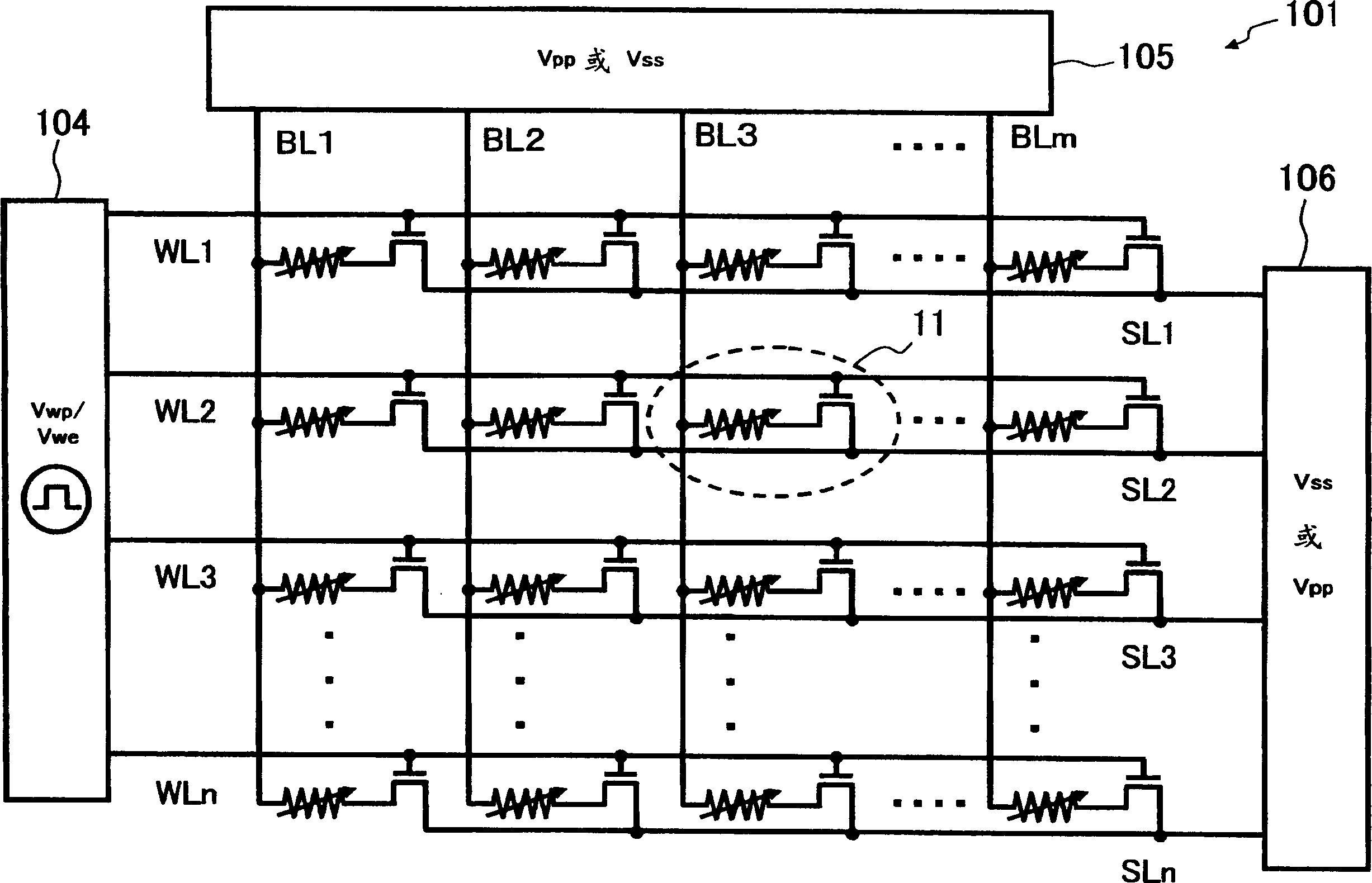

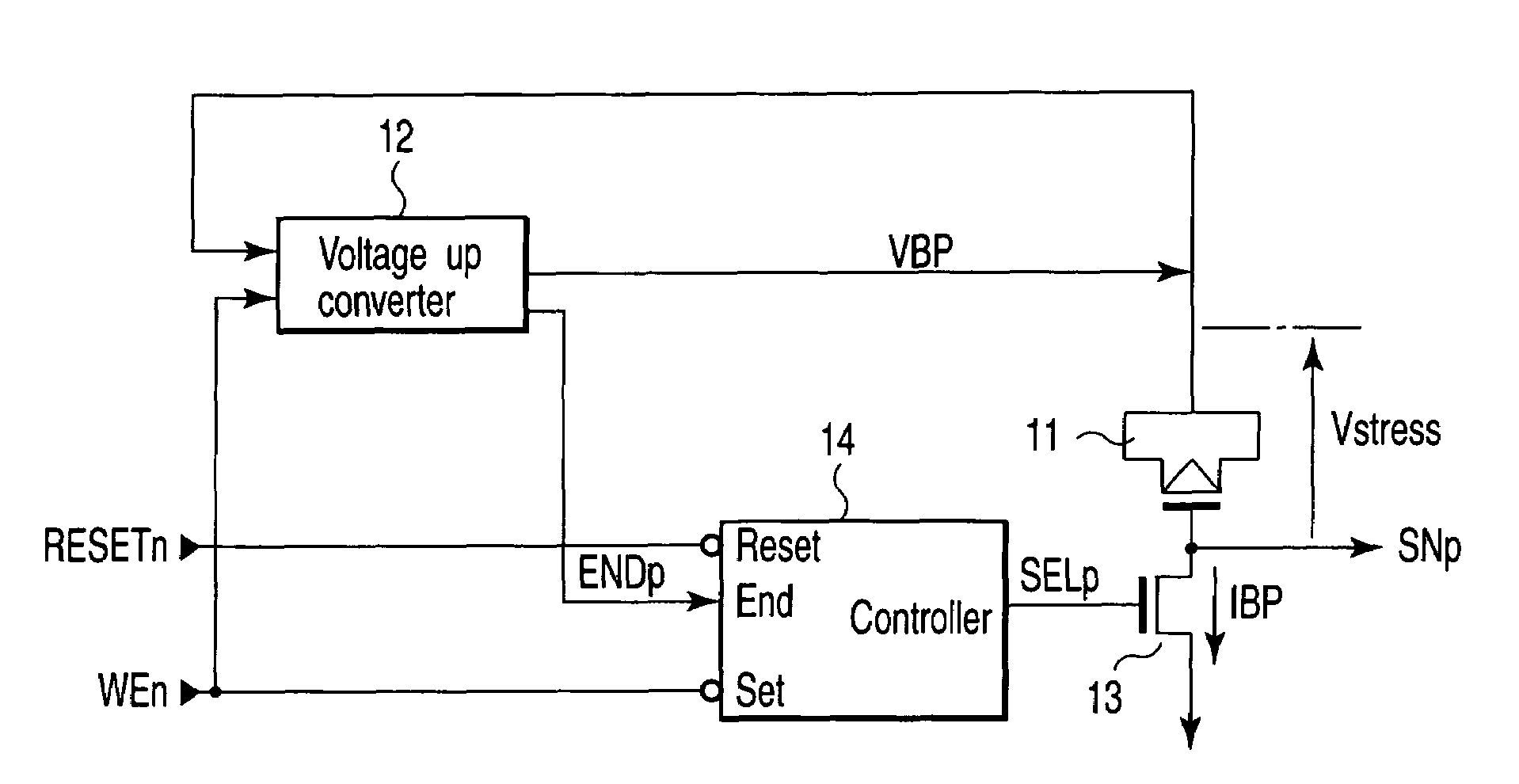

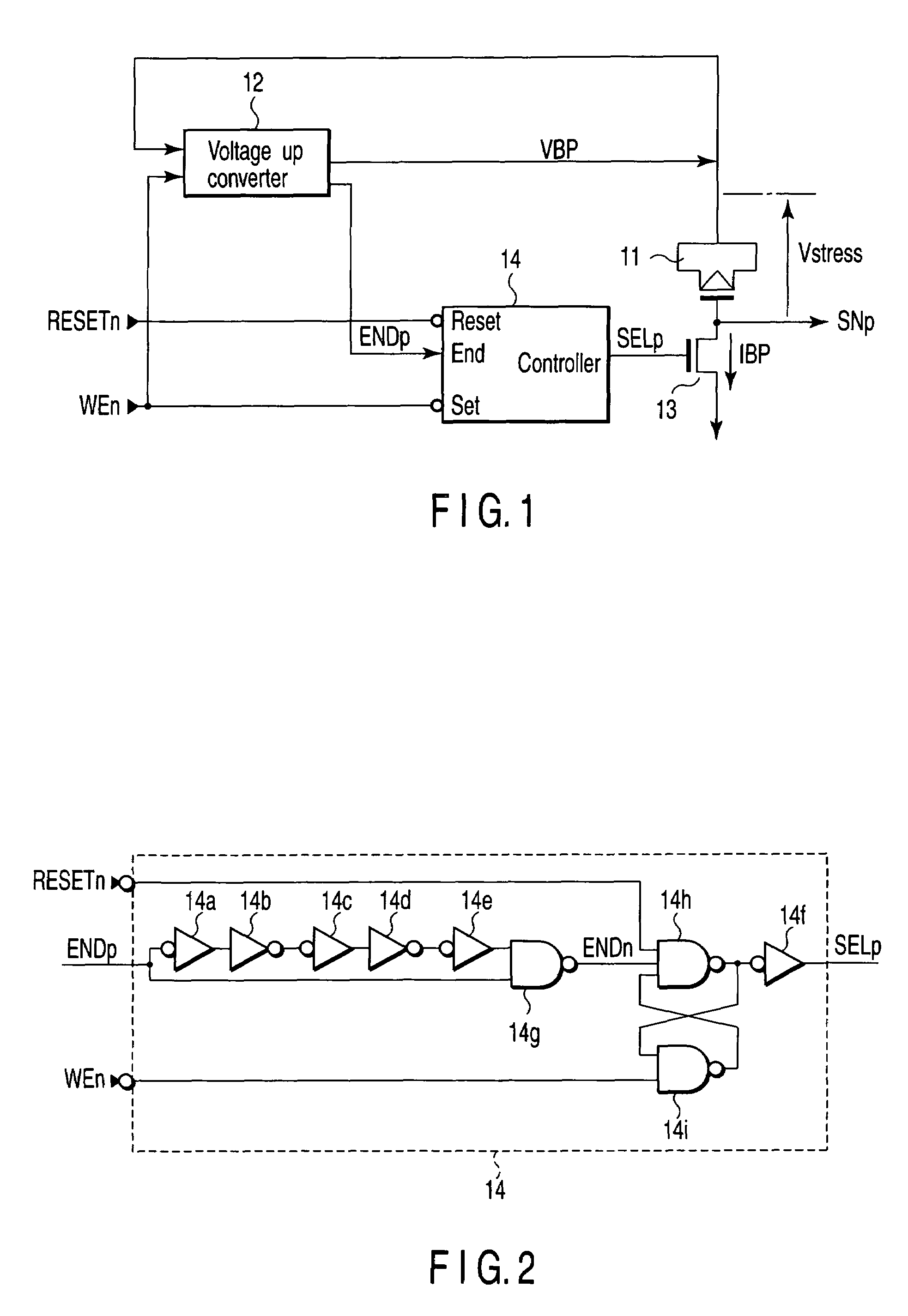

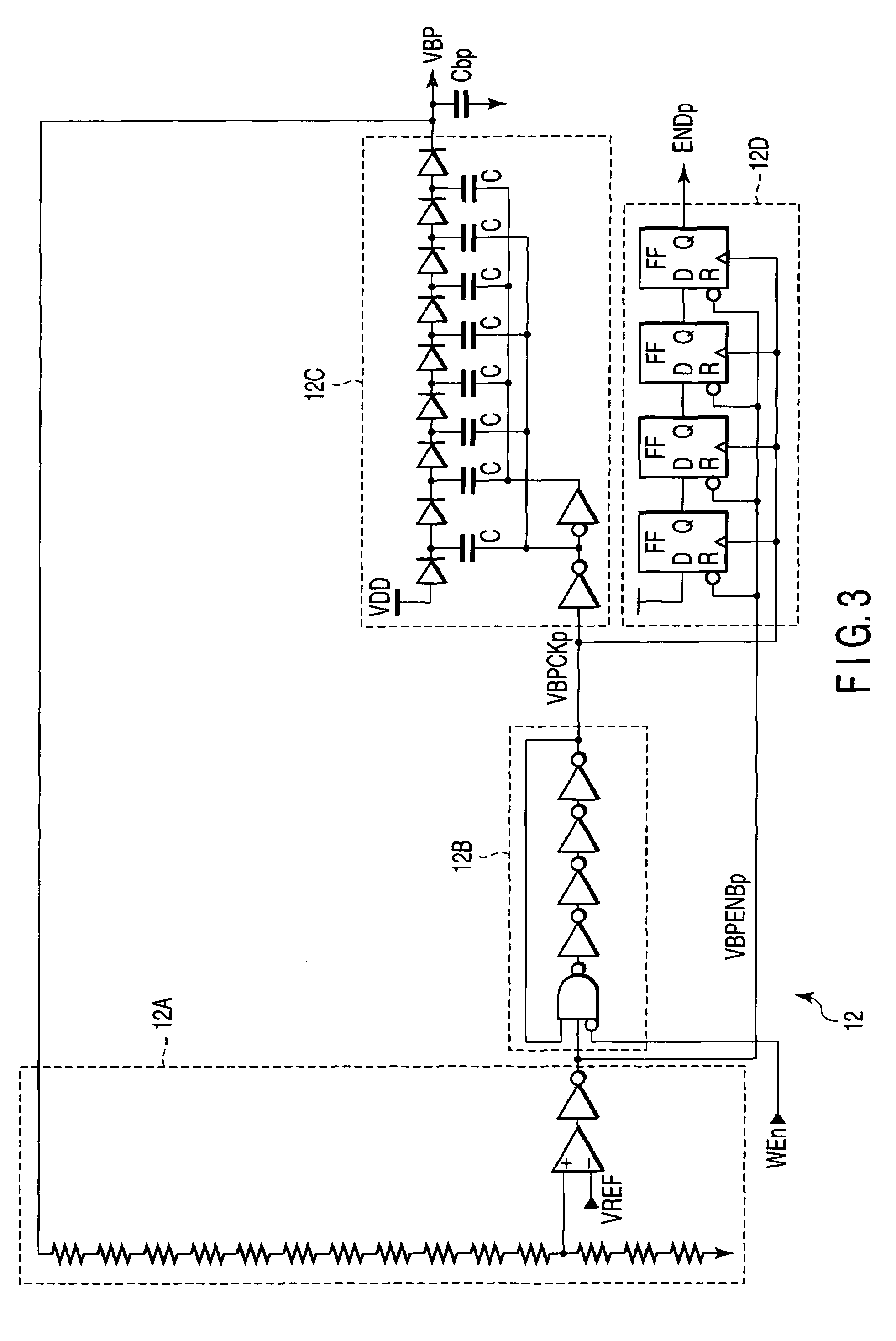

Nonvolatile semiconductor memory device and control method thereof

ActiveUS6995999B2Total current dropInhibition of current increaseSolid-state devicesRead-only memoriesBit lineVoltage pulse

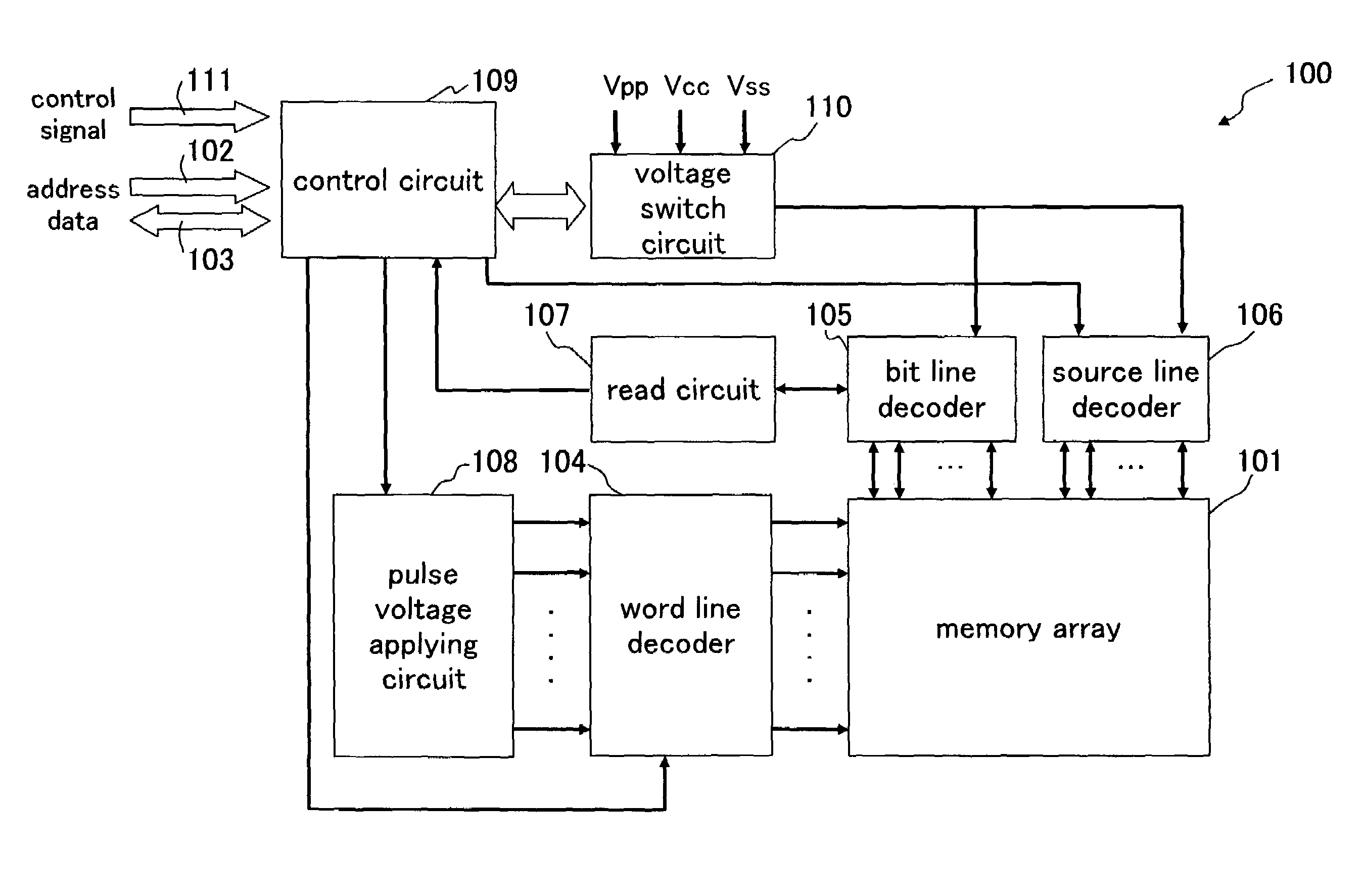

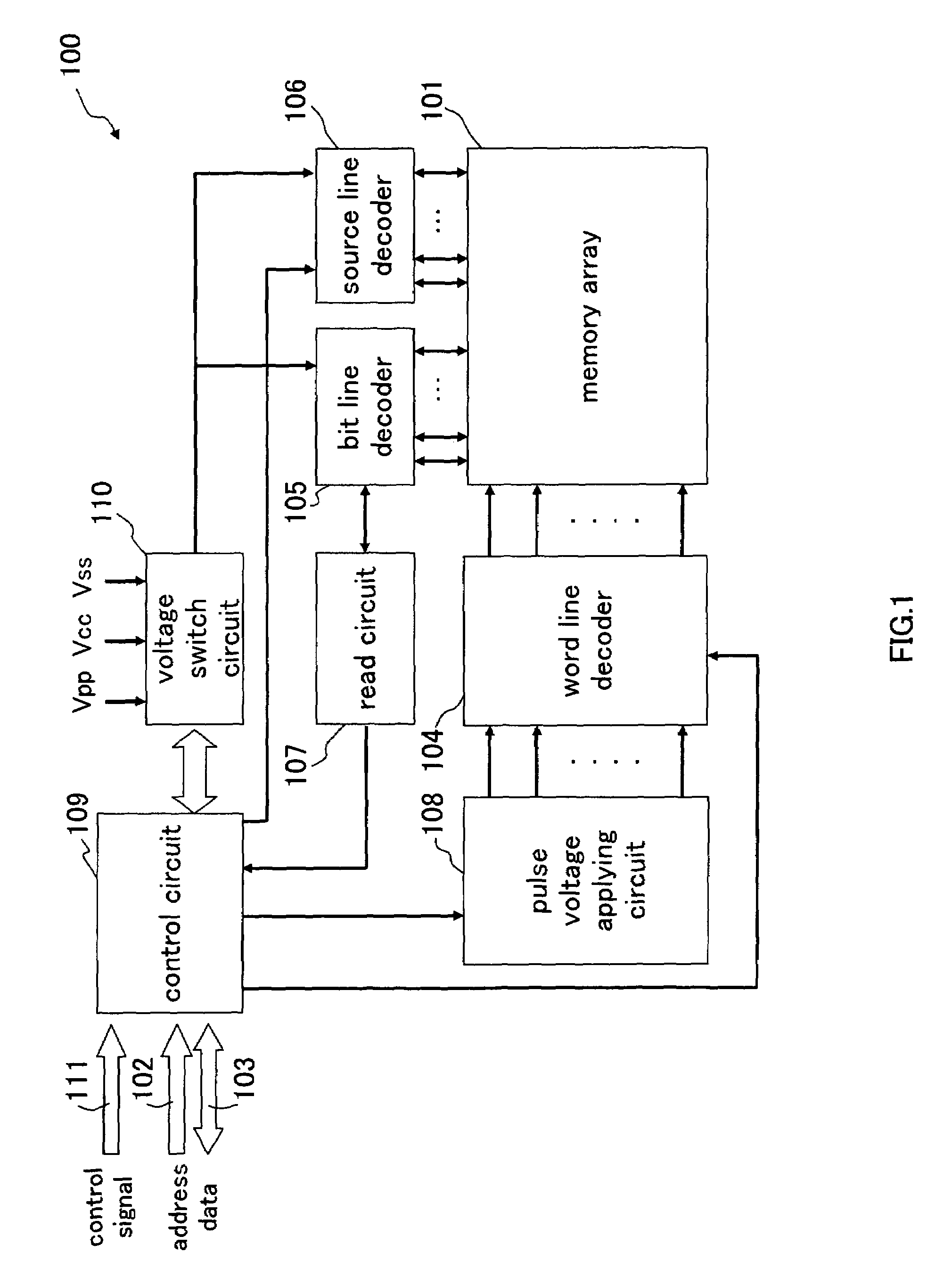

A nonvolatile semiconductor memory device includes a memory array in which a plurality of memory cells are arranged in a row direction and a column direction, each of the memory cells being formed by connecting one end of a variable resistive element for storing information according to a change in electric resistance caused by an electric stress and a drain of a selection transistor to each other on a semiconductor substrate, a voltage switch circuit for switching among a program voltage, an erase voltage and a read voltage to be applied to the source line and the bit line connected to the memory cell, and a pulse voltage applying circuit. In the state where the program voltage or erase voltage corresponding to the bit line and the source line is applied to the bit line and the source line connected to a memory cell to be programmed or erased in the memory array via the voltage switch circuit, the pulse voltage applying circuit applies a voltage pulse for programming or erasing to the word line connected to the gate electrode of the selection transistor connected to the memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film transistor and method of manufacturing the same

ActiveUS20110042670A1Rate control can be preventedReduce parasitic resistanceTransistorSemiconductor/solid-state device manufacturingHydrogenEngineering

Provided are a coplanar structure thin film transistor that allows a threshold voltage to change only a little under electric stress, and a method of manufacturing the same. The thin film transistor includes on a substrate at least: a gate electrode; a gate insulating layer; an oxide semiconductor layer including a source electrode, a drain electrode, and a channel region; a channel protection layer; and an interlayer insulating layer. The channel protection layer includes one or more layers, the layer in contact with the oxide semiconductor layer among the one or more layers being made of an insulating material containing oxygen, ends of the channel protection layer are thinner than a central part of the channel protection layer, the interlayer insulating layer contains hydrogen, and regions of the oxide semiconductor layer that are in direct contact with the interlayer insulating layer form the source electrode and the drain electrode.

Owner:CANON KK

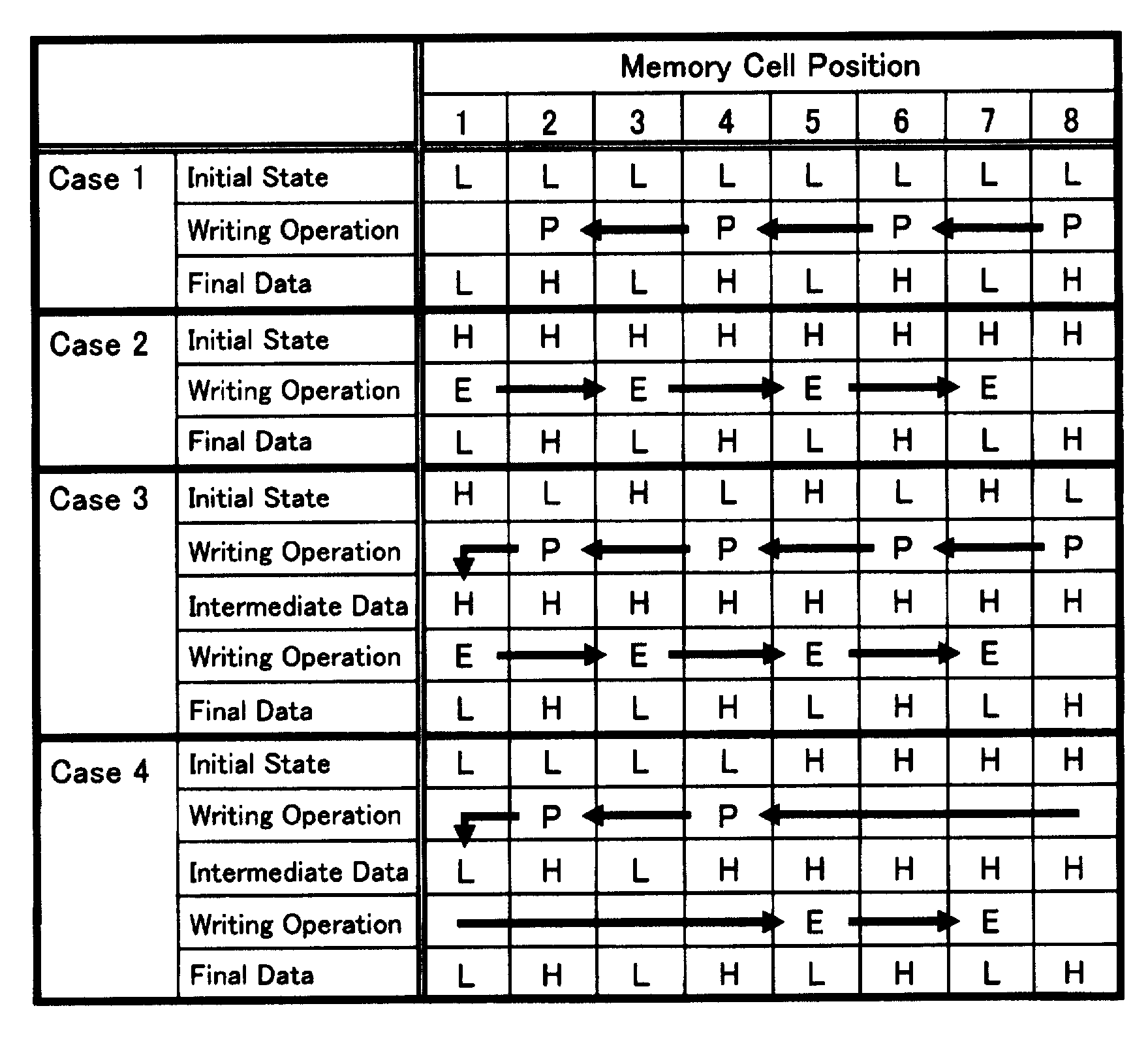

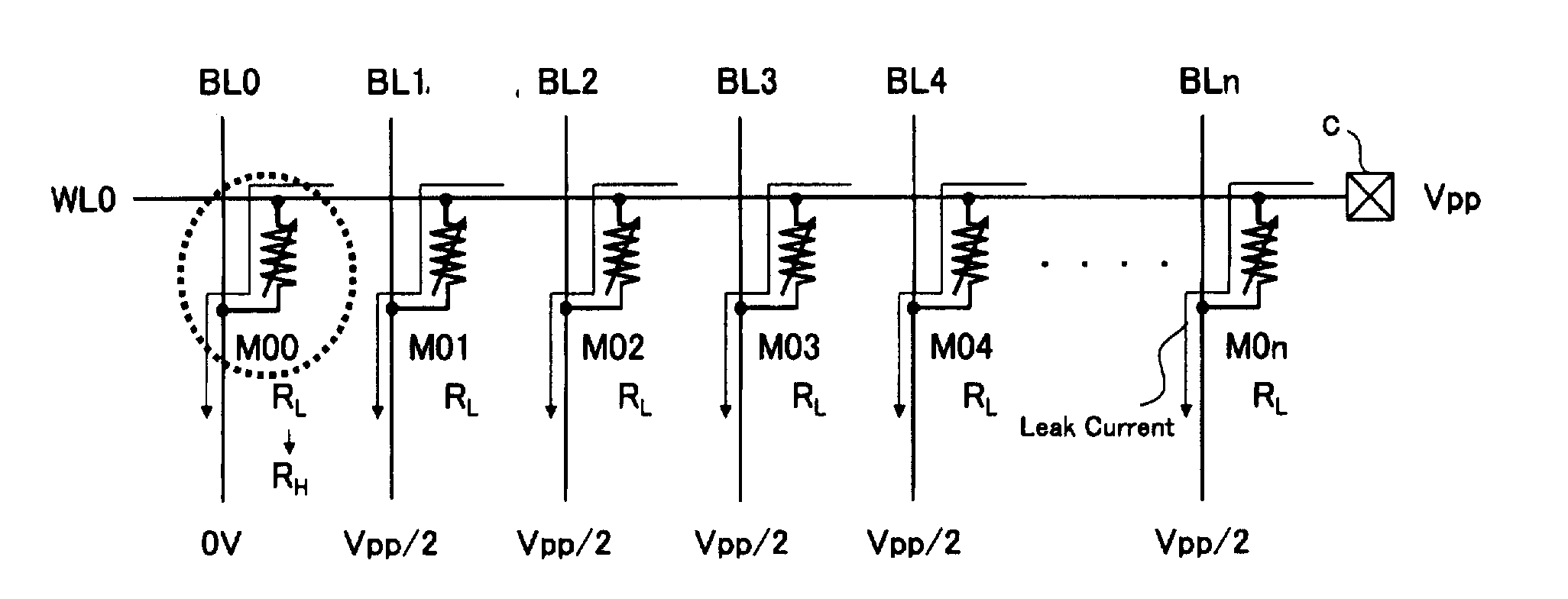

Nonvolatile semiconductor memory device and data writing method

InactiveUS7508695B2Drop in speedEasy to operateElectric analogue storesRead-only memoriesElectricityBit line

A data writing method for writing data sequentially in a cross-point memory cell array having a variable resistive element whose electric resistance is changed by application of an electric stress is provided. When data is sequentially written in memory cells in the same row or column, the writing order of the memory cells to be written is determined according to the length from an electric connection point to a selected memory cell to be written and the increase / decrease direction of the electric resistance of each selected memory cell changed by data writing, the electric connection point being between a write voltage applying circuit, which applies a data writing voltage to a same wiring of the selected word line or bit line connected to the selected memory cell, and the same wiring, and the data writing is executed based on the determined writing order.

Owner:XENOGENIC DEV LLC

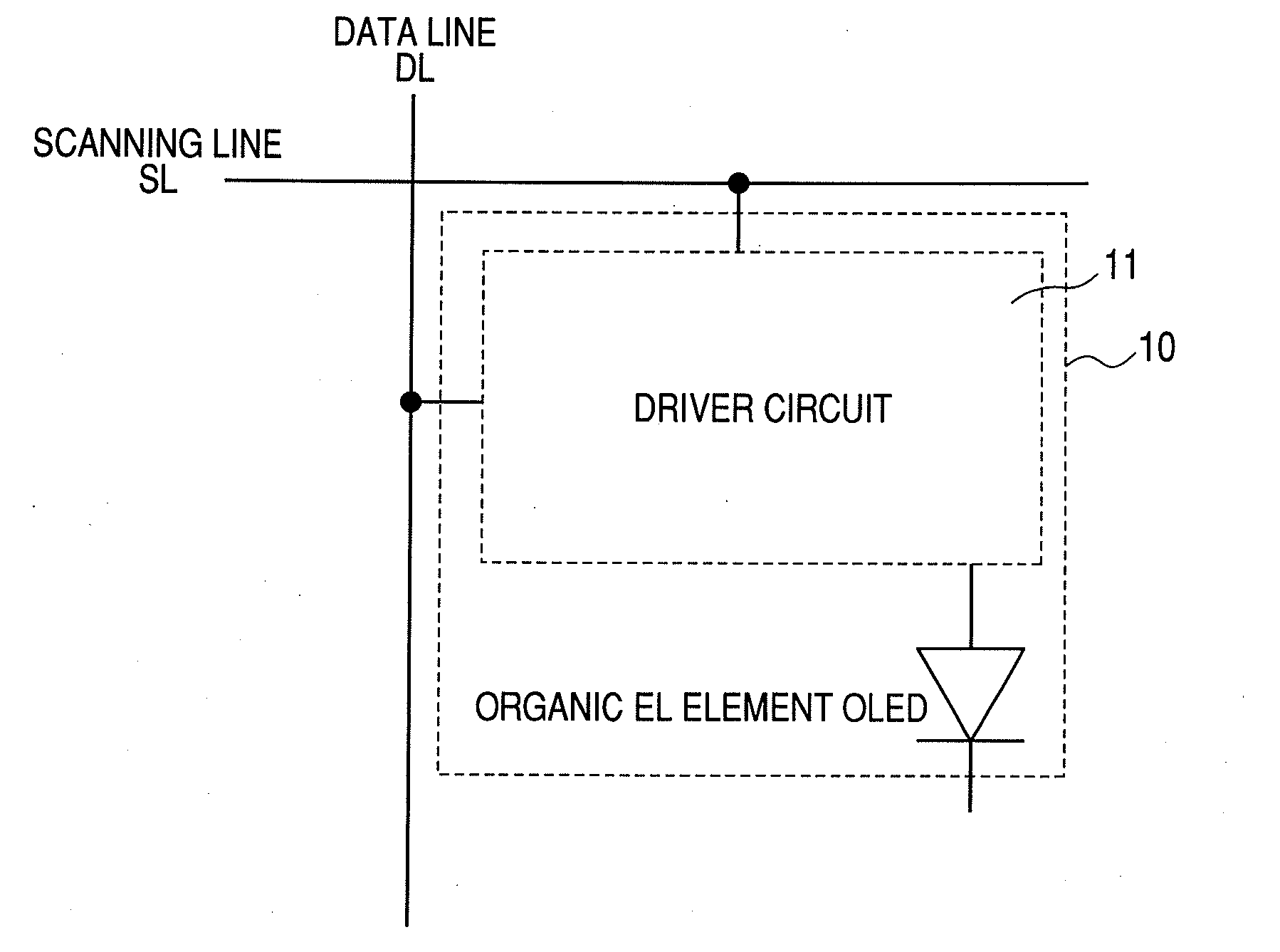

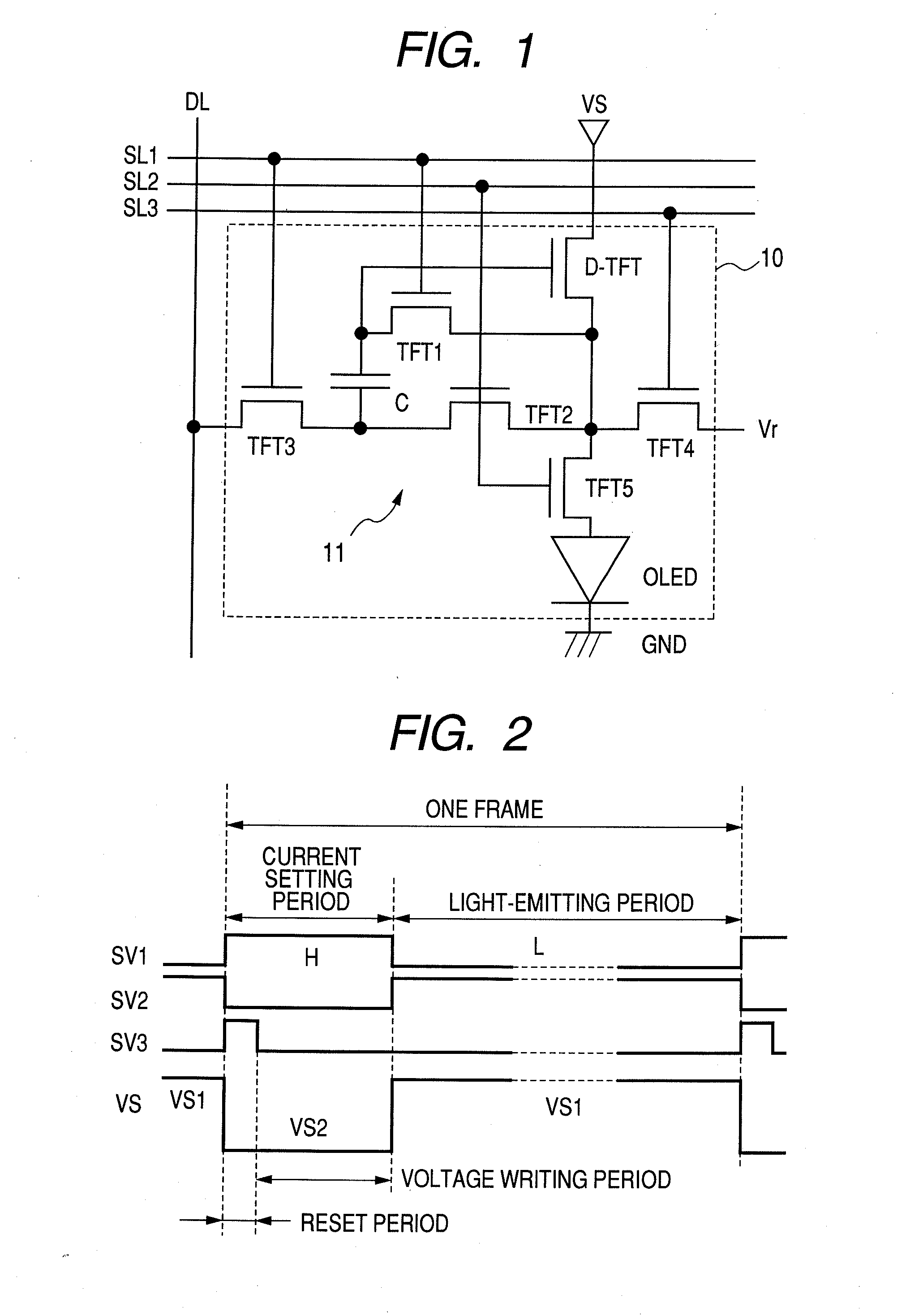

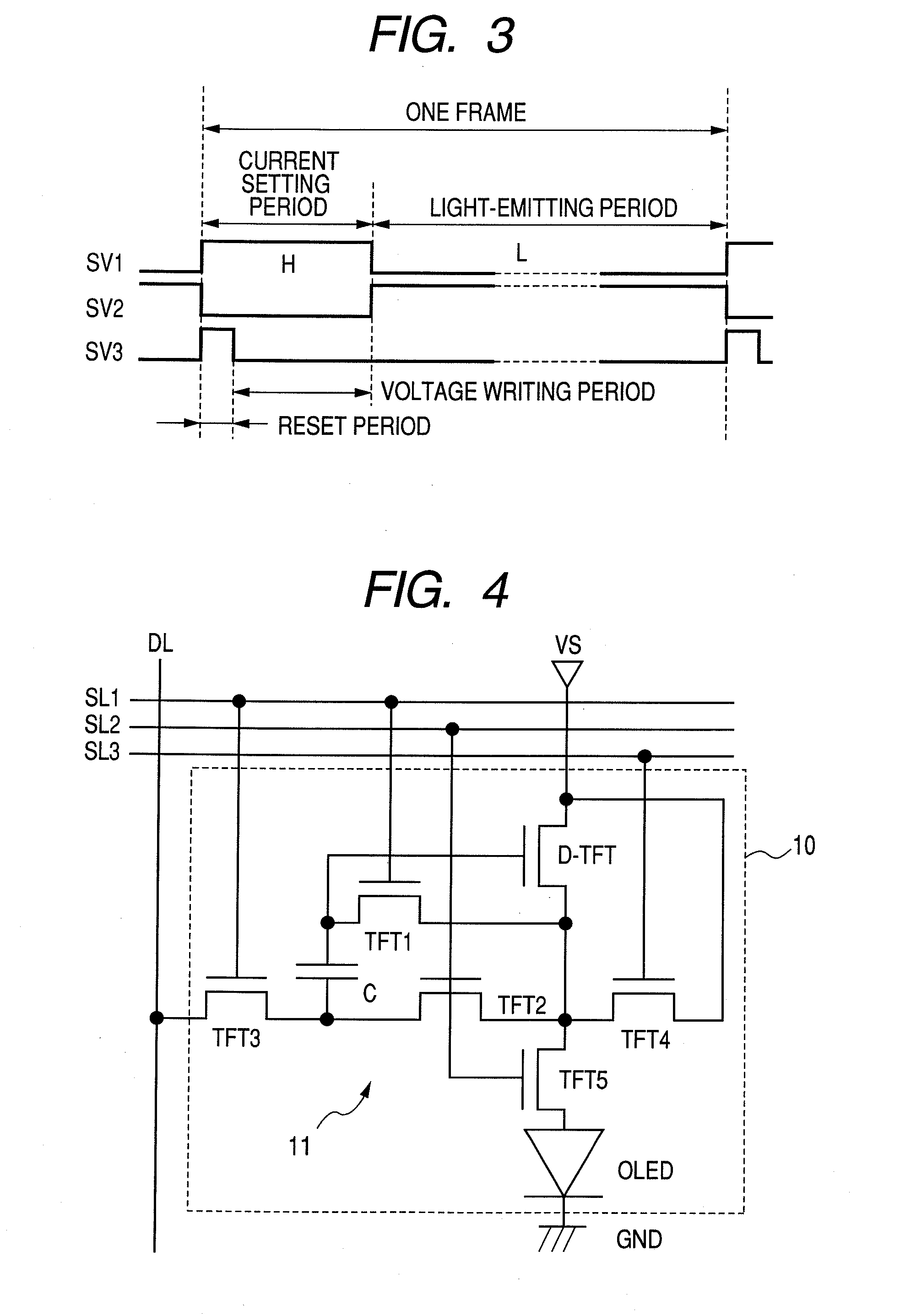

Light-emitting display device

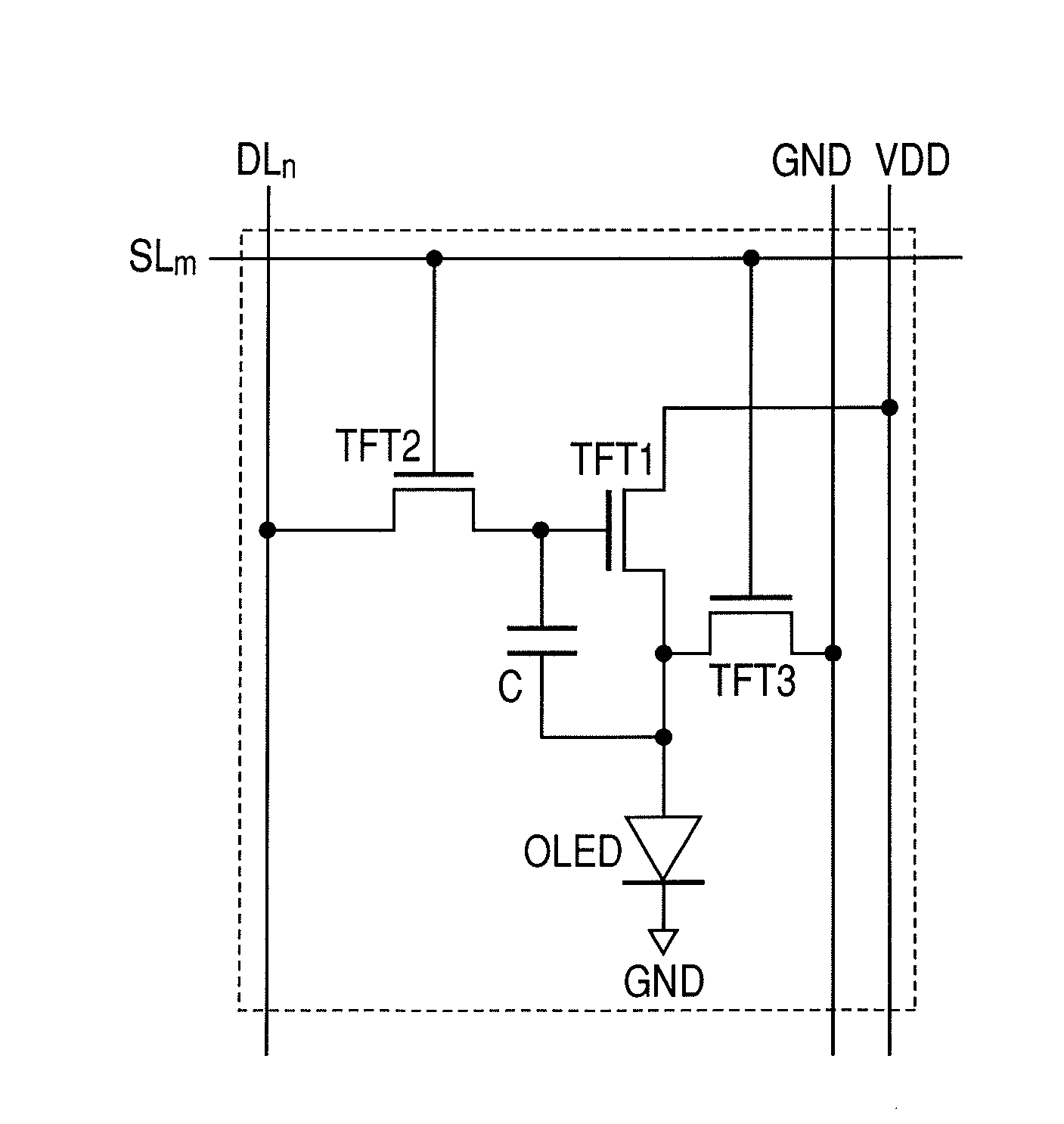

ActiveUS20100001983A1Reduce power consumptionImprove mobilityCathode-ray tube indicatorsInput/output processes for data processingHemt circuitsDisplay device

A light-emitting display device which suppresses influence of characteristic variations of a driving transistor and characteristic shift caused by electrical stress. The device includes multiple pixels including an organic EL element (OLED) which emits light at a luminance determined based on supplied current and a drive circuit for supplying current to OLED based on a control voltage from a data line. The drive circuit includes a driving transistor (D-TFT) for OLED, a capacitor element, and multiple switch elements. D-TFT has a source terminal connected with an anode terminal of OLED. The capacitor and switch elements operate so that, when current is supplied from the drive circuit to OLED, a voltage difference between gate and source terminals of D-TFT is a sum of threshold voltage of the driving transistor and voltage determined from voltage of a drain terminal of the driving transistor and the control voltage during current setting period.

Owner:CANON KK

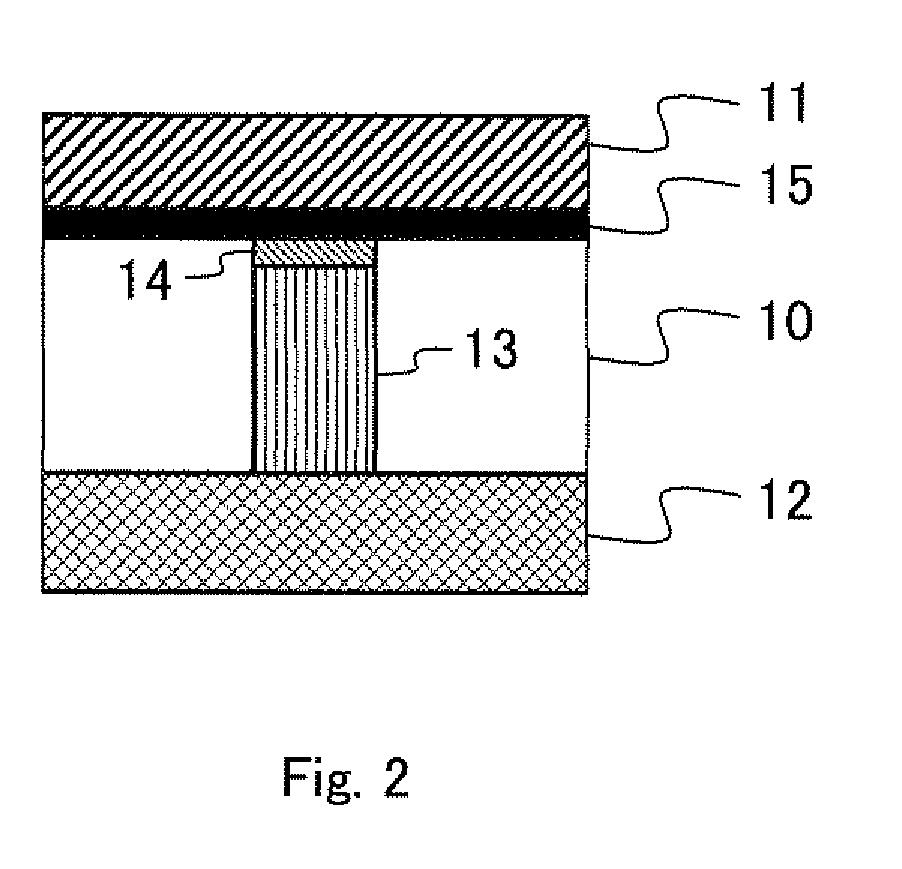

Variable resistive element, manufacturing method for same, and non-volatile semiconductor memory device

ActiveUS20100172170A1Reduce power consumptionInconsistency in resistanceSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceInterfacial oxide

Provided is a variable resistive element which performs high speed and low power consumption operation. The variable resistive element comprises a metal oxide layer between first and second electrodes wherein electrical resistance between the first and second electrodes reversibly changes in accordance with application of electrical stress across the first and second electrodes. The metal oxide layer has a filament, which is a current path where the density of a current flowing between the first and second electrodes locally increases. A portion including at least the vicinity of an interface between the certain electrode, which is one or both of the first and second electrodes, and the filament, on an interface between the certain electrode and the metal oxide layer is provided with an interface oxide which is an oxide of at least one element included in the certain electrode and different from the oxide of the metal oxide layer.

Owner:SHARP KK +1

Nonvolatile semiconductor memory device and data writing method

InactiveUS20070195590A1Provide effectDeterioration in programmingElectric analogue storesRead-only memoriesBit lineElectricity

The invention provides a data writing method for writing data sequentially in a cross-point memory cell array having a variable resistive element whose electric resistance is changed by application of an electric stress. When data is sequentially written in memory cells in the same row or column, the writing order of the memory cells to be written is determined according to the length from an electric connection point to a selected memory cell to be written and the increase / decrease direction of the electric resistance of each selected memory cell changed by data writing, the electric connection point being between a write voltage applying circuit, which applies a data writing voltage to a same wiring of the selected word line or bit line connected to the selected memory cell, and the same wiring, and the data writing is executed based on the determined writing order.

Owner:XENOGENIC DEV LLC

Thin film transistor circuit, light emitting display apparatus, and driving method thereof

InactiveUS8654114B2Suppresses degradation of display qualityInhibition effectCathode-ray tube indicatorsElectric pulse generatorHemt circuitsElectric stress

In order to suppress an influence of an electrical stress on a TFT characteristic in use of a TFT, a light emitting display apparatus according to the present invention comprises organic EL devices and driving circuits for driving the organic EL devices. The driving circuit includes plural pixels each having a thin film transistor of which a threshold voltage reversibly changes due to the electrical stress applied between a gate terminal and a source terminal, and a voltage applying unit which sets gate potential of the thin film transistor higher than source potential. The voltage applying unit applies the electrical stress between the gate terminal and the source terminal at a time when the thin film transistor is not driven, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress.

Owner:CANON KK

Nonvolatile semiconductor memory device and control method thereof

A nonvolatile semiconductor memory device includes a memory array (101) in which a plurality of memory cells are arranged in a row direction and a column direction, each of the memory cells being formed by connecting one end of a variable resistive element for storing information according to a change in electric resistance caused by an electric stress and a drain of a selection transistor to each other on a semiconductor substrate, a voltage switch circuit (110) for switching among a program voltage, an erase voltage and a read voltage to be applied to the source line and the bit line connected to the memory cell, and a pulse voltage applying circuit (108). In the state where the program voltage or erase voltage corresponding to the bit line and the source line is applied to the bit line and the source line connected to a memory cell to be programmed or erased in the memory array via the voltage switch circuit (110), the pulse voltage applying circuit (108) applies a voltage pulse for programming or erasing to the word line connected to the gate electrode of the selection.

Owner:SAMSUNG ELECTRONICS CO LTD

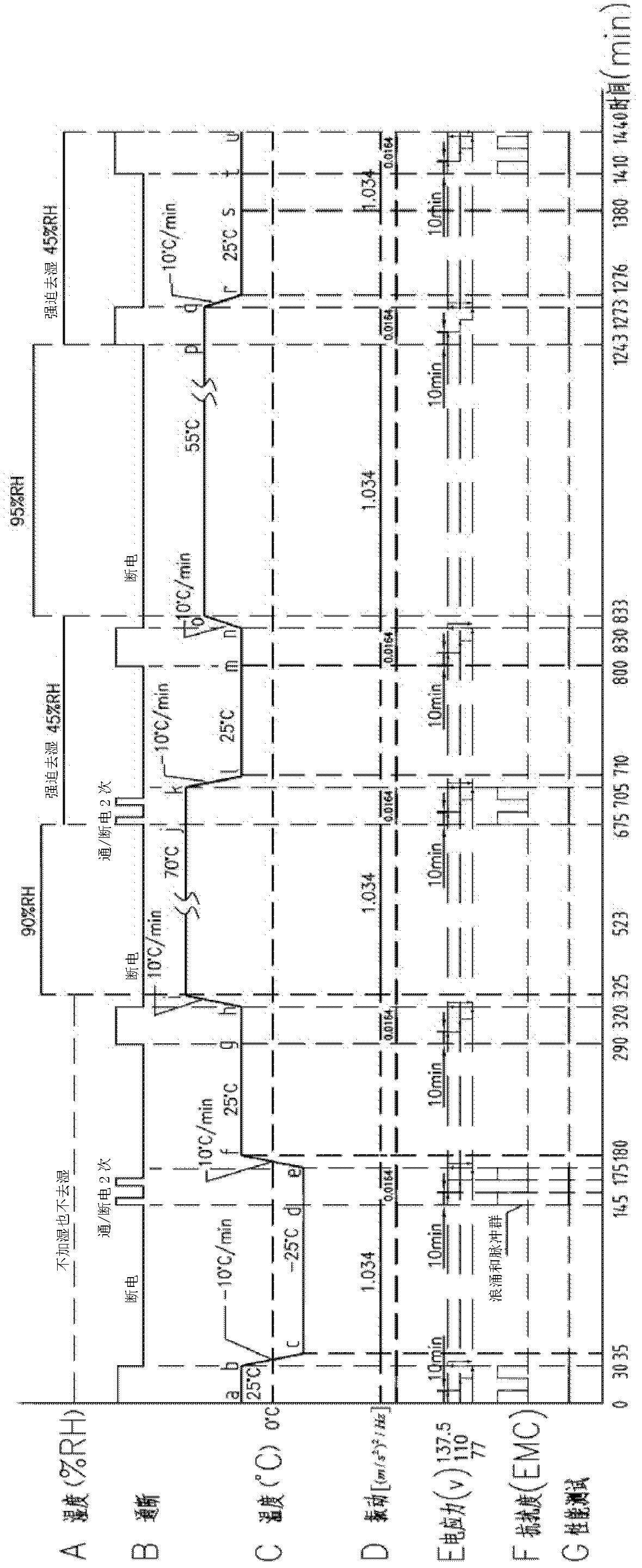

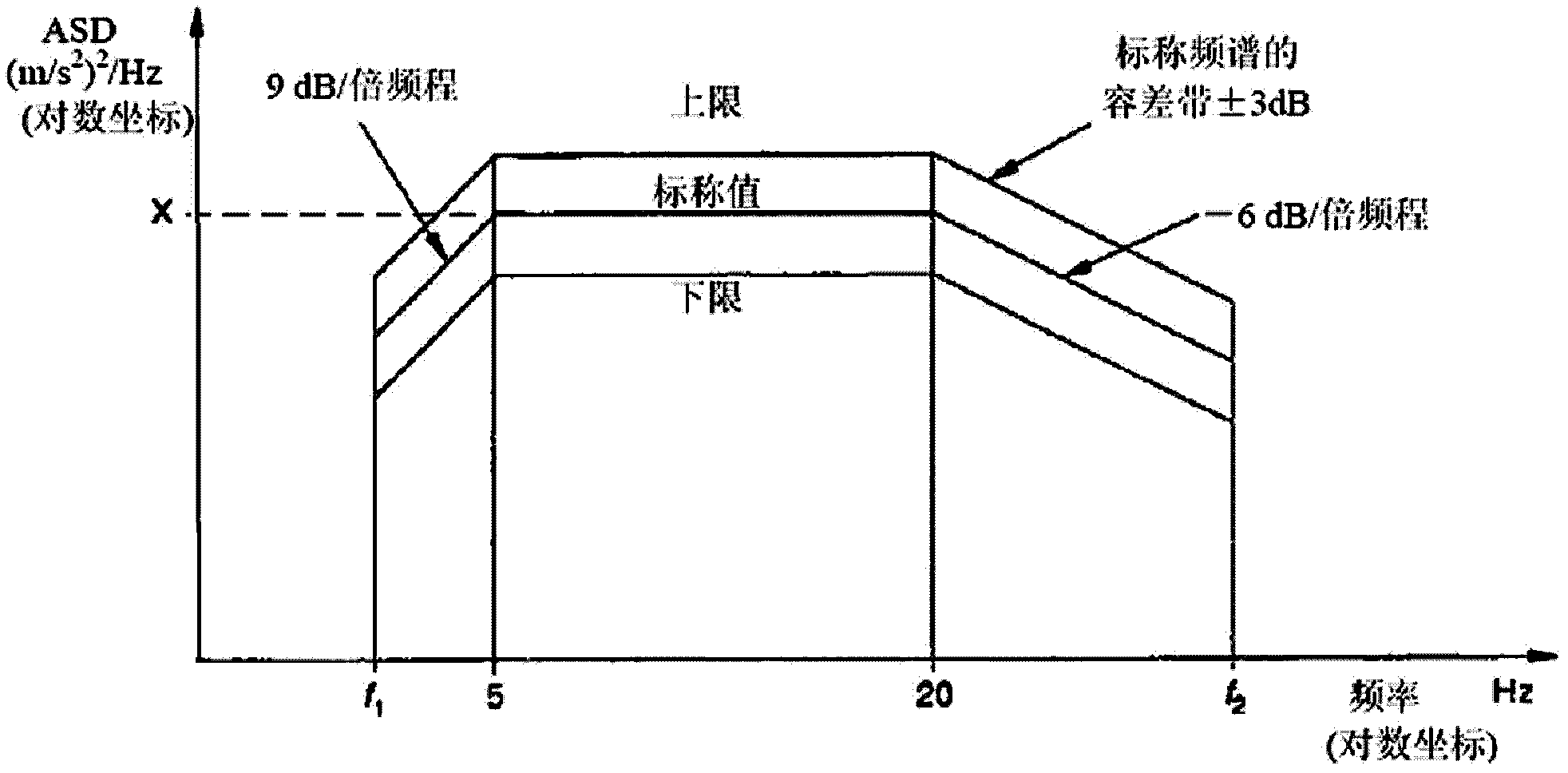

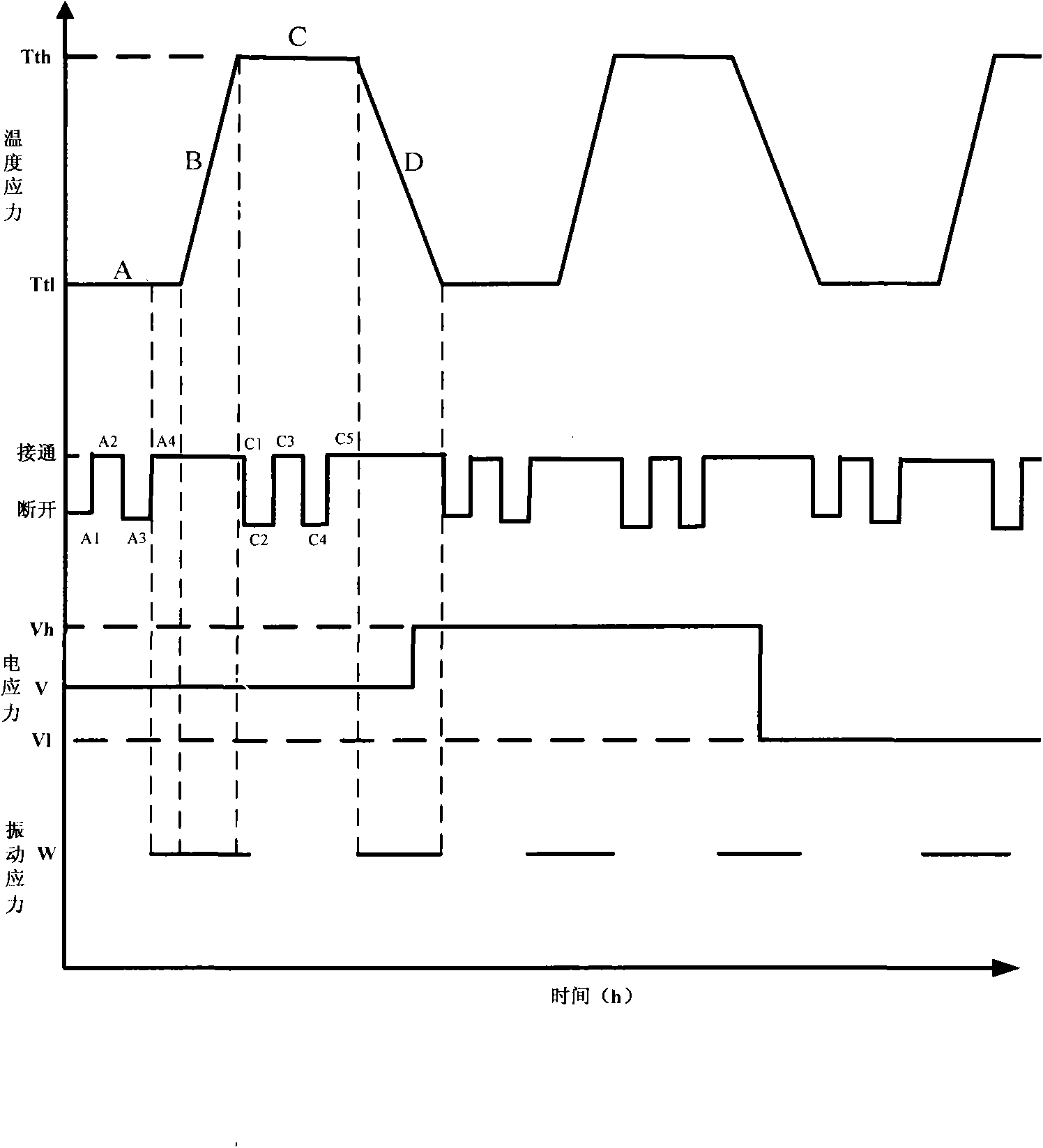

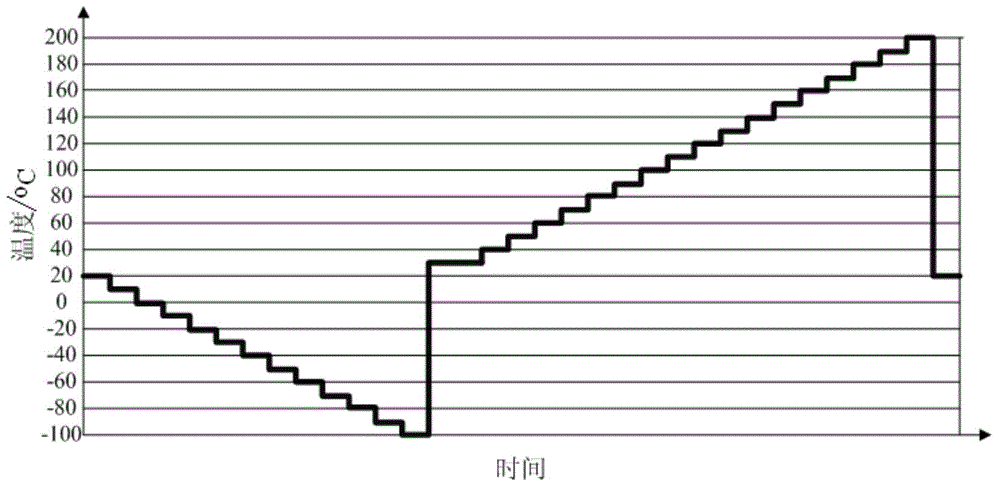

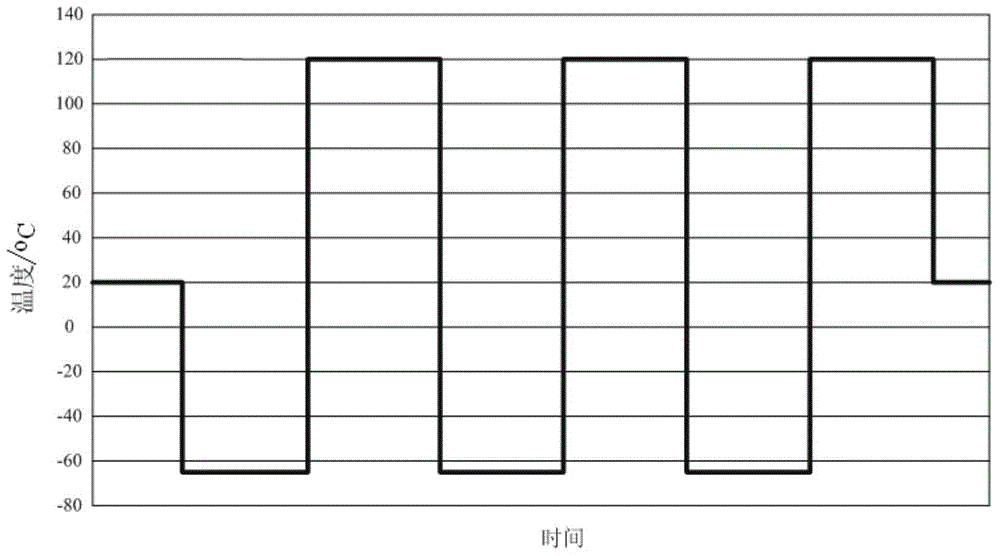

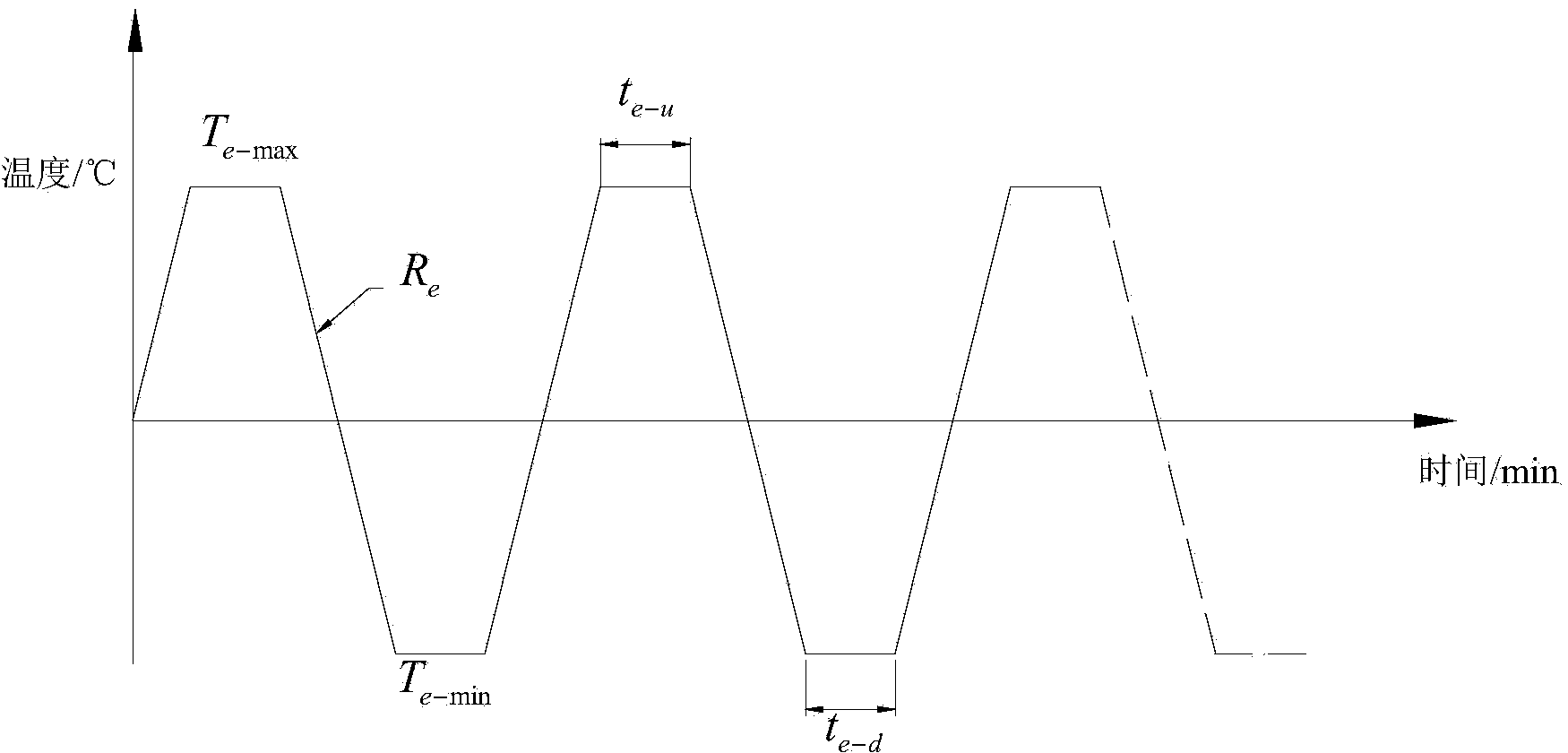

Rail transit electrical equipment reliability test method

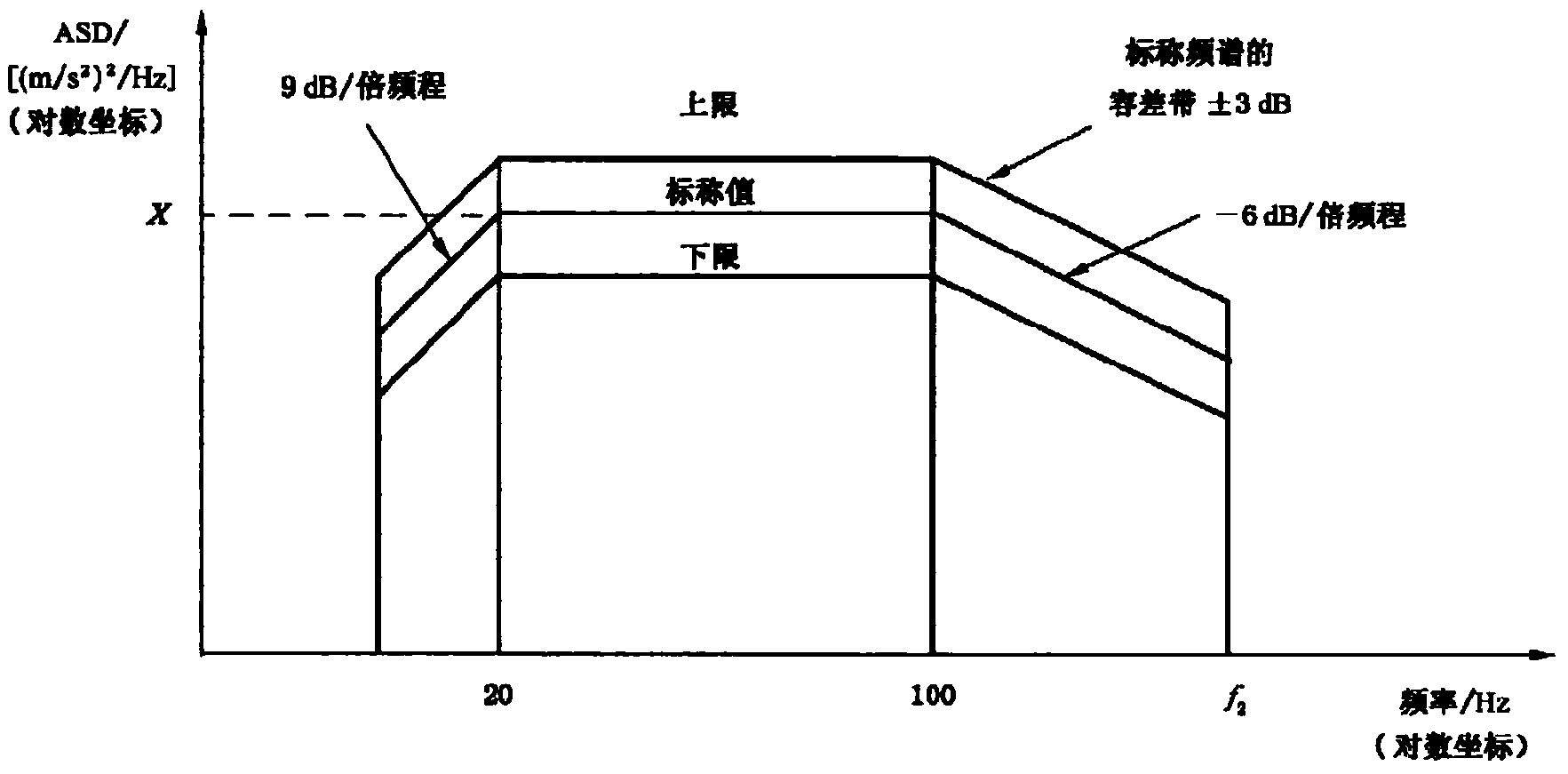

ActiveCN102628901AReduce maintenance costsImprove reliabilityElectrical testingVibration testingTemperature stressStress level

The invention discloses a rail transit electrical equipment reliability test method. The method comprises the test process with one or more test cycles and the test process of adding one or more on / off test process, performance test process and noise immunity test process in the specific period of one test cycle, wherein the test process with one or more test cycles comprises combination of any stress level and time sequence of one or more of humidity stress test process, temperature stress test process, vibration stress test process and electric stress test process. According to the method, the potential defects of the tested rail transit electrical equipment are completely exposed at the early development stage, the reliability of the rail transit electrical equipment is improved, and the maintenance cost of the rail transit electrical equipment in the full-life period is effectively reduced; the change rule of the tested equipment along with the using time of users can be reflected and basis is provided for quality guarantee; and the reliability index of the equipment can be distributed to the related devices, and the reliability of the rail transit electrical equipment is improved by improving the reliability of the devices.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

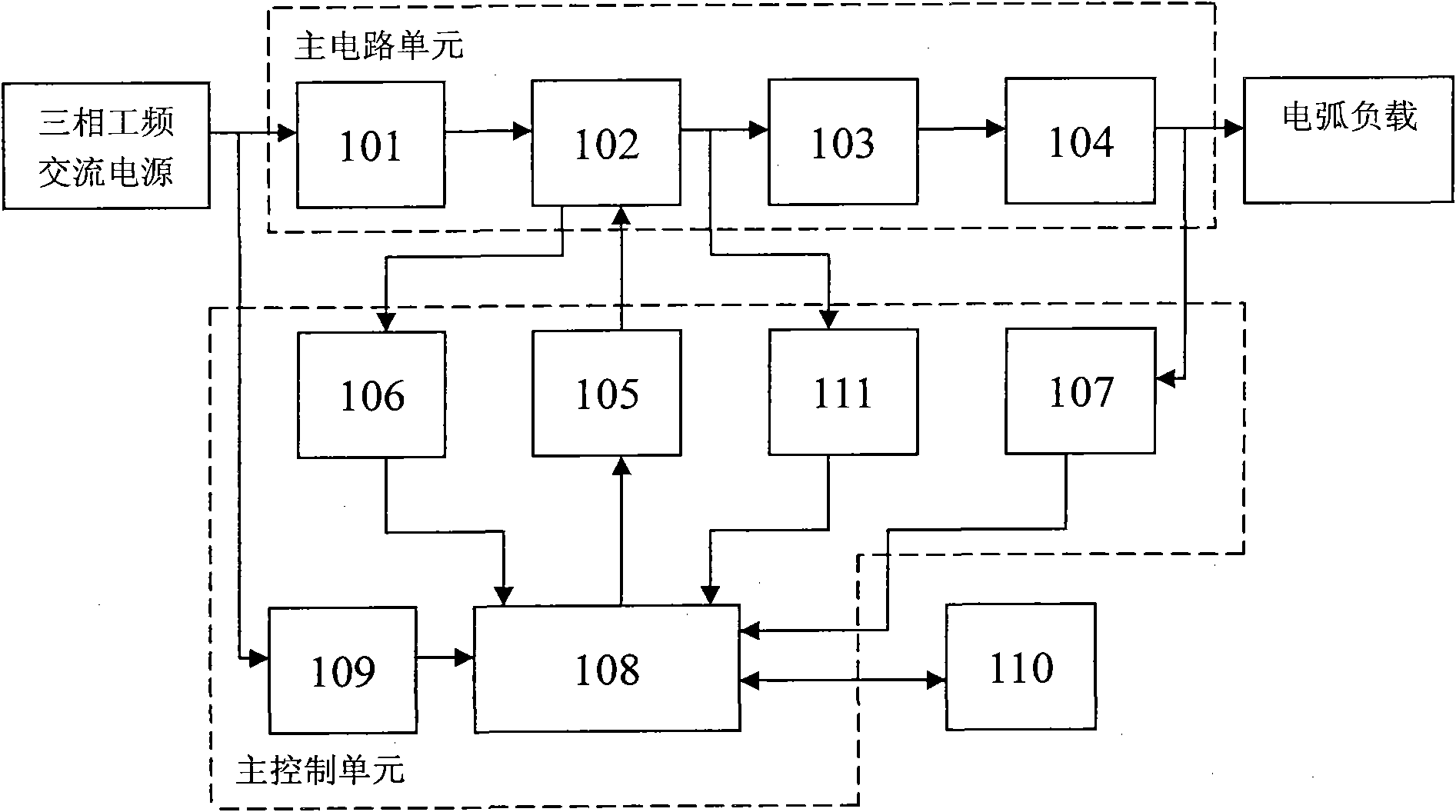

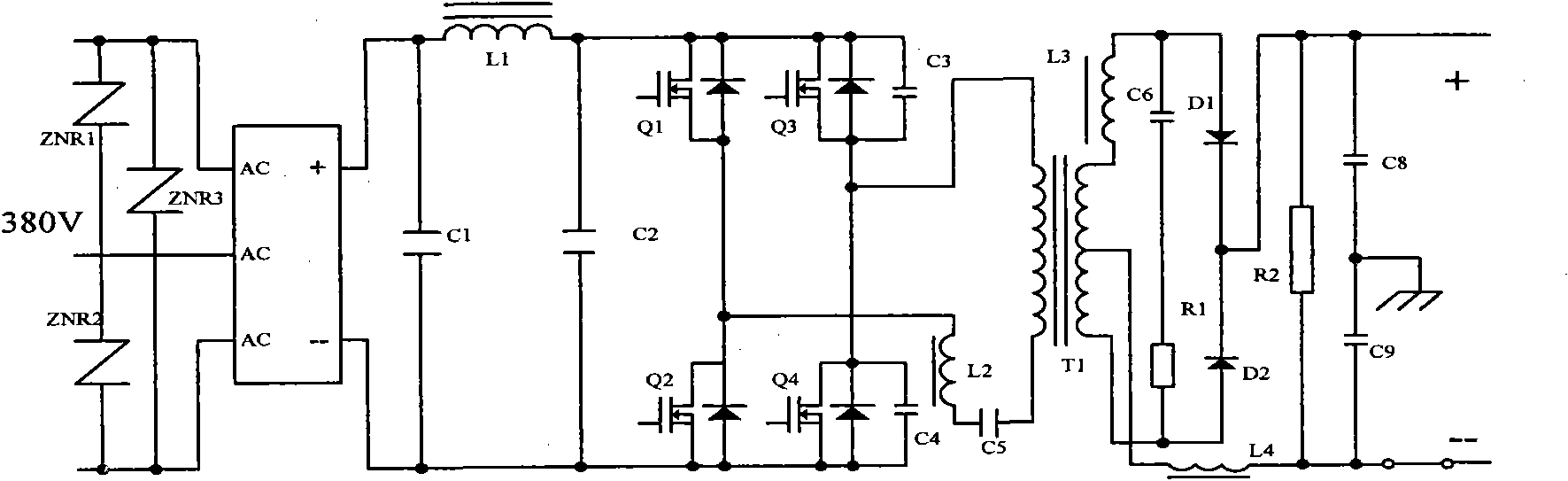

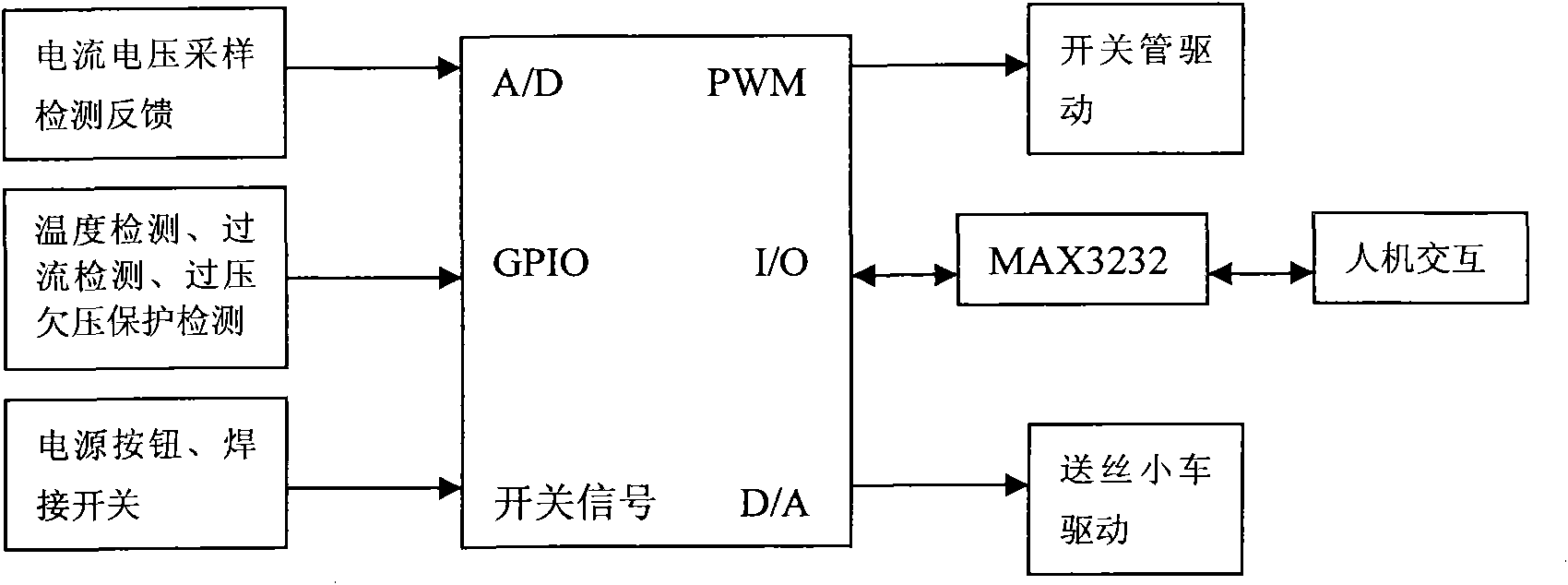

Gas-protective submerged-arc welding digitalized power supply system for dual ARM (Automated Route Management) control and control method thereof

InactiveCN101862881AAdvanced technologyImprove welding stabilityEfficient power electronics conversionArc welding apparatusLow voltageFull bridge

The invention discloses a gas-protective submerged-arc welding digitalized power supply system for dual ARM (Automated Route Management) control and a control method thereof. The system comprises a case and a built-in circuit, wherein the built-in circuit comprises a main circuit unit and a main control unit; the main circuit unit is a full-bridge inverting main circuit of a limited bipolar soft switch; and an ARM9S3C2440 controller is used in the main control unit. In the control method, a corresponding welding mode is selected through the controller, the welding process is monitored by the main control unit and three-phase power frequency alternating current is converted by the main circuit unit to obtain the required smooth direct current with heavy flow and low voltage. The invention can provide two different welding processes of submerged-arc welding and gas-protective welding for one welding machine, realize the soft switch in all range, greatly reduce the switch loss and the electric stress, effectively reduce the electromagnetic interference of an inverting welding machine while improving the efficiency and saving energy and improve the electromagnetic compatibility and the reliability of the inverting welding machine.

Owner:GUANGDONG POWER ENG +1

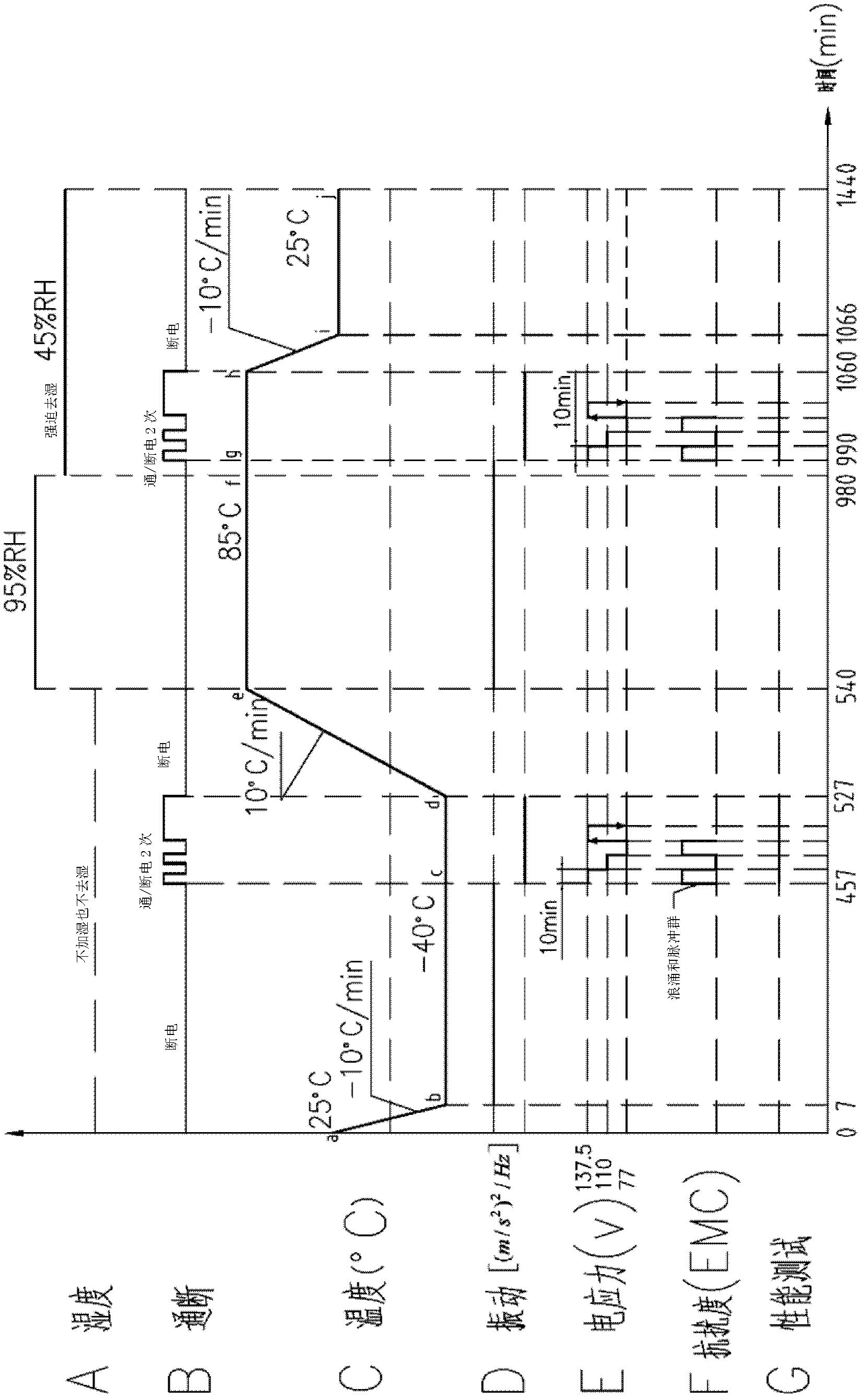

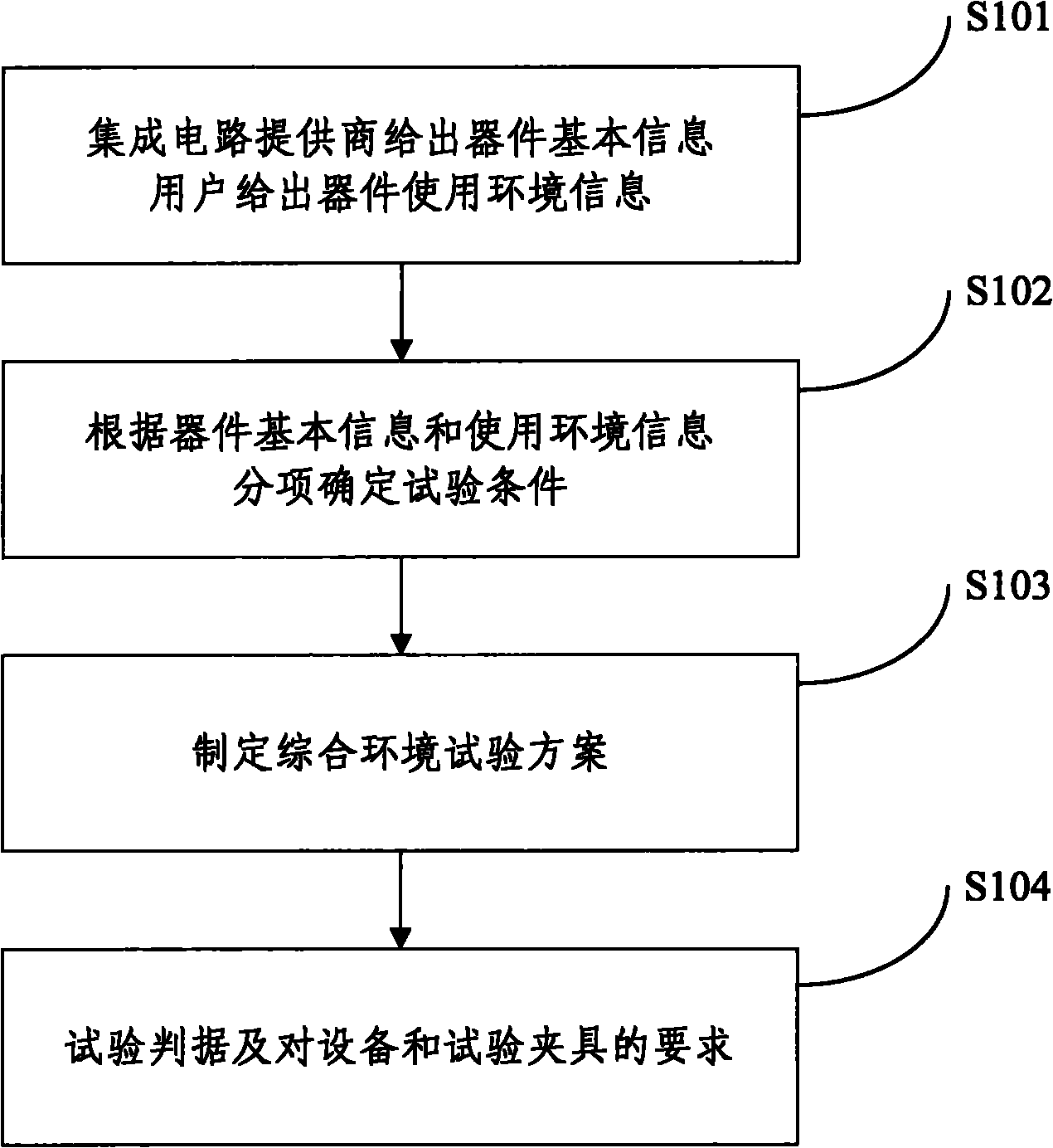

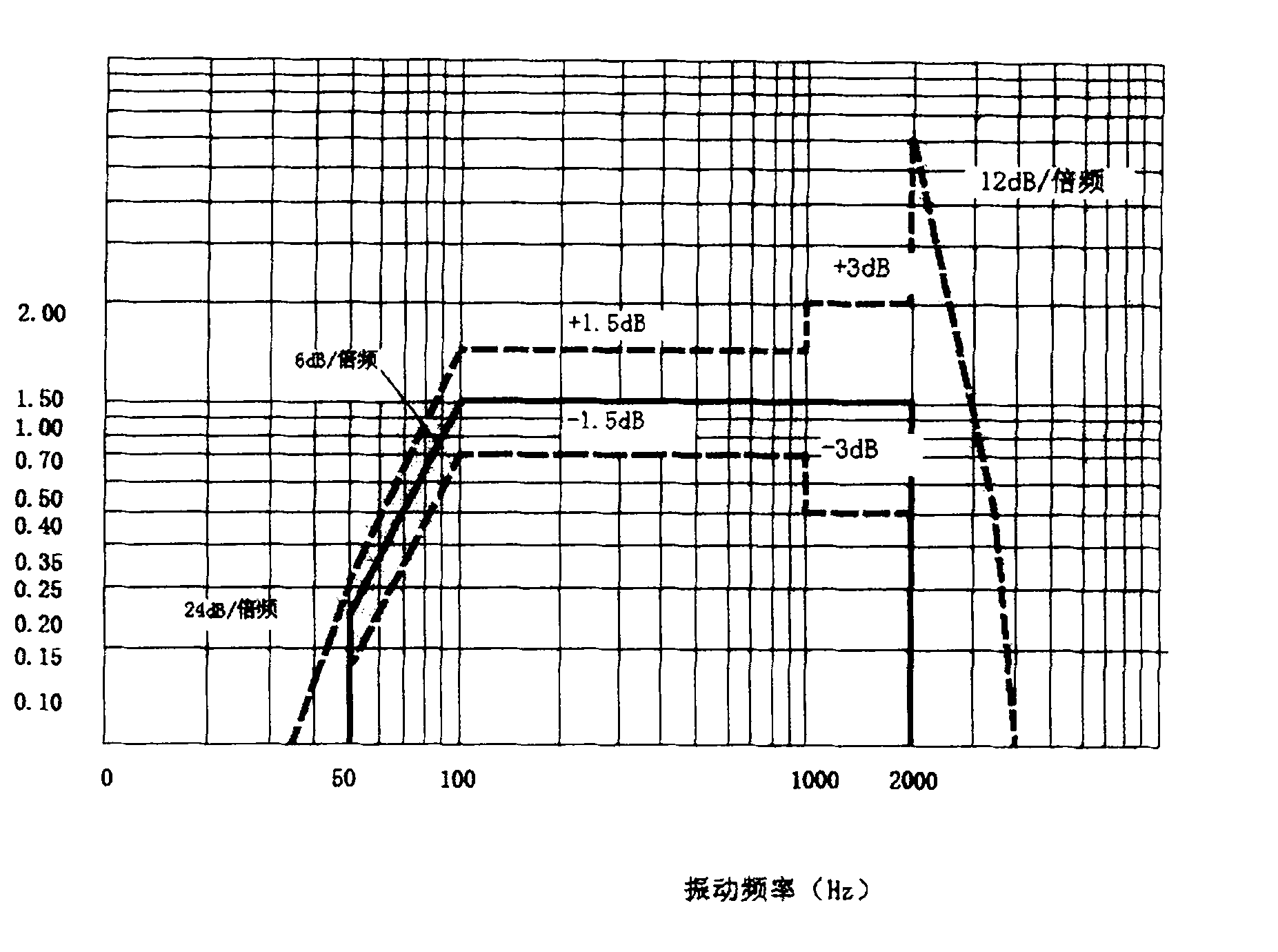

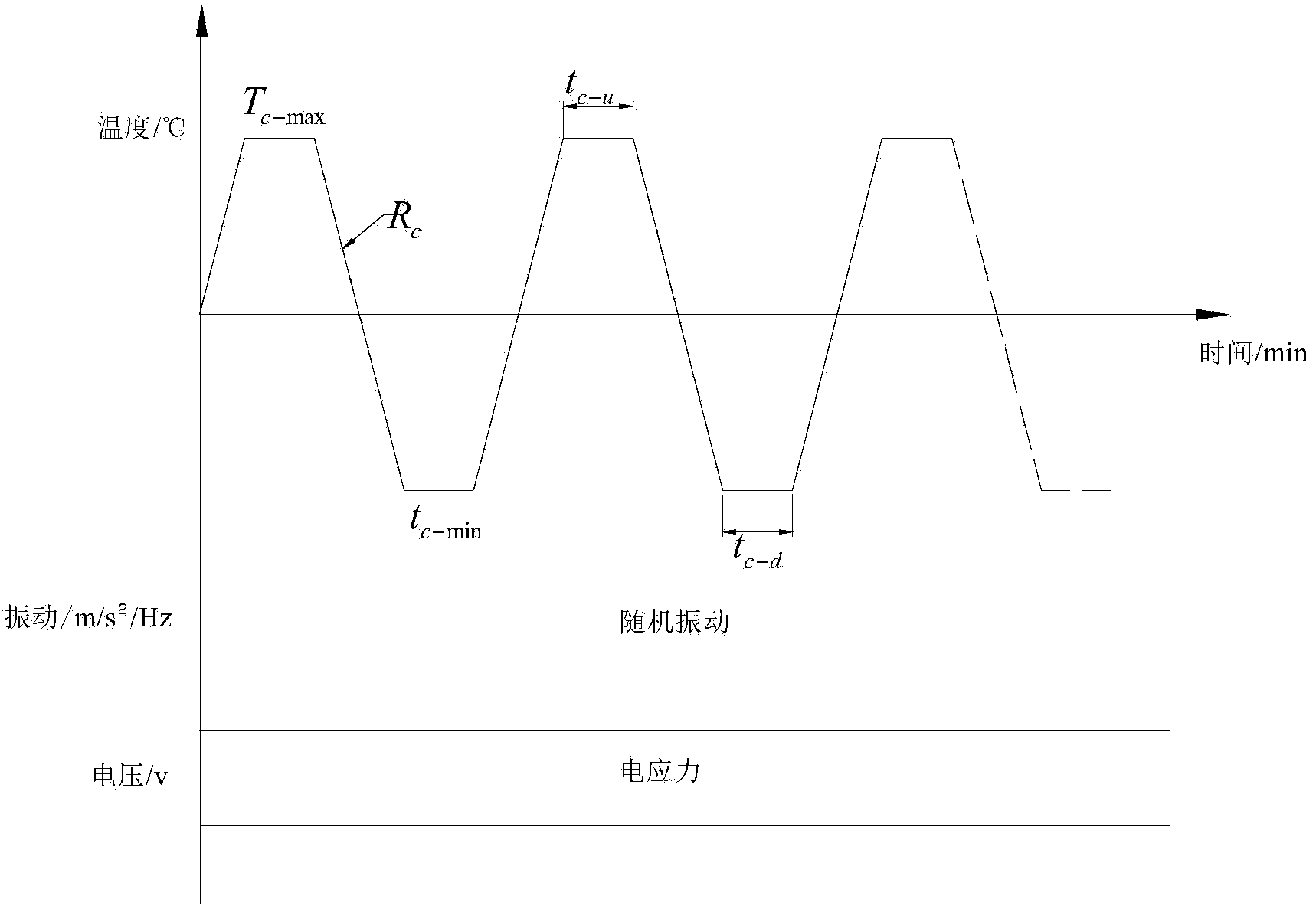

Combined environment test method for integrated circuit

InactiveCN101957426AAccurately evaluate qualityAccurately evaluate reliabilityElectronic circuit testingTest powerFunctional testing

The invention discloses a combined environment test method for an integrated circuit, which comprises the following steps of: S1) acquiring the highest test temperature, the lowest test temperature, the highest test temperature change rate delta TE, a test power density spectrum, a test humidity and a test electric stress according to the basic product information of the integrated circuit and the used environment information, S2) according to the test data, performing a temperature cycling test, a random vibration test and a humid test while respectively exerting a rated operational voltage, the maximum operating voltage and the minimum operating voltage on the integrated circuit, and S3) after finishing the tests, performing a functional test on the integrated circuit, confirming the integrated circuit invalid if the integrated circuit loses the function or any property parameter value exceeds a designed scope, otherwise, confirming the integrated circuit being in good condition. The invention can really simulate the actual using environment of the integrated circuit, quickly and completely arouse the faults of the products and provide a reference to improve the design and the manufacturing shortcomings of the integrated circuit.

Owner:BEIJING SHENGTAOPING TEST ENG TECH RES INST

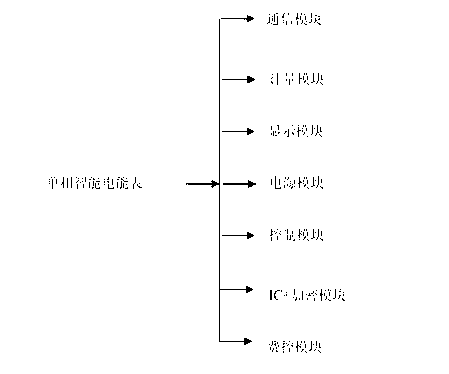

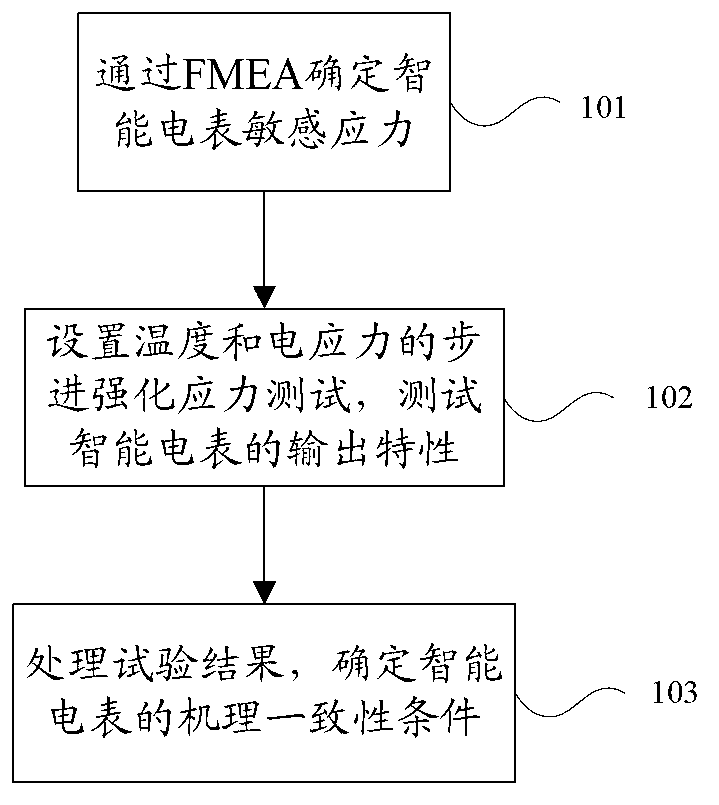

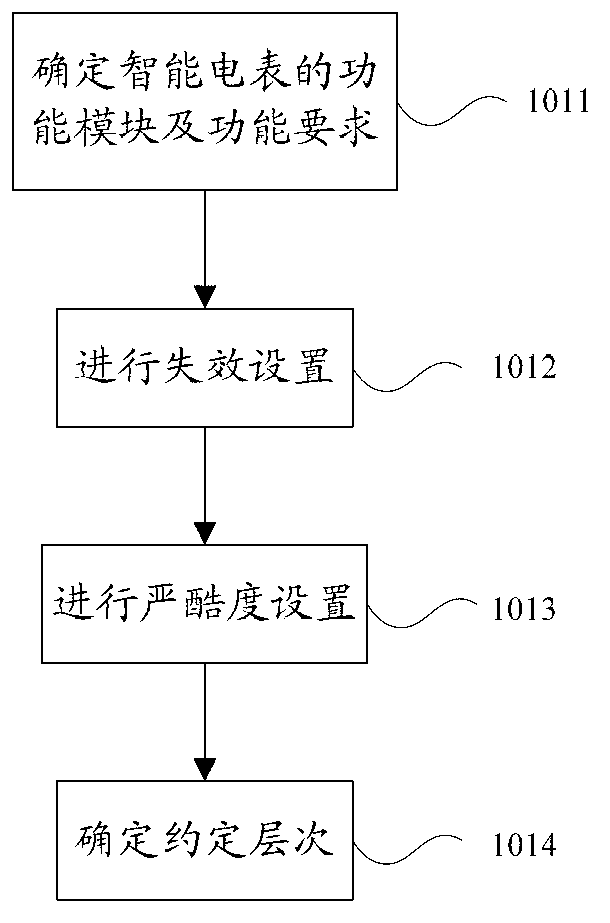

Multi-stress limit determination method for intelligent ammeter

ActiveCN102707257AHardened test data is scarceMake up for the flaws in processing intensive test dataElectrical measurementsSmall sampleElectric stress

The invention discloses a multi-stress limit determination method for an intelligent ammeter. The method comprises the following steps: determining the sensitive stress of the intelligent ammeter through FMEA (Failure Mode and Effects Analysis); respectively setting the stepping reinforcement stress tests of both temperature and electric stress; testing the output characteristics of the intelligent ammeter; processing the test result; and determining the mechanism consistency condition. The method provided by the invention is specially for determining the mechanism consistency of the intelligent ammeter and makes up the blank that a matched method specially researched and developed for the intelligent ammeter is unavailable in the present market. The conventional reinforcement test data of the intelligent ammeter is less, and can not be analyzed more accurately by adopting a traditional data processing method. The grey theory method provided by the invention can be used under the small-sample poor-information condition, thereby compensating defects when the reinforcement testing data is processed by the traditional method.

Owner:JIBEI ELECTRIC POWER COMPANY LIMITED CENT OF METROLOGY

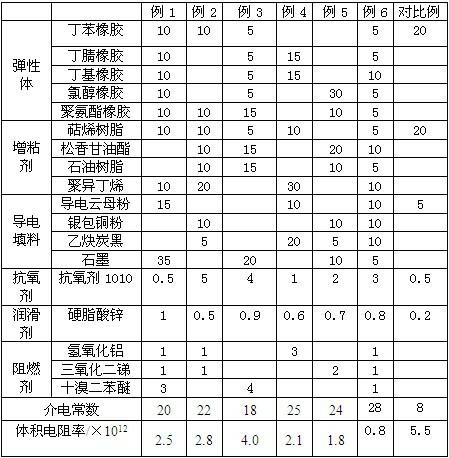

Electric stress relief adhesive for connecting thermal shrinkage cable accessory

ActiveCN102399517AHigh tensile strengthProper dielectric constantMineral oil hydrocarbon copolymer adhesivesPolyureas/polyurethane adhesivesElastomerAdhesive

The invention discloses an electric stress relief adhesive for connecting thermal shrinkage cable accessories. The electric stress relief adhesive comprises ingredients of, by weight, 20-50 parts of elastomer, 20-50 parts of adhesion agent, 15-50 parts of conductive filling material, 0.5-5 parts of anti-oxidant, 2-5 parts of fire retardant and 0.5-1 part of lubricant. The electric stress relief adhesive for connecting thermal shrinkage cable accessories of the invention has good bonding intensity on aluminium, lead, copper and oil isolating pipe, has excellent bonding sealing, airtight, weatherability and aging resistance in an insulating cable joint, and has proper dielectric constant and volume resistivity, large tensile strength and good effect on mitigating and dispersing electric stress.

Owner:JIANGSU DASHENG HEAT SHRINKABLE MATERIALS

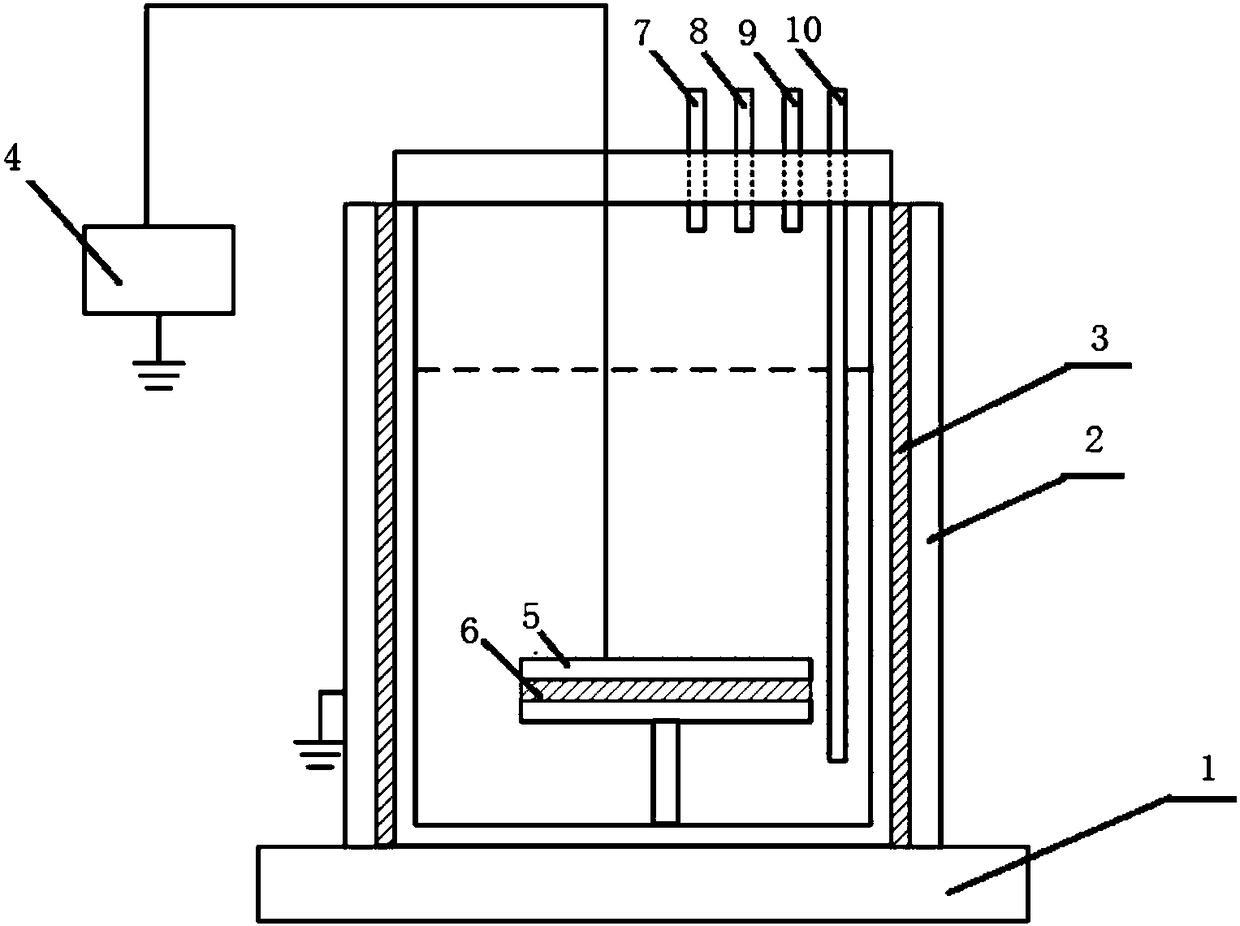

Thermal-electric-mechanical multi-stress ageing test platform of extra-high voltage converter transformer paper oil insulation materials and testing method thereof

InactiveCN108226726AAging effectFeatures miniaturizationTesting dielectric strengthTransformerTest chamber

The present invention discloses a thermal-electric-mechanical multi-stress ageing test platform of extra-high voltage converter transformer paper oil insulation materials and a testing method thereof.The test platform comprises three stress modules; a thermal stress module comprises a heating plate arranged at the outer wall of an ageing test chamber to allow paper oil insulation materials to reach an assigned temperature; an electric stress module is formed by a voltage source and an electrode and is configured to provide a direct current voltage, an alternating current voltage and an alternating current / direct current compound voltage for the paper oil insulation materials, wherein the direct current voltage and the alternating current voltage can reach an assigned voltage level; and amechanical stress module is formed by a vibration table, wherein the vibration table can provide mechanical vibration with assigned frequency and amplitude. When the thermal-electric-mechanical modules work at the same time, the thermal-electric-mechanical modules can provide various stress ageing conditions for the paper oil insulation materials to simulate the complex work conditions of the internal portion of a converter transformer and perform individual regulation of three stresses so as to facilitate analysis and obtain ageing effects of three different stresses for the paper oil insulation materials.

Owner:XI AN JIAOTONG UNIV

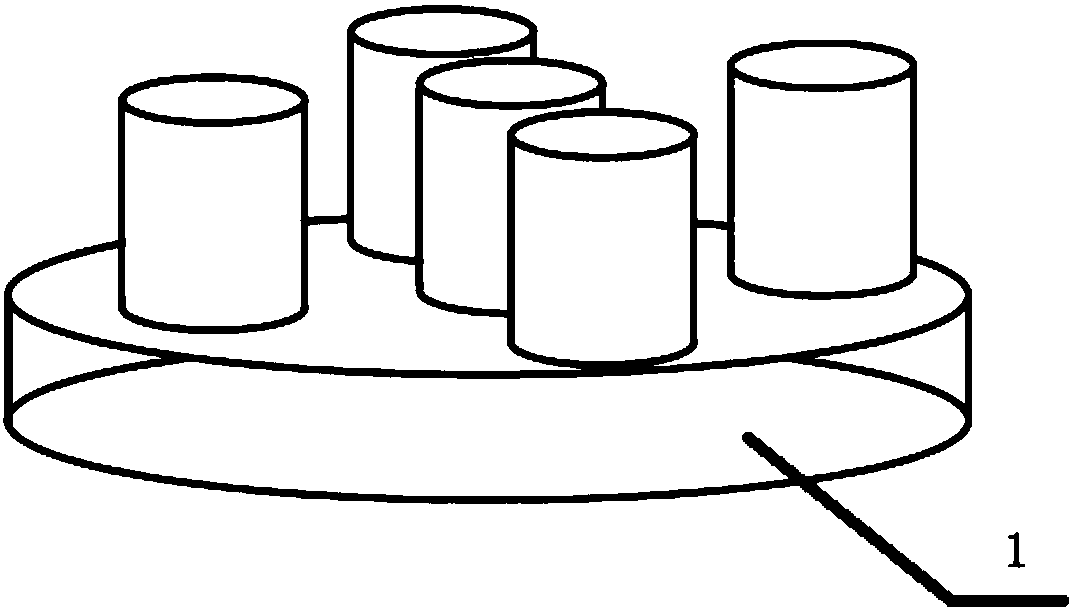

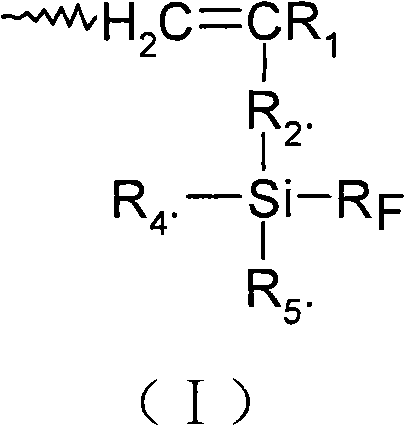

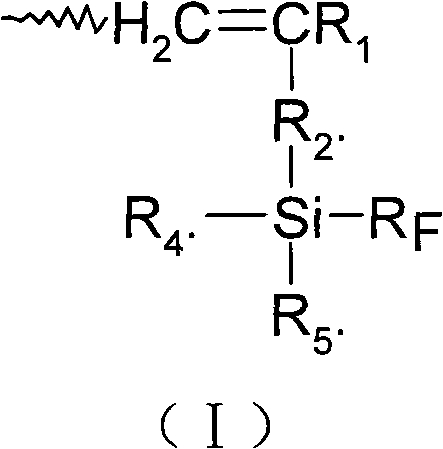

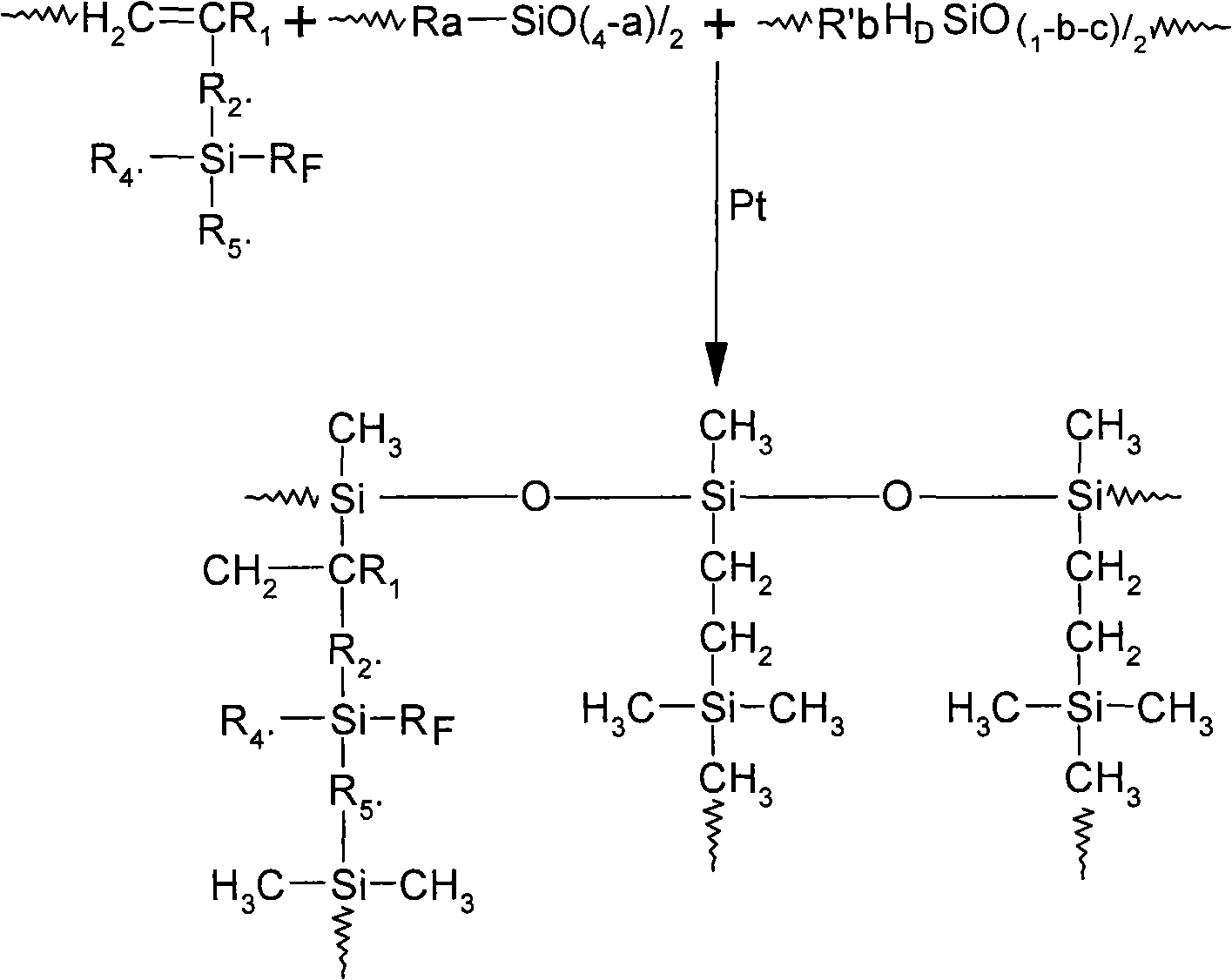

High dielectric constant silastic used for electric stress control and preparation method and application thereof

Owner:GUANGDONG BIOMAX SIANDF NEW MATERIAL CO LTD

One-time programable memory with additional programming time to ensure hard breakdown of the gate insulating film

A nonvolatile semiconductor memory device includes a storage element which is programmed with information by breaking an insulating film by application of electrical stress to the storage element, a control switch which controls the application of electrical stress to the storage element, and a control circuit which controls conduction / nonconduction of the control switch. The device further includes a power supply circuit including a voltage generation circuit which generates a first voltage to cause the electrical stress in program operation, a sensing circuit which senses that the insulating film is broken down, and a counter circuit which controls the control circuit to interrupt the application of electrical stress to the storage element when a given period of time elapses after the sensing circuit senses that the insulating film is broken down.

Owner:KK TOSHIBA

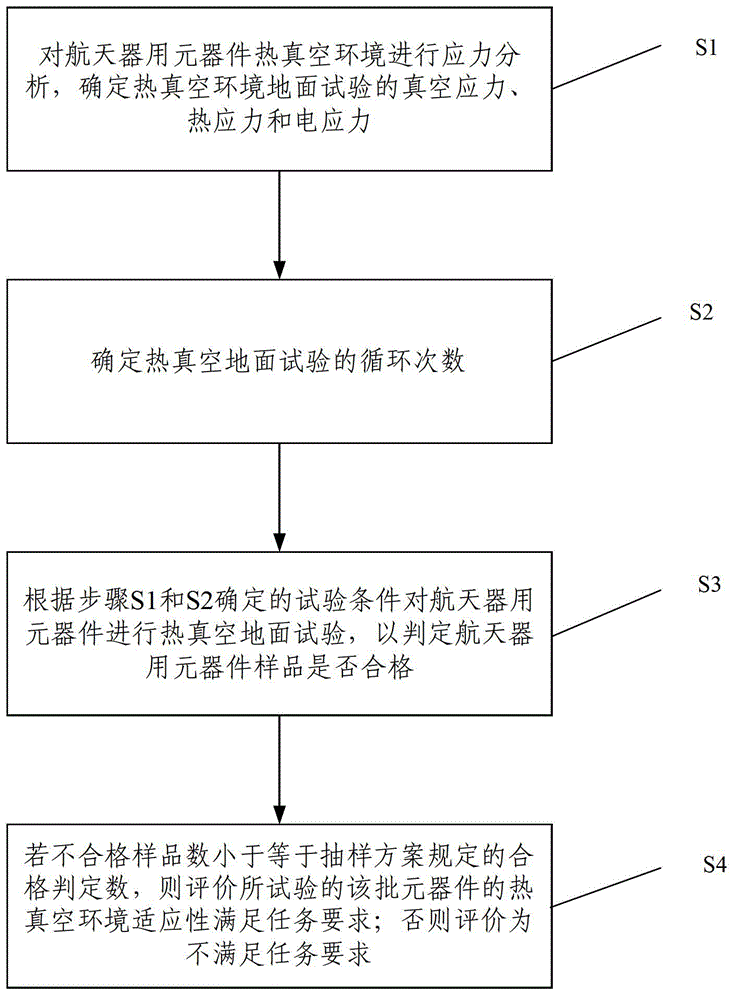

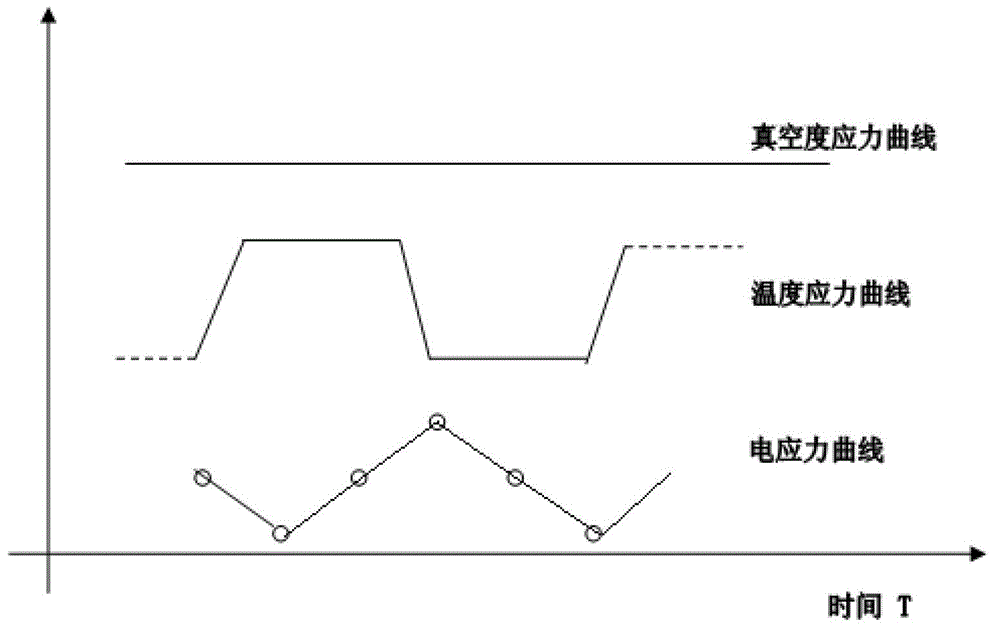

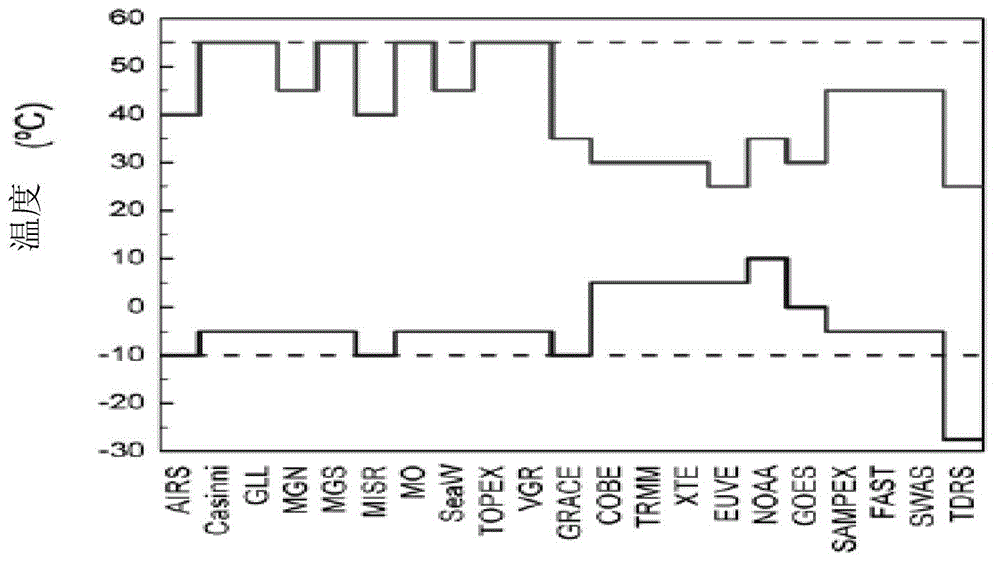

Evaluation method of thermal vacuum environmental adaptability of elements and components for spacecraft

ActiveCN102981081AQuick evaluationAccurate evaluationElectrical testingFluid-tightness measurementElectric stressEngineering

The invention relates to the technical field of the evaluation of thermal vacuum environmental adaptability, and discloses an evaluation method of the thermal vacuum environmental adaptability of elements and components for a spacecraft. The method comprises the following steps: S1, performing stress analysis to the thermal vacuum environment of the elements and components for the spacecraft, so as to fix the vacuum stress, thermal stress and electric stress of thermal vacuum environmental ground tests, S2, fixing the cycle index of the thermal vacuum environmental ground tests, S3, performing thermal vacuum ground testing to the elements and components for the spacecraft according to test conditions fixed through S1 and S2, so as to judge whether samples of the elements and components for the spacecraft are qualified, and S4, evaluating that the thermal vacuum environmental adaptability of the elements and components meets task requirements if the quantity of unqualified samples is smaller than or equal to the acceptance number regulated in a sampling scheme, or evaluating that the thermal vacuum environmental adaptability of the elements and components does not meet the task requirements. The method can rapidly and accurately evaluate performances of the elements and components for the spacecraft under the thermal vacuum environment, and provides a basis for reasonably selecting the elements and components for the spacecraft.

Owner:BEIJING SHENGTAOPING TEST ENG TECH RES INST

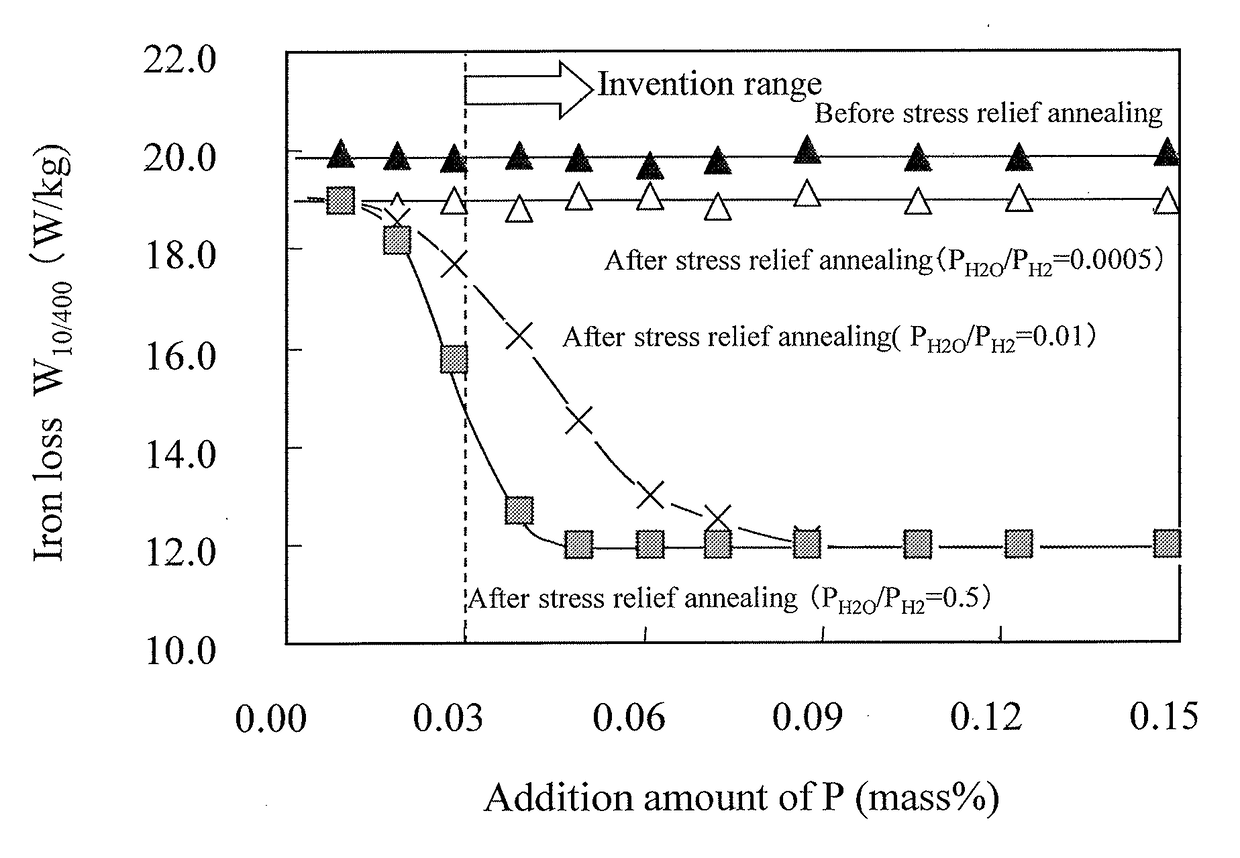

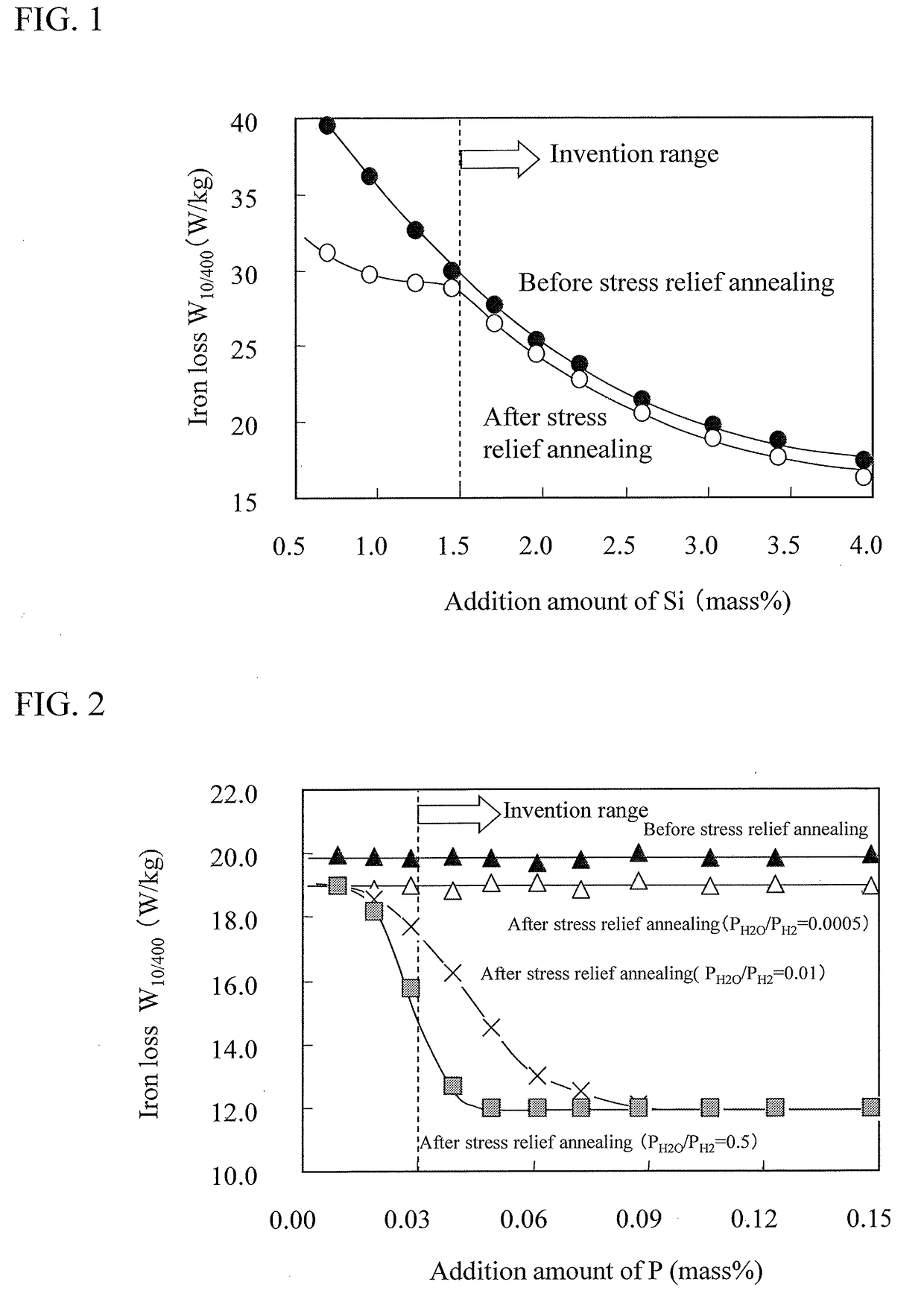

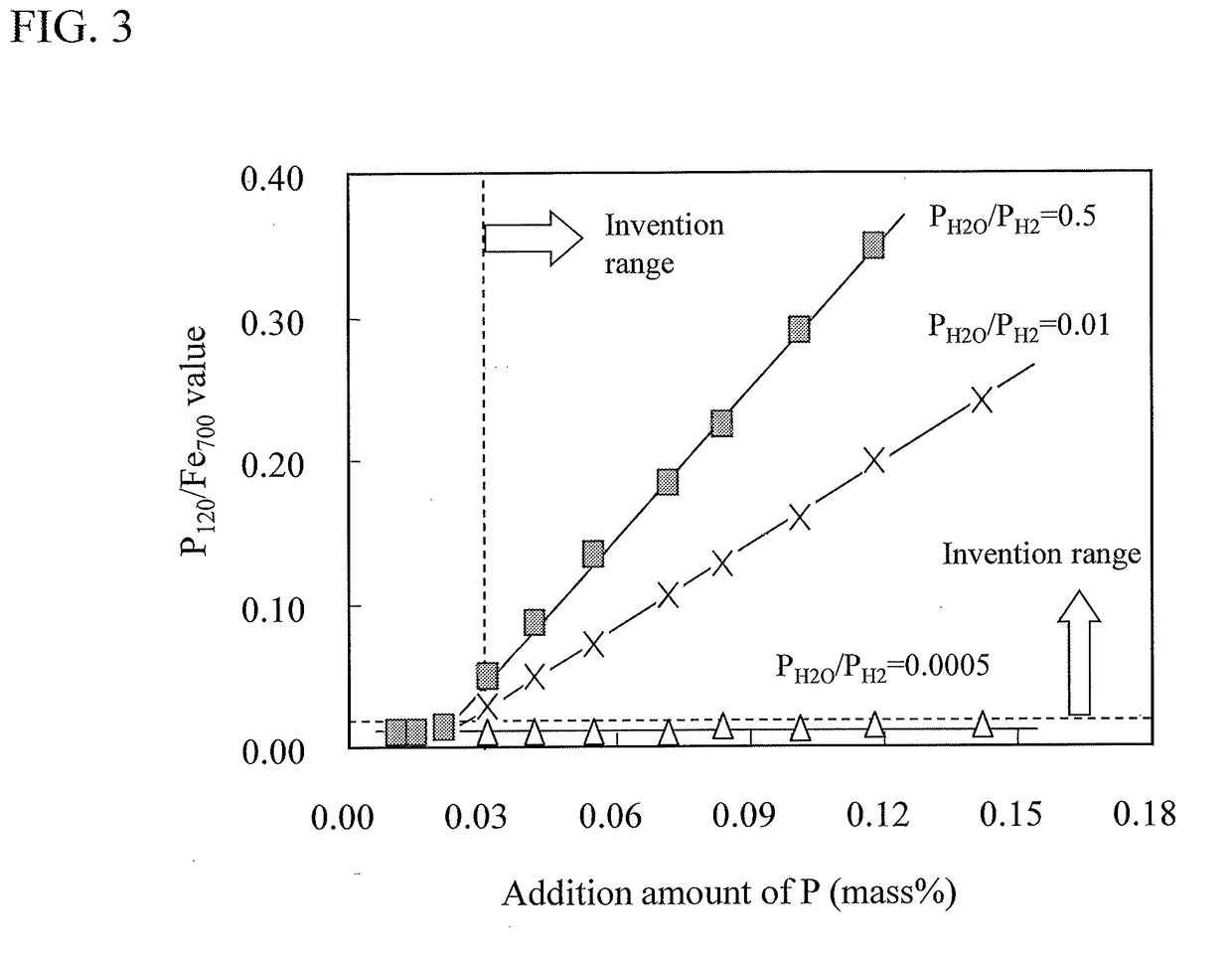

Non-oriented electrical steel sheet, production method therefor, and motor core

ActiveUS20180066333A1High strengthLow iron-lossInorganic material magnetismFurnace typesElectrical steelChemical composition

In the production of a non-oriented electrical stress sheet by hot rolling a slab having a chemical composition comprising, by mass %, C: not more than 0.005, Si: 1.5-6.0, Mn: 0.05-2.0 and P: 0.03-0.15, subjecting to a hot band annealing, if necessary, cold rolling, finish annealing, and forming an insulation coating, the cooling from 700° C. to 500° C. in the finish annealing is conducted in an oxidizing atmosphere with an oxygen potential PH2O / PH2of not less than 0.001 for 1-300 seconds, whereby P is segregated into the surface of the steel sheet after the finish annealing to obtain a non-oriented electrical steel sheet enhancing a crystal grain growth properties in the stress relief annealing.

Owner:JFE STEEL CORP

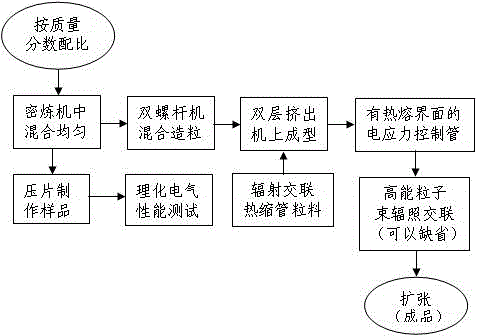

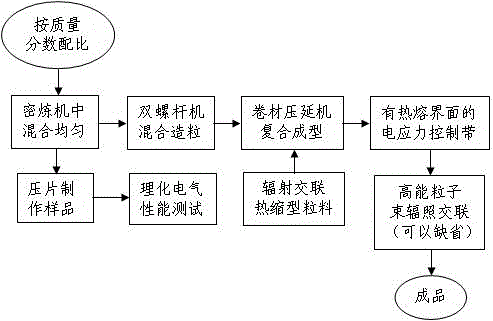

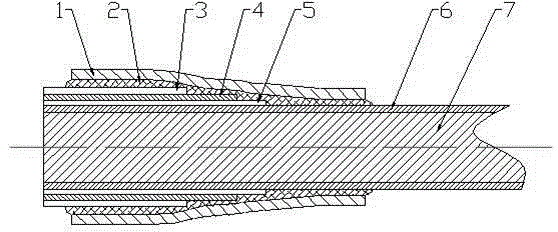

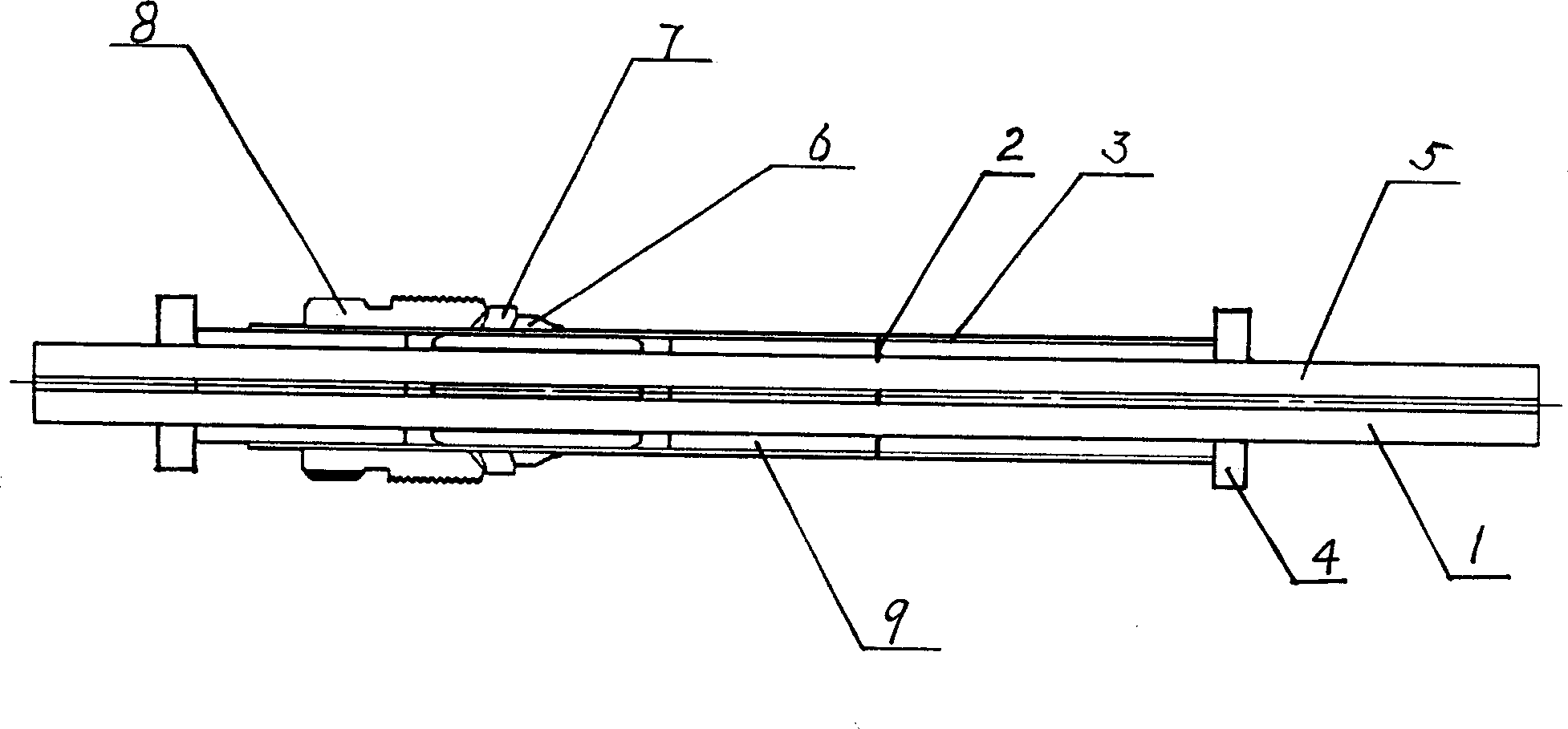

Electrical stress control hot melting composition and control element provided with hot melting interface

InactiveCN104804295AImprove composition qualityImprove reliabilityCable fittingsDielectricElectric stress

The invention discloses electrical stress control hot melting composition which comprises components by weight as follows: 100 parts of matrix resin, 5-20 parts of tackifying resin, 40-120 parts of filler with high dielectric constant, 1-30 pats of conductive filler and 1-3 parts of an antioxidant. The invention further discloses an electrical stress control element provided with a hot melting interface. An electrical stress control tube is formed when the hot melting composition is composited with the inner wall of a heat shrink tubing, an electrical stress control tape is formed when the hot melting composition is composited with a base band, and the thickness of the hot melting composition interface layer is in a range from 5 mu m to 5 mm.

Owner:SHENZHEN WOER HEAT SHRINKABLE MATERIAL +4

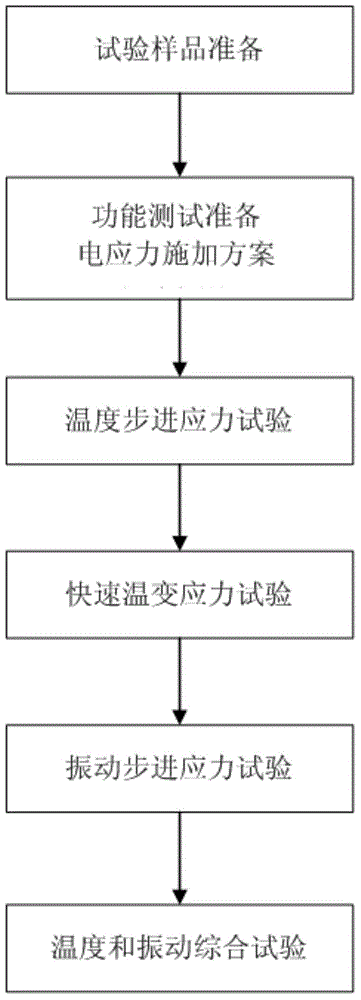

Quick evaluation method for ultimate stress strength of integrated circuit for spaceflight

InactiveCN104596719AQuickly determine damage limitsQuickly identify jobsVibration testingStrength propertiesCombined testUltimate stress

The invention discloses a quick evaluation method for ultimate stress strength of an integrated circuit for spaceflight. The quick evaluation method includes temperature stepping stress test, quick temperature change stress test, vibration stepping stress test, and temperature and vibration comprehensive stress test. The whole process of each test tests the functions of a sample to be evaluated and records fault phenomenons. The other special stress can be exerted to the sample to be evaluated when exerting temperature or vibration stress, such as electric stress. According to the quick evaluation method for the ultimate stress strength of the integrated circuit for the spaceflight, through exerting a series of combined tests, the failure time of the product is reduced, and the evaluation test finishing time is reduced to one week from the original six months to one year; through the heat, power and electric stress combined test, a superimposed or coordination effect is formed, and the evaluation test completeness and precision are greatly improved. Multiple verification results prove that the product fault mode coverage rate discovered in the test evaluation can arrive at more than 98%.

Owner:北京自动测试技术研究所有限公司

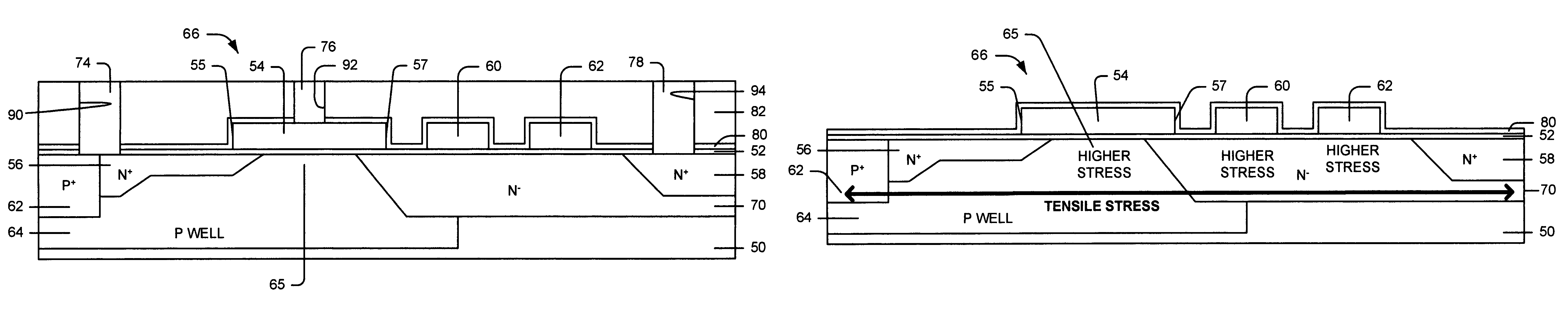

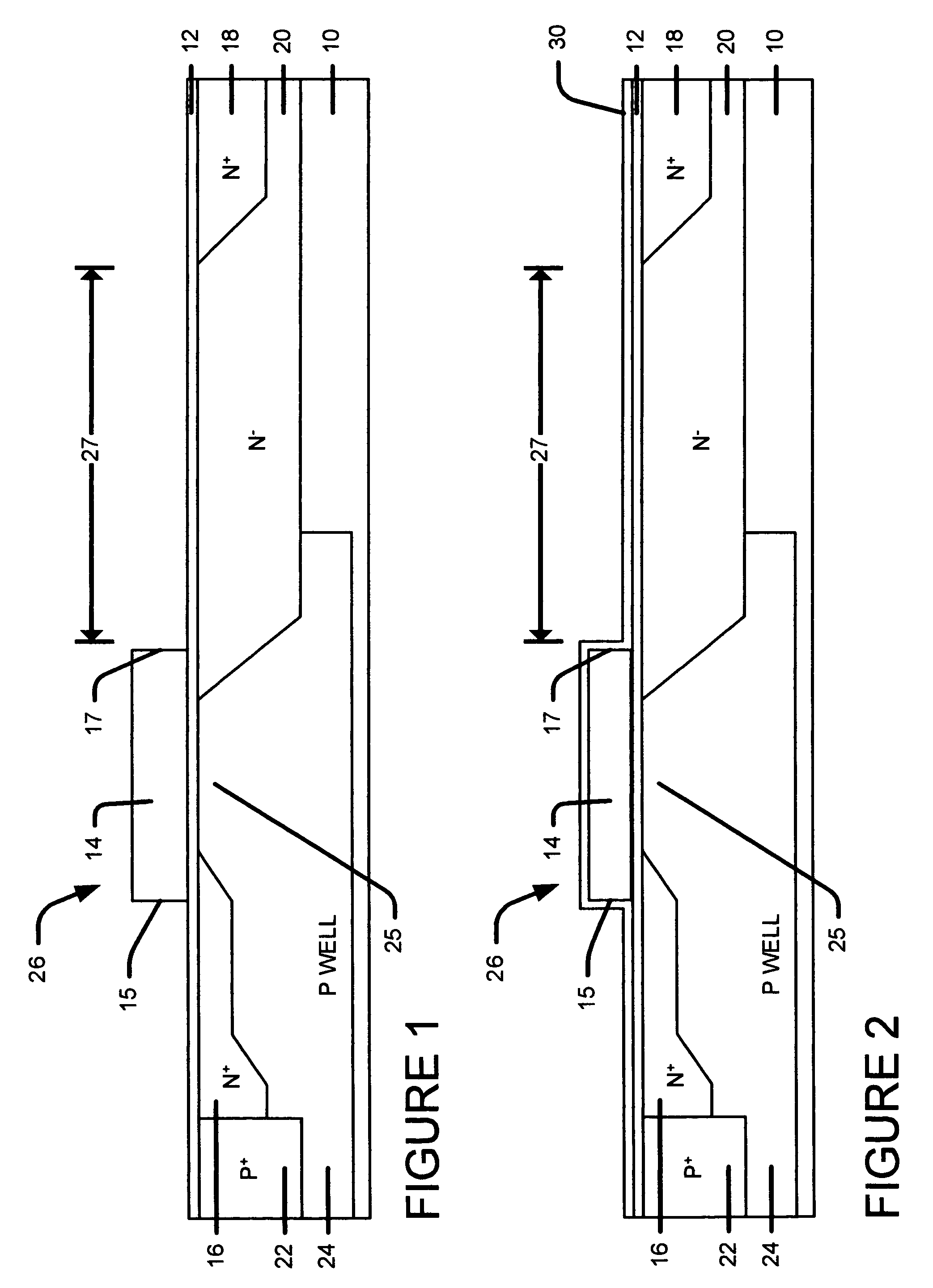

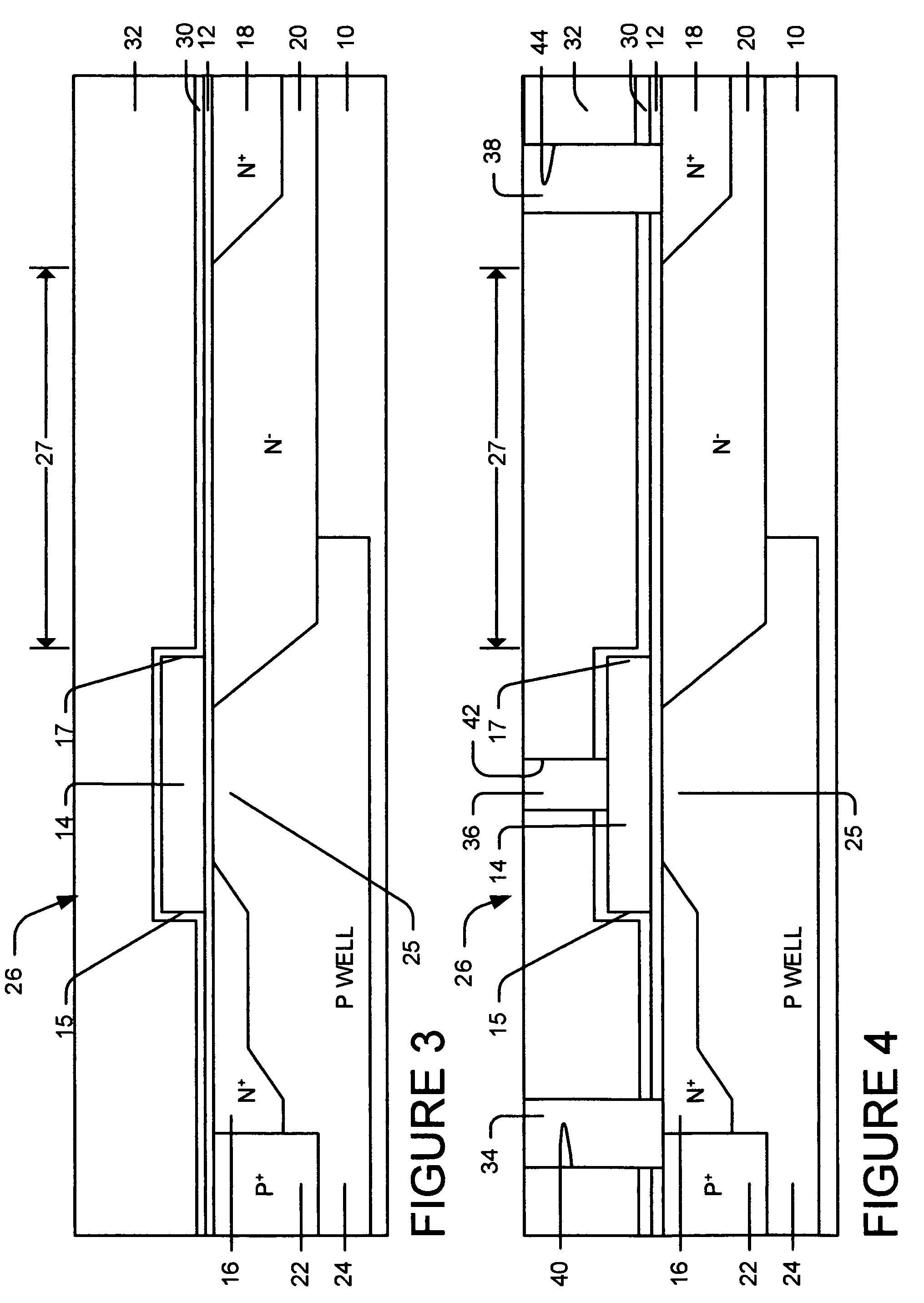

LDMOS using a combination of enhanced dielectric stress layer and dummy gates

ActiveUS7824968B2Semiconductor/solid-state device manufacturingSemiconductor devicesLDMOSElectrical and Electronics engineering

First example embodiments comprise forming a stress layer over a MOS transistor (such as a LDMOS Tx) comprised of a channel and first, second and third junction regions. The stress layer creates a stress in the channel and the second junction region of the Tx. Second example embodiments comprises forming a MOS FET and at least a dummy gate over a substrate. The MOS is comprised of a gate, channel, source, drain and offset drain. At least one dummy gate is over the offset drain. A stress layer is formed over the MOS and the dummy gate. The stress layer and the dummy gate improve the stress in the channel and offset drain region.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

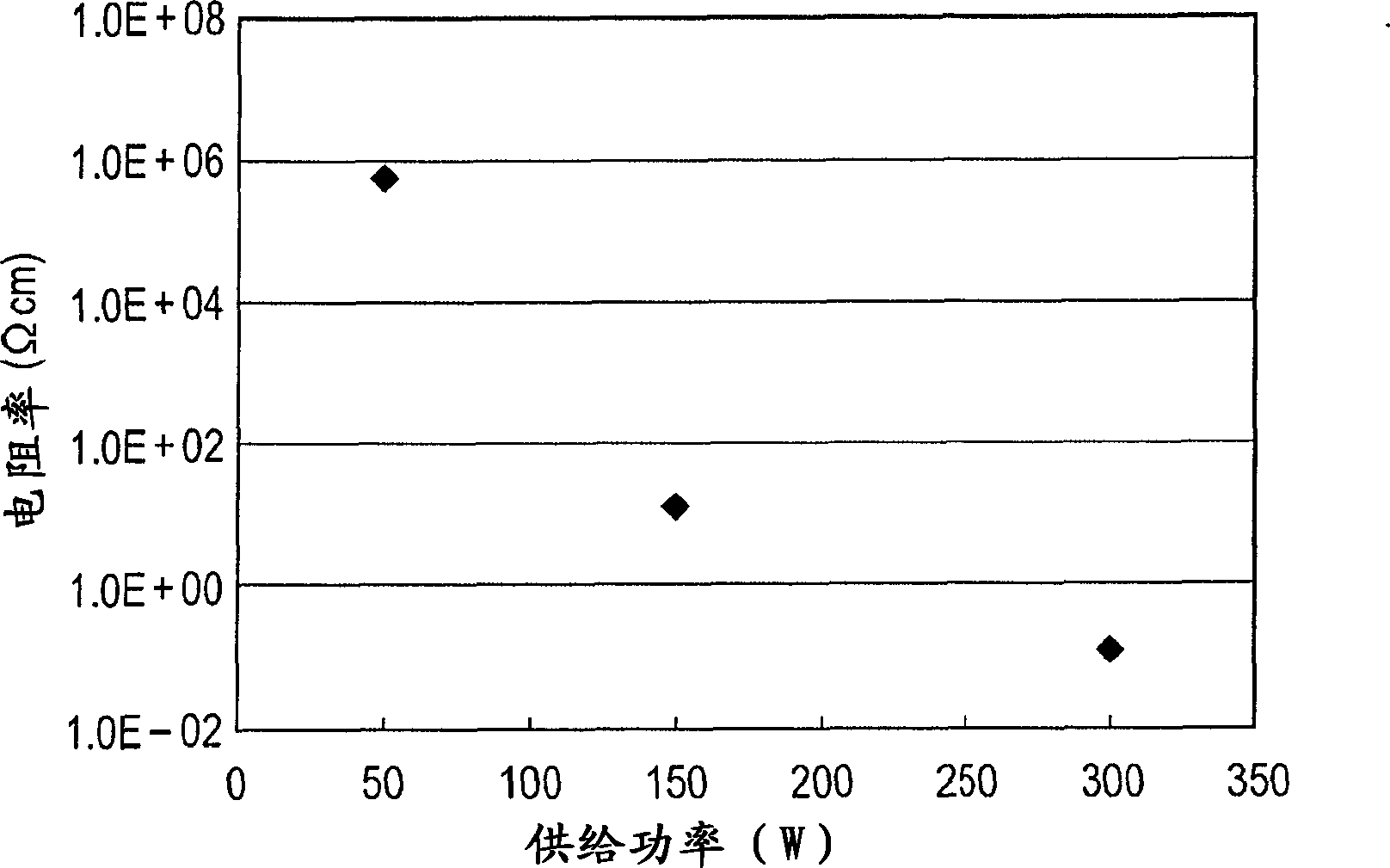

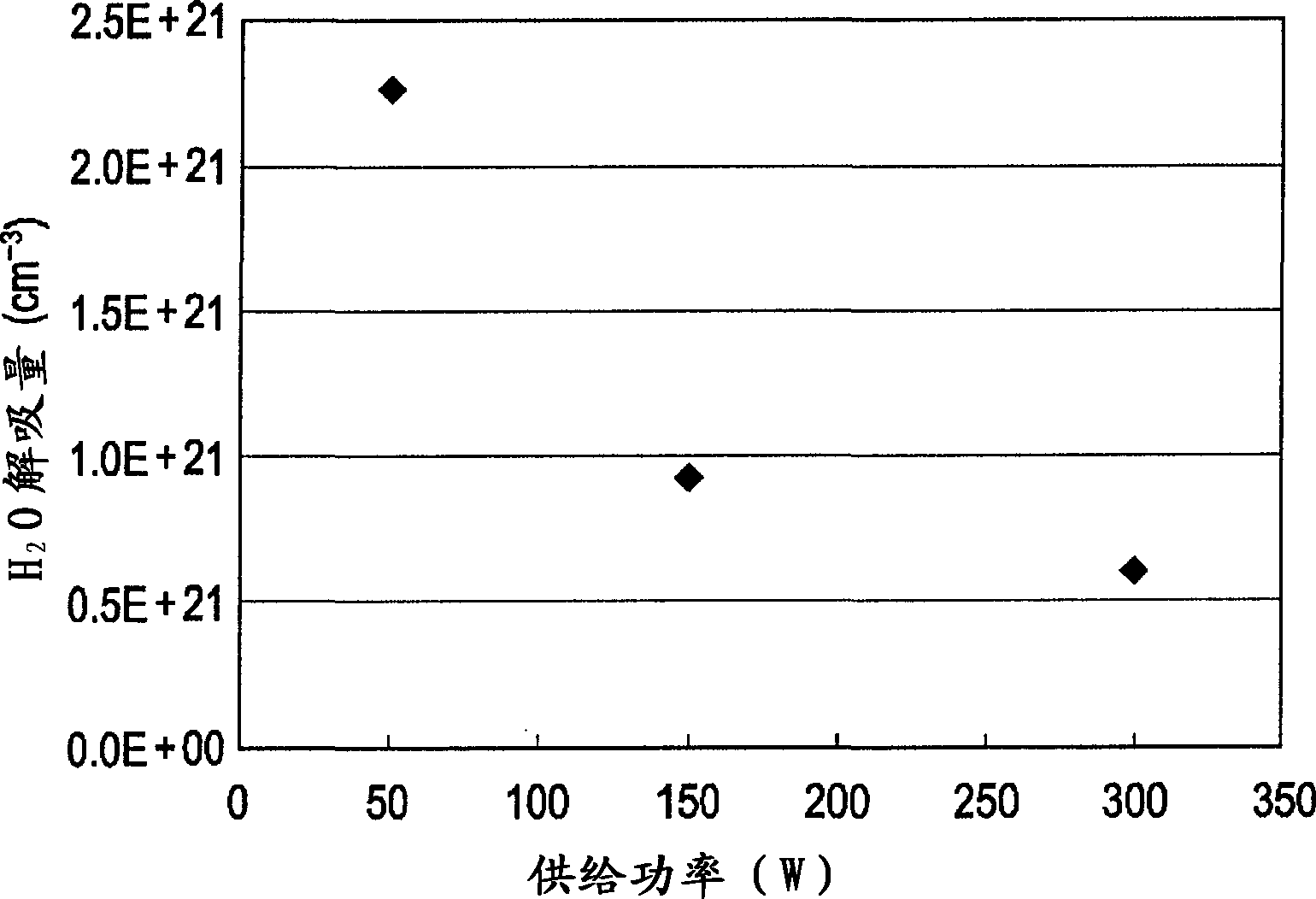

Thin-film transistor

InactiveCN102549757ALittle changeTransistorSemiconductor/solid-state device manufacturingHydrogen concentrationHydrogen atom

Owner:CANON KK

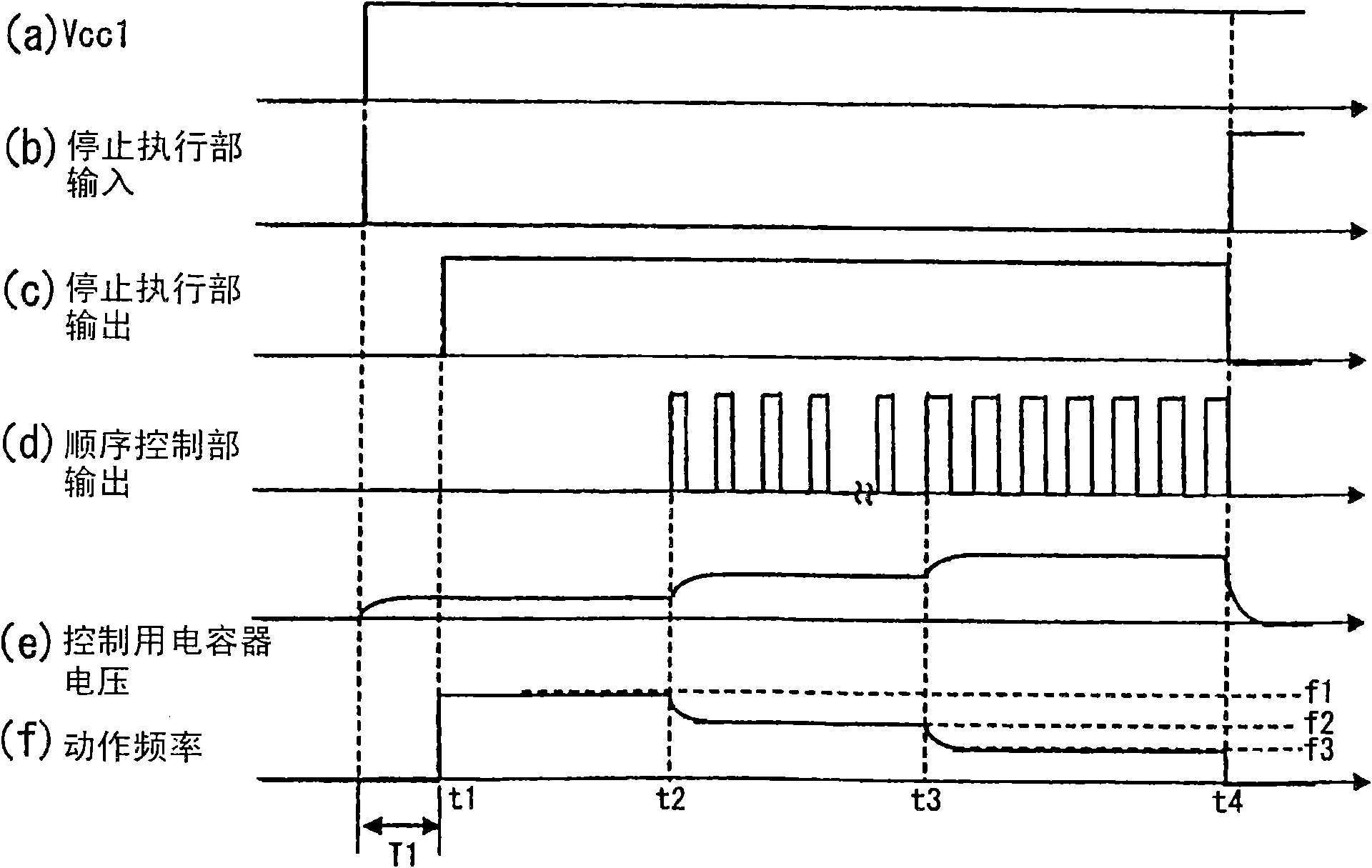

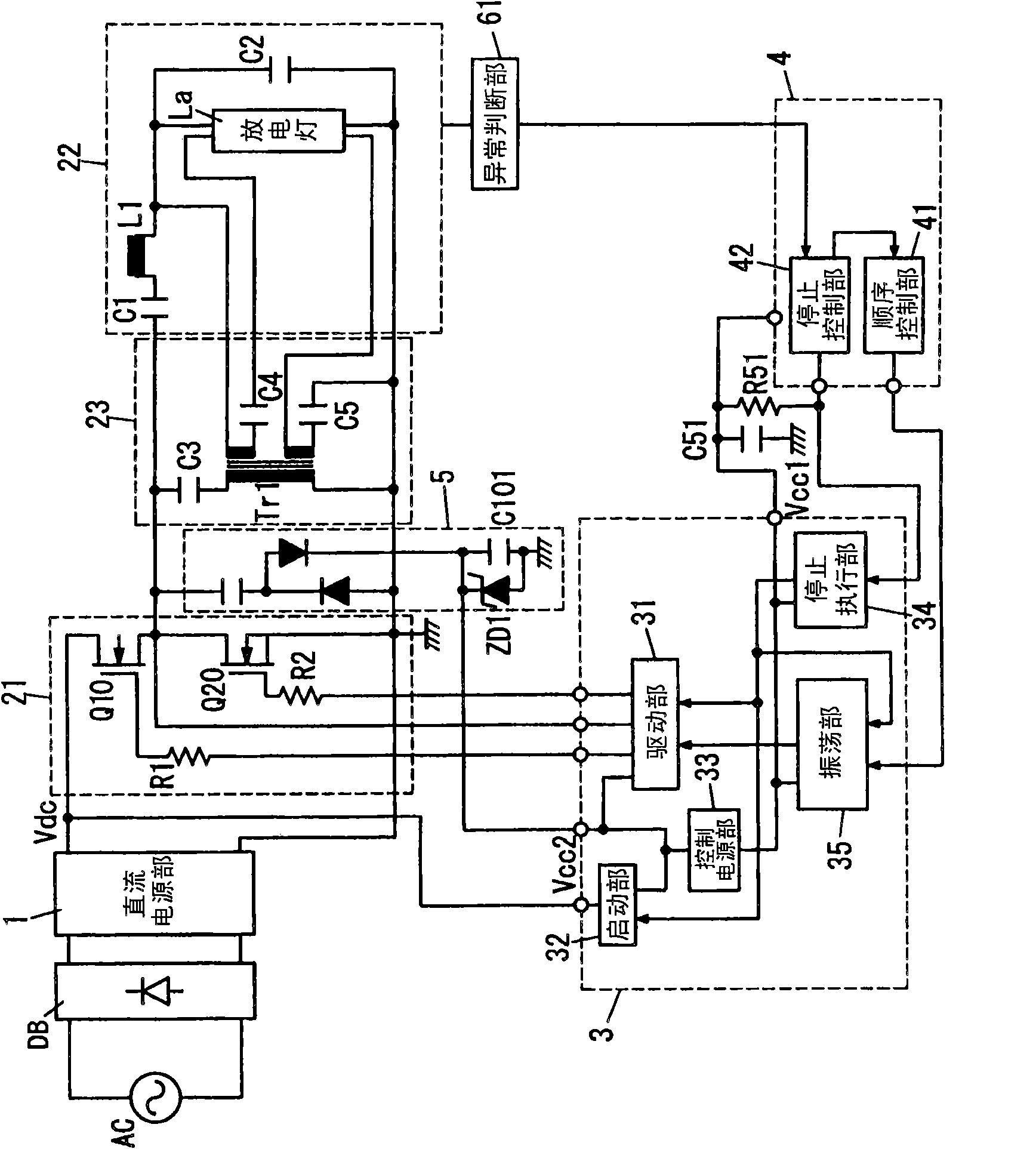

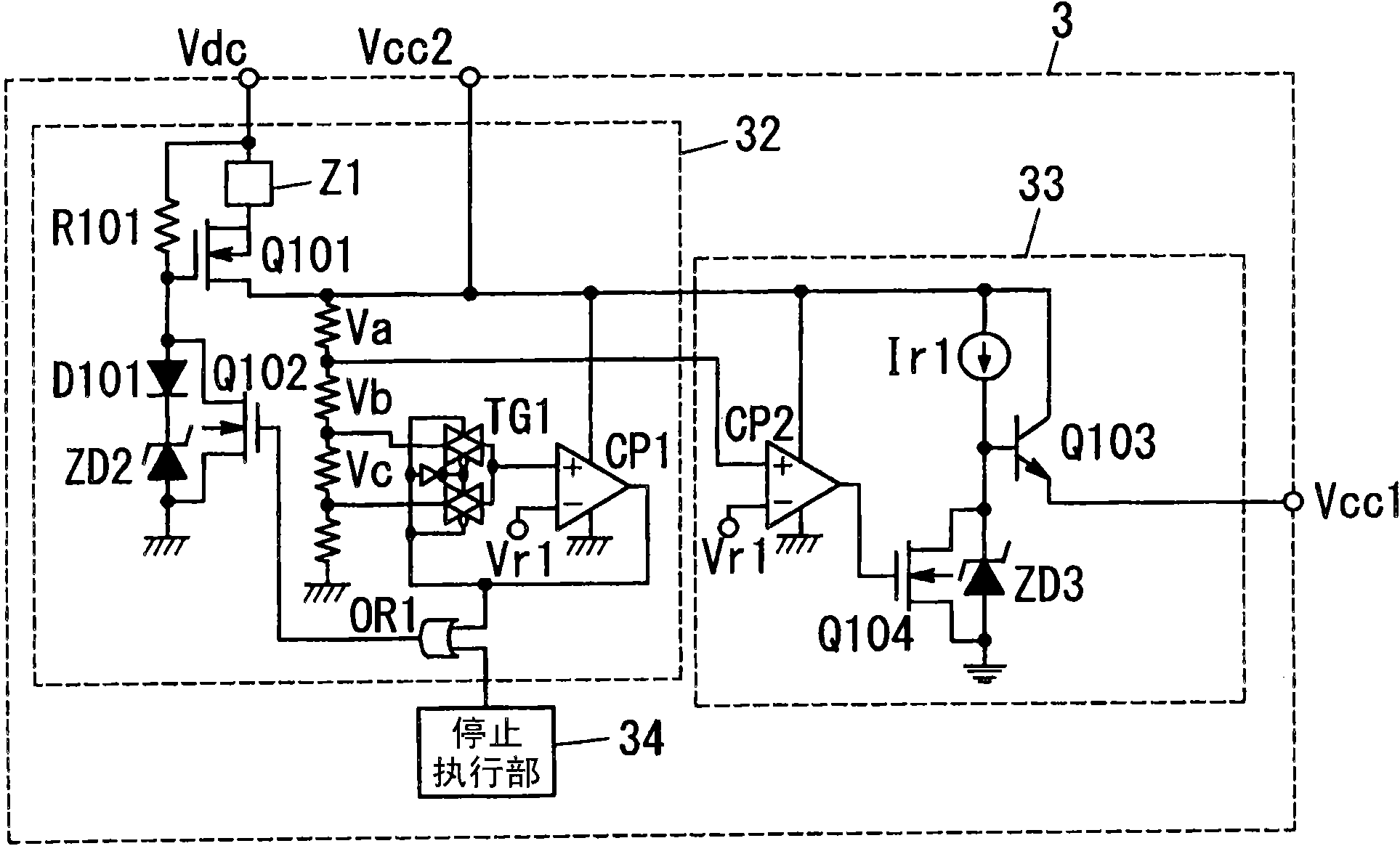

Discharge lamp lighting device, power supply device and illuminator

The invention provides a discharge lamp lighting device, a power supply device and an illuminator, which can prevent an overlarge electric stress on a circuit element or the discharge clamp after lighting the lamp. The device is provided with a direct current power supply part, a resonance part formed a resonance circuit together with the discharge lamp. A switch part for switching the DC power supply part and the resonance part, and a driving part for driving the switch part to output an alternated current to the discharge lamp from the resonance part through the voltage frequencies on two ends of a controlling capacitor. After the driving part is started and still cannot work in a preset stopping time T1, the driving part starts to work after stopping for the stopping time T1. The voltages on two ends of the capacitor can be stabled in the stopping time T1, so the overlarge electric stress on the circuit element or the discharge clamp can be avoided after starting, even if starting again after stopping for a short period of time.

Owner:PANASONIC CORP

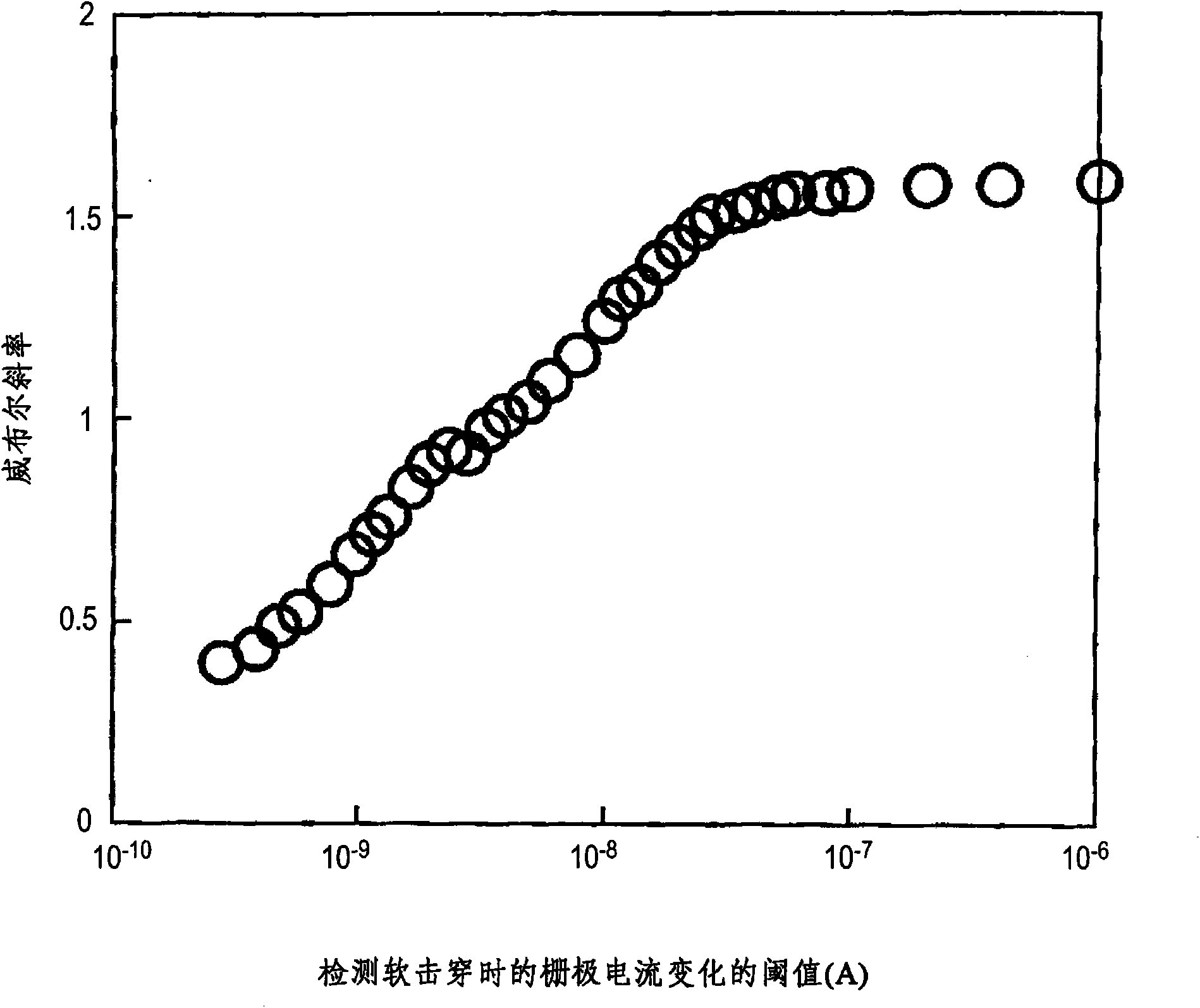

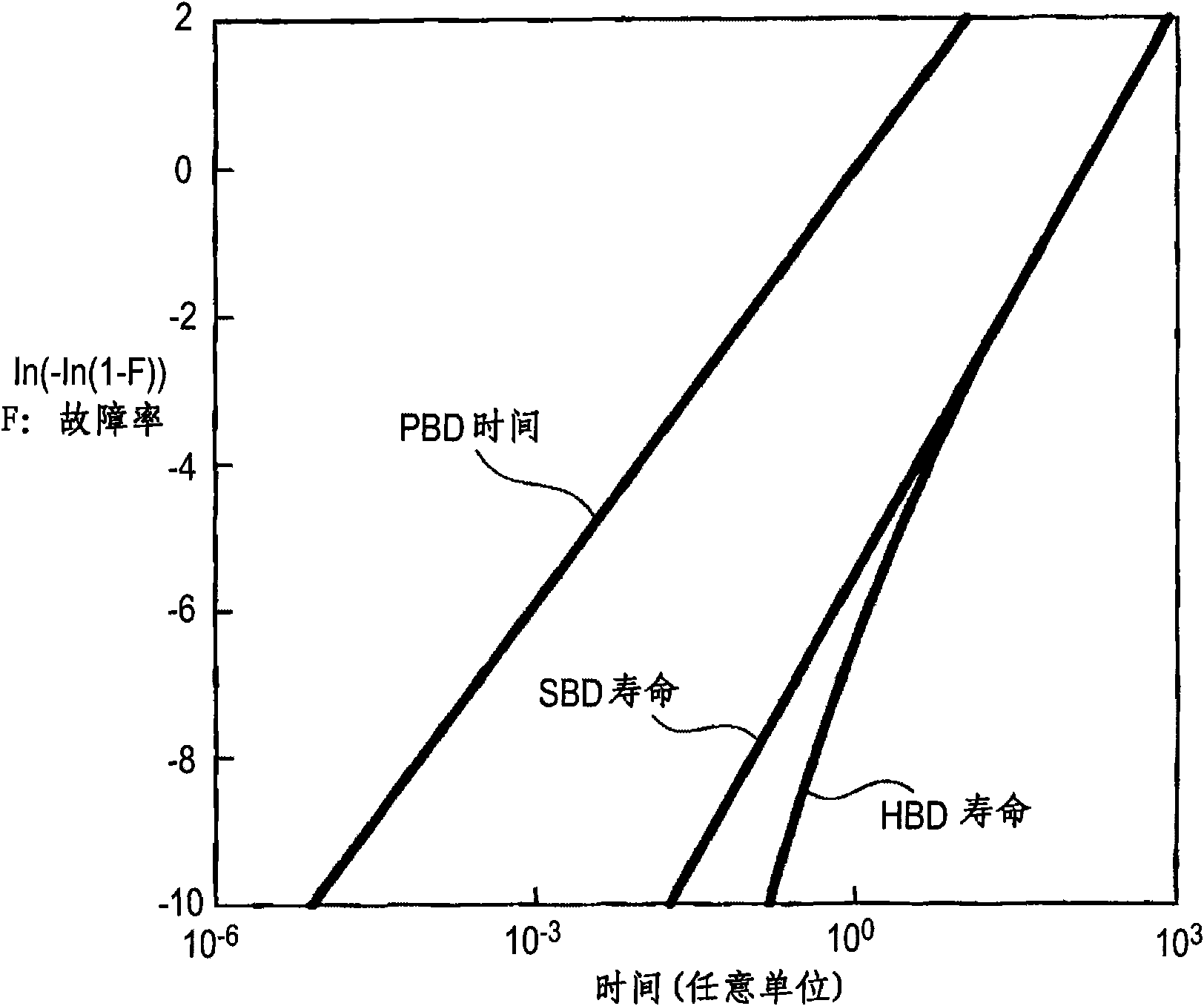

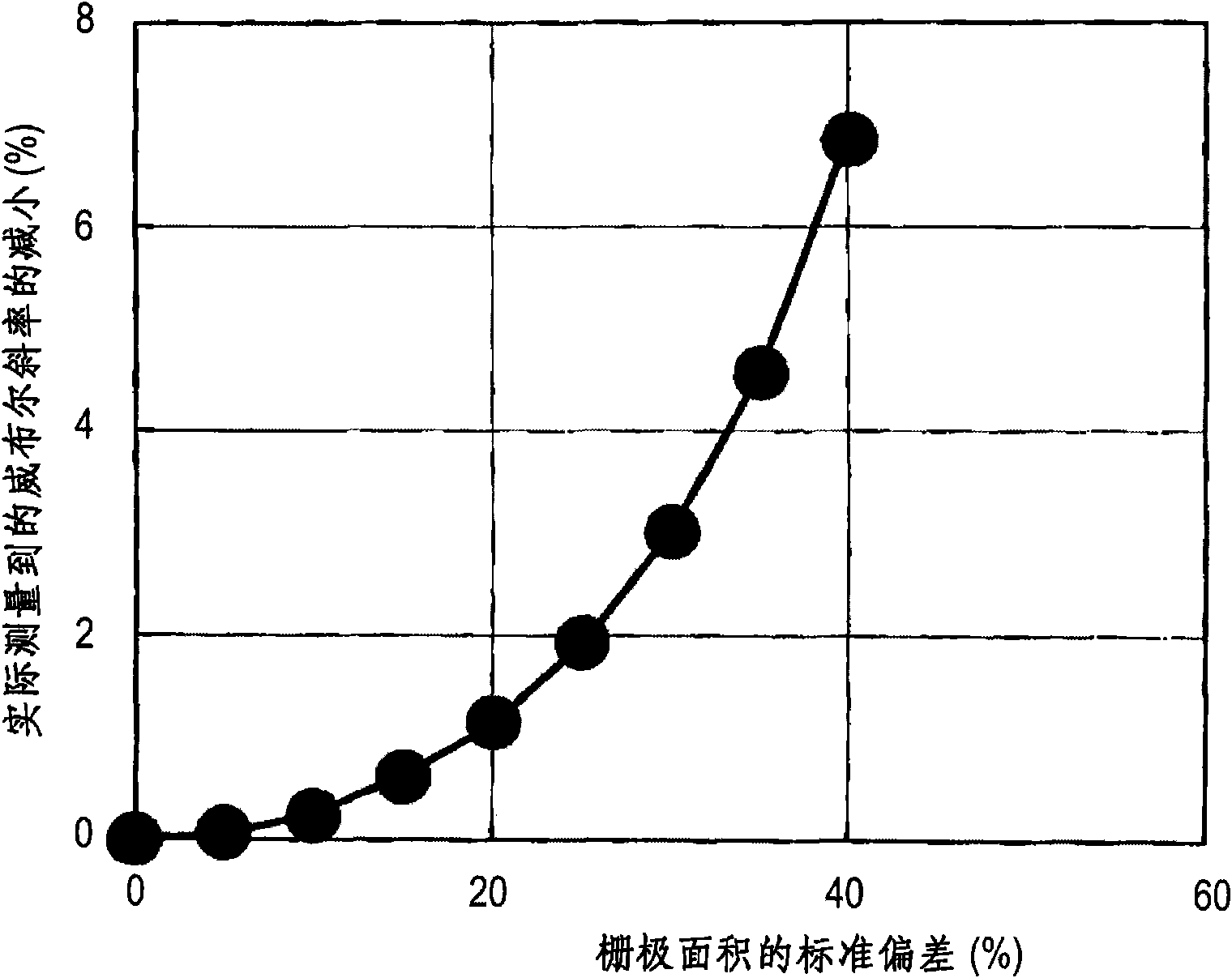

Valuation method of dielectric breakdown lifetime of gate insulating film, valuation device of dielectric breakdown lifetime of gate insulating film and program for evaluating dielectric breakdown lifetime of gate insulating film

InactiveCN101995536AAccurate assessmentNo loss of detectionTesting dielectric strengthSemiconductor/solid-state device testing/measurementRoom temperatureElectric stress

The present invention discloses a valuation method, a valuation device and a valuation program of dielectric breakdown lifetime of a gate insulating film, used for evaluating dielectric breakdown lifetime of the gate insulating film of a MOS type element. The valuation method includes the following steps of: deciding a Weibull slope of lifetime distribution until reaching a soft breakdown of the gate insulating film of the MOS type element; deciding a detection condition of the soft breakdown from the decided Weibull slope after the above step; and executing a dielectric breakdown test by using the decided detection condition. The valuation device includes: a voltage supply unit to supply a voltage for the MOS type element so as to apply an electric stress to the MOS type element; a current measuring unit to measure a leakage current across the gate insulating film; and a temperature holding unit to hold temperature of a testing element containing the MOS type element to below a room temperature. According to the valuation method, the valuation device and the valuation program, the dielectric breakdown lifetime can be determined suitably.

Owner:SONY CORP

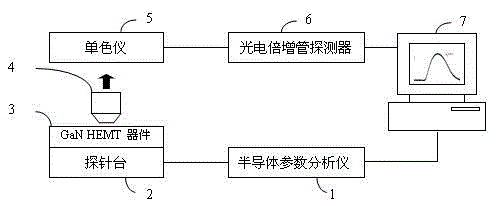

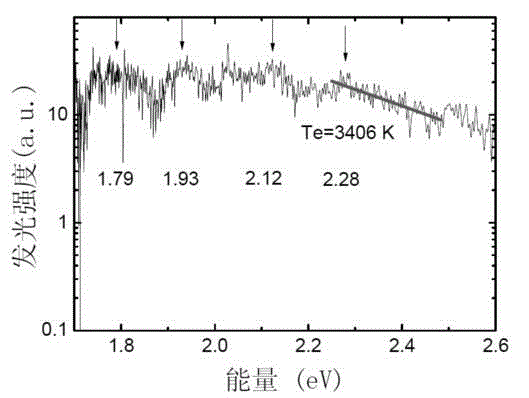

In-wafer reliability screening method for GaN HEMT (High Electron Mobility Transistor) device

ActiveCN102721913AImprove reliabilityAvoid preparationOptically investigating flaws/contaminationIndividual semiconductor device testingHeterojunctionLuminous intensity

The invention discloses an in-wafer reliability screening method for a GaN HEMT (High Electron Mobility Transistor) device. The in-wafer reliability screening method is characterized by comprising the following steps that: firstly, in-wafer electroluminescence spectrum testing platform is established, a GaN heterojunction HEMT device wafer is placed on a probe platform in a darkroom, and then probes are respectively pressed on a grid electrode, a source electrode and a leakage electrode; and then, the source electrode is grounded, certain forward bias is applied to the leakage electrode, backward bias Vgs, which changes from pinch-off voltage Vp to 0V, is applied to the grid electrode, a change relationship between the luminous intensity of a GaN heterojunction HEMT device and grid voltage is tested by virtue of a spectrum testing system, the luminescence spectrum of the device is tested under the adopted bias point Vgsm with the largest luminous intensity, and then the spectrum is analyzed to evaluate the reliability of the device. The in-wafer reliability screening method has the advantages that in-wafer screening can be realized; a series of reliability screening preparation procedures, such as scribing and packaging, is eliminated without long-time electric stress; and the reliability screening time is shortened, costs are saved, and work efficiency is improved.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

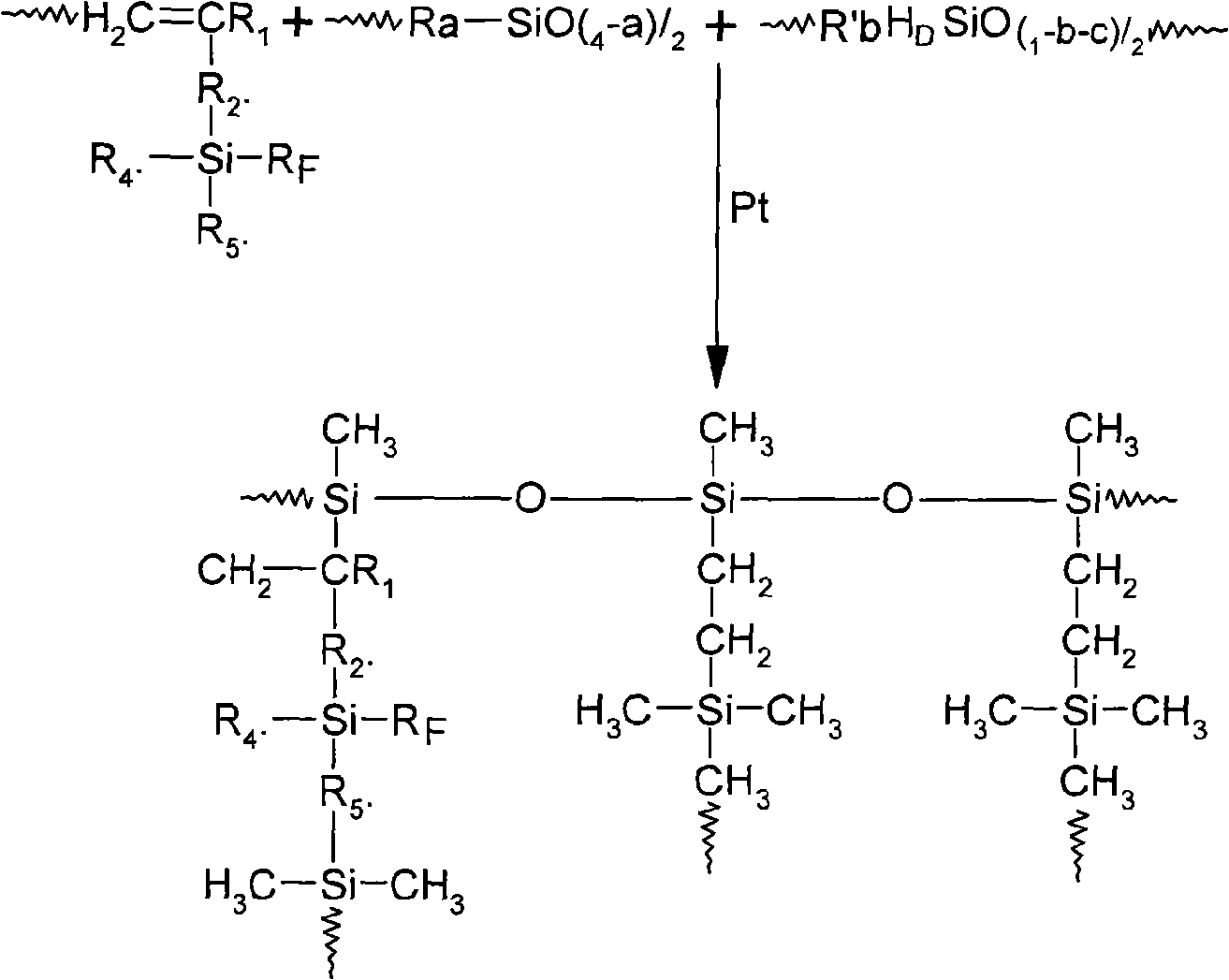

Liquid conductive silastic used for electric stress control and preparation method thereof

InactiveCN101575454AImprove liquidityImprove mechanical propertiesNon-conductive material with dispersed conductive materialElectric stressFumed silica

The invention provides a liquid conductive silastic used for electric stress control, which is prepared by component A and component B according to the weight ratio of 1:1; the component A and the component B both contain 35-80 parts by weight of organopolysiloxane, 40-60 parts of acetylene black and fumed silica and 0.5-2.0 parts of fluorine silicon multipolymer; wherein, the component A further contains catalyst with routine dosage, and the component B further contains 3.0-5.0 parts by weight of organic hydrogenated polysiloxane and inhibitor with routine dosage. The invention further provides a preparation method of the above liquid conductive silastic; the component A and the component B are respectively blended for 6-8h at the temperature of 80-130 DEG C, and are then heated up to 150-175 DEG C and vacuumized for 1-3h, are stirred and cooled, go through a three-roll grinder and are blended evenly, and foam is discharged, finally the liquid conductive silastic is prepared. The liquid conductive silastic provided by the invention has better liquidity, good mechanical property and wide application prospect.

Owner:GUANGDONG BIOMAX SIANDF NEW MATERIAL CO LTD

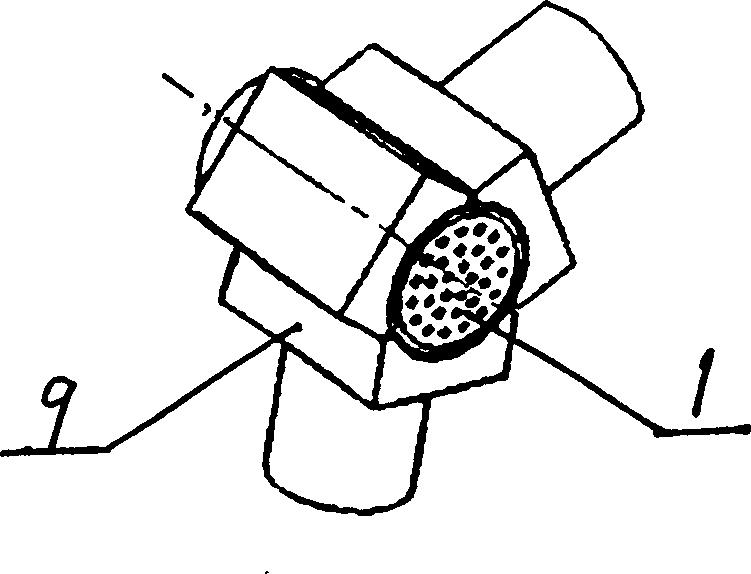

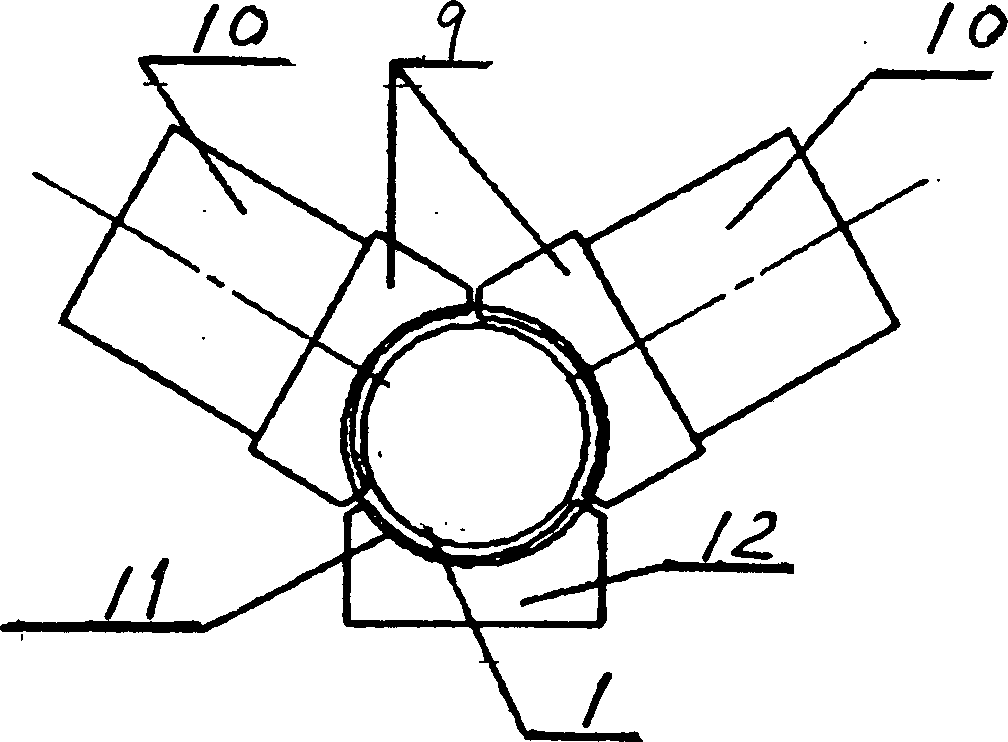

A radial compression applied sealing member processing method

The invention relates to a method for processing the reducing sealing element. It comprises: first, processing the sealing element; then compressing the sealing element radial; adding the sealing element into reducing mould; processing uniform reducing deform force on the sealing element, while rotating and compressing it at the same time, to make the deformation of reducing neck to 0.8-0.92%. The invention has the advantages that: said sealing element can be used in the electric connection and sealing between the inner and outer parts of support container, especially used in the safe frame of atomic reactor or research reactor, to effectively prevent electric stress power, high temperature, high pressure, temperature change, accumulated radiation, chemical corrosion, and vibrations. It can confirm the sealing and electric properties of support container.

Owner:SHANGHAI POWER EQUIP RES INST +1

BGA (ball grid array) welding point acceleration service life prediction method

ActiveCN104344988AGet Predicted LifespanThe test method is simple and reliableStrength propertiesAcceleration factorMechanical equipment

The invention relates to a BGA (ball grid array) welding point acceleration service life prediction method, which comprises the following steps that (a) n BGA welding point samples are randomly selected, wherein the n is greater than or equal to 5, and the BGA welding point samples are subjected to environment stress screening processing; (b) the samples processed in the step (a) are subjected to integral stress processing, and the integral stress processing comprises second temperature circulation processing, random vibration processing and electric stress processing on the samples processed in the step (a), and in addition, the sample failure time is recorded; (c) the samples processed in the step (b) are subjected to third temperature circulation processing; (d) a model shown in a formula (III) is used for calculating an acceleration factor, and finally, a formula (IV) is used for calculating the use average failure before time MTTR<use> for predicting the service life of the BGA welding point. The invention also provides application of the method to the preparation of electronic products and mechanical equipment.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD