Combined environment test method for integrated circuit

A technology of integrated circuits and test methods, which is applied in the field of integrated circuits, can solve problems such as the inability to truly simulate the use environment of integrated circuits, and achieve the effect of accurate evaluation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

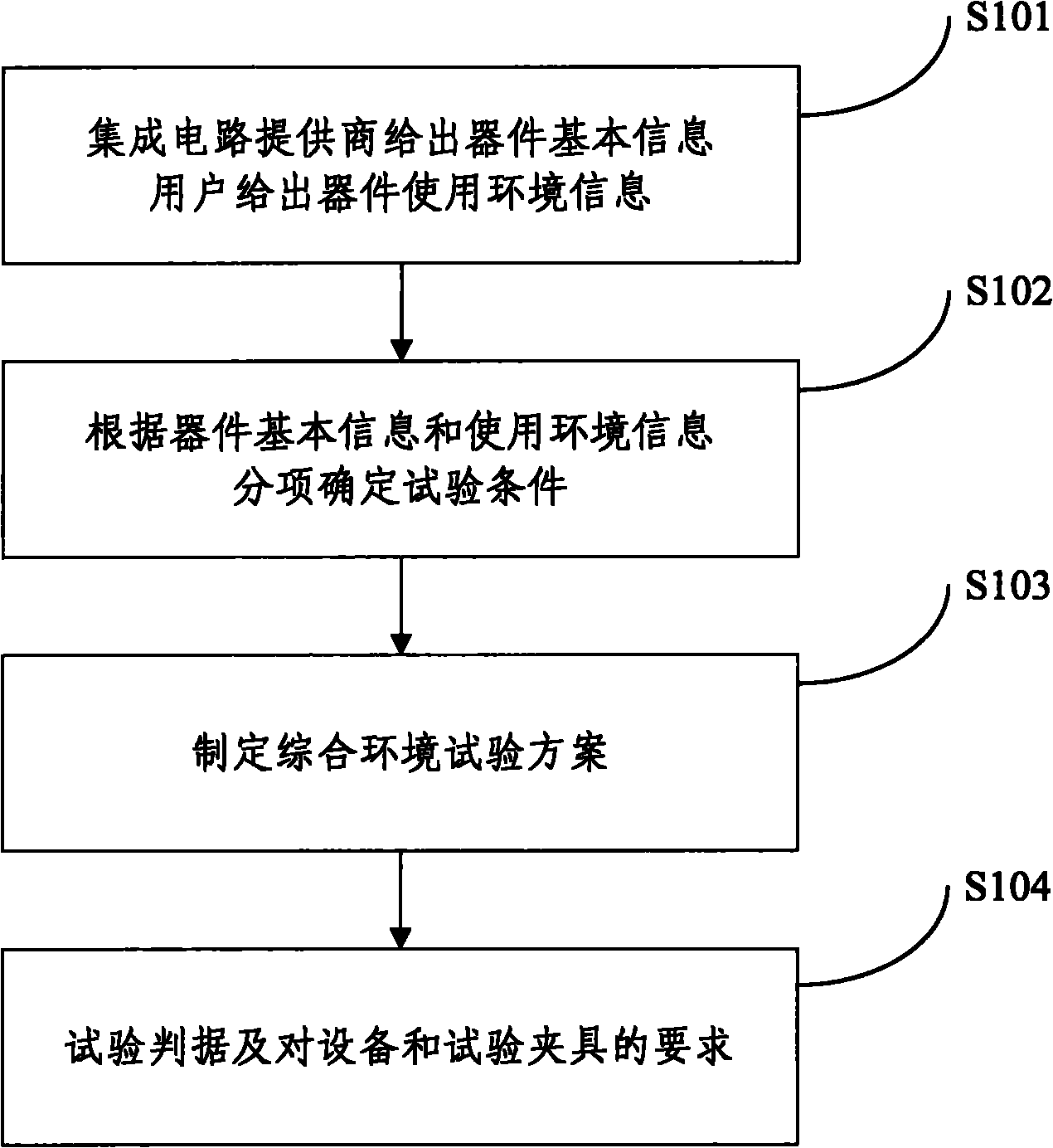

[0026] figure 1 It is a flow chart of an embodiment of the integrated circuit comprehensive environmental test method of the present invention, and the test method of the present embodiment includes the following steps:

[0027] S101. The integrated circuit provider provides basic information of the product, and the user provides information on the environment in which the device (integrated circuit) is used as an input for formulating comprehensive test conditions.

[0028] The basic product information that the integrated circuit supplier should provide includes: the maximum operating temperature of the device, the minimum operating temperature of the device, the rated operating voltage of the device, the maximum operating voltage of the device, and the minimum operating voltage of the device, etc.

[0029] The user provides the env...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More