Quick evaluation method for ultimate stress strength of integrated circuit for spaceflight

An integrated circuit and ultimate stress technology, which is used in the field of rapid evaluation of the ultimate stress strength of aerospace integrated circuits, which can solve the problem of large deviation of evaluation results, inability to fully evaluate the reliability of integrated circuits, and failure to distinguish between product working limit and damage limit, etc. problems, to achieve the effect of shortening evaluation time, improving integrity, and reducing product failure time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054]The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

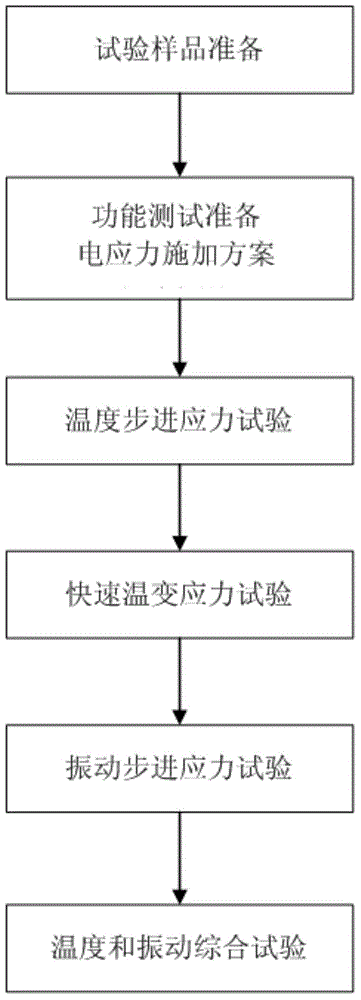

[0055] The flowchart of the method used in this embodiment is as follows figure 1 As shown, it specifically includes the following steps:

[0056] Step 1, preparation before the test.

[0057] (1) Through functional testing, select integrated circuits with qualified functional performance indicators as samples to be evaluated. The test described in the present invention is a destructive test, and the samples to be evaluated after the test should be removed from their corresponding batches.

[0058] (2) Identify the batch number and serial number of the sample to be evaluated.

[0059] (3) According to the size and weight of the sample to be evaluated, select the appropr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More