Patents

Literature

408results about "Marginal checking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Self-heating integrated circuit

ActiveUS8358145B1Driving/moving recording headsSemiconductor/solid-state device detailsDriver circuitEngineering

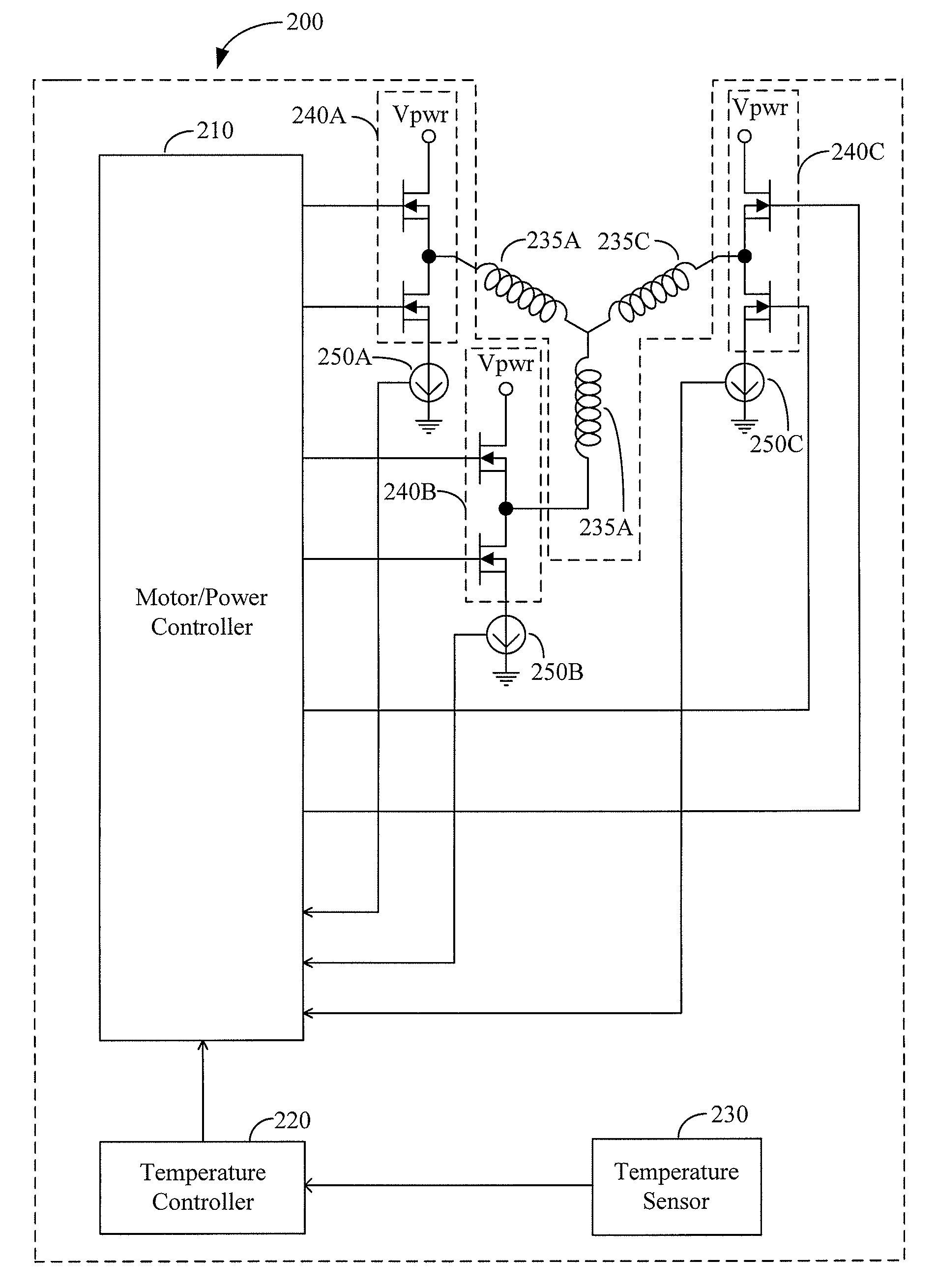

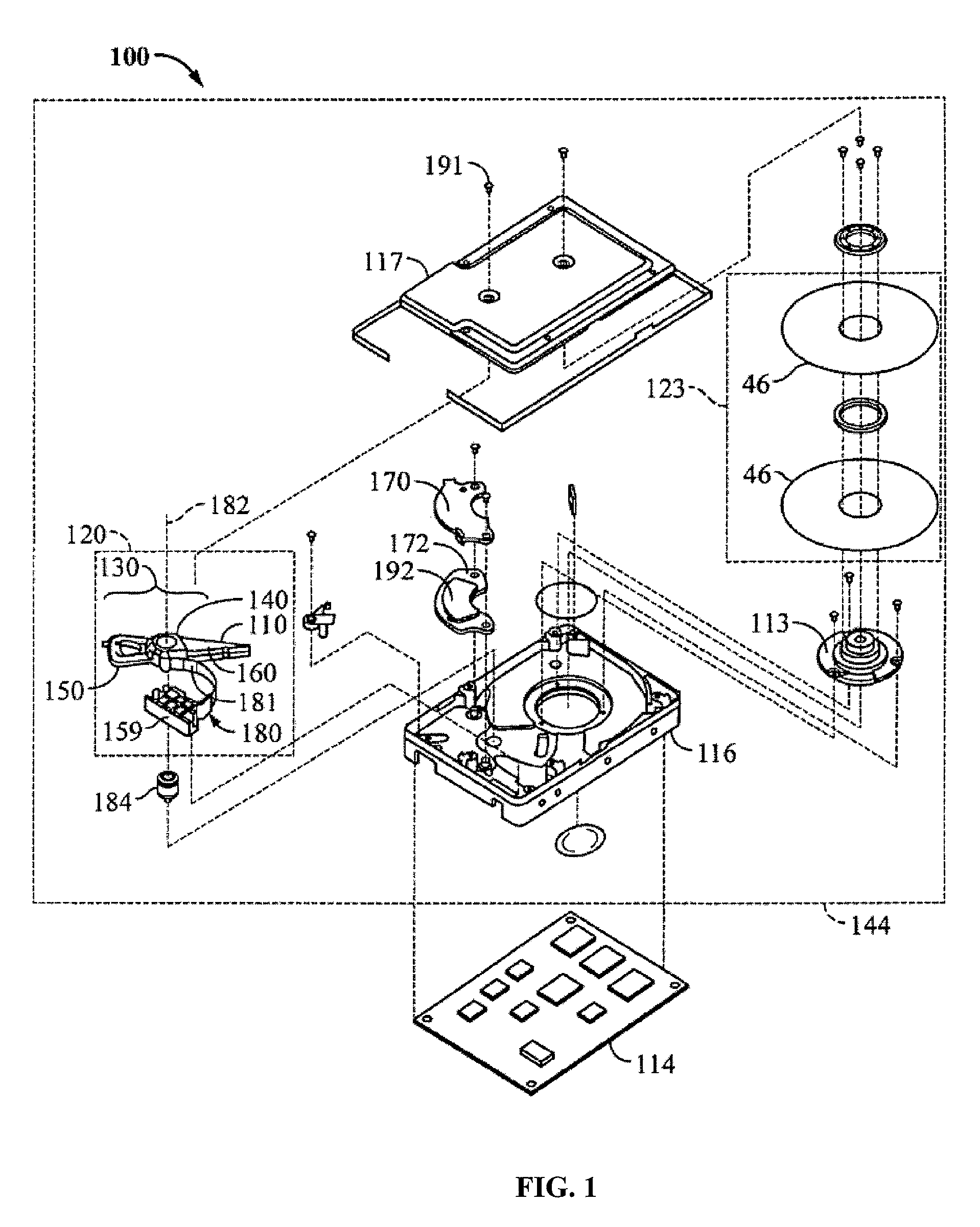

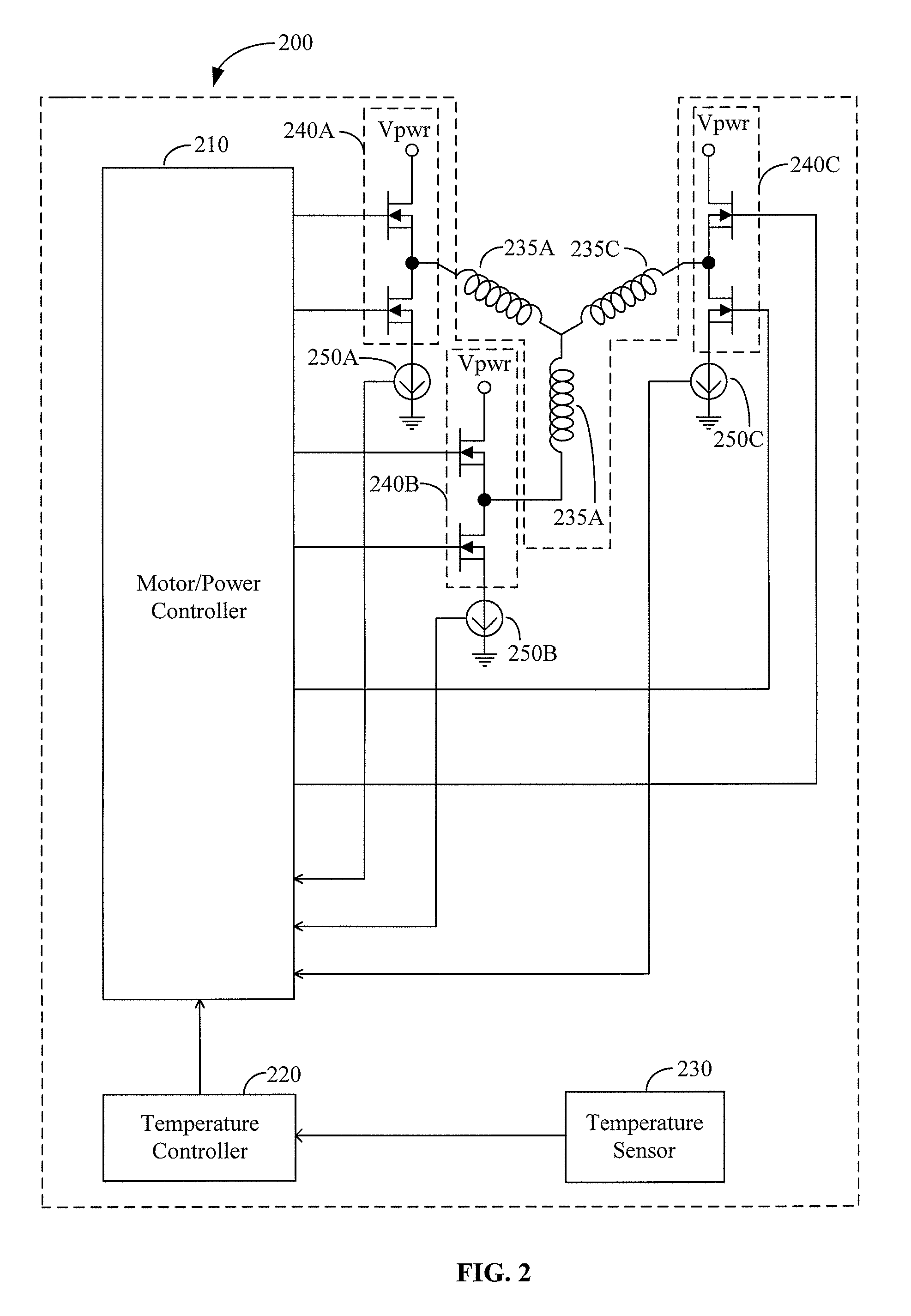

Self-heating integrated circuits are provided. In one embodiment, a self-heating integrated circuit comprises a drive circuit configured to drive a device and a controller configured to selectively operate the drive circuit in a first mode or a second mode. In the first mode, the controller is configured to operate the drive circuit to drive the device and, in the second mode, the controller is configured to operate the drive circuit to heat the integrated circuit to a target temperature.

Owner:WESTERN DIGITAL TECH INC

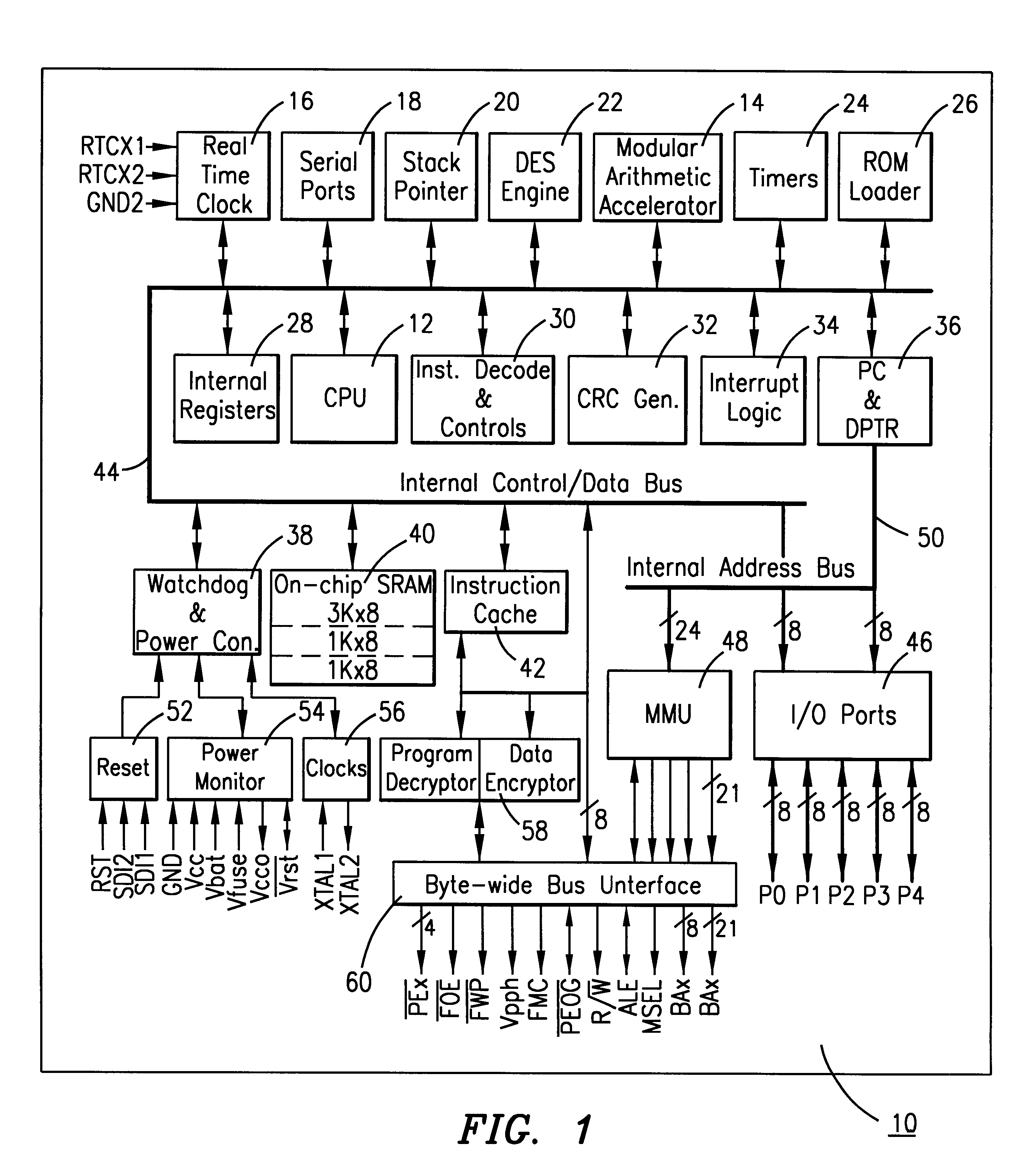

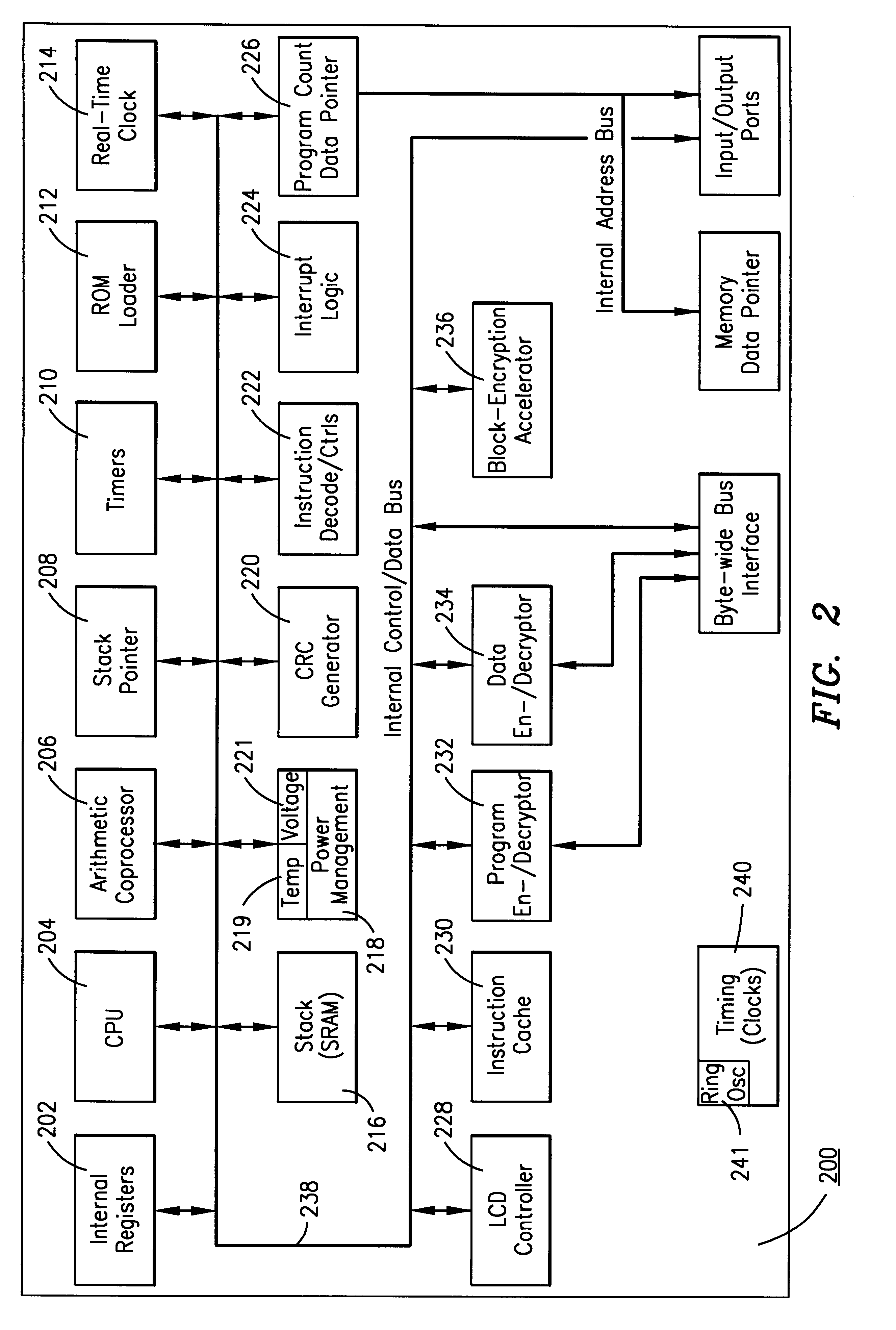

Integrated circuit having hardware circuitry to prevent electrical or thermal stressing of the silicon circuitry

InactiveUS6330668B1Digital data processing detailsAnalogue secracy/subscription systemsElectricityEngineering

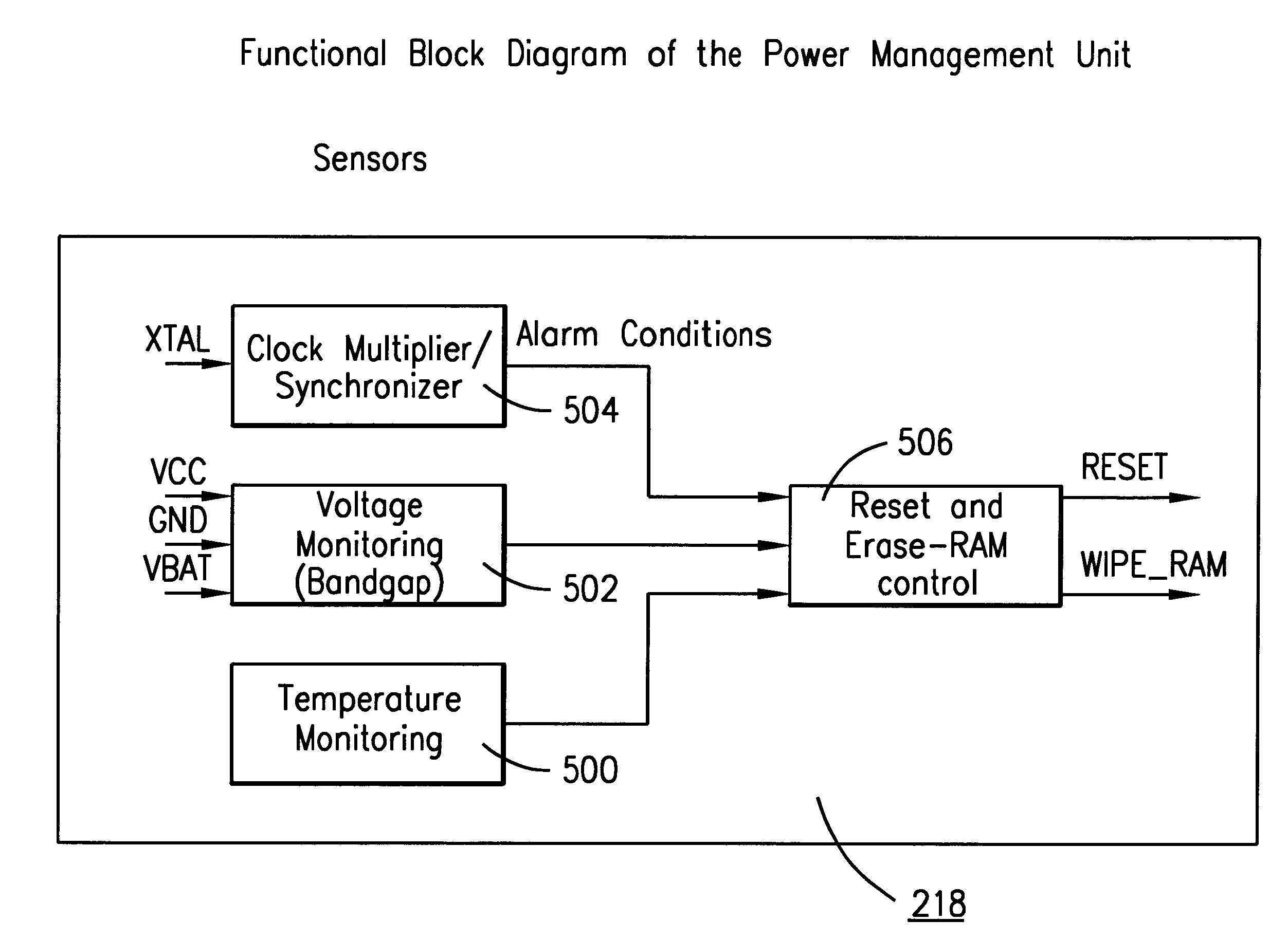

An integrated circuit, such as a microprocessor, which incorporates hardware mechanisms to prevent the circuitry from operating outside the proper bounds of design. The hardware circuitry prevents the microprocessor circuitry from being forced to operate at clock speeds that are greater than it is designed for, from operating at temperatures above or below that which it is designed for, and from being forced to operate at voltages that are above or below voltages that the microprocessor is designed to operate at.

Owner:MAXIM INTEGRATED PROD INC

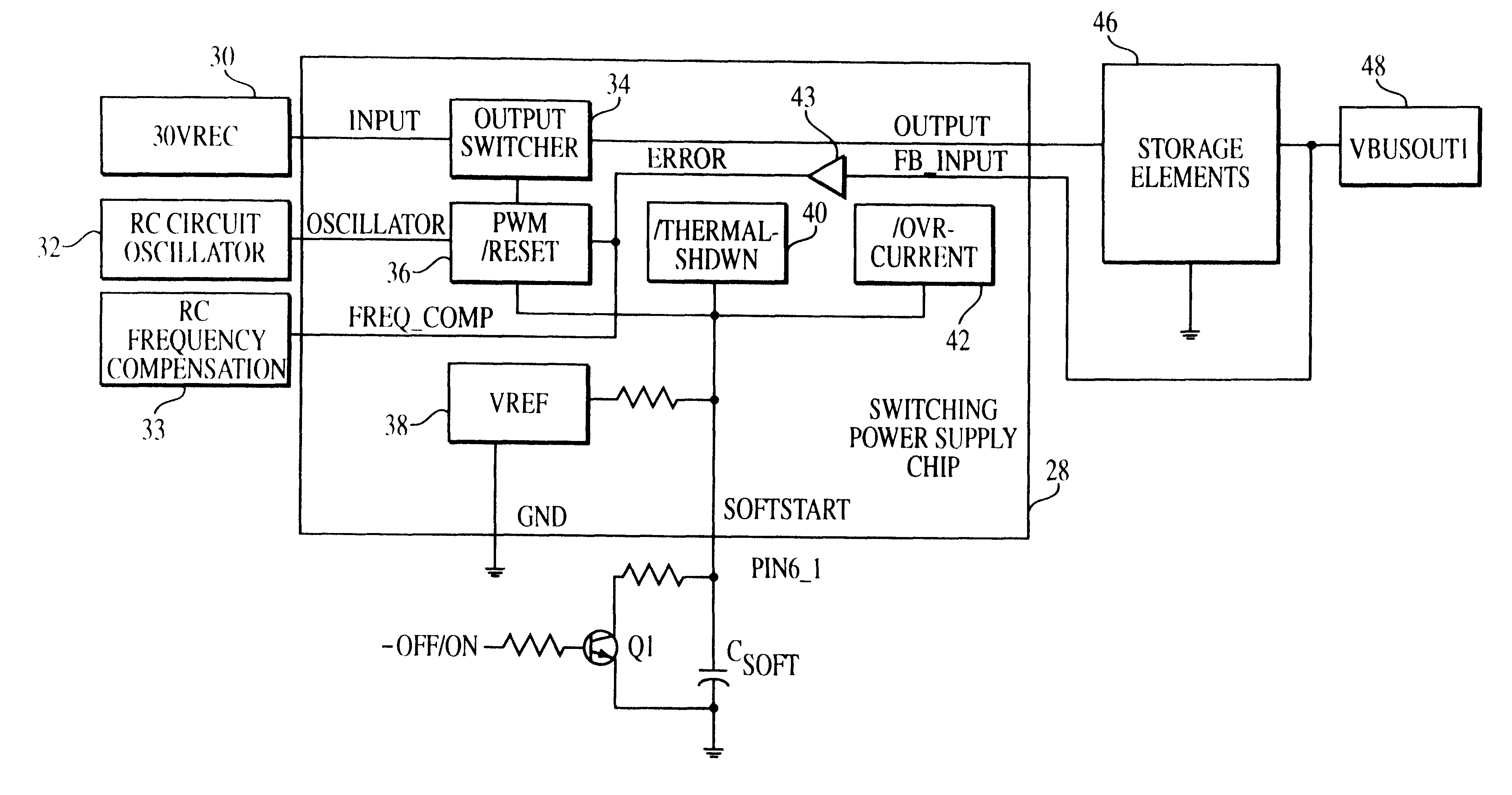

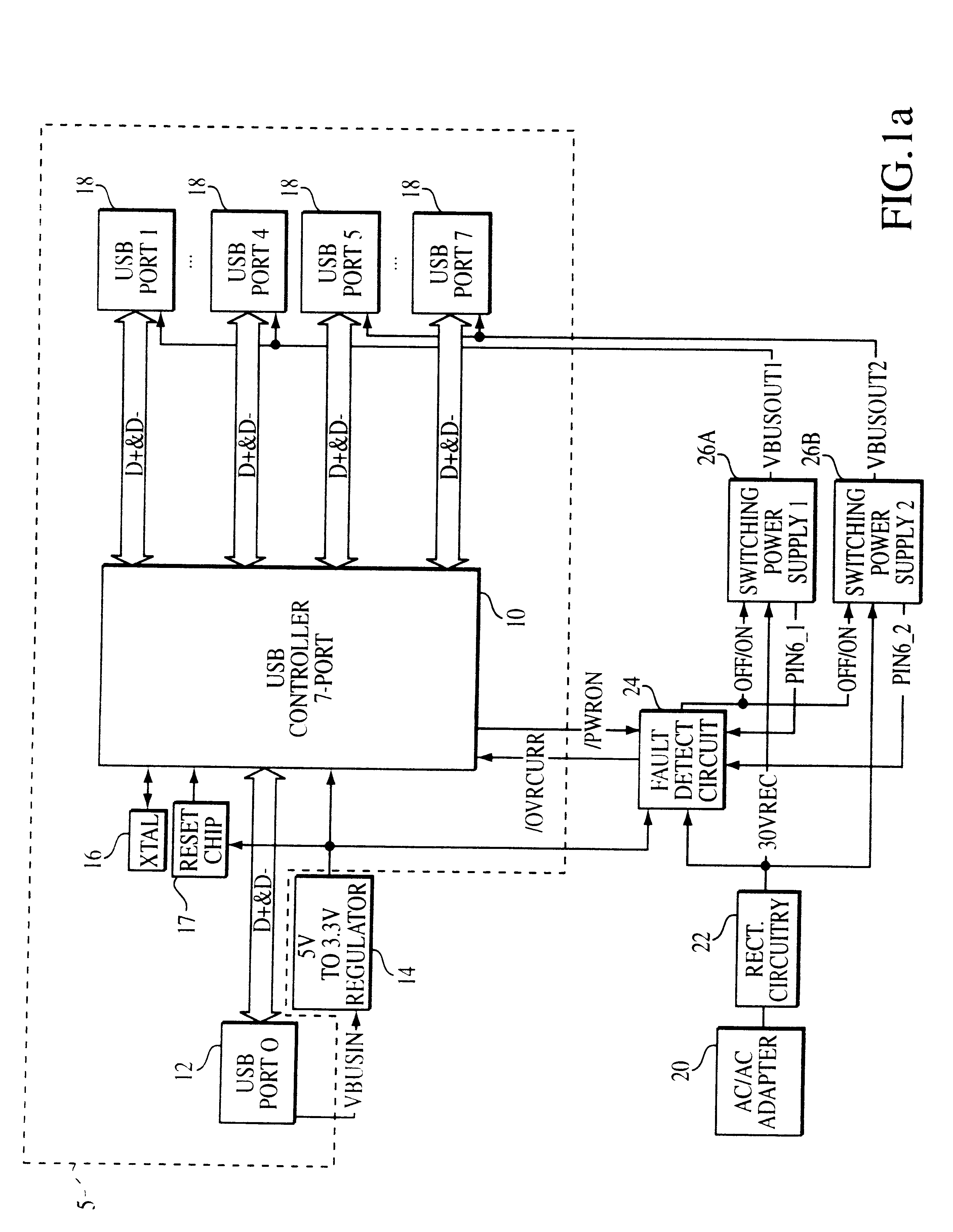

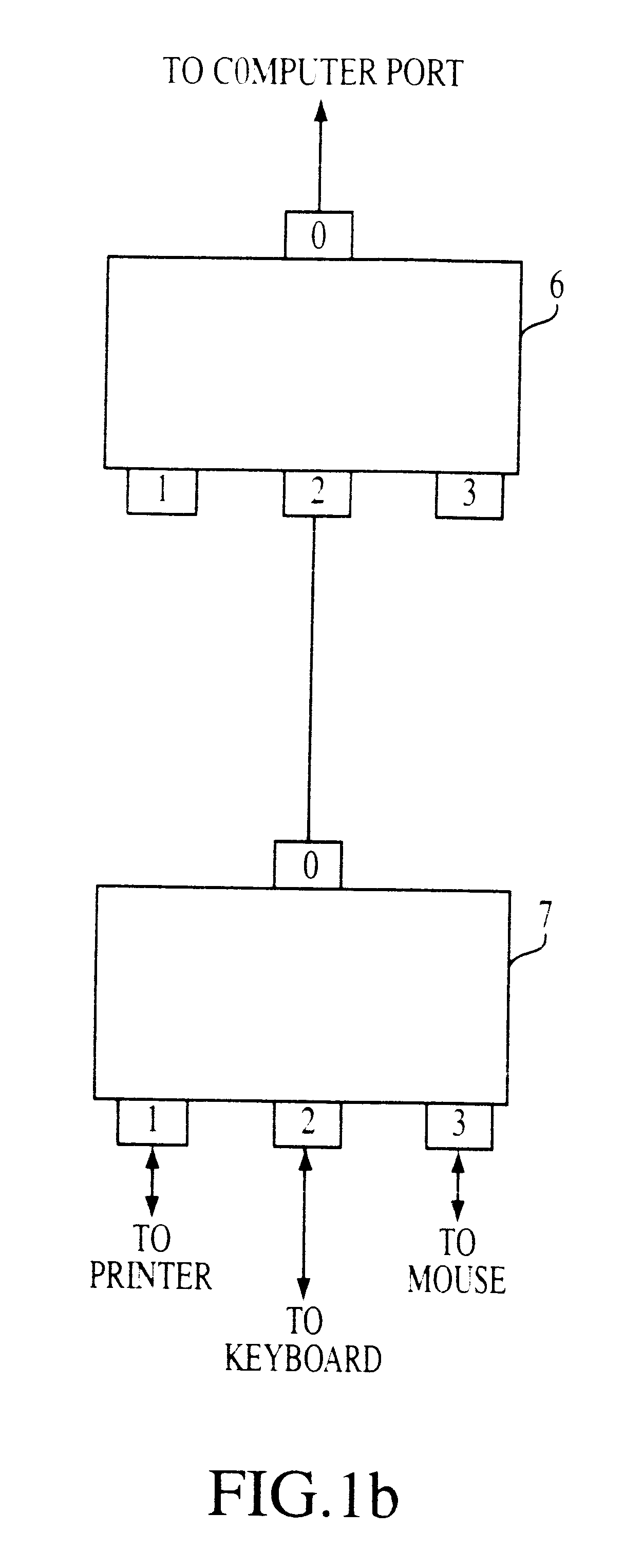

Fault detection on dual supply system for a universal serial bus system

InactiveUS6170062B1Easy to manufactureVolume/mass flow measurementMarginal checkingElectric power systemBus mastering

A method and apparatus for a dual power supply on a universal serial bus system using an overcurrent detect circuit. Dual power supplies in the universal serial bus system allows for greater flexibility of operation and is based on two separate power systems. The first power system is achieved using the power line on the bus connecting to the universal serial bus controller. The second power system is a separate power supply to power the downstream ports. Moreover, the universal serial bus system has an overcurrent and thermal error detect circuit based on the power system in order to achieve an efficient and cost effective method and apparatus in which to notify the universal serial bus controller of any error in the power system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

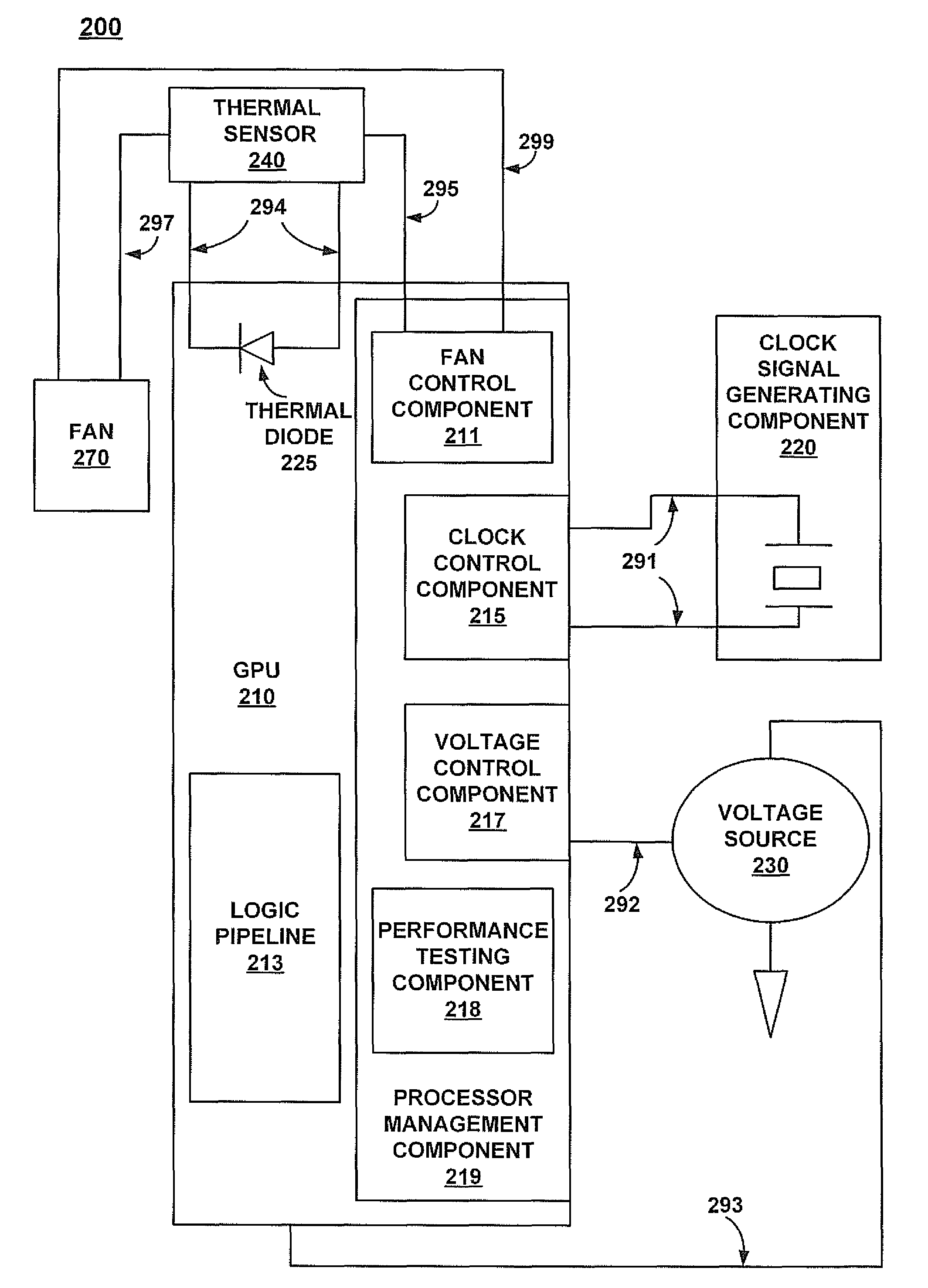

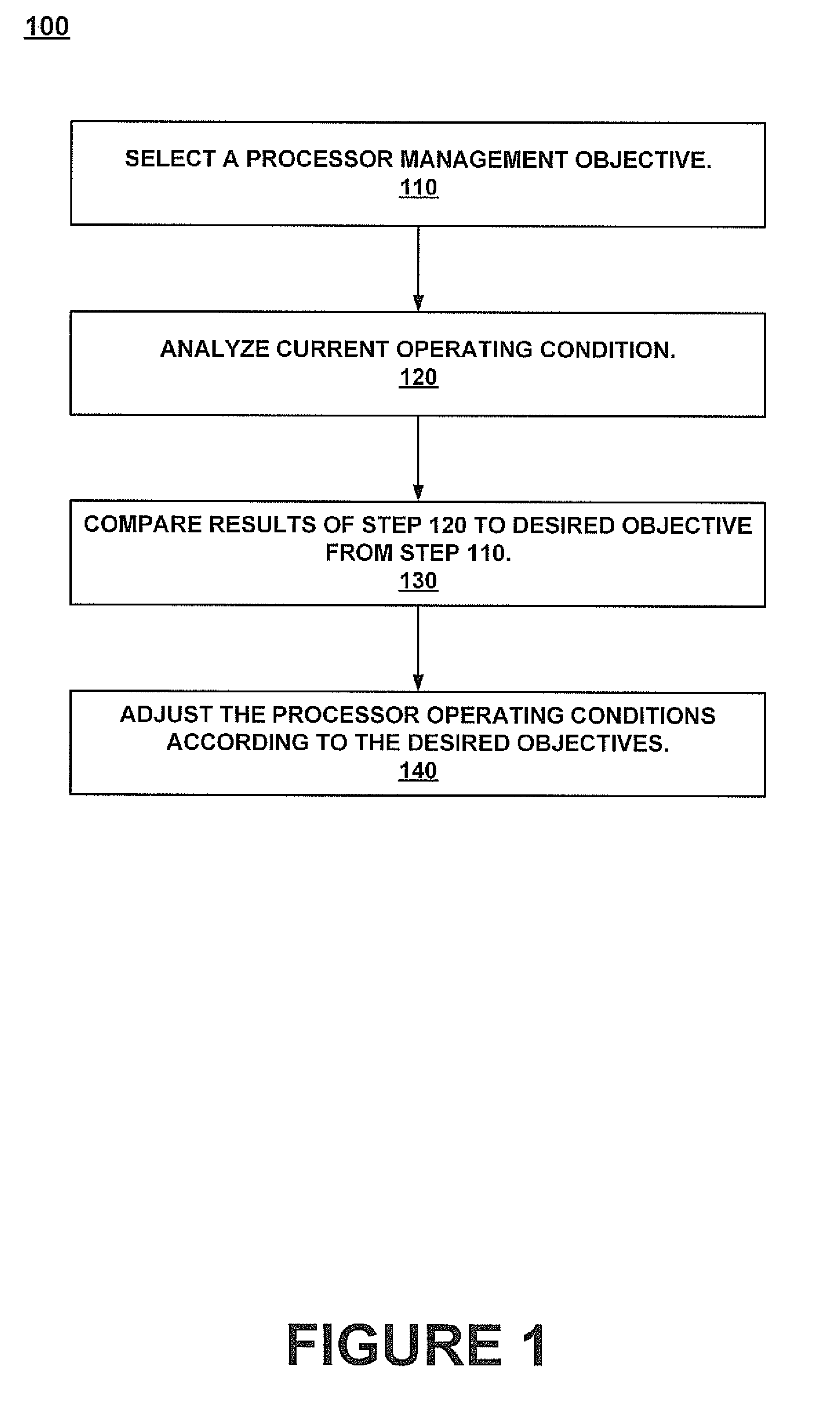

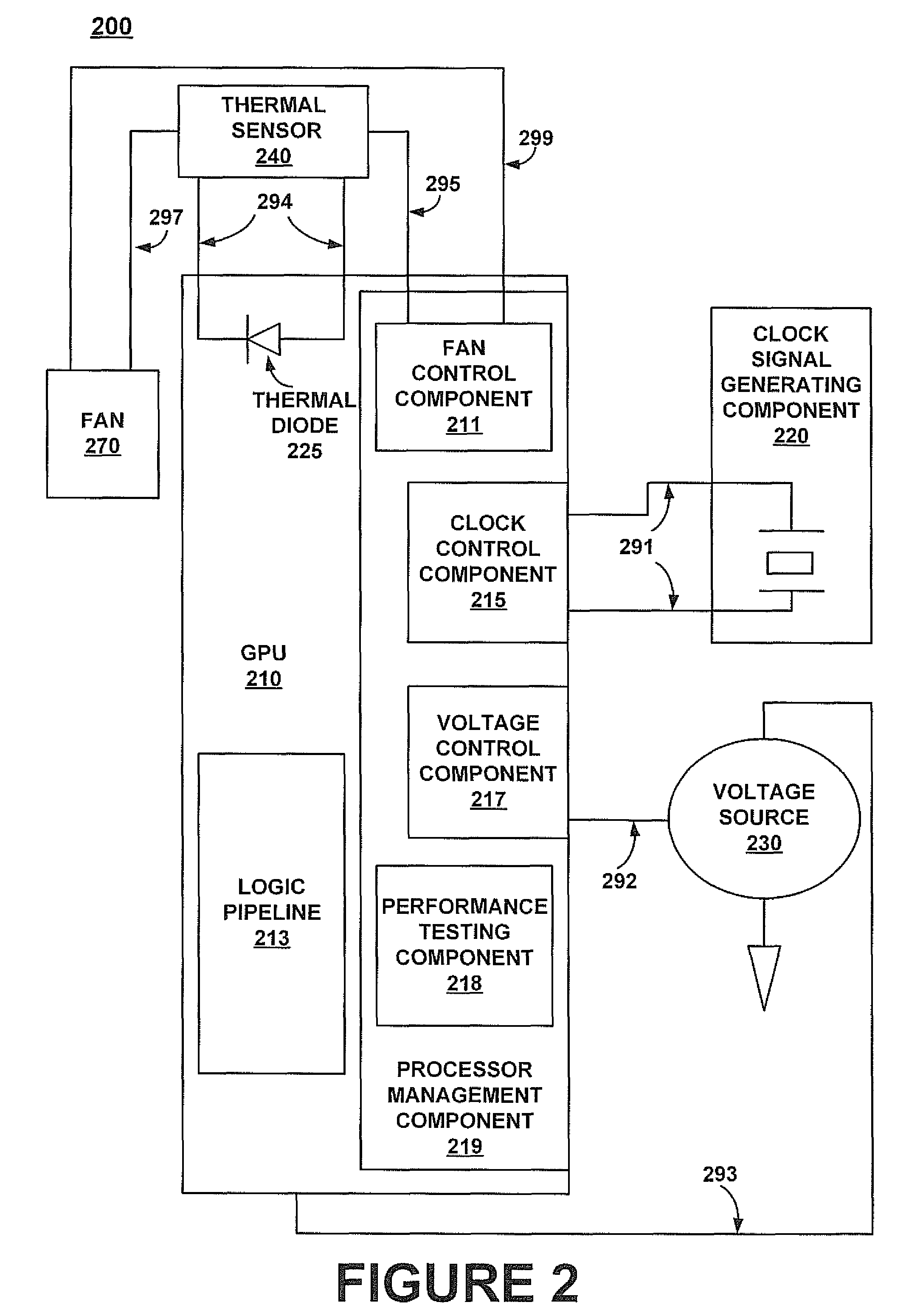

Processor temperature adjustment system and method

ActiveUS7886164B1Facilitates processor speed adjustmentEasy maintenanceEnergy efficient ICTVolume/mass flow measurementEngineeringThermal threshold

The present invention facilitates processor speed adjustments within acceptable temperature ranges. In one embodiment, a present invention system includes a temperature sensor that senses the temperature of the processor. When the temperature sensor senses the processor temperature approaching predetermined levels one or more adjustments are performed. For example, the adjustment can include automatically increasing or decreasing a voltage level in response to crossing a temperature threshold.

Owner:NVIDIA CORP

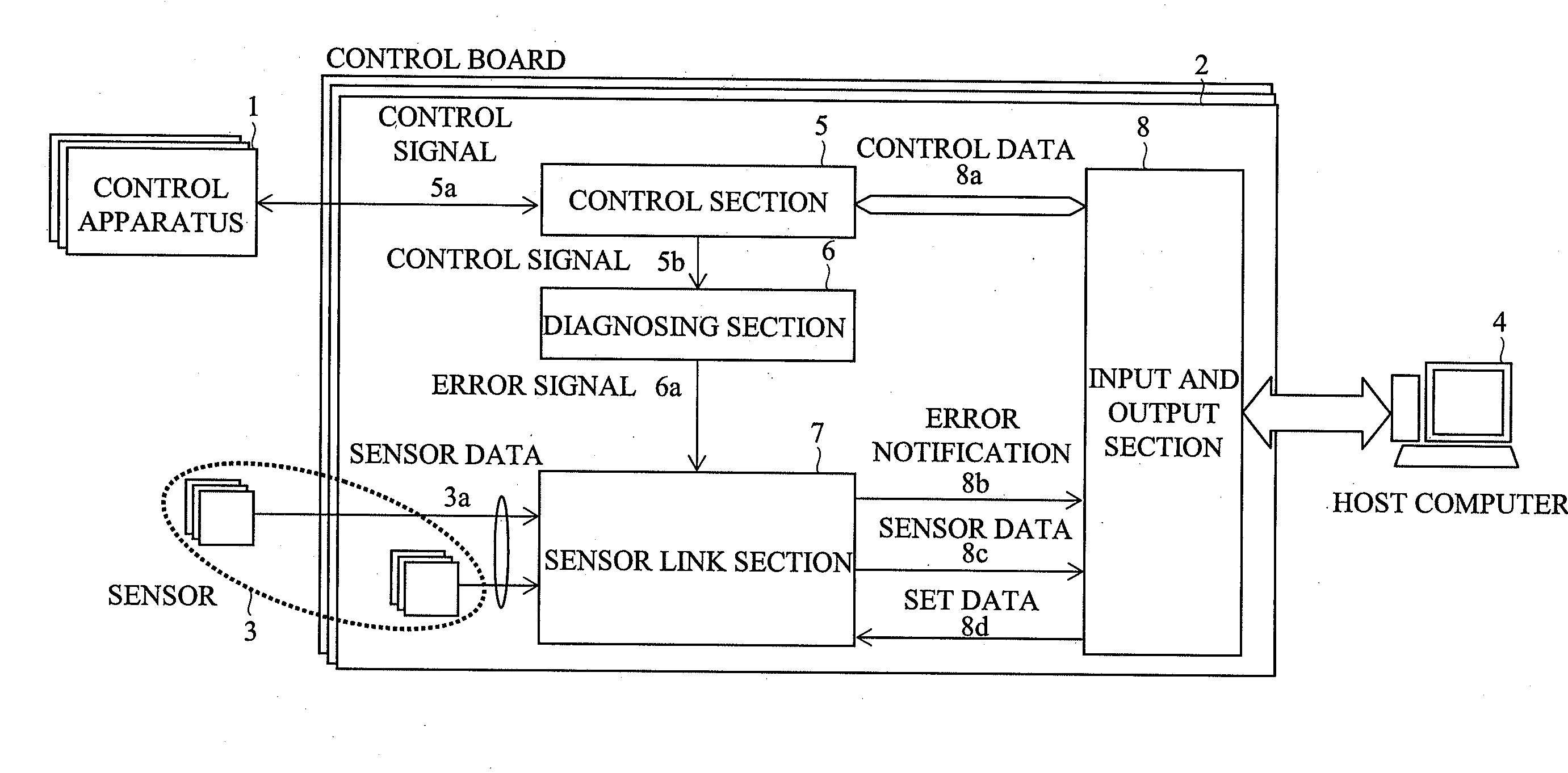

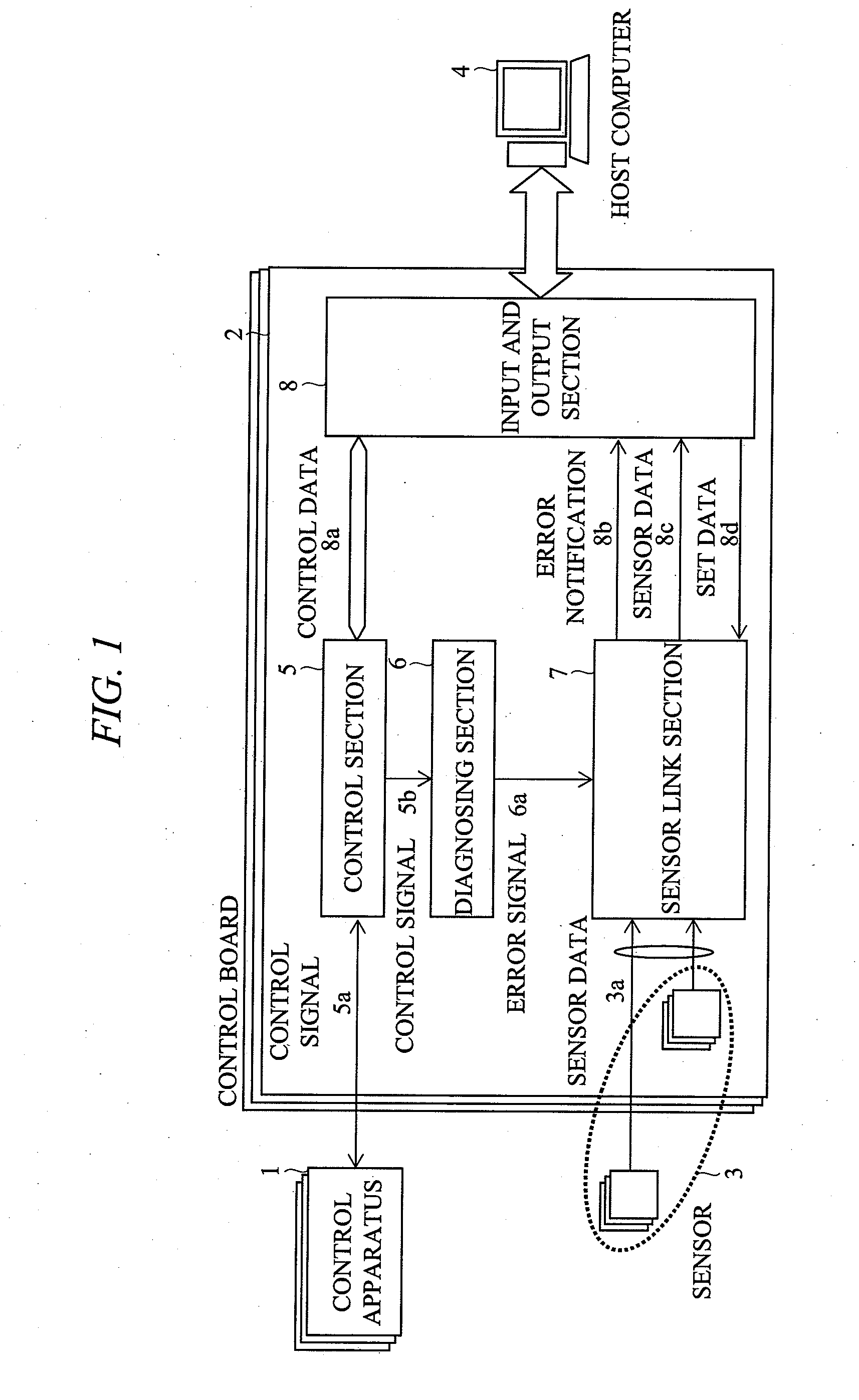

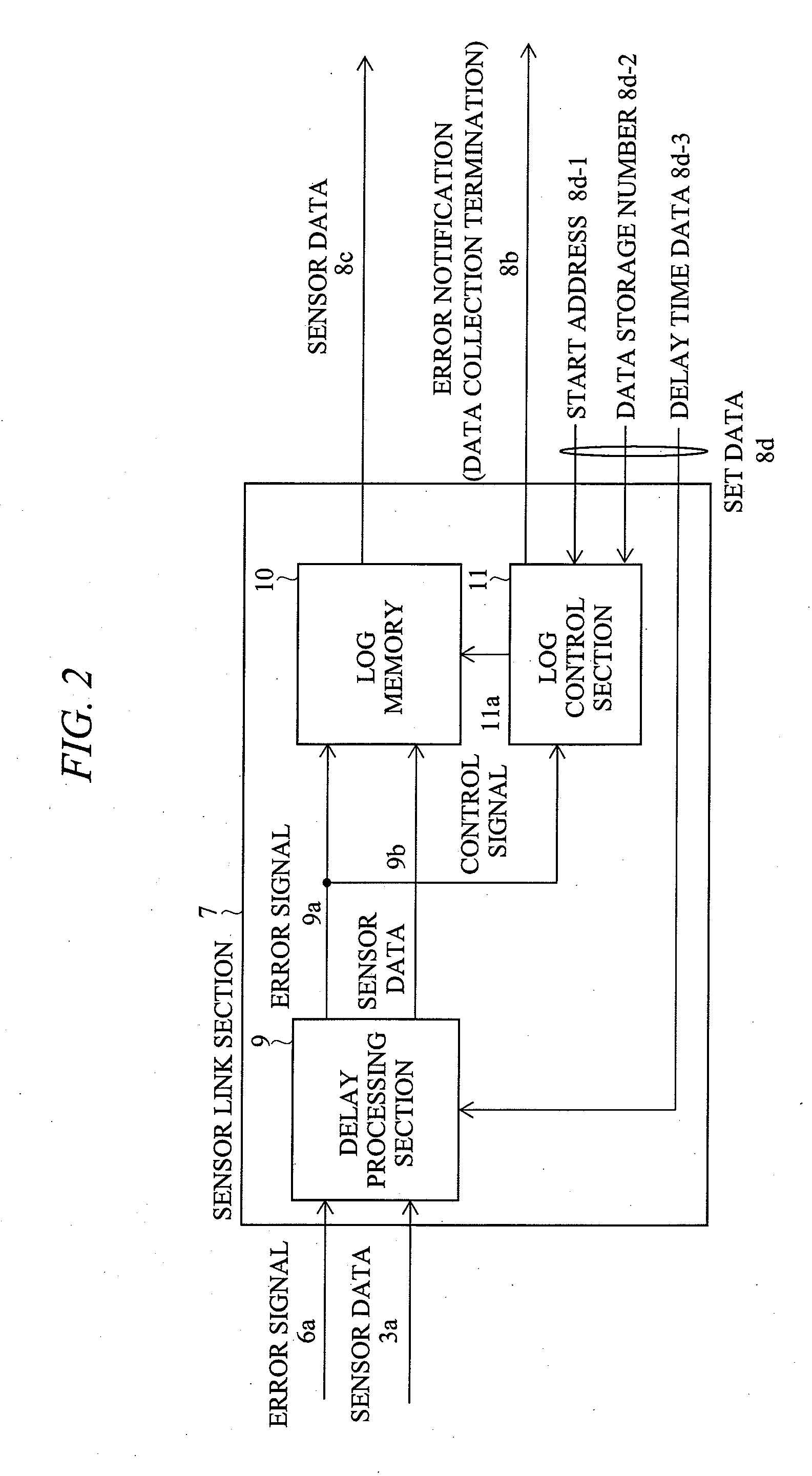

Apparatus diagnosing method, apparatus diagnosis module, and apparatus mounted with apparatus diagnosis module

InactiveUS20080244329A1Easy to specifySmall sizeMarginal checkingTesting/calibration of speed/acceleration/shock measurement devicesControl equipmentDiagnostic methods

An apparatus diagnosing method is a method in which, in an apparatus including a control apparatus and a control board for controlling the control apparatus, on the controlling board, an error occurrence at the control apparatus and the control board is detected, an error signal is outputted, sensor data outputted from a sensor acquiring data about operation environments of the control apparatus and the control board is collected, and an environmental factor causing a failure or an error of the control apparatus and the control board is specified based upon the error signal and the sensor data, and the sensor data is collected in association with the error signal when the sensor data is collected.

Owner:HITACHI LTD

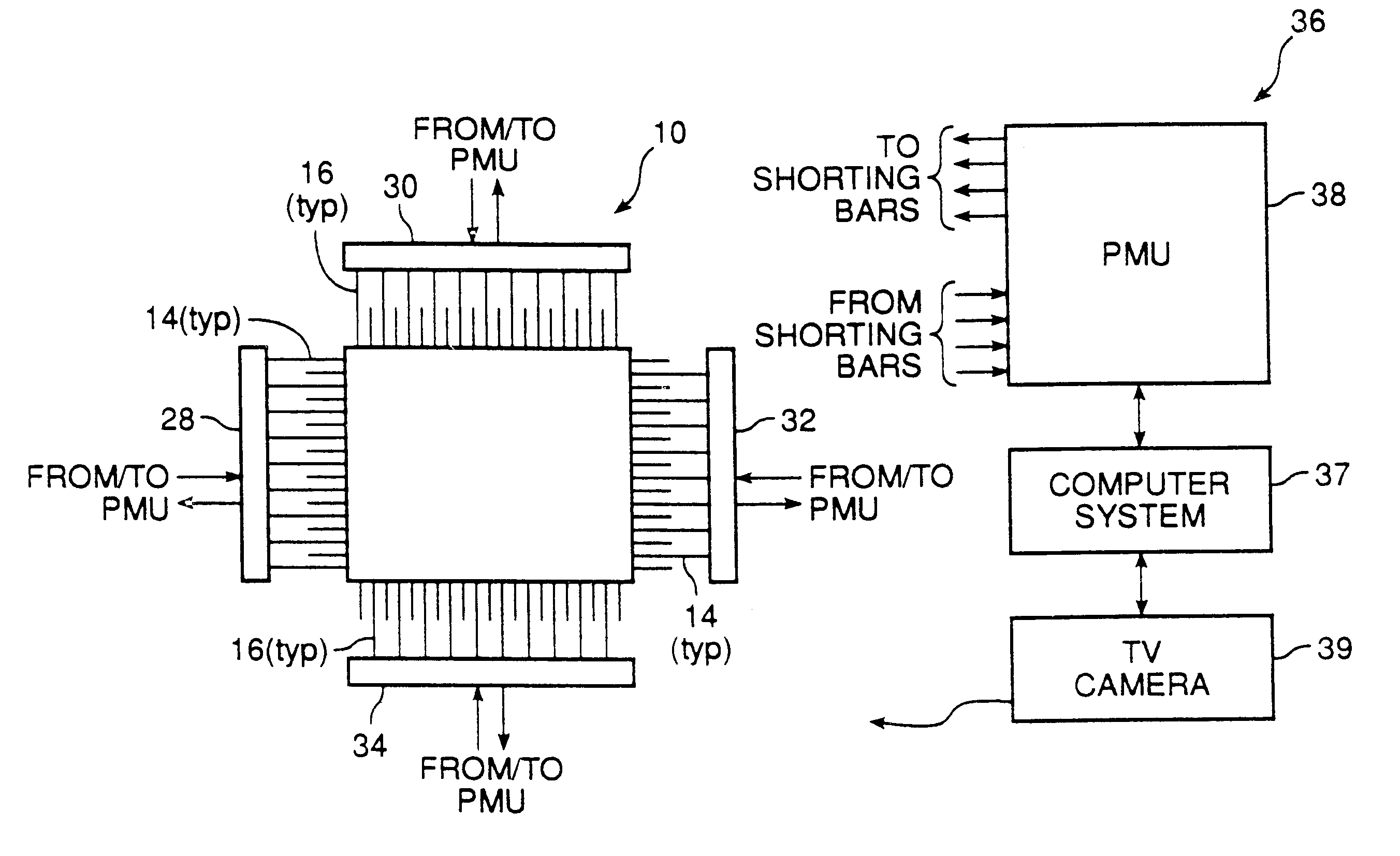

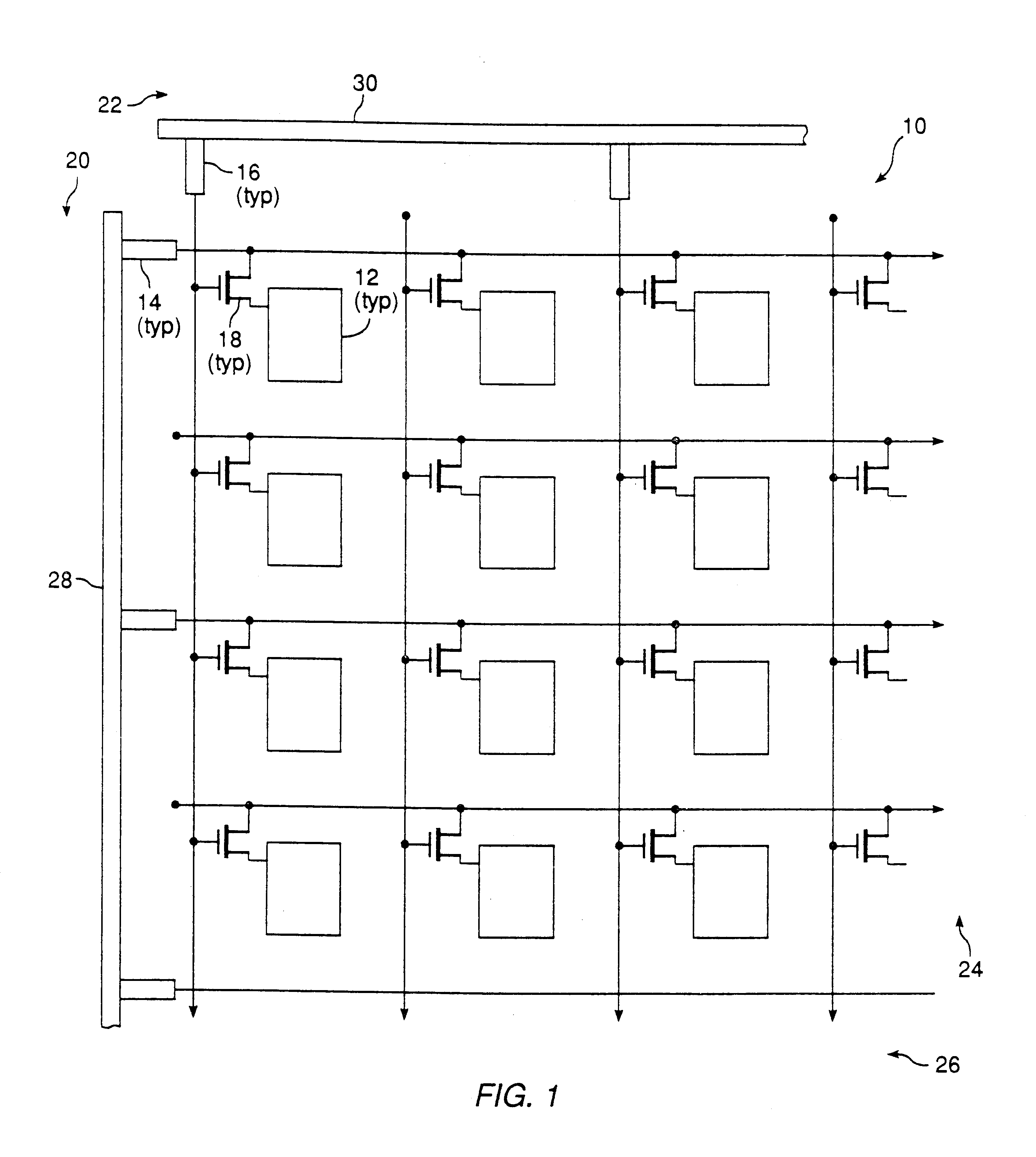

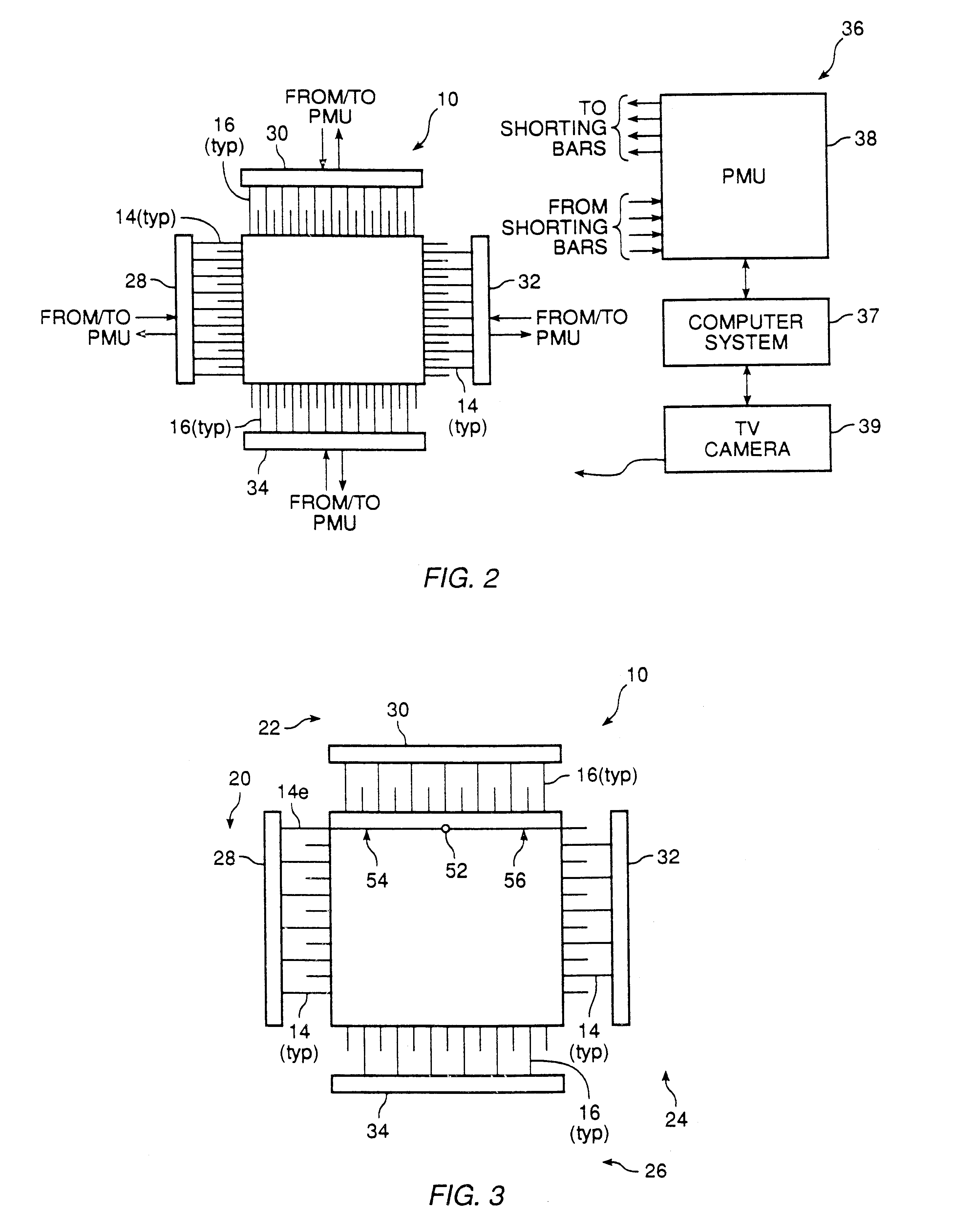

Method and apparatus for testing LCD panel array prior to shorting bar removal

Final testing of an LCD panel or the like is performed after preliminary testing for short circuit defects. During final testing, the panel is exposed to signals at the shorting bars and the resulting display pattern is imaged. The resulting image data then is processed at a computer system to determine whether the resulting display pattern differs from an expected display pattern. If differences are present then an open circuit or pixel defect is present. The applied test signals and the pattern or differences determine the type of defect present. For an open circuit defect along a gate line, a partial row (column) of the resulting display pattern does not activate. For an open circuit along a drive line, a partial column (row) of the resulting display does not activate. Pixel shorts are identified by applying test signals to the shorting bars during a first test cycle, then imaging the display during a second test cycle after at least one of the test signals is removed. Pixels which remain active that should be inactive have short circuit defects.

Owner:PHOTON DYNAMICS

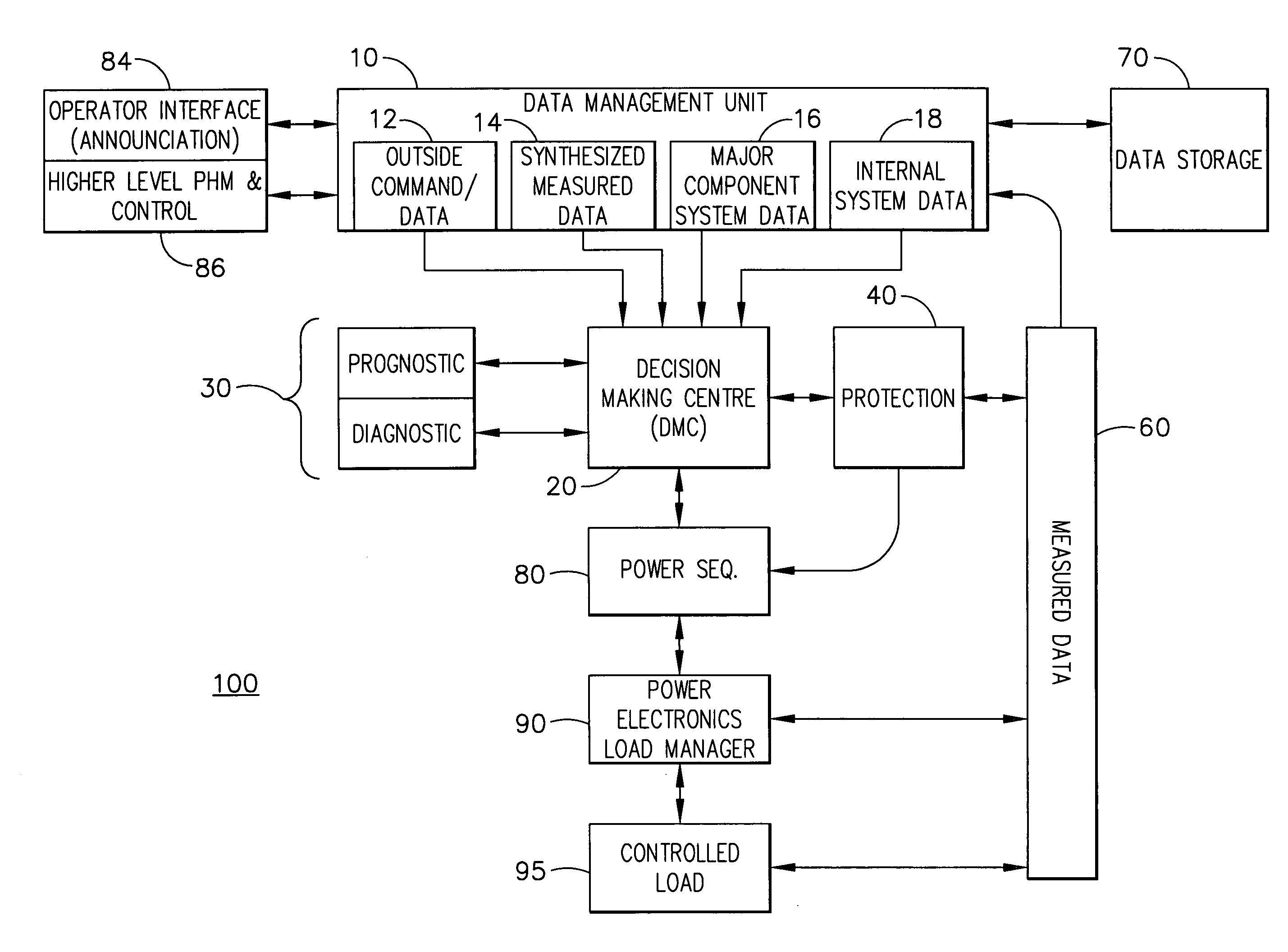

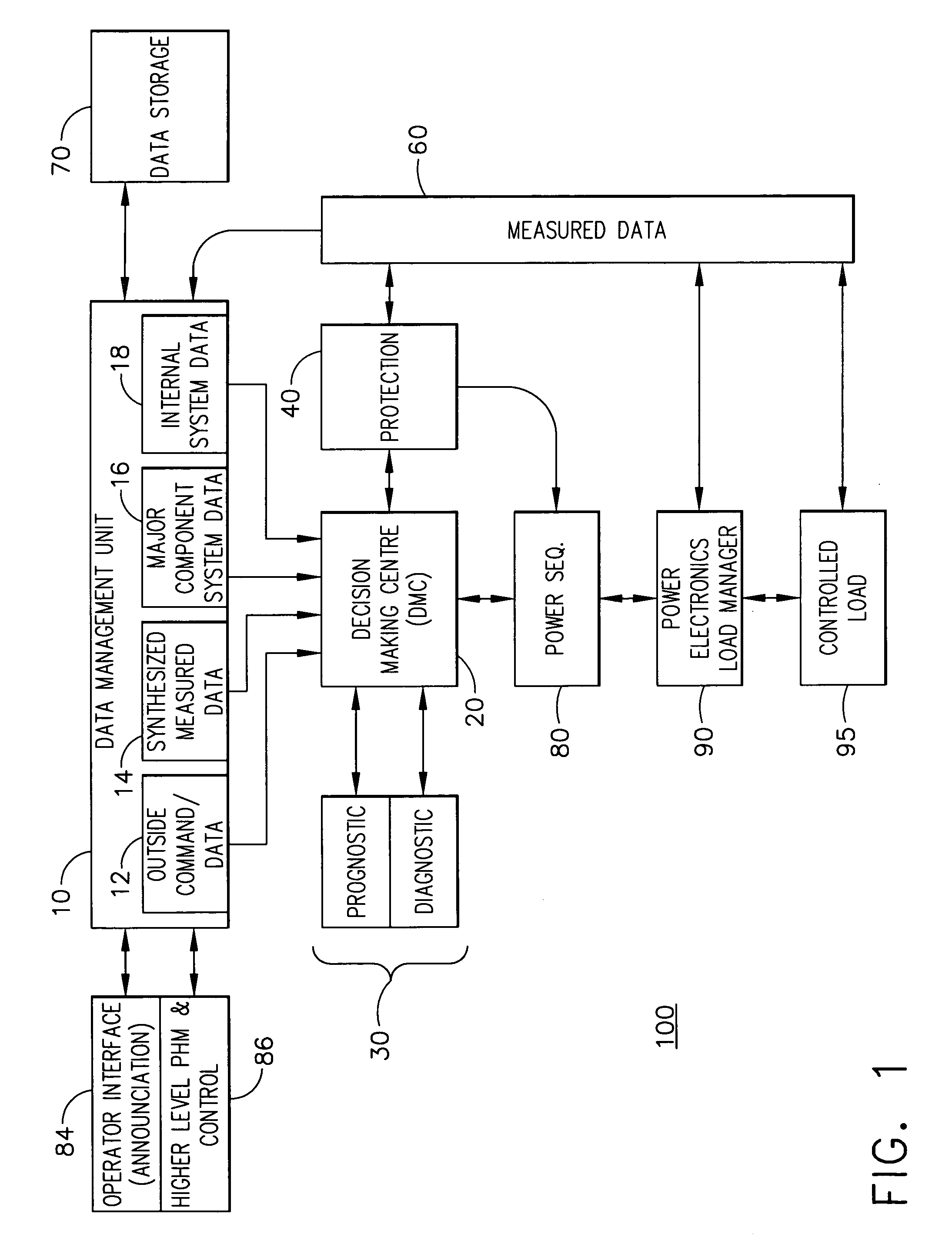

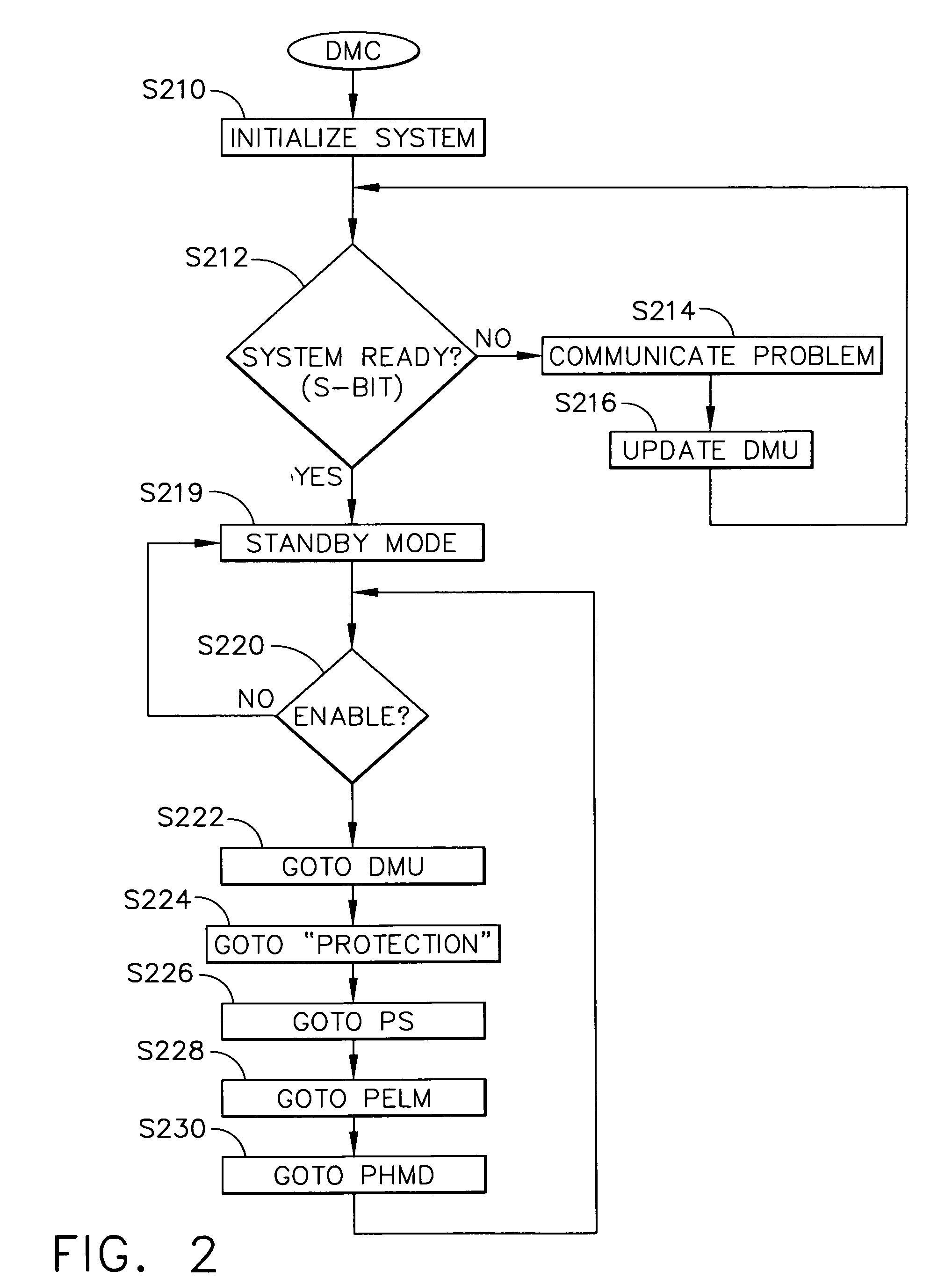

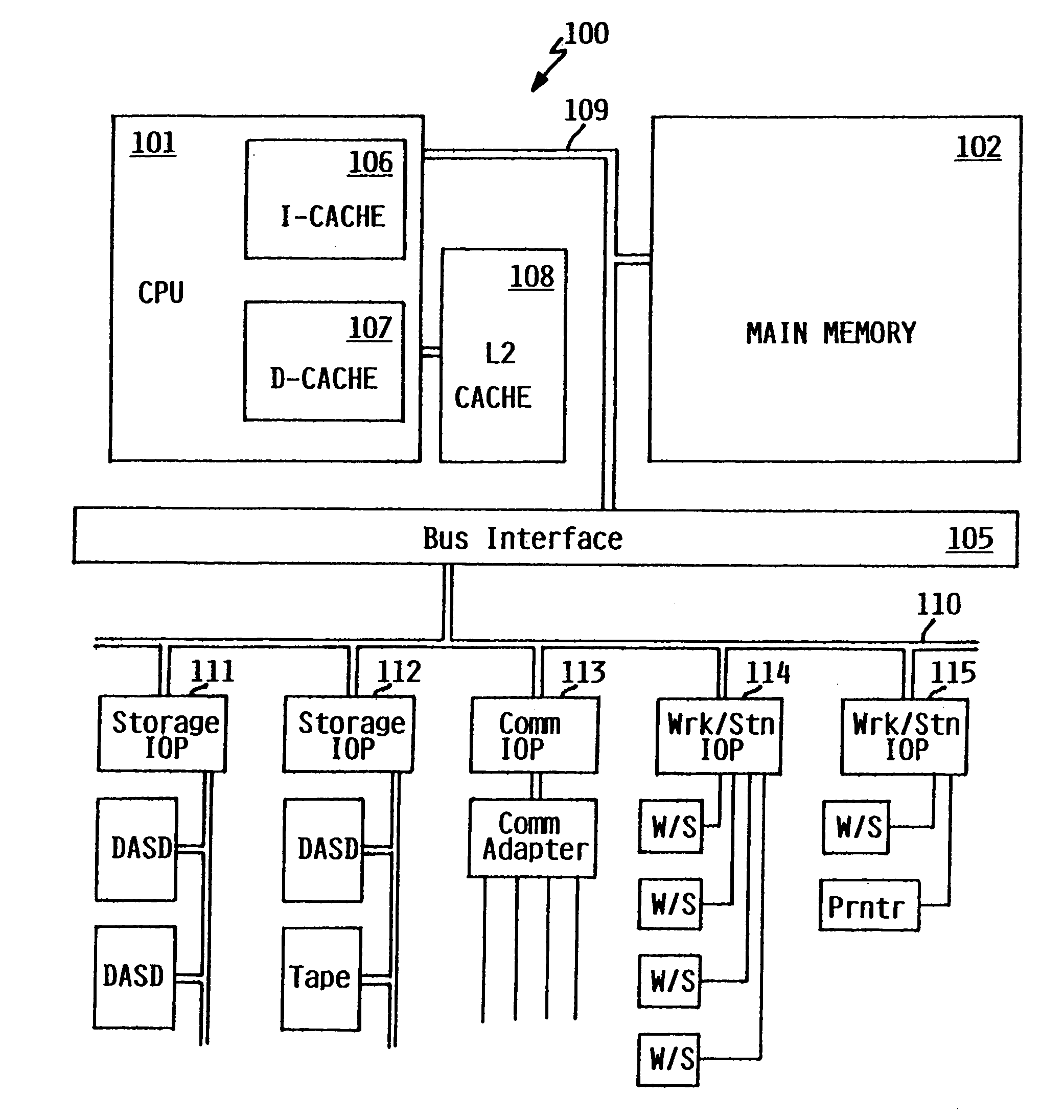

Control sequencing and prognostics health monitoring for digital power conversion and load management

InactiveUS7308614B2Vehicle testingRegistering/indicating working of vehiclesOperation modeSafe operation

An electronics-based system (100) for power conversion and load management provides control sequencing and prognostic health monitoring and diagnostics for fault tolerant operation of the system. The system (100) includes a prognostic health monitoring and diagnostic unit (30) for identifying present out-of-range conditions, overload conditions, and trending violations, for components of the system and a decision making unit (20), which controls transitions between a plurality of operating modes to ensure fail-safe operation without unnecessary tripping, cold-starts or system resets upon the occurrence of certain fault conditions.

Owner:HONEYWELL INT INC

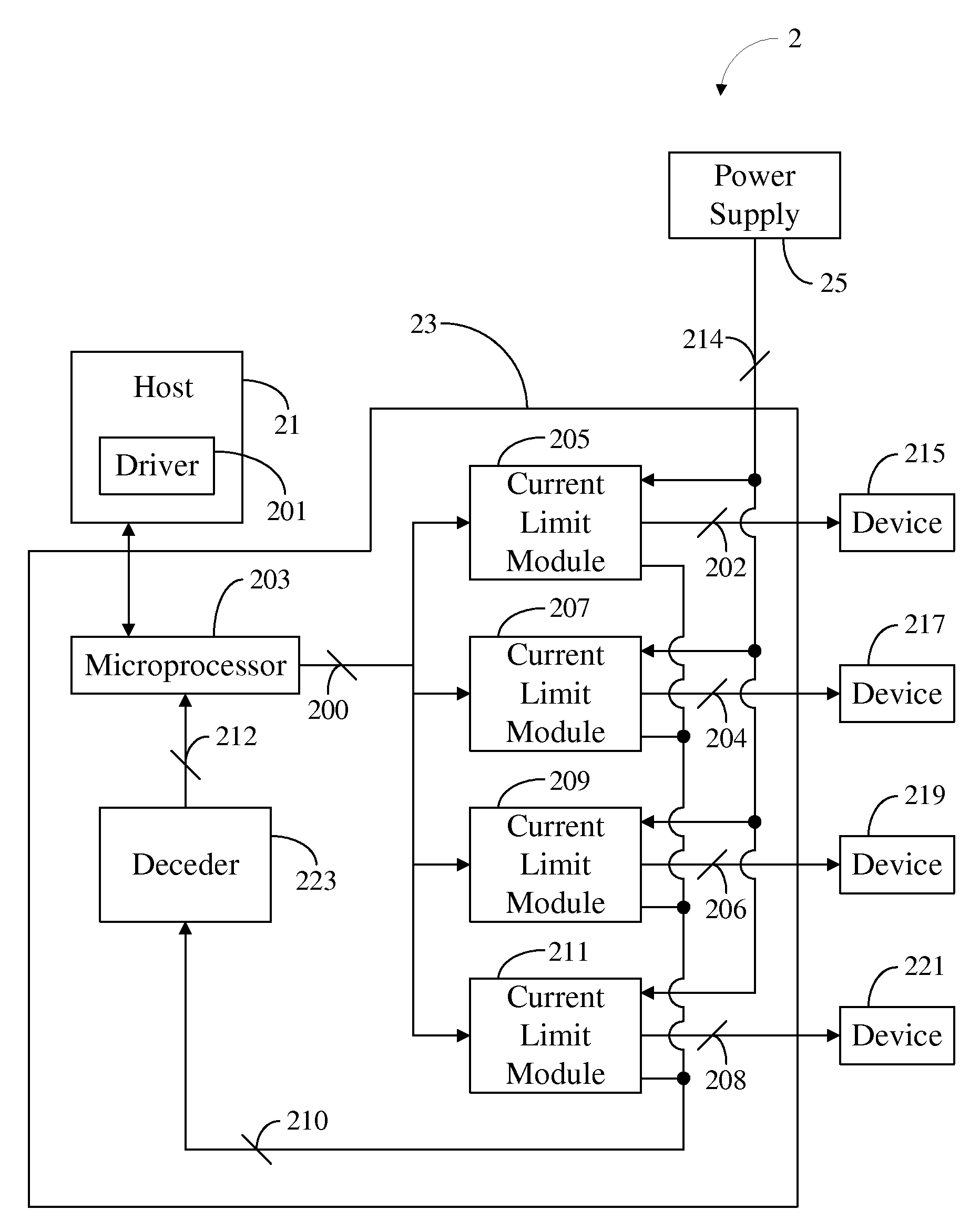

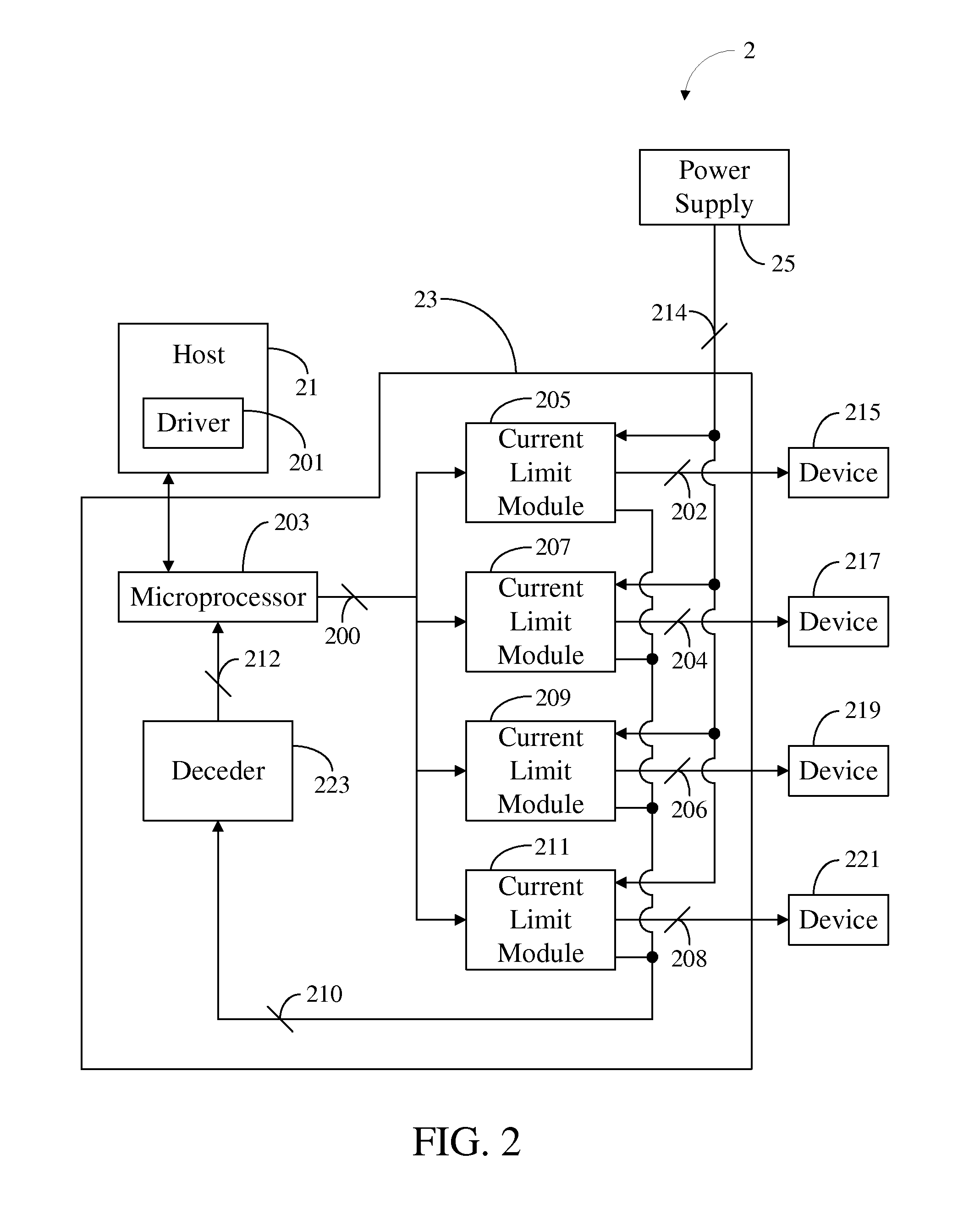

Testing Apparatus, System, and Method for Testing at Least One Device with a Connection Interface

A system, a testing apparatus, and a method for testing at least one device with a connection interface are provided. The system comprises a host, a testing apparatus, and a power supply. The testing apparatus further comprises a microprocessor and at least one current limit module. The host sending a test signal. The power supply provides a voltage to the testing apparatus. The at least one current limit module of the testing apparatus, which is electrically connected to the microprocessor, the at least one device, and the power supply, provides the voltage to the at least one device. When the current passing through the at least one device is greater than the predetermined value, the at least one current limit module of the testing apparatus stops providing the voltage to the at least one device and sends an over current signal to the host via the microprocessor.

Owner:SILICON MOTION INC (TW)

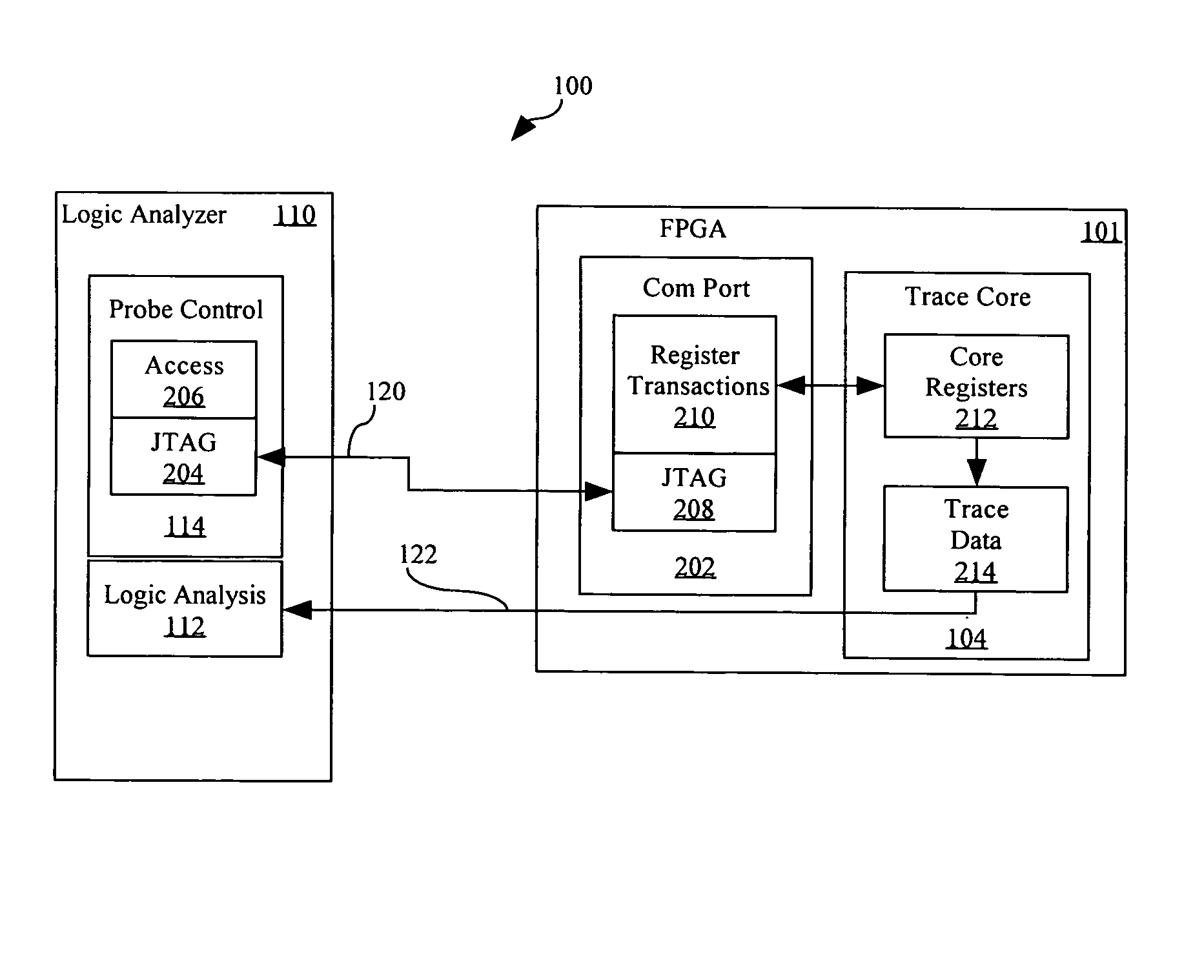

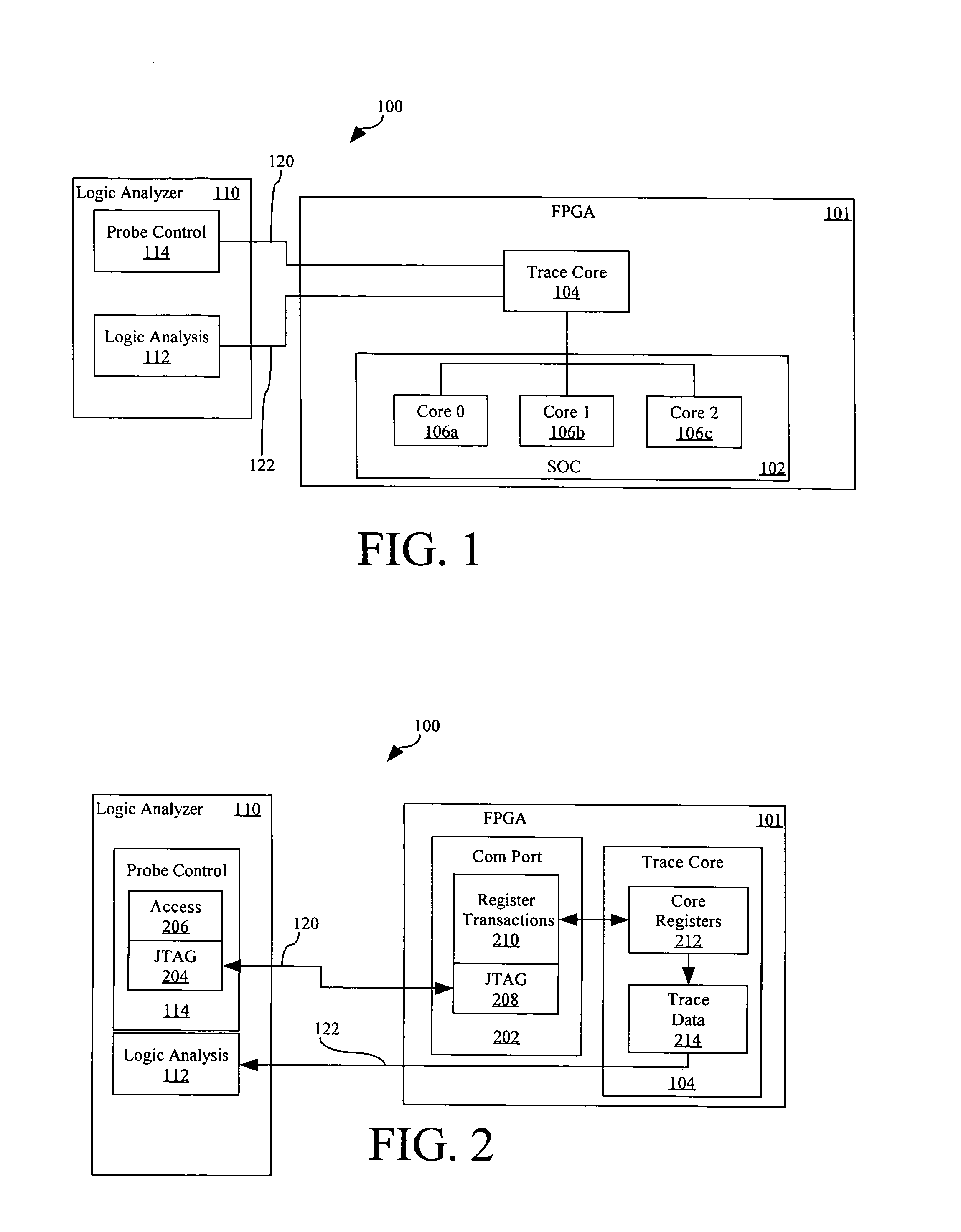

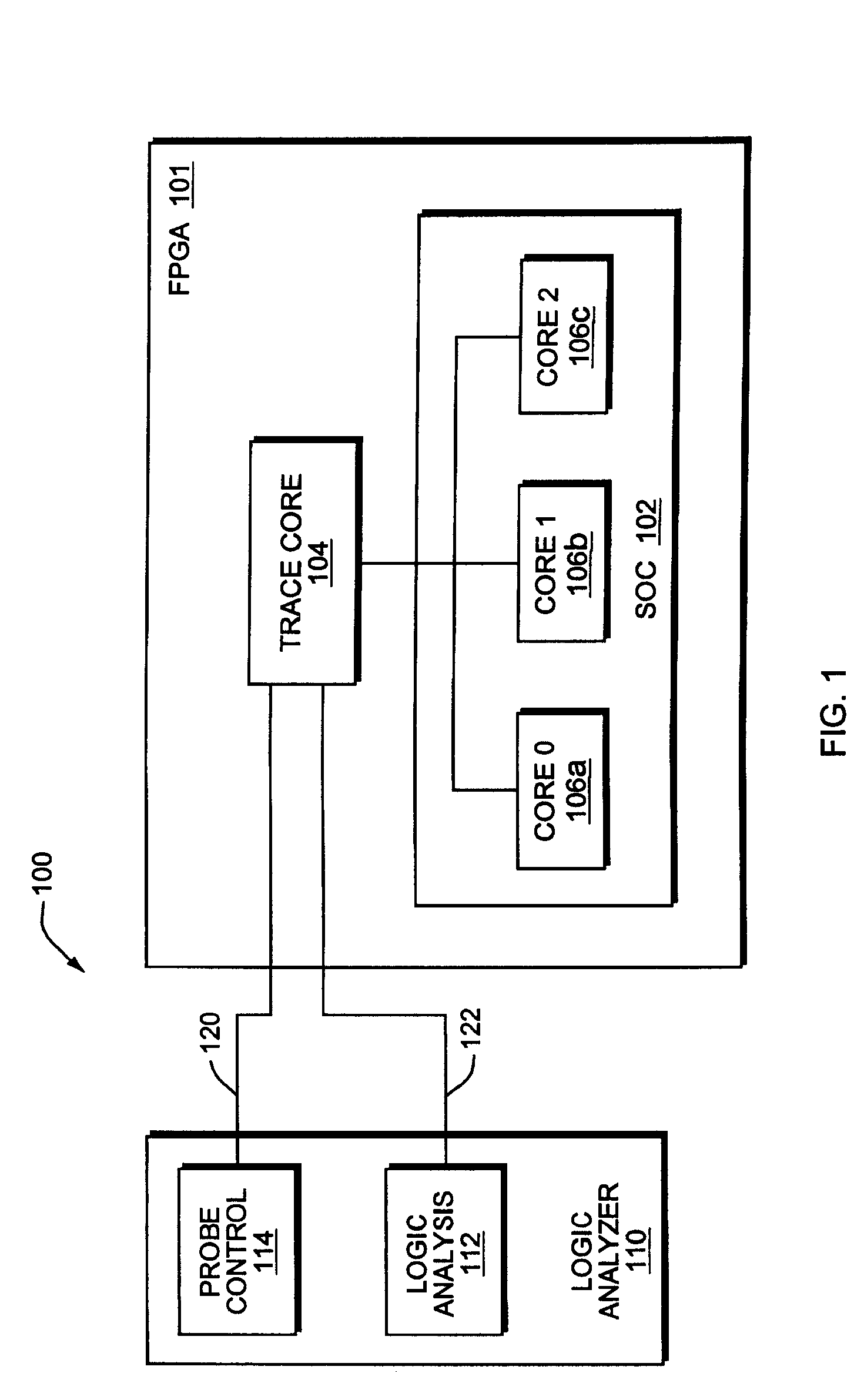

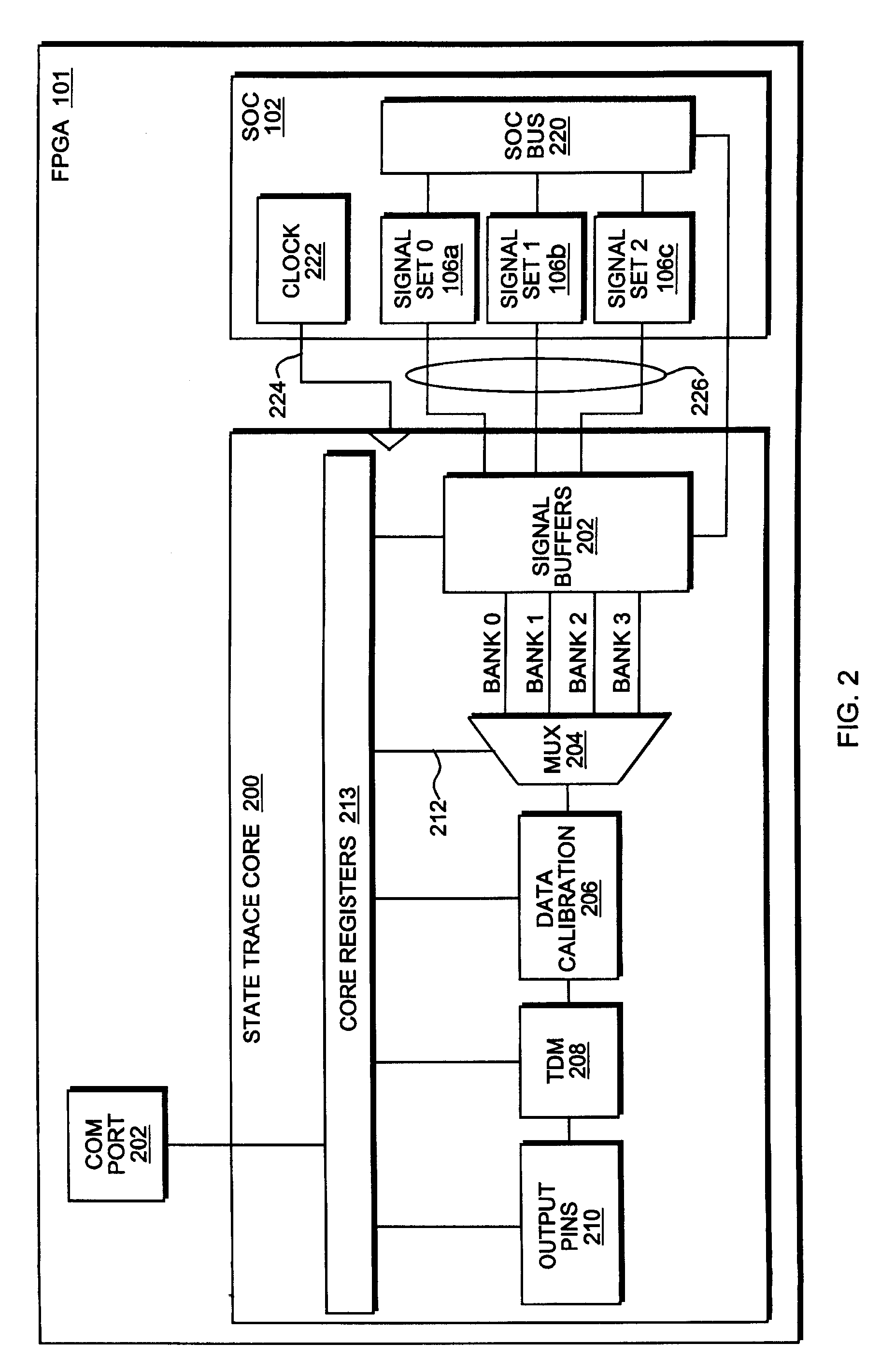

Apparatus and method for dynamic in-circuit probing of field programmable gate arrays

A dynamic probe system for probing a FPGA with at least one core. A trace core is added to the FPGA, the trace core in communication with a plurality of signal banks, each signal bank comprising a plurality of signals in the at least one core. A logic analyzer, in communication with the trace core and selecting the bank of signal to be sent from the trace core to the logic analyzer.

Owner:KEYSIGHT TECH

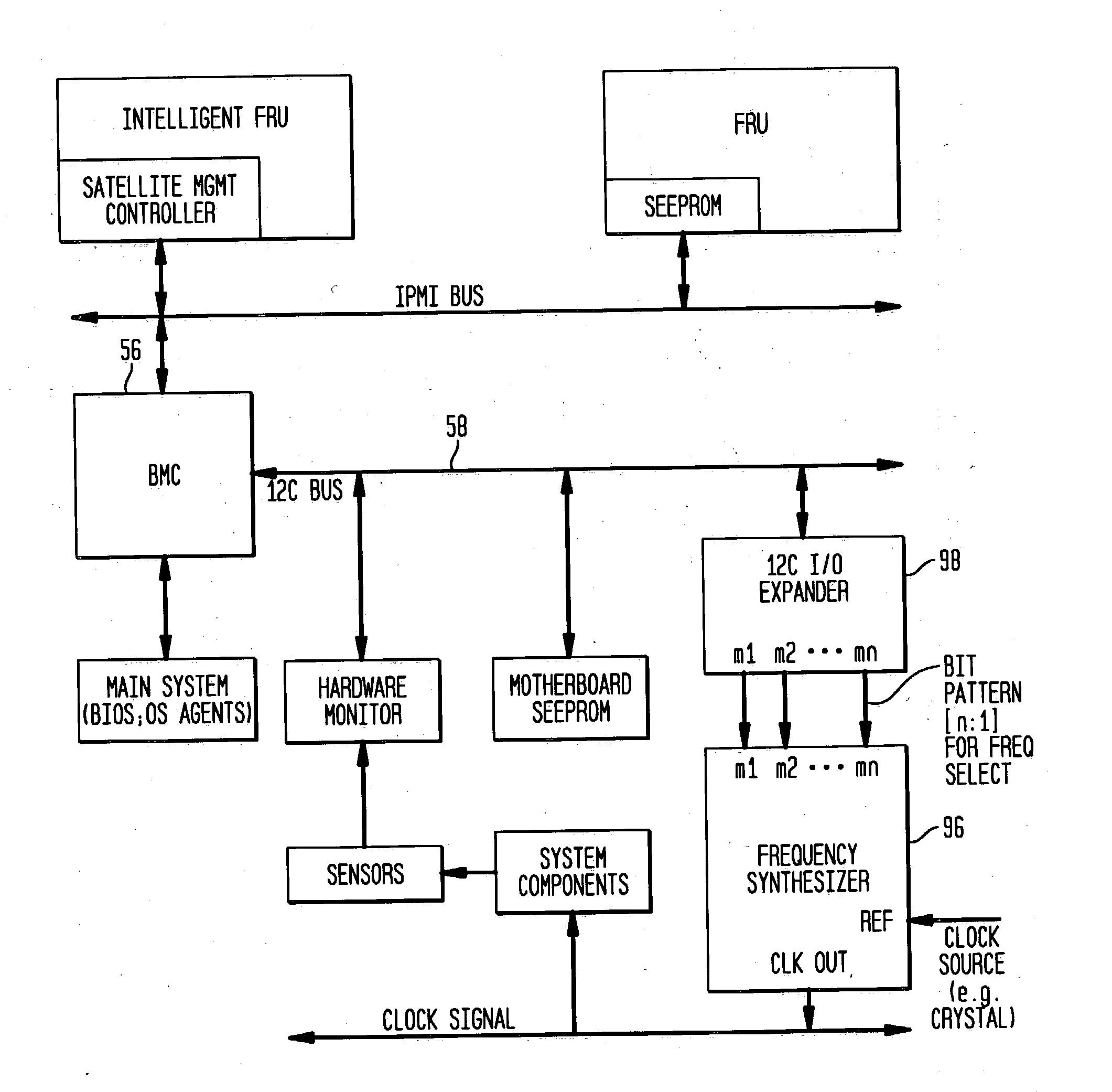

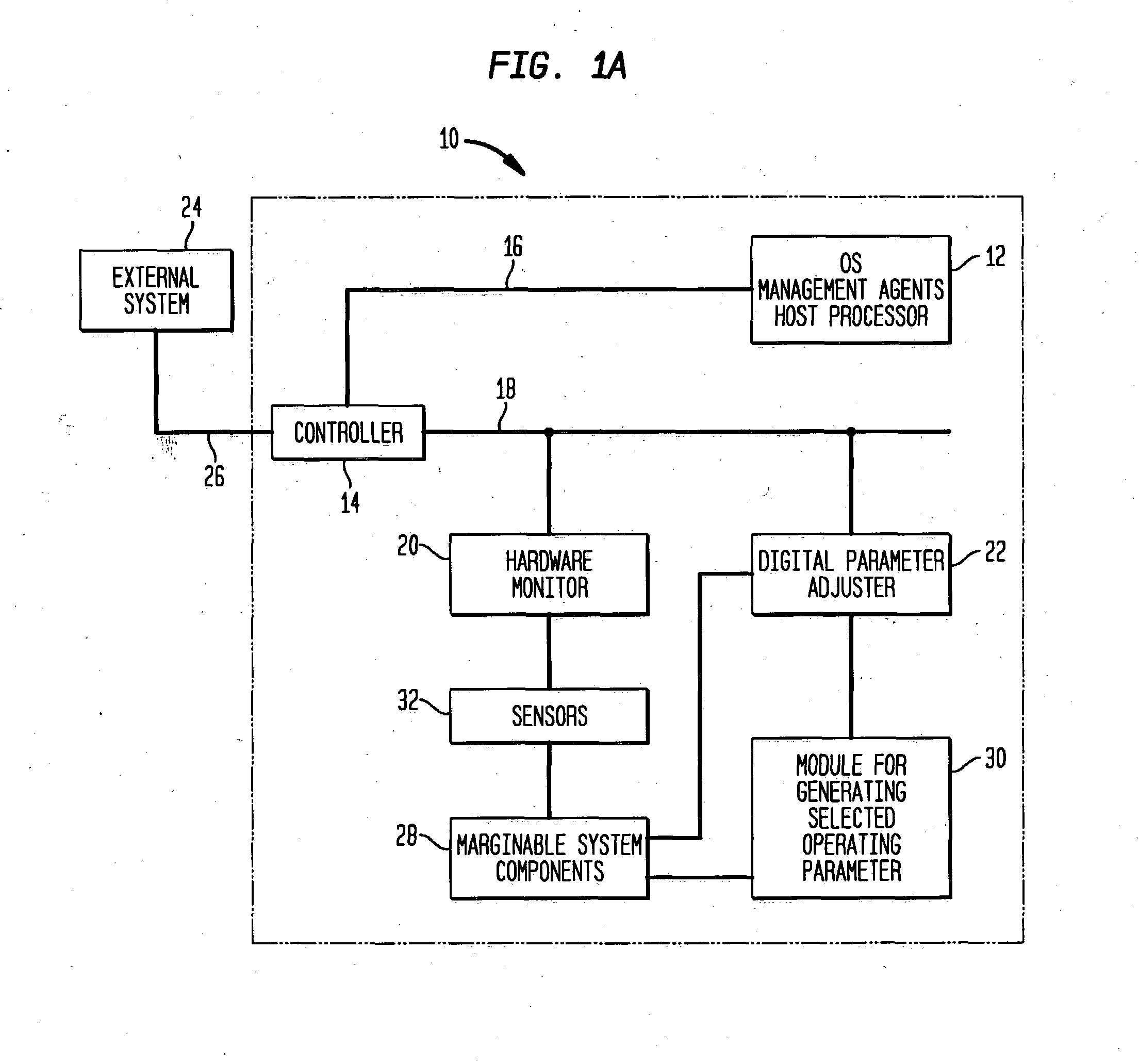

Use of I2C programmable clock generator to enable frequency variation under BMC control

InactiveUS20050021260A1Electronic circuit testingResistance/reactance/impedenceClock rateFrequency synthesizer

The present invention provides systems and methods for performing frequency margin testing of a computer system, such as a server. A system of the invention can include a controller, e.g., a BMC, internal to the computer system and a digital frequency synthesizer that can communicate with the controller and can apply clock frequency to marginable components of the computer system. In response to commands from the controller, the synthesizer generates one or more test frequencies that are applied to one or more of the marginable components. The response of the system to each of the test frequencies is then monitored.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

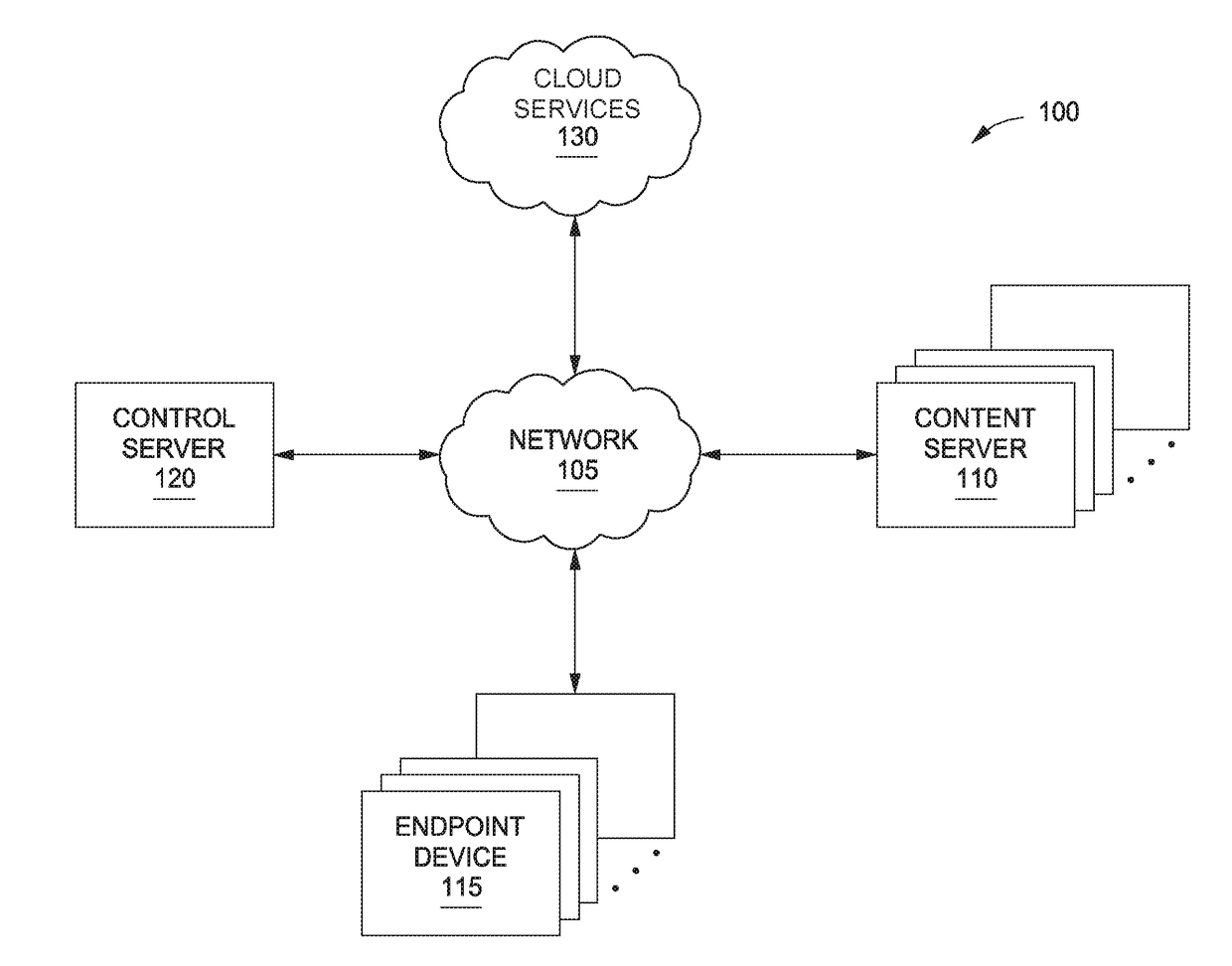

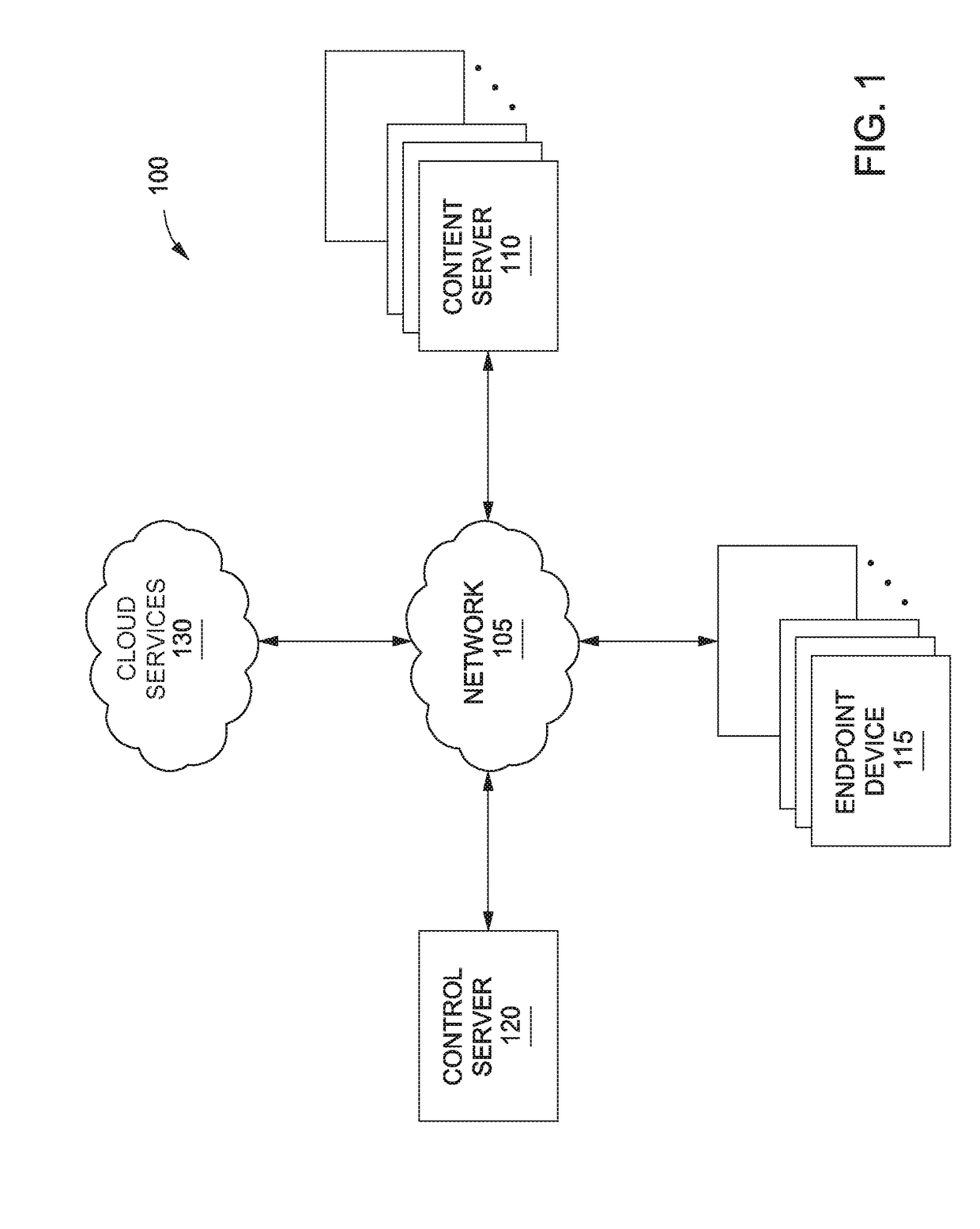

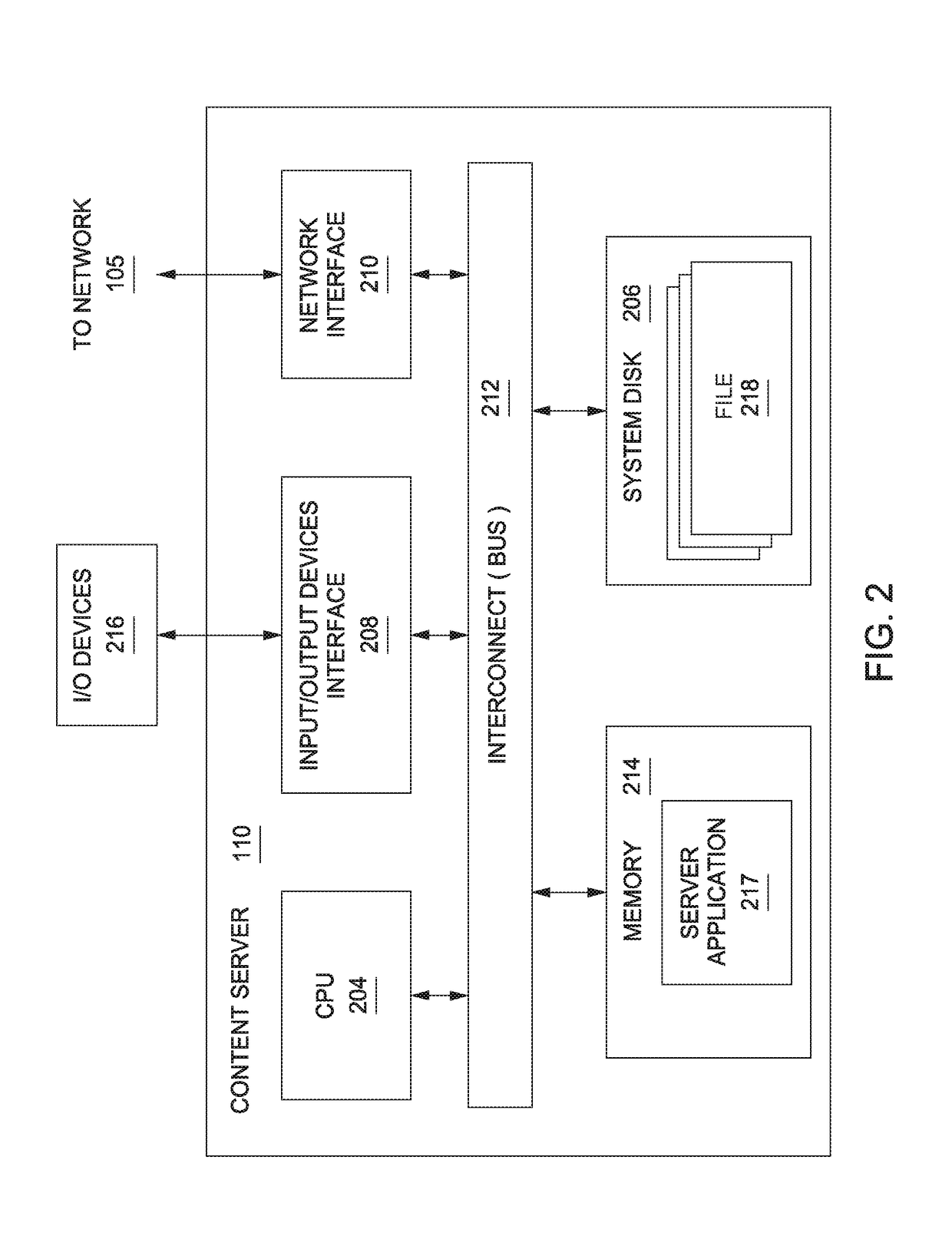

Detecting service vulnerabilities in a distributed computing system

ActiveUS20180089011A1Reducing systemic uncertaintyIncreases performance and flexibilityMarginal checkingReliability/availability analysisTraffic capacityMicroservices

One embodiment of the present invention sets forth a technique for testing microservices in distributed computing systems. The technique includes routing a first traffic sample associated with request traffic from one or more client devices to a first instance of a first service implemented in a distributed computing system, wherein the first instance generates a first plurality of request responses in response to a first plurality of data requests included in the first traffic sample and transmits the first plurality of request responses to a second service included in the sequence of services, and routing a second traffic sample associated with the request traffic to a second instance of the first service, wherein the second instance generates a second plurality of request responses in response to a second plurality of data requests included in the second traffic sample and transmits the second plurality of request responses to the second service.

Owner:NETFLIX

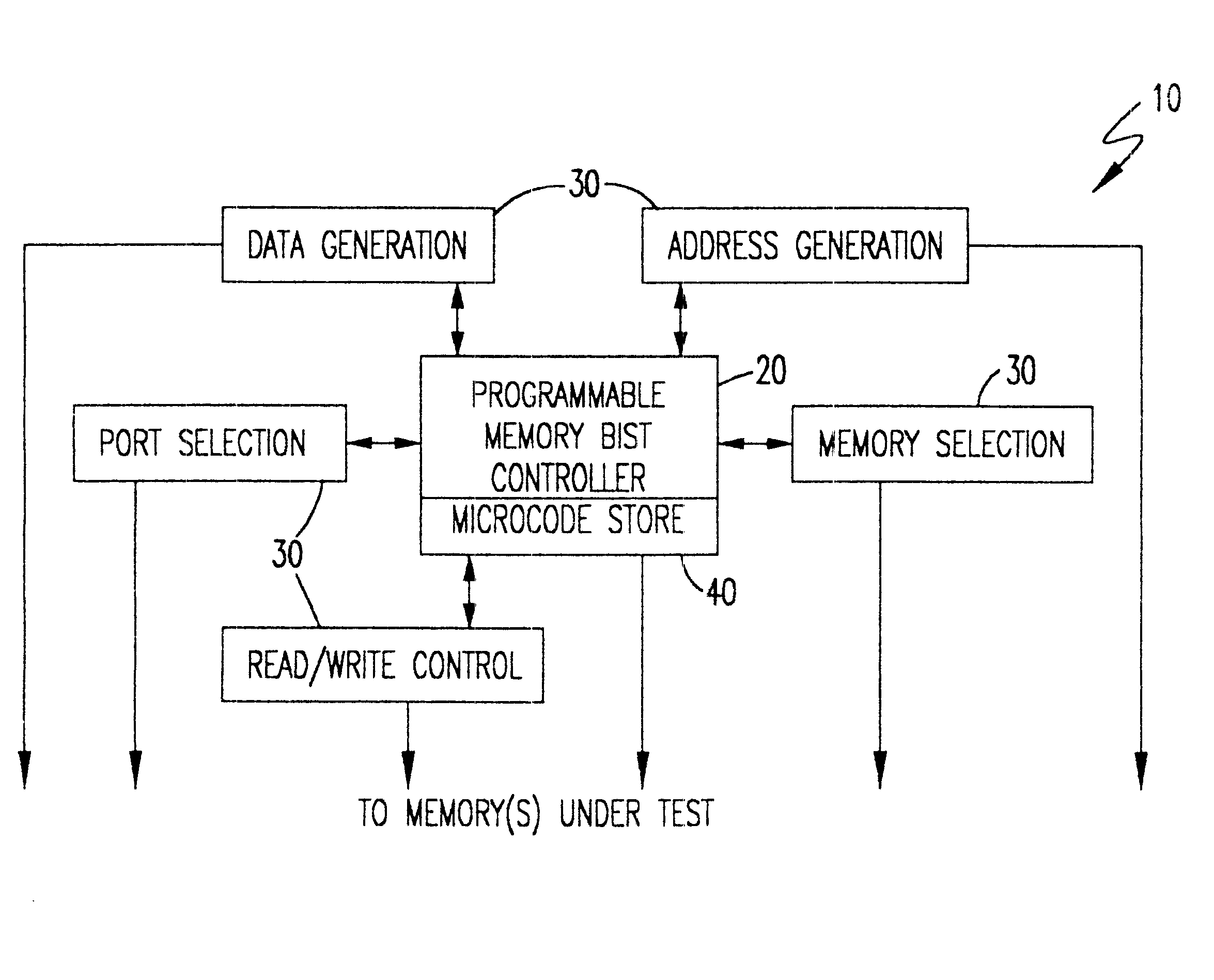

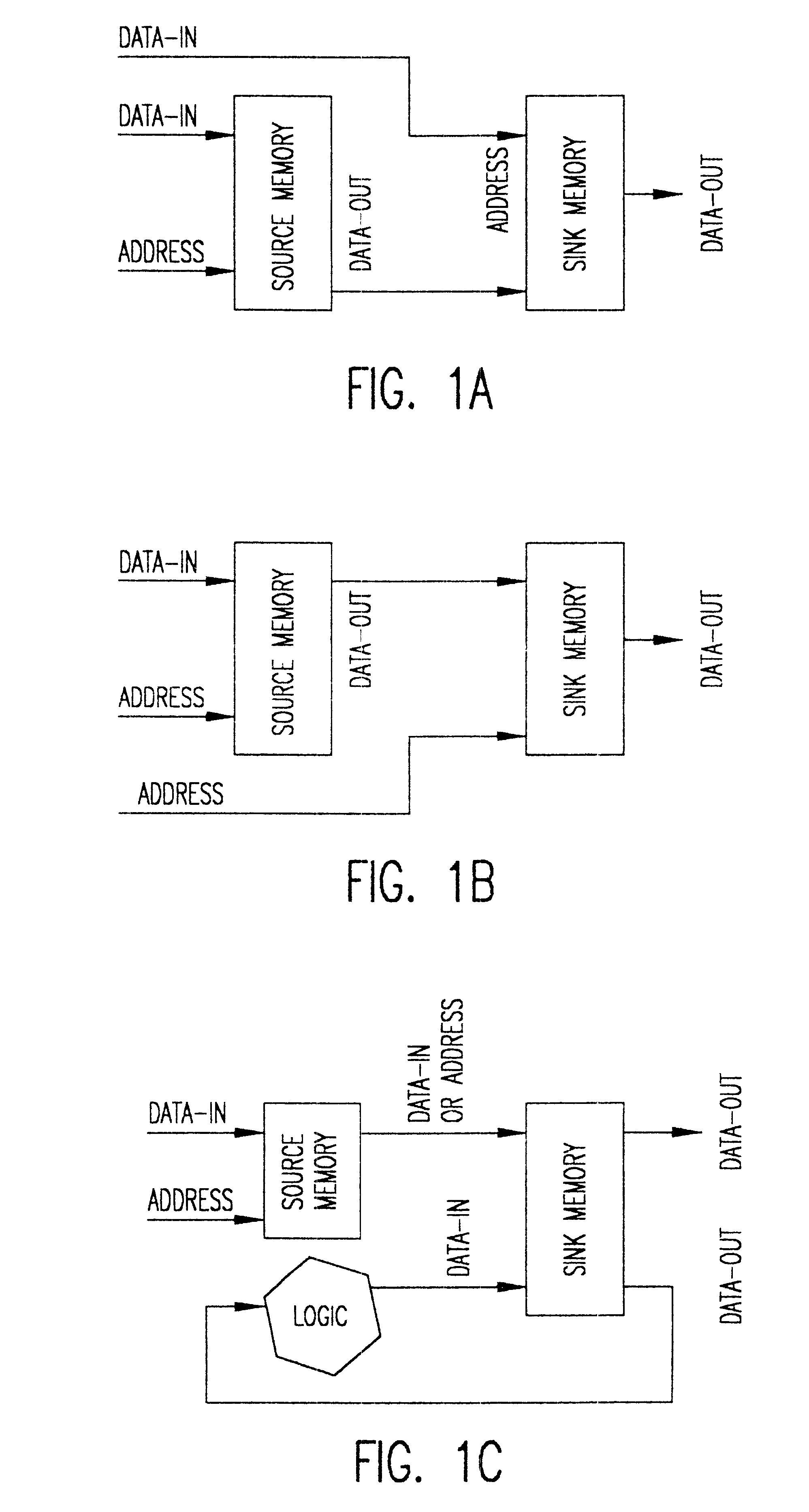

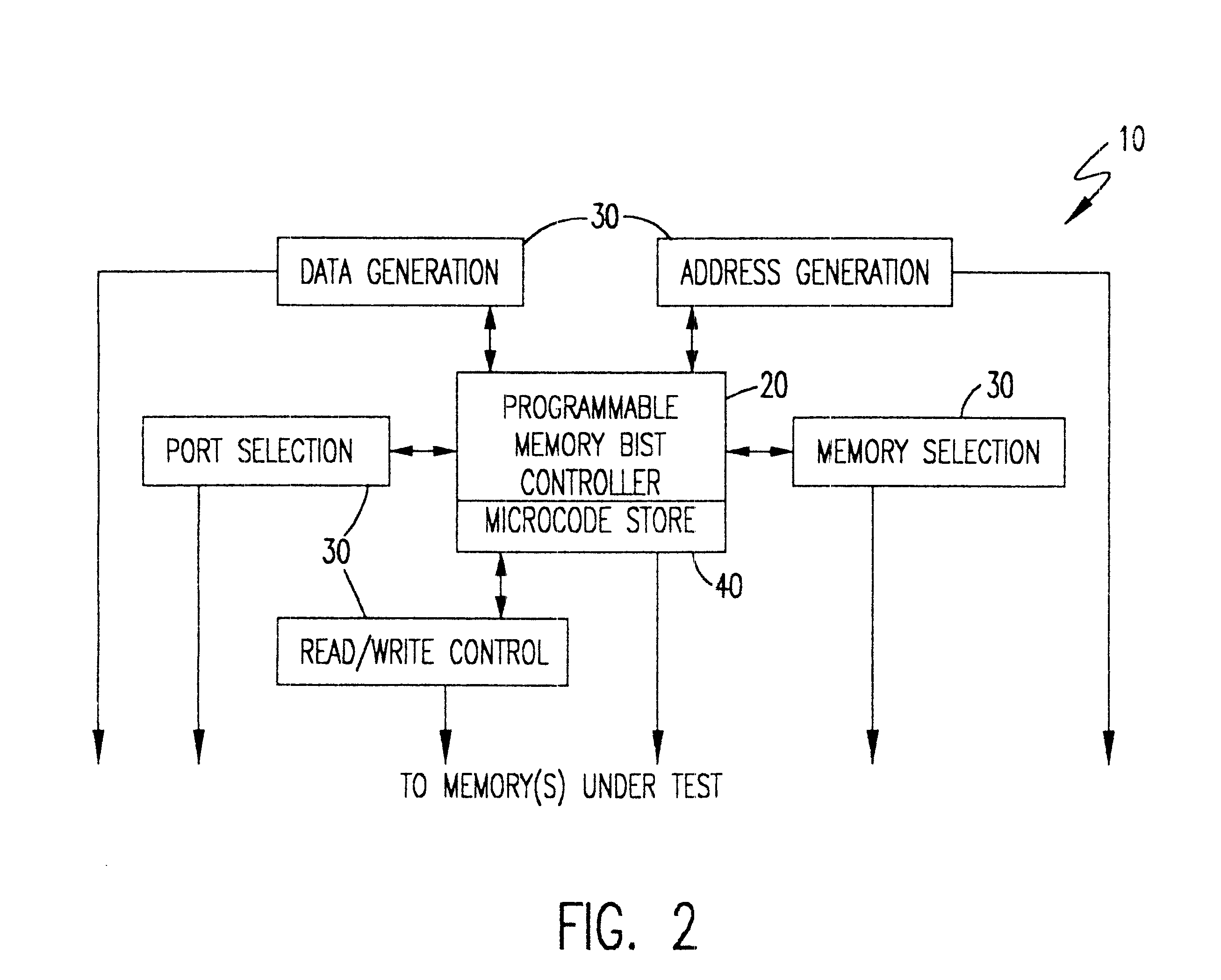

Programmable memory built-in self-test combining microcode and finite state machine self-test

A finite state machine (FSM) is used to generate, in real time, potentially long sequences of signals which control generation of signals for application to a memory structure during a self-test procedure which is provided in hardware on the same chip with the memory structure. The FSM-based instruction generator requires much less area than is required for storage of a corresponding number of microcode instructions and allows the built-in self-test (BIST) controller to have a modular architecture permitting re-use of hardware designs for the BIST arrangement with consequent reduction of elimination of design costs of the BIST arrangement to accommodate new memory designs. The sequential nature of the operation of a finite state machine as it progresses through a desired sequence of states is particularly well-suited to controlling capture of signals where access to high. speed data transfer circuits cannot otherwise be accommodated.

Owner:GOOGLE LLC

Method and apparatus for testing, characterizing and monitoring a chip interface using a second data path

InactiveUS20060190642A1Accurate measurementAccurately determineInput/output to record carriersResistance/reactance/impedenceComputer scienceData path

A data receiver circuit in a receiving chip provides the capability to characterize an interface, which includes one or more inter-chip communication lines, between a transmitting chip and the receiving chip by transmitting the data across a primary data path and a secondary data path, latching the data in the secondary data path using a clock signal that is skewed relative to a clock signal used to latch the primary data path, comparing the data latched from the primary and secondary data paths, and recording errors. Because the primary data path is not impacted by the test cycle, the test cycle may be run while data associated with applications running on the system are transmitted across the inter-chip communication lines.

Owner:LENOVO GLOBAL TECH INT LTD

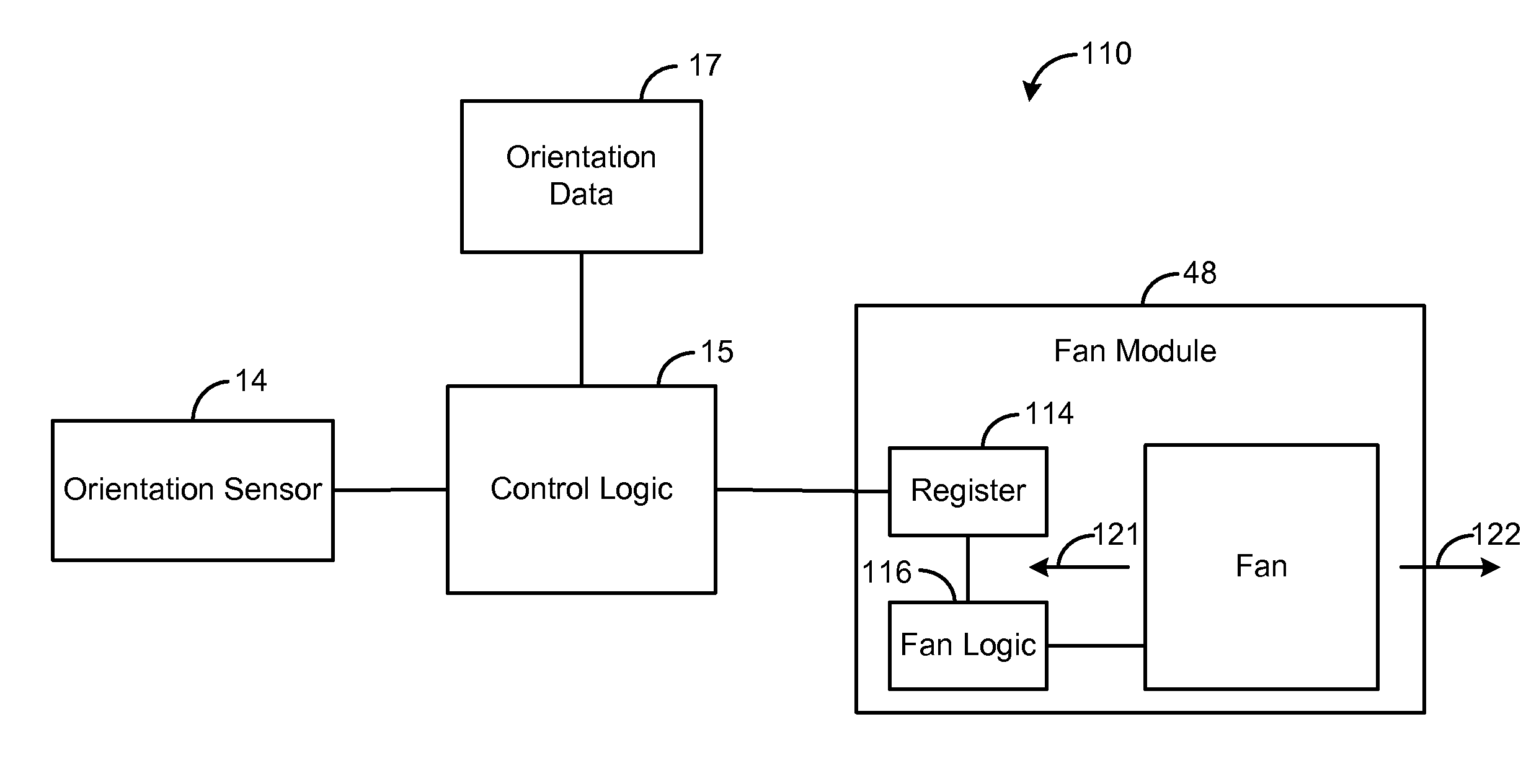

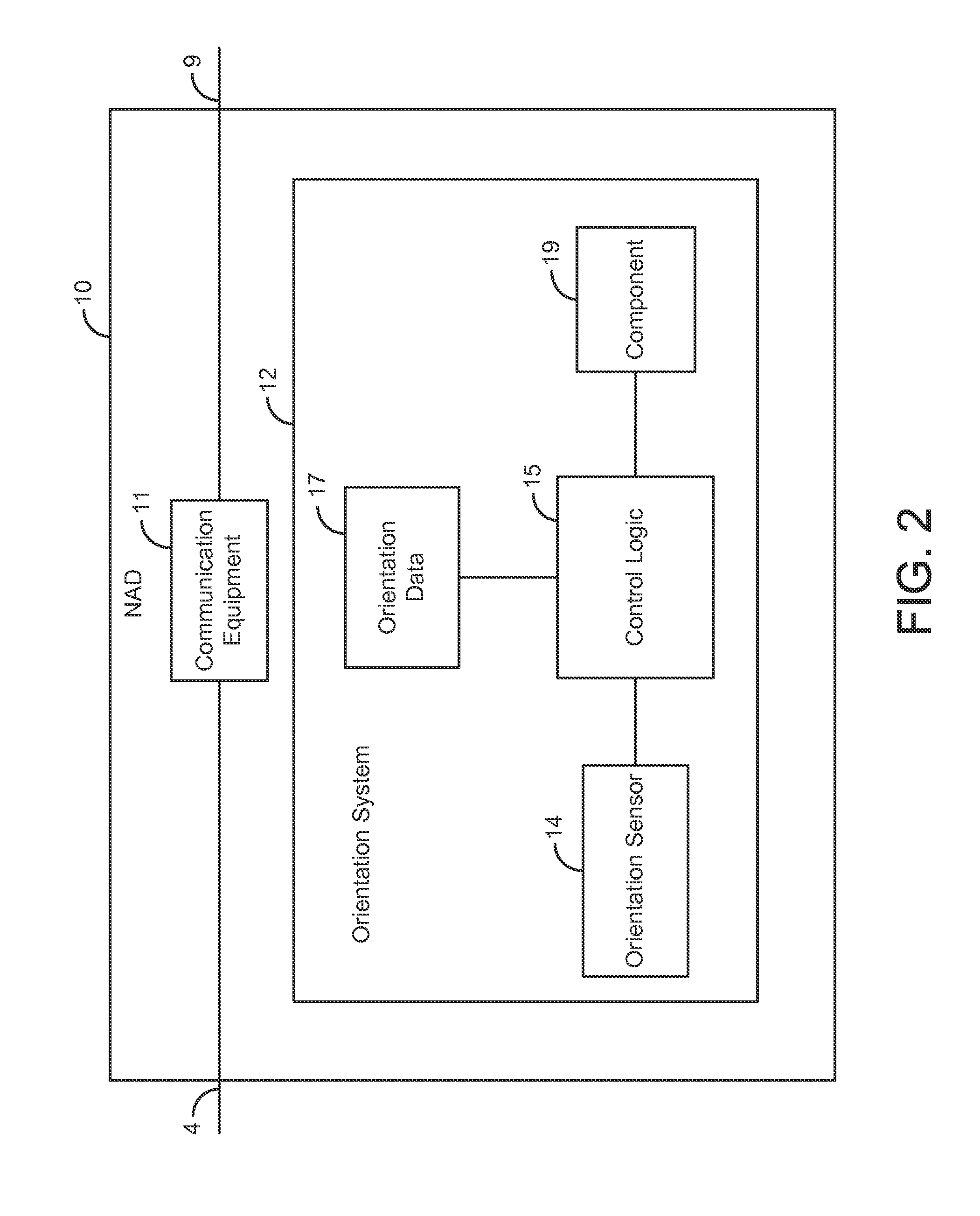

Systems and methods for sensing and indicating orientation of electrical equipment with active cooling

ActiveUS8823531B1Energy efficient ICTDigital data processing detailsActive coolingElectrical devices

A system for sensing and indicating orientation of electrical equipment has an orientation sensor and control logic. The control logic is configured to compare predefined data with a sensed orientation of the electrical equipment in order to determine whether the sensed orientation of the equipment is within an acceptable range such that sufficient cooling by a cooling system is likely to occur. If the sensed orientation of the equipment is not within the acceptable range, the control logic transmits a notification signal so that corrective action can occur. As an example, the notification signal may be used to notify a user of the improper orientation. In another example, the notification signal automatically triggers an action that compensates for the improper orientation.

Owner:ADTRAN

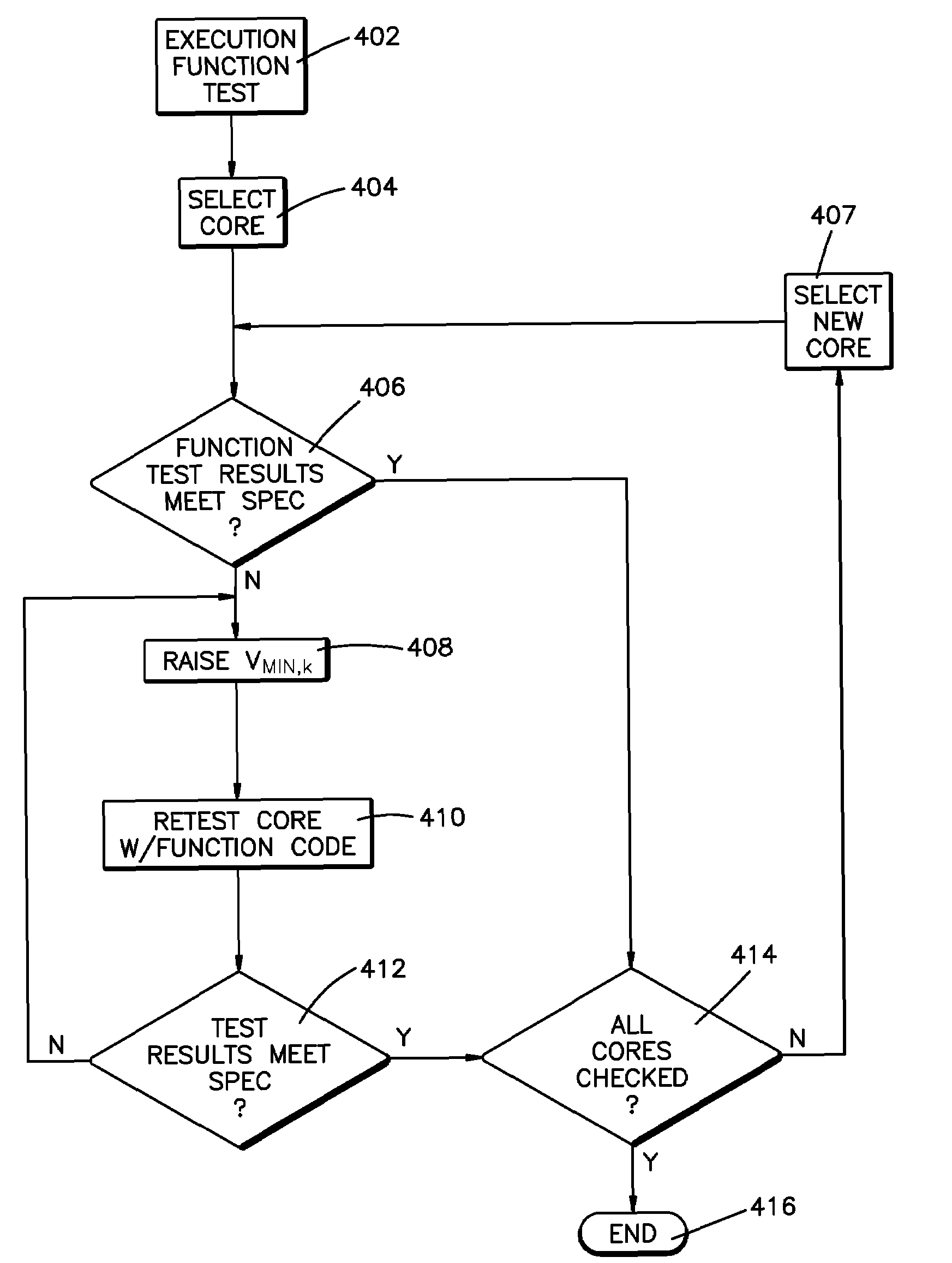

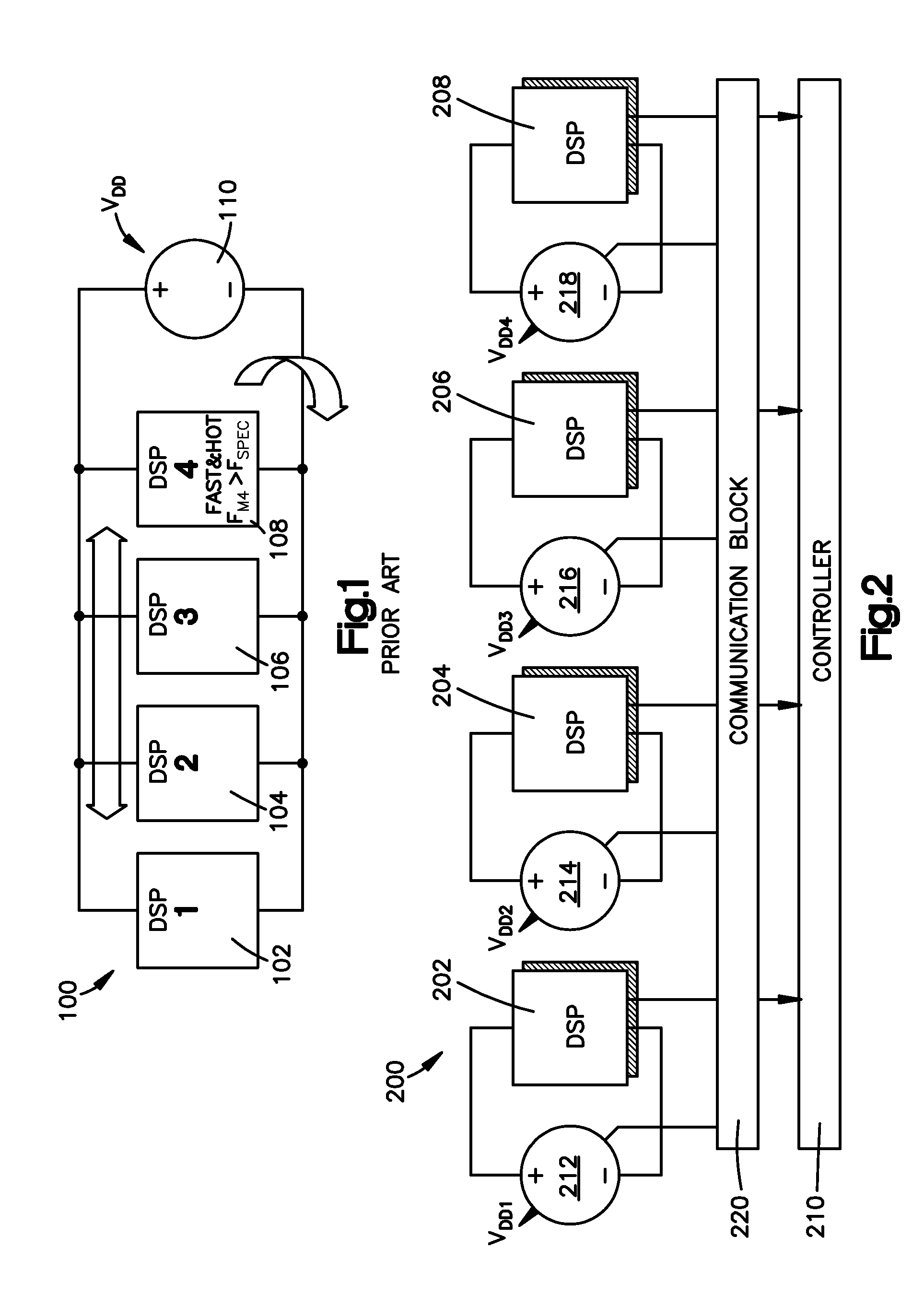

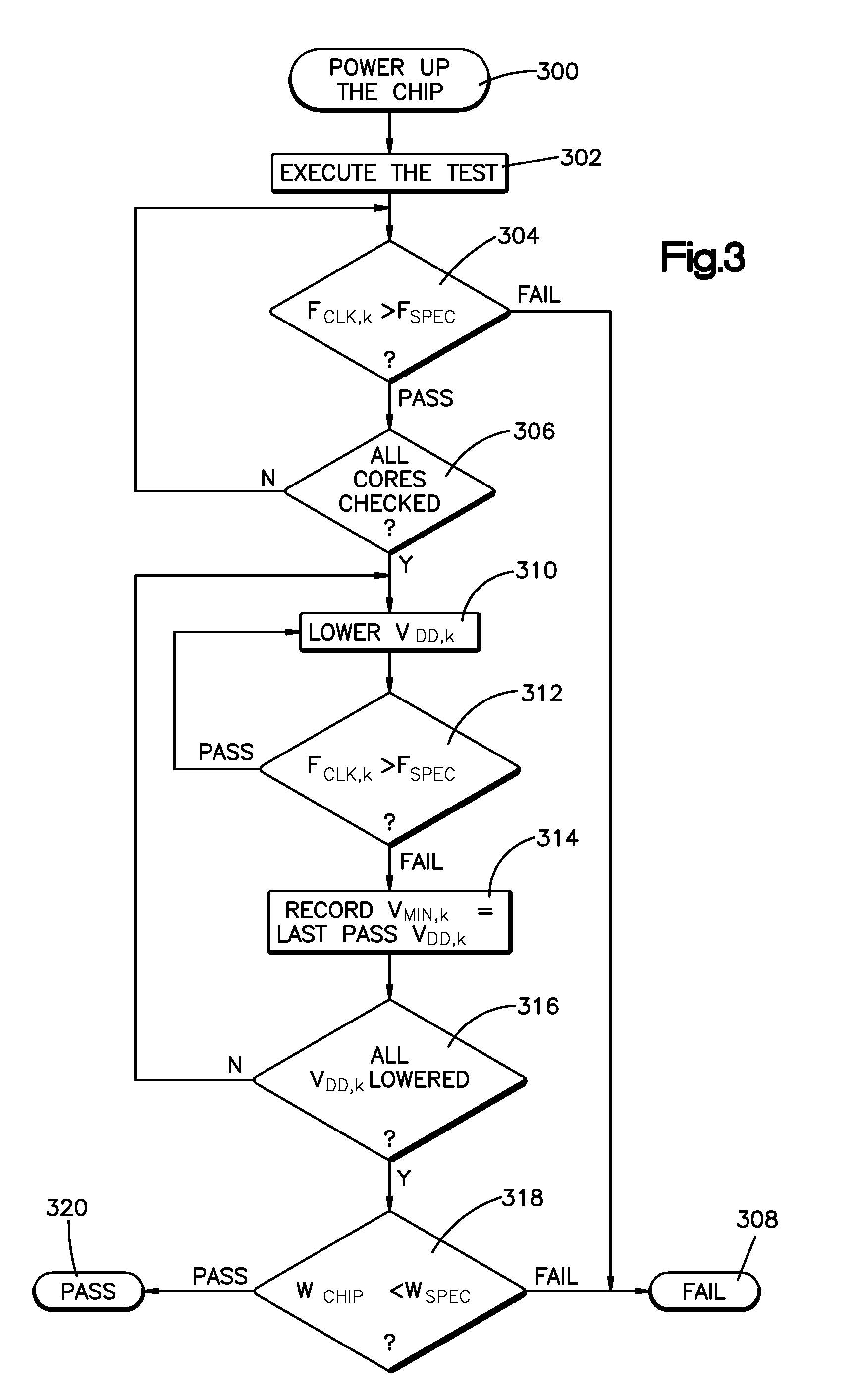

Method and system for testing processor cores

Systems, methods and program codes are provided for testing multi-core processor chip structures. Individual processor core power supply voltages are provided through controlling individual power supplies for each core, in one aspect to ensure that one or more cores operate at clock rates in compliance with one or more performance specifications. In one example, a first power supply voltage supplied to a first processing core differs from a second core power supply voltage supplied to a second processing core, both cores operating in compliance with a reference clock rate specification. Core power supply voltages may be selected from ordered discrete supply voltages derived by progressively raising or lowering a first supply voltage, optionally wherein the selected supply voltage also enables the core to operate within another performance specification.

Owner:KYNDRYL INC

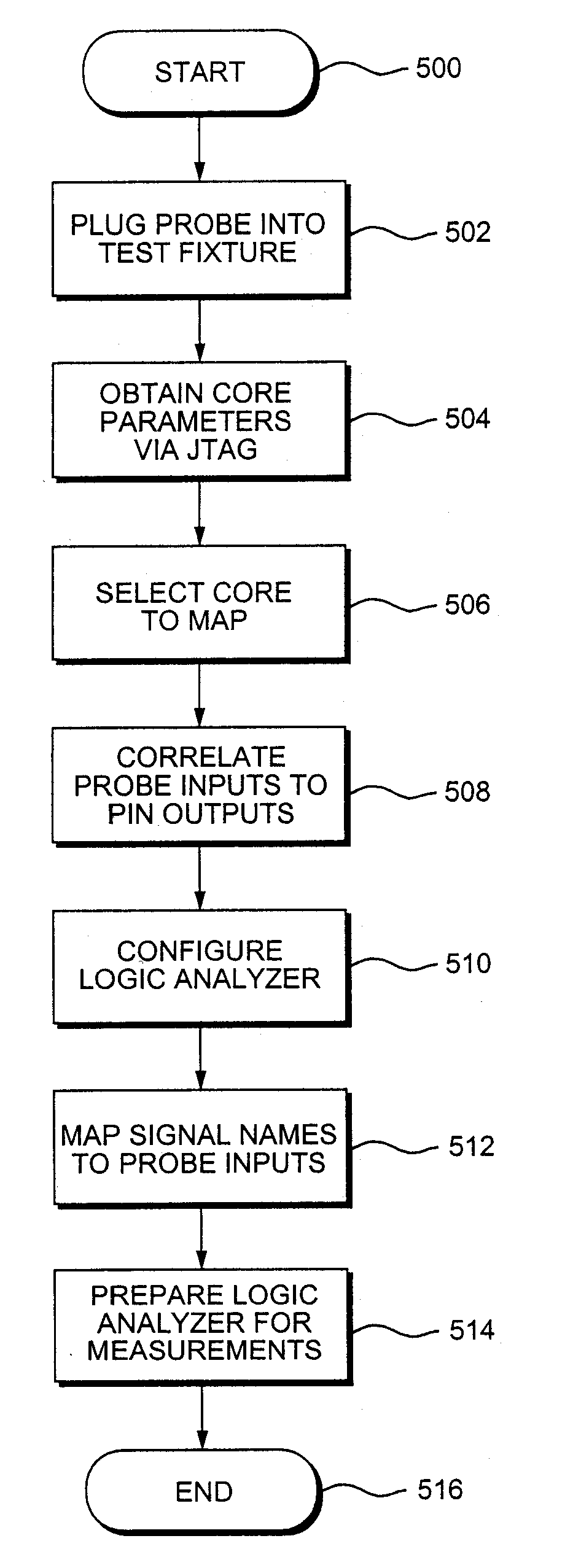

Apparatus and method for automated test setup

Apparatus and methods for setting up a test instrument to perform measurements on a circuit having a plurality of signal applied to a plurality of output pins. Configuration parameters including an identification of the output pins are retrieved and the test instrument is configured to interface with the output pins based on the configuration parameters. A list of output pins and a list of input lines associated with the test instrument are graphically displaying on a screen associated with the test instrument. Interacting with the graphical display, the user then associates each output pin with an input line to which each output pin is connected.

Owner:AGILENT TECH INC

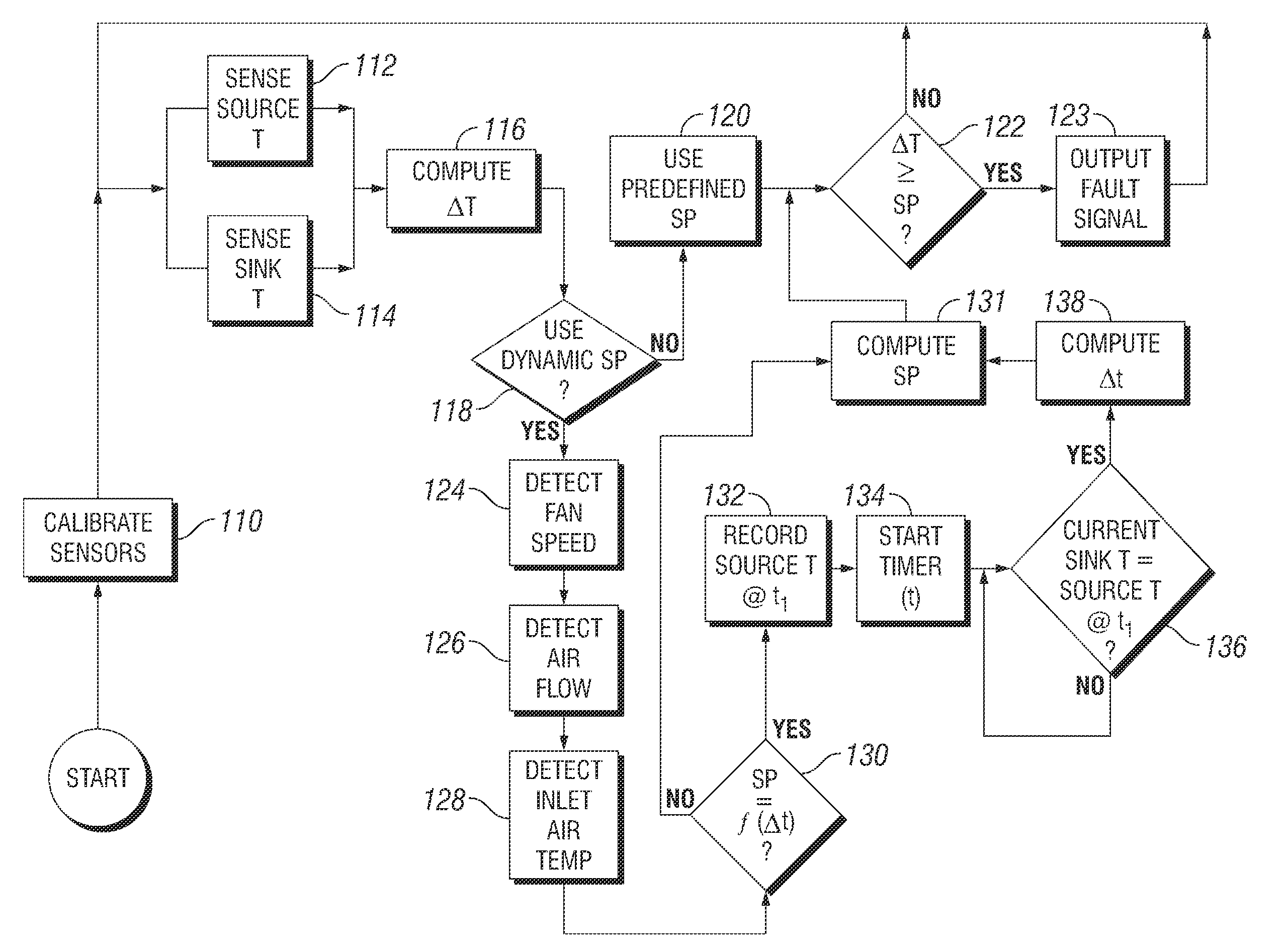

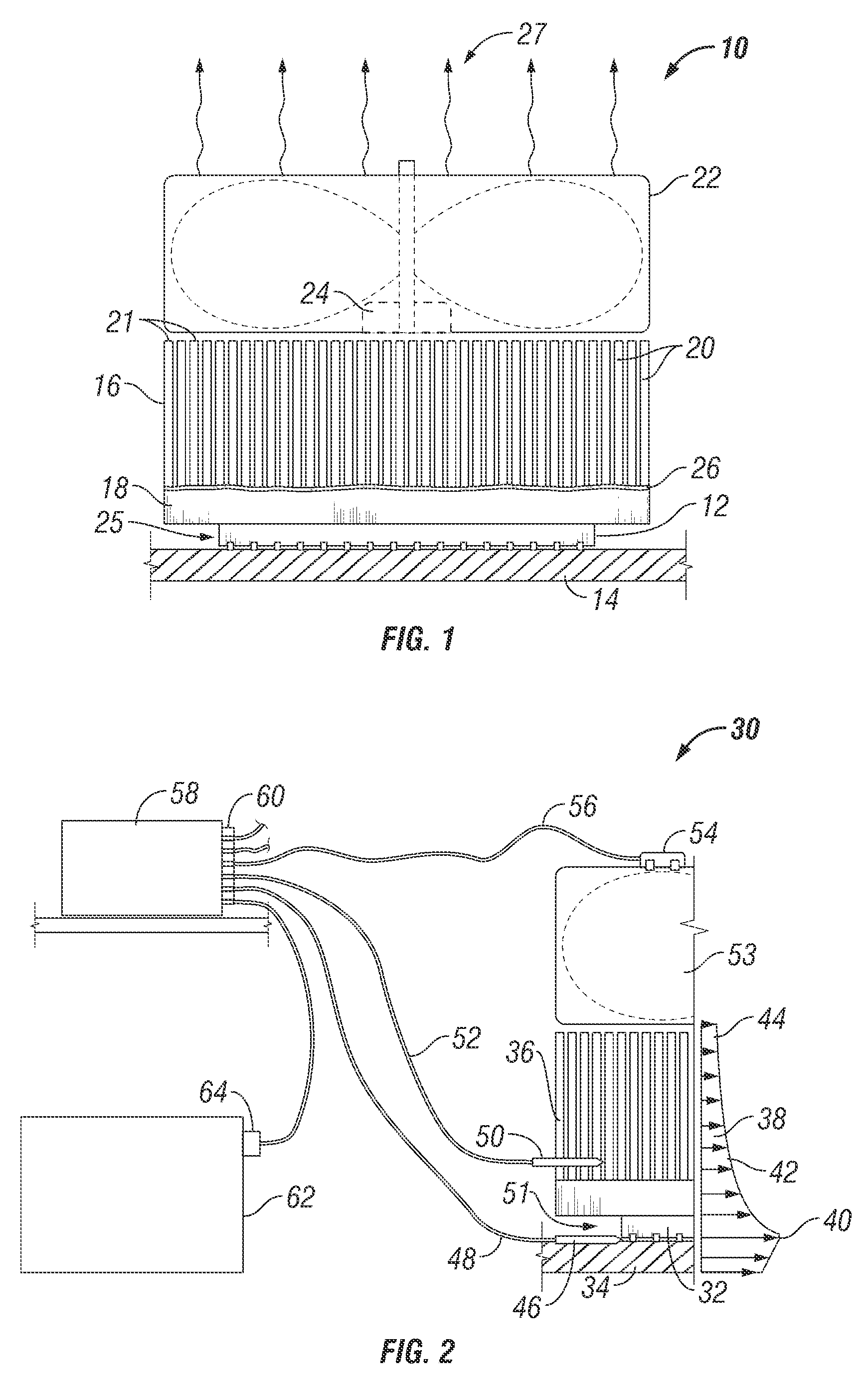

Method and apparatus for detecting heat sink faults

InactiveUS20080040067A1Thermometer detailsTemperatue controlPredictive failure analysisComputerized system

Detecting, predicting, and diagnosing faults in a cooling system. According to one embodiment, a heat sink is in thermal contact with a heat-generating electronic component. When a temperature differential between the electronic component and the heat sink exceeds a set point, a fault signal is generated. The set point may be empirically or theoretically determined. The set point may be a static set point, or it may be a dynamic set point determined according to real-time operational parameters of the system. The system may be implemented with predictive failure analysis (PFA) to provide a more reliable, efficient, inexpensive, and robust computer system.

Owner:GOOGLE LLC

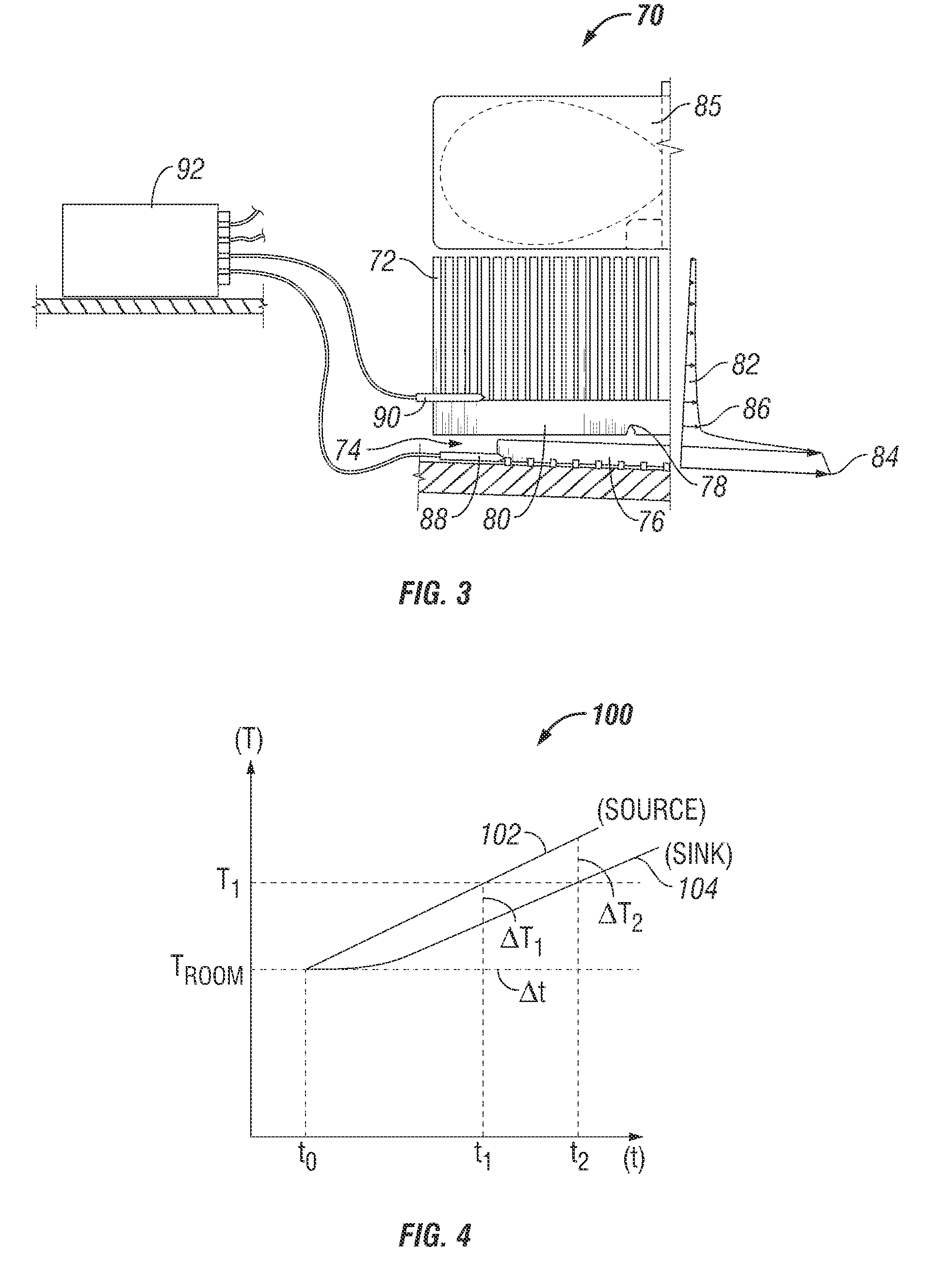

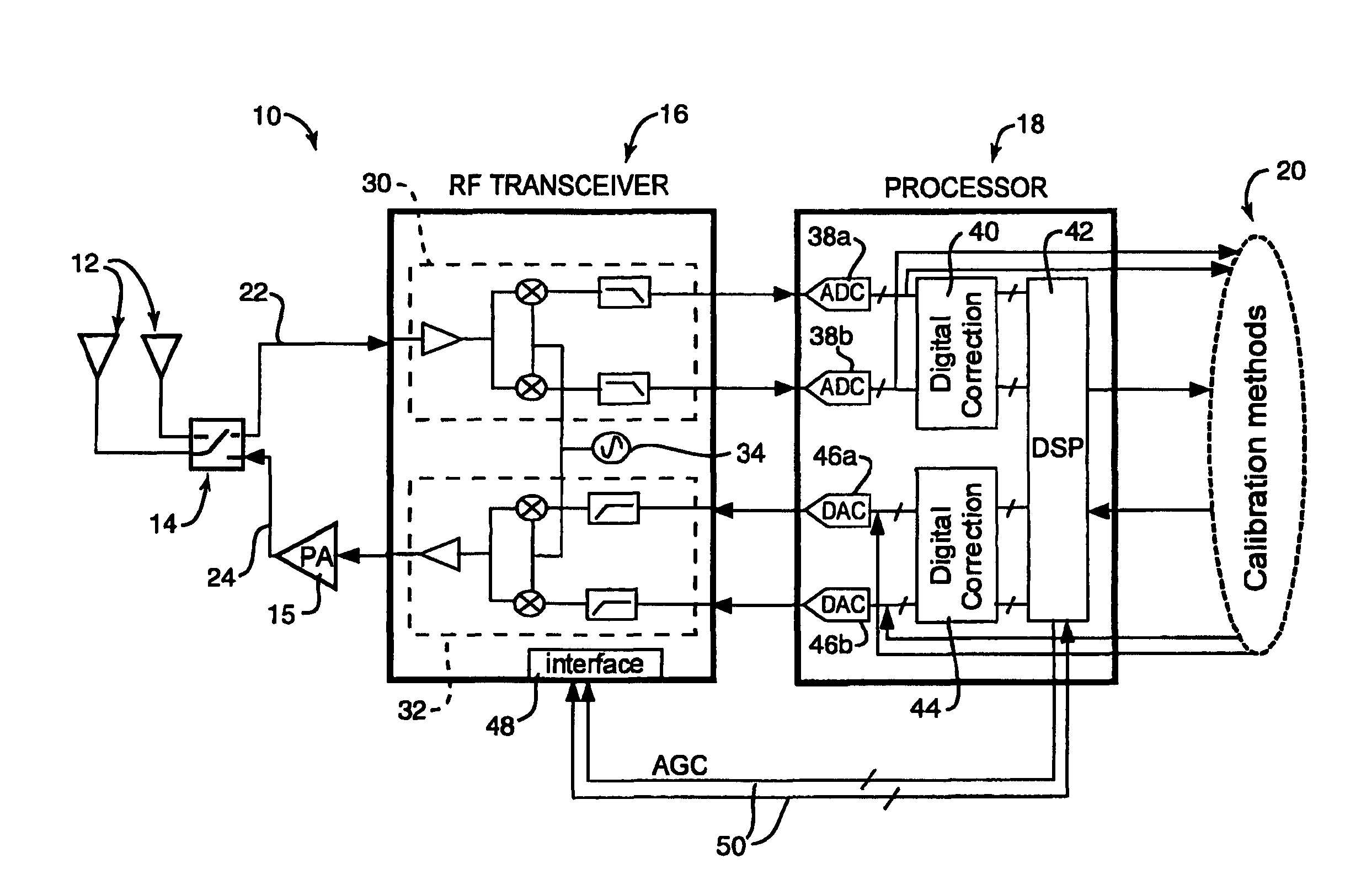

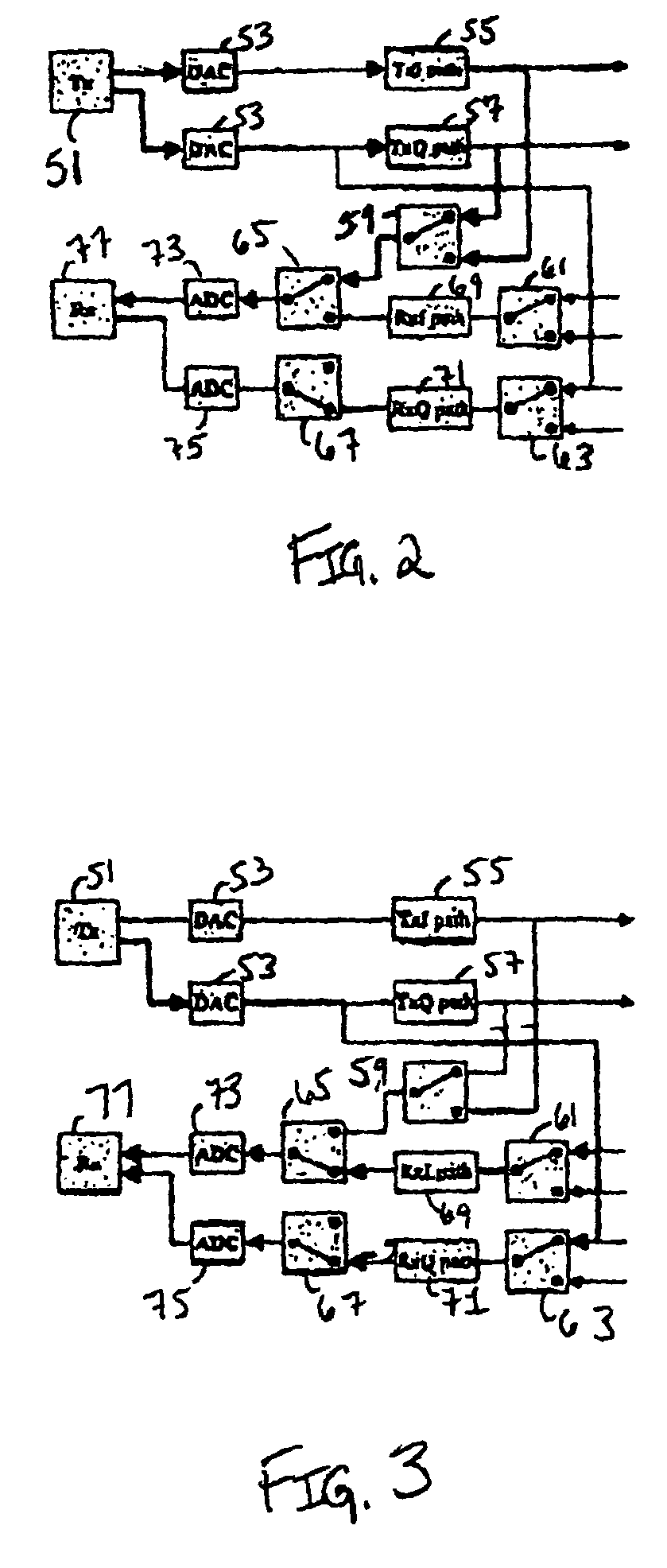

Method and system for measuring IQ path mismatch

Aspects for measuring IQ path mismatch in signal modulation are described. The aspects include estimating a transmitter IQ mismatch in a form of gain and phase response for transmitter I and Q paths sharing a receiver path, and estimating a receiver IQ mismatch in a form of gain and phase response for receiver I and Q paths sharing a signal source. Further included is compensating for the difference of the transmitter and receiver I and Q paths using a digital FIR filter. Iterative estimation is utilized for filter tap parameters during the compensating.

Owner:AVAGO TECH INT SALES PTE LTD

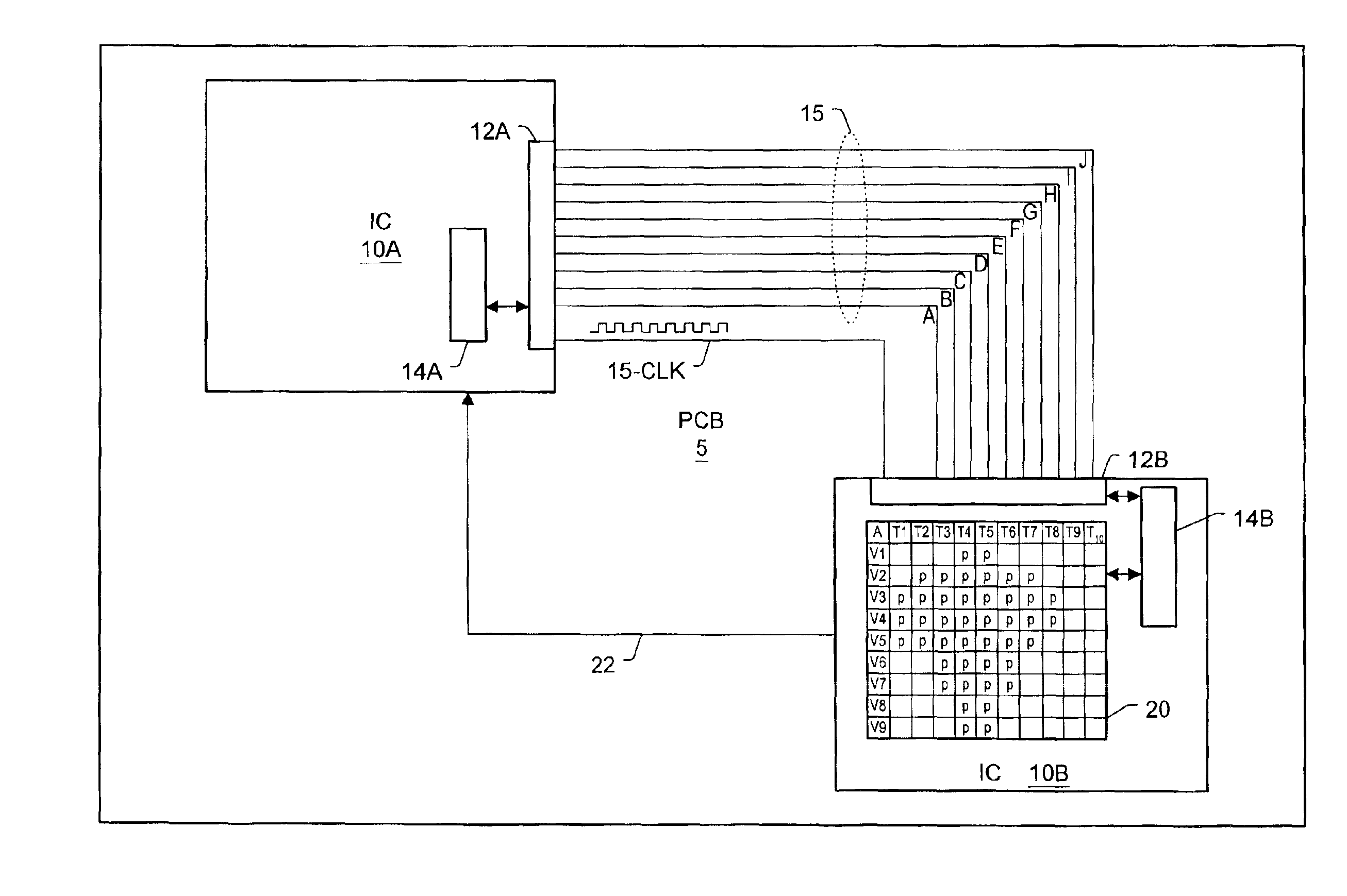

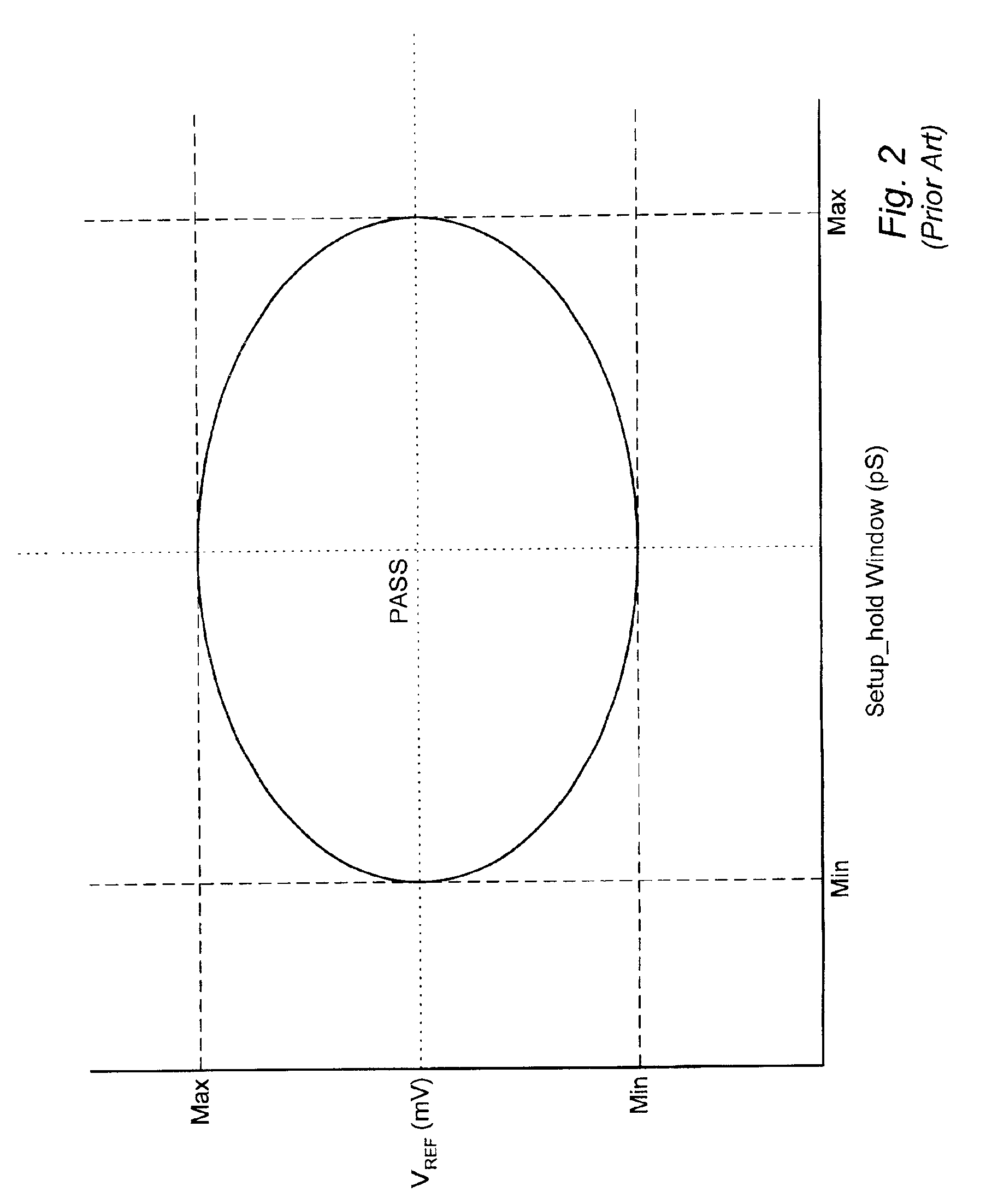

Automated calibration of I/O over a multi-variable eye window

InactiveUS6944692B2Automatically performMarginal checkingEmergency protective arrangement detailsData transmissionData value

A method and apparatus for automated calibration of I / O over a multi-variable eye window is provided. A transmitter may conduct data transmissions to a receiver of an integrated circuit (IC) over a plurality of signal lines. The data transmissions may be conducted according to a certain parameters or sets of parameters. Parameters may include voltage levels at which signals are transmitted or timing delays. The receiver may determine whether the correct data value was received over each signal line. The results may be recorded in a storage mechanism in the same IC as the receiver. The storage mechanism may, for each signal line, store a pass / fail result corresponding to the particular parameters for the data transmission. The system may select the parameters which subsequent transmissions are to be conducted over each of the plurality of signal lines from the storage mechanism.

Owner:ORACLE INT CORP

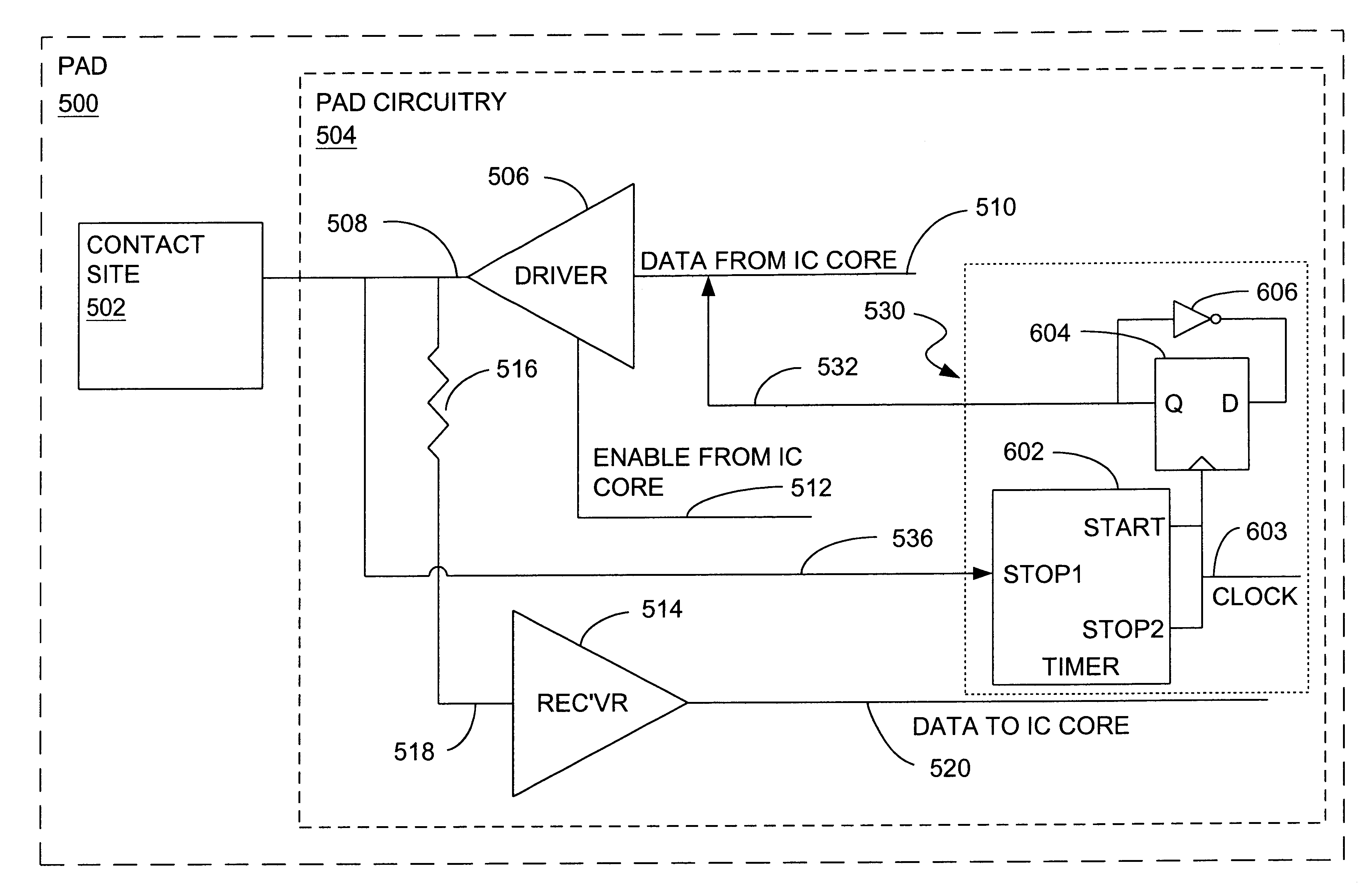

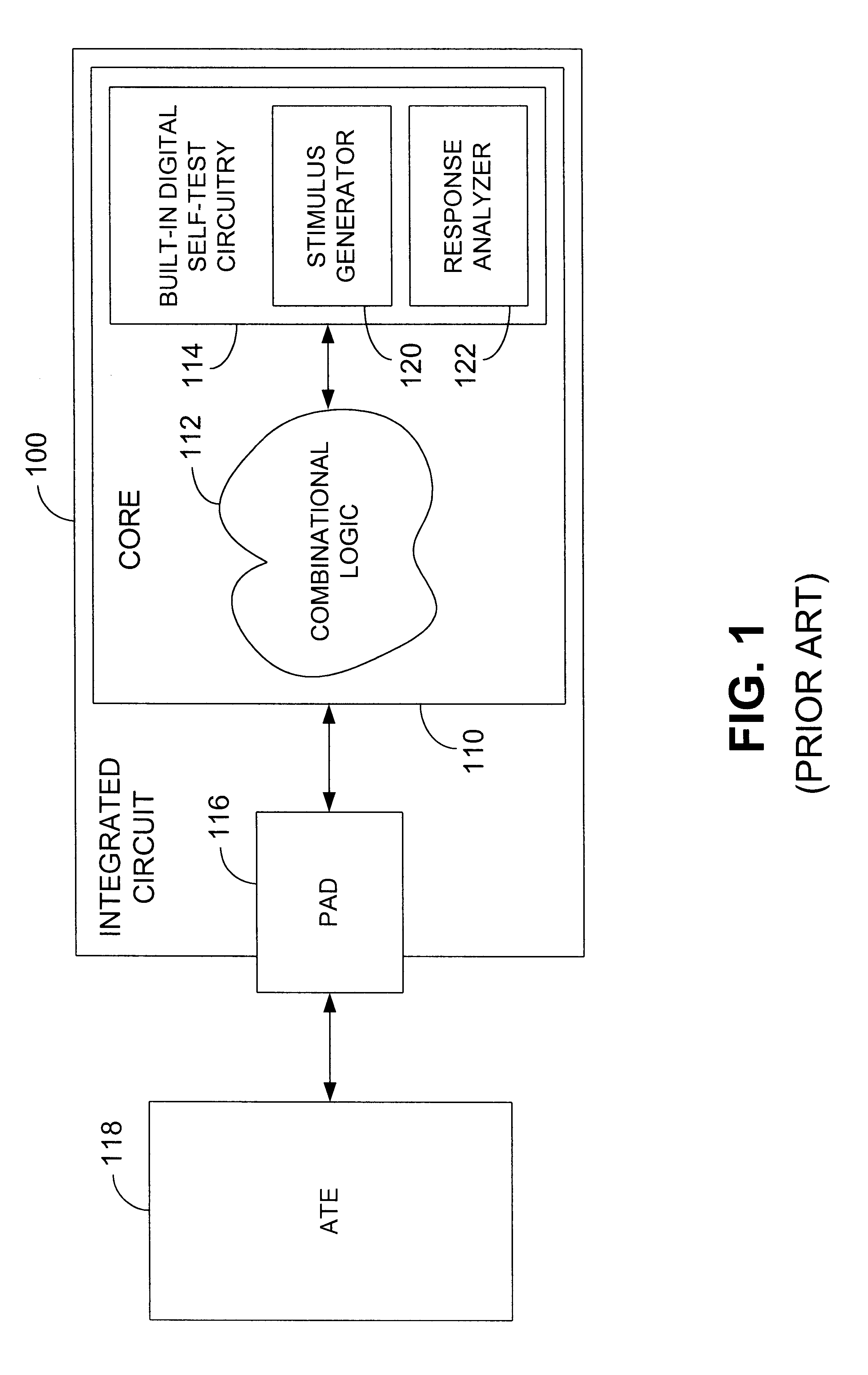

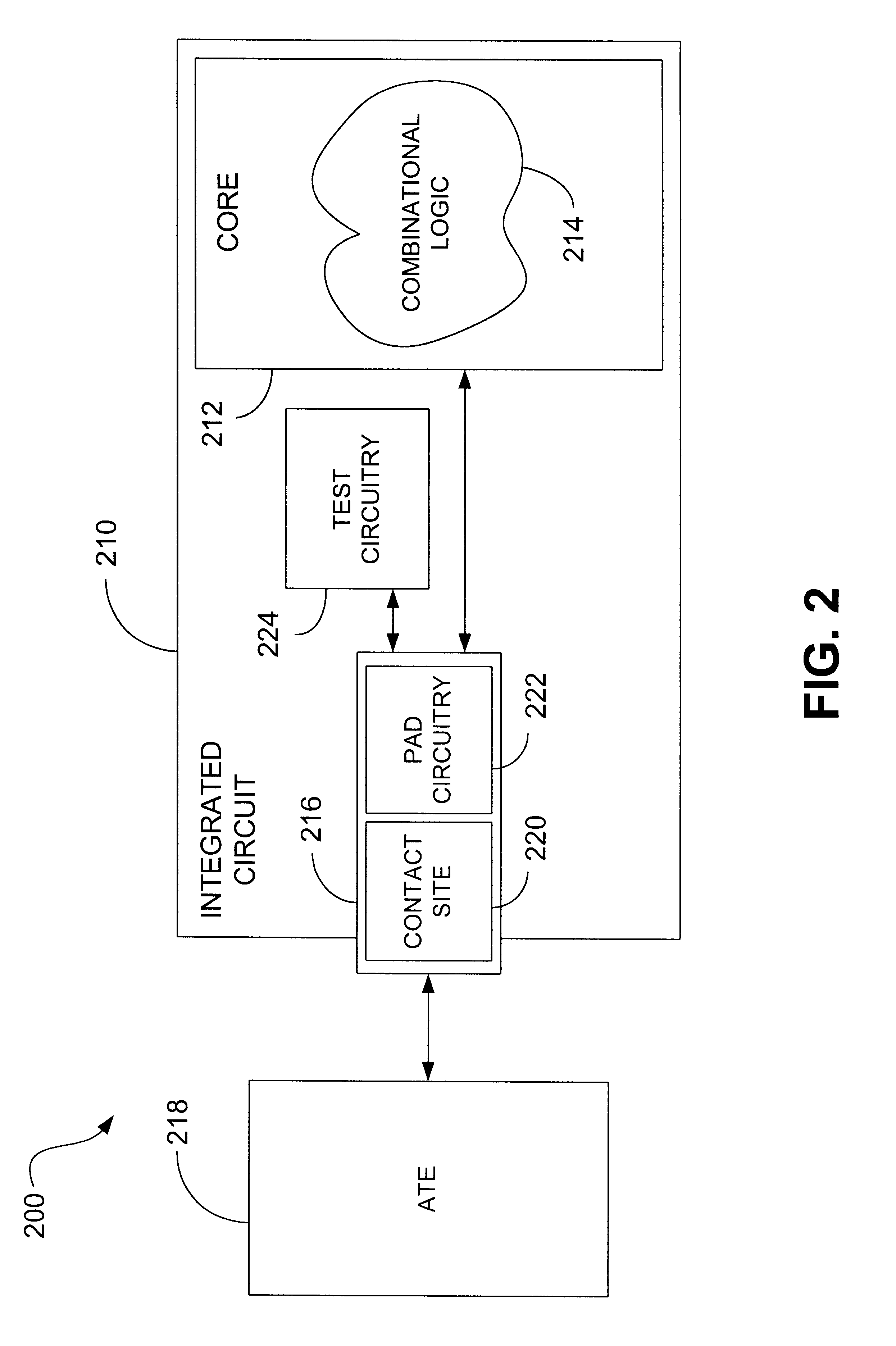

Systems and methods for facilitating testing of pad drivers of integrated circuits

InactiveUS6721920B2Digital circuit testingDigital data processing detailsElectricityIntegrated circuit

A preferred integrated circuit (IC) includes a first pad electrically communicating with at least a portion of the IC. The first pad includes a first driver and a first receiver, with the first driver being configured to provide a first pad output signal to a component external to the IC, and the first receiver being configured to receive a first pad input signal from a component external to the IC. The first receiver also is configured to provide, to a component internal to the IC, a first receiver digital output signal in response to the first pad input signal. A first test circuit also is provided that is internal to the IC. The first test circuit is adapted to provide information corresponding to the driver clock-to-q time of the first pad. Systems, methods and computer-readable media also are provided.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

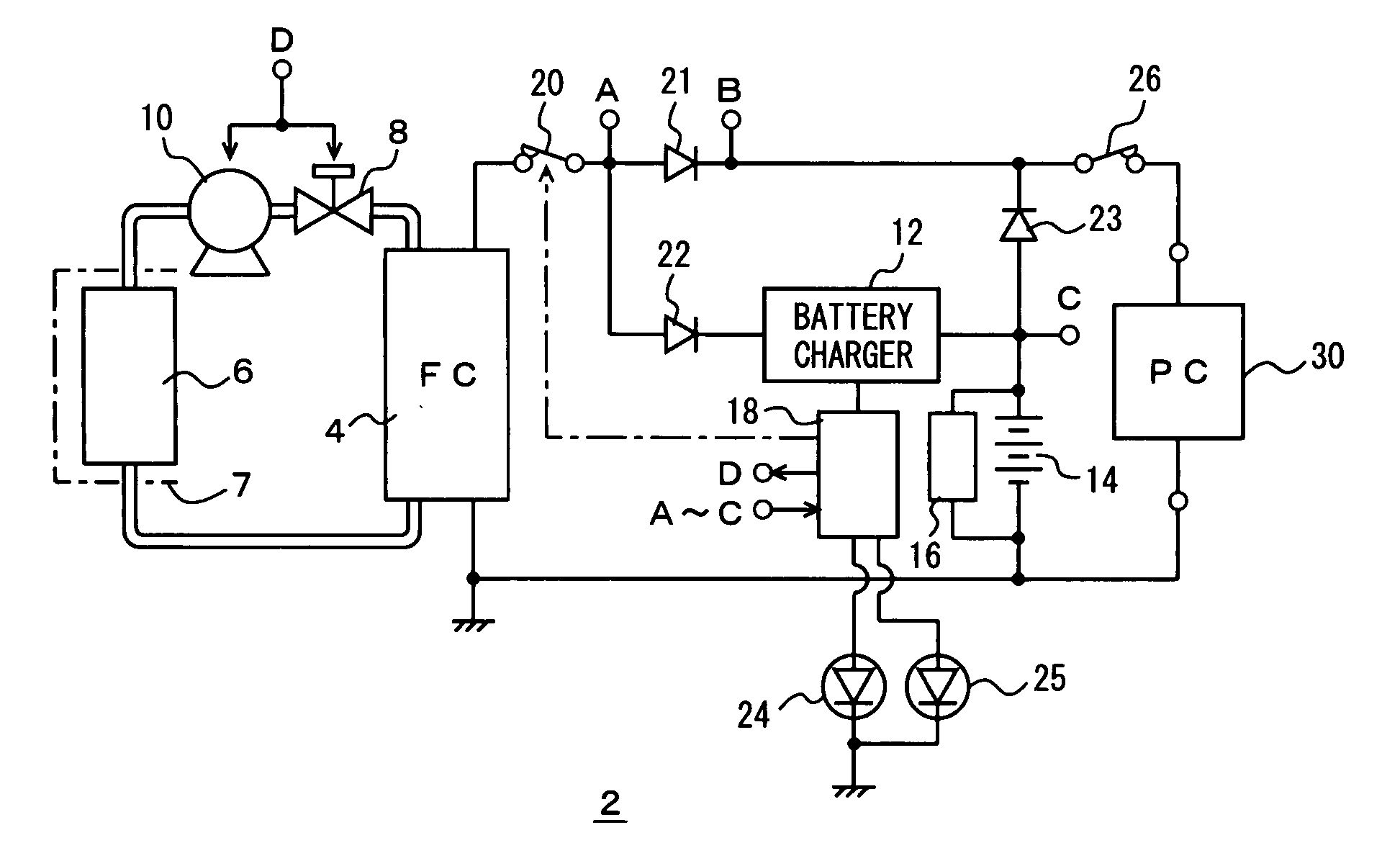

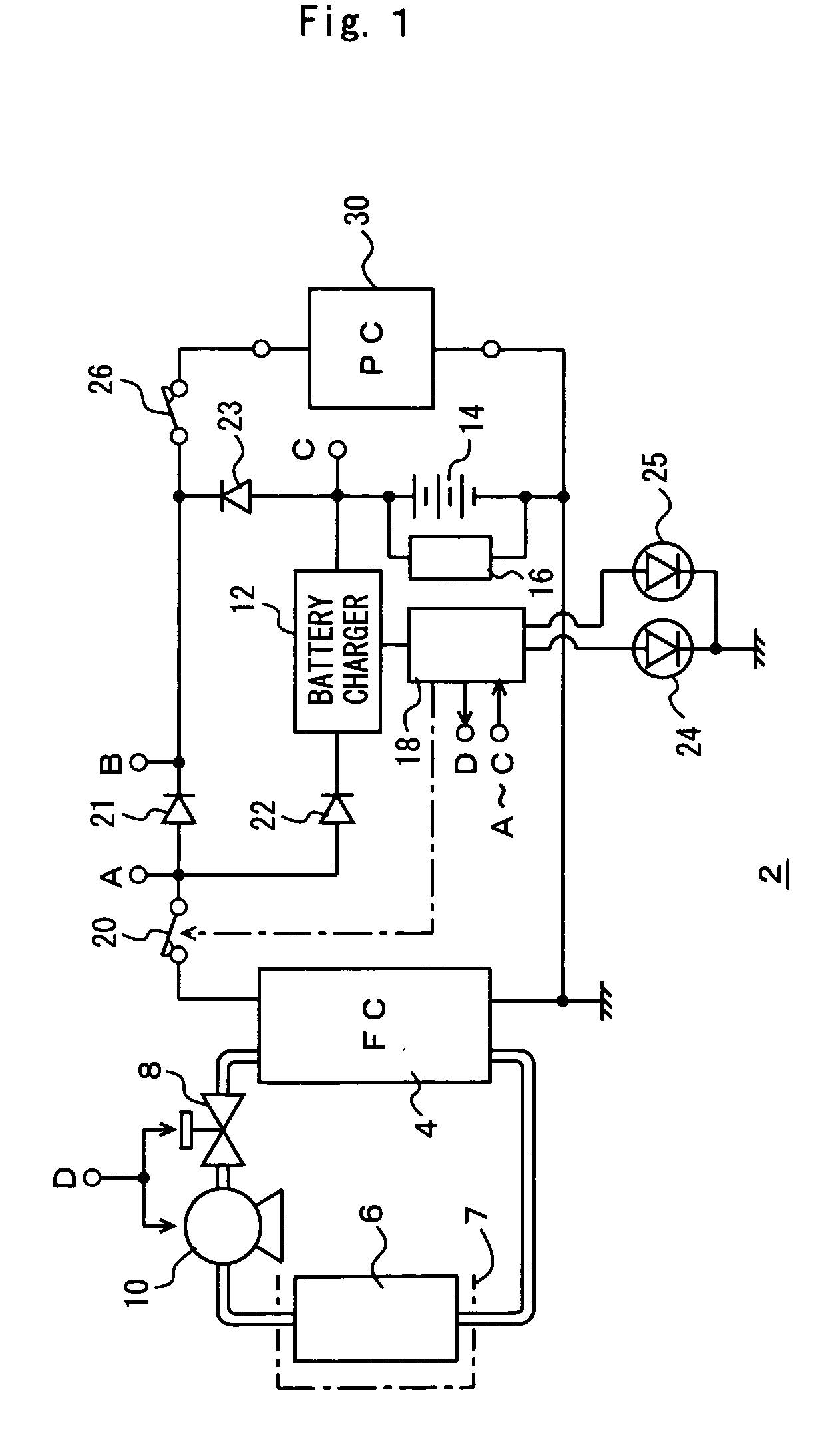

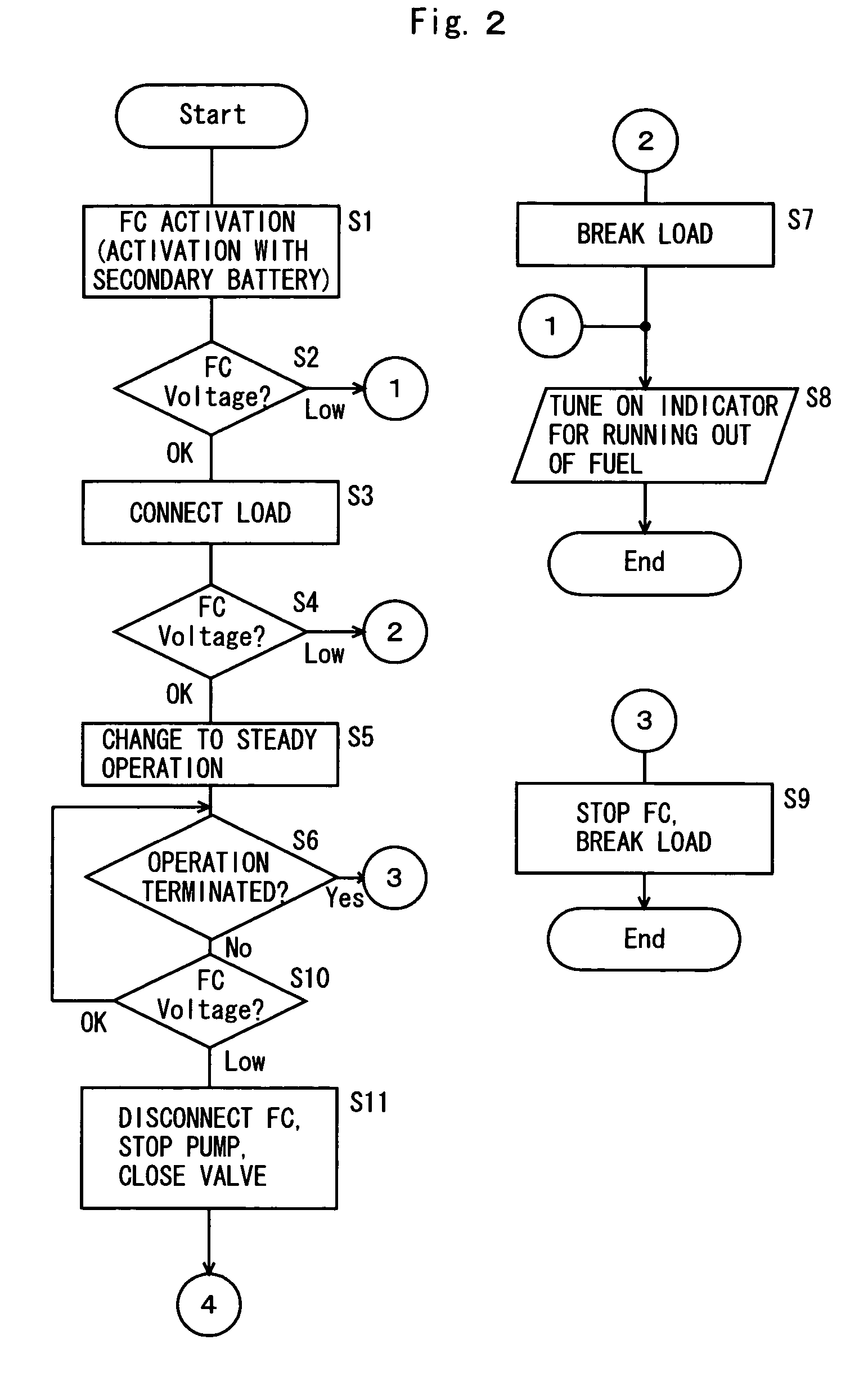

Fuel cell system and method for detecting running out of fuel in fuel cell

InactiveUS20060166045A1Reduce outputDc network circuit arrangementsBatteries circuit arrangementsFuel cellsAutomotive engineering

A secondary battery is connected to a fuel cell, the fuel cell is disconnected from a load when the output of the fuel cell falls, and the load is activated with the secondary battery. When the remaining capacity of the secondary battery decreases and becomes less than or equal to a first level, an indicator for indicating running out of fuel is turned on to require refueling. When the remaining capacity becomes less than or equal to a second level, the load is disconnected even from the secondary battery.

Owner:GS YUASA CORP

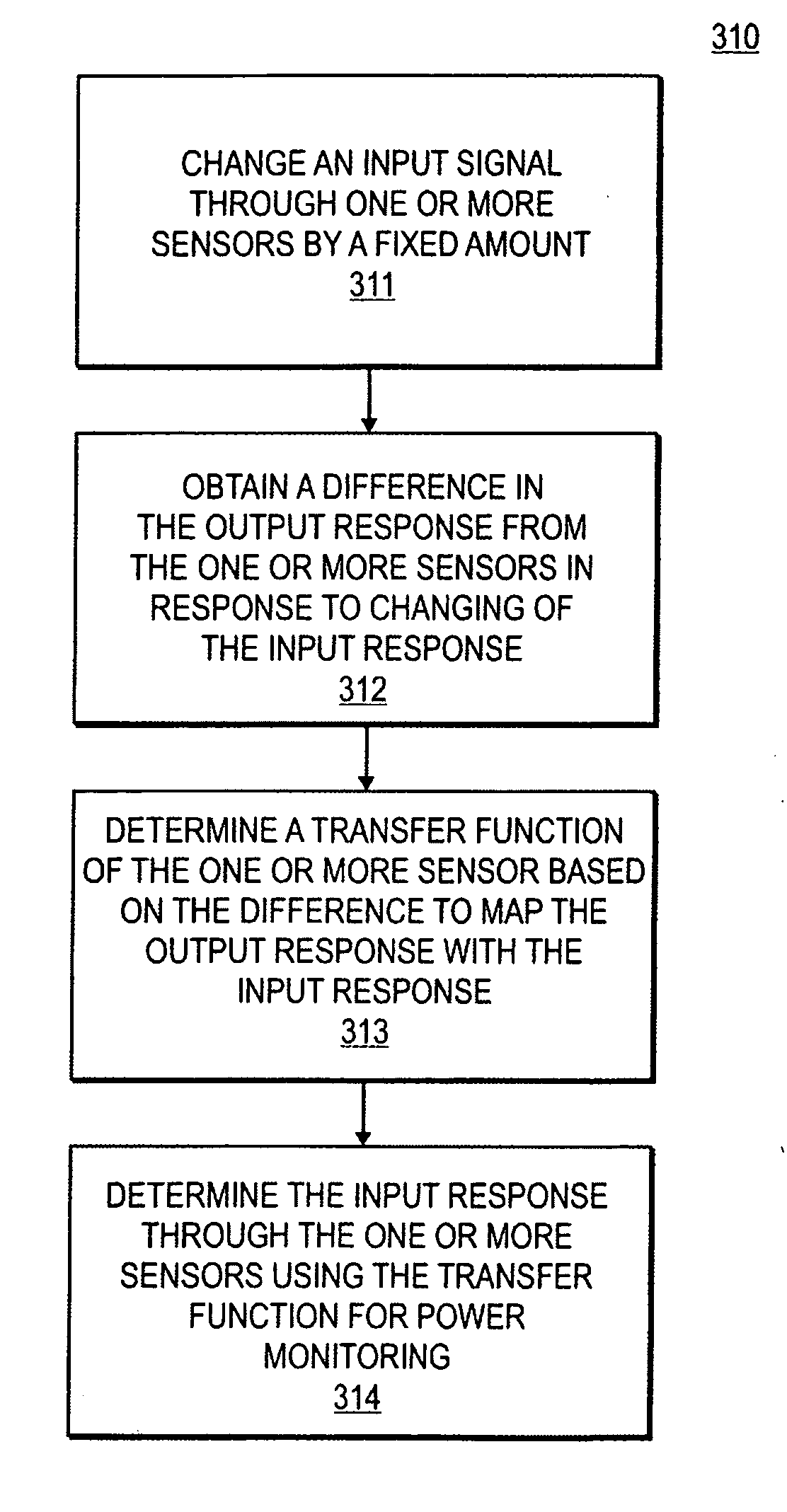

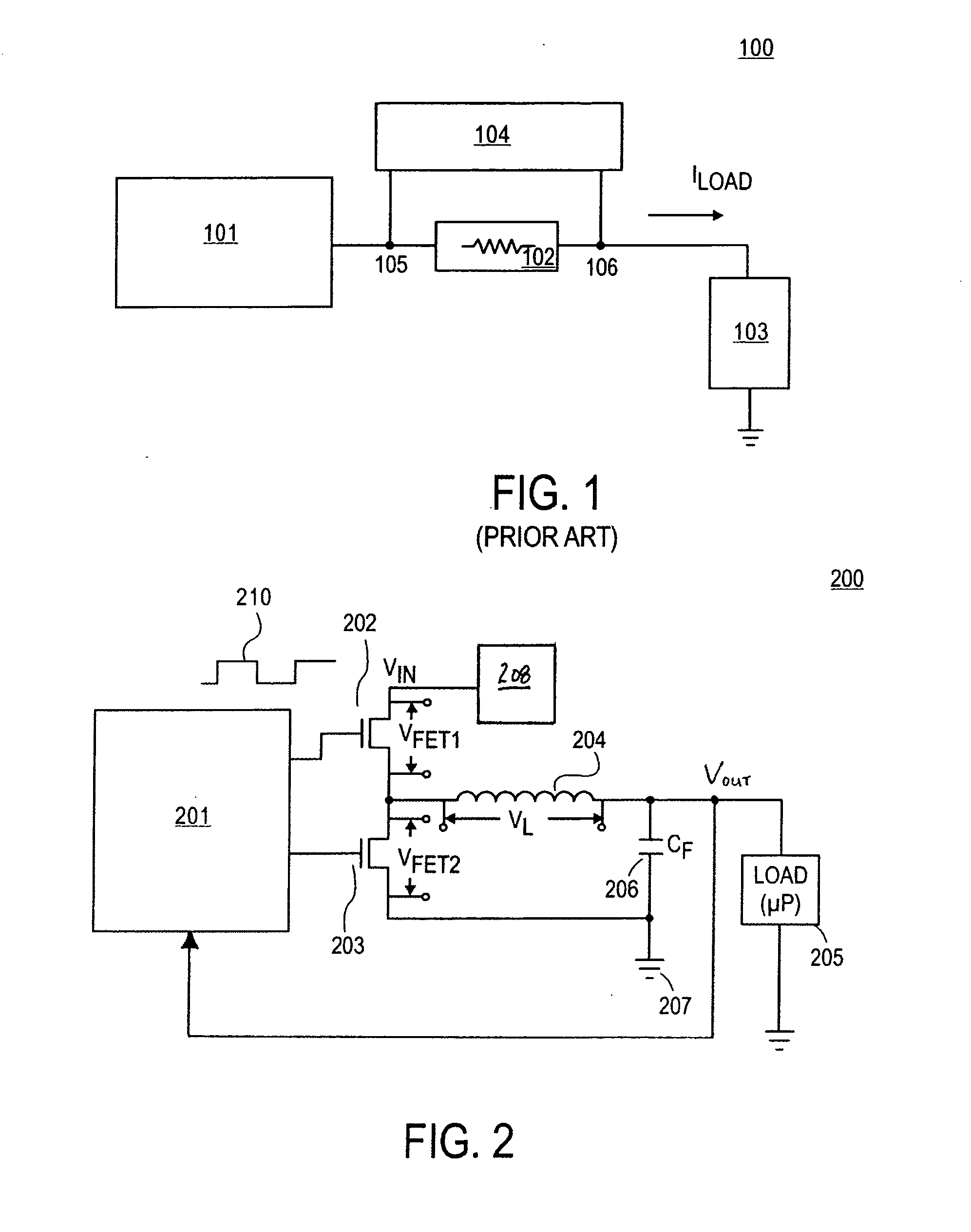

Methods and apparatuses for calibrating sensors

InactiveUS20080040055A1Accurate predictionMaximize probabilityTesting/calibration apparatusTesting/calibration of speed/acceleration/shock measurement devicesData processing systemElectronic load

Methods and apparatuses to perform calibration of imprecise sensors for power monitoring in a data-processing system are described. The system includes a load coupled to one or more sensors. An electronic load changes a first input signal through one or more sensors by a predetermined amount. A difference in an output signal from the one or more sensors in response to the changing is obtained. The output signal is measured and sampled. A distribution of samples of the output signal is determined. The estimated parameters of the distribution that most likely to explain actual data are determined. Next, a transfer function of the one or more sensors is determined based on the estimated parameters. The input signal through the load is accurately predicted using the transfer function of the one or more sensors to monitor the power usage by the load.

Owner:APPLE INC

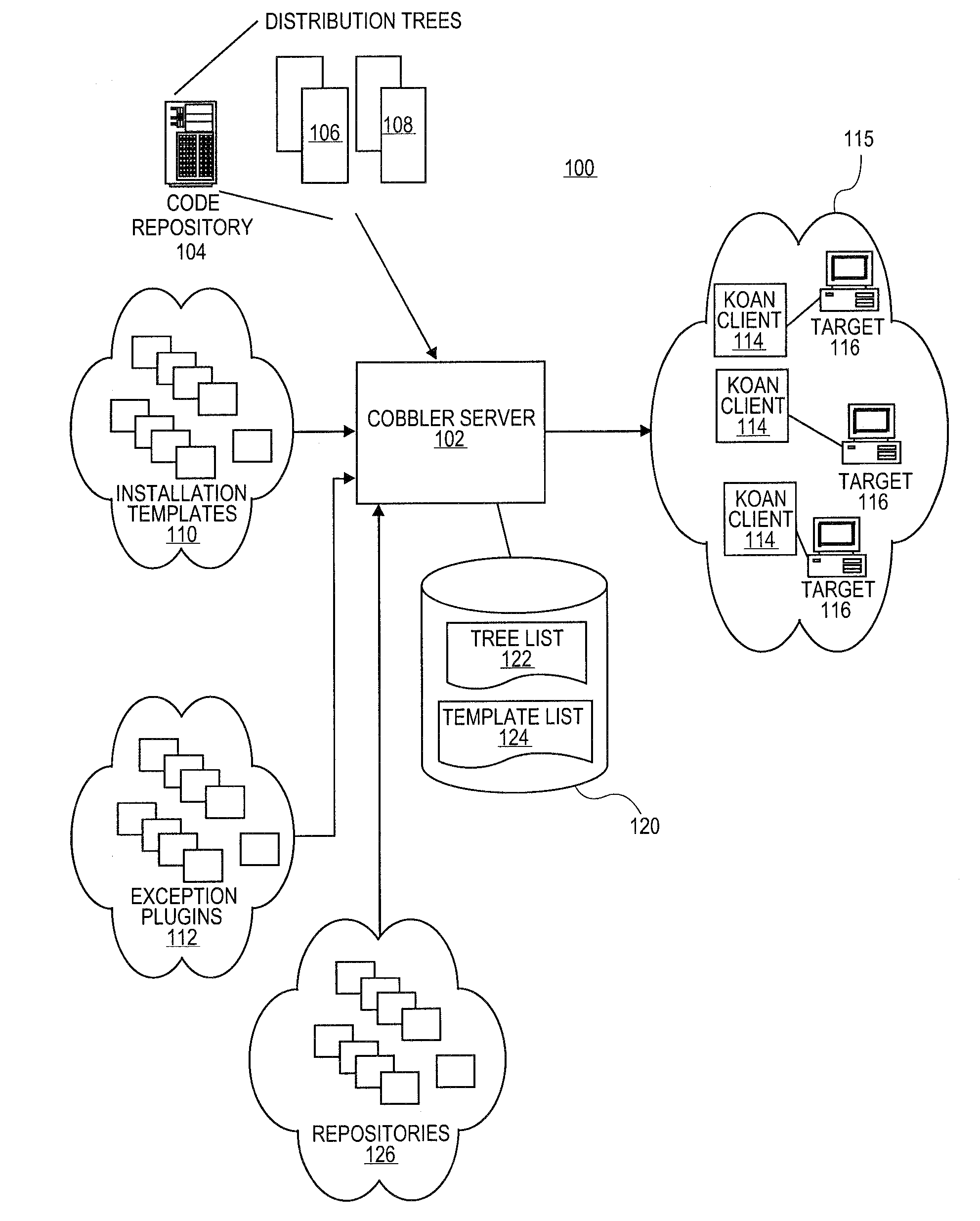

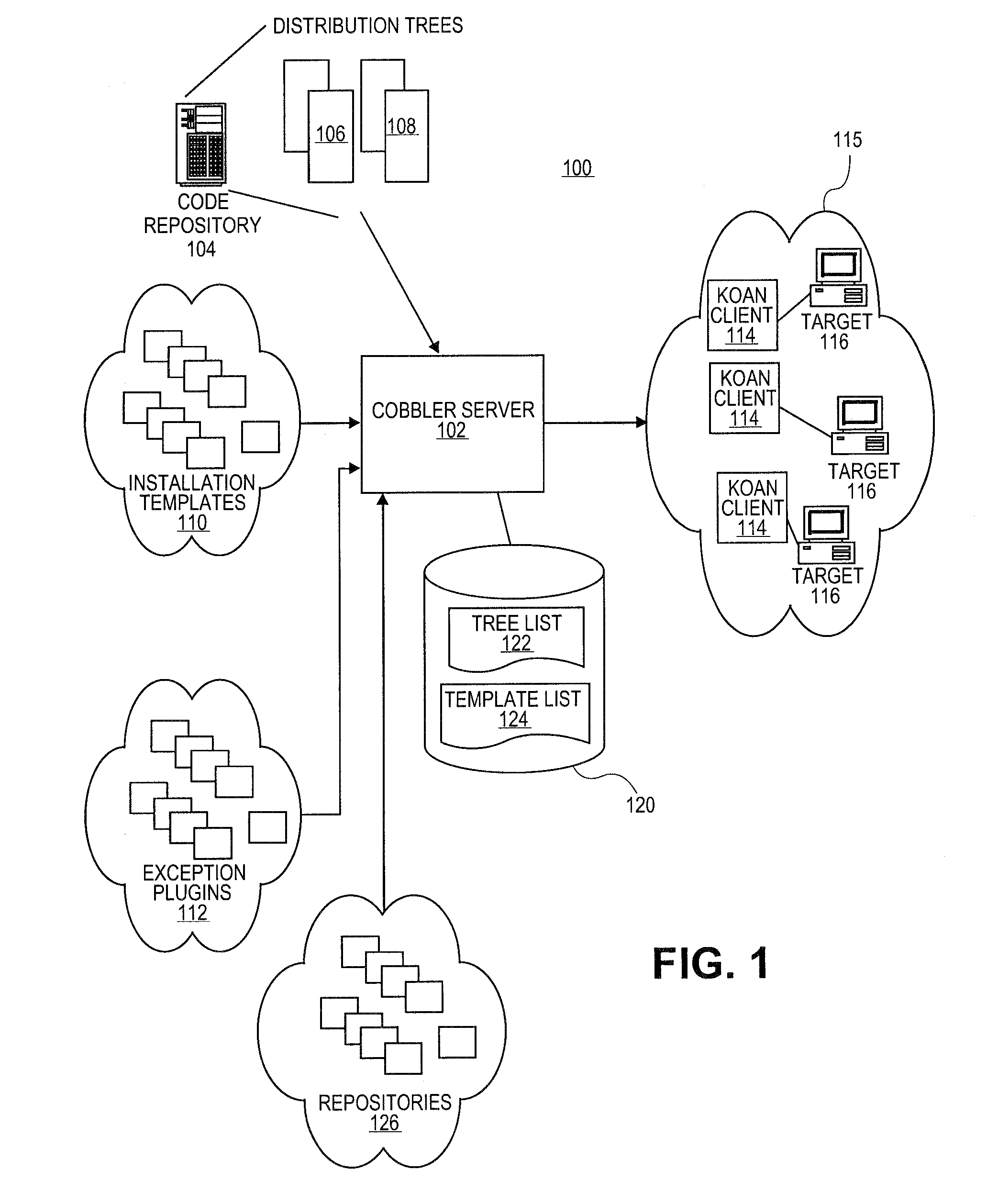

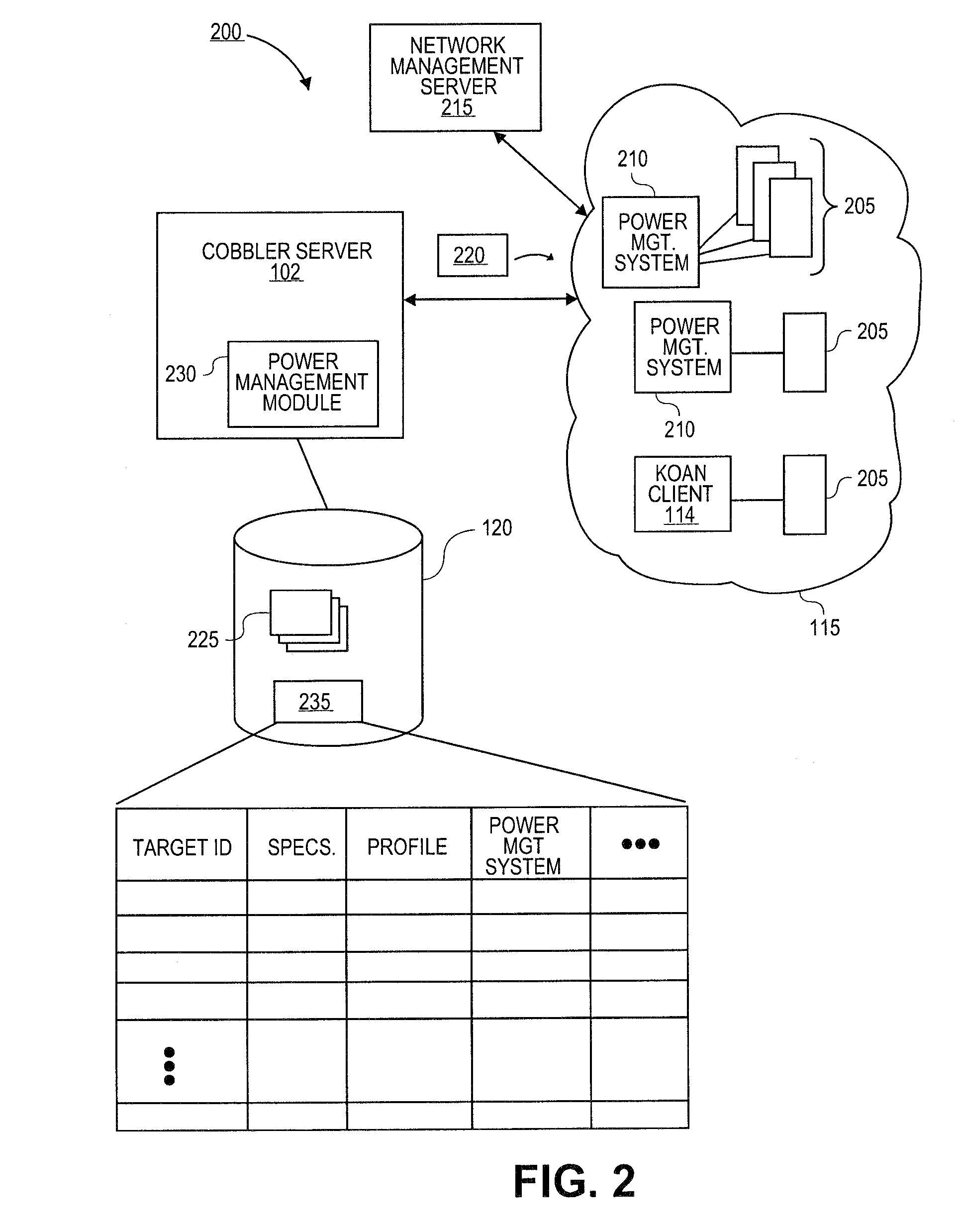

Methods and systems for providing a rescue environment in a software provisioning environment

A provisioning server can remotely deliver a rescue environment to a malfunctioning target machine. The provisioning server can operate in conjunction with a network management server in order to identify malfunctioning target machines, for example, target machines with damaged operating systems. Once a malfunctioning target machine is identified, the provisioning server can be configured to identify a rescue environment to repair the malfunctioning target machine and provide the rescue environment to the malfunctioning target machine.

Owner:RED HAT

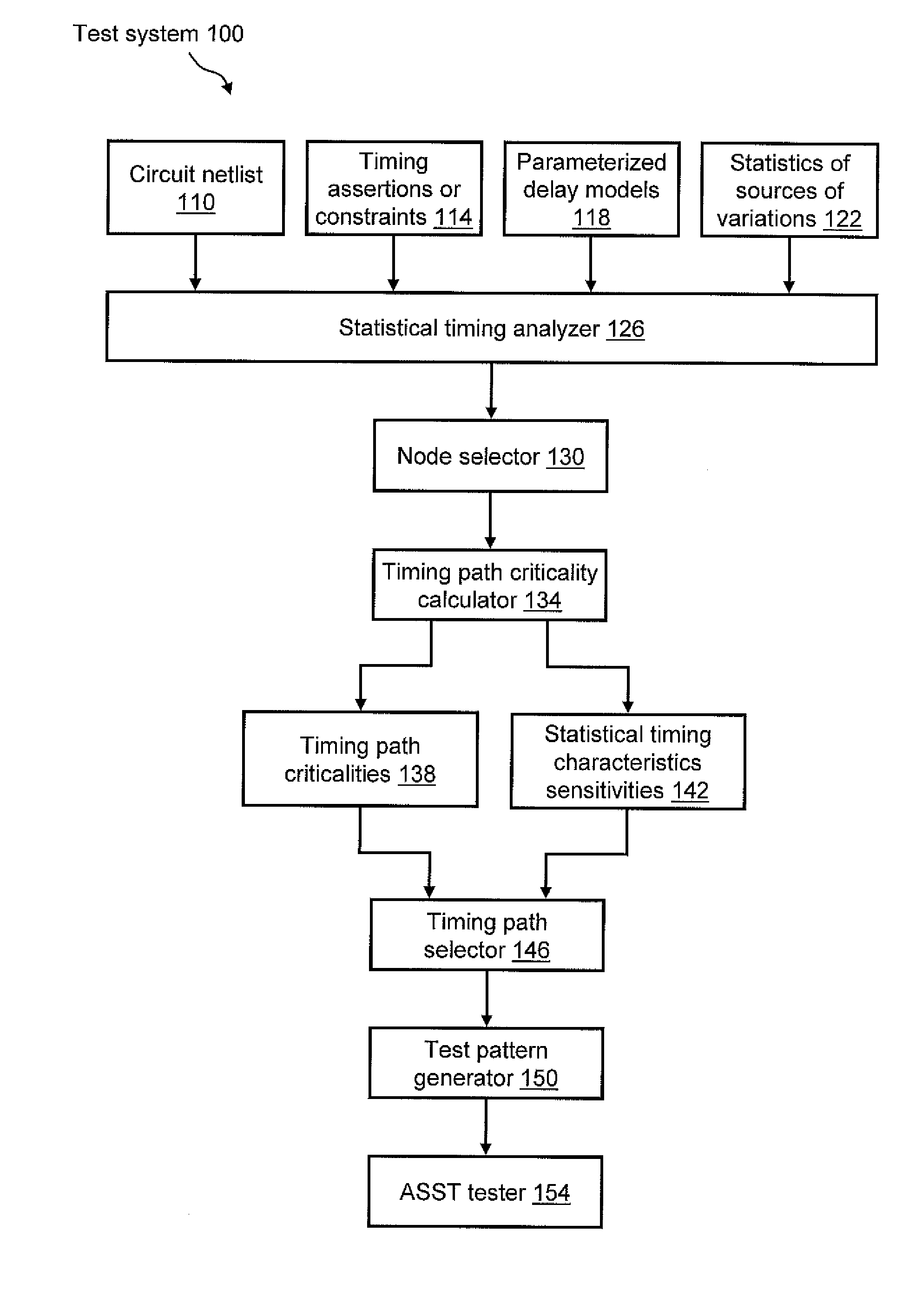

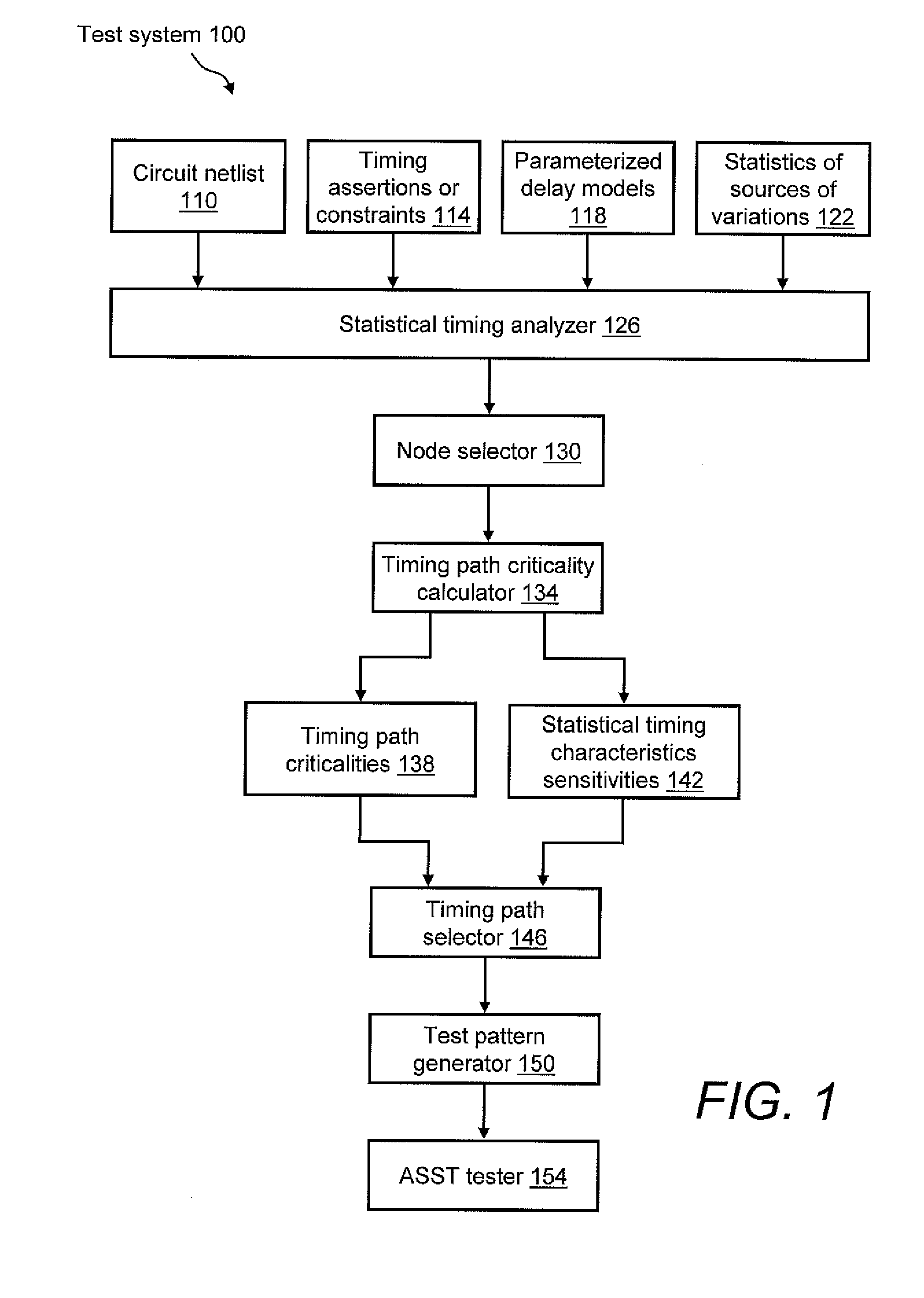

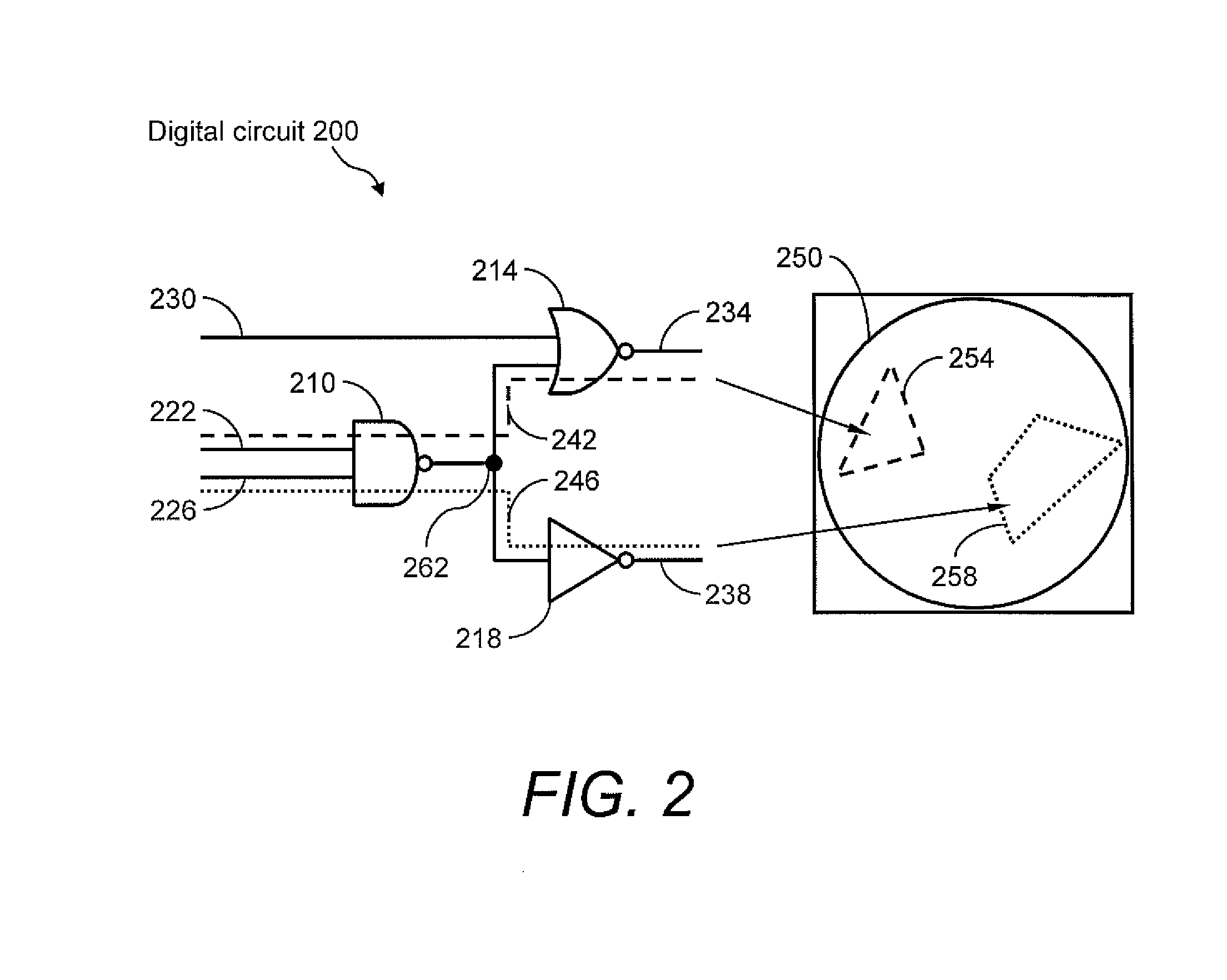

System and method for generating at-speed structural tests to improve process and environmental parameter space coverage

A system for enhancing the practicability of at-speed structural testing (ASST). In one embodiment, the system includes first means for performing statistical timing analysis on a design of logic circuitry. A second means performs a criticality analysis on the logic circuitry as a function of the statistical timing analysis so as to determine a criticality probability for each node of the logic circuitry. A third means selects nodes of the logic circuitry as a function of the criticality analysis. A fourth means selects timing paths as a function of the criticality probabilities of the selected nodes. A fifth means generates an ASST pattern for each of the selected timing paths. A sixth mean is provided to perform ASST on a fabricated instantiation of the design at functional speed using the generated ASST pattern.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

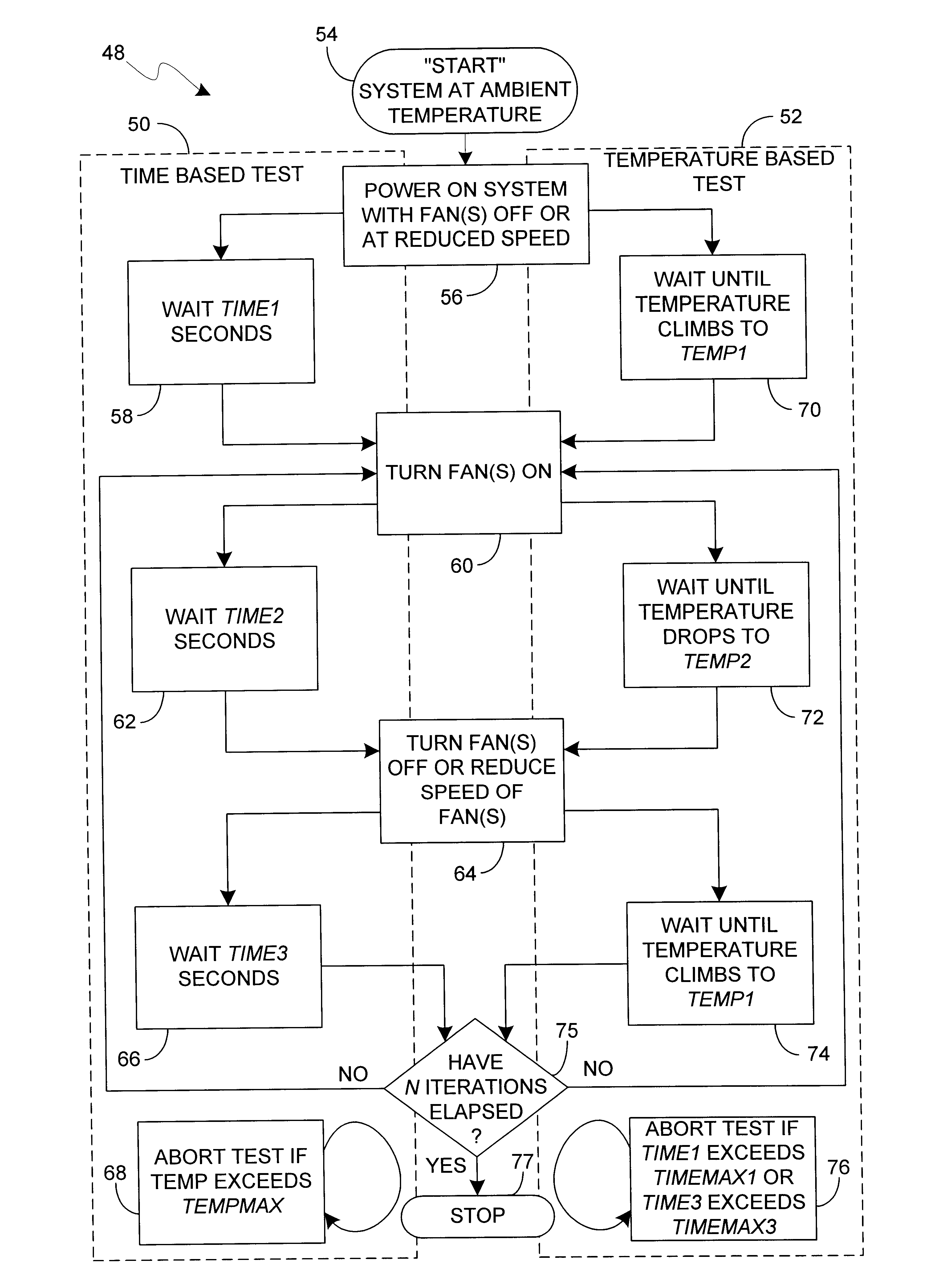

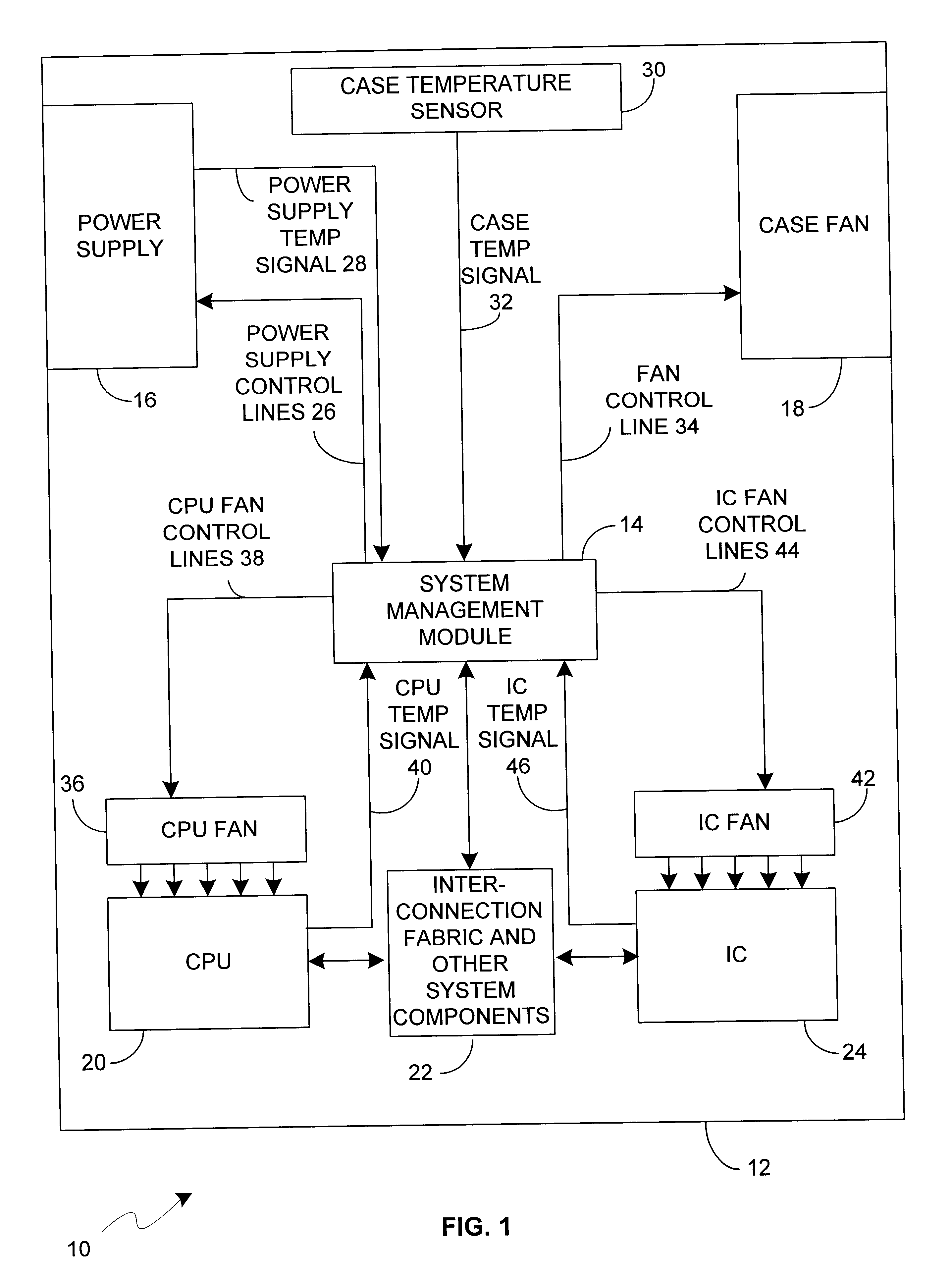

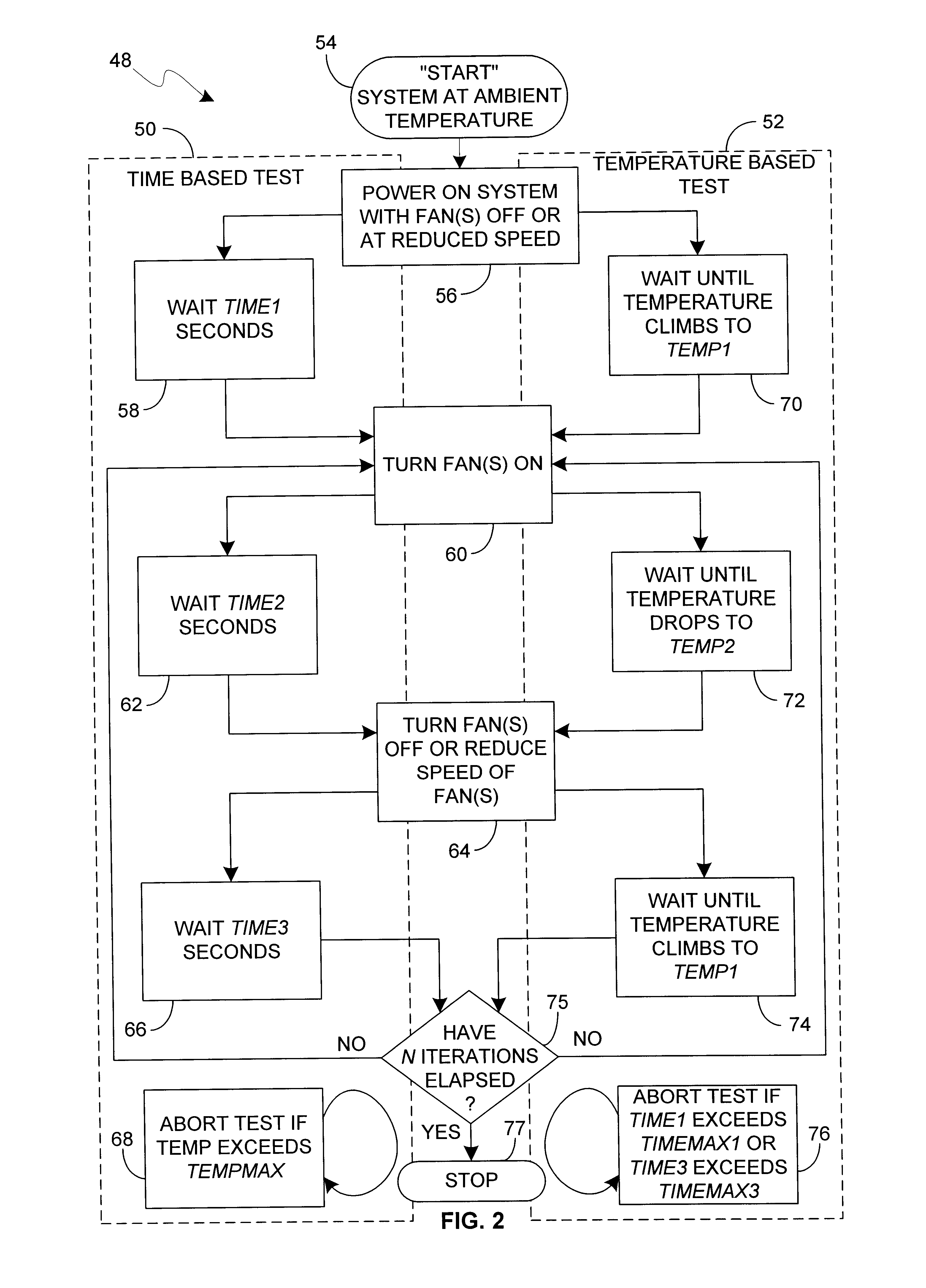

Method and apparatus for controlling fans and power supplies to provide accelerated run-in testing

InactiveUS6901303B2Quality improvementLow costSafety arrangmentsTemperatue controlComputerized systemEngineering

A method and apparatus controls fans and power supplies to provide accelerated run-in testing. By modulating fans to increase case temperatures and adjusting power supplies to provide “worst case” voltages, a computer system can be subjected to a run-in tests under taxing conditions. By alternately cooling and heating devices such as CPUs, devices can be subjected to mechanical stresses associated with power-on / power off cycles. A time based test implements the present invention based on time, and a temperature based test implements the present invention based on temperature. The present invention can be used to implement a run-in test in which the computer system is operated at an elevated temperature, thereby achieving results similar to those achieved by performing a run-in test in an environmental chamber at an elevated temperature. Alternatively, the a run-in test can be performed by repeatedly cycling the temperature between relatively high and low values.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

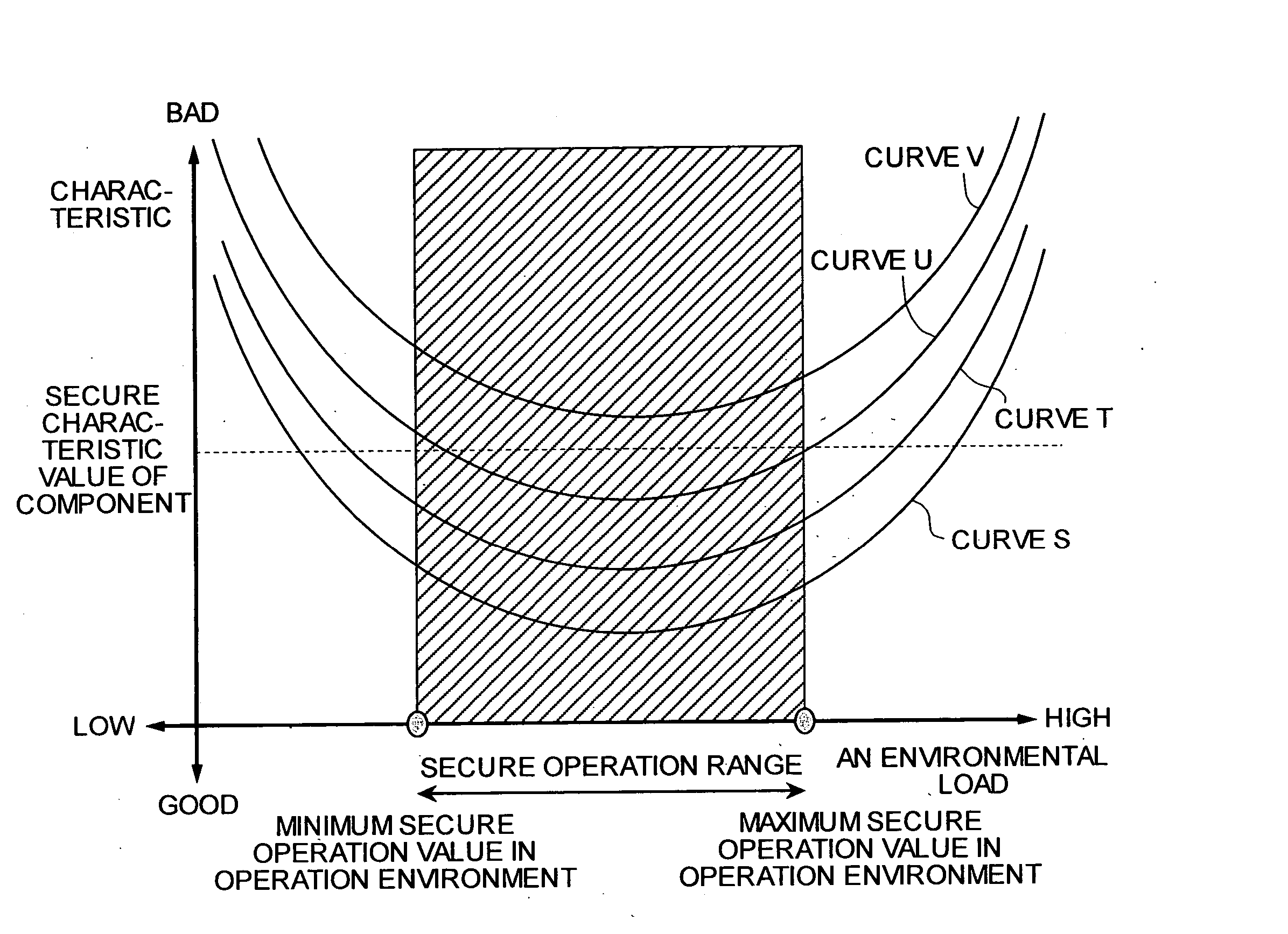

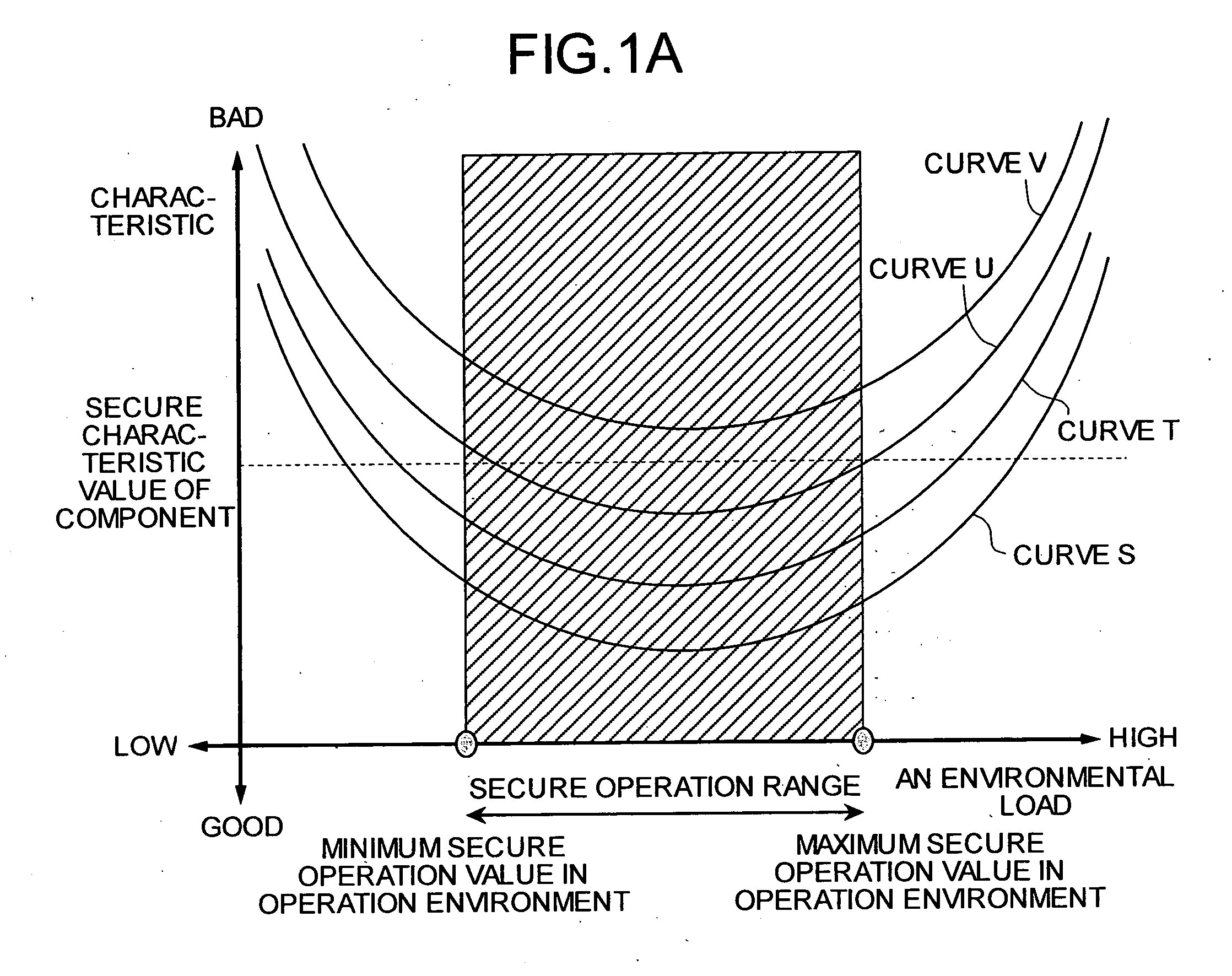

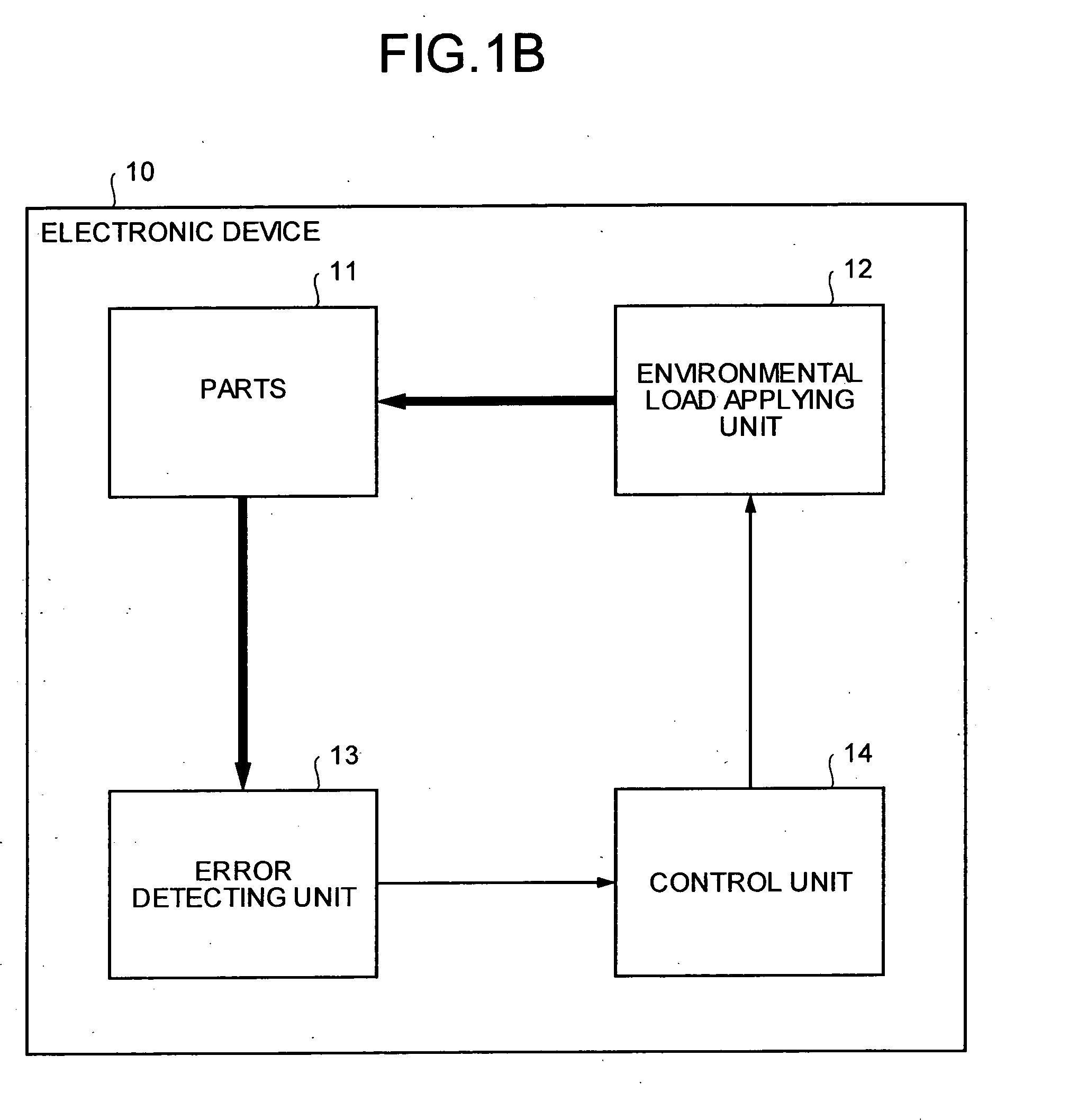

Electronic device, failure prediction method, and computer product

InactiveUS20050193284A1Solve problemsMarginal checkingElectrical testingPredictive methodsComputer science

Owner:FUJITSU LTD

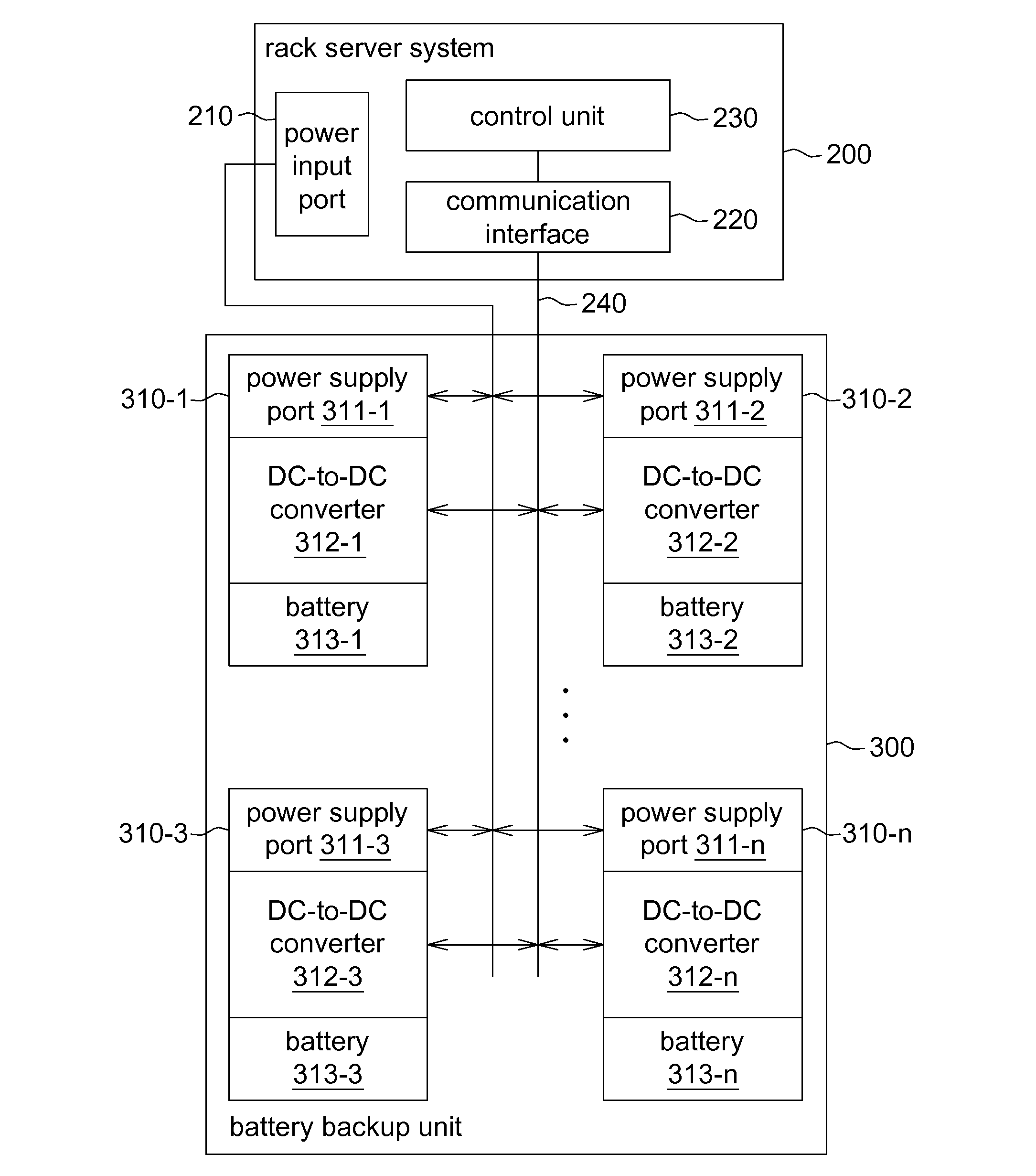

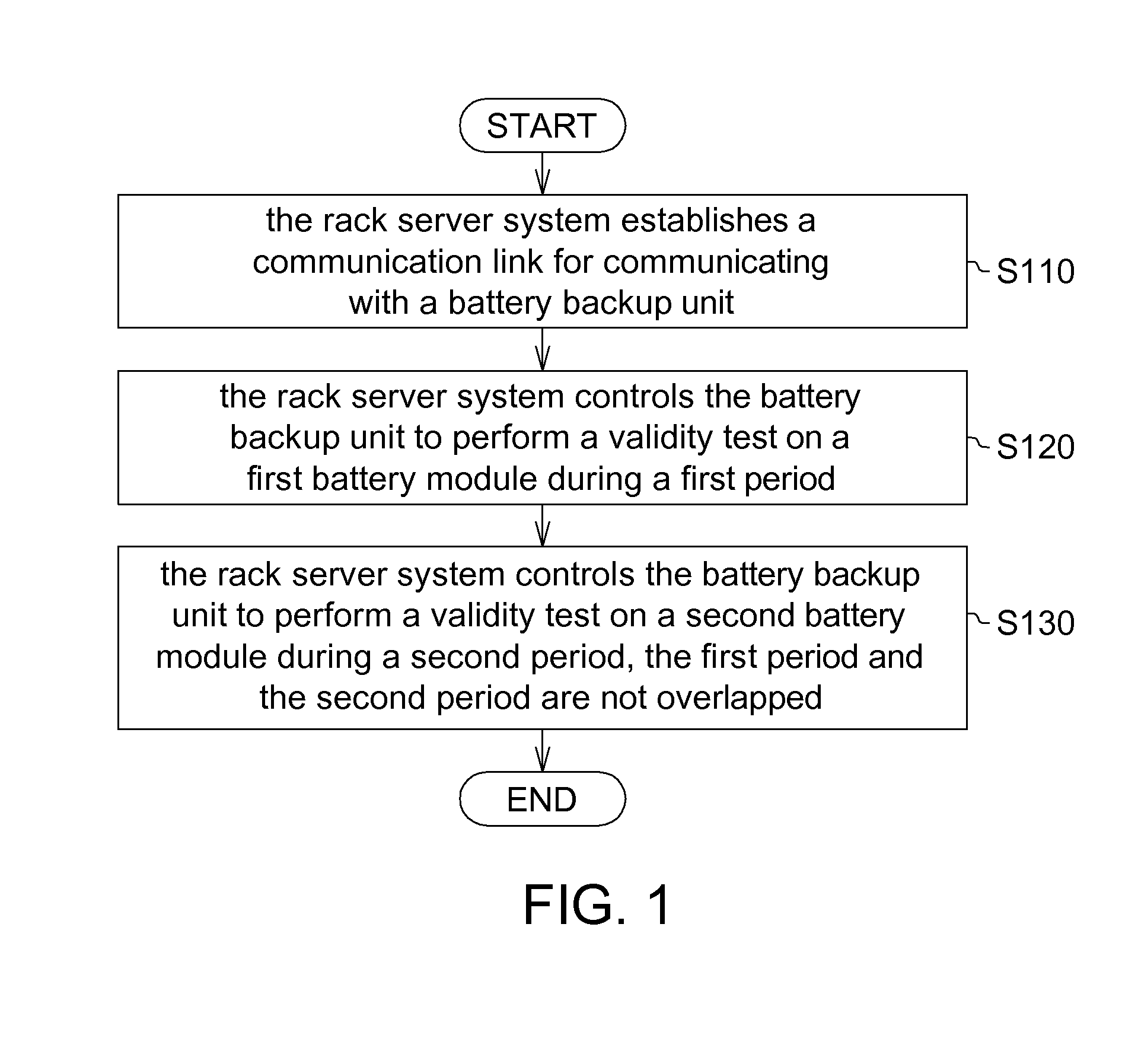

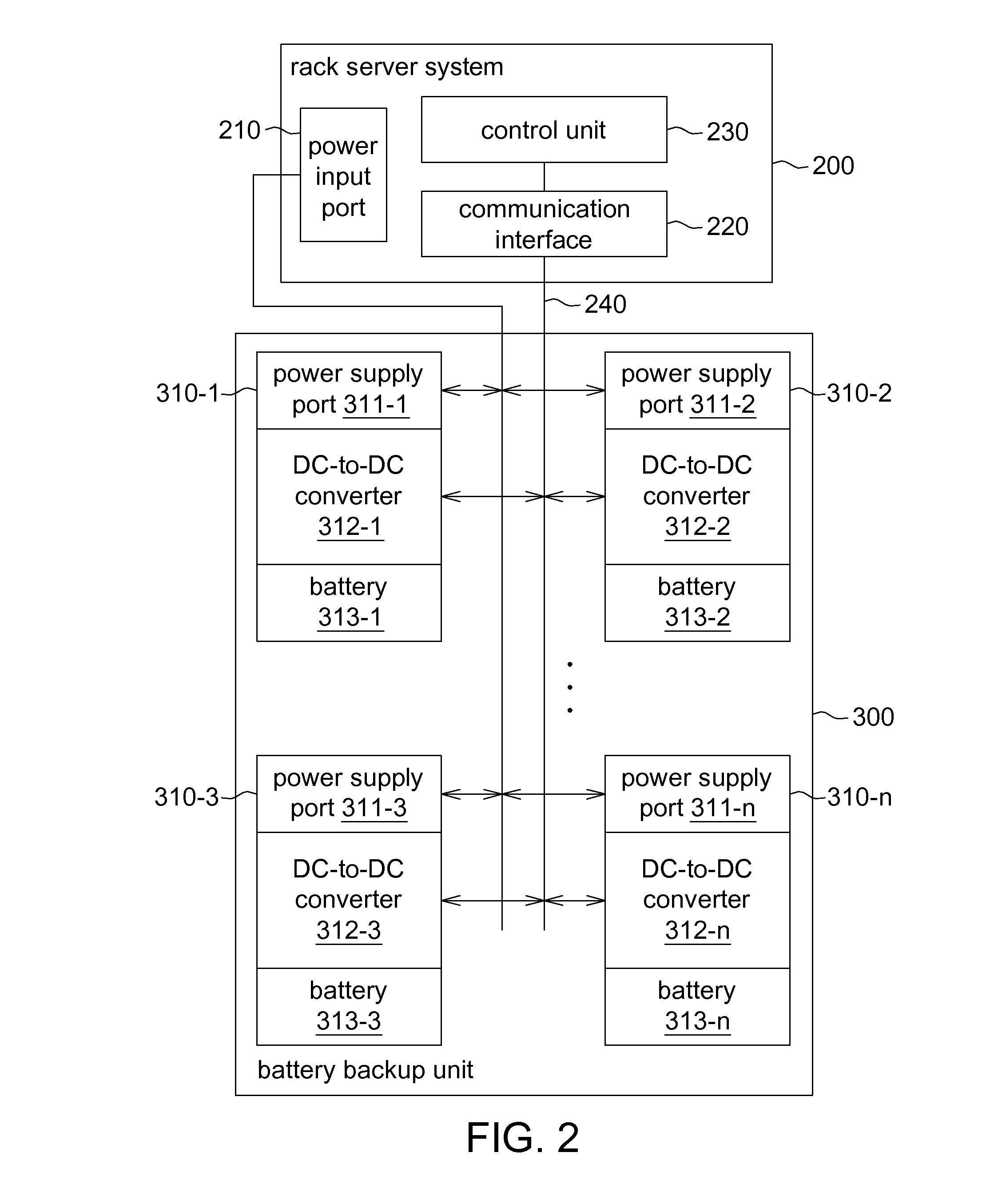

Rack server system and control method thereof

ActiveUS20130030735A1Reduce riskMarginal checkingElectrical testingTelecommunications linkEngineering

A rack server system and a control method thereof are provided. The rack server system establishes a communication link for communicating with a battery backup unit. The battery backup unit is connected to a power input port of the rack server system, and includes a number of battery modules connected with each other in parallel. The rack server system controls the battery backup unit to perform validity test on a first battery module during a first period and to perform validity test on a second battery module during a second period, wherein the first period and the second period are not overlapped with each other.

Owner:QUANTA COMPUTER INC

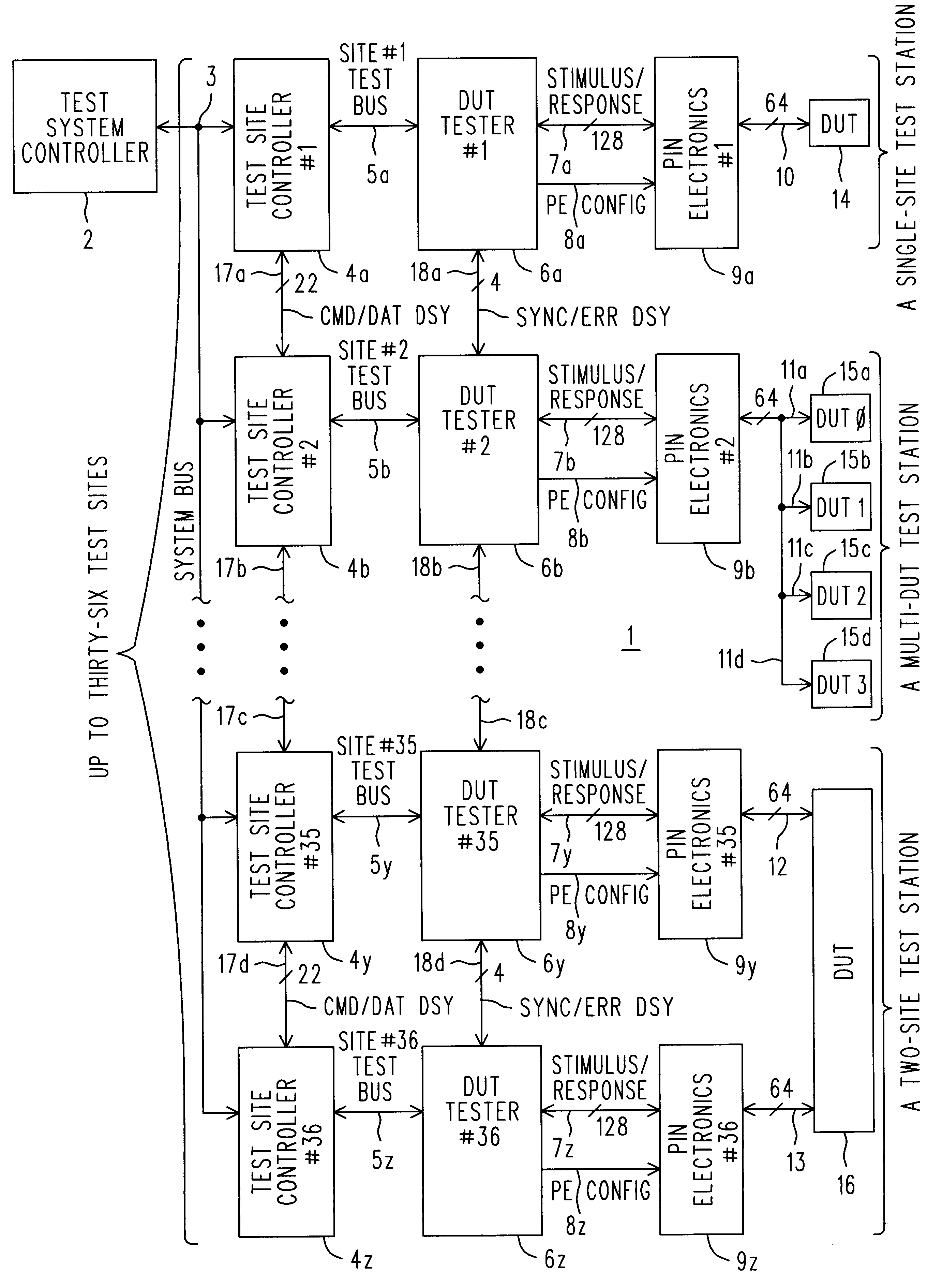

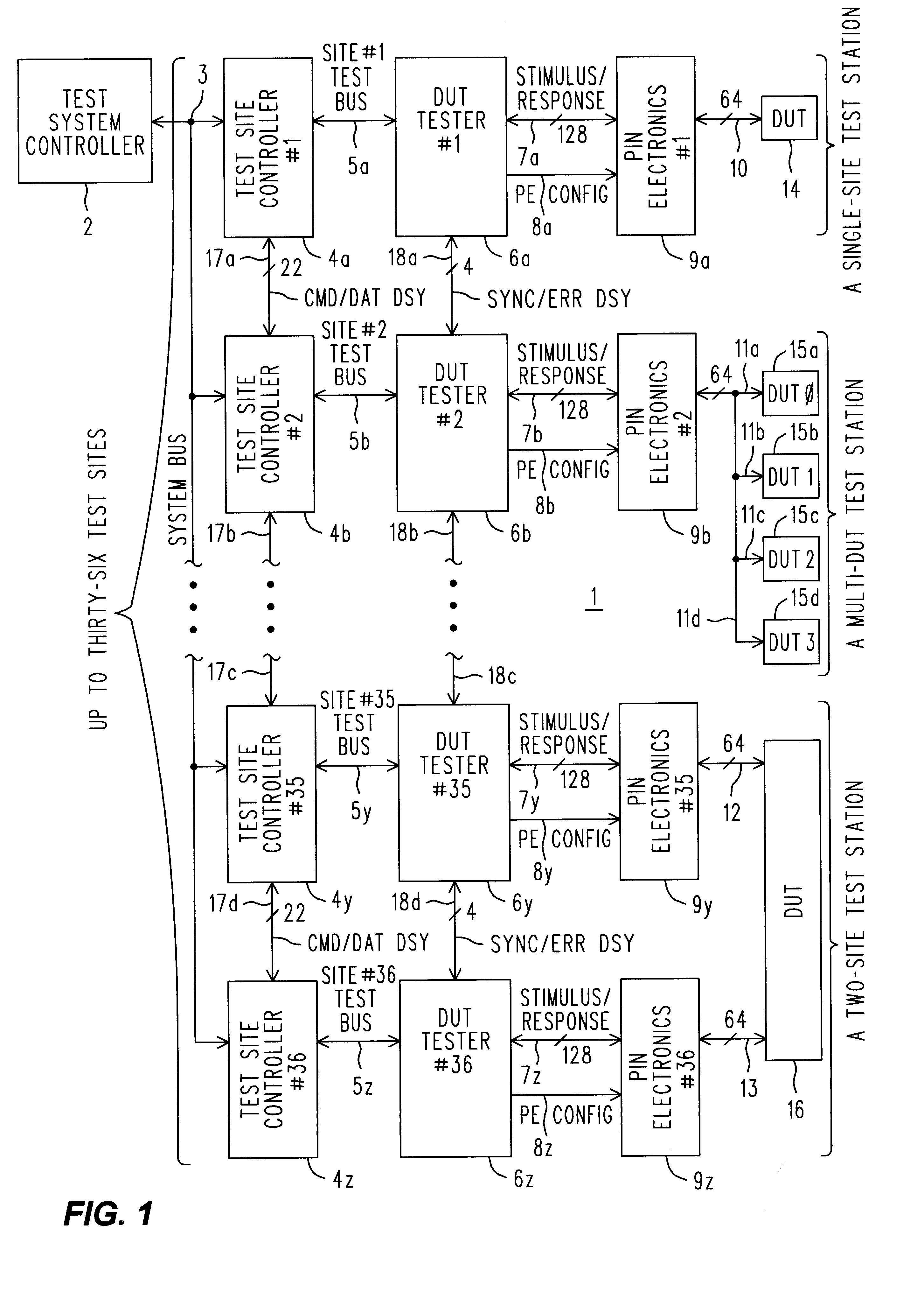

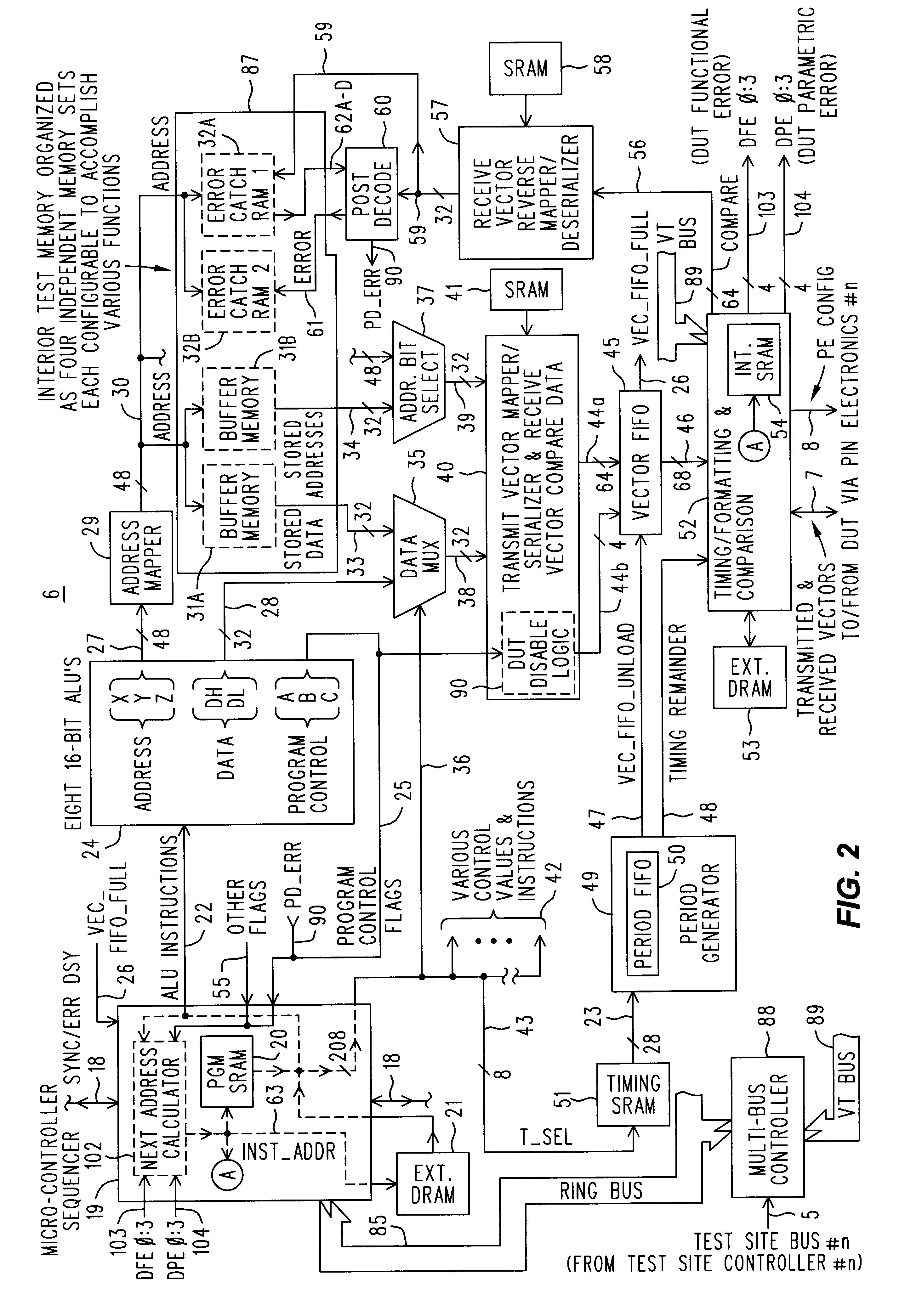

Algorithmically programmable memory tester with history FIFO's that aid in error analysis and recovery

InactiveUS6574764B2Increase overheadDigital circuit testingMarginal checkingMemory testerTester device

The problem is to branch back to an appropriate location within a memory tester test program, and also restore its state of algorithmic control, when an error associated therewith occurs later in time at the DUT. Owing to delays in pipelines connecting the program execution environment to the DUT and back again. These delays allow the program to arbitrarily advance beyond where the stimulus was given. The arbitrary advance makes it difficult to determine the exact circumstances that were associated with the error. A branch based on the error signal can restart a section of the test program, but it is likely only a template needing further test algorithm control information that varies dynamically as the test program executes. The solution is to equip the memory tester with History FIFO's whose depths are adjusted to account for the sum of the delays of the pipelines, relative to the location of that History FIFO. When the error flag is generated the desired program location and state information is present at the bottom of an appropriate History FIFO.

Owner:ADVANTEST CORP

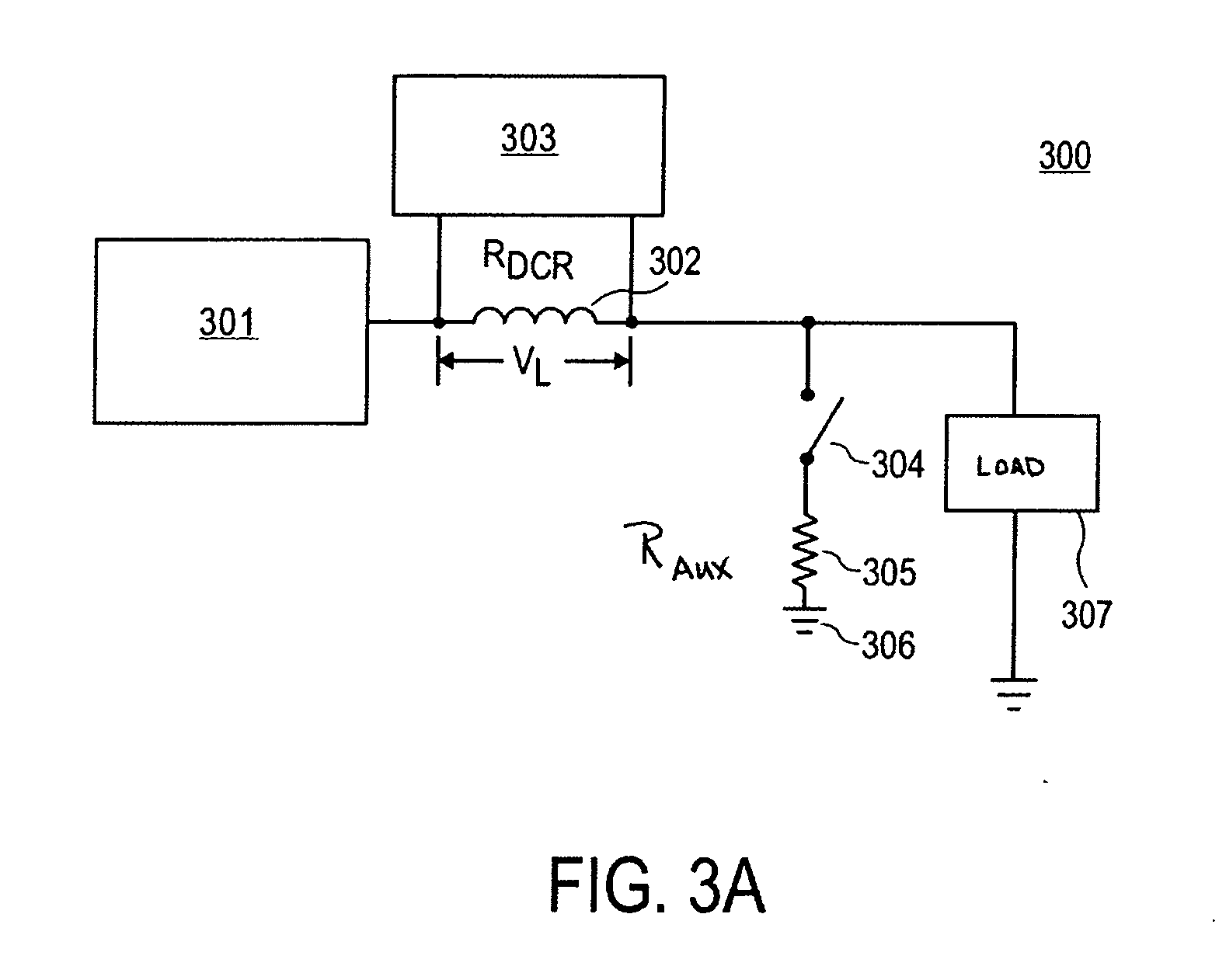

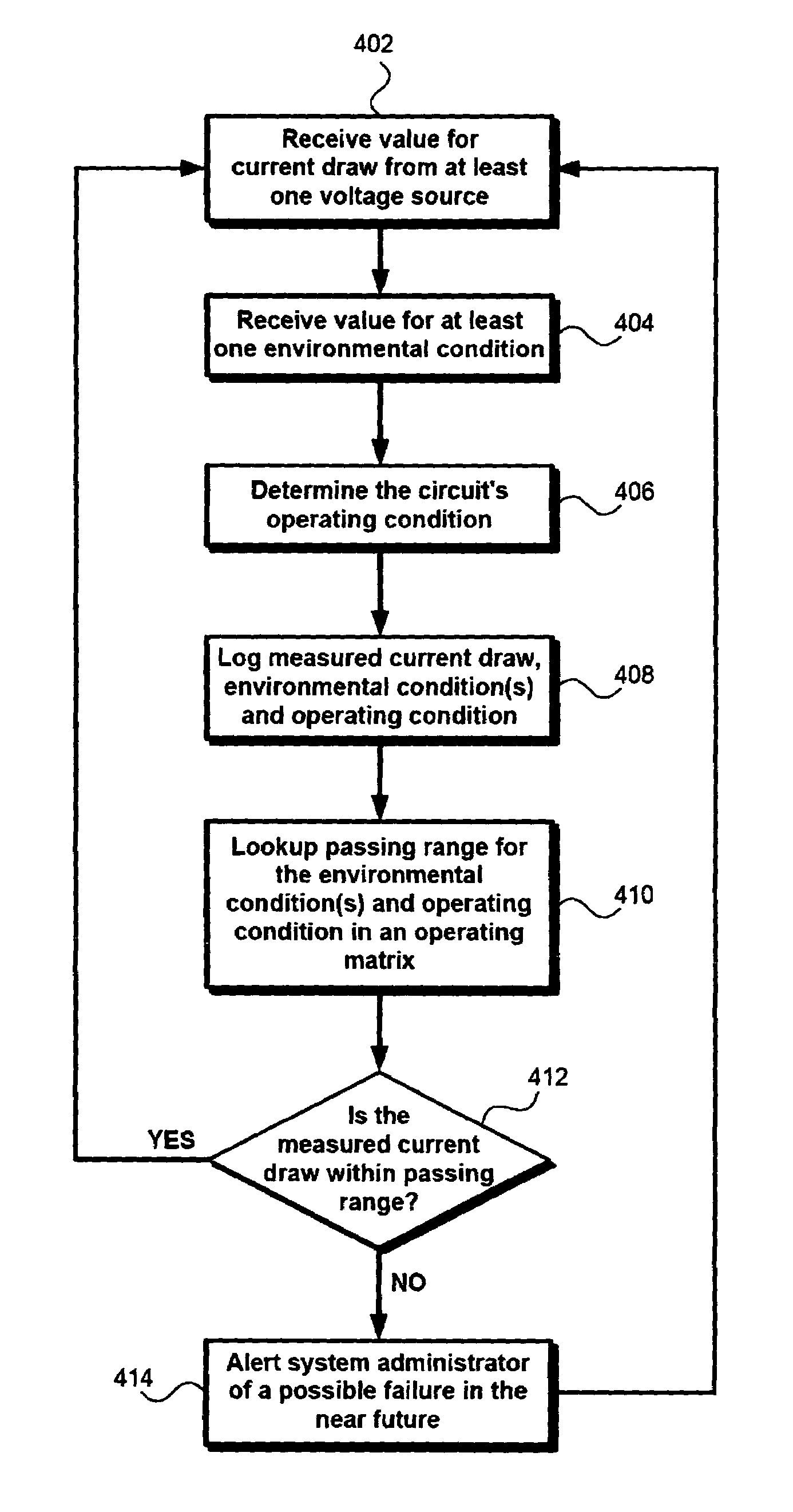

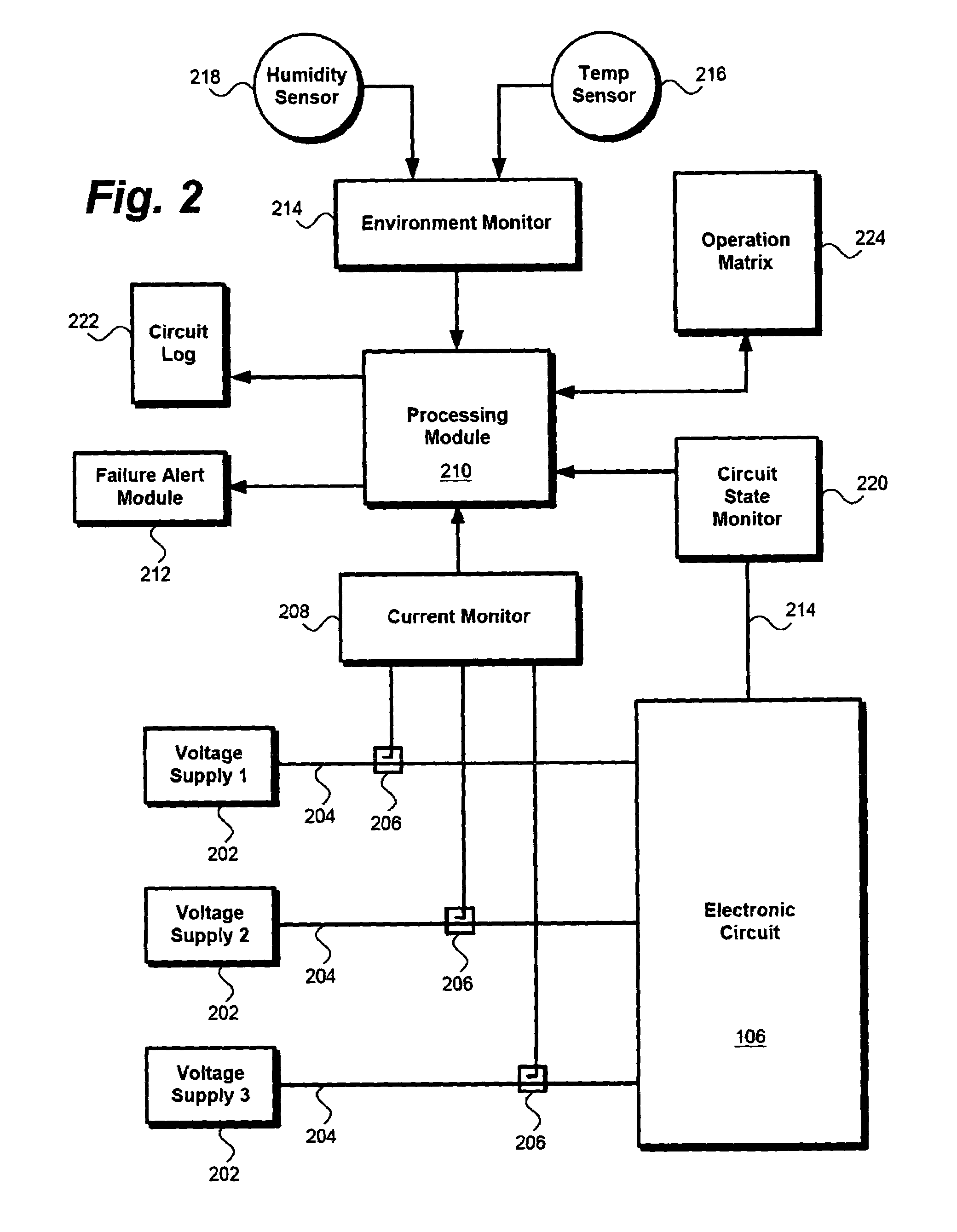

Predictive failure analysis and failure isolation using current sensing

InactiveUS7003409B2Reduce downtimeElectric devicesVolume/mass flow measurementPredictive failure analysisOperant conditioning

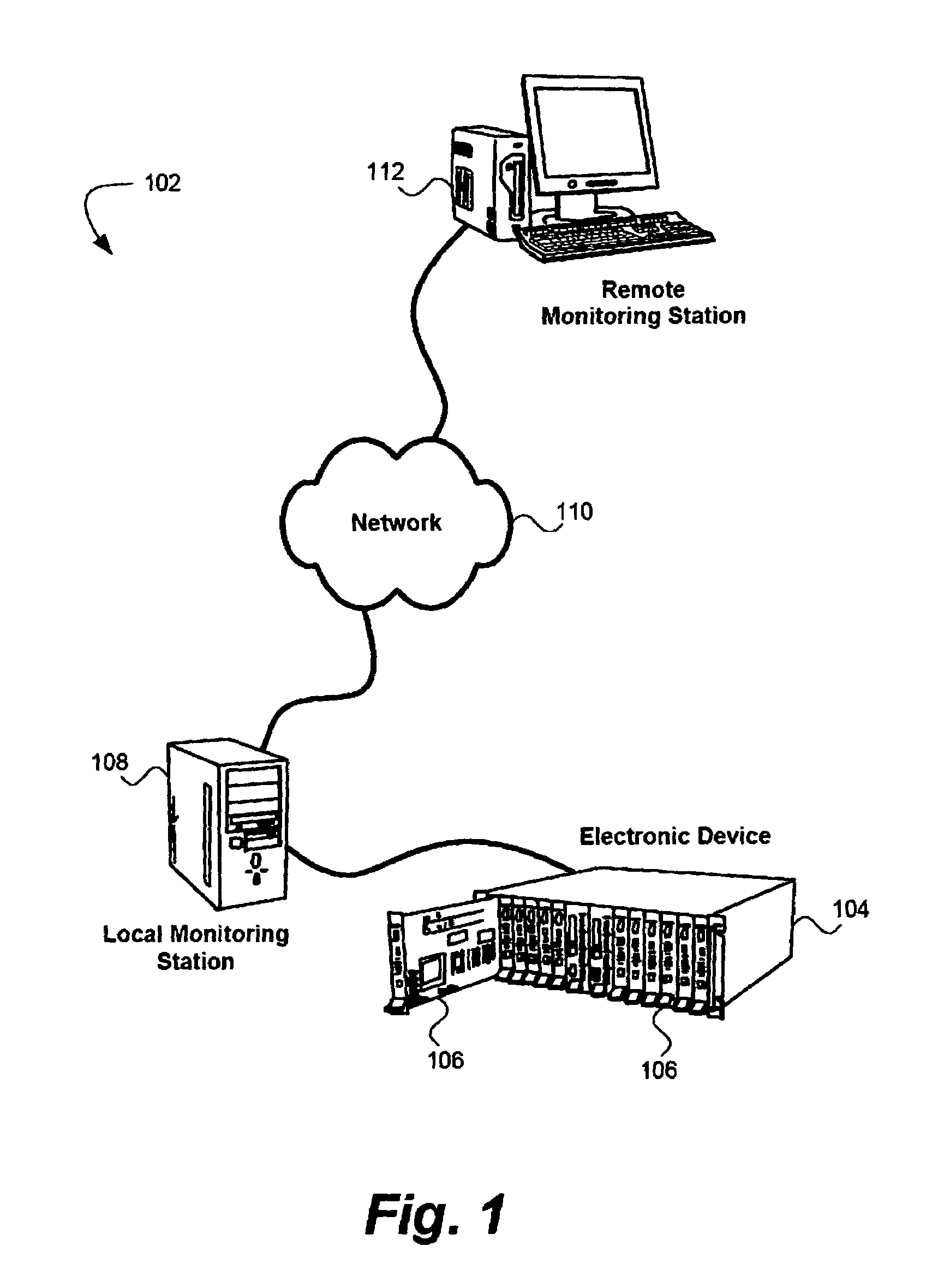

A method, system, and computer program for predicting the failure of an electronic circuit. One embodiment of the invention monitors the current utilization, environment conditions, and operating conditions of the electronic circuit. A system manager is altered if the current utilization of the electronic circuit is outside a pass range at the measured environmental conditions and the measured operating conditions of the electronic circuit. The invention may also be configured such that if the electronic circuit fails, the electronic circuit is isolated from among a plurality of potentially failed electronic circuits using the measured current utilization, environment conditions, and operating conditions of the electronic circuit.

Owner:UNILOC 2017 LLC

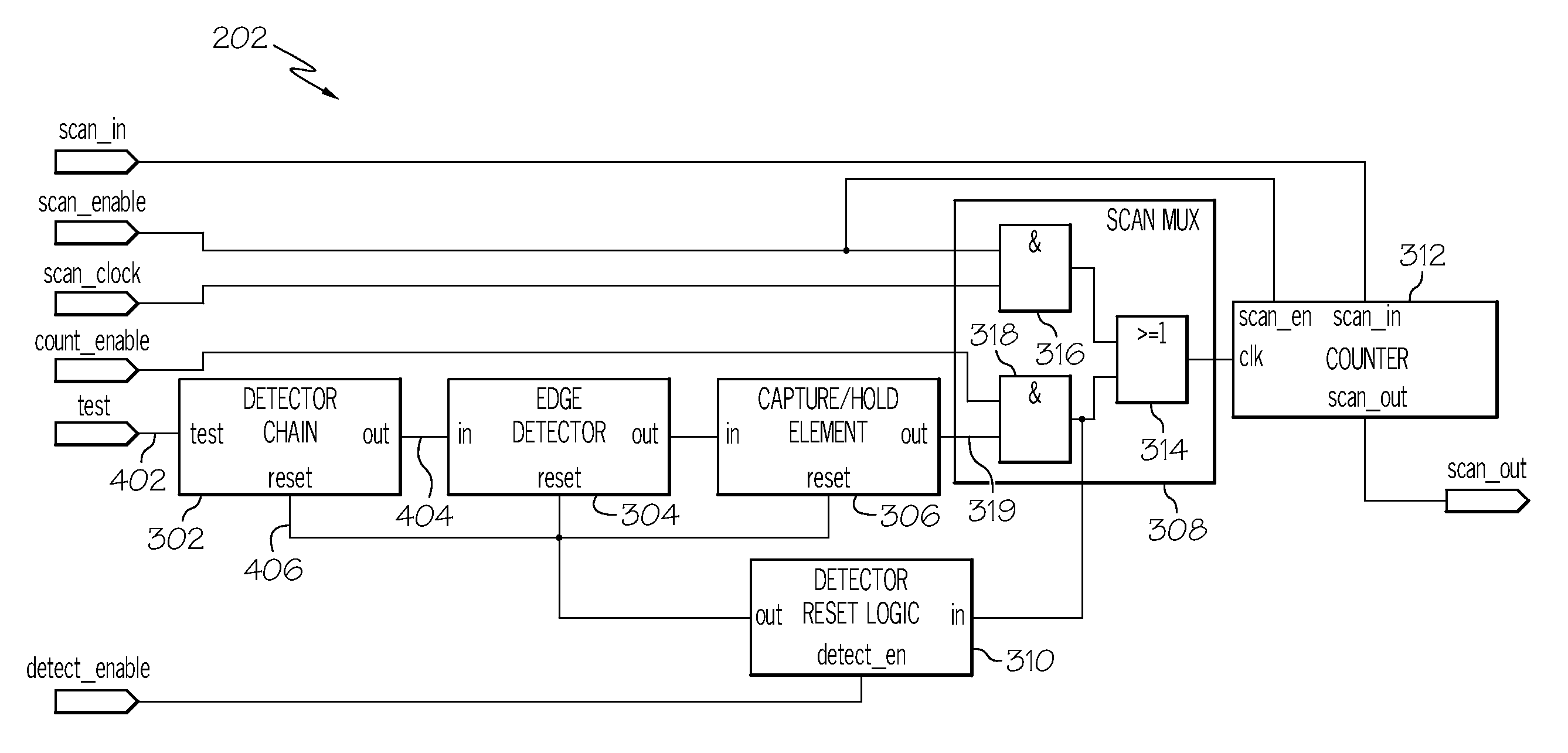

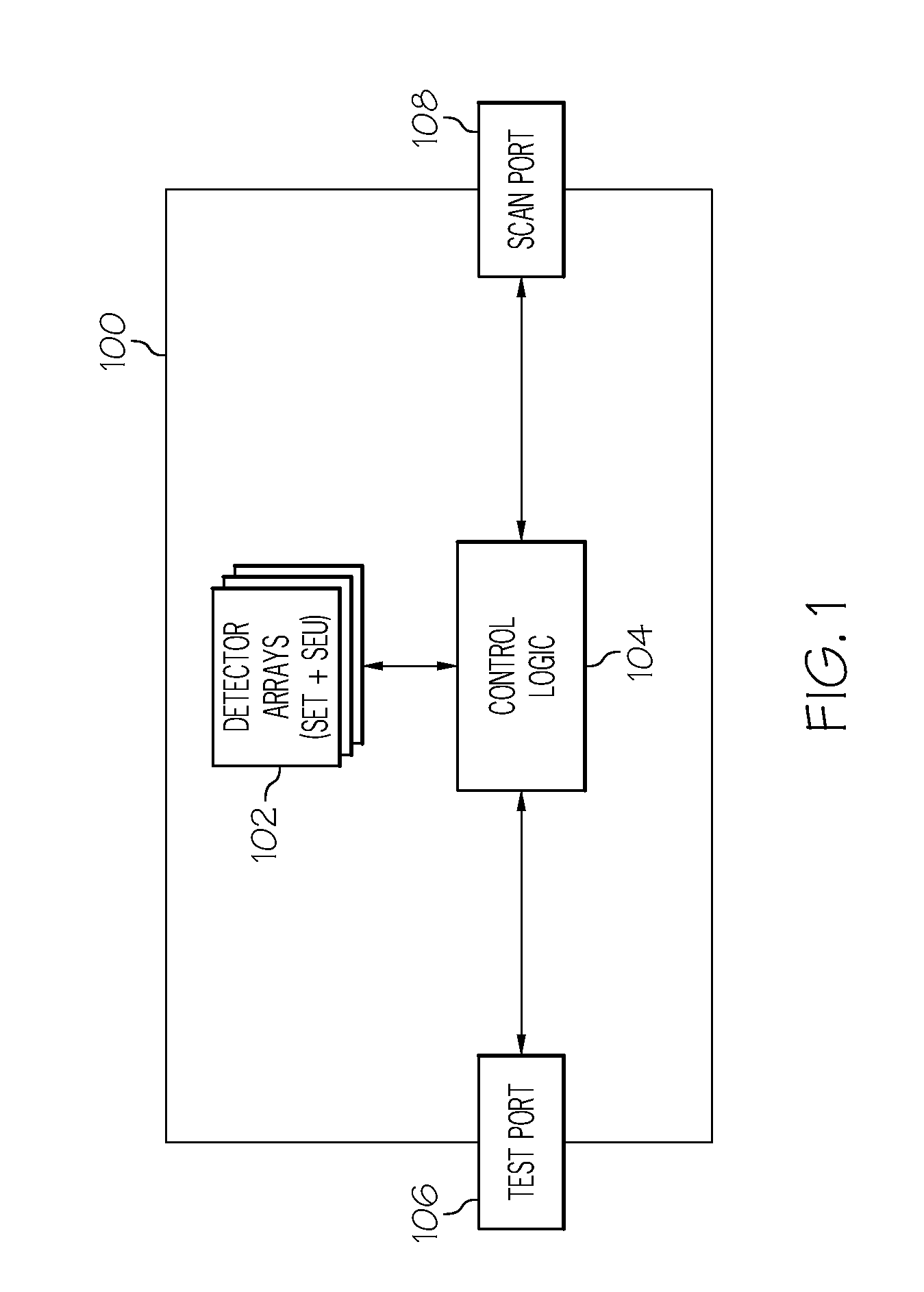

Soft error rate detector

The soft error rate (SER) detector circuit presented here can be used to measure SER in combinatorial logic devices caused by radiation. The SER detector circuit includes a plurality of detector arrays coupled in series, and each having a plurality of SER test structures coupled in series. Each of the SER test structures includes a plurality of detector elements coupled in series. Each of the SER test structures is configured to detect single event transients (SETs) in a first operating mode and single event upsets (SEUs) in a second operating mode. The SER detector circuit also has control logic elements to control operation of the plurality of detector arrays.

Owner:GLOBALFOUNDRIES US INC

Popular searches

Solid-state devices Record information storage Fault location by increasing destruction at fault Semiconductor devices Individual semiconductor device testing Internal/peripheral component protection Error avoidance Programme control in sequence/logic controllers Special data processing applications Microprogram loading