Systems and methods for facilitating testing of pad drivers of integrated circuits

a technology of integrated circuits and pad drivers, which is applied in the field of integrated circuits, can solve the problems of imposing other testing restrictions, limiting the number of ic pins (or pads) that can be tested by a particular ate, and oftentimes being cost prohibitive to provide an ate with an appropriately high pin count and/or an appropriately high operating frequency in order to eliminate the aforementioned deficiencies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Reference will now be made in detail to the description of the invention as illustrated in the drawings with like numerals indicating like parts throughout the several views.

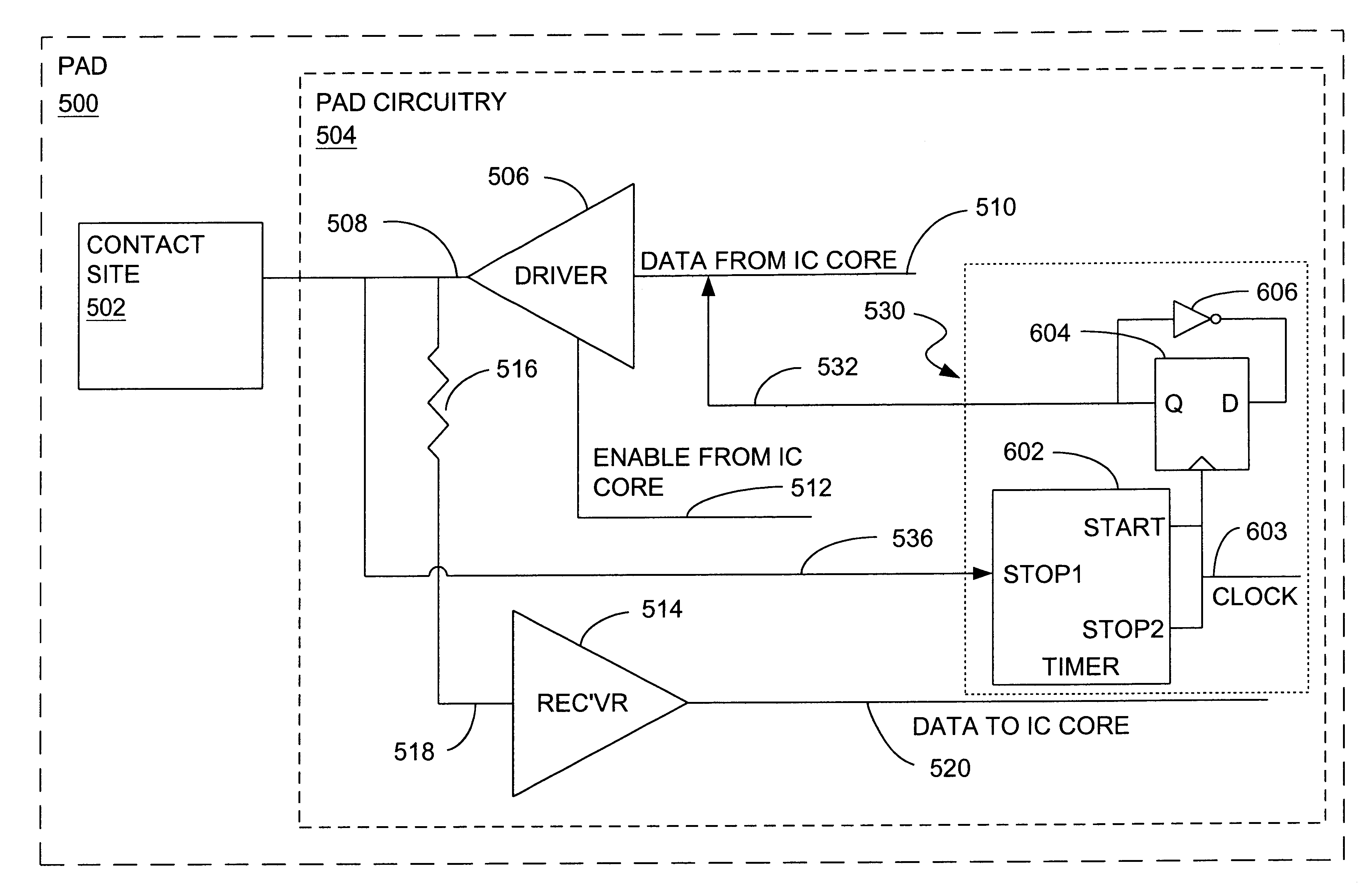

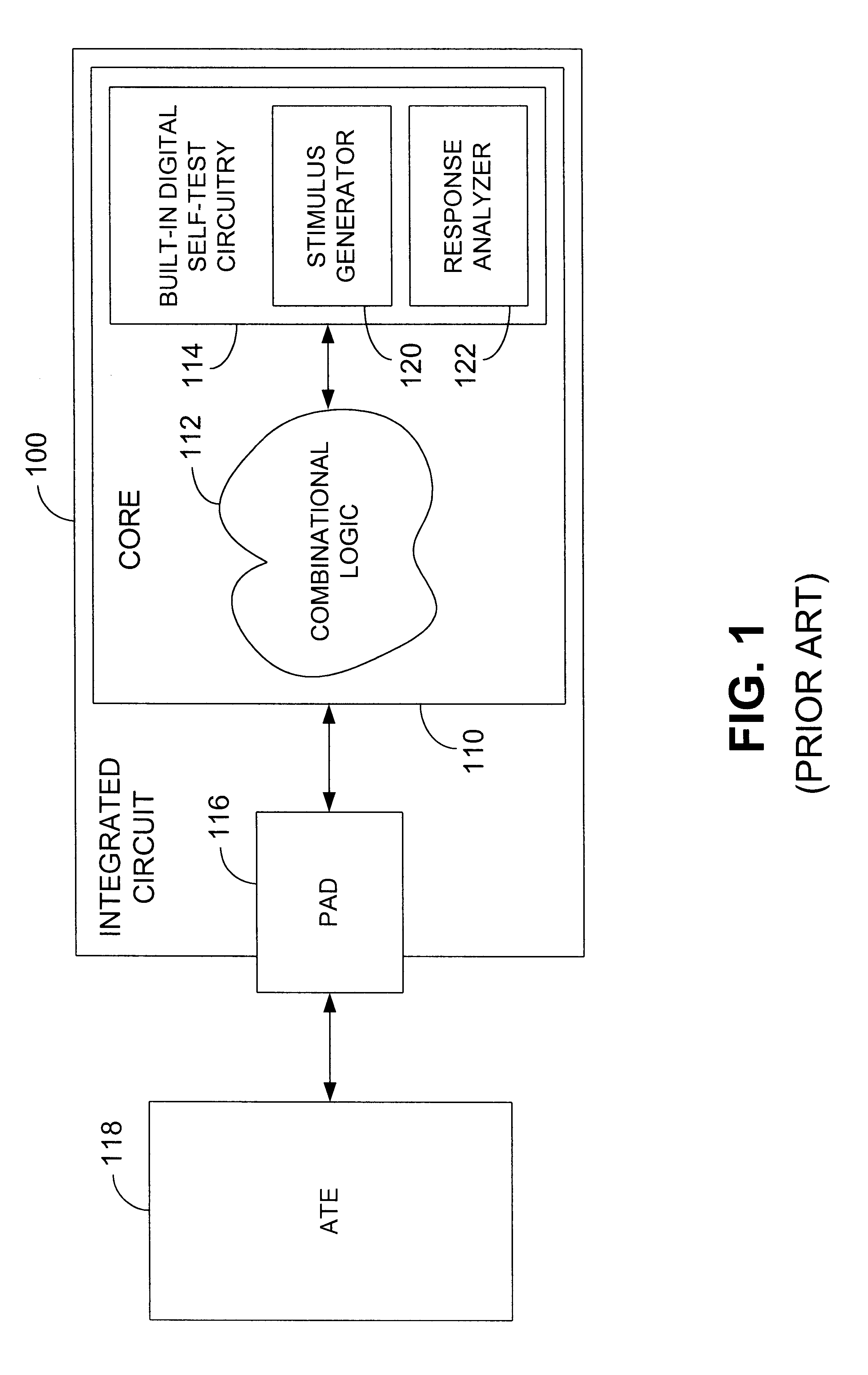

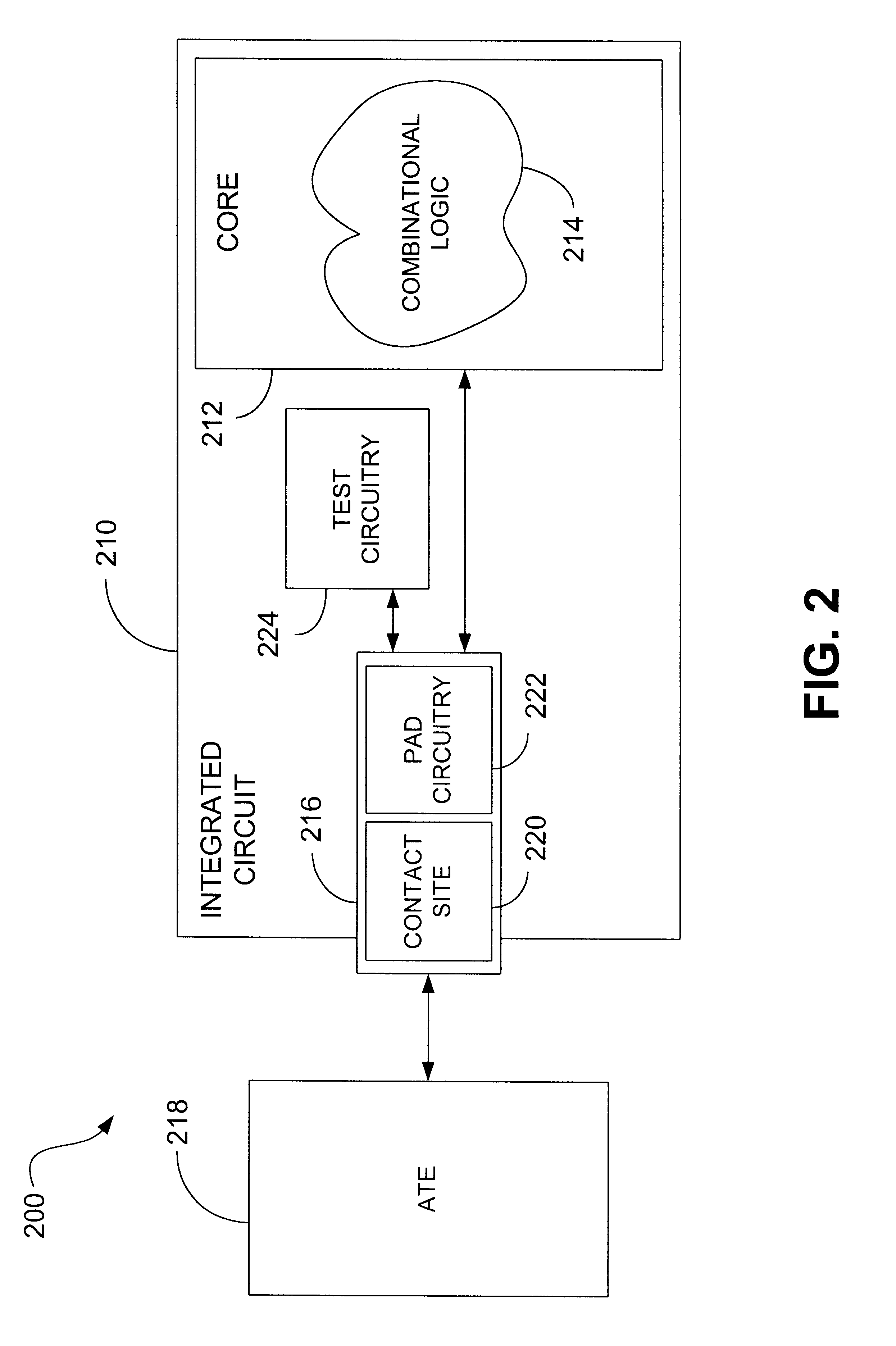

Utilizing the digital self-test circuitry of FIG. 1 as a point of comparison, general characteristics of a preferred embodiment of the test system of the present invention will now be described in reference to the schematic diagram of FIG. 2. As depicted in FIG. 2, test system 200 incorporates an integrated circuit 210 which includes a core 212. Core 212 incorporates logic 214 and electrically communicates with a pad 216, which is configured to allow intercommunication of the logic with devices, such as ATE 218, for example, external to the integrated circuit. As mentioned hereinbefore, a pad, such as pad 216, includes a physical or contact site 220, which serves as an electrical contact for IC 210, as well as pad circuitry 222, which cooperates with the contact site to enable electrical communication between co...

PUM

| Property | Measurement | Unit |

|---|---|---|

| driver clock-to-q time | aaaaa | aaaaa |

| driver clock-to-g time | aaaaa | aaaaa |

| receiver setup time | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More