Patents

Literature

95results about "Counting chain asynchronous pulse counters" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

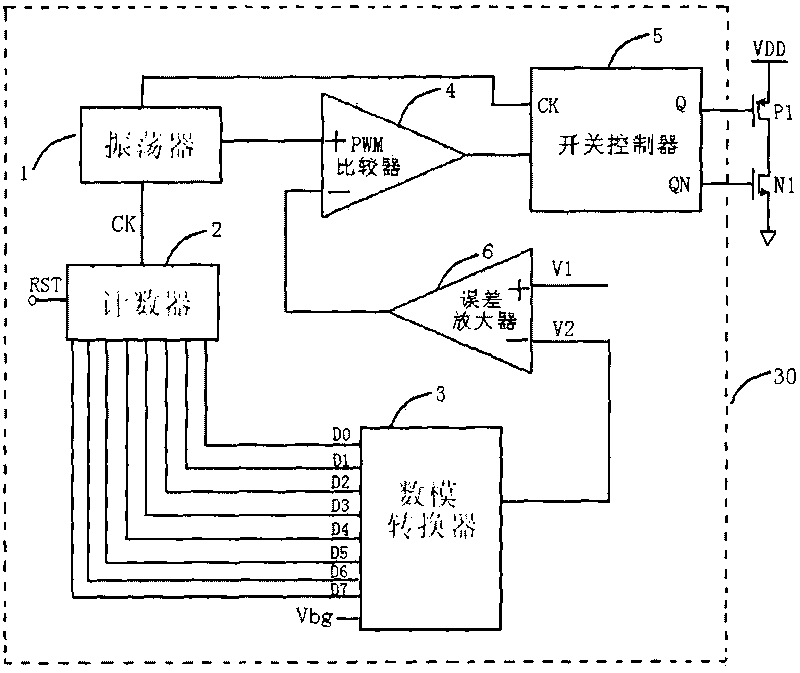

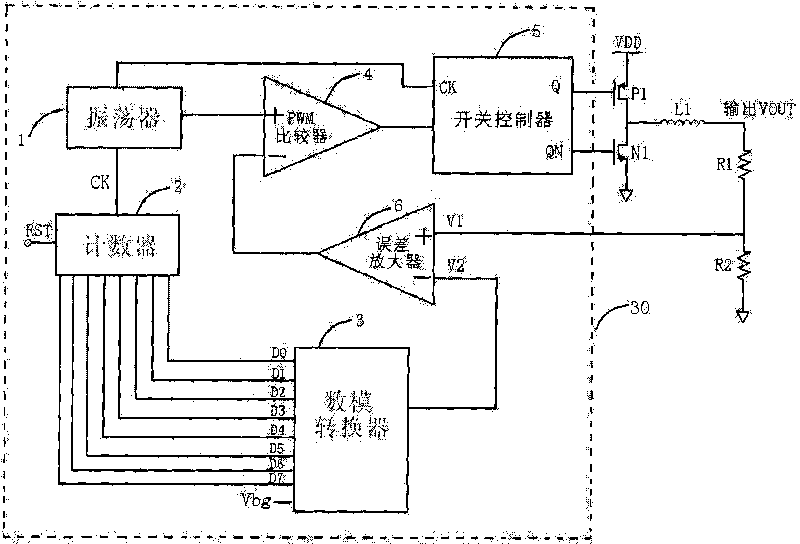

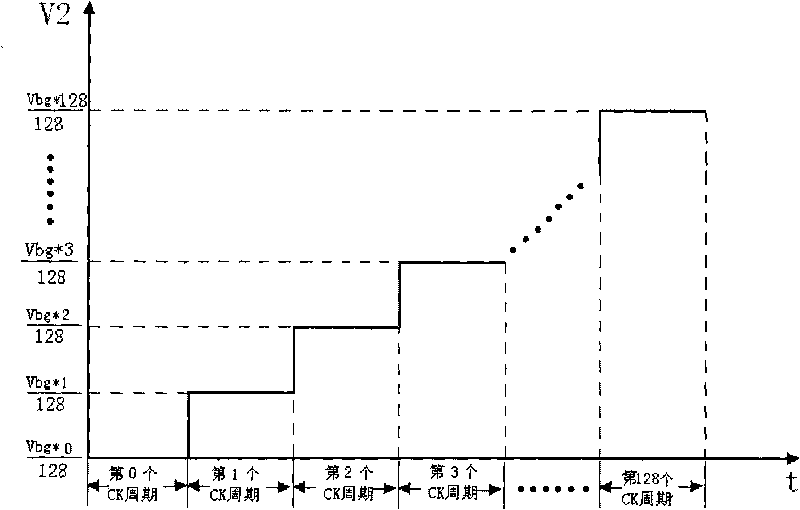

DC-DC switch power soft-start circuit of digital-to-analogue conversion control

ActiveCN101741233AEasy to integrateGood soft start performanceAnalogue/digital conversionElectric signal transmission systemsDigital analog converterComparator

The invention discloses a DC-DC switch power soft-start circuit of digital-to-analogue conversion (DAC) control, comprising an oscillator, a counter, a digital-to-analog converter, an error comparator, a PWM comparator and an on-off controller. In the invention, a Q output end of the on-off controller is connected with a grid of an outer switch rectifier tube, a QN output end is connected with a grid of an outer follow current tube, the output end of the PWM comparator and the output end of the oscillator are connected with the input end of the on-off controller, the input end of the PWM comparator is respectively connected with the output end of the oscillator and the output end of the error comparator, one end of the input end of the error comparator outputs sample voltage, the other end of the input end of the error comparator inputs the voltage generated by the digital-to-analog converter, the output end of the error comparator outputs a difference value amplifying signal of the sample voltage and the voltage generated by the digital-to-analog converter, one end of the counter is connected with the output end of the oscillator, and the other end of the counter is a zero clearing signal and outputs an 8-digit parallel signal. When the power is electrified, the reference voltage of the input end of the error comparator is controlled to enable the reference voltage to rise step by step from small to large, and the voltage of the output end of the error comparator goes up slowly with the reference voltage, thereby avoiding overshoot voltage in the starting procedure and realizing the function of soft-start.

Owner:WUXI CHIPOWN MICROELECTRONICS

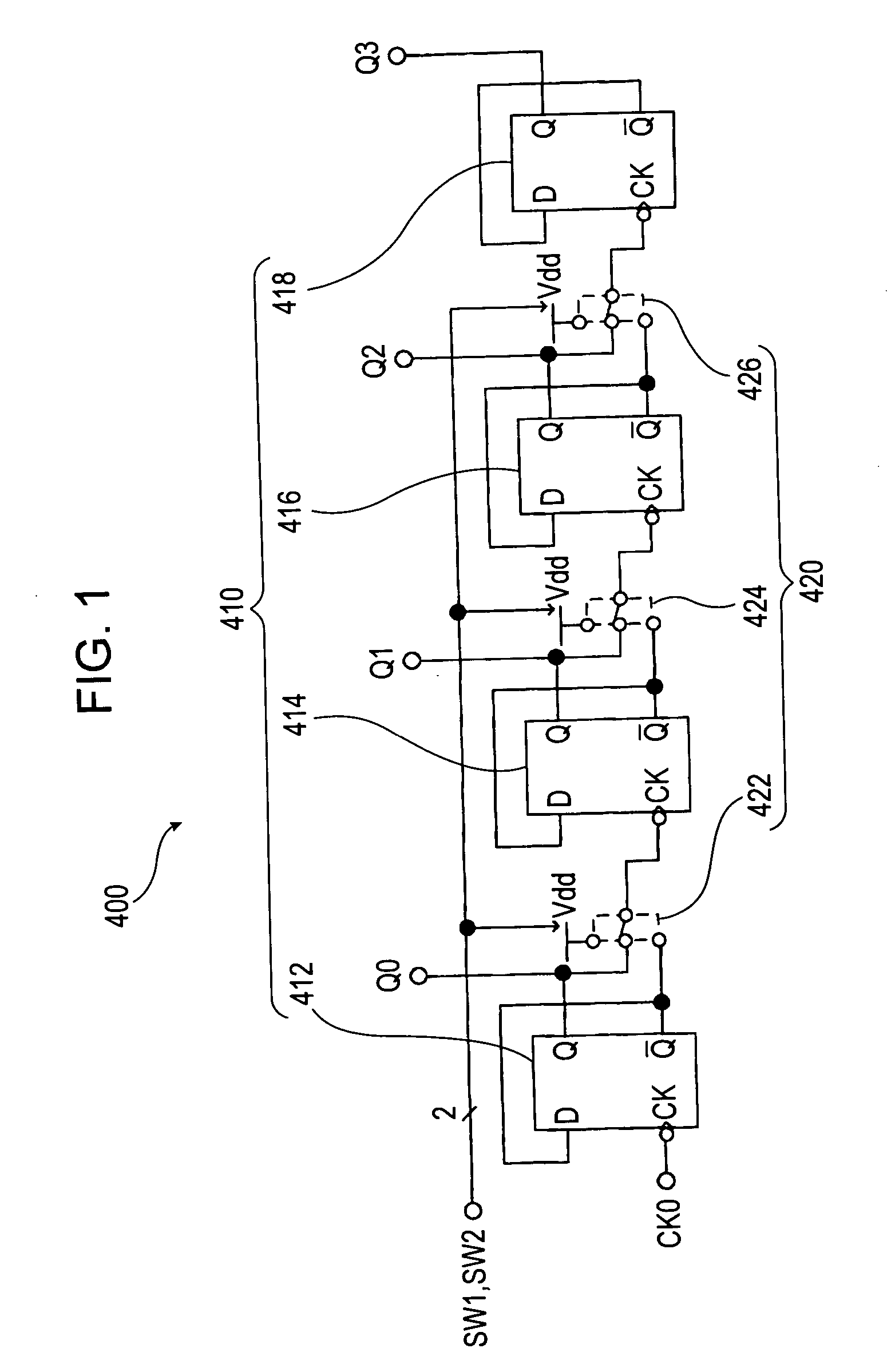

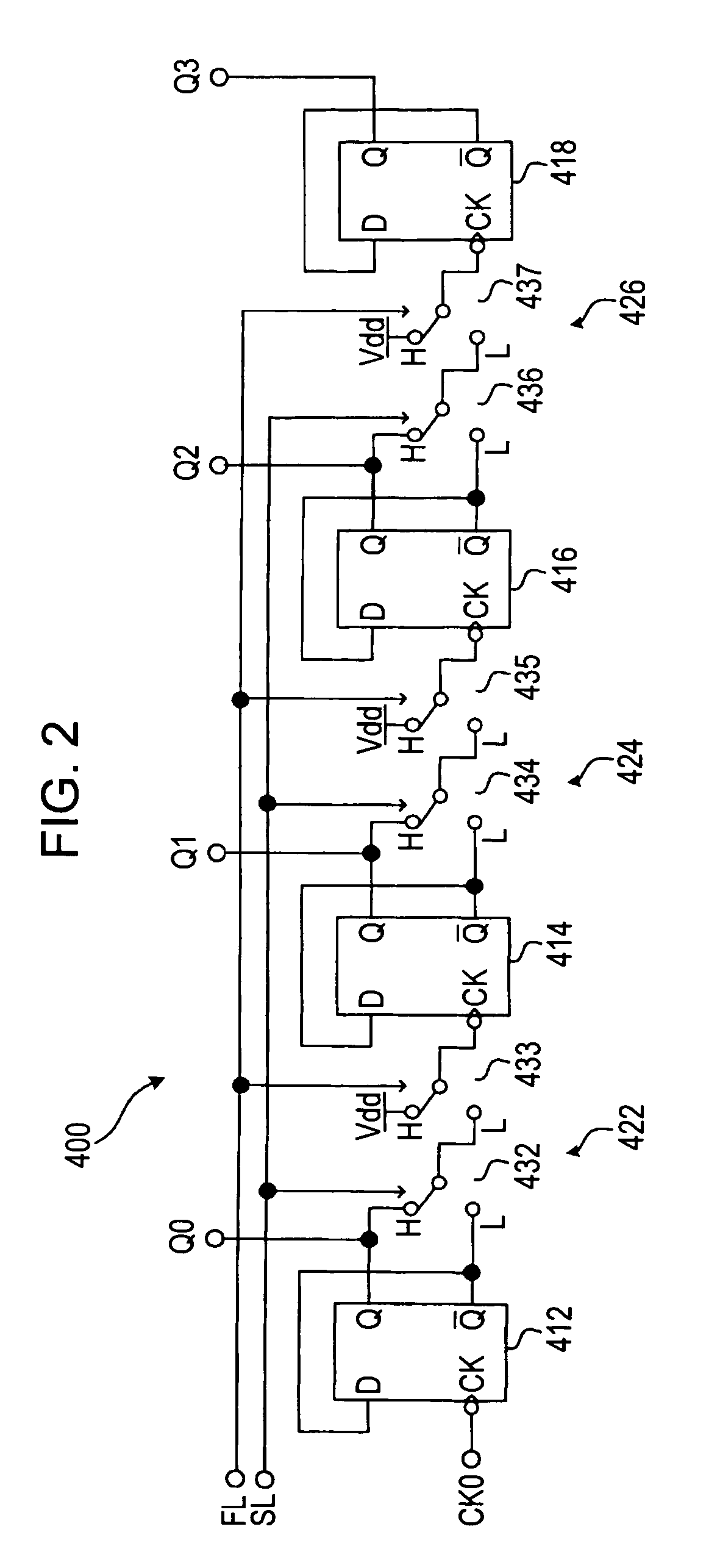

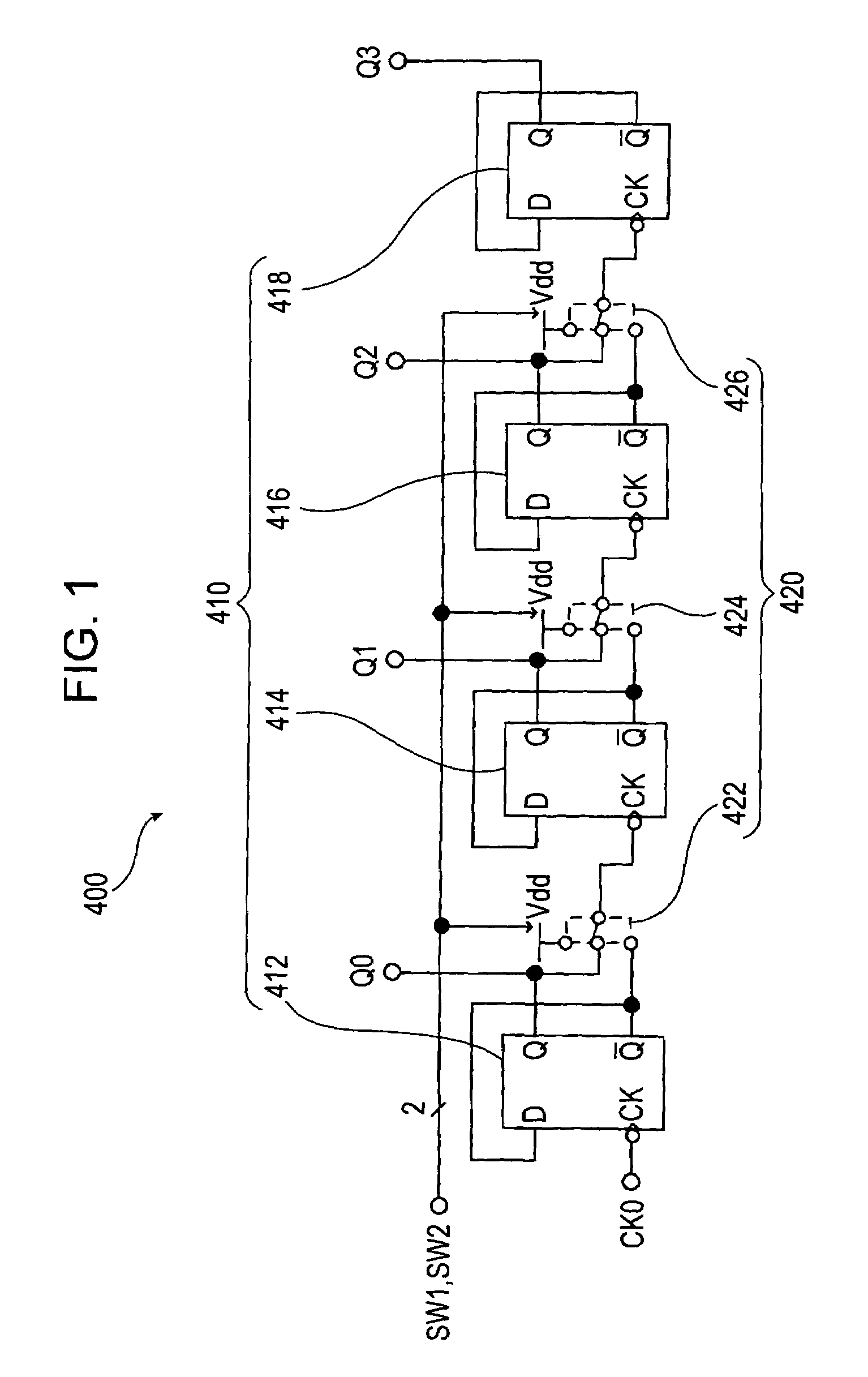

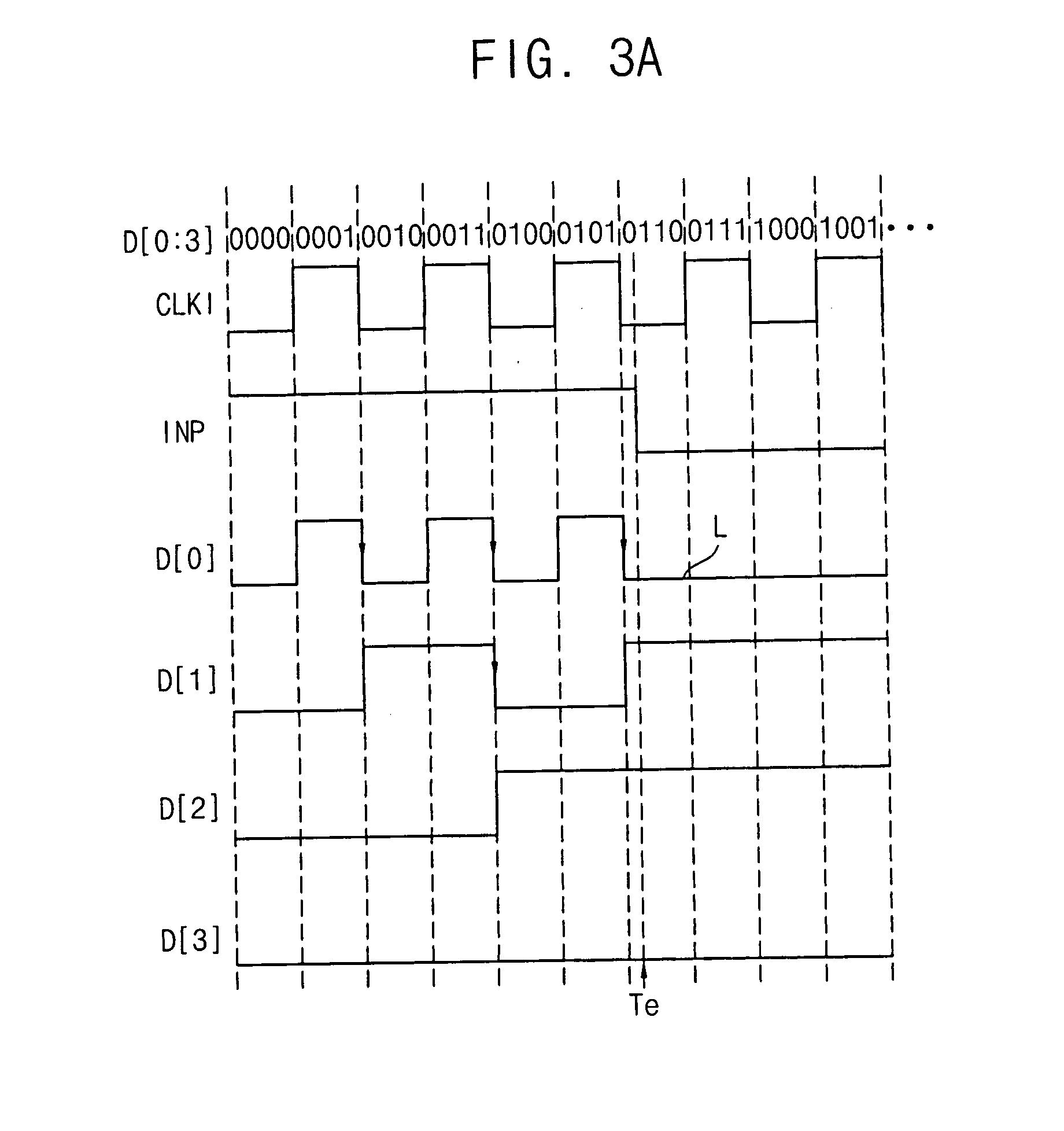

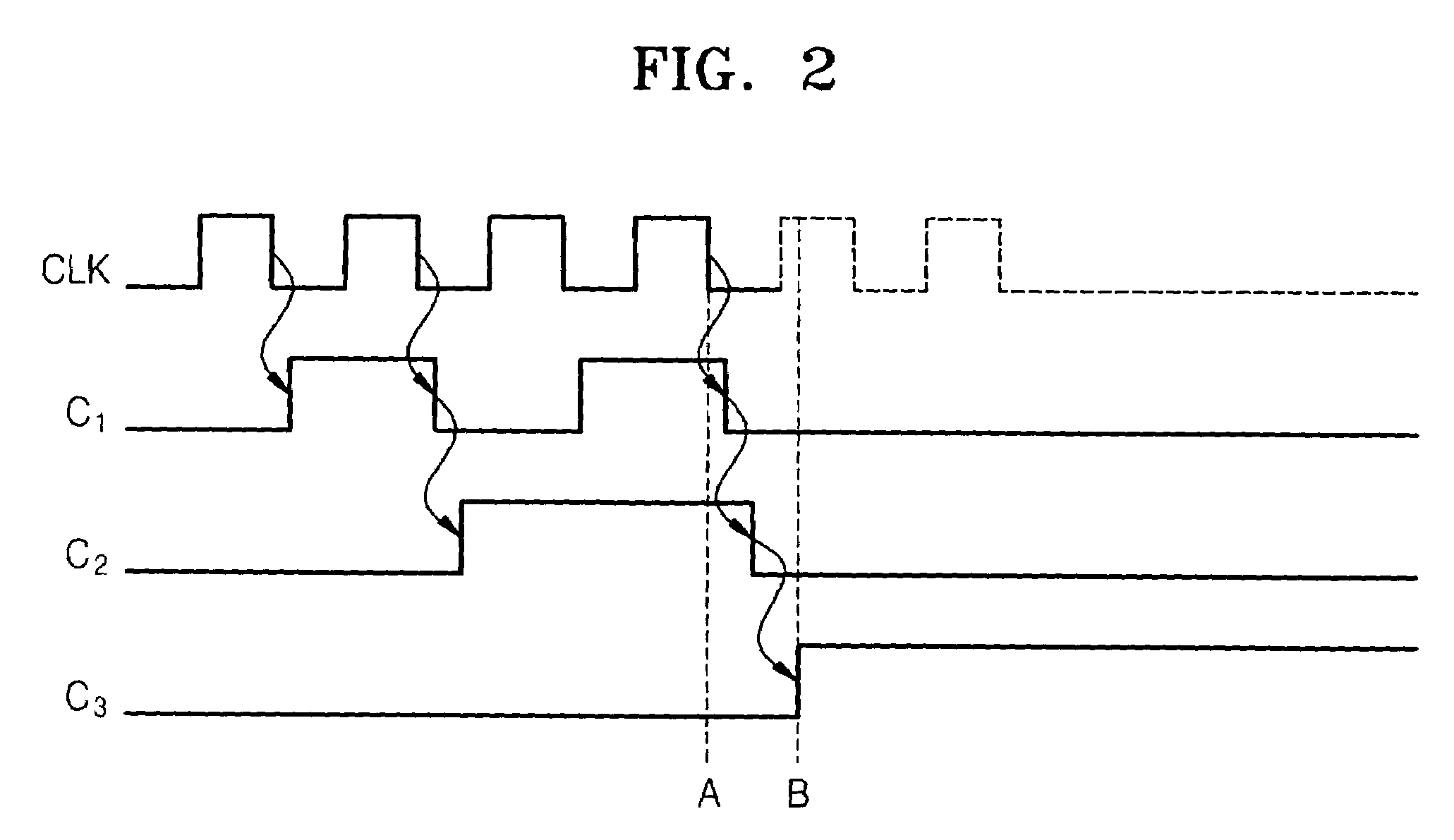

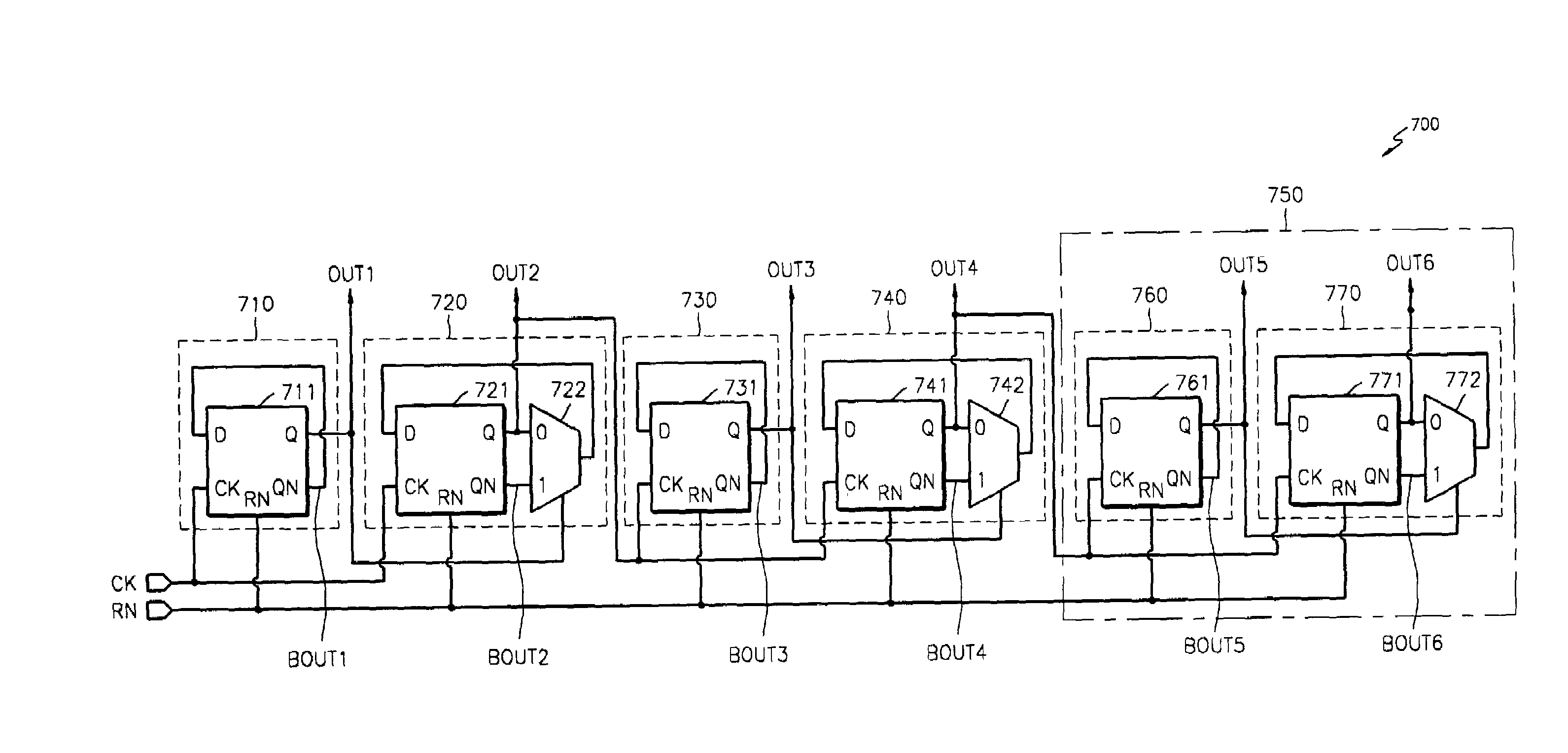

Counter circuit, AD conversion method, AD converter, semiconductor device for detecting distribution of physical quantities, and electronic apparatus

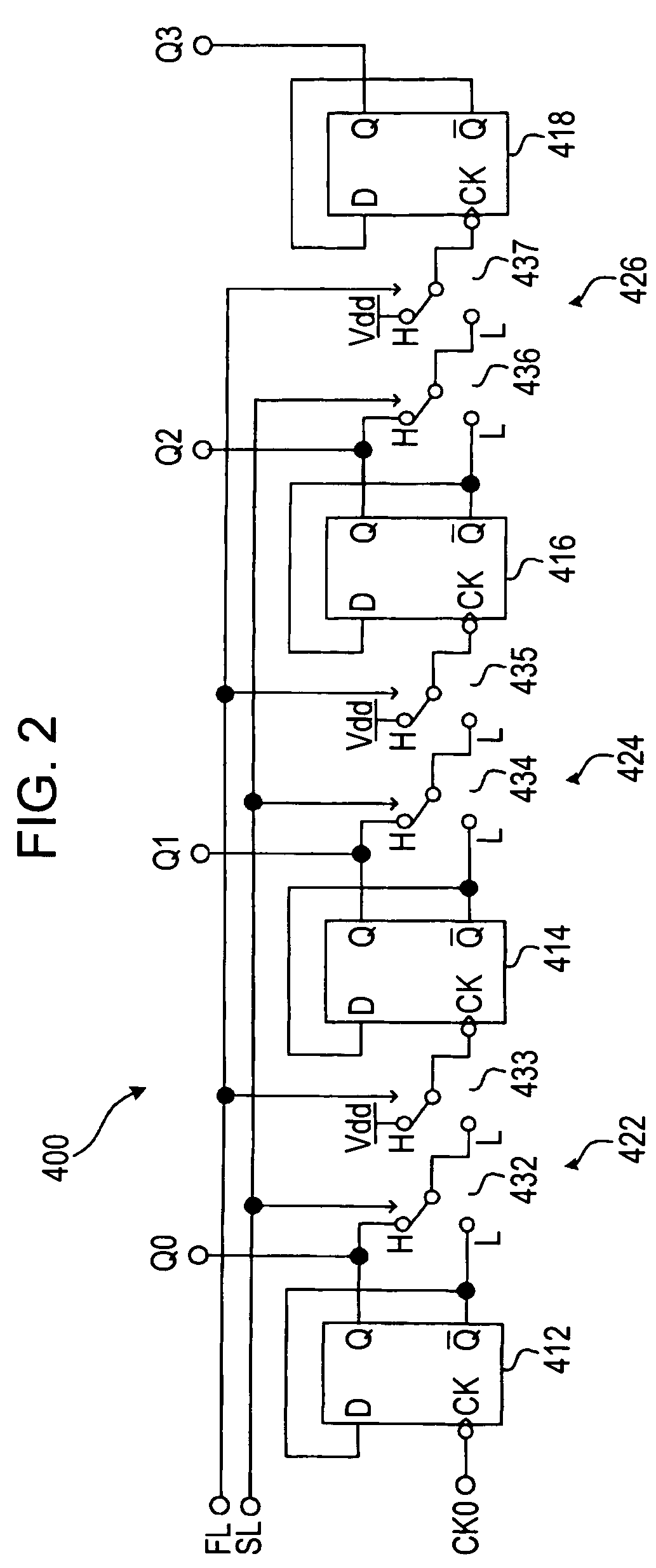

An asynchronous counter that is capable of switching count mode includes flip-flops, and three-input single-output tri-value switches respectively provided between the adjacent pairs of the flip-flops. The tri-value switches switch among three values, namely, non-inverting outputs and inverting outputs of the flip-flops and a power supply level. Each of the tri-value switches switch among the three input signals according to two-bit control signals, and input a selected signal to a clock terminal of a subsequent flip-flop. When count mode is switched according to the control signals, a count value immediately before the mode switching is set as an initial value, and counting after the mode switching is started from the initial value.

Owner:SONY CORP

Counter circuit, AD conversion method, AD converter, semiconductor device for detecting distribution of physical quantities, and electronic apparatus

An asynchronous counter that is capable of switching count mode includes flip-flops, and three-input single-output tri-value switches respectively provided between the adjacent pairs of the flip-flops. The tri-value switches switch among three values, namely, non-inverting outputs and inverting outputs of the flip-flops and a power supply level. Each of the tri-value switches switch among the three input signals according to two-bit control signals, and input a selected signal to a clock terminal of a subsequent flip-flop. When count mode is switched according to the control signals, a count value immediately before the mode switching is set as an initial value, and counting after the mode switching is started from the initial value.

Owner:SONY CORP

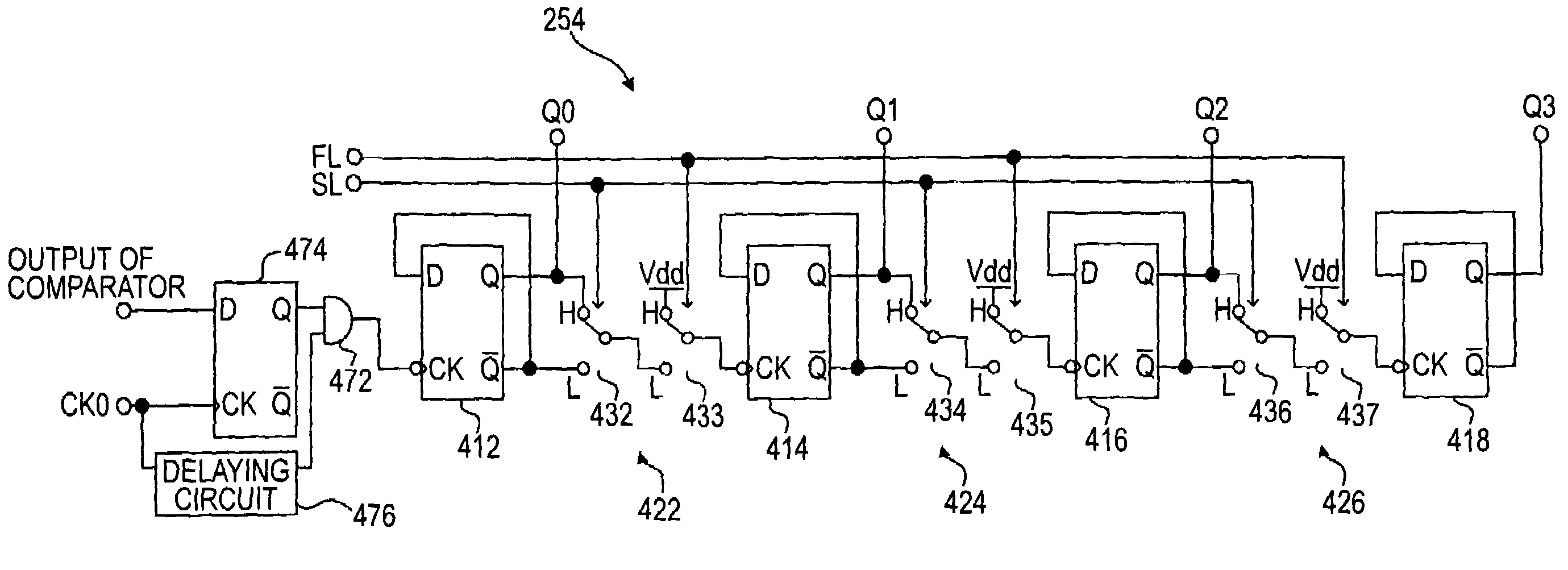

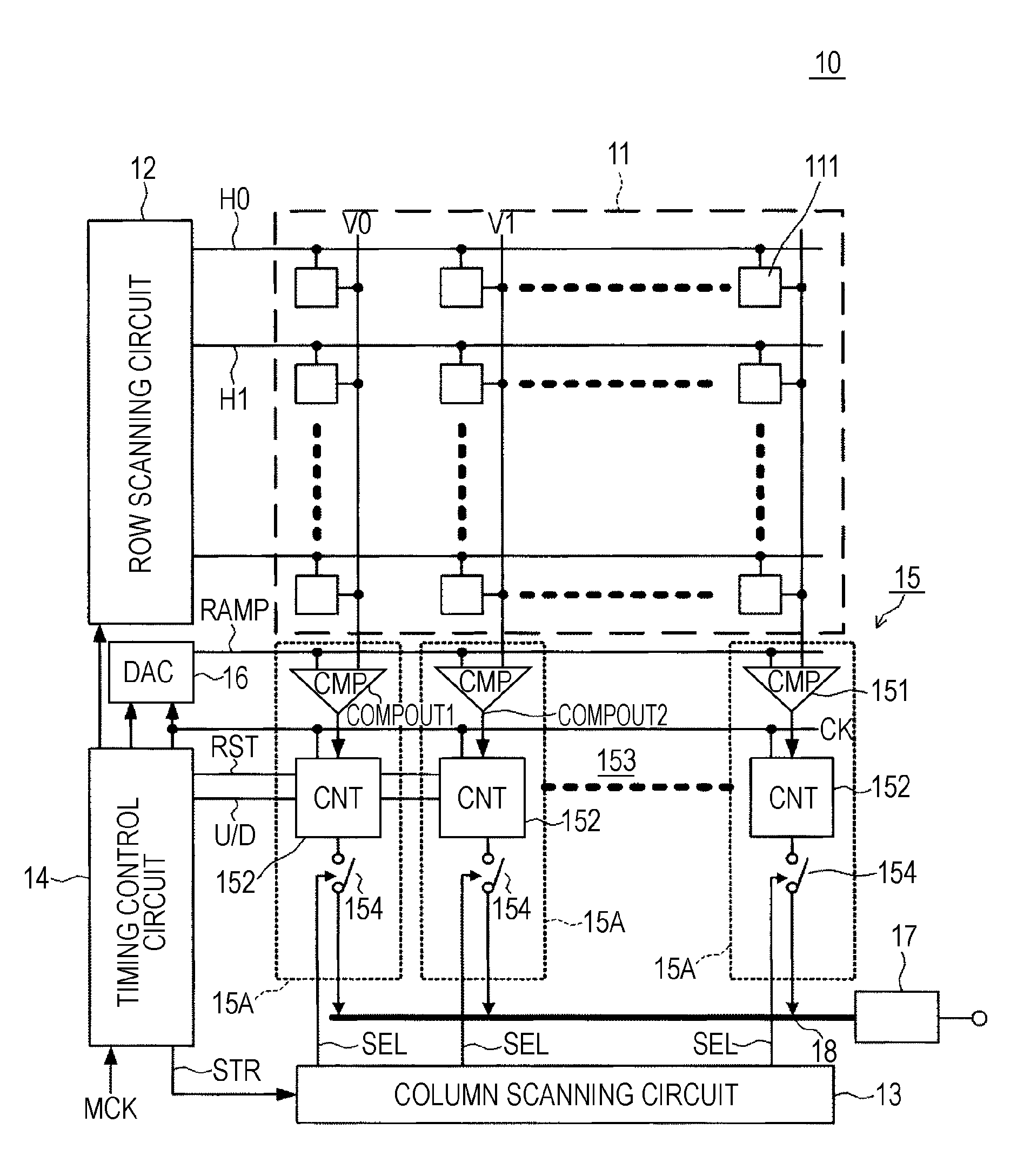

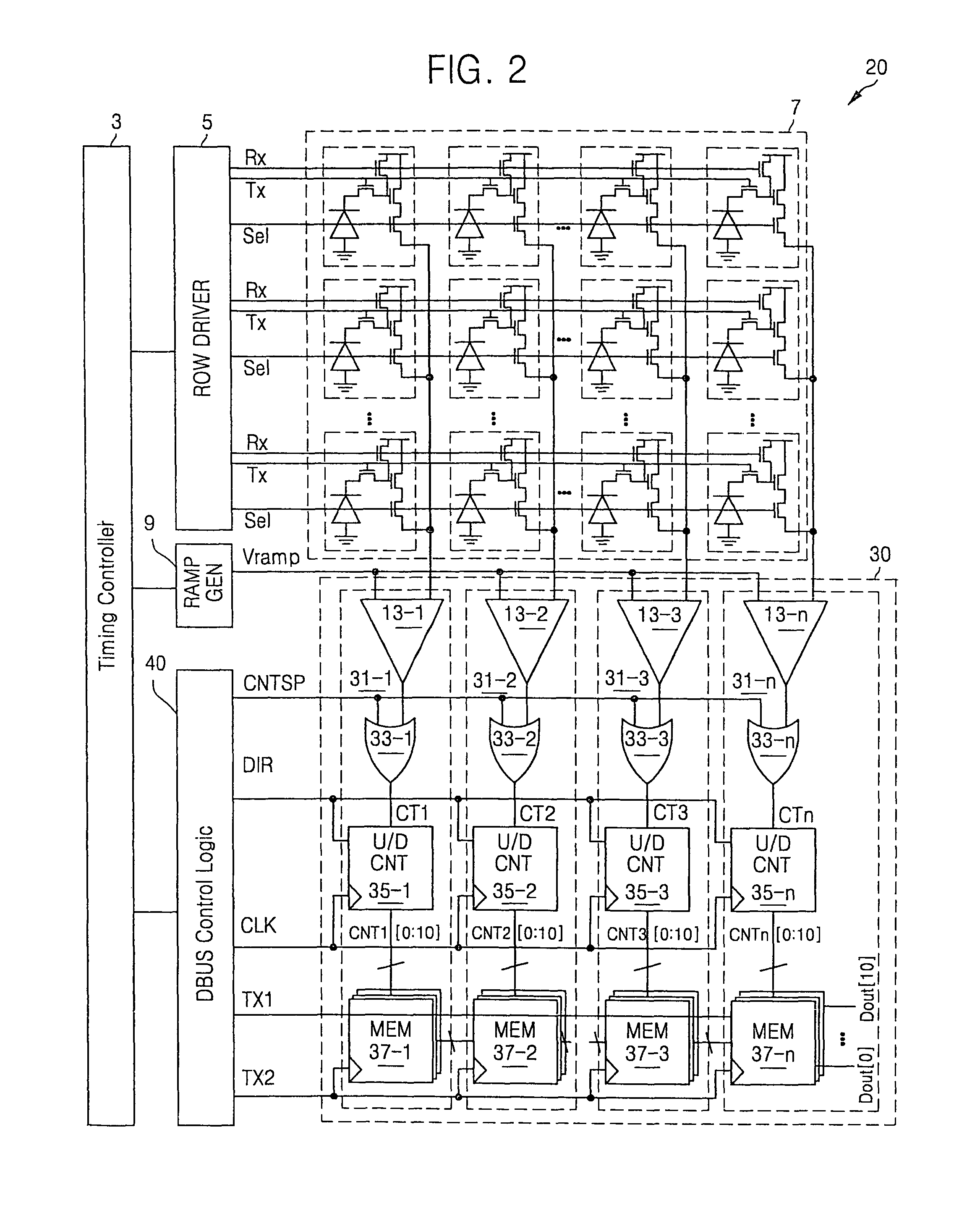

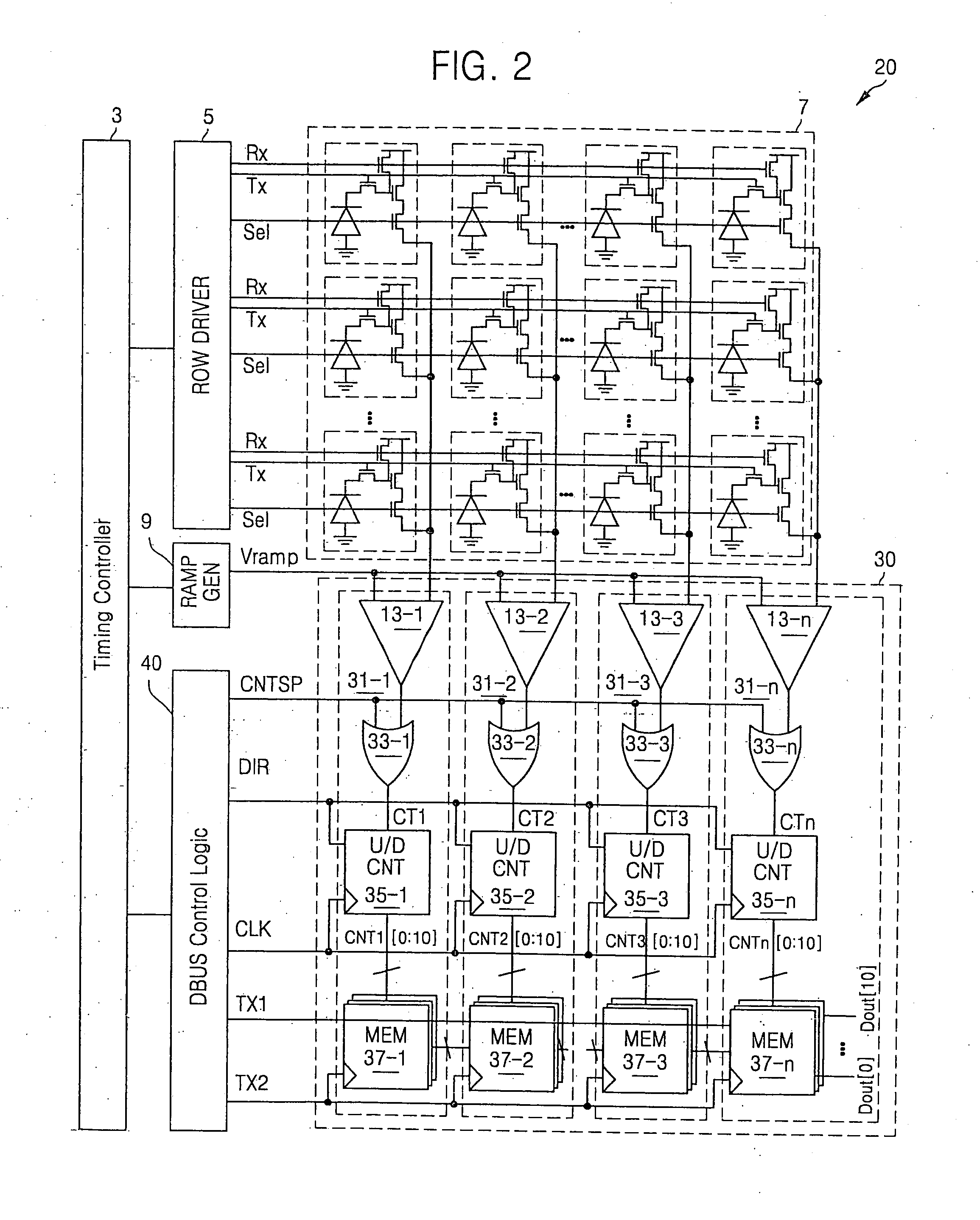

A/d conversion circuit, solid-state image sensor, and camera system

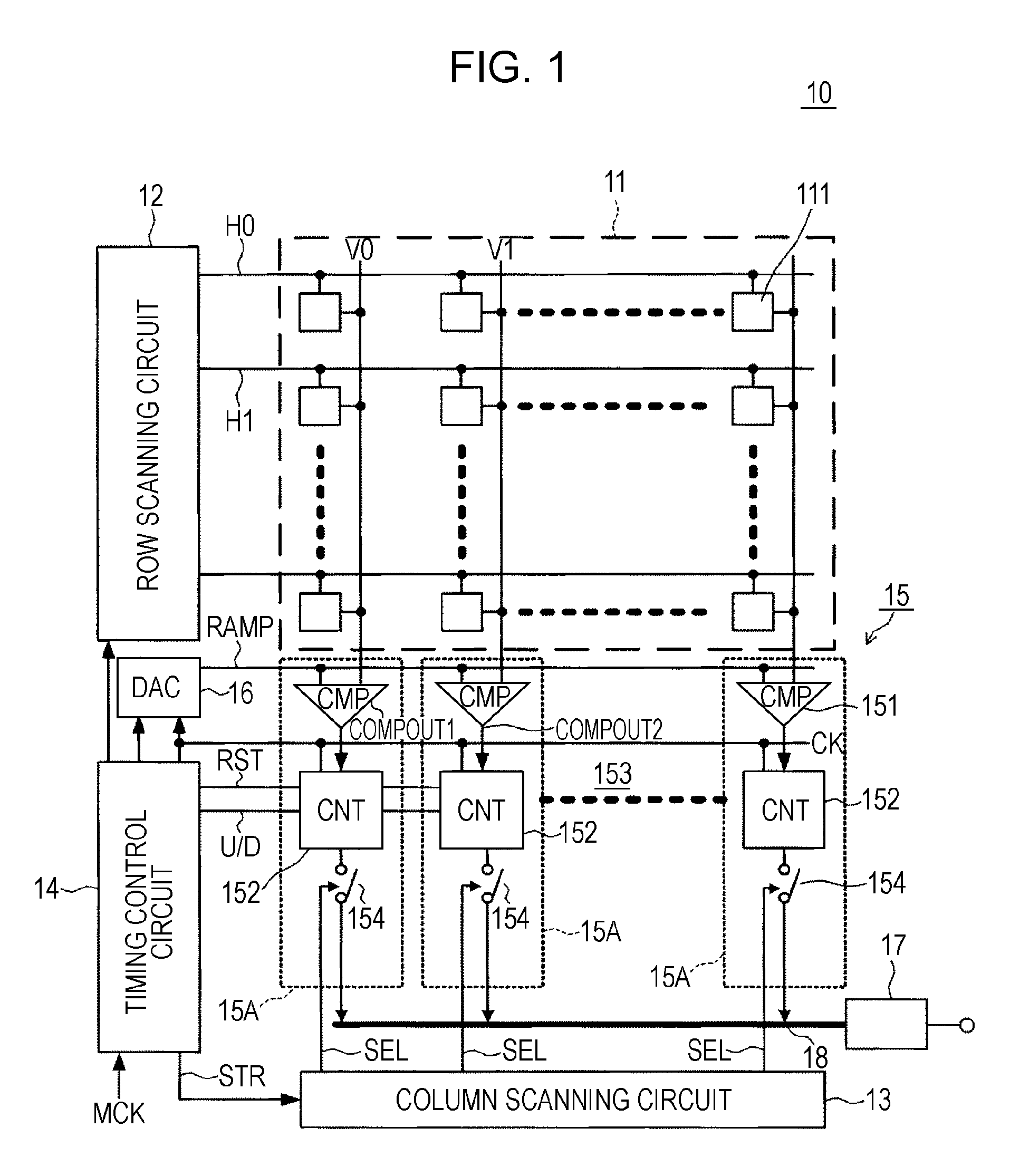

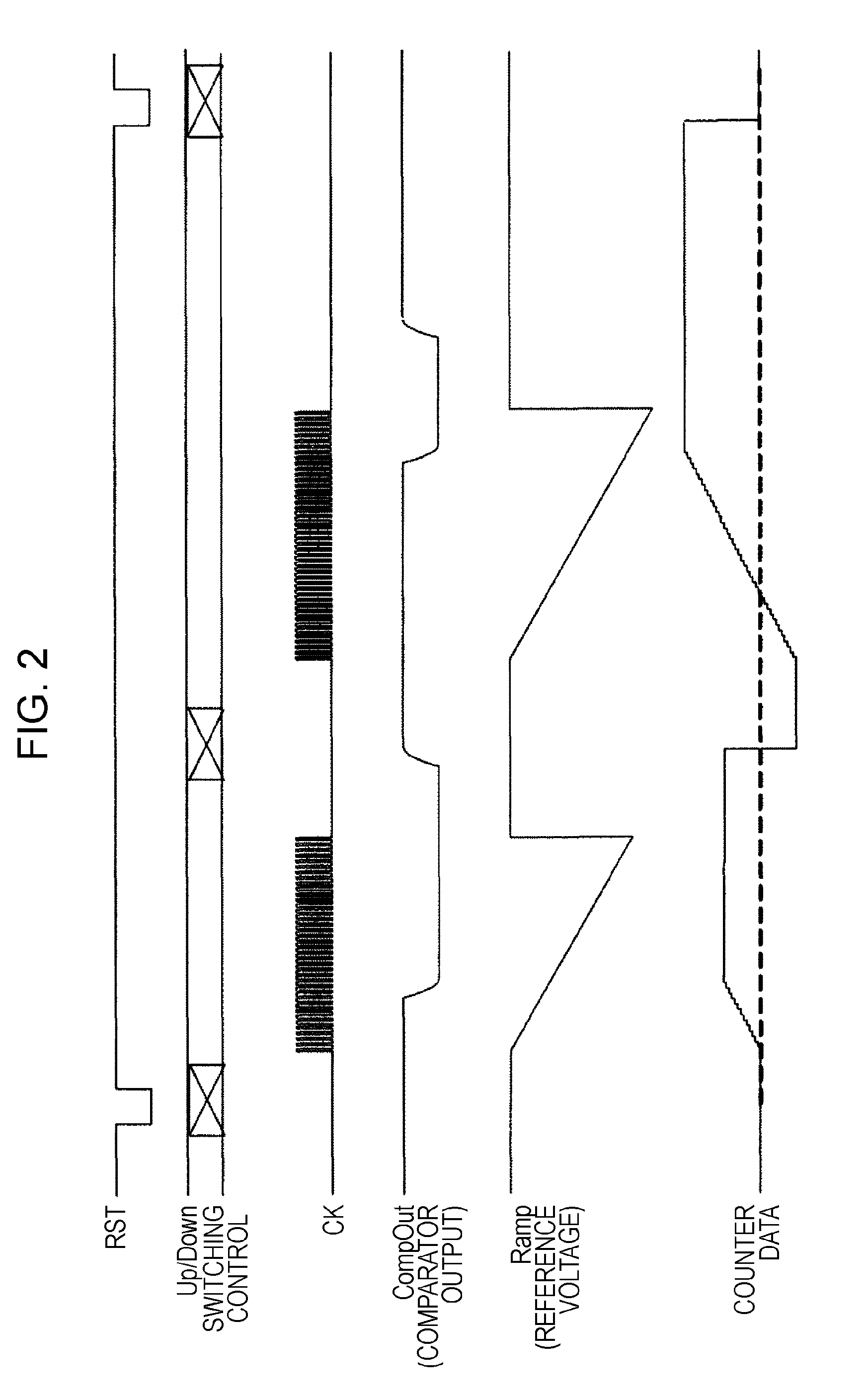

ActiveUS20100194949A1Difficult to operateTelevision system detailsElectric signal transmission systemsEngineeringComparator

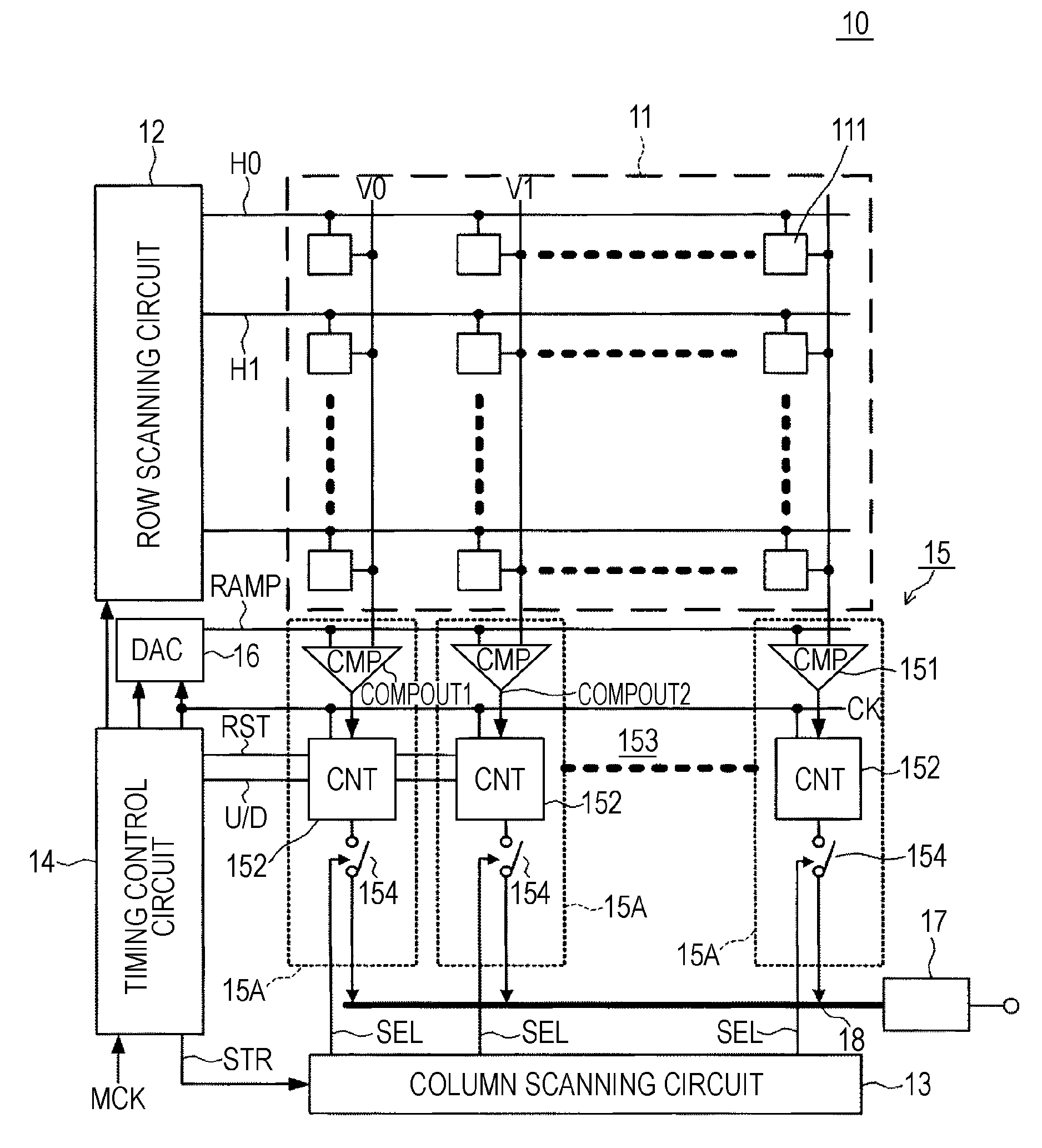

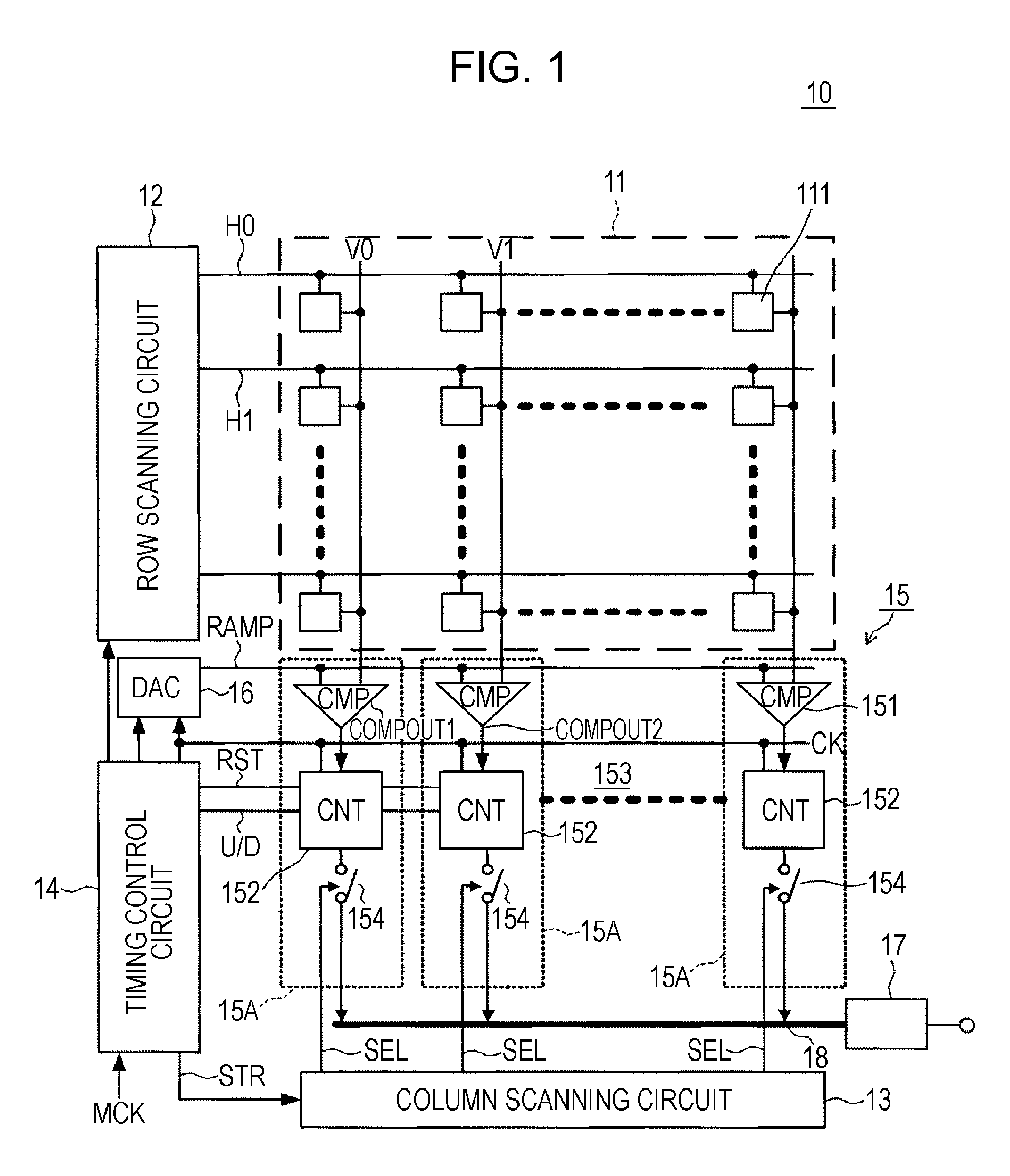

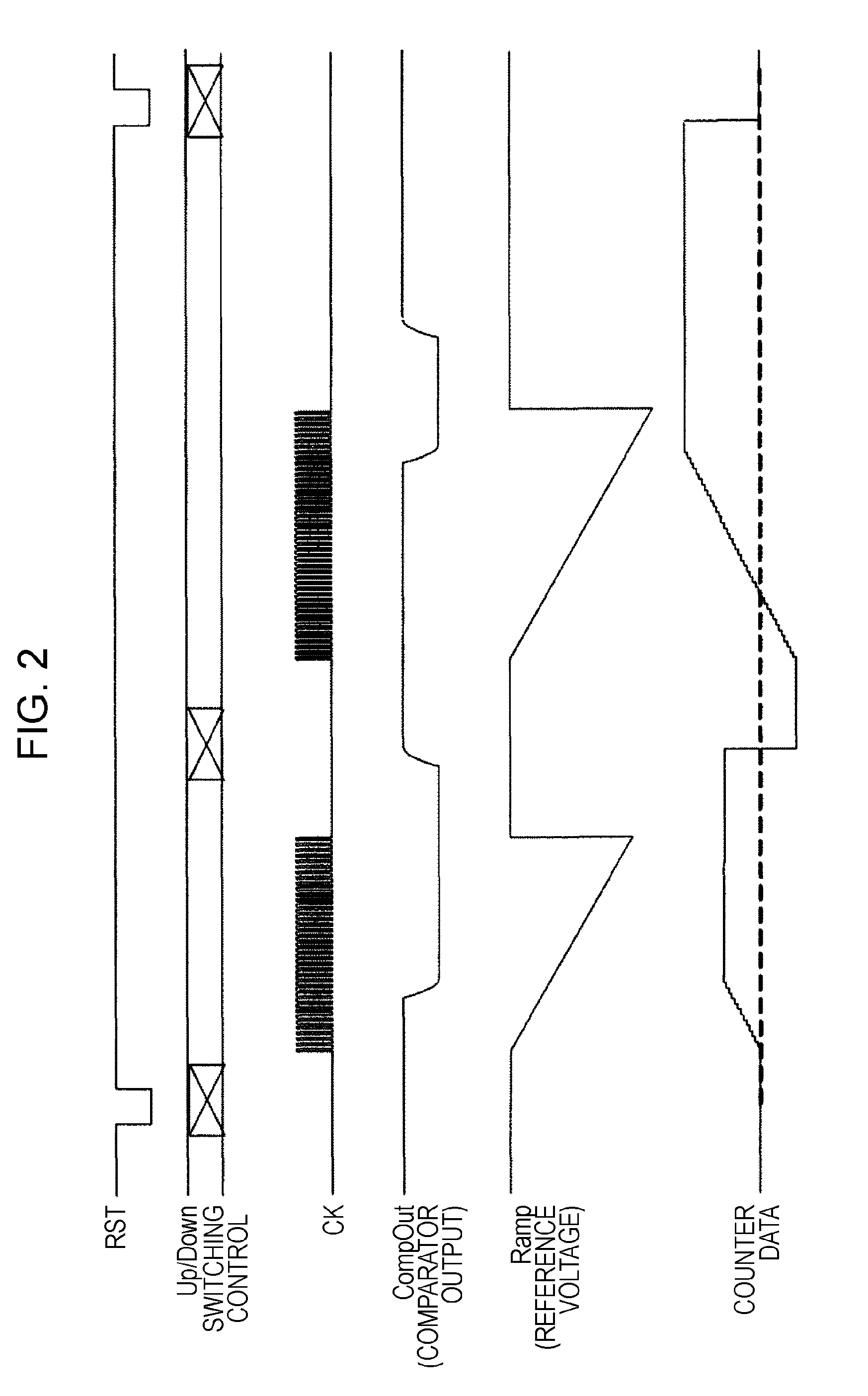

There are provided an A / D conversion circuit in which a counter is made to be capable of performing counting at both edges of a clock, up / down count values can be switched while the up / down count values are held, and the duty of the counting operation is difficult to be distorted even with the both-edge counting, a solid-state image sensor, and a camera system. An ADC 15A is configured as an integrating-type A / D conversion circuit using a comparator 151 and a counter 152. The counter 152 has a function of switching a count mode from an up count to a down count and from a down count to an up count while a value is held, a function of performing counting at both rising and falling edges of an input clock CK at a frequency two times as high as that of the input clock, and a function of latching the input clock CK in accordance with an output signal of the comparator 151 and setting non-inverted or inverted data of the latched data to be data of an LSB.

Owner:SONY CORP

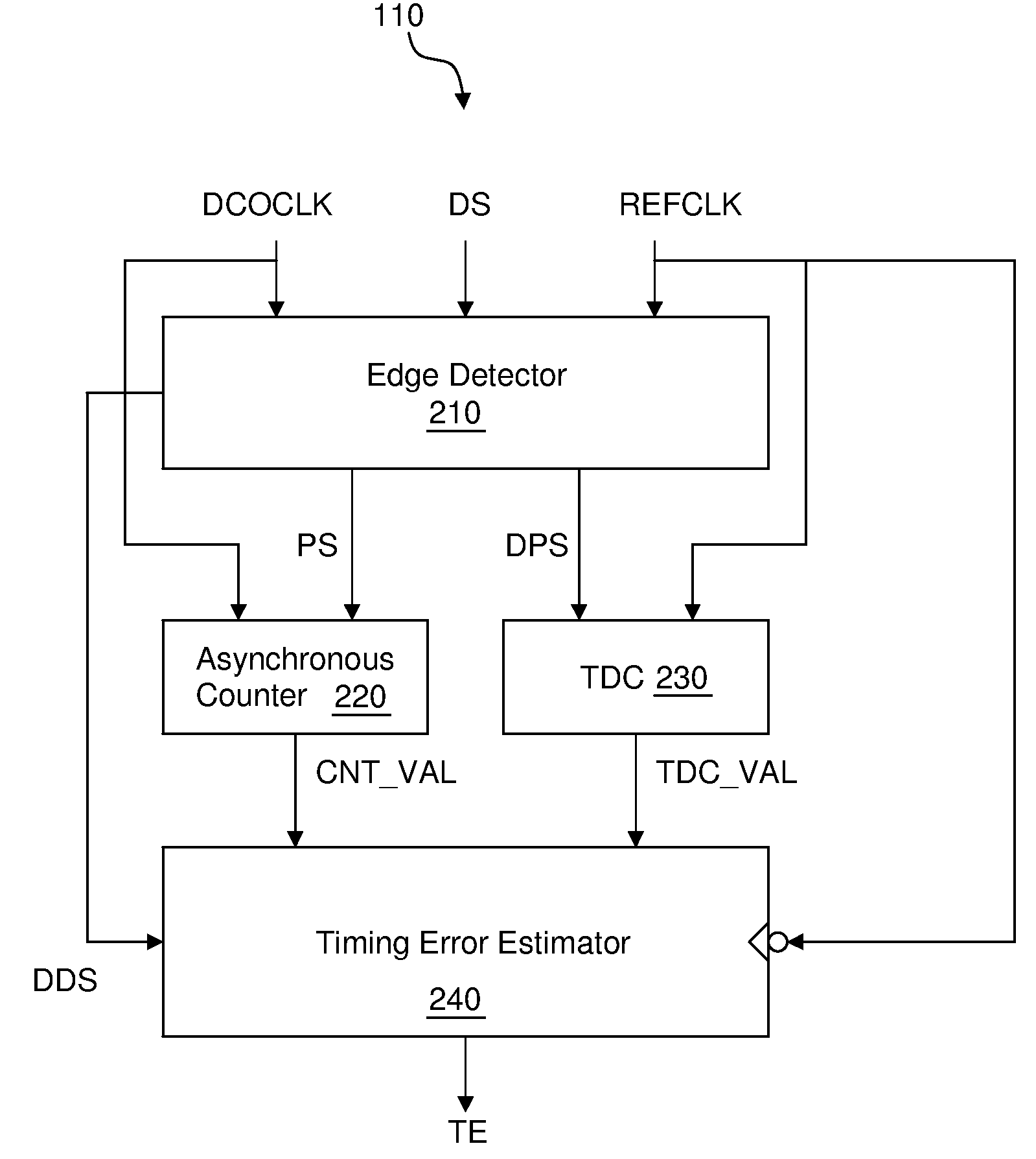

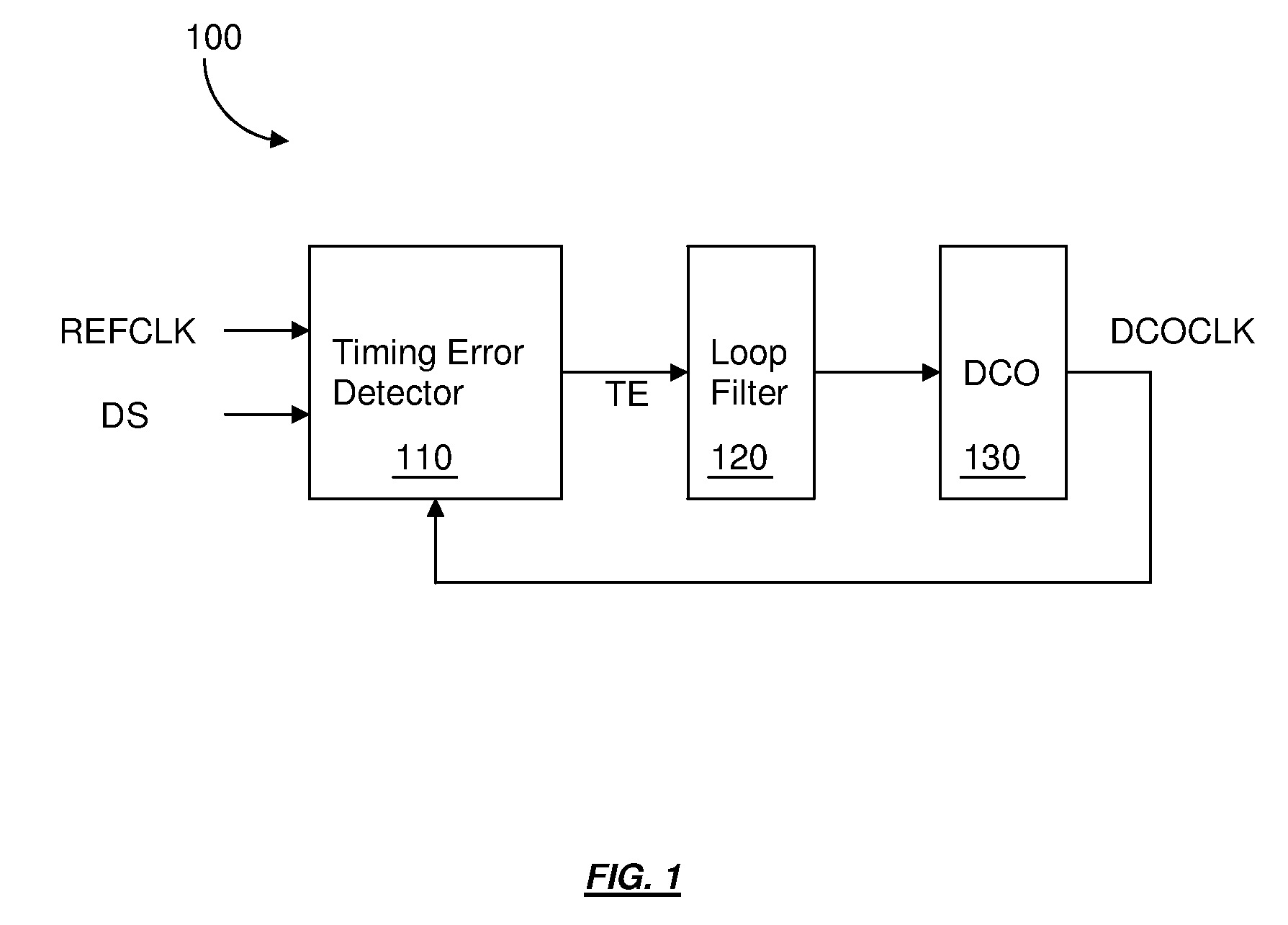

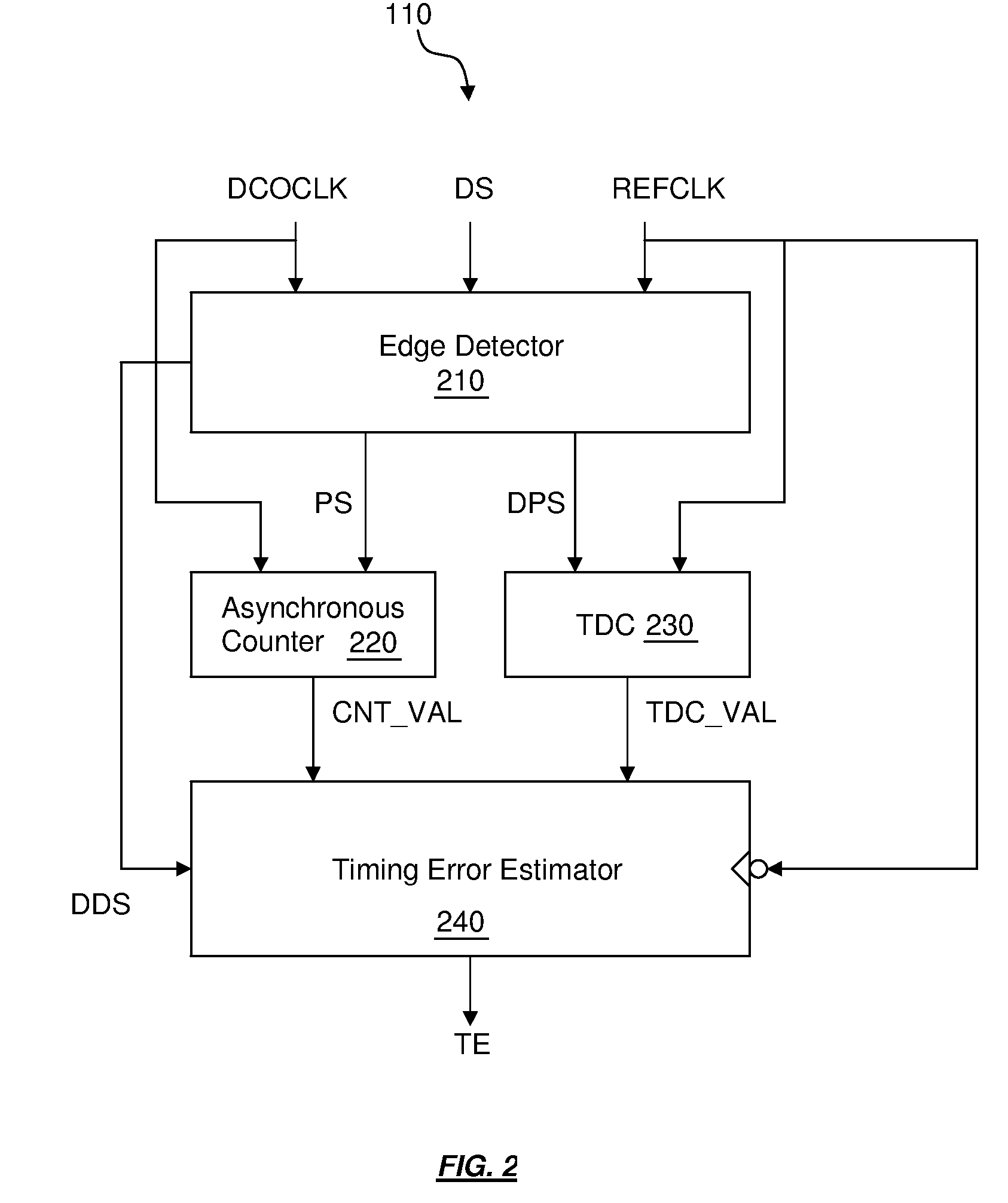

Asynchronous counter based timing error detection

ActiveUS20090307518A1Pulse automatic controlCounting chain asynchronous pulse countersAsynchronous circuitDigital converter

A method for estimating a timing difference between a first clock signal and a second clock signal is disclosed. The estimating method comprising: generating an edge signal by detecting an edge of the second clock signal by sampling the second clock signal using the first clock signal; generating a delayed edge signal by a further sampling of the second clock signal using the first clock signal; generating a first intermediate code by counting a number of clock edges of the first clock signal within a duration defined by the edge signal using an asynchronous counter; generating a second intermediate code to represent a timing difference between the second clock signal and the delayed edge signal using a time-to-digital converter; and generating an output code using a weighted sum of the first intermediate code and the second intermediate code.

Owner:REALTEK SEMICON CORP

A/D conversion circuit, solid-state image sensor, and camera system

ActiveUS8330635B2Difficult to operateTelevision system detailsElectric signal transmission systemsEngineeringComparator

There are provided an A / D conversion circuit in which a counter is made to be capable of performing counting at both edges of a clock, up / down count values can be switched while the up / down count values are held, and the duty of the counting operation is difficult to be distorted even with the both-edge counting, a solid-state image sensor, and a camera system. An ADC 15A is configured as an integrating-type A / D conversion circuit using a comparator 151 and a counter 152. The counter 152 has a function of switching a count mode from an up count to a down count and from a down count to an up count while a value is held, a function of performing counting at both rising and falling edges of an input clock CK at a frequency two times as high as that of the input clock, and a function of latching the input clock CK in accordance with an output signal of the comparator 151 and setting non-inverted or inverted data of the latched data to be data of an LSB.

Owner:SONY CORP

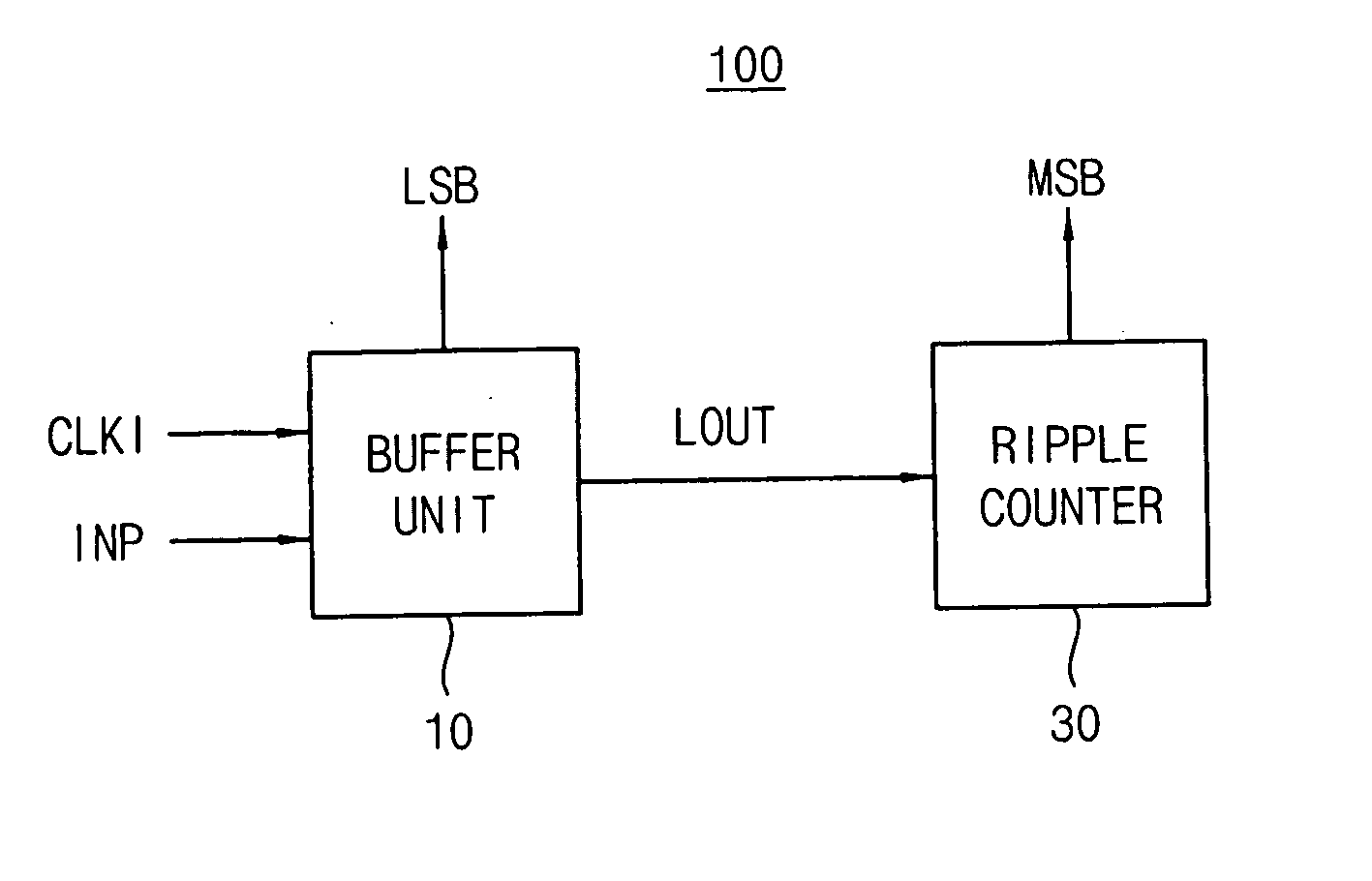

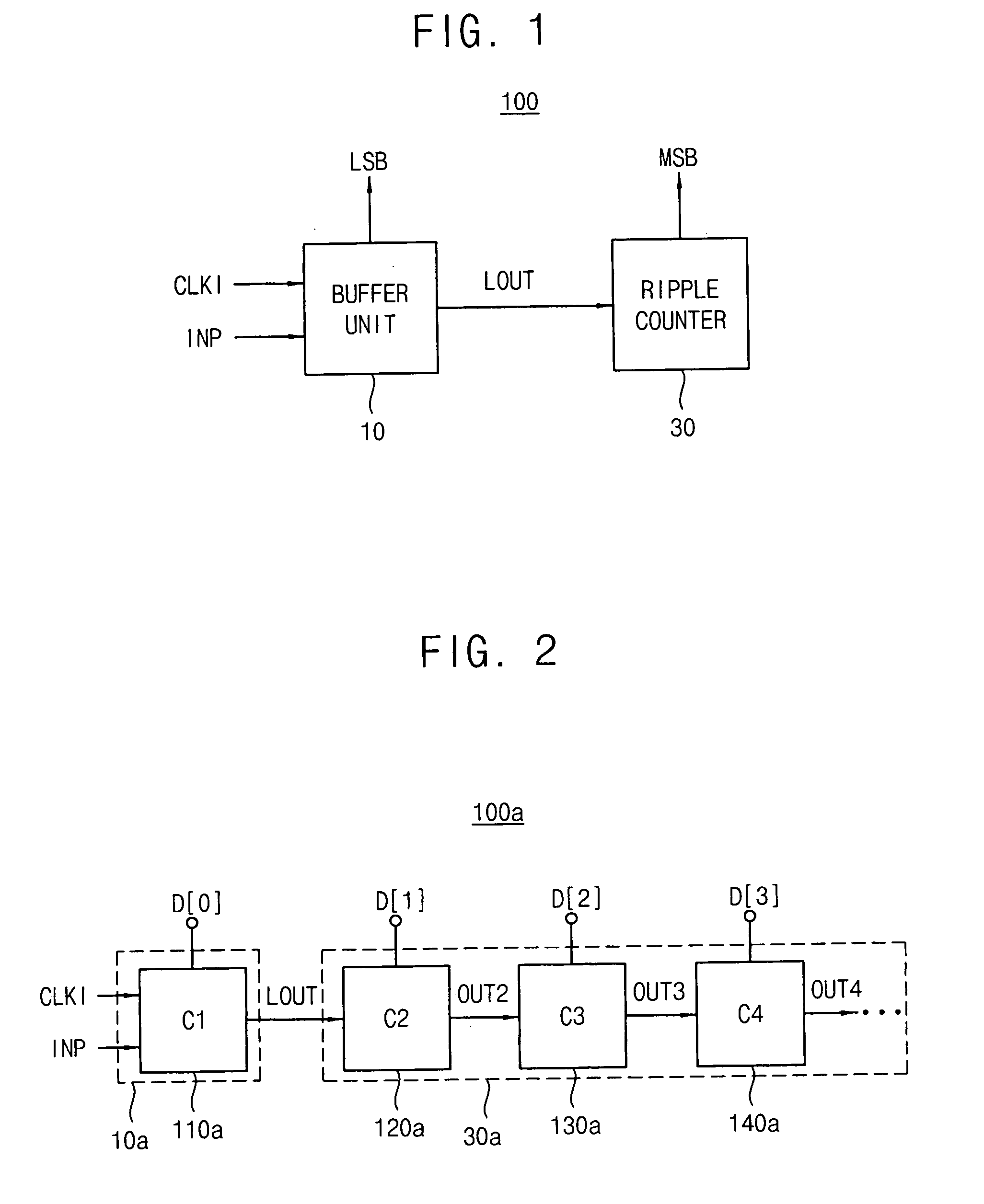

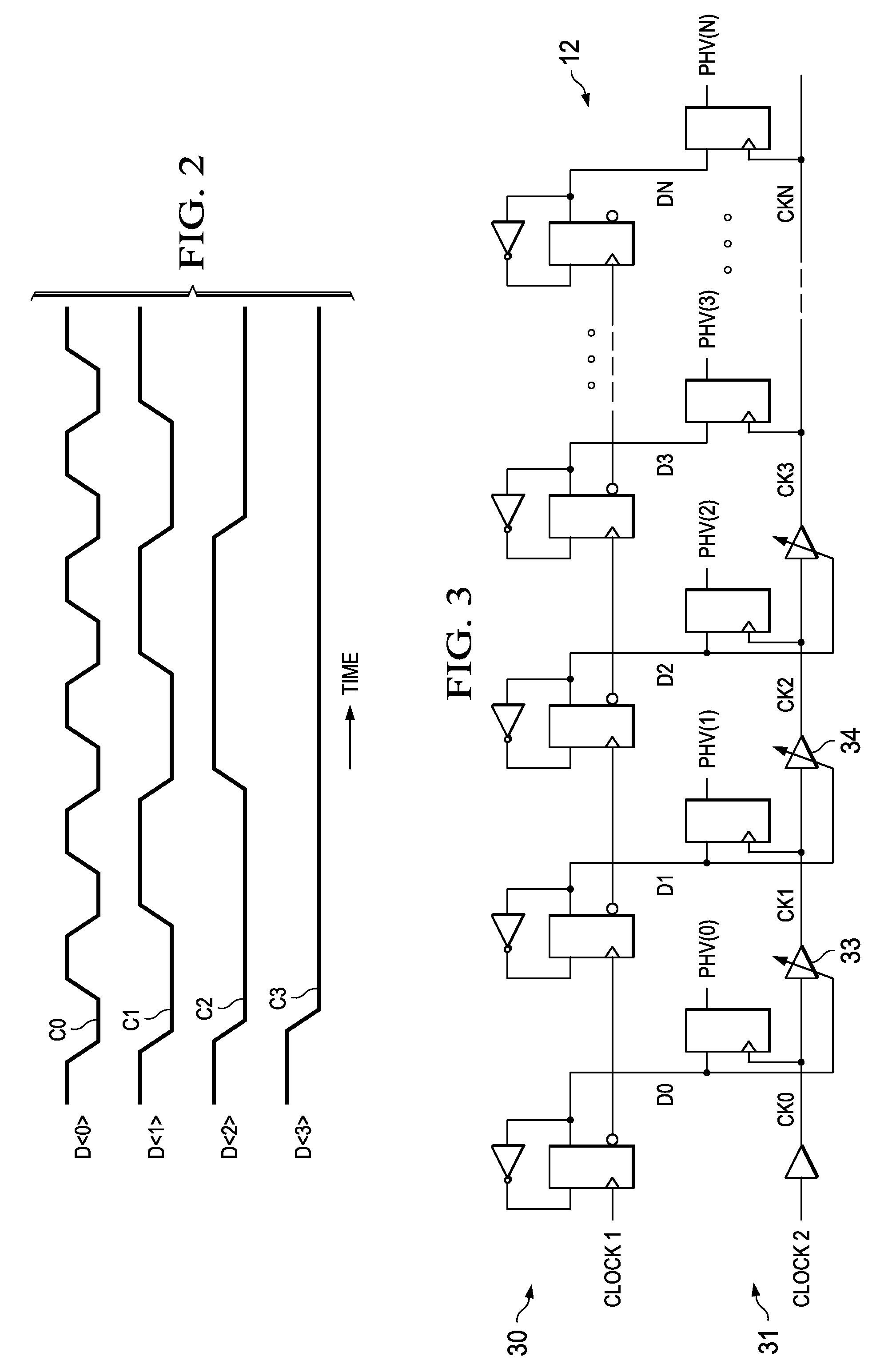

Multiple data rate counter, data converter including the same, and image sensor including the same

ActiveUS20110074968A1Improve performanceFaster and efficient operation of counterTelevision system detailsElectric signal transmission systemsData rateComputer science

A counter includes a buffer unit and a ripple counter. The buffer unit generates at least one least significant signal of a count by buffering at least one clock signal until a termination time point. The ripple counter generates at least one most significant signal of the count by sequentially toggling in response to at least one of the least significant signal. The counter performs multiple data rate counting with enhance operation speed and reduced power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

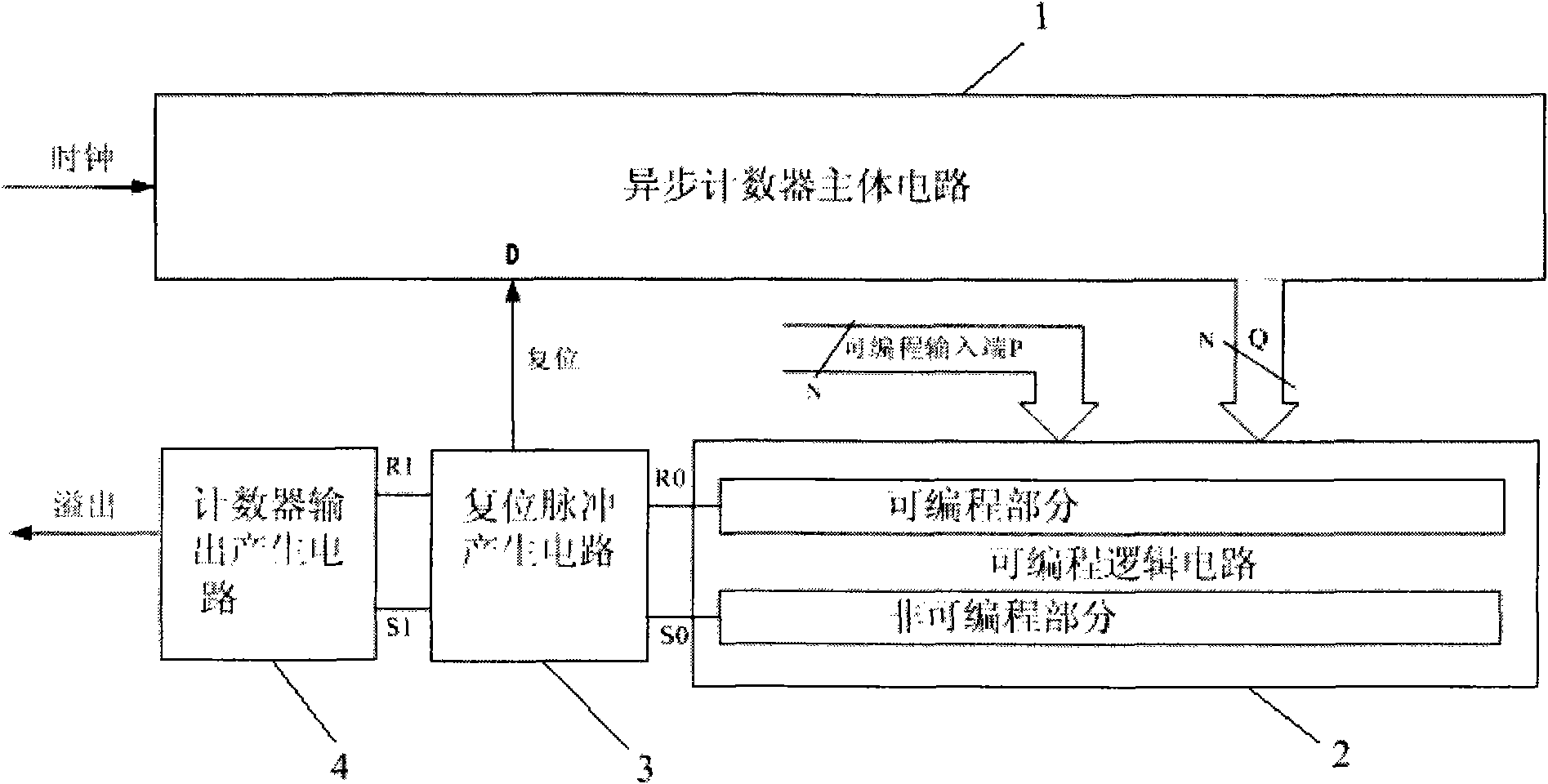

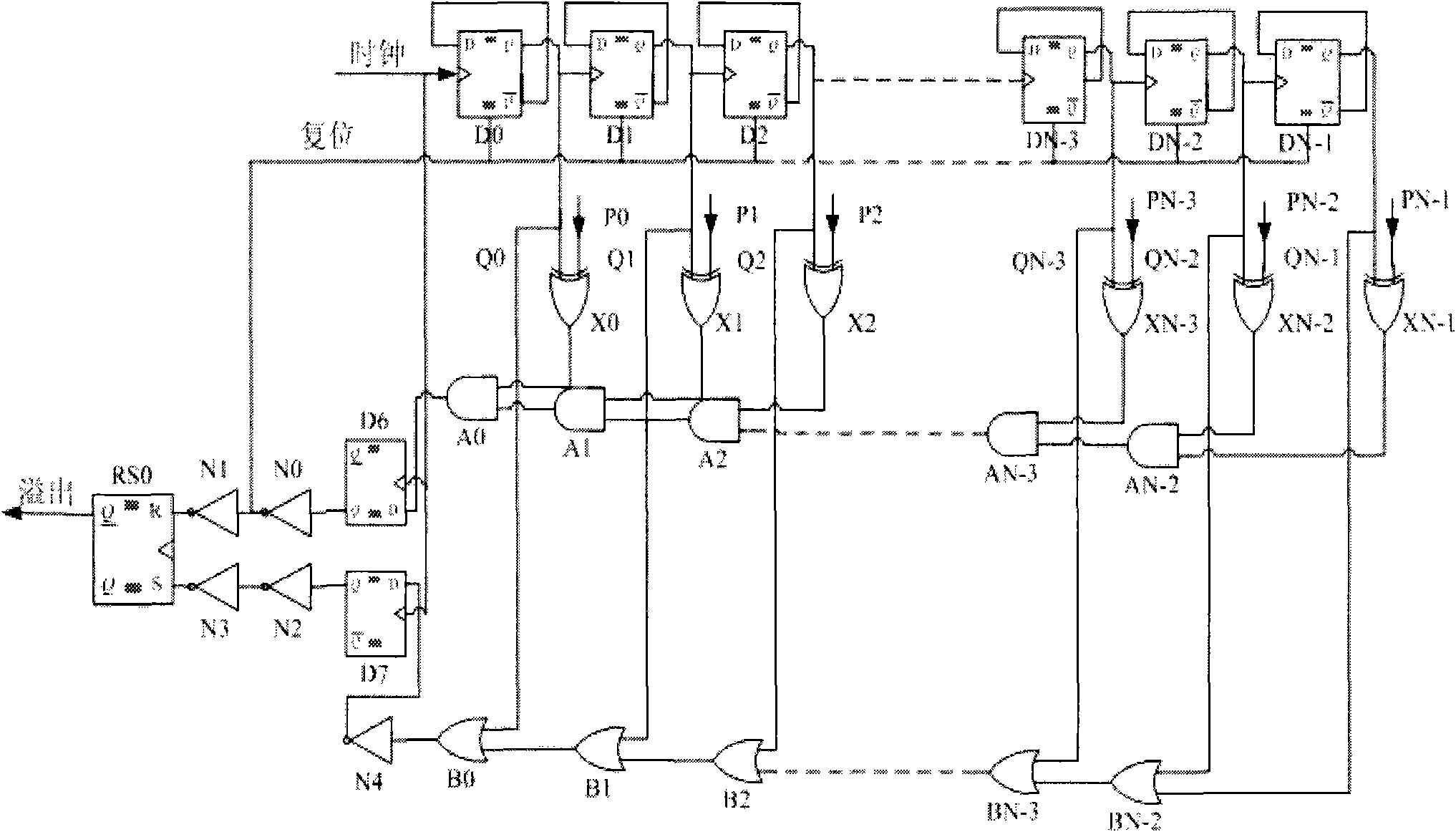

Glitch-eliminating programmable counter

InactiveCN101944907ANovel structureStrong elimination abilityCounting chain asynchronous pulse countersNAND logicNOR logic

The invention discloses a glitch-eliminating programmable counter, which comprises an asynchronous counter main body circuit, a programmable logic circuit, an reset pulse generation circuit and a counter output generation circuit, wherein the asynchronous counter main body circuit is provided with N-bit frequency division output end (Q0...QN-1), a programmable input end P and a trigger D; the programmable logic circuit is divided into a programmable part and a non-programmable part, the programmable part adopts a NAND logic, while the non-programmable part adopts a NOR logic; the reset pulse generation circuit is provided with two input ends R0 and S0 and three output ends; and the counter output generation circuit is provided with two input ends R1 and S1 and one outlet end. The glitch-eliminating programmable counter has the characteristics of simple design, novel circuit structure, high glitch-eliminating capability, easy realization and the like.

Owner:SOUTHEAST UNIV

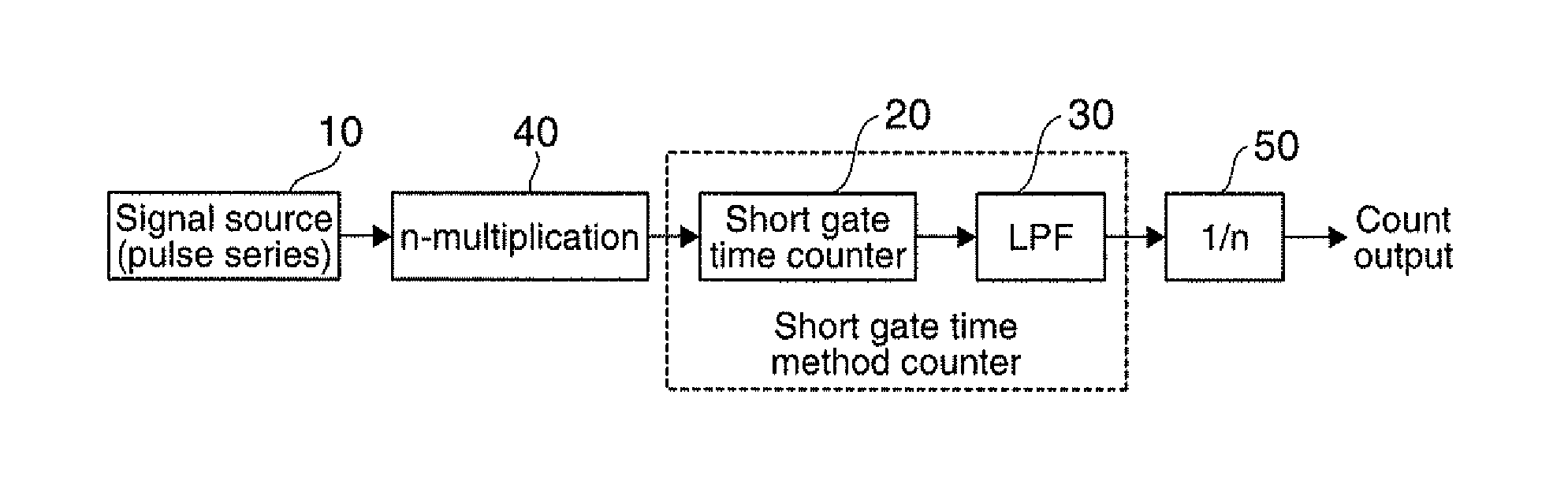

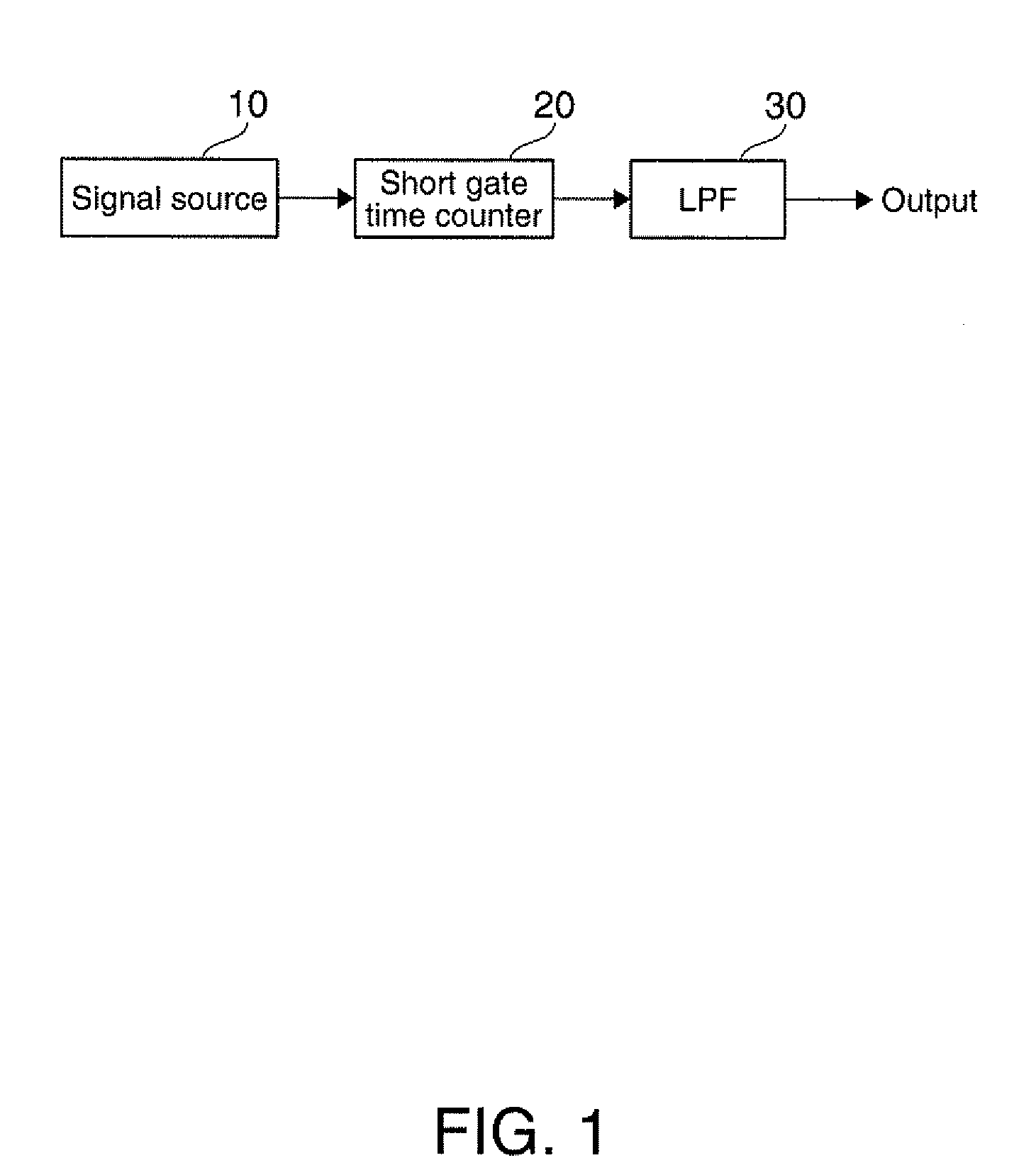

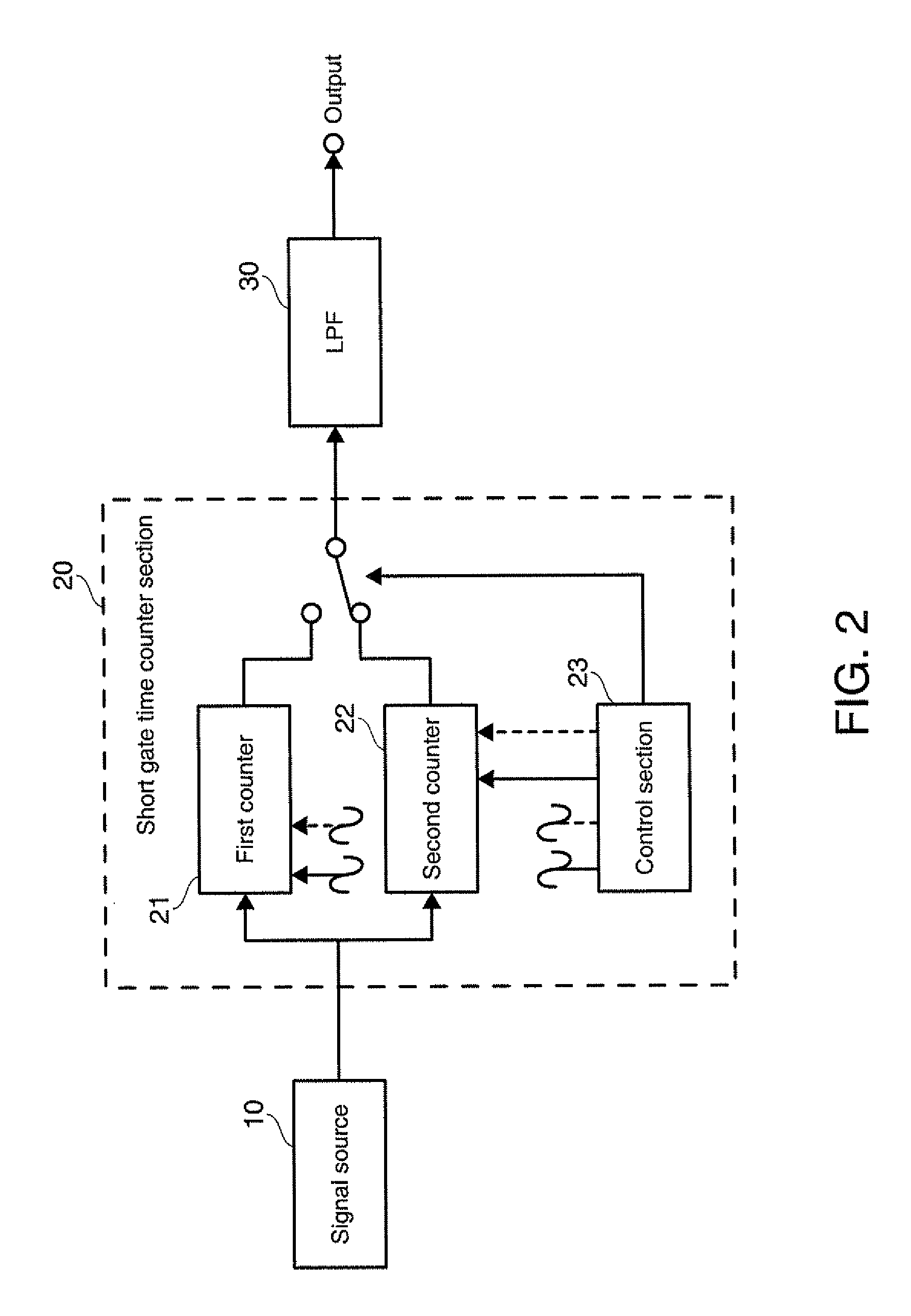

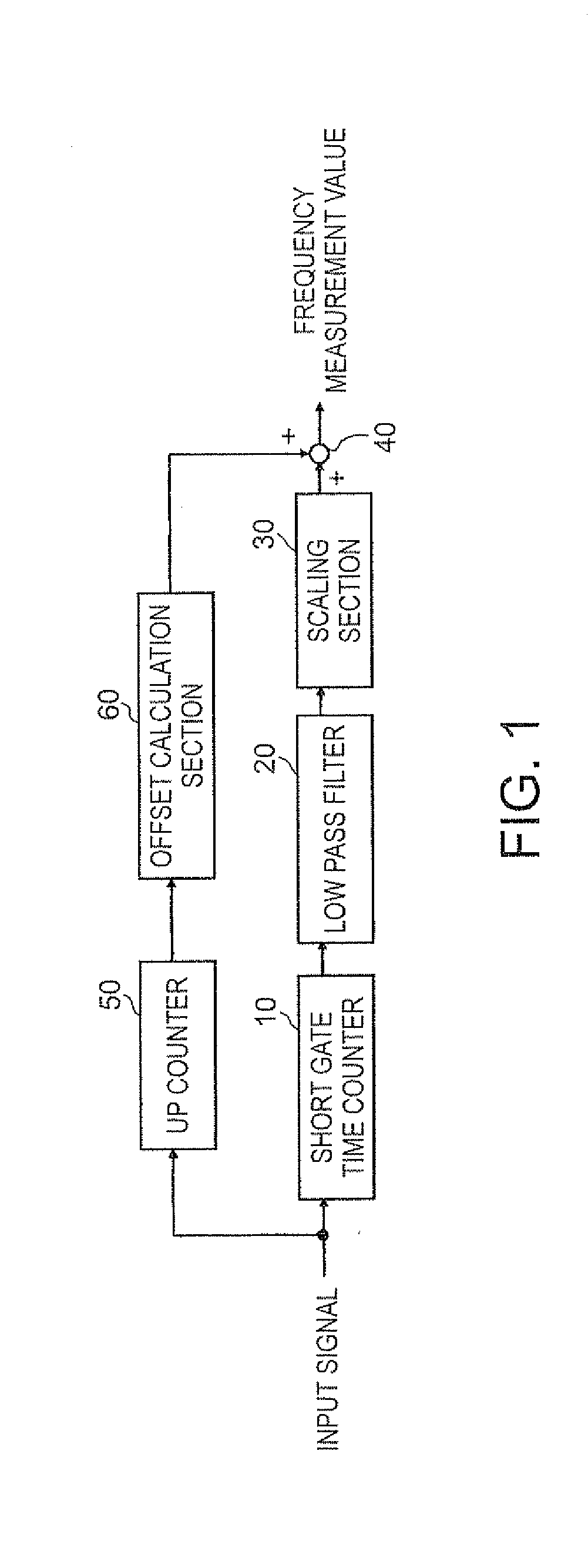

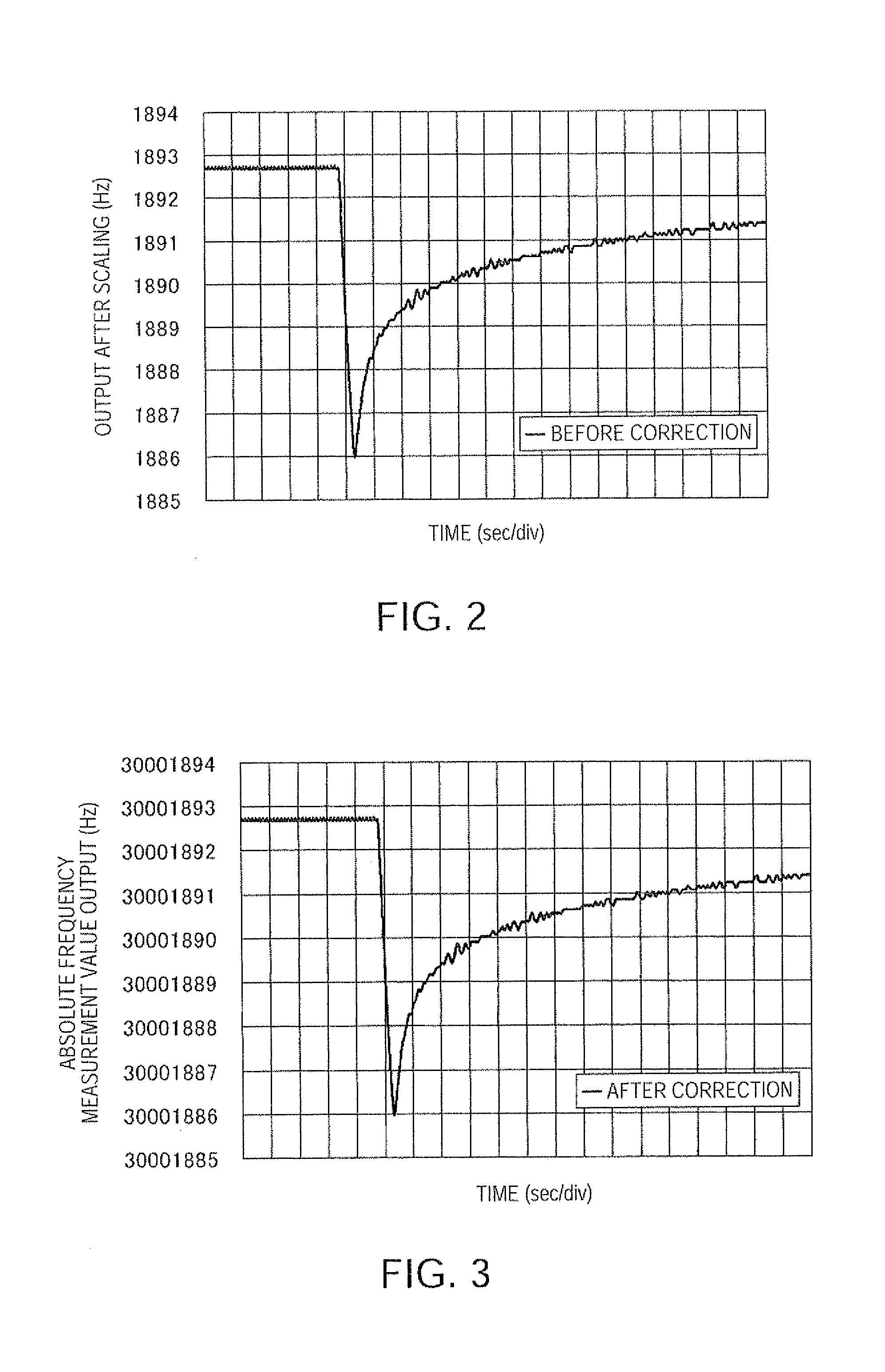

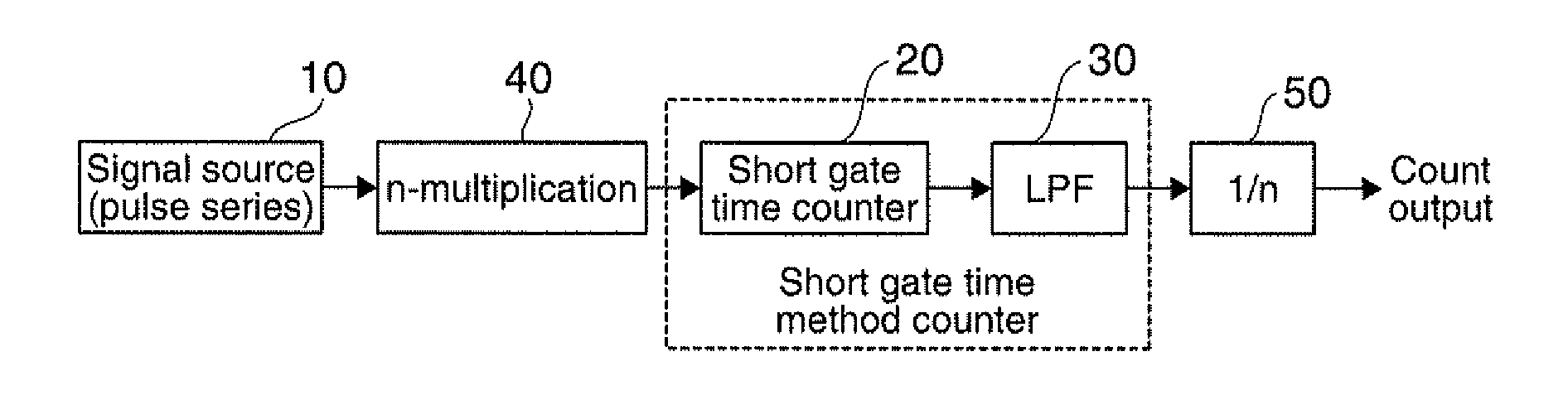

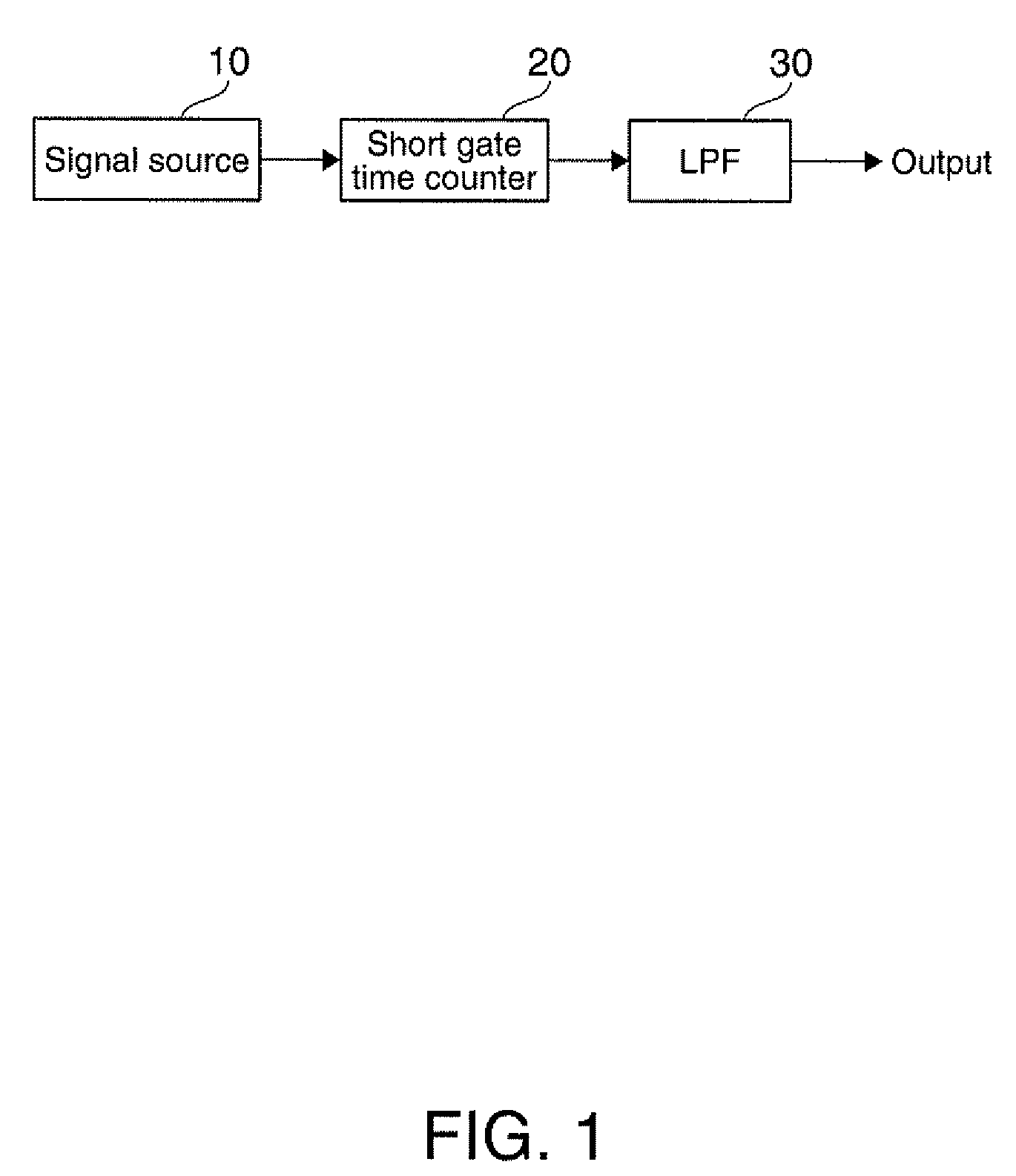

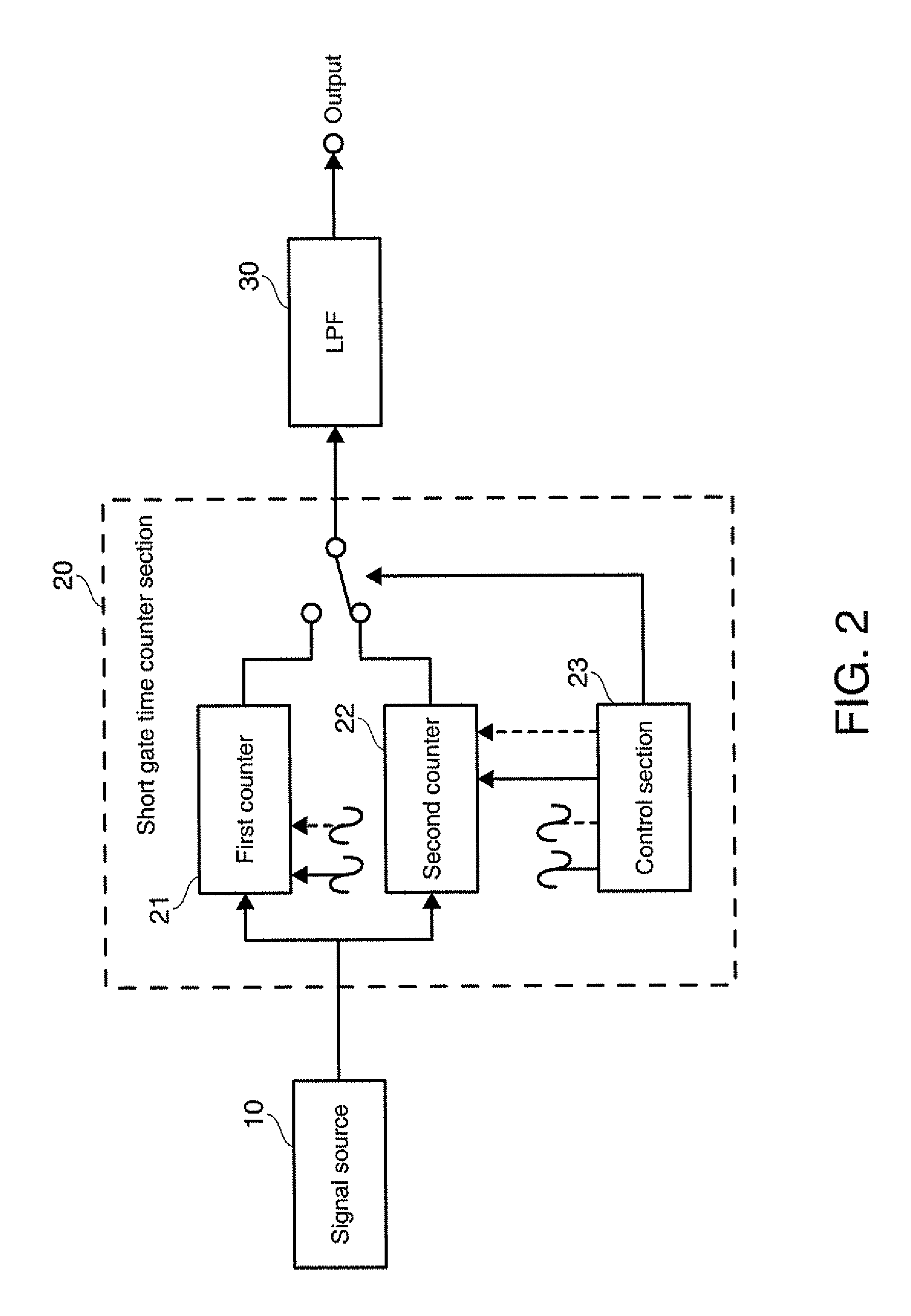

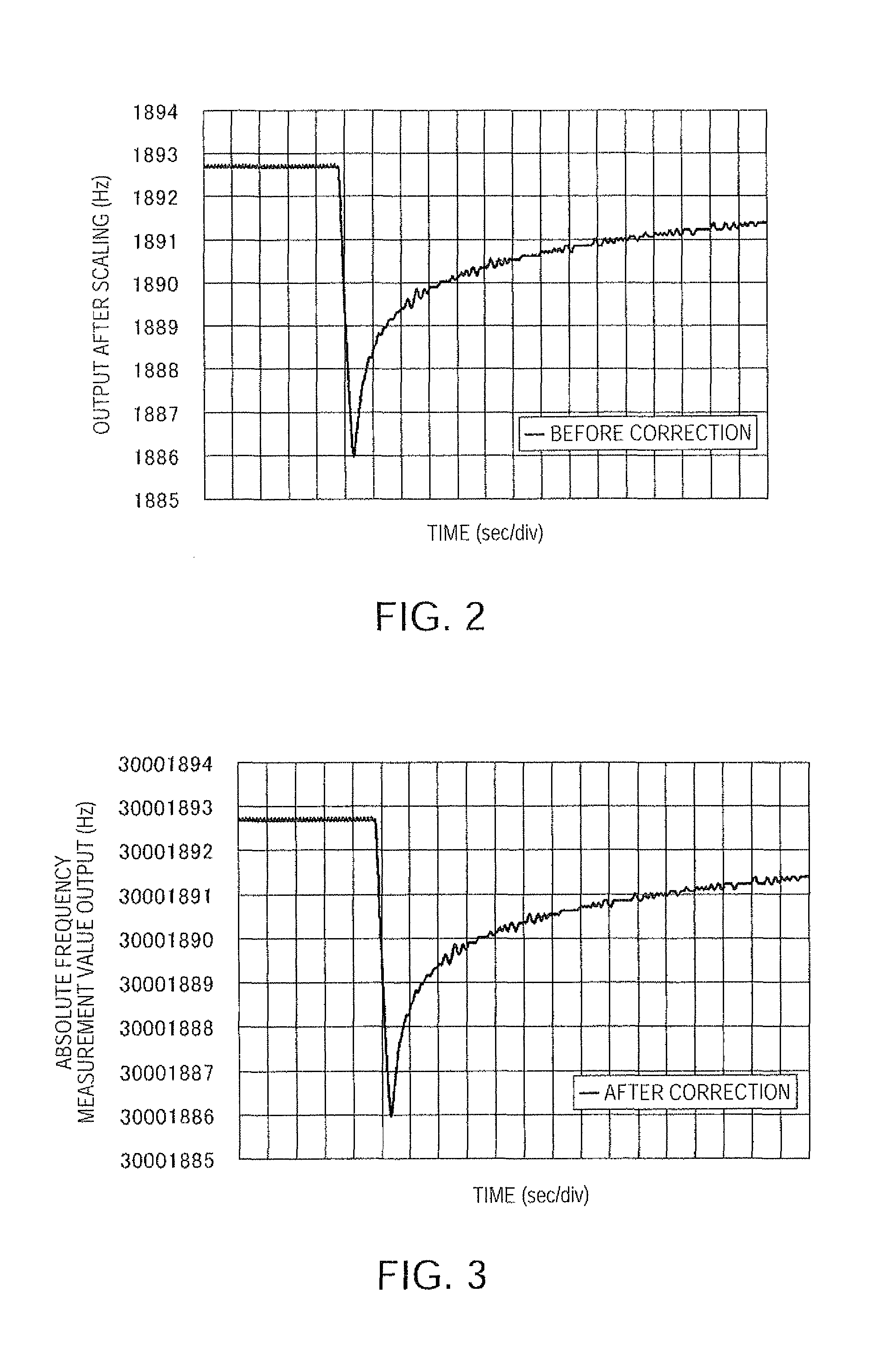

Frequency measurement device

ActiveUS20100295535A1High detection sensitivityImprove dynamic rangeDigital variable displayCounting chain synchronous pulse countersFrequency measurementsLow-pass filter

A frequency measurement device for measuring a frequency of a signal to be measured including a pulse signal, includes: a signal multiplier section that multiplies the signal to be measured by n is an integer) and outputs a multiplied signal; a counter section that counts the multiplied signal with a predetermined gate time and outputs a count value of the frequency of the signal to be measured at a predetermined period; and a low-pass filter that outputs a signal corresponding to the frequency of the signal to be measured based on the count value outputted at the predetermined period.

Owner:SEIKO EPSON CORP

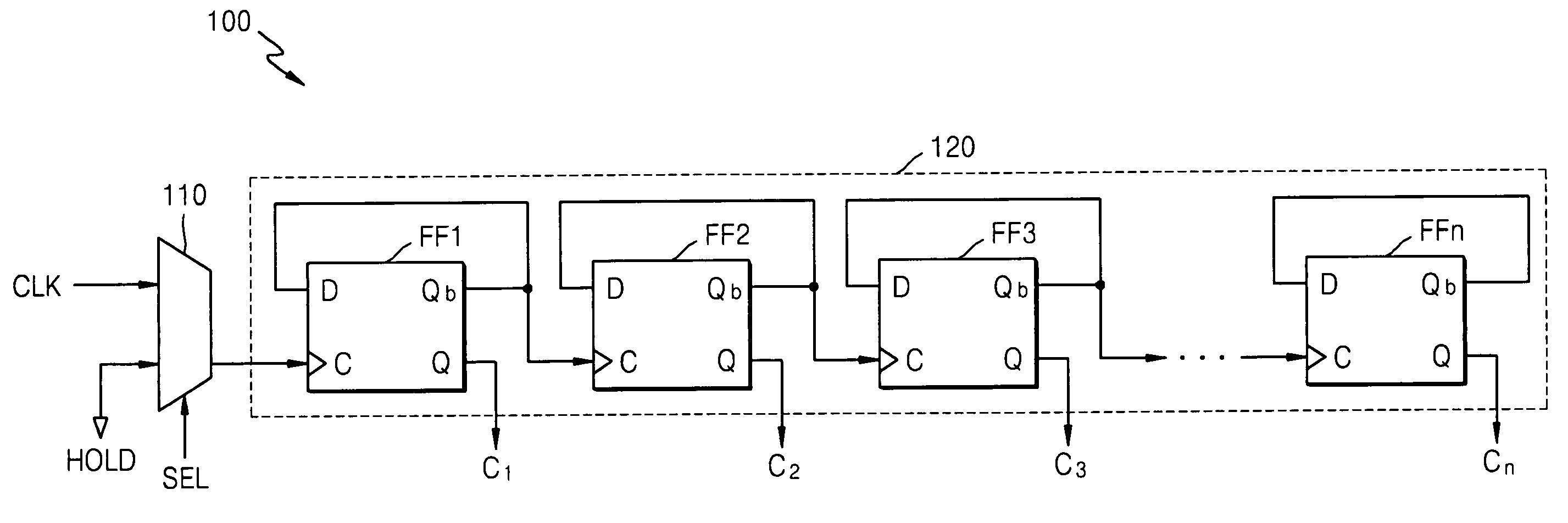

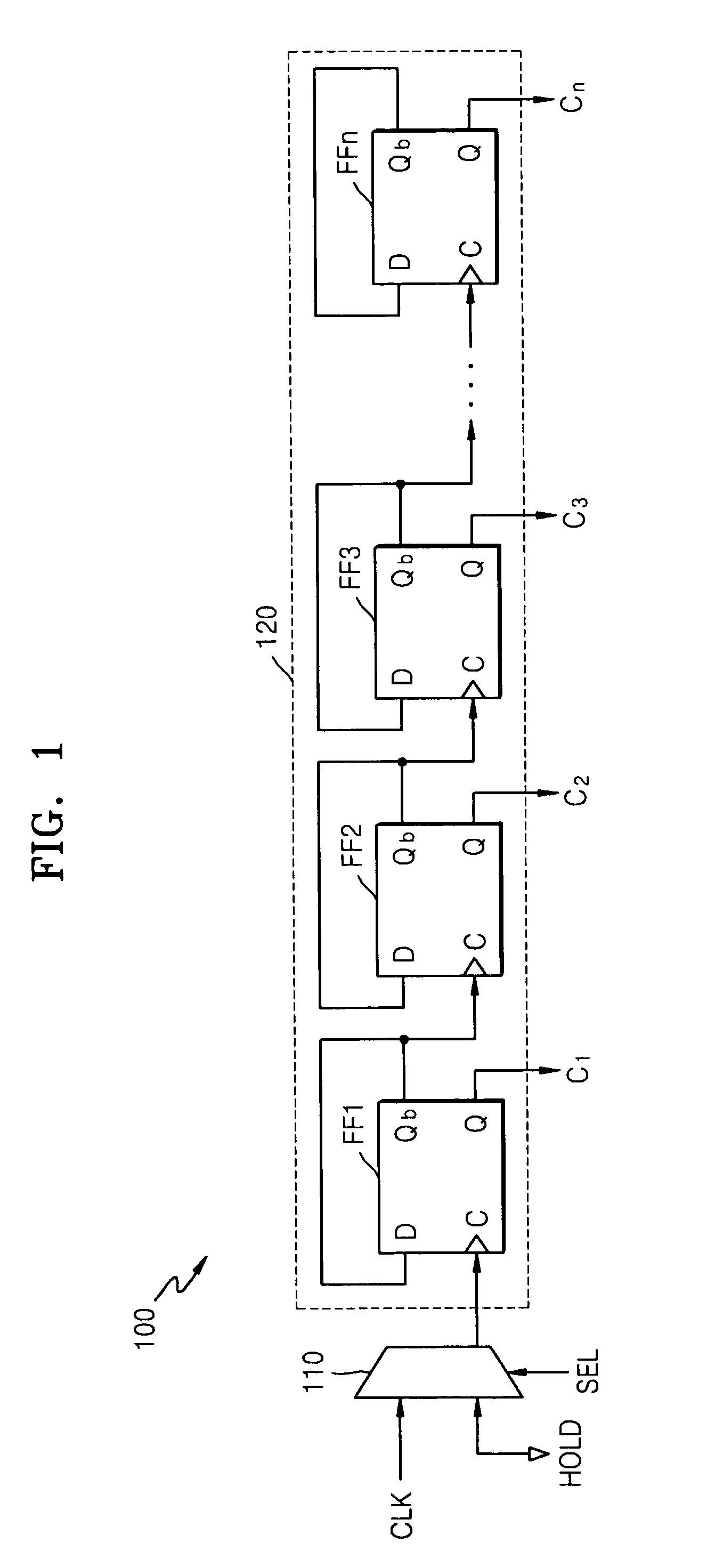

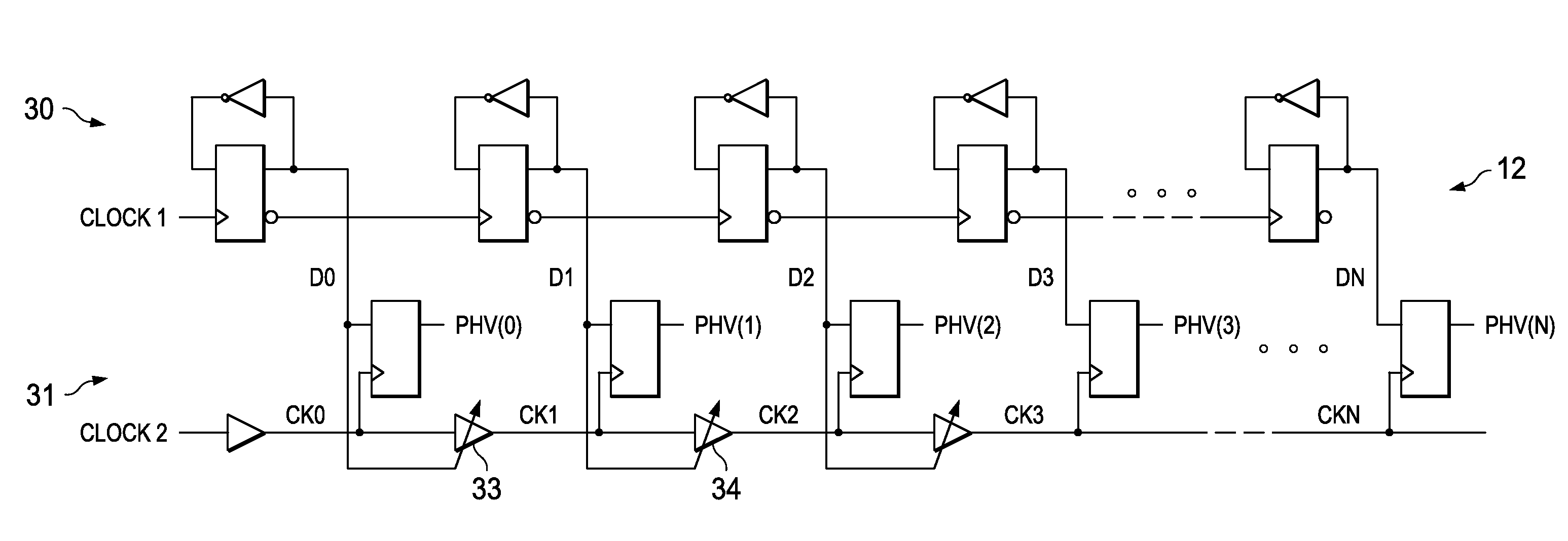

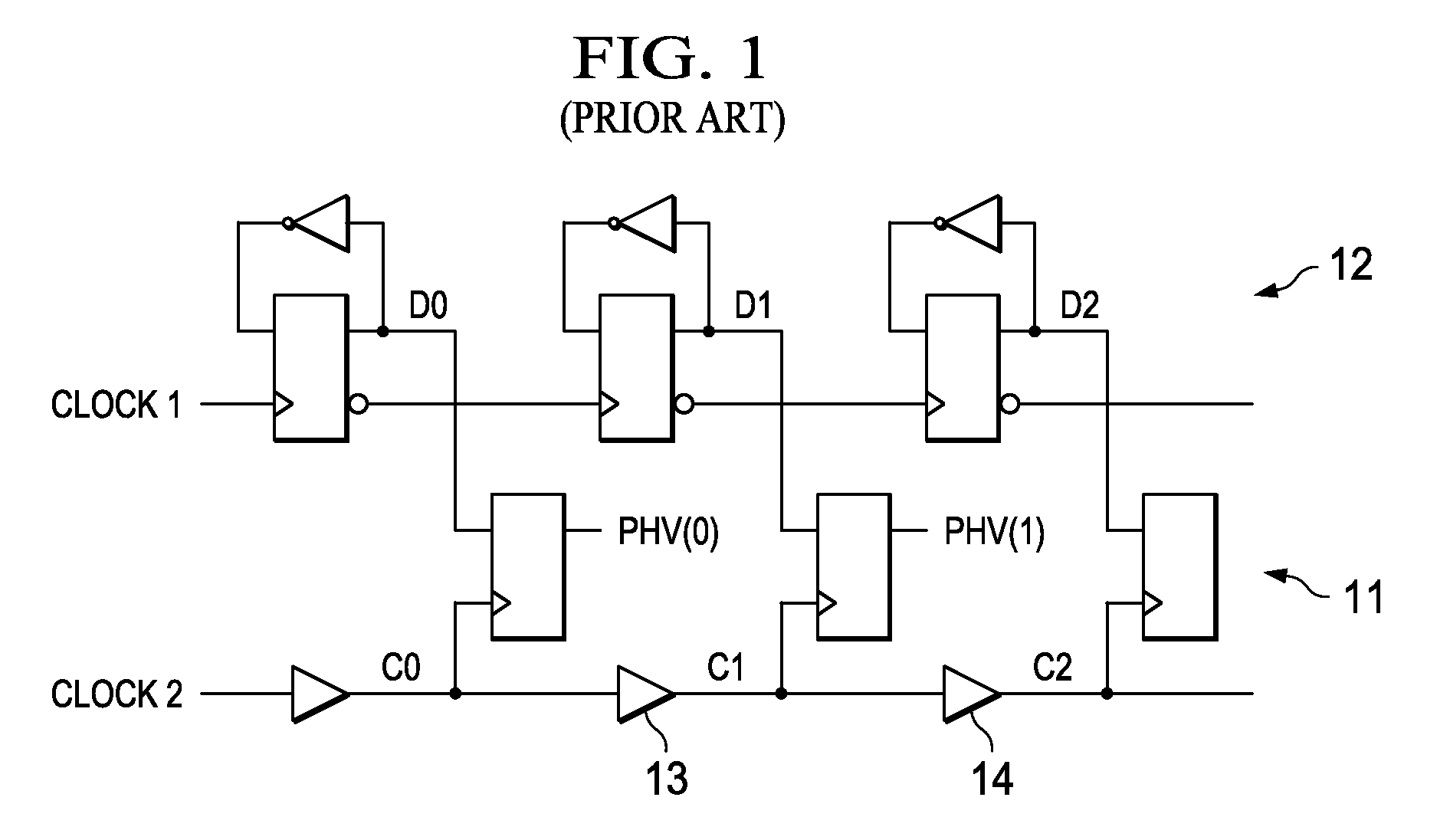

Counter capable of holding and outputting a count value and phase locked loop having the counter

ActiveUS7555094B2Pulse automatic controlCounting chain asynchronous pulse countersEngineeringPhase-locked loop

Owner:SAMSUNG ELECTRONICS CO LTD

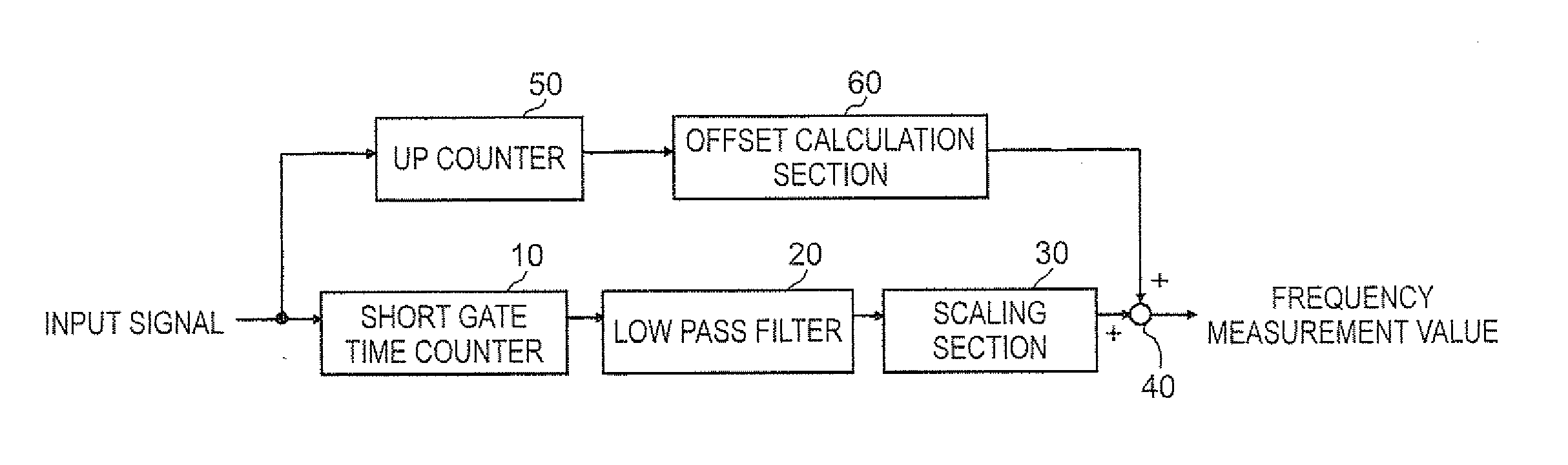

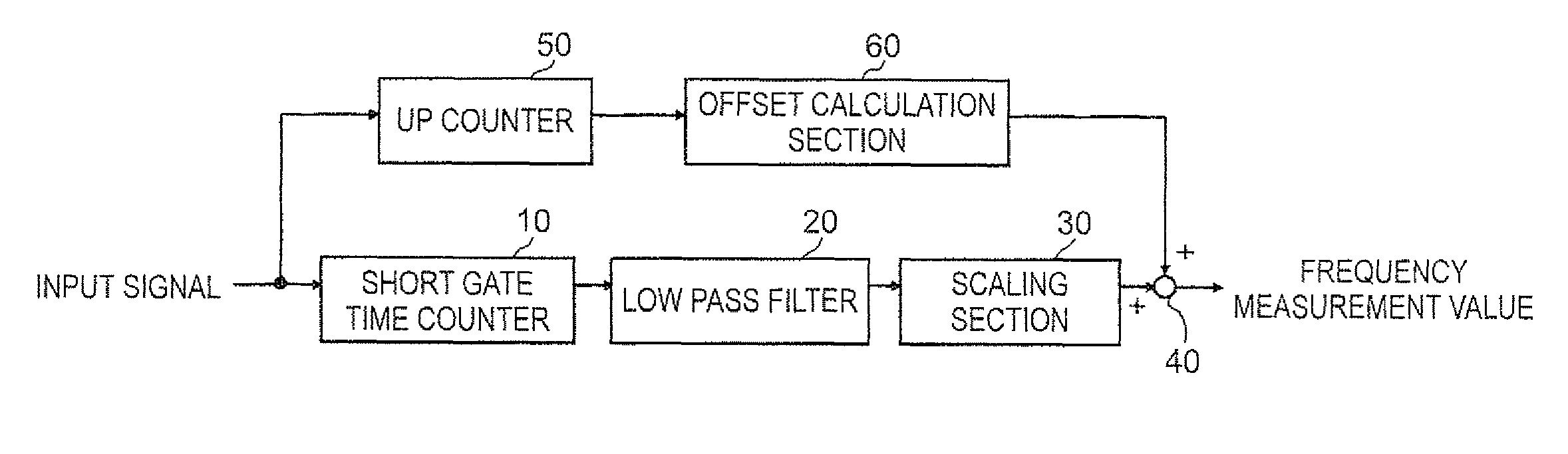

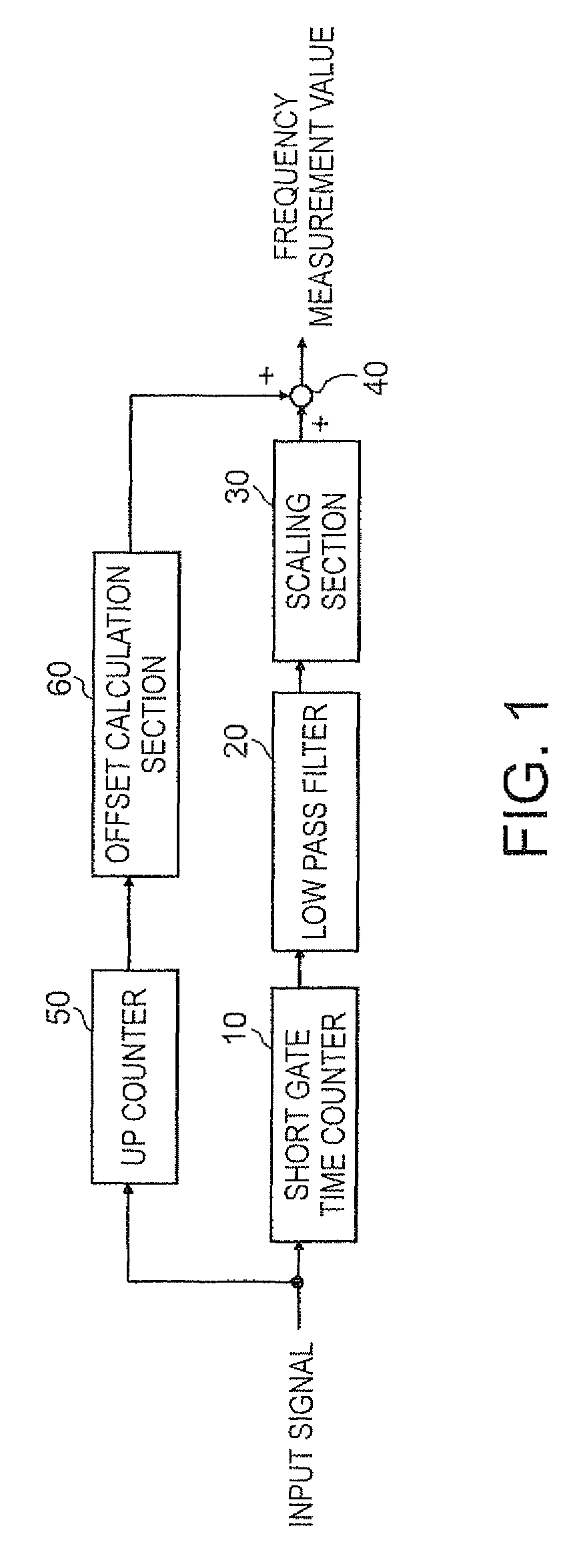

Frequency measuring apparatus

ActiveUS20100295537A1SpeedConducive to simplificationDigital variable displayCounting chain synchronous pulse countersComputer engineeringSignal frequency

A frequency measuring apparatus includes: a high-order digit calculation section adapted to measure an input signal and output a high-order digit value of a frequency value of the input signal; a low-order digit calculation section adapted to measure the input signal and output a low-order digit value of the frequency value of the input signal; and an adding section adapted to add the high-order digit value and the low-order digit value to each other to output the frequency value of the input signal.

Owner:SEIKO EPSON CORP

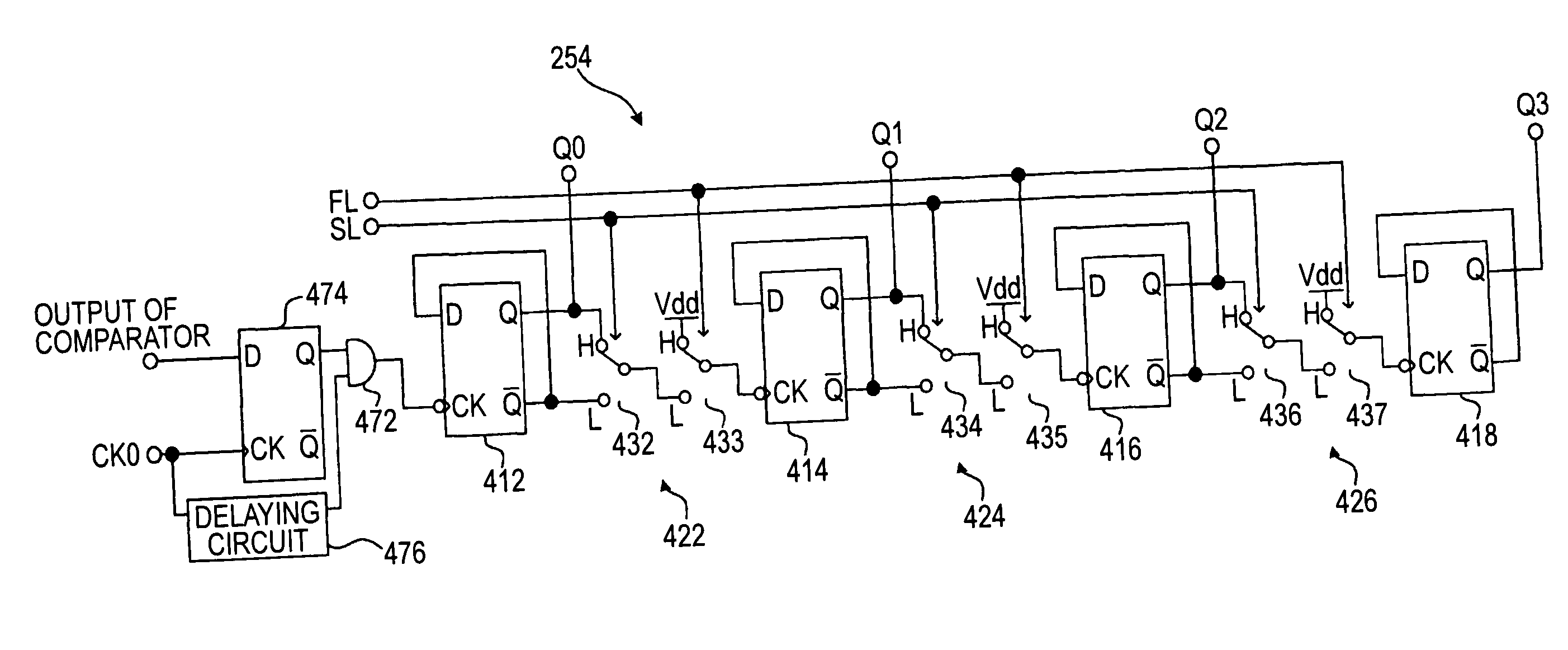

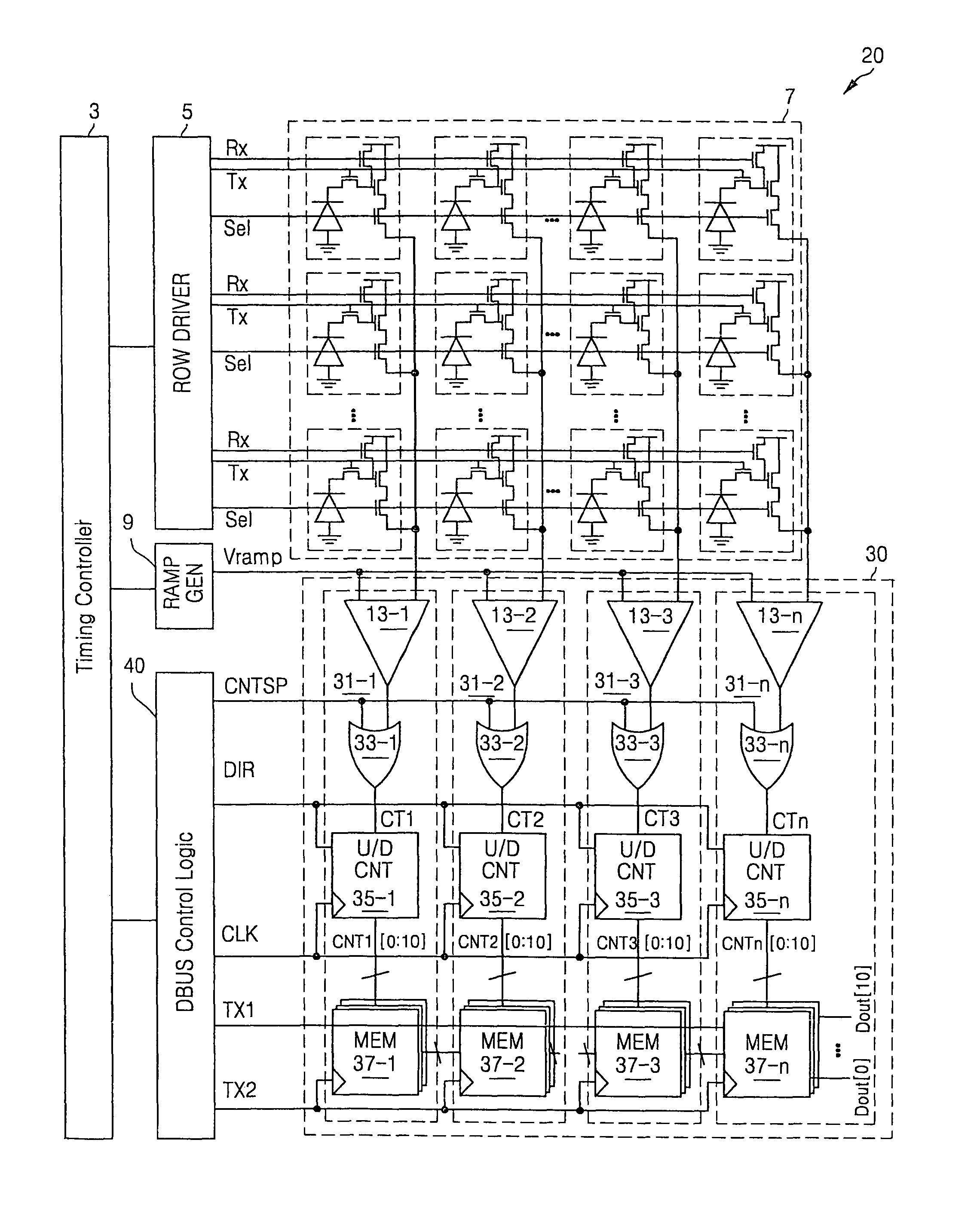

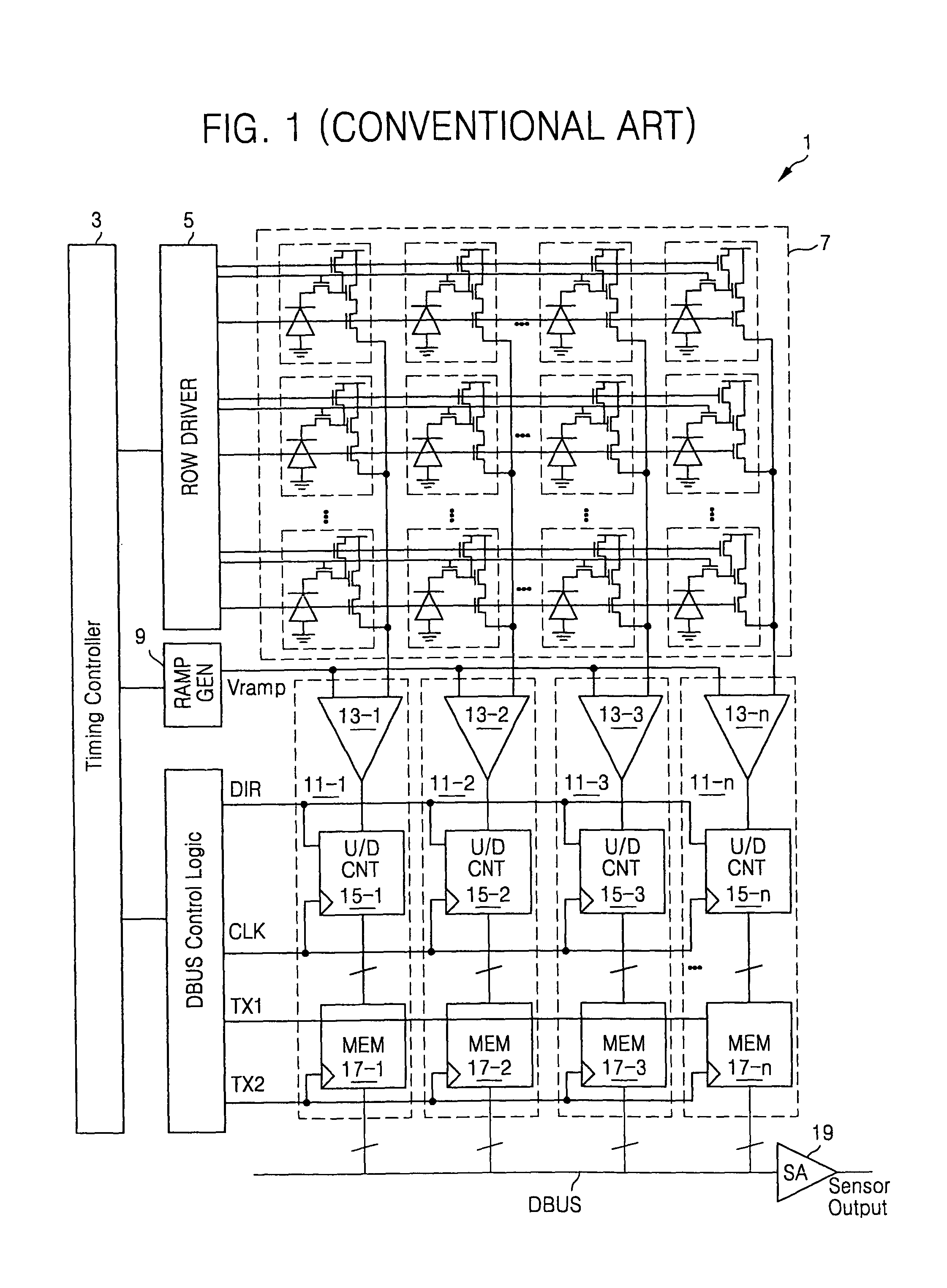

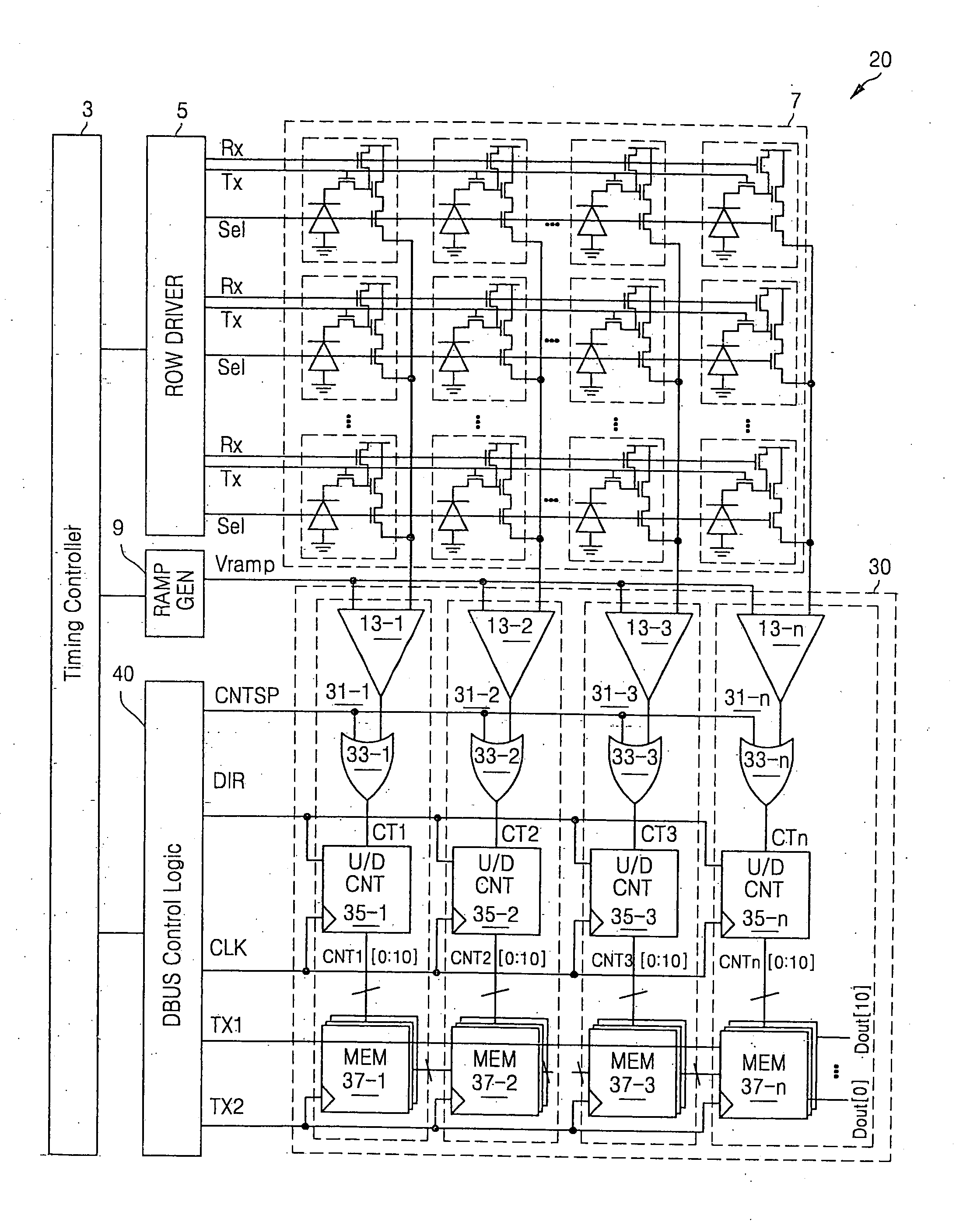

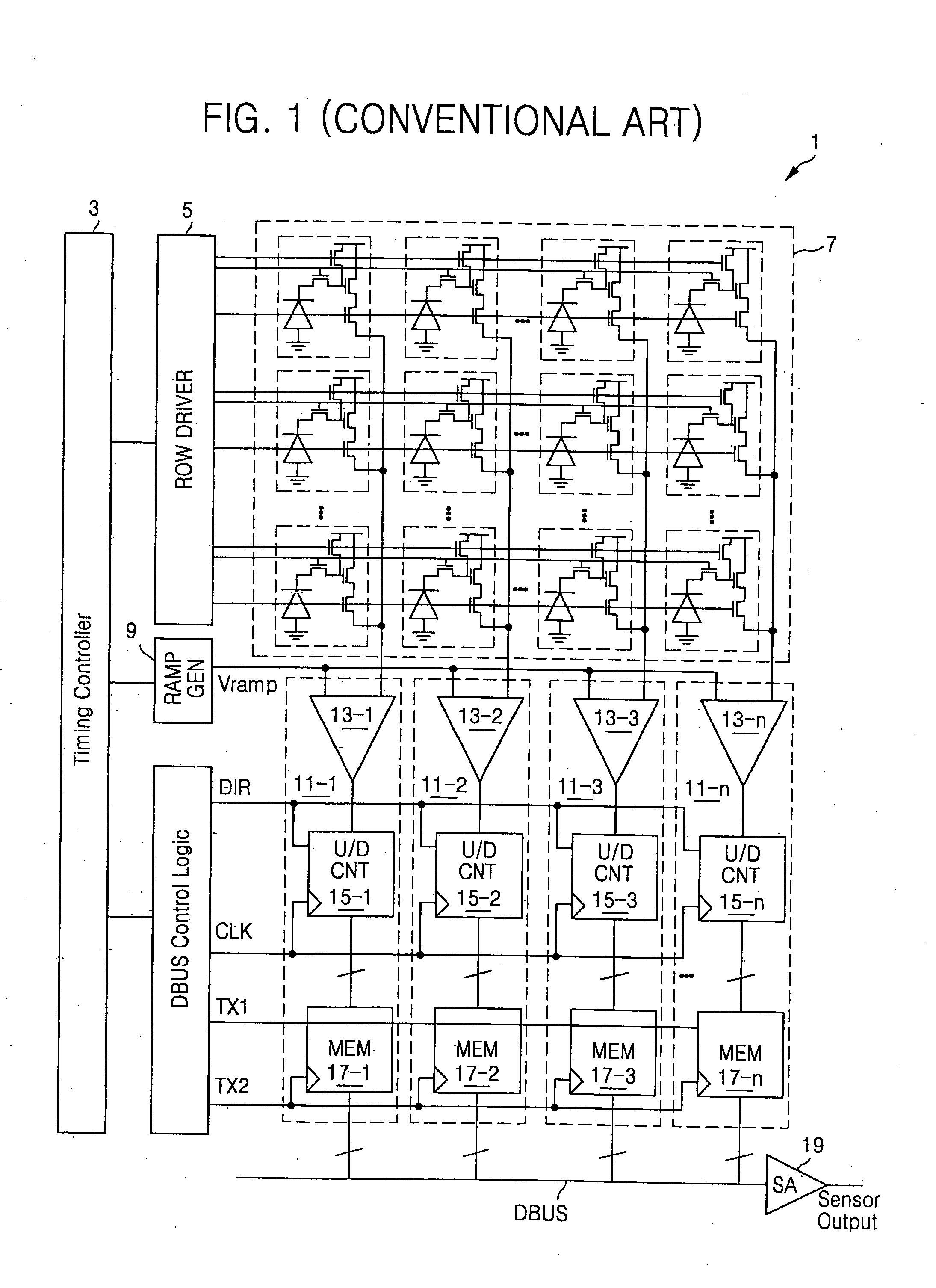

Method of operating ripple counter, image sensor having ripple counter, method of operating image sensor, and analog-to-digital converter of image sensor

ActiveUS8174594B2Reduce chip sizeSmall sizeTelevision system detailsTelevision system scanning detailsControl signalA d converter

An example embodiment of an image sensor may include a controller and a plurality of up / down ripple counters. The controller may generate a first control signal and a second control signal. Each of the up / down ripple counters may perform a stop operation or a count operation in response to a corresponding one of a plurality of operation control signals generated based on at least in part on the first control signal. The count operation may be an up-count operation or a down-count operation based on the second control signal. The image sensor may also include a plurality of memory chains. Each of the memory chains may receive a count value output from the up / down counters and may shift the received count value in response to a third control signal and a fourth control signal output from the controller.

Owner:SAMSUNG ELECTRONICS CO LTD

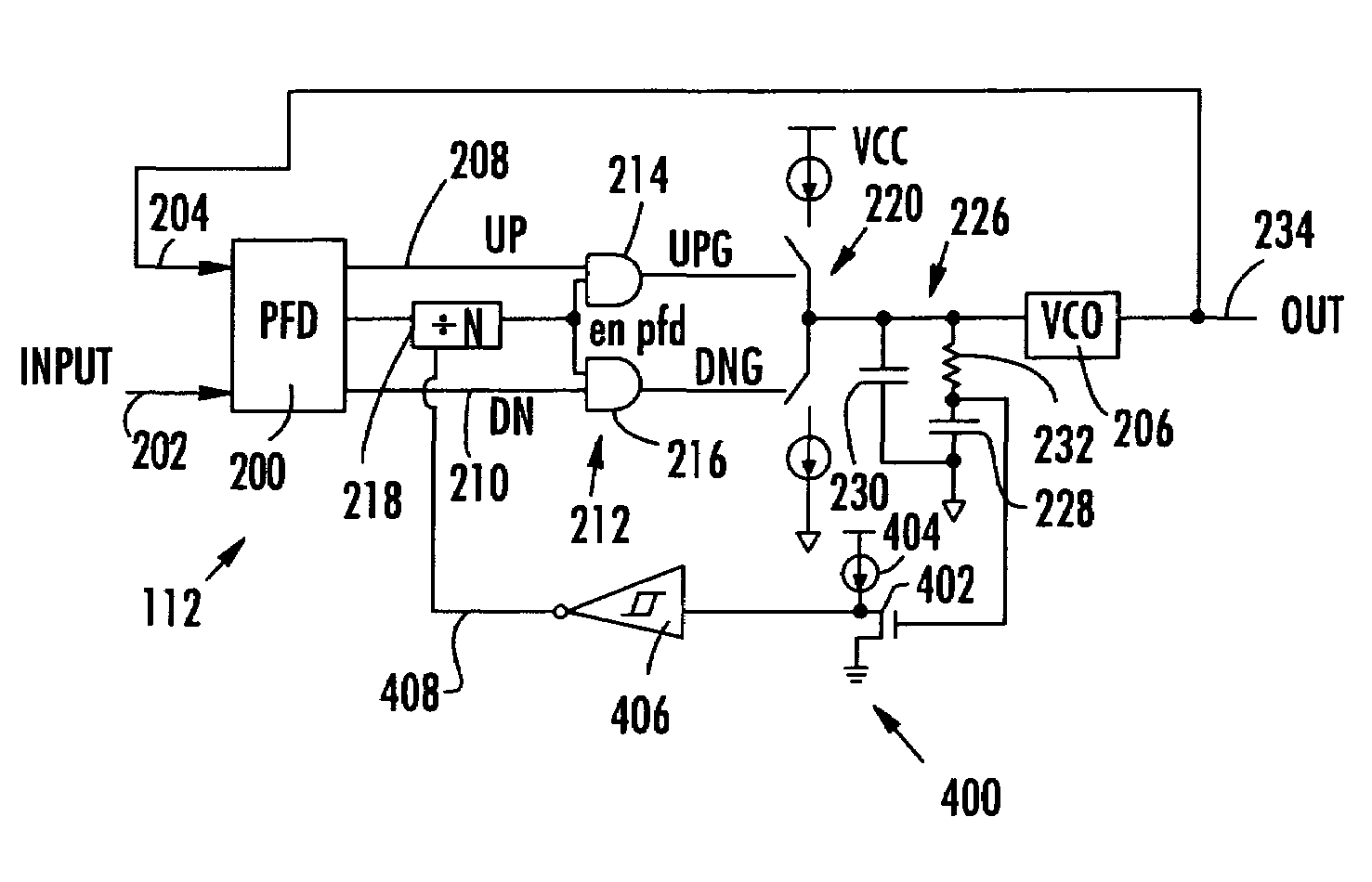

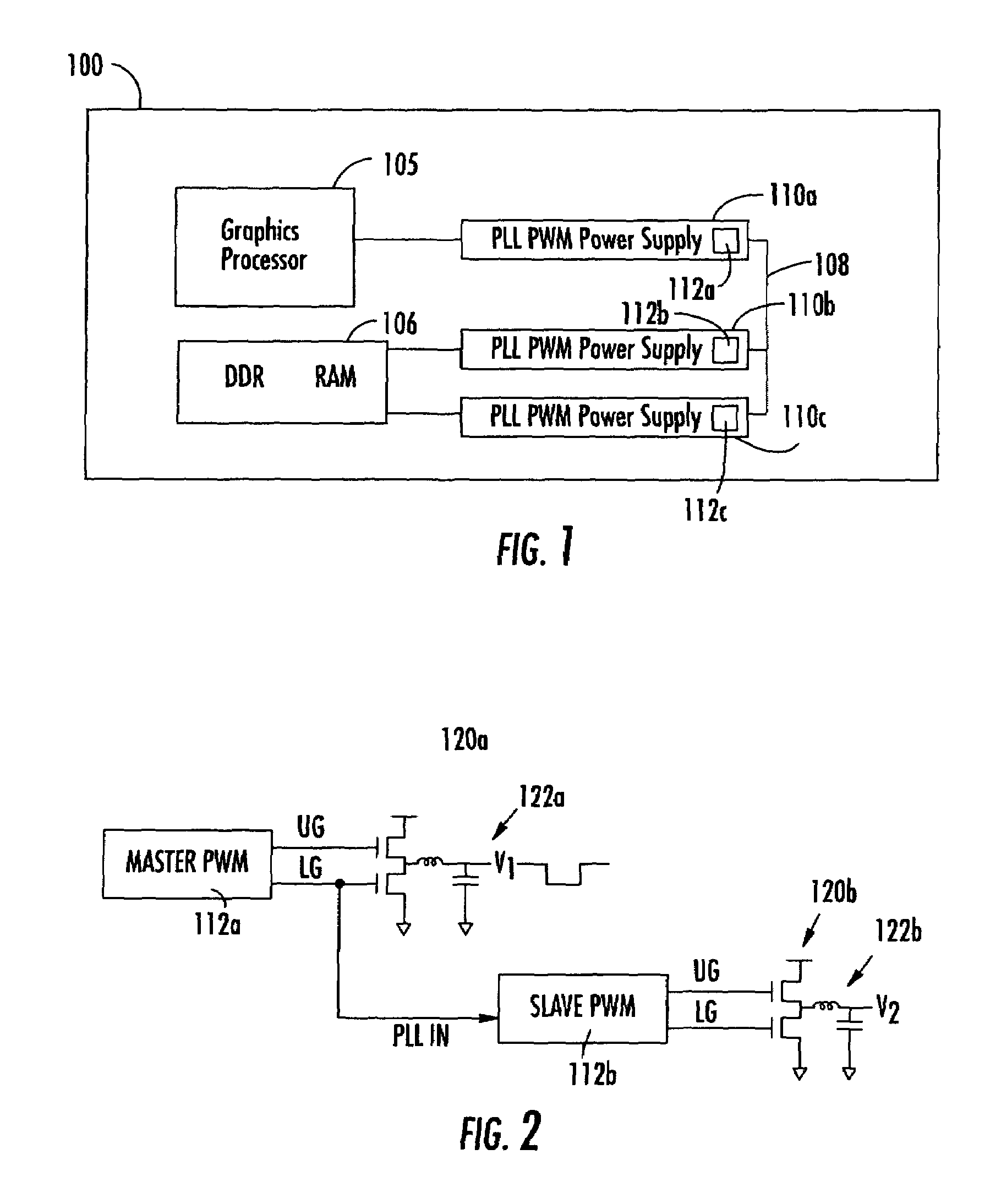

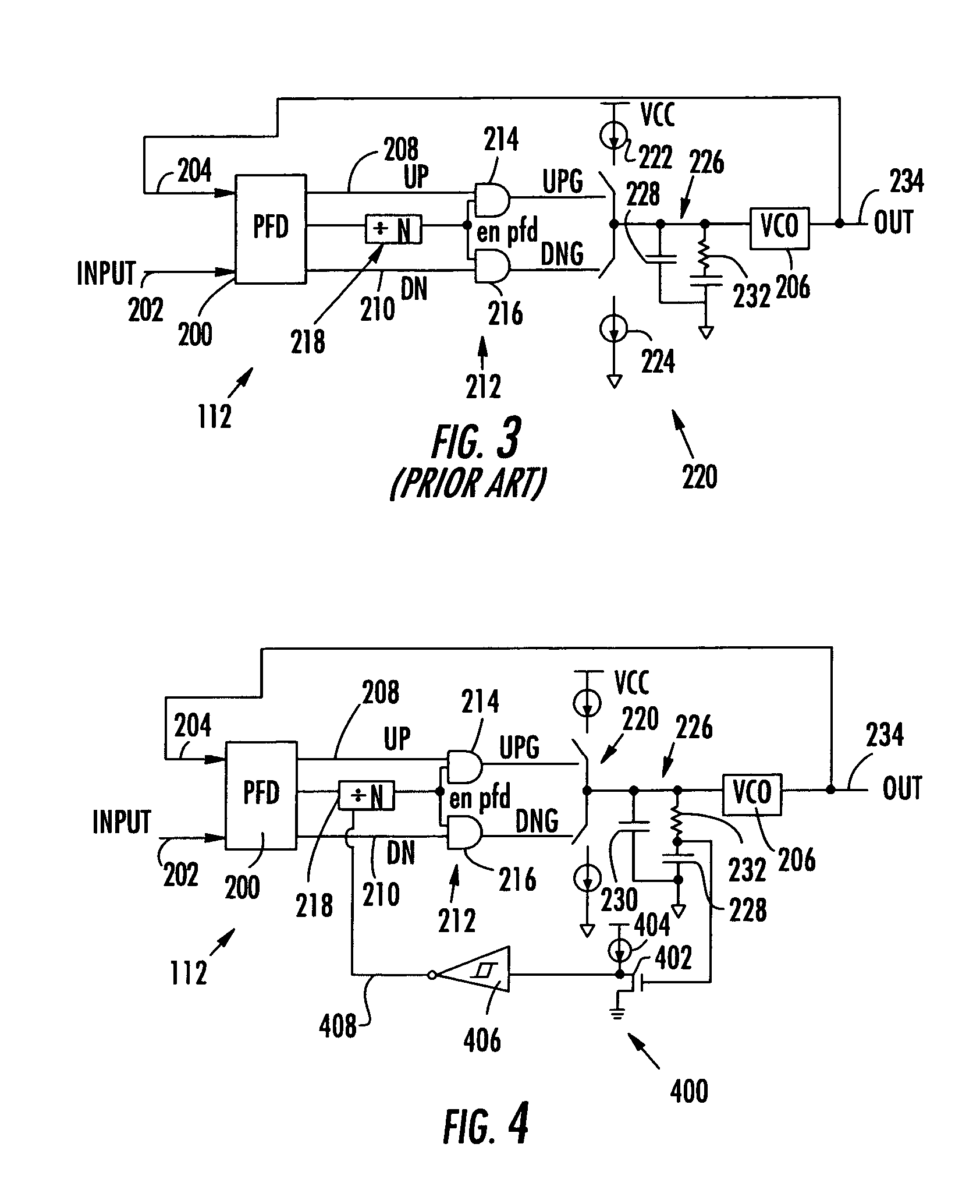

Programmable bandwidth during start-up for phase-lock loop

InactiveUS7023250B2Pulse automatic controlCounting chain asynchronous pulse countersPhase differencePhase frequency detector

A phase lock loop PLL which includes an oscillator having an oscillator signal whose frequency is related to a received error correction signal and phase frequency detector receiving and comparing the oscillator signal and a reference signal from a master circuit and generating the error correction signal based on the phase difference of the oscillator signal and the reference signal. A filter, including a capacitor, connects the error correction signal from the phase-frequency detector to the oscillator. A rate selector monitors a charge on the capacitor and controls the rate of error connection signals as a function of the charge on the capacitor.

Owner:INTERSIL INC

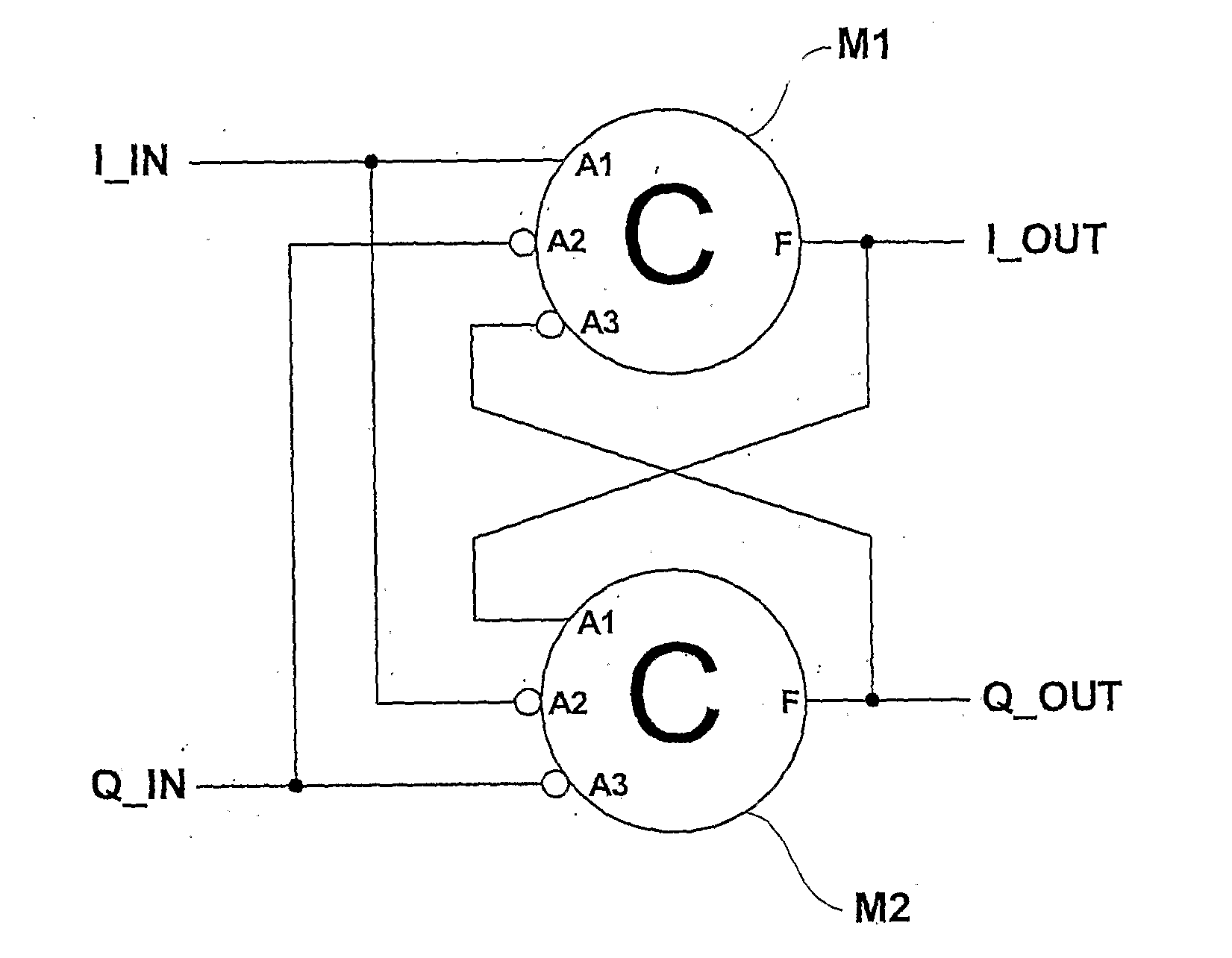

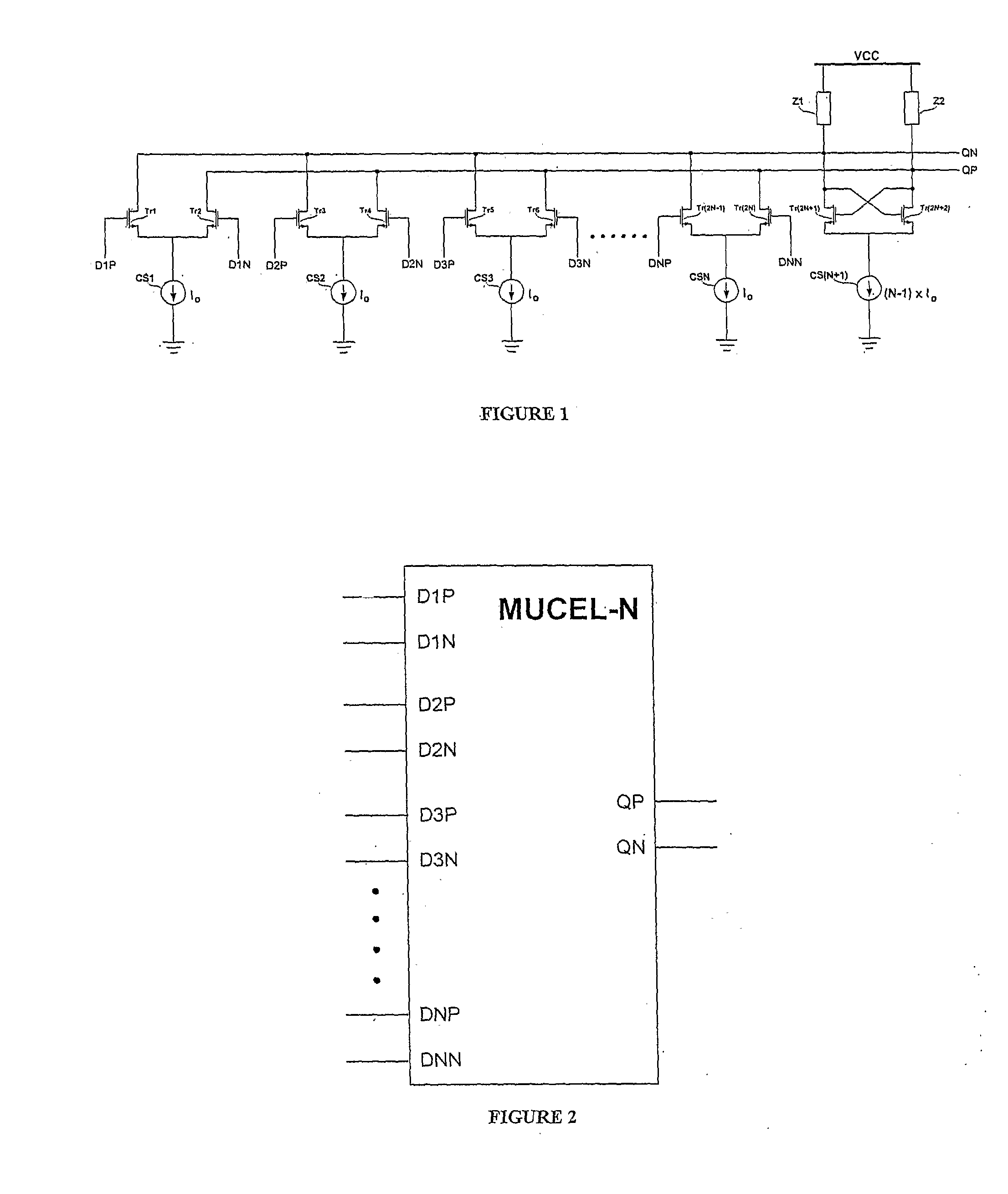

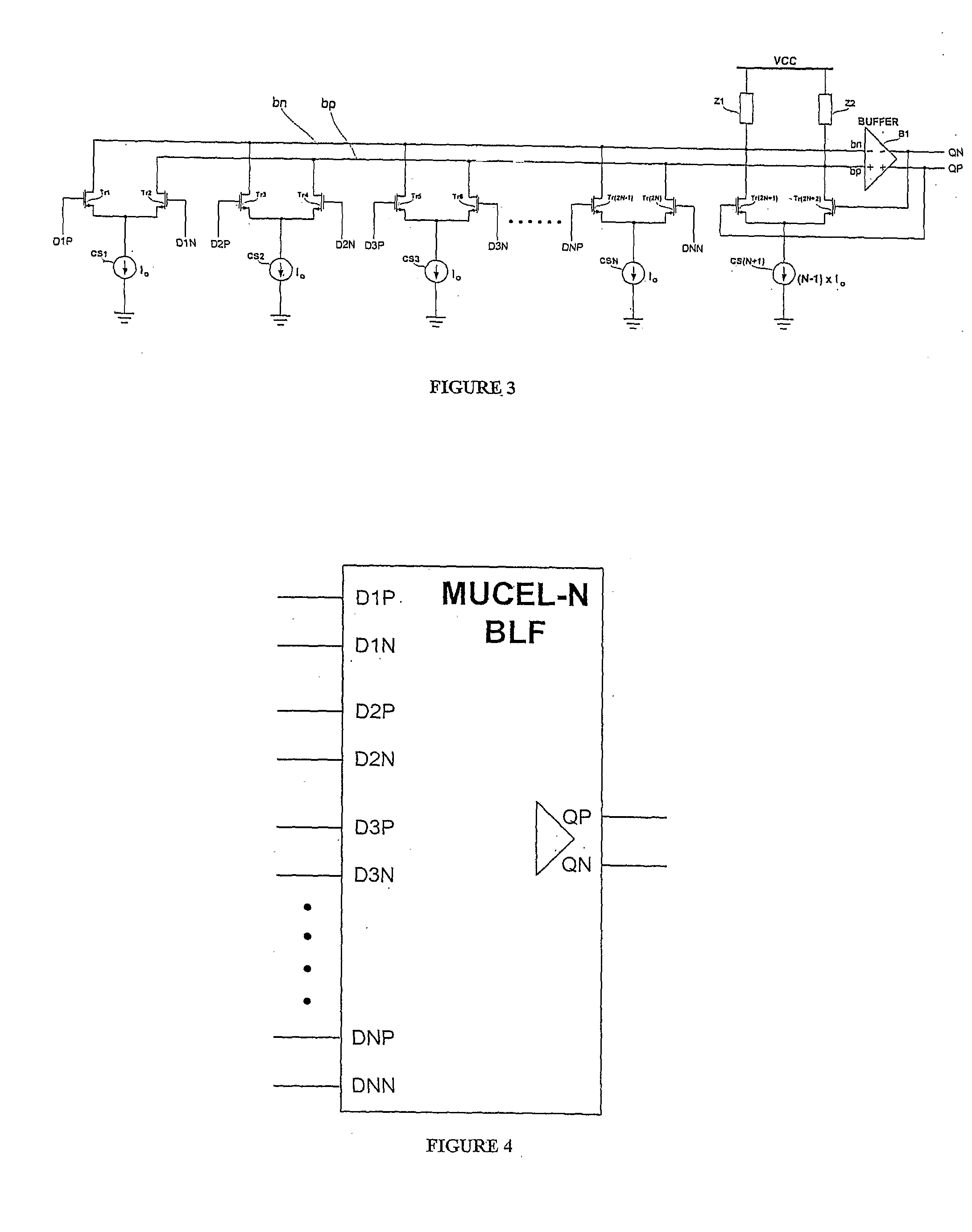

Quadrature Divide-By-Three Frequency Divider and Low Voltage Muller C Element

ActiveUS20080260089A1Cost advantageEnsure effective implementationMajority/minority circuitsPulse counters with static storageLow voltageLocal oscillator

A low voltage, low power, wideband quadrature divide-by-three frequency divider using a wideband low voltage, low power differential Muller C element with multiple inputs operates on quadrature input and quadrature output signals. This frequency divider can be used in frequency synthesisers and as quadrature local oscillator generator.

Owner:TEXAS INSTR INC

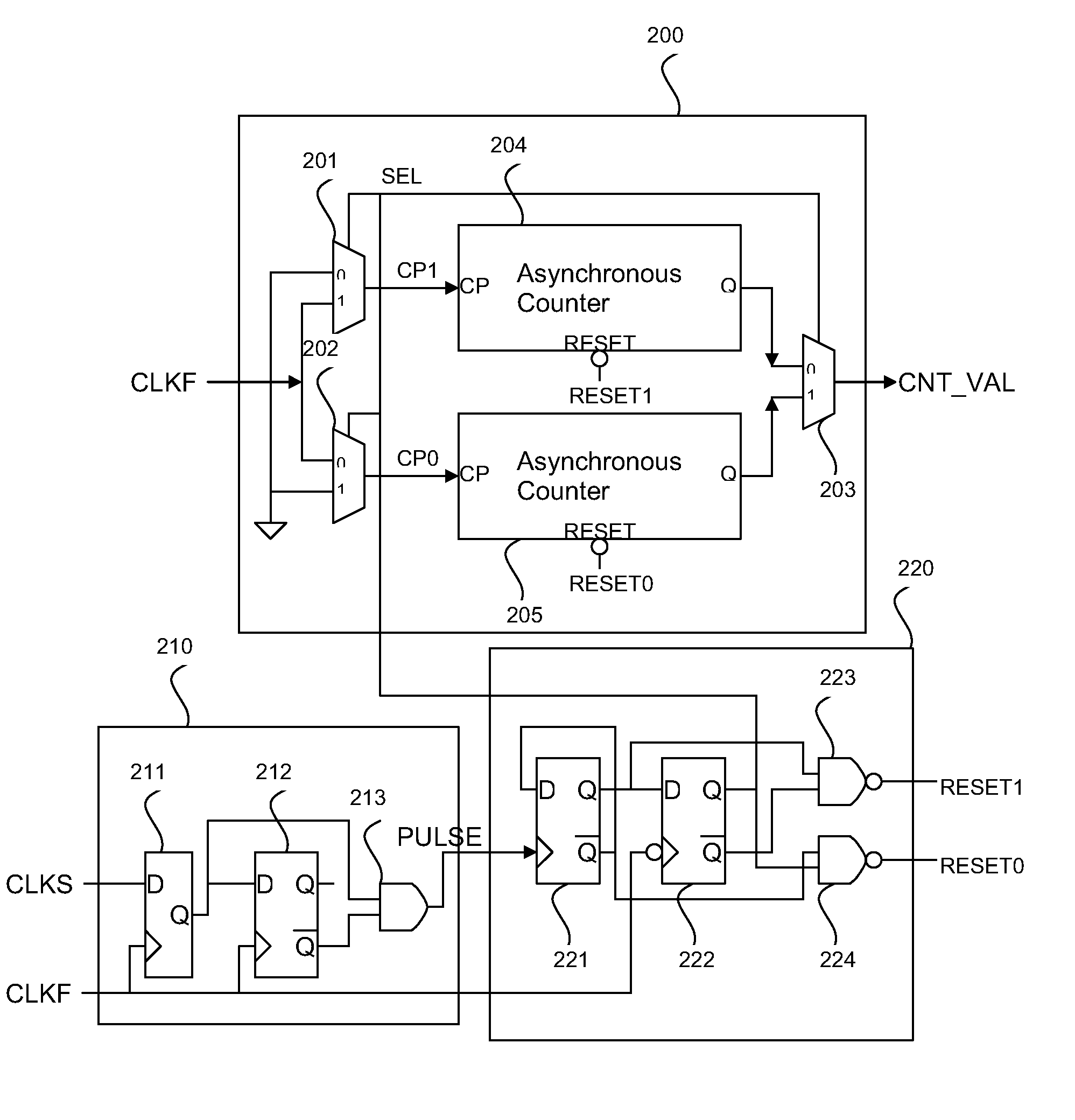

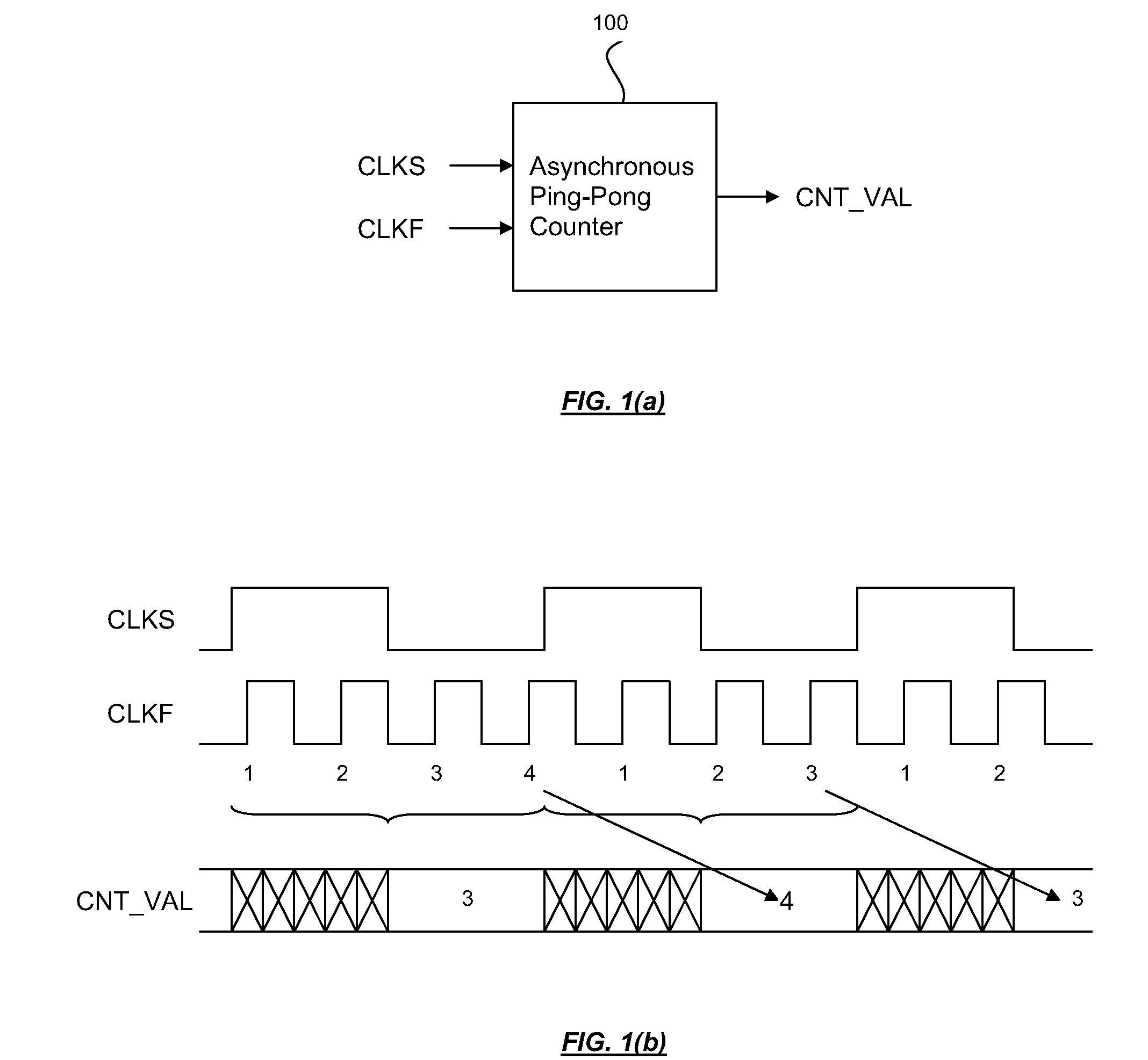

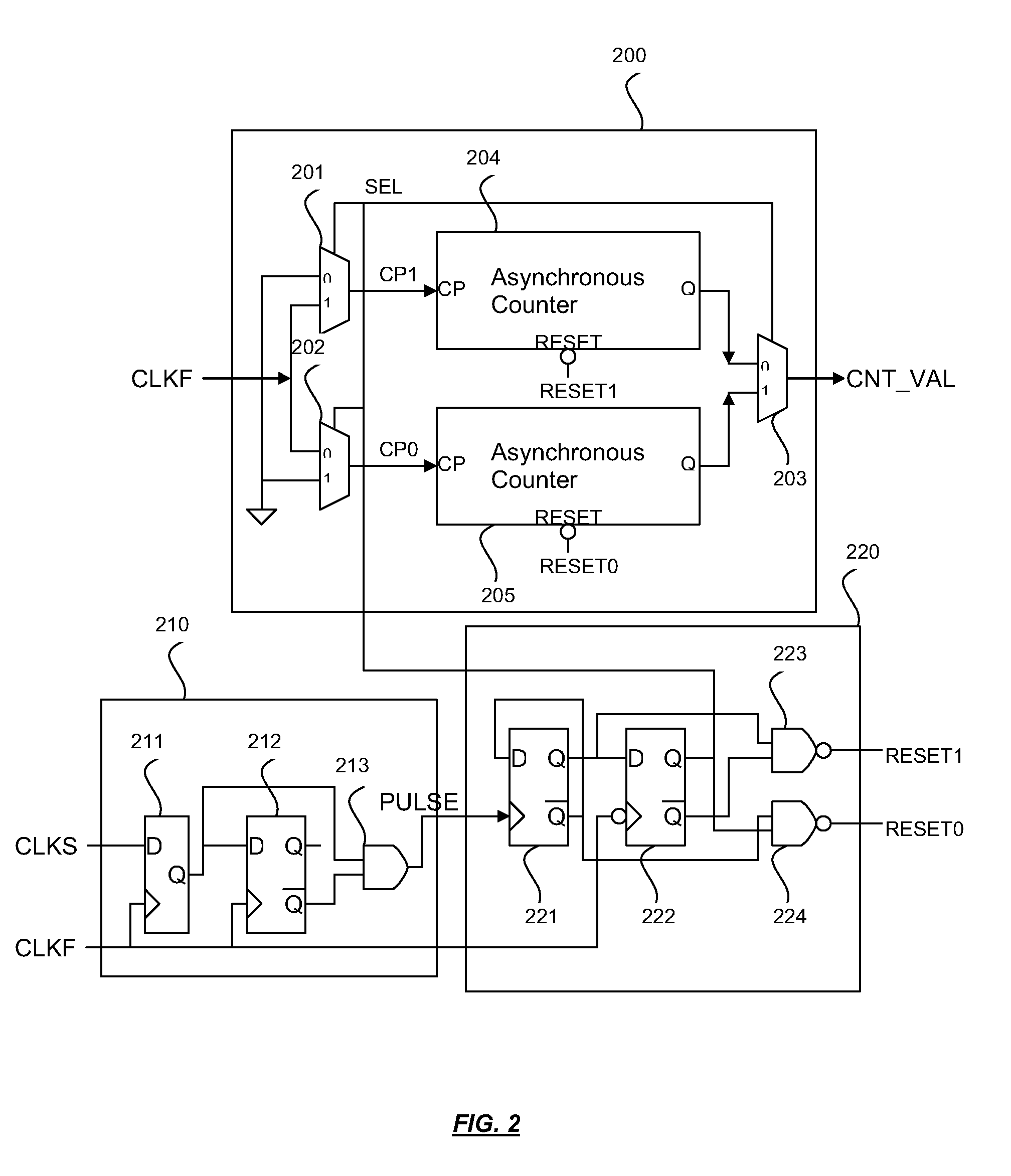

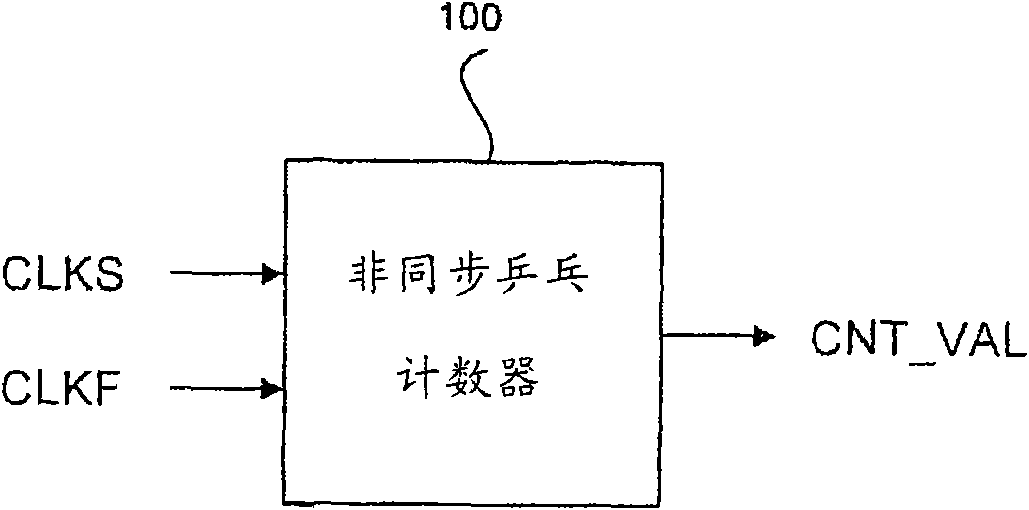

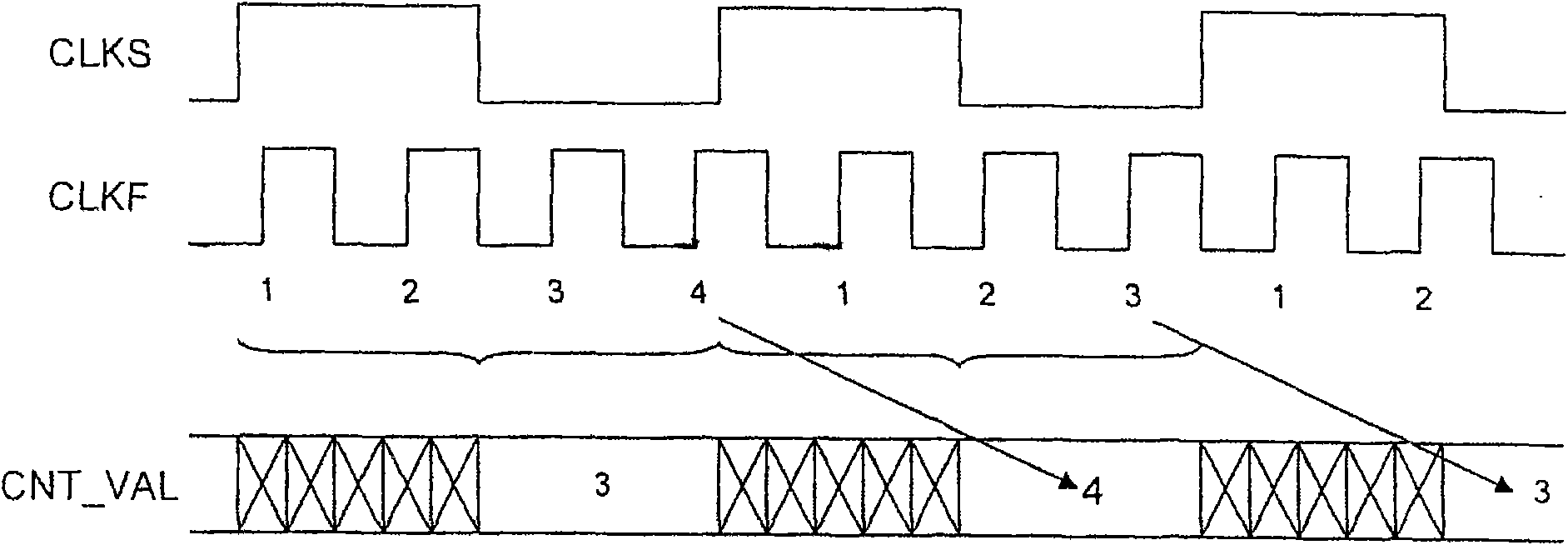

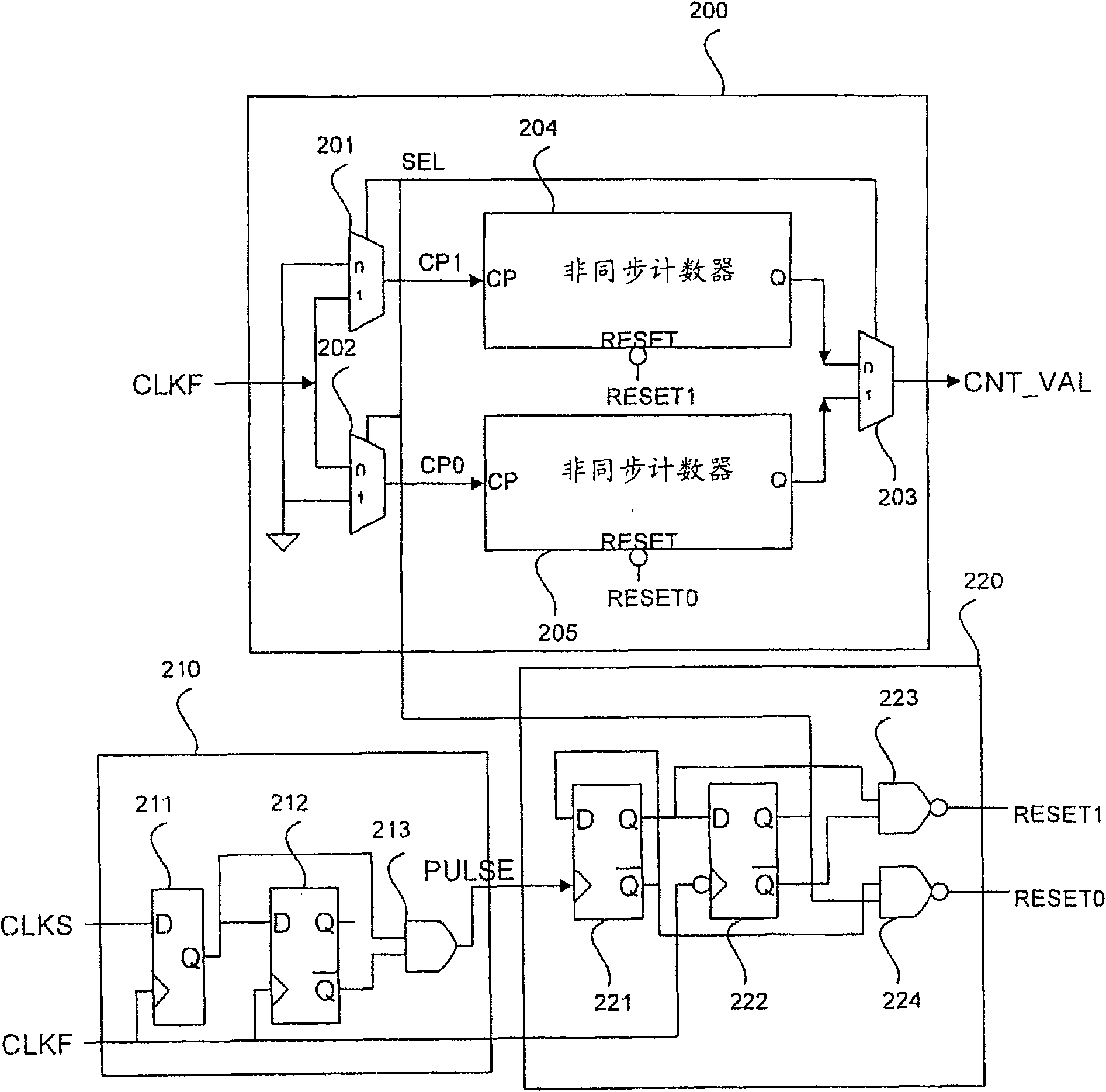

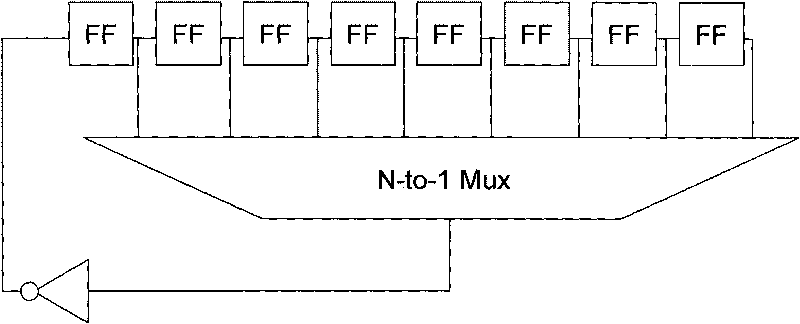

Asynchronous ping-pong counter and therof method

ActiveUS20090304140A1Counting chain synchronous pulse countersCounting chain asynchronous pulse countersPing pongClock signal

An asynchronous ping-pong counter is disclosed. The asynchronous ping-pong counter comprises a first asynchronous counter, a second synchronous counter, and a controller, the asynchronous ping-pong counter operates between a first state and a second state. In the first state, the first asynchronous counter counts a first number of clock edges of a fast clock signal, and the second asynchronous counter holds a first counter output value. In the second state, the second asynchronous counter counts a second number of clock edges of the fast clock signal, and the first asynchronous counter holds a second counter output value. The controller determines a state transition based on a sampling of a slow clock signal by the fast clock signal.

Owner:REALTEK SEMICON CORP

Frequency measurement device

ActiveUS8508213B2High detection sensitivityImprove dynamic rangeDigital variable displayCounting chain synchronous pulse countersFrequency measurementsLow-pass filter

Owner:SEIKO EPSON CORP

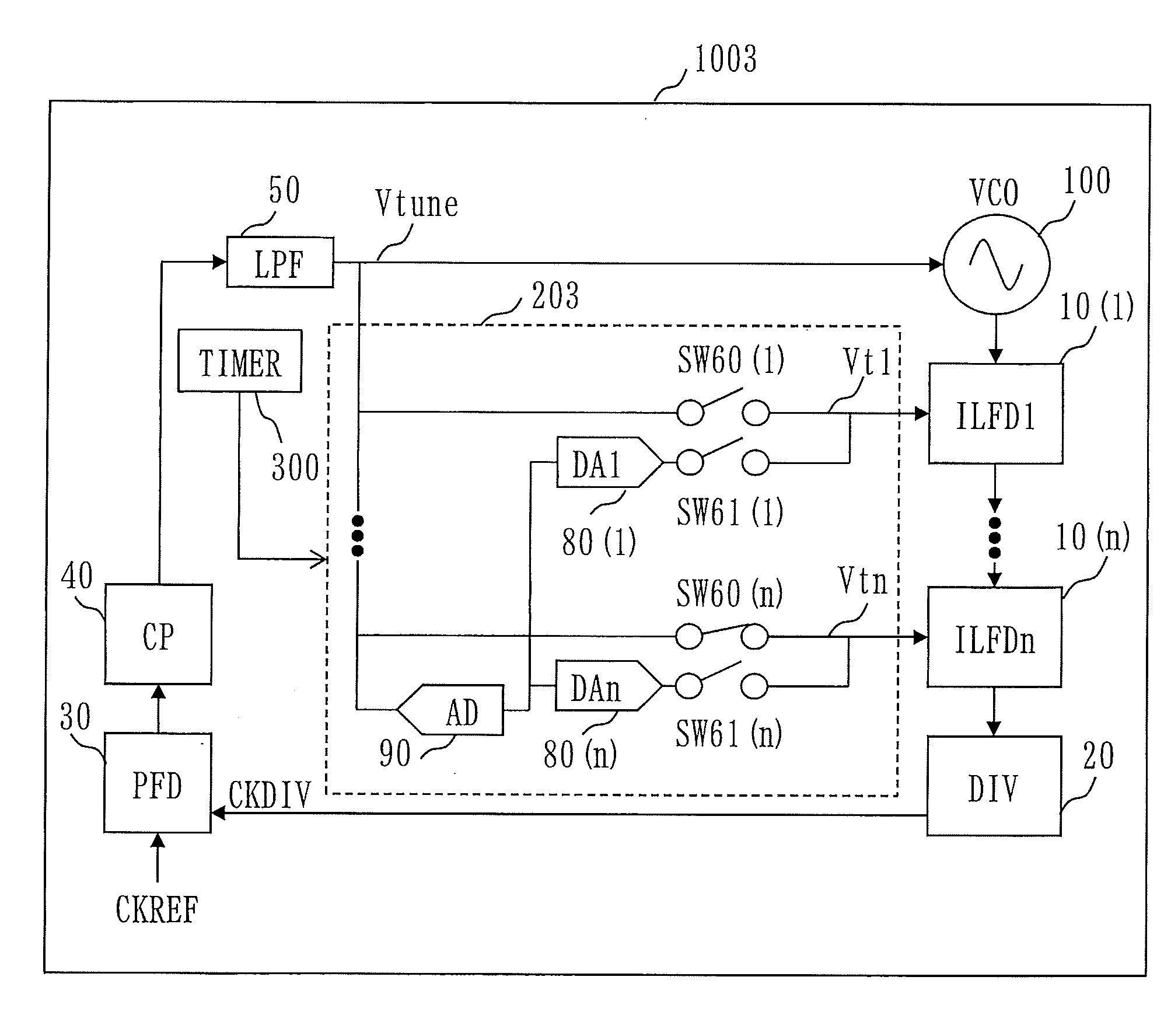

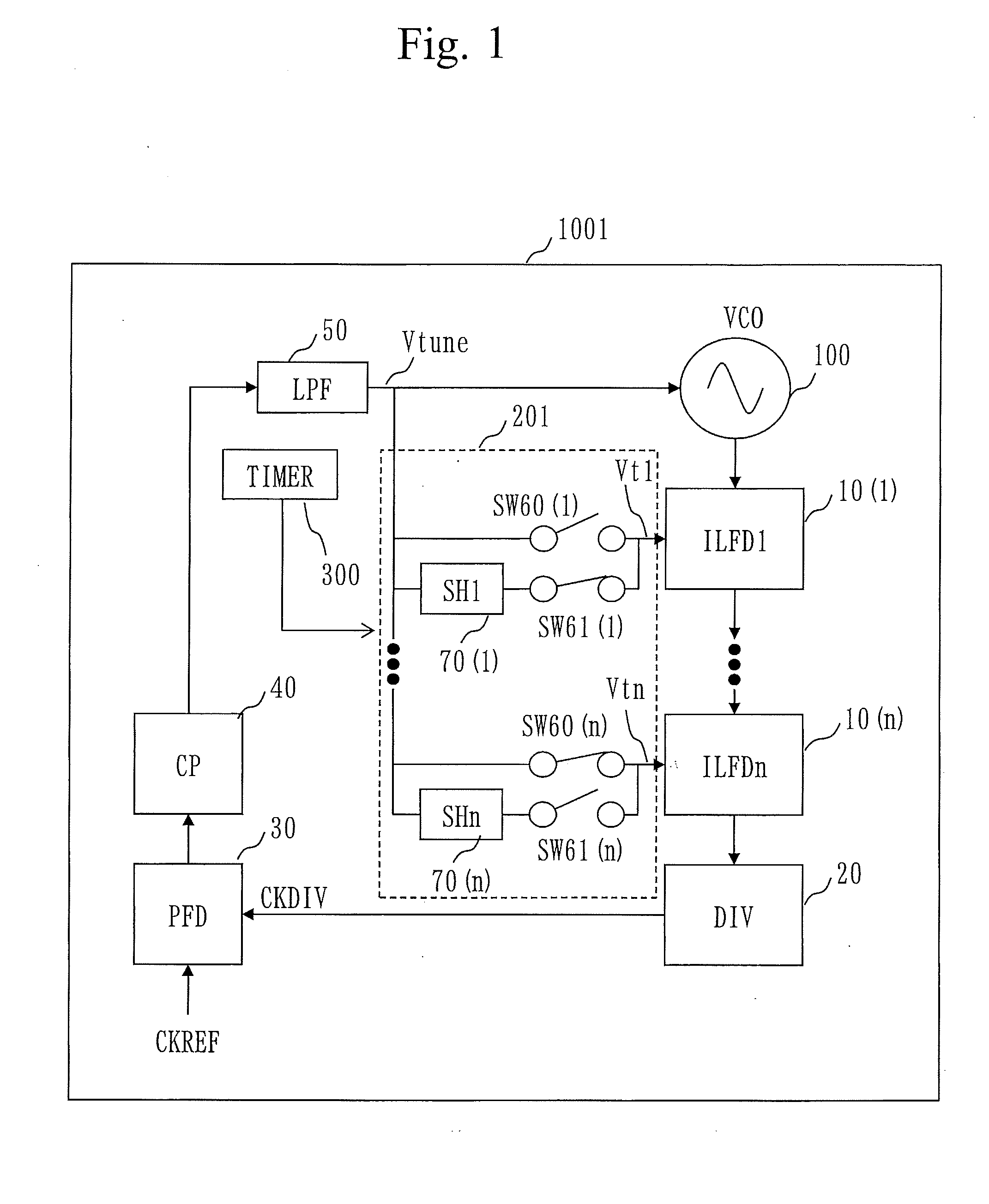

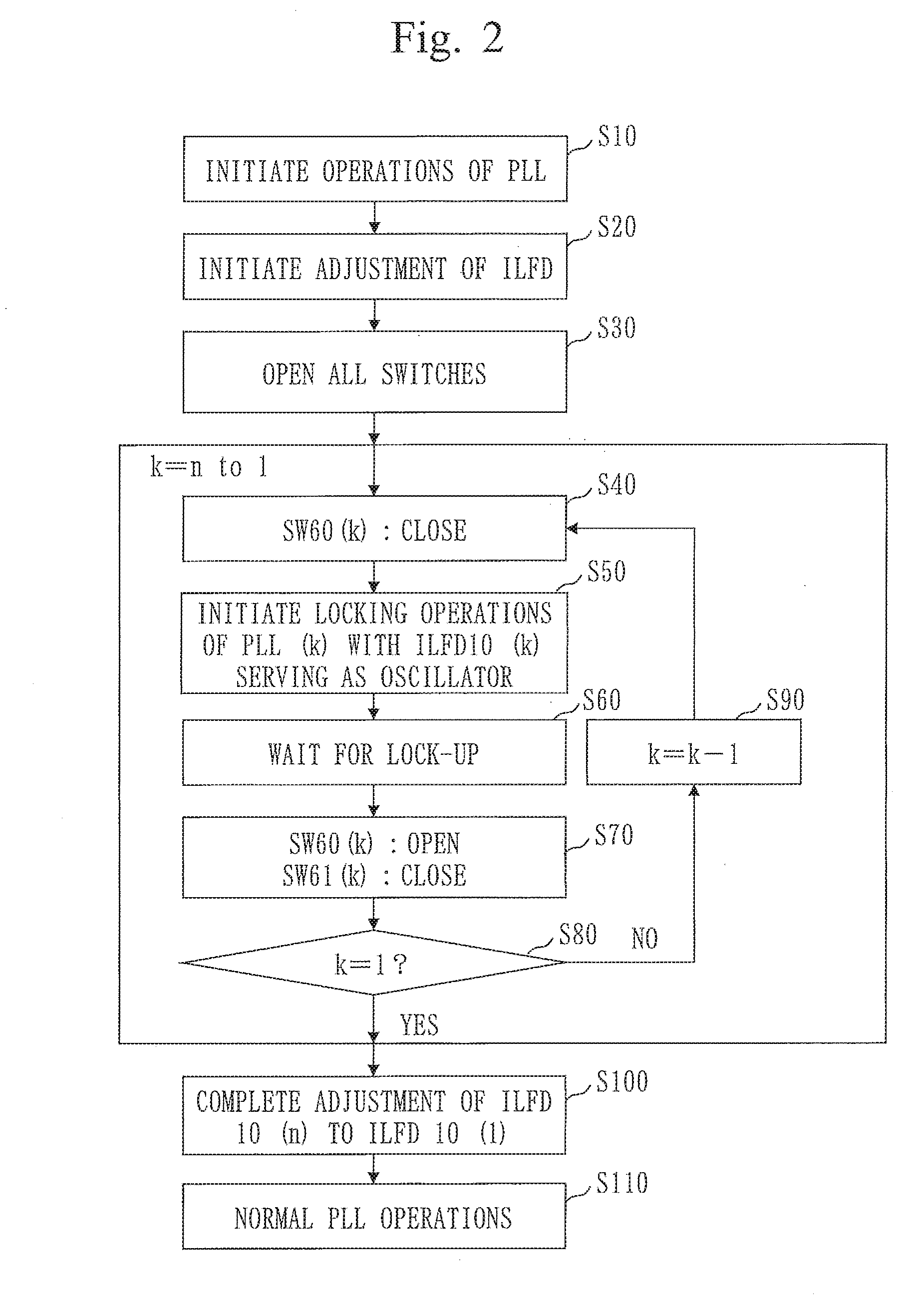

Phase locked loop circuit and method of frequency adjustment of injection locked frequency divider

InactiveUS20160336944A1Simple circuit configurationStable operation of frequencyPulse automatic controlCounting chain asynchronous pulse countersInjection lockedLoop filter

In a PLL circuit, first an ILFD is connected to an output voltage Vtune from an LPF, thereby causing the ILFD to operate as an oscillator. The ILFD, a DIV, PFD, CP, and LPF form a PLL and thereby locking operations are initiated. When a predetermined time elapses, an output frequency from the ILFD converges into a certain value and the PLL is subjected to a locked state. After the locked state is reached, a sample hold circuit SH holds the output voltage Vtune from the loop filter as of that time and frequency adjustment of the ILFD is completed. Similar frequency adjustment is sequentially performed on other ILFDs.

Owner:MITSUBISHI ELECTRIC CORP

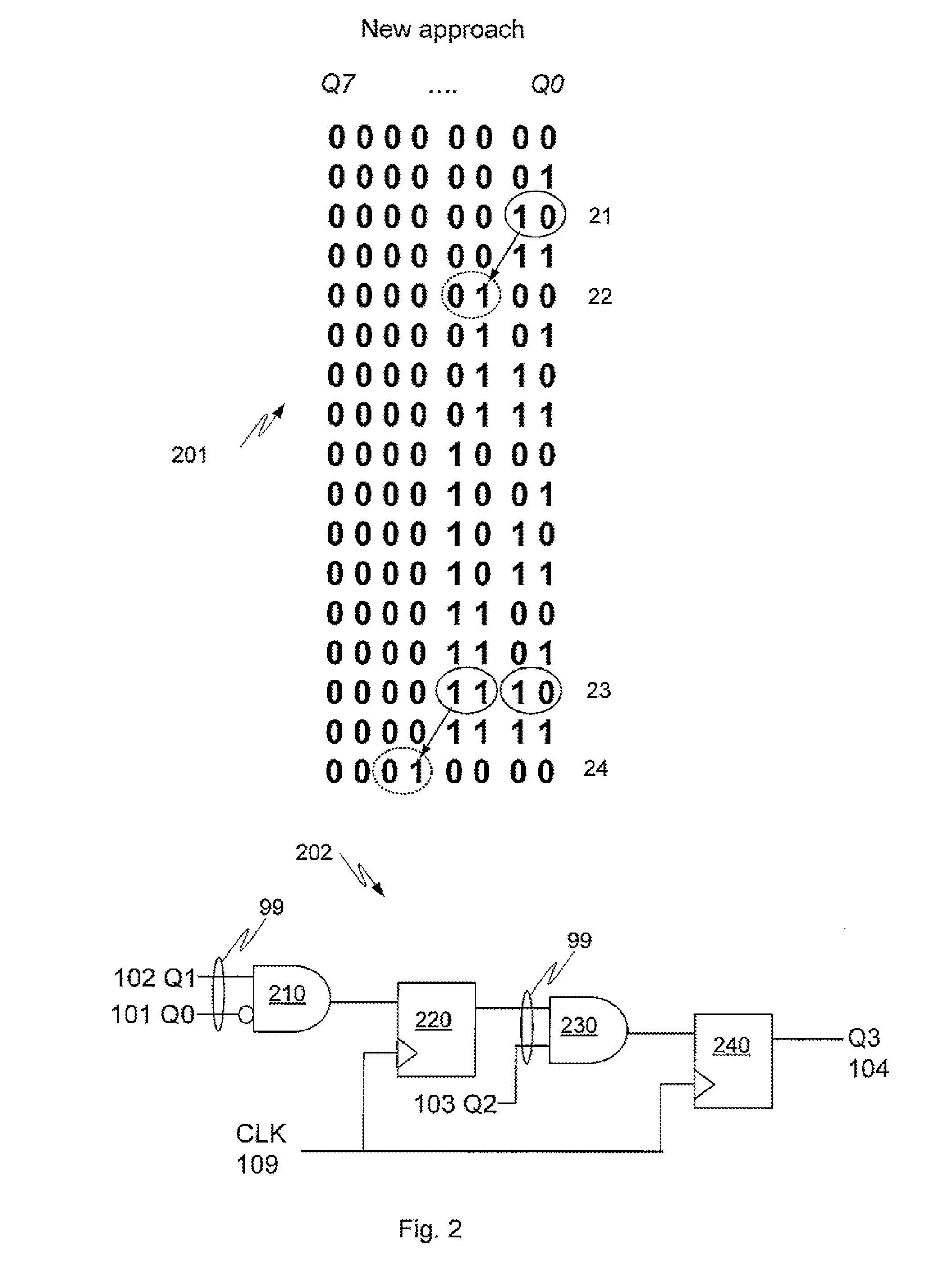

Digital self-gated binary counter

ActiveUS20150010124A1Counting chain synchronous pulse countersCounting chain asynchronous pulse countersLogical combinationComputer module

An n-bit counter is formed from cascading counter sub-modules. The counter includes combinatorial control logic coupled to a lower order counter sub-module. The control logic is arranged to clock gate at least one higher order counter sub-module dependent on a logical combination of outputs of the lower order counter sub-module and where the control logic uses pipelining to store at least one previous control logic output for use in determining a later control logic output.

Owner:NXP USA INC

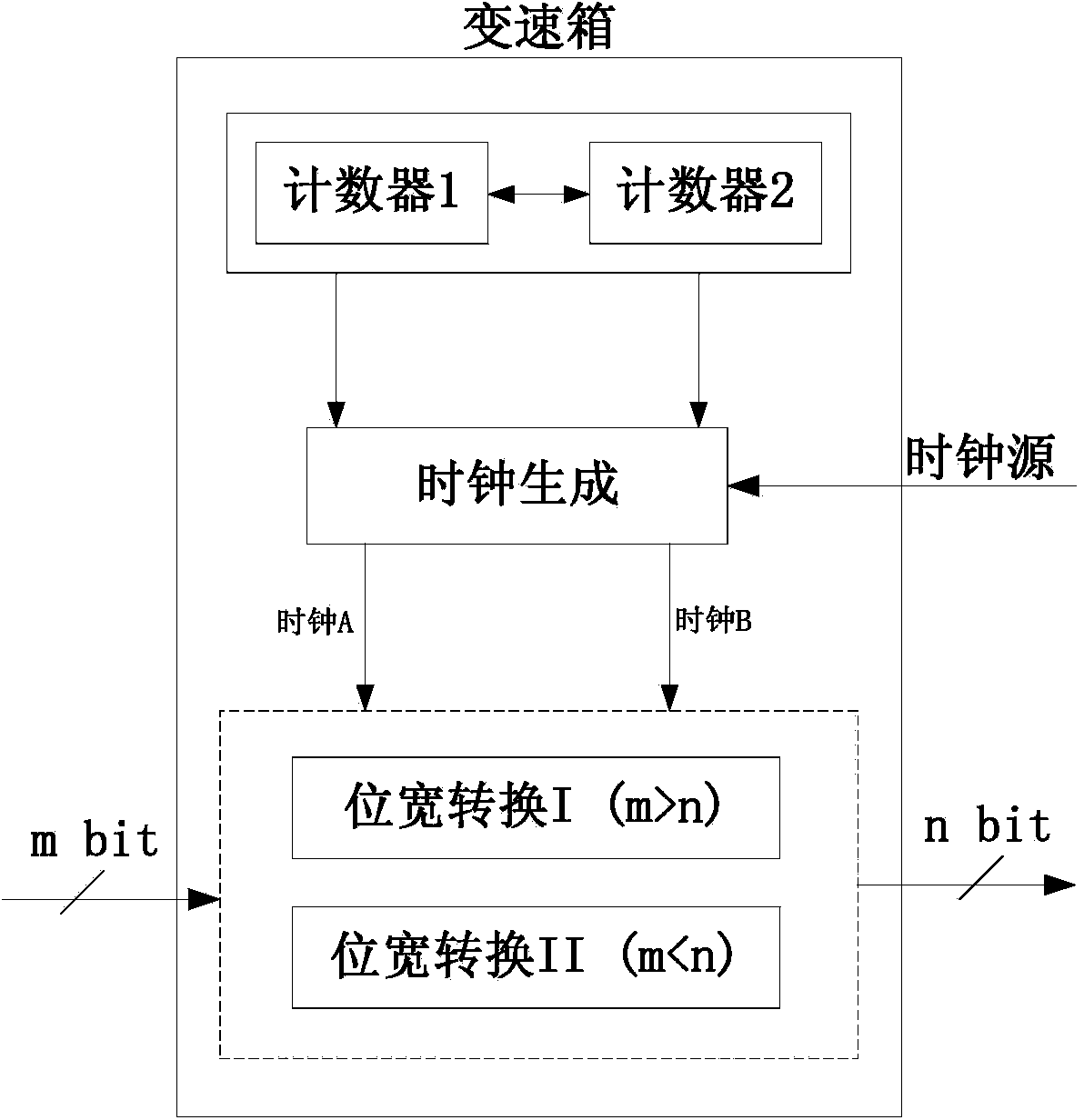

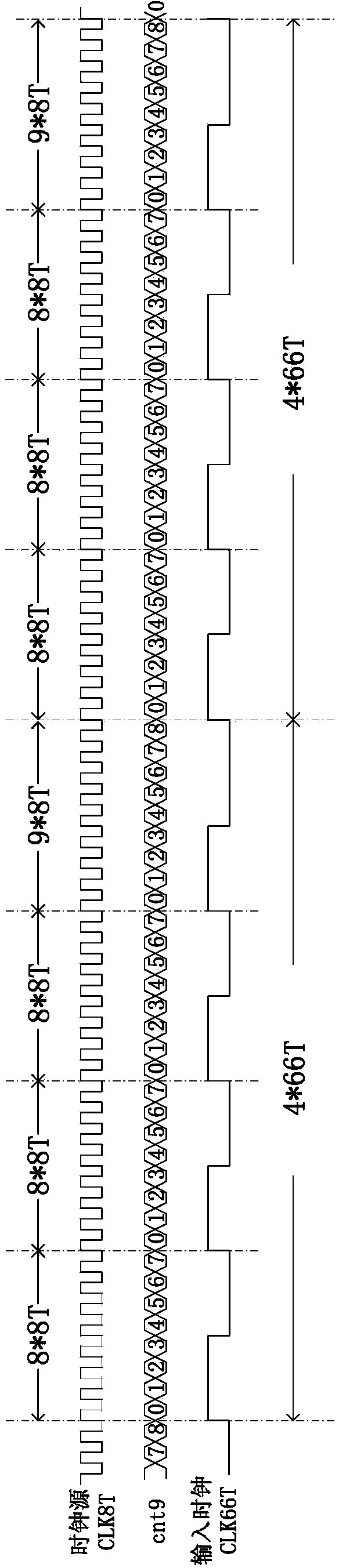

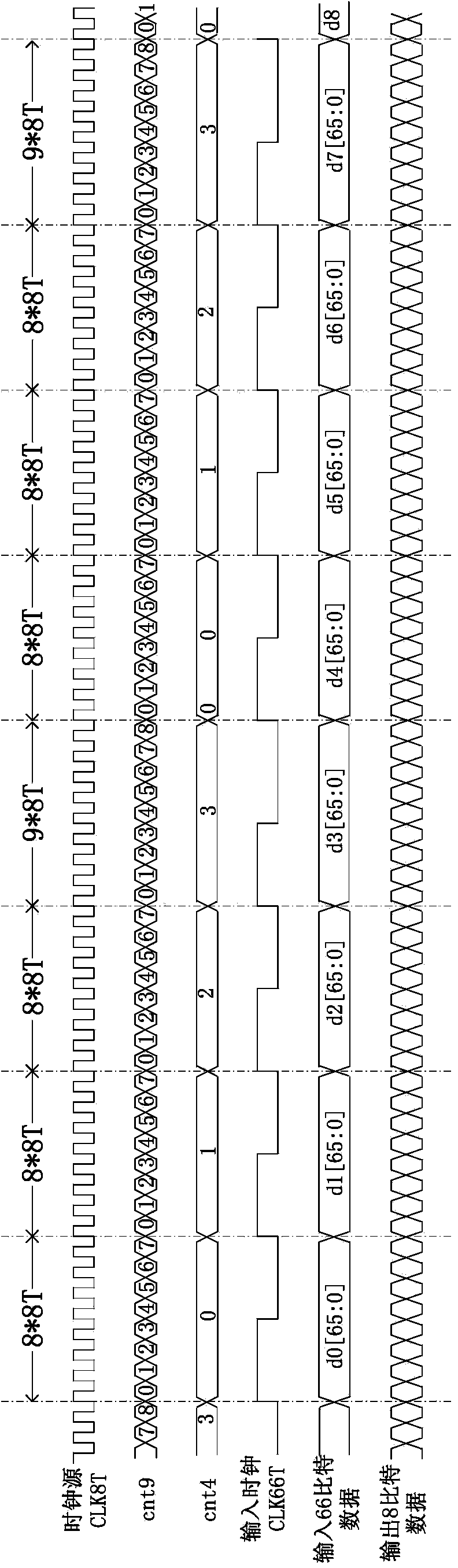

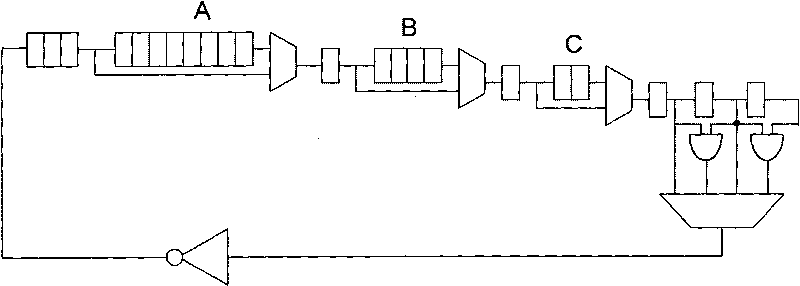

Gearbox circuit for changing data bit widths in high-speed transceiver and working method thereof

ActiveCN103780250ANo reduction in data transfer efficiencyCounting chain asynchronous pulse countersData bitsData transmission

The invention relates to a gearbox circuit for changing data bit widths in a high-speed transceiver and a working method of the gearbox circuit. Conversion between different data bit widths is controlled by controlling generation of a clock used for data input and a clock used for data output and the phase relation between the two clocks, and then data bit width matching between internal modules is achieved. The gearbox circuit comprises a counter generation circuit, a clock generation circuit, a first data width conversion circuit and a second data width conversion circuit. The output of the counter generation circuit is connected with the clock generation circuit, the input of the clock generation circuit is connected with a clock source, and the output of the clock generation circuit is connected with the first data width conversion circuit and the second data width conversion circuit. The gearbox circuit and the working method have the advantages that under the conditions that the data transmission bit rate is not affected, and data transmission efficiency is not reduced, conversion of the data bit widths can be conducted at will, and the gearbox circuit and the working method are suitable for the design method and the circuit in the gearbox circuit field with any chip design.

Owner:58TH RES INST OF CETC

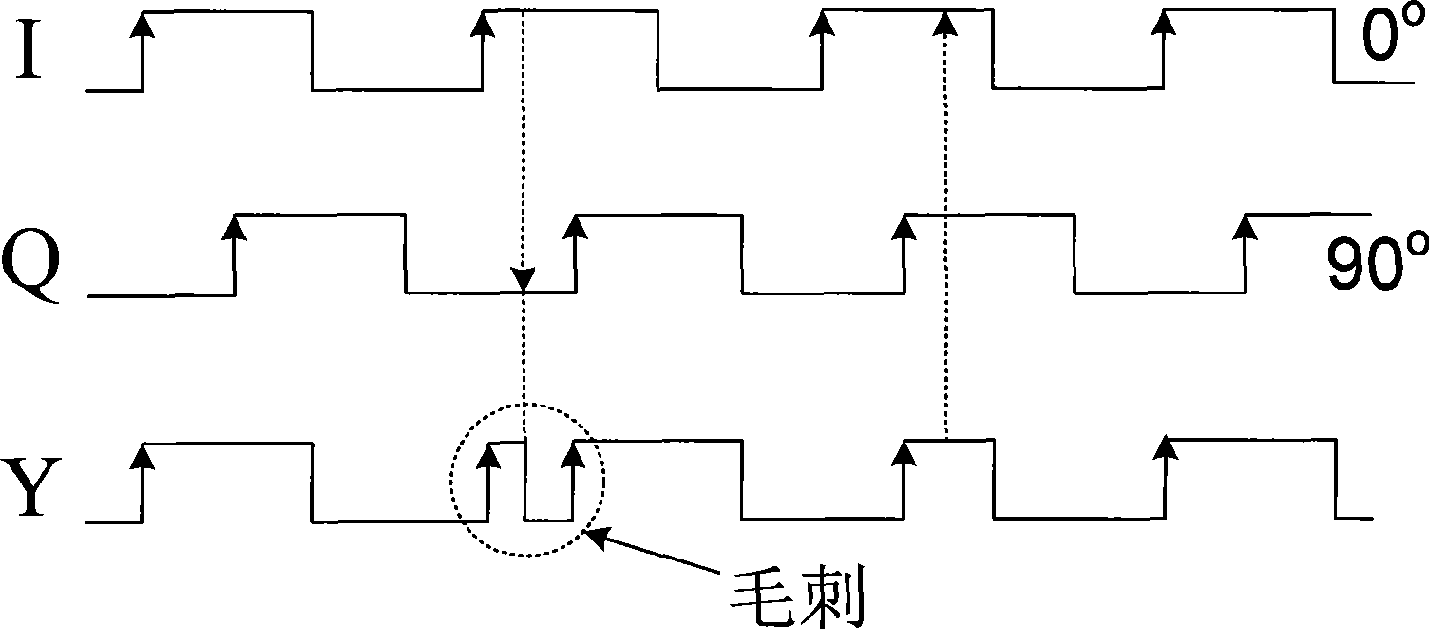

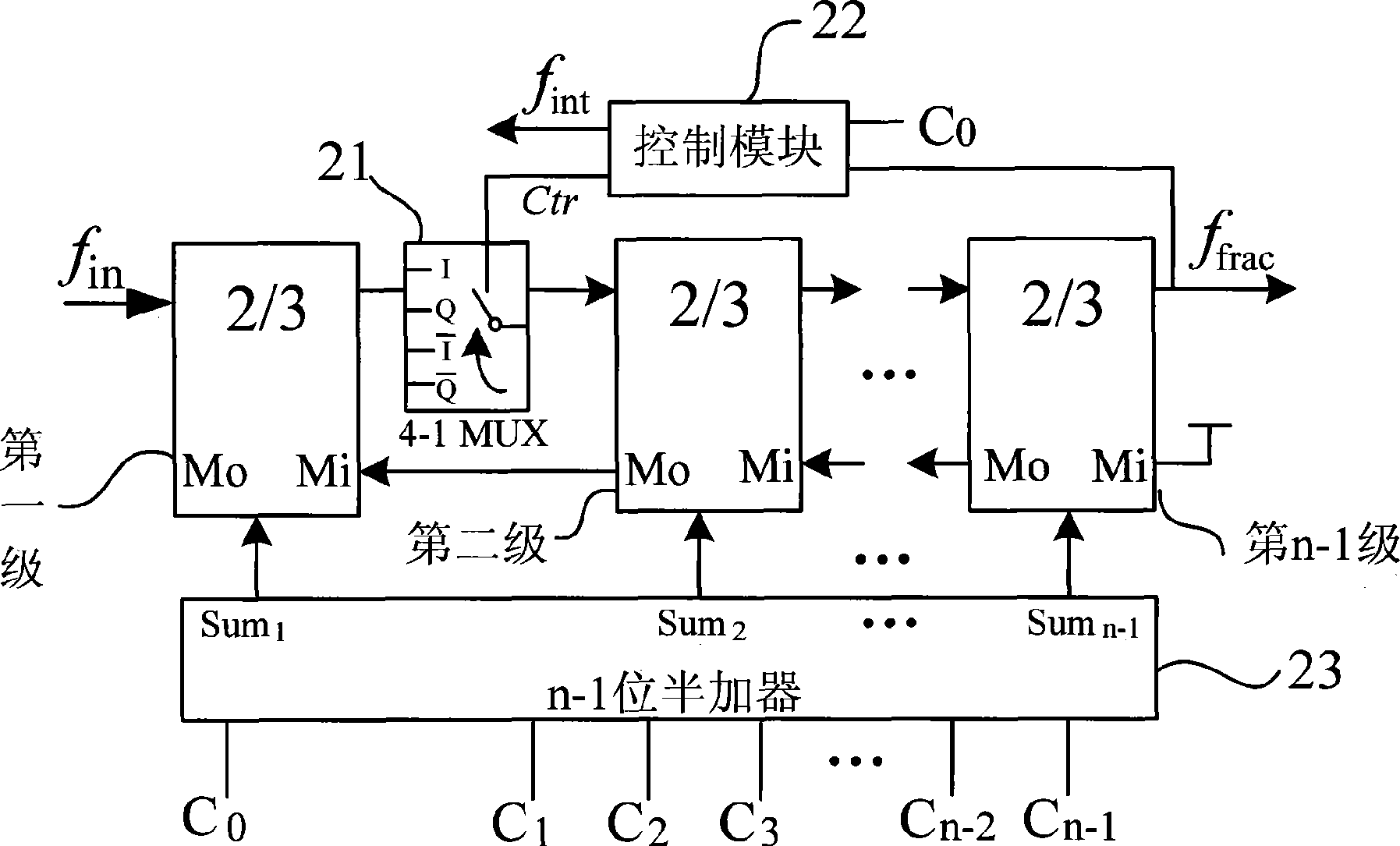

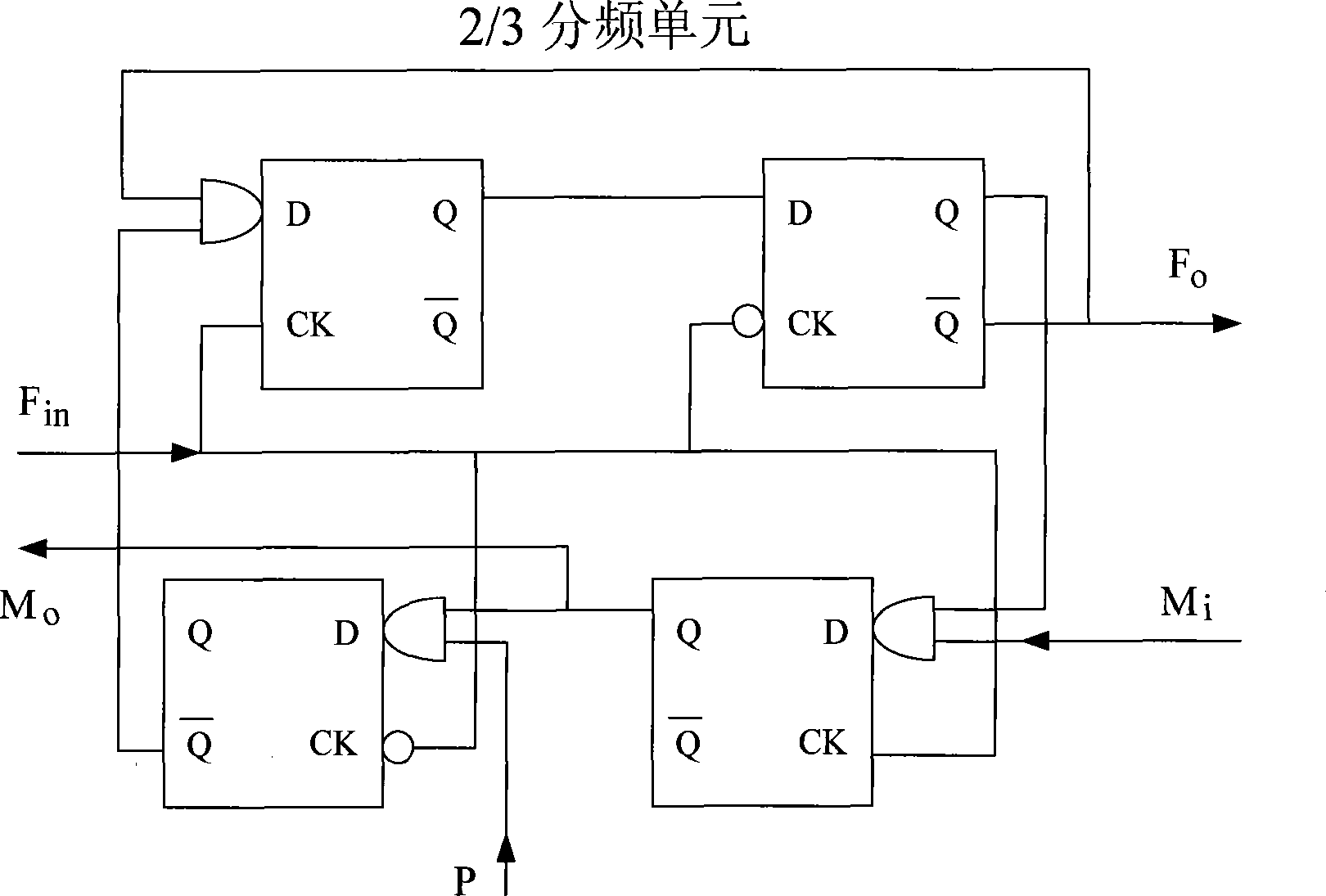

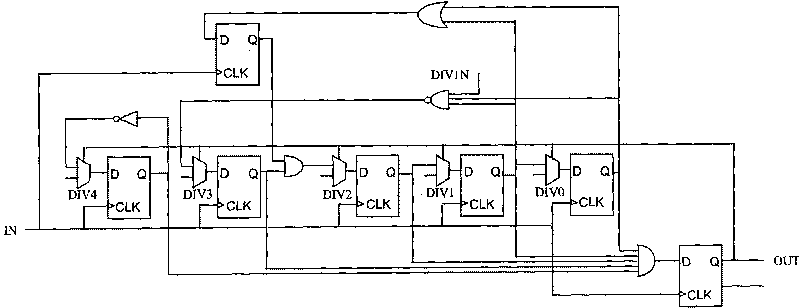

Multi-mode programmable frequency divider with 0.5 frequency division step

InactiveCN101483429AReduce power consumptionSimple structureCounting chain asynchronous pulse countersLength frequencyMode control

The present invention discloses a multi- module programmable frequency demultiplier as 0.5 frequency demultiplication step length which comprises 2 / 3 frequency demultiplier unit, multiplex selector and a controller that cascade mutually; a half-adder of n-1 bit used to adjust frequency dividing ratio timely is also included; enable signal C0 of phase switch control module and 2 / 3 unit number setting signal constitute binary system frequency dividing ratio control bit together; output signal can be lead out from any 2 / 3 unit mode control signal output terminal. The fractional step length frequency demultiplier circuit structure of the invention is simple with no bur, increased power consumption is few and flexibility is strong.

Owner:SOUTHEAST UNIV

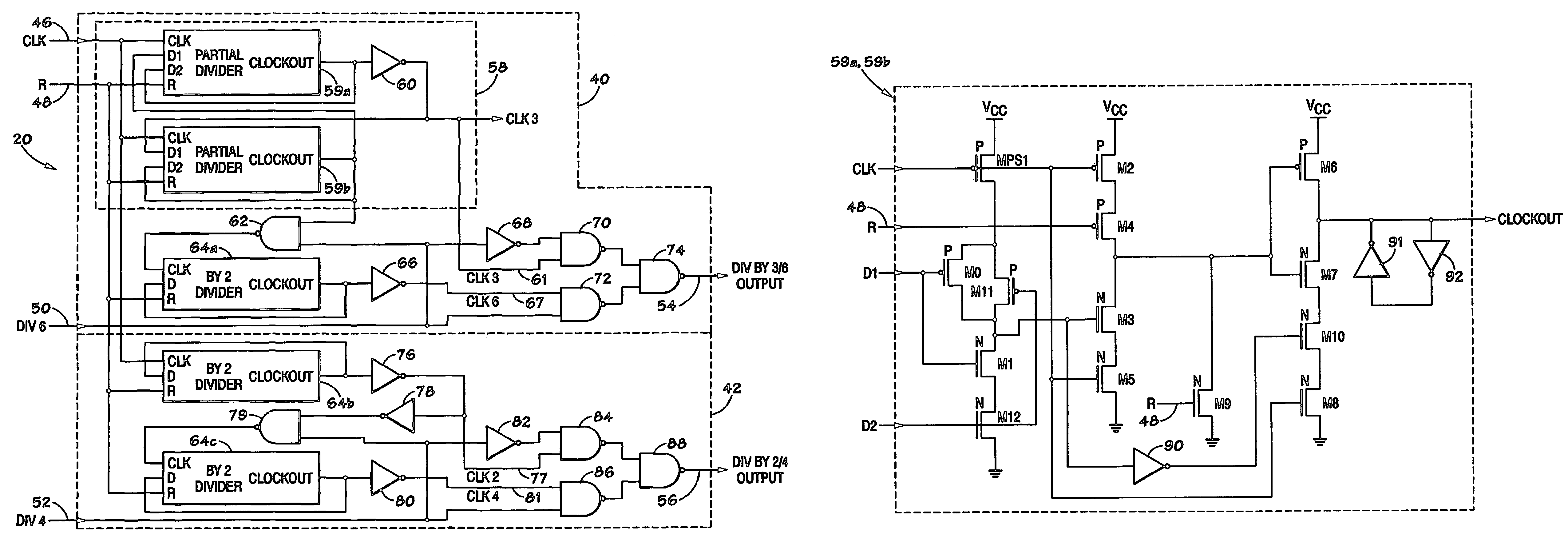

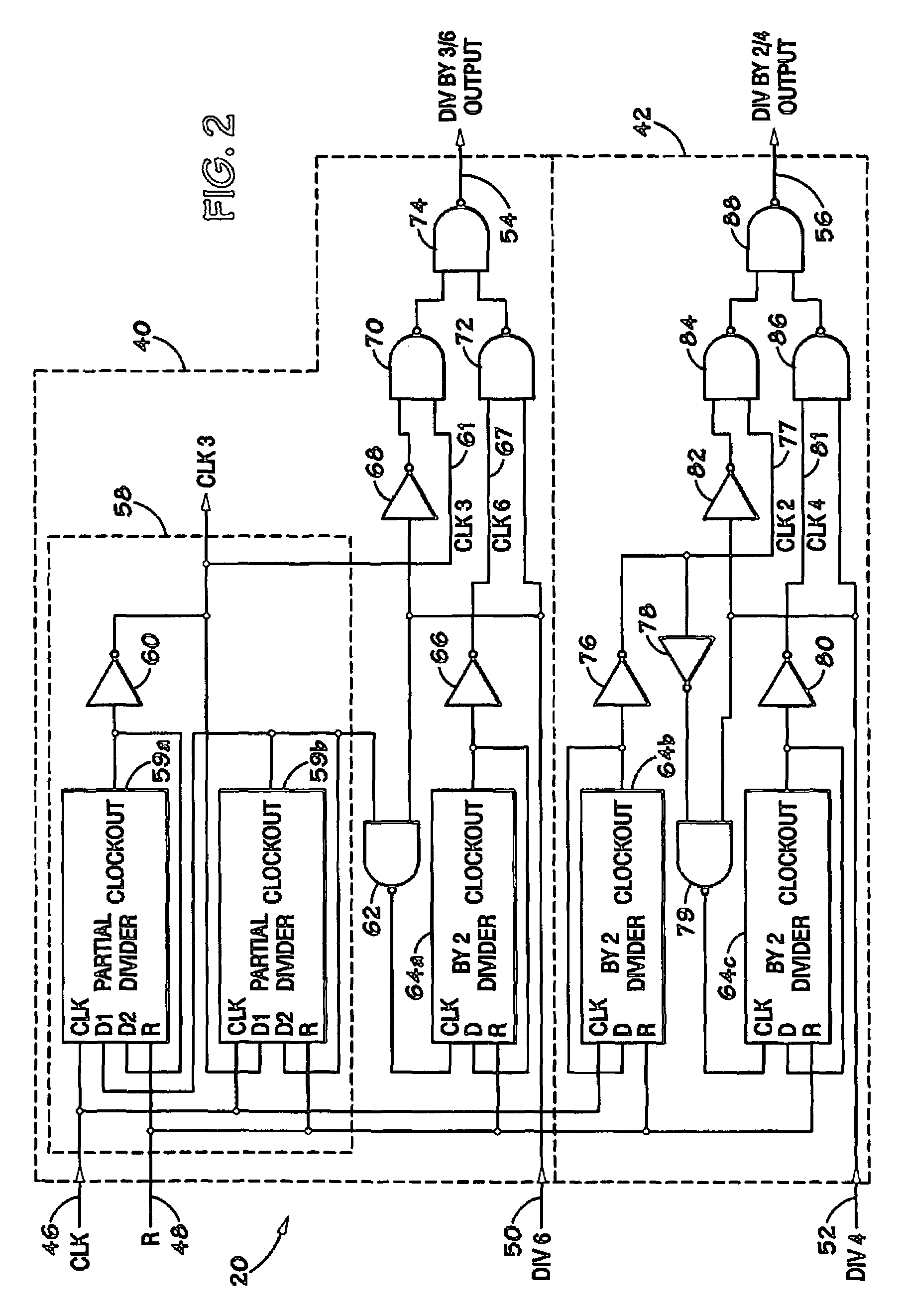

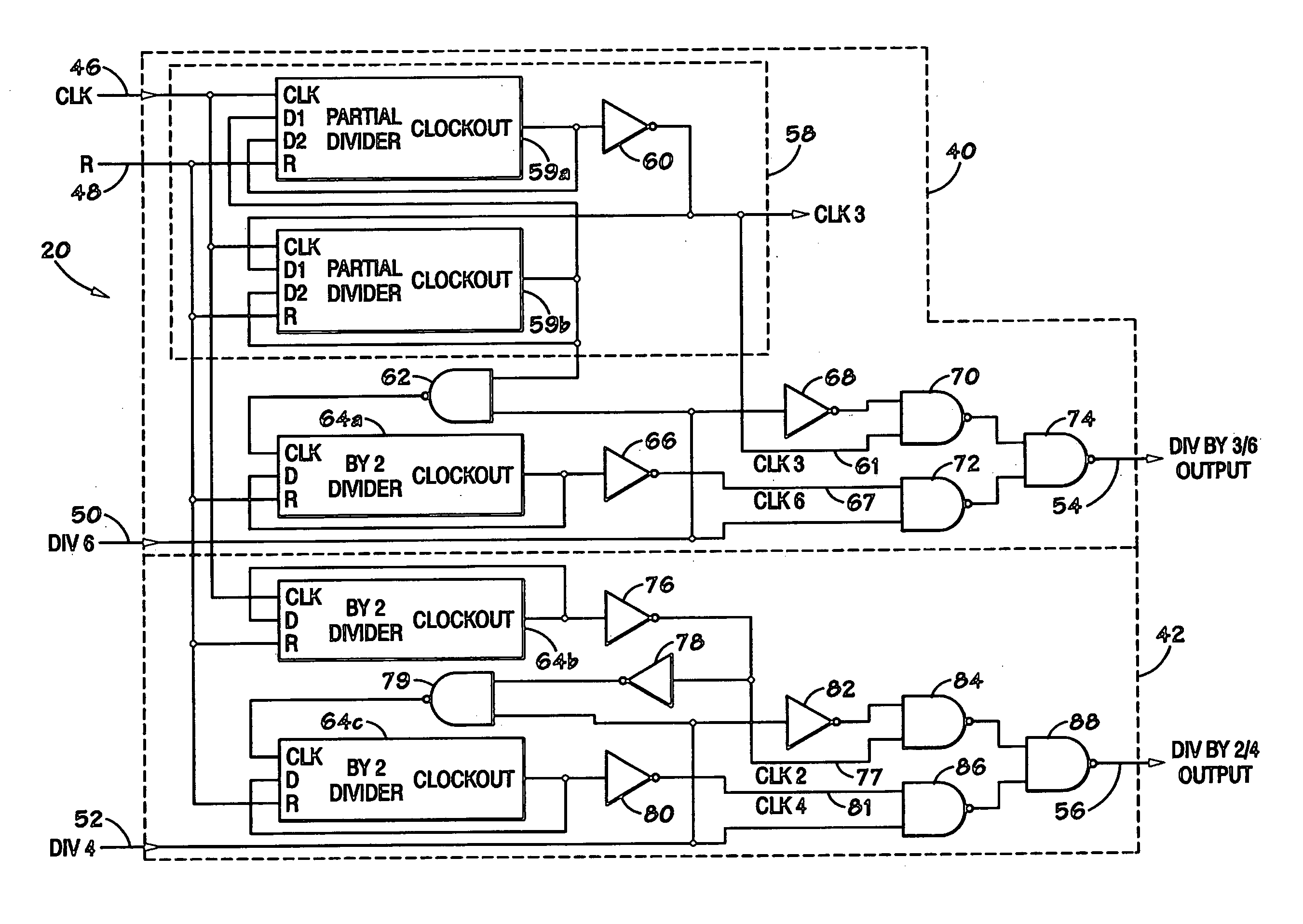

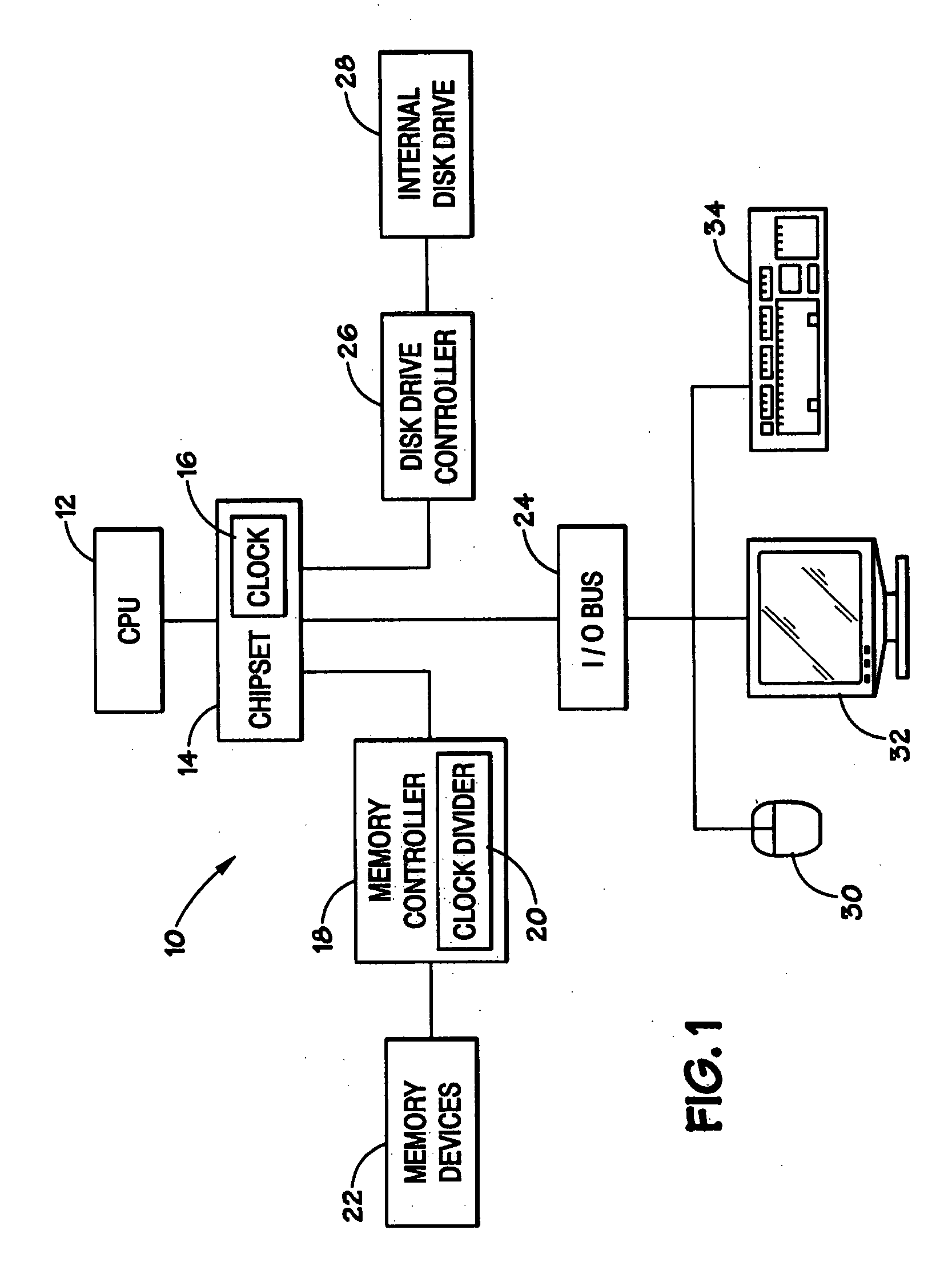

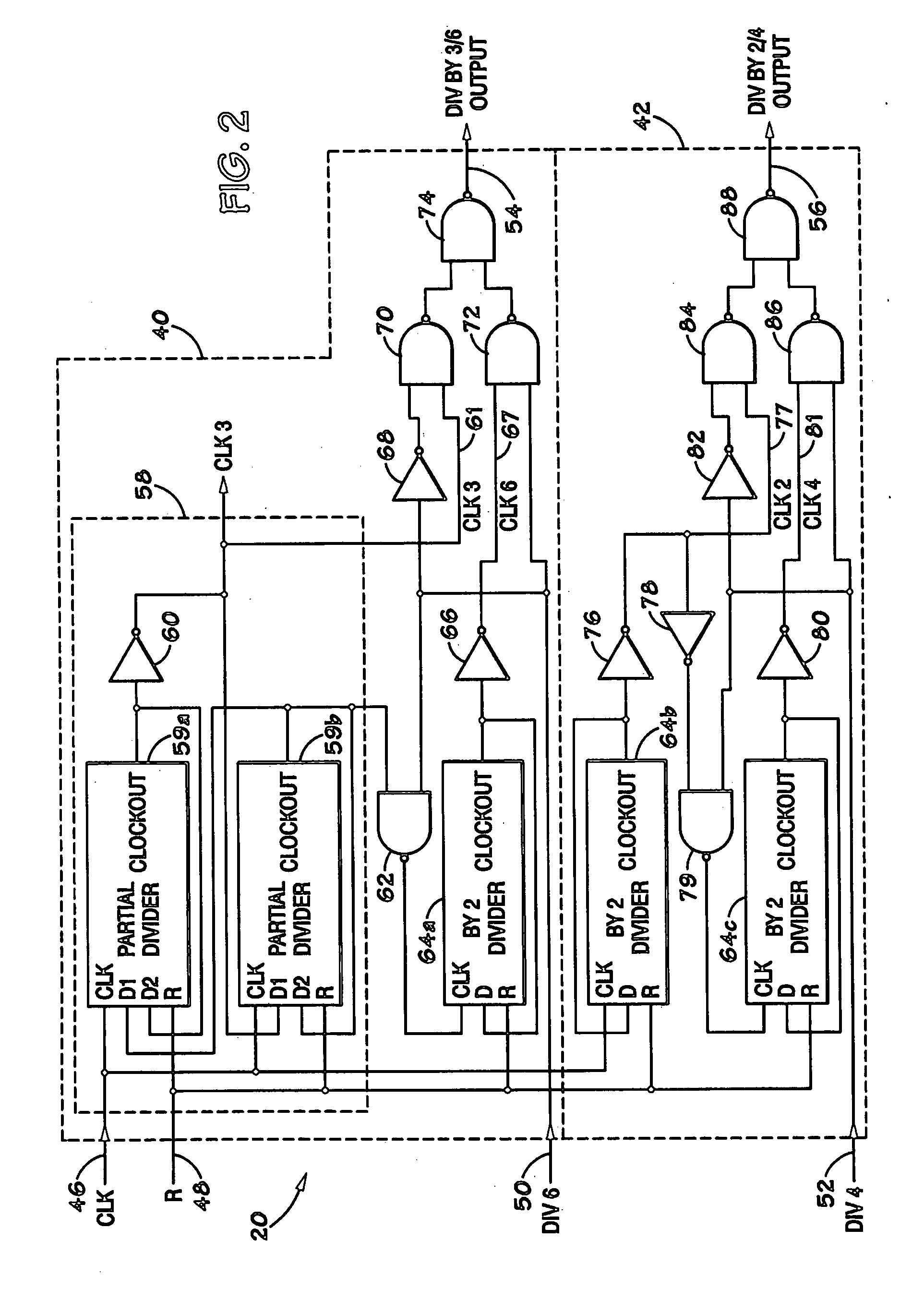

Methods and apparatus for dividing a clock signal

ActiveUS7538590B2Reliably dividedElectrothermal relaysCounting chain synchronous pulse countersLogic gateSingle phase

There is provided a true single phase logic clock divider that is configured to divide a clock signal by increments of two, three, four, or six. Because the true single phase logic clock divider is based on true single phase logic instead of static logic, the true single phase logic clock divider is able to reliably divide clock signals that could not reliably be divided by clock dividers based on static logic gates. There is also provided a method comprising receiving an input signal with a frequency between 2.5 gigahertz and 4 gigahertz and producing an output signal with a frequency approximately one-third of the frequency of the input signal.

Owner:MICRON TECH INC

Asynchronous ping-pong counter

An asynchronous ping-pong counter is disclosed. The asynchronous ping-pong counter comprises a first asynchronous counter, a second synchronous counter, and a controller, the asynchronous ping-pong counter operates between a first state and a second state. In the first state, the first asynchronous counter counts a first number of clock edges of a fast clock signal, and the second asynchronous counter holds a first counter output value. In the second state, the second asynchronous counter counts a second number of clock edges of the fast clock signal, and the first asynchronous counter holds a second counter output value. The controller determines a state transition based on a sampling of a slow clock signal by the fast clock signal.

Owner:REALTEK SEMICON CORP

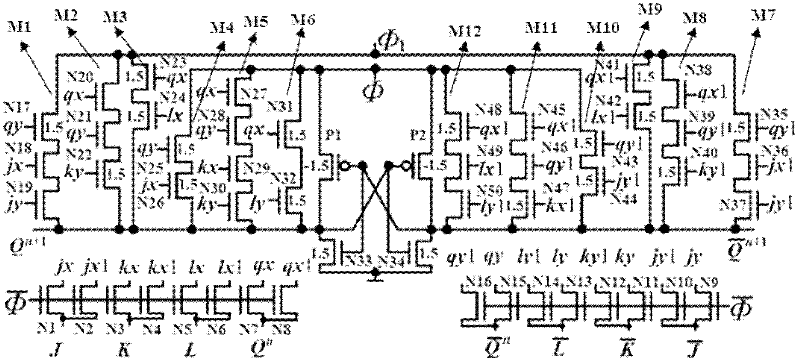

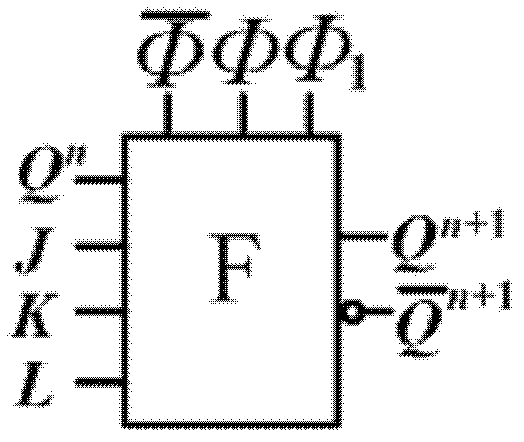

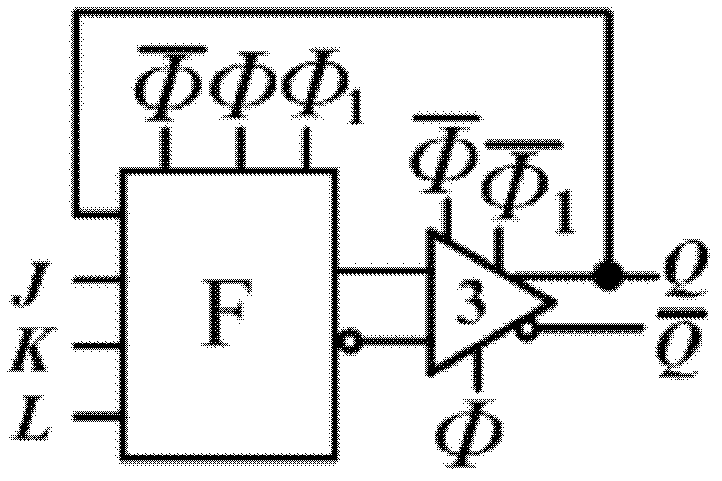

Ternary adiabatic JKL flip-flop and adiabatic novenary asynchronous counter

InactiveCN102394638AReduce power consumptionIncrease information densityCounting chain asynchronous pulse countersDelayed timeInformation density

The invention discloses a ternary adiabatic JKL flip-flop comprising a ternary adiabatic JKL fundamental circuit and a DTCTGAL buffer, wherein the signal input end of the ternary adiabatic JKL fundamental circuit is connected with the signal output end of the DTCTGAL buffer, the signal output end of the ternary adiabatic JKL fundamental circuit is connected with the signal input end of the DTCTGAL buffer; the complementary signal output end of the ternary adiabatic JKL fundamental circuit is connected with the complementary signal input end of the DTCTGAL buffer; both the ternary adiabatic JKL fundamental circuit and the DTCTGAL buffer are connected with a power clock signal of an amplitude level corresponding logic 1, a first clock pulse signal of an amplitude level corresponding logic 2 and a second clock pulse signal of the amplitude level corresponding logic 2; and the delay time of the DTCTGAL buffer is the same as that of the ternary adiabatic JKL fundamental circuit, and is half a clock period. The ternary adiabatic JKL flip-flop disclosed by the invention has the advantages that the circuit has very low power consumption, ternary input and output of the adiabatic circuit are realized while an energy recovery characteristic is provided, and the circuit has a higher information density and high operational reliability.

Owner:HANGZHOU MAEN TECH

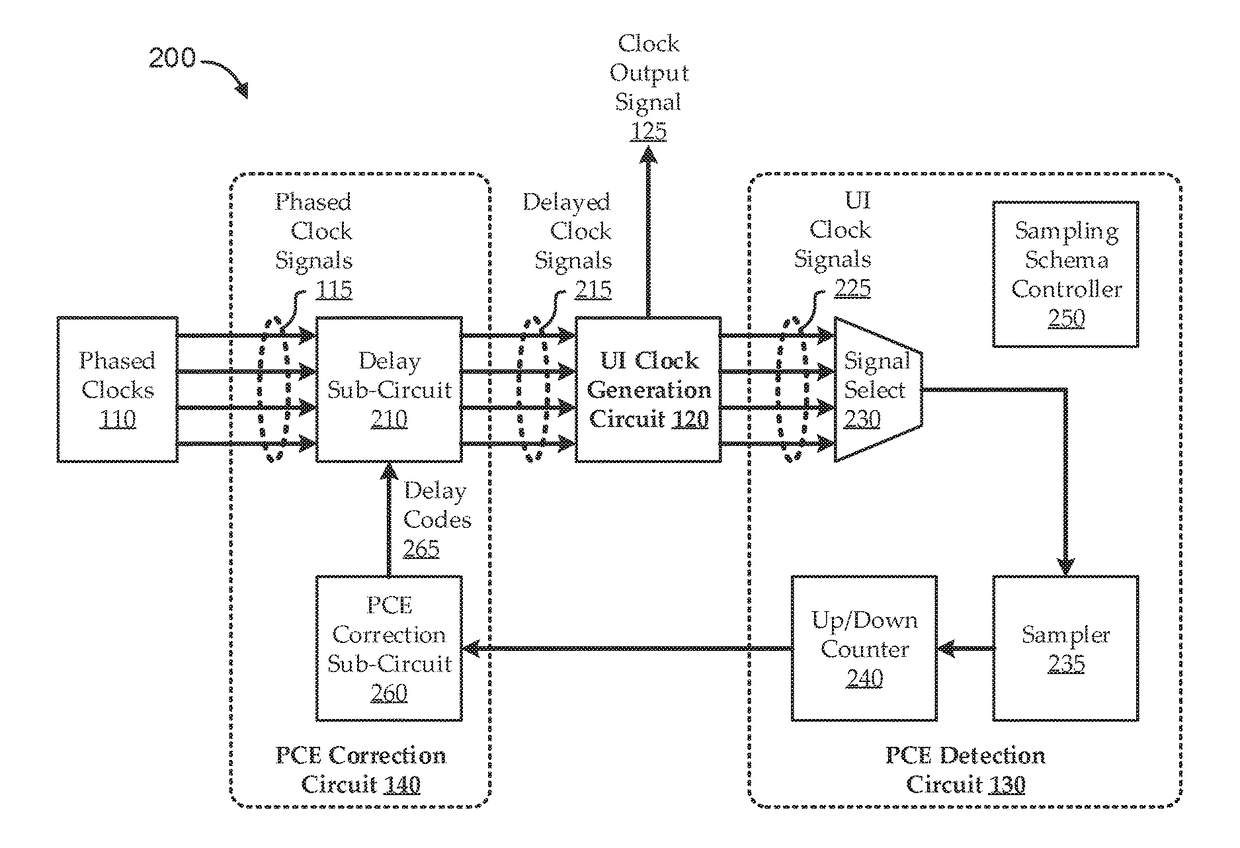

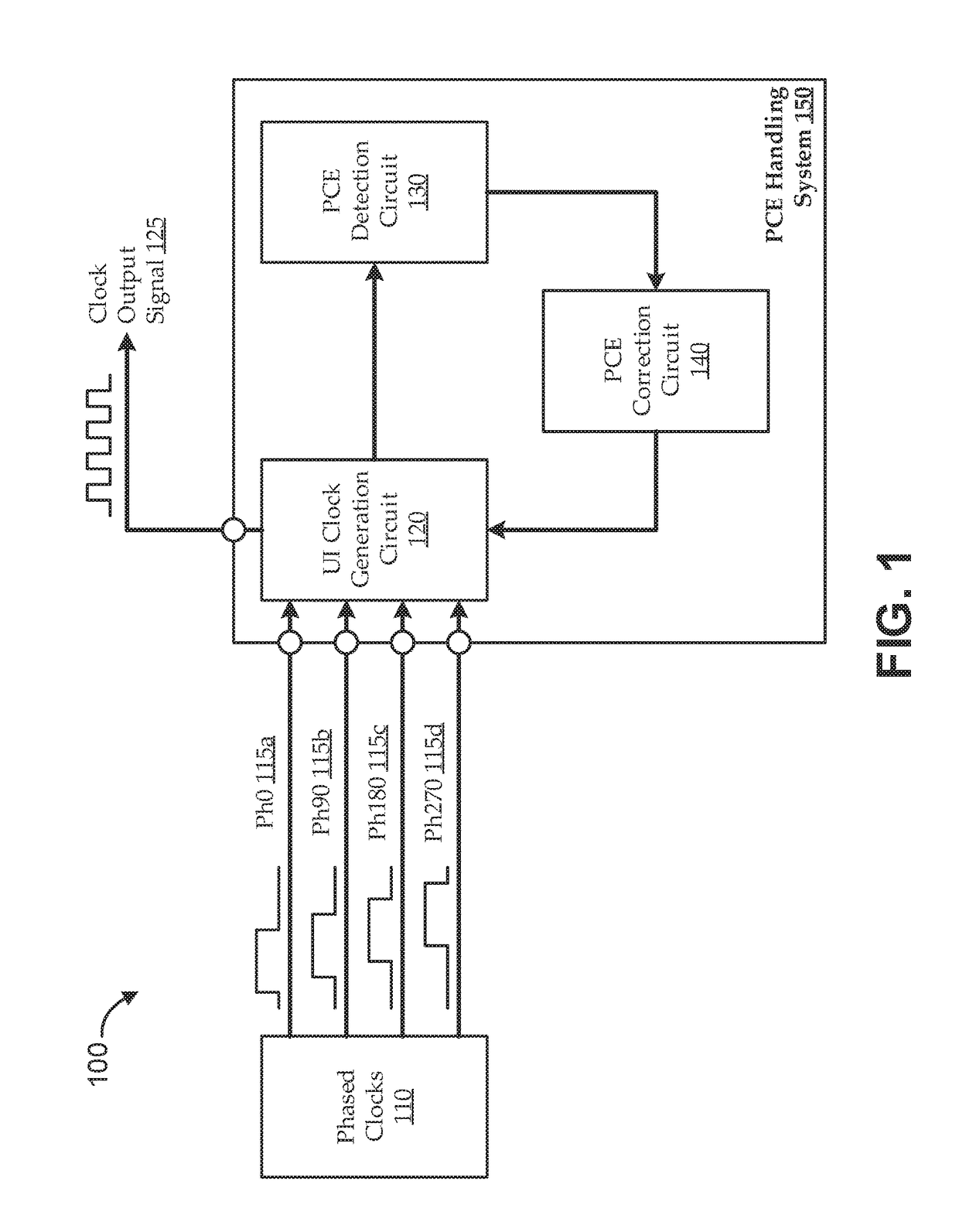

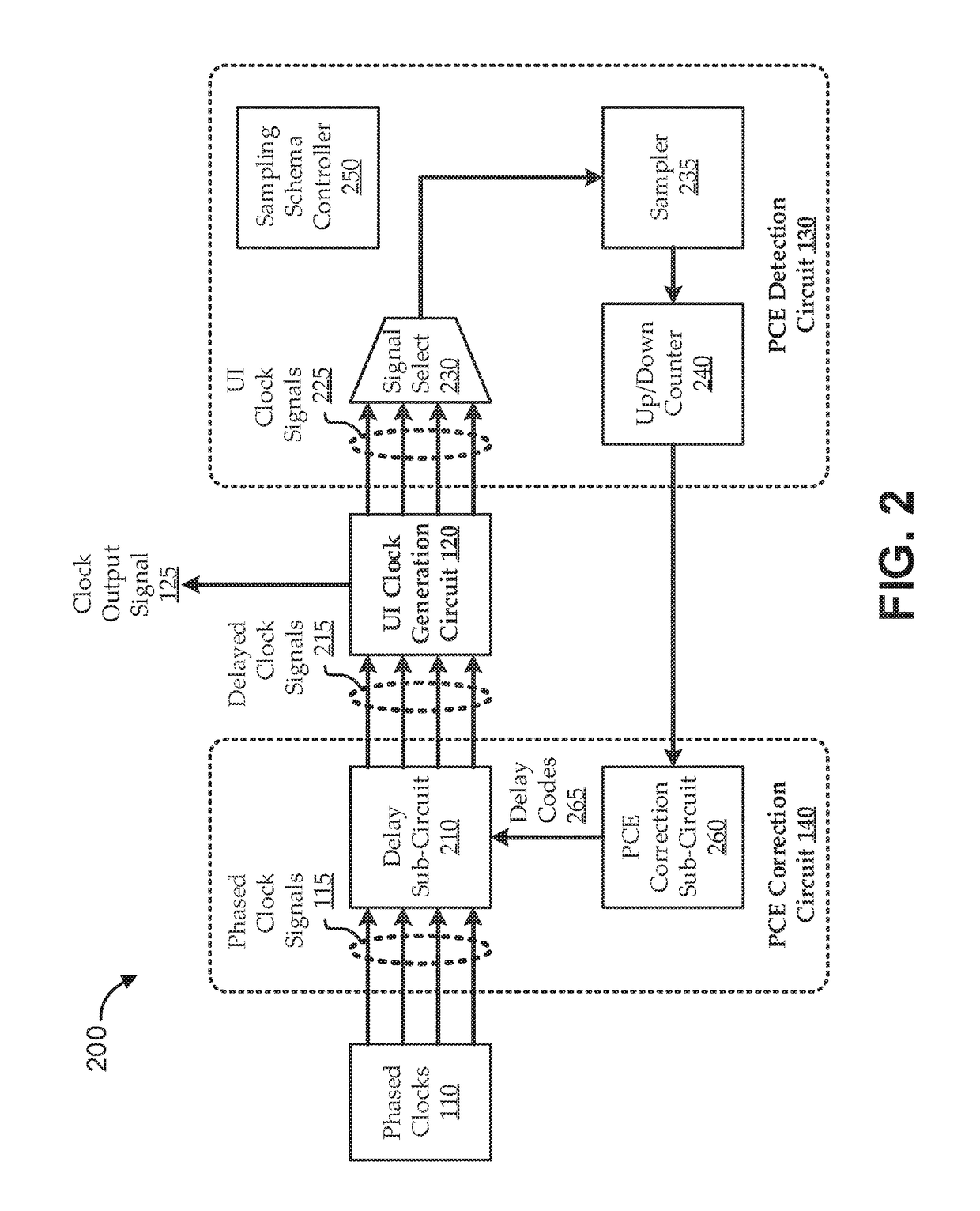

Phased clock error handling

ActiveUS20170222796A1Easy to useSmall resolutionVoltage-current phase angleCounting chain asynchronous pulse countersImage resolutionError processing

Embodiments include systems and methods for detecting and correcting phased clock error (PCE) in phased clock circuits (e.g., in context of serializer / deserializer (SERDES) transmission (TX) clock circuits). For example, phased input clock signals can be converted into unit interval (UI) clocks, which can be combined to form an output clock signal. PCE in the output clock signal can be detected by digitally sampling the UI clocks to characterize their respective clock pulse widths, and comparing the respective clock pulse widths (i.e., PCE in the output clock signal can result from pulse width differences in UI clocks). Delay can be applied to one or more UI clock generation paths to shift UI clock pulse transitions, thereby adjusting output clock pulse widths to correct for the detected PCE. Approaches described herein can achieve PCE detection over a wide error range and can achieve error correction with small resolution.

Owner:ORACLE INT CORP

Methods and apparatus for dividing a clock signal

ActiveUS20070013418A1Reliably dividedElectrothermal relaysCounting chain synchronous pulse countersLogic gateSingle phase

There is provided a true single phase logic clock divider that is configured to divide a clock signal by increments of two, three, four, or six. Because the true single phase logic clock divider is based on true single phase logic instead of static logic, the true single phase logic clock divider is able to reliably divide clock signals that could not reliably be divided by clock dividers based on static logic gates. There is also provided a method comprising receiving an input signal with a frequency between 2.5 gigahertz and 4 gigahertz and producing an output signal with a frequency approximately one-third of the frequency of the input signal.

Owner:MICRON TECH INC

Method of operating ripple counter, image sensor having ripple counter, method of operating image sensor, and analog-to-digital converter of image sensor

ActiveUS20090060118A1Reduce chip sizeSmall sizeTelevision system detailsTelevision system scanning detailsControl signalA d converter

An example embodiment of an image sensor may include a controller and a plurality of up / down ripple counters. The controller may generate a first control signal and a second control signal. Each of the up / down ripple counters may perform a stop operation or a count operation in response to a corresponding one of a plurality of operation control signals generated based on at least in part on the first control signal. The count operation may be an up-count operation or a down-count operation based on the second control signal. The image sensor may also include a plurality of memory chains. Each of the memory chains may receive a count value output from the up / down counters and may shift the received count value in response to a third control signal and a fourth control signal output from the controller.

Owner:SAMSUNG ELECTRONICS CO LTD

High-speed programmable frequency divider

InactiveCN101764606AImprove convenienceRealize any adjustable functionPulse automatic controlCounting chain asynchronous pulse countersNAND gateEngineering

The invention relates to a high-speed programmable frequency divider comprising four nand gates and multiple stages of latch combinations. The output end of the first nand gate, the output end of the second nand gate and the output end of the third nand gate are respectively connected with the input end of the fourth nand gate; the first nand gate, the second nand gate and the third nand gate are respectively provided with a control input end; each stage of latch combination comprises a clock high-openness latch and a clock low-openness latch; adjacent latches are connected by a different clock openness latch, namely, the output end of the clock high-openness latch is connected with the input end of the clock low-openness latch, and the output end of the clock low-openness latch is connected with the input end of the clock high-openness latch; the output end of the first stage of clock low-openness latch is connected with the input end of the first nand gate; the output end of the first stage of clock high-openness latch is connected with the input end of the second nand gate; and the output end of the second stage of clock high-openness latch is connected with the input end of the third nand gate.

Owner:浩凯微电子(上海)有限公司

Frequency measuring apparatus

ActiveUS8461821B2Improve accuracyEasily and simply configuredDigital variable displayCounting chain synchronous pulse countersAlgorithmFrequency measurements

A frequency measuring apparatus includes: a high-order digit calculation section adapted to measure an input signal and output a high-order digit value of a frequency value of the input signal; a low-order digit calculation section adapted to measure the input signal and output a low-order digit value of the frequency value of the input signal; and an adding section adapted to add the high-order digit value and the low-order digit value to each other to output the frequency value of the input signal.

Owner:SEIKO EPSON CORP

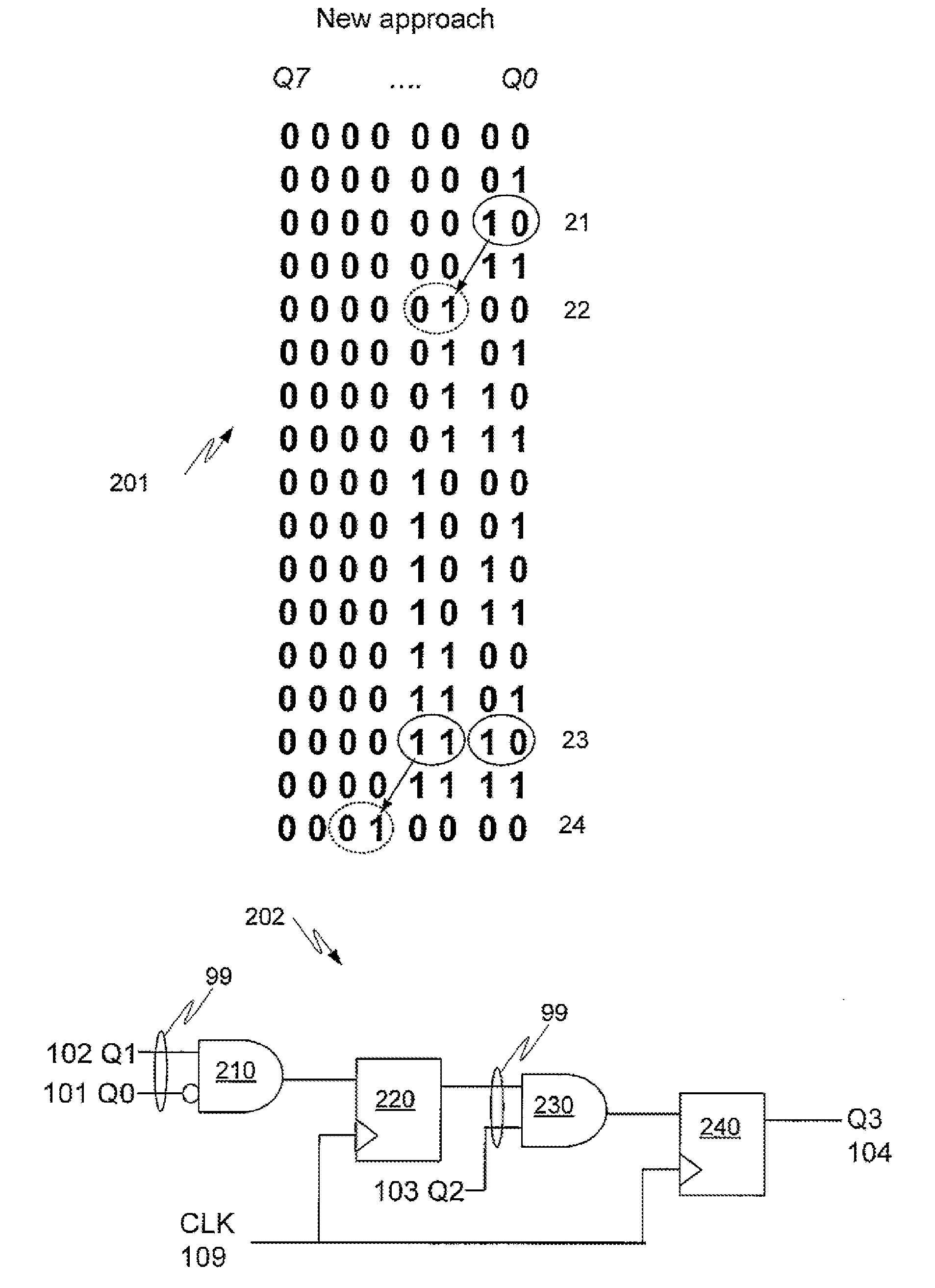

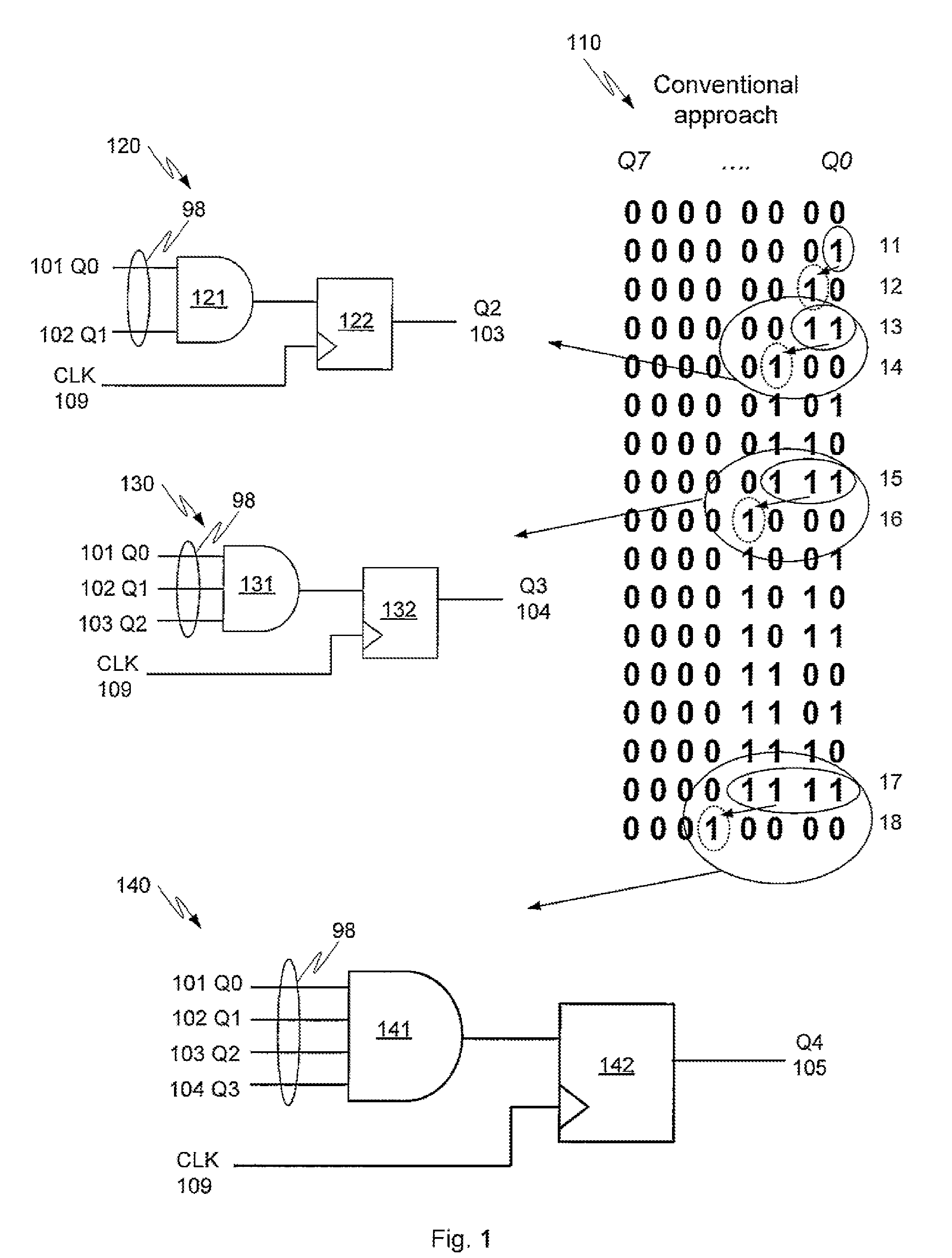

Counter having improved counting speed

InactiveUS7123679B2Reduce latencyWide operation marginCounting chain synchronous pulse countersCounting chain asynchronous pulse countersLeast significant bitDelayed time

A counter having enhanced counting speed is provided. The counter includes first through N-th output signal generators. The first output signal generator responds to a clock signal and outputs a first output signal in which a low level and a high level are output once per cycle of the clock signal. The second output signal generator responds to the clock signal and the first output signal and outputs a second output signal in which a low level and a high level are output every two cycles of the clock signal. The third output signal generator responds to the clock signal and the second output signal and outputs a third output signal in which a low level and a high level are output every four cycles of the clock signal. The N-th output signal generator responds to the clock signal and the N−1th output signal and outputs an N-th output signal in which a low level and a high level are output every 2N−1 (where N is a natural number greater than 1) cycles of the clock signal. The first through N-th output signals represent logic values of an N-bit counter in which the first output signal is the least significant bit and the N-th output signal is the most significant bit. A synchronous or non-synchronous counter according to the present invention has reduced delay time, thereby ensuring a spacious operation margin in the design of peripheral circuits of the counter.

Owner:SAMSUNG ELECTRONICS CO LTD

Binary ripple counter sampling with adjustable delays

The output bits of a binary ripple counter are used to control the sampling of those output bits, thereby ensuring accurate sampling. A sampler is provided with adjustable delay elements that permit accurate sampling regardless of: delay mismatch between the sampler and a data path of the counter; the length of the counter; operating speed; or PVT variations.

Owner:TEXAS INSTR INC

Popular searches

Power conversion systems Counters with additional facilities Color television details Analogue-digital converters Physical parameters compensation/prevention Analogue/digital conversion calibration/testing Generating/distributing signals Pulse manipulation Time-to-digital converters Frequency/rate-modulated pulse demodulation