Asynchronous ping-pong counter

一种计数器、非同步的技术,应用在计数器领域,能够解决不可能符合时序要求、缓慢时钟脉冲频率低等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

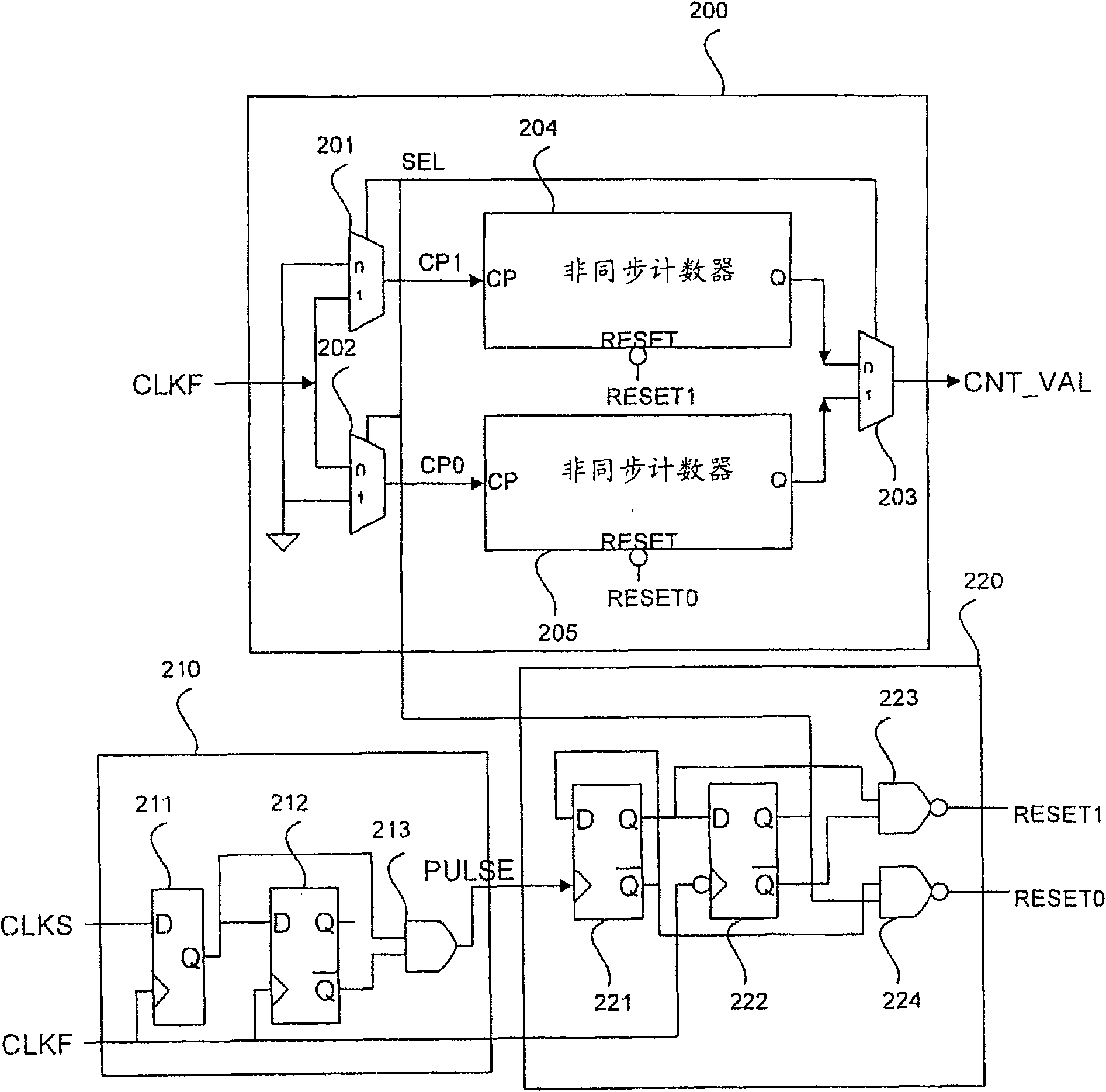

[0031] The following description will illustrate several preferred exemplary embodiments of the present invention, such as various electronic circuits, components and related methods. Those skilled in the art should understand that the present invention can be implemented in various possible ways, and is not limited to the following exemplary embodiments or the features in the embodiments. In addition, well-known details are not repeatedly shown or described in order to avoid obscuring the gist of the present invention.

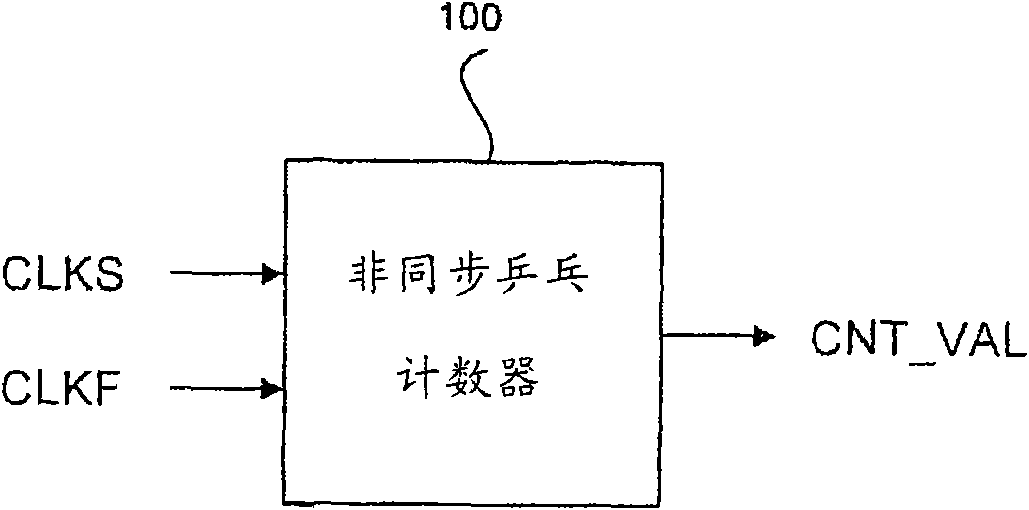

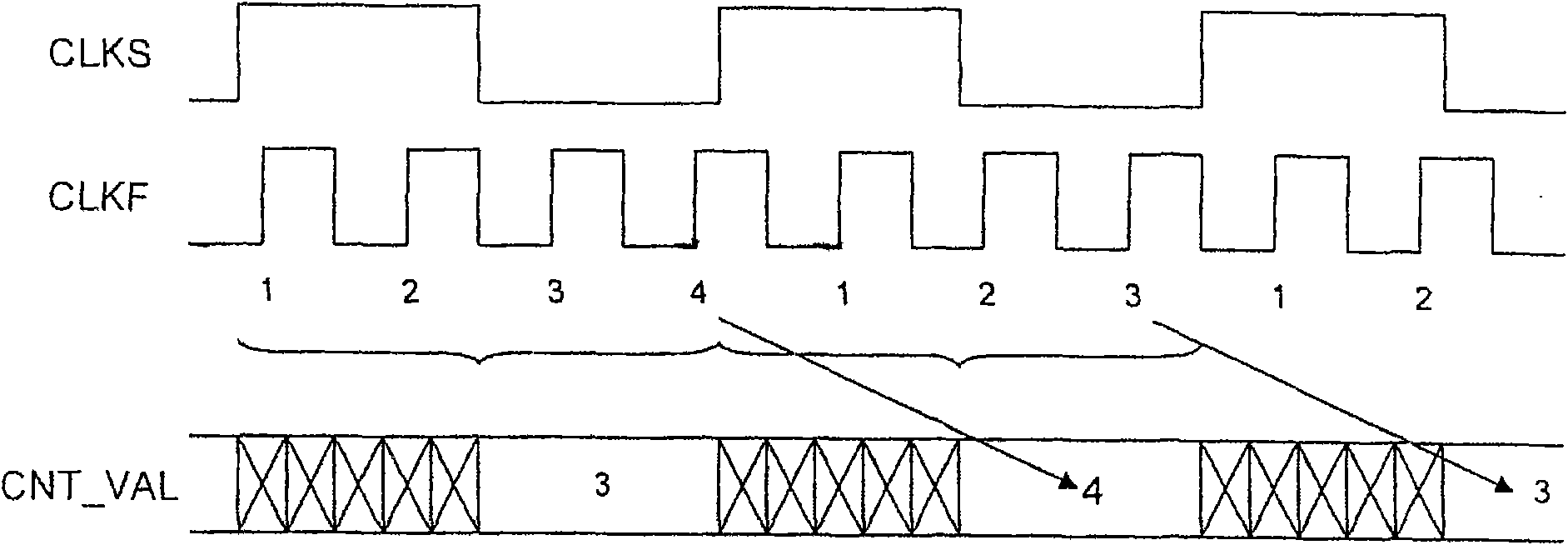

[0032] FIG. 1A shows a block diagram of an embodiment of the asynchronous ping-pong counter of the present invention. Please refer to Fig. 1A, the asynchronous ping-pong counter 100 of the present invention receives a first input clock pulse (CLKF in Fig. 1A) and a second input clock pulse (CLKS in Fig. 1A) to generate a digital output value ( CNT_VAL in FIG. 1A ), the digital output value represents the number of occurrences of the rising edge of the first ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More