Patents

Literature

67results about How to "Increase information density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

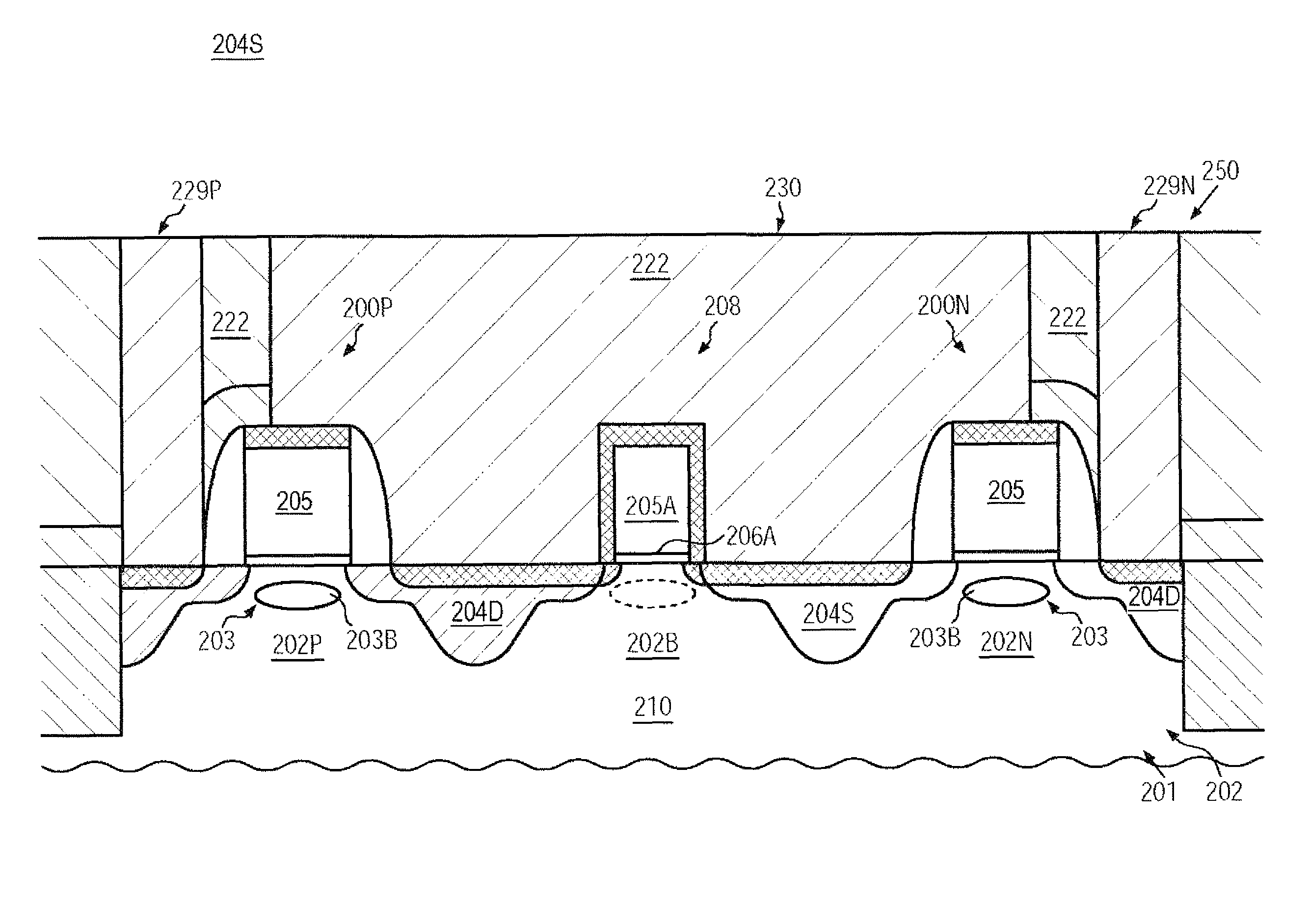

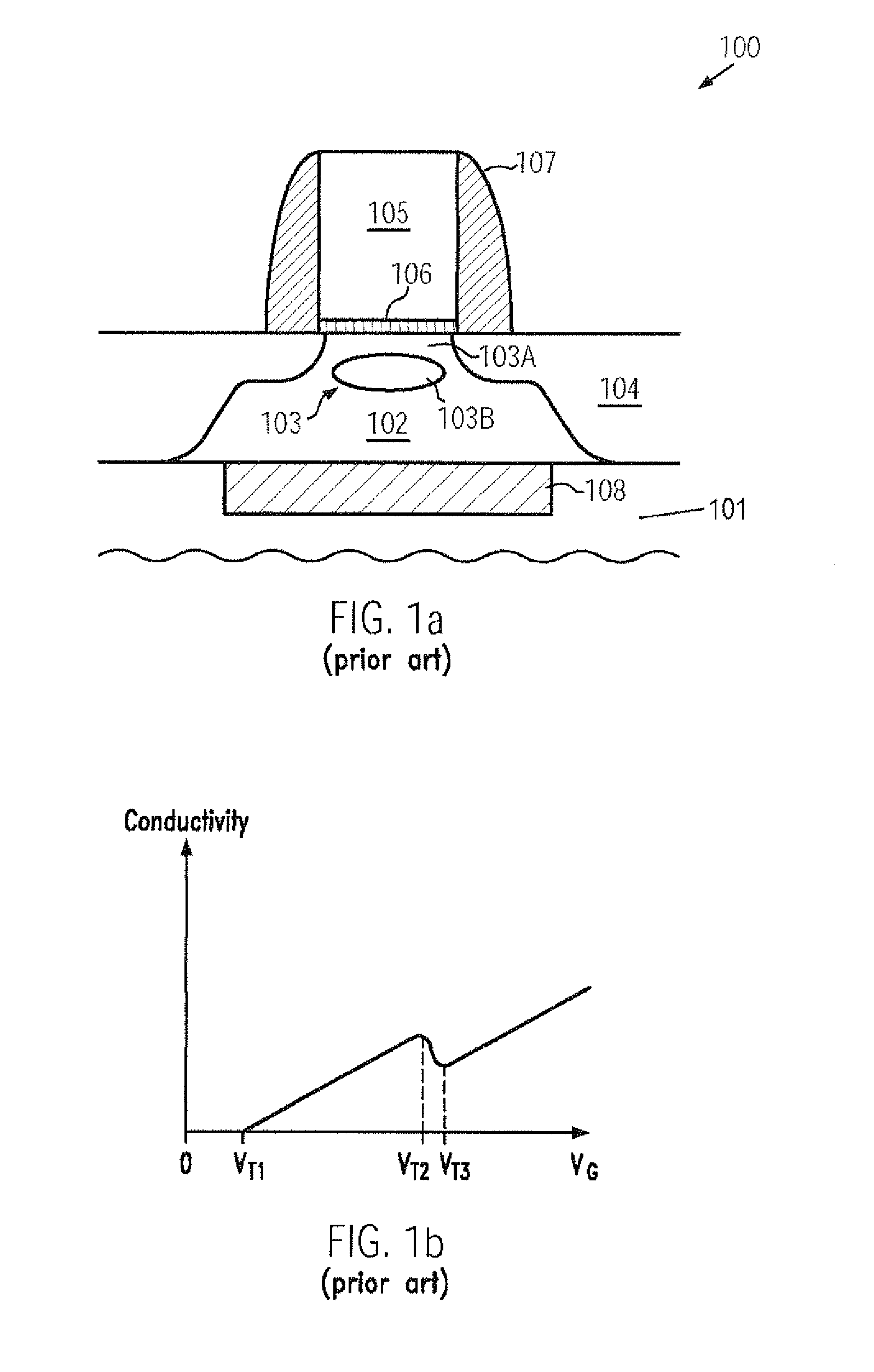

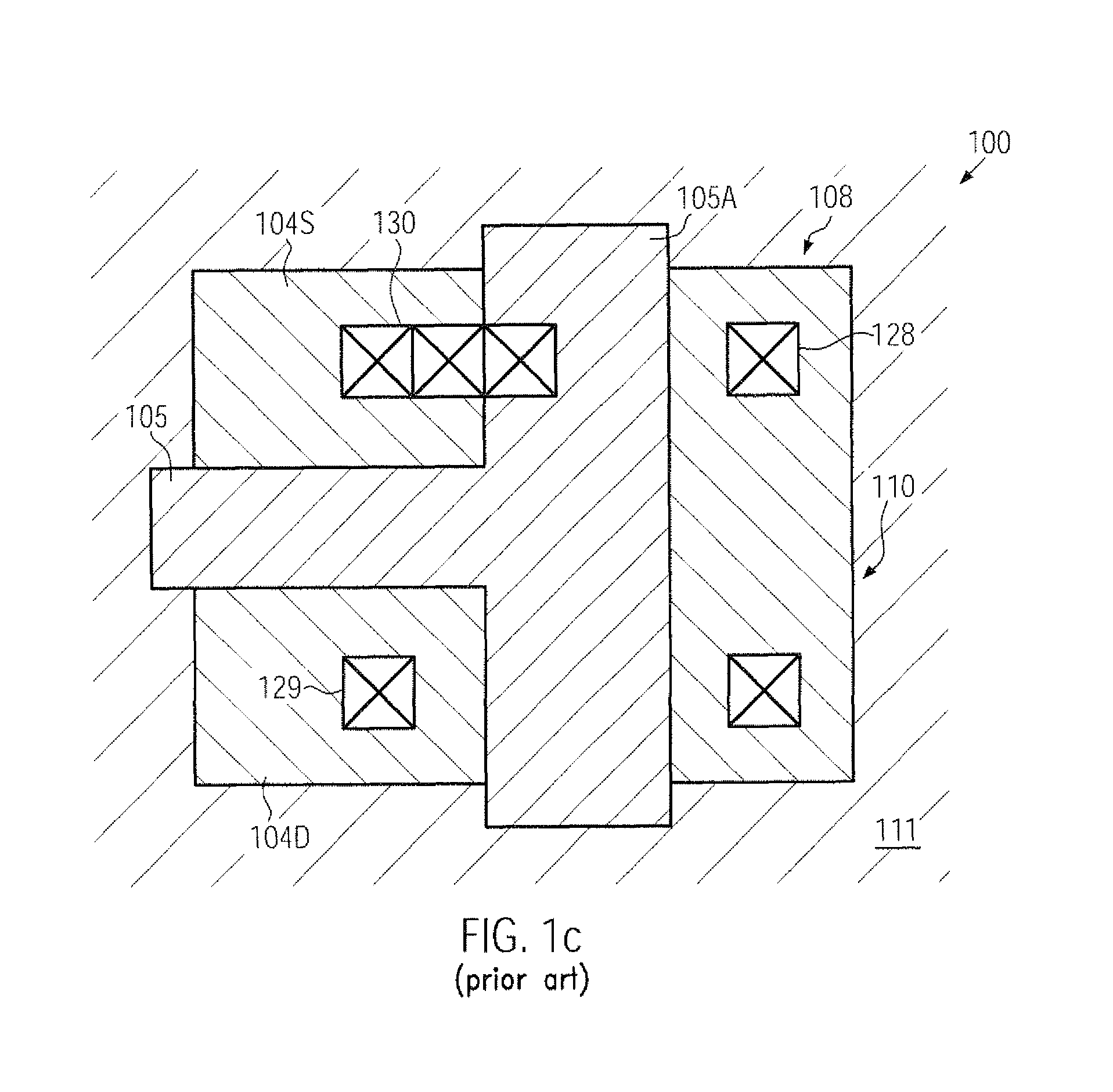

Static RAM cell design and multi-contact regime for connecting double channel transistors

ActiveUS8183096B2Improve space efficiencyLow resistivityTransistorSolid-state devicesBody contactCell design

A static RAM cell may be formed on the basis of two double channel transistors and a select transistor, wherein a body contact may be positioned laterally between the two double channel transistors in the form of a dummy gate electrode structure, while a further rectangular contact may connect the gate electrodes, the source regions and the body contact, thereby establishing a conductive path to the body regions of the transistors. Hence, compared to conventional body contacts, a very space-efficient configuration may be established so that bit density in static RAM cells may be significantly increased.

Owner:ADVANCED MICRO DEVICES INC

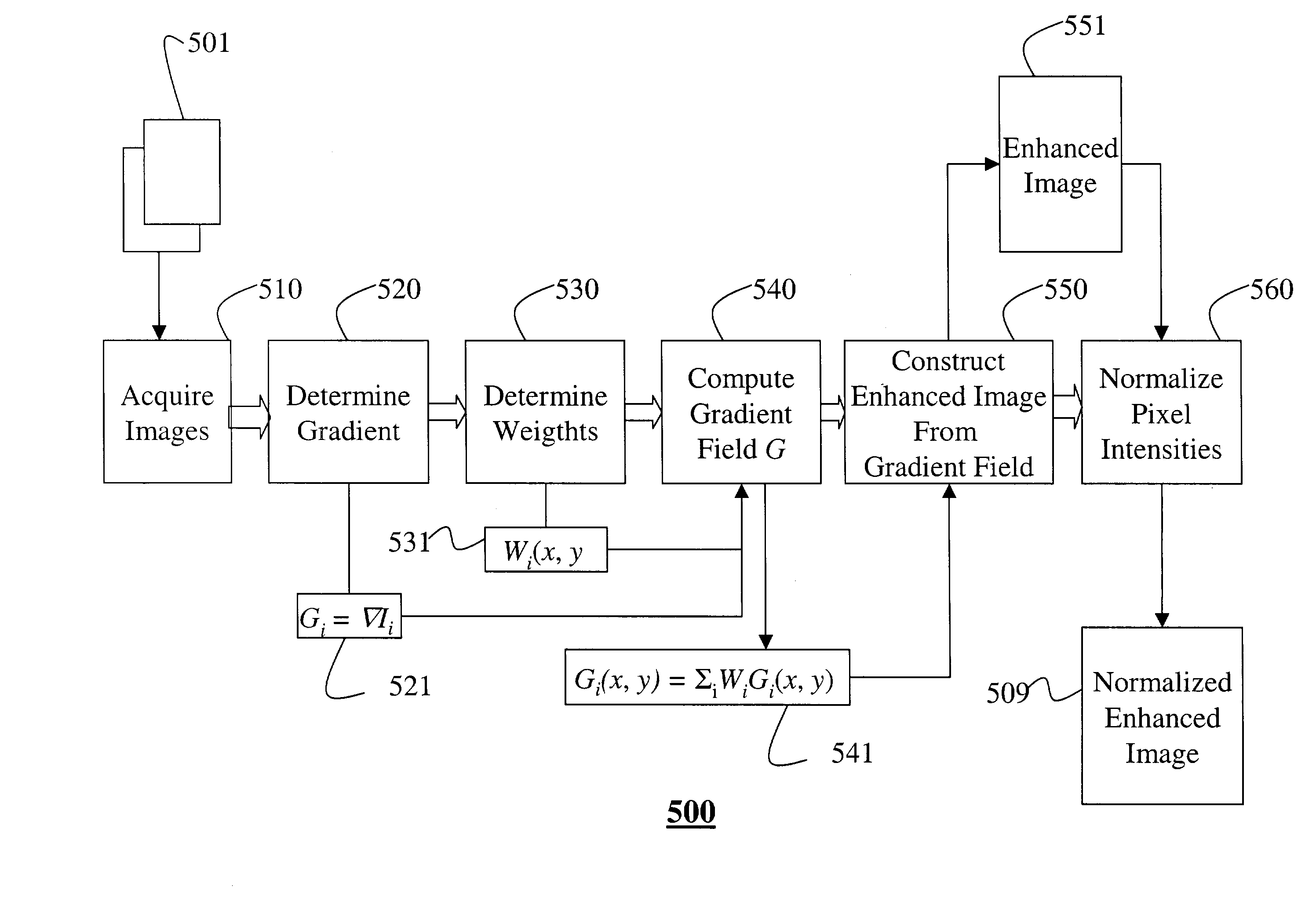

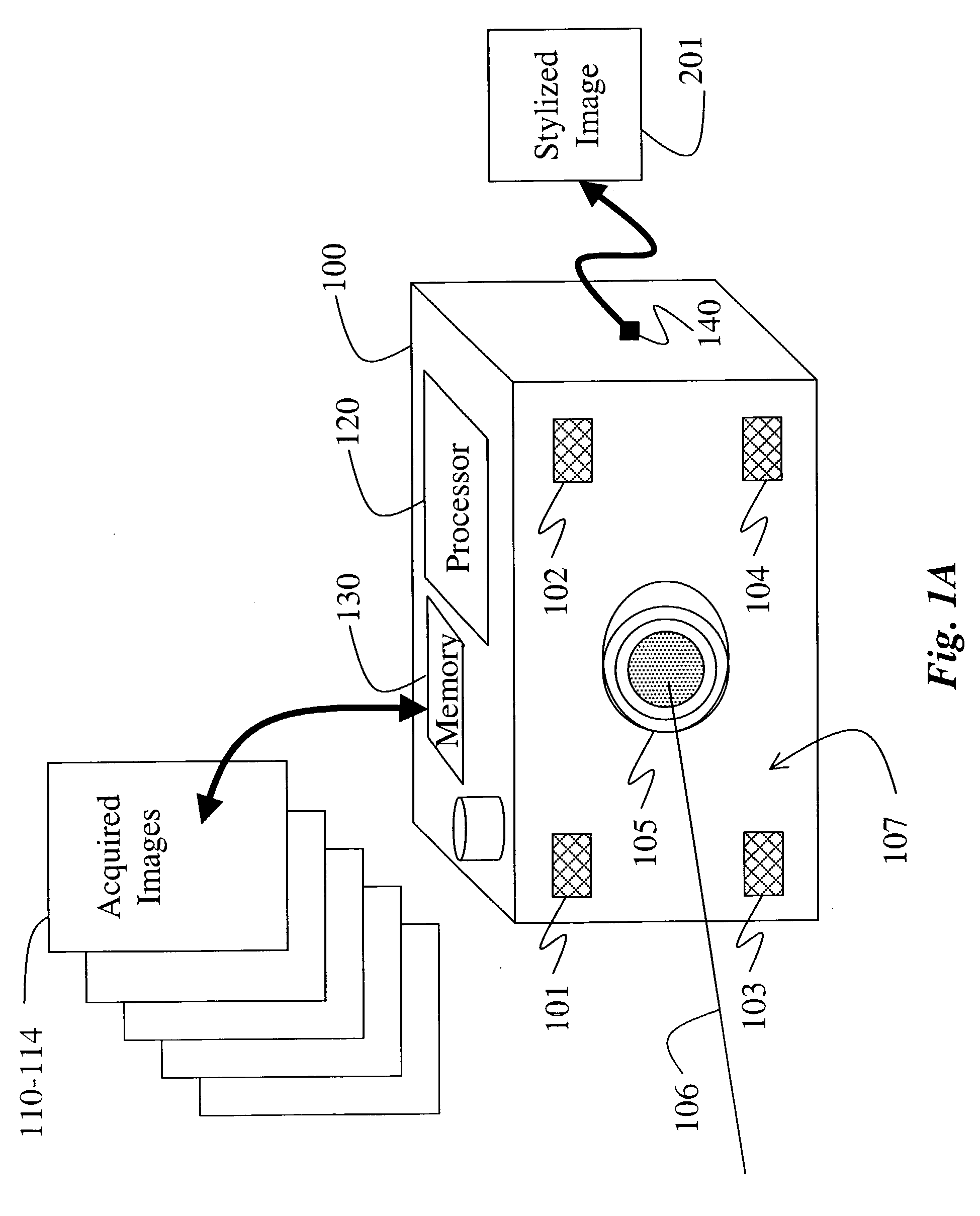

Enhancing low quality images of naturally illuminated scenes

Owner:MITSUBISHI ELECTRIC RES LAB INC

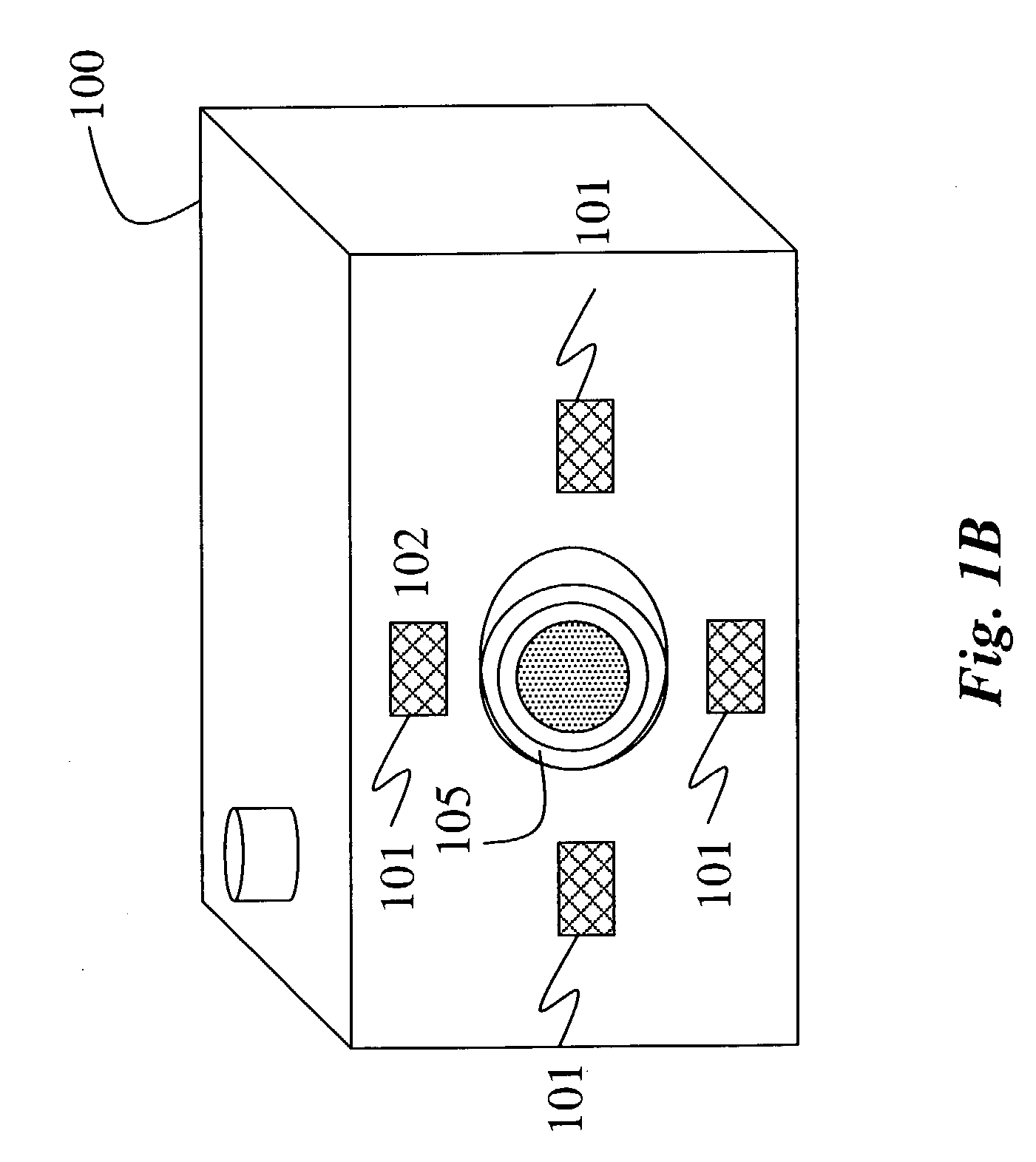

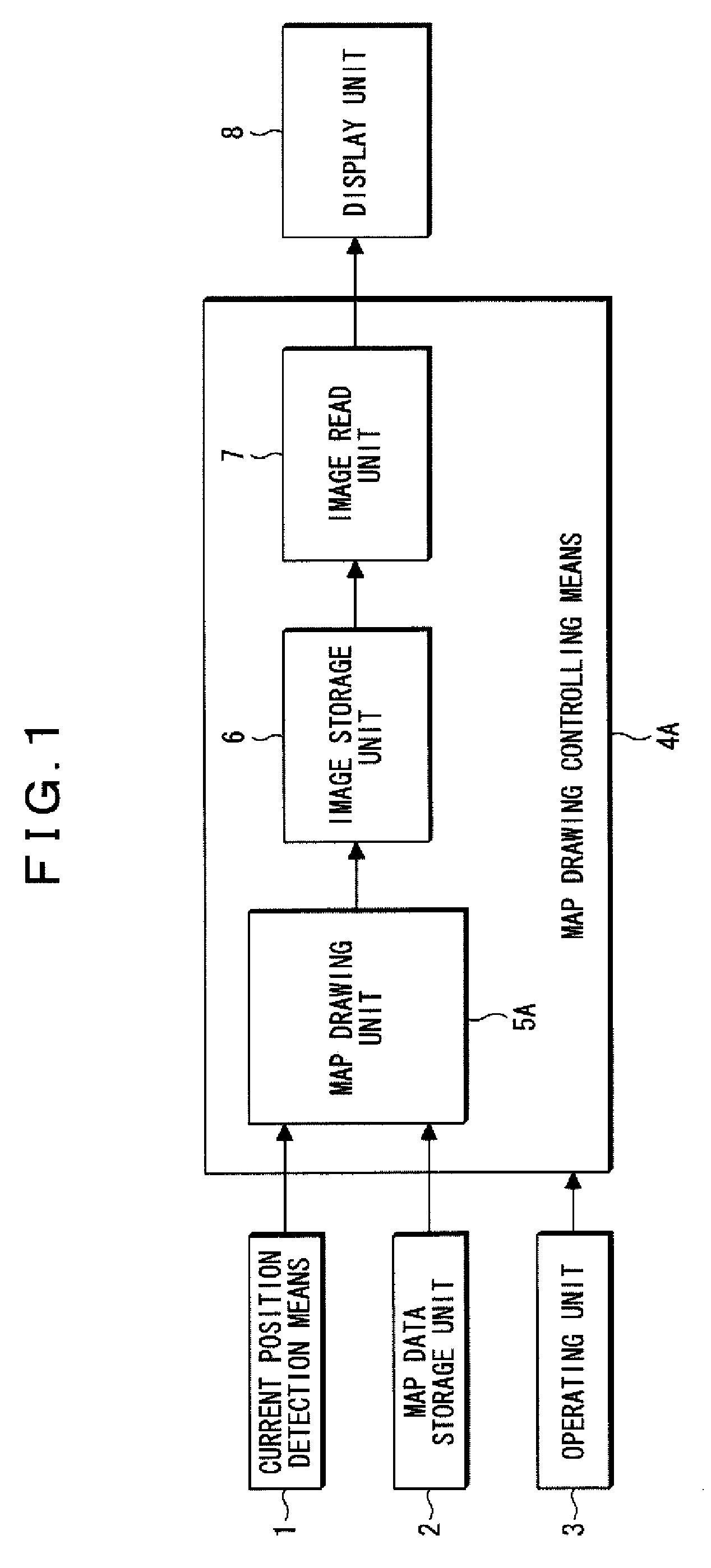

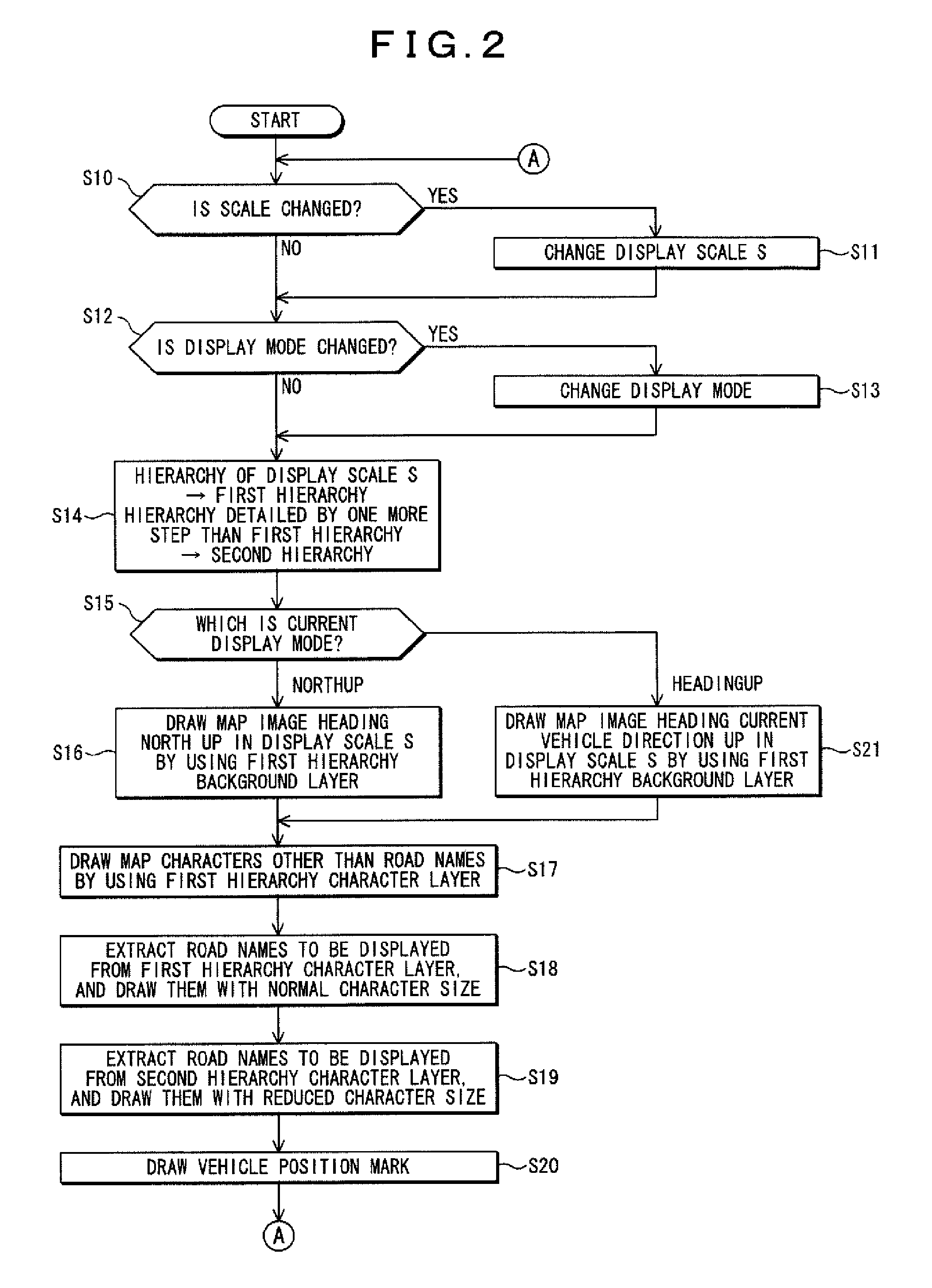

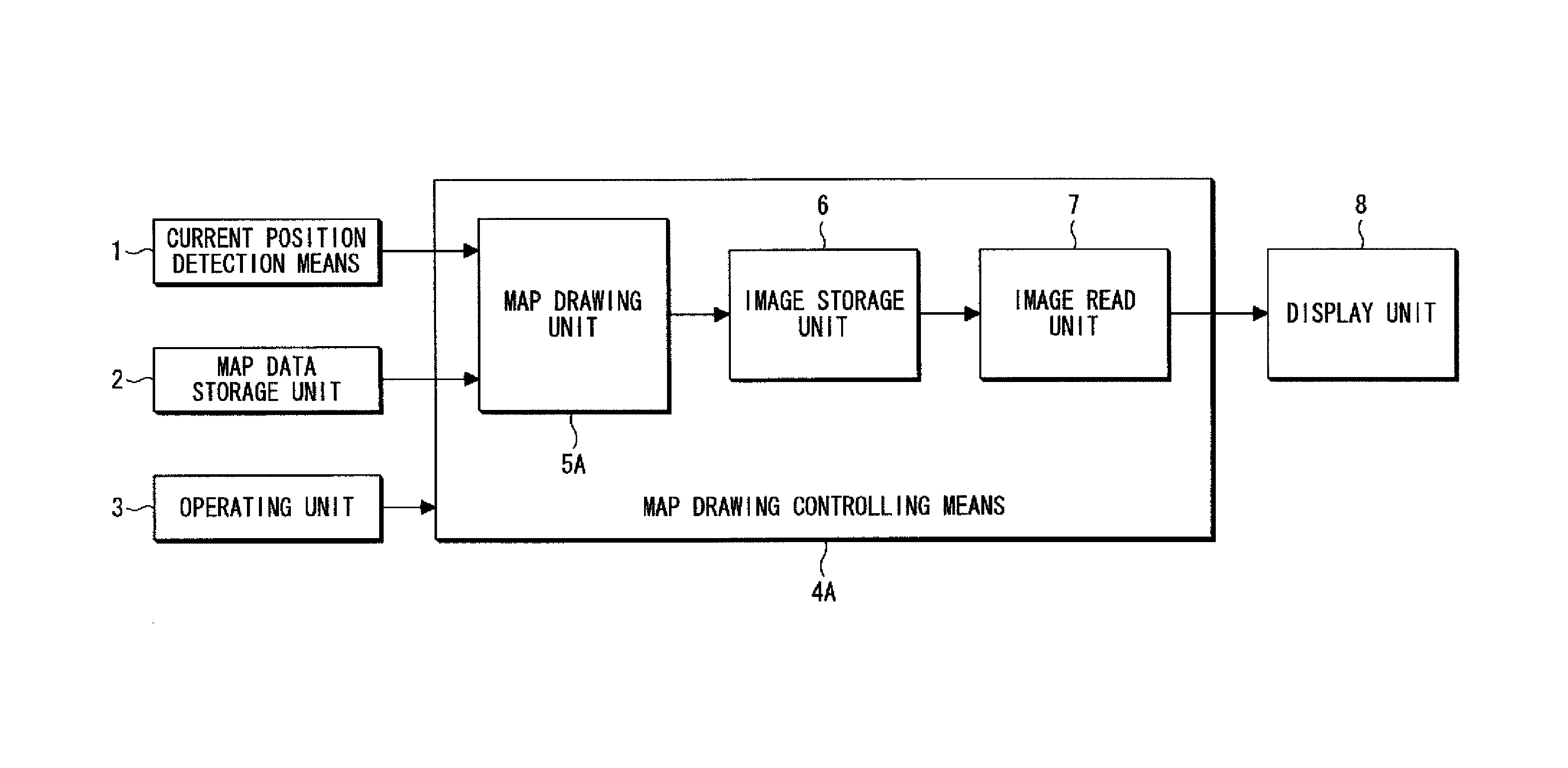

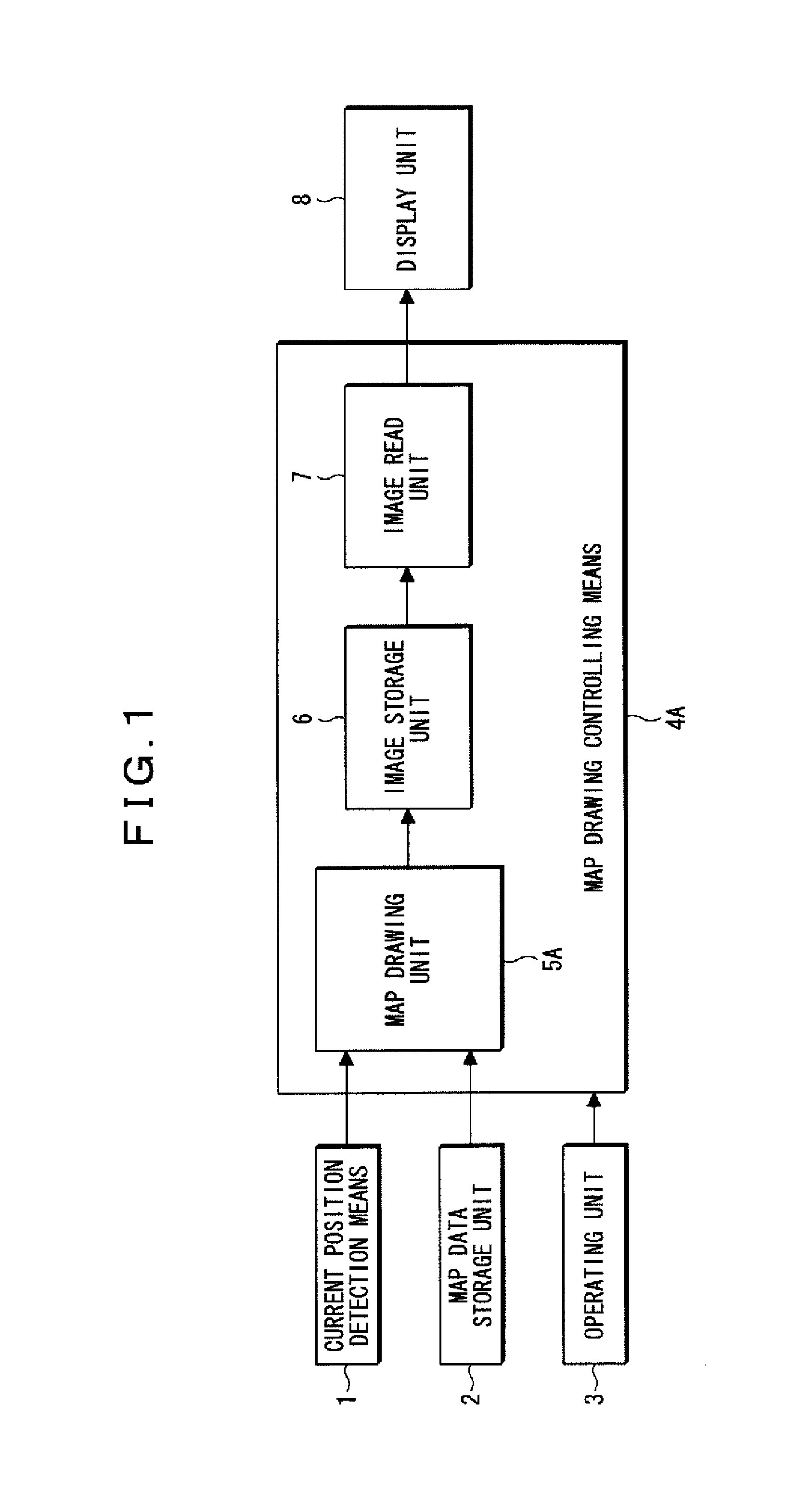

Map Display Device And Map Display Method

ActiveUS20080306684A1Increase information densityDecreasing legibilityInstruments for road network navigationRoad vehicles traffic controlDisplay deviceInformation density

The invention provides a map display device and map display method that enhance the information density of displayed road names while maintaining legibility of a map image. First, the map drawing unit draws, to an image storage unit, a map image of roads and so forth in a desired scale, by using the background layer of a first hierarchy corresponding to the desired scale. Second, the map drawing unit draws place names and facility names by using the character layer of the first hierarchy to superimpose them on the map image. Third, the map drawing unit extracts the road names that do not overlap with the map characters of the place names and facility names on the map image by using the character layer of the first hierarchy, and superimposes them on the map image at the normal character size. Fourth, the map drawing unit extracts, by using the character layer of a second hierarchy corresponding to a scale level smaller by one step than the desired scale level, road names that do not overlap with the map characters of the other road names, place names, facility names and so forth on the map image, and superimposes them on the map image at a smaller character size. Finally, the map drawing unit superimposes the vehicle position mark on the map image.

Owner:ALPINE ELECTRONICS INC

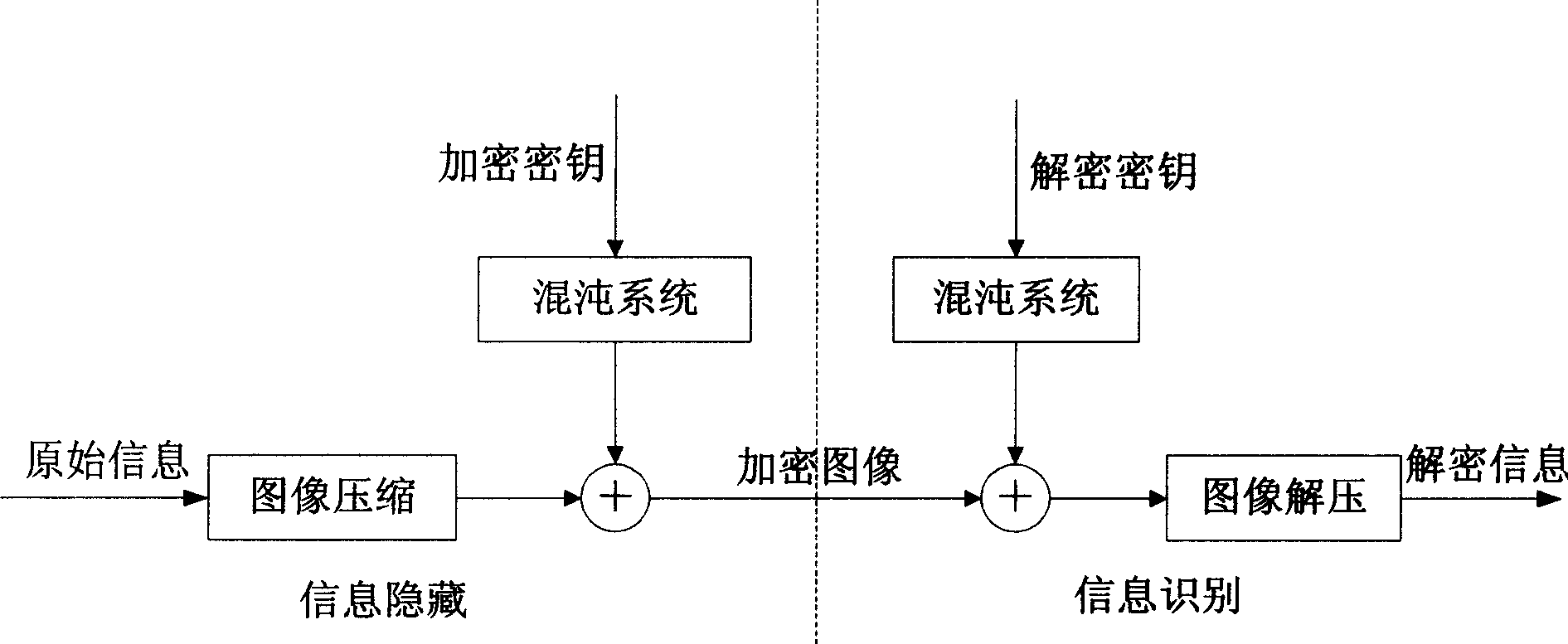

Image false-proof method based on chaotic characteristic

InactiveCN1738235AImplement encryptionAchieve decryptionImage data processing detailsSensing record carriersChaotic systemsImage segmentation

The invention discloses a image counterfeit deterrence method based on the chaotic feature, comprising: first, by the chaotic mapping system, using the information needed keep secret and counterfeit deterrence to generate the chaotic sequence which is used to encode the information, then, printing the encoded information to the two-dimension bar code image according to the PDF417 bar code; collecting the two-dimension bar code image by the scanner, and operating the preprocessing of image segmentation, filtration, geometric correction and stratified on collected image, then decoding the bar code according to the decoding rule of national standard PDF417 bar code to attain the chaotic encoded information carried by bar code image. The invention fully utilizes the features of chaotic system and two-dimension bar code technique which are combined for image counterfeit deterrence. The invention has the characters as strong secret-keeping property and large information carried, while it can recognize automatically.

Owner:XI AN JIAOTONG UNIV

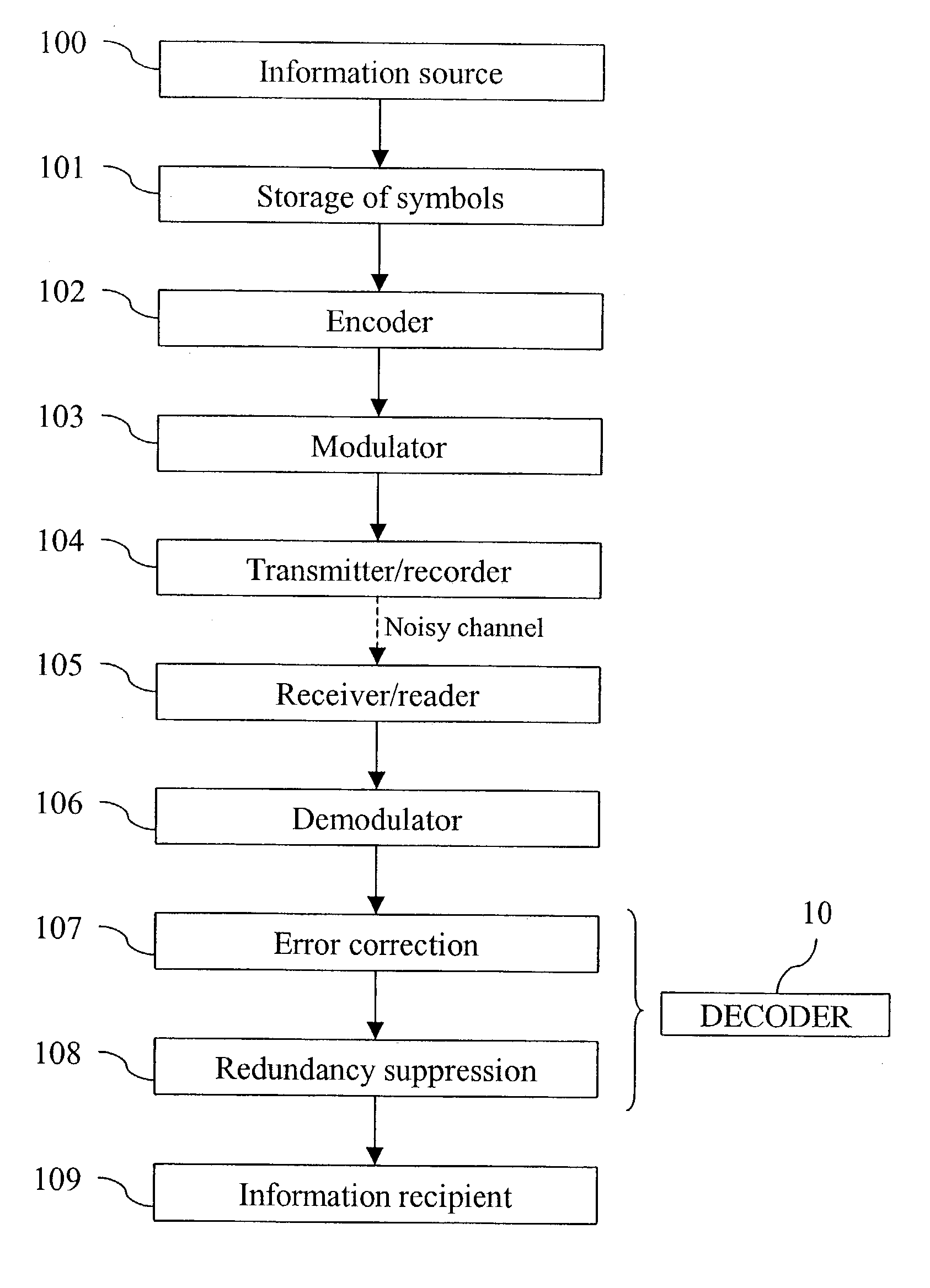

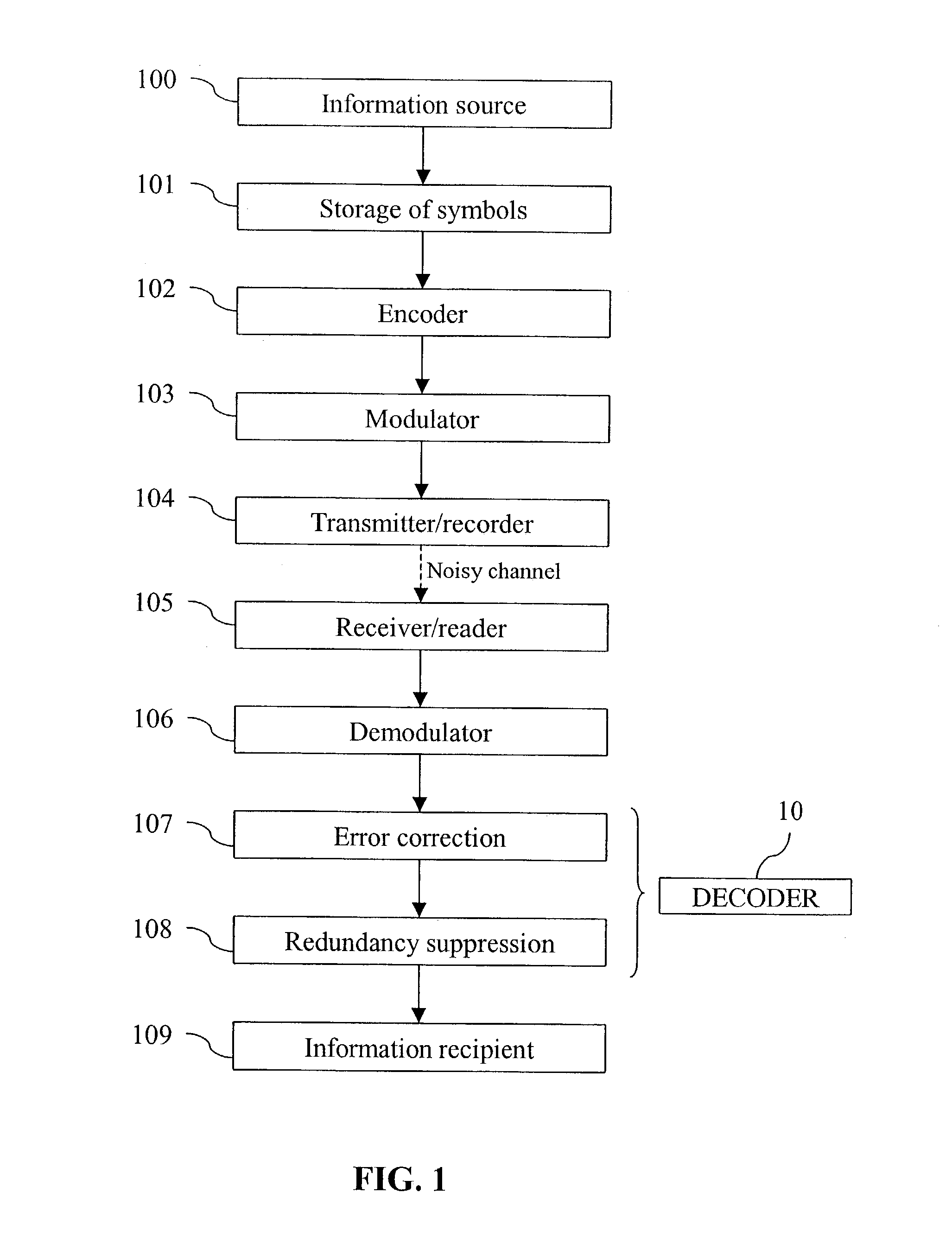

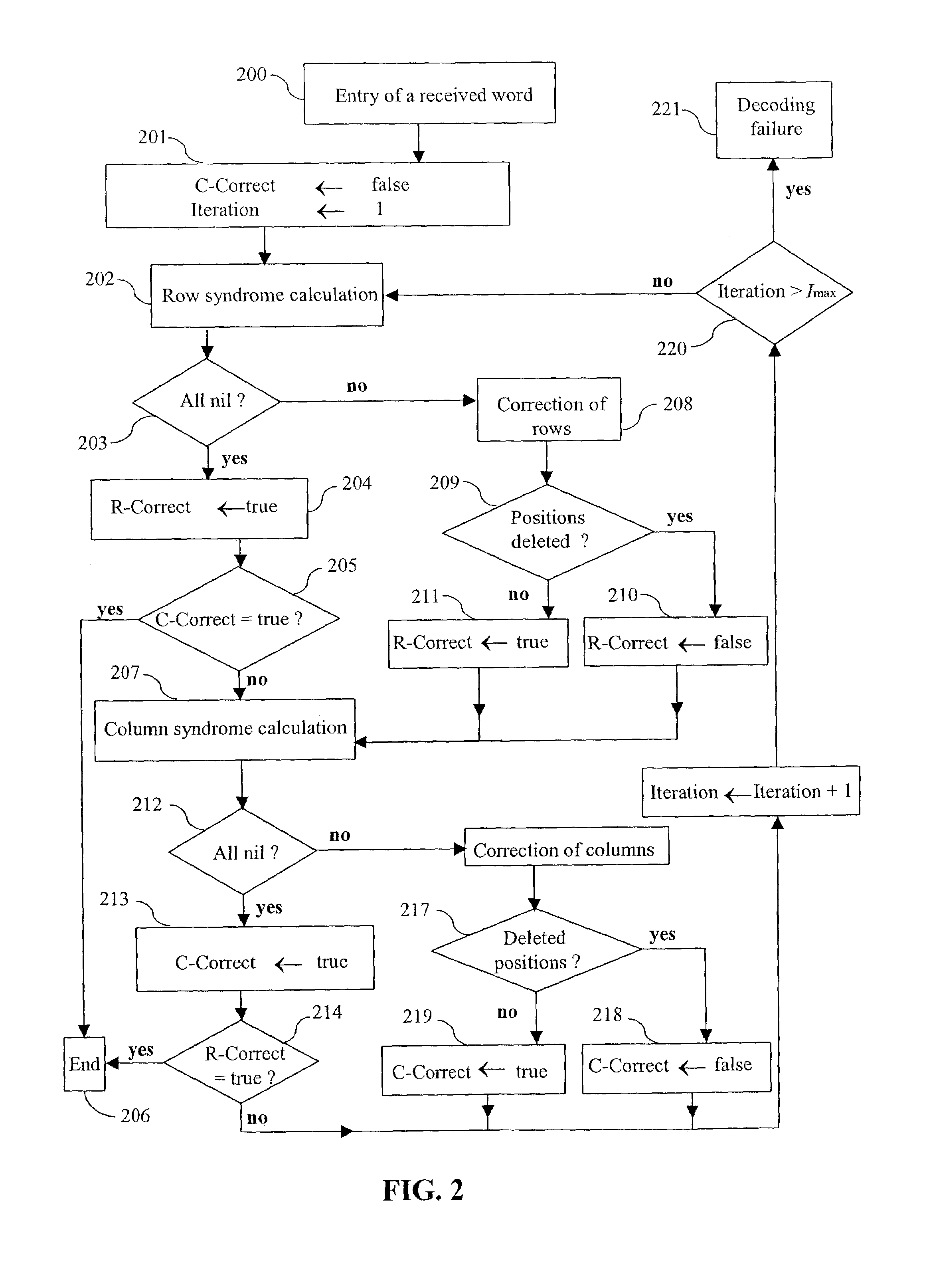

Low-cost methods and devices for the decoding of product cases

InactiveUS7120850B2Increase information densityConvenient lengthError preventionTransmission systemsAlgorithm

A method of decoding product codes is disclosed, in which the symbols of each codeword may be placed in a table comprising n2 rows and n1 columns, such that the symbols constituting each row form a permitted word of length n1 according to a first component code able to be decoded by means of an algorithm A1 for correction with erasures, and the symbols constituting each column form a permitted word of length n2 according to a second component code able to be decoded by means of an algorithm A2 for correction with erasures. According to the method, a correction of a row or column is only accepted when the result of the correction is deemed reliable, otherwise all the symbols of that row or column are erased. Devices and apparatus adapted to implement this method are also disclosed. The method is preferably applied to algebraic geometric codes.

Owner:CANON KK

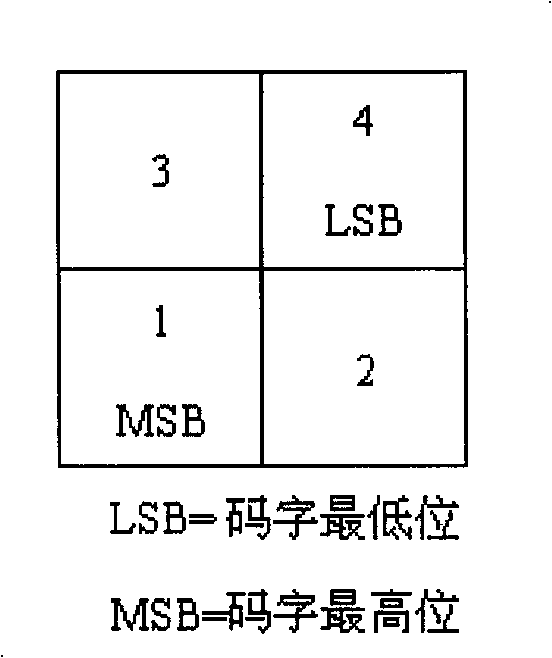

Color two dimension bar code with high compression ratio Chinese character coding capability and its coding and decoding method

InactiveCN101515335AIncrease the compression ratioIncrease information densitySensing record carriersRecord carriers used with machinesChinese charactersPartition of unity

The invention discloses a color two dimension bar code with high compression ratio Chinese character coding capability, the whole bar code image comprises rectangular modules which are regularly ranged and includes a functional image and a data area, the functional image is the four sides of the color two dimension bar code, wherein the left side comprise two alternate color blocks with different chemical feature, the lower side comprises single color block, the upper side and the right side comprises four alternate color modules with different chemical feature from left to right and from bottom to up; the data area is the middle part of square and comprises two alternate two-color modules which are vertical and have different chemical feature, the code words in the data area are arranged from left to right and from the up down. The invention also provides a method for coding and decoding the color two dimension bar cod. The invention effectively improves the compression ratio of Chinese character, the information density of the bar code and the information content of the unit area.

Owner:ZHEJIANG UNIV OF TECH

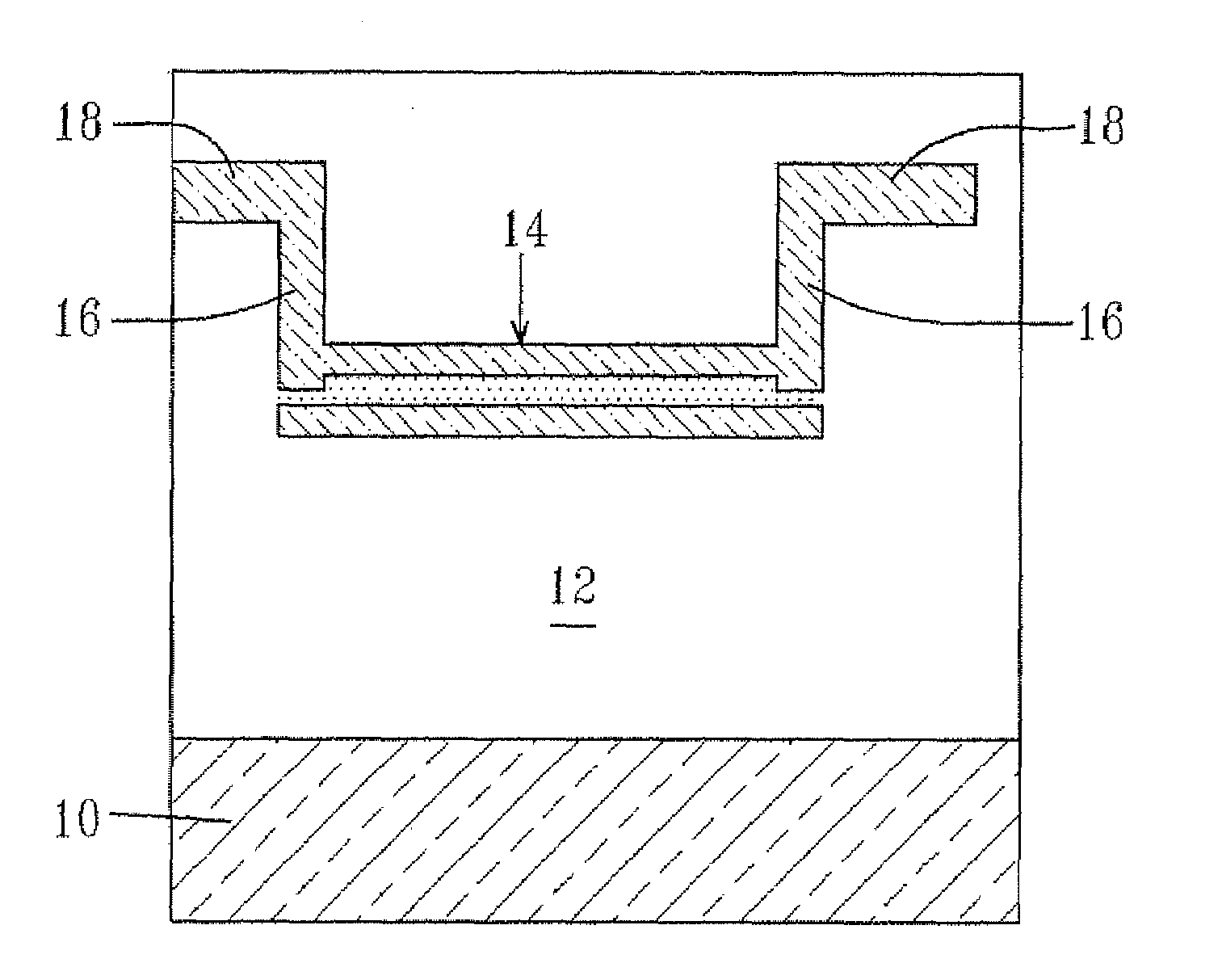

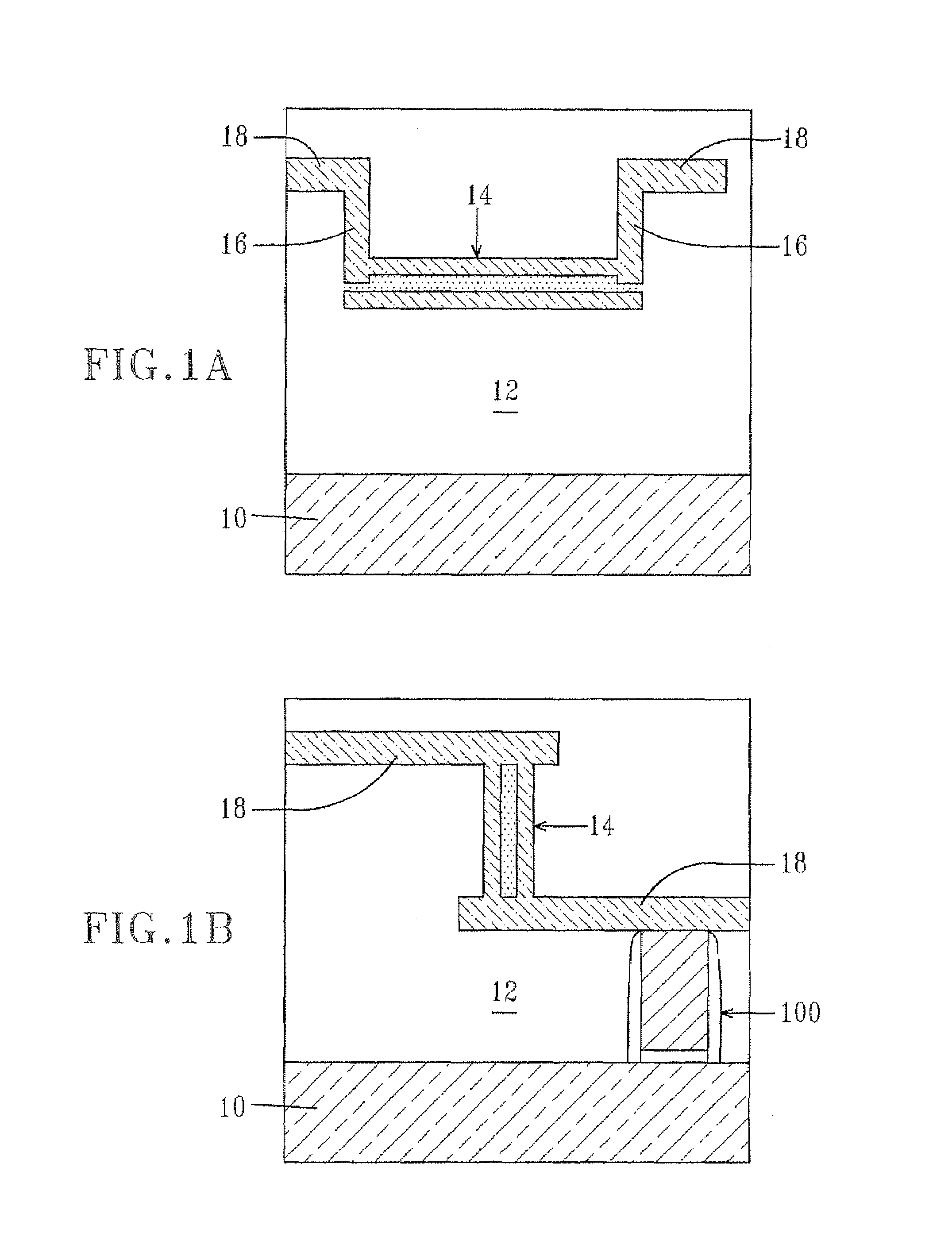

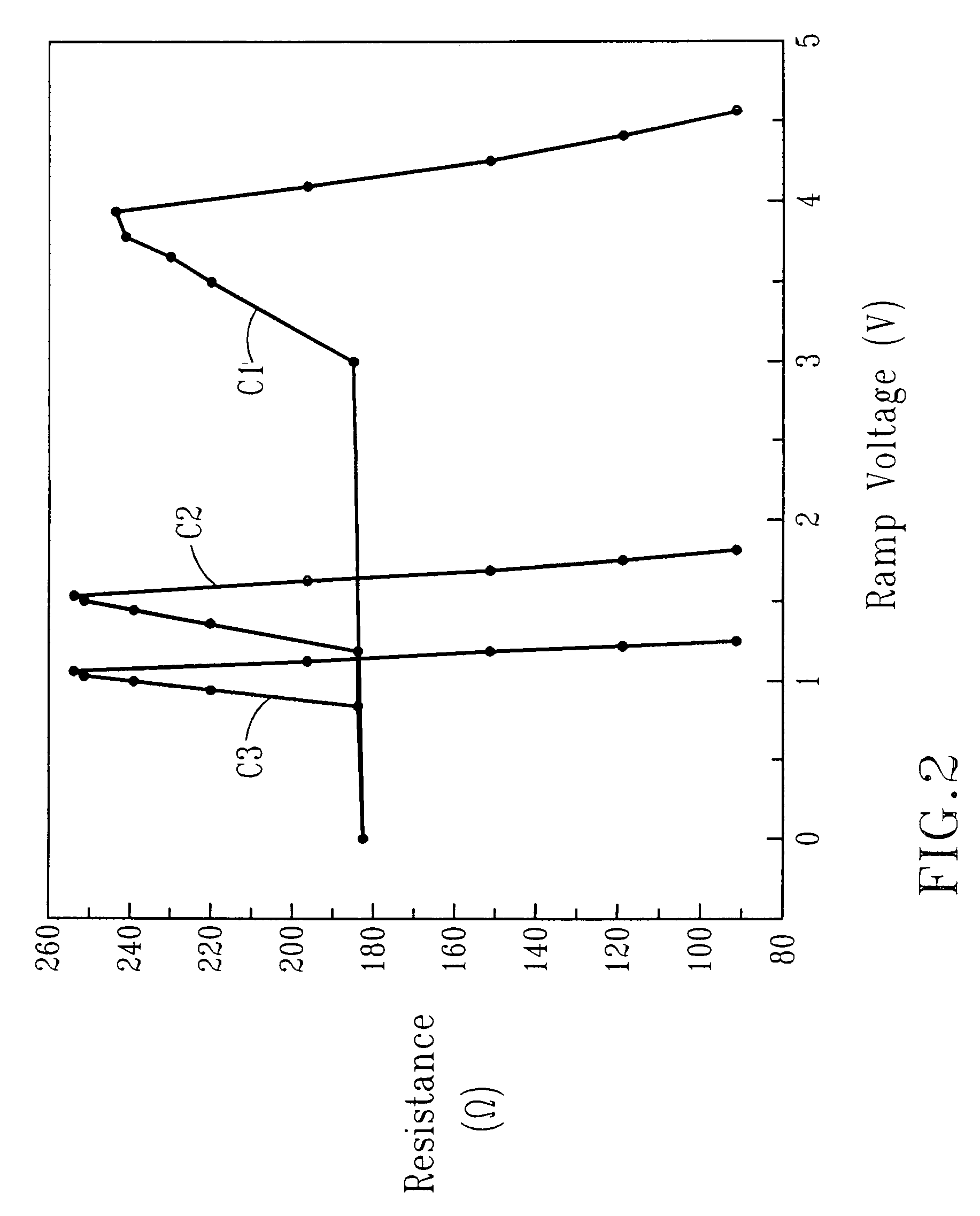

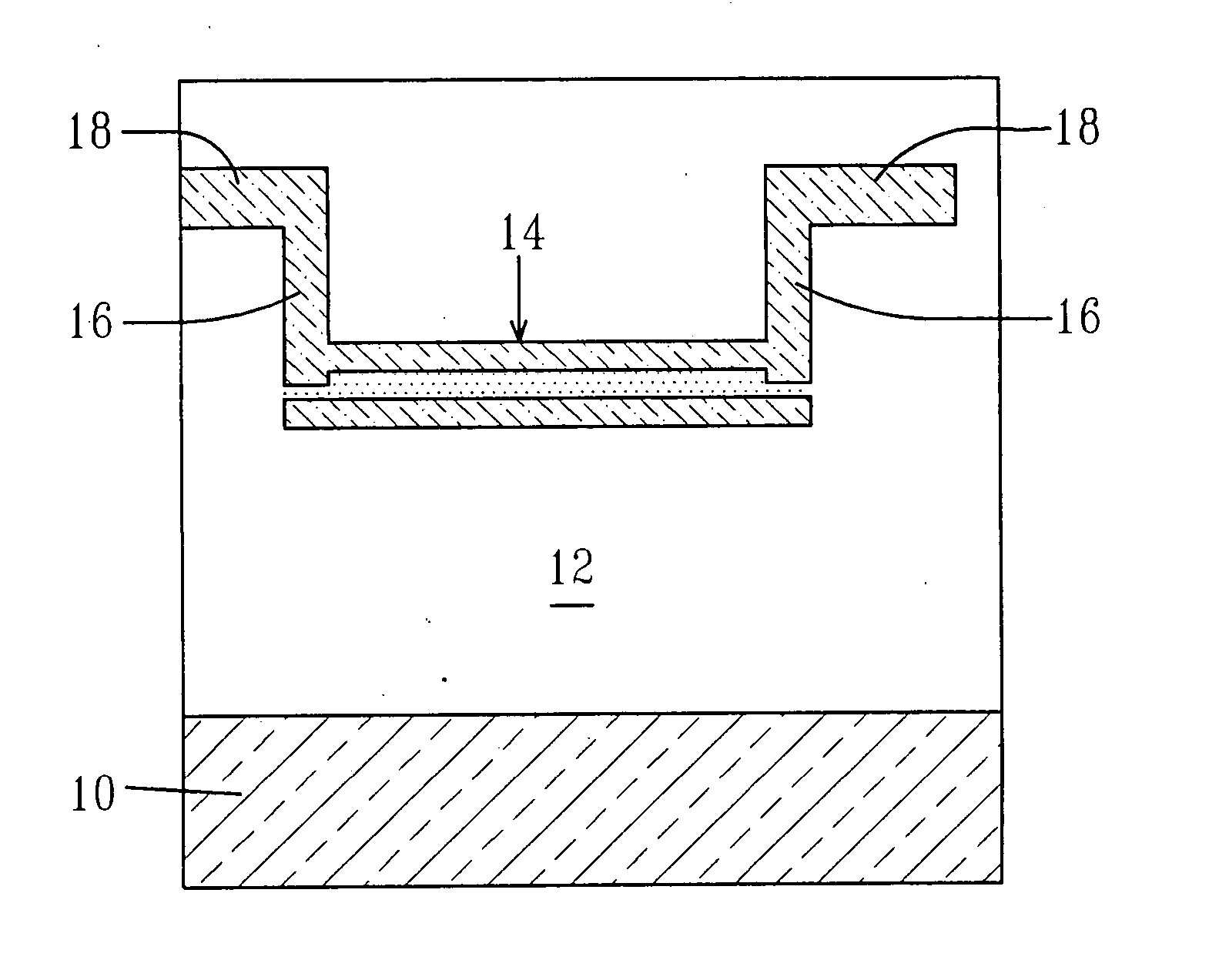

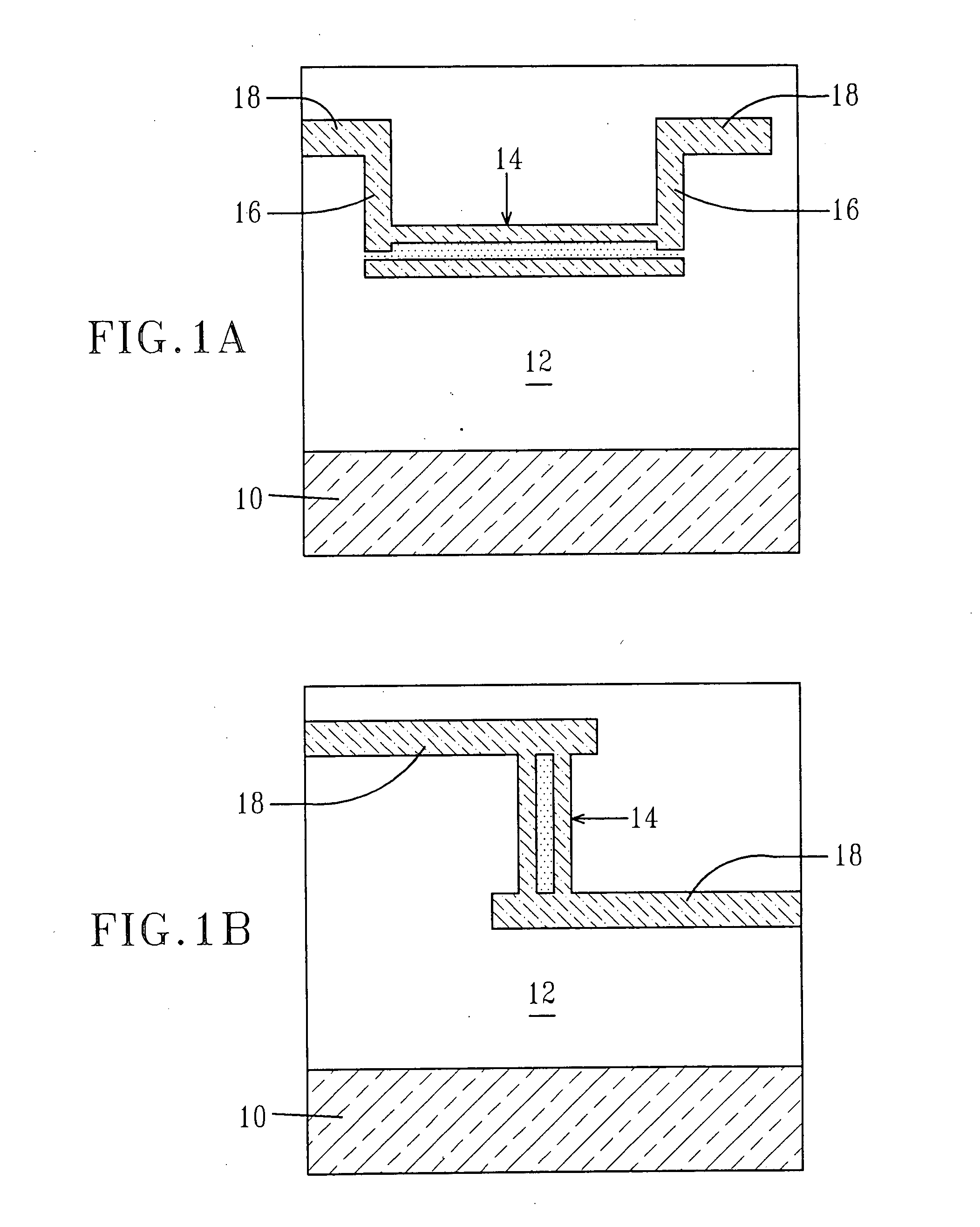

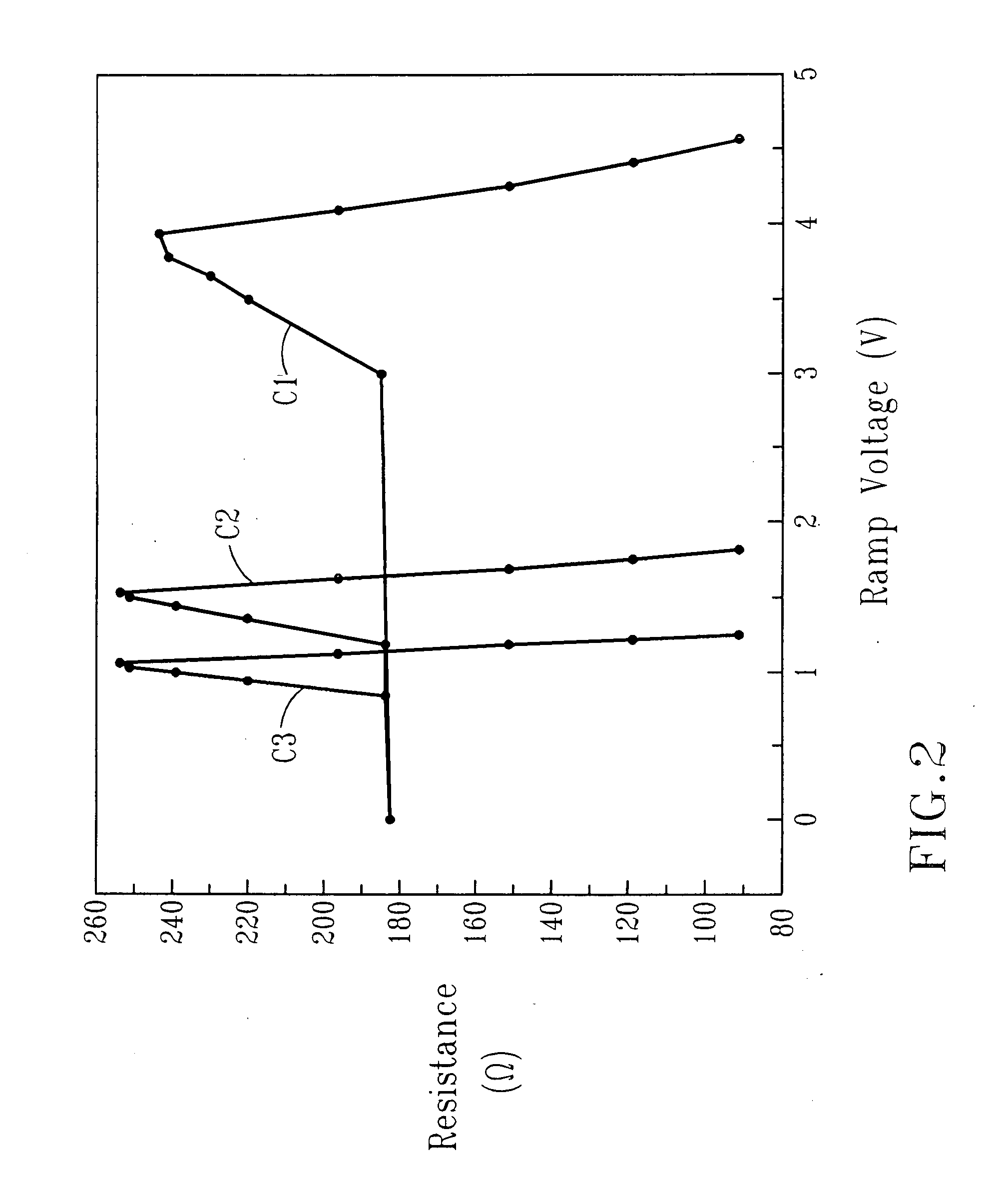

Phase-change TaN resistor based triple-state/multi-state read only memory

ActiveUS7381981B2Without consuming extra die surface areaIncrease information densitySolid-state devicesRead-only memoriesElectrical resistance and conductanceEPROM

The present invention relates to a nonvolatile memory such as, for example a ROM or an EPROM, in which the information density of the memory is increased relative to a conventional nonvolatile memory that includes two logic state devices. Specifically, the nonvolatile memory of the present invention includes a SiN / TaN / SiN thin film resistor embedded within a material having a thermal conductivity of about 1 W / m-K or less; and a non-linear Si-containing device coupled to the resistor. Read and write circuits and operations are also provided in the present application.

Owner:INT BUSINESS MASCH CORP

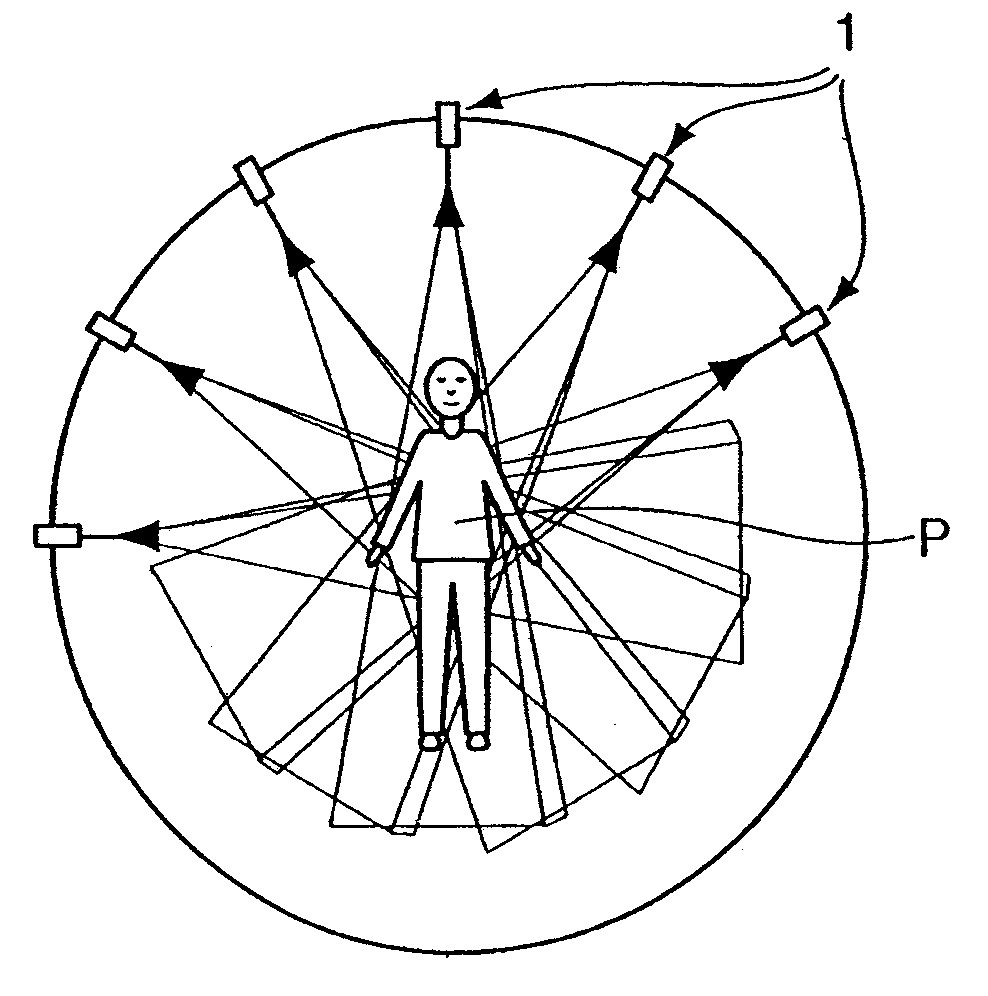

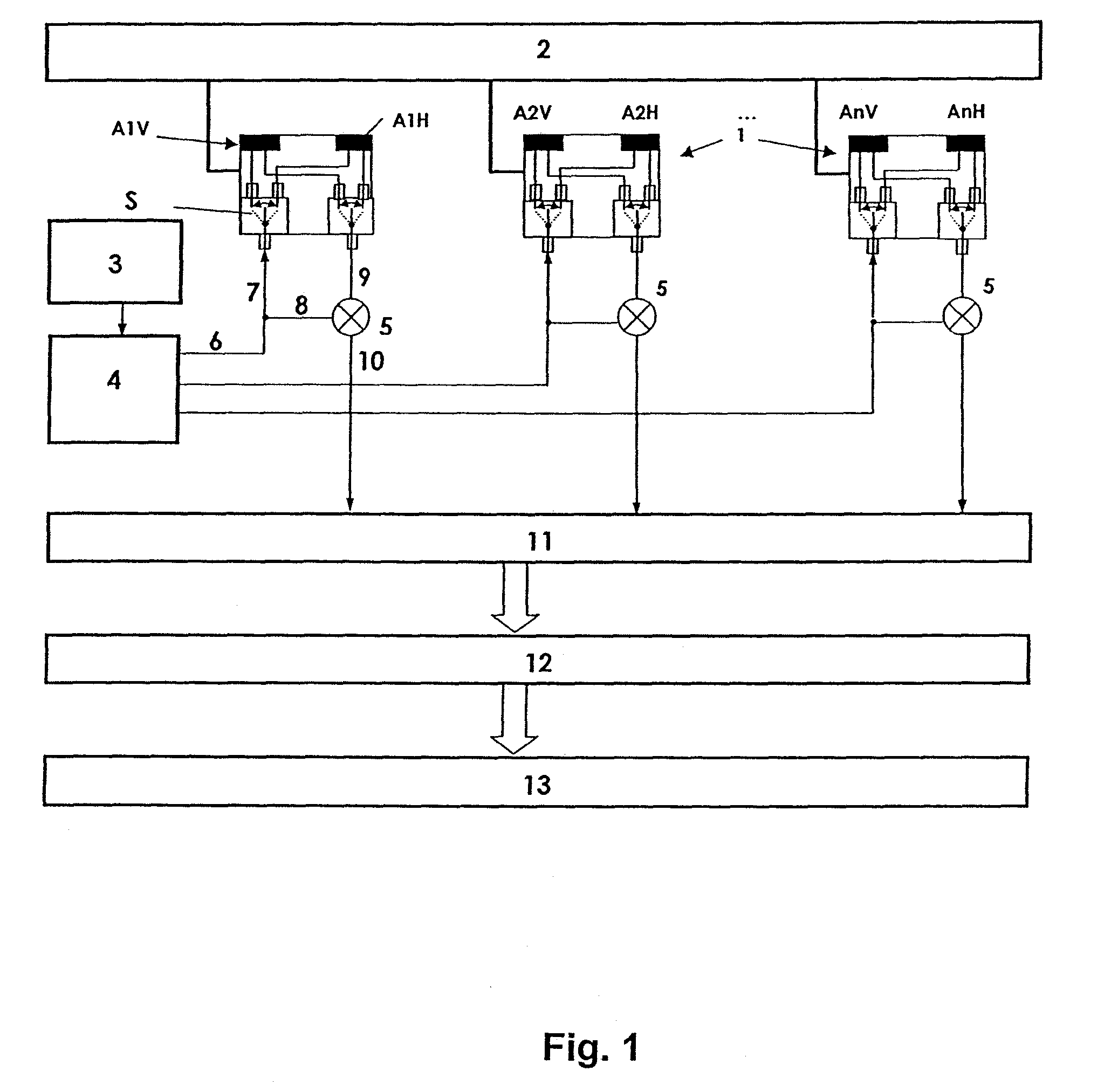

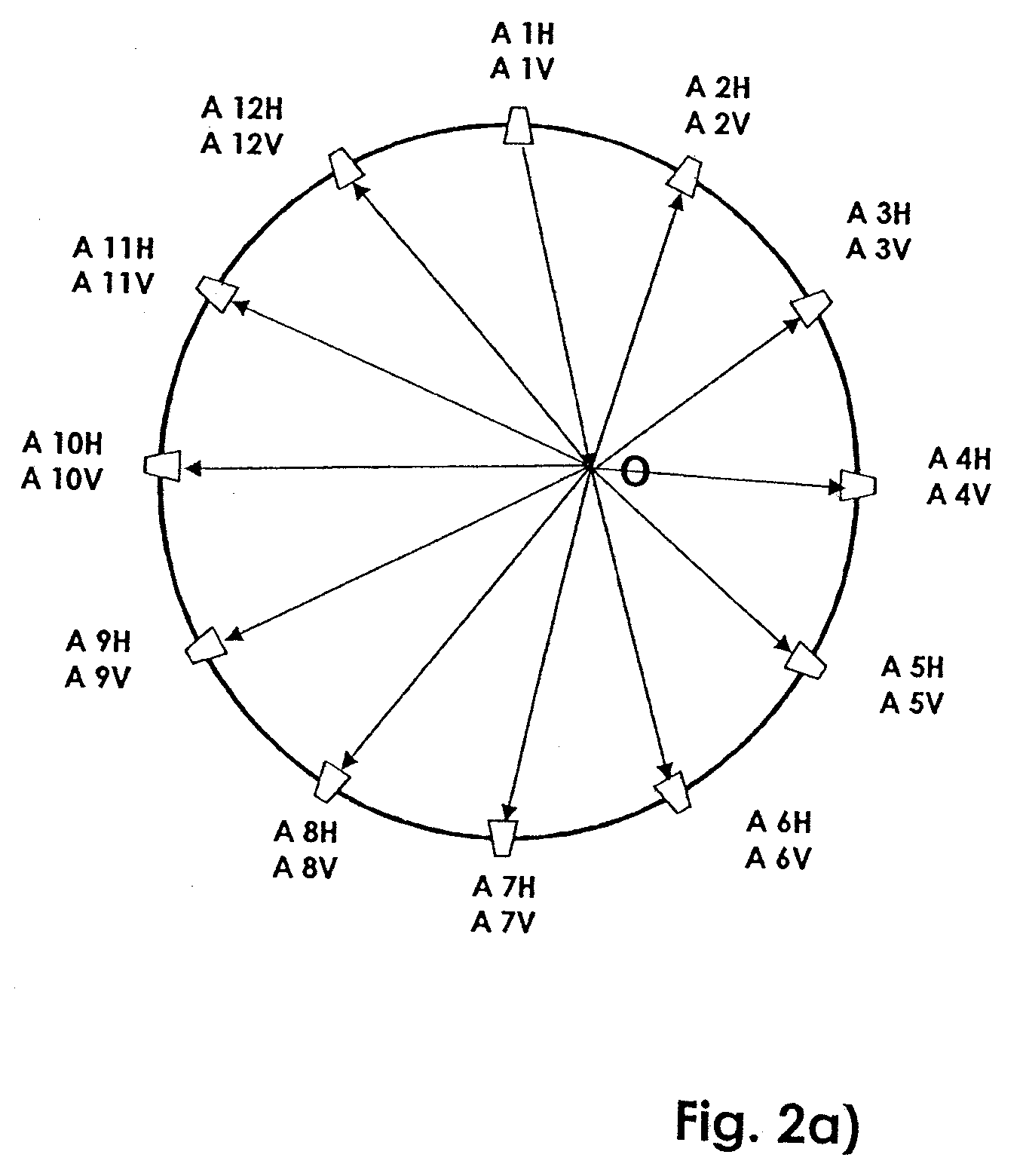

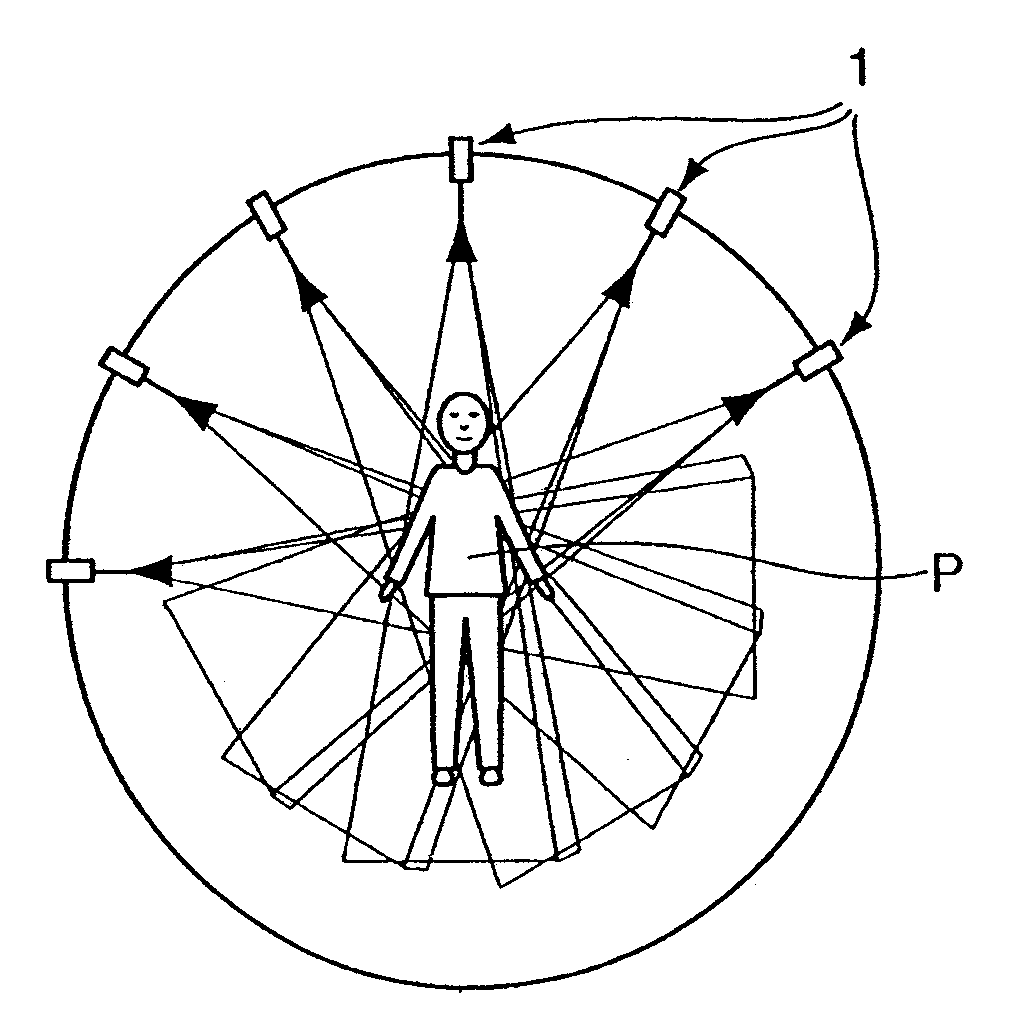

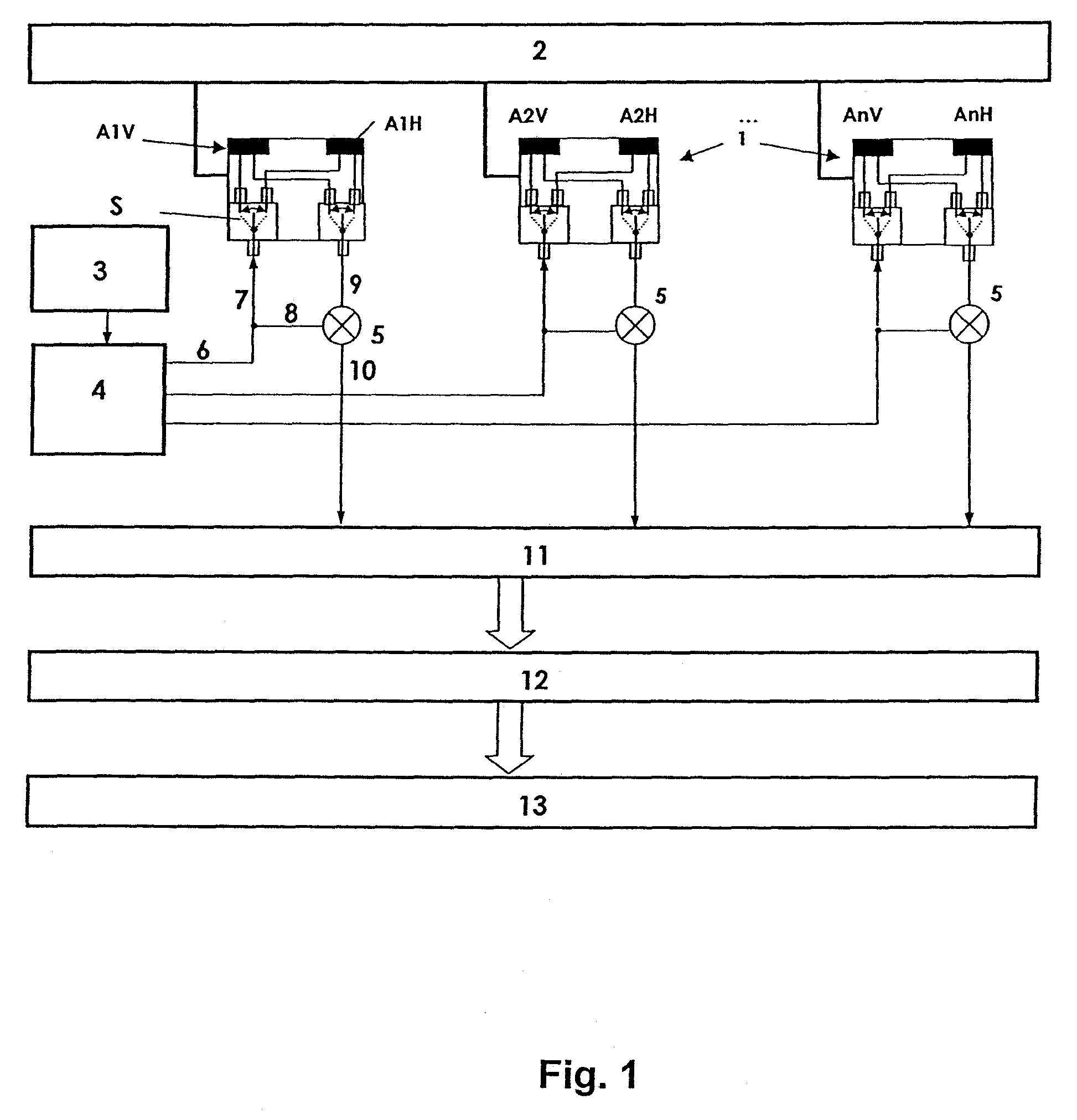

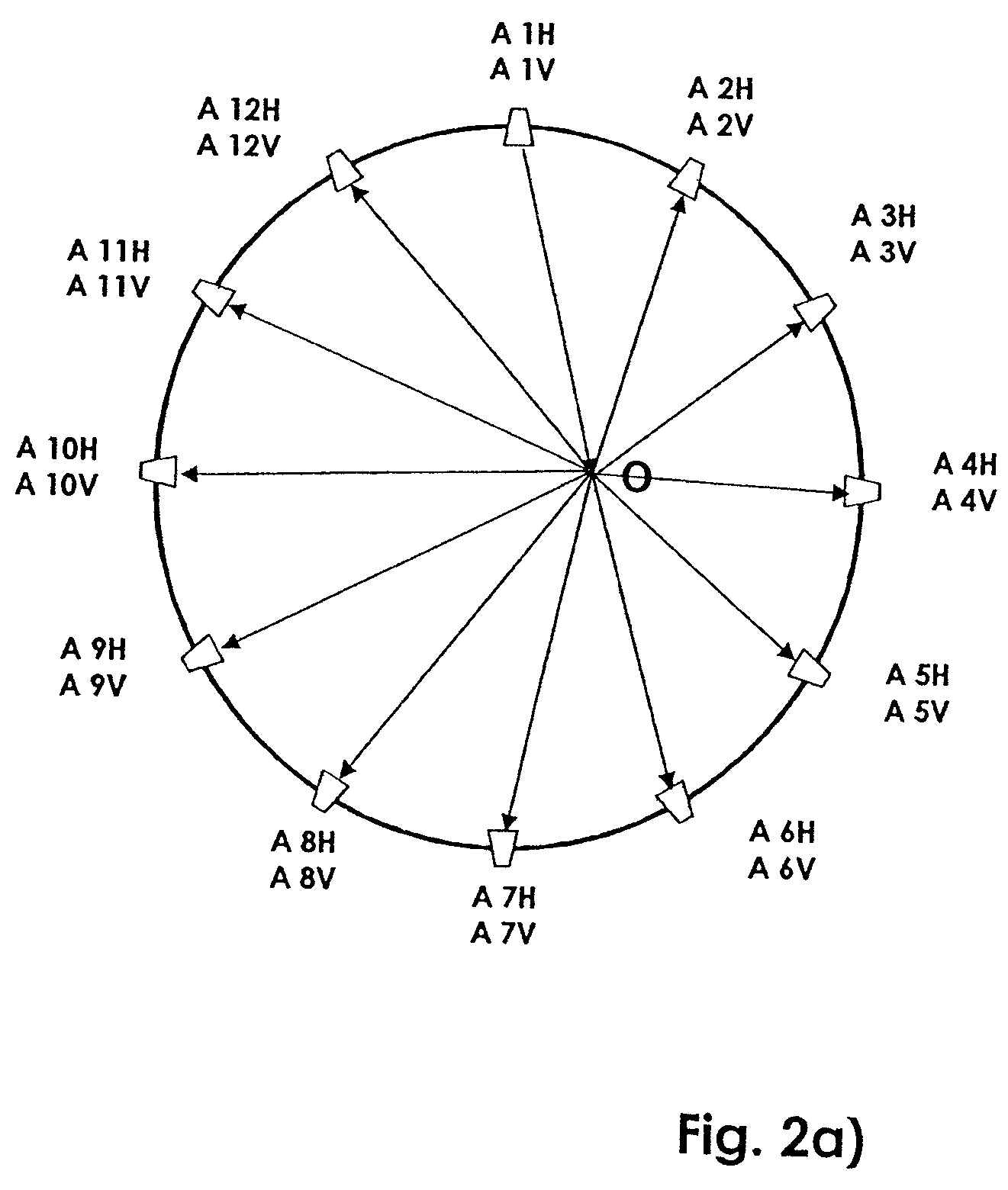

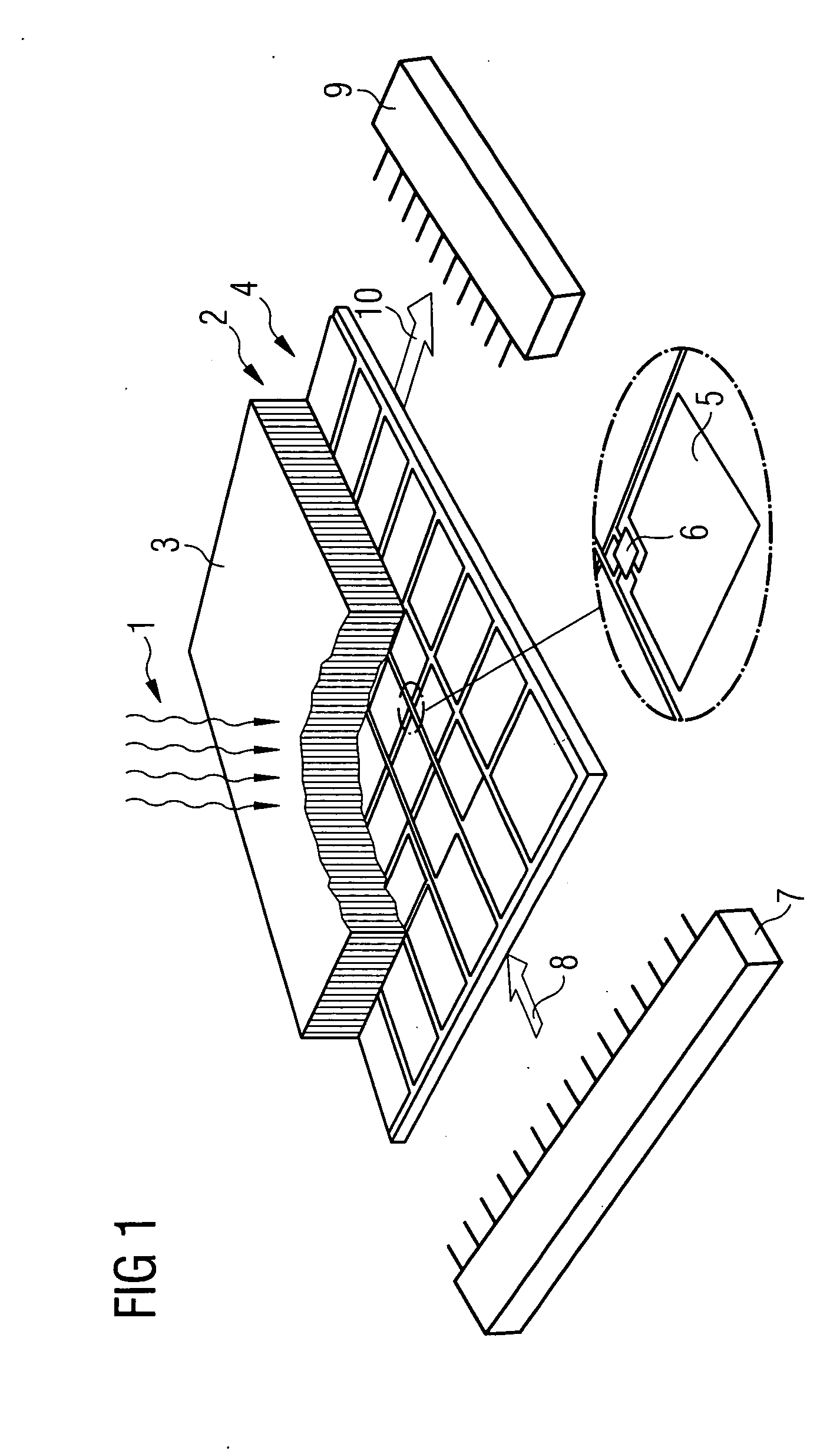

Method and Device For The Spatially Resolved Detection and Reconstruction of Objects By Means of Microwaves

InactiveUS20110050480A1Improve analysis accuracyIncrease information densityRadio wave reradiation/reflectionSpatially resolvedImage resolution

A method and a device for the spatially resolved detection and reconstruction of objects using microwaves is described, in which at least one object to be detected is subjected to microwaves that are generated by a plurality of microwave antennas and microwave fractions reflected by the object are detected and converted into microwave signals that can be analyzed, based on which an analysis for the spatially resolved object detection is carried out.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

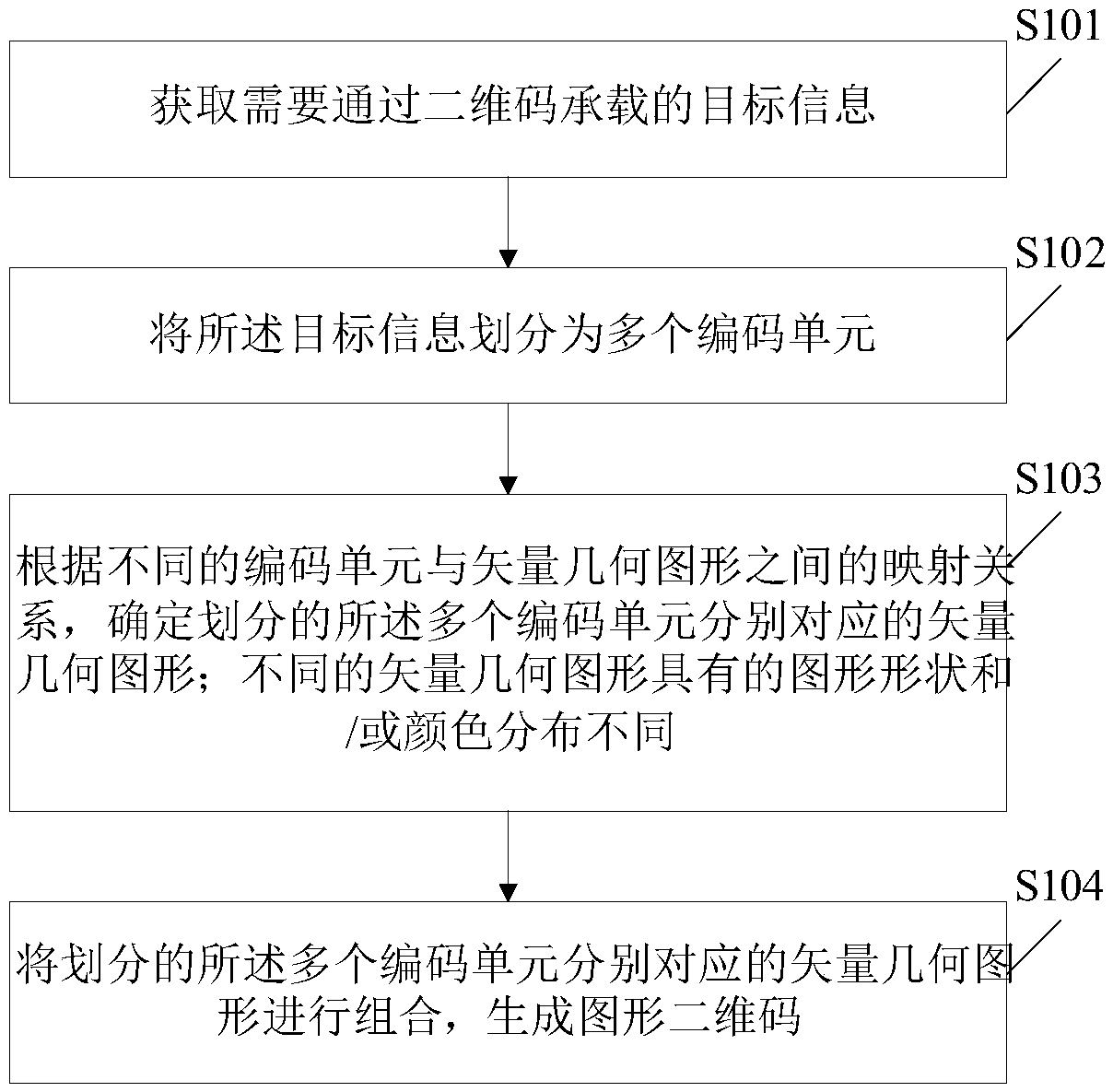

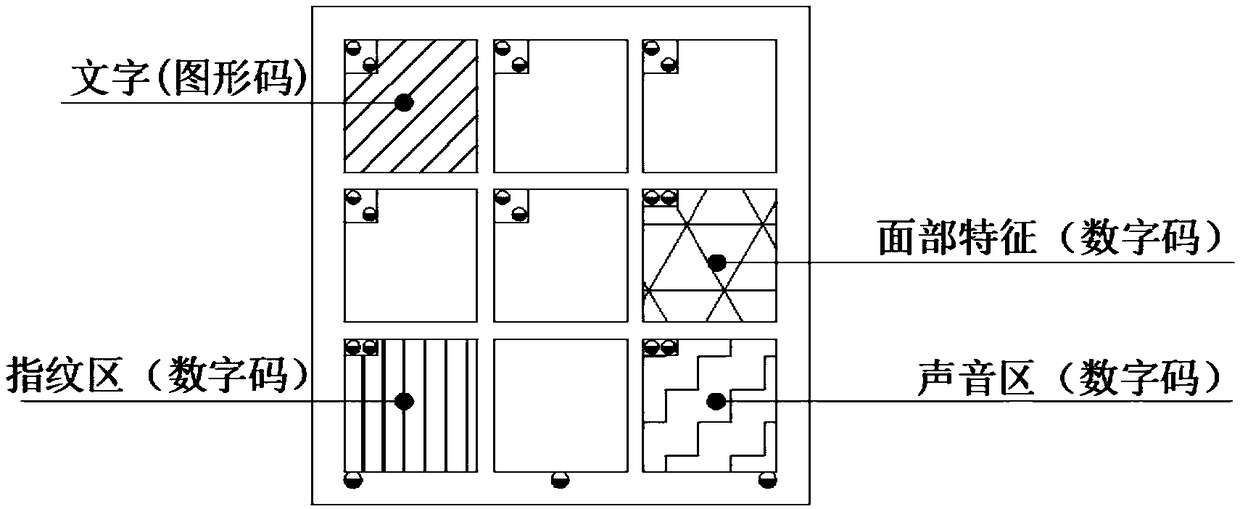

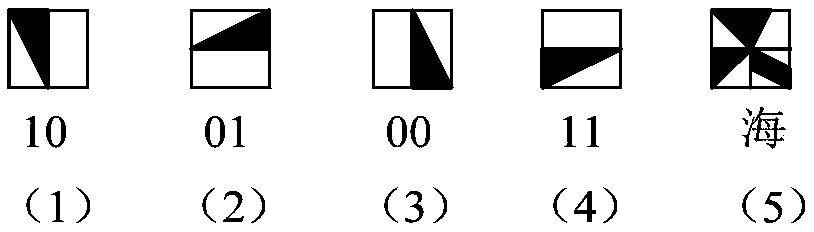

Two-dimensional code generation method and device, and electronic equipment

ActiveCN108710932AIncrease information capacityReduce restrictionsRecord carriers used with machinesInformation technologyGraphics

The invention relates to the technical field of information, in particular to a two-dimensional code generation method. The method comprises the following steps that: obtaining target information which needs to be borne by a two-dimensional code; dividing the target information into a plurality of coding units; according to a mapping relationship between different coding units and vector geometricfigures, determining the vector geometric figures independently corresponding to the plurality of divided coding units, wherein different vector geometric figures have different figure shapes and / orcolor distribution; and combining vector geometric figures independently corresponding to the plurality of divided coding units to generate a figure two-dimensional code. The invention also providesa two-dimensional code generation device and electronic equipment.

Owner:周冰

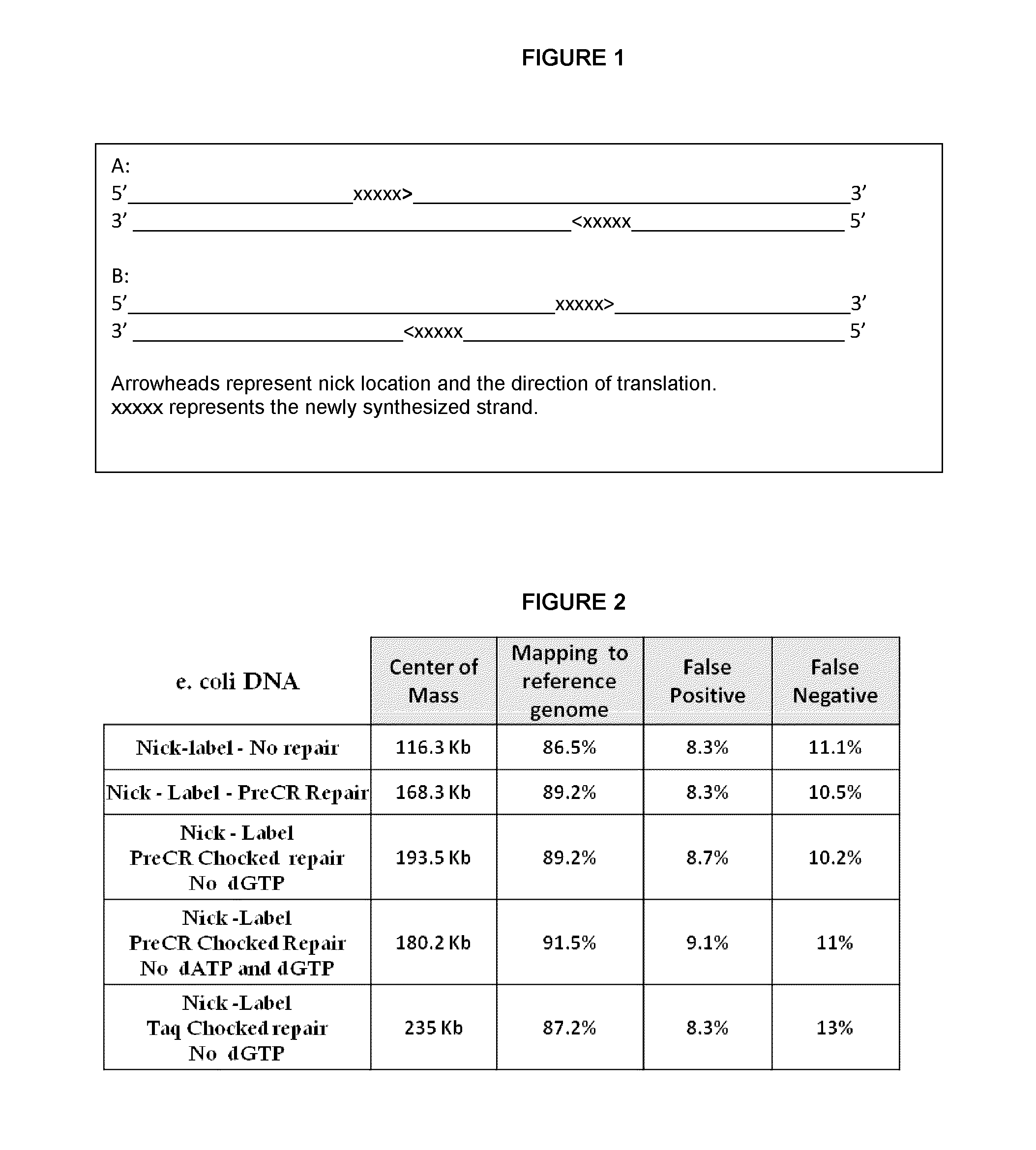

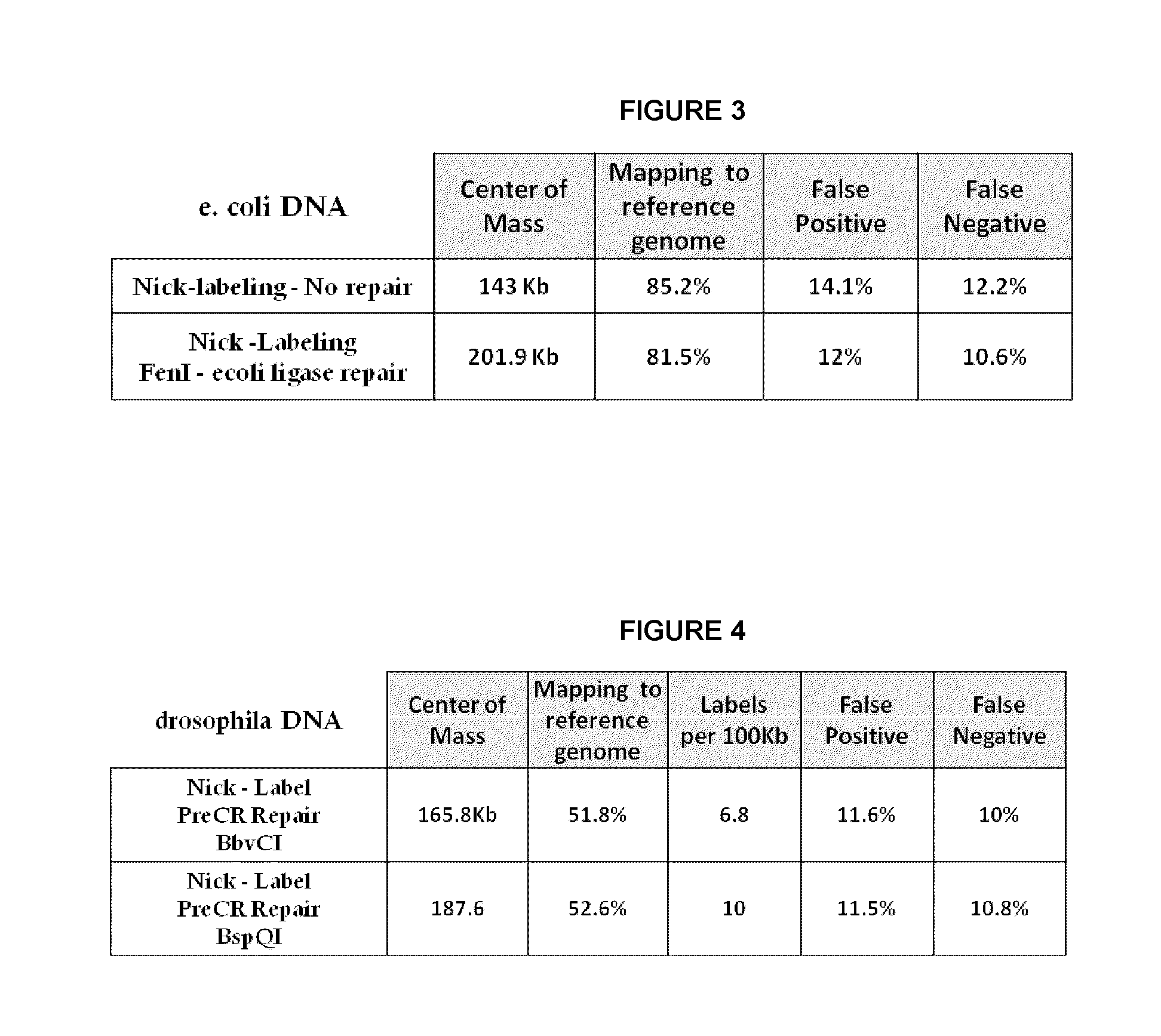

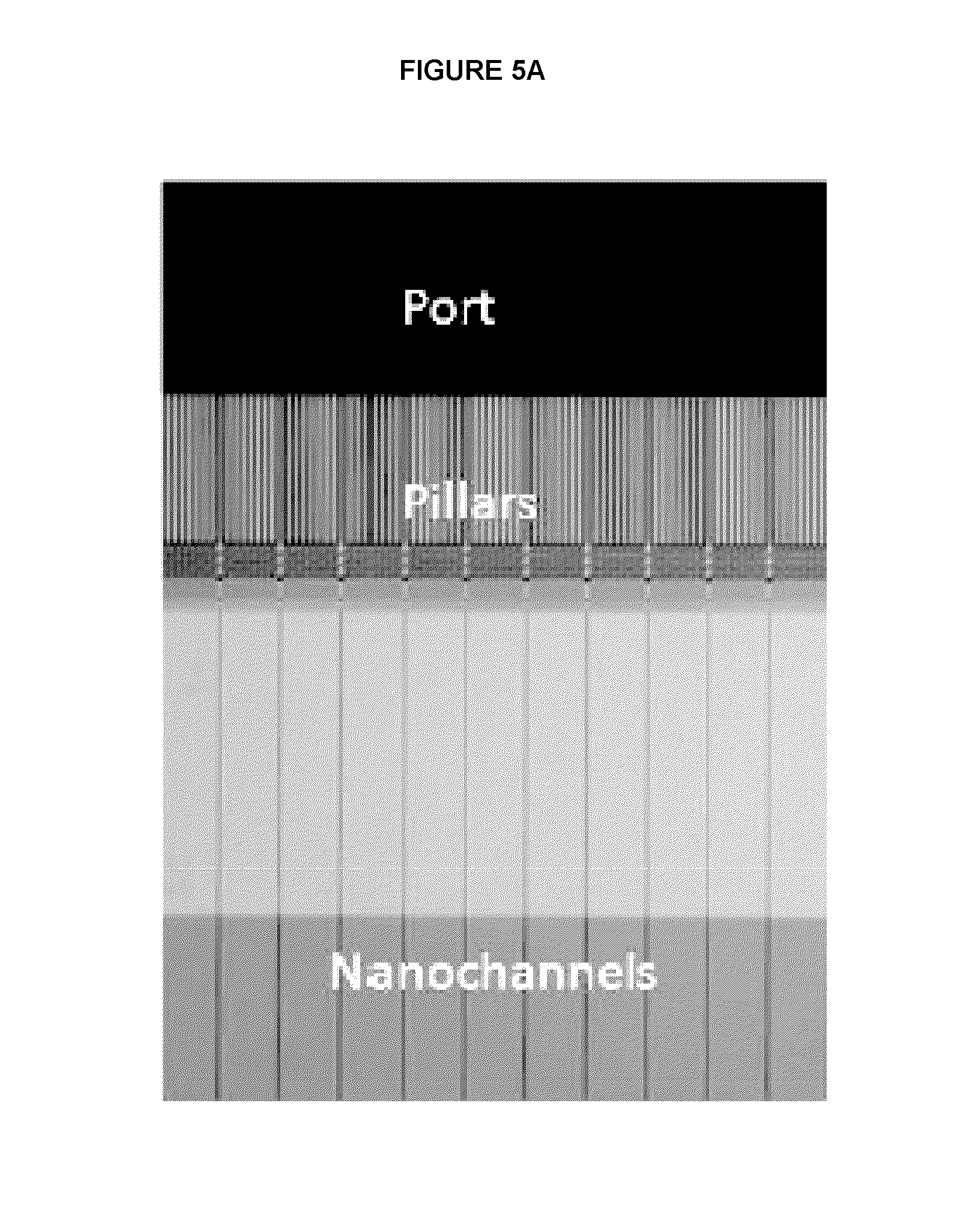

Methods for single-molecule analysis

InactiveUS20140221218A1Reduce effectImprove information densityMicrobiological testing/measurementLibrary member identificationAnalysis methodDNA

Methods for single-molecule preparation and analysis are disclosed herein. The methods can, for example, be used for isolating and analyzing DNA from various biological samples.

Owner:BIONANO GENOMICS

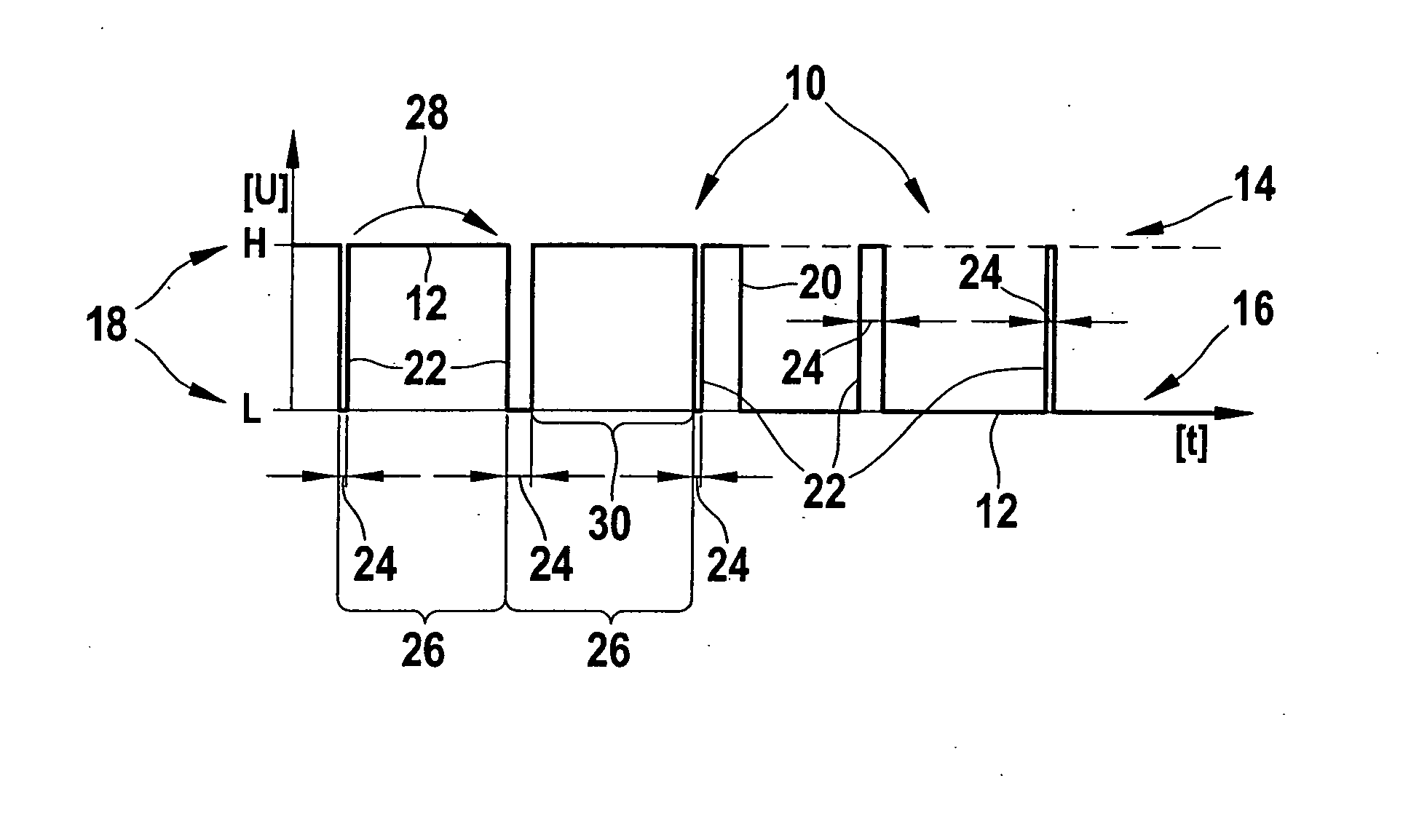

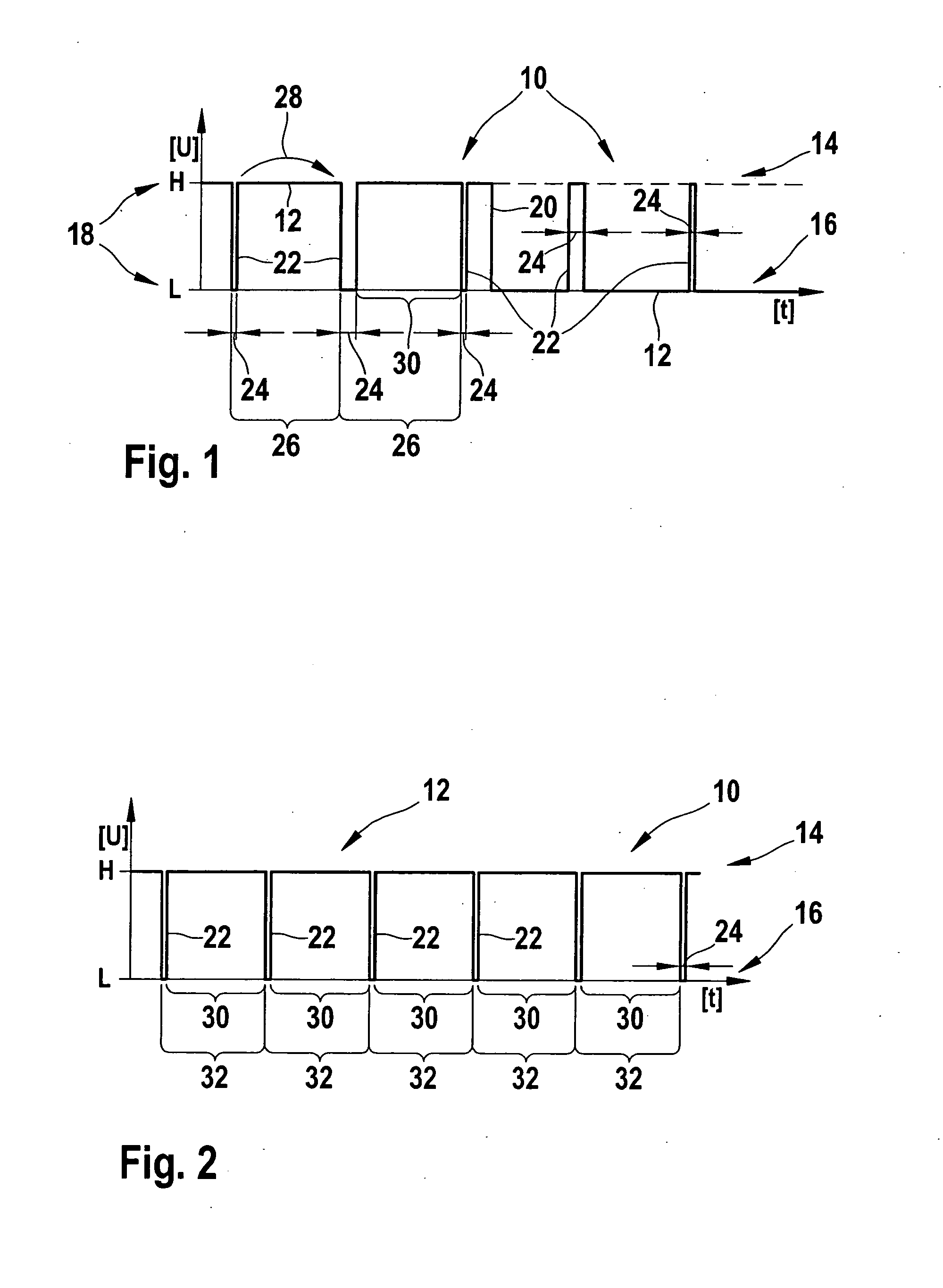

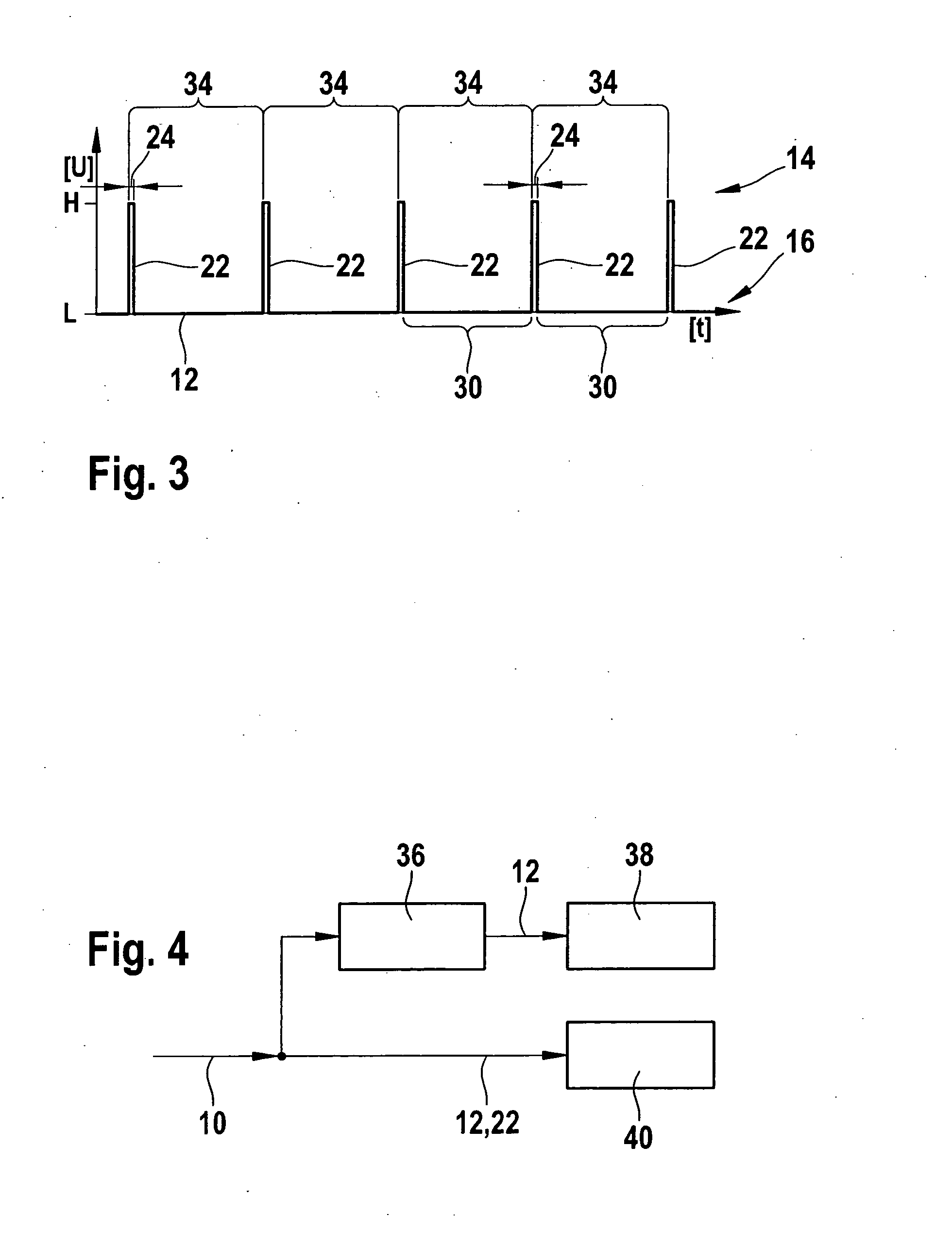

Method for increasing the information density in signal-transmission lines

InactiveUS20070177321A1Increase information densityHigh densityArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentPulse frequencyPulse duration

A method for increasing the information density on a signal-transmission line. The signal-transmission line extends from a sensor to a control unit. A modulated signal, which includes a digital signal, is transmitted on the signal-transmission line. The digital signal assumes either a high level or a low level. The modulated signal includes an encoded pulse signal, which is superimposed on the digital signal and has both an encoded pulse duration and a variable pulse frequency.

Owner:ROBERT BOSCH GMBH

Method and device for the spatially resolved detection and reconstruction of objects by means of microwaves

InactiveUS8248293B2Improve analysis accuracyIncrease information densityRadio wave reradiation/reflectionSpatially resolvedMicrowave signals

A method and a device for the spatially resolved detection and reconstruction of objects using microwaves is described, in which at least one object to be detected is subjected to microwaves that are generated by a plurality of microwave antennas and microwave fractions reflected by the object are detected and converted into microwave signals that can be analyzed, based on which an analysis for the spatially resolved object detection is carried out.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

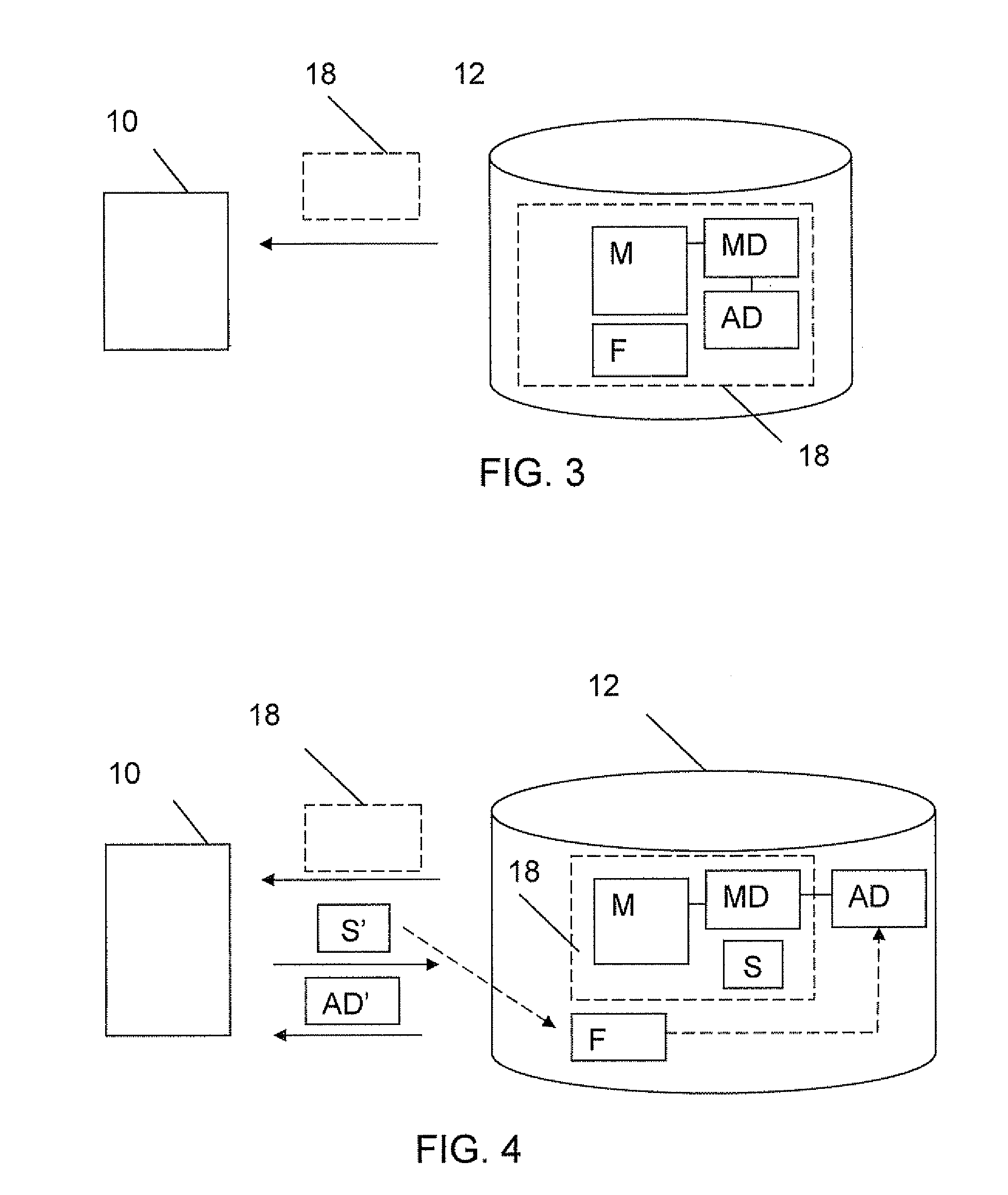

Enhanced use of map and map metadata

InactiveUS20070233734A1Increase information densityHigh densityNavigational calculation instrumentsDigital data processing detailsComputer scienceElectronic map

An electronic map together with metadata relating to at least one position on the map is provided for a user. A pointer to additional data related to the metadata may also be provided based on the reception of a selection of additional information according to a user made selection profile. In this way, additional data can be presented together with the metadata on the map and the density associated with information on the map may be increased.

Owner:SONY ERICSSON MOBILE COMM AB

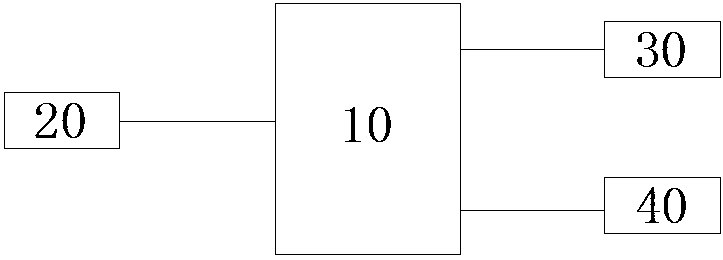

Online jewel leasing method, online jewel leasing system and business model

InactiveCN107609936AEliminate the pitfalls of leasingIncrease information densityBuying/selling/leasing transactionsHigh densityOperability

The invention relates to an online jewel leasing method, an online jewel leasing system and a business model. The system includes a user terminal, a server, a delivery terminal, and a return terminal.According to the online jewel leasing method, the online jewel leasing system and the business model of the invention, jewelry, a special item, is leased by combining an online mode and an offline mode, and fast information flow, high density of information and quick online payment of the online mode and high operability of real object observation and inspection and good visual property of the offline mode are respectively utilized. Therefore, the property safety of both the lessor and the lessee is guaranteed, and the defects of the existing jewelry leasing are eliminated. The online jewel leasing method, the online jewel leasing system and the business model have a good application prospect and broad market potential.

Owner:秦伏尹 +1

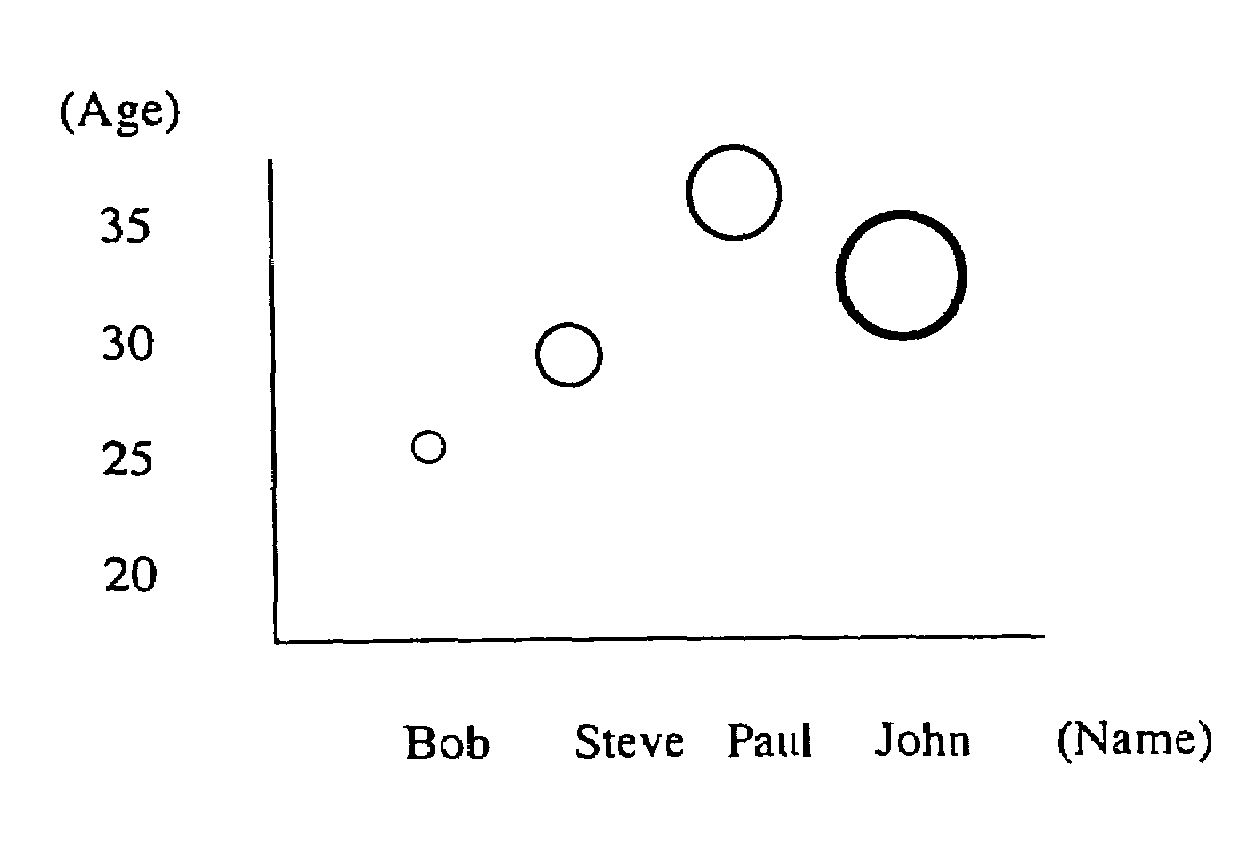

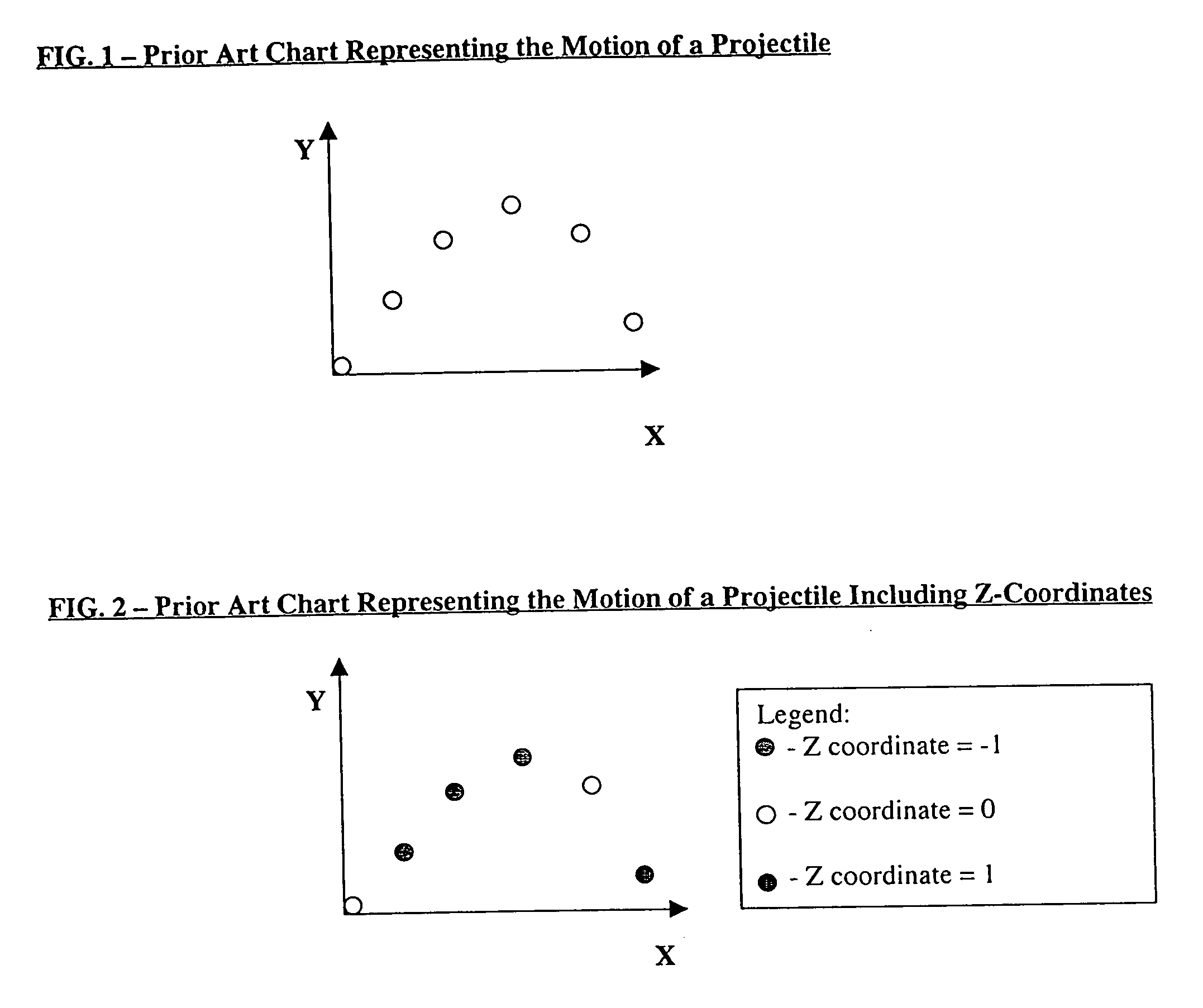

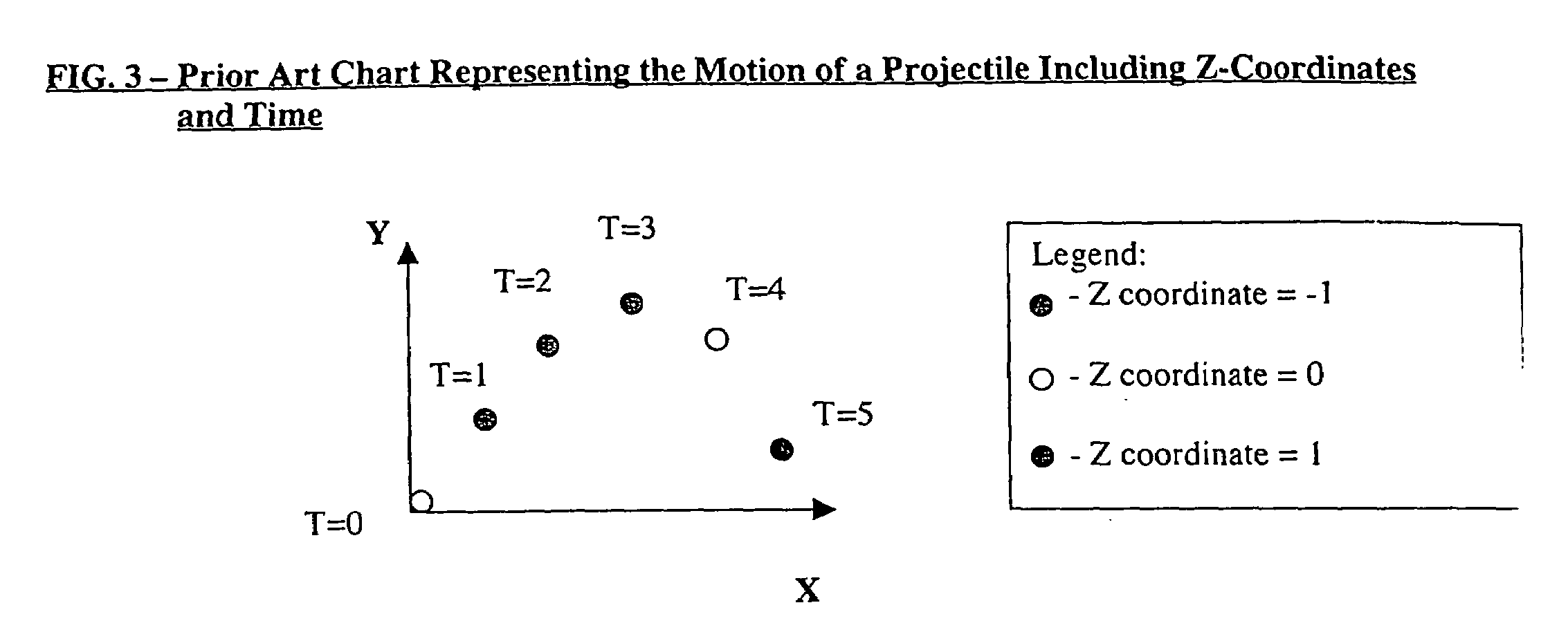

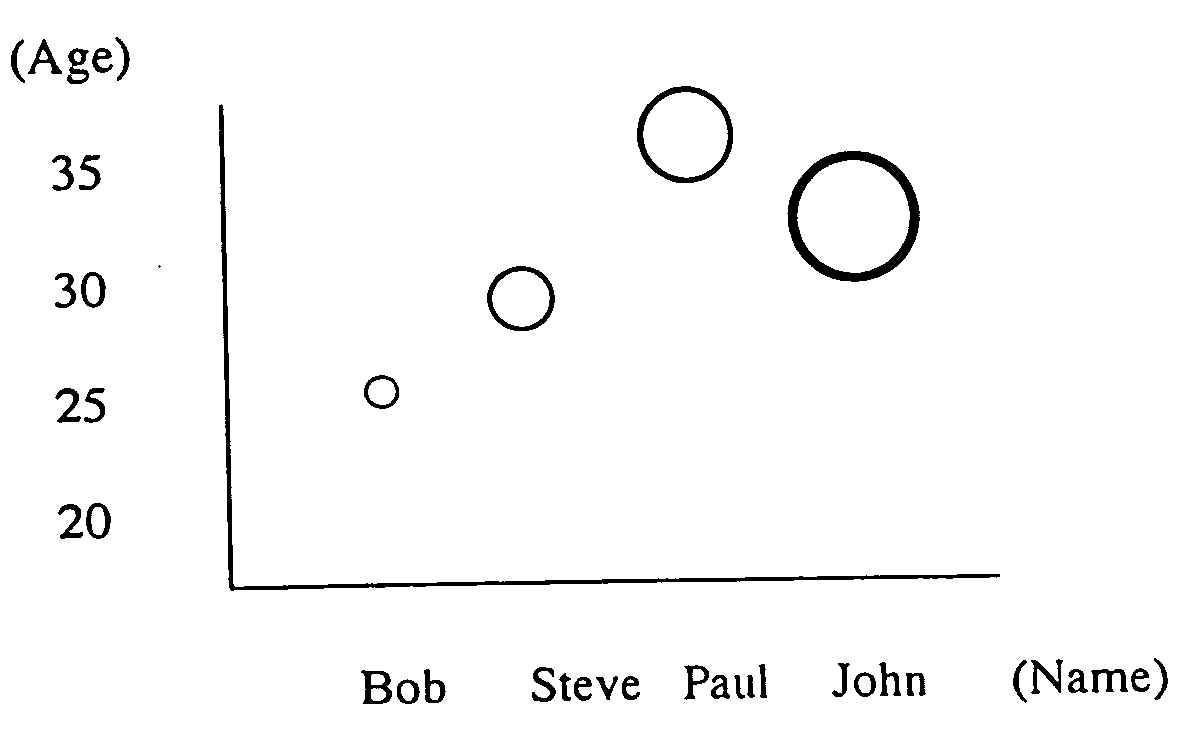

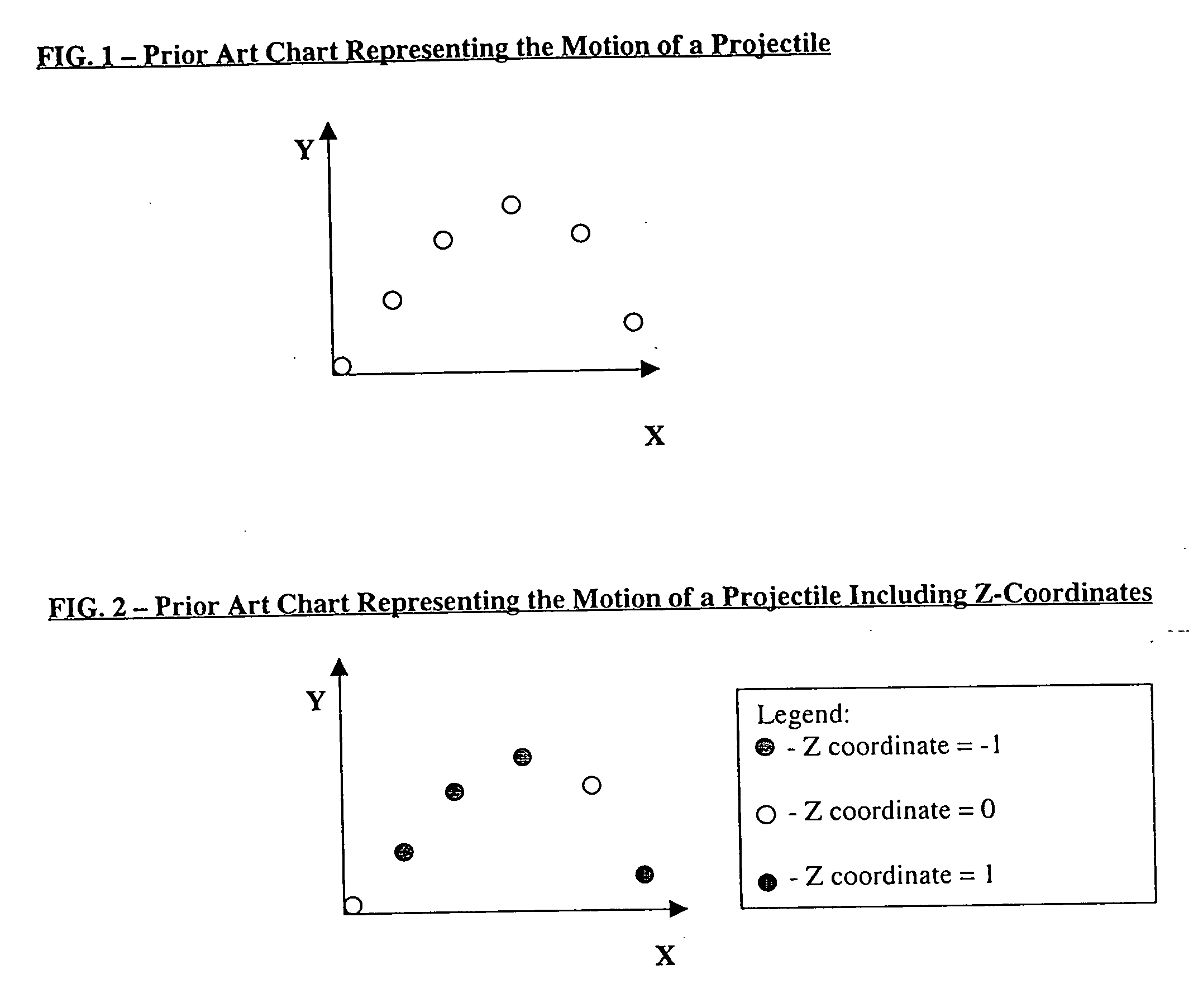

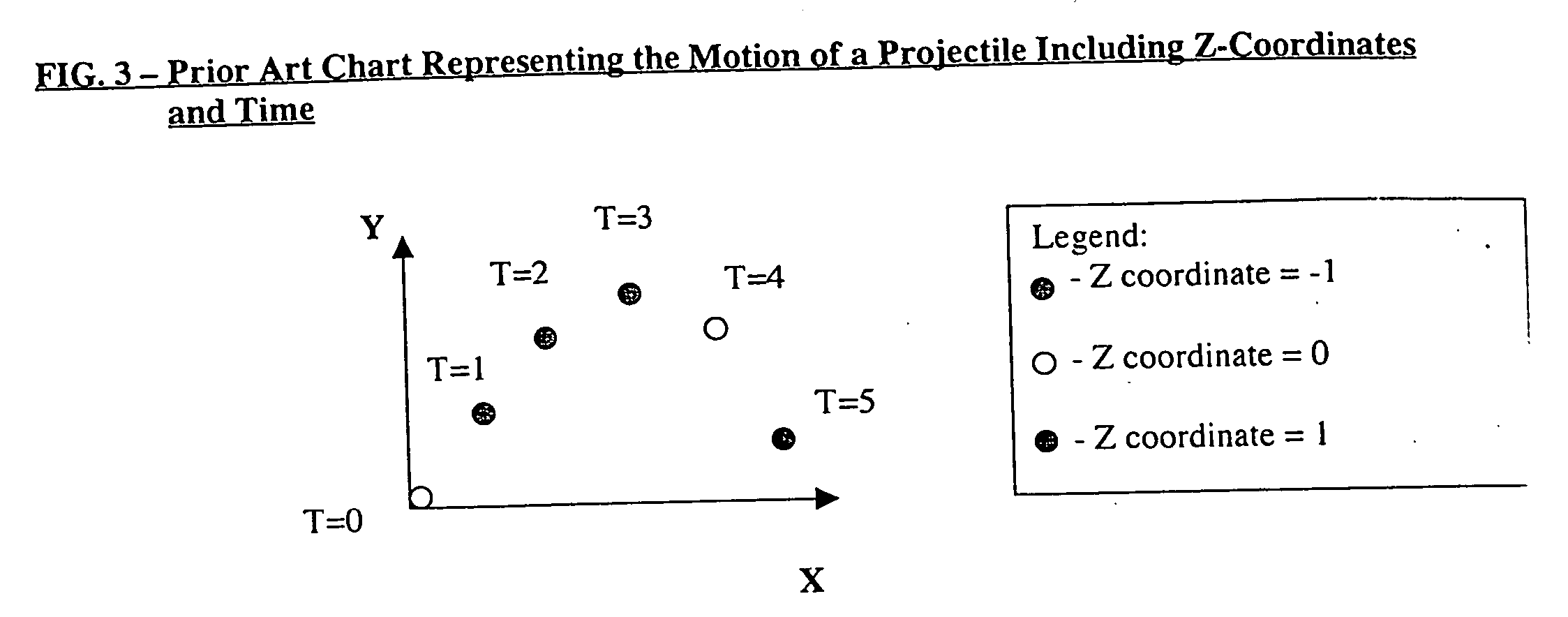

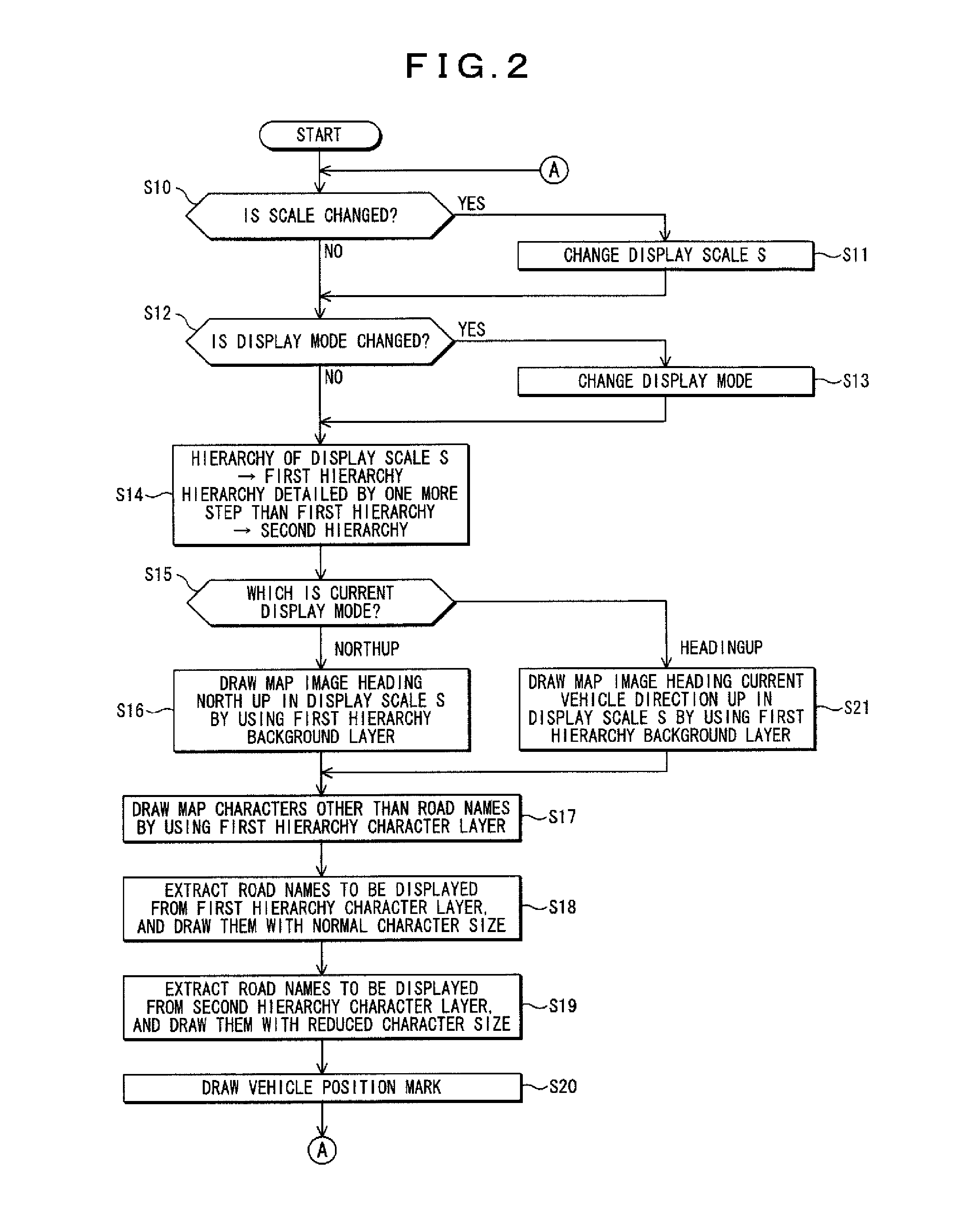

Formatting object for modifying the visual attributes of visual objects to reflect data values

InactiveUS7176925B2Increase information densityDrawing from basic elementsMultiple digital computer combinationsComputer graphics (images)Boundary values

A formatting object according to the present invention conveys information to the reader of a document (such as a table or chart) by associating visual attributes (such as color, fill type, border width, line width, line style, font size, marker size and marker type) to characters or markers within the document. The formatting object may be used to emphasize data within a table or a chart by modifying the structural visual attributes of characters or markers within the table or chart according to pre-defined criteria. Similarly, the formatting object may be used to increase information density within a table or chart, and to elegantly represent the relationships between four or more interrelated variables in a two-dimensional chart. The formatting object accomplishes this by defining at least one format map that comprises one or more mapping segments. Each mapping segment includes a beginning boundary value, an ending boundary value, at least one beginning visual attribute corresponding to the beginning boundary value, and at least one ending visual attribute corresponding to the ending boundary value. The formatting object uses the information within the format maps, in combination with interpolation techniques, to determine one or more visual attributes that correspond to data points falling within the various mapping segments. The formatting object then expresses the data values by applying the appropriate visual attribute to a visual object displayed on a computer screen.

Owner:MICROSOFT TECH LICENSING LLC

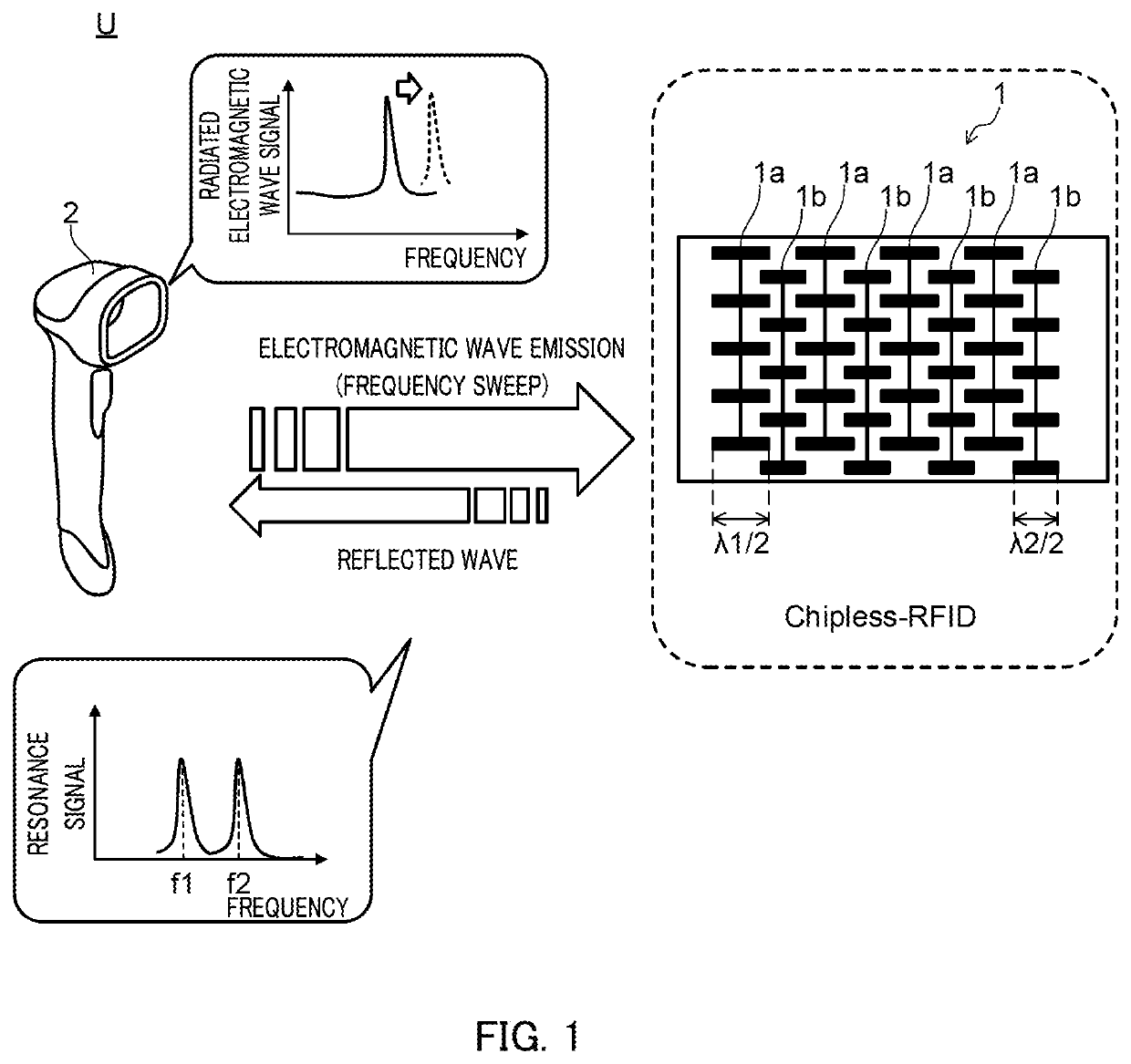

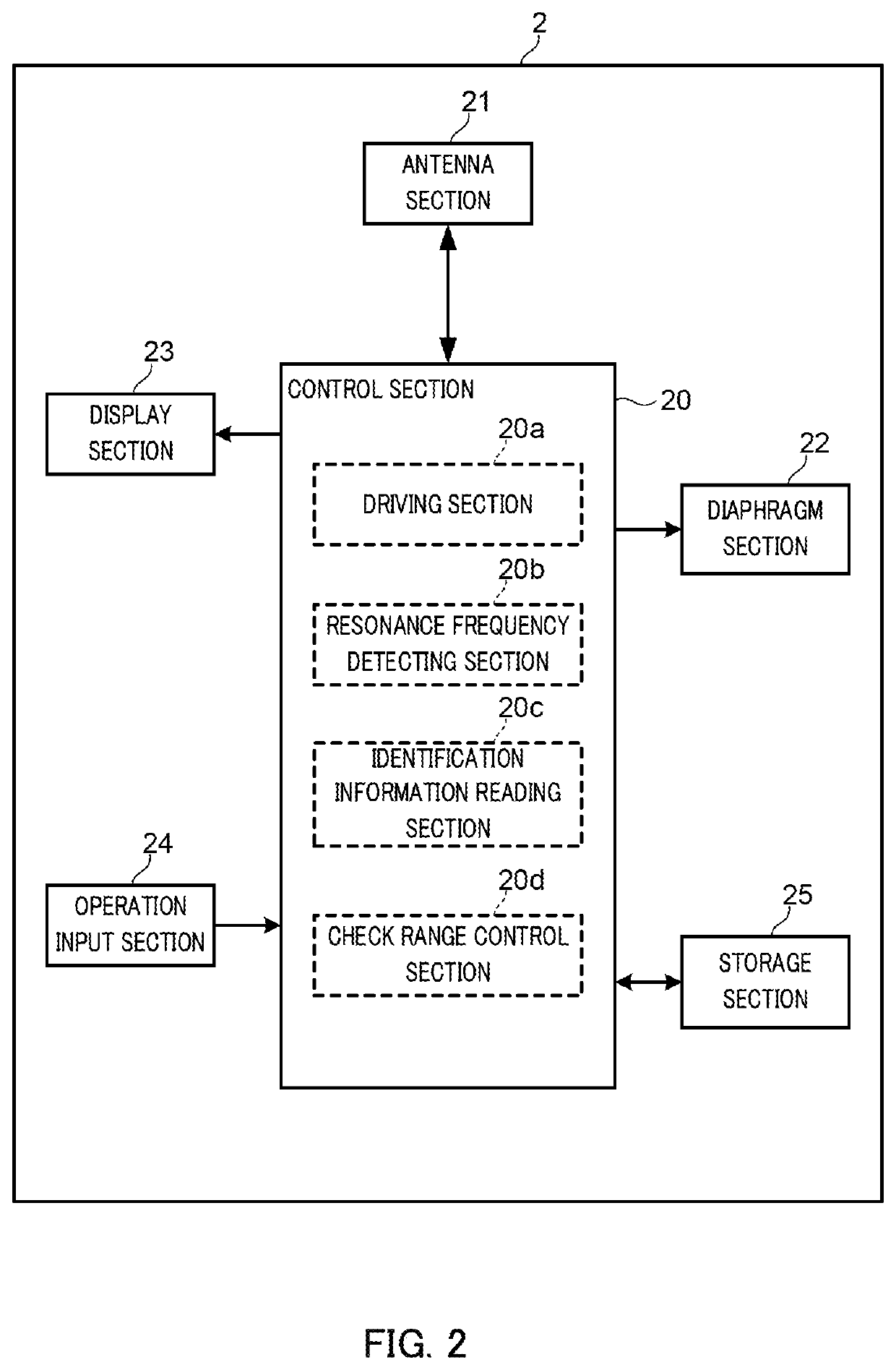

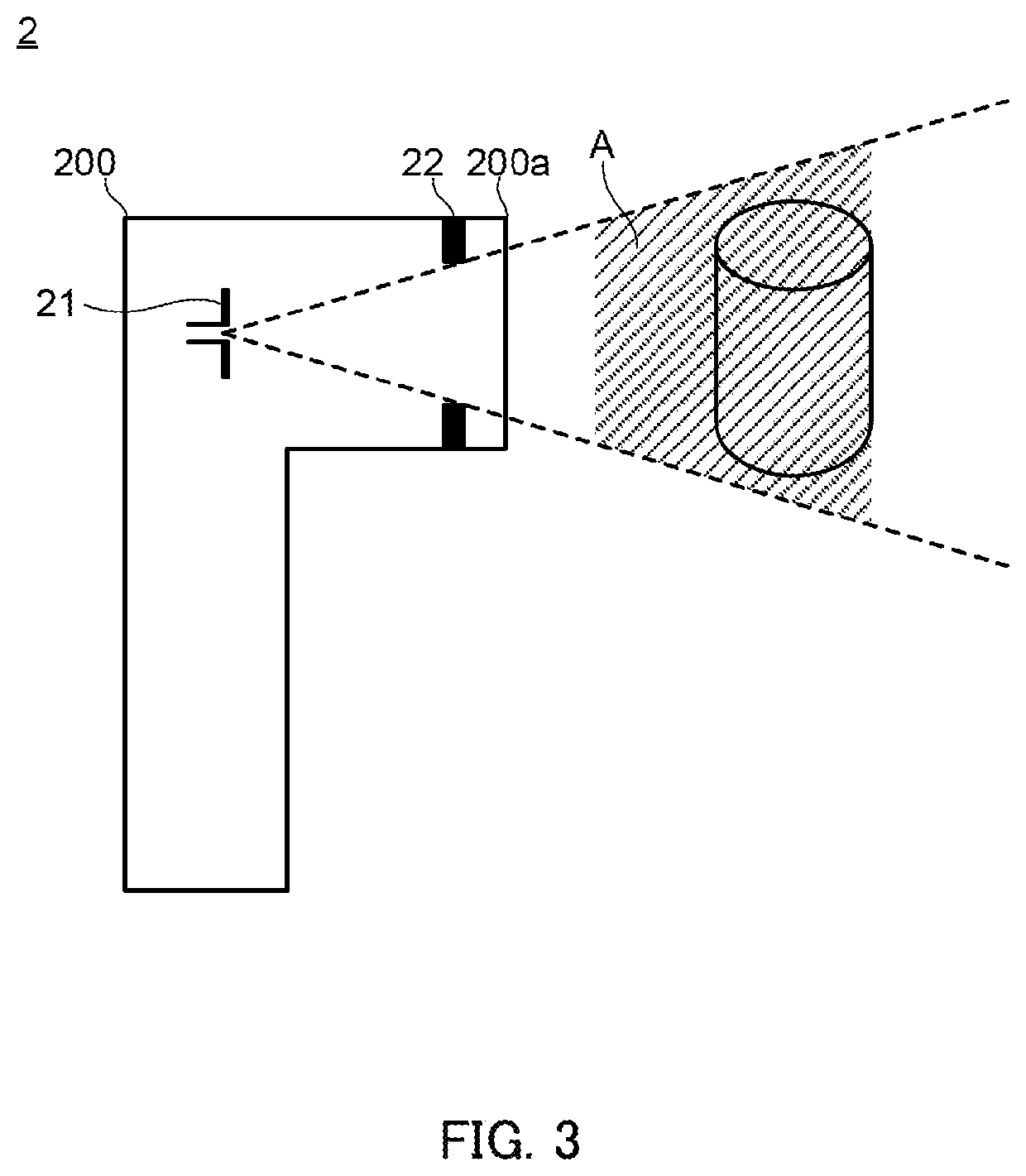

Tag Reader, RFID System, and Method for Reading Identification Information

ActiveUS20200250387A1Increase information densityImprove accuracyRecord carriers used with machinesAntennasChipless RFIDEngineering

This tag reader can be applied to a chipless RFID tag having a plurality of resonance frequencies that are associated with identification information. The tag reader is provided with: a radiation unit that radiates electromagnetic waves within a predetermined millimeter wave or microwave frequency band so as to cause sweeping of the radiation frequency; and a detection unit that detects the plurality of resonance frequencies of a chipless RFID tag on the basis of the reflection characteristics of waves reflected from the chipless RFID tag when the electromagnetic waves are radiated.

Owner:KONICA MINOLTA INC

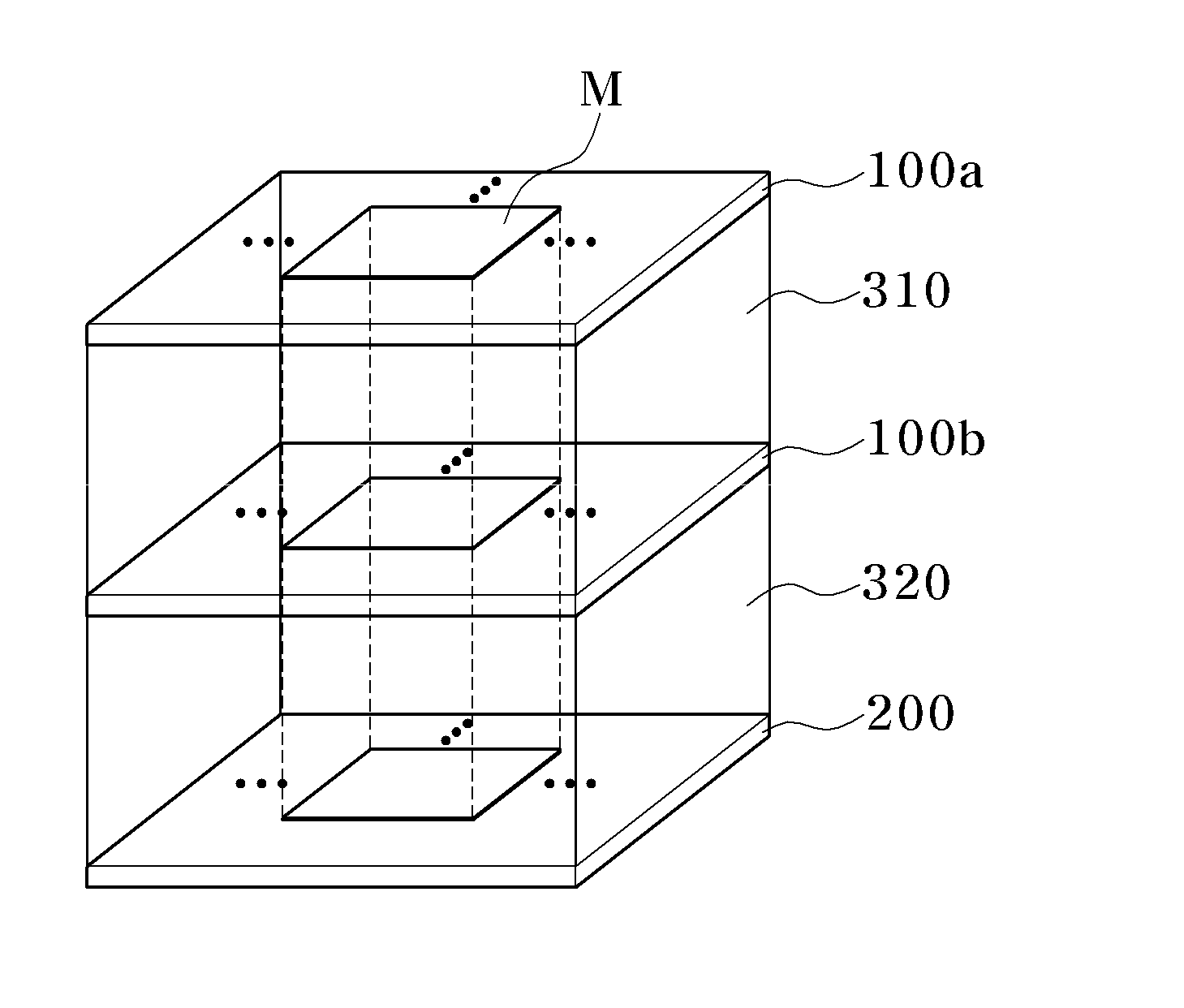

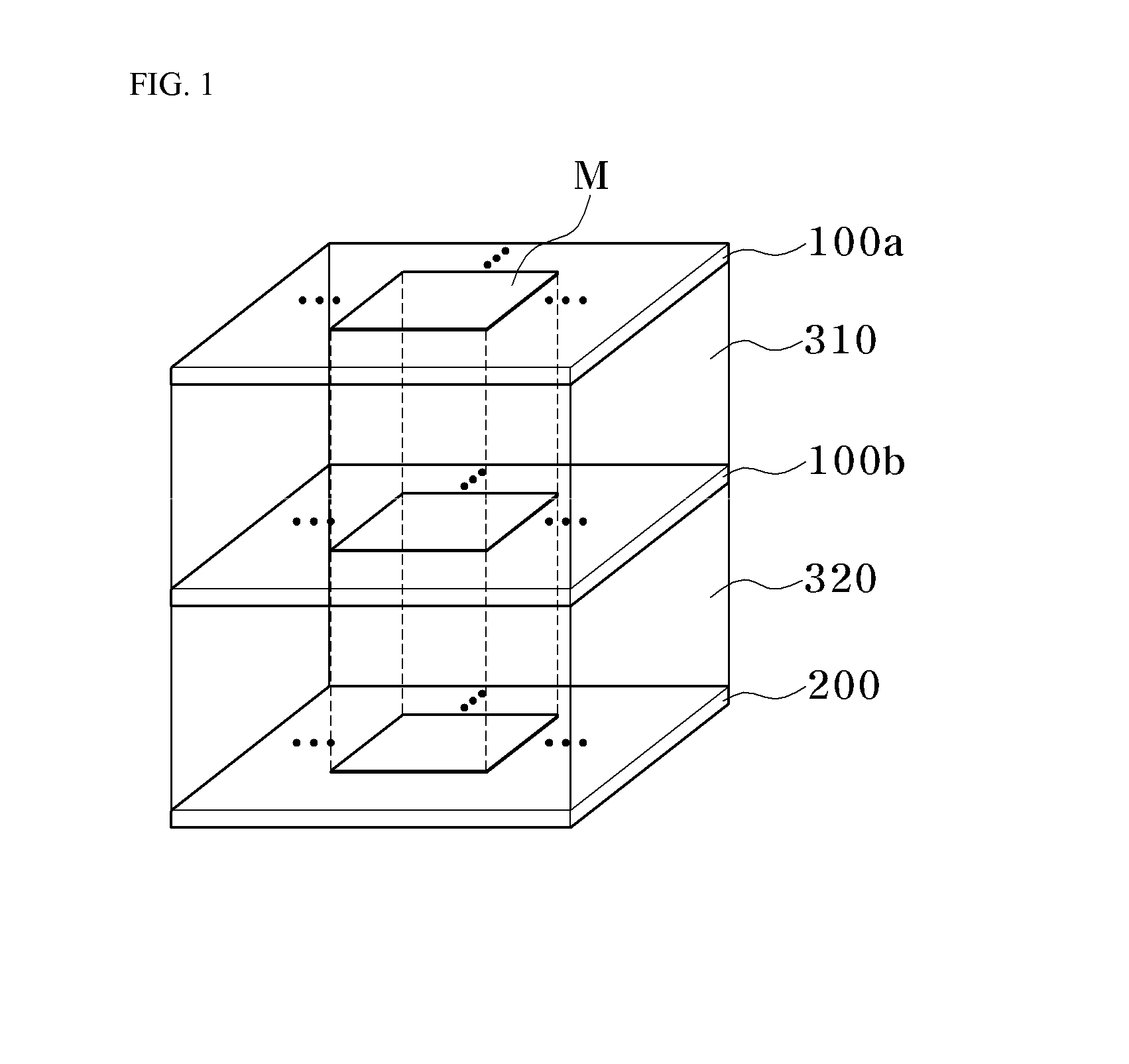

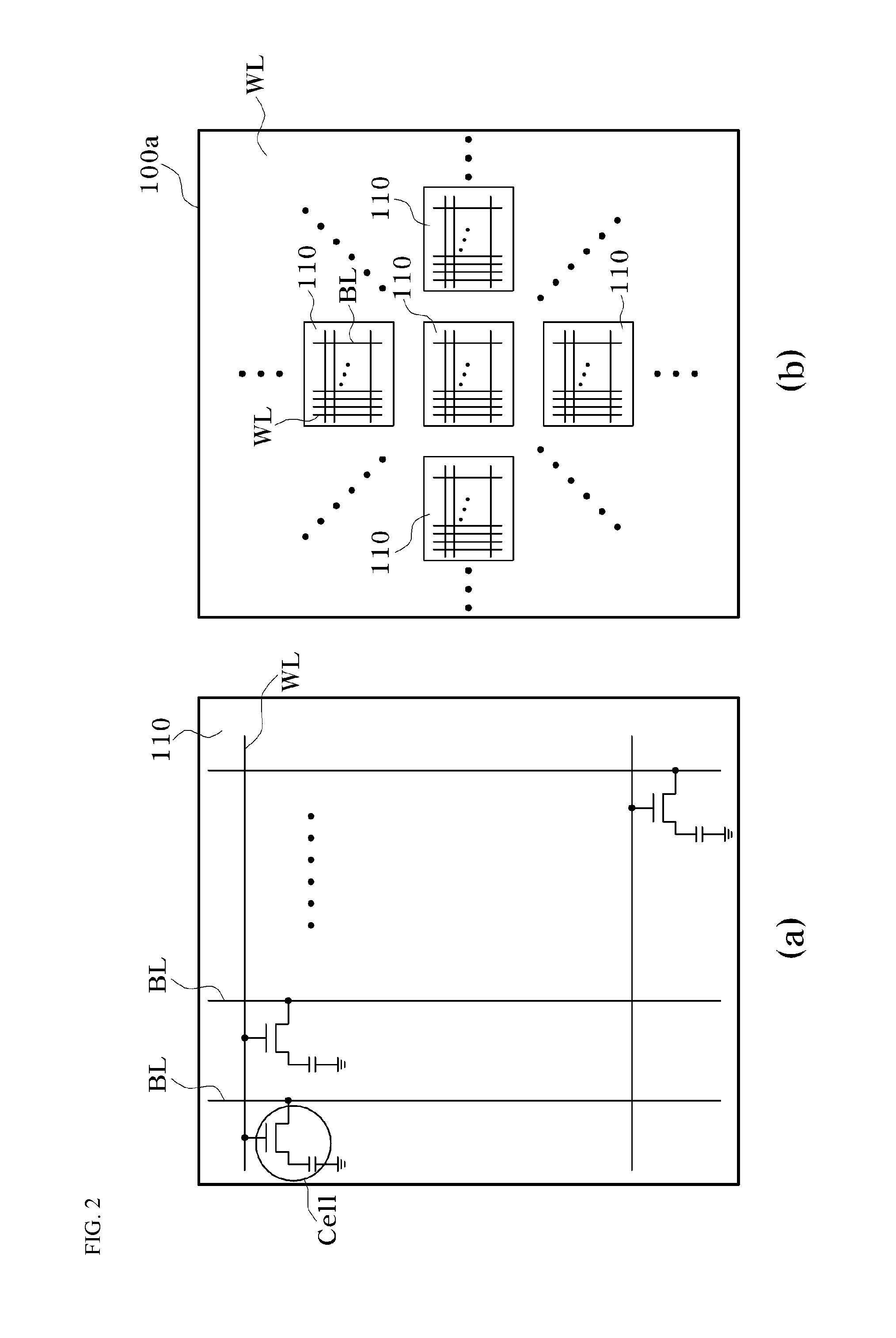

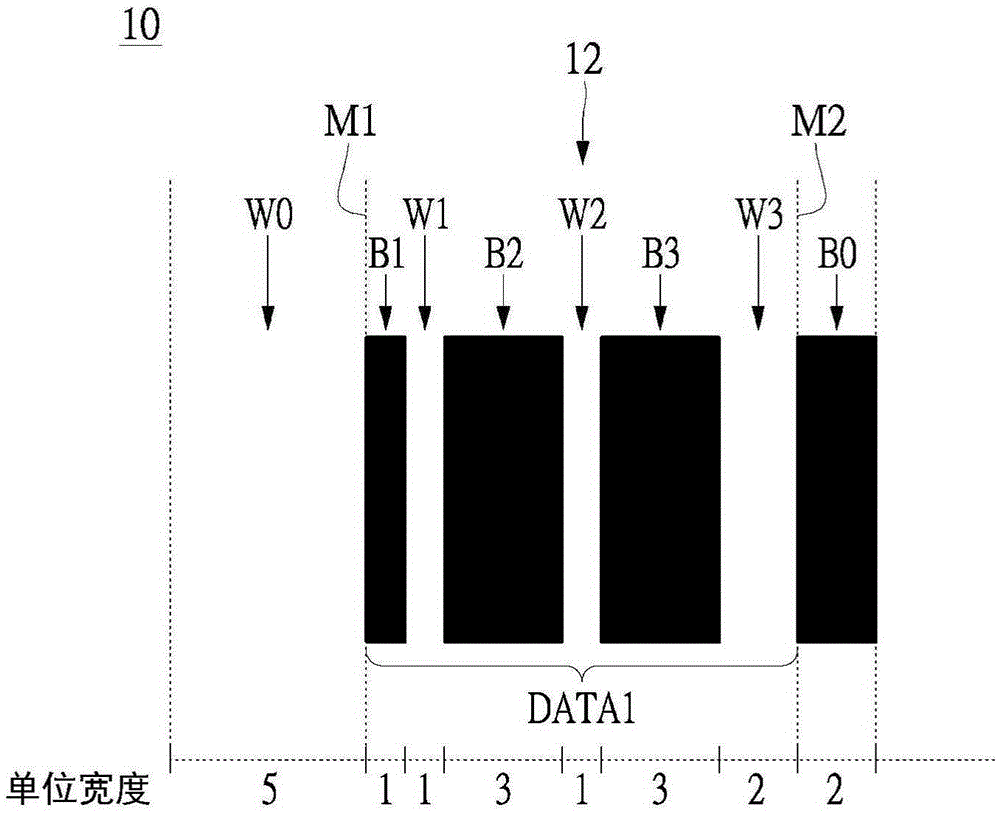

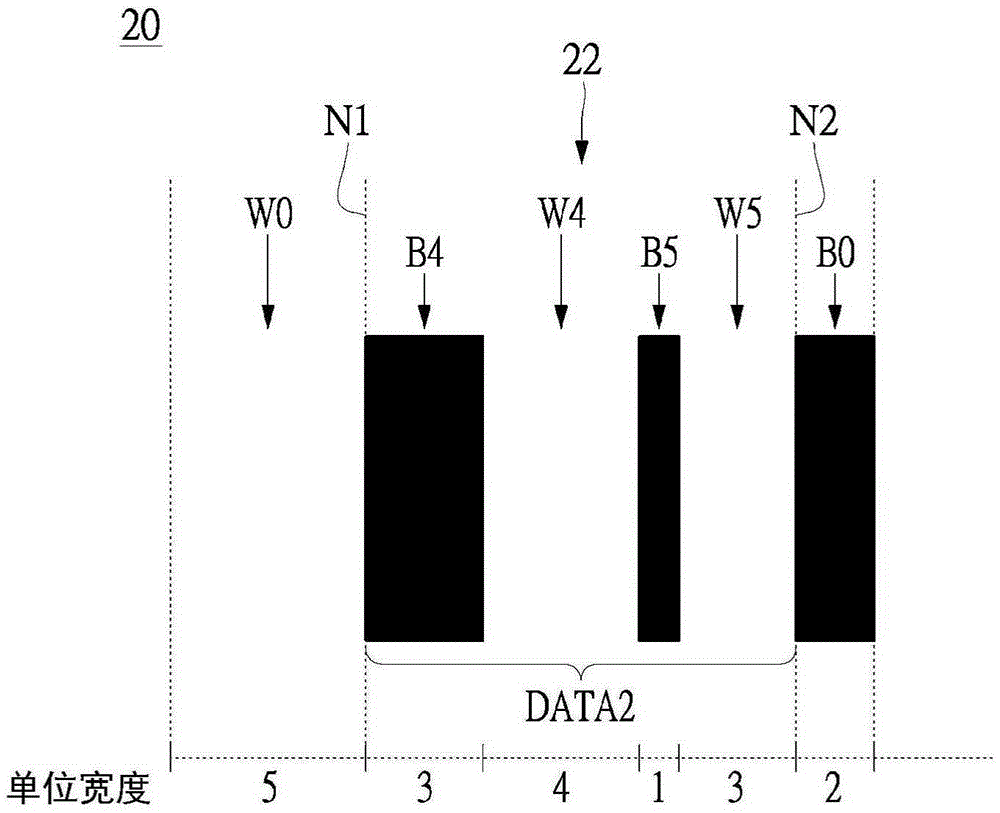

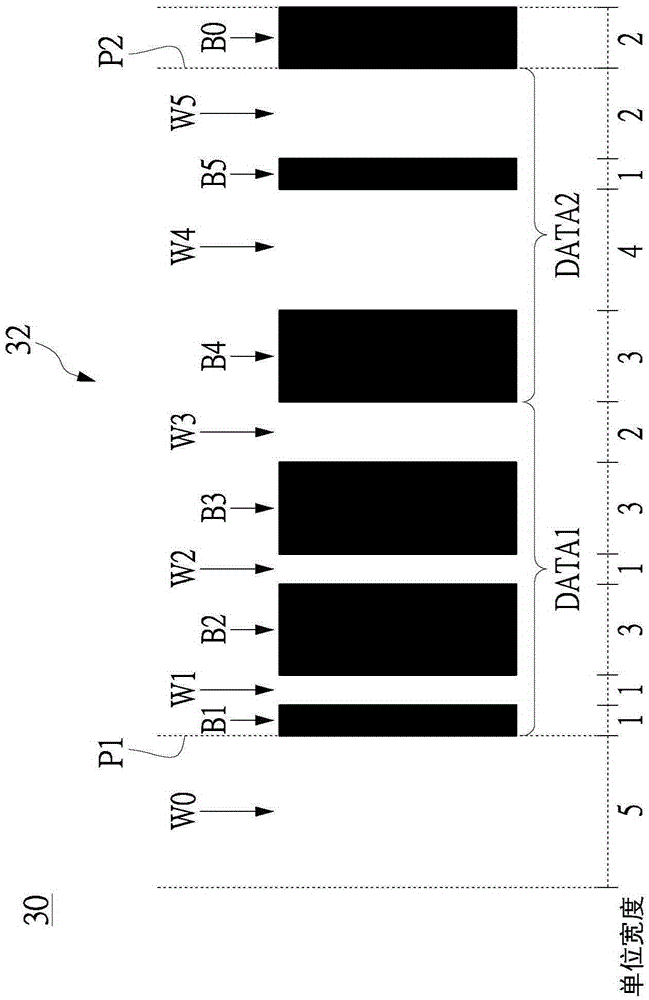

Stacked dynamic random access memory

ActiveUS20140119090A1High densityIncrease demandDigital storageStatic random-access memoryAudio power amplifier

A memory includes at least one first substrate on which unit memory arrays are disposed as a matrix type, each unit memory array including unit memory cells disposed in an array, a second substrate stacked with the at least one first substrate, the second substrate including a sense amplifier region in which sense amplifiers configured to sense information stored in the unit memory cells are disposed, and a plurality of vertical conduction traces configured to electrically connect the at least one first substrate with the second substrate. The sense amplifier region is disposed in a memory region of the second substrate, wherein the memory region of the second substrate corresponds to the memory region of the first substrate.

Owner:SEOUL NAT UNIV R&DB FOUND

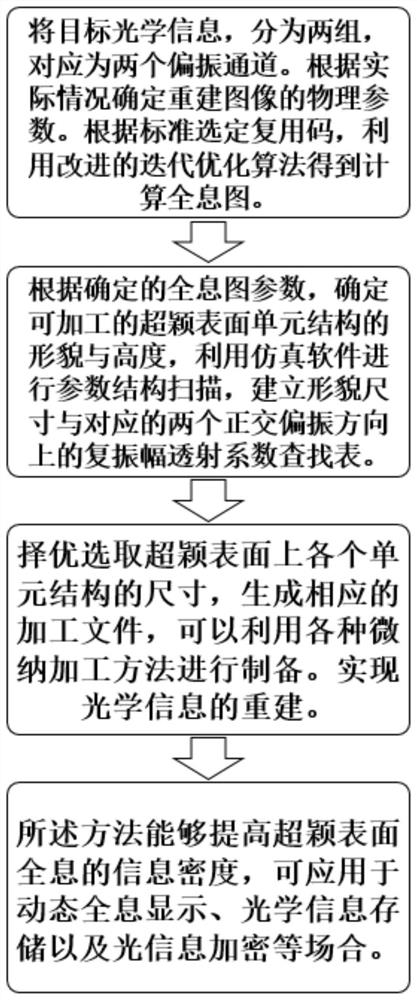

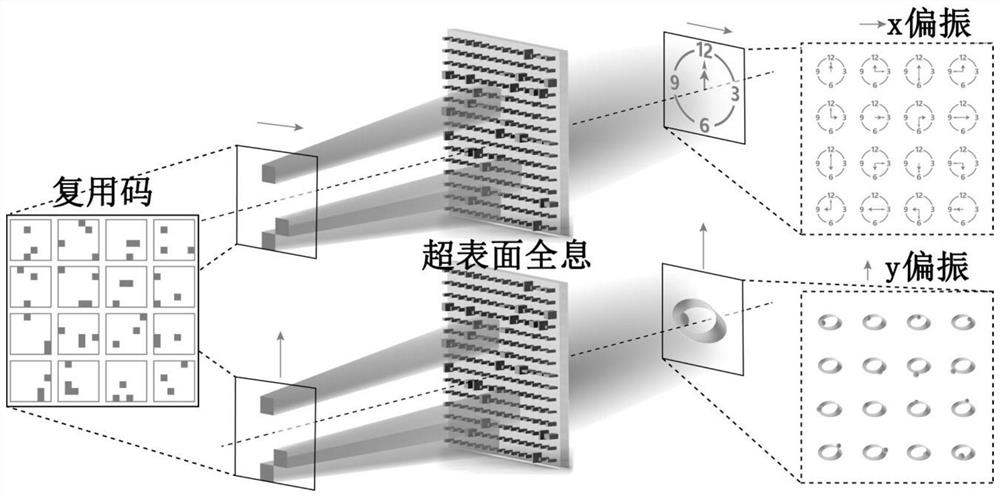

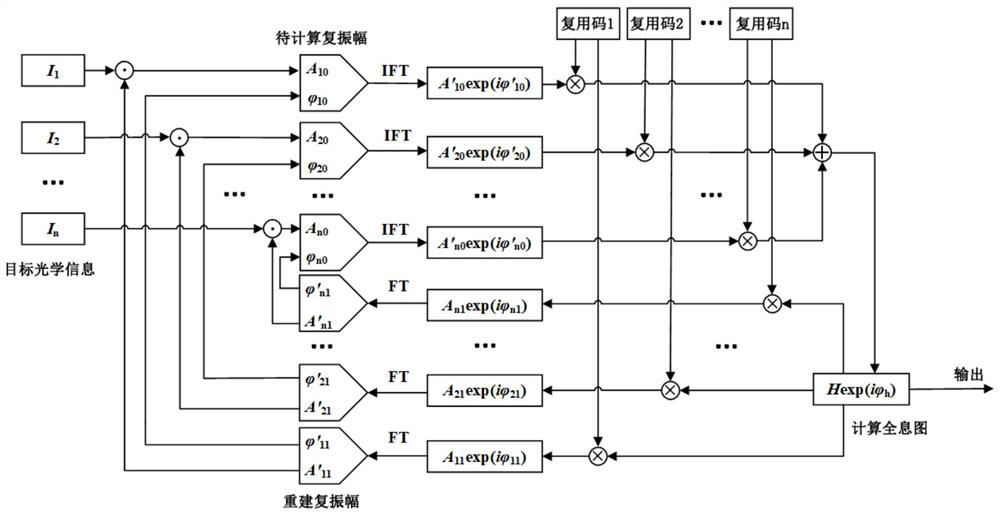

Code division multiplexing method based on metasurface holography

ActiveCN113238470AIncrease information densityRealize the storage functionInstrumentsMultiplexingEngineering

The invention relates to a metasurface-based code division multiplexing method for realizing multi-channel optical information coding, and belongs to the application field of micro-nano optics and holography. According to the invention, on the basis of phase regulation and control of the anisotropic unit structure of a metasurface, the design original of the metasurface structure is obtained according to a code division multiplexing iterative optimization algorithm, and then machining is guided; by using the method of the invention, under the conditions of a specific polarization state and reference light illumination, the completely independent image reconstruction function of each channel can be realized, and the information density of metasurface holography can be effectively improved; and the method can effectively improve the information density of the single metasurface, and can be applied to occasions such as dynamic holographic display, optical information storage and optical information encryption.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

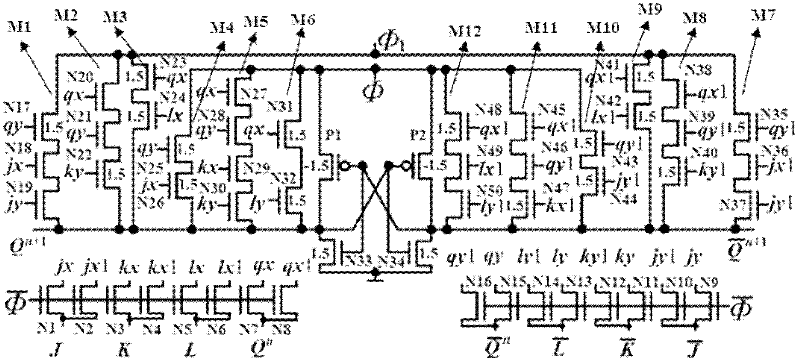

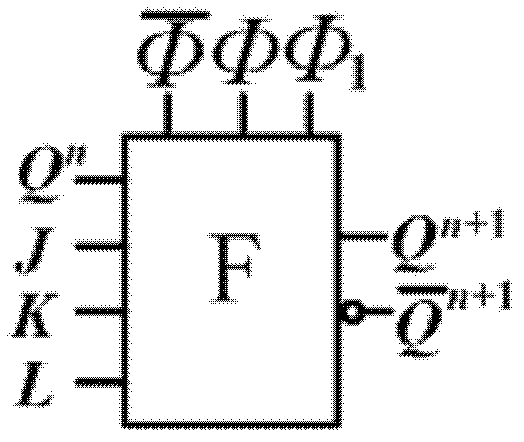

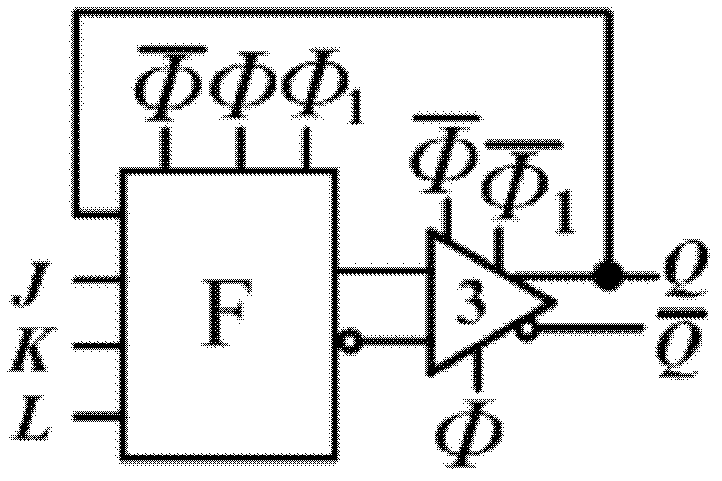

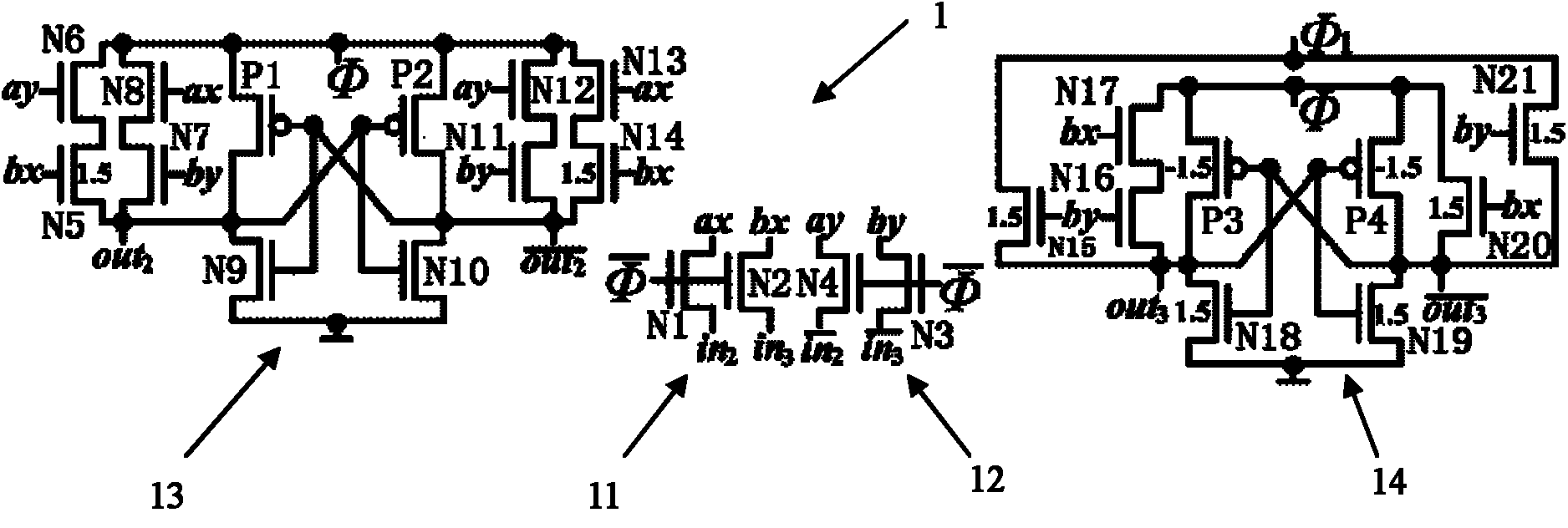

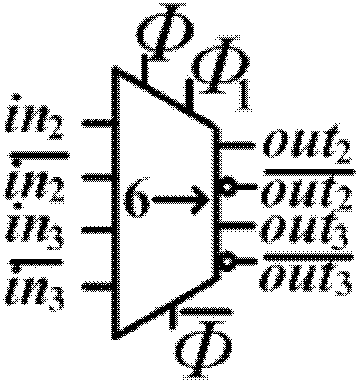

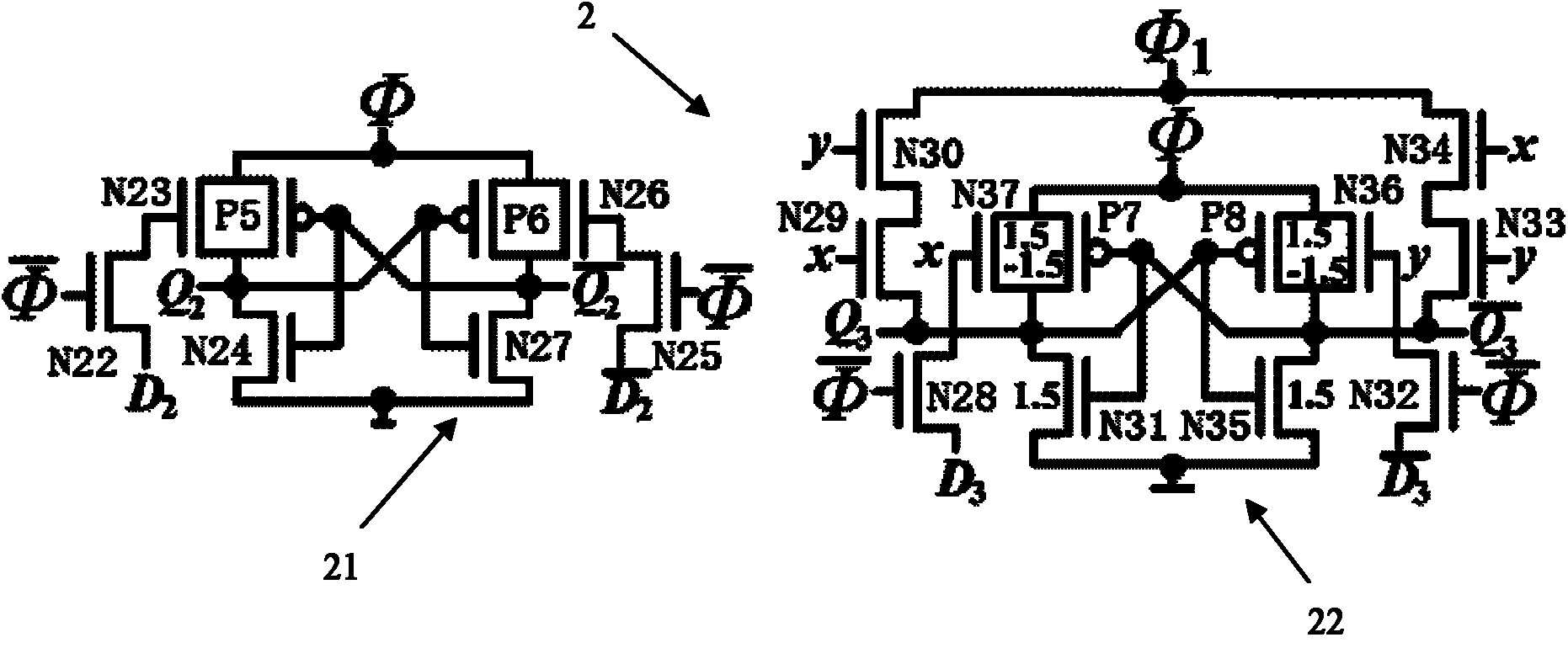

Ternary adiabatic JKL flip-flop and adiabatic novenary asynchronous counter

InactiveCN102394638AReduce power consumptionIncrease information densityCounting chain asynchronous pulse countersDelayed timeInformation density

The invention discloses a ternary adiabatic JKL flip-flop comprising a ternary adiabatic JKL fundamental circuit and a DTCTGAL buffer, wherein the signal input end of the ternary adiabatic JKL fundamental circuit is connected with the signal output end of the DTCTGAL buffer, the signal output end of the ternary adiabatic JKL fundamental circuit is connected with the signal input end of the DTCTGAL buffer; the complementary signal output end of the ternary adiabatic JKL fundamental circuit is connected with the complementary signal input end of the DTCTGAL buffer; both the ternary adiabatic JKL fundamental circuit and the DTCTGAL buffer are connected with a power clock signal of an amplitude level corresponding logic 1, a first clock pulse signal of an amplitude level corresponding logic 2 and a second clock pulse signal of the amplitude level corresponding logic 2; and the delay time of the DTCTGAL buffer is the same as that of the ternary adiabatic JKL fundamental circuit, and is half a clock period. The ternary adiabatic JKL flip-flop disclosed by the invention has the advantages that the circuit has very low power consumption, ternary input and output of the adiabatic circuit are realized while an energy recovery characteristic is provided, and the circuit has a higher information density and high operational reliability.

Owner:HANGZHOU MAEN TECH

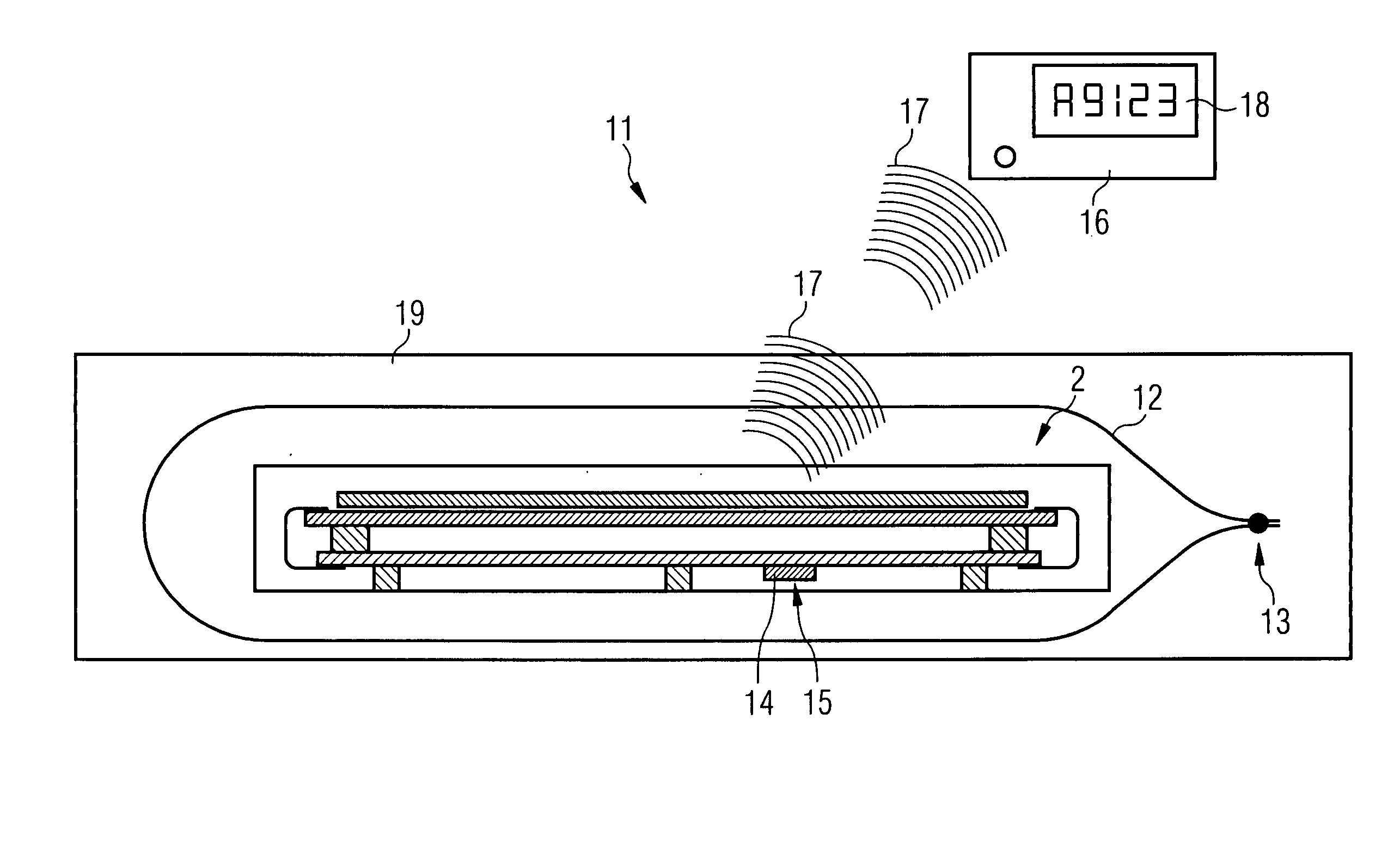

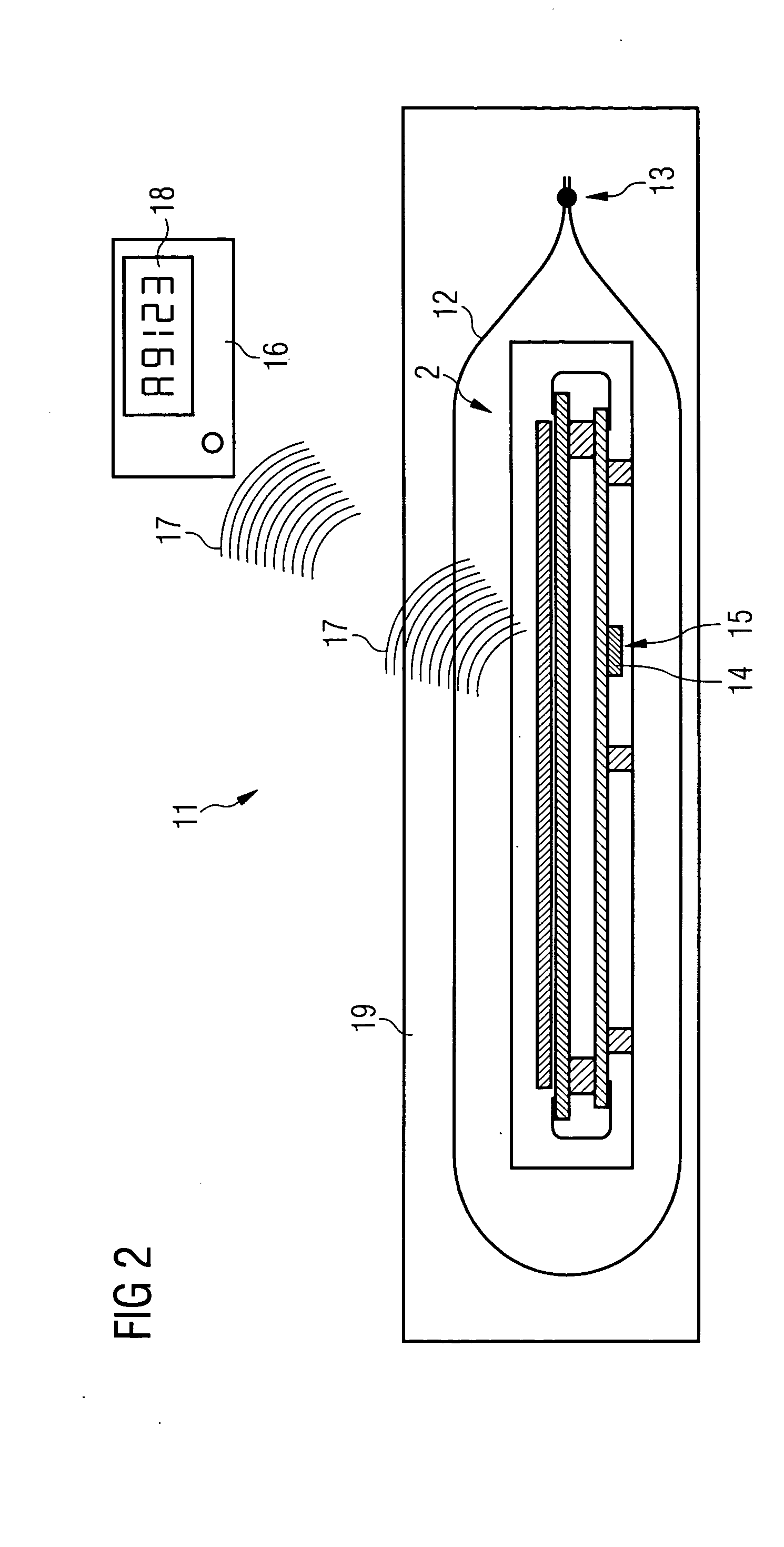

Device and method for identifying a component surrounded by an outer package

ActiveUS20050073414A1Increase information densityHigh densityTransistorSemiconductor/solid-state device detailsBiomedical engineeringR package

Device and method for identification of a component surrounded by an external package A device (11) for identification of a component (2) surrounded by an external package (12, 19) is described. For this purpose an identification element (14) is arranged in the area of the component (2). The identification element (14) can be identified through the external package by means of an acoustic method and / or scanning method. Furthermore a method for identifying a component (2) surrounded by an external package (12, 19) using the device in accordance with the invention (11) is described.

Owner:SIEMENS HEALTHCARE GMBH

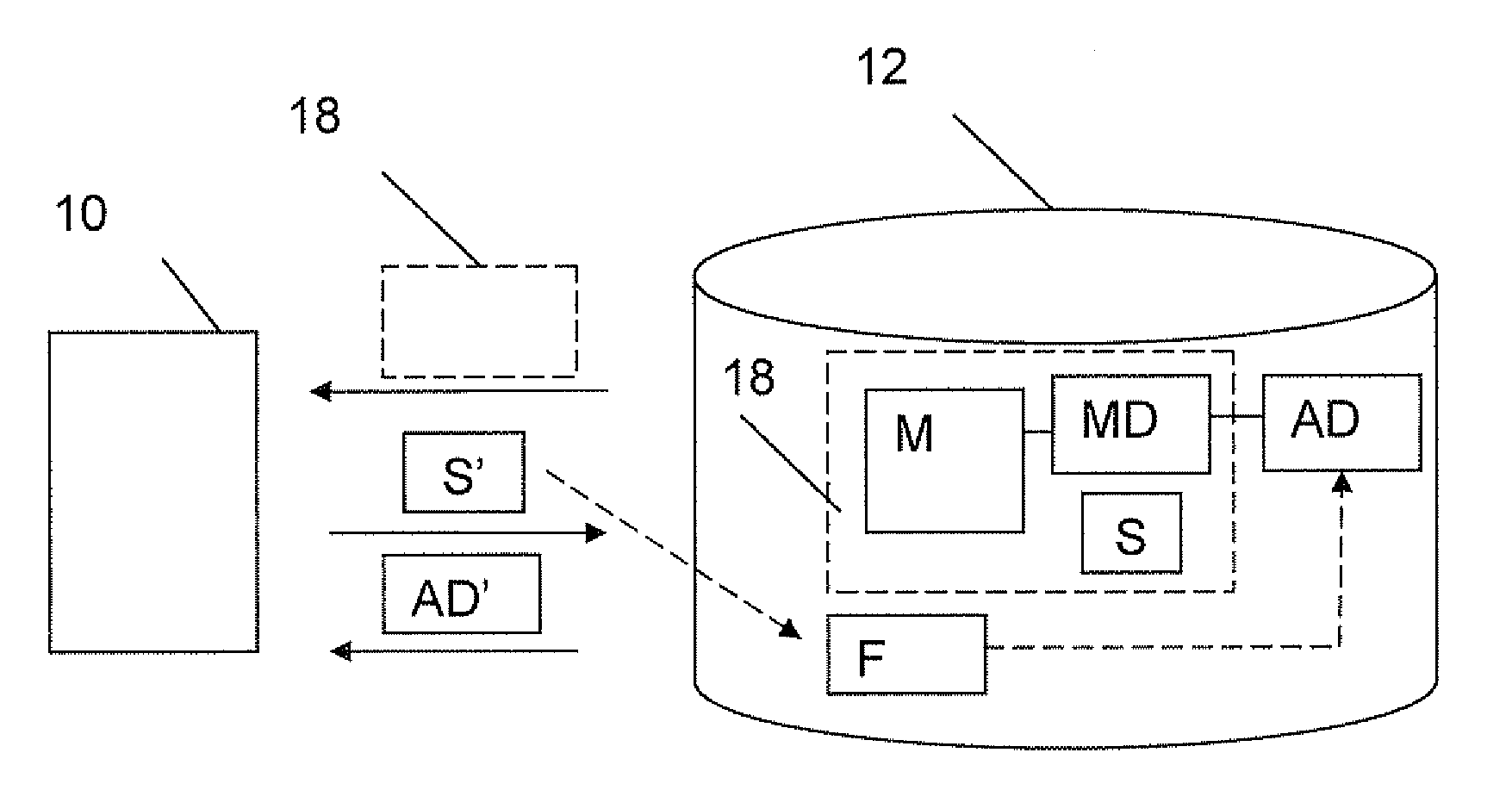

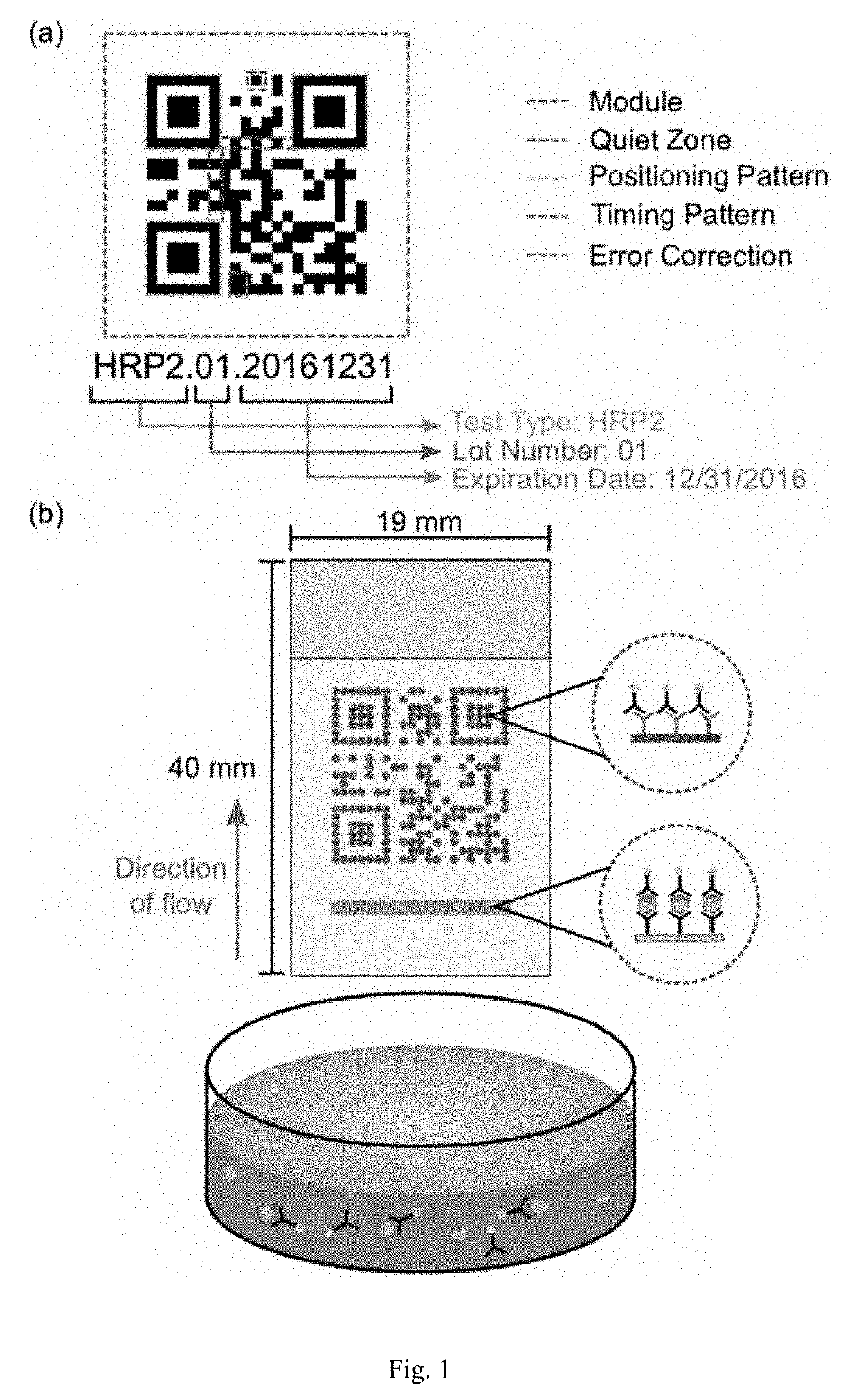

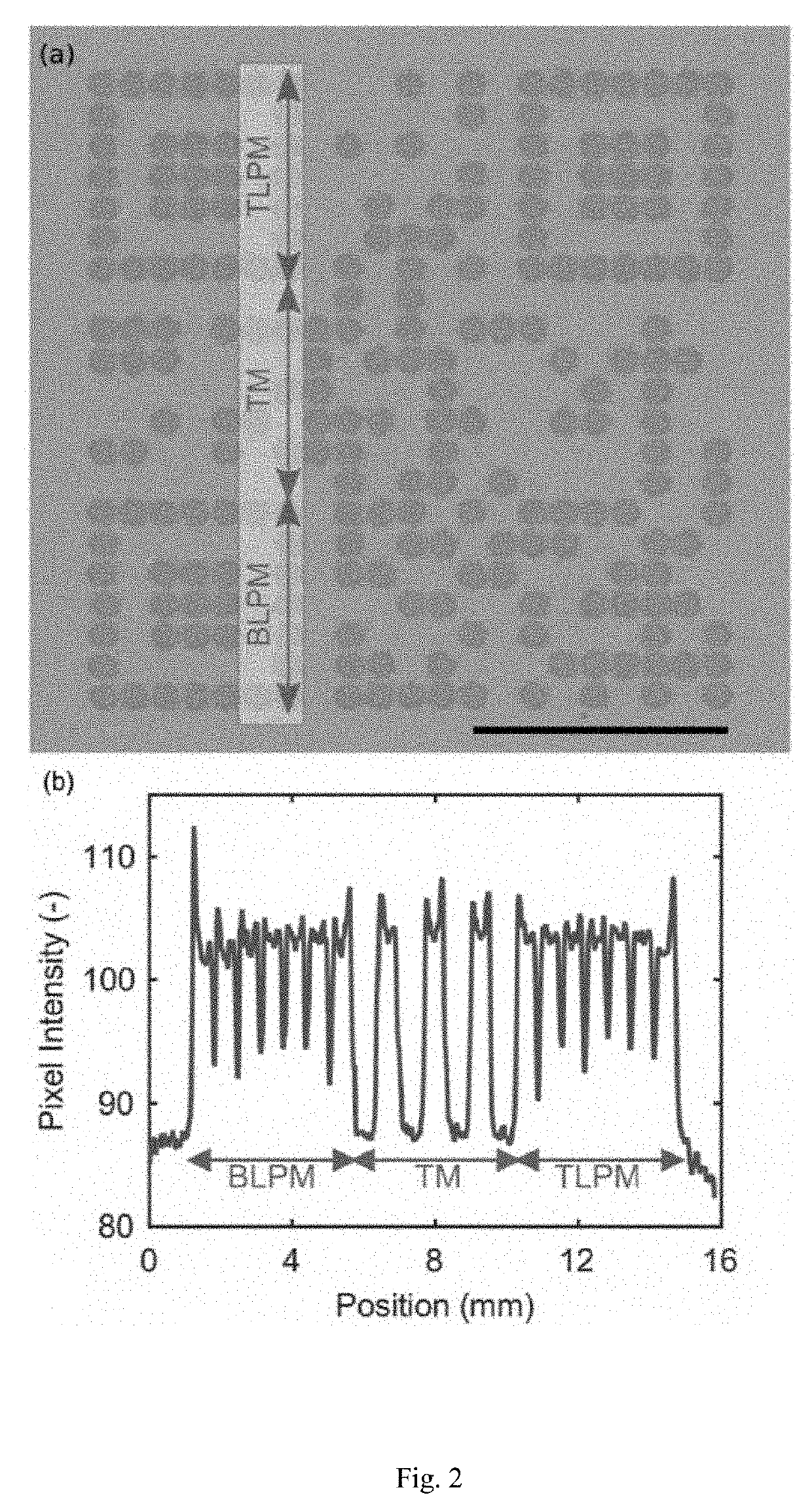

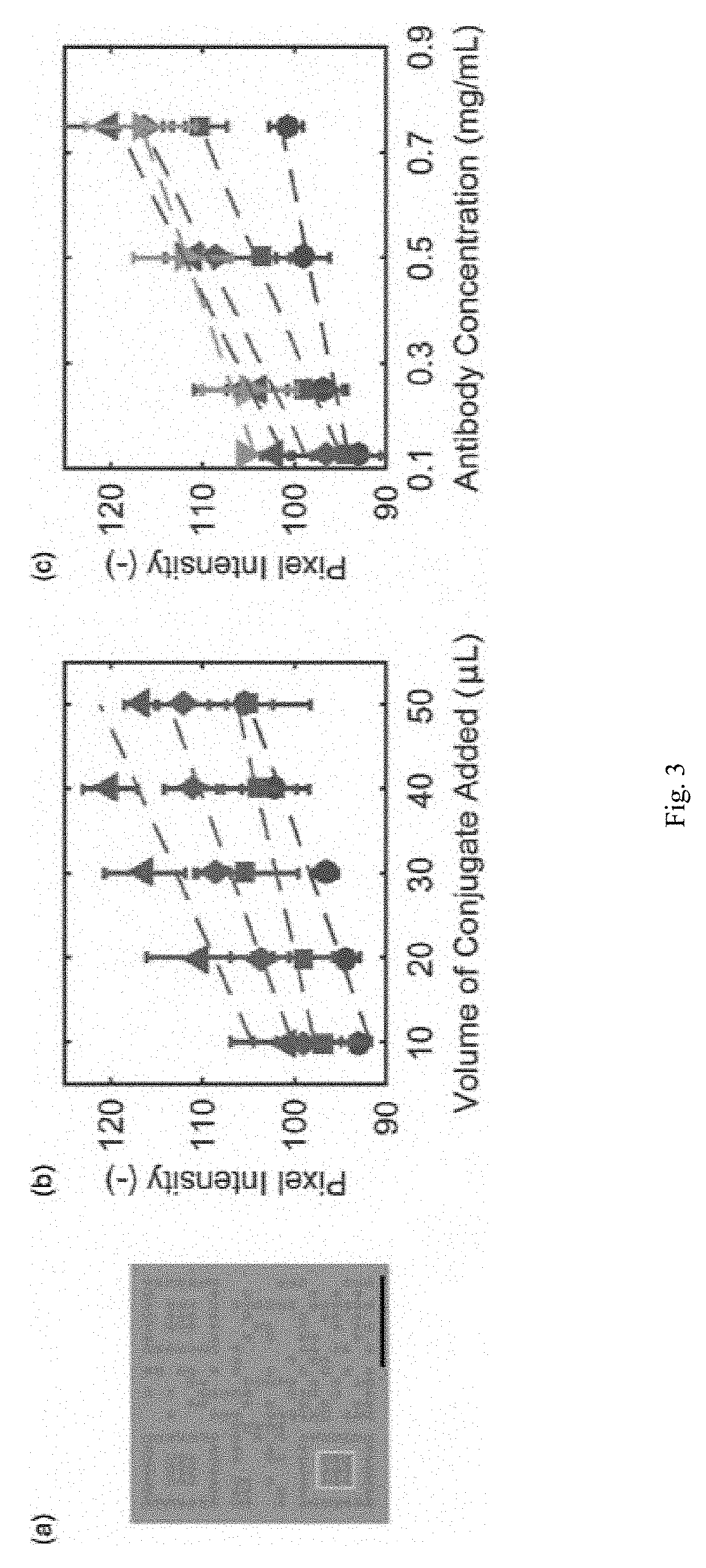

Secure machine readable code-embedded diagnostic test

InactiveUS20190257822A1Facilitate accurate quantitative image processingSimple processCharacter and pattern recognitionSensing record carriersRapid screening testApplication software

Disclosed herein is an information-augmented rapid diagnostic test in which control and test modules of a barcode, such as a QR code, are responsive to biomarkers in an analyte to become visible and form at least a portion of the barcode upon detection of the presence of such biomarkers. The barcode embeds test manufacturing details, serves as a trigger for image capture, enables registration for image analysis, and corrects for lighting effects. An accompanying mobile application preferably automatically captures an image of the test when the QR code is recognized, decodes the QR code, performs image processing to determine the concentration of the particular biomarker that is being diagnosed, and transmits the test results and QR code payload to a secure web portal.

Owner:PRAGMADX INC

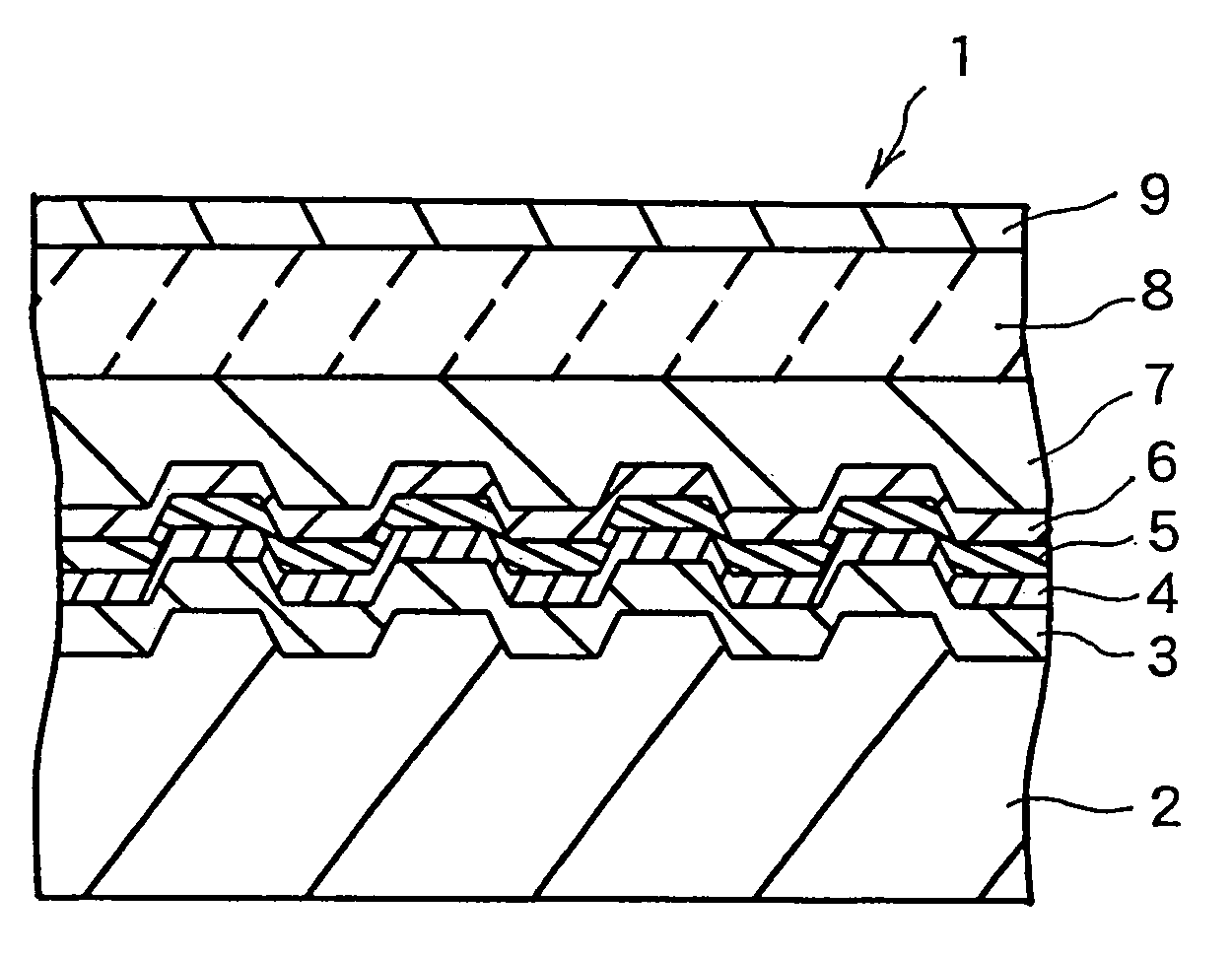

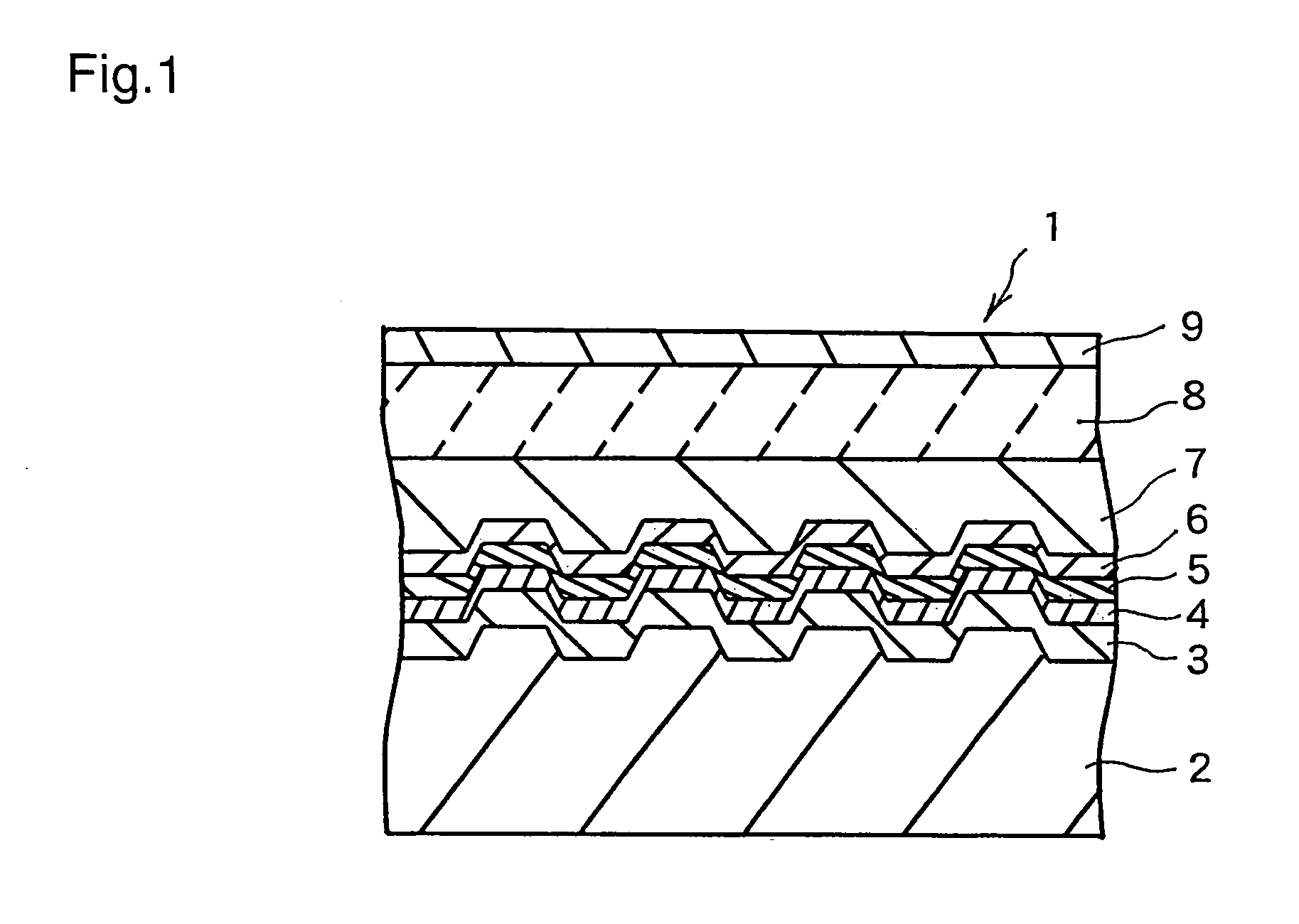

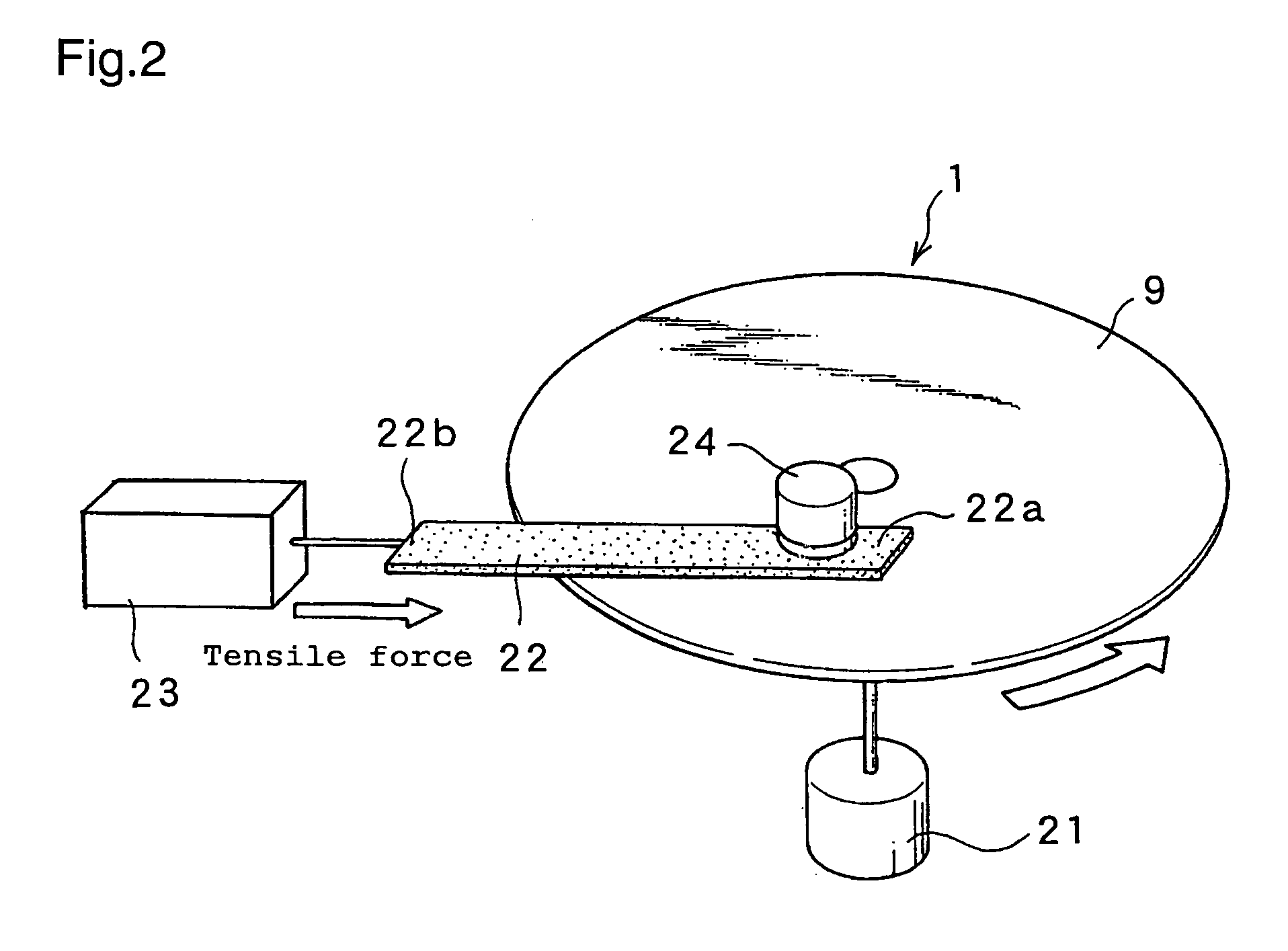

Optical information medium and production method therefor

InactiveUS7153558B2Reduce coefficient of frictionImprove scratch resistanceLayered productsPhotomechanical apparatusChemical compoundEngineering

The present invention provides an optical information medium that is less susceptible to warp in the disk surface while offering significantly high scratch resistance and abrasion resistance, and a method for producing the optical information medium. An optical information medium (1) comprising a supporting substrate (2) and a film element, the film element disposed on the supporting substrate (2) and composed of one or more layers including at least a recording layer (5) or a reflective layer (3), wherein at least one of the supporting substrate-side surface and the film element-side surface is formed of a hard coat layer (9) of a cured product of a composition comprising (A) inorganic fine particles with an average particle size of 100 nm or less, (B) a reactive silicone, and (C) an active energy ray-curable compound.

Owner:TDK CORPARATION

Mixed-value based sexenary adiabatic asynchronous adding/subtracting counter units and counter

InactiveCN102360275AAchieve recoveryReduce energy consumptionComputation using non-contact making devicesTransmission gateEnergy consumption

The invention discloses a mixed-value based sexenary adiabatic asynchronous adding / subtracting counter which comprises N mixed-value based sexenary adiabatic asynchronous adding / subtracting counter units, N-1 sexenary adiabatic carry / borrow circuits, and a DTCTGAL (double power clock ternary clocked transmission gate adiabatic logic) buffer, wherein the DTCTGAL buffer is arranged between the ith sexenary adiabatic carry / borrow circuit and the (i+1)th mixed-value based sexenary adiabatic asynchronous adding / subtracting counter unit, and each mixed-value based sexenary adiabatic asynchronous adding / subtracting counter unit is composed of a sexenary adiabatic right-shift door and a sexenary adiabatic D trigger. The counter disclosed by the invention has the advantages that according to a theory of three essential circuit elements, an adiabatic technique is introduced into a design on sexenary logic circuits, and the design on a mixed-value (2-3 mixed values) based sexenary adiabatic asynchronous adding / subtracting counter is implemented by using a mixed-value coding technique, so that an effect of energy consumption saving is significantly achieved, and the counter has a characteristic of high information density; and compared with a conventional sexenary adiabatic asynchronous adding / subtracting counter, by using the counter disclosed by the invention, about 94% of energy consumption can be saved.

Owner:NINGBO UNIV

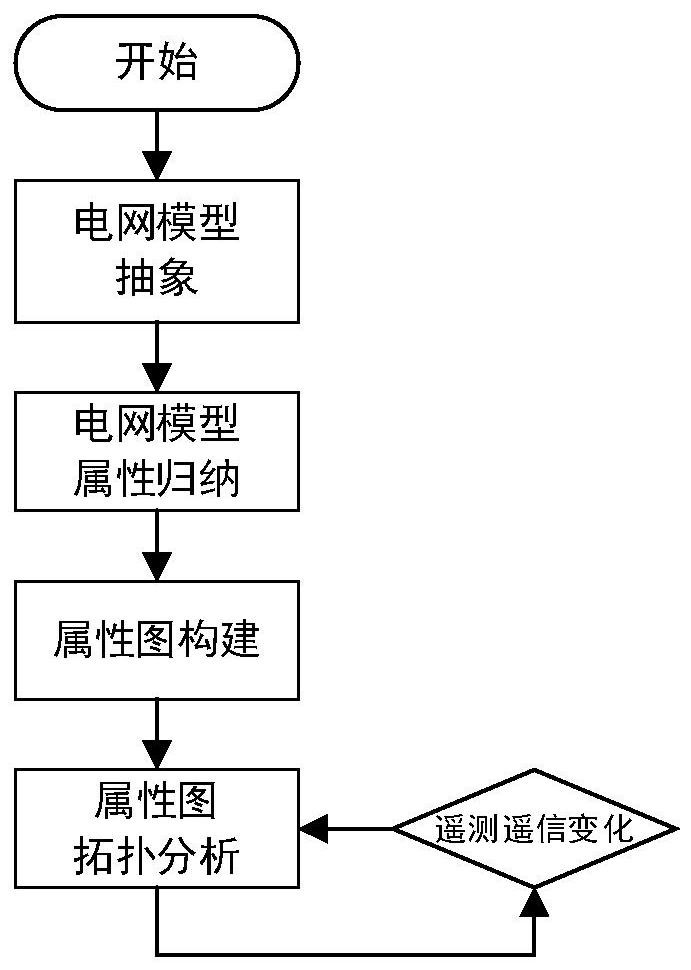

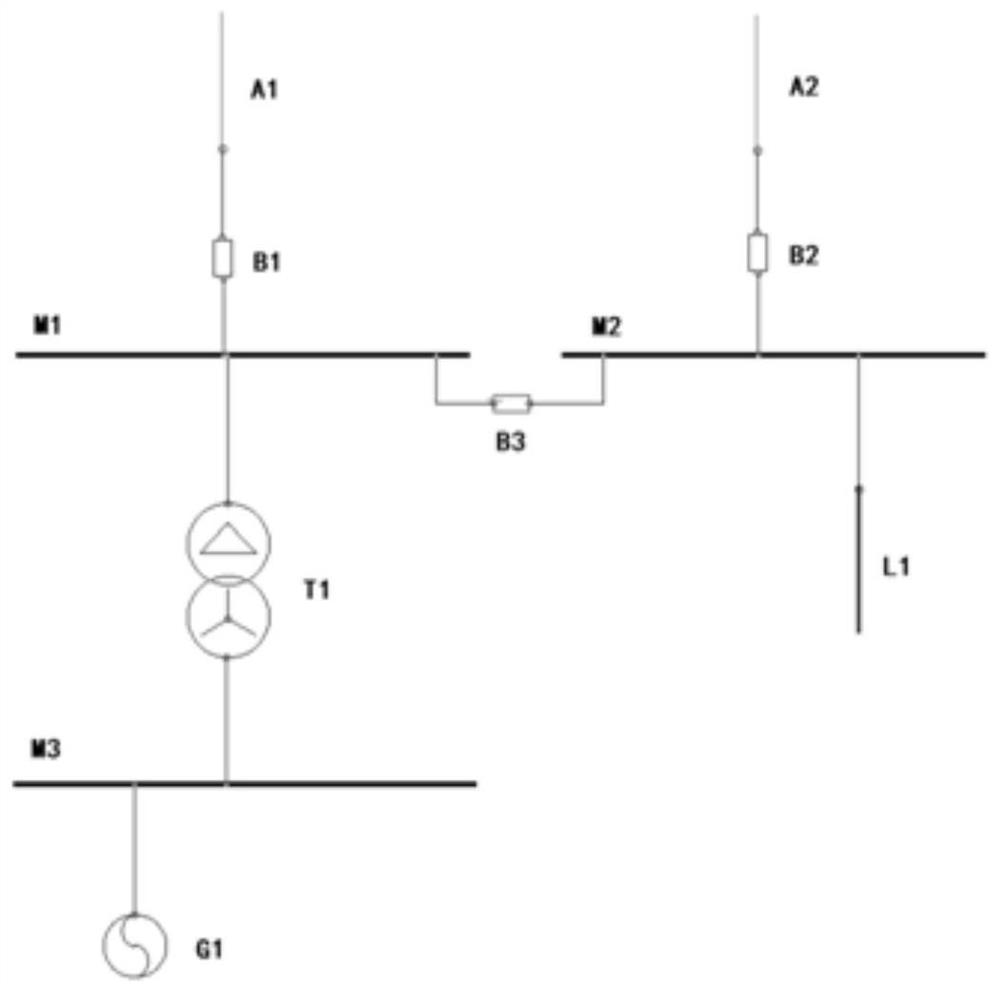

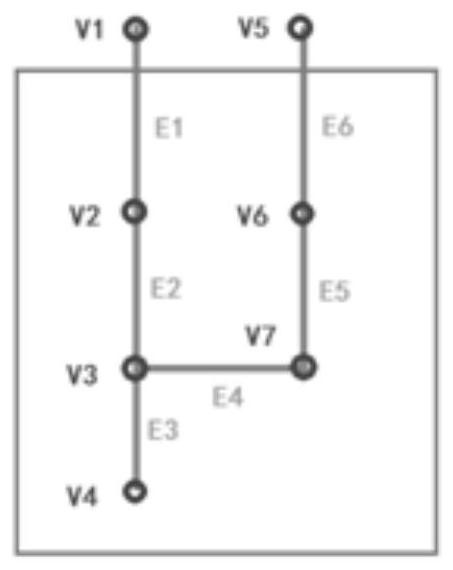

Power system topology analysis method based on attribute graph

ActiveCN112231871AIncrease information densityImprove efficiencyGeometric CADSpecial data processing applicationsPower gridAlgorithm

Owner:NARI TECH CO LTD +2

PHASE-CHANGE TaN RESISTOR BASED TRIPLE-STATE/MULTI-STATE READ ONLY MEMORY

ActiveUS20070023743A1Minimize increasing FEOL complexityIncrease memory densitySolid-state devicesRead-only memoriesRead-only memoryThermal conductivity

The present invention relates to a nonvolatile memory such as, for example a ROM or an EPROM, in which the information density of the memory is increased relative to a conventional nonvolatile memory that includes two logic state devices. Specifically, the nonvolatile memory of the present invention includes a SiN / TaN / SiN thin film resistor embedded within a material having a thermal conductivity of about 1 W / m-K or less; and a non-linear Si-containing device coupled to the resistor. Read and write circuits and operations are also provided in the present application.

Owner:IBM CORP

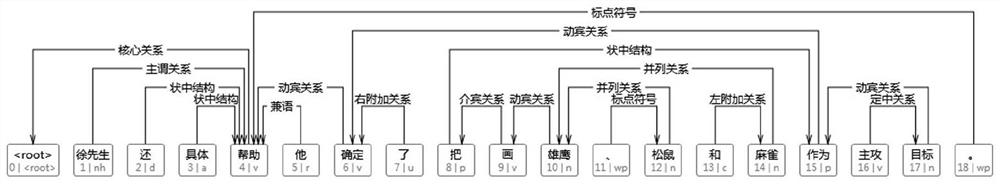

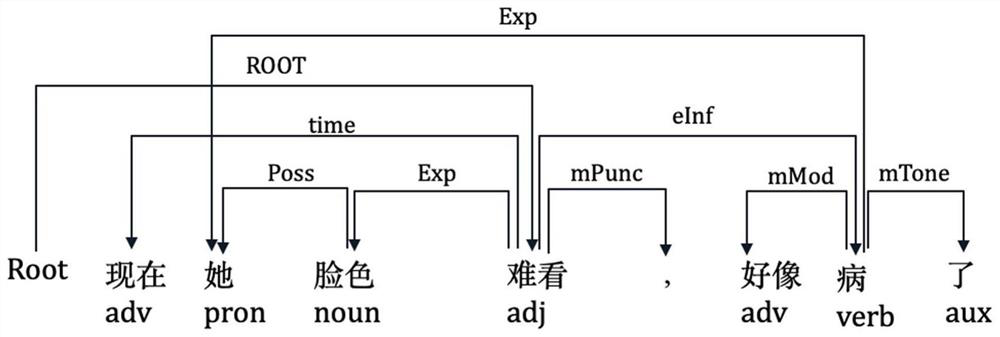

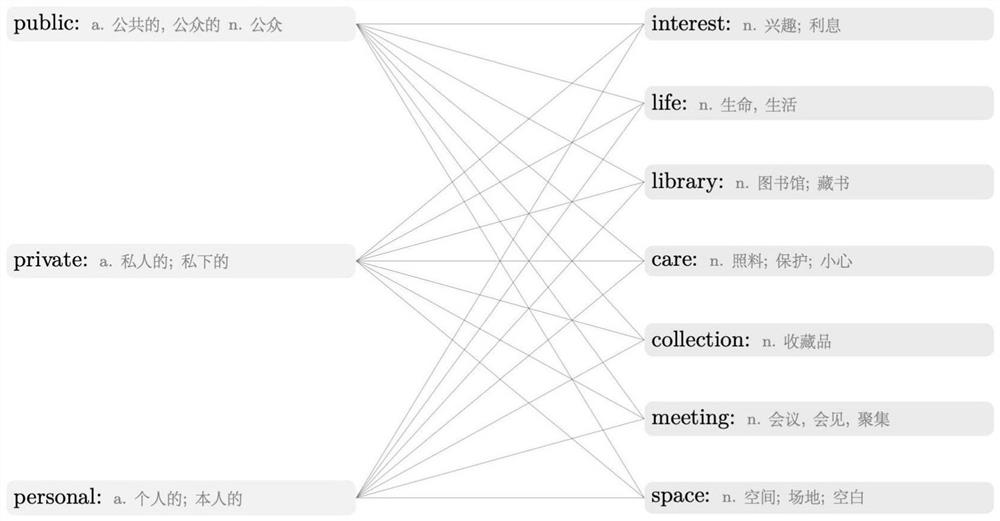

Mining and displaying method combining vocabulary matching extraction and semantic classification

PendingCN112860781AIncrease information densitySemantic analysisVisual data miningPattern recognitionCollocation

The invention discloses a mining and displaying method combining vocabulary matching extraction and semantic classification, and belongs to the field of natural language processing and language learning application. The method comprises: extracting and filtering word collocation by using a deep learning-based dependency syntax semantic model and a statistical method; in combination with the sorted word classification and the extracted collocation, calculating a many-to-many collocation matrix; screening, sorting and recombining the collocation words and the word classification according to the collocation density; displaying the finally obtained word classification matching matrix in an m*n or m*n*o card form; and the cards are displayed according to a hierarchical sequence of lexical semantic classification. Through the method, a collocation and vocabulary classification system with more general significance and a many-to-many word classification collocation matrix display form can be obtained, the display form is visual and vivid, the information density is large, and systematic learning of language vocabularies is facilitated through a semantic and pragmatic combination grouping mode.

Owner:陈永朝

Formatting object for modifying the visual attributes of visual objects ot reflect data values

InactiveUS20050001839A1Increase information densityDrawing from basic elementsMultiple digital computer combinationsComputer graphics (images)Boundary values

A formatting object according to the present invention conveys information to the reader of a document (such as a table or chart) by associating visual attributes (such as color, fill type, border width, line width, line style, font size, marker size and marker type) to characters or markers within the document. The formatting object may be used to emphasize data within a table or a chart by modifying the structural visual attributes of characters or markers within the table or chart according to pre-defined criteria. Similarly, the formatting object may be used to increase information density within a table or chart, and to elegantly represent the relationships between four or more interrelated variables in a two-dimensional chart. The formatting object accomplishes this by defining at least one format map that comprises one or more mapping segments. Each mapping segment includes a beginning boundary value, an ending boundary value, at least one beginning visual attribute corresponding to the beginning boundary value, and at least one ending visual attribute corresponding to the ending boundary value. The formatting object uses the information within the format maps, in combination with interpolation techniques, to determine one or more visual attributes that correspond to data points falling within the various mapping segments. The formatting object then expresses the data values by applying the appropriate visual attribute to a visual object displayed on a computer screen.

Owner:MICROSOFT TECH LICENSING LLC

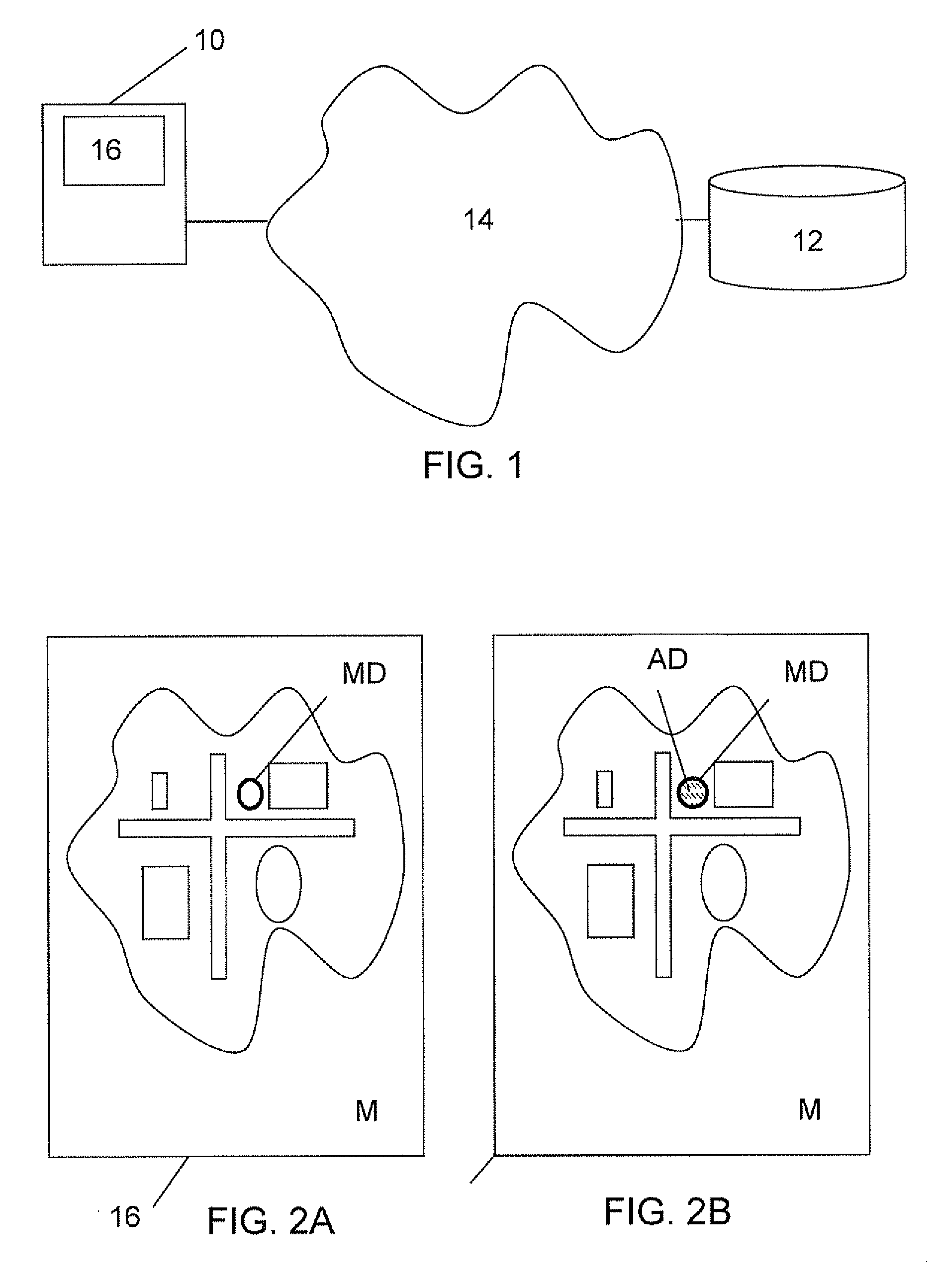

Map display device and map display method

ActiveUS8781734B2Increase information densityDecreasing legibilityInstruments for road network navigationRoad vehicles traffic controlDisplay deviceInformation density

The invention provides a map display device and map display method that enhance the information density of displayed road names while maintaining legibility of a map image. First, the map drawing unit draws, to an image storage unit, a map image of roads and so forth in a desired scale, by using the background layer of a first hierarchy corresponding to the desired scale. Second, the map drawing unit draws place names and facility names by using the character layer of the first hierarchy to superimpose them on the map image. Third, the map drawing unit extracts the road names that do not overlap with the map characters of the place names and facility names on the map image by using the character layer of the first hierarchy, and superimposes them on the map image at the normal character size. Fourth, the map drawing unit extracts, by using the character layer of a second hierarchy corresponding to a scale level smaller by one step than the desired scale level, road names that do not overlap with the map characters of the other road names, place names, facility names and so forth on the map image, and superimposes them on the map image at a smaller character size. Finally, the map drawing unit superimposes the vehicle position mark on the map image.

Owner:ALPINE ELECTRONICS INC

Bar code structure, bar code decoding method and bar code decoding apparatus

ActiveCN106650862AIncrease information densitySimplify the coding processRecord carriers used with machinesSensing by electromagnetic radiationProgramming languageCircular disc

Owner:LITE ON ELECTRONICS (GUANGZHOU) LTD +1

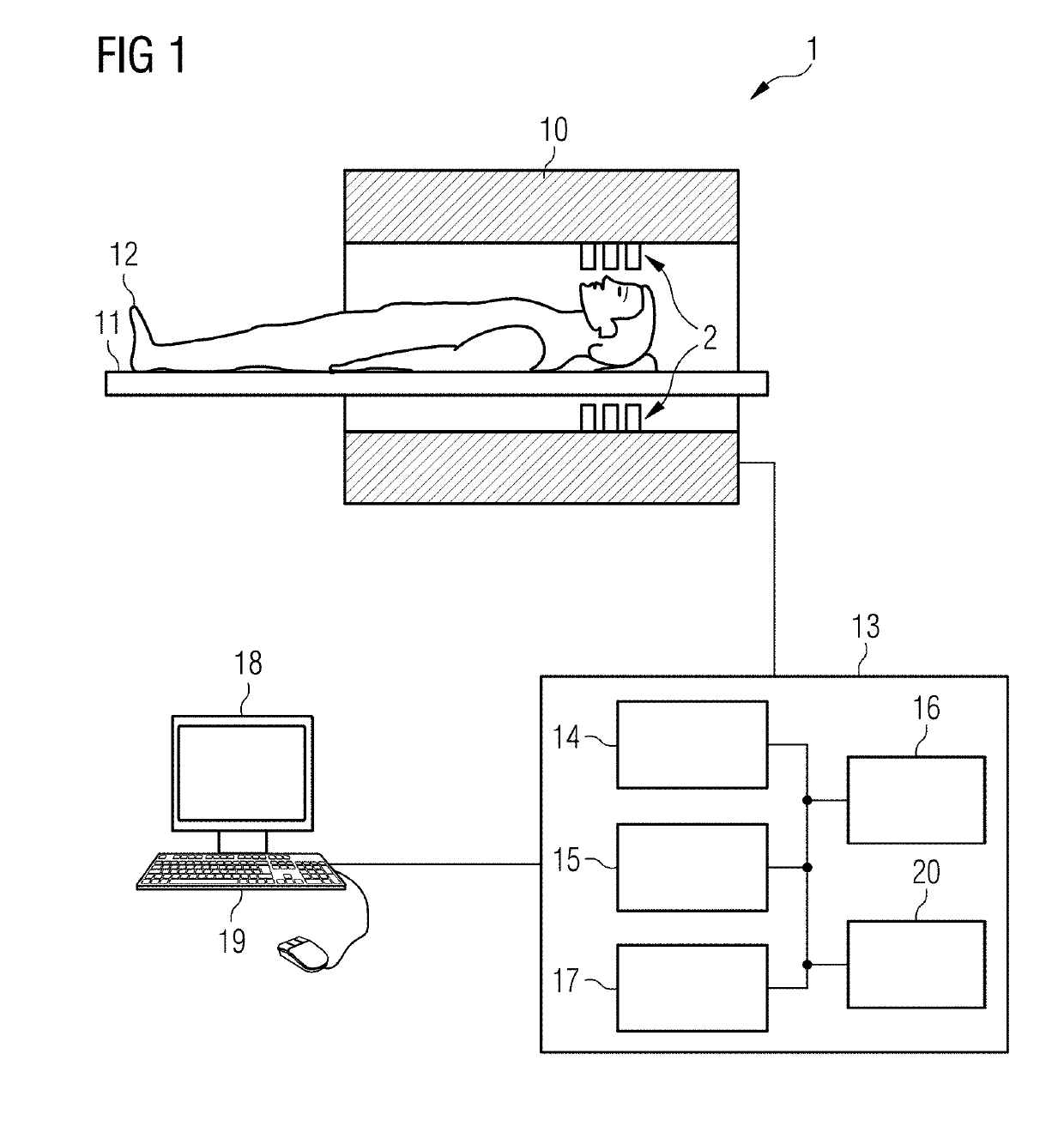

Method and magnetic resonance apparatus for performing electrical impedance tomography with the aid of an mr system

ActiveUS20190298217A1Accurate informationHigh densityDiagnostic recording/measuringMeasurements using NMR imaging systemsElectrical resistance and conductanceResonance

The present invention relates to a method for performing electrical impedance tomography (EIT) by an MR system, wherein during the MR measurement continuous RF signals for an EIT measurement are emitted by at least one RF coil of the MR system, and continuous RF signals modulated by the object undergoing examination are received by the receiving coils of the MR system. An image of the object undergoing examination is determined, based on the modulated continuous RF signals, by an EIT technique.

Owner:SIEMENS HEALTHCARE GMBH