Mixed-value based sexenary adiabatic asynchronous adding/subtracting counter units and counter

An addition, subtraction, and counter technology, which is applied in the field of six-value adiabatic asynchronous addition and subtraction counter units and counters, can solve the problems of MOS tube threshold detection difficulties, high power supply voltage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

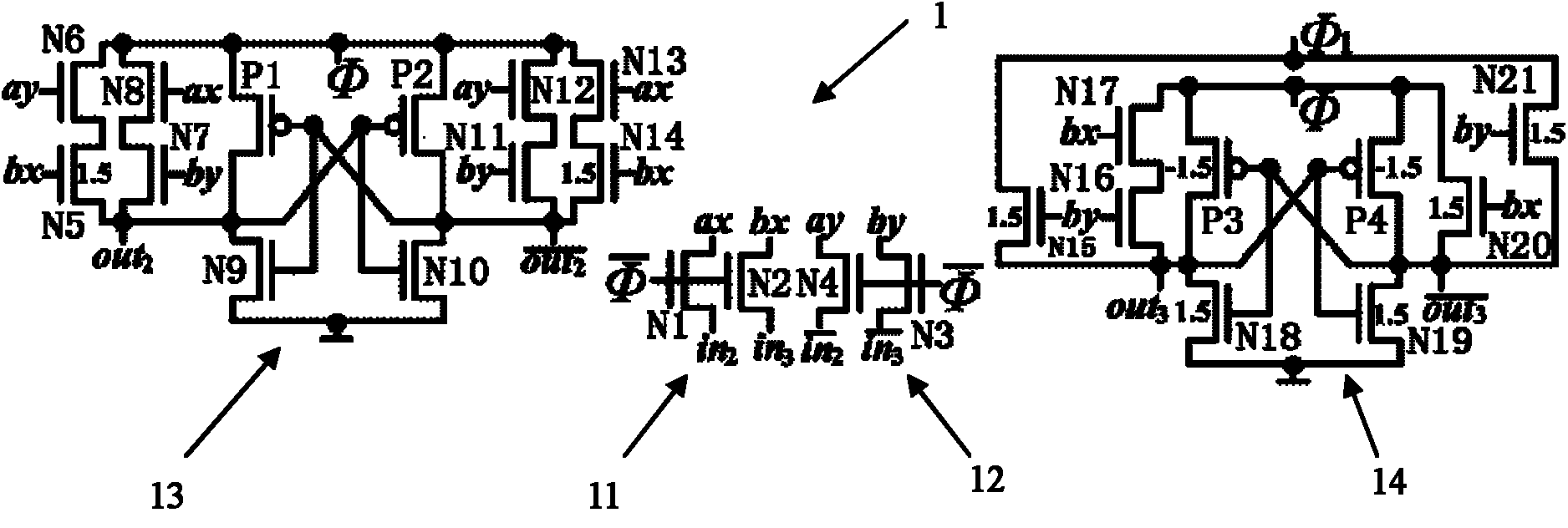

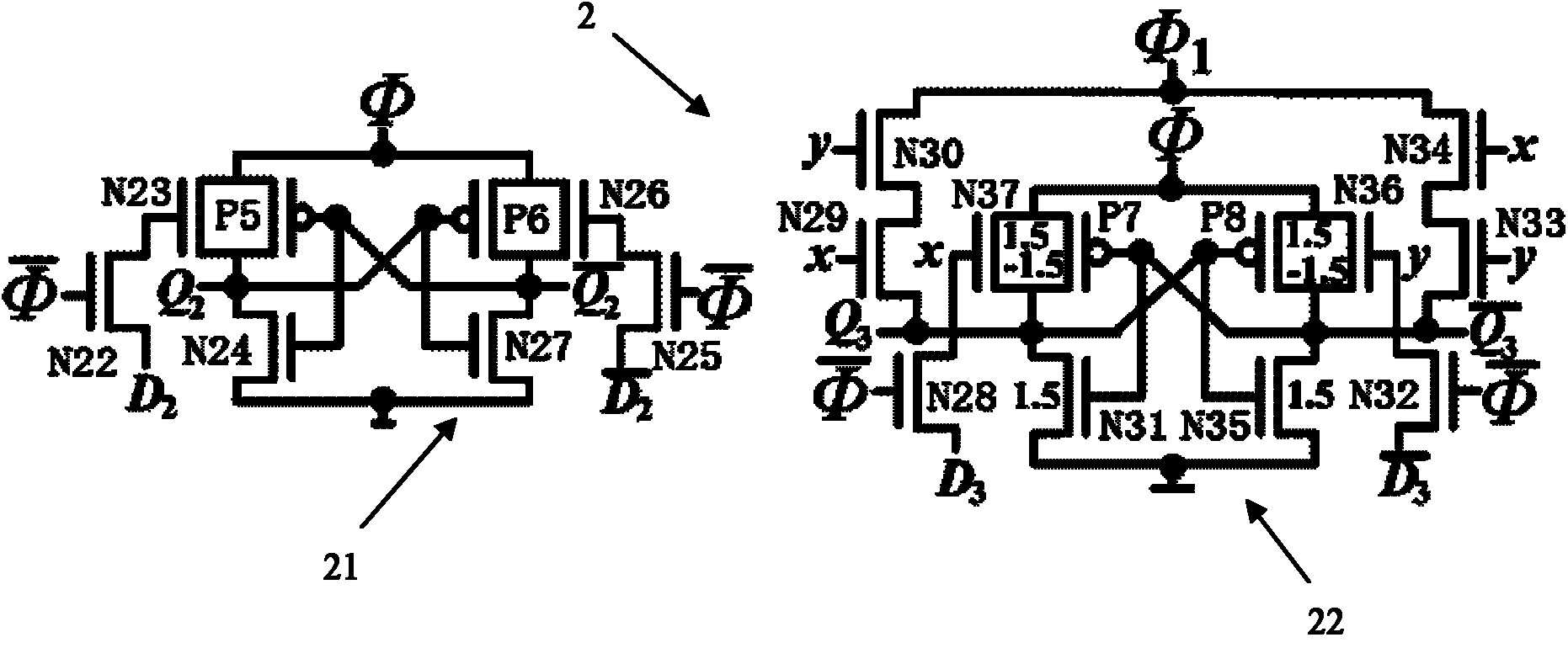

Embodiment 1

[0021] Embodiment 1: For a one-bit six-value signal, if a binary signal is used for encoding, three binary signals are required, and the encoding efficiency is 6 / 2 3 =75%, resulting in 2 redundant items, resulting in a waste of coding, which not only increases the IC chip area and production cost, but also reduces the data processing speed and affects the reliability of circuit work. If 2-3 mixed-value coding is introduced, only one bit of binary signal and one bit of three-valued signal are needed, as shown in Table 1, where a 2 Represents a binary signal (0, 2), a 3 Represents a three-valued signal (0, 1, 2), a binary signal a 2 The highest logical value of 2 and the three-valued signal a 3 The levels corresponding to the highest logic value of 2 are equal. It can be found from Table 1 that the 2-3 mixed value coding does not have any redundant states, and the coding efficiency reaches 100%.

[0022] Table 12-3 Mixed value encoding

[0023]

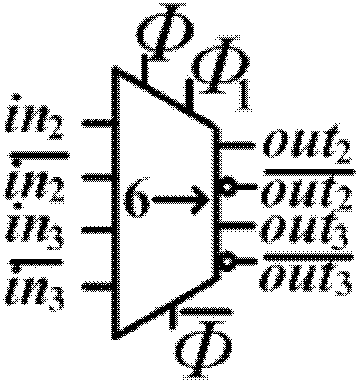

[0024] According to the ...

Embodiment 2

[0030] Embodiment two: a kind of six-value adiabatic asynchronous addition and subtraction counter based on the mixed value (2-3 mixed value) six-value adiabatic asynchronous addition and subtraction counter unit based on the mixed value (2-3 mixed value) given in embodiment one constitutes, including N A six-value adiabatic asynchronous addition and subtraction counter unit based on a mixed value, an N-1 six-value adiabatic carry / borrow circuit 3 and a six-value adiabatic carry / borrow circuit 3 set at the i-th bit and the i+1-th bit based on DTCTGAL buffer 4 between the mixed-valued six-valued adiabatic asynchronous addition and subtraction counter unit, the i-th bit based on the mixed-valued six-valued adiabatic asynchronous asynchronous addition and subtraction counter unit’s first up count output and the i-th bit six-valued adiabatic The binary signal input terminal of the carry / borrow circuit 3 is connected to the second addition and counting output terminal of the i-th bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More