High-speed programmable frequency divider

A frequency divider, high-speed technology, applied in the field of high-speed programmable frequency divider, can solve the problems of complex logic design of the decoder and the decrease of frequency divider speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

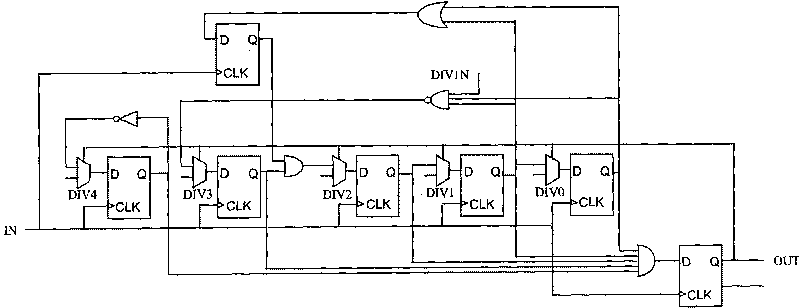

[0030] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

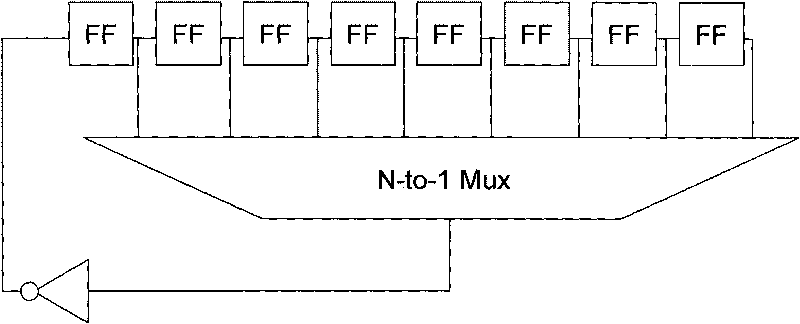

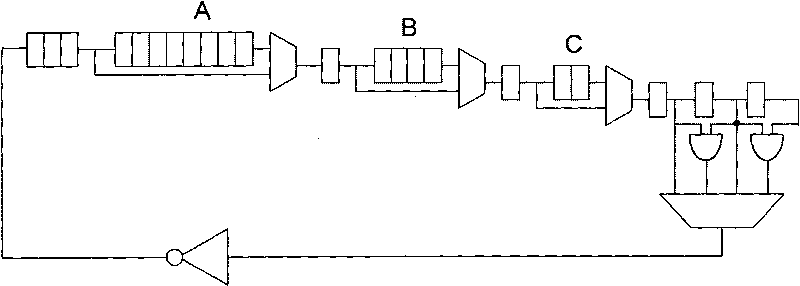

[0031] The high-speed programmable frequency divider provided by the present invention adopts a basic unit different from the traditional Johnson counter: the shift register is completely separated into a single latch, so that any two adjacent latches may form a traditional The single shift register in the Johnson counter makes the frequency division range of the frequency divider unlimited, and a certain regular grid is formed by many latches, so that the frequency division range is extended from 12-40 to 2-N(N for any large value).

[0032] The frequency divider of the present invention is composed of multi-stage latches to form a regular grid; each latch has a plurality of selectable input terminals and a plurality of output terminals, and its initial value is preset when the input is closed. 0 or 1 function. The input terminals of each l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More