Patents

Literature

132 results about "Binary logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Binary logic, also referred to as two-value or Boolean logic, is a set of rules for dealing with propositions that must be either true or false. Its primary applications are in computer programming and mathematics, although there are also recreational games and puzzles based upon more formal logic.

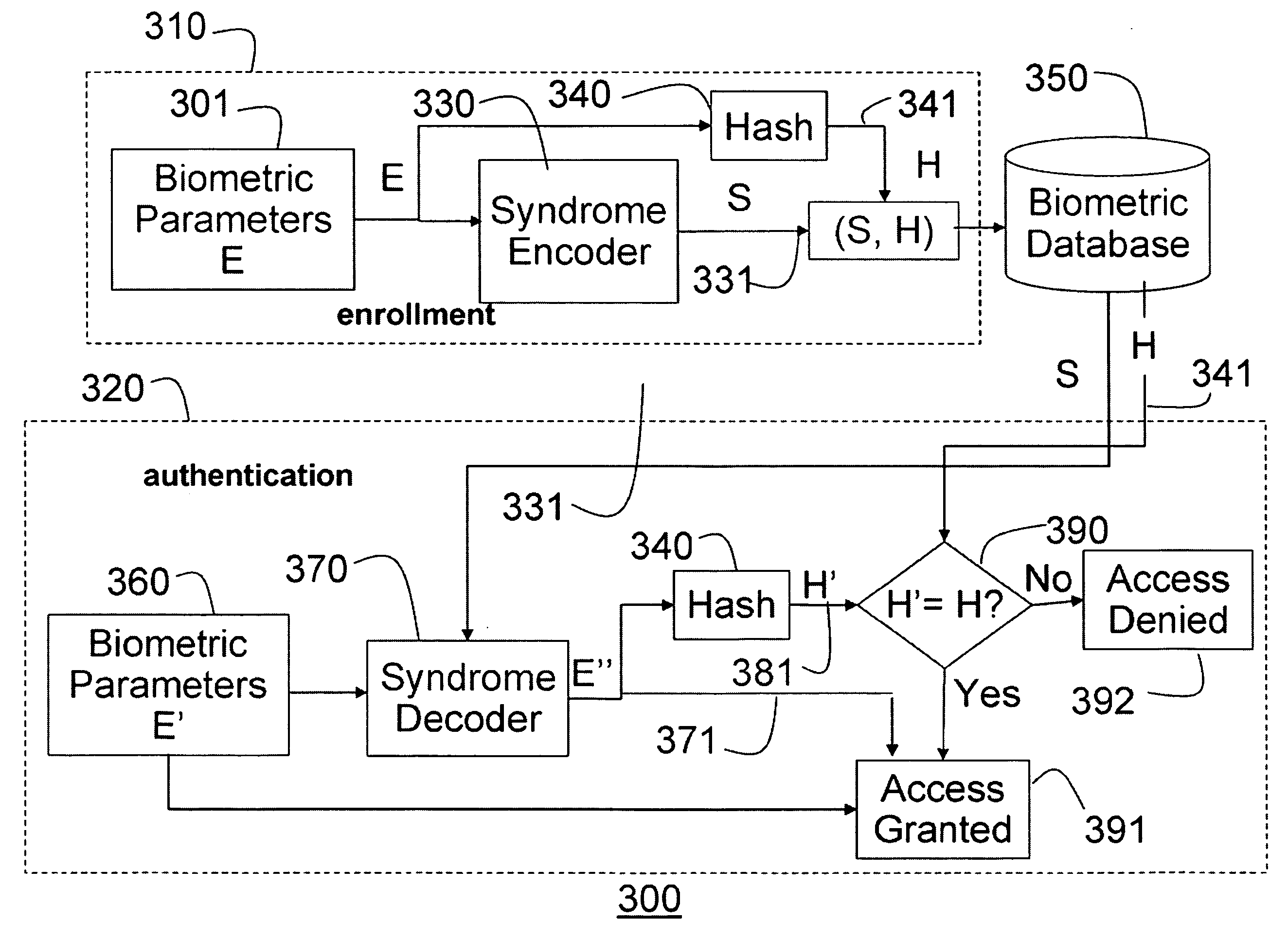

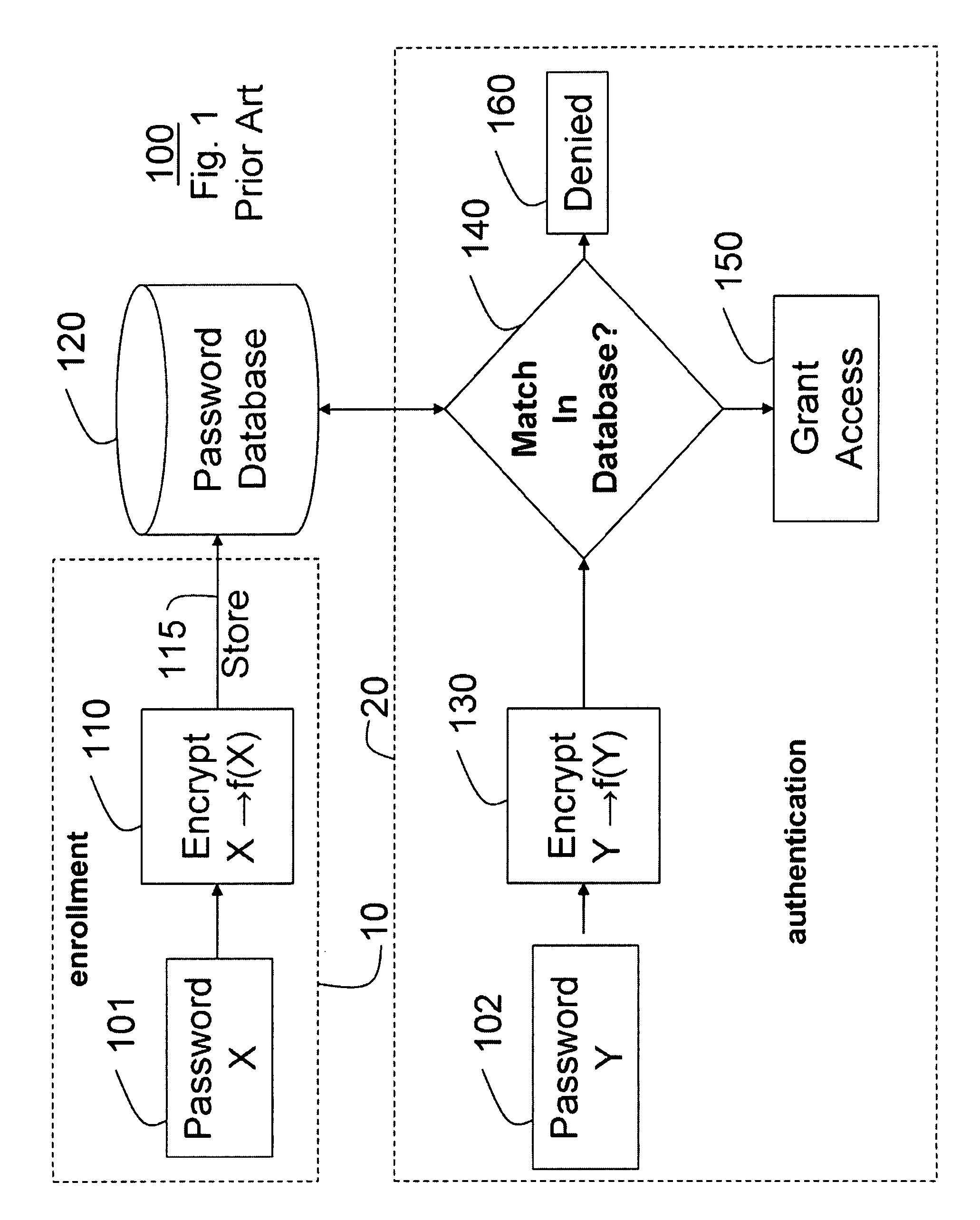

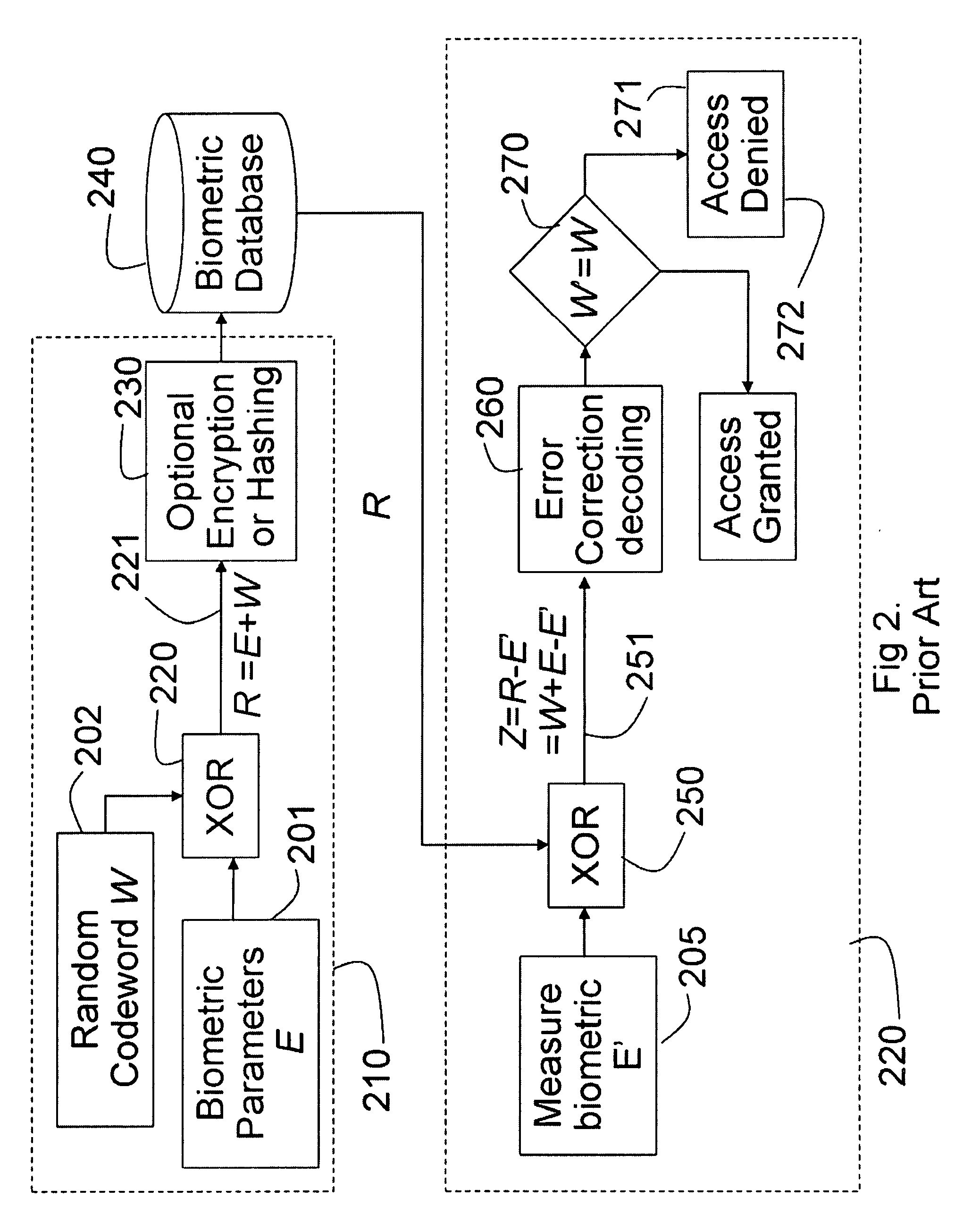

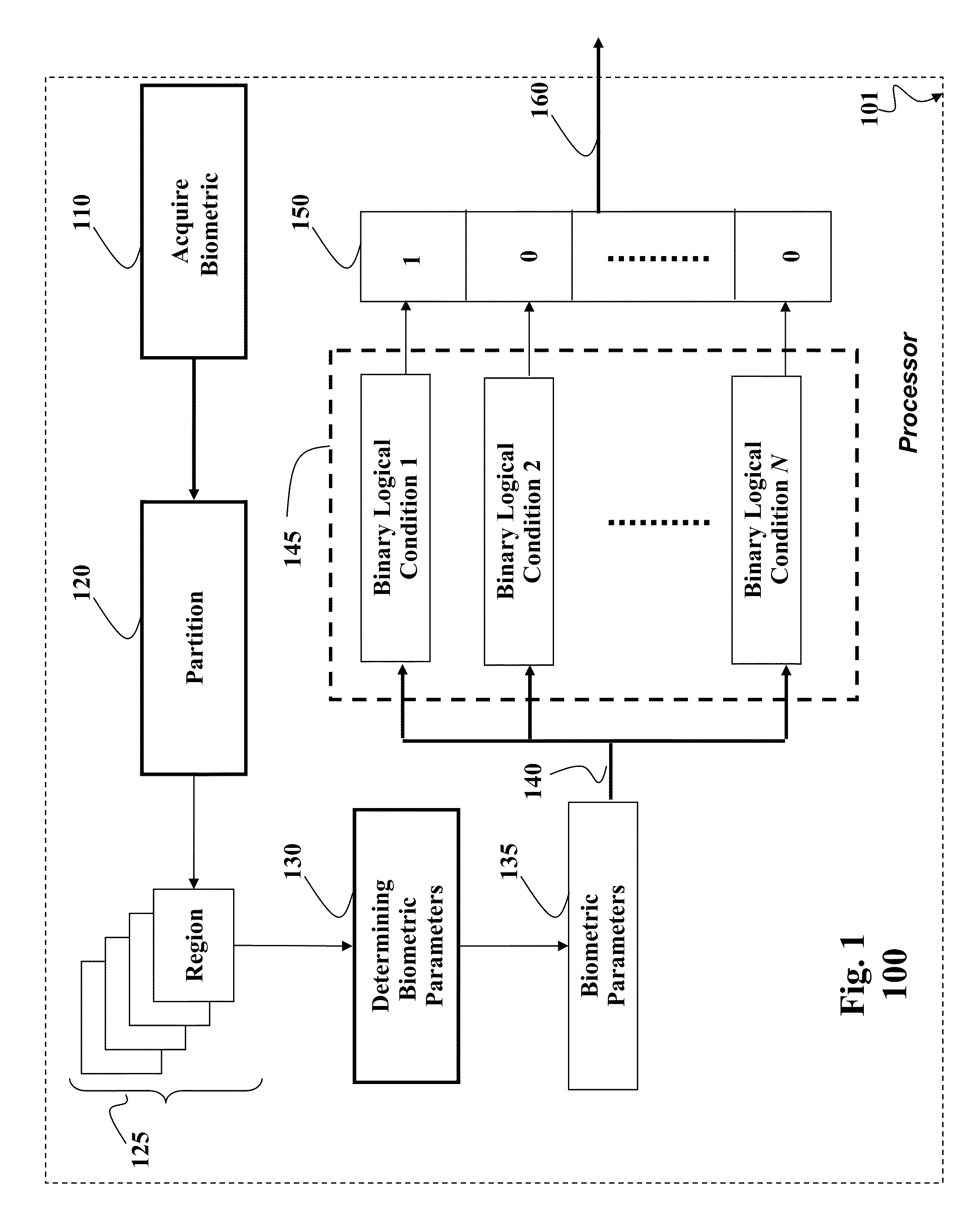

Pre-processing Biometric Parameters before Encoding and Decoding

ActiveUS20080235515A1Efficient modelingThe relationship is accurateAcquiring/recognising eyesComputer security arrangementsBiometric dataUser authentication

Biometric parameters acquired from human faces, voices, fingerprints, and irises are used for user authentication and access control. Because the biometric parameters are continuous and vary from one reading to the next, syndrome codes are applied to determine biometric syndrome vectors. The biometric syndrome vectors can be stored securely, while tolerating an inherent variability of biometric data. The stored biometric syndrome vector is decoded during user authentication using biometric parameters acquired at that time. The syndrome codes can also be used to encrypt and decrypt data. The biometric parameters can be pre-processed to form a binary representation, in which the binary representation has a set of predetermined statistical properties enforced imposed by a set of binary logical conditions.

Owner:MITSUBISHI ELECTRIC RES LAB INC

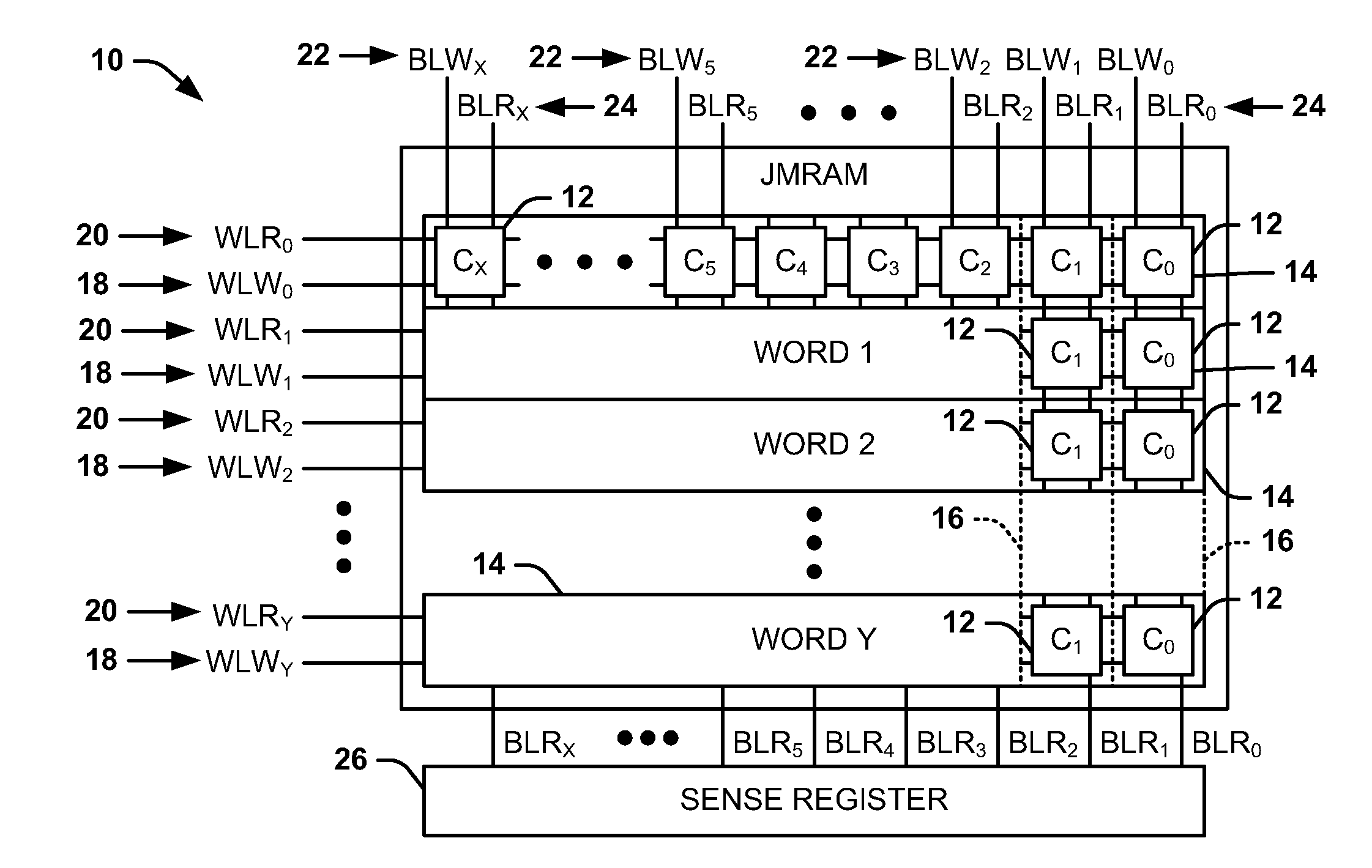

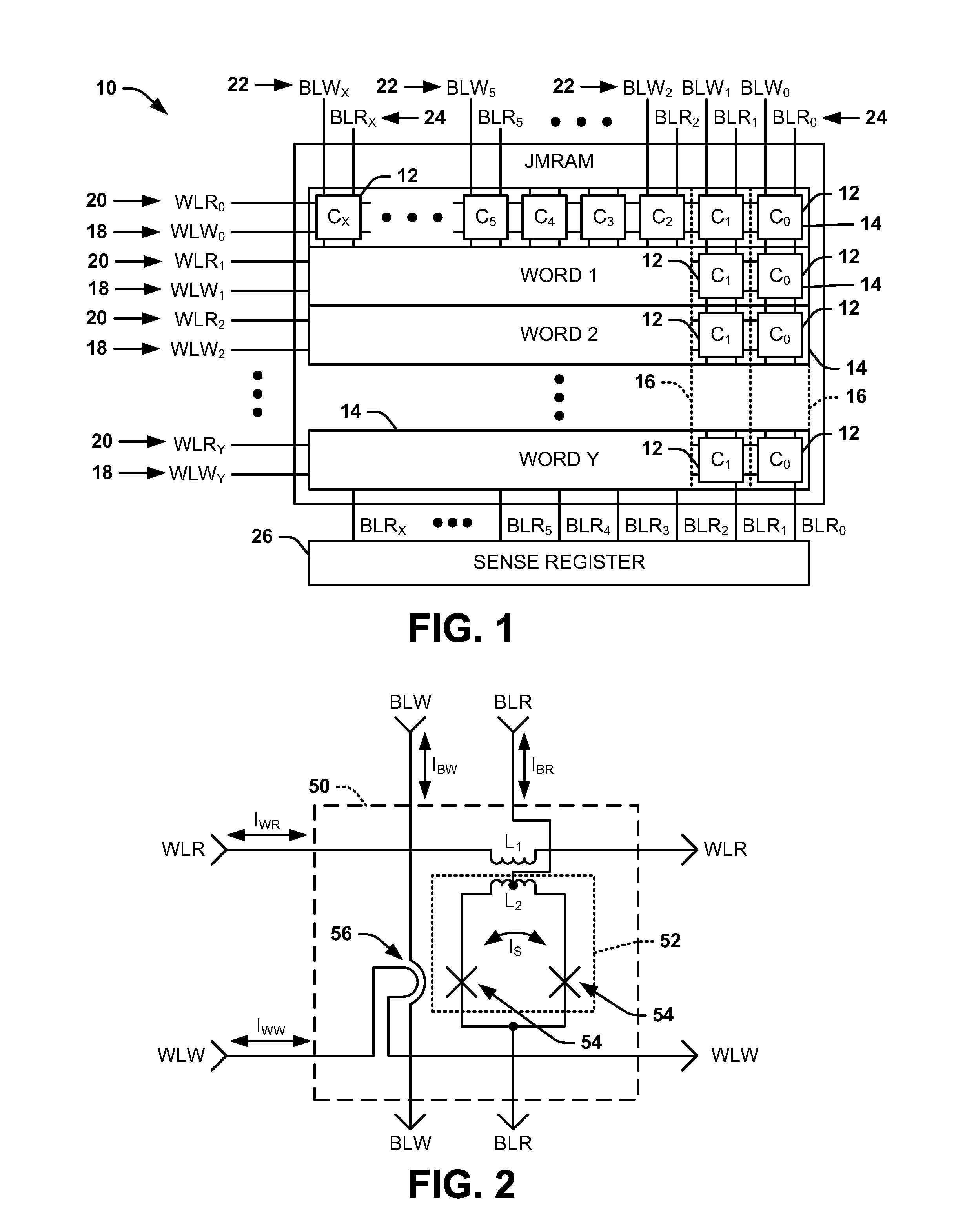

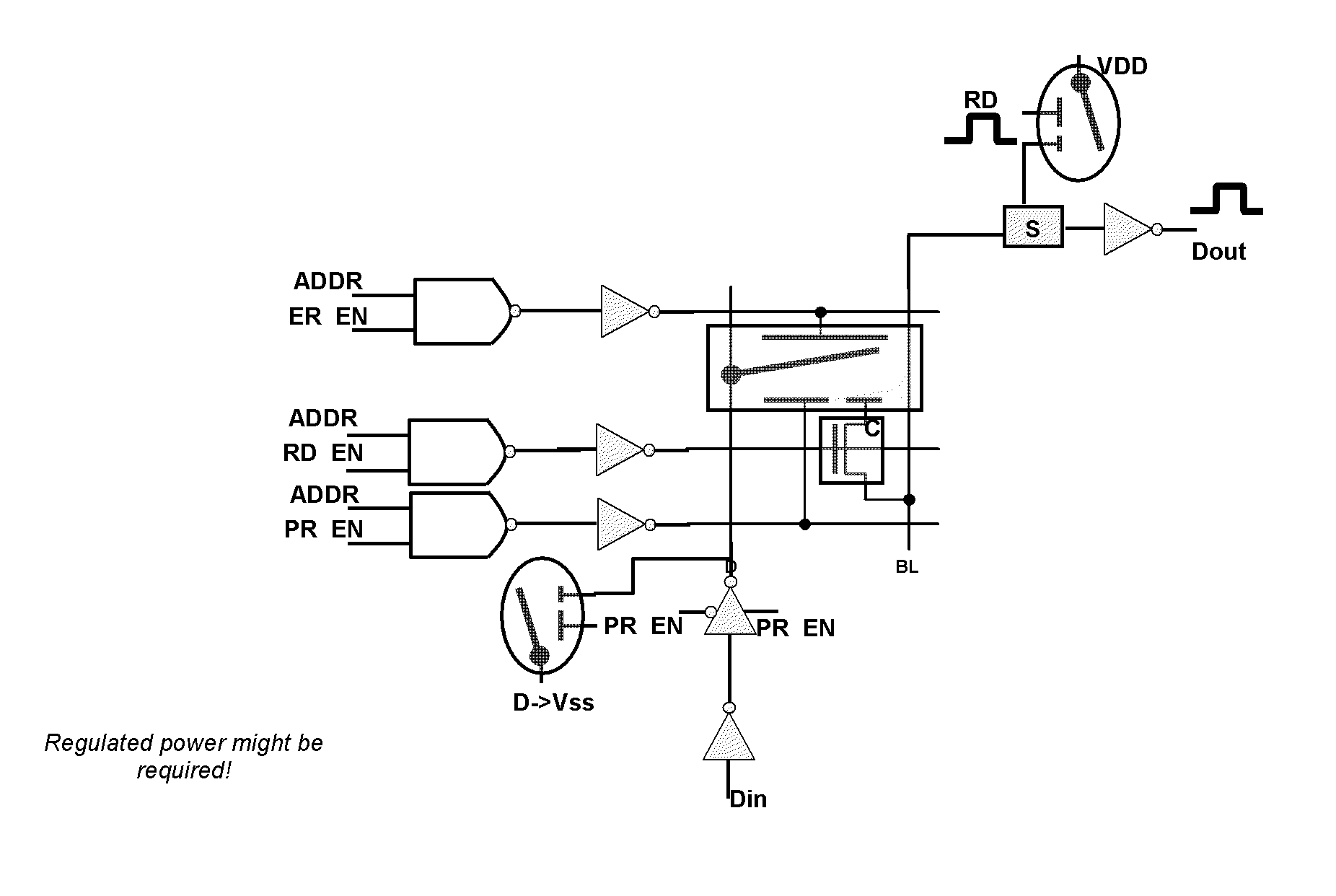

Josephson Magnetic Random Access Memory System and Method

One aspect of the present invention includes a Josephson magnetic random access memory (JMRAM) system. The system includes an array of memory cells arranged in rows and columns. Each of the memory cells includes an HMJJD that is configured to store a digital state corresponding to one of a binary logic-1 state and a binary logic-0 state in response to a word-write current that is provided on a word-write line and a bit-write current that is provided on a bit-write line. The HMJJD is also configured to output the respective digital state in response to a word-read current that is provided on a word-read line and a bit-read current that is provided on a bit-read line.

Owner:NORTHROP GRUMMAN SYST CORP

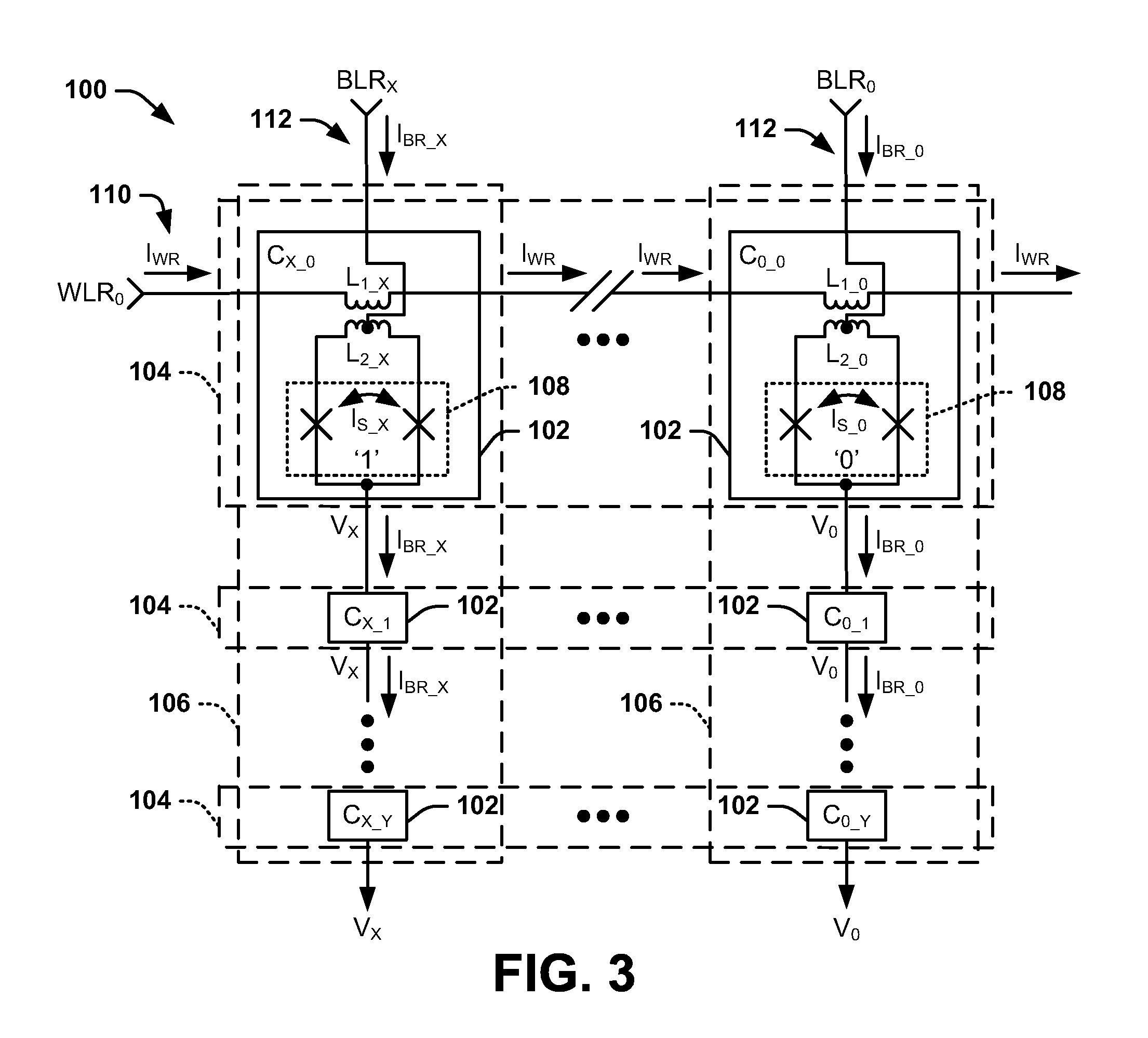

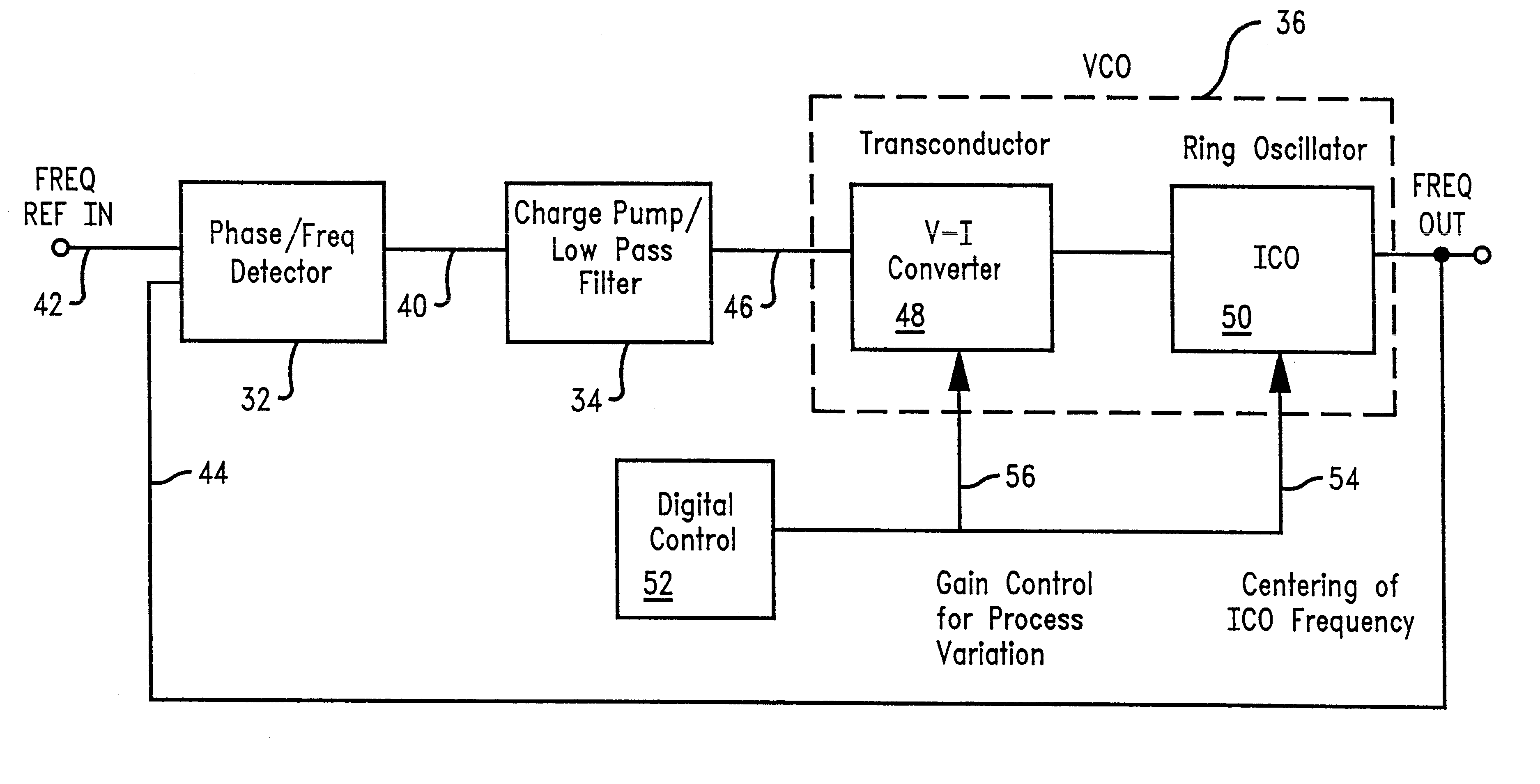

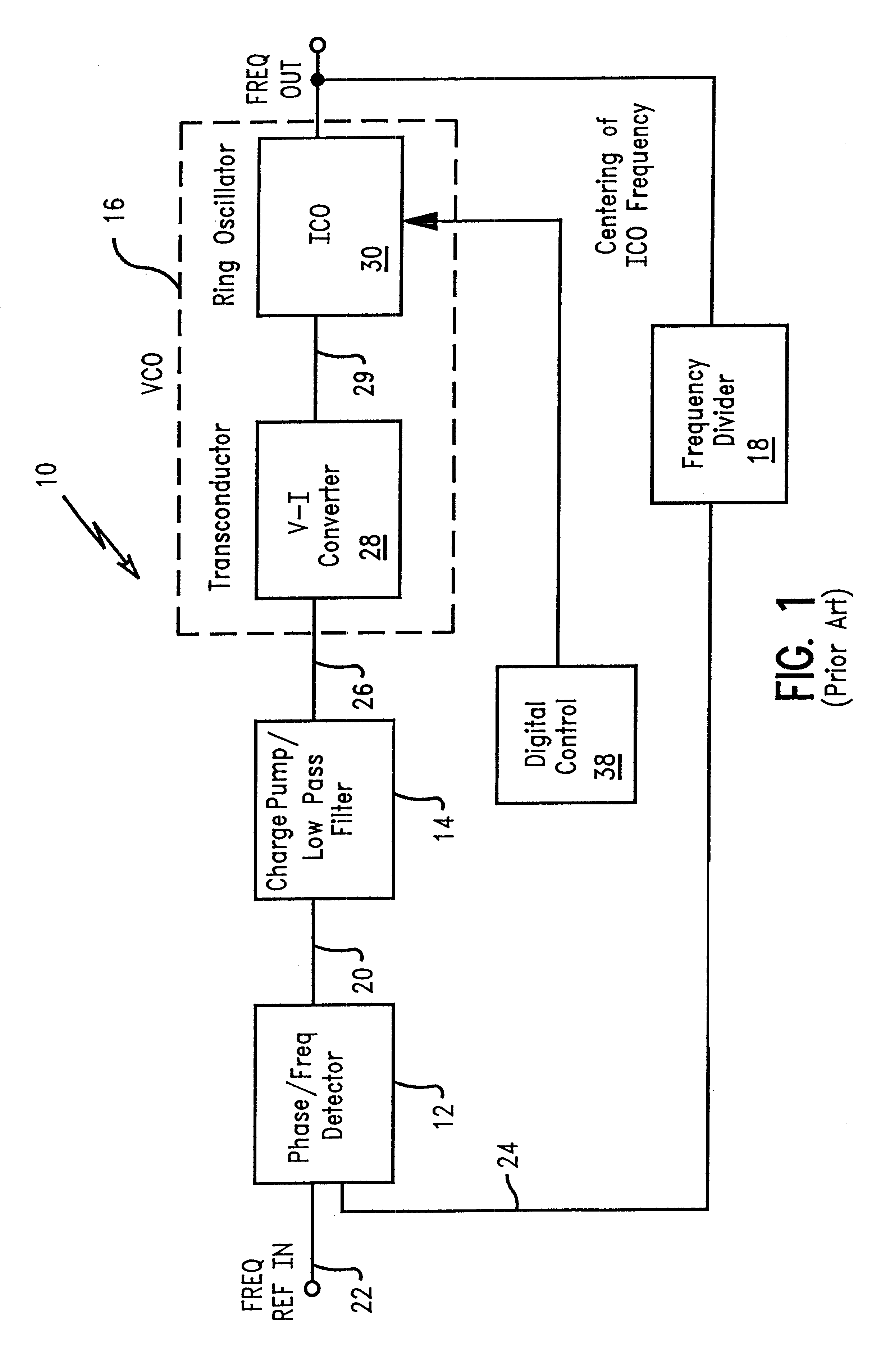

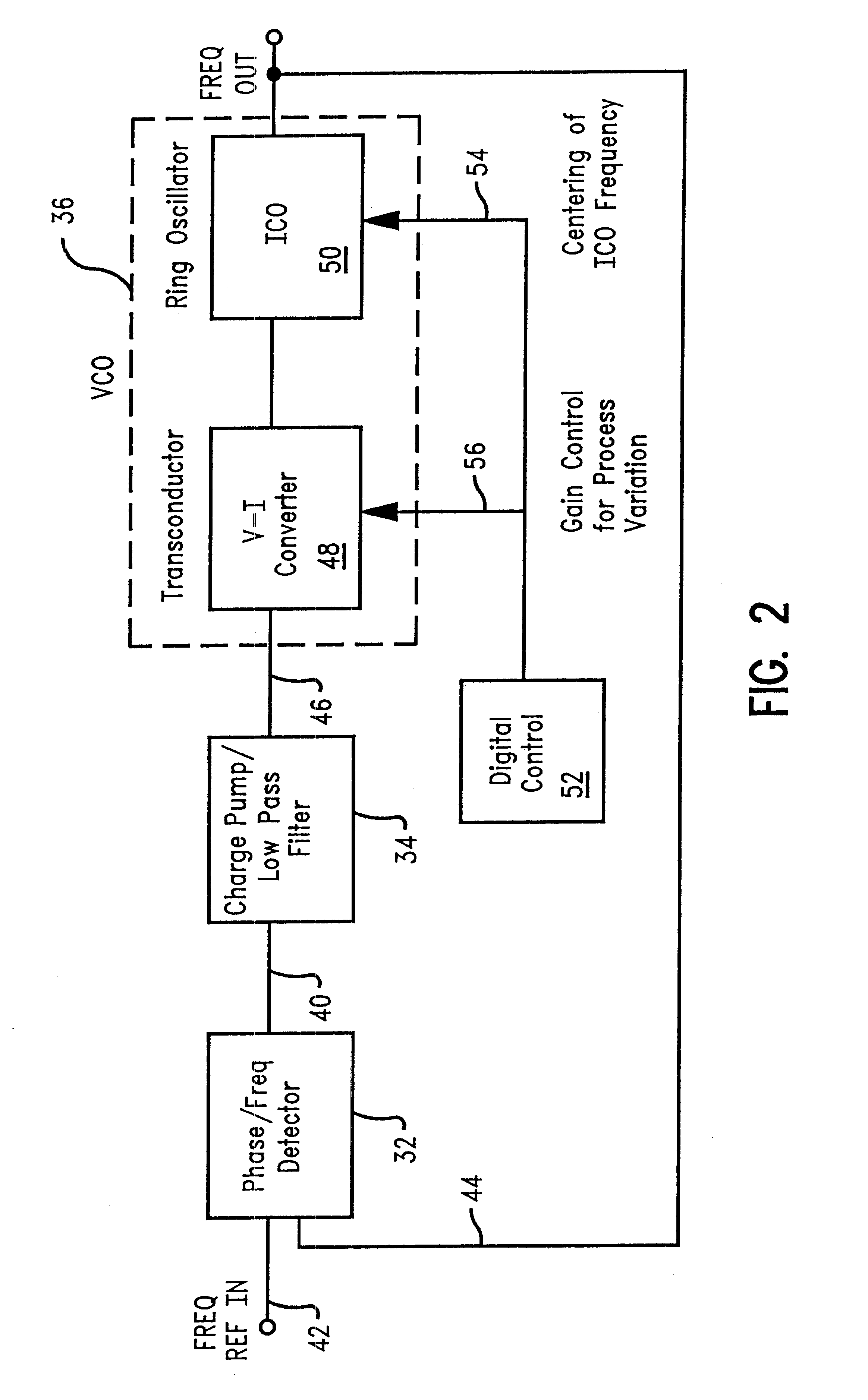

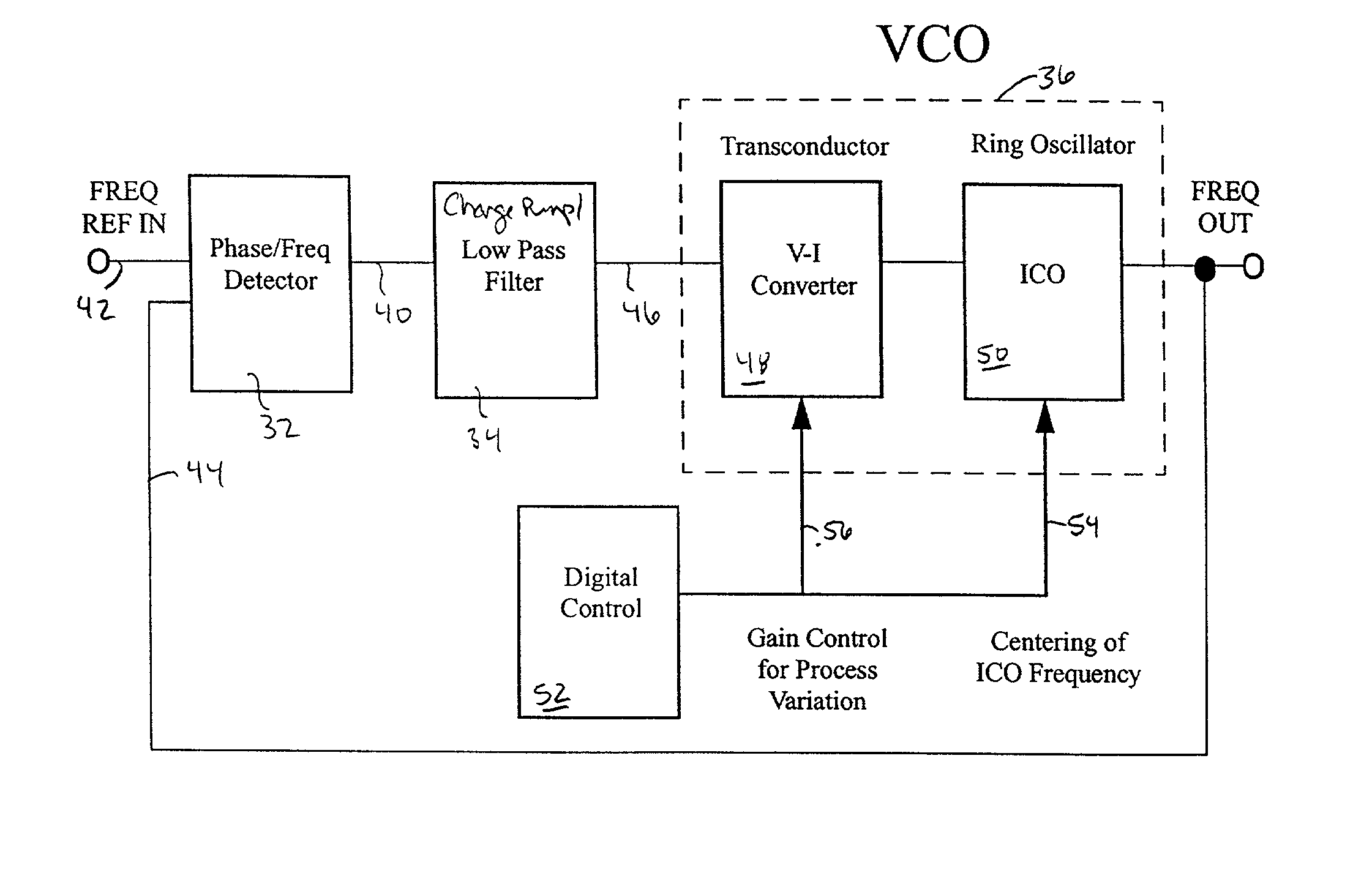

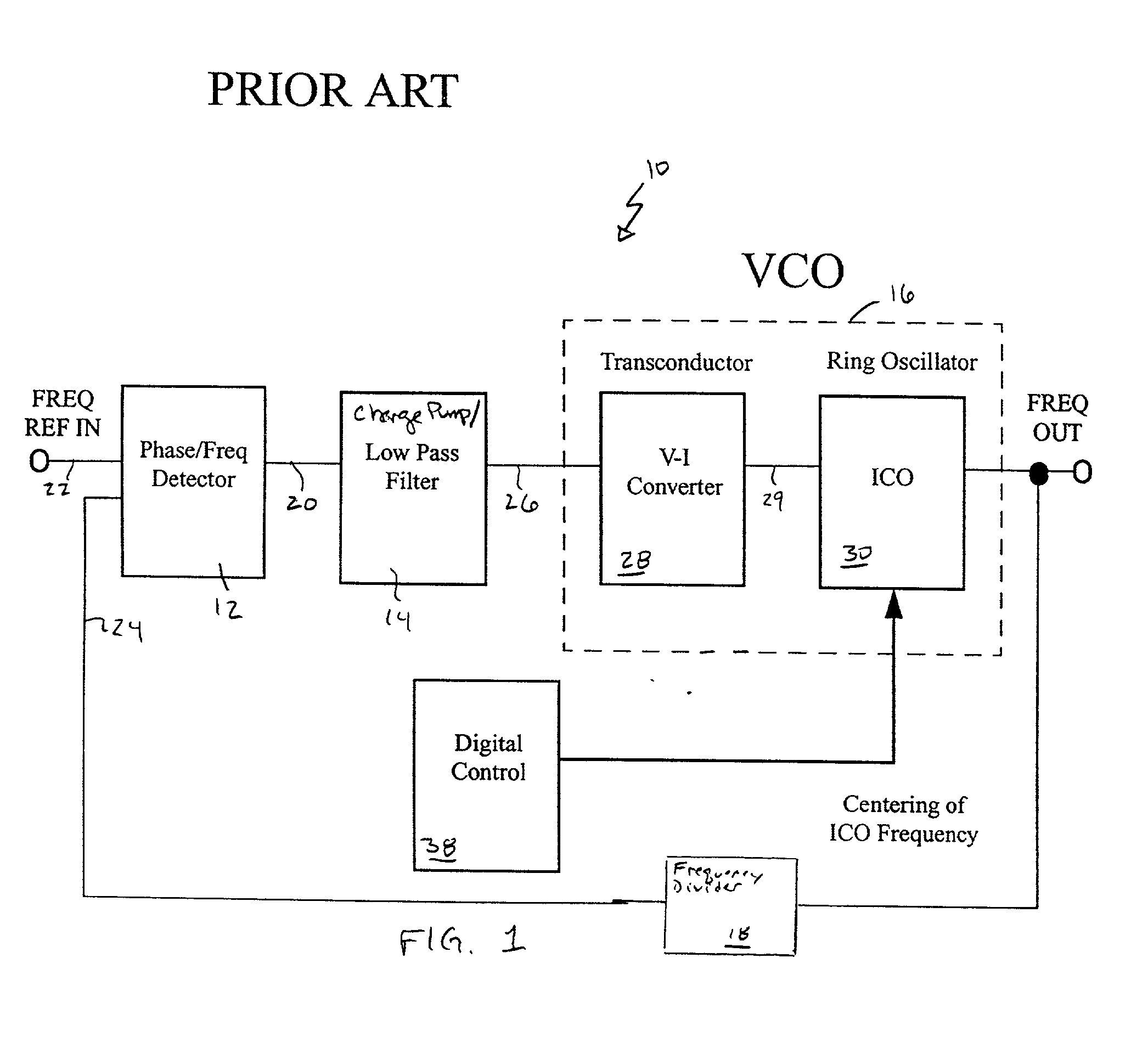

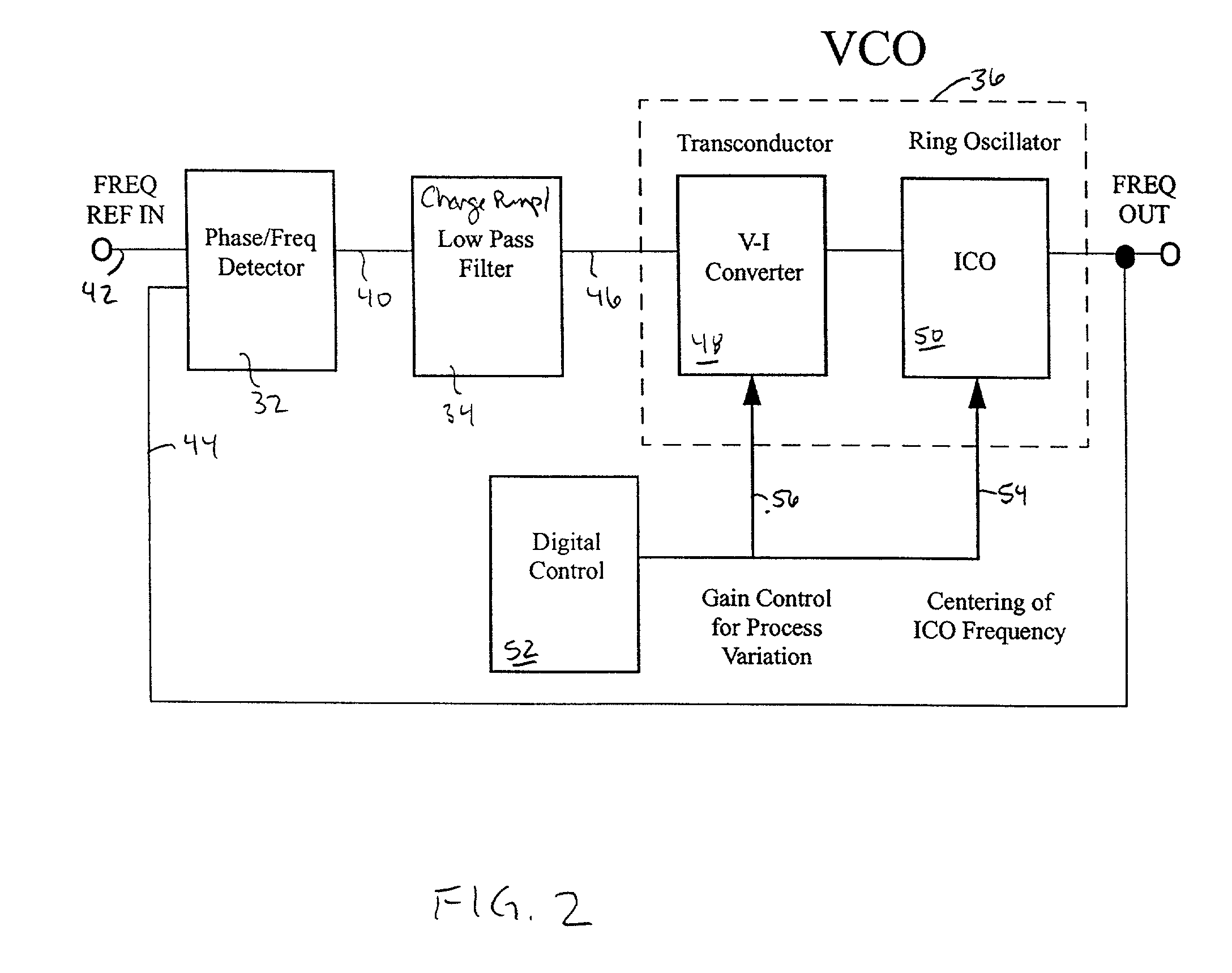

Linear voltage controlled oscillator transconductor with gain compensation

InactiveUS6466100B2More of the gainLess of the gainPulse automatic controlPulse generation by logic circuitsPhase locked loop circuitLow-pass filter

A voltage controlled oscillator of a phase locked loop circuit having digitally controlled gain compensation. The digital control circuitry provides binary logic input to the voltage controlled oscillator for a digitally controlled variable resistance circuit, a digitally controlled variable current transconductor circuit, or differential transistor pairs having mirrored circuitry for adjusting the V-I gain. The latter configuration requires the voltage controlled oscillator to incorporate a source-coupled differential pair which is driven by a low pass filter capacitor output voltage, and connected to load transistors; a current source and a current mirror for generating a tail current; individual banks of transistors to mirror the load transistor currents; a digital-to-analog converter with control lines outputted there from, the digital-to-analog converter used to increase the amount of current allowed to flow to the transconductor output, the current being digitally increased and decreased corresponding to an amount of current pulled from the current source, and mirroring the current through at least one transistor mirror circuit.

Owner:MARVELL ASIA PTE LTD

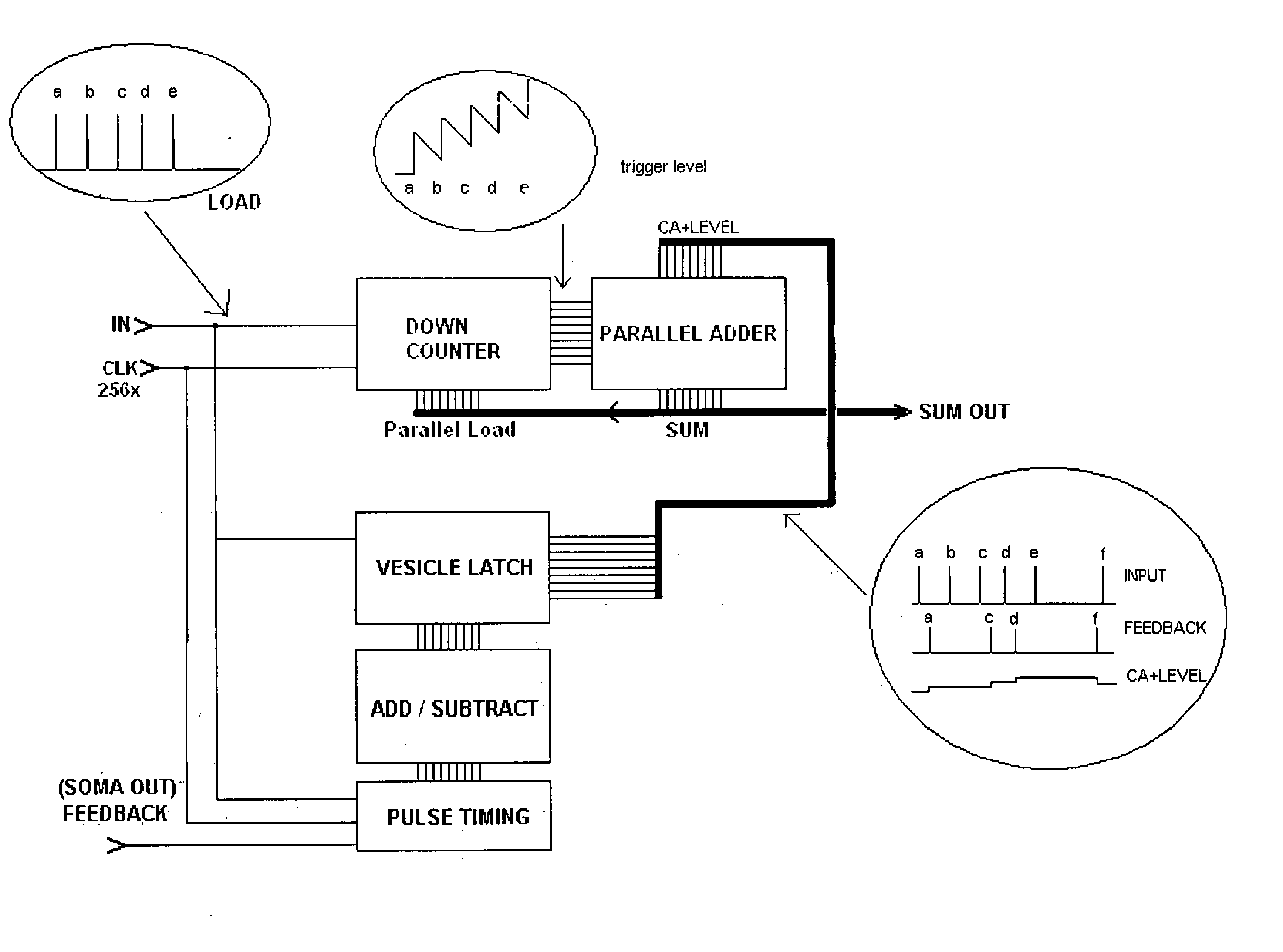

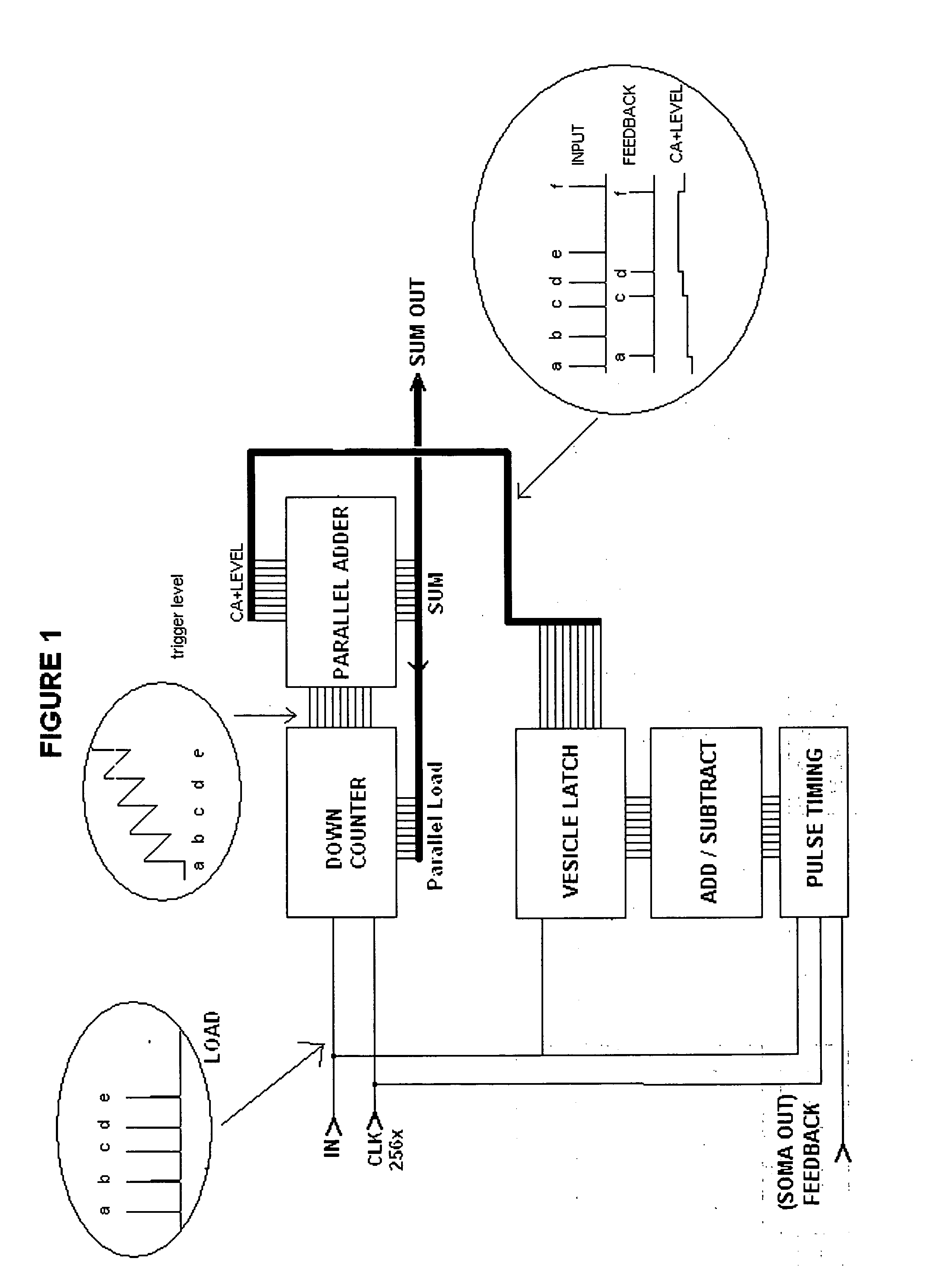

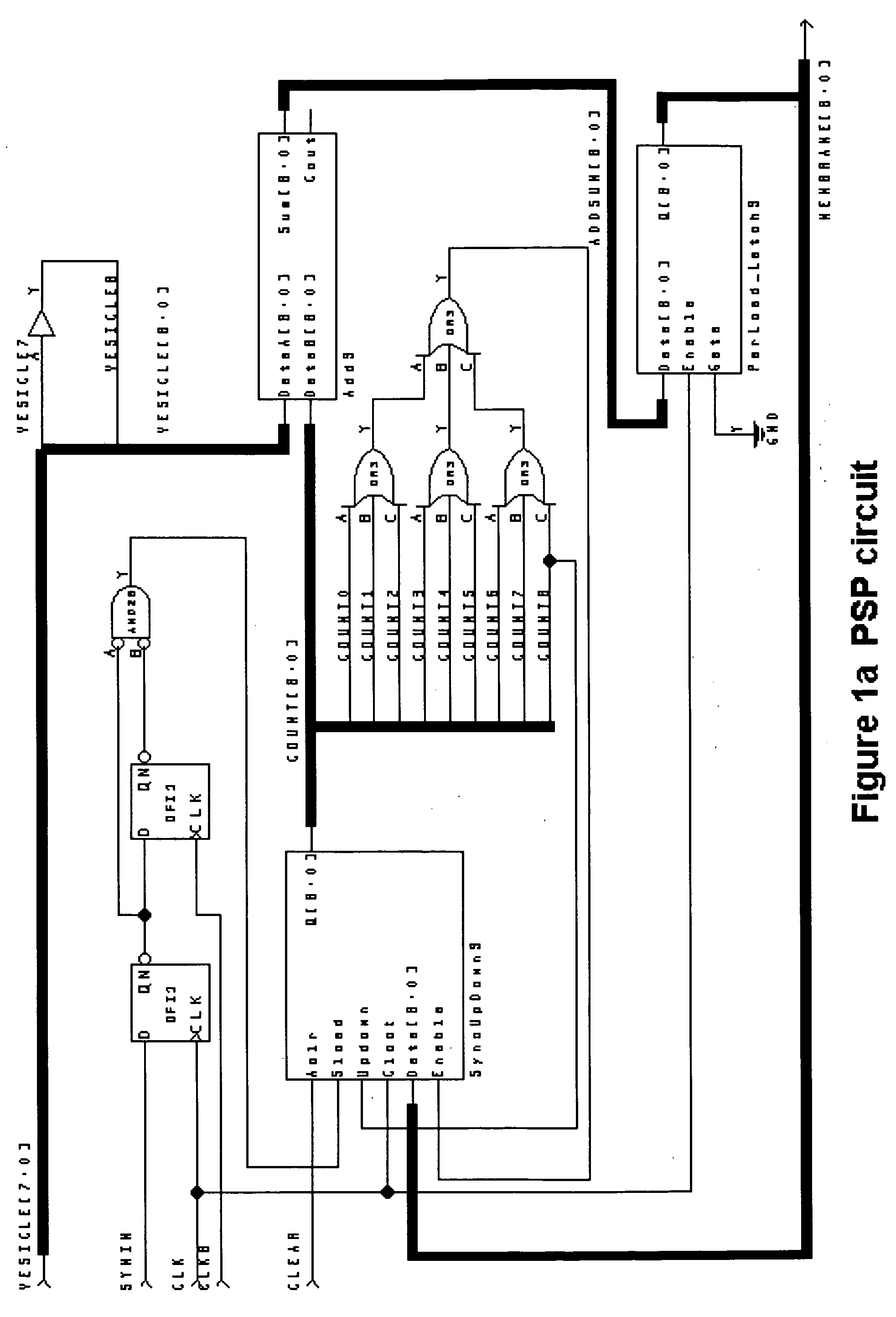

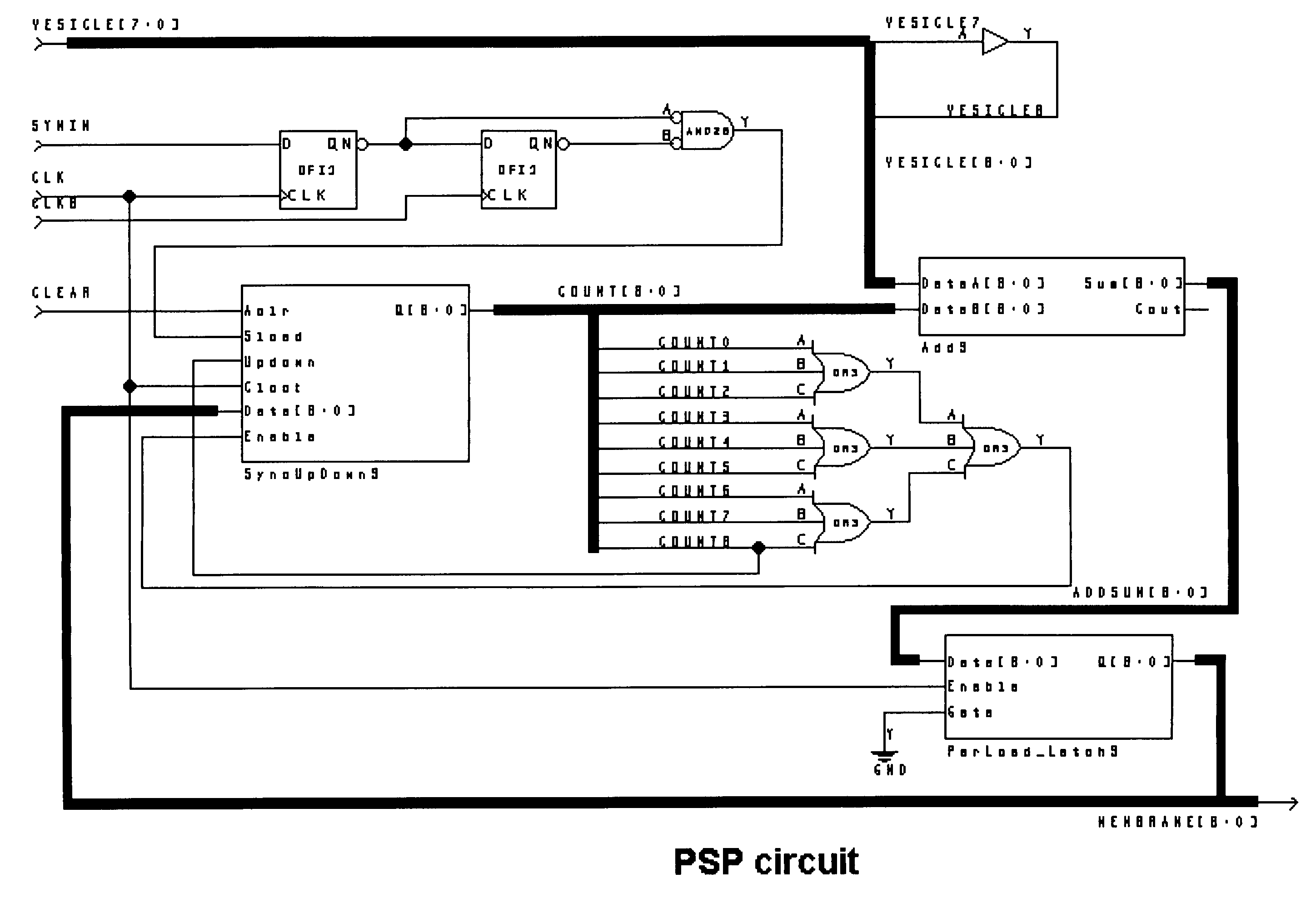

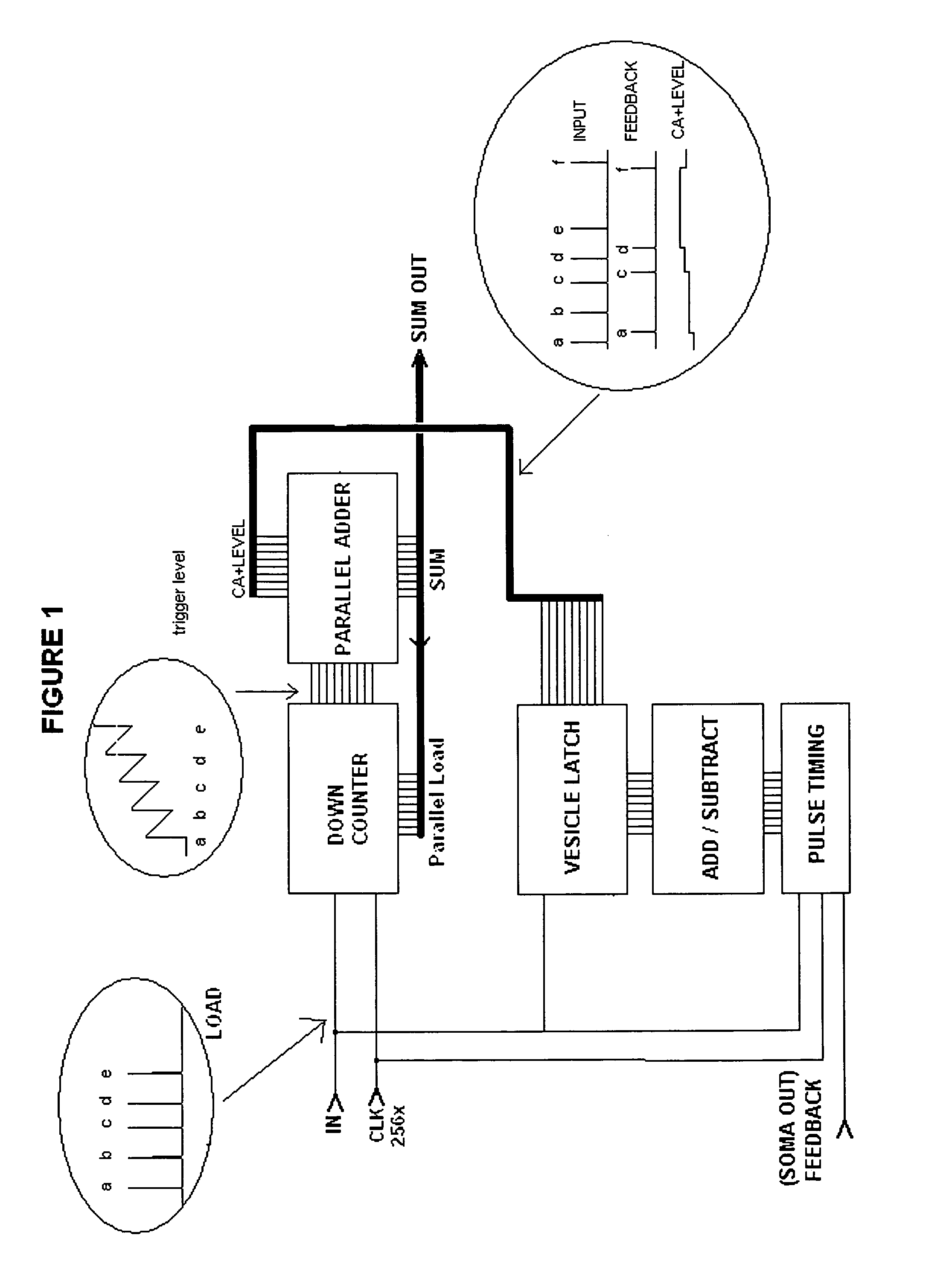

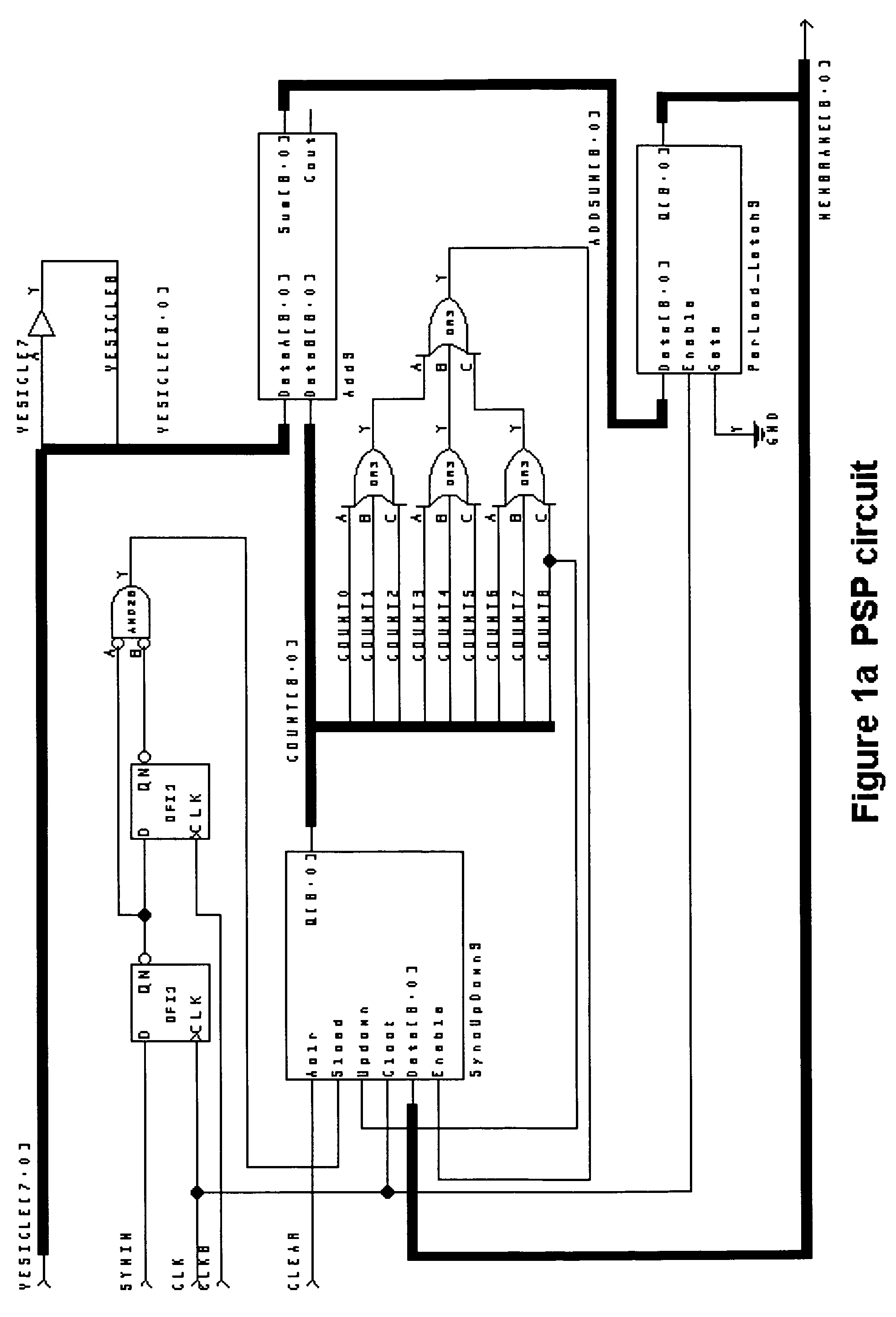

Autonomous Learning Dynamic Artificial Neural Computing Device and Brain Inspired System

ActiveUS20100076916A1Digital computer detailsAnalogue computers for chemical processesInformation processingNervous system

A hierarchical information processing system is disclosed having a plurality of artificial neurons, comprised of binary logic gates, and interconnected through a second plurality of dynamic artificial synapses, intended to simulate or extend the function of a biological nervous system. The system is capable of approximation, autonomous learning and strengthening of formerly learned input patterns. The system learns by simulated Synaptic Time Dependent Plasticity, commonly abbreviated to STDP. Each artificial neuron consisting of a soma circuit and a plurality of synapse circuits, whereby the soma membrane potential, the soma threshold value, the synapse strength and the Post Synaptic Potential at each synapse are expressed as values in binary registers, which are dynamically determined from certain aspects of input pulse timing, previous strength value and output pulse feedback.

Owner:BRAINCHIP INC

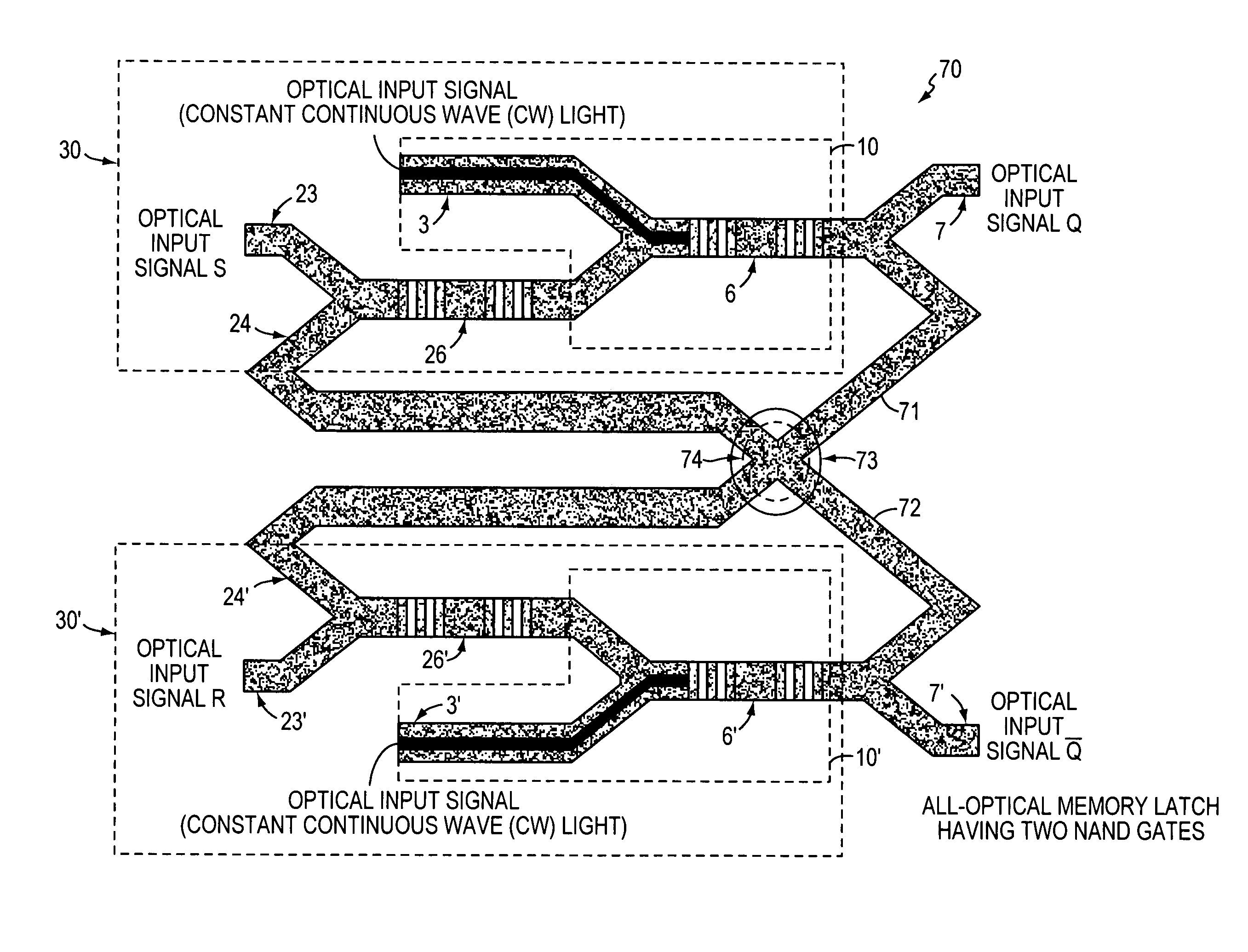

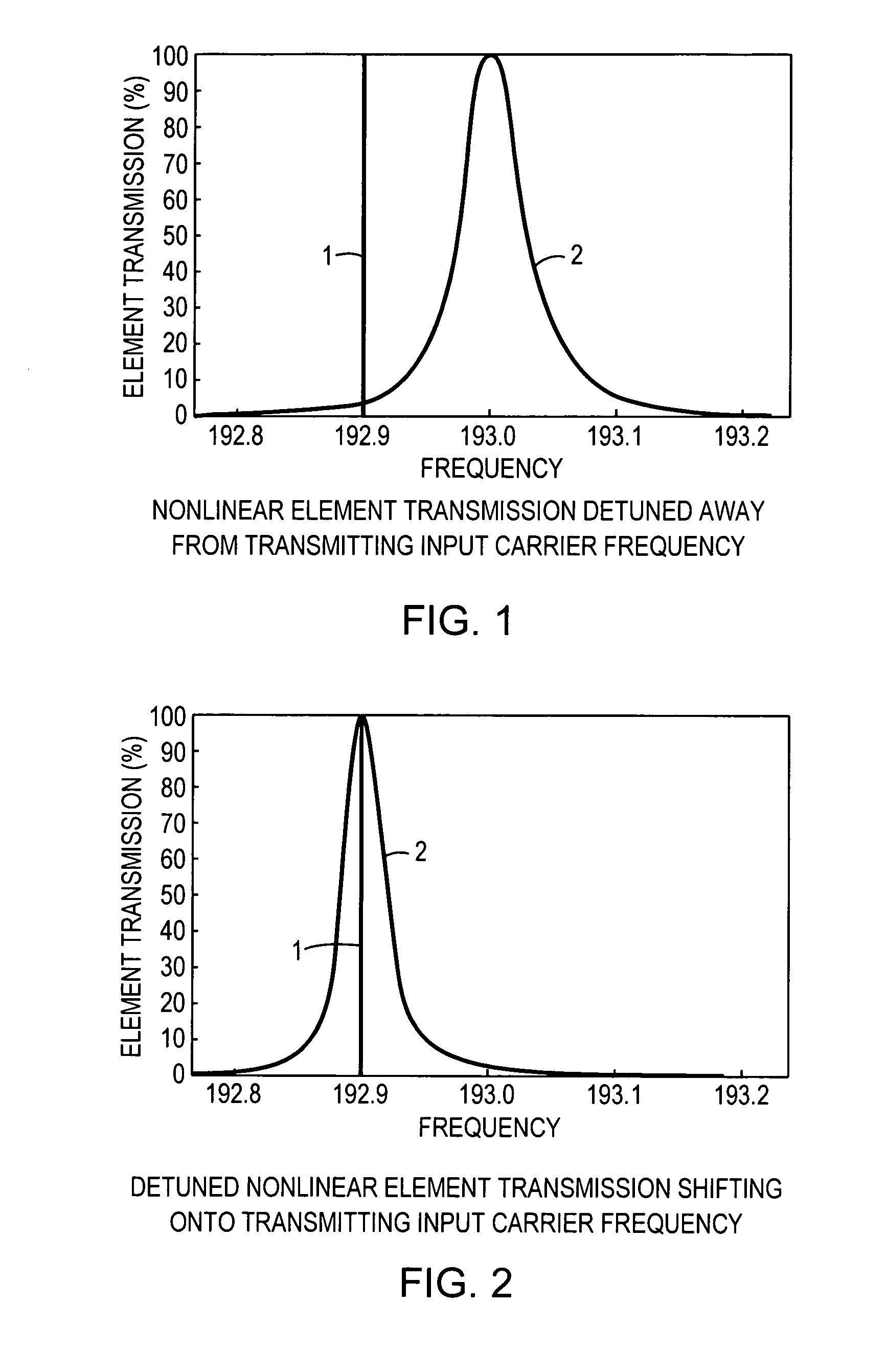

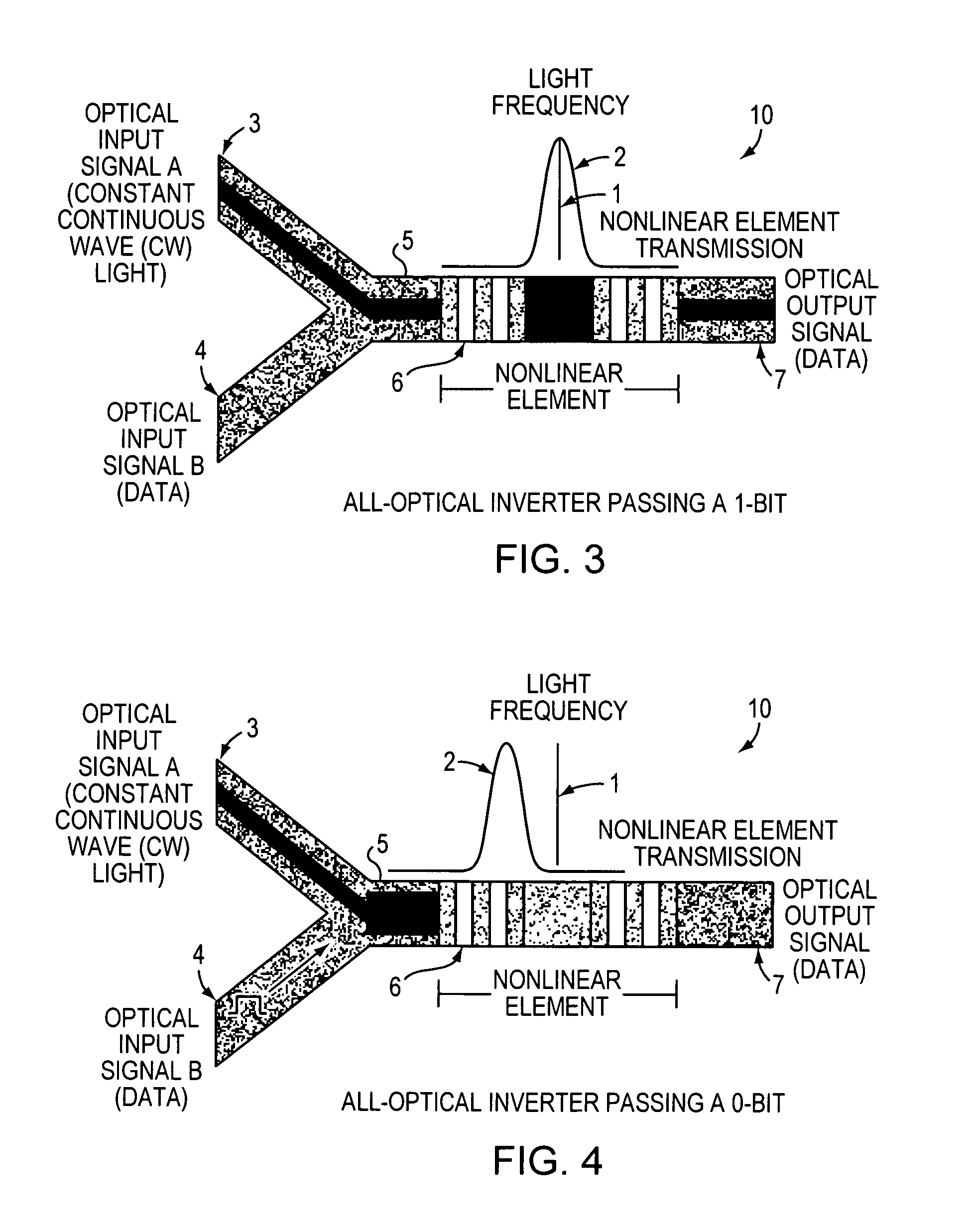

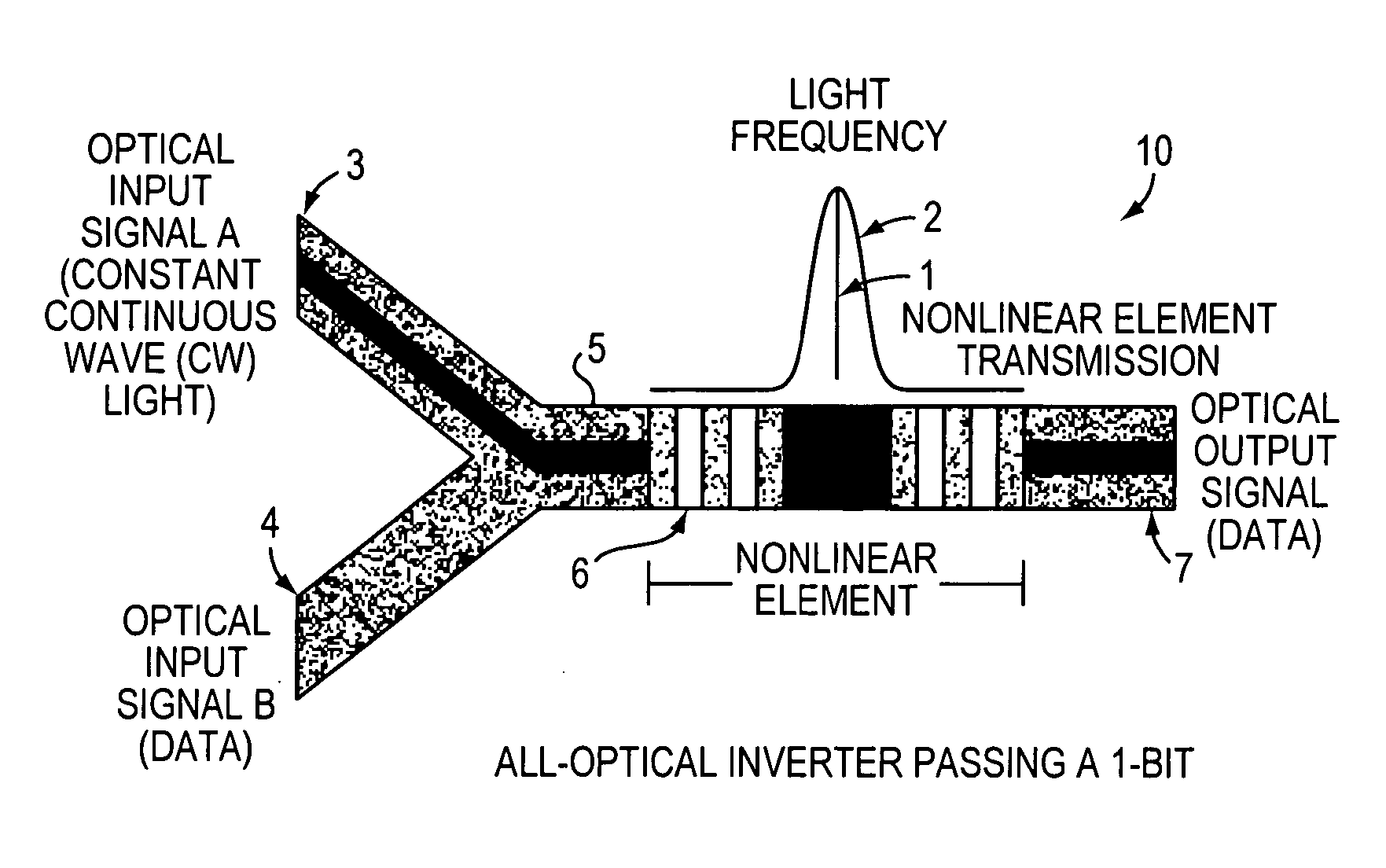

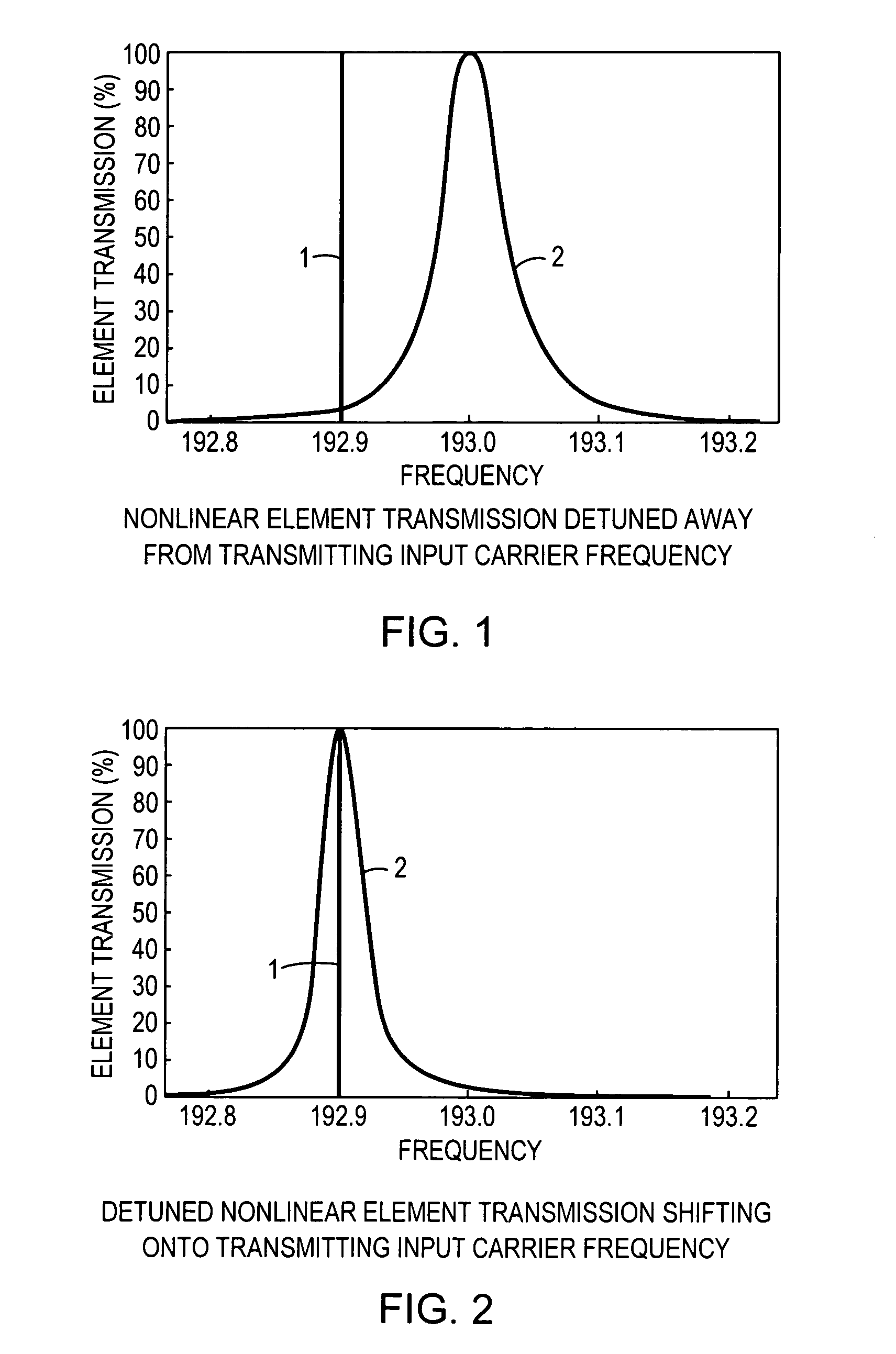

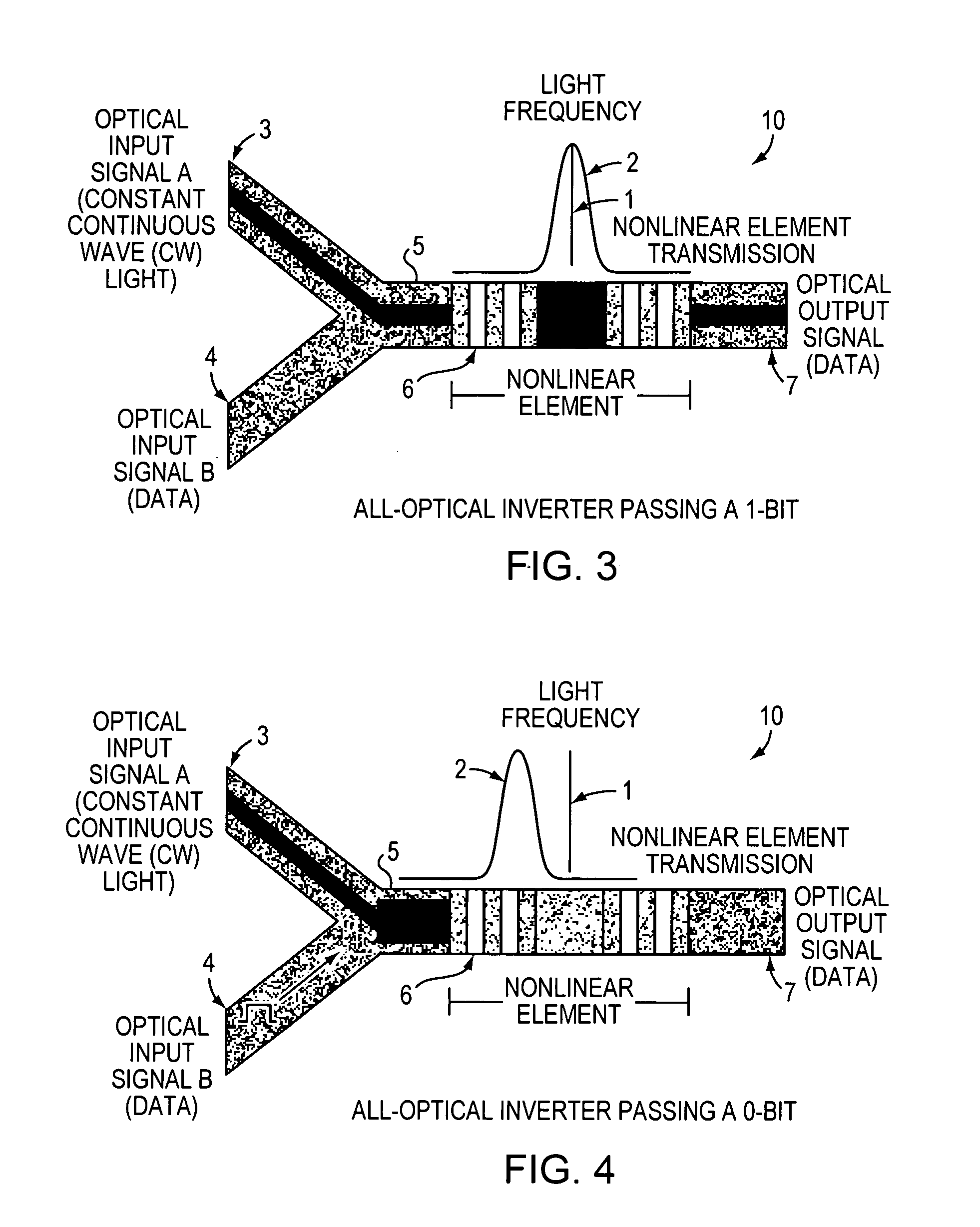

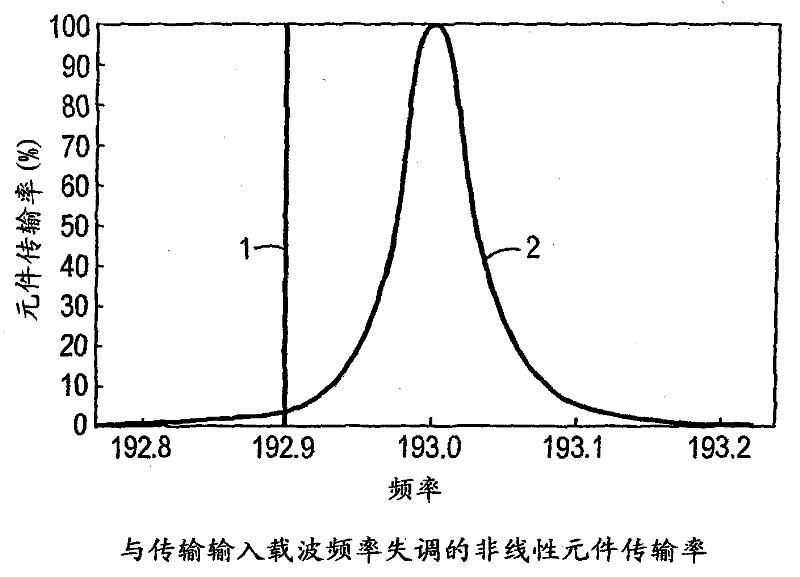

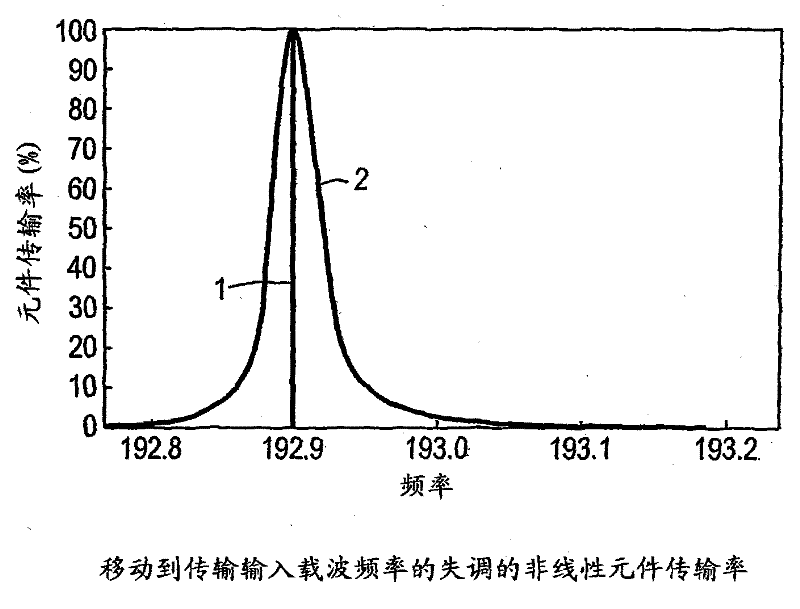

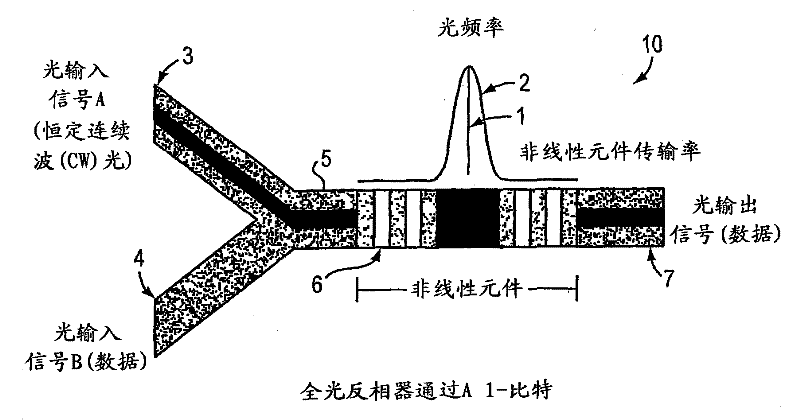

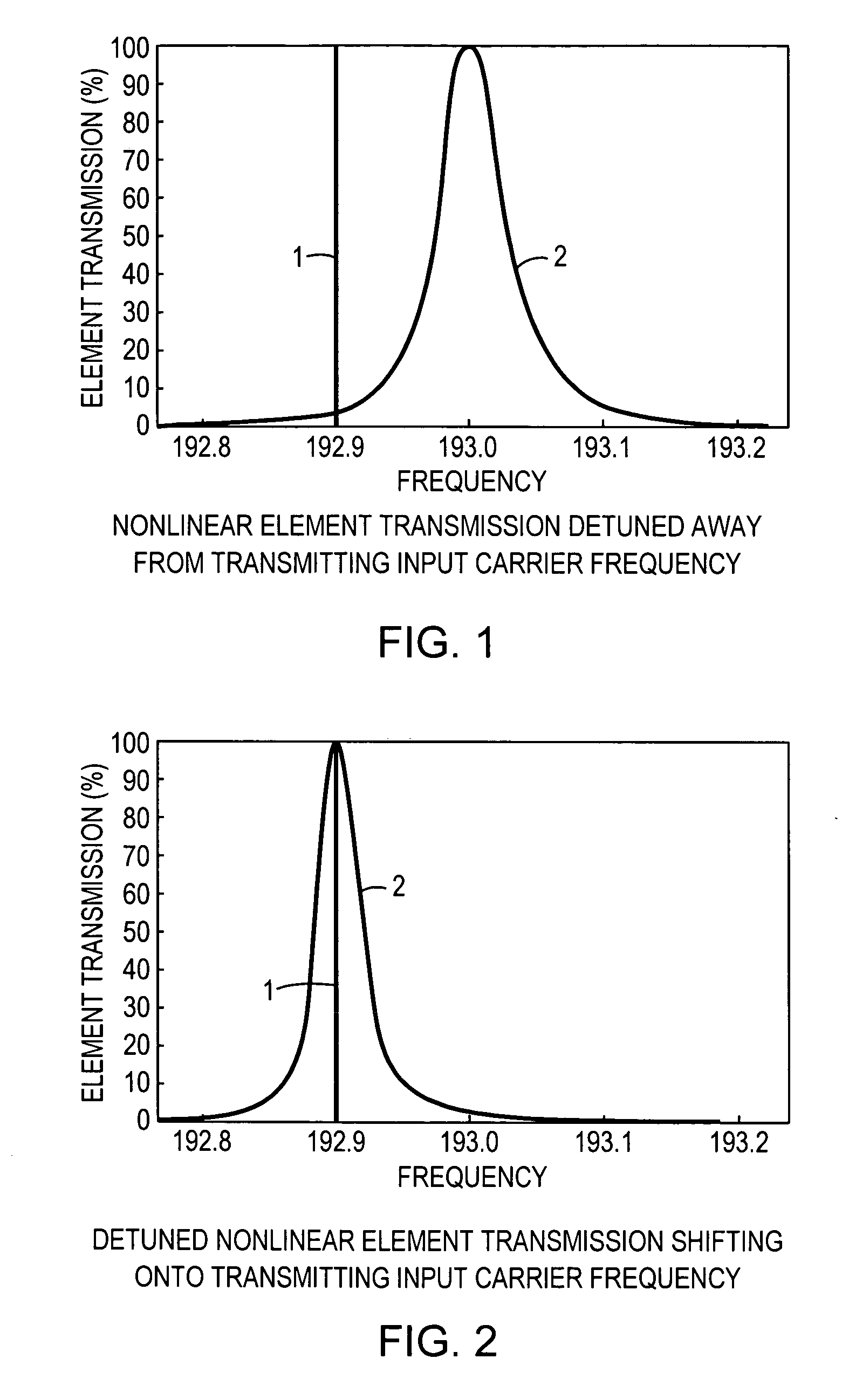

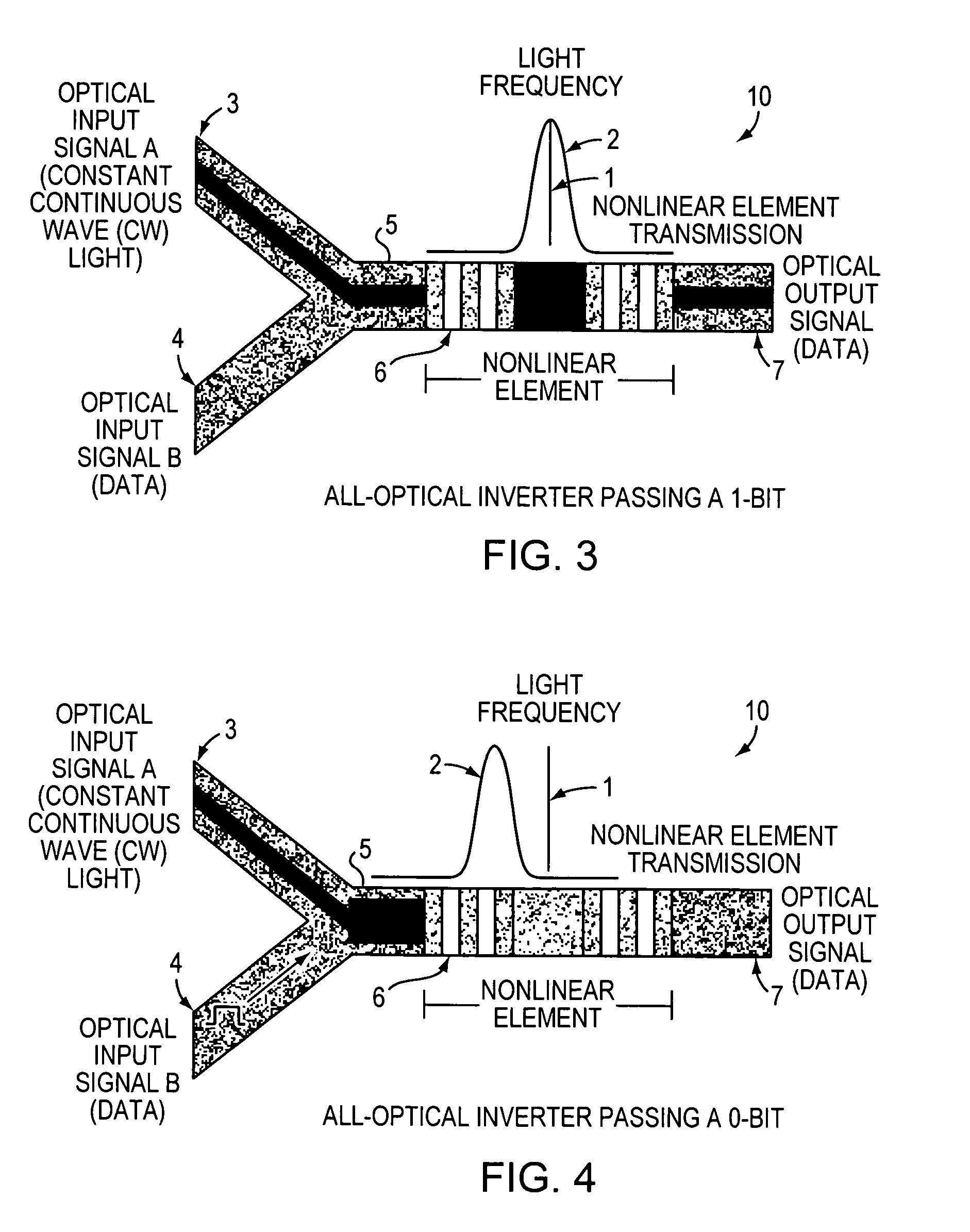

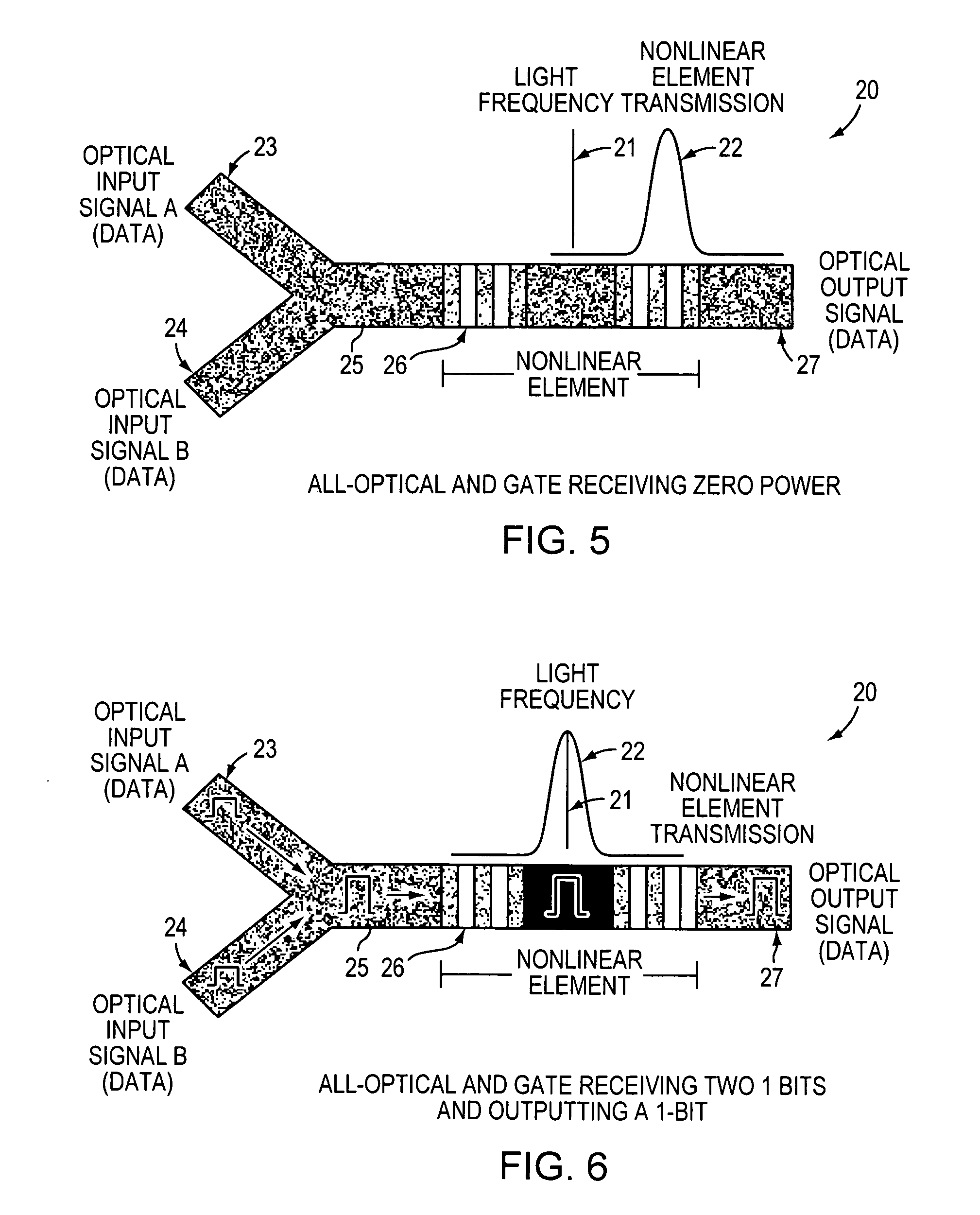

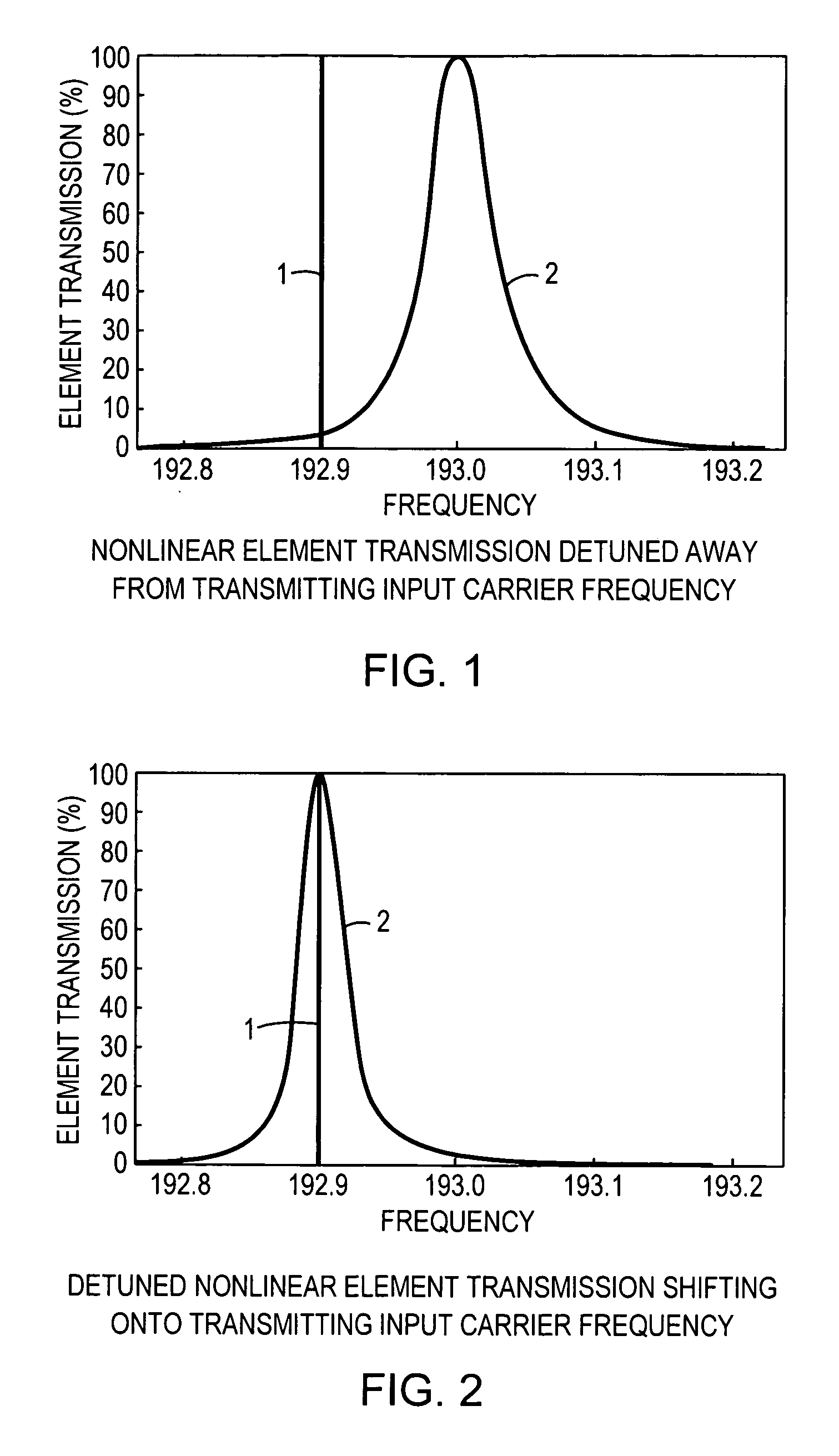

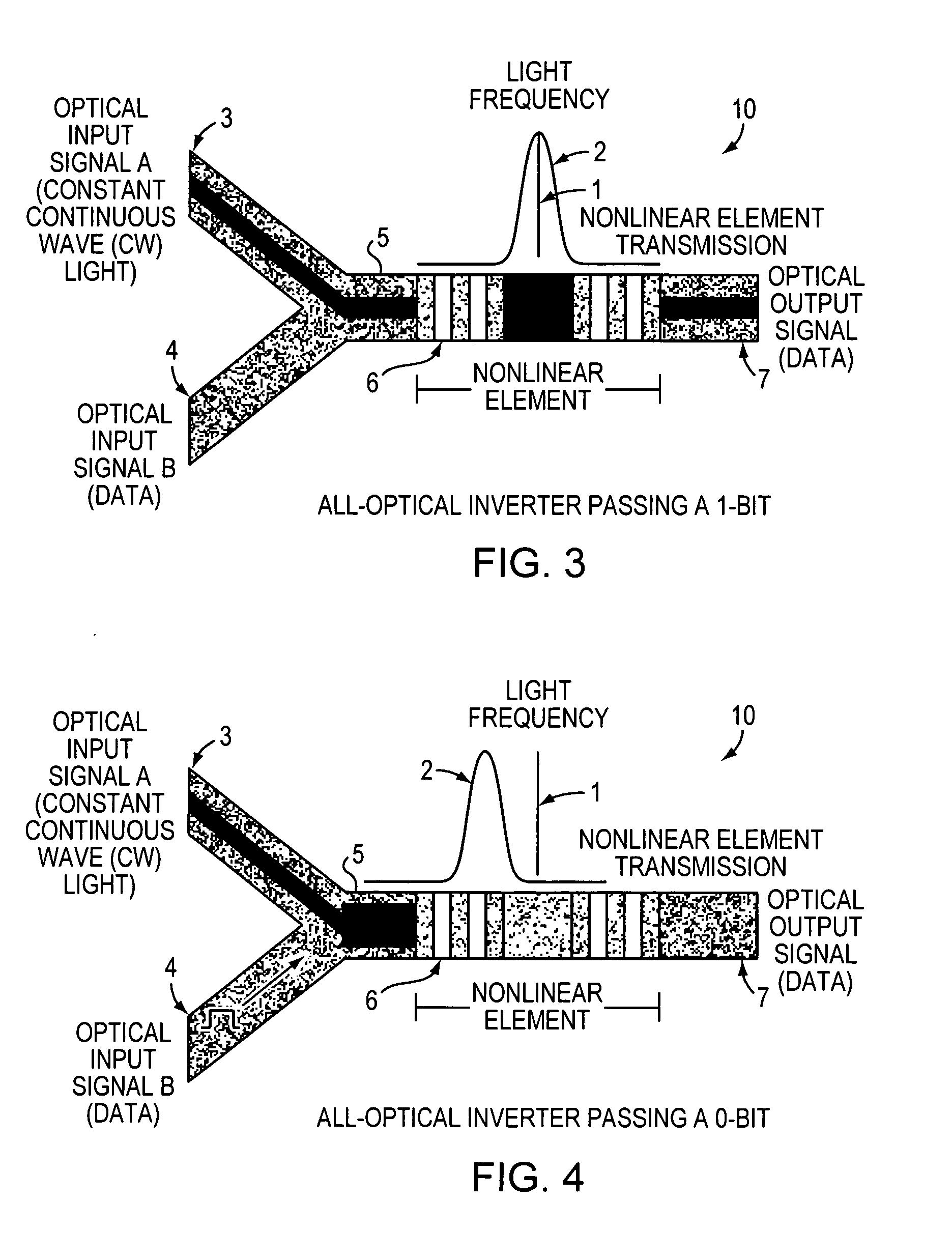

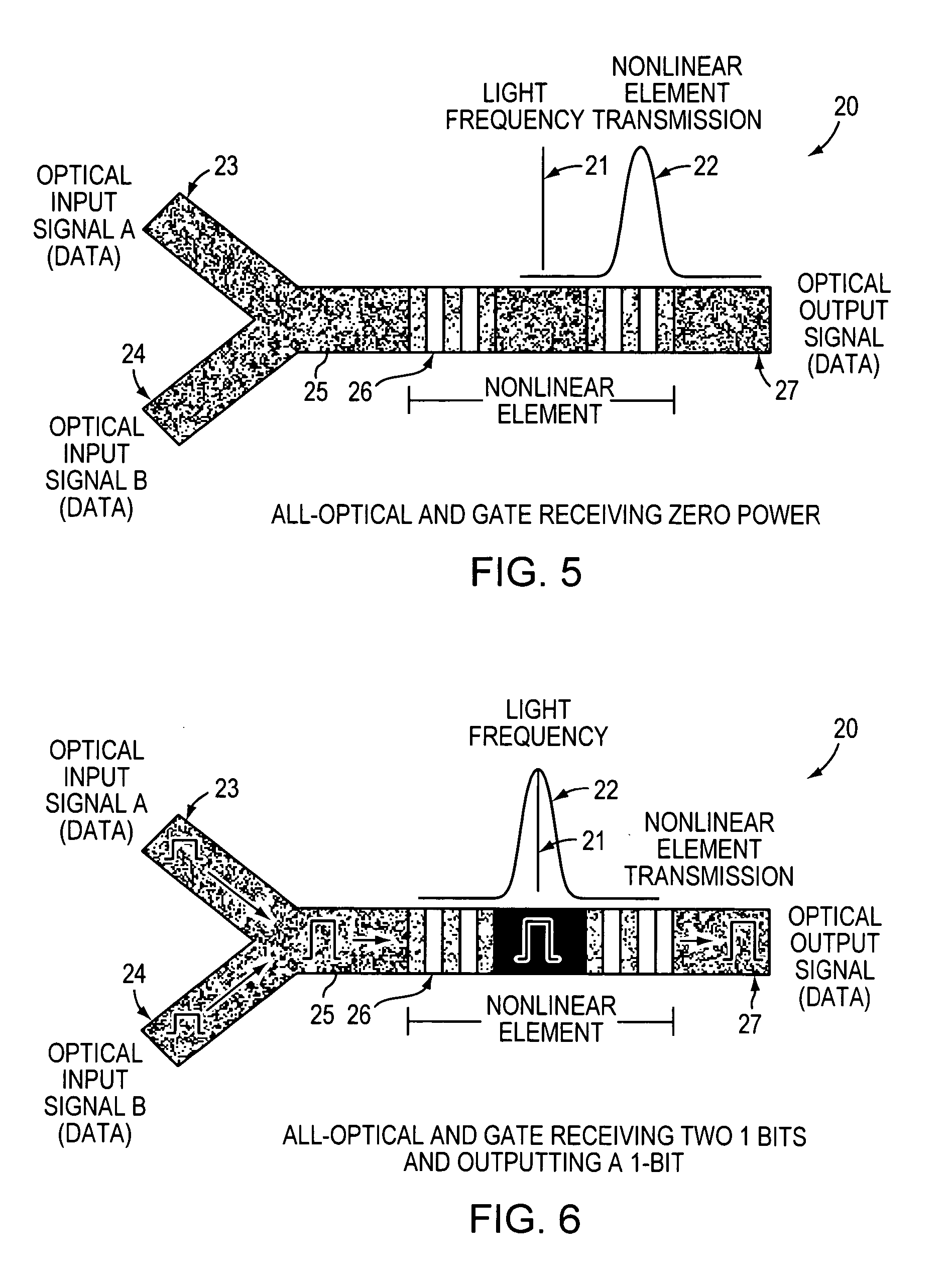

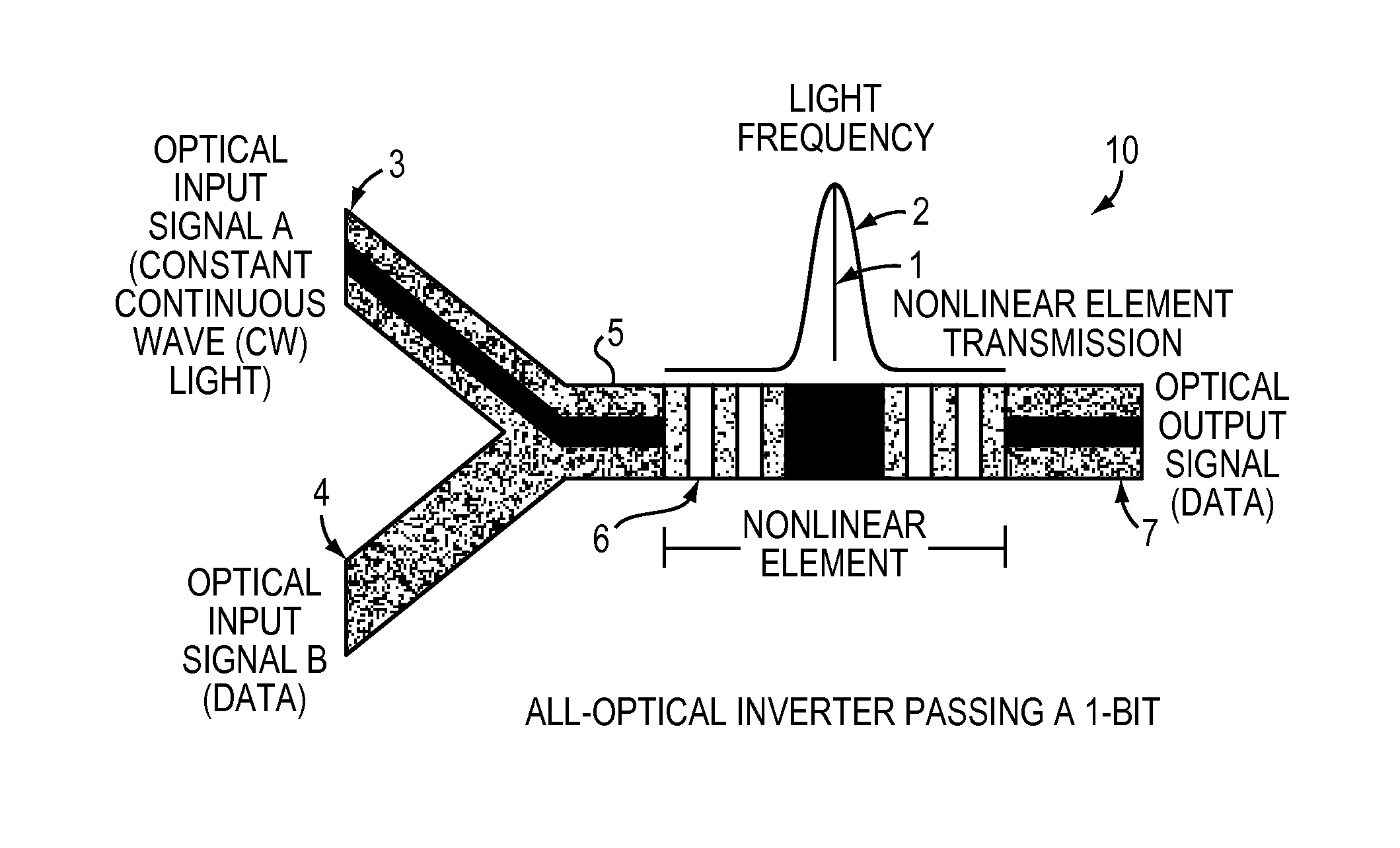

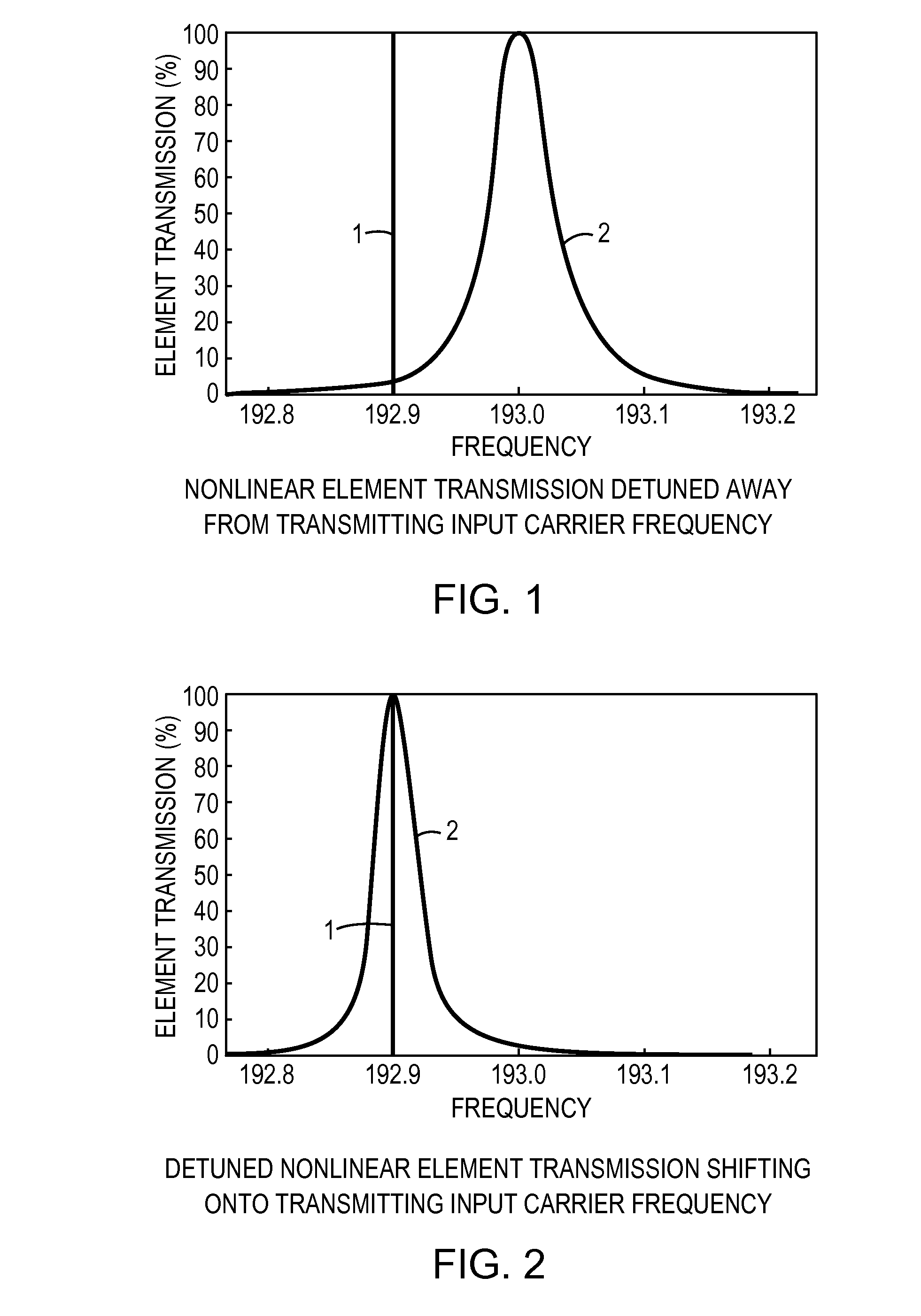

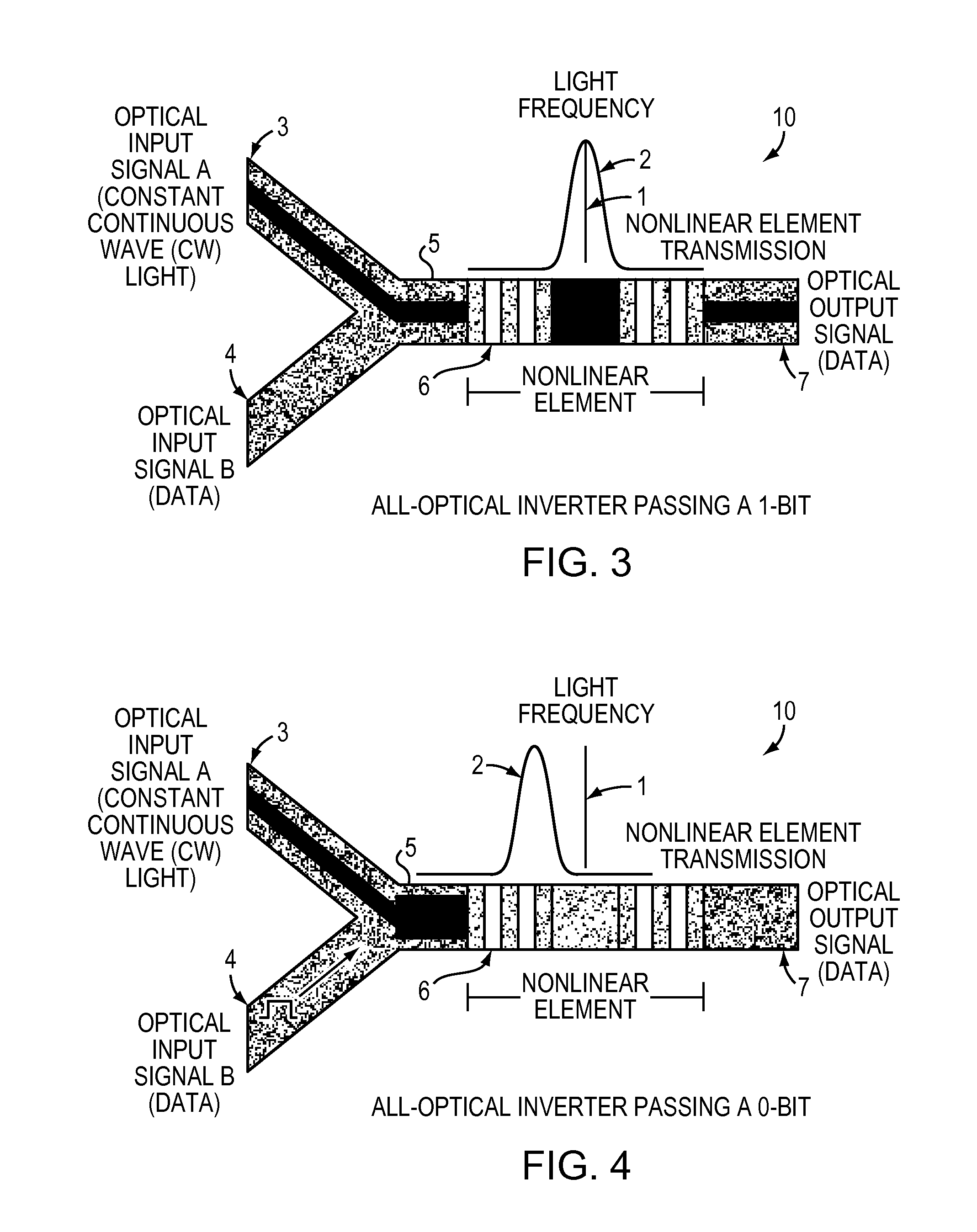

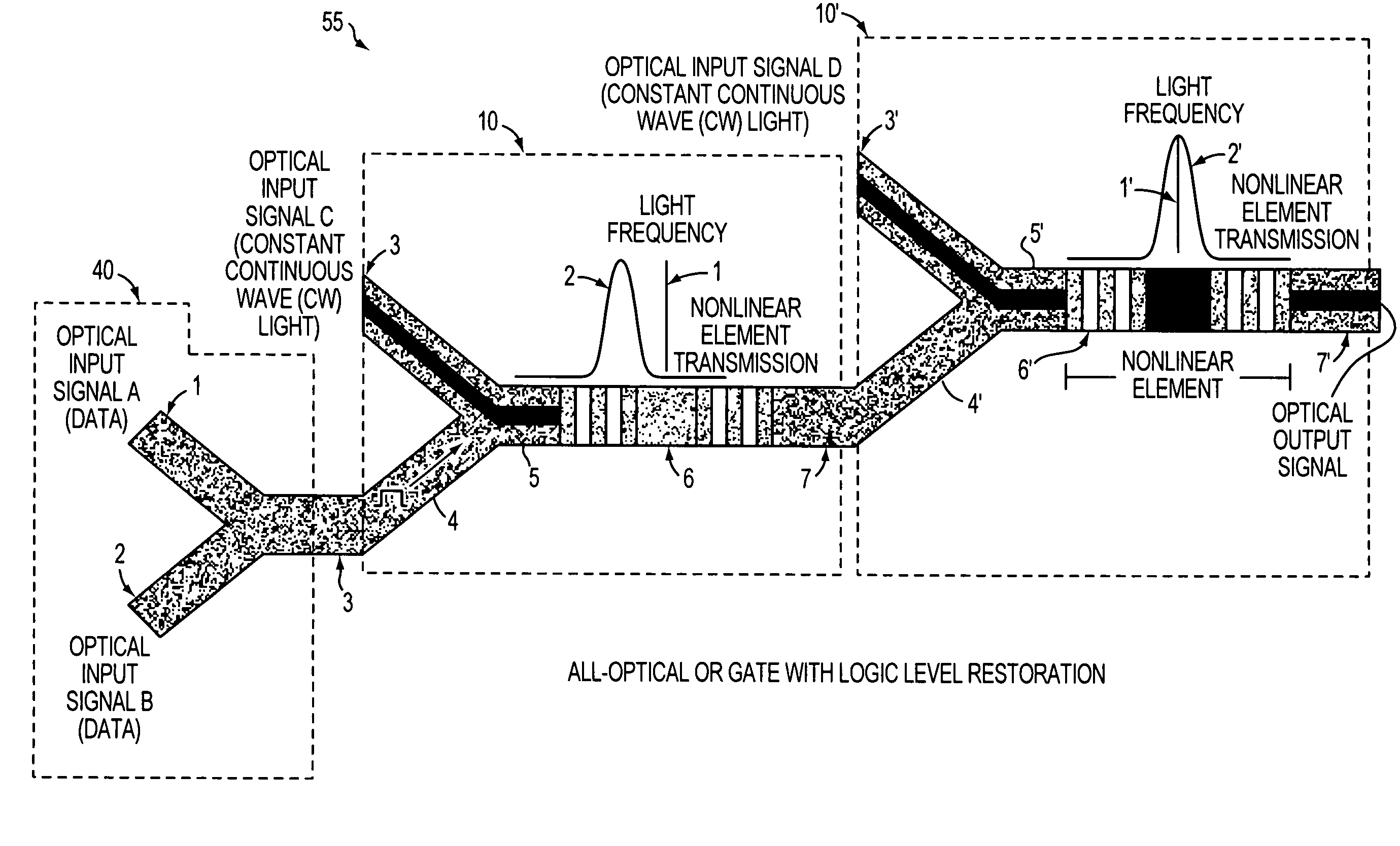

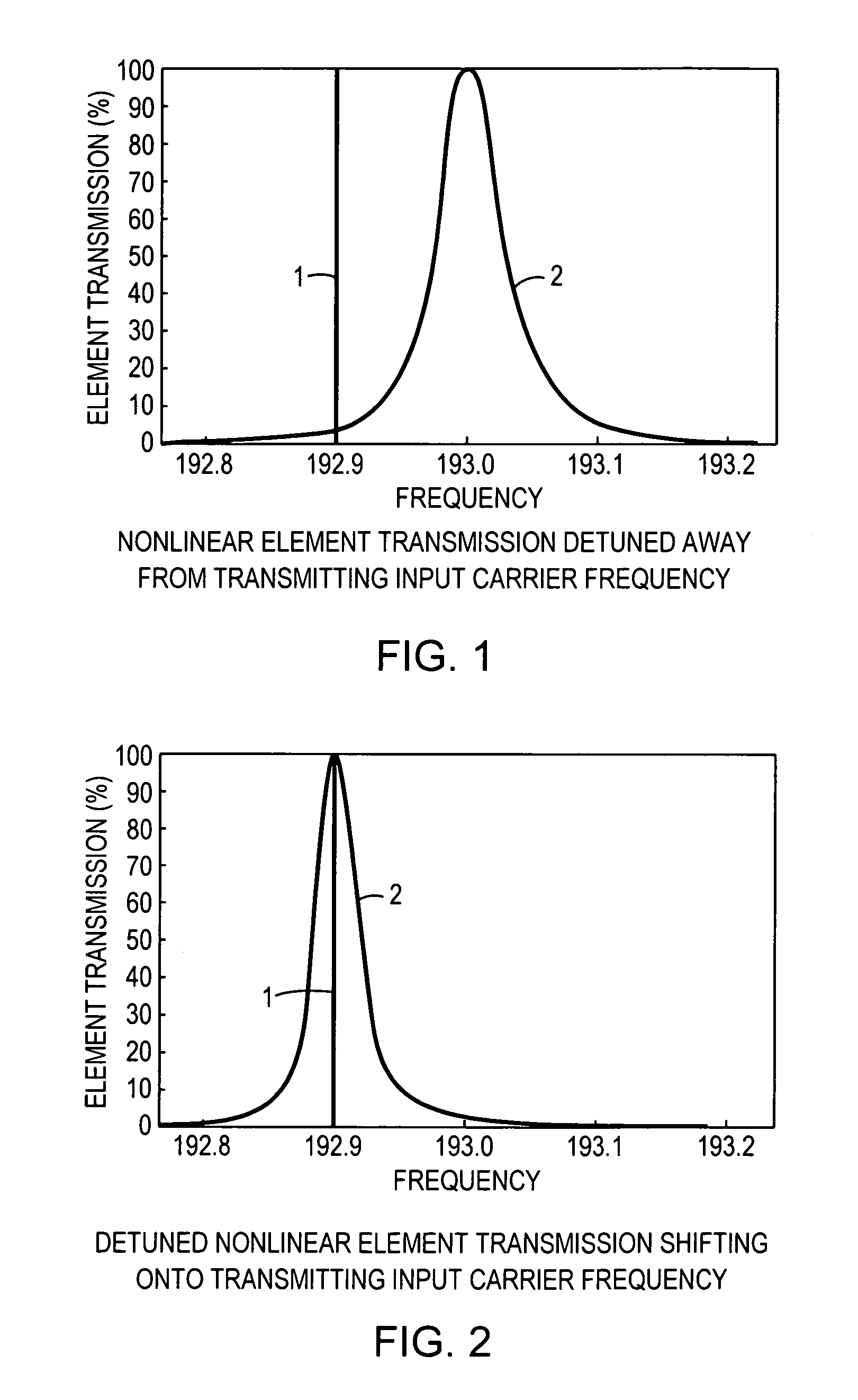

All-optical logic gates using nonlinear elements-claim set VI

InactiveUS7263262B1Change quantityPrecise arrangementCoupling light guidesOptical bistable devicesNonlinear elementLogic gate

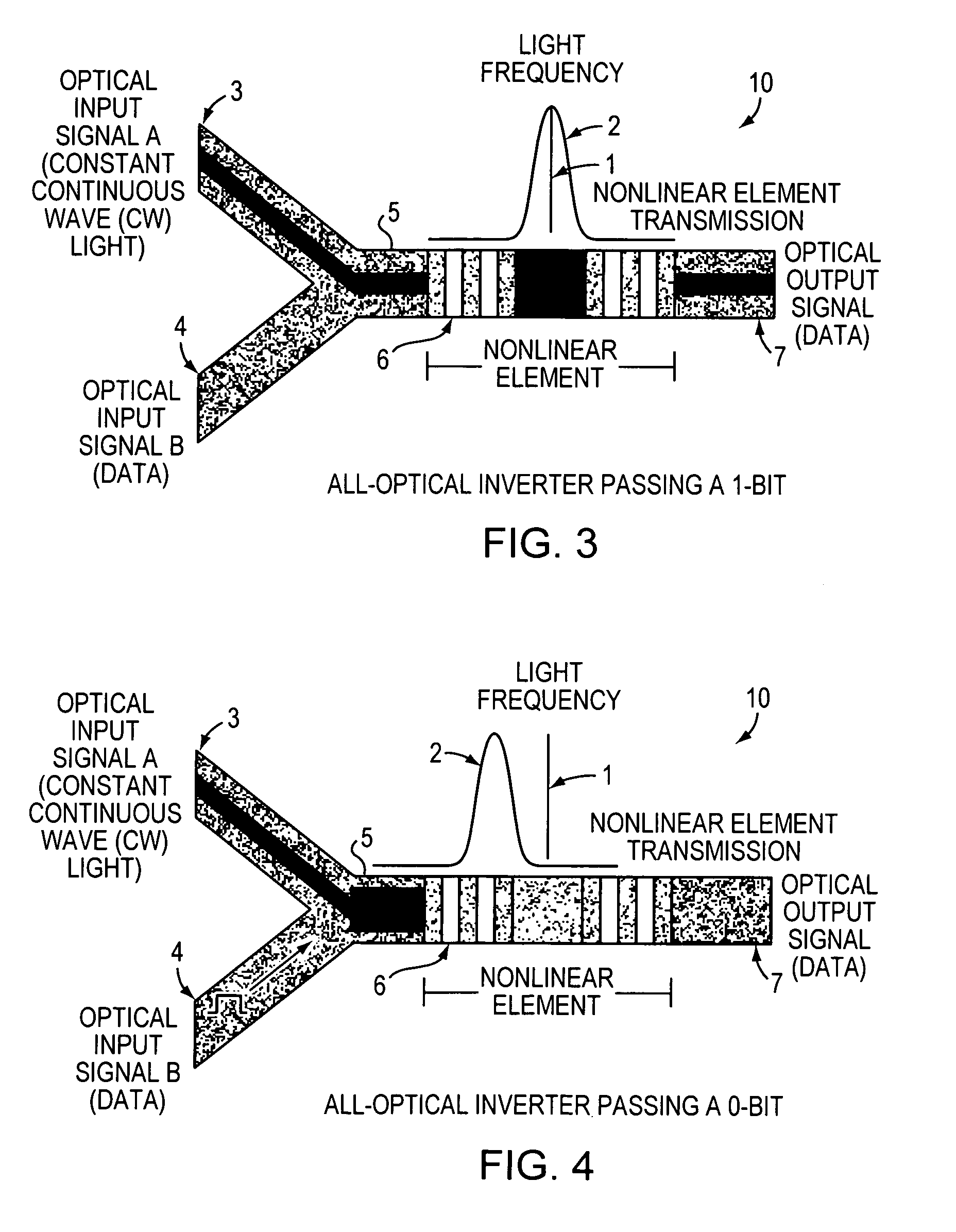

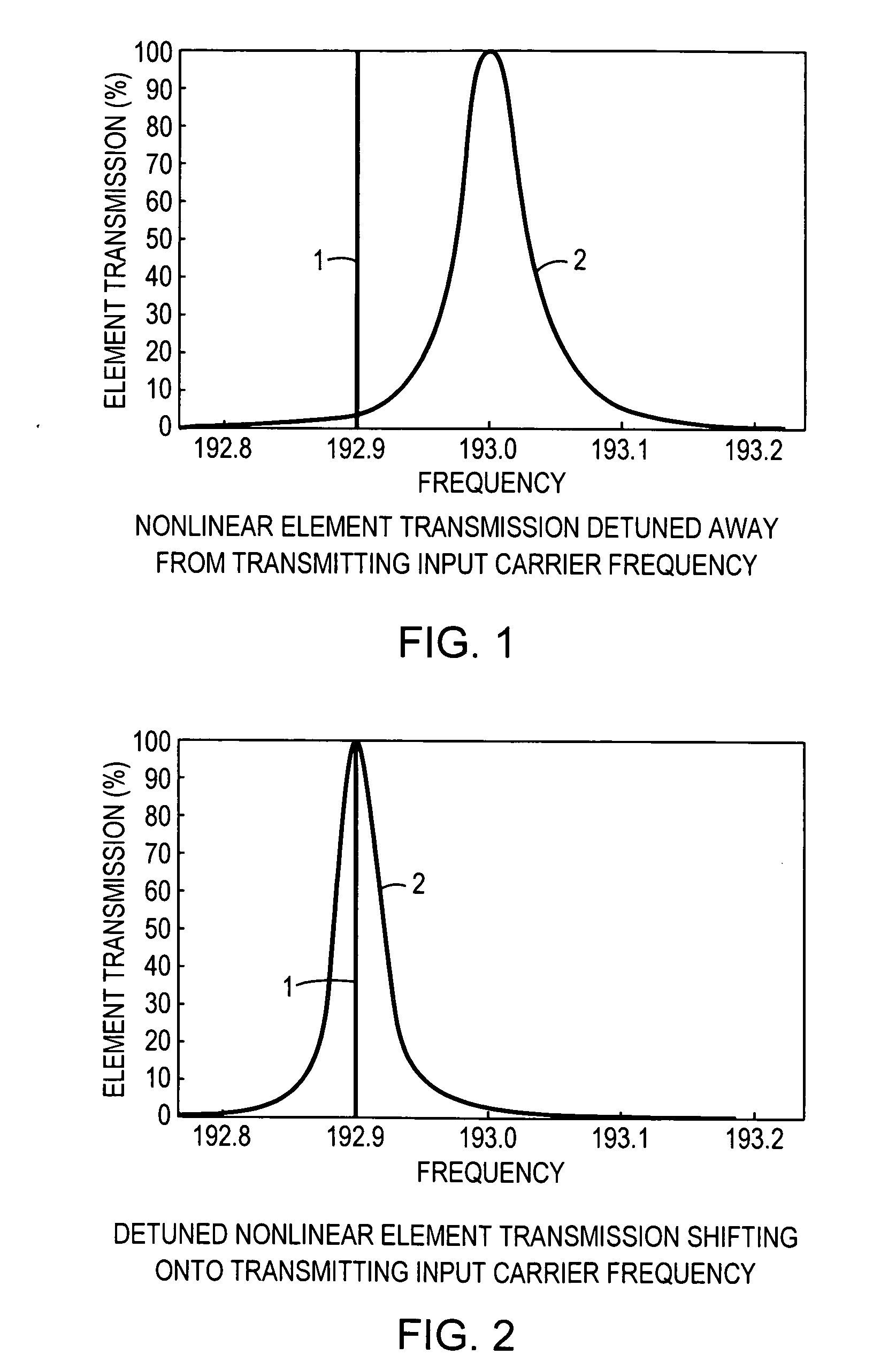

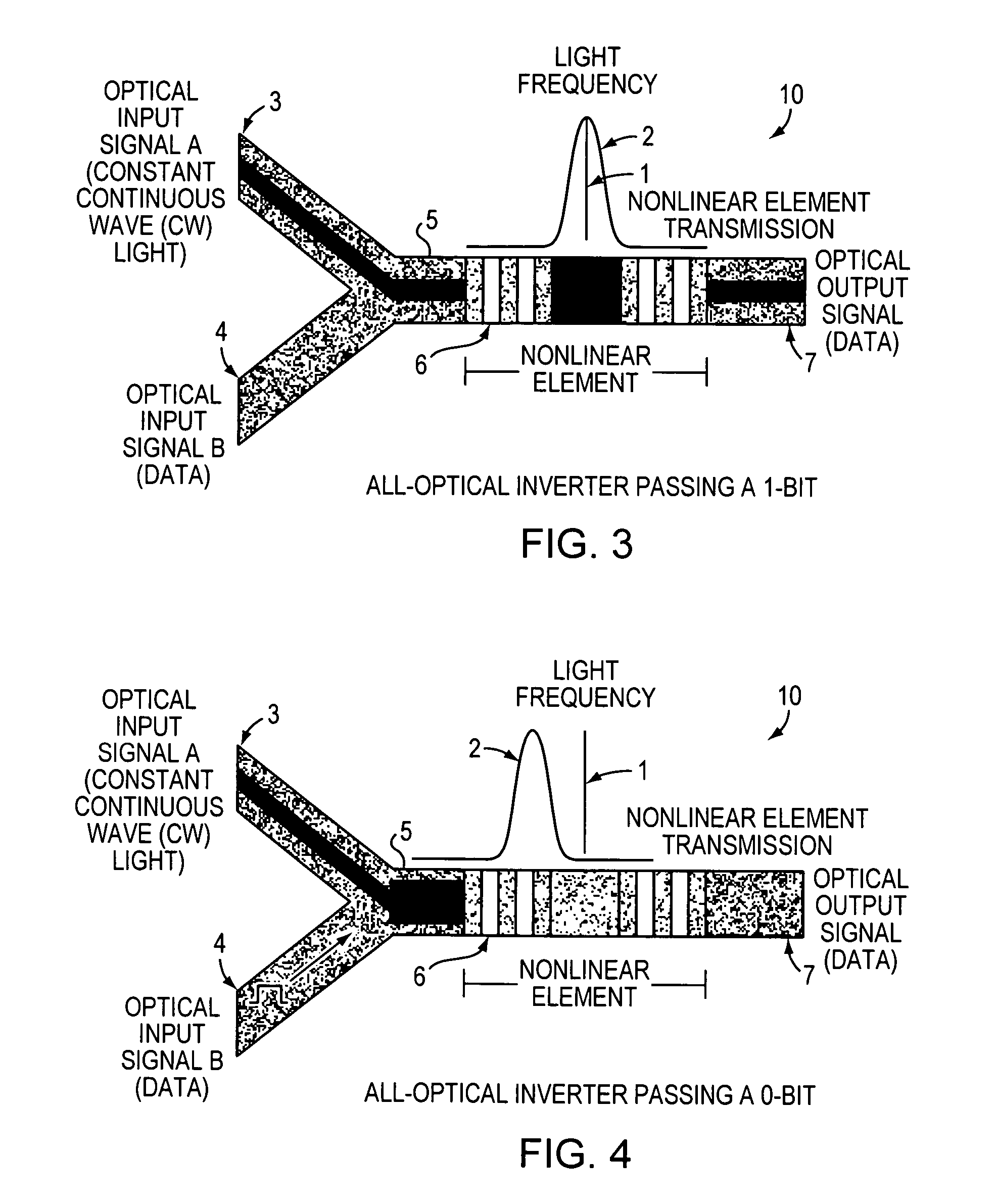

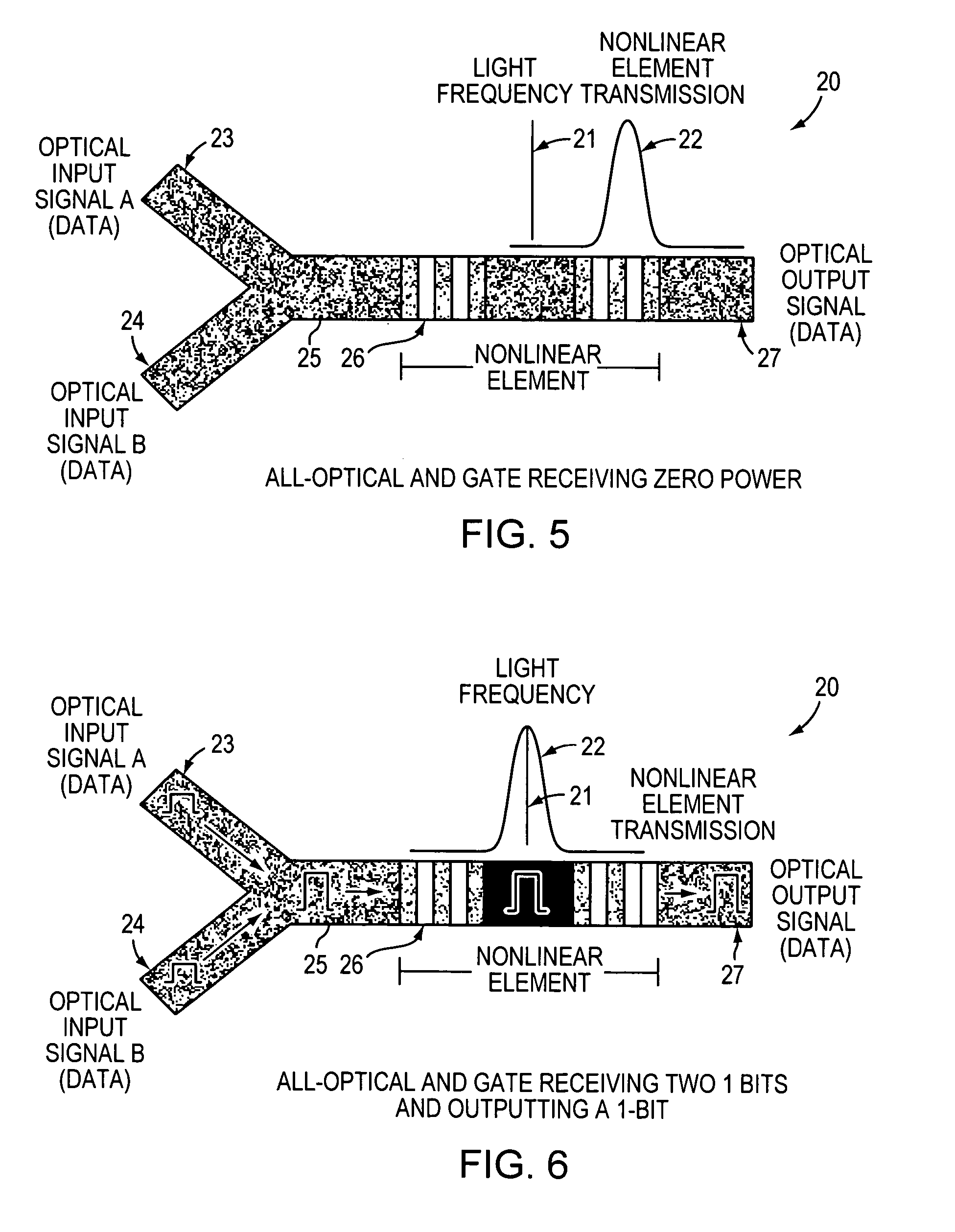

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEY JOHN

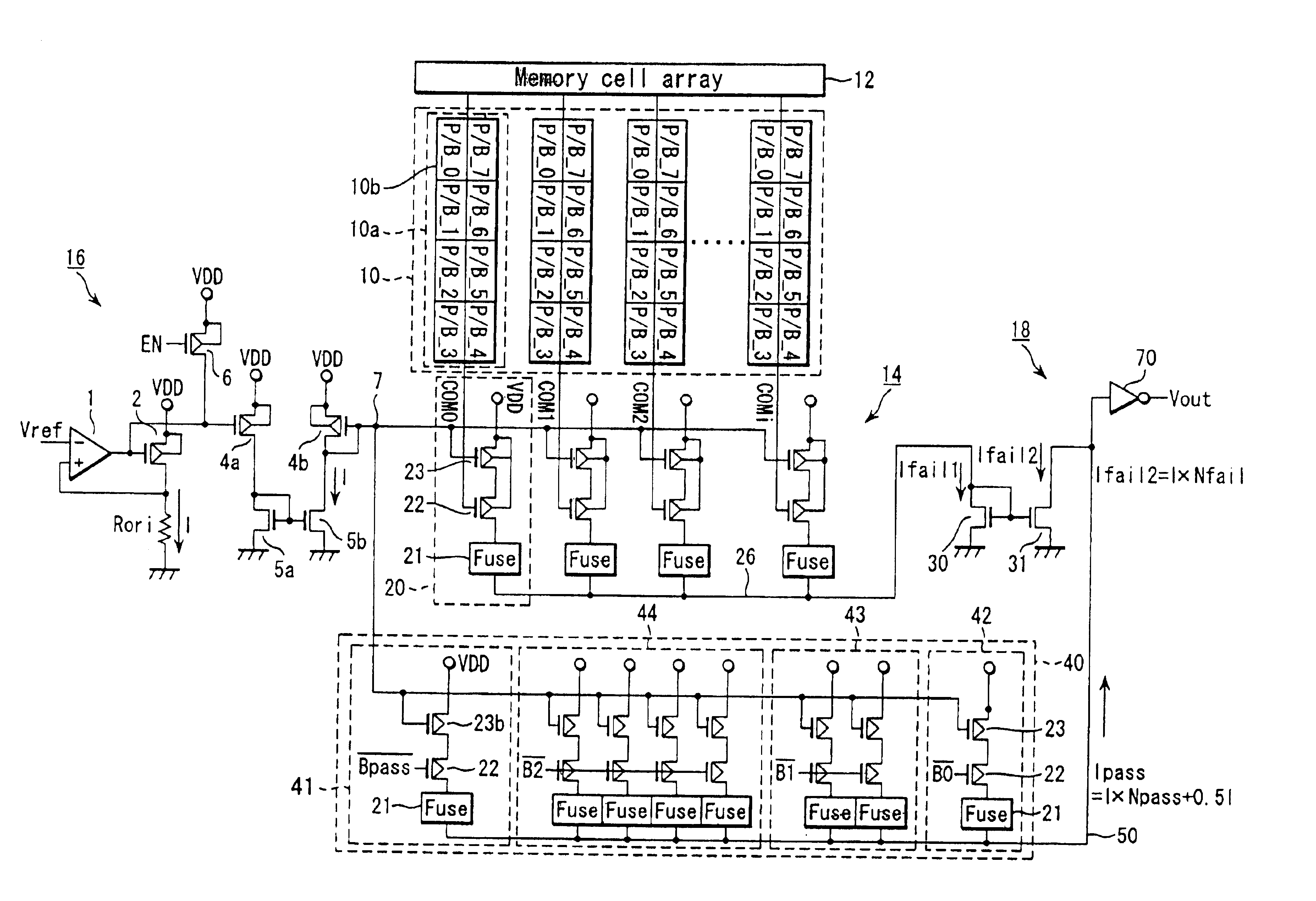

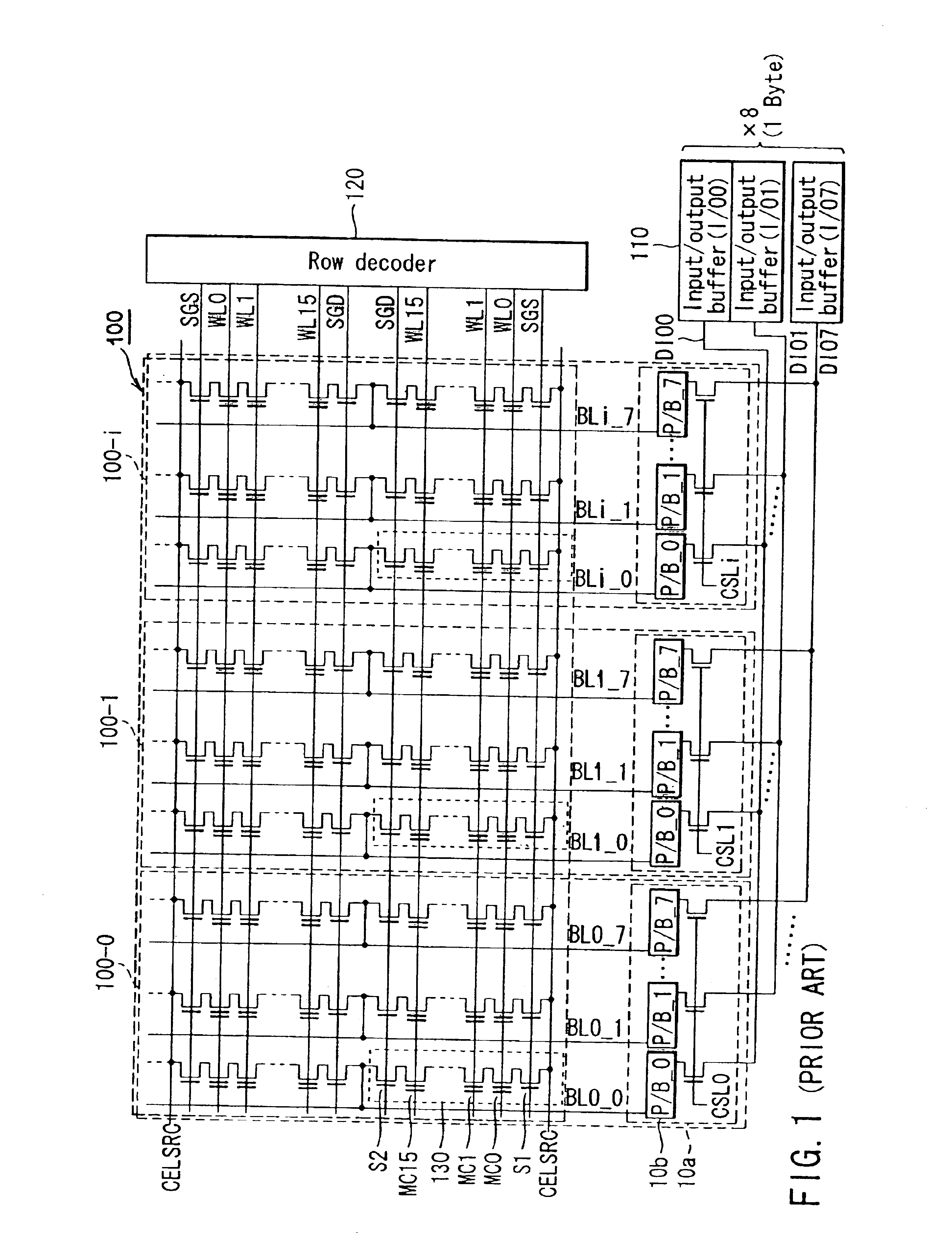

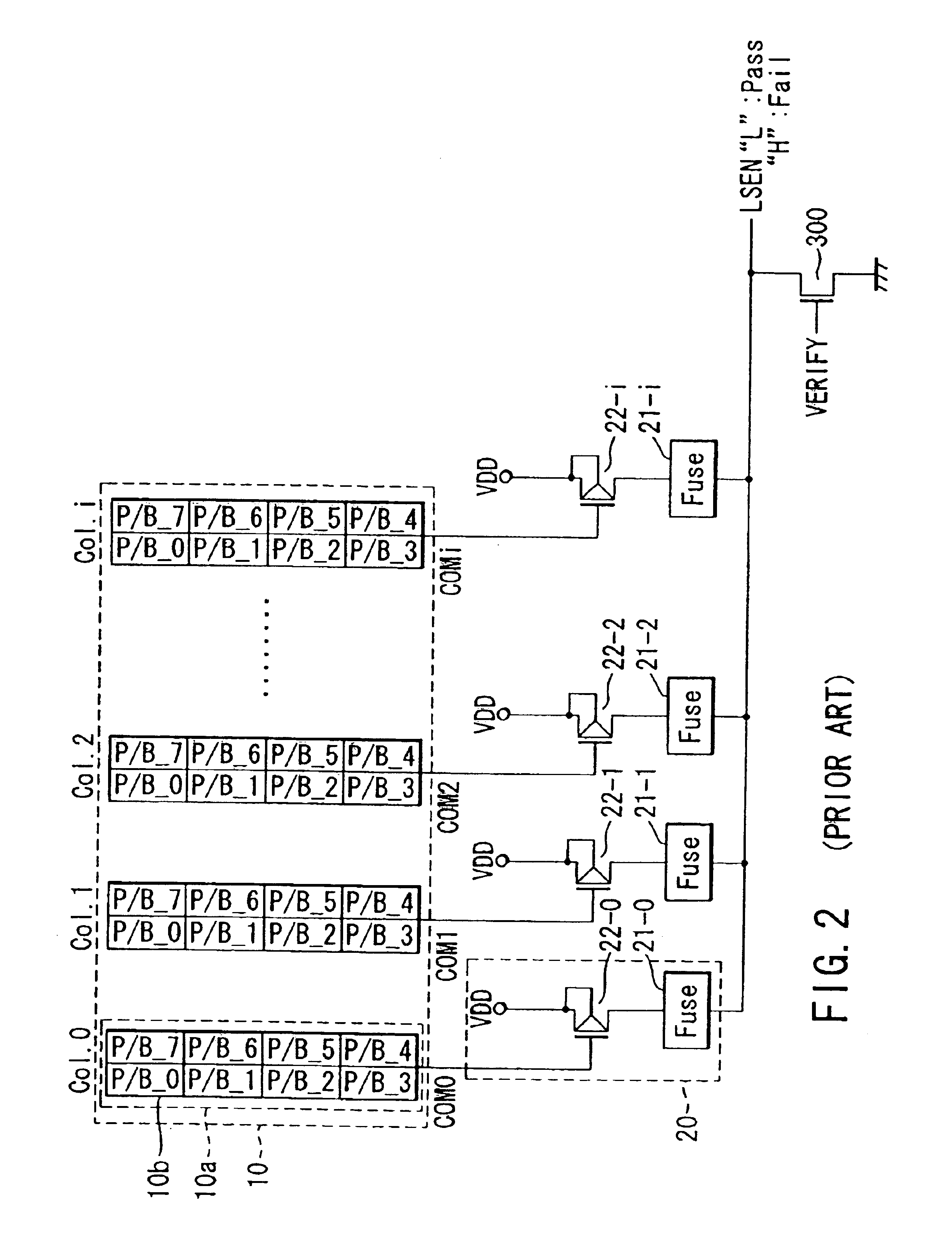

Fail number detecting circuit of flash memory

A semiconductor device includes a memory cell array, latch circuits, first to third circuits and a current control circuit. The memory cell array includes NAND cells arranged therein. The latch circuits temporarily hold data read out from the memory cell array. The first circuit generates a first current varying in proportion to “1” or “0” of binary logic data of one end of the plurality of latch circuits. The second circuit generates a second current which is preset. The third circuit compares the first current with the second current. The value of “1” or “0” of binary logic data of the one end of the plurality of latch circuits is detected based on a result of the comparison between the first current and the second current.

Owner:TOSHIBA MEMORY CORP

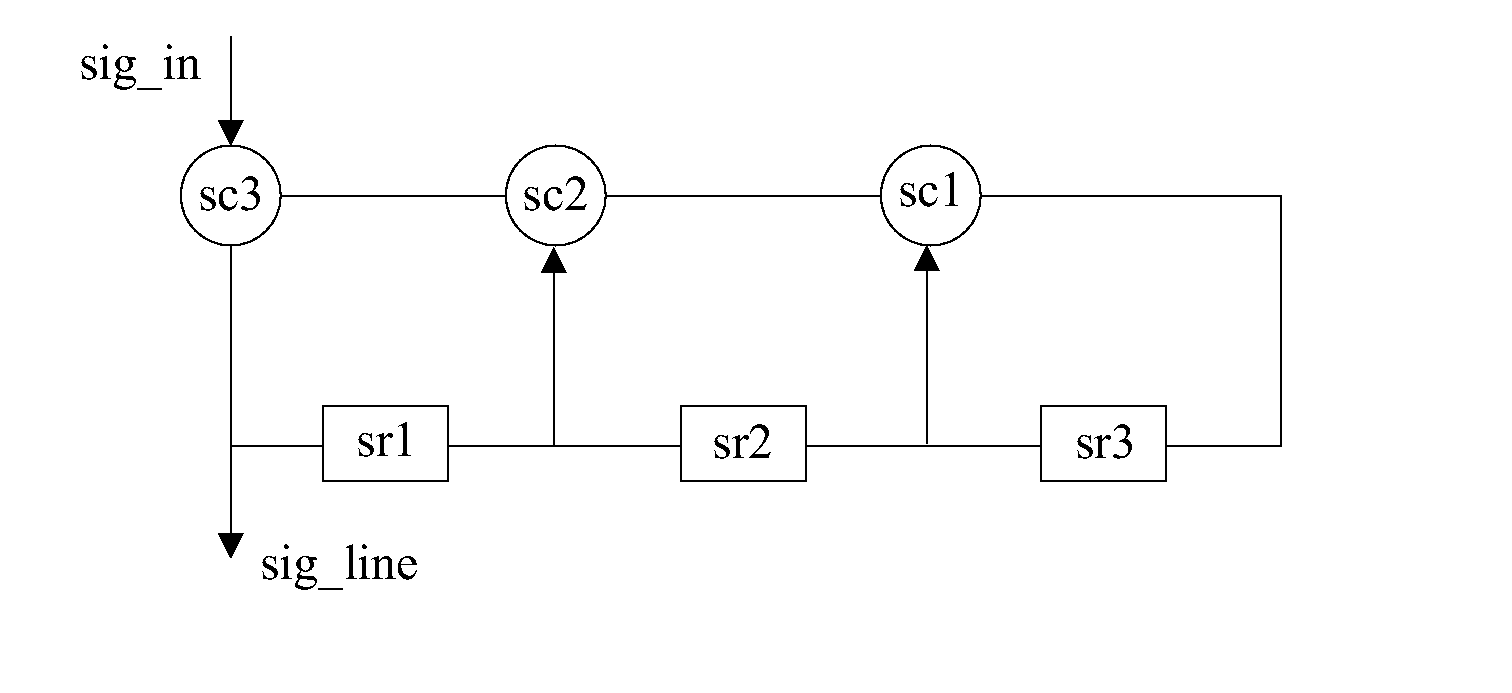

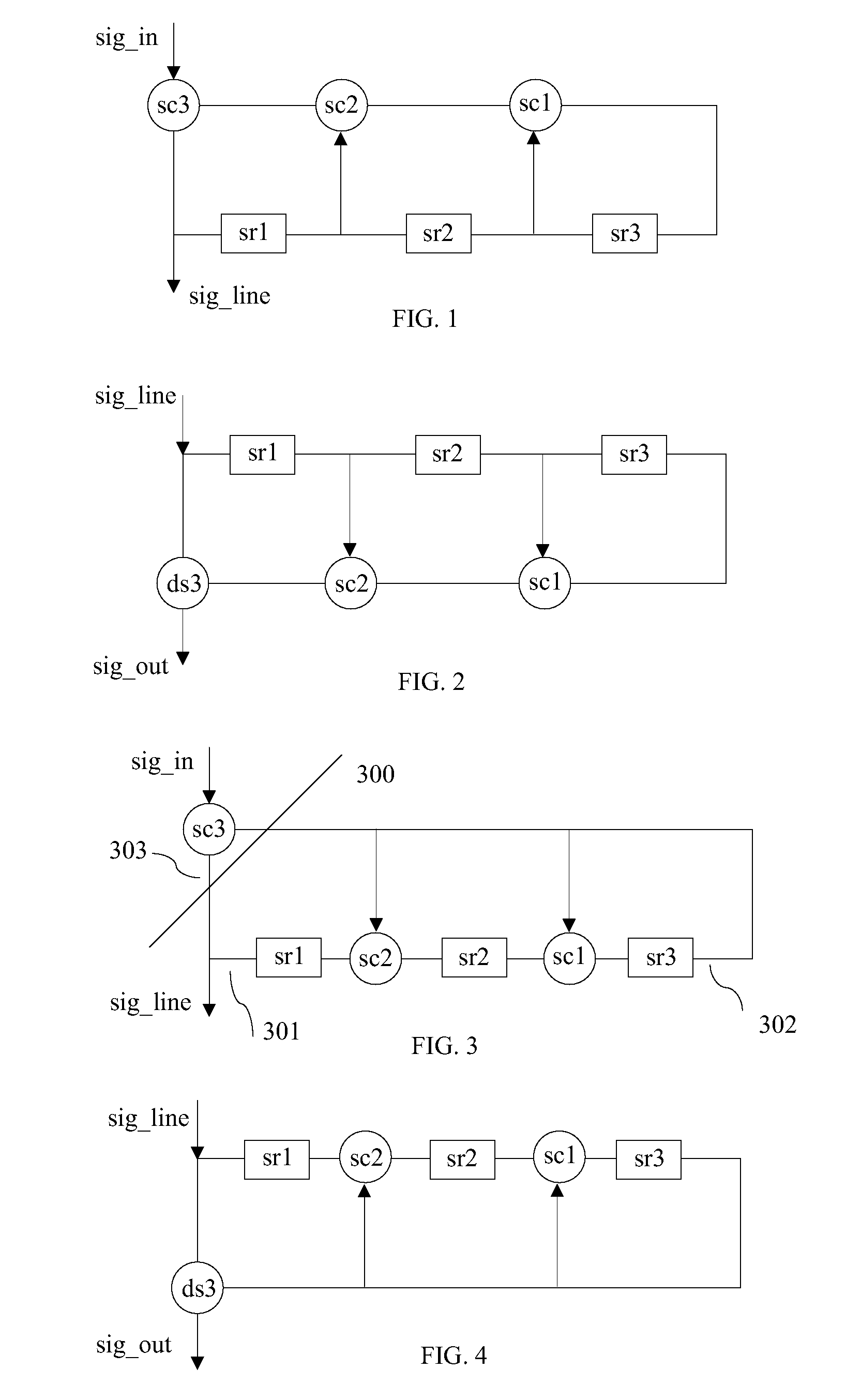

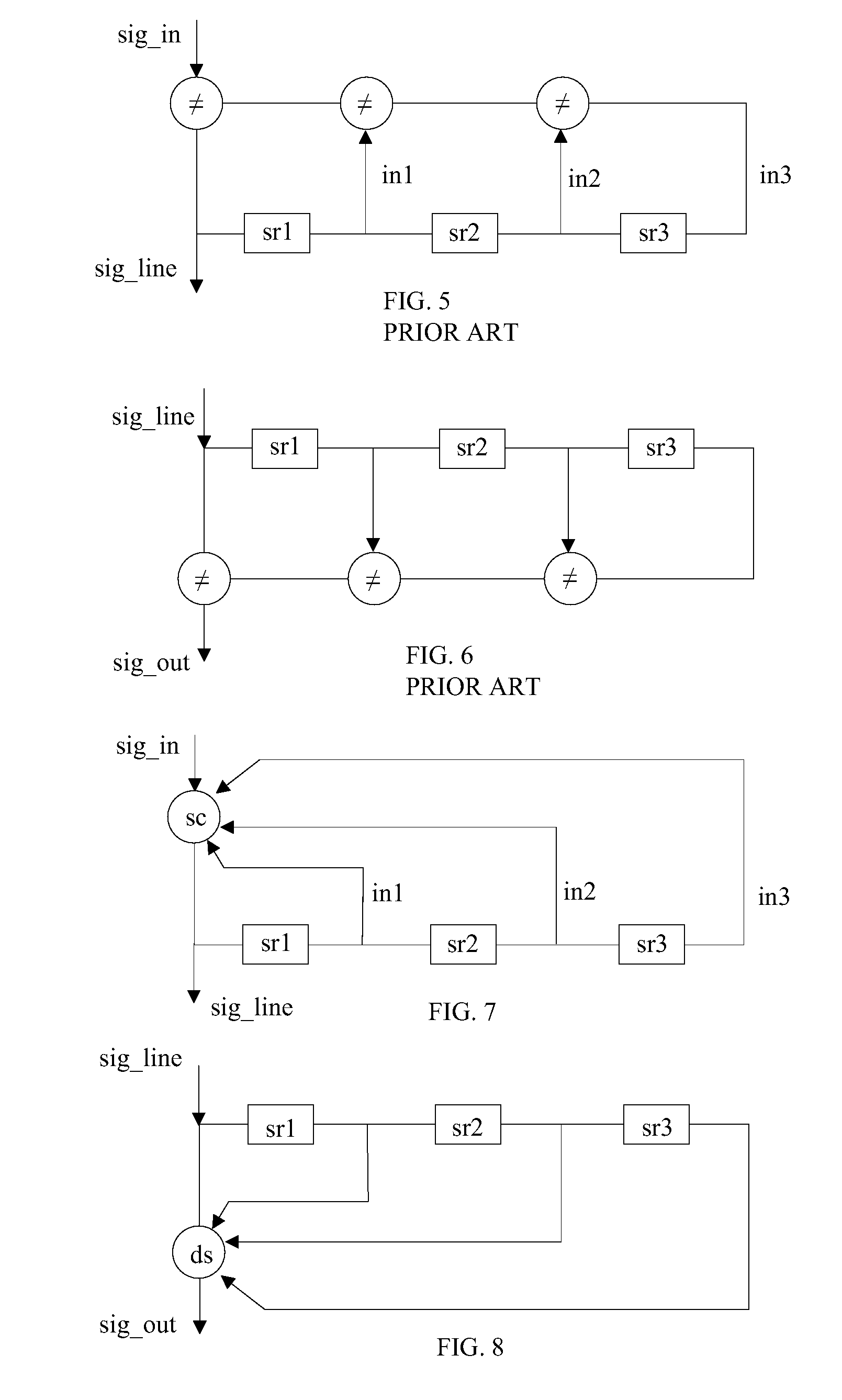

Methods and Systems for N-State Signal Processing with Binary Devices

InactiveUS20090092250A1Synchronising transmission/receiving encryption devicesDigital data processing detailsCommunications systemBinary combinatory logic

Linear Feedback Shift Registers (LFSRs) based 2p state with p>2 or p≧2 scramblers, descramblers, sequence generators and sequence detectors in binary implementation are provided. An LFSR may apply devices implementing a binary XOR or EQUIVALENT function, a binary shift register and binary inverters and binary state generator, wherein at least an output of one shift register element in a first LFSR is connected to a device implementing a reversible binary logic function is a second LFSR. They may also apply 2p state inverters using binary combinational logic are applied. Memory based binary 2p state inverters are also applied. Non-LFSR based n-state scramblers and descramblers in binary logic are also provided. A method for simple correlation calculation is provided. Communication systems and data storage systems applying the provided LFSR devices are also disclosed.

Owner:TERNARYLOGIC

Autonomous learning dynamic artificial neural computing device and brain inspired system

ActiveUS8250011B2Analogue computers for chemical processesDigital computer detailsInformation processingSynapse

A hierarchical information processing system is disclosed having a plurality of artificial neurons, comprised of binary logic gates, and interconnected through a second plurality of dynamic artificial synapses, intended to simulate or extend the function of a biological nervous system. The system is capable of approximation, autonomous learning and strengthening of formerly learned input patterns. The system learns by simulated Synaptic Time Dependent Plasticity, commonly abbreviated to STDP. Each artificial neuron consisting of a soma circuit and a plurality of synapse circuits, whereby the soma membrane potential, the soma threshold value, the synapse strength and the Post Synaptic Potential at each synapse are expressed as values in binary registers, which are dynamically determined from certain aspects of input pulse timing, previous strength value and output pulse feedback.

Owner:BRAINCHIP INC

All-optical logic gates using nonlinear elements-claim set III

InactiveUS20070189680A1Change quantityPrecise arrangementNanoopticsCoupling light guidesLinear elementEngineering

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEY JOHN

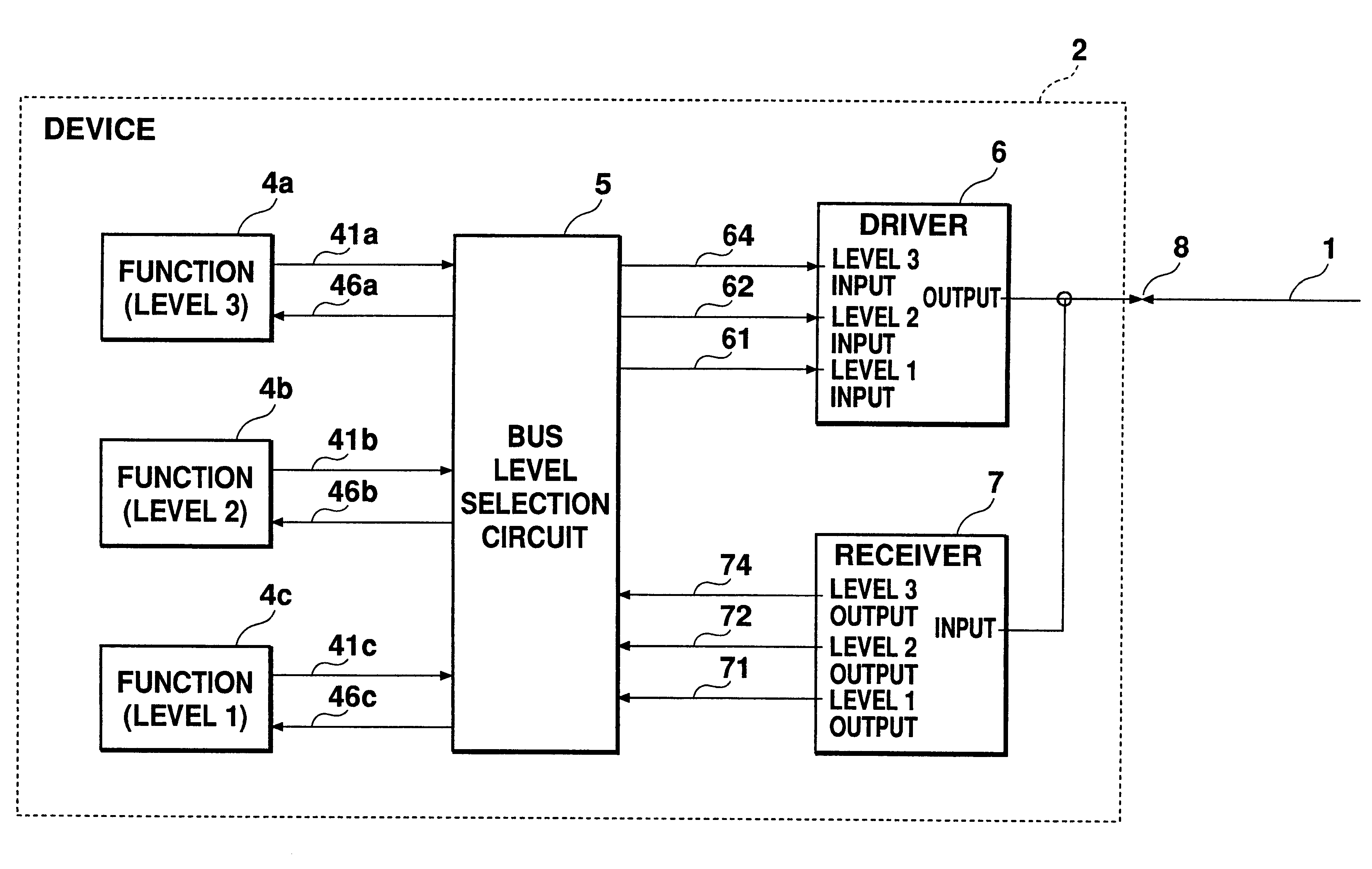

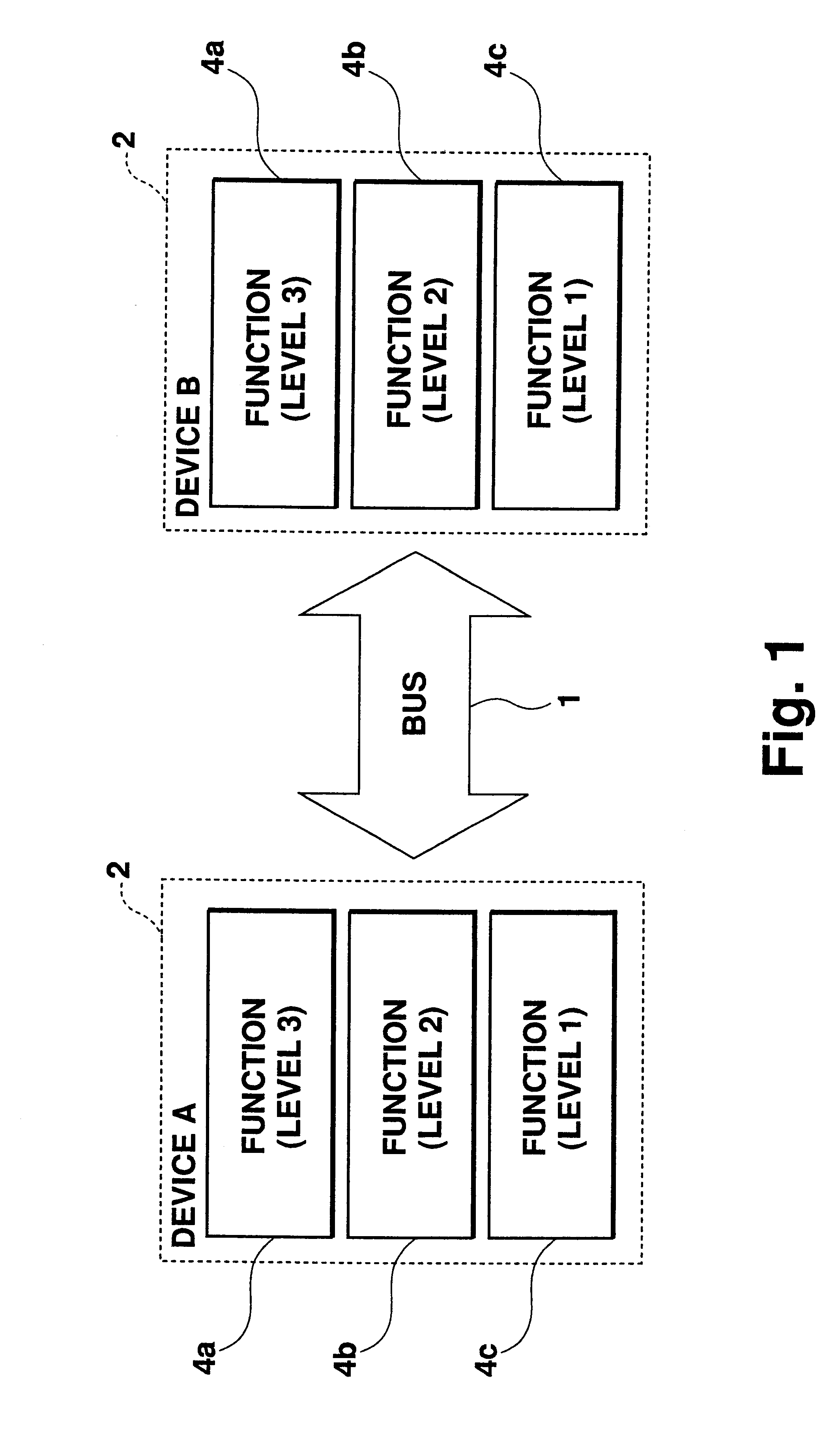

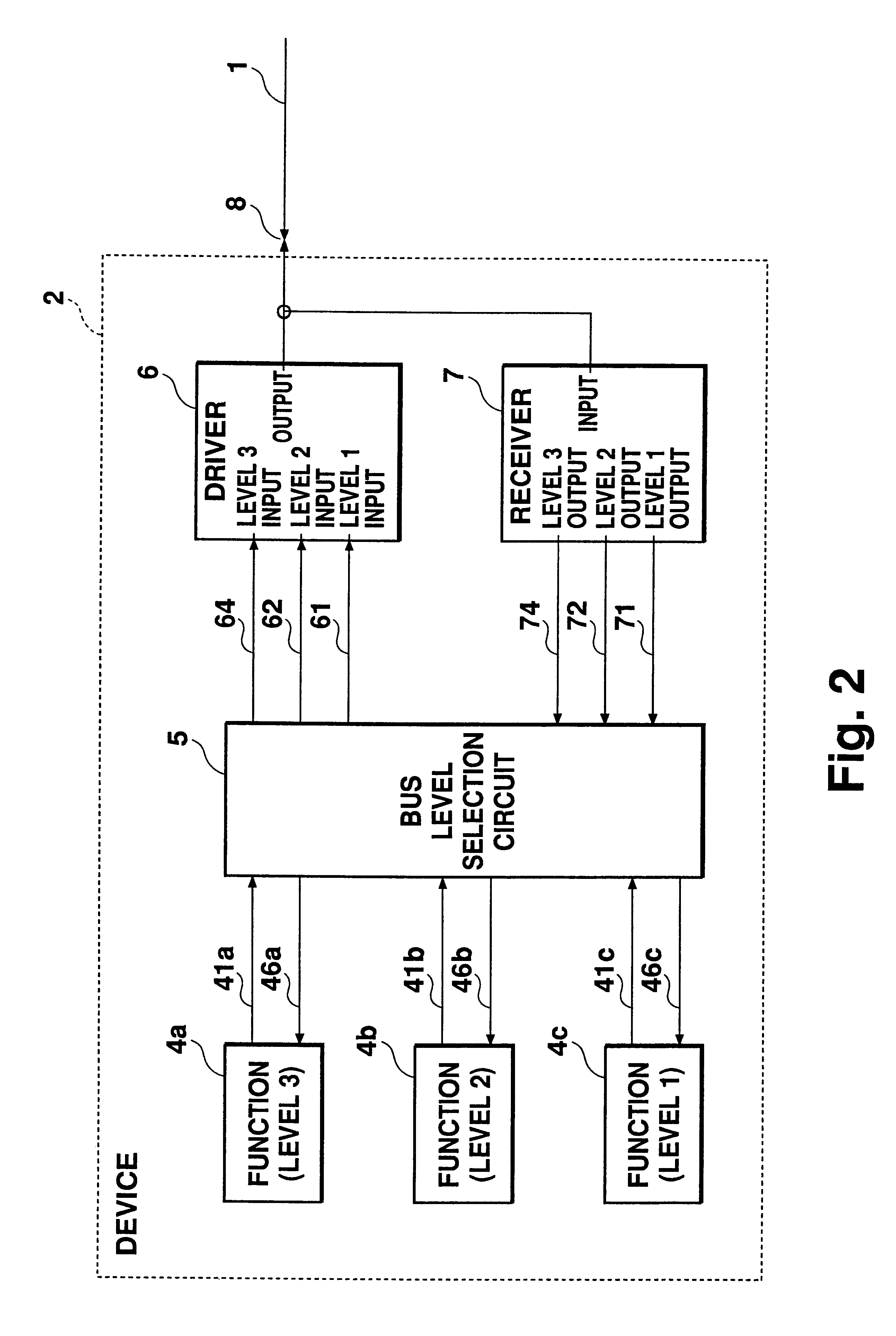

Multi-value logic device, bus system of multi-value logic devices connected with shared bus, and network system of information processors loaded with multi-value logic devices and connected with shared network

InactiveUS6266722B1Logic circuits characterised by logic functionInput/output processes for data processingElectrical conductorNetwork connection

A multi-value logic device in which a unique bus level is allocated beforehand to each binary logic signal outputted by a function of the multi-value logic device. Upon receipt of the binary logic signal via a bus level selection circuit, a driver converts the binary logic signal to an analog signal with a voltage having an amplitude of e.2n-1, in which n is the bus level of the binary logic signal and e is a reference voltage. When a plurality of binary logic signals are simultaneously inputted, the driver superimposes analog signals in accordance with the bus level of each binary logic signal to generate a multi-value logic signal, so that multiplex communication is realized. A receiver performs an operation reverse to the operation of the driver, and encodes a multi-value logic signal received via a bus to convert the signal to a binary logic signal and transmit the signal to each function. In this manner, the multi-value logic device suppresses an increase in the number of bus signal conductors, and enhances throughput by realizing multiplex communication.

Owner:MITSUBISHI ELECTRIC CORP

All-optical logic gates using nonlinear elements

InactiveCN102226862ALogic circuits using opto-electronic devicesOptical waveguide light guideNonlinear elementHelical resonator

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEYTECH LLC

All-optical logic gates using nonlinear elements-claim set I

InactiveUS20070189703A1Change quantityPrecise arrangementNanoopticsOptical light guidesLinear elementLogic gate

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEYTECH LLC

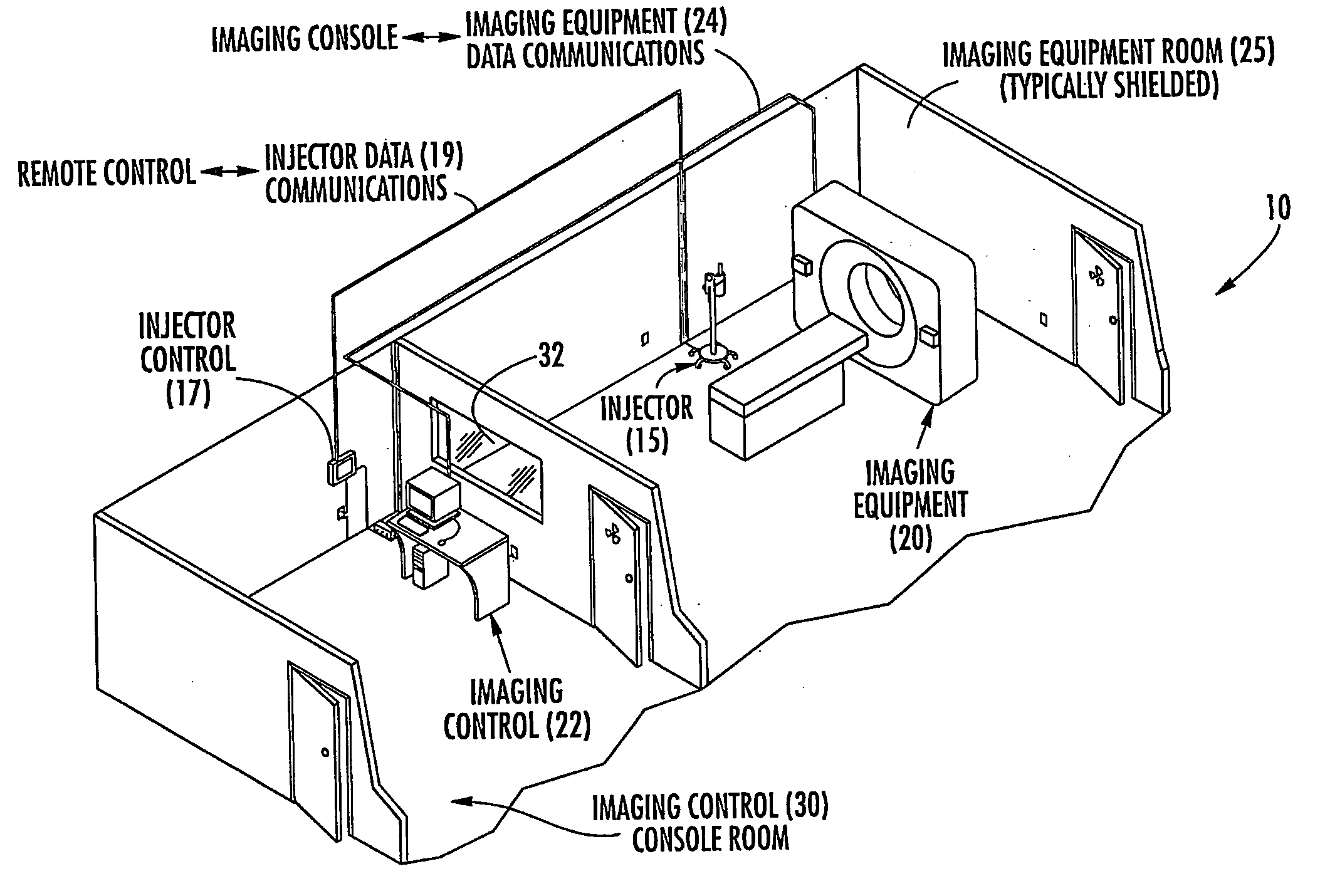

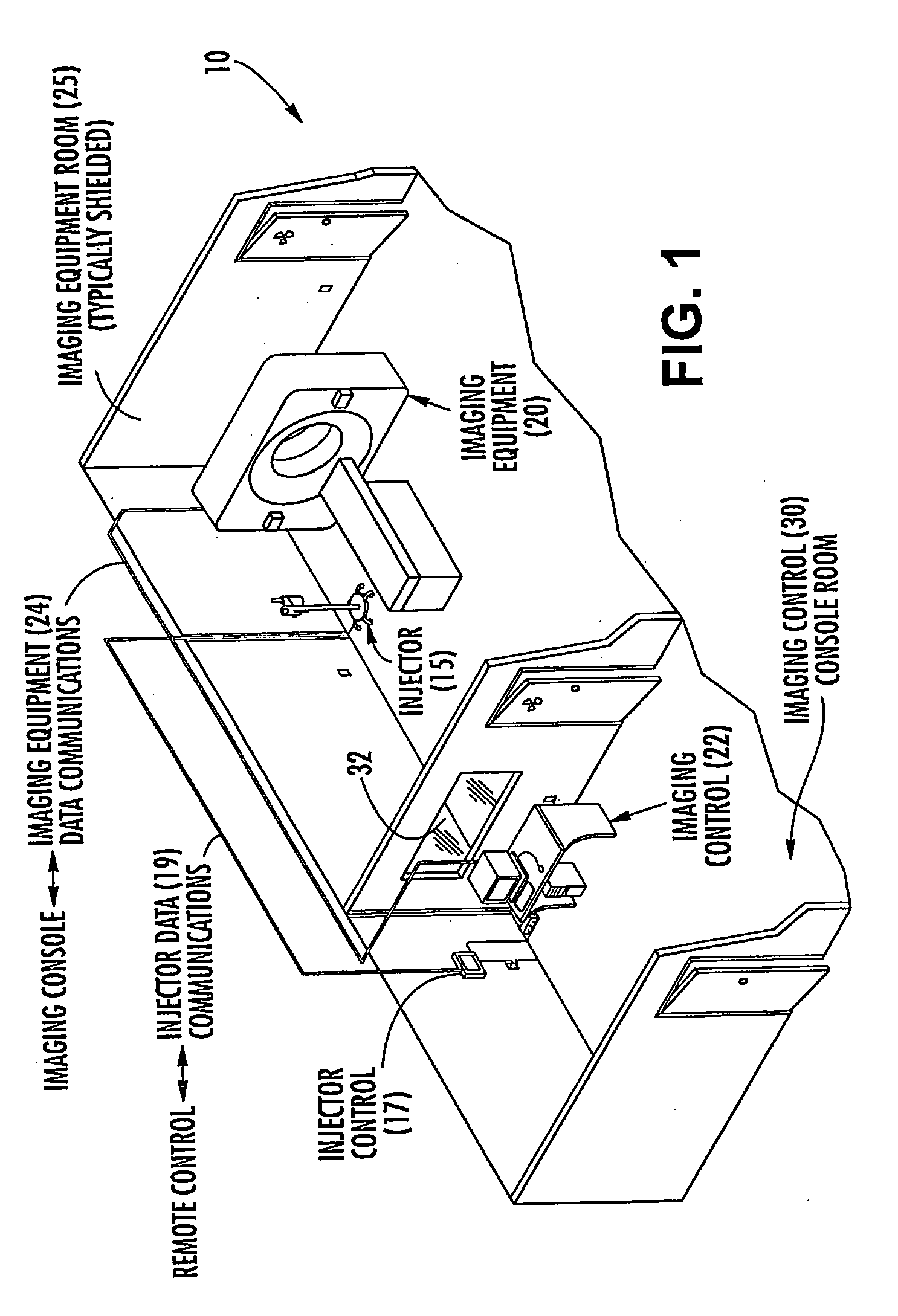

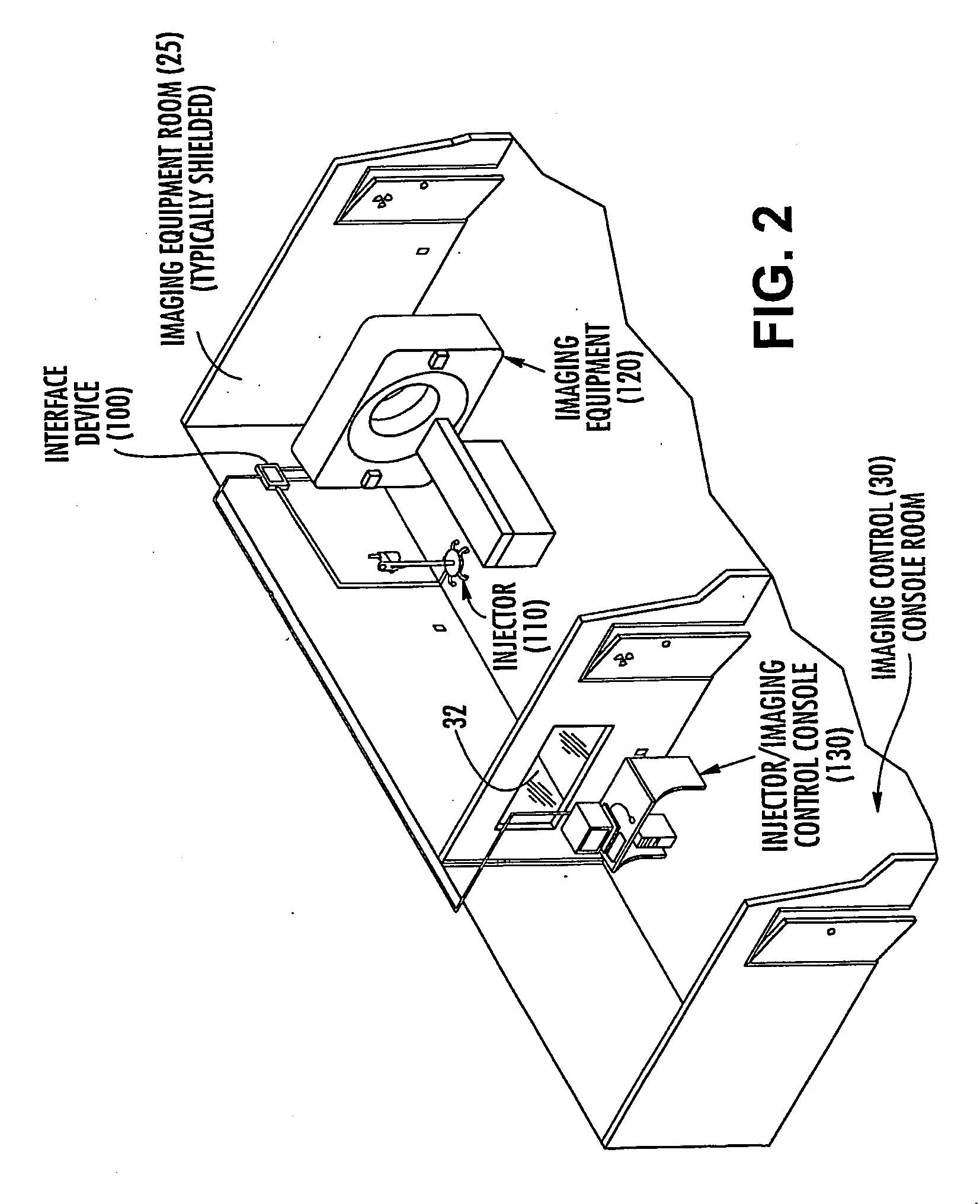

Interface Device and Protocol

ActiveUS20090214094A1Local control/monitoringMedical devicesHigh signal intensityNetwork Communication Protocols

The invention is an interface device and system for establishing an operating interface between an injector device and diagnostic imaging equipment. In one embodiment, the interface device may permit an operator to concurrently operate and control the injector device and the imaging equipment. The interface device may permit the injector system and the imaging system to communicate information regarding their current and future operational status with each other. The interface device may be used to synchronize the operation of the imaging equipment and the injector device. In one embodiment, the injector device and the imaging equipment may be able to communicate with each other directly or through the interface device via a communications protocol comprising binary logic signals. The binary logic signals may comprise one or more of a low strength signal, a high strength signal, an oscillating signal that oscillates between low and high signal strength, and combinations thereof.

Owner:ACIST MEDICAL SYST

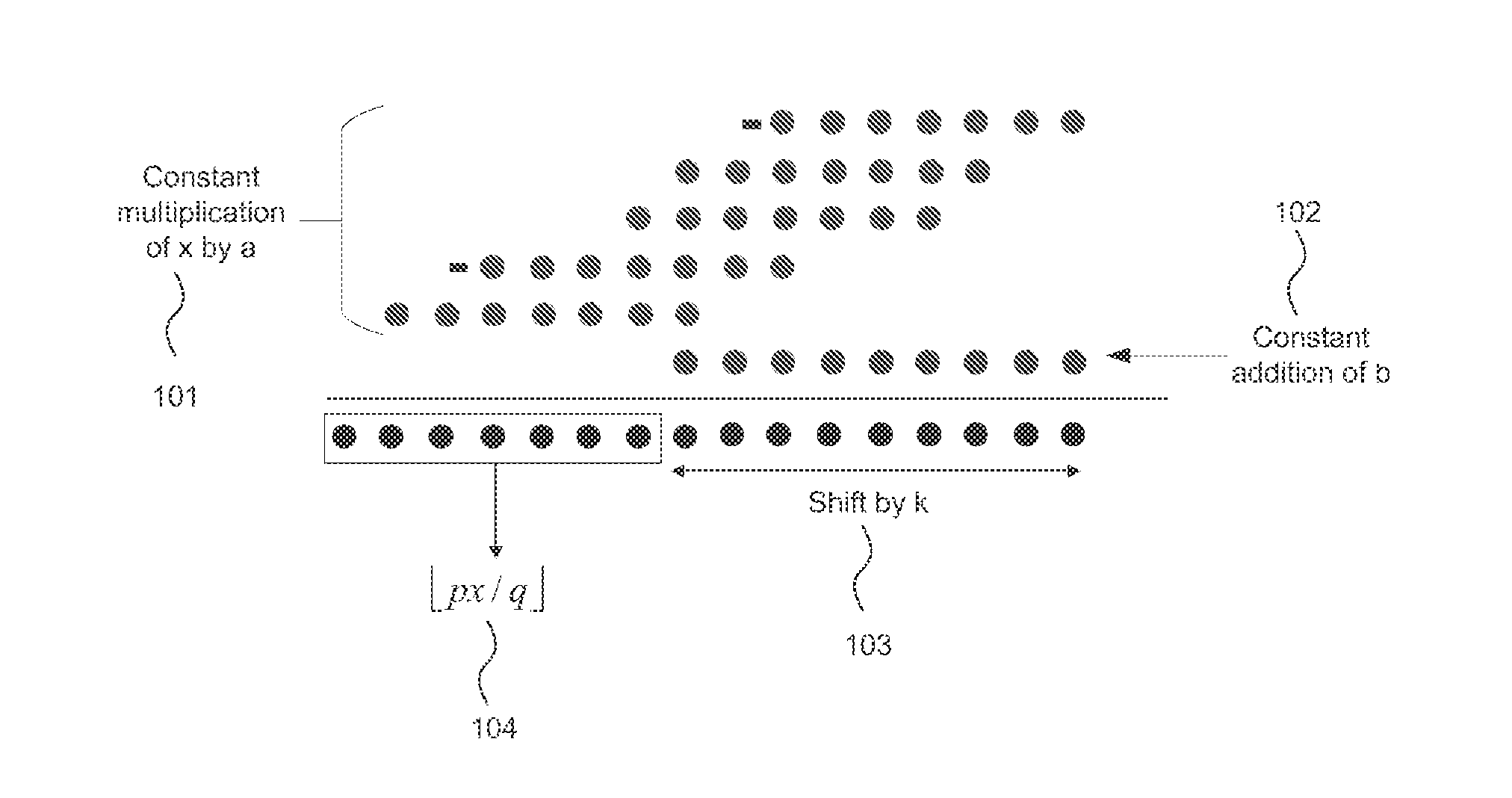

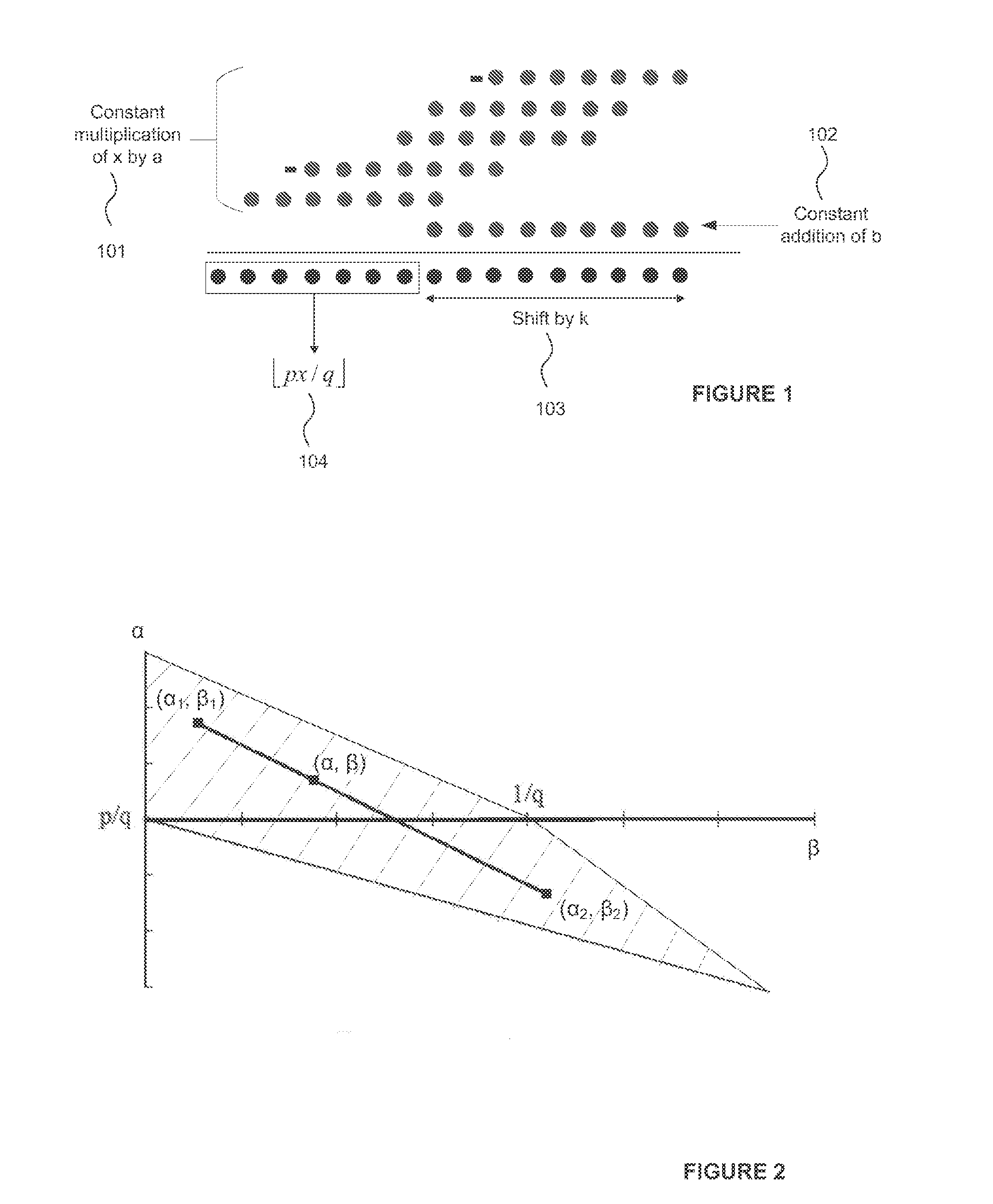

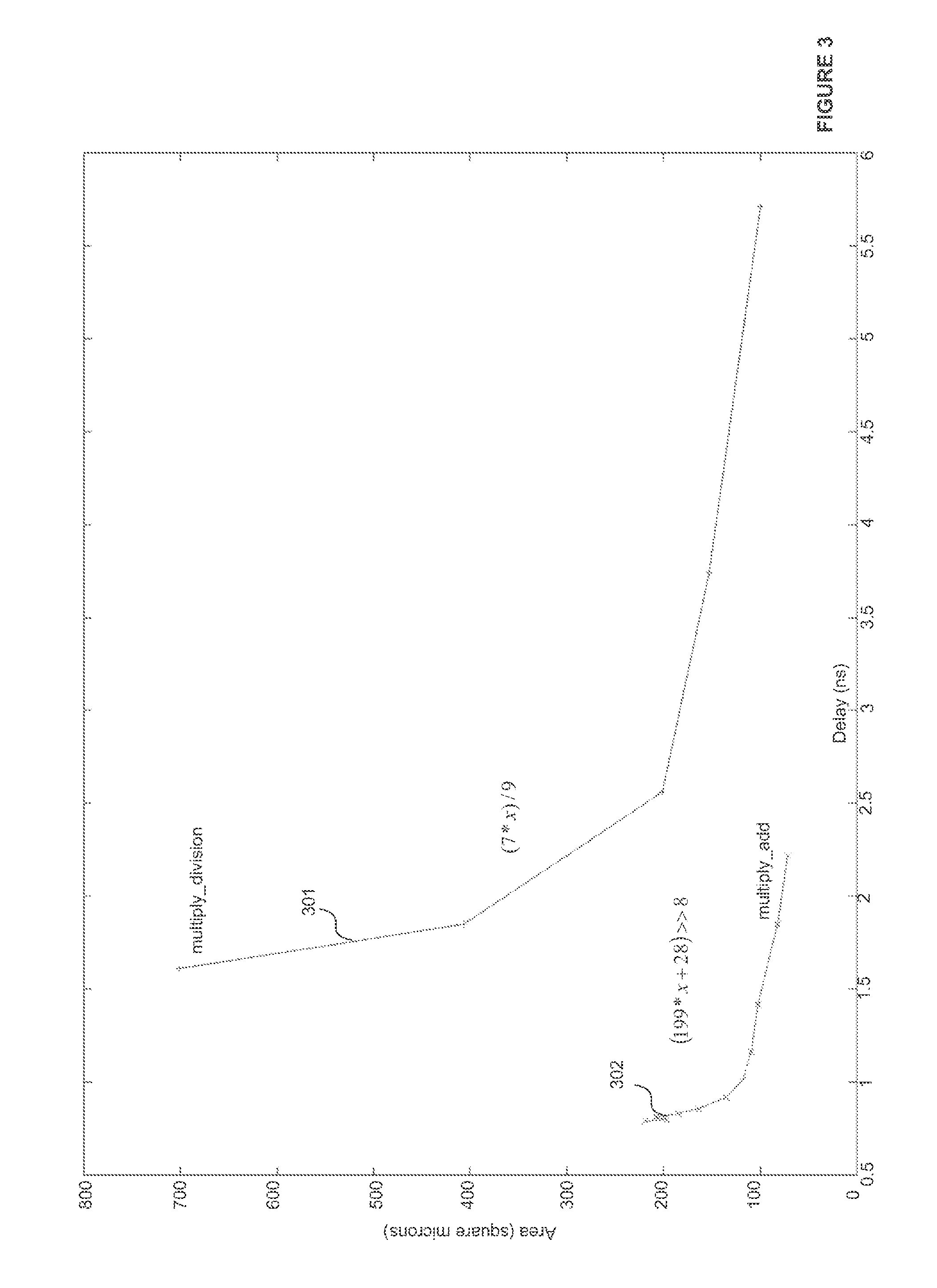

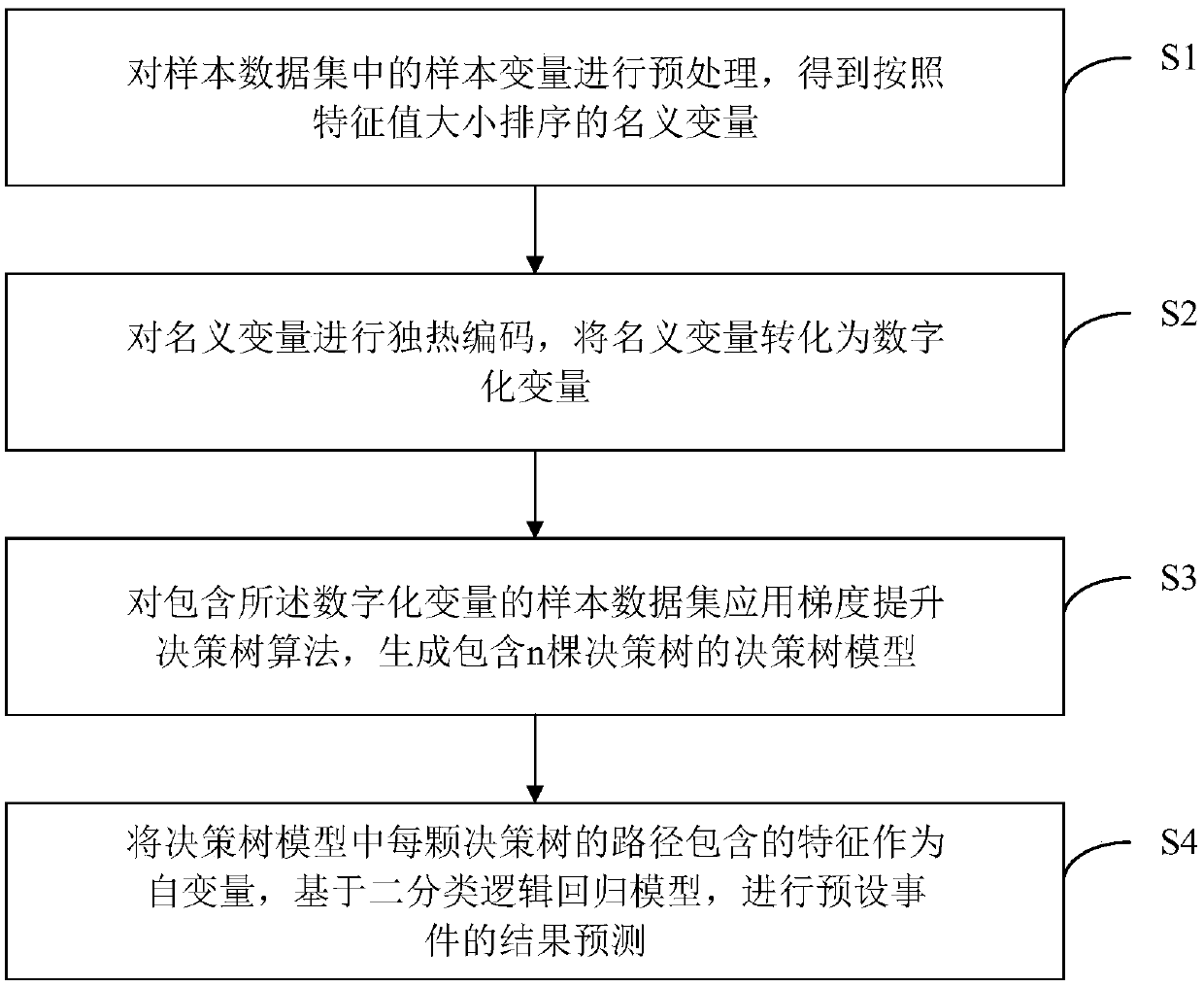

Constant Fraction Integer Multiplication

ActiveUS20140280410A1Computation using non-contact making devicesDigital computer detailsAlgorithmBinary logic

A binary logic circuit is provided for determining a rounded value ofpxq,where p and q are coprime constant integers with p<q and q≠2i, i is any integer, and x is an integer variable between 0 and integer M where M≧2q, the binary logic circuit implementing in hardware the optimal solution of the multiply-add operationax+b2kwhere a, b and k are fixed integers.

Owner:IMAGINATION TECH LTD

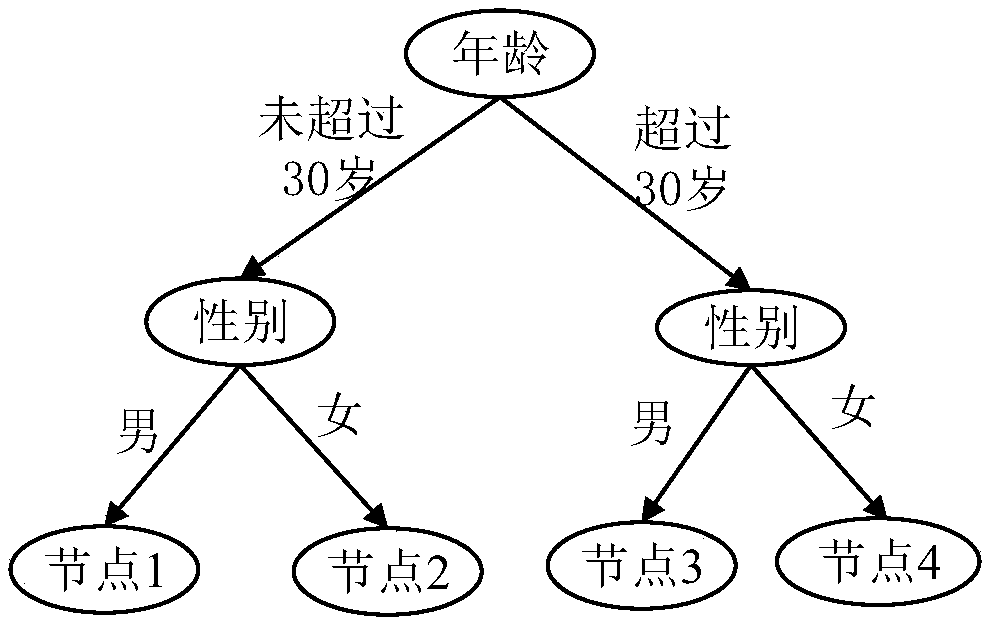

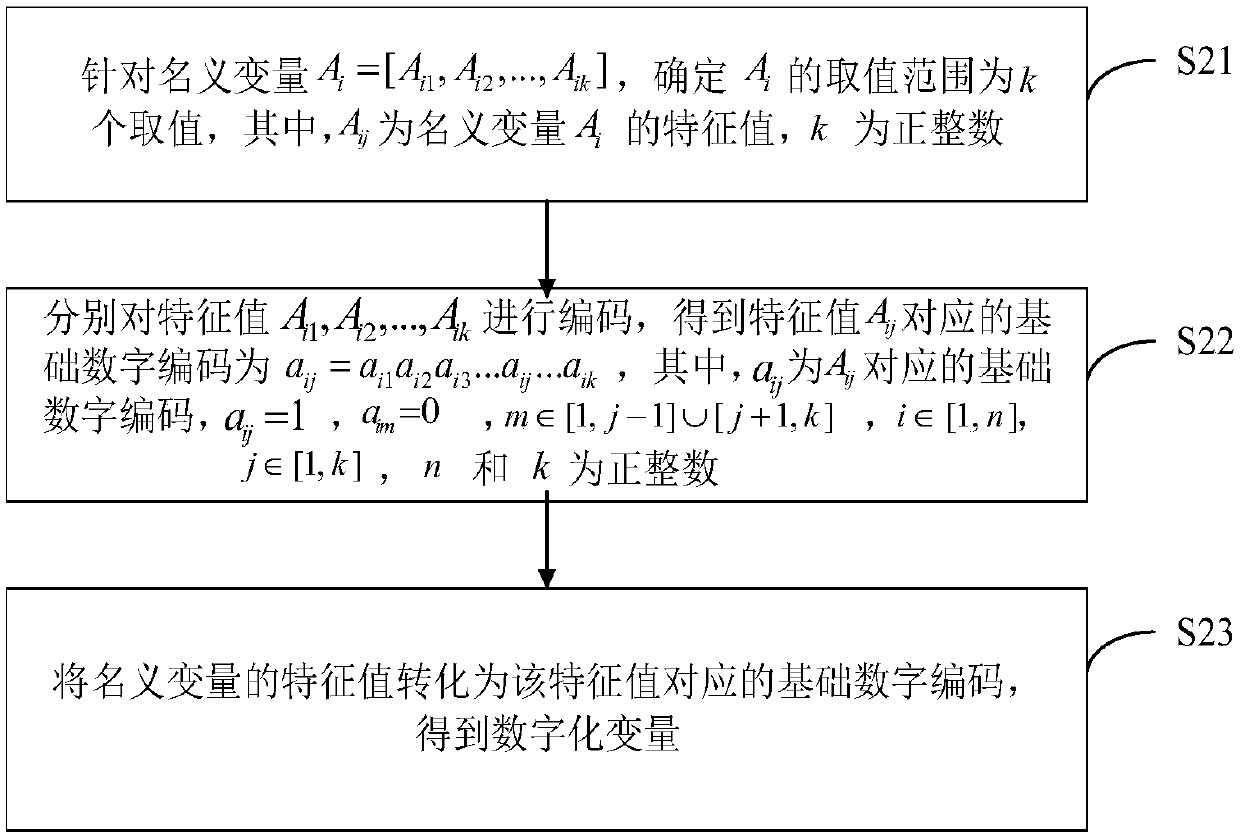

Data evaluation method and device, terminal equipment and storage medium

The invention discloses a data evaluation method and device, terminal equipment and a storage medium. The method comprises the following steps of carrying out preprocessing on sample variables in a sample data set in order to obtain nominal variables which are ordered according to the sizes of characteristic values; carrying out one-hot coding on the nominal variables which are ordered according to the sizes of the characteristic values, and converting the nominal variables into digital variables; applying a gradient lifting decision-making tree algorithm to the sample data set containing thedigital variables; generating a decision tree model comprising n decision trees; and acquiring combined characteristics by adopting the gradient lifting decision-making tree algorithm. The accuracy ofprediction of the combined characteristics of sample data is improved, and the efficiency of acquisition of the combined characteristics is also improved, so that the combined characteristics are used as input characteristics of a binary logic regression model to carry out prediction of a preset event result, and thus the complexity and the uncertainty of manual searching of the characteristics are avoided, the prediction accuracy of the sample data for the preset event result is improved, and meanwhile, the accuracy and the efficiency of sample data evaluation are also improved.

Owner:CHINA PING AN LIFE INSURANCE CO LTD

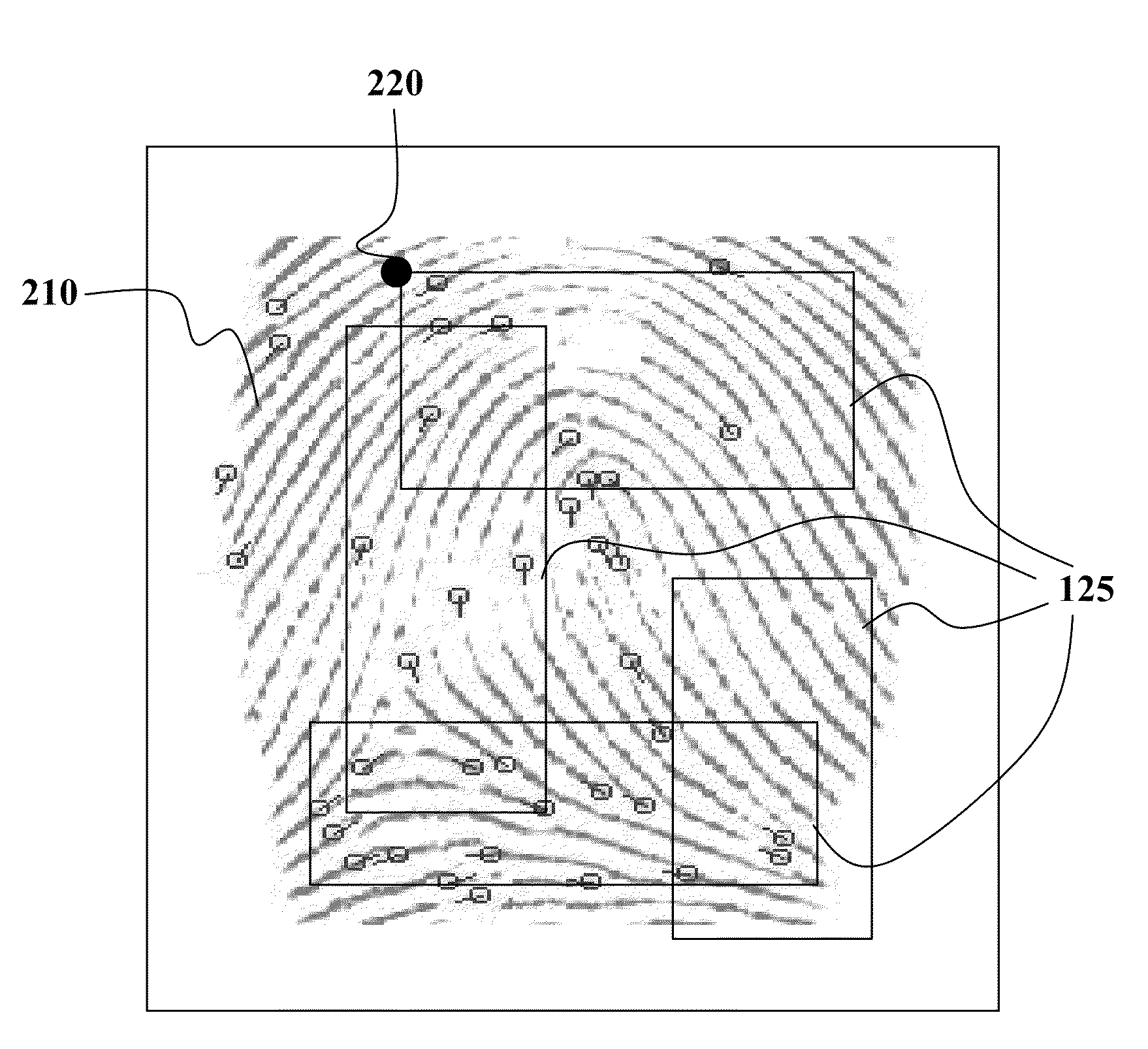

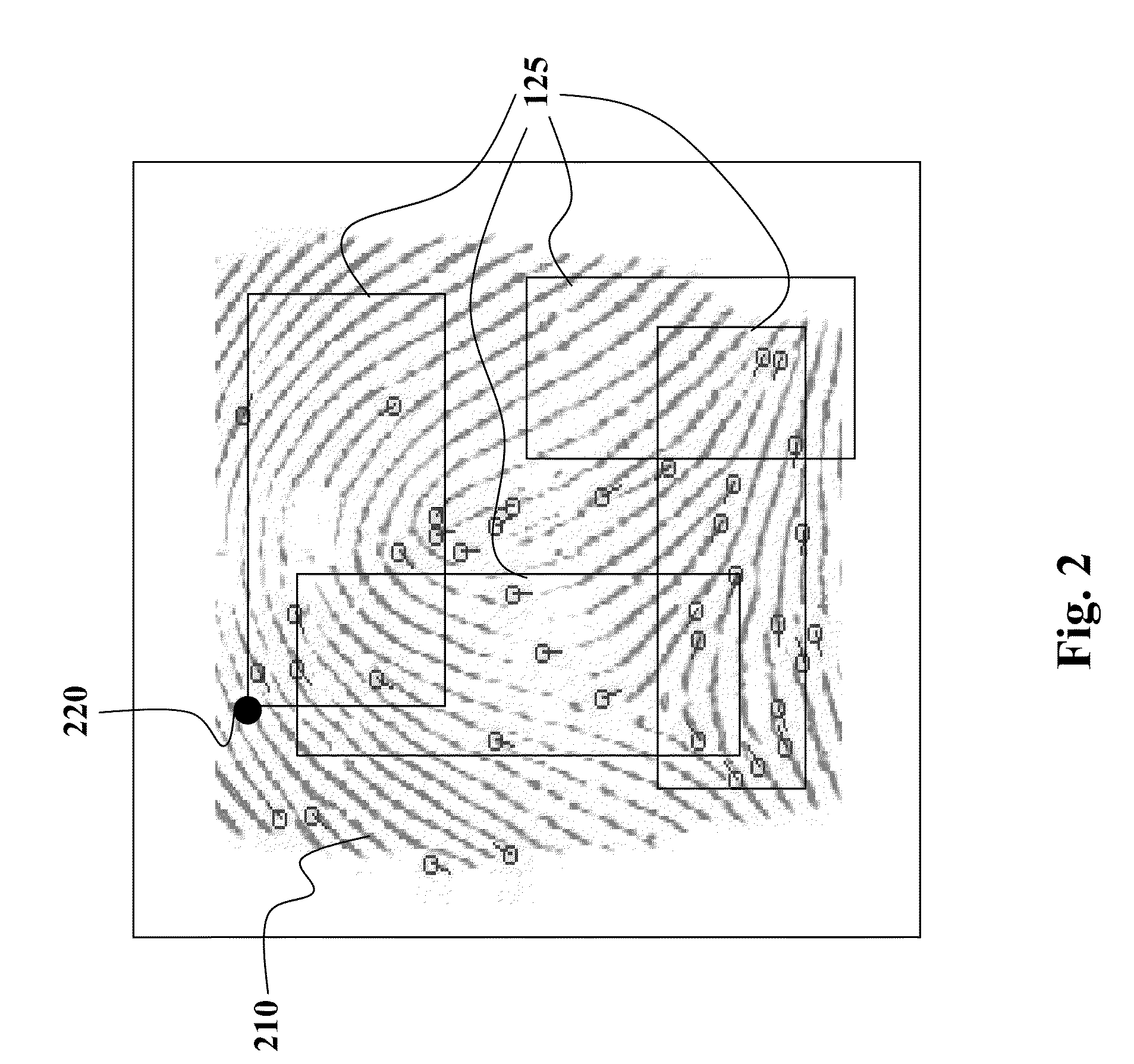

Method and System for Binarization of Biometric Data

ActiveUS20100119126A1Reliable informationCharacter and pattern recognitionSecuring communicationFeature vectorBiometric data

Embodiments of the invention disclose a system and a method for transforming a biometric of a user to a binary feature vector suitable for user authentication, comprising steps of: partitioning the biometric into a set of regions, wherein each region is a contiguous region confining a part of the biometric; determining, for each region, biometric parameters; applying, to each region, binary logical conditions to produce at least one bit of the binary feature vector, wherein the applying is performed by a processer; and outputting the binary feature vector.

Owner:MITSUBISHI ELECTRIC RES LAB INC

All-optical logic gates using nonlinear elements-claim set II

InactiveUS20070189705A1Change quantityPrecise arrangementNanoopticsOptical light guidesLinear elementLogic gate

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEY JOHN

Medical image robust watermarking method based on SIFT-DCT

The invention discloses a medical image robust watermarking method based on SIFT-DCT, and belongs to the field of multimedia signal processing. The method comprises the steps of firstly, carrying outsymbol encryption on a watermark in a frequency domain by utilizing the properties of a Logistic Map; secondly, extracting an eigenvector by performing SIFT-DCT on a medical image to perform watermarkembedding, associating the eigenvector with a binary watermark to obtain a binary logic sequence, and storing the binary sequence in a third party; and thirdly, extracting an eigenvector by performing the SIFT-DCT on the to-be-tested medical image again, and associating the eigenvector with the binary sequence stored in the third party to carry out watermark extraction. The method is a medical image digital watermarking technology based on the SIFT-DCT, has relatively good robustness, and is especially outstanding for geometric attacks such as rotation, translation, shearing and the like; and watermark embedding does not change contents of original encrypted volume data, so that the method is a zero watermarking technology.

Owner:HAINAN UNIVERSITY

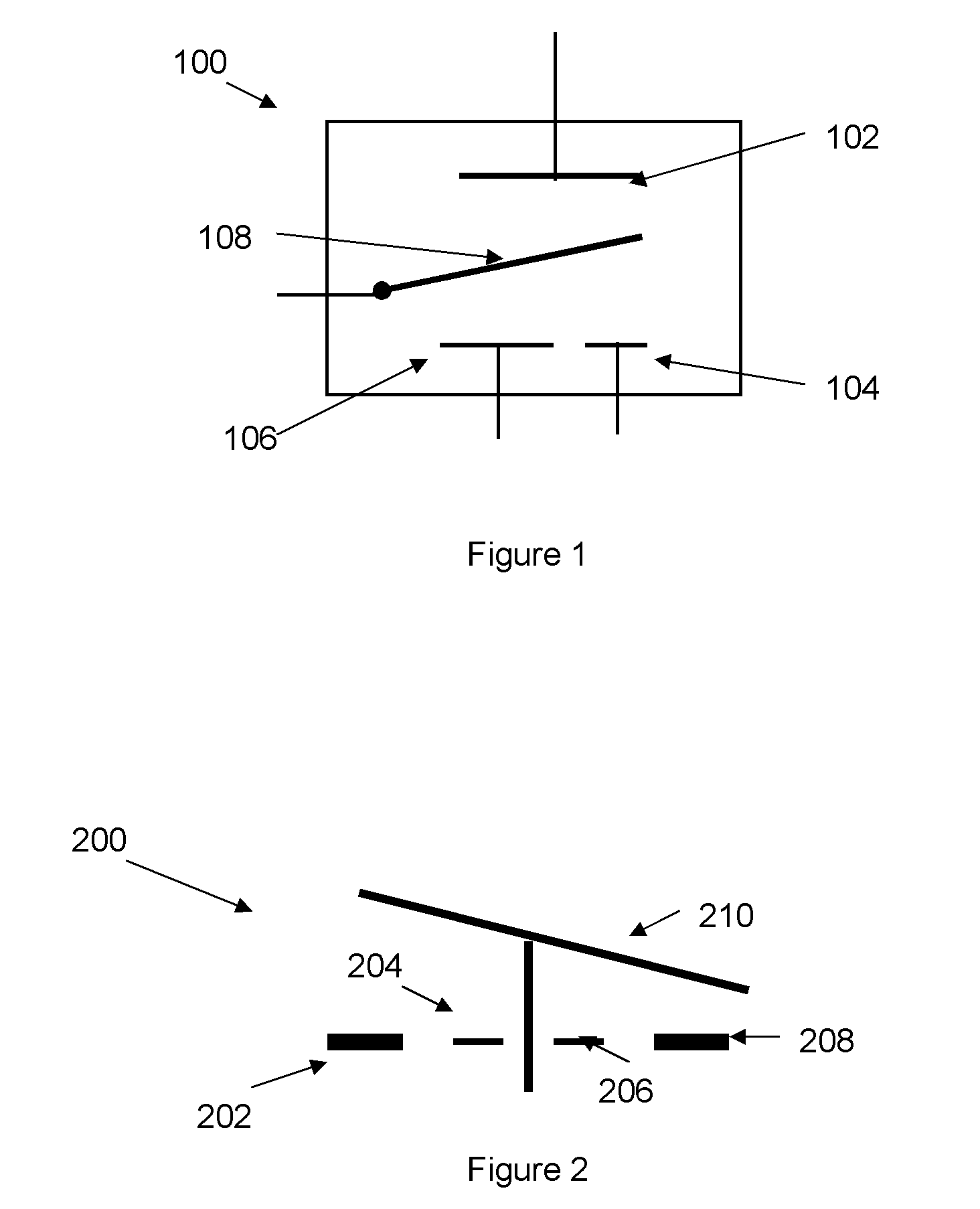

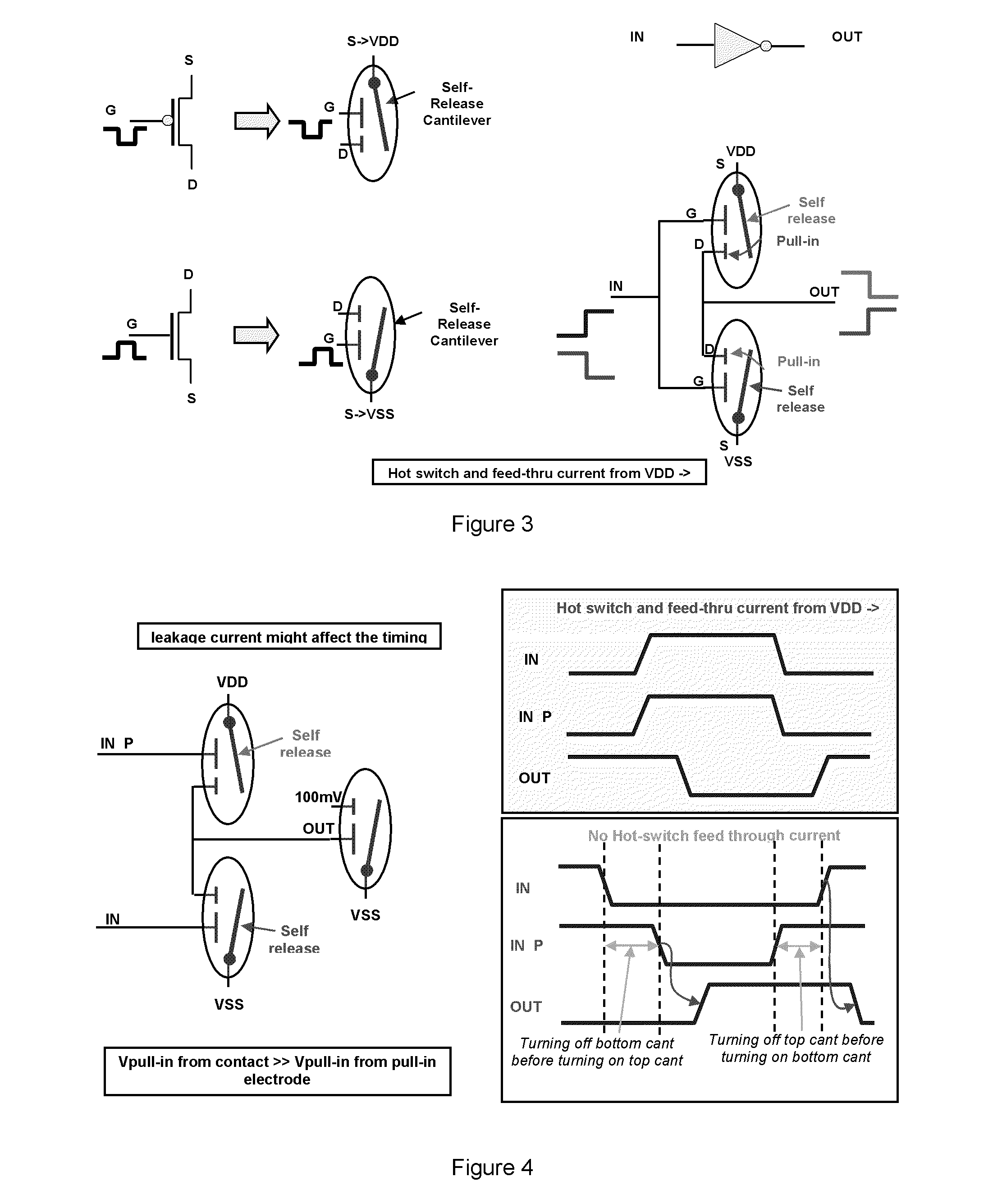

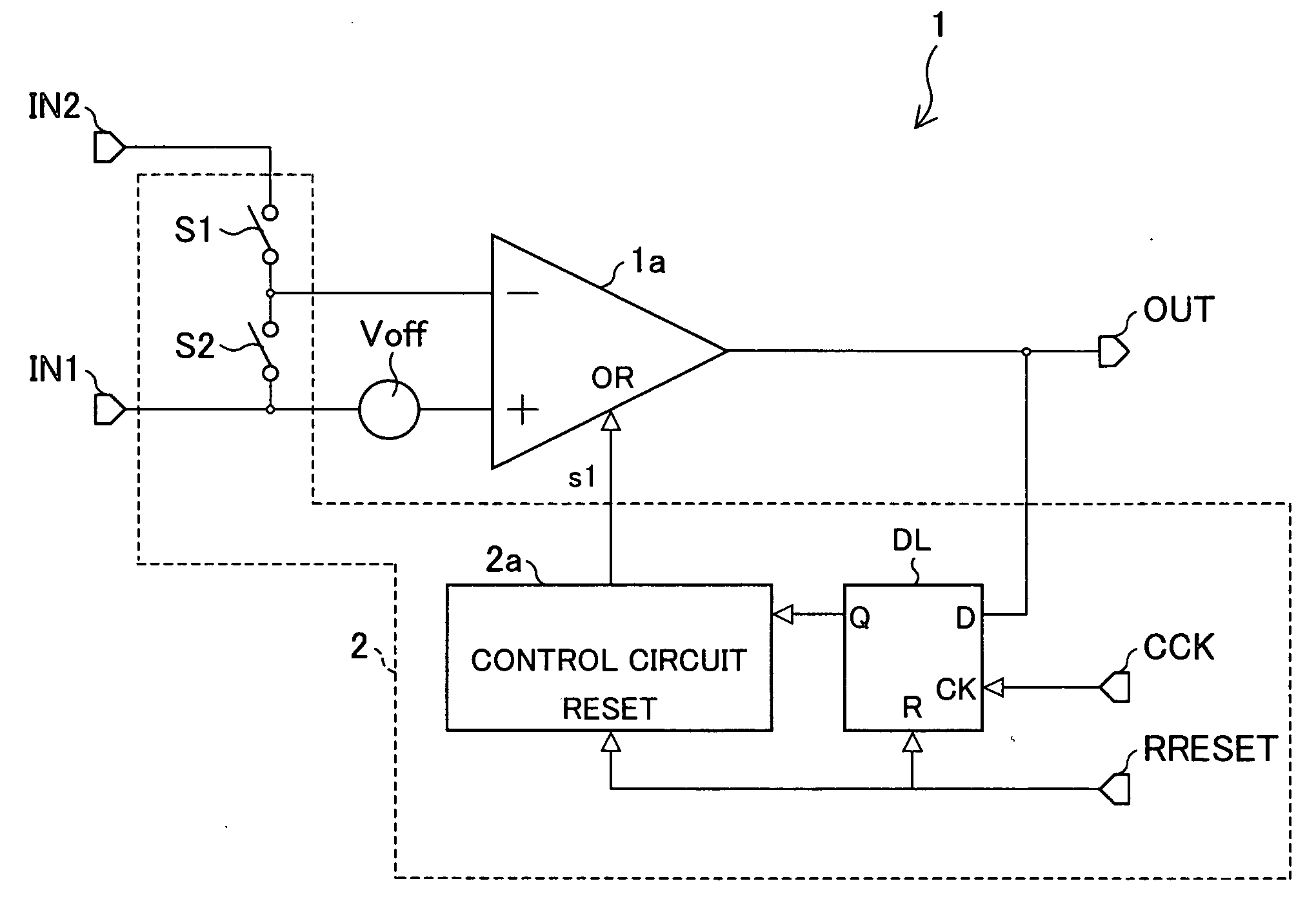

Binary Logic Utilizing MEMS Devices

ActiveUS20110002168A1Space utilizationNecessitating useRead-only memoriesDigital storageNvSRAMTransistor

Embodiments disclosed herein generally relate to switches that utilize micro-electromechanical systems (MEMS). By replacing transistors in many devices with switches such as MEMS switches, the devices may be used for logic applications. MEMS switches may be used in devices such as FPGAs, NAND devices, nvSRAM devices, AMS chips and general memory logic devices. The benefit of utilizing MEMS devices in place of transistors is that the transistors utilize more space on the chip. Additionally, the MEMS devices can be formed in the BEOL without having any negative impacts on the FEOL or necessitating the use of additional layers within the chip.

Owner:QORVO US INC

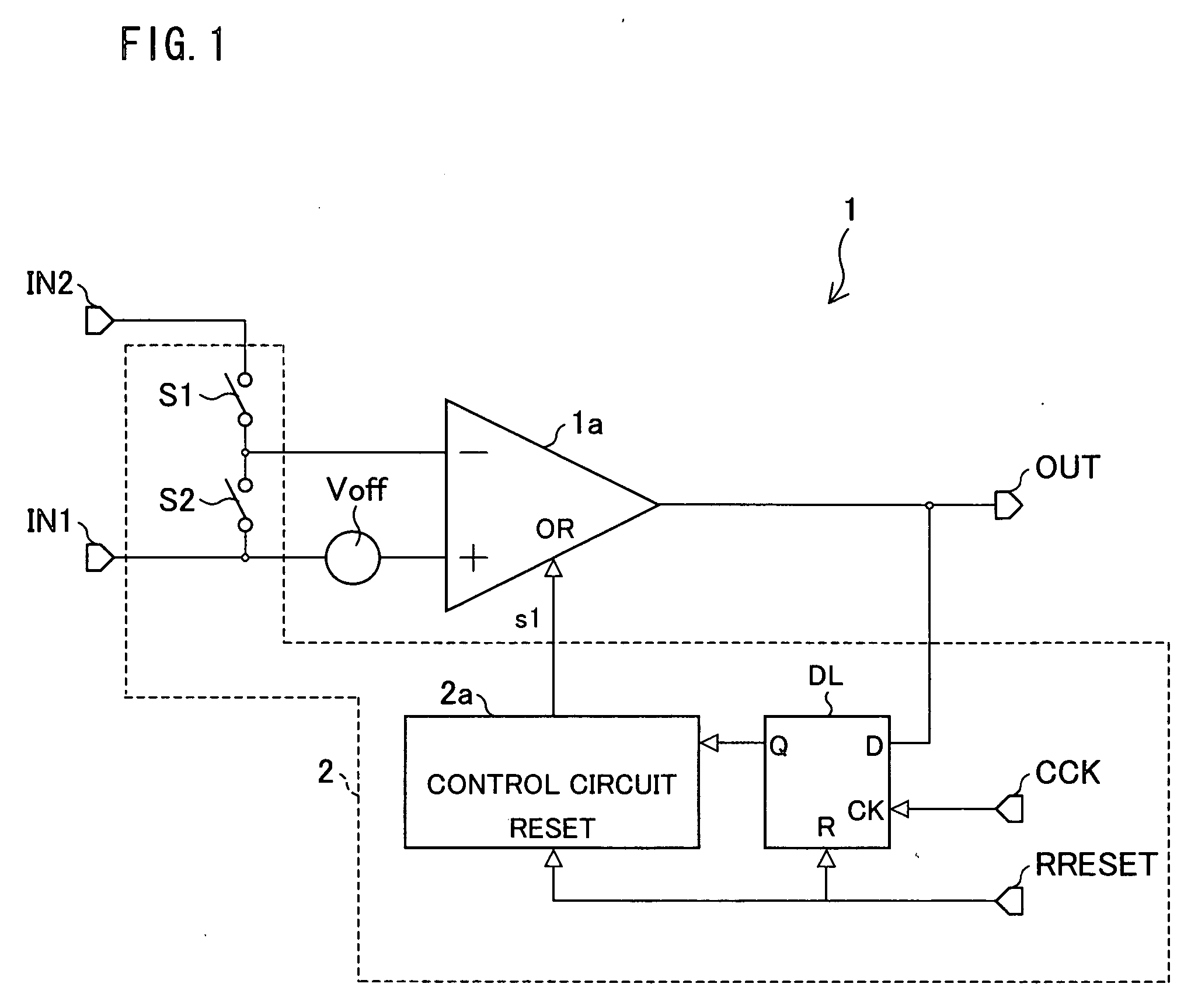

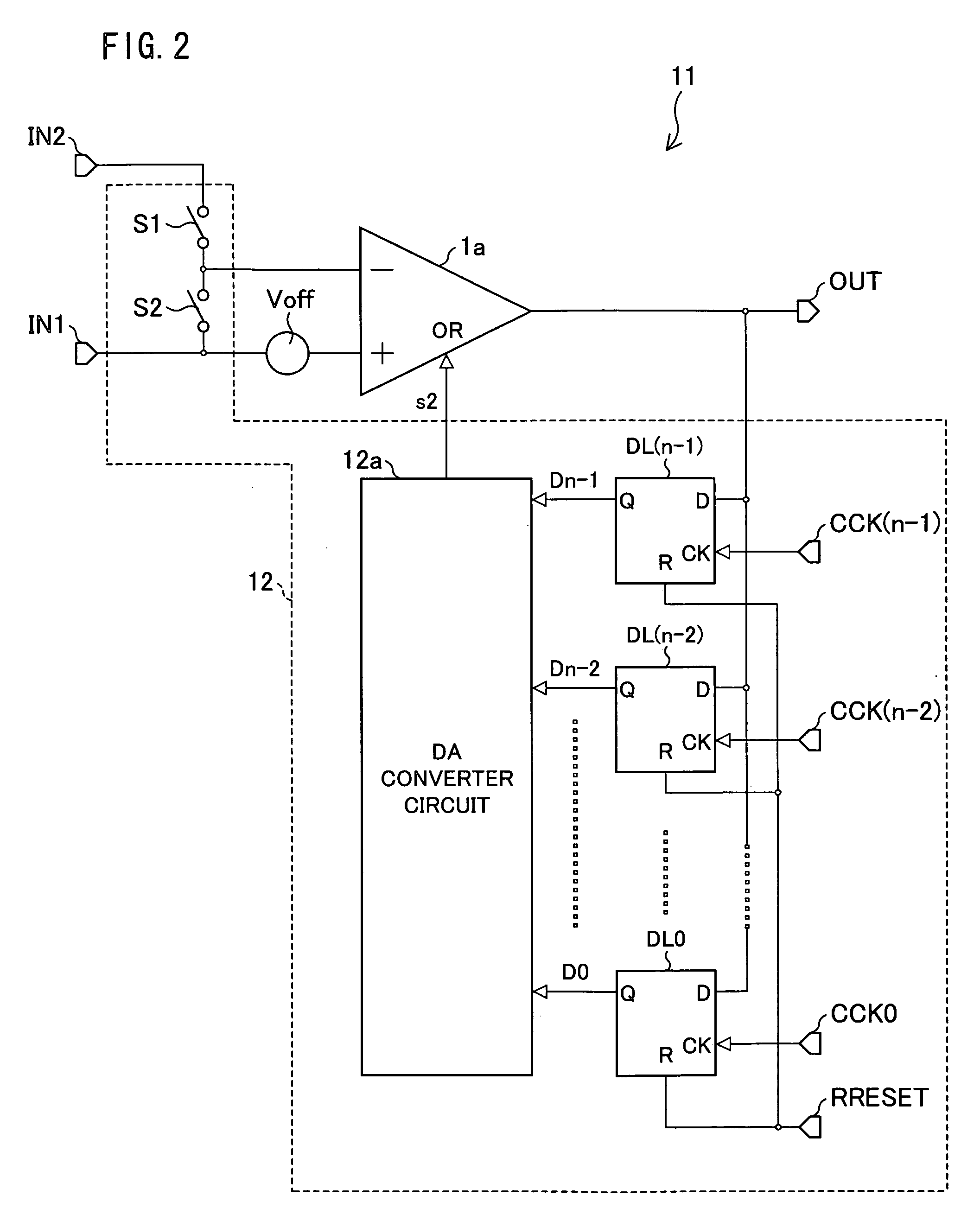

Offset adjusting circuit and operational amplifier circuit

InactiveUS20060255855A1Reduce variationLow costAmplifier modifications to raise efficiencyDc-amplifiers with dc-coupled stagesEngineeringBinary logic

The present invention provides an offset adjusting circuit and an operational amplifier circuit. In the operational amplifier circuit (1), a switching element (S1) is closed and a switching element (S2) is opened. The latch circuit DL latches an output voltage of an operational amplifier (1a), and output a Q-output in accordance with the output voltage. The control circuit (2a) inputs an offset adjustment signal s1 to an offset adjustment input terminal OR of the operational amplifier (1a). Then, the latch circuit DL latches the output voltage having been subjected to the offset adjustment, and the offset adjustment signal s1 is finely adjusted for adjusting the remaining offset. In this way, the offset in the output voltage of the operational amplifier (1a) is quantized in accordance with the number of times the latching operation has been performed, and is stored in the control circuit (2a) in the form of a binary logical signal.

Owner:SHARP KK

All-optical logic gates using nonlinear elements - claim set vi

InactiveUS20070248124A1Change quantityPrecise arrangementLaser using scattering effectsCoupling light guidesLogic gateNonlinear element

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEY JOHN

Linear voltage controlled oscillator transconductor with gain compensation

InactiveUS20020089381A1Decrease resistance of variable resistanceMore of the gainPulse automatic controlPulse generation by logic circuitsPhase locked loop circuitLow-pass filter

A voltage controlled oscillator of a phase locked loop circuit having digitally controlled gain compensation. The digital control circuitry provides binary logic input to the voltage controlled oscillator for a digitally controlled variable resistance circuit, a digitally controlled variable current transconductor circuit, or differential transistor pairs having mirrored circuitry for adjusting the V-I gain. The latter configuration requires the voltage controlled oscillator to incorporate a source-coupled differential pair which is driven by a low pass filter capacitor output voltage, and connected to load transistors; a current source and a current mirror for generating a tail current; individual banks of transistors to mirror the load transistor currents; a digital-to-analog converter with control lines outputted there from, the digital-to-analog converter used to increase the amount of current allowed to flow to the transconductor output, the current being digitally increased and decreased corresponding to an amount of current pulled from the current source, and mirroring the current through at least one transistor mirror circuit.

Owner:MARVELL ASIA PTE LTD

All-optical logic gates using nonlinear elements - claim set V

InactiveUS20070189665A1Change quantityPrecise arrangementCoupling light guidesLogic circuits using opto-electronic devicesLinear elementLogic gate

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEY JOHN

All-optical logic gates using nonlinear elements - claim set IV

InactiveUS20070189704A1Change quantityPrecise arrangementNanoopticsLight demodulationLinear elementEngineering

An all-optical logic gates comprises a nonlinear element such as an optical resonator configured to receive optical input signals, at least one of which is amplitude-modulated to include data. The nonlinear element is configured in relation to the carrier frequency of the optical input signals to perform a logic operation based on the resonant frequency of the nonlinear element in relation to the carrier frequency. Based on the optical input signals, the nonlinear element generates an optical output signal having a binary logic level. A combining medium can be used to combine the optical input signals for discrimination by the nonlinear element to generate the optical output signal. Various embodiments include all-optical AND, NOT, NAND, NOR, OR, XOR, and XNOR gates and memory latch.

Owner:COVEY JOHN

Medical image robust watermarking method based on Arnold scrambling transformation and DCT (discrete cosine transformation)

InactiveCN102930500ASolve the quickness problemImprove safety and reliabilityImage data processing detailsFeature vectorHash function

The invention discloses a medical image robust watermarking method based on Arnold scrambling transformation and DCT (discrete cosine transformation), belonging to the field of multimedia signal processing. The method comprises the following steps: firstly embedding a watermark, specifically including (1) carrying out Arnold transformation on the watermark to be embedded to implement the pretreatment, (2) carrying out overall image DCT transformation on a medical image, and extracting a vector of a feature in a transformation domain, (3) obtaining a binary logic sequence through a Hash function by using the feature vector and the pre-treated watermark; and then carrying out watermark extraction, specifically including (4) carrying out overall image DCT transformation on a medical image to be tested, and extracting a feature vector; (5) extracting the watermark by using the property of the Hash function and a binary logic sequence of a third party; and (6) obtaining the original watermark through inverse transformation of the Arnold scrambling transformation. The experiment shows that the method has a very good information hiding capability and is of great significance in protecting the information of a patient in telemedicine.

Owner:HAINAN UNIVERSITY

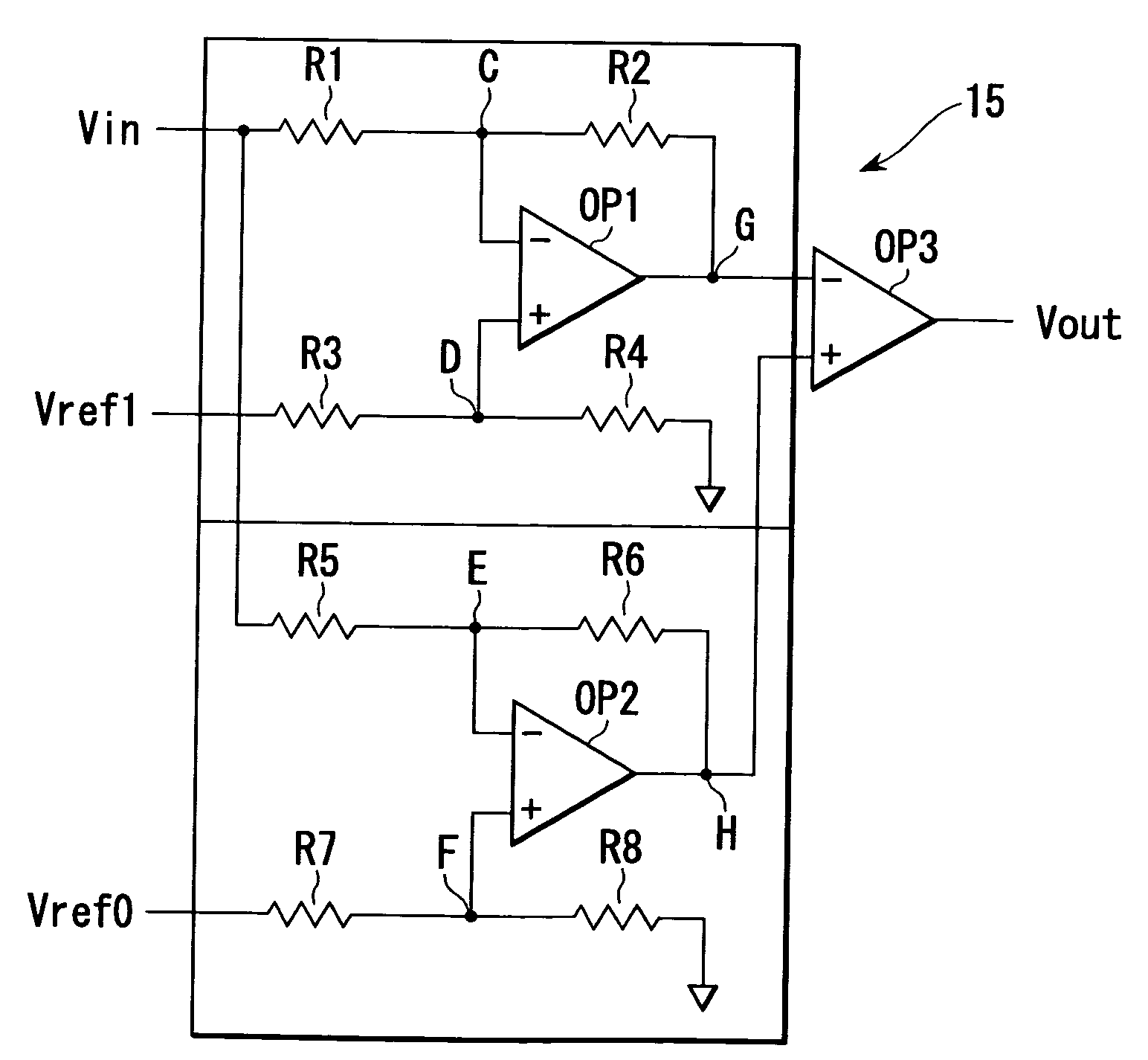

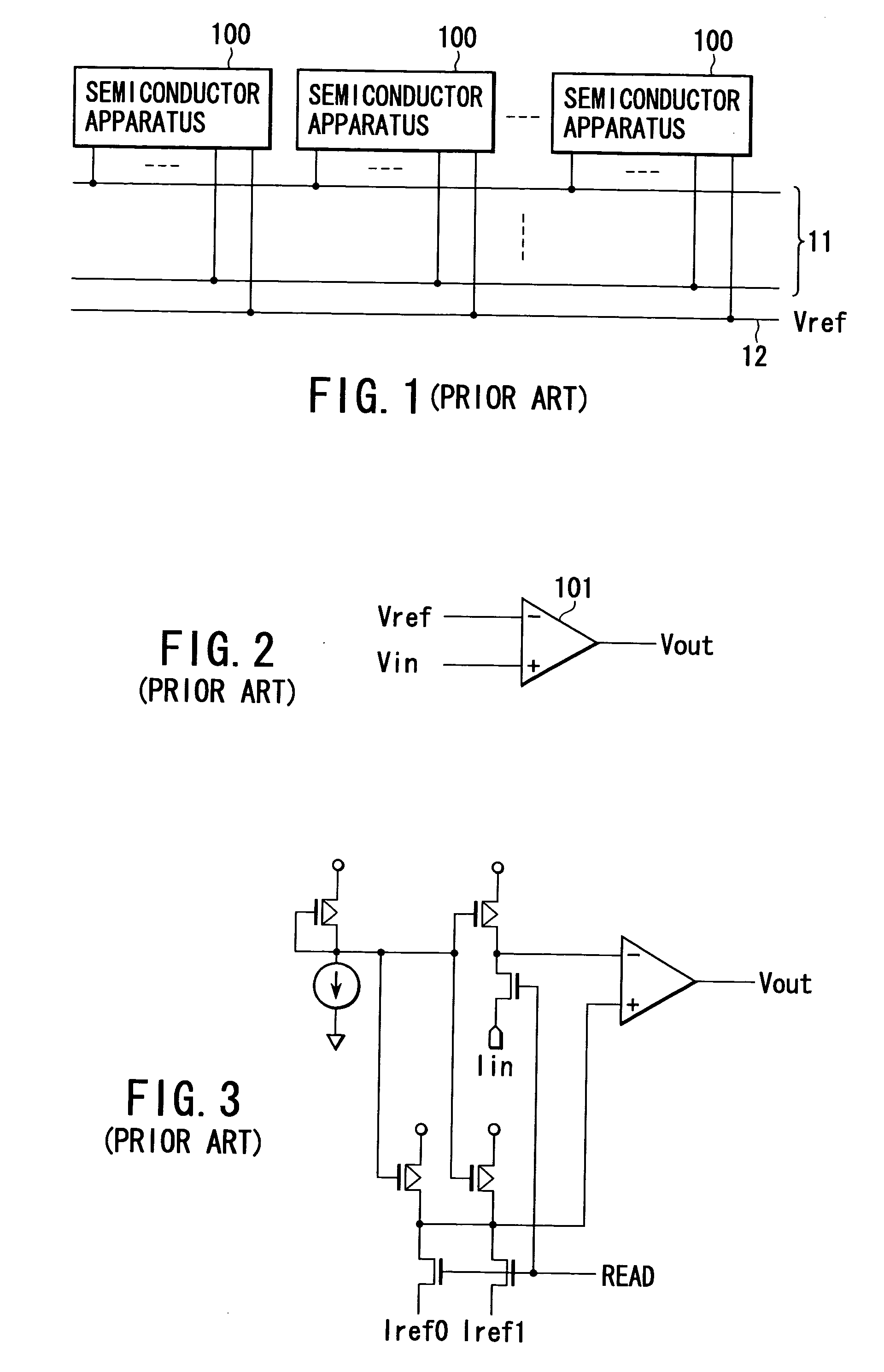

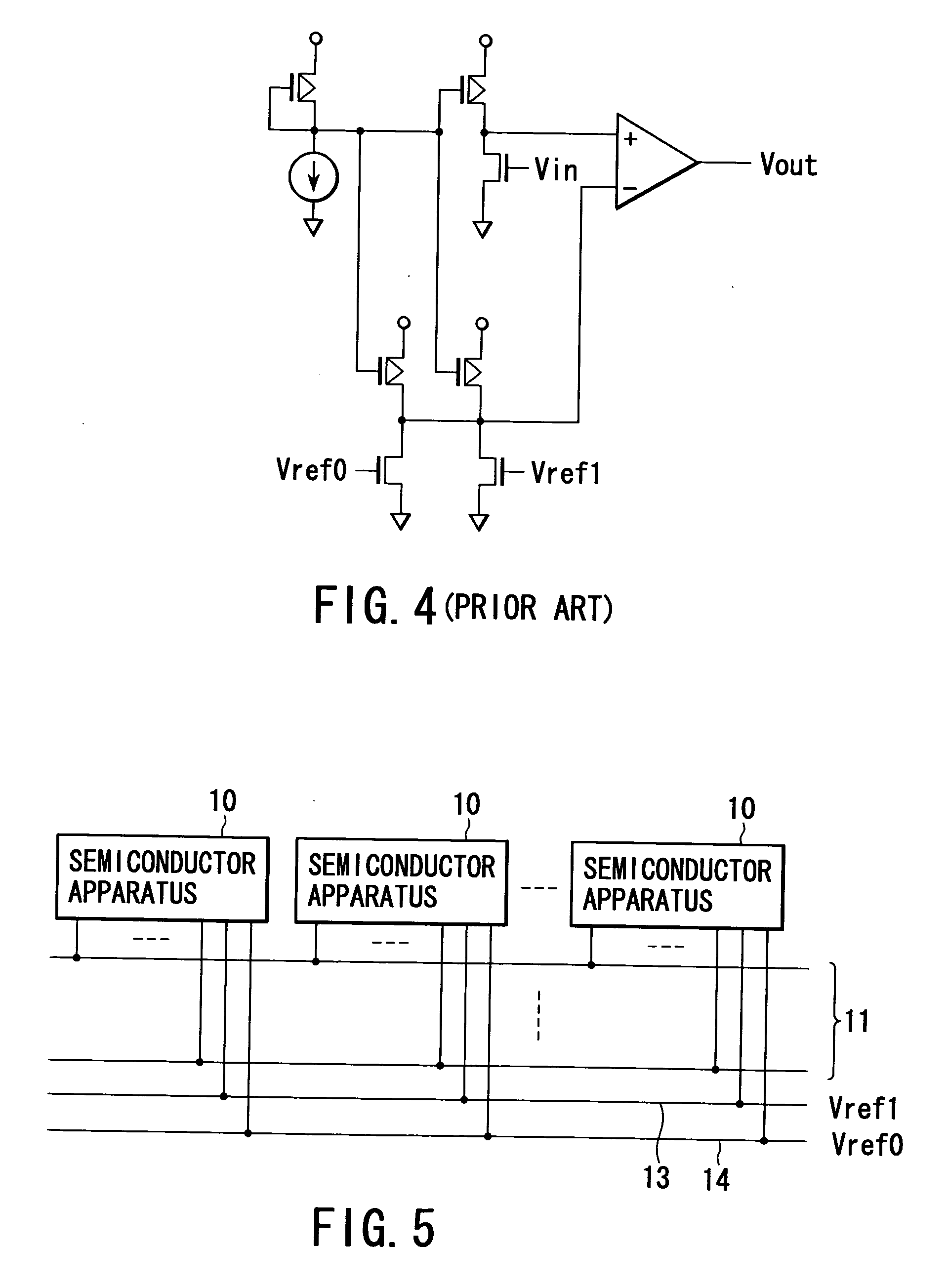

Semiconductor apparatus having logic level decision circuit and inter-semiconductor apparatus signal transmission system

InactiveUS20060023518A1Reliability increasing modificationsAmplifier combinationsDecision circuitSemiconductor

In a signal transmission system between a plurality of semiconductor apparatuses, a logic level decision circuit deciding a logic level of an input signal in accordance with which of two reference signals a signal level of the input signal is close to, by using two reference signals Vref1, Vref0 having a “1” level and a “0” level as reference signals for deciding the logic level of the input signal having a binary logic level, is used as an input receiver of the each semiconductor apparatus.

Owner:KK TOSHIBA

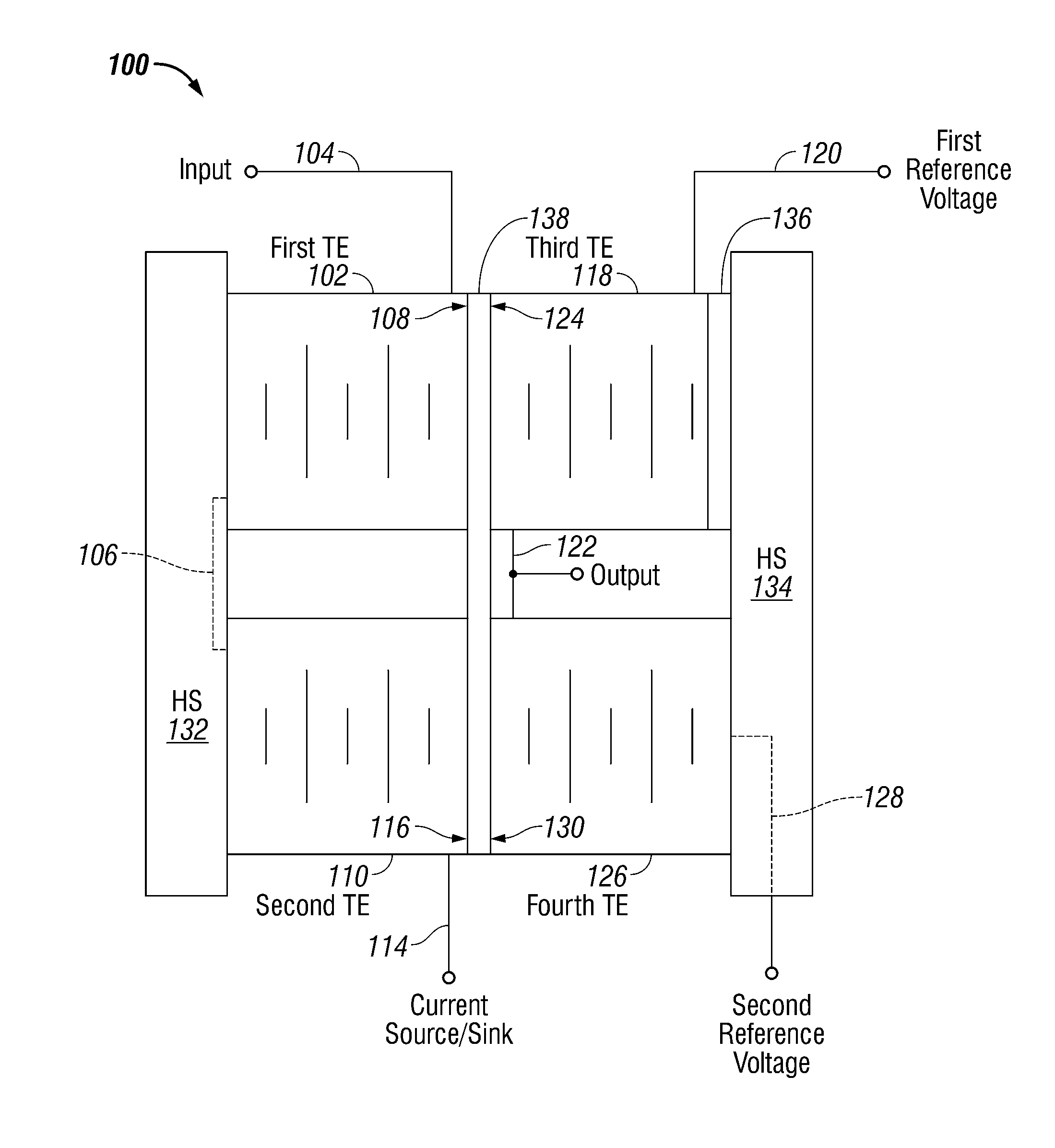

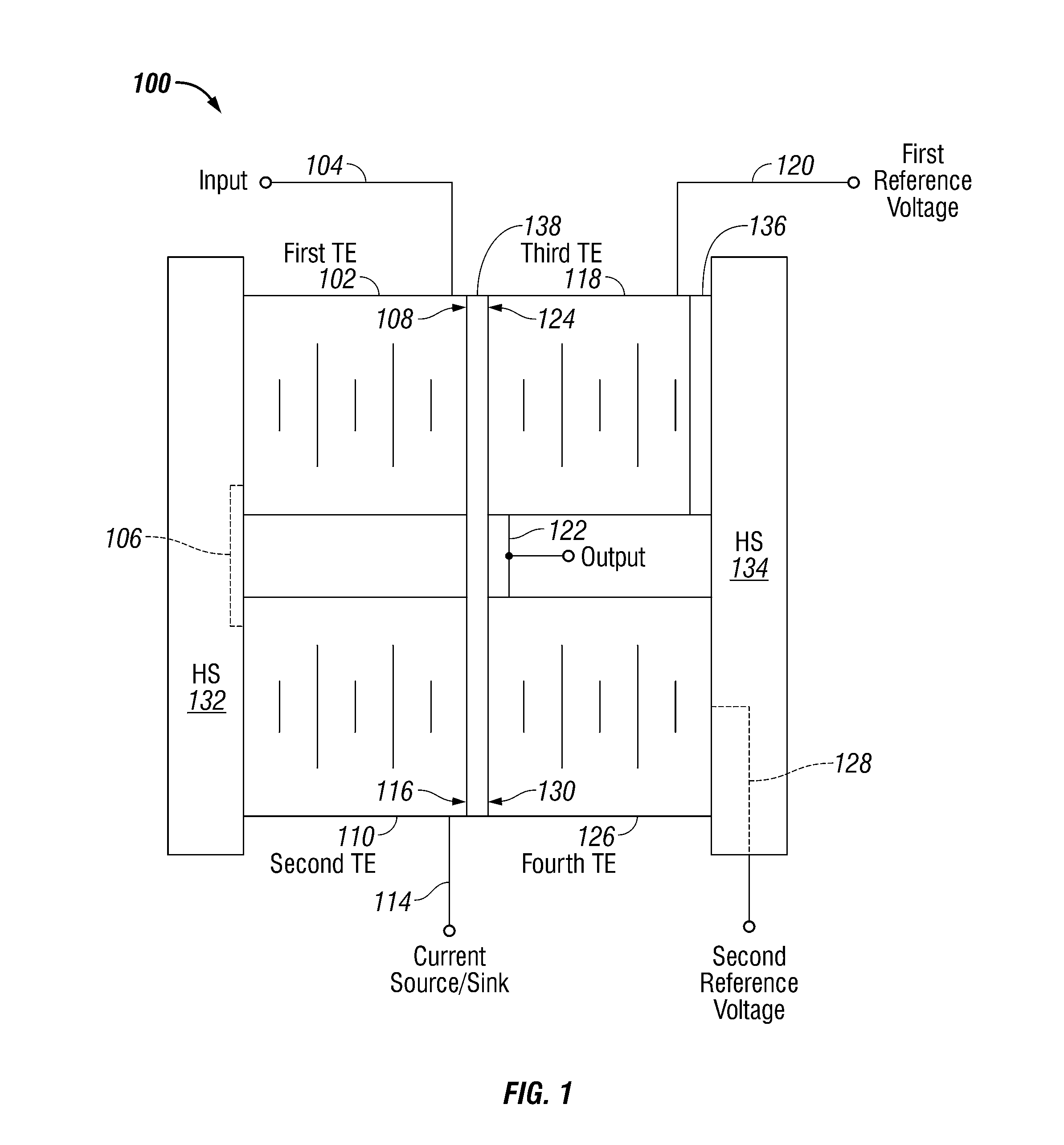

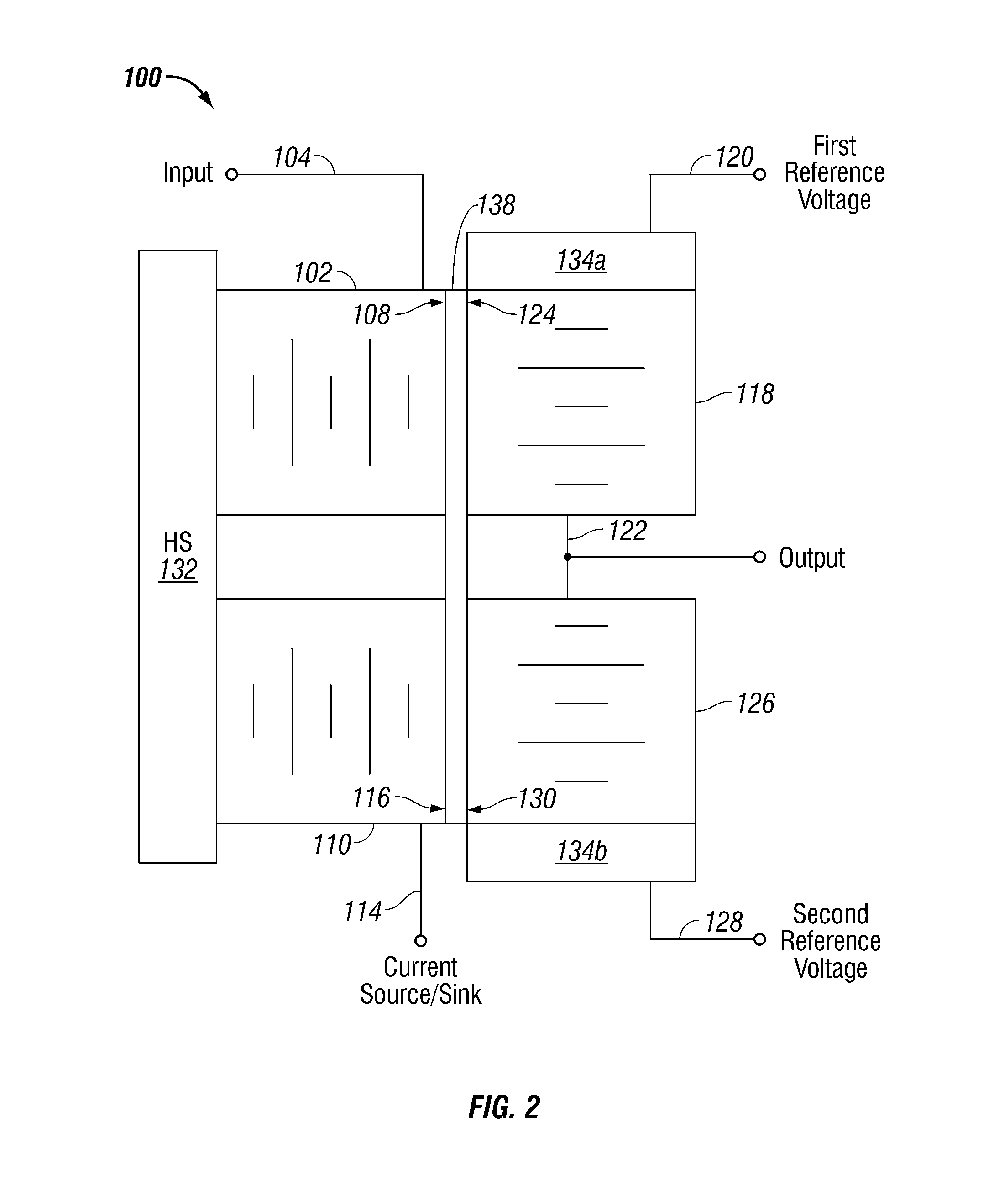

Thermal electric logic circuit

InactiveUS7564267B1Less overall consumptionHigh densityLogic circuits characterised by logic functionLogic circuits using superconductive devicesElectricityVoltage reference

A thermal electric binary logic circuit is provided along with a method for switching a thermal electric binary logic circuit. The method accepts an input voltage representing an input logic state and generates a thermal electric (TE) temperature value in response to the input voltage. Then, in response to the TE temperature value, a TE voltage is generated and supplied as an output voltage representing an output logic state. In one aspect, a first TE element is connected to the input voltage and to a current source / sink having an intermediate voltage. As a result, the first TE element generates a first temperature reference. A second TE thermally is connected to the first TE, electrically connected to a first voltage reference, and electrically connected to an output to supply the output voltage. As a result, a first voltage varies across the second TE in response to the first temperature.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

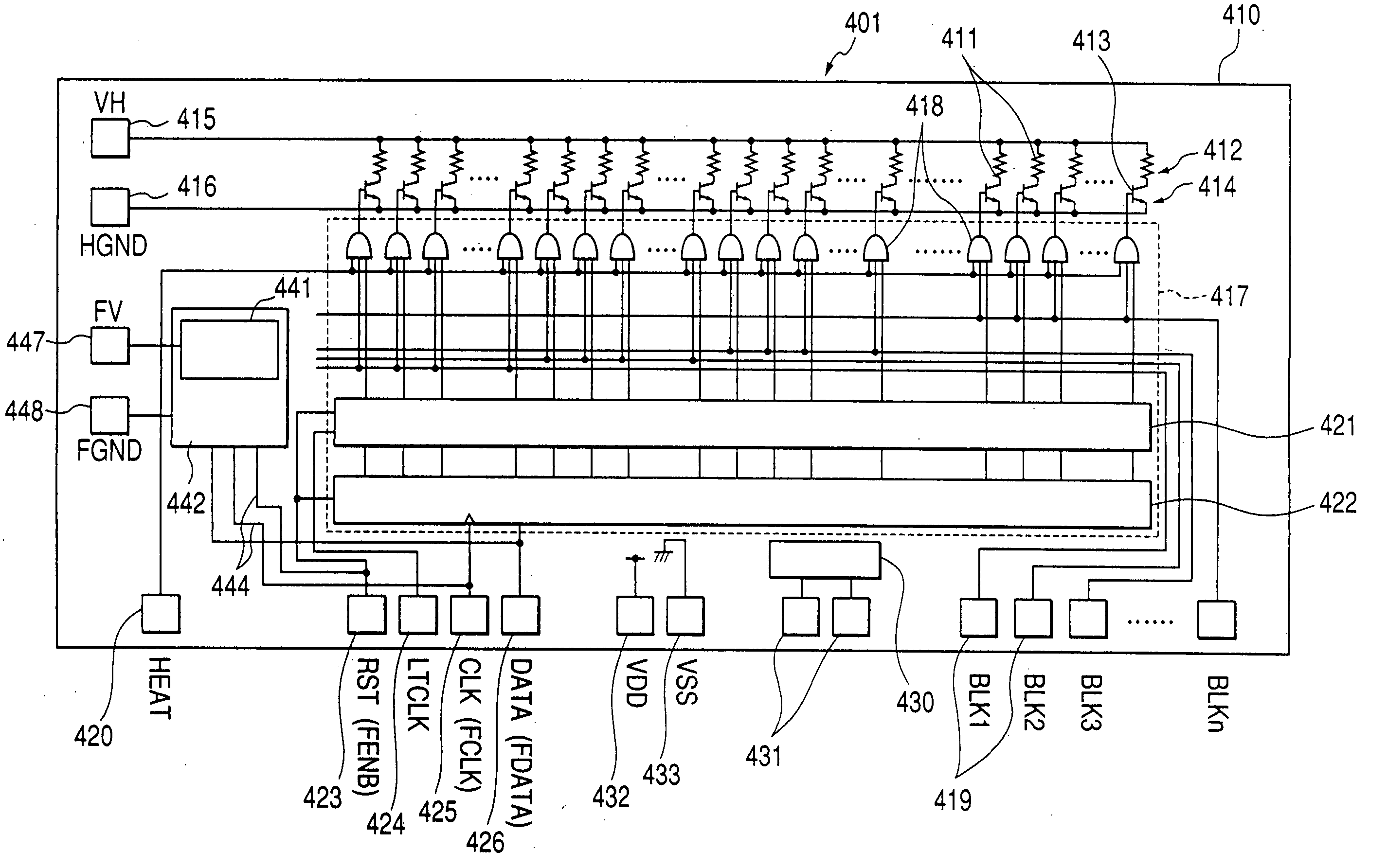

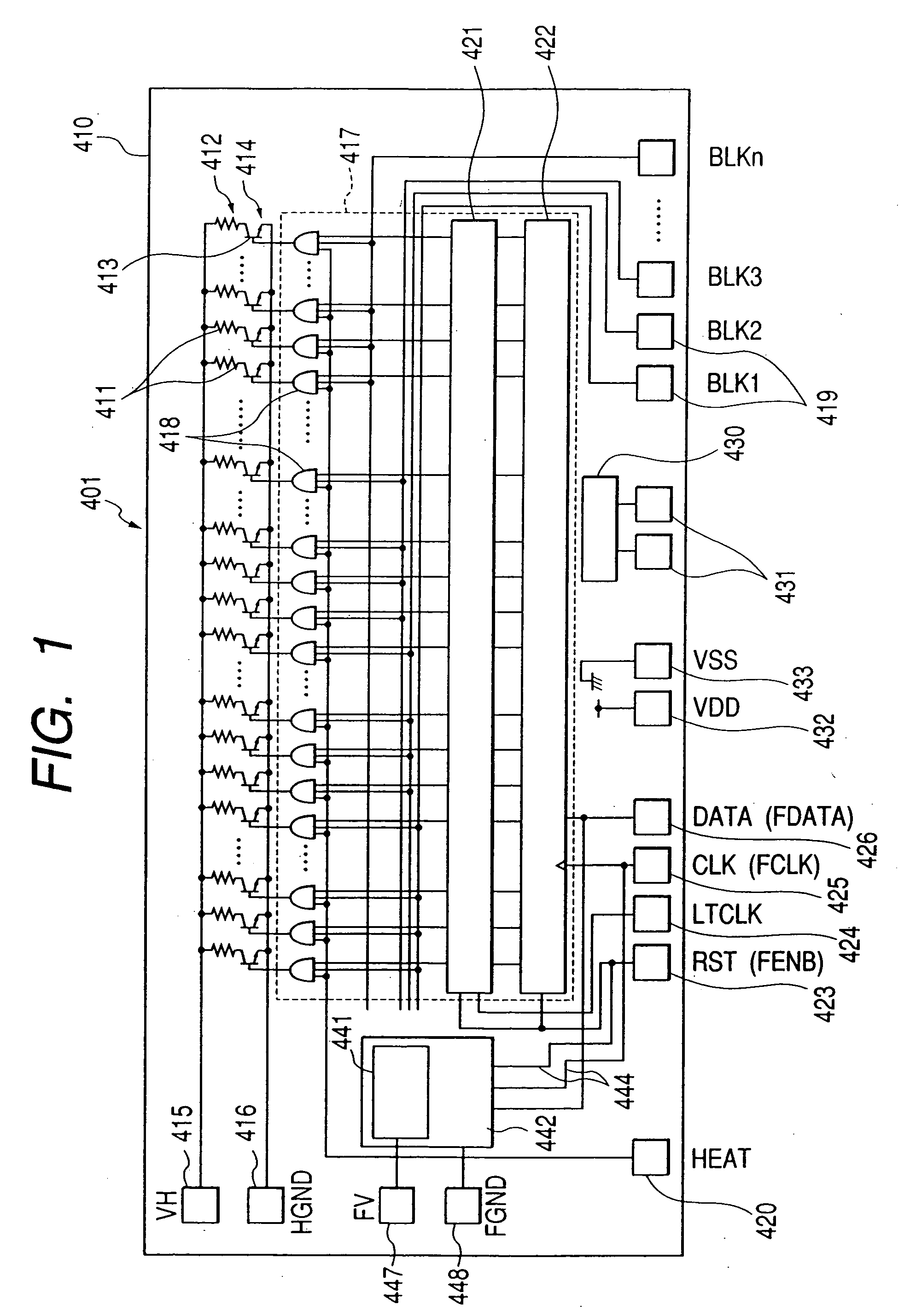

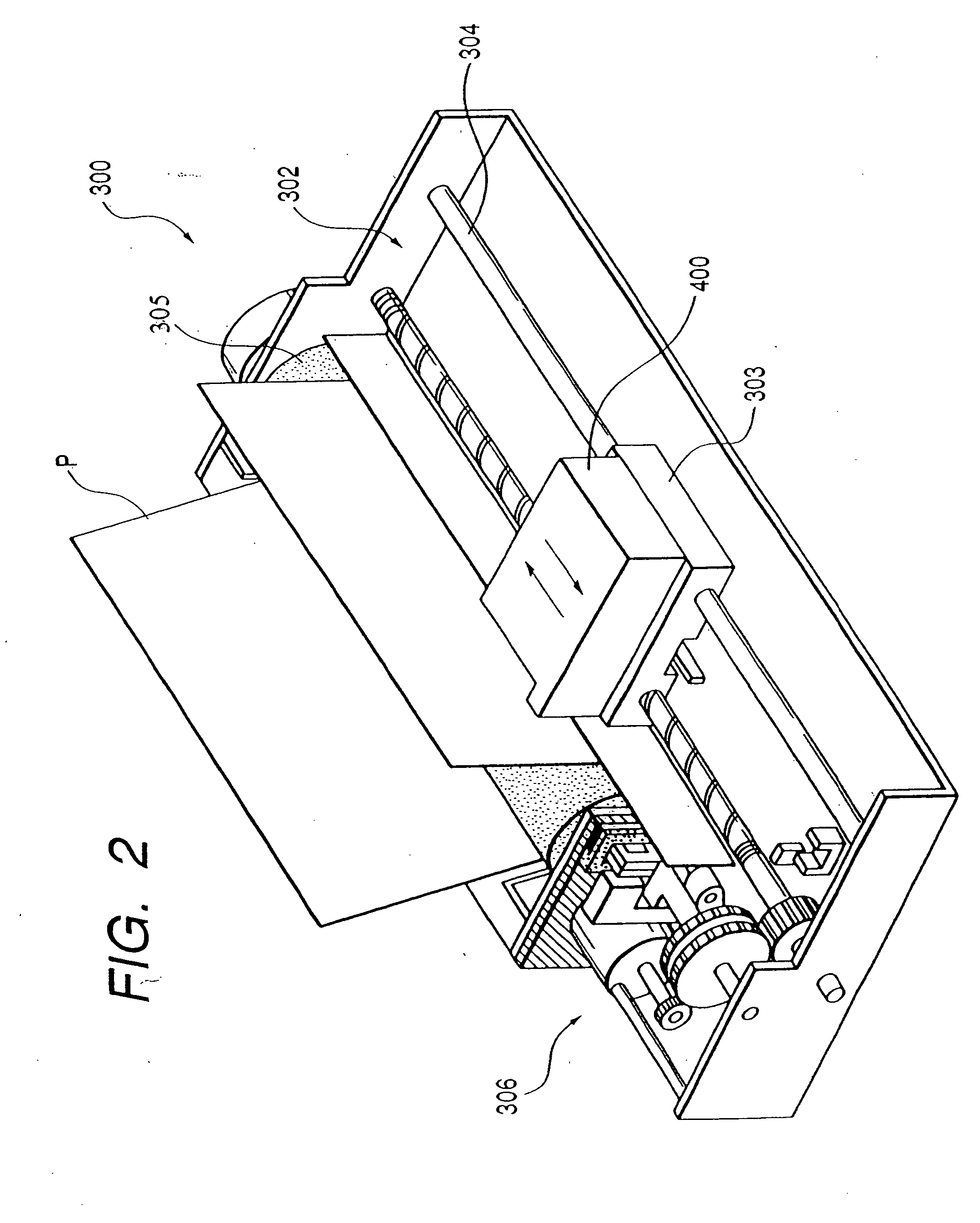

Head substrate having data memory, printing head, printing apparatus and producing method therefor

InactiveUS20060077215A1Minimized increaseAvoiding unnecessary overwritingInking apparatusOther printing apparatusData memoryImage signal

There is disclosed a head substrate of a printing head detachably mounted on a printer main body, comprising plural external connection terminals individually receiving, from the exterior, a binary logic signal corresponding to whether or not to execute a recording operation, a recording image signal and a clock signal, recording execution means for executing the recording operation according to the recording image signal and the clock signal entered through the external connection terminals, in case the binary logic signal is in a first state, data memory means for and data readout, and memory access means for recognizing the binary logic signal in a second state as an access permission signal and executing the memory access to the data memory means at a timing corresponding to the clock signal when the logic signal is a second state.

Owner:CANON KK

Watermarking method for medical images on basis of DFT (discrete Fourier transform) and LogisticMap

InactiveCN102938132ASolve the quickness problemImprove securityImage data processing detailsFeature vectorHash function

The invention relates to a robust watermarking method on the basis of DFT (discrete Fourier transform) and a Logistic Map, and belongs to the field of multimedia signal processing. The robust watermarking method includes preprocessing and embedding watermarks and then extracting and reducing the watermarks, and particularly includes steps of (1), generating a binary encrypted matrix by the aid of the Logistic Map; (2), obtaining encrypted watermarks; (3), performing DFT for an original image and extracting feature vectors; (4), generating a binary logic sequence by the aid of the feature vectors and the chaotically encrypted watermarks to complete the process for preprocessing and embedding the watermarks; (5), performing DFT for an image to be measured to extract vectors of a feature; (6), extracting watermarks by the aid of a Hash function and the binary logic sequence generated when the watermarks are embedded; (7), generating a binary encrypted matrix by the Logistic Map; and (8), solving the reduced watermarks so as to complete the process for extracting and reducing the watermarks. The robust watermarking technology has a high practical value in the aspect of protecting personal information of patients during remote medical treatment.

Owner:HAINAN UNIVERSITY

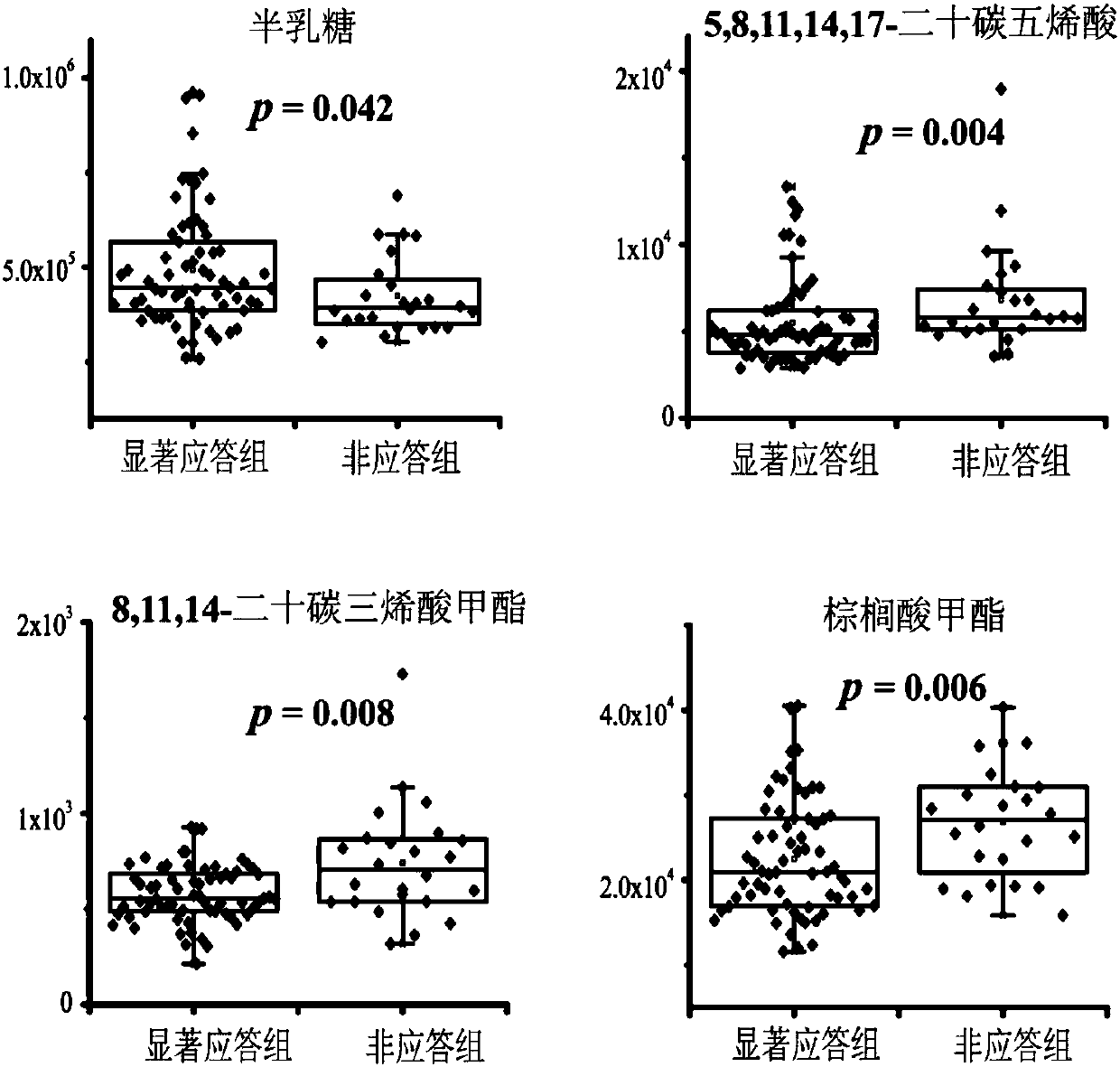

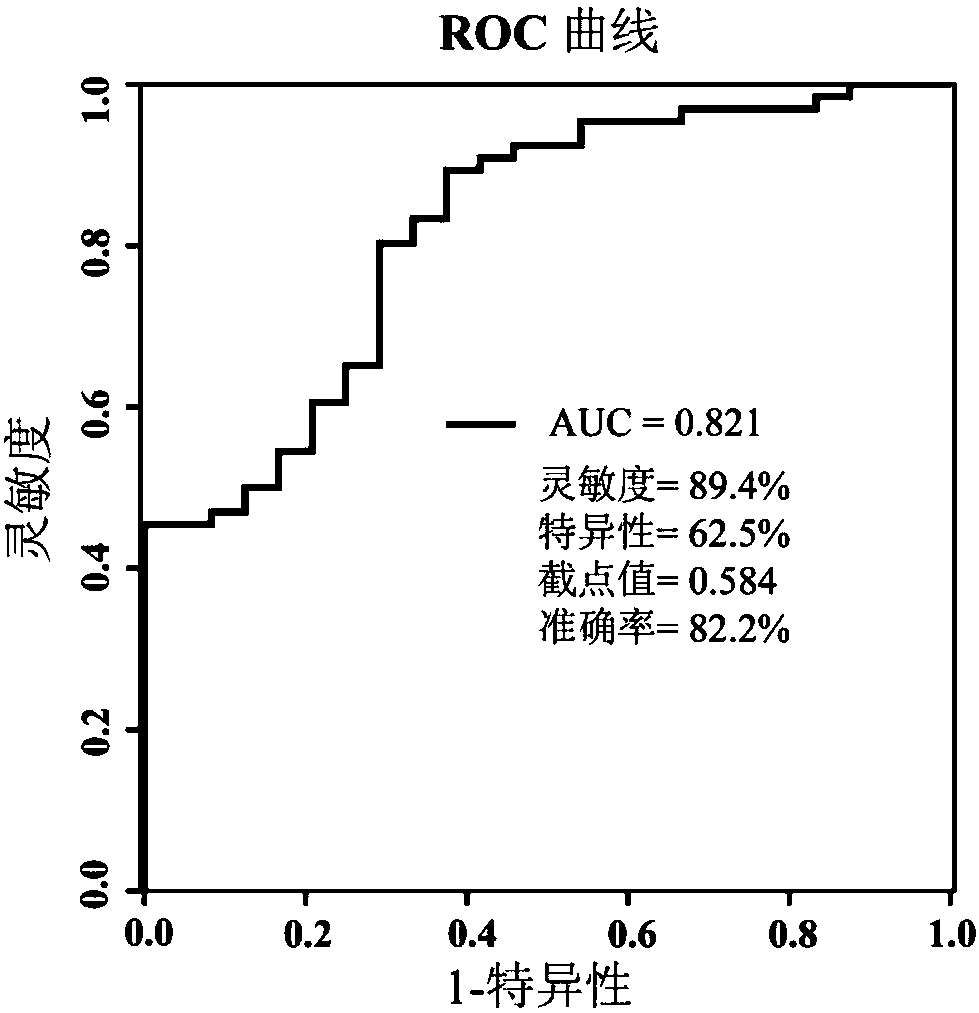

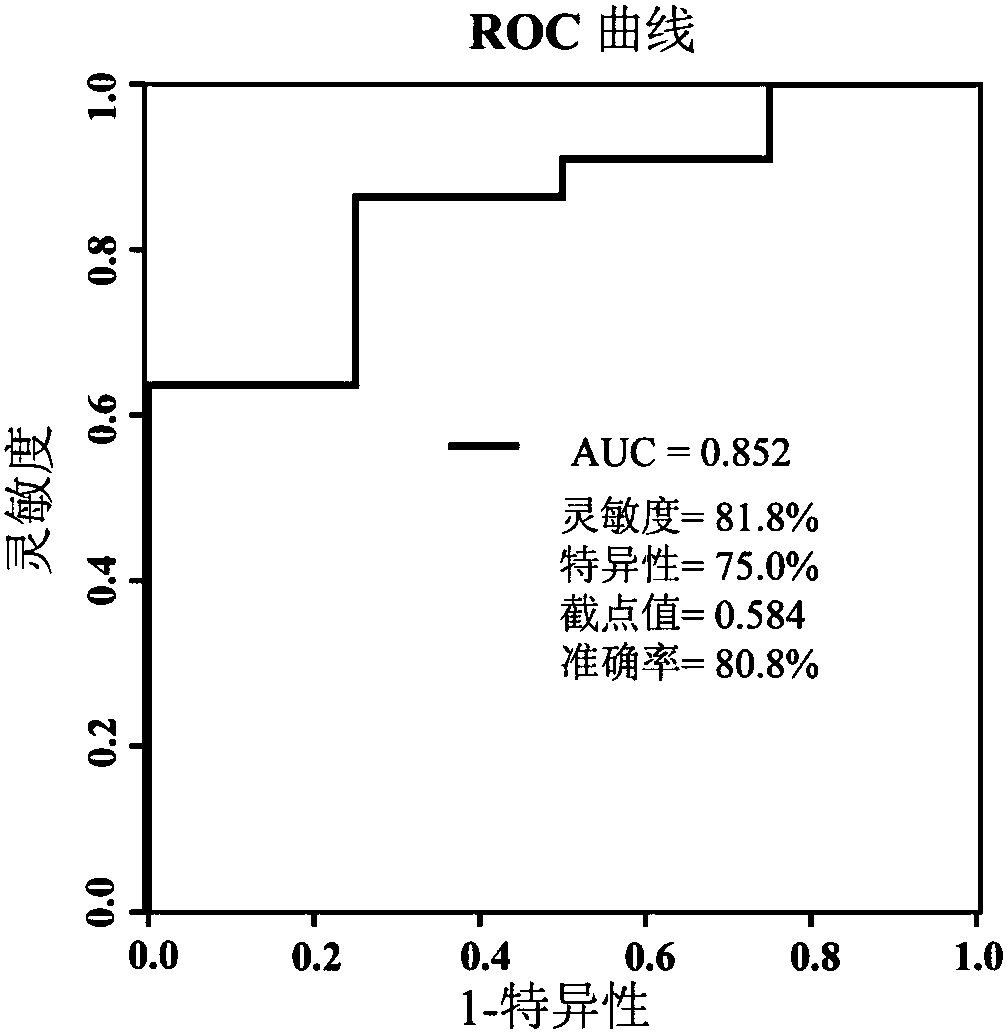

Serum combination marker for evaluating gliclazide applicability of type 2 diabetes mellitus and detection kit thereof

ActiveCN109682909AHigh sensitivityGood repeatabilityComponent separationMetaboliteSmall molecule metabolism

The invention relates to a serum combination marker for evaluating the gliclazide applicability of type 2 diabetes mellitus and a detection kit thereof, in particular to novel application of small-molecule metabolites, namely galactose, 5,8,11,14,17-eicosapentaenoic acid, 8,11,14-epoxyeicosatrienoic acid methyl ester and methyl palmitate, in serum samples in preparing the kit used for evaluating the gliclazide applicability of subjects as combination markers. The invention further relates to a kit for detecting patients remarkably responding to gliclazide in the subjects. By detecting relativeconcentrations of the combination markers in the serum samples of the subjects, the variables of the combination markers are calculated on the basis of a binary logic regression equation, and then onthe basis of determined section values, whether or not the subjects are suitable for gliclazide treatment is judged. The kit can achieve high-sensitivity high-efficiency detection of the small-molecule metabolites, and has the advantages of being low in detection cost, good in repeatability and high in diagnosis sensitivity.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI