Patents

Literature

32 results about "Scalable design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

“Scalable design is a web design solution, it is an turning point that urges designers and developers to become involved, make meaningful contributions and embrace the simplicity for a more productive future”.

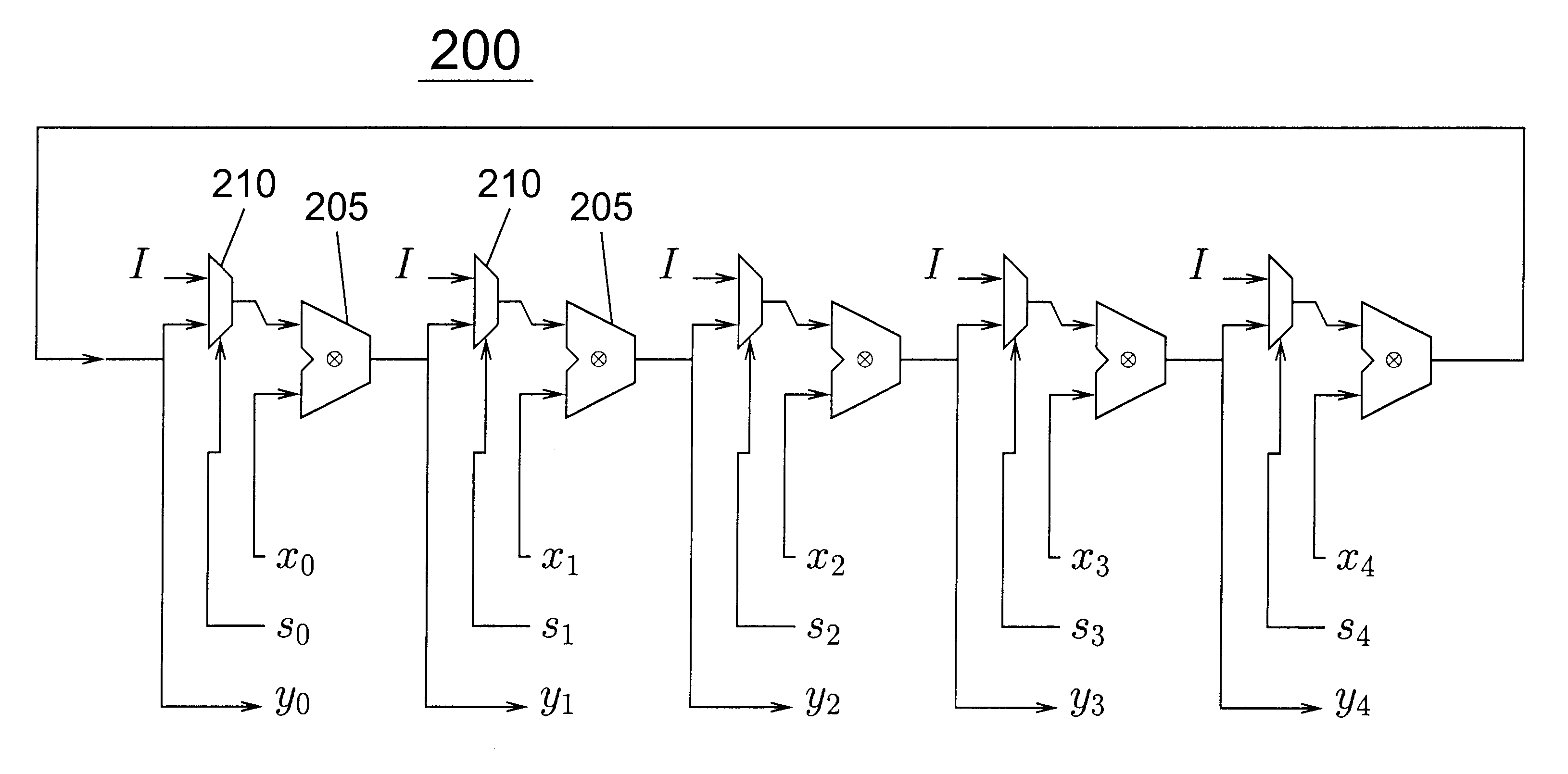

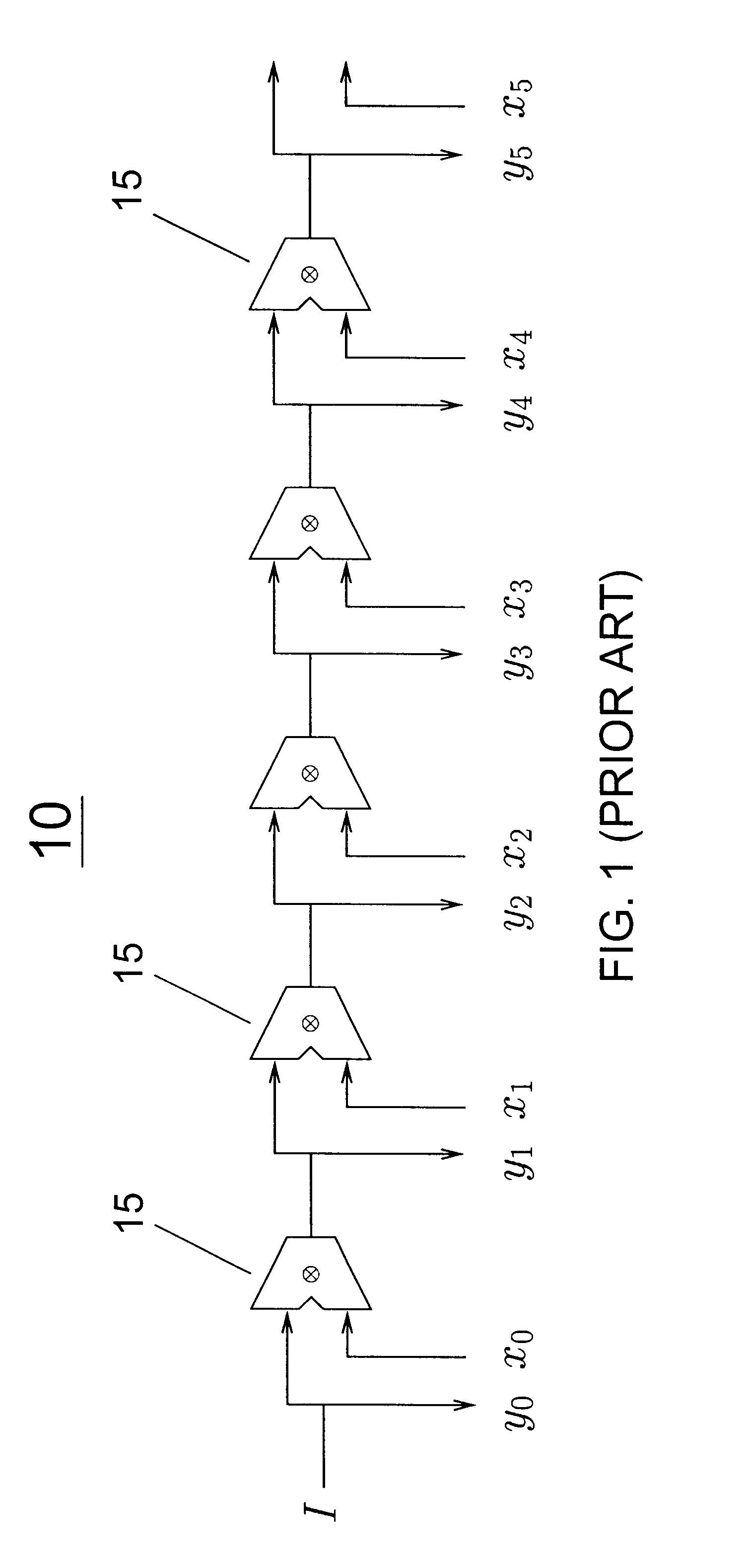

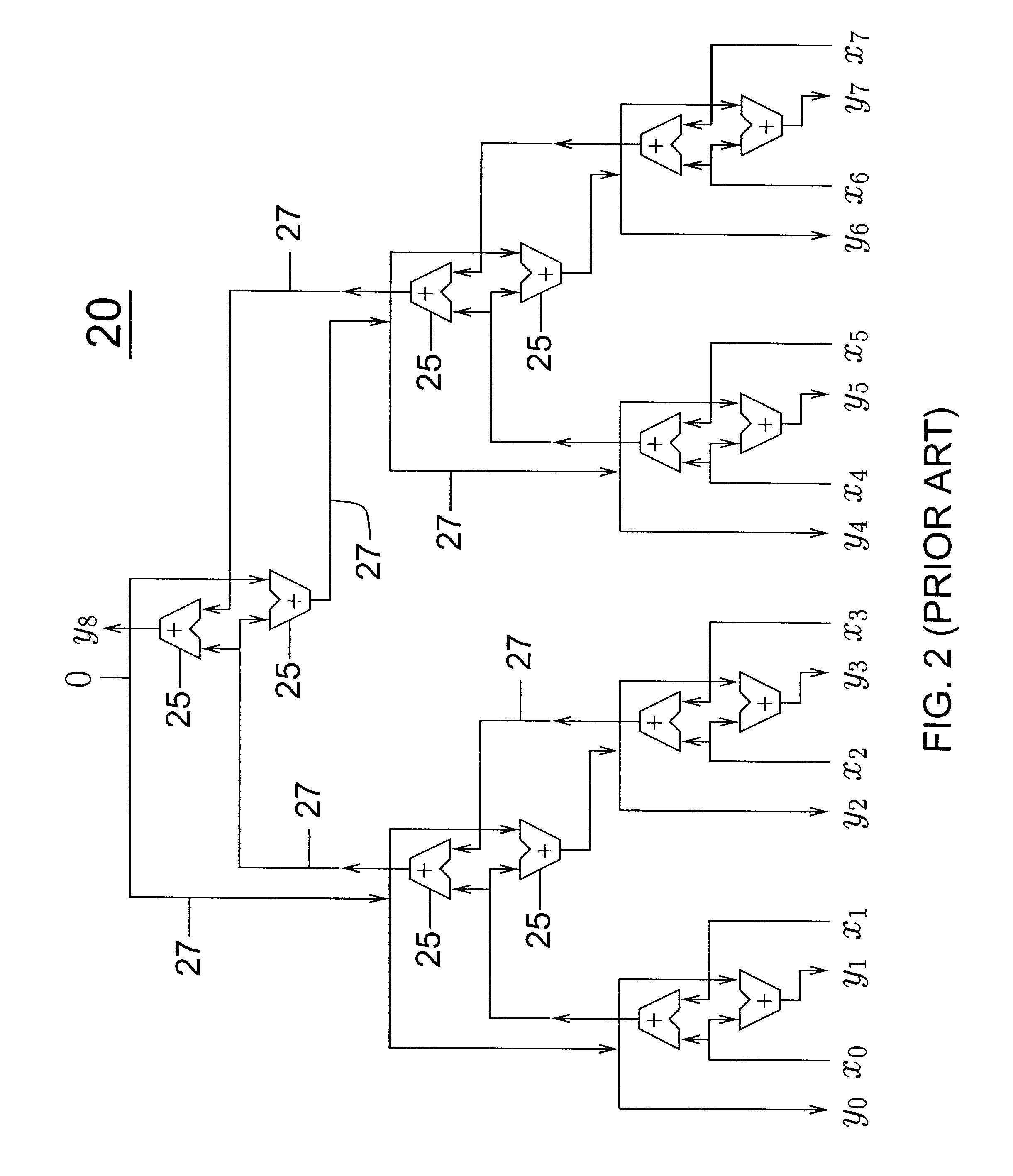

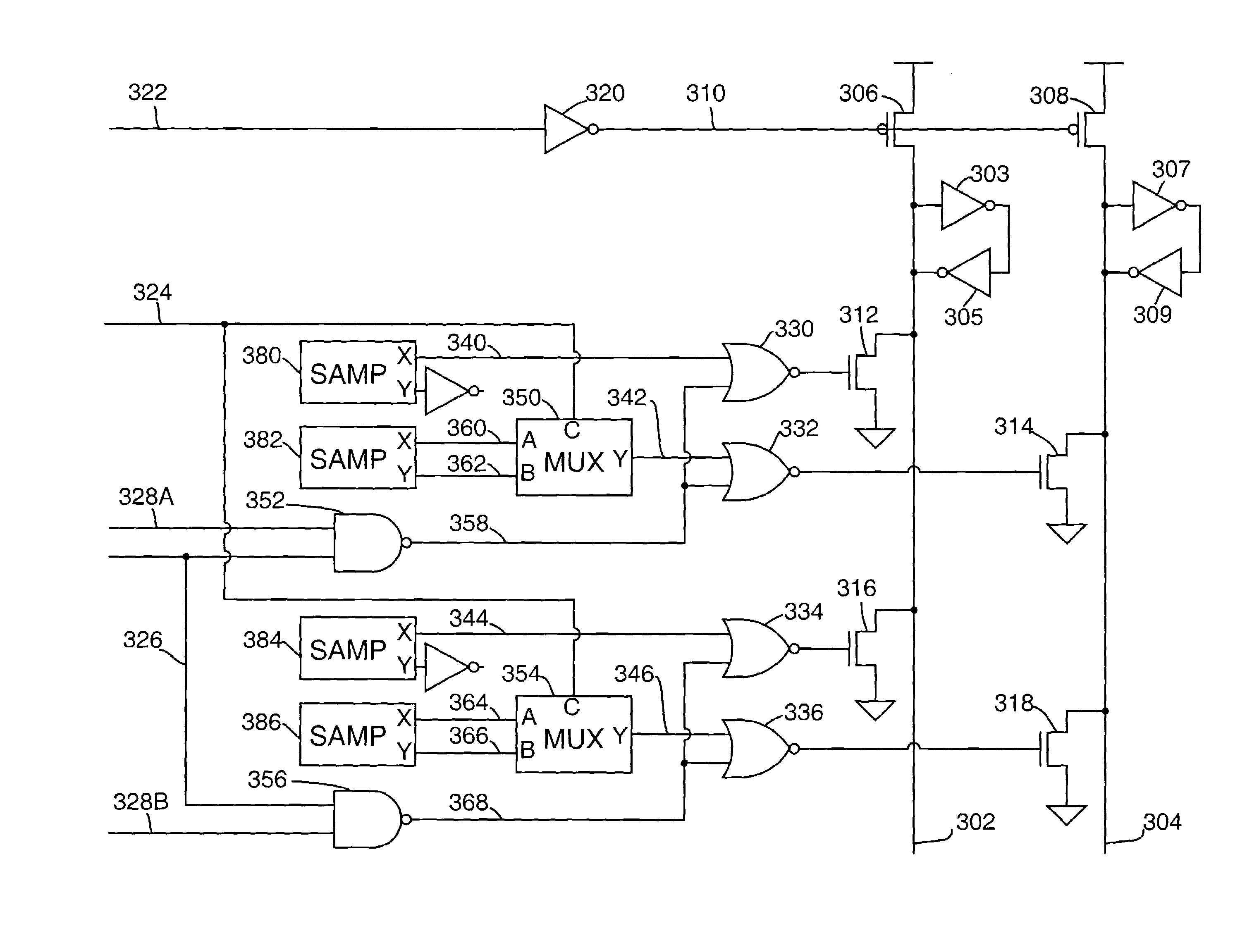

Cycle segmented prefix circuits

InactiveUS6609189B1Improve performanceAvoid performanceComputation using non-contact making devicesGeneral purpose stored program computerExtensibilityScalar processor

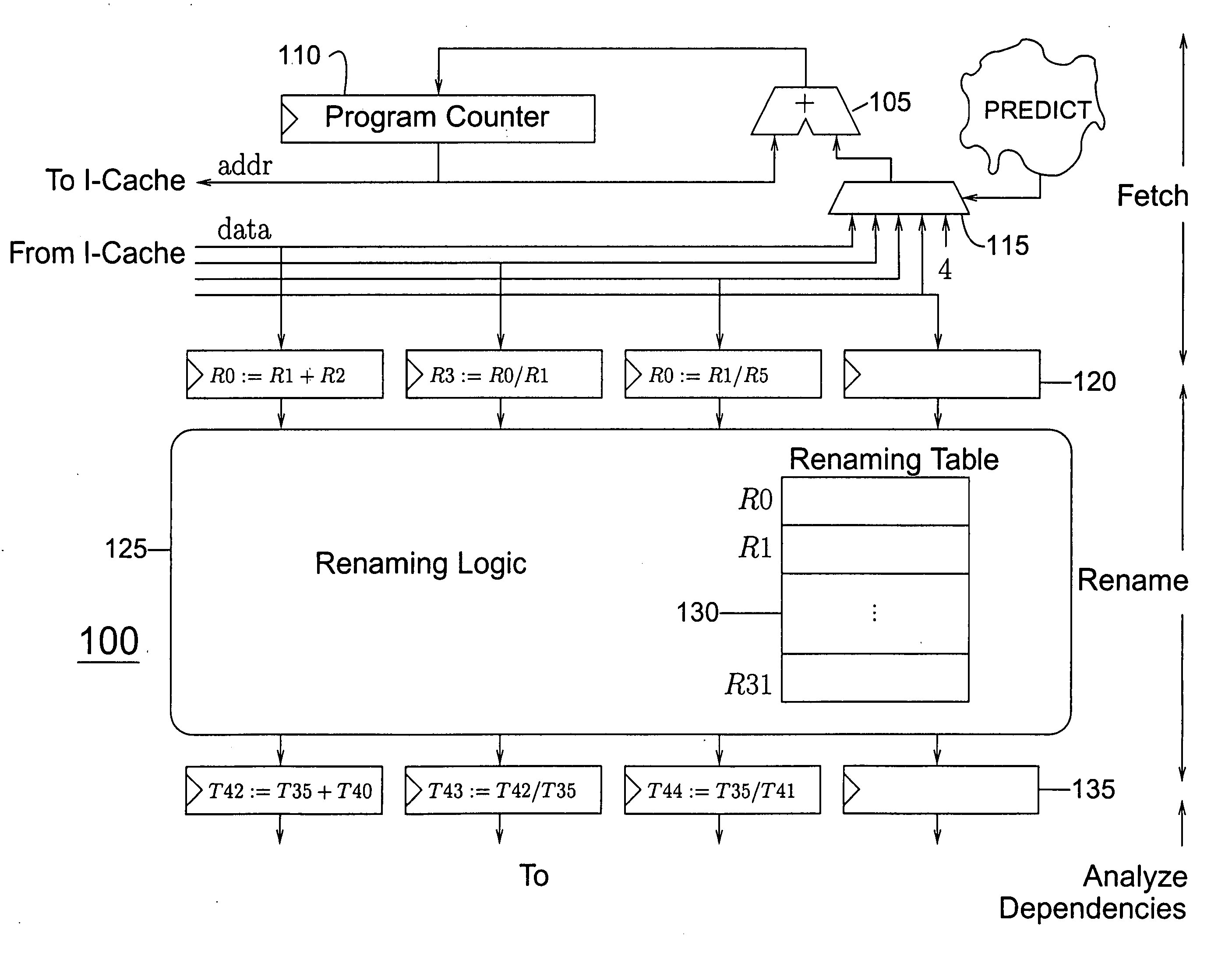

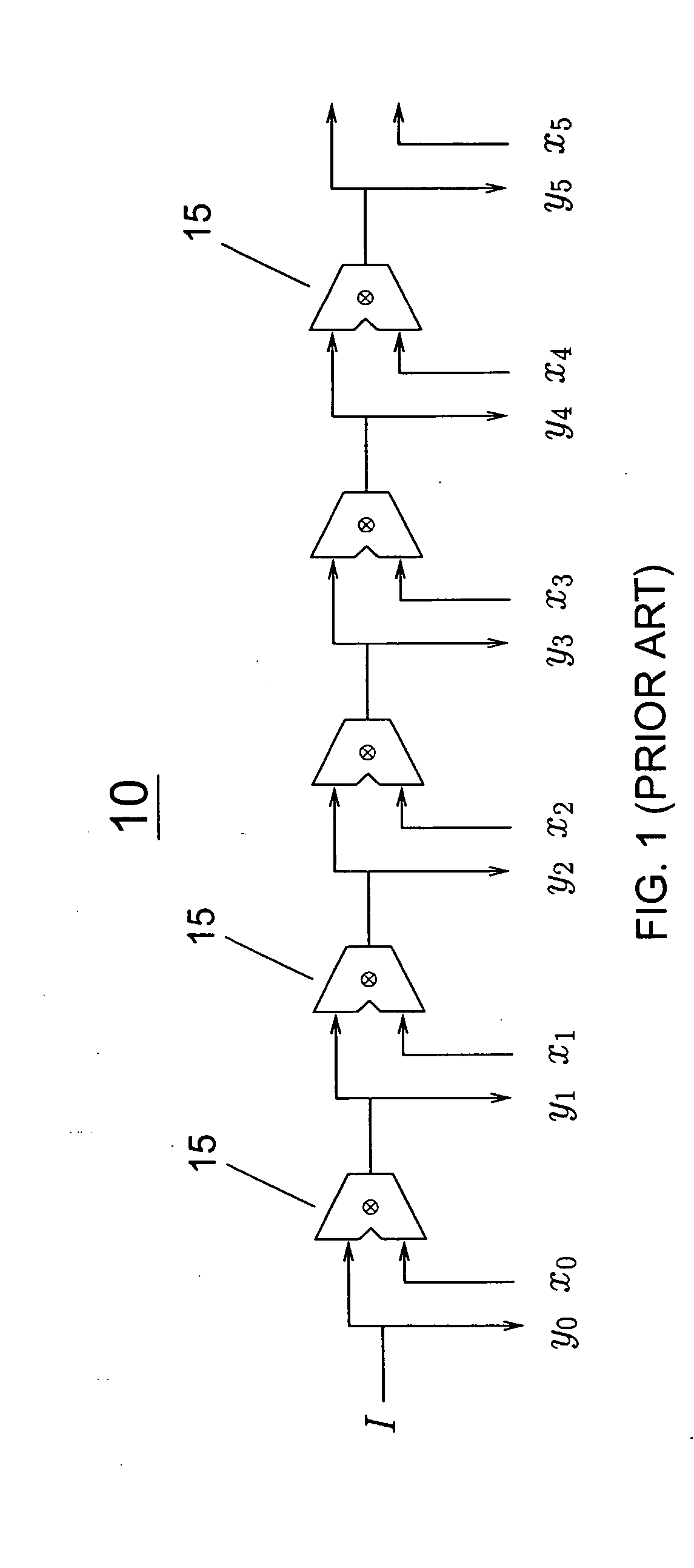

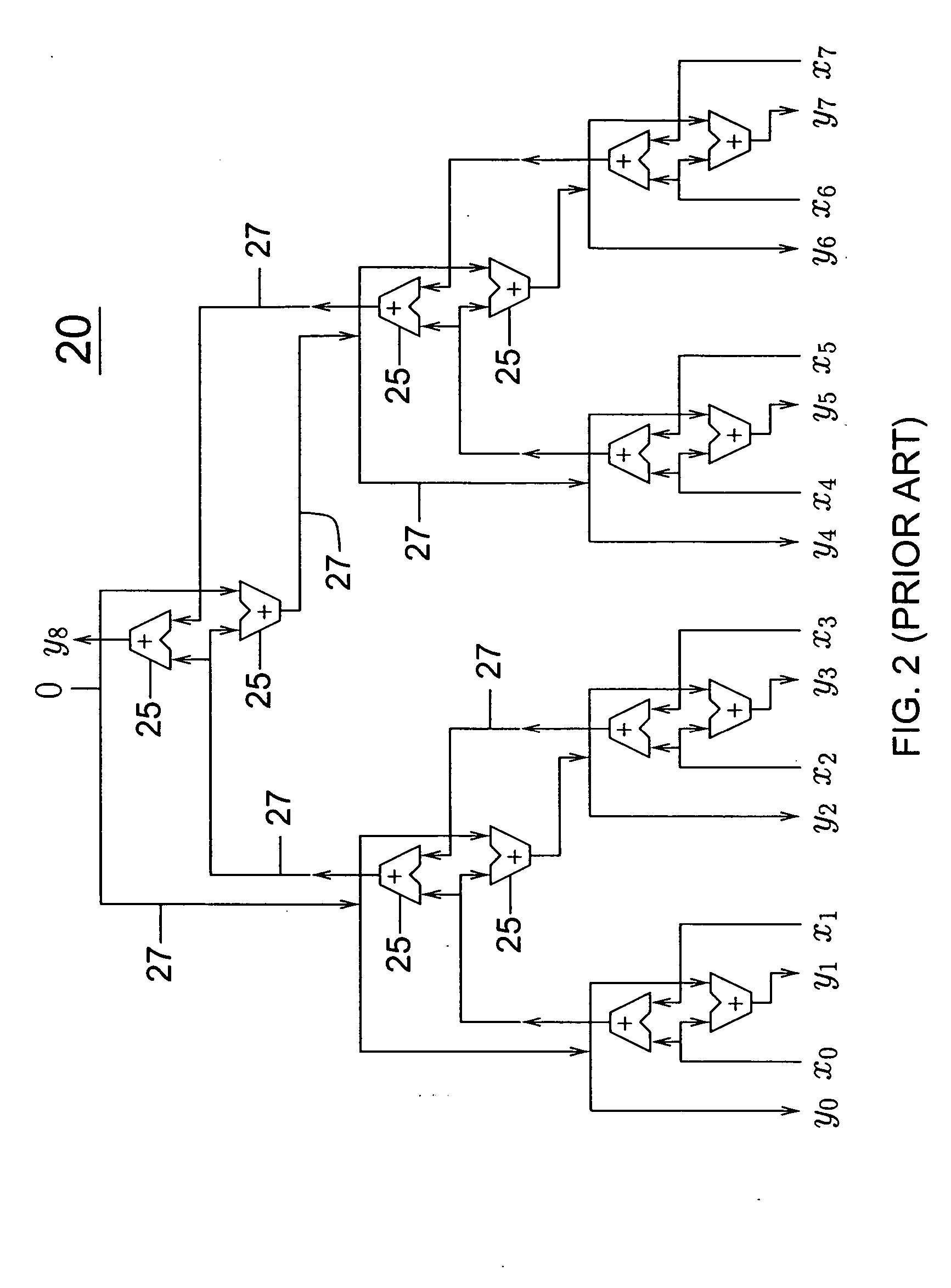

The poor scalability of existing superscalar processors has been of great concern to the computer engineering community. In particular, the critical-path delays of many components in existing implementations grow quadratically with the issue width and the window size. This patent presents a novel way to reimplement these components and reduce their critical-path delay growth. It then describes an entire processor microarchitecture, called the Ultrascalar processor, that has better critical-path delay growth than existing superscalars. Most of our scalable designs are based on a single circuit, a cyclic segmented parallel prefix (cspp). We observe that processor components typically operate on a wrap-around sequence of instructions, computing some associative property of that sequence. For example, to assign an ALU to the oldest requesting instruction, each instruction in the instruction sequence must be told whether any preceding instructions are requesting an ALU. Similarly, to read an argument register, an instruction must somehow communicate with the most recent preceding instruction that wrote that register. A cspp circuit can implement such functions by computing for each instruction within a wrap-around instruction sequence the accumulative result of applying some associative operator to all the preceding instructions. A cspp circuit has a critical path gate delay logarithmic in the length of the instruction sequence. Depending on its associative operation and its layout, a cspp circuit can have a critical path wire delay sublinear in the length of the instruction sequence.

Owner:YALE UNIV

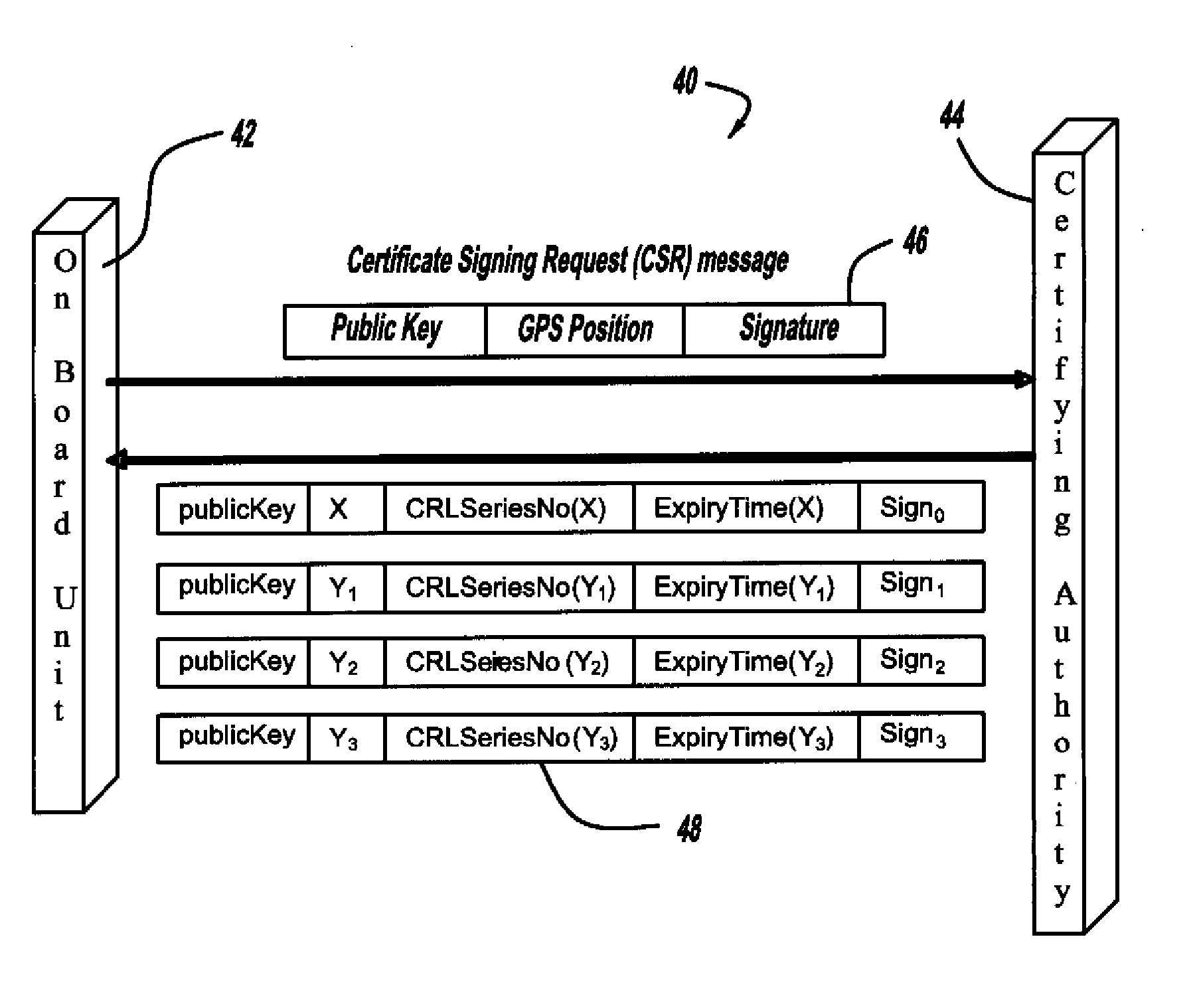

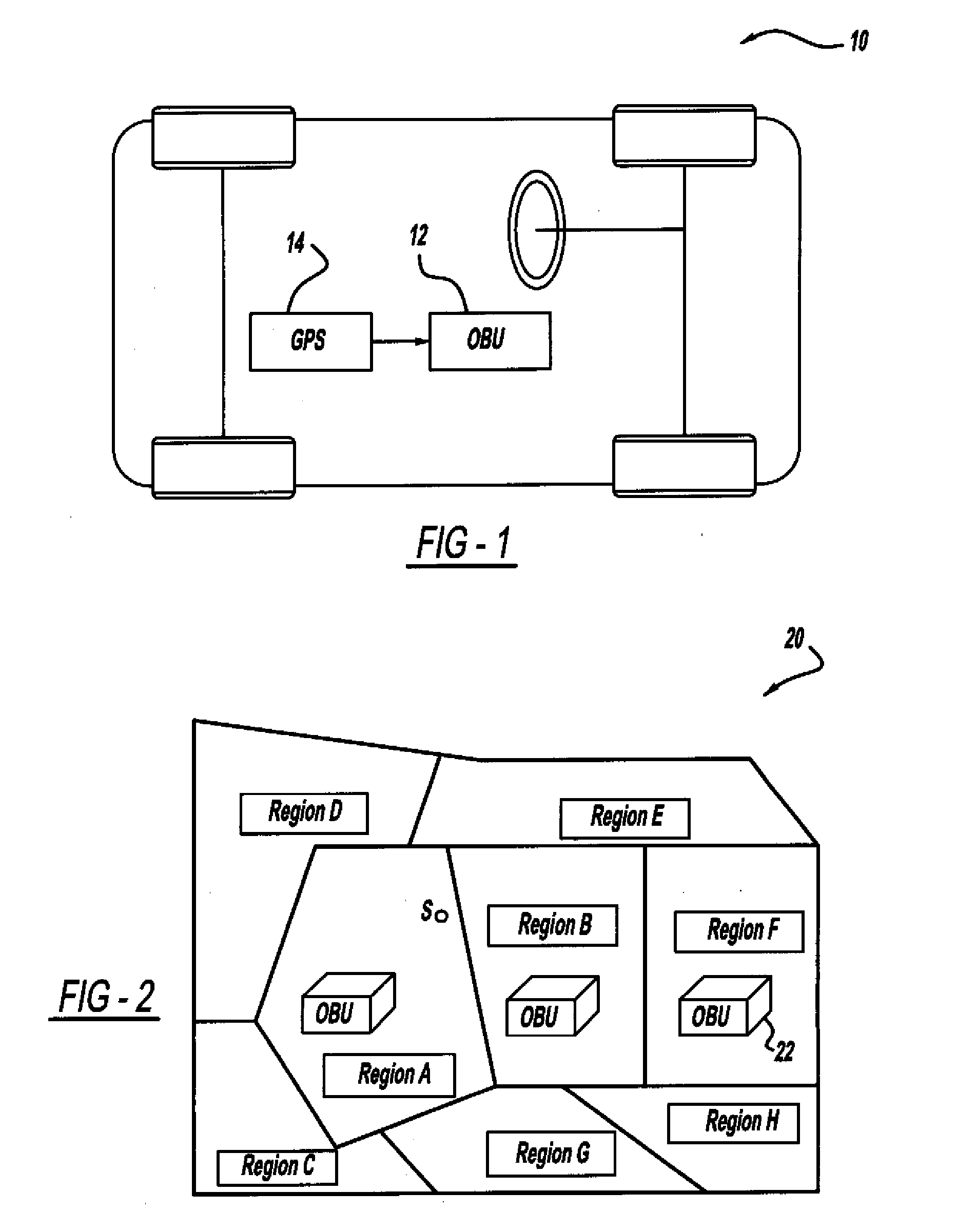

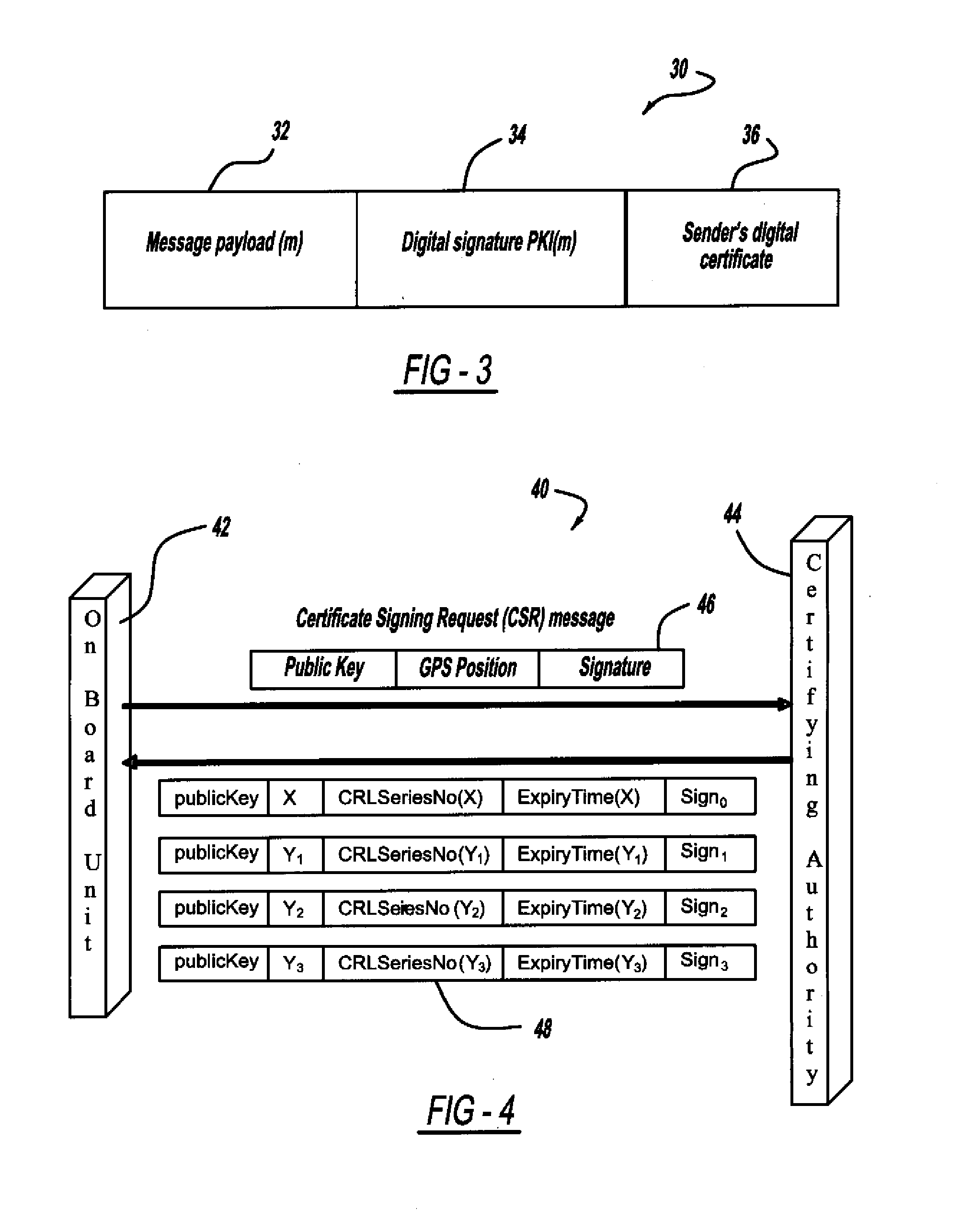

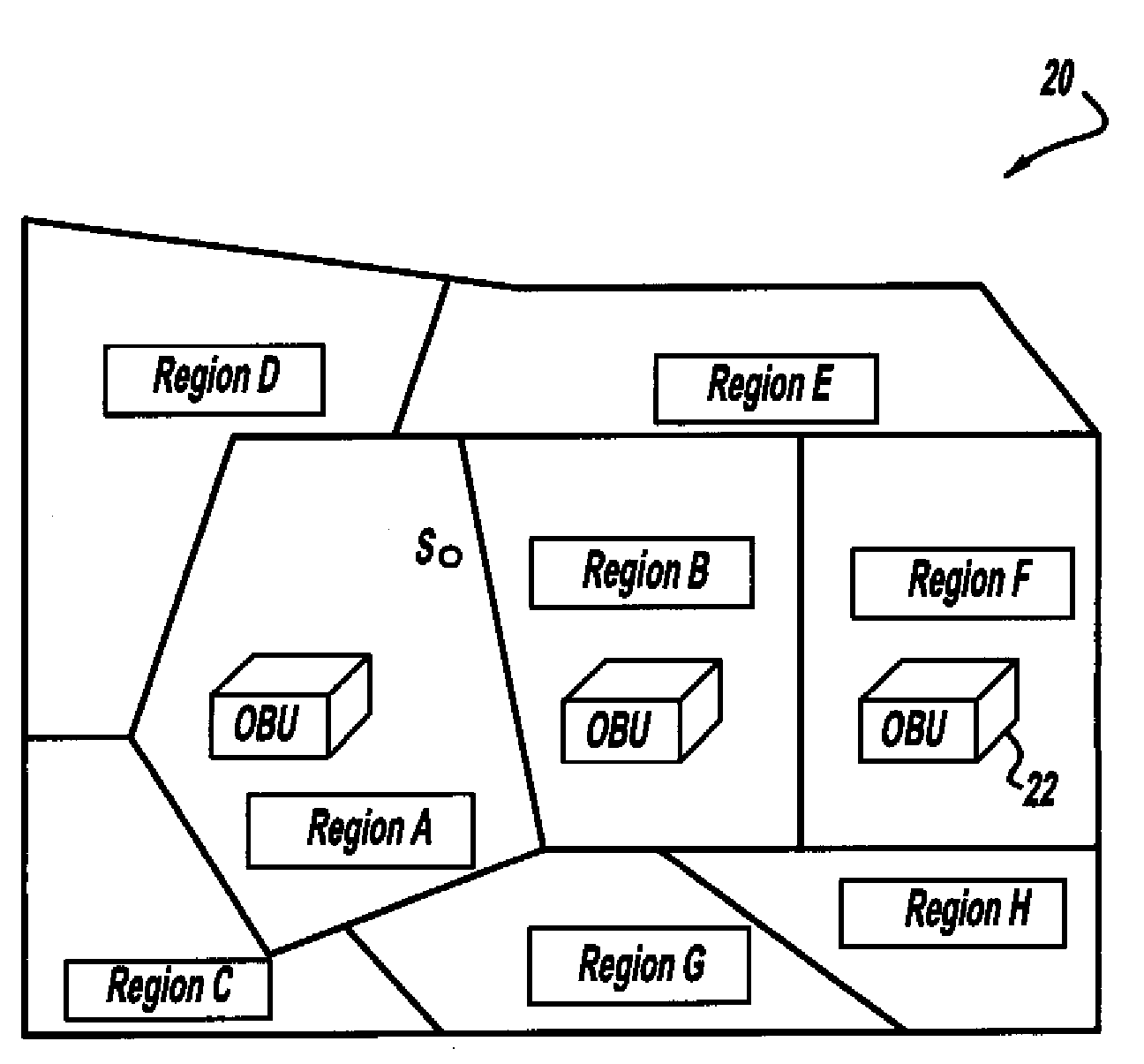

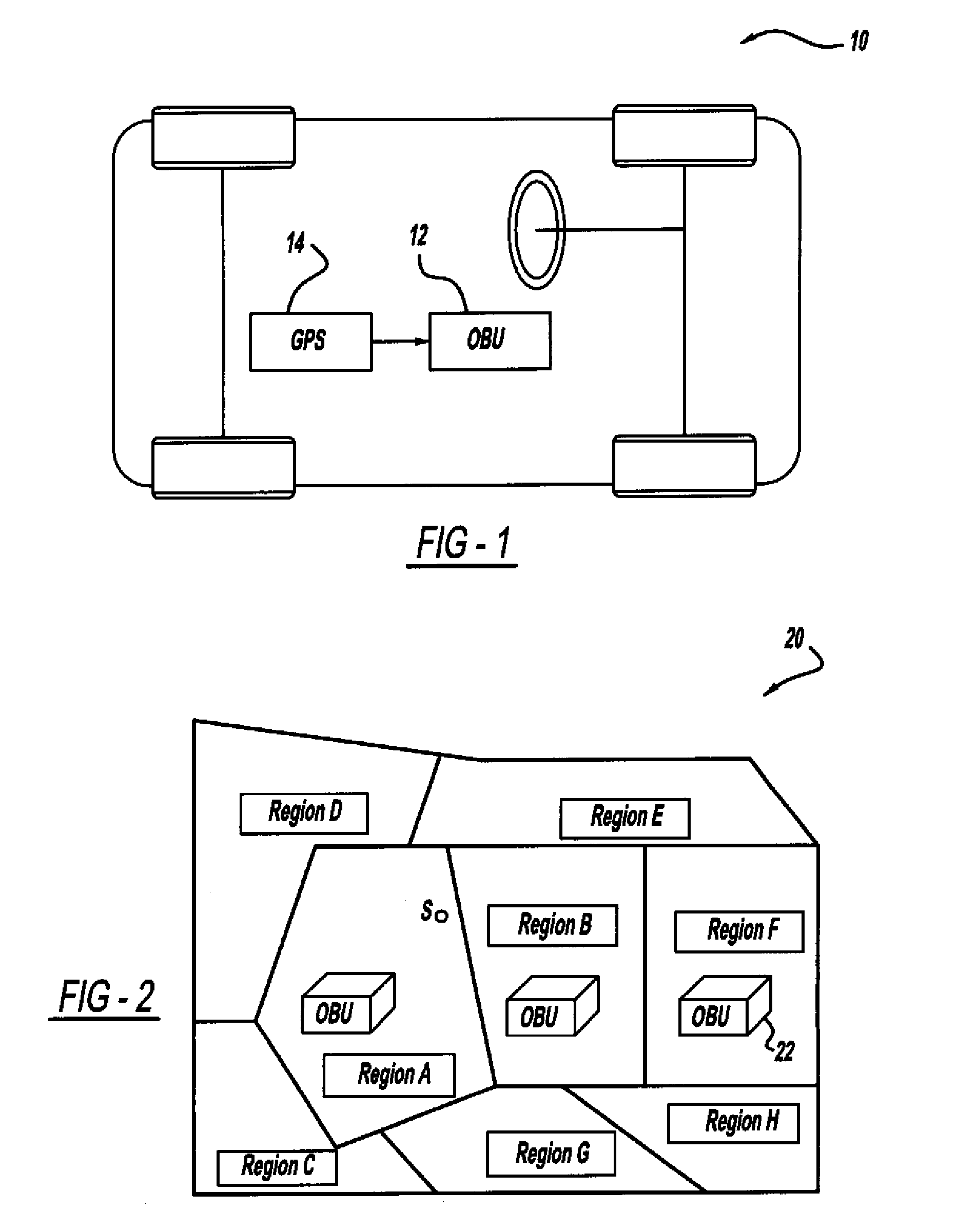

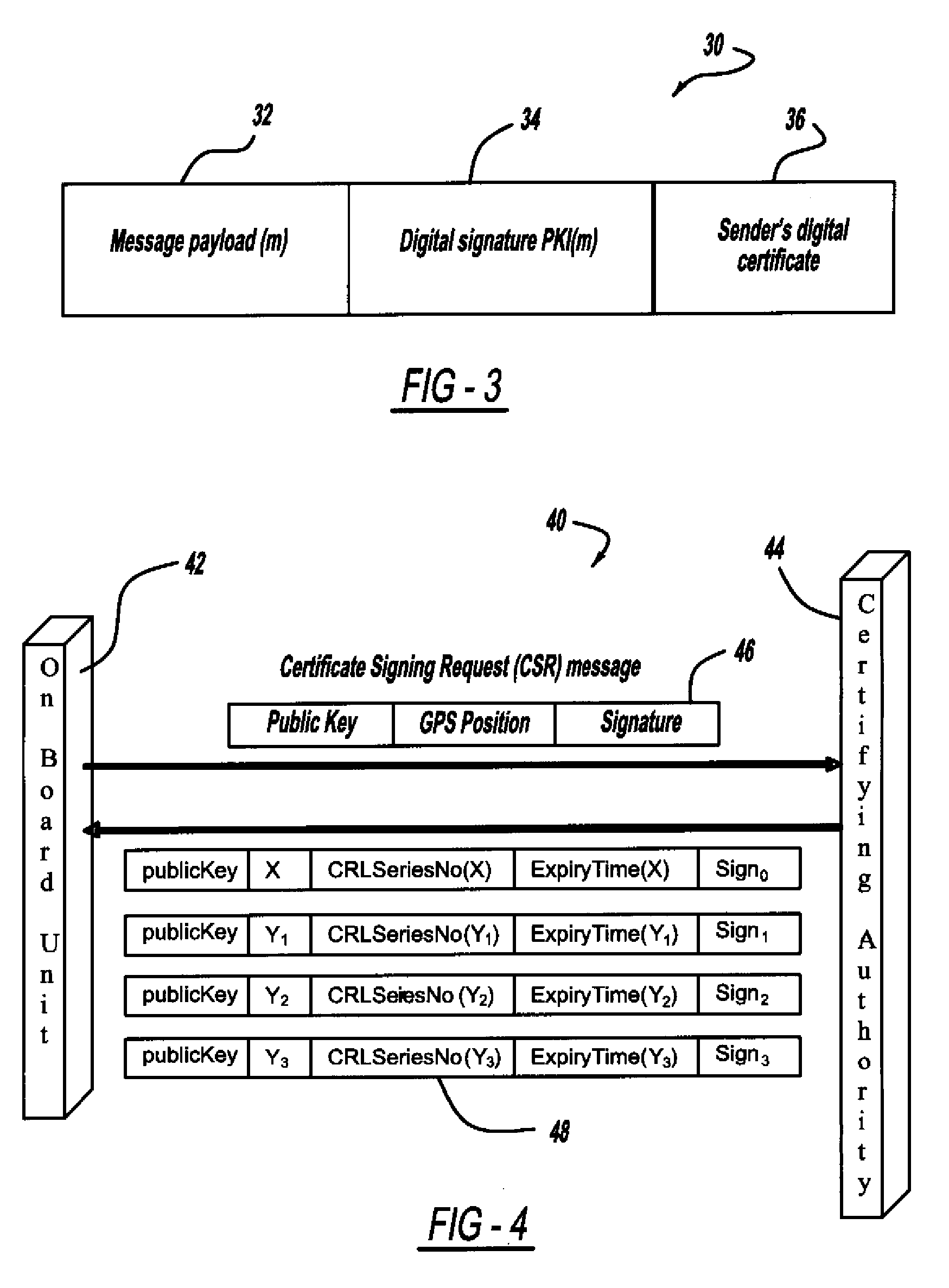

Certificate assignment strategies for efficient operation of the pki-based security architecture in a vehicular network

InactiveUS20090235071A1Small sizeReduce complexityTemperatue controlUser identity/authority verificationExpiration TimeCommunications system

A system and method for assigning certificates and reducing the size of the certificate revocation lists in a PKI based architecture for a vehicle wireless communications system that includes separating a country, or other area, into geographic regions and assigning region-specific certificates to the vehicles. Therefore, a vehicle need only process certificates and certificate revocation lists for the particular region that it is traveling in. Vehicles can be assigned multiple certificates corresponding to more than one region in the vehicles vicinity as advance preparation for possible travel or transmission into nearby regions. Further, the expiration time of certificates assigned to vehicles corresponding to a given geographic region can be tailored to be inversely proportional to the distance from a registered home region of the vehicle. A scalable design for a back-end certifying authority with region-based certificates can also be provided.

Owner:GM GLOBAL TECH OPERATIONS LLC

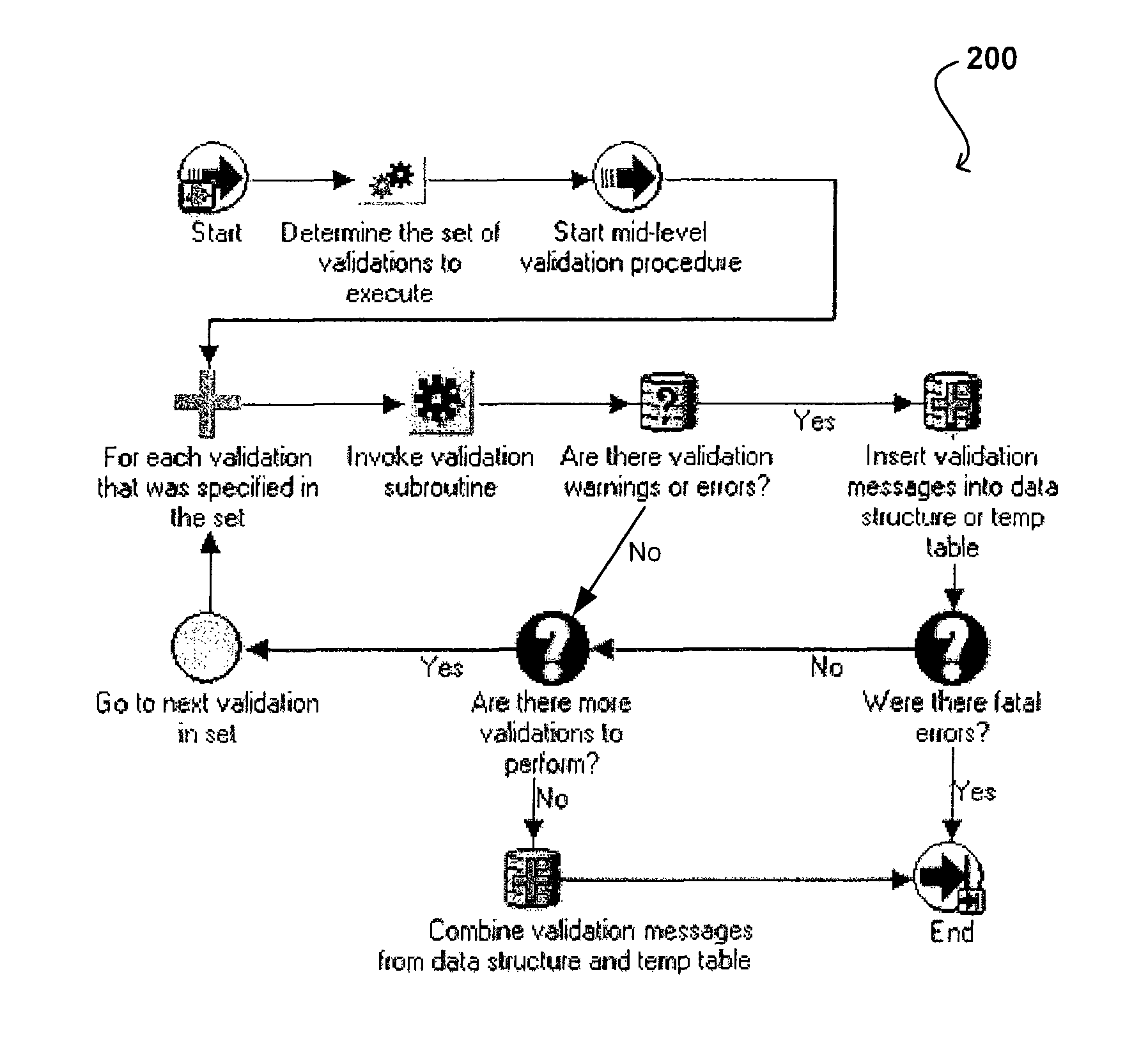

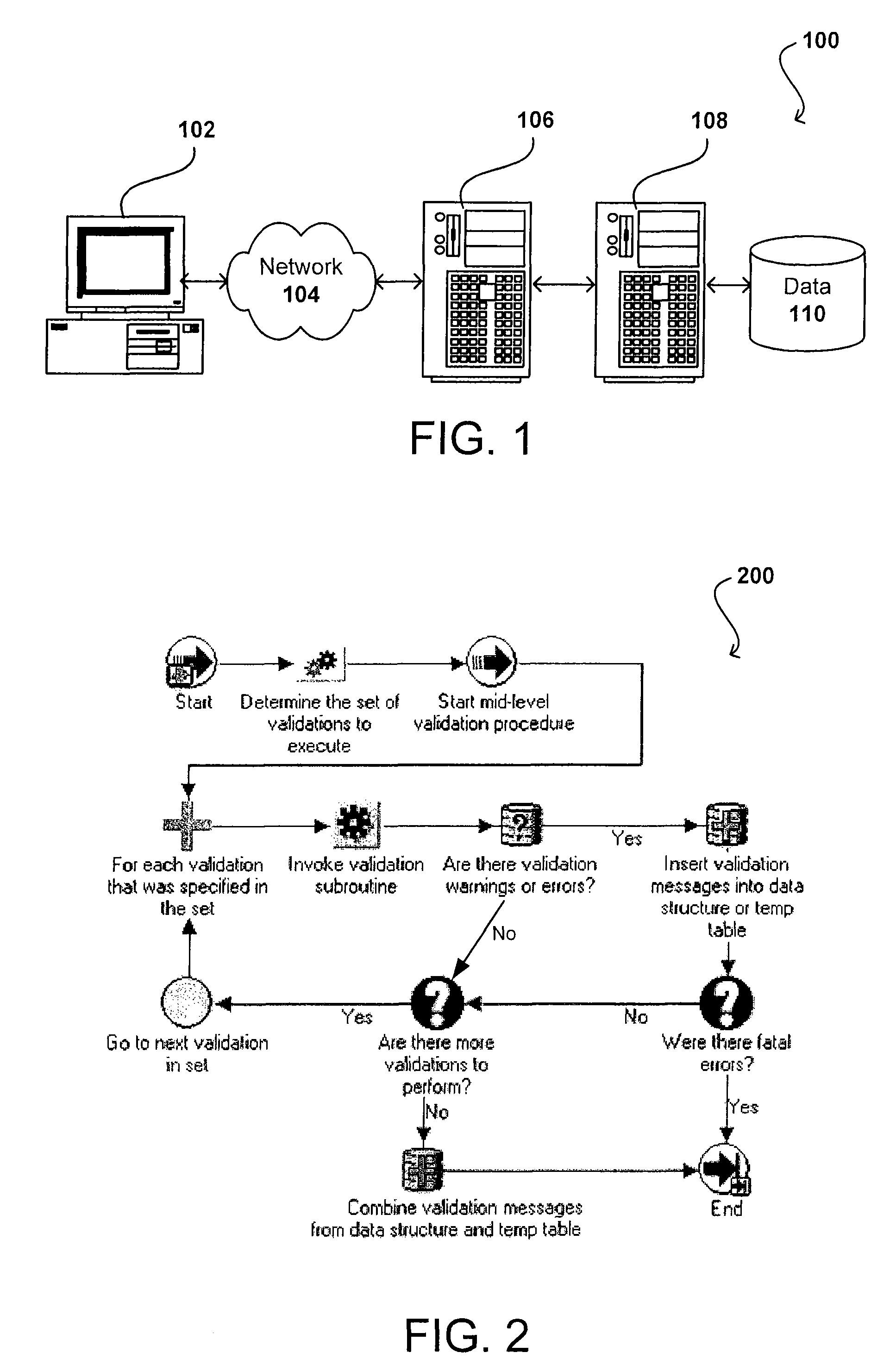

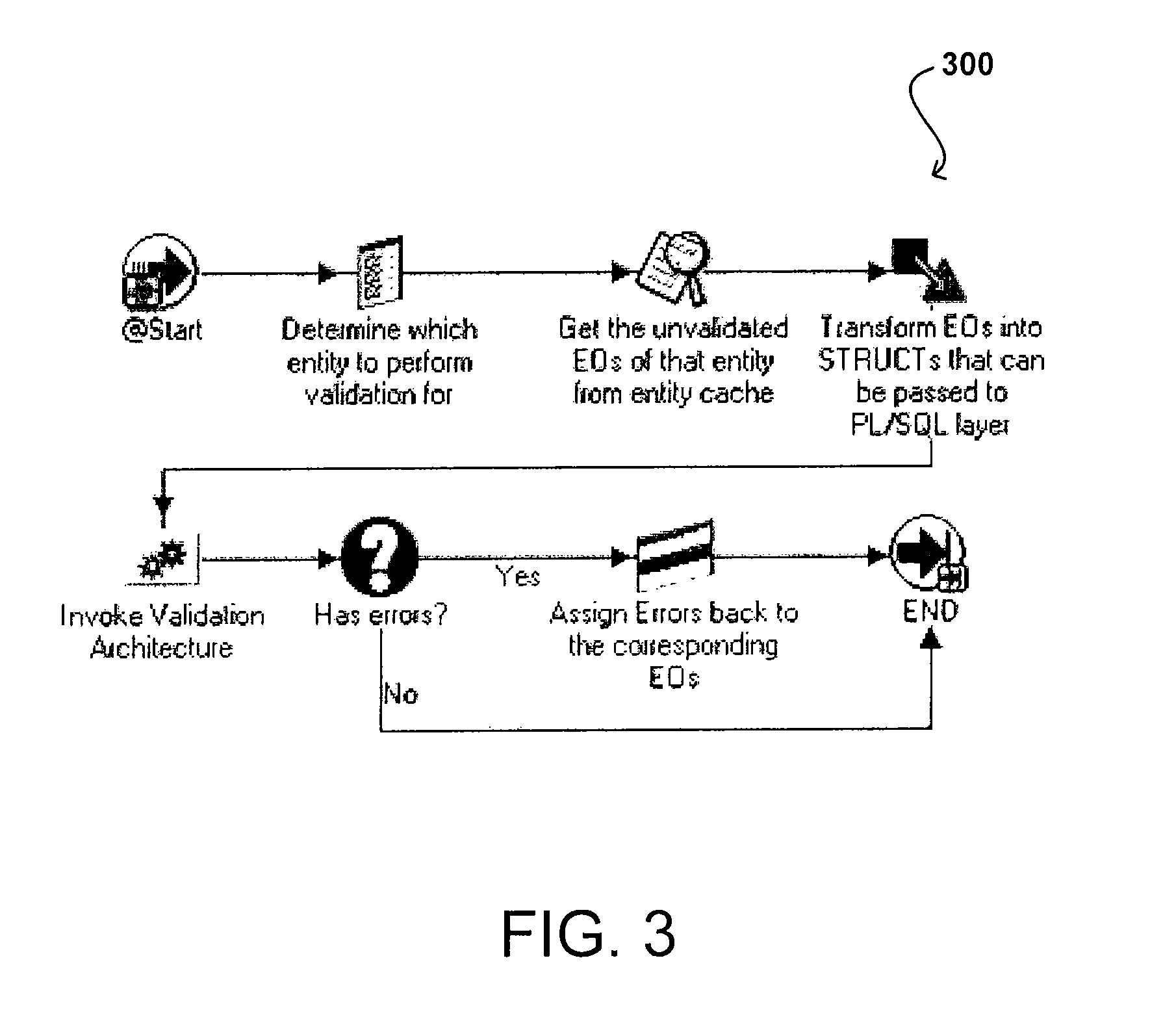

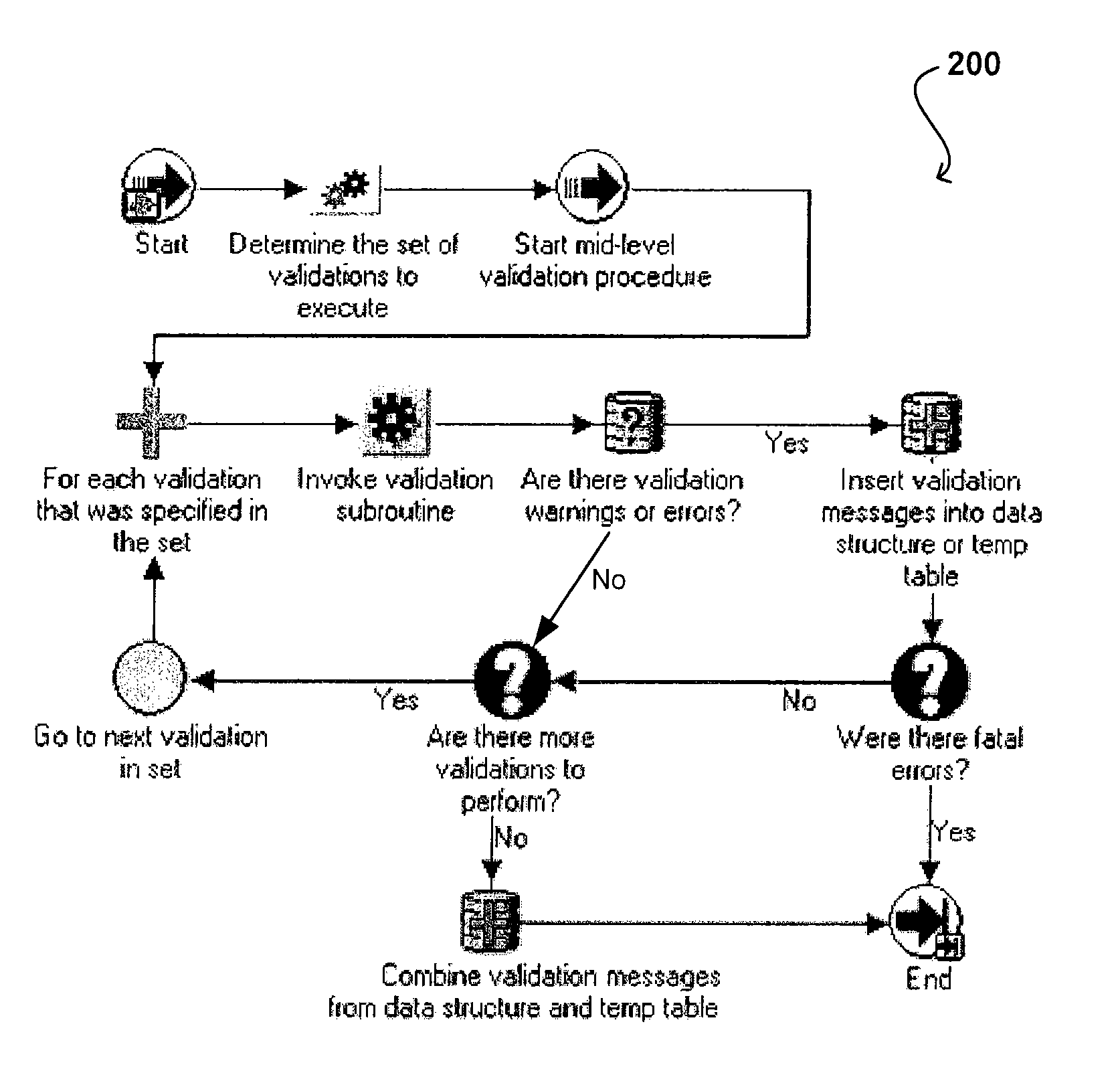

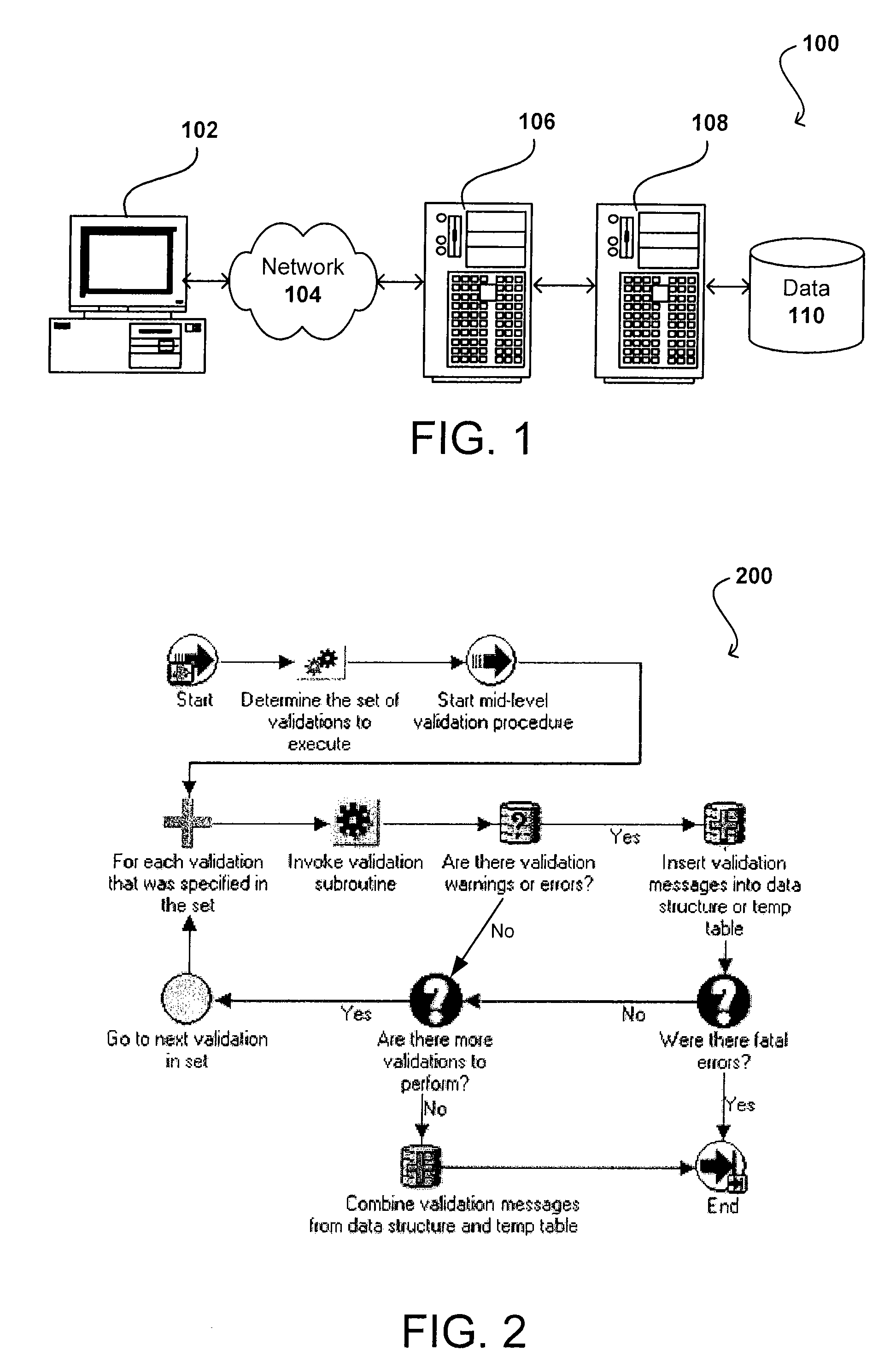

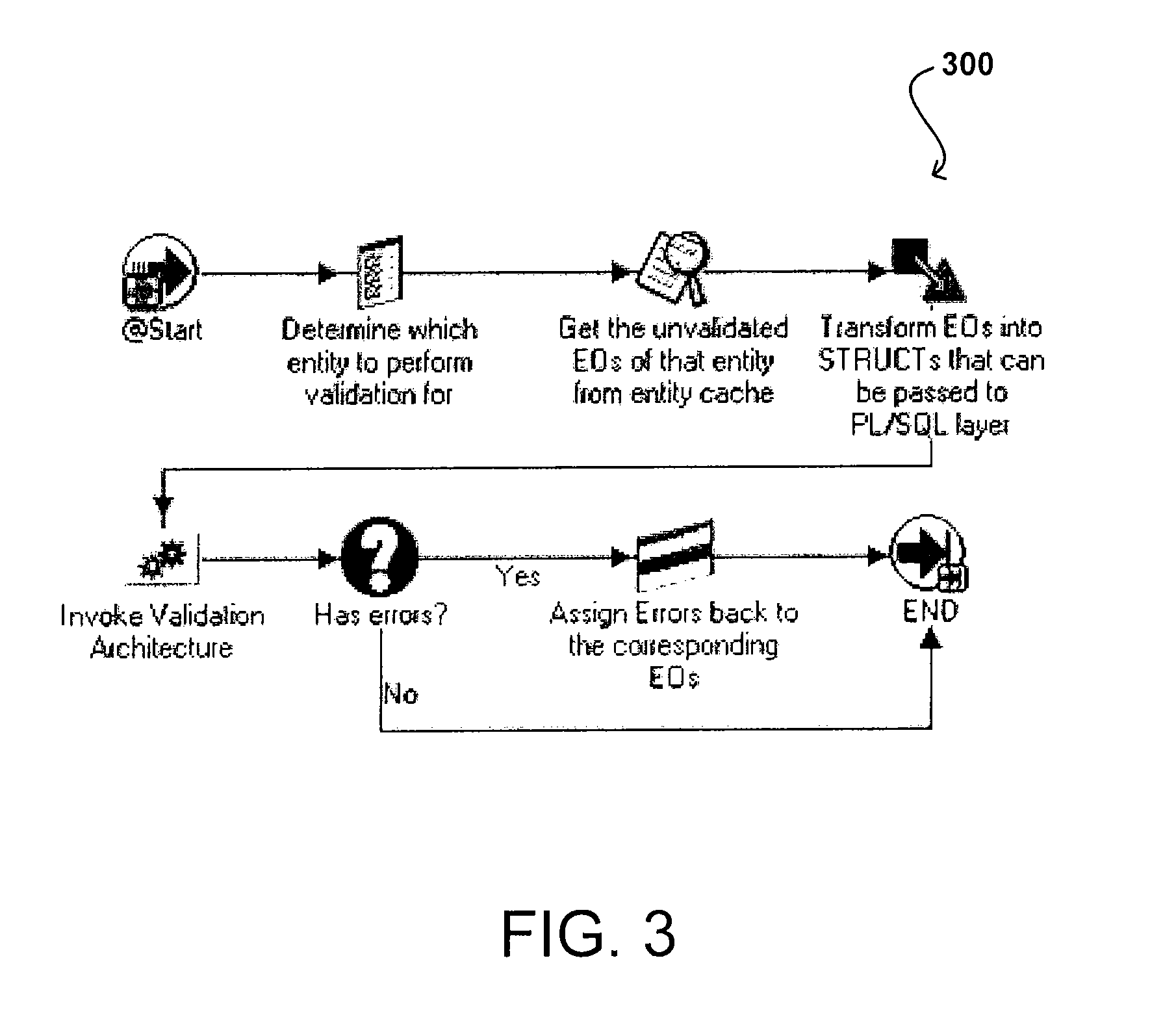

Architecture for data validation

ActiveUS8418142B2Easy to createSufficient flexibilitySoftware designSpecific program execution arrangementsData validationDuplicate code

A data validation architecture is provided that minimizes duplicate code and enables easy creation of new validations using a high-performance and scalable design. Such an architecture provides sufficient flexibility to disable certain validations when they are not applicable to the flow, interpret validation failures differently according to requirements of the calling application, and specify the type of document for which a particular validation is applicable. The architecture provides a standardized flow for performing data validation, specifying a set of required parameters for validation subroutines, as well as where validation results are to be stored for access by a calling program. Such an architecture also provides a framework for performing common processing required for most validation flows without restricting the flexibility of the validation subroutines.

Owner:ORACLE INT CORP

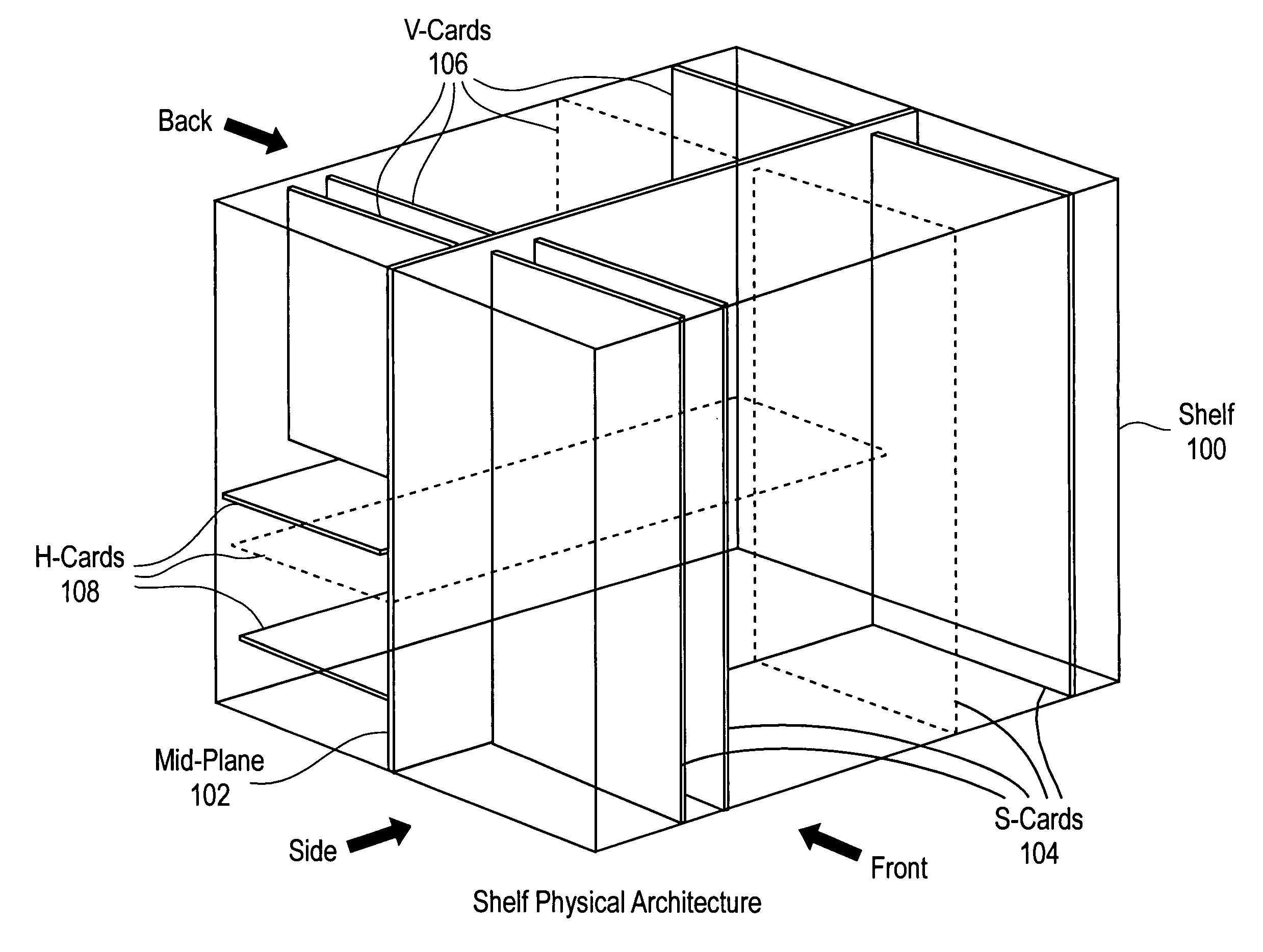

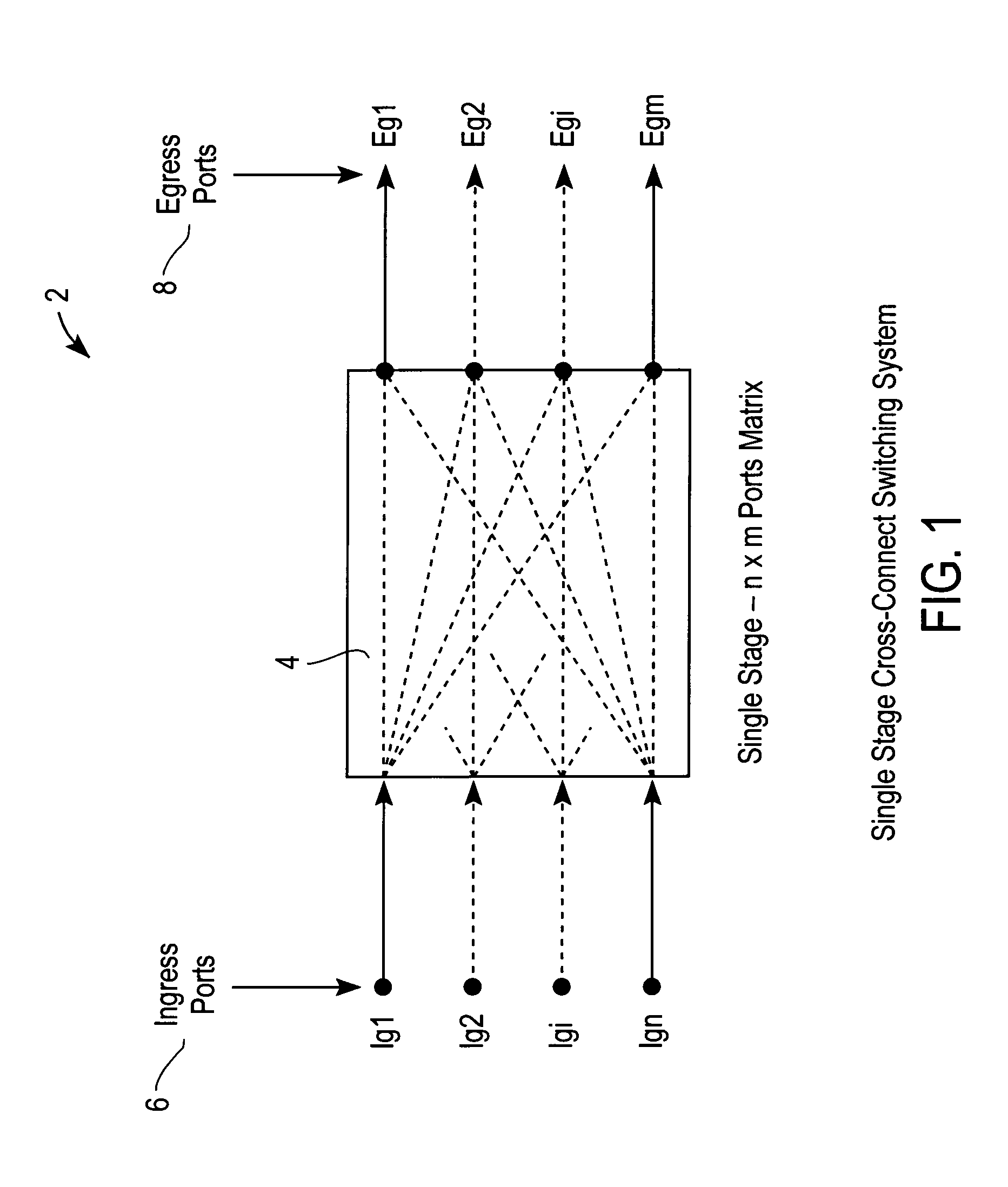

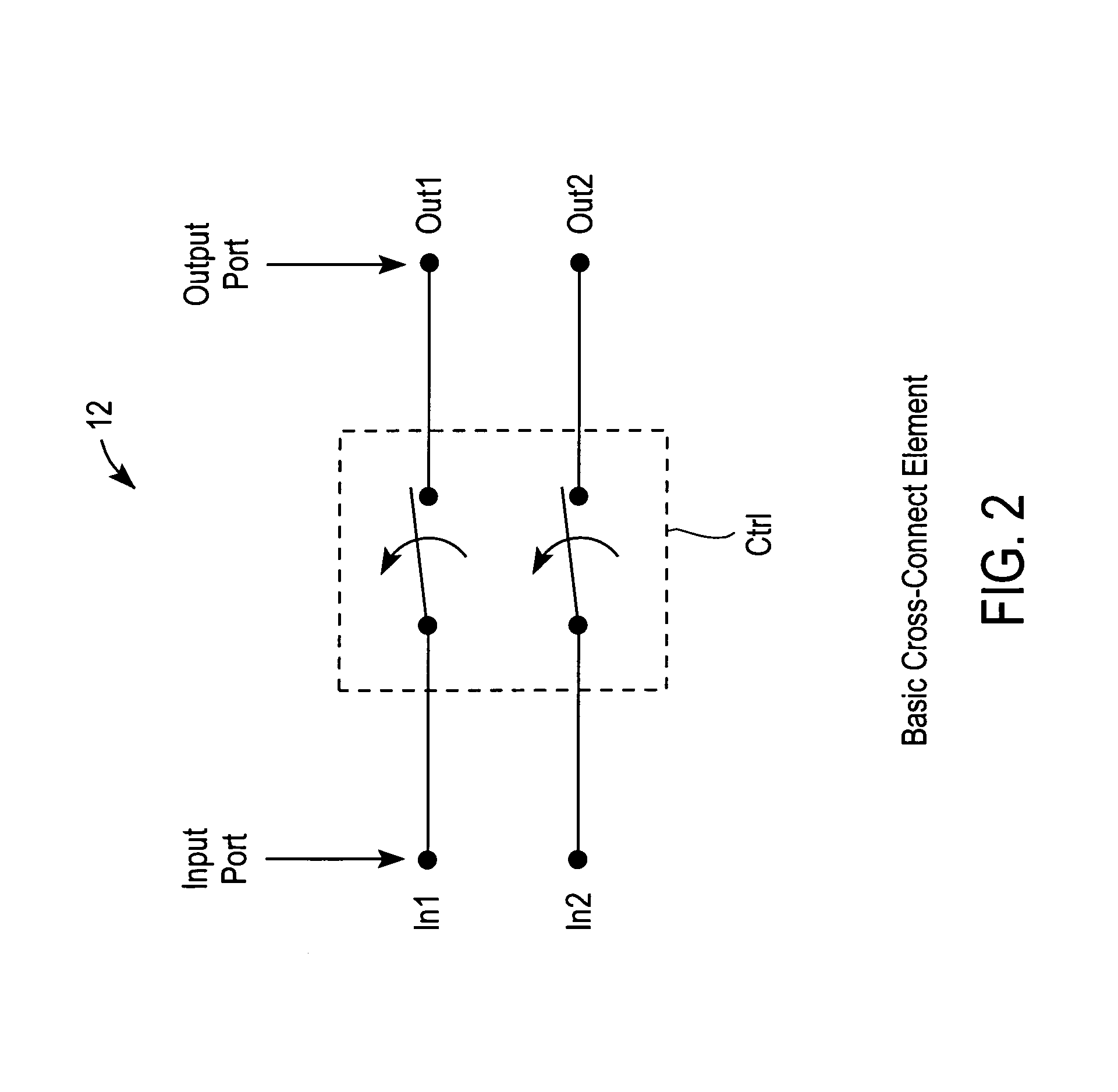

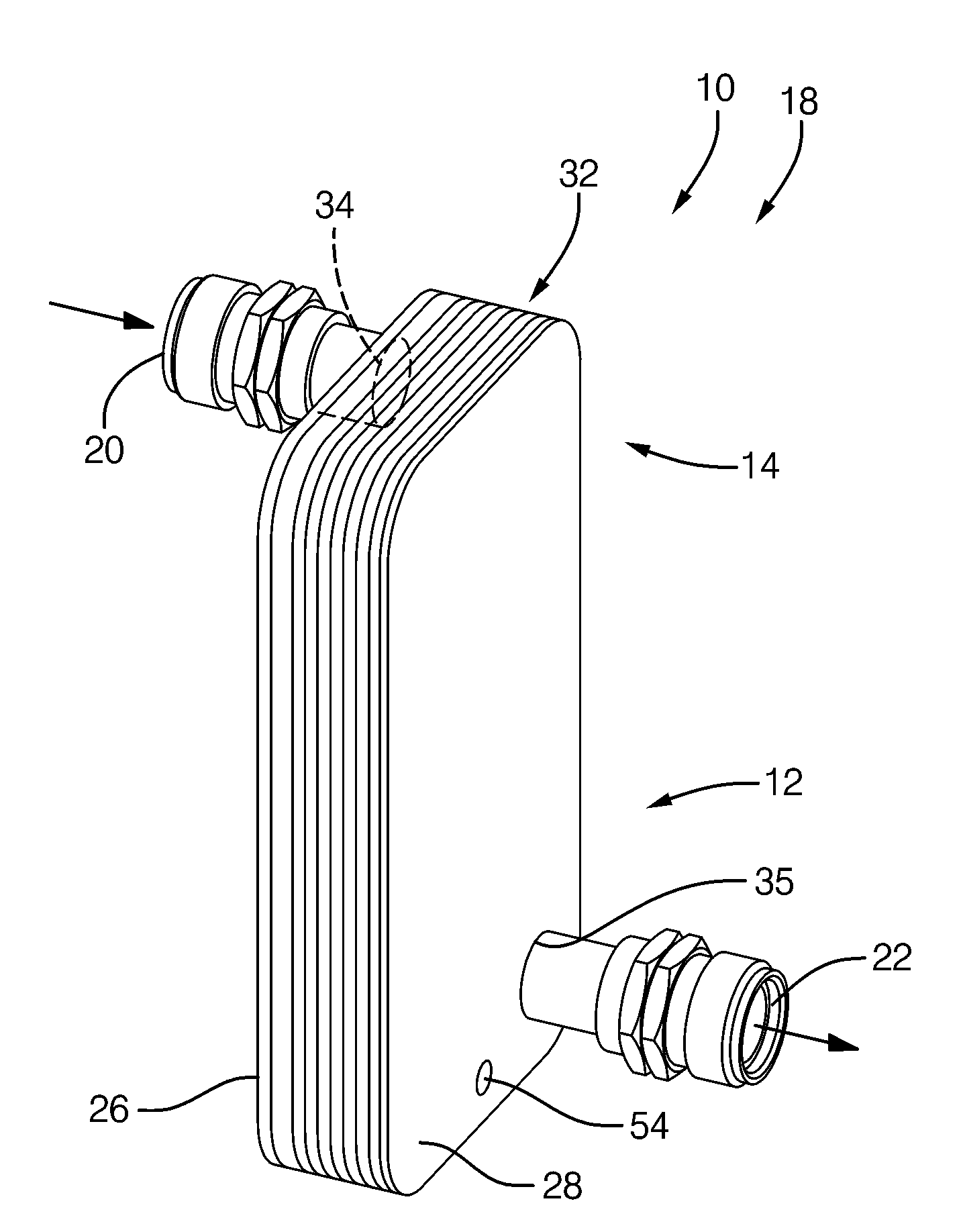

Physical architecture for design of high density metallic cross connect systems

InactiveUS6903939B1Electrical connection printed elementsSupport structure mountingCross connectionHigh density

The present invention discloses a physical shelf architecture for high density metallic cross connect systems. The present invention is intended to overcome the problems associated with the physical interconnections of metallic paths in cross connect switching systems. The physical architecture of the present invention effectively performs physical interconnections required by high density metallic cross connect systems. The physical architecture enables for a scalable design and structure of racks and shelves. In particular, inter-connect levels can be performed with devices-to-devices, boards-to-boards, shelves-to-shelves, and racks-to-racks.

Owner:TURNSTONE SYST

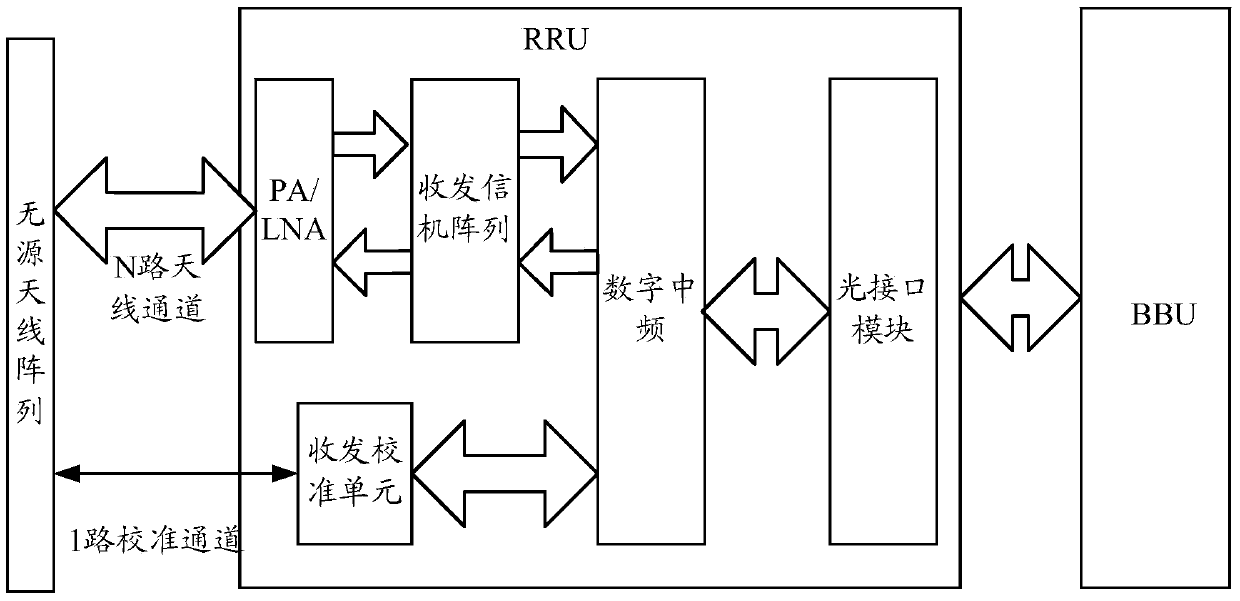

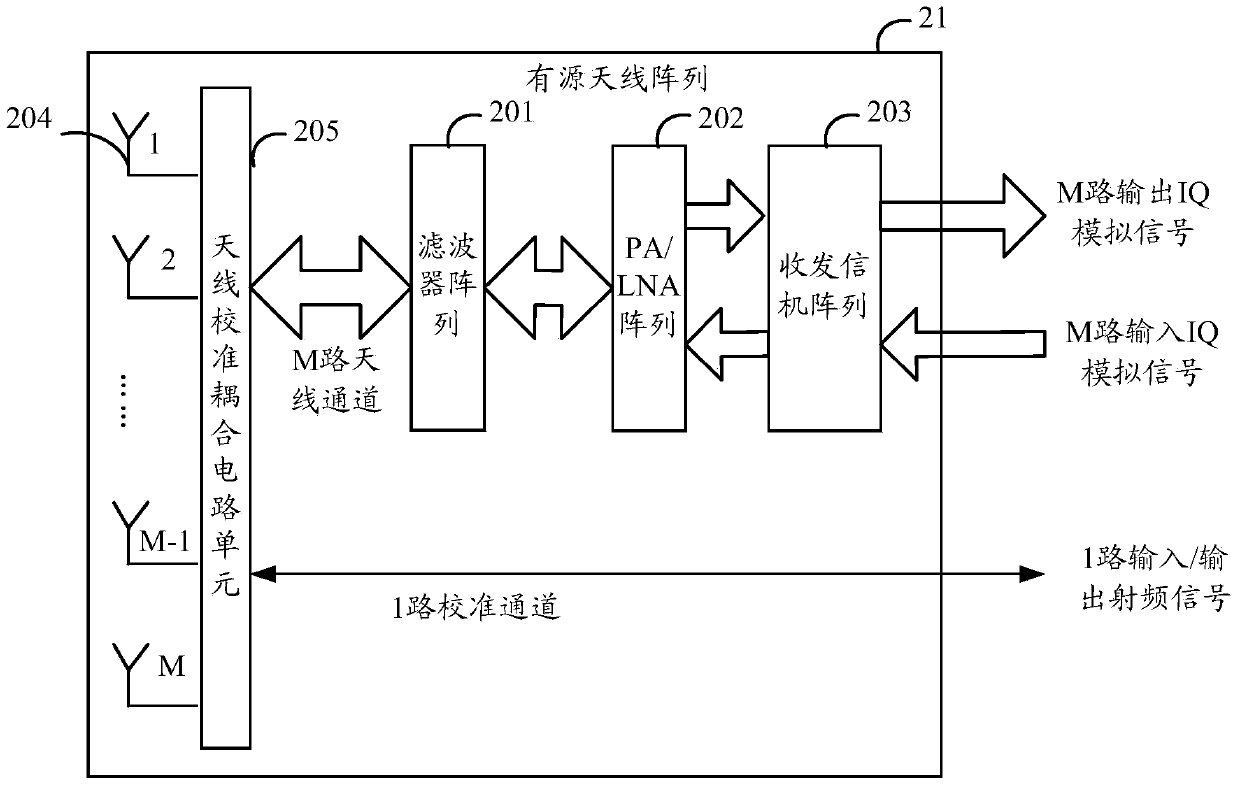

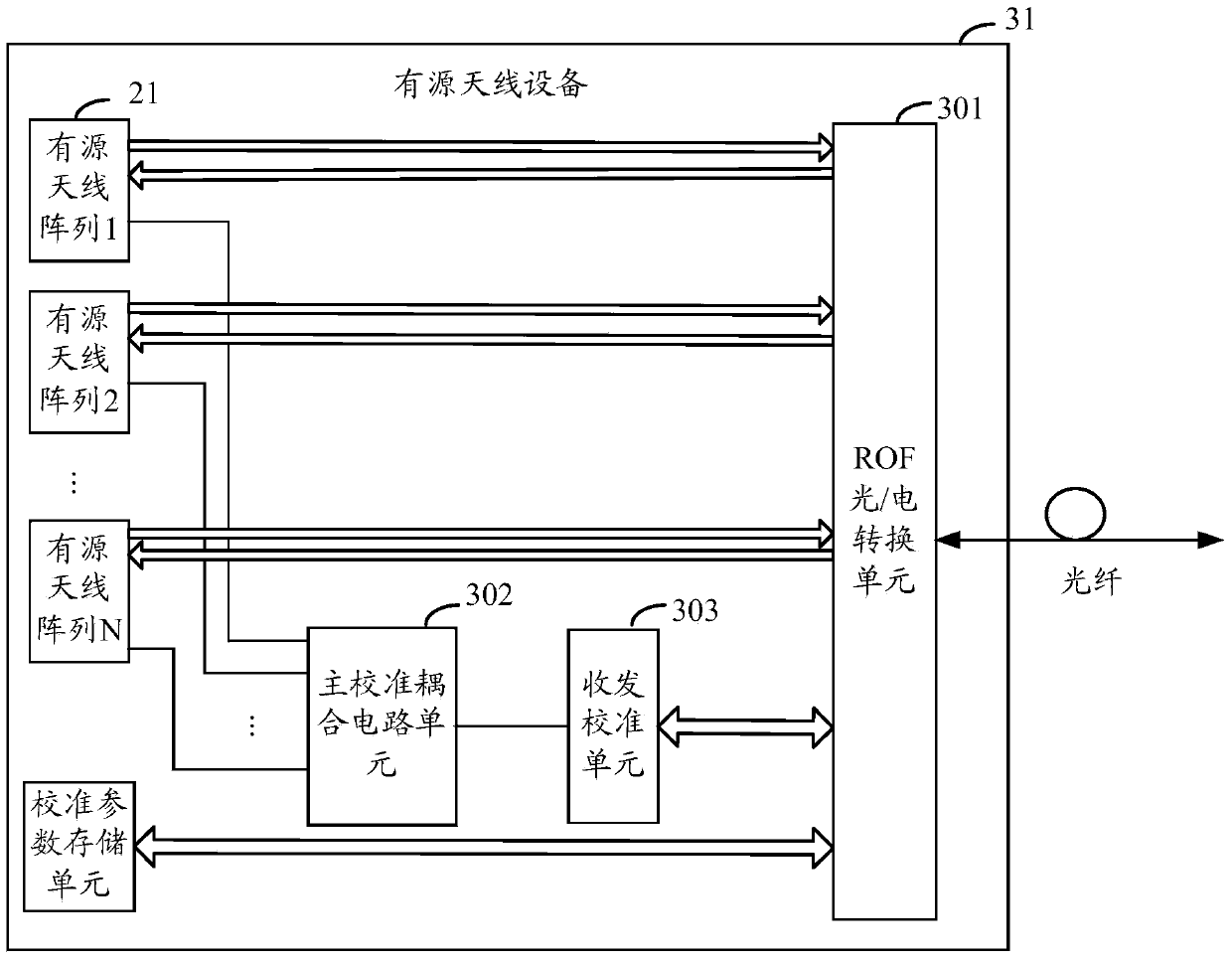

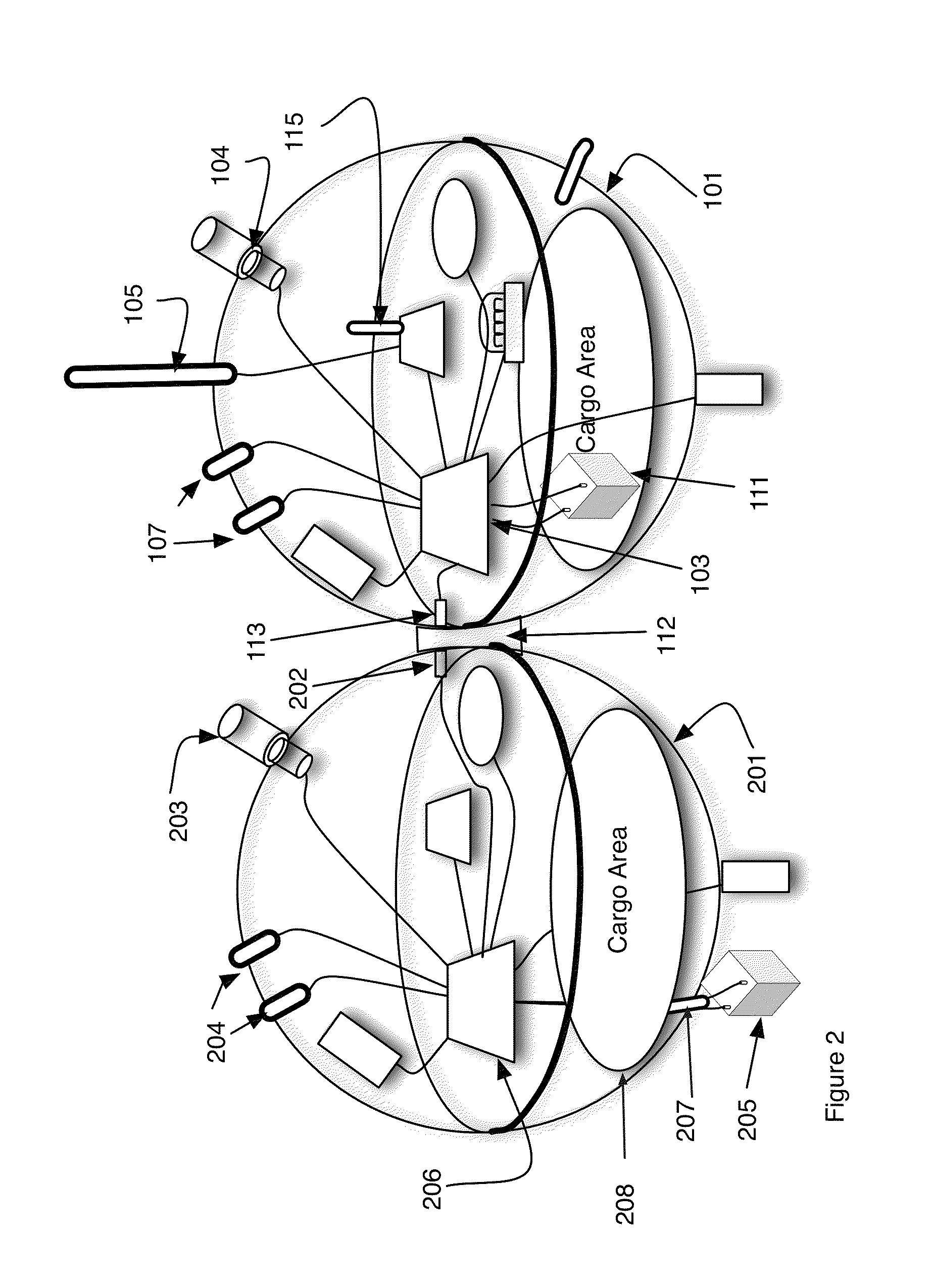

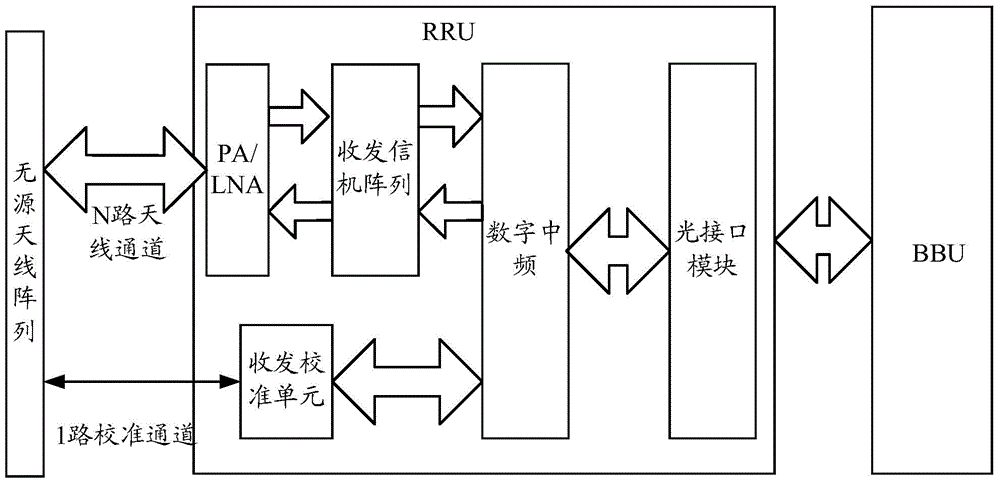

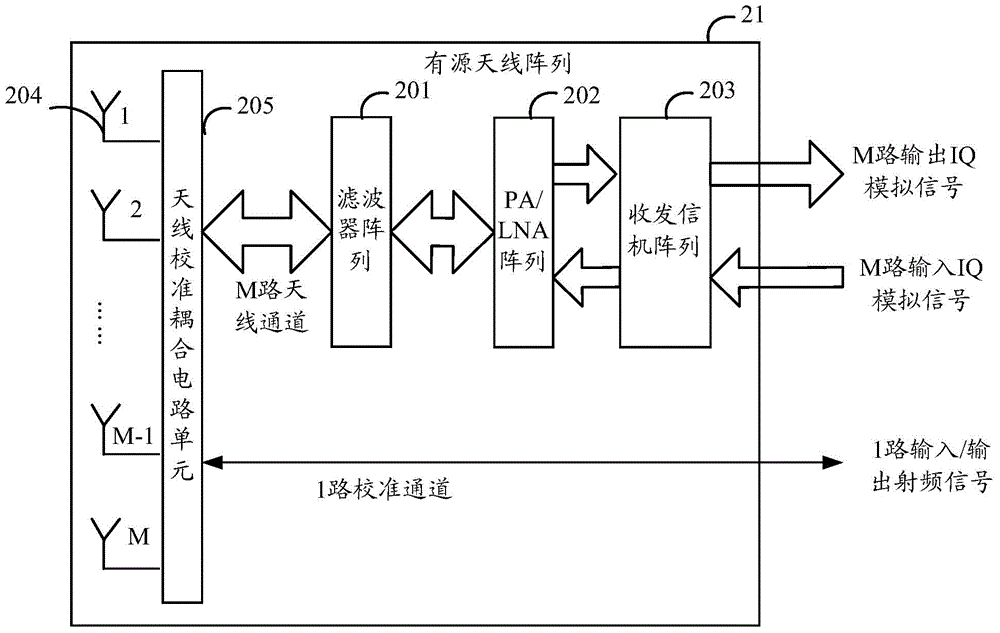

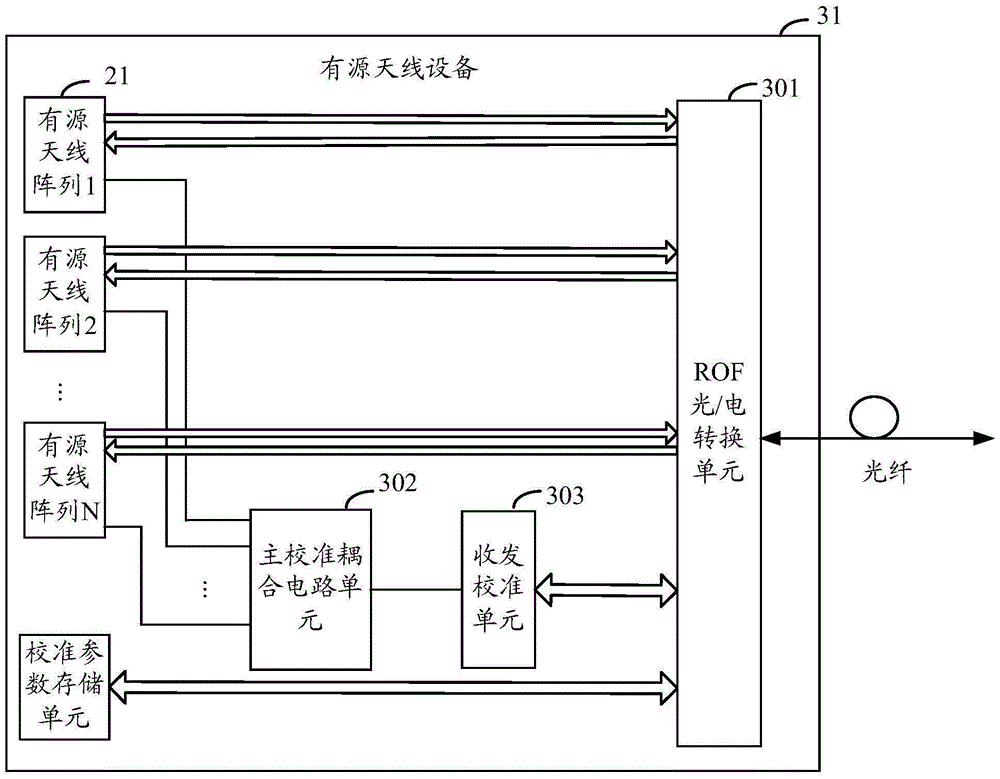

Active antenna associated equipment, system and transmitting and receiving calibration method

ActiveCN103997352AConsistent performanceReduce the difficulty of implementationTransmitters monitoringSimultaneous aerial operationsRadio over fiberScalable design

The invention discloses active antenna associated equipment, a system and a transmitting and receiving calibration method. Extensible design of an antenna array is achieved, construction implementation difficulty is reduced, and meanwhile construction implementation reliability is provided. The active antenna equipment comprises N active antenna arrays, a main calibration coupling circuit unit, a transmitting and receiving calibration unit, a calibration parameter storage unit and a radio over fiber (ROF) photoelectricity conversion unit, wherein the N is larger than 1. Each active antenna array at least comprises an antenna coupling circuit unit and M antenna oscillators connected to the antenna coupling circuit unit, wherein the M is larger than 1. Antenna calibration coupling circuit units of the active antenna arrays are connected to the main calibration coupling circuit unit through a calibration channel. The main calibration coupling circuit is connected with the transmitting and receiving calibration unit. The transmitting and receiving calibration unit and the calibration parameter storage unit are respectively connected to the ROF photoelectricity conversion unit.

Owner:DATANG MOBILE COMM EQUIP CO LTD

Certificate assignment strategies for efficient operation of the PKI-based security architecture in a vehicular network

InactiveUS8090949B2Small sizeReduce complexityTemperatue controlUser identity/authority verificationExpiration TimeCommunications system

Owner:GM GLOBAL TECH OPERATIONS LLC

Architecture for data validation

ActiveUS20090187879A1Easy to createSufficient flexibilitySoftware designSpecific program execution arrangementsData validationSource Data Verification

A data validation architecture is provided that minimizes duplicate code and enables easy creation of new validations using a high-performance and scalable design. Such an architecture provides sufficient flexibility to disable certain validations when they are not applicable to the flow, interpret validation failures differently according to requirements of the calling application, and specify the type of document for which a particular validation is applicable. The architecture provides a standardized flow for performing data validation, specifying a set of required parameters for validation subroutines, as well as where validation results are to be stored for access by a calling program. Such an architecture also provides a framework for performing common processing required for most validation flows without restricting the flexibility of the validation subroutines.

Owner:ORACLE INT CORP

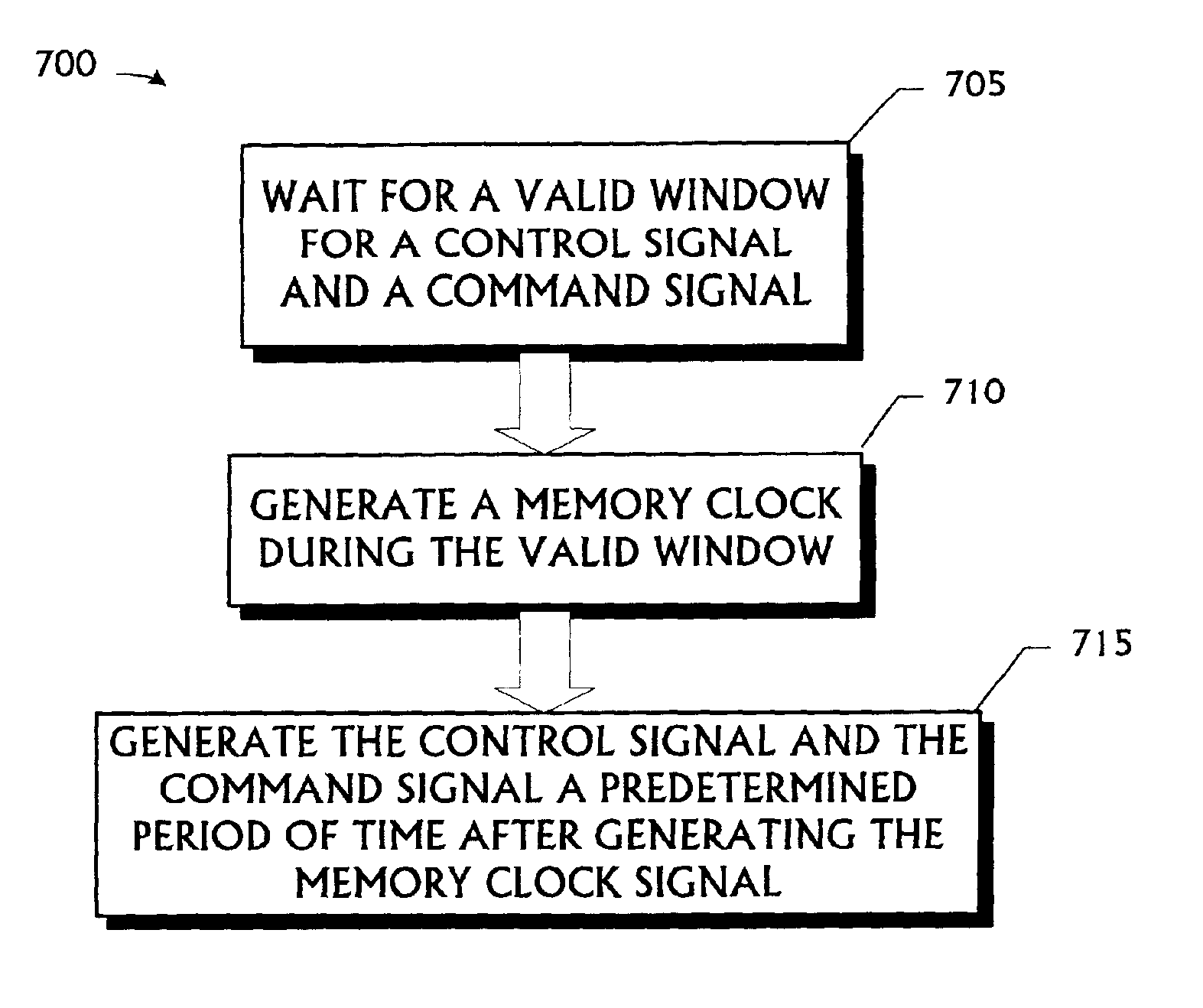

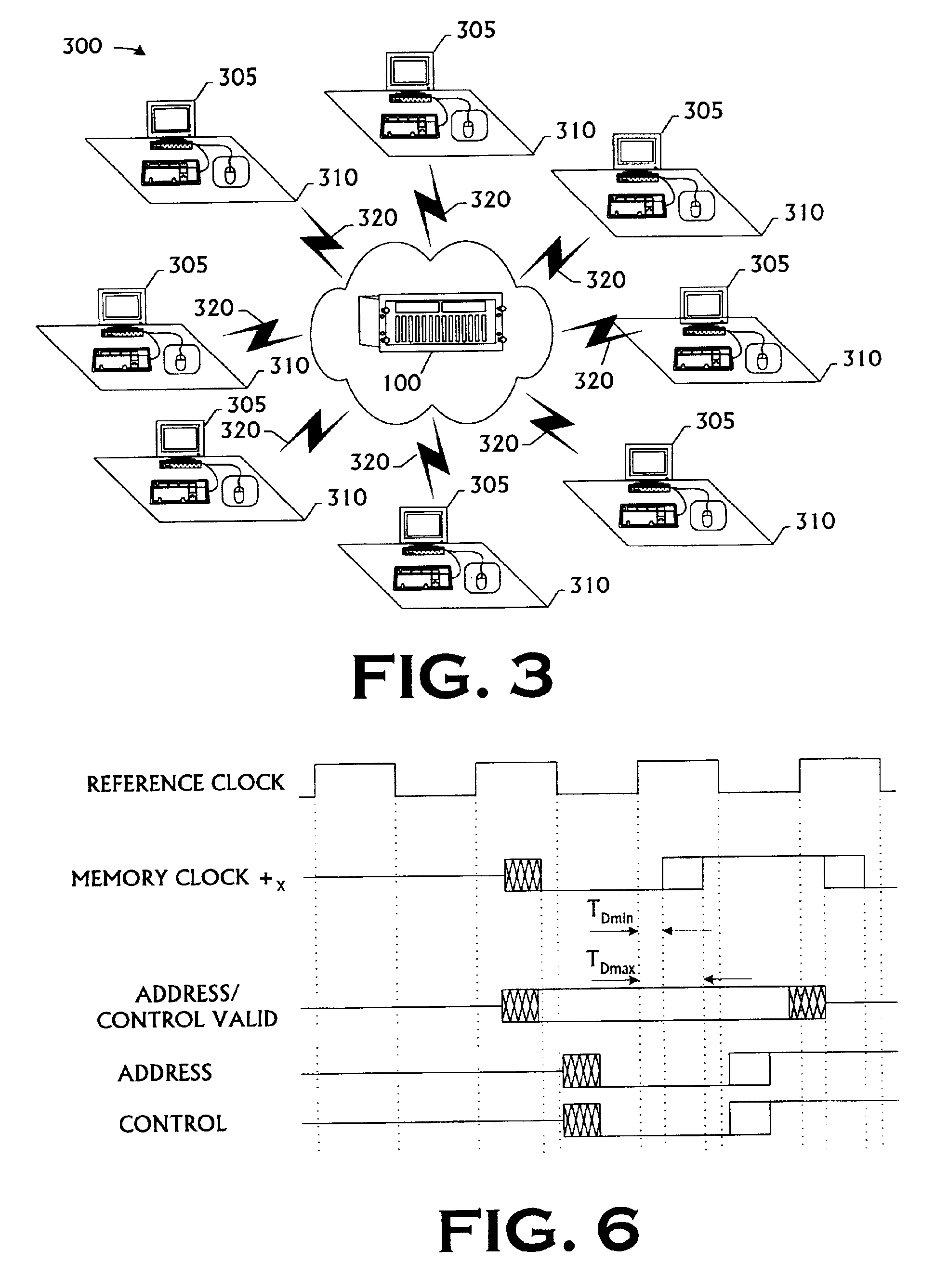

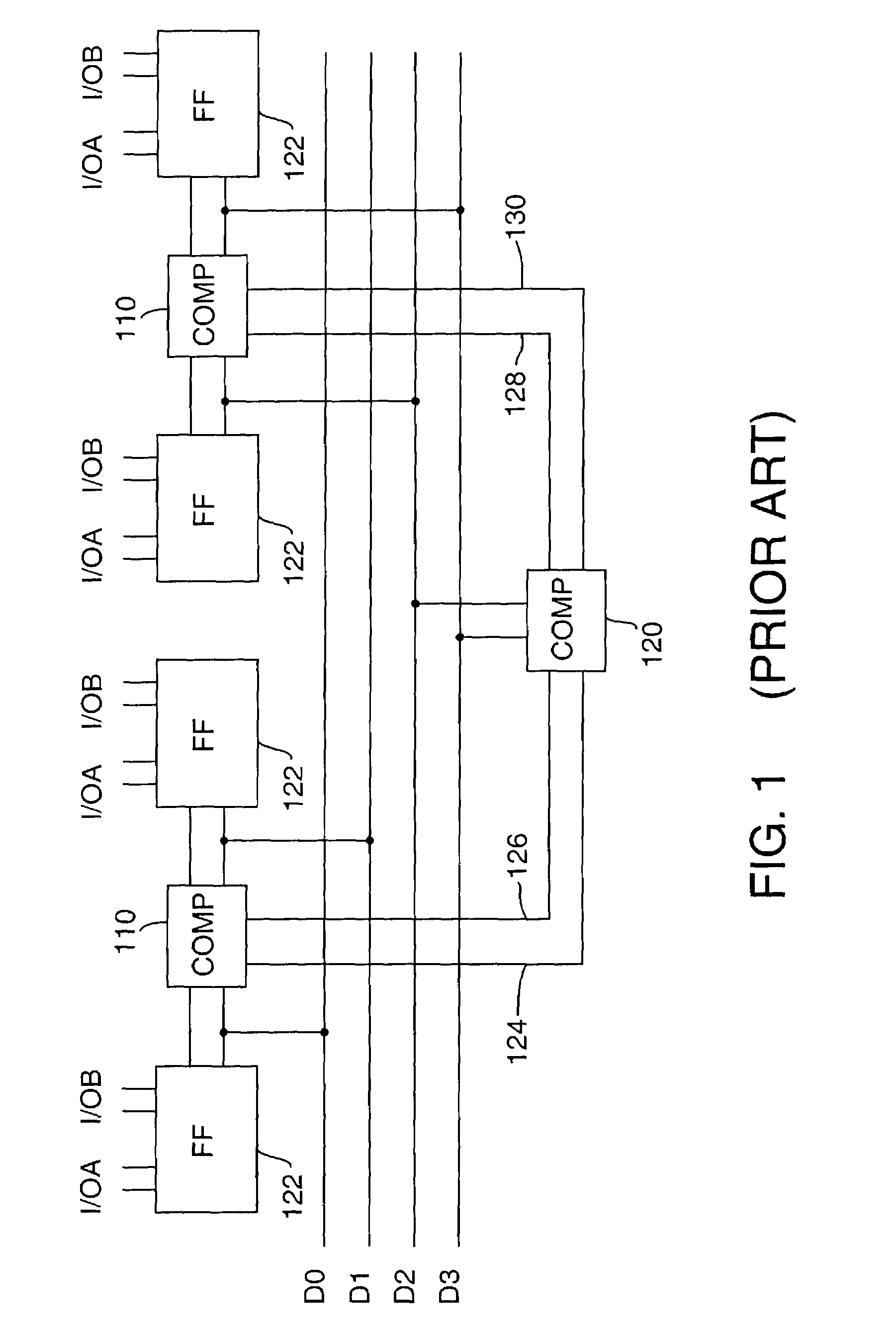

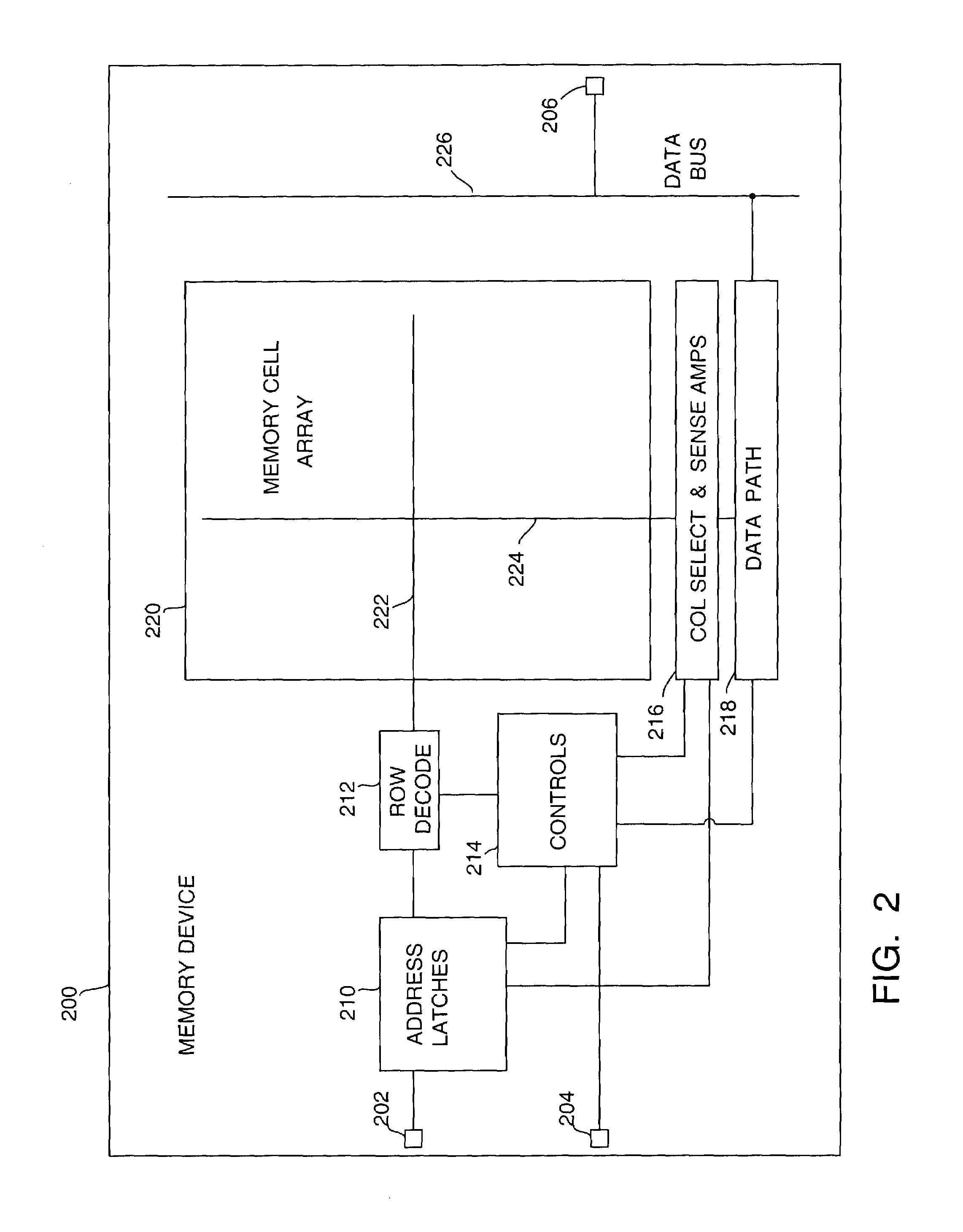

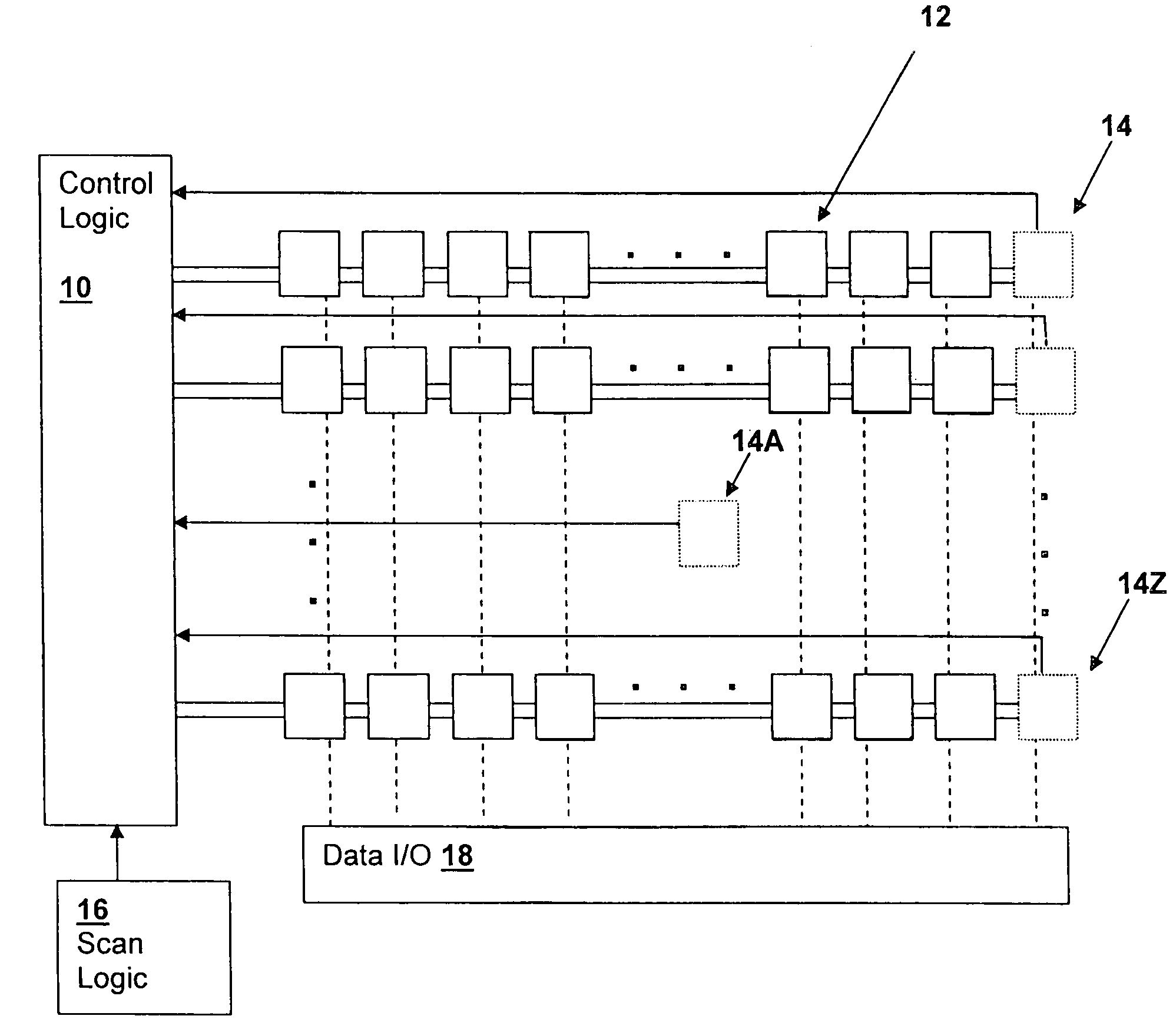

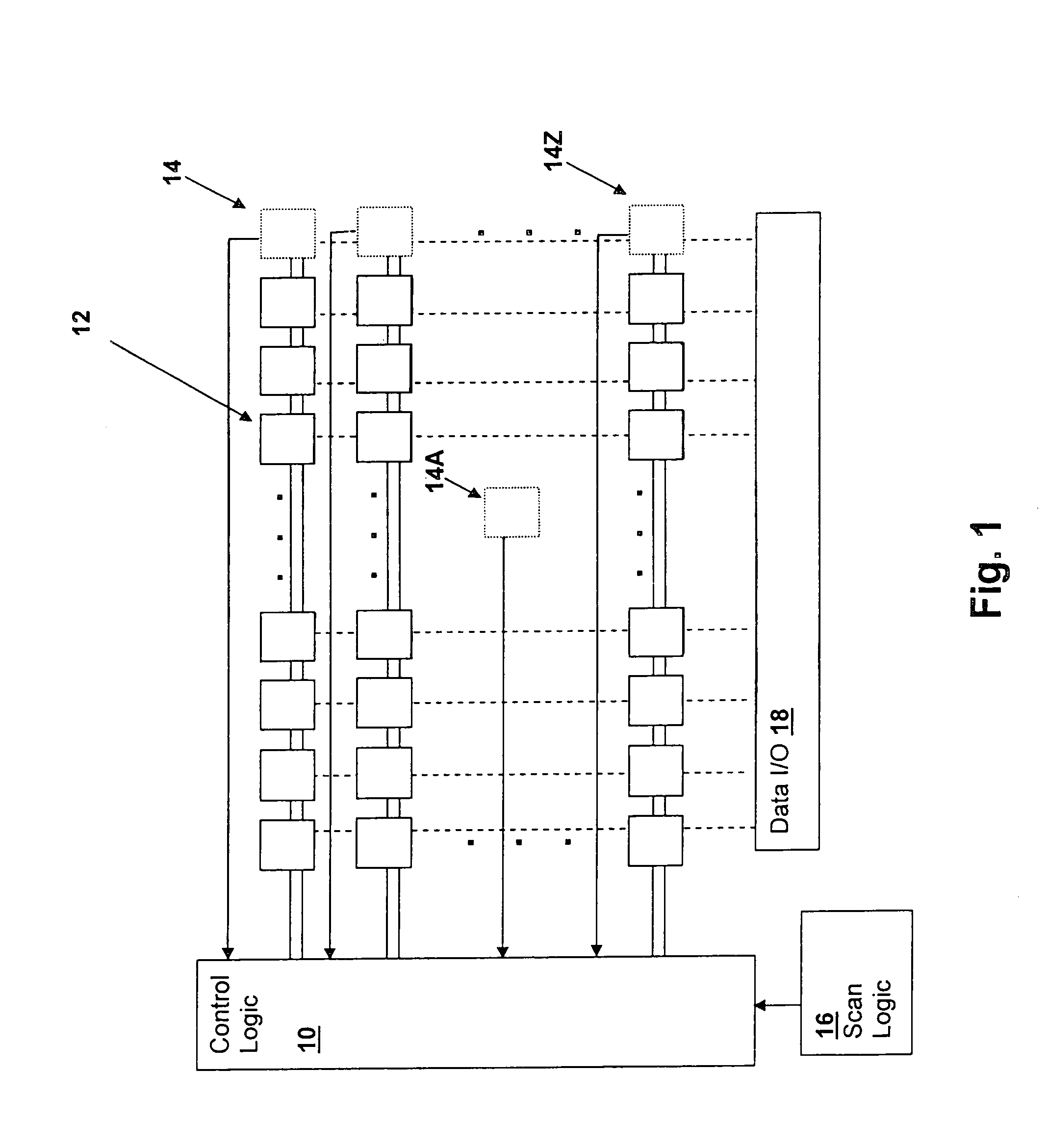

Scalable design for DDR SDRAM buses

A memory subsystem and a method for use in accessing a memory system are disclosed. The memory subsystem comprising a plurality of SDRAM memory modules and a memory controller. The memory controller is capable of waiting to generate a memory clock signal for each of the SDRAM memory modules until a valid window for a control signal and an address signal; generating the memory clock signals during the valid window, and generating the control and address signals. The method comprises: waiting for a valid window for a control signal and an address signal; generating a memory clock during the valid window; and generating the control signal and the command signal a predetermined period of time after generating the memory clock signal.

Owner:ORACLE INT CORP

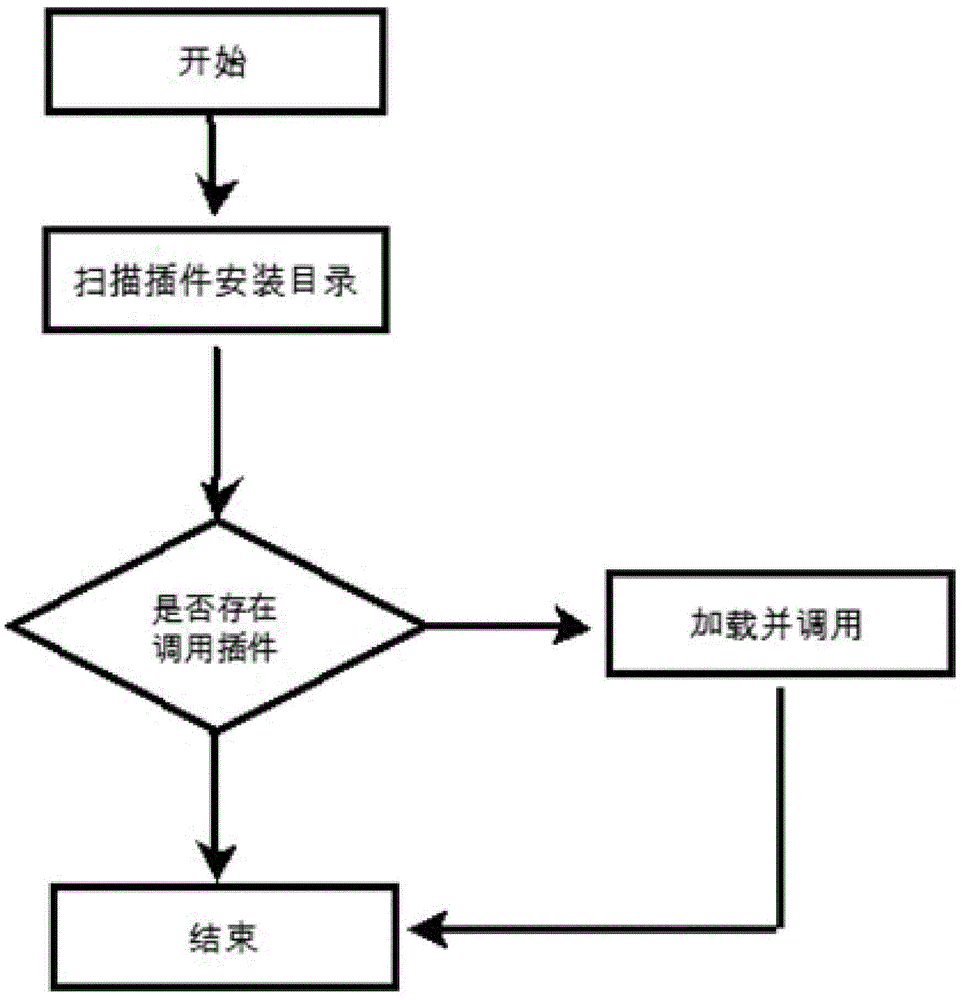

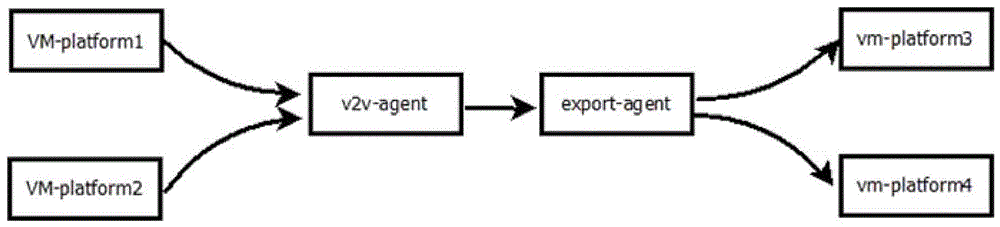

Plug-in mechanism-based virtual machine migration method

InactiveCN106775922AImprove migration efficiencyImplement automatic migrationSoftware simulation/interpretation/emulationScalable designDisk image

The invention discloses a plug-in mechanism-based virtual machine migration method. According to the plug-in mechanism-based virtual machine migration method, a source virtual machine management platform and a target virtual machine management platform are provided, and a migration agent module, a driving module and an import guide module are designed. Based on the three modules, the particular migration process of the virtual machine is as follows: the migration agent module acquires a virtual machine disk image and a configuration specification parameter of the virtual machine from the source virtual machine management platform and finishes conversion; the driving module is used for managing and driving a plug-in; the import agent module rebuilds a virtual machine on the target virtual machine management platform by using the converted virtual machine disk image. Compared with the prior art, the plug-in mechanism-based virtual machine migration method has the advantages that automatic migration of the cross-platform virtual machine is realized; the virtual machine migration efficiency in the operating and maintaining process of the virtual machine management platform is effectively improved; the method is based on an extensible design architecture, so that the new virtual machine management platform can be supported without modifying the original system, and the practicability is high.

Owner:SHANDONG INSPUR CLOUD SERVICE INFORMATION TECH CO LTD

Memory data path circuit

InactiveUS7032143B1Improve scalabilityIncrease the compression ratioDigital storageDatapath circuitsNOR logic

A memory device with a data path circuit having support in the sense-amp region for compression testing of the device. The data path circuit uses NOR logic compression to provide a scalable design which may be extended to large circuits.

Owner:WALLER WILLIAM KENNETH

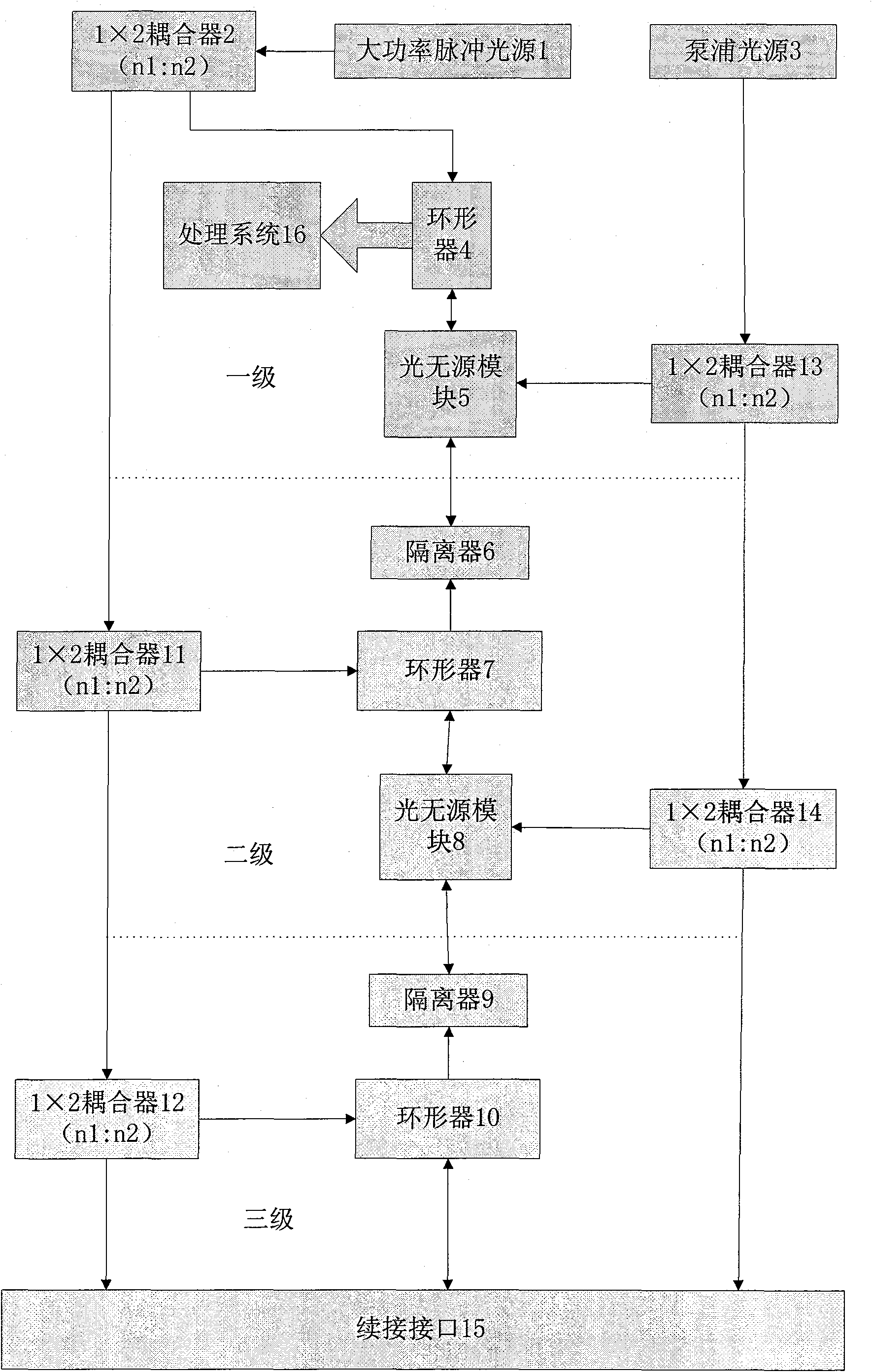

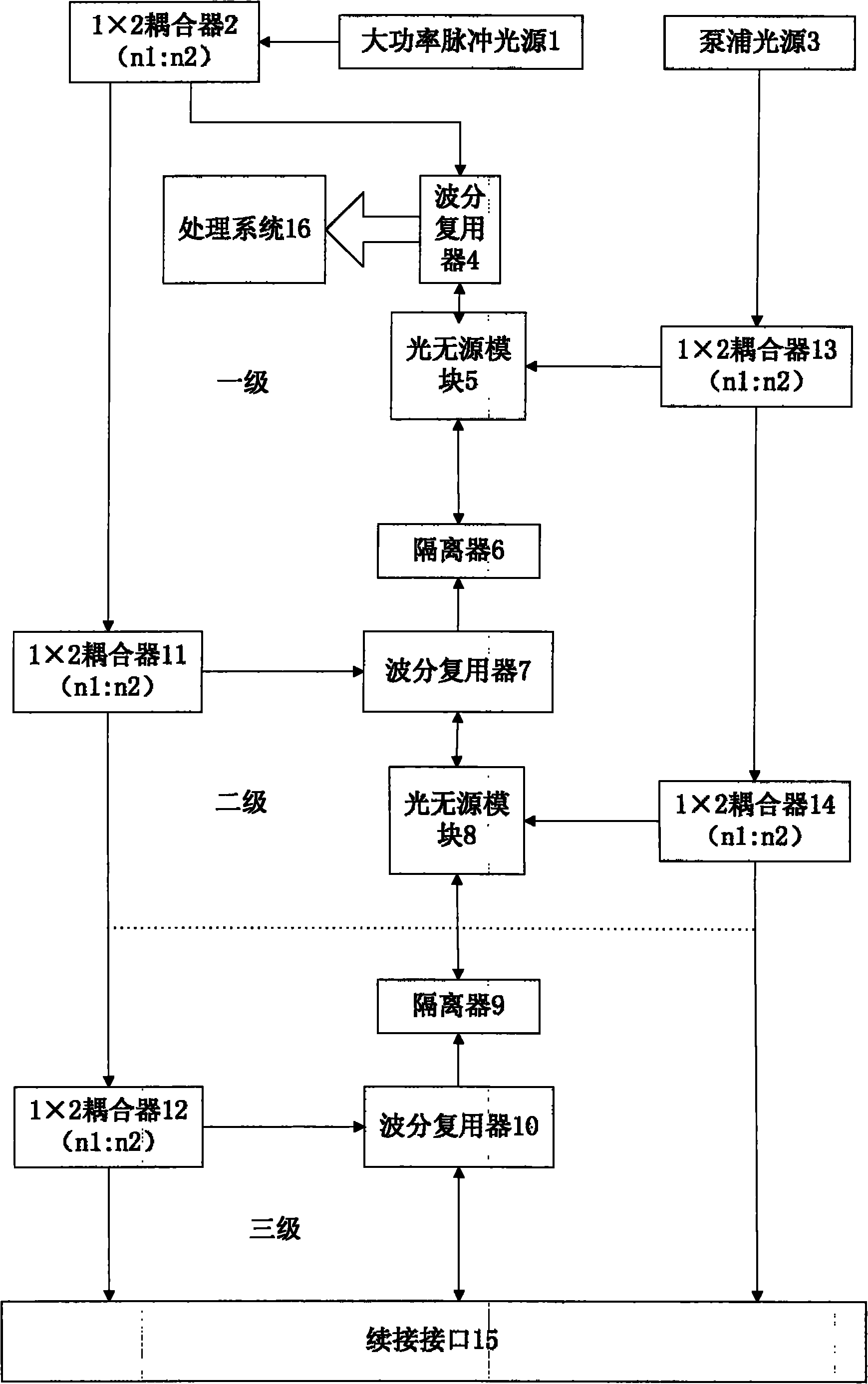

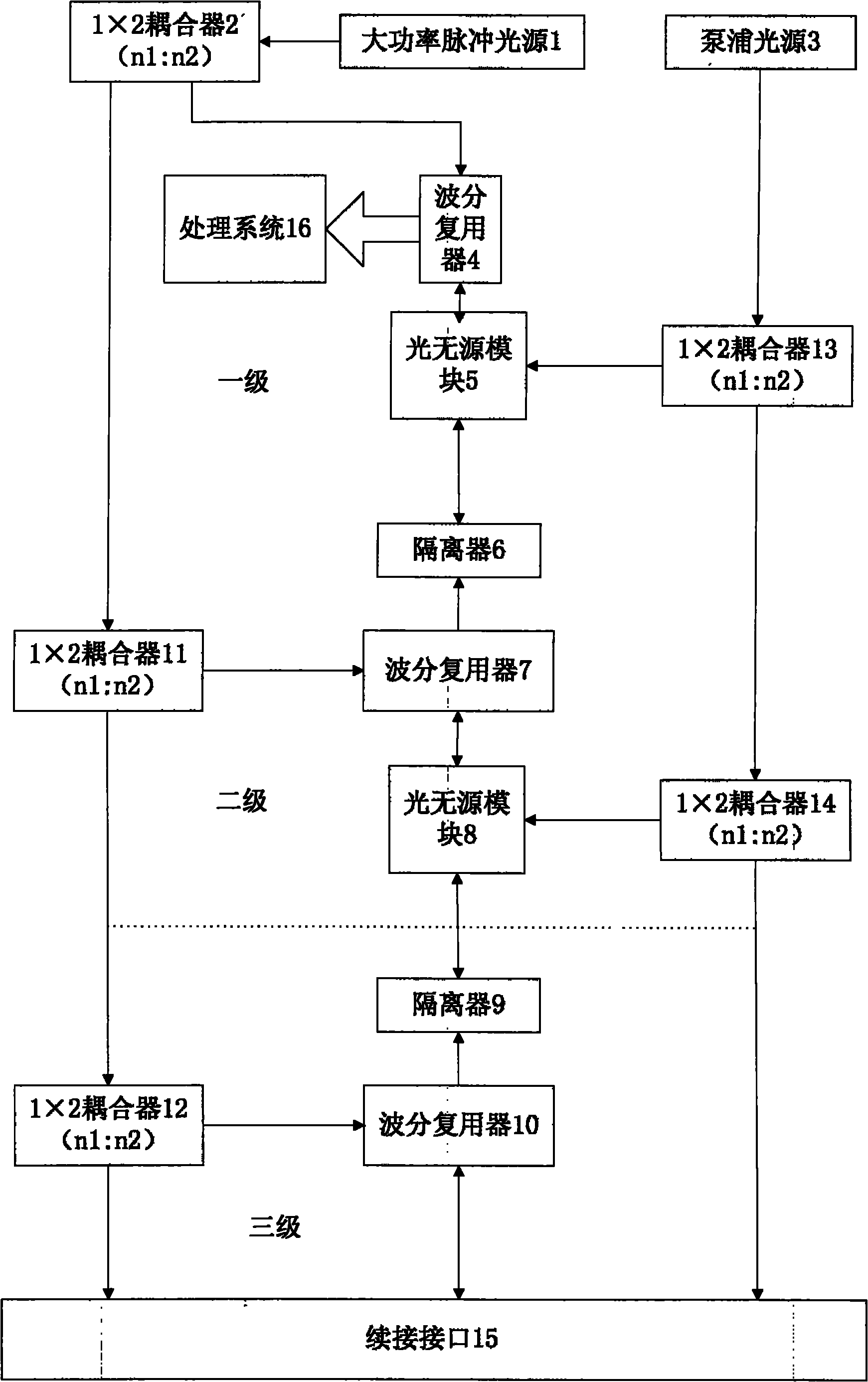

Ultra-long distance distribution type optical fiber sensor and using method thereof

InactiveCN102072741AReduce receiver sensitivityLower requirementSubsonic/sonic/ultrasonic wave measurementThermometers using physical/chemical changesContinuous lightHigh energy

The invention discloses an ultra-long distance distribution type optical fiber sensor and a method for measuring temperature and vibration signals. The ultra-long distance distribution type optical fiber sensor adopts a multi-stage relay amplifier, and a high-power pulse light source enters a detecting optical fiber stage by stage through proportional allocation of a plurality of optical fiber couplers and transmission of transmission fibers, and re-amplifies the pulse of the detecting light at a specified length, thereby improving the signal to noise ratio of the system in terms of 'source', being capable of avoiding non-linear scattering caused by overrun light which enters a detecting optical cable directly on one hand, and being capable of reducing higher energy loss caused by continuous light transmission on the other hand. The ultra-long distance distribution type optical fiber sensor adopts the staged design, thereby greatly reducing the requirement on receiving sensitive and dynamic range of a receiving circuit. In addition, the ultra-long distance distribution type optical fiber sensor adopts the expandable design, thereby being capable of conveniently realizing short-distance detection, long-distance detection and ultra-long distance detection in sequence.

Owner:SHANGHAI BOOM FIBER SENSING TECH

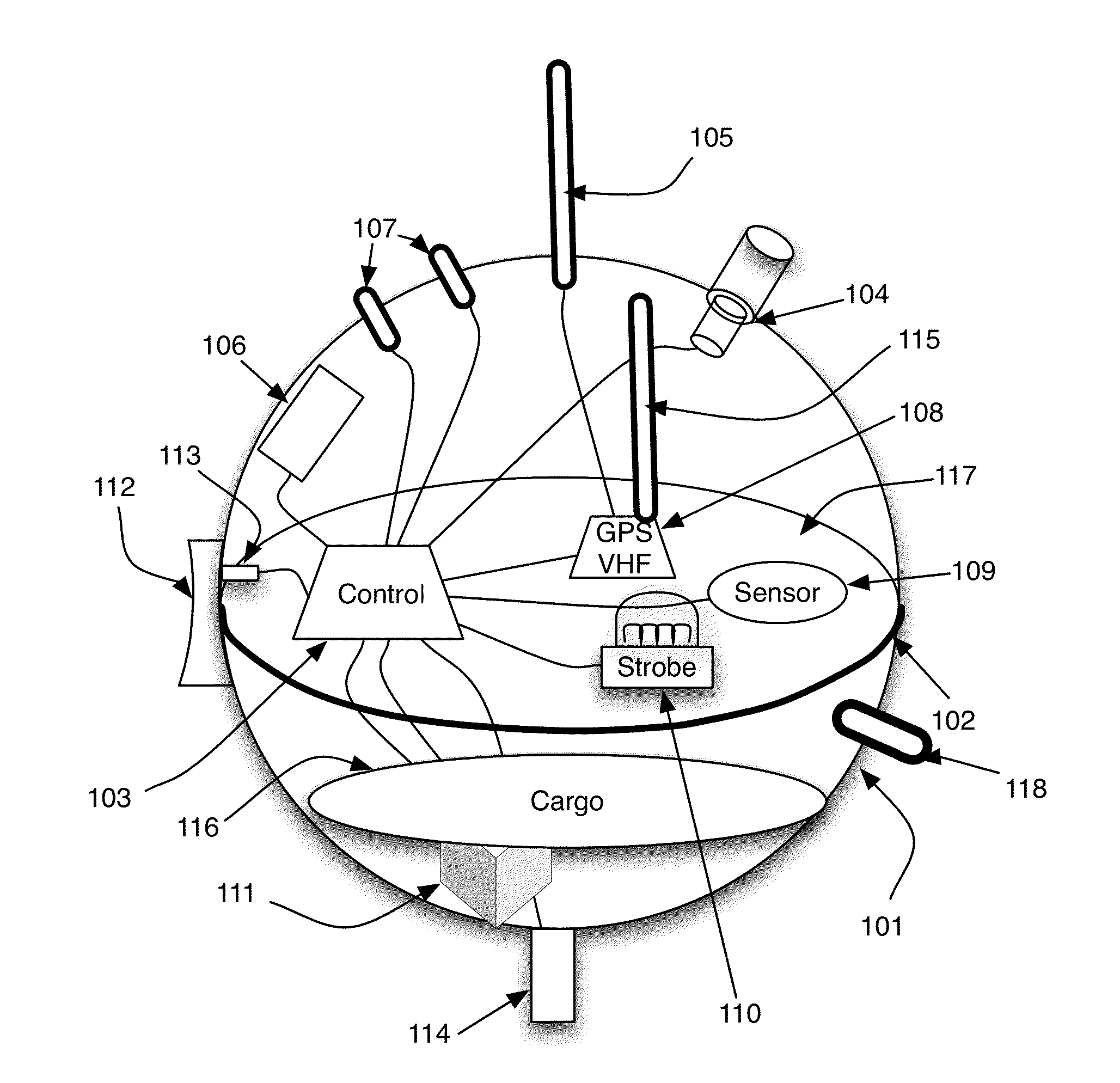

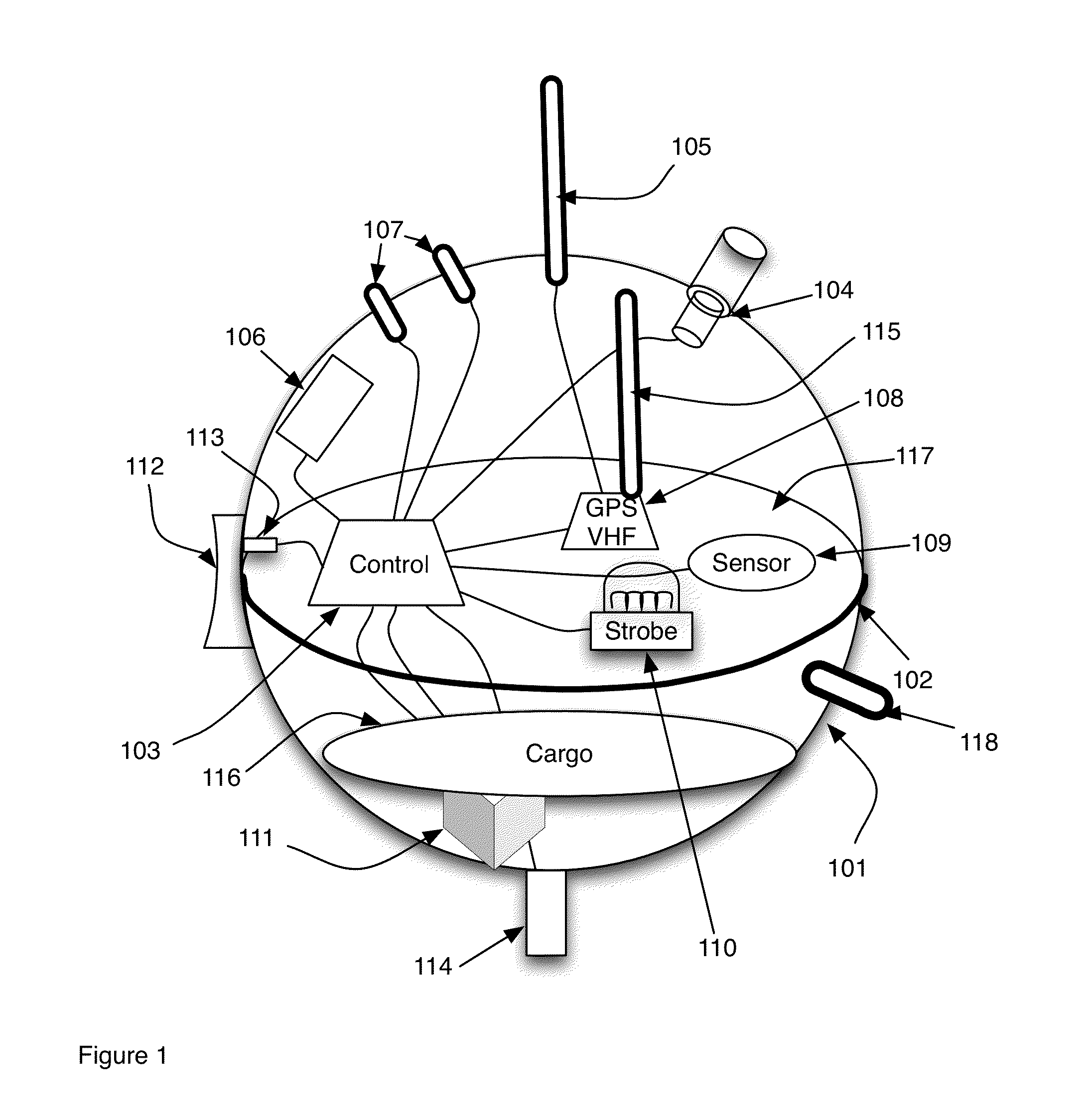

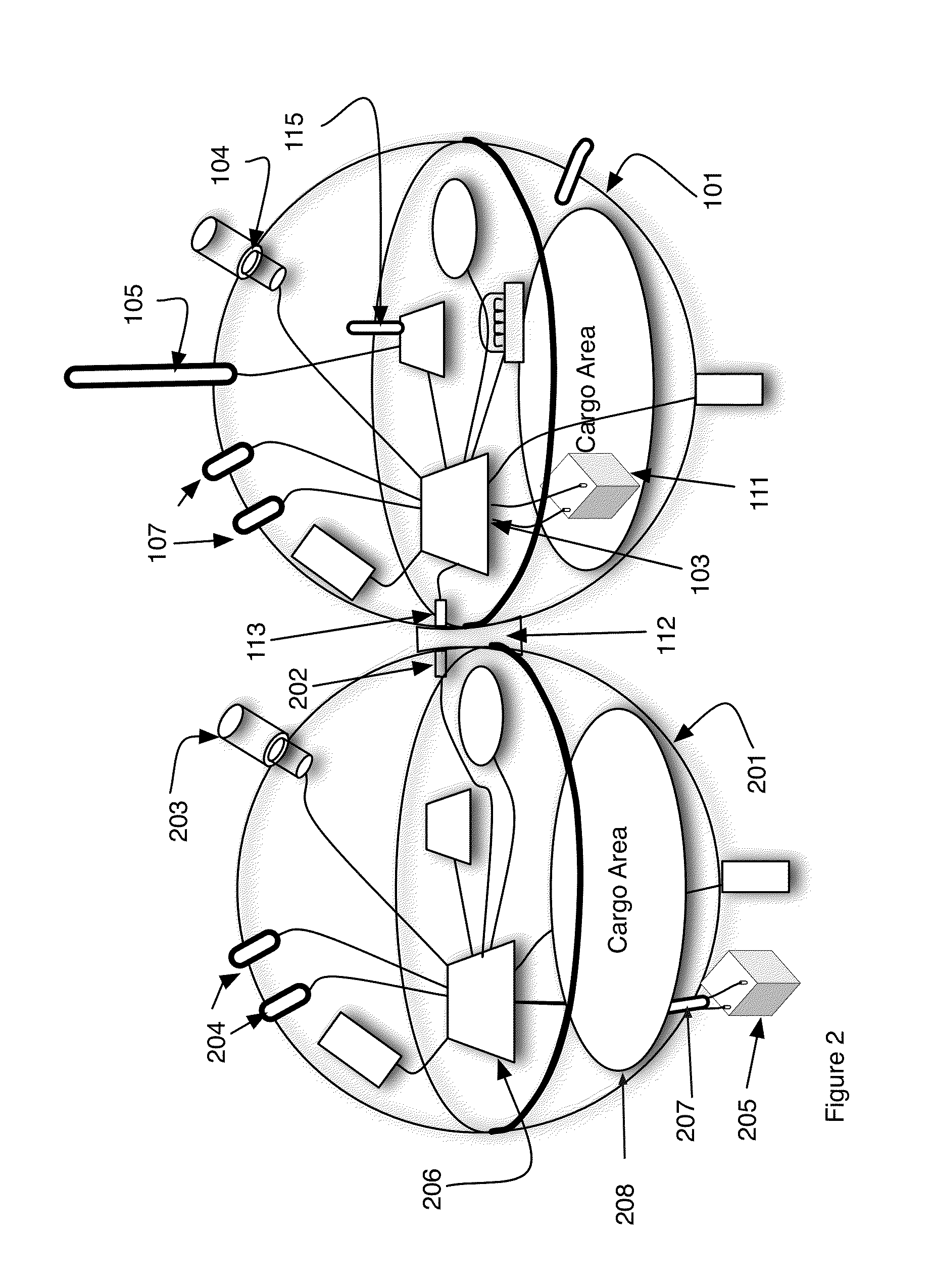

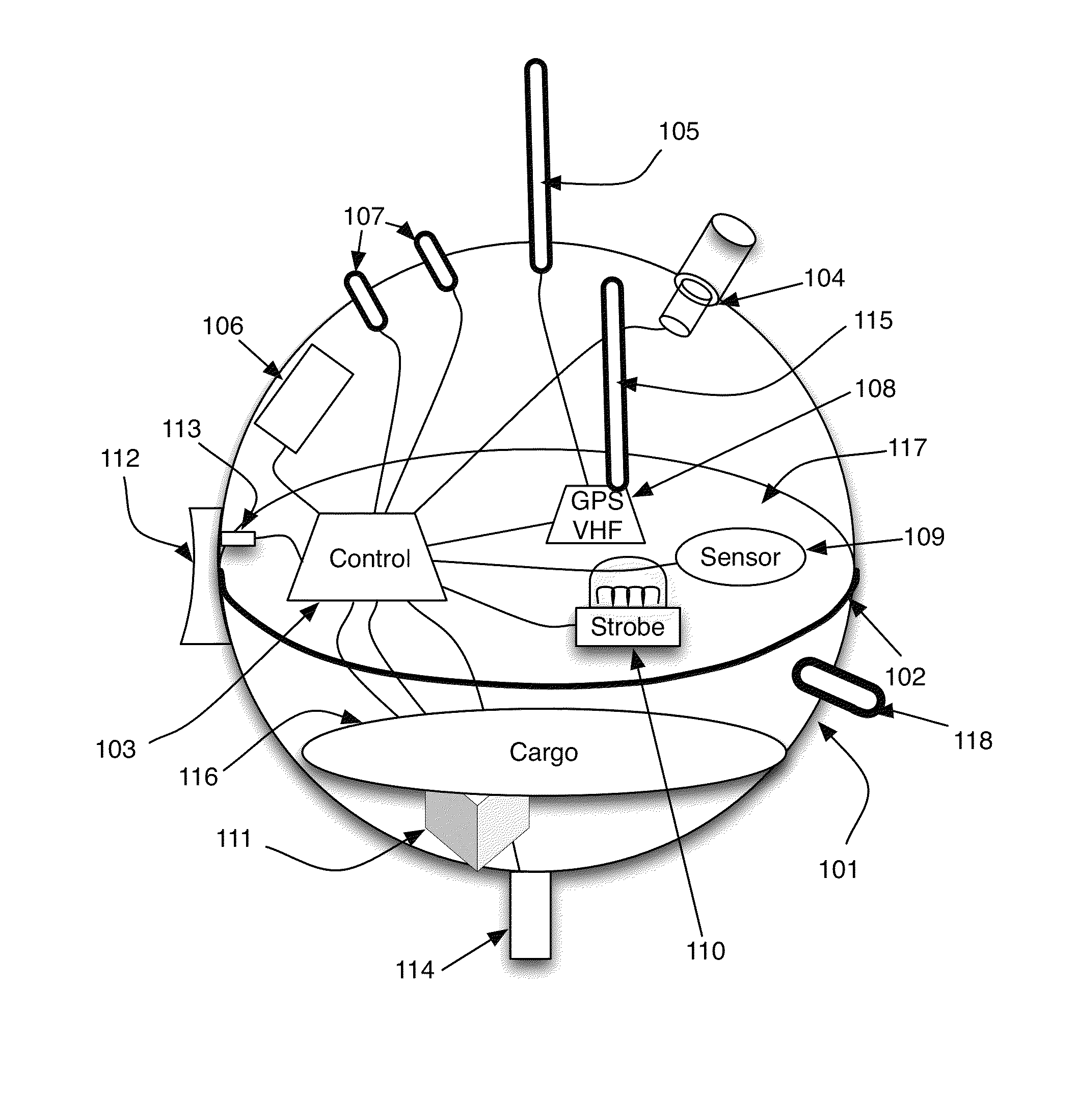

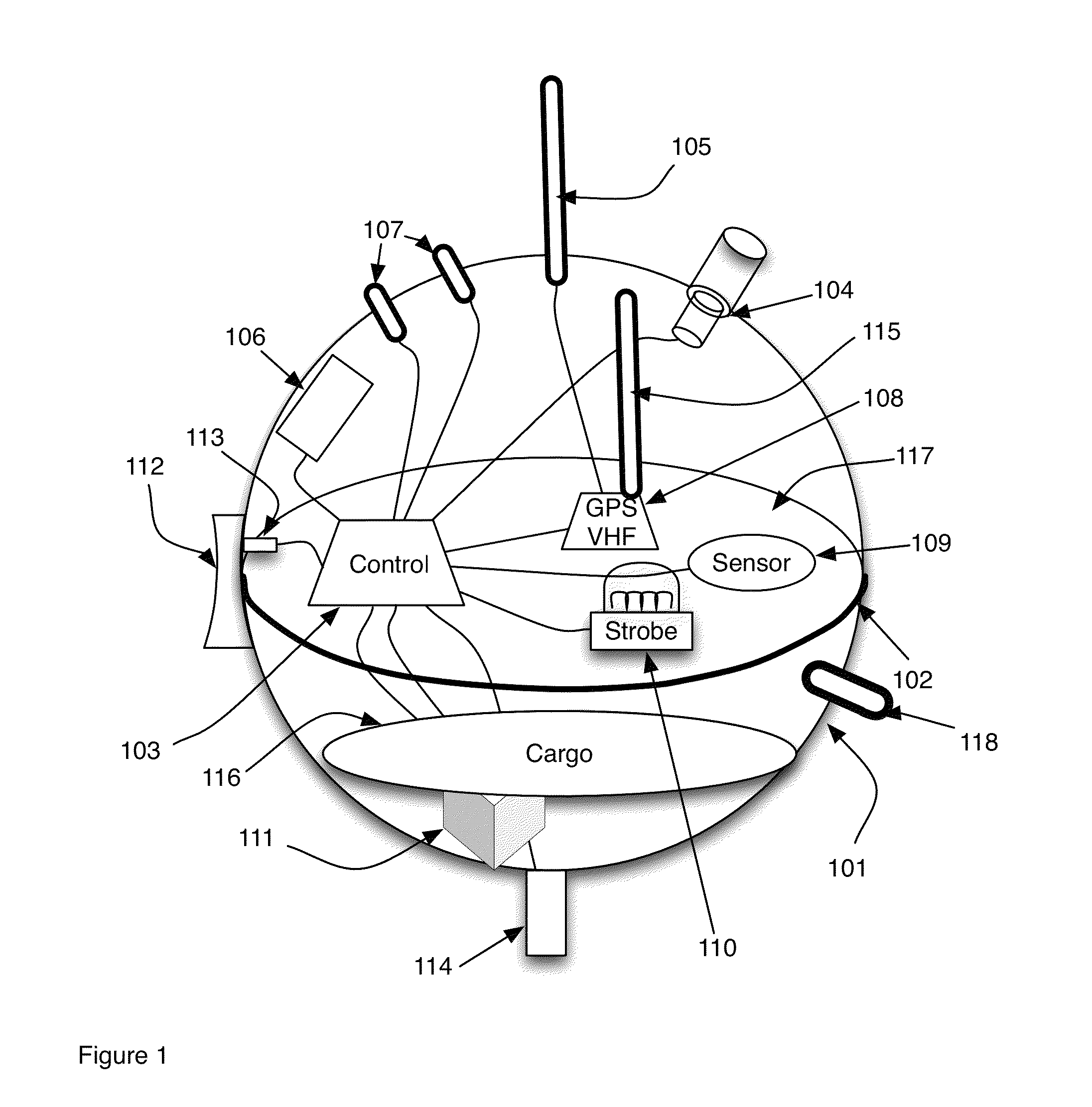

Undersea Free Vehicle and Components

ActiveUS20140216325A1Easy to reconfigureMake up for deficienciesUnderwater vesselsUnderwater equipmentOcean bottomControl electronics

A free vehicle suitable to serve as a platform to carry a variety of equipment to the ocean floor, actuate devices at the floor and at intermediate points on the way to and returning from the ocean floor is described. The free vehicle includes standardized power, control electronics, navigation equipment and mechanical release mechanisms that can be used in conjunction with custom experiments. Exemplary experiments include sensors and sampling equipment used for deep-sea exploration. The free vehicle platform provides for scalable designs to meet scientific needs and surface vessel constraints.

Owner:HARDY KEVIN RICHARD +1

Efficient circuits for out-of-order microprocessors

InactiveUS20060015547A1Improve performanceAvoid performanceDigital data processing detailsDigital computer detailsExtensibilityScalar processor

The poor scalability of existing superscalar processors has been of great concern to the computer engineering community. In particular, the critical-path delays of many components in existing implementations grow quadratically with the issue width and the window size. This patent presents a novel way to reimplement these components and reduce their critical-path delay growth. It then describes an entire processor microarchitecture, called the Ultrascalar processor, that has better critical-path delay growth than existing superscalars. Most of our scalable designs are based on a single circuit, a cyclic segmented parallel prefix (cspp). We observe that processor components typically operate on a wrap-around sequence of instructions, computing some associative property of that sequence. For example, to assign an ALU to the oldest requesting instruction, each instruction in the instruction sequence must be told whether any preceding instructions are requesting an ALU. Similarly, to read an argument register, an instruction must somehow communicate with the most recent preceding instruction that wrote that register. A cspp circuit can implement such functions by computing for each instruction within a wrap-around instruction sequence the accumulative result of applying some associative operator to all the preceding instructions. A cspp circuit has a critical path gate delay logarithmic in the length of the instruction sequence. Depending on its associative operation and its layout, a cspp circuit can have a critical path wire delay sublinear in the length of the instruction sequence.

Owner:YALE UNIV

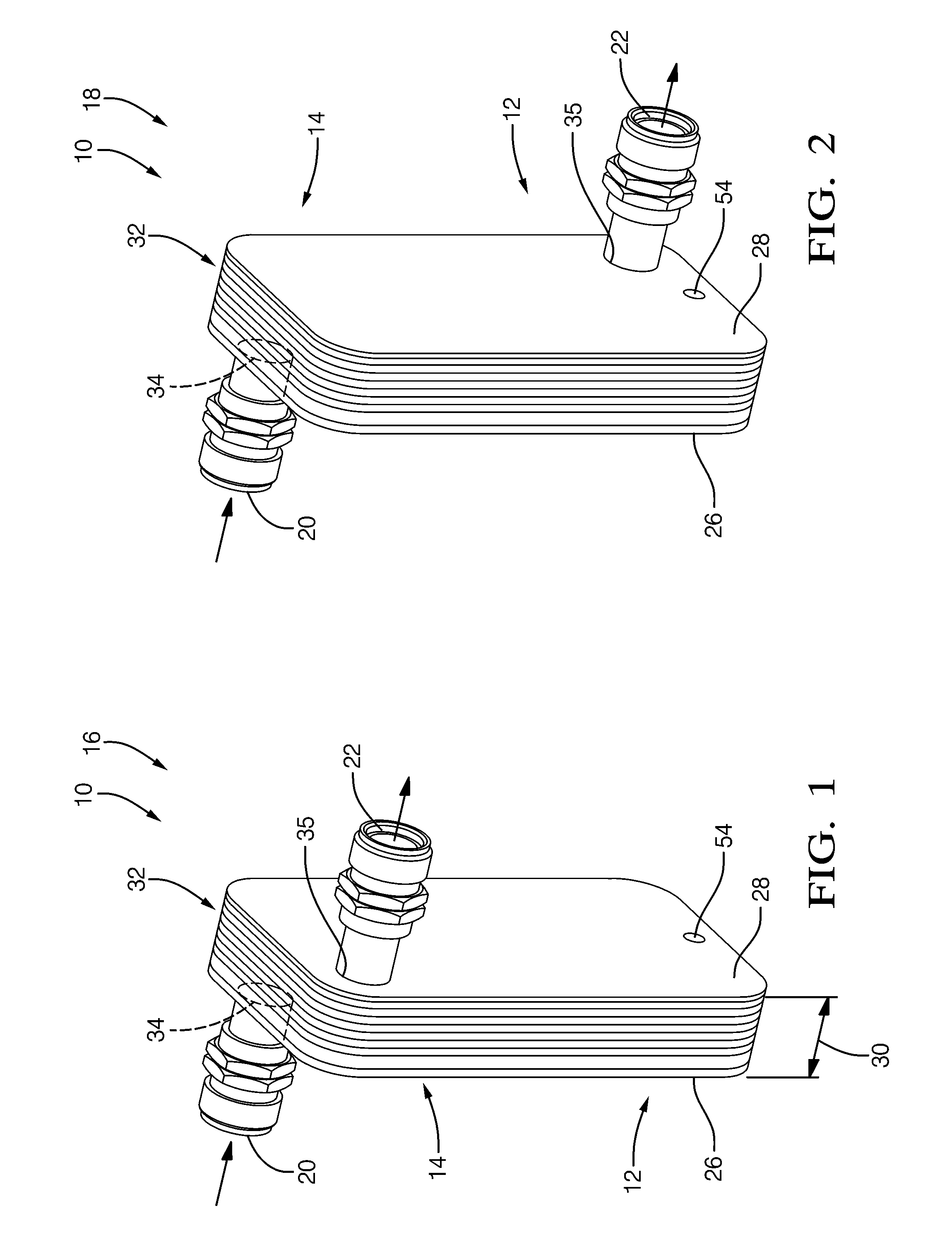

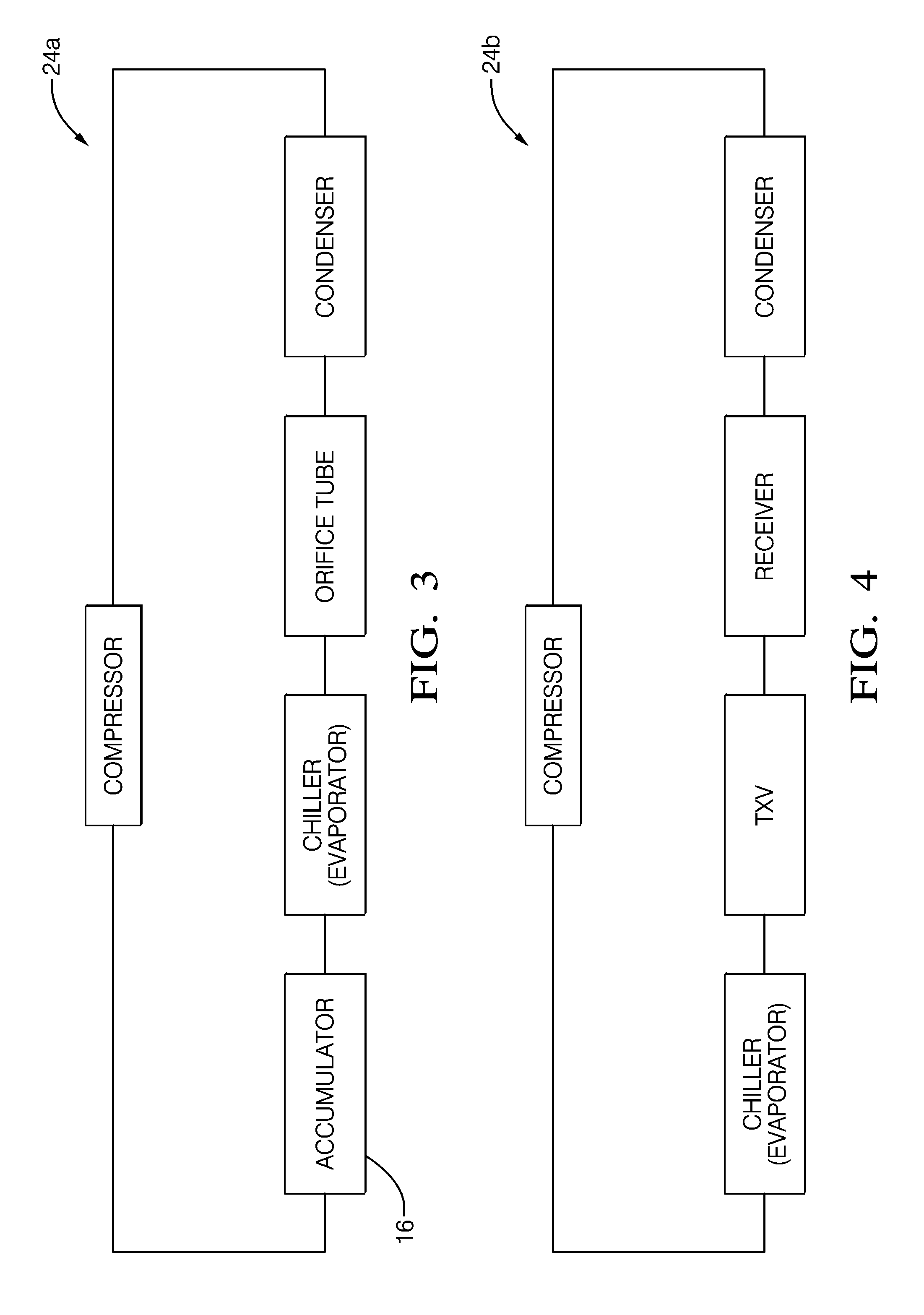

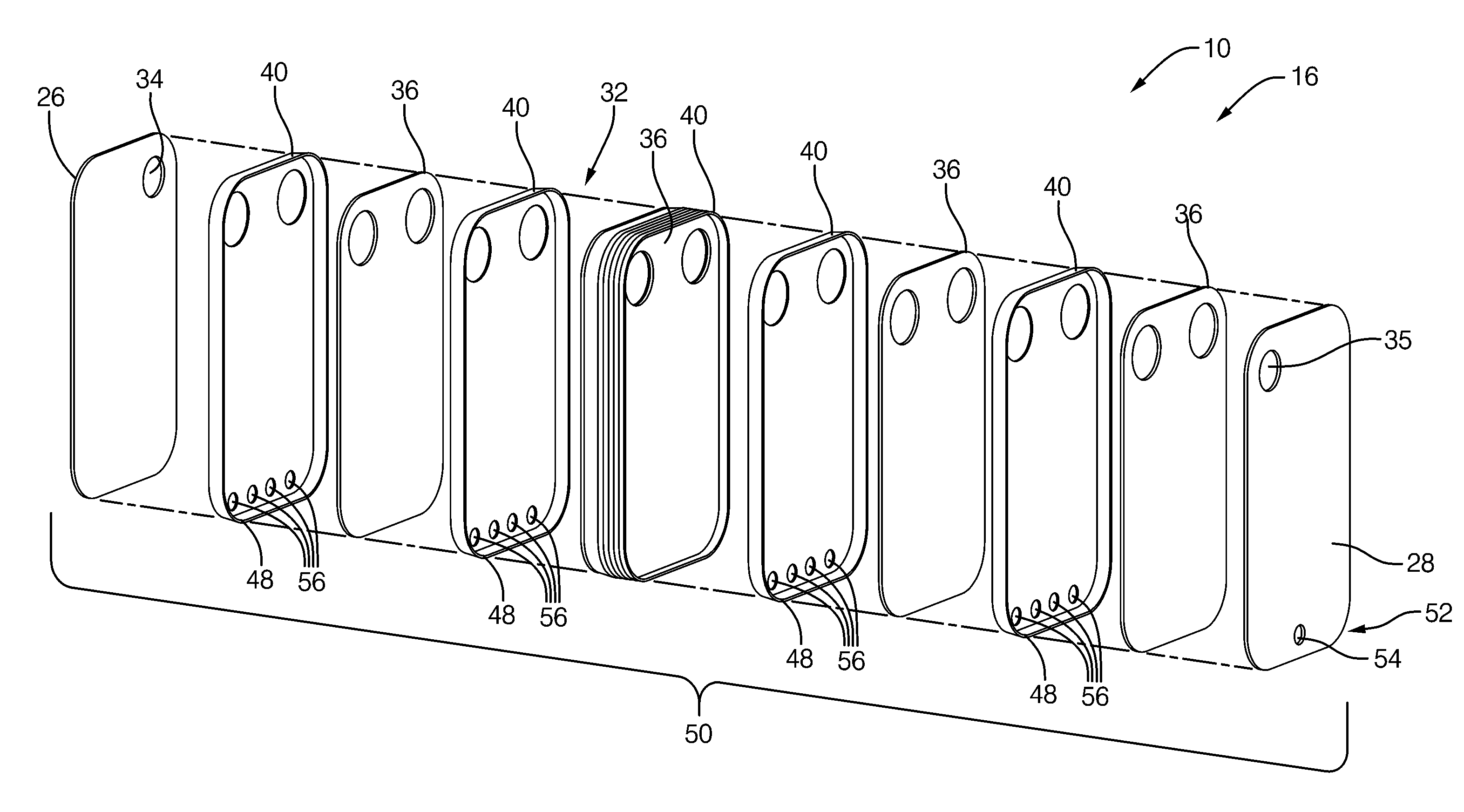

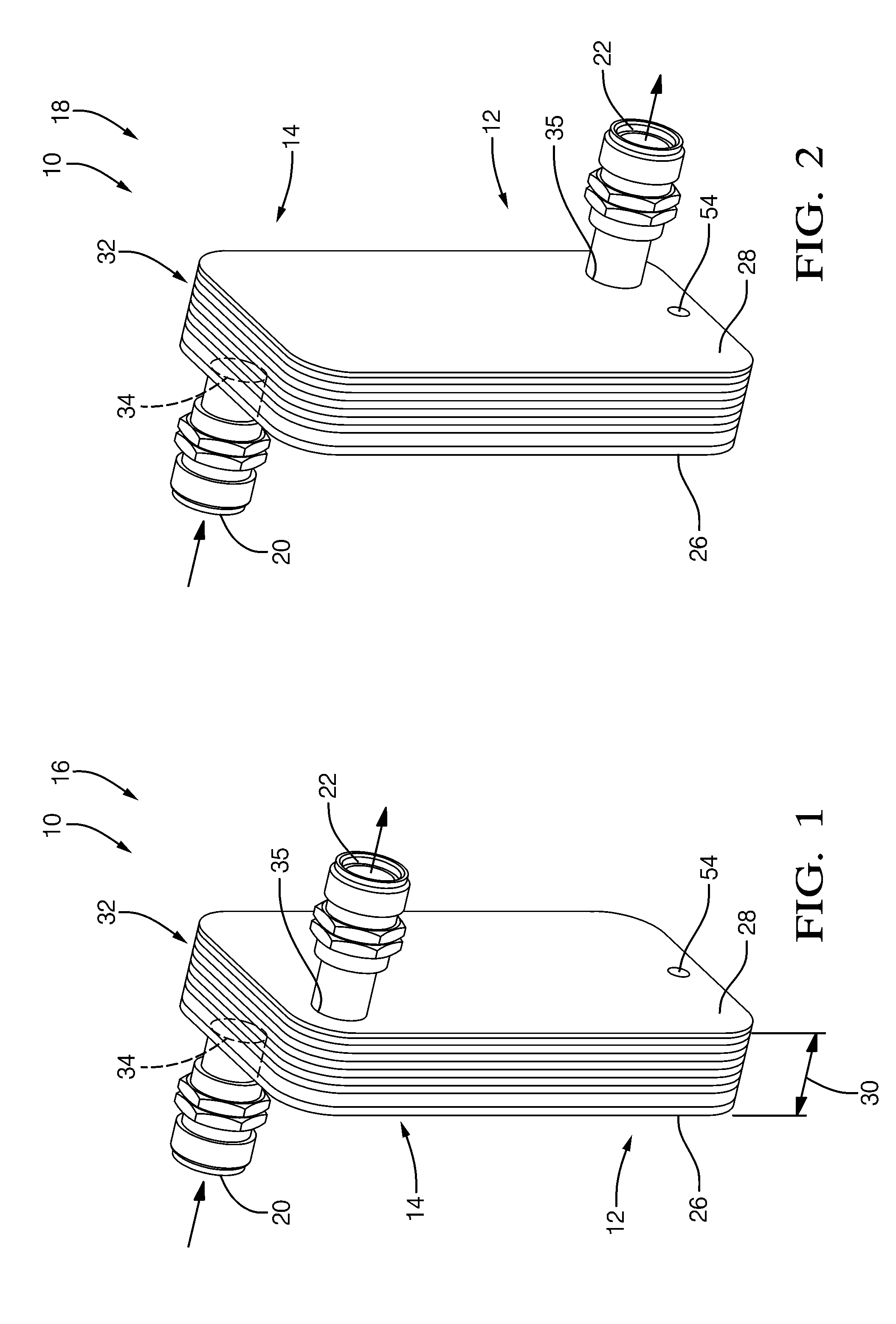

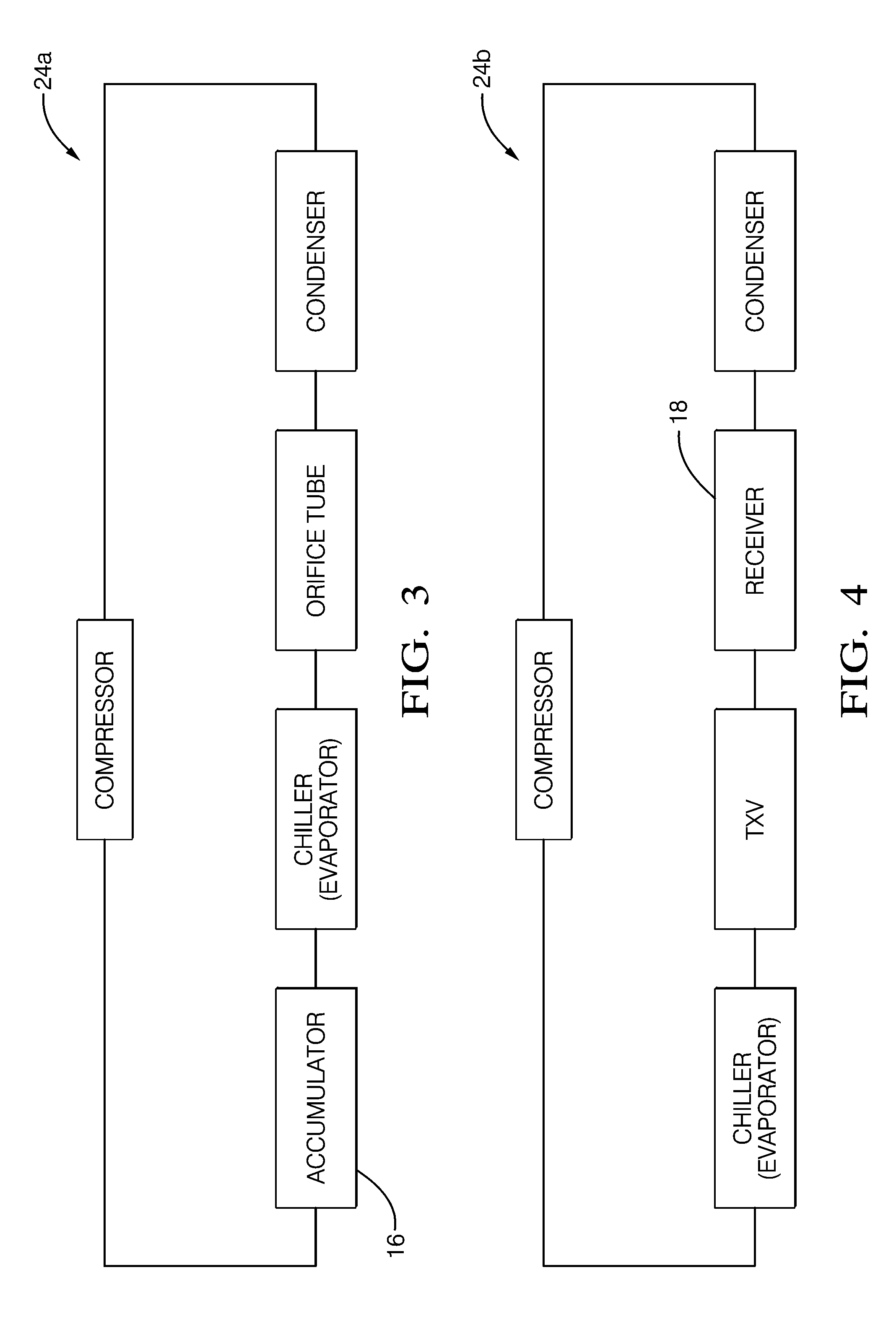

Parallel plate type refrigerant storage device

A refrigerant storage device that arranges two end plates to form a cavity and includes a turbulator plate within the cavity. The turbulator plate is arranged within the cavity to reinforce the cavity by providing a plurality of reinforcement portions between the end plates. The cavity is sized and the turbulator plate is configured so a liquid portion of refrigerant flowing through the cavity collects onto the turbulator plate. The device has a rectangular shape that simplifies vehicle packaging and allows the device to be readily integrated into a plate-type refrigerant-to-liquid coolant heat exchanger. The device is formed by a stacking arrangement of parts that provides for a readily scalable design.

Owner:MAHLE INT GMBH

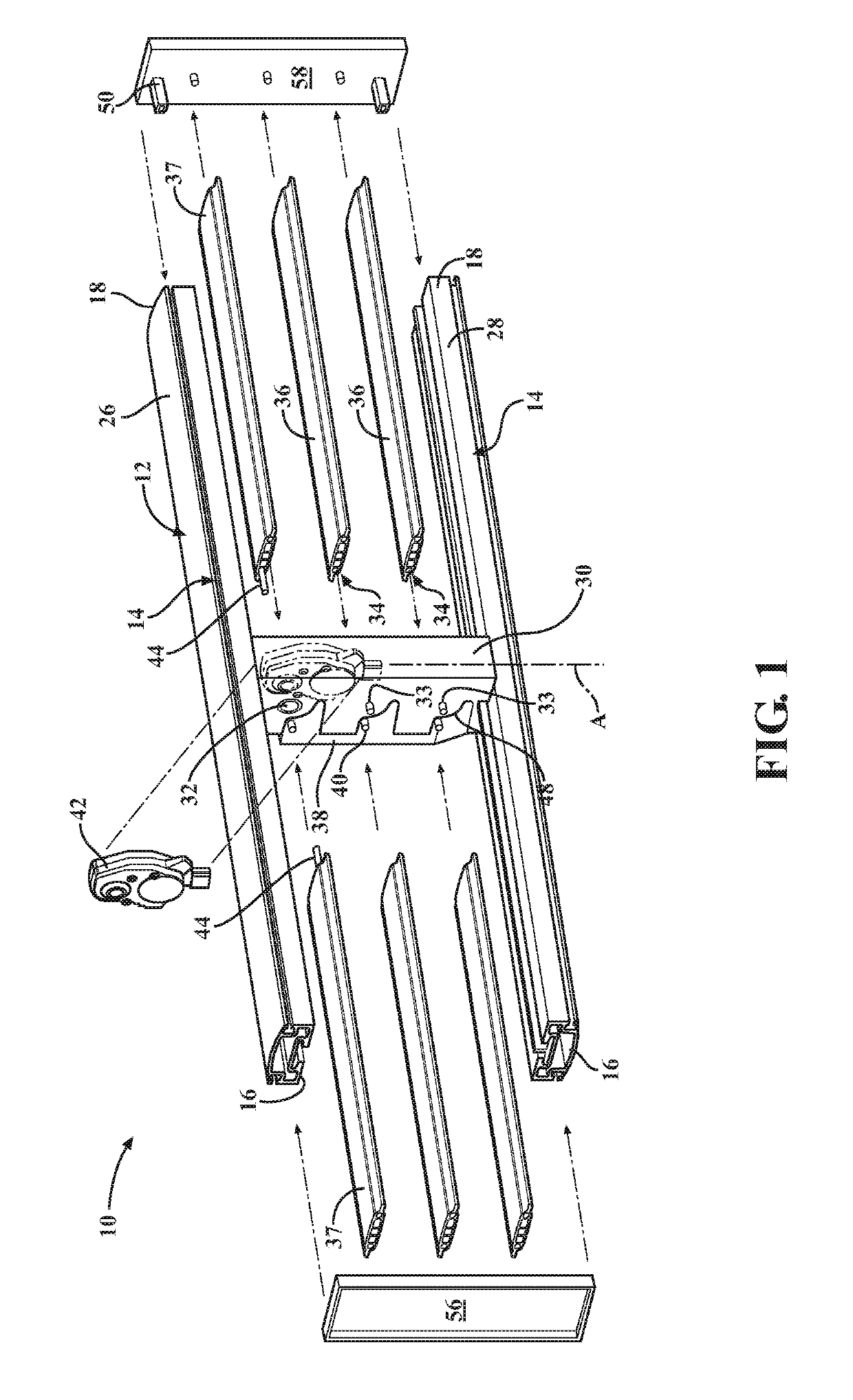

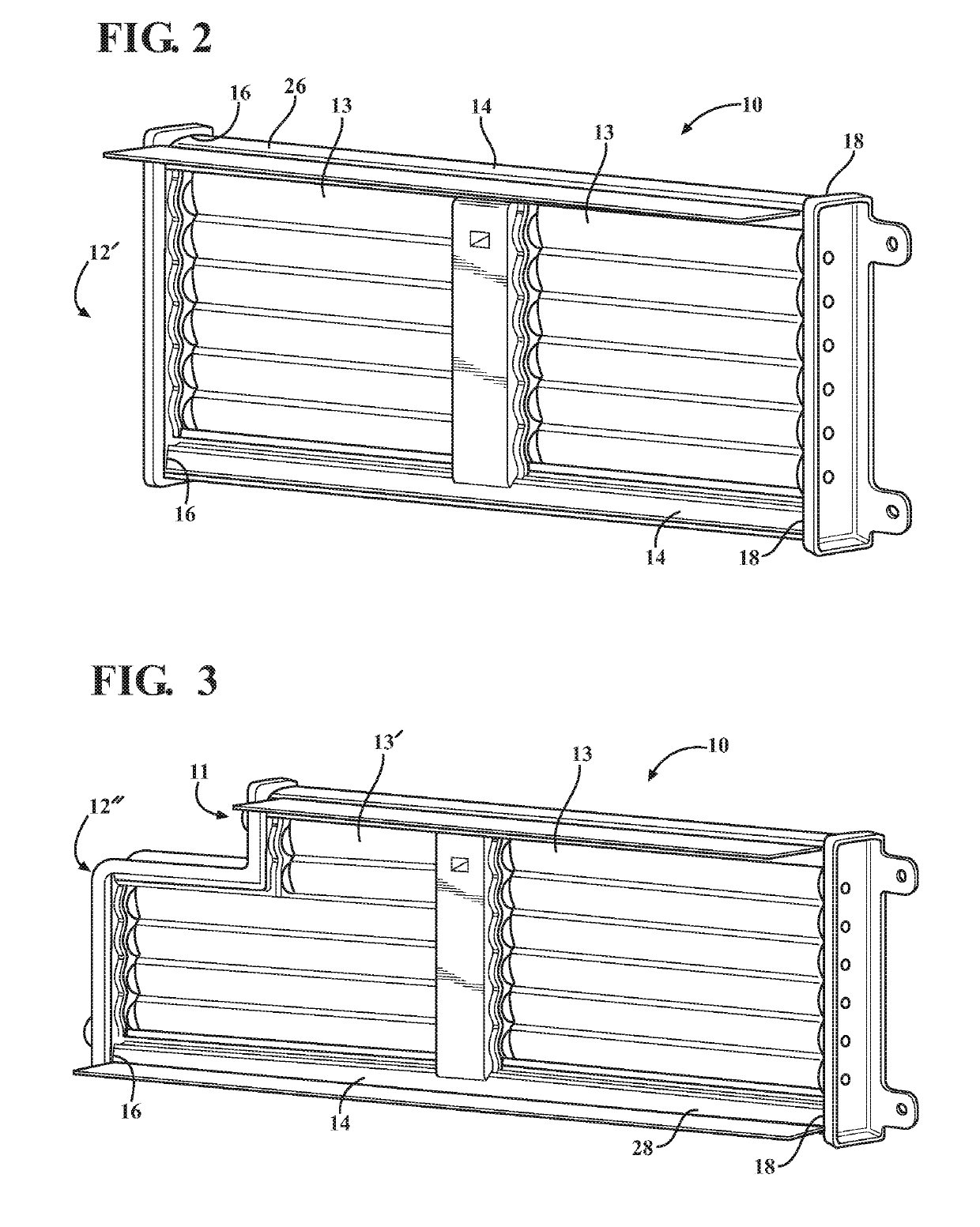

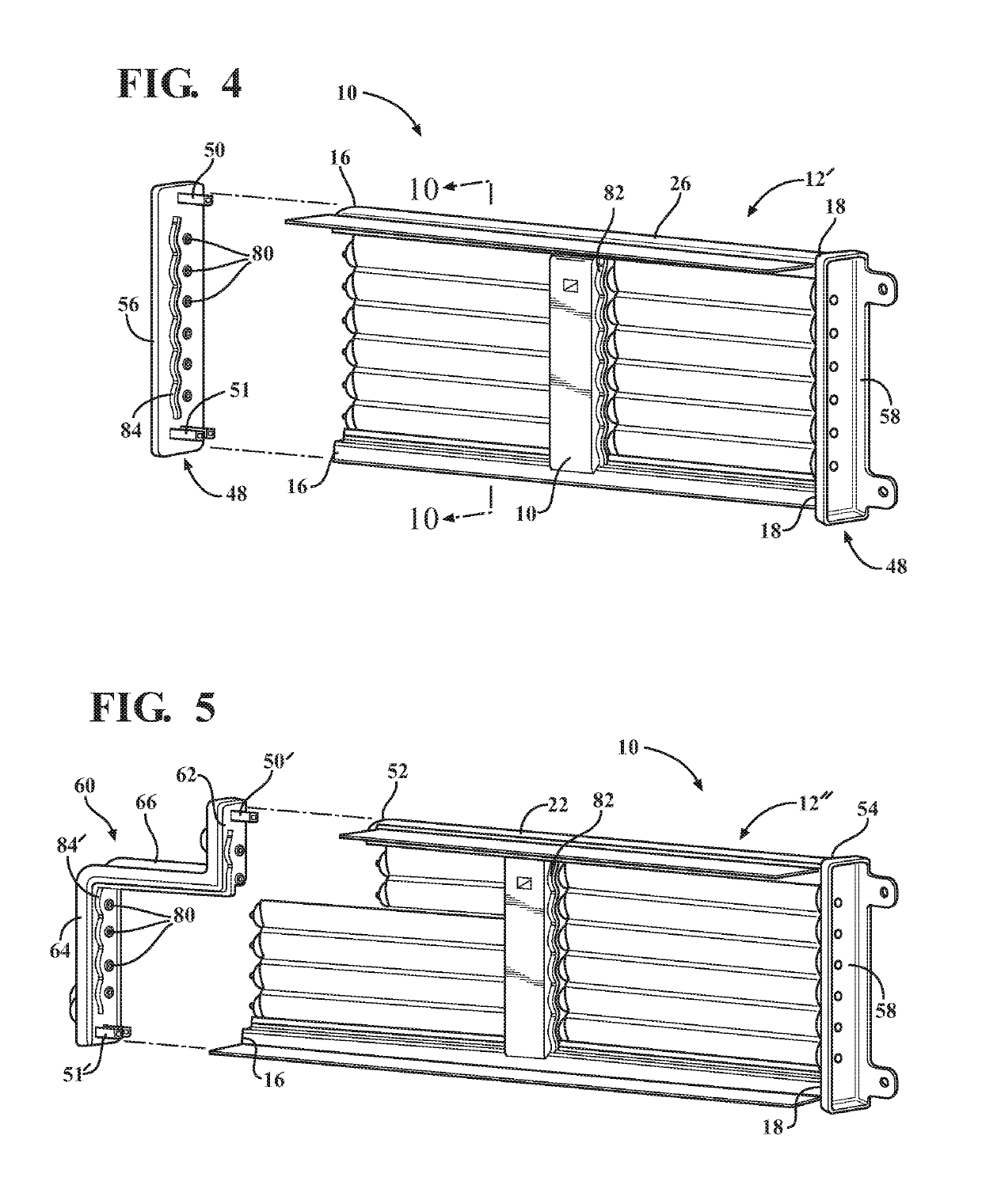

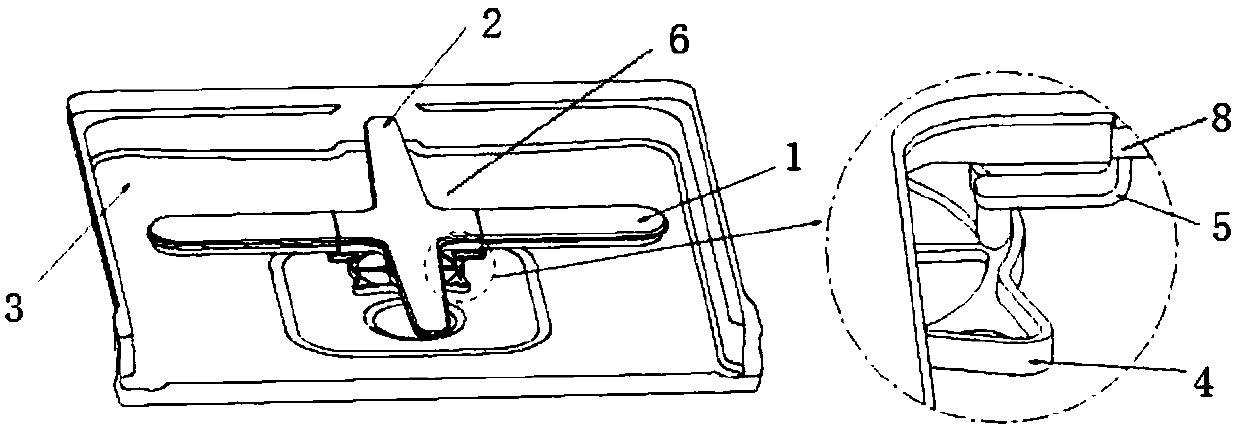

Active grille, scalable design

An active grille shutter arrangement having an assembled modular frame with a plurality of primary frame pieces formed by extrusion. Each one of the plurality of primary frame pieces has a first end, a second end and at least one key slot extending between the first end and the second end. Each of the plurality of frame pieces also includes a hollow bore extending through the each one of the plurality of primary frame pieces forming an aperture at the first end and an aperture at the second end. When the modular frame is assembled there is an upper frame portion and lower frame portion, both formed from one of the plurality of primary frame pieces. The arrangement also includes a number of alternate frame and vane pieces that allow several different active grille shapes and configurations to be formed.

Owner:MAGNA EXTERIORS INC

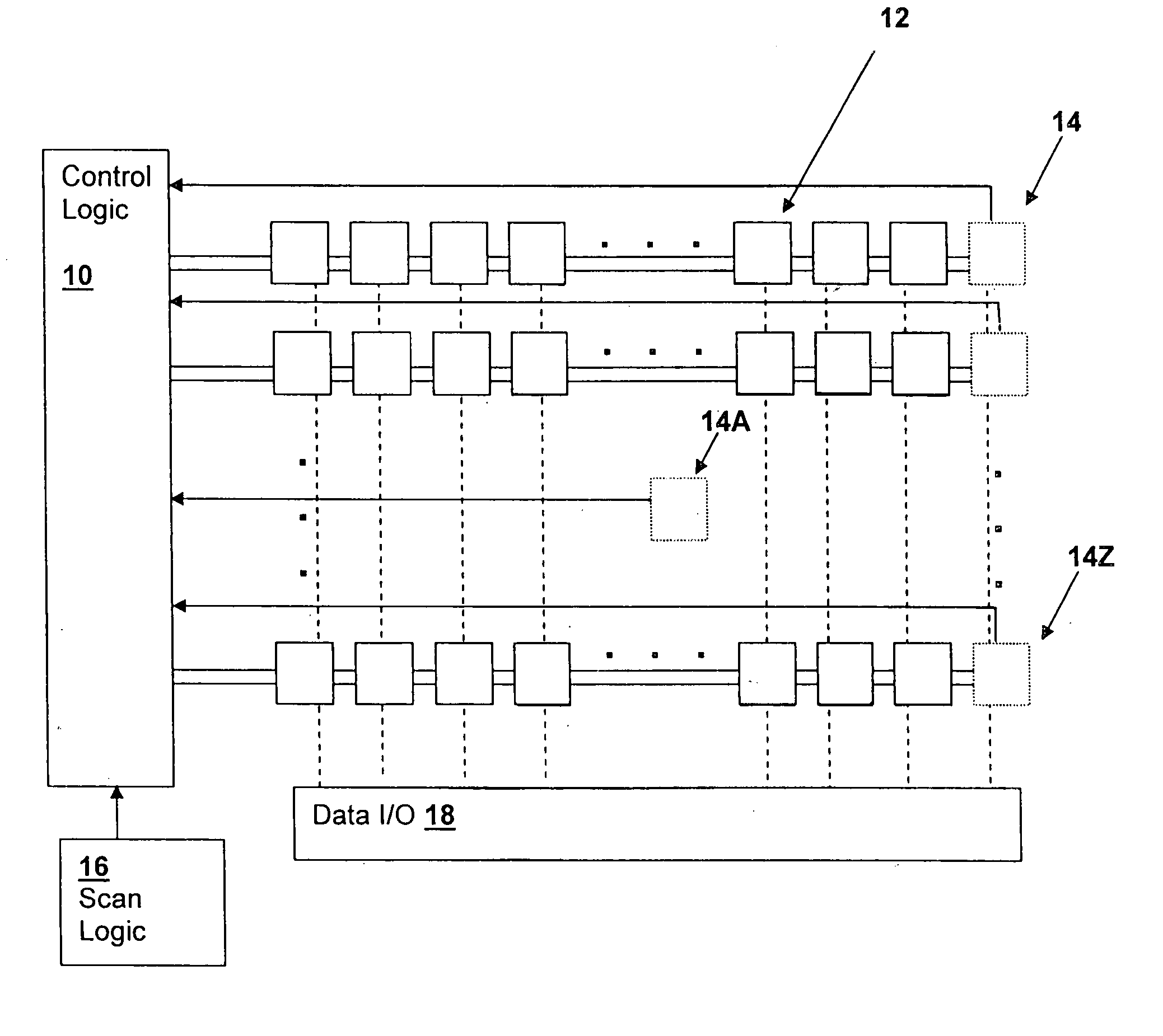

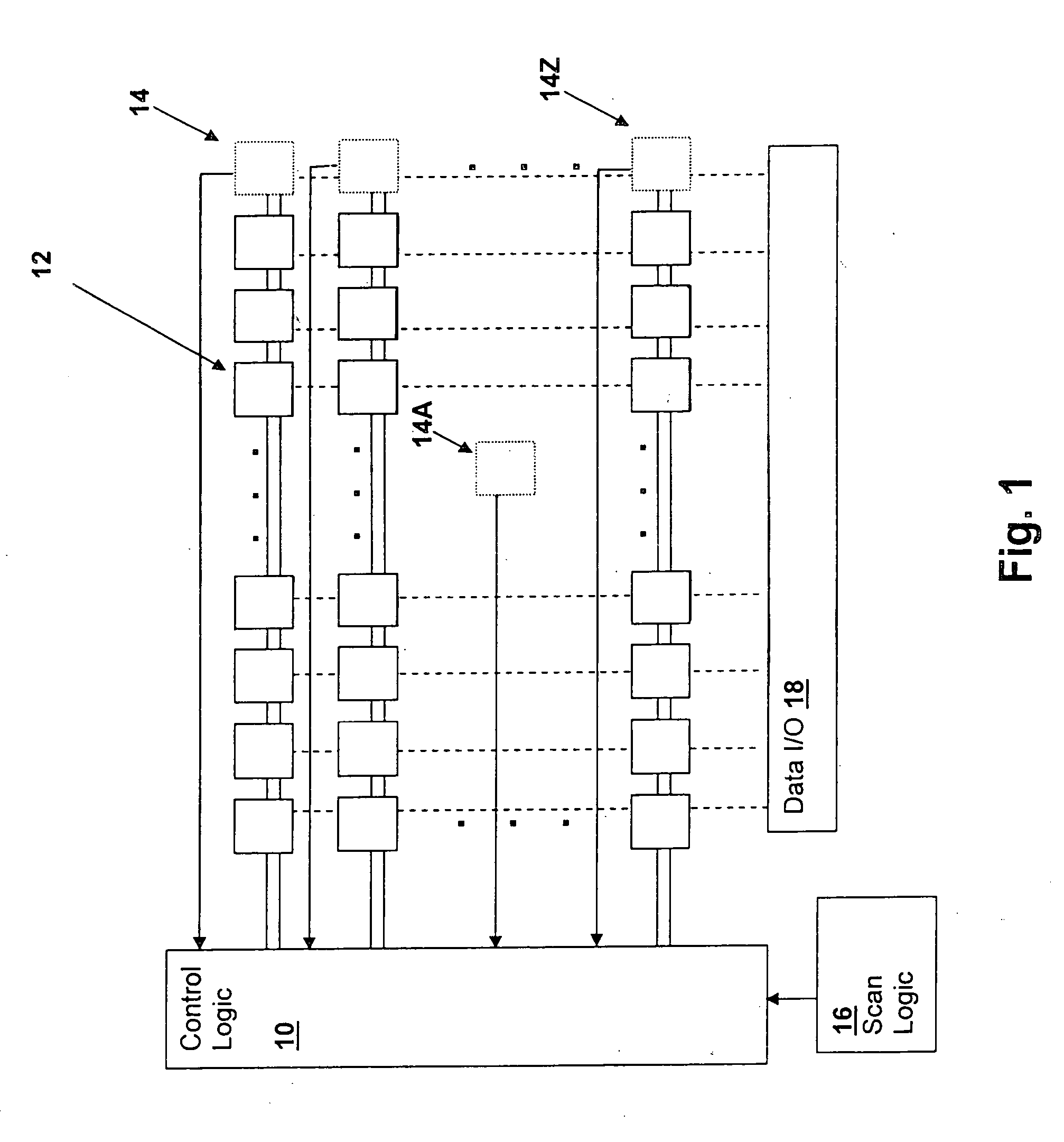

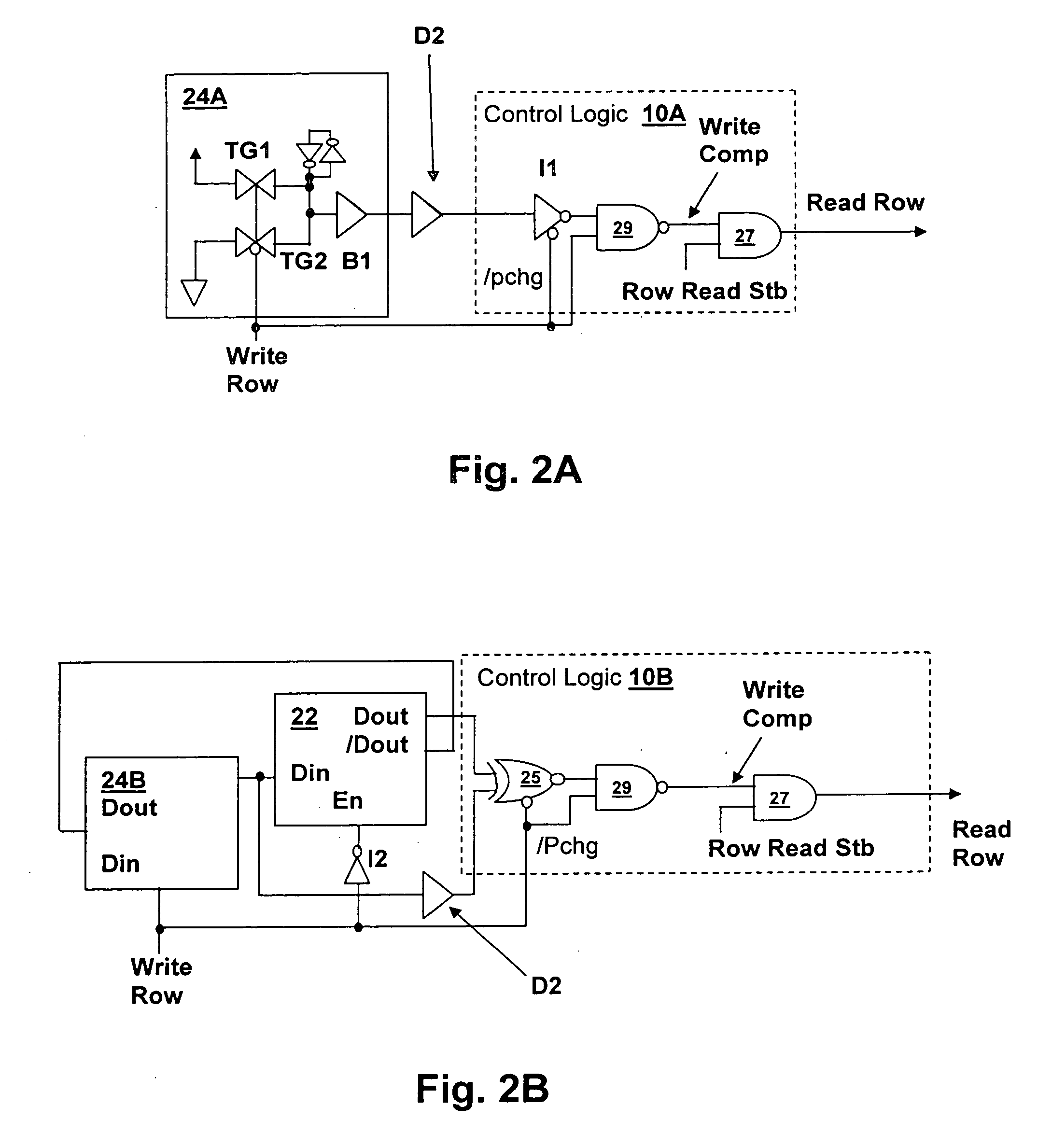

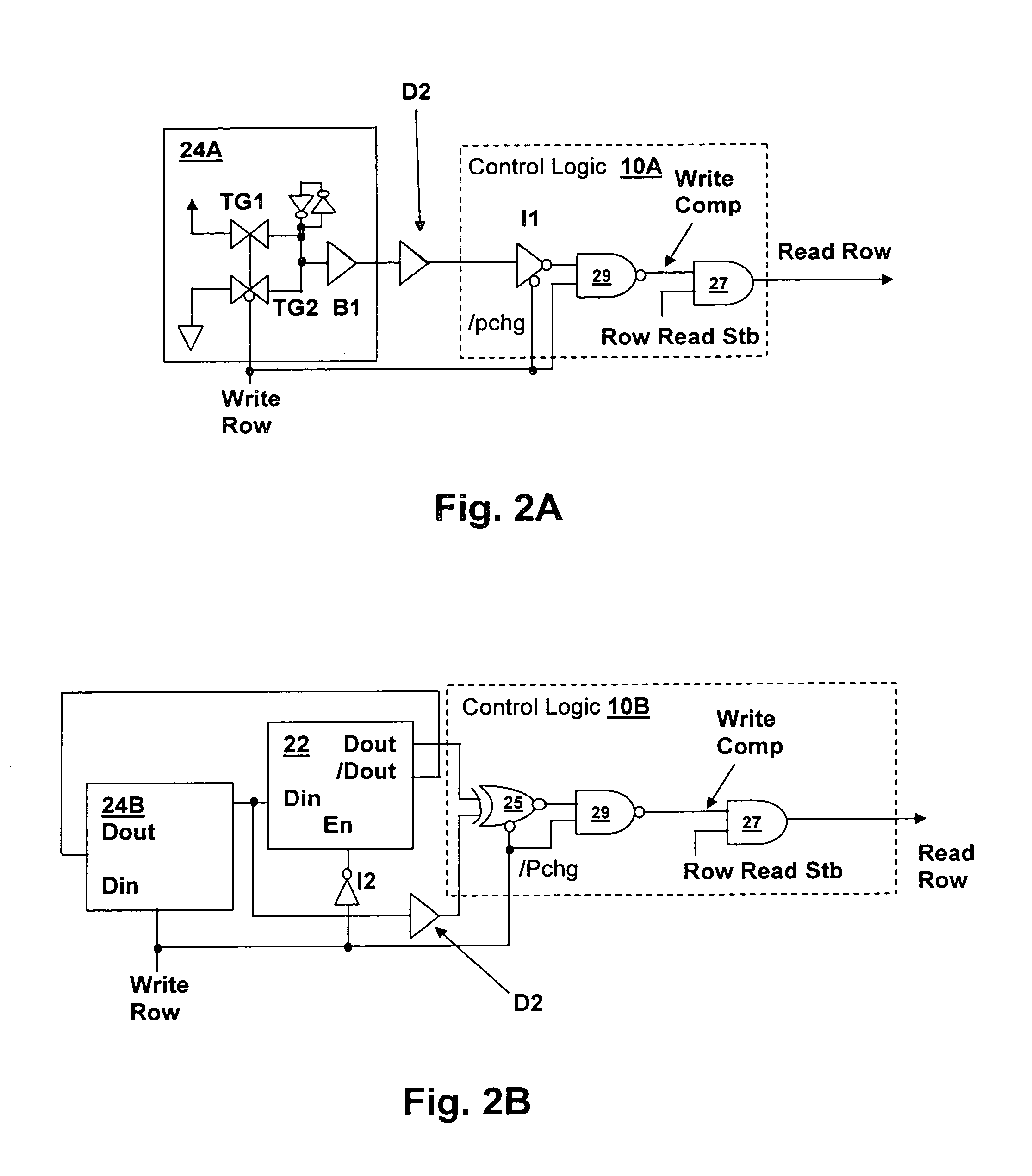

Register file apparatus and method incorporating read-after-write blocking using detection cells

A register file apparatus and method incorporating read-after-write blocking using detection cells provides improved read access times in high performance register files. One or more detection cells identical to the register file cells and located in the register file array are used to control the read operation in the register file by configuring the detection cells to either alternate value at each write or change to a particular value after a write and then detecting when the write has completed by detecting the state change of an active detection cell. The state change detection can be used to delay the leading edge of a read strobe or may be used in the access control logic to delay generation of a next read strobe. The register file thus provides a scalable design that does not have to be tuned for each application and that tracks over voltage and clock skew variation.

Owner:IBM CORP

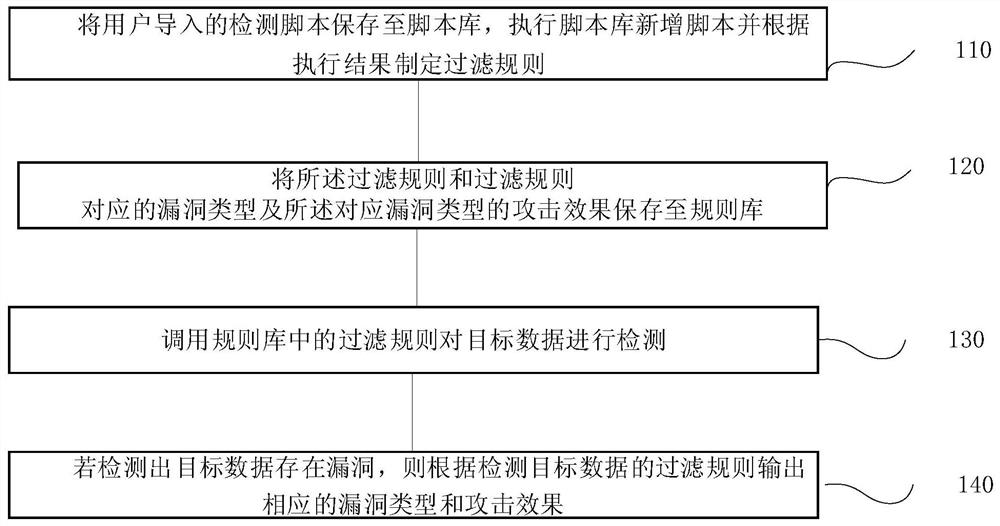

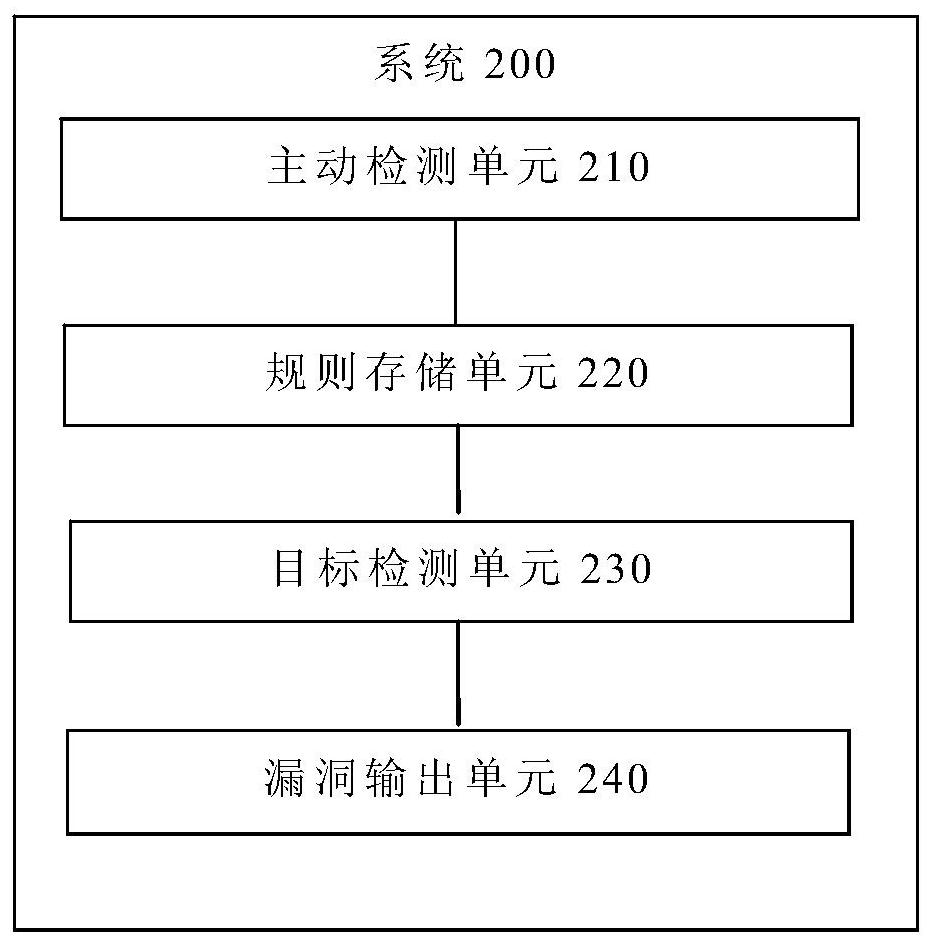

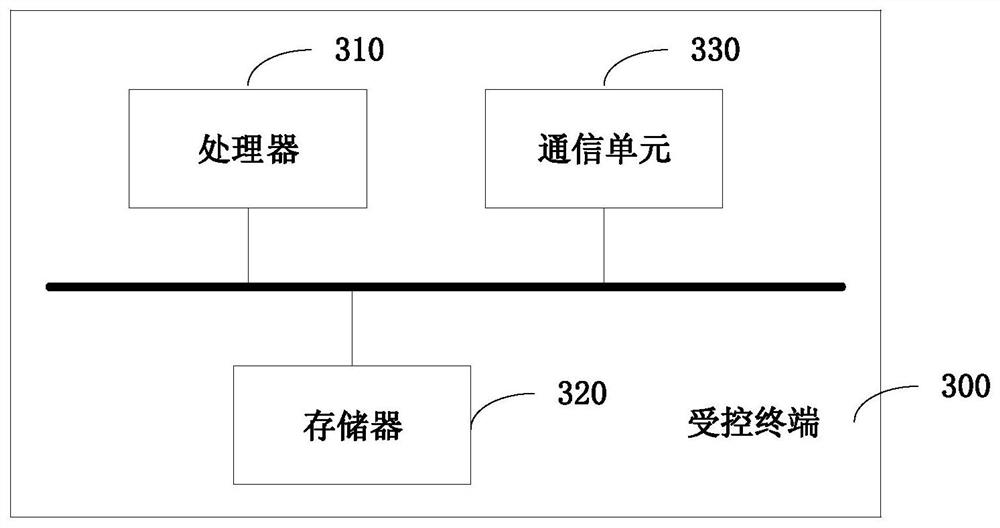

Extensible network security vulnerability monitoring method and system, terminal and storage medium

ActiveCN112738094AMake the most of vulnerability miningGive full play to the repair abilityTransmissionAttackFiltering rules

The invention provides an extensible network security vulnerability monitoring method and system, a terminal and a storage medium, and the method comprises the steps: storing a detection script imported by a user in a script library, executing a newly-added script of the script library, and formulating a filtering rule according to an execution result; storing the filtering rule, the vulnerability type corresponding to the filtering rule and the attack effect of the corresponding vulnerability type into a rule base; calling a filtering rule in the rule base to detect the target data; and if it is detected that the target data has the vulnerability, outputting a corresponding vulnerability type and an attack effect according to a filtering rule for detecting the target data. The invention is based on an active vulnerability detection model, extensible design is achieved, multi-language writing of vulnerability detection programs is supported, the method can be reused by similar vulnerabilities, autonomous early warning can be achieved after the vulnerabilities are found, and the vulnerability mining and repairing capacity of staff is brought into full play.

Owner:BINZHOU POWER SUPPLY COMPANY OF STATE GRID SHANDONG ELECTRIC POWER +1

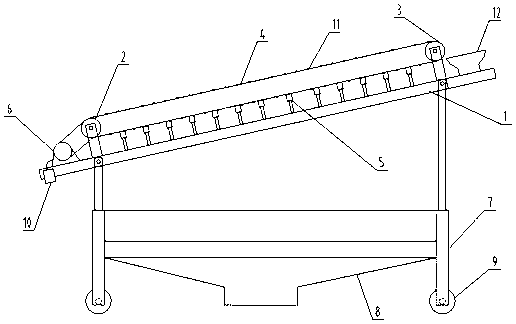

Food conveying device

PendingCN107934403AEfficient collectionCompact and reasonable structureConveyorsCleaningSlagEngineering

The invention relates to the technical field of conveying devices, in particular to a food conveying device. The food conveying device comprises a rack, a left roller, a right roller and a conveying belt; the left roller and the right roller are rotatably and fixedly mounted at the left and right ends of the rack correspondingly; at least one brush is fixedly mounted in the position, on the lowerportion of the conveying belt, of the rack; a motor capable of driving the left roller to rotate is fixedly mounted on the left side of the rack; four telescopic supporting legs are hinged to the bottom of the rack; and a residue receiving container corresponding to the conveying belt is detachably and fixedly mounted in the position, below the brushes, of the supporting legs. The food conveying device is compact and reasonable in structure; by arranging the residue receiving container and a residue receiving bowl, food residues falling from the conveying belt can be effectively collected, thesituation that the food residues fall onto a floor and consequently the factory environment is polluted is avoided, the time and labor are saved, and the situation of sweeping the floor frequently byworkers is no longer needed; through the design that the supporting legs are telescopic, the food conveying device can be adjusted to be in a horizontal conveying mode or an inclined conveying mode,so that using is more flexible, the functions are richer, and the production cost can be saved greatly.

Owner:湖州星座食品有限公司

Register file apparatus and method incorporating read-after-write blocking using detection cells

A register file apparatus and method incorporating read-after-write blocking using detection cells provides improved read access times in high performance register files. One or more detection cells identical to the register file cells and located in the register file array are used to control the read operation in the register file by configuring the detection cells to either alternate value at each write or change to a particular value after a write and then detecting when the write has completed by detecting the state change of an active detection cell. The state change detection can be used to delay the leading edge of a read strobe or may be used in the access control logic to delay generation of a next read strobe. The register file thus provides a scalable design that does not have to be tuned for each application and that tracks over voltage and clock skew variation.

Owner:IBM CORP

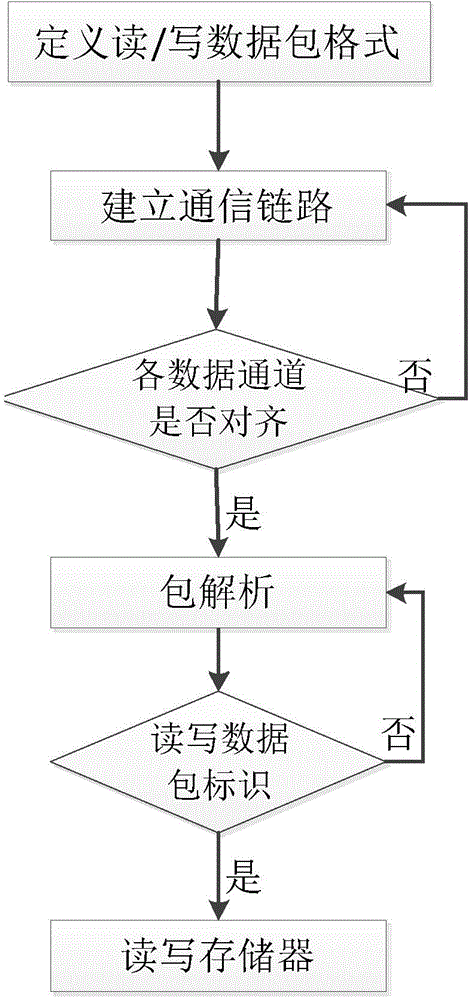

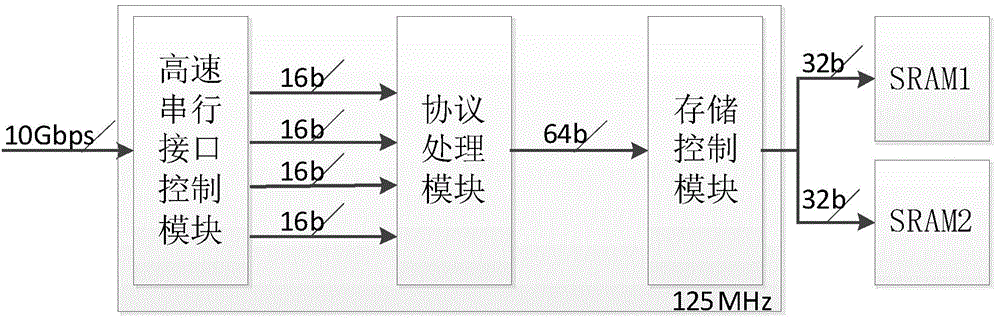

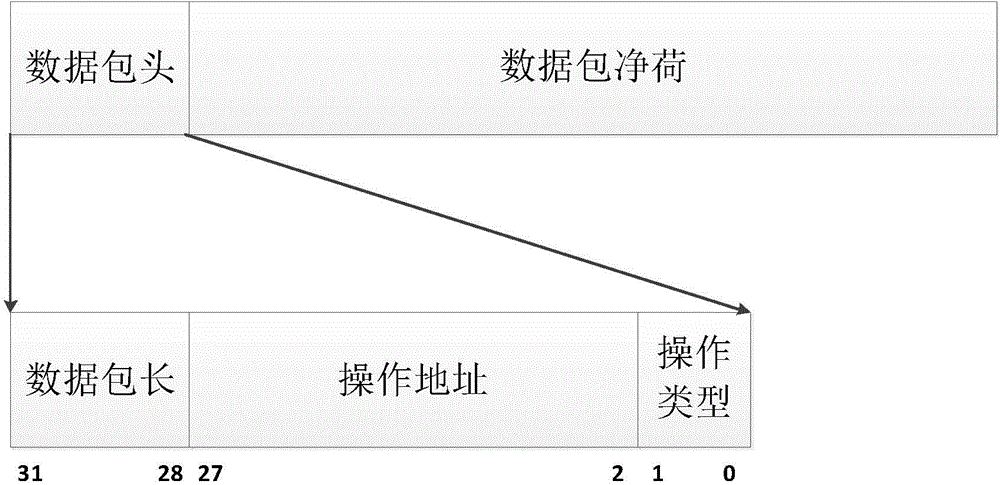

Method and device for controlling high-speed serial storage

ActiveCN104461963ALarge capacityHigh data reliabilityElectric digital data processingStatic random-access memoryTelecommunications link

The invention discloses a method and device for controlling high-speed serial storage. The method includes the steps of S1, defining a data package writing format and / or a data package reading format; S2, building a communication chain of a plurality of data channels, and aligning the multiple data channels; S3, analyzing a data package according to the defined data package writing format and / or the defined data package reading format; S4, carrying out writing / reading on a memory. The device comprises at least one high-speed serial channel, a high-speed serial interface control module, a protocol processing module and a storage control module. According to the method and device, due to protocol conversion and storage control, the perfect combination of the high throughput rate of a high-speed serial interface and rapid reading or rapid writing of a static random access memory is achieved, the extensible design of the number of the channels of the high-speed serial interface and the capacity of the static random access memory is achieved, then a storage body large in capacity, high in speed and high in intensity is built, and the method and device further have the advantages of being simple in interface and high in data reliability. The method and device can be widely applied to various high-speed serial storage control systems.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

Undersea free vehicle and components

ActiveUS9162740B2Easy to reconfigureMake up for deficienciesUnderwater vesselsUnderwater equipmentOcean bottomControl electronics

A free vehicle suitable to serve as a platform to carry a variety of equipment to the ocean floor, actuate devices at the floor and at intermediate points on the way to and returning from the ocean floor is described. The free vehicle includes standardized power, control electronics, navigation equipment and mechanical release mechanisms that can be used in conjunction with custom experiments. Exemplary experiments include sensors and sampling equipment used for deep-sea exploration. The free vehicle platform provides for scalable designs to meet scientific needs and surface vessel constraints.

Owner:HARDY KEVIN RICHARD +1

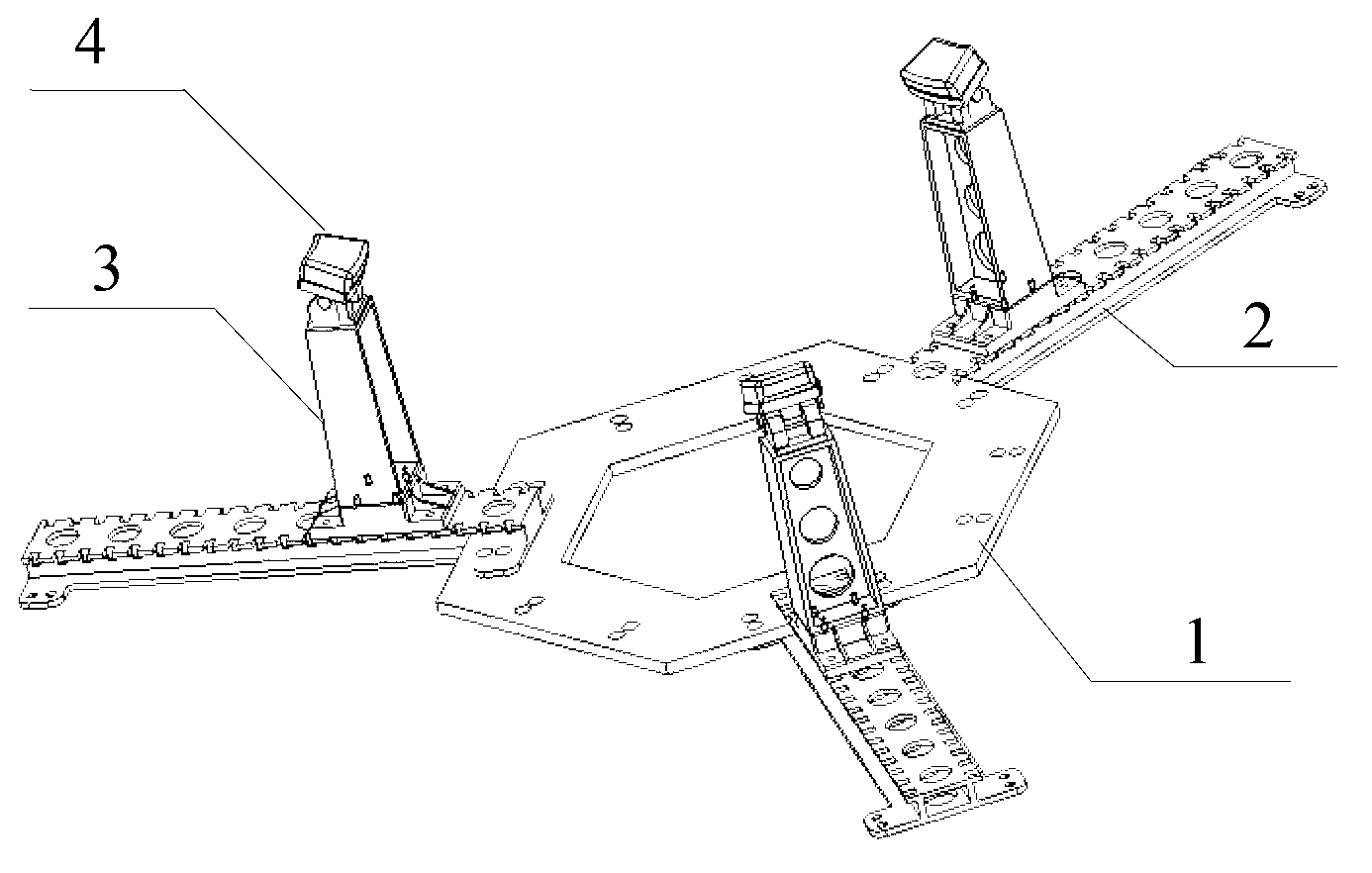

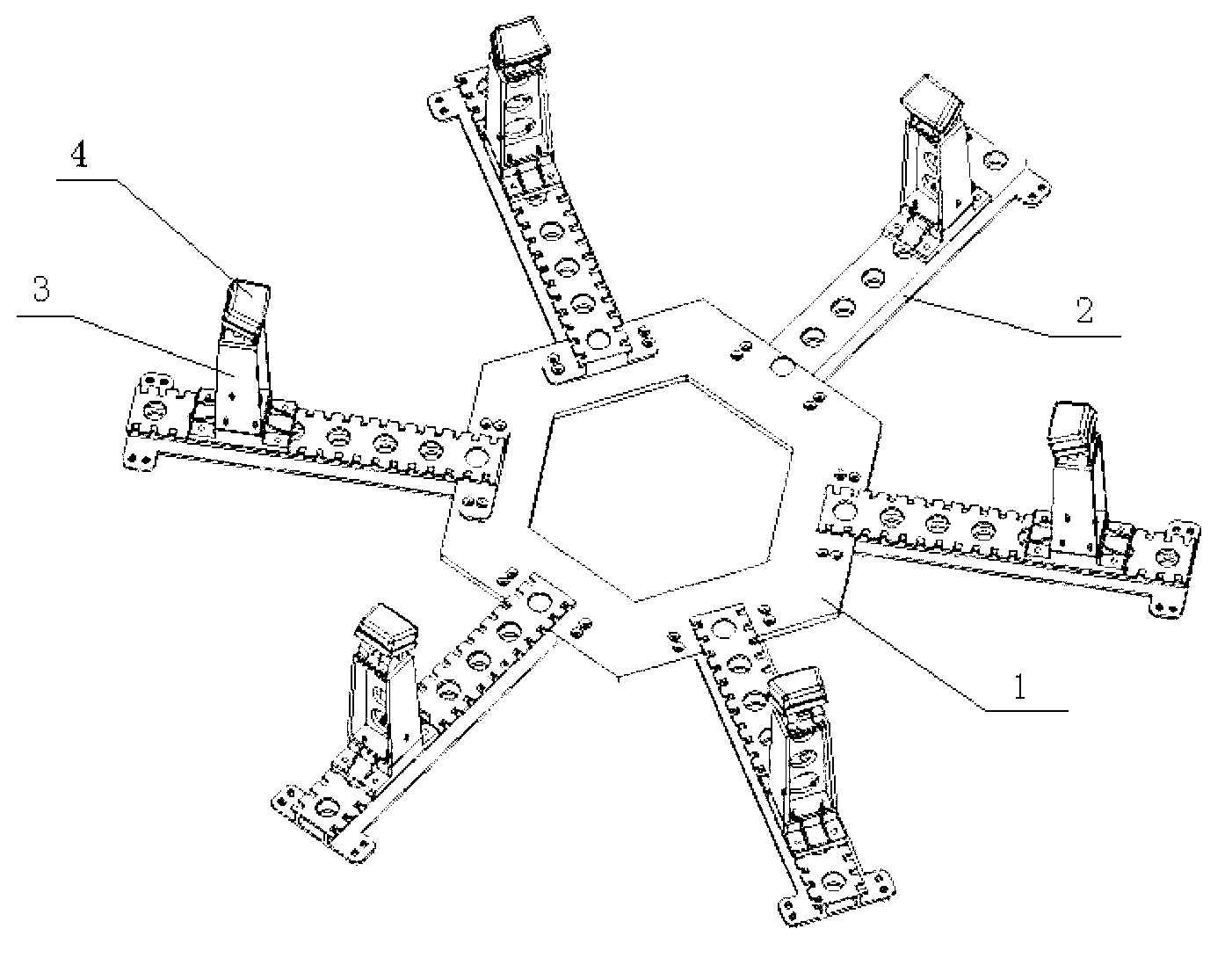

Expandable parking device for planet entering prober experiments

The invention discloses an expandable parking device for planet entering prober experiments. The expandable parking device is characterized by comprising a flange, cuboid guide rails, supports and supporting legs, wherein the flange provides mounting connectors for the guide rails, two sides of each guide rail are provided with positioning holes for providing mounting connectors for each support, the lower end of each support is vertically mounted on each guide rail, the upper end of each support is connected with each supporting leg, and the supporting legs mounted on the supports are adjustable in pitching direction and are in contact with a large conical bottom surface of a planet entering prober so as to serve as flexible supporting points. The expandable parking device for the planet entering prober experiments adopts the expandable design concept and is applicable to parking of planet entering probers different in diameter, half-cone angle and weight by adjusting corresponding components.

Owner:SHANGHAI SATELLITE ENG INST

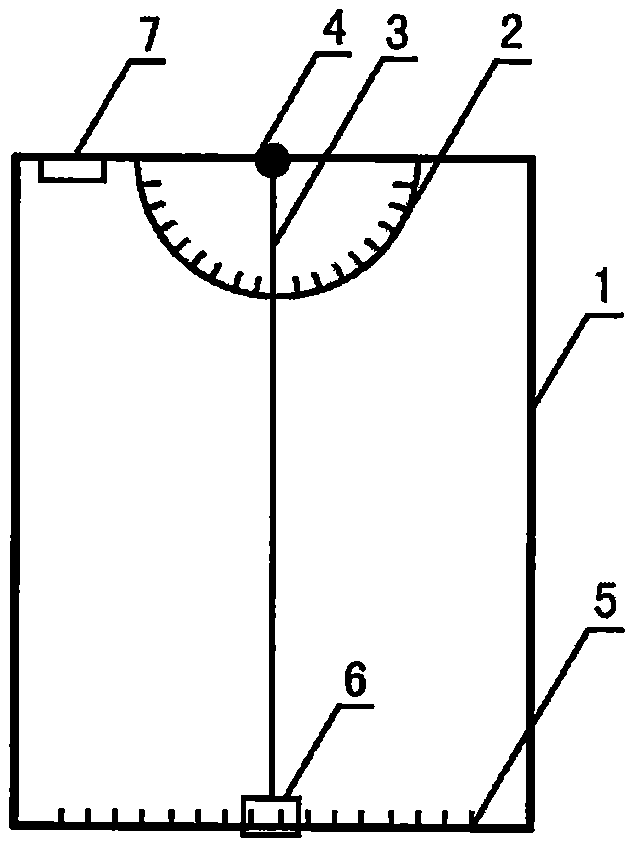

Multi-angle auxiliary drawing device

InactiveCN107192315AImprove practicalityImprove usage accuracyAngles/taper measurementsOther workshop equipmentVertical barProtractor

A multi-angle auxiliary traction device, comprising a frame (1), the frame is a fully transparent module design, a protractor (2) is arranged on one side of the frame, a vertical rod (3) is arranged in the middle of the protractor, and the vertical rod is on the When the angle is not set, it is vertically downward and has a retractable design; the top of the vertical rod is provided with a fixed module (4), which fixes one end of the vertical rod to the center point of the protractor; a scale is provided on the side opposite the protractor in the frame (5), limit the moving size of the vertical rod; set the buckle (6) at the end of the vertical rod against the scale, and fix it at the end of the scale after the vertical rod is selected; the level measuring instrument (7) is set above the frame, Keep it level when in use; the angle and size can be adjusted arbitrarily to assist traction, the transparent bottom design increases the practicality of the device, and the double-scale design improves the accuracy of use.

Owner:XINCHANG HONGYU IND PROD DESIGN

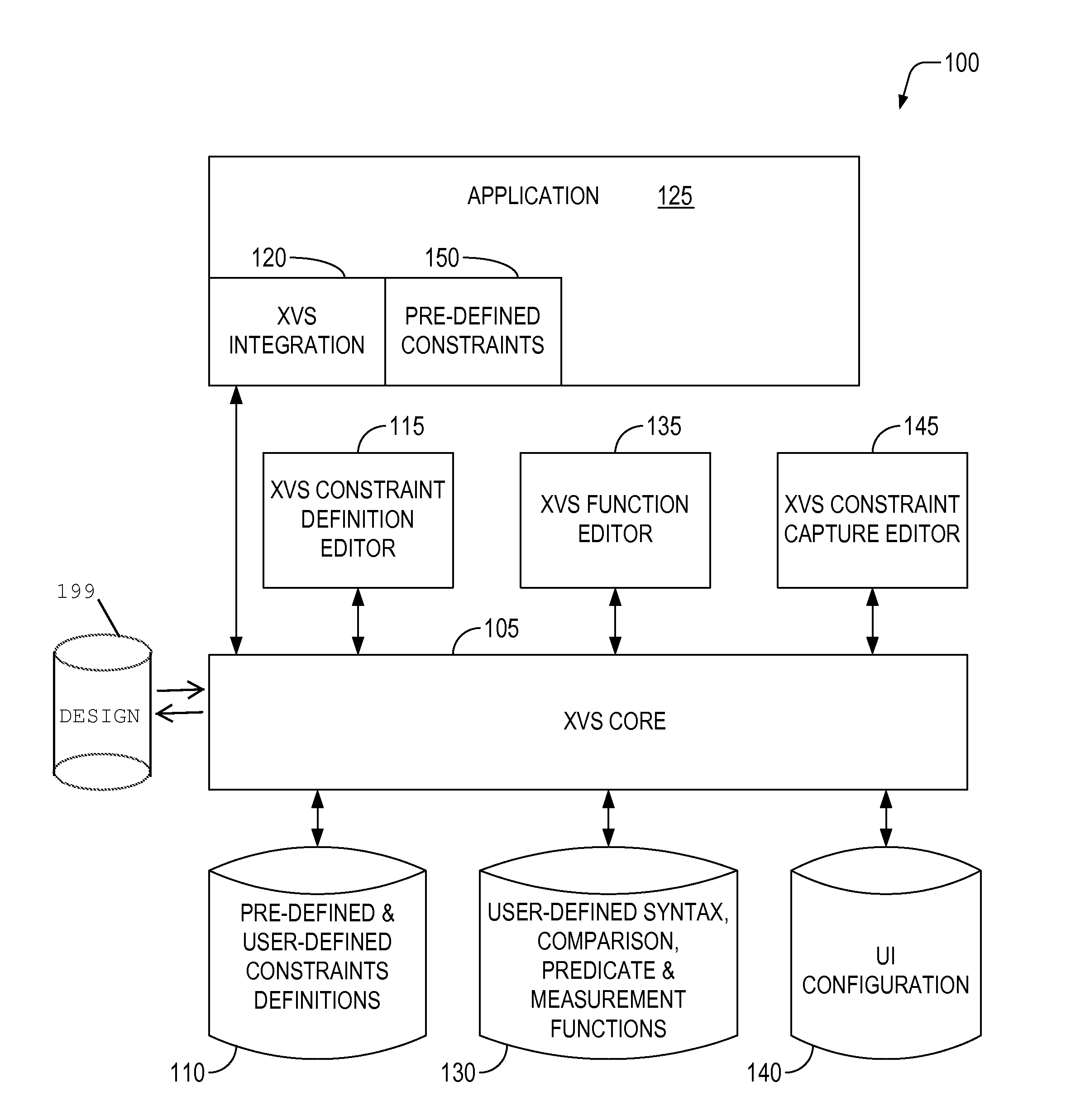

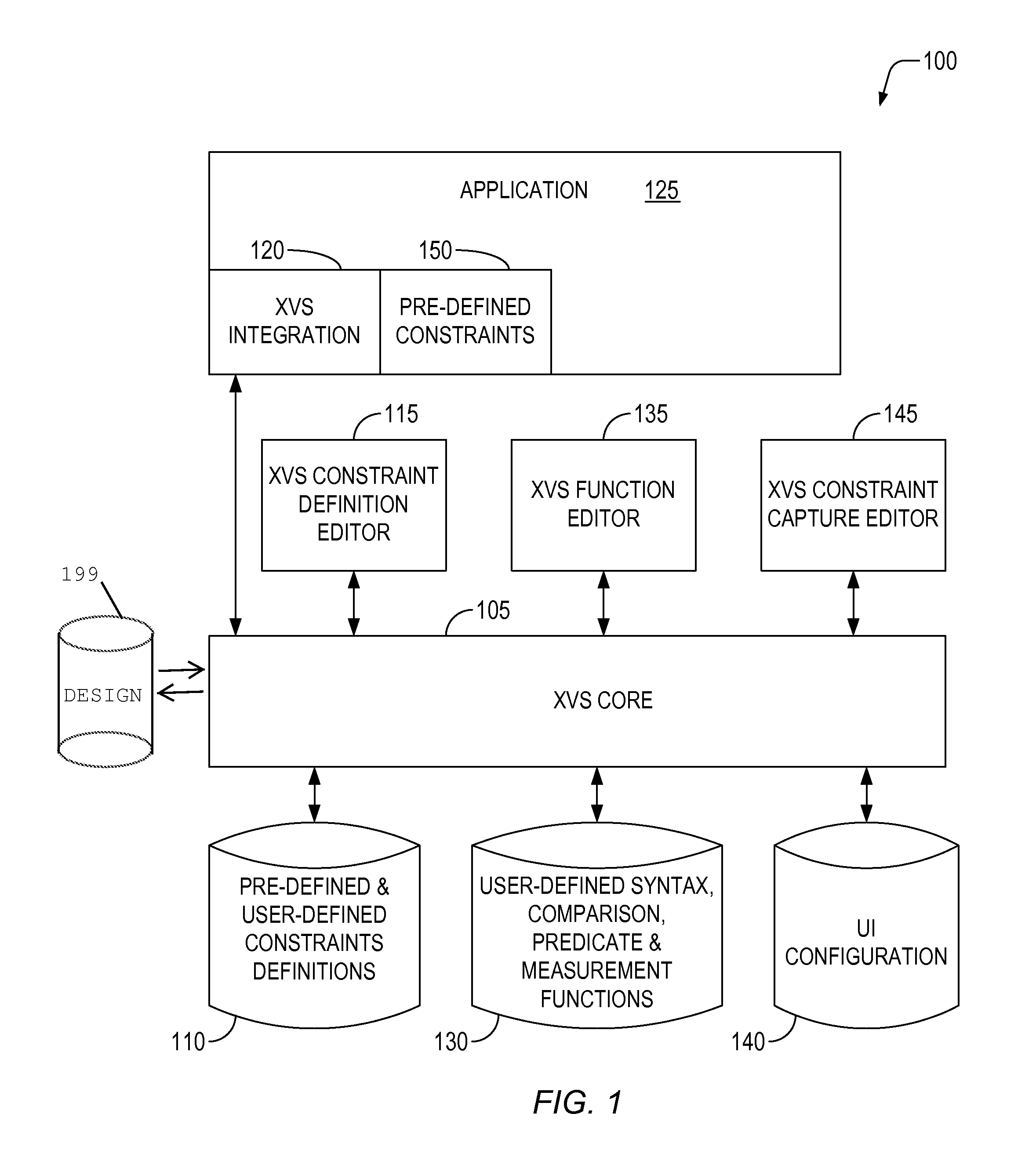

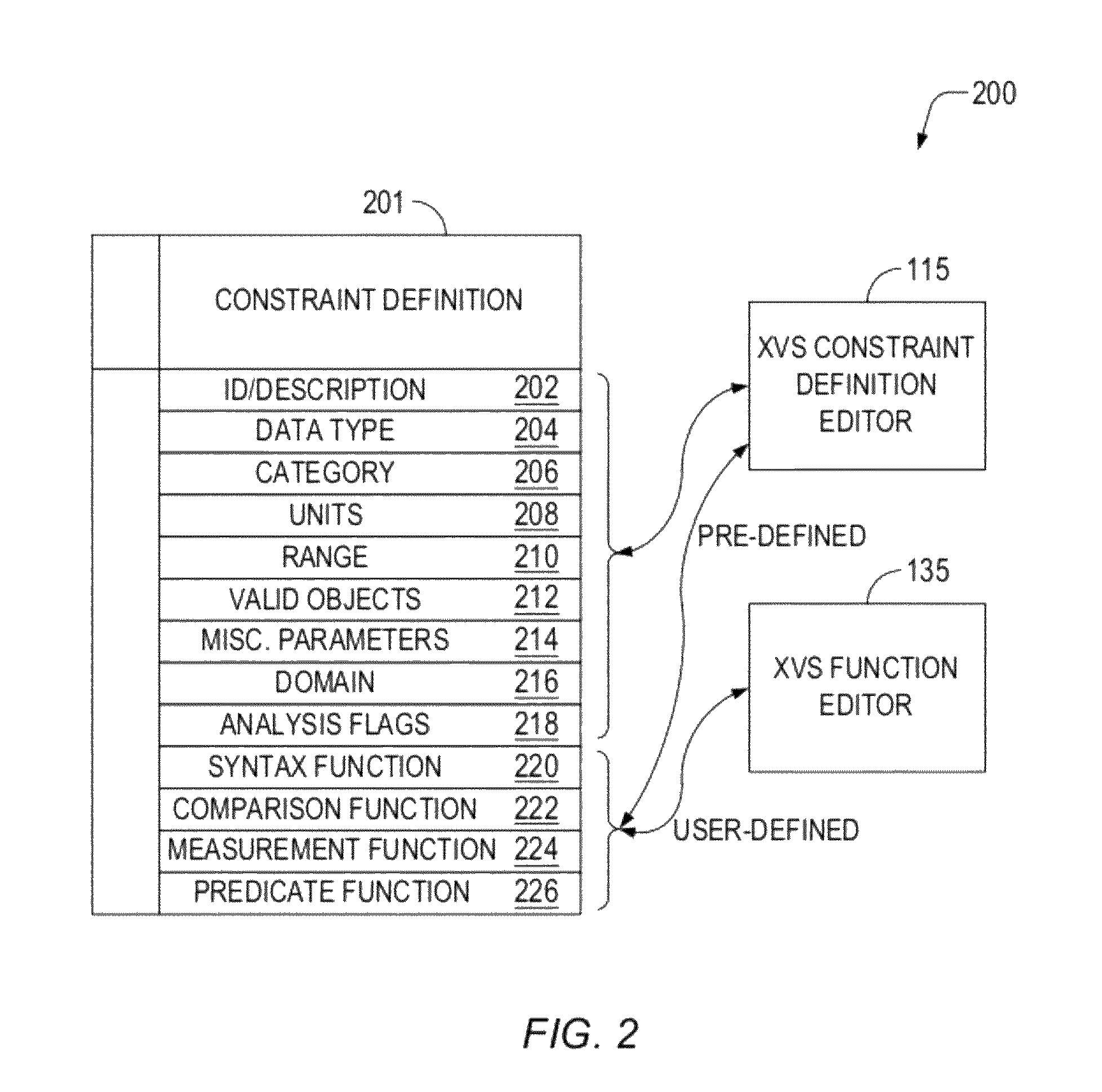

Extensible verification system

ActiveUS8209647B1Design optimisation/simulationConstraint-based CADApplication softwareVerification system

An extensible design verification system and methods thereof are disclosed. Pre-defined constraints from an integrated verification application are registered with a core which manages the verification system. The core is utilized by the integrated verification application to execute one or more verification tasks to generate a result. The result can be captured by a user interface. Constraints and the user-interface can be either pre-defined or user-defined. User-defined constraints and interface are managed in the same manner as those that are pre-defined. The user-defined constraints and interface are exportable for reuse by other designs.

Owner:CADENCE DESIGN SYST INC

Parallel plate type refrigerant storage device

A refrigerant storage device that arranges two end plates to form a cavity and includes a turbulator plate within the cavity. The turbulator plate is arranged within the cavity to reinforce the cavity by providing a plurality of reinforcement portions between the end plates. The cavity is sized and the turbulator plate is configured so a liquid portion of refrigerant flowing through the cavity collects onto the turbulator plate. The device has a rectangular shape that simplifies vehicle packaging and allows the device to be readily integrated into a plate-type refrigerant-to-liquid coolant heat exchanger. The device is formed by a stacking arrangement of parts that provides for a readily scalable design.

Owner:MAHLE INT GMBH

Active antenna related equipment, system and method for transmitting and receiving calibration

ActiveCN103997352BConsistent performanceReduce the difficulty of implementationTransmitters monitoringReceivers monitoringTransceiverEngineering

The invention discloses an active antenna related device, a system and a sending and receiving calibration method, which are used to realize the scalable design of the antenna array, reduce the difficulty of engineering implementation and provide engineering implementation reliability. The active antenna device includes: N active antenna arrays, a main calibration coupling circuit unit, a transceiver calibration unit, a calibration parameter storage unit, and an optical radio communication ROF photoelectric conversion unit, wherein the N is greater than 1; the active antenna array At least including an antenna coupling circuit unit and M antenna elements connected to the antenna coupling circuit unit, where M is greater than 1; the antenna calibration coupling circuit unit of the active antenna array is connected to the main calibration coupling circuit through a calibration channel unit, the main calibration coupling circuit is connected to the transceiver calibration unit, and the transceiver calibration unit and the calibration parameter storage unit are respectively connected to the ROF photoelectric conversion unit.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD +1

Highly-decoupled method capable of dynamically managing crawlers

ActiveCN112818198AReduce complexityImprove robustnessWeb data indexingFile/folder operationsMessage queueDynamic management

The invention discloses a highly-decoupled method capable of dynamically managing a crawler, which comprises the following steps that: the crawler is divided into two stages of data analysis and new target generation, rules of the two stages corresponding to a collection target are compiled into json data according to a protocol, and the json data are stored into a host end; the host runs a task and sends the task to a client with sufficient resources through a message queue module according to a resource scheduling algorithm, the client receives task information, converts the task information into executable information through the crawler protocol core, runs the executable information through a crawler running module, and finally obtains data; the host end obtains data and a new task, and stores and updates a task pool; and the host end is separated from a crawler server, so that the coupling of the system can be reduced. Therefore, after the functions of the crawler are separated, the complexity of the crawler server can be reduced, and the host end can be modified while the distributed crawler system runs so as to achieve the purpose of specific control management, so that the whole module is subjected to decoupling and extensible design, and the robustness and stability of the whole framework are enhanced.

Owner:苏州市中地行信息技术有限公司

A highly decoupled method for dynamically managing reptiles

ActiveCN112818198BReduce complexityImprove robustnessWeb data indexingFile/folder operationsMessage queueDynamic management

The invention discloses a highly decoupled and dynamically managed crawler method. The method divides the crawler into two stages: data analysis and new target generation, and writes the rules corresponding to the two stages of acquisition targets into json data and stores them in the host computer according to the protocol. end; the host end runs the task, sends it to the client with sufficient resources through the message queue module according to the resource scheduling algorithm, and the client receives the task information, converts it into executable information through the crawler protocol core and runs it by the crawler running module, and finally obtains the data; The host end obtains data and new tasks, stores and updates the task pool; separating the host end from the crawler server can reduce the coupling of the system. Therefore, after the crawler function is separated, the complexity of the crawler server can be reduced, and the host side can be modified while the distributed crawler system is running to achieve specific control and management purposes, thereby decoupling and extensible the entire module Design to enhance the robustness and stability of the entire framework.

Owner:苏州市中地行信息技术有限公司

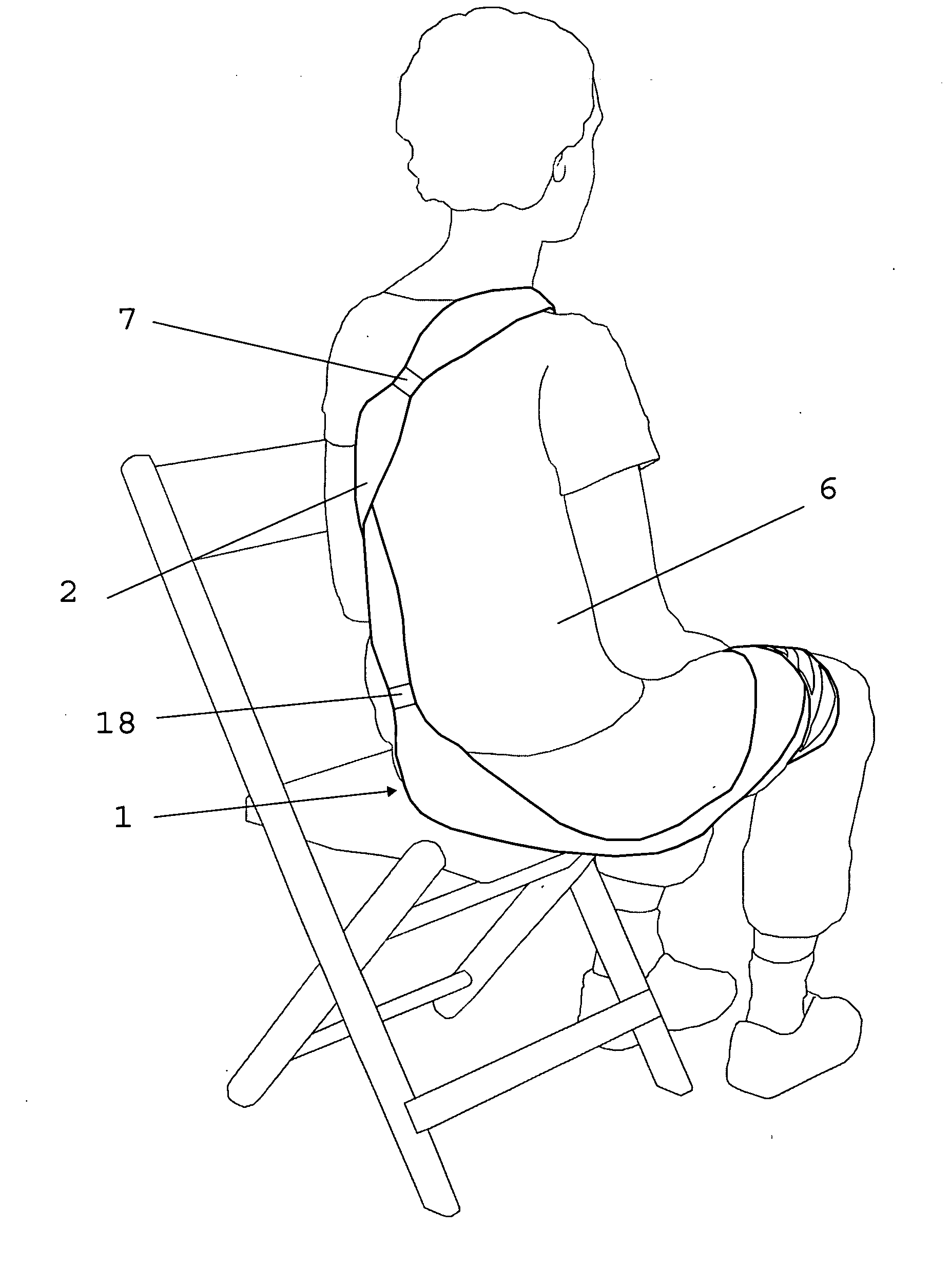

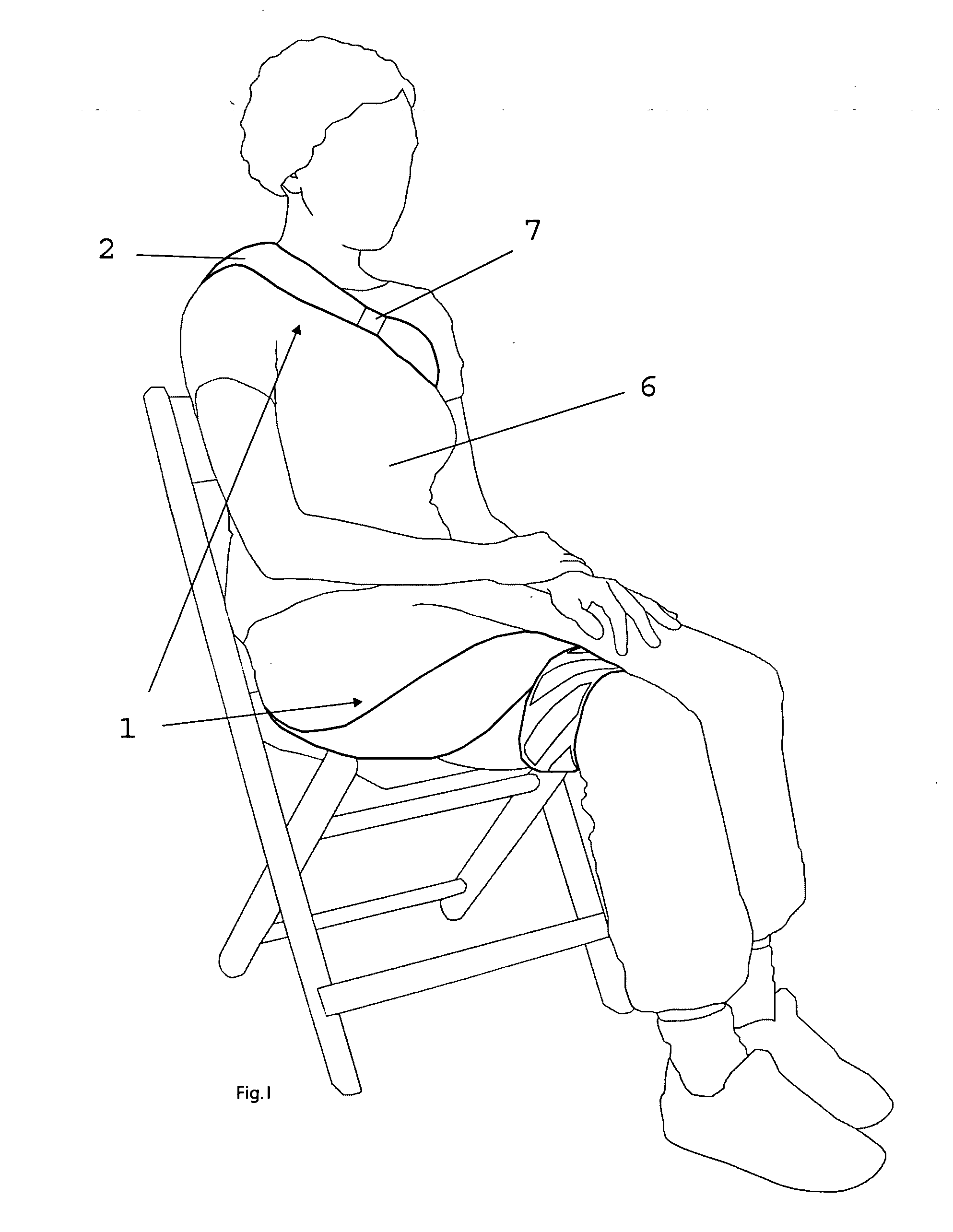

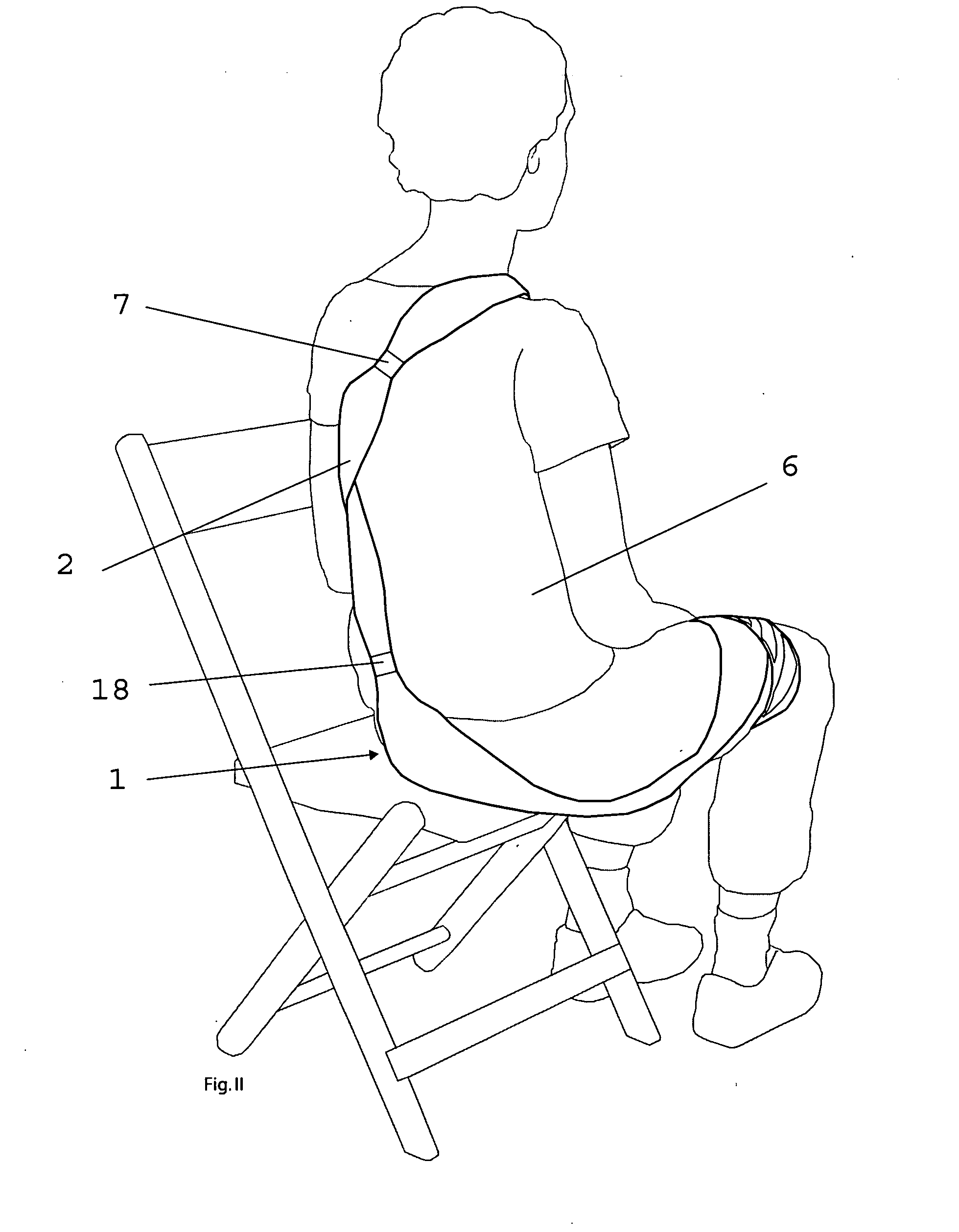

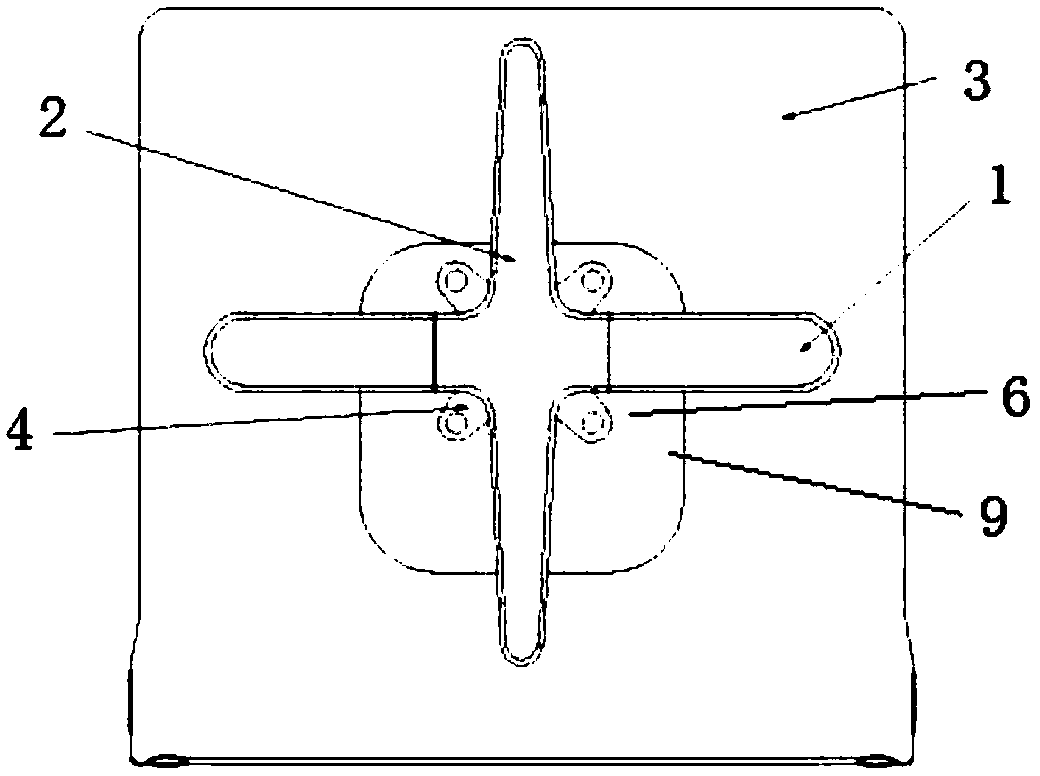

Wrap-around support sling

InactiveUS20100198123A1Quickly and easily securedEasy to storeRestraining devicesNursing bedsWhole bodyStanding Positions

The present invention is a wrap-around support sling which comprises a reinforced elongate fabric strap that wraps around the patient's upper torso (over one shoulder and under the other arm) and is secured thereabout in a loop by hook and loop fasteners. The sling continues down the back and is wrapped around the patient's leg, where it is secured in a loop around the leg by hook and loop fasteners. The sling gives full body support, and may be gripped in both hands by an attending via integral handles positioned at the sternum and lumbar region to readily lift the patient out of a chair to a standing position without stress or risk of injury to either the patient or attending. The sling is rugged and possesses a simple and scalable design and may be economically manufactured and sold to provide for widespread use and disposability.

Owner:SEFF KIMBERLY

Telescopic spray arm for dish washing machine and dish washing machine

PendingCN107550430AIncrease the areaSolve the problem of unclean corner cleaningTableware washing/rinsing machine detailsWater dischargeEngineering

The invention relates to a telescopic spray arm for a dish washing machine and the dish washing machine. The telescopic spray arm comprises a fixed part, a movable part, a spray arm base and a guidingdevice, the fixed part and the movable part are both provided with water-spouts which are communicated with a spray arm frame through a waterway, the spray arm base is located on an inner container bottom shell, the movable part is movably arranged on the fixed part in a sleeving mode, the guiding frame is arranged on the spray arm base, one end of the guiding device is connected to the movable part, and the other end of the guiding device is connected with the guiding frame and move in the guiding frame, so that limitation of displacement distance is achieved when the movable part moves along the fixed part in a telescopic mode. The telescopic spray arm has the advantages that by means of the design of the telescopic spray arm, when the spray arm rotates around a center shaft, the telescopic spray arm can be elongated when the spray arm frame rotates to the four corners under the guiding effect of the guiding frame on the spray arm base, the spray arm spray area is increased, and theproblem that the four corners of the dish washing machine are not cleaned completely is solved.

Owner:HANGZHOU ROBAM APPLIANCES CO LTD