Thin film transistor array substrate, manufacturing method and liquid crystal display panel

A technology of thin film transistors and array substrates, applied in the field of liquid crystal display, capable of solving problems such as affecting the driving capability of thin film transistors 14, affecting the display effect of the screen, and large signal delay, so as to improve the display effect of the screen, reduce the layout area, and reduce the capacitive load. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

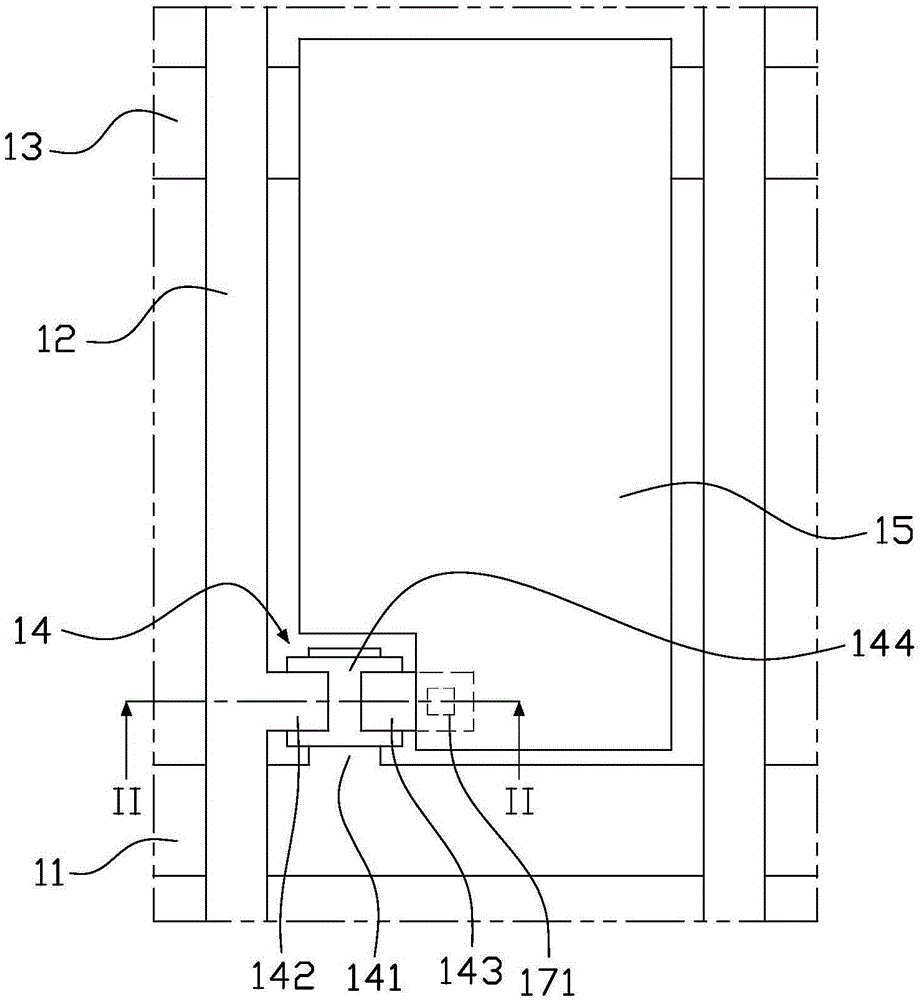

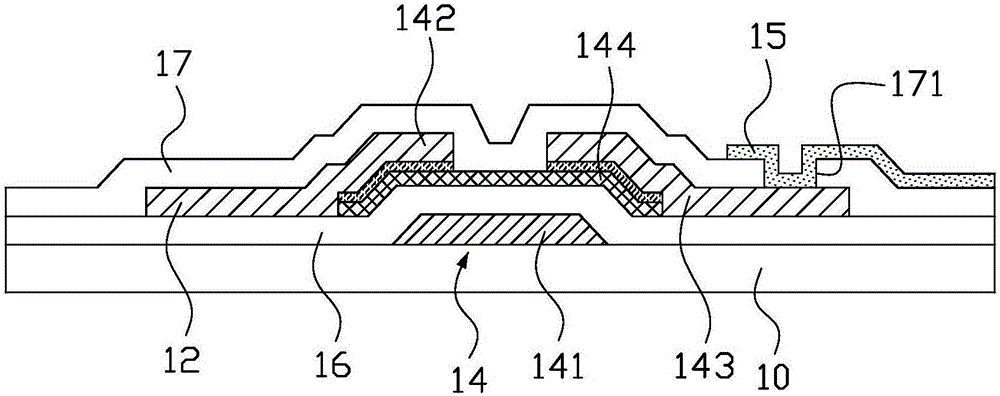

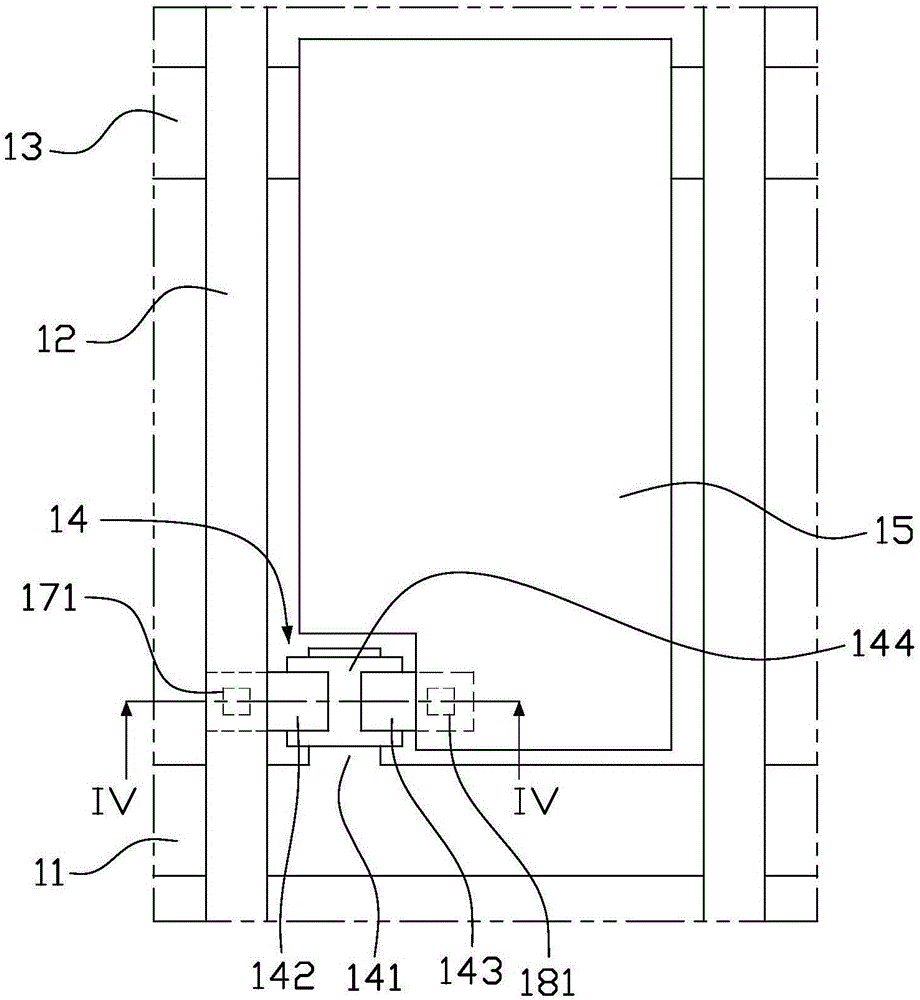

[0047] image 3 is a partial schematic diagram of the thin film transistor array substrate in the first embodiment of the present invention, Figure 4 for image 3 Schematic cross-section along the IV-IV direction, such as Figure 3-4 As shown, the thin film transistor array substrate provided in this embodiment includes a substrate 10, a first metal layer formed on the substrate 10, a first insulating layer 16 covering the first metal layer, and a first insulating layer 16 formed on the first insulating layer 16. The active layer 144 on the top, the second metal layer formed on the first insulating layer 16, the second insulating layer 17 covering the second metal layer, the third metal layer formed on the second insulating layer 17, covering The third insulating layer 18 on the third metal layer, and the pixel electrode 15 formed on the third insulating layer 18 .

[0048] The first metal layer includes scan lines 11 and gates 141 ; the second metal layer includes source ...

no. 2 example

[0071] Figure 7 It is a schematic cross-sectional view of a thin film transistor array substrate in the second embodiment of the present invention. The structure and manufacturing method of this embodiment are basically the same as those of the above-mentioned first embodiment. The fourth insulating layer 19 of 15, and the common electrode 20 (common electrode) is fabricated on the fourth insulating layer 19, so that the above-mentioned array substrate can be used as an array substrate of a fringe field switching mode (Fringe Field Switching, FFS) liquid crystal display panel.

no. 3 example

[0073] Figure 8 It is a schematic cross-sectional view of the thin film transistor array substrate in the third embodiment of the present invention. The structure and manufacturing method of this embodiment are basically the same as those of the first embodiment above. A common electrode 20 (common electrode) is formed on the layer 18, wherein the pixel electrode 15 and the common electrode 20 are comb-shaped structures and are inserted into each other in the same layer, so that the above-mentioned array substrate can be used as an in-plane switch mode (In-Plane Switch , IPS) the array substrate of the liquid crystal display panel.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More