Inverter of grid integrated driving circuit, grid integrated driver and driving method

A gate integrated drive and gate drive circuit technology, applied in instruments, static indicators, etc., can solve the problems of large DC loop, increased circuit noise, and large dynamic power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

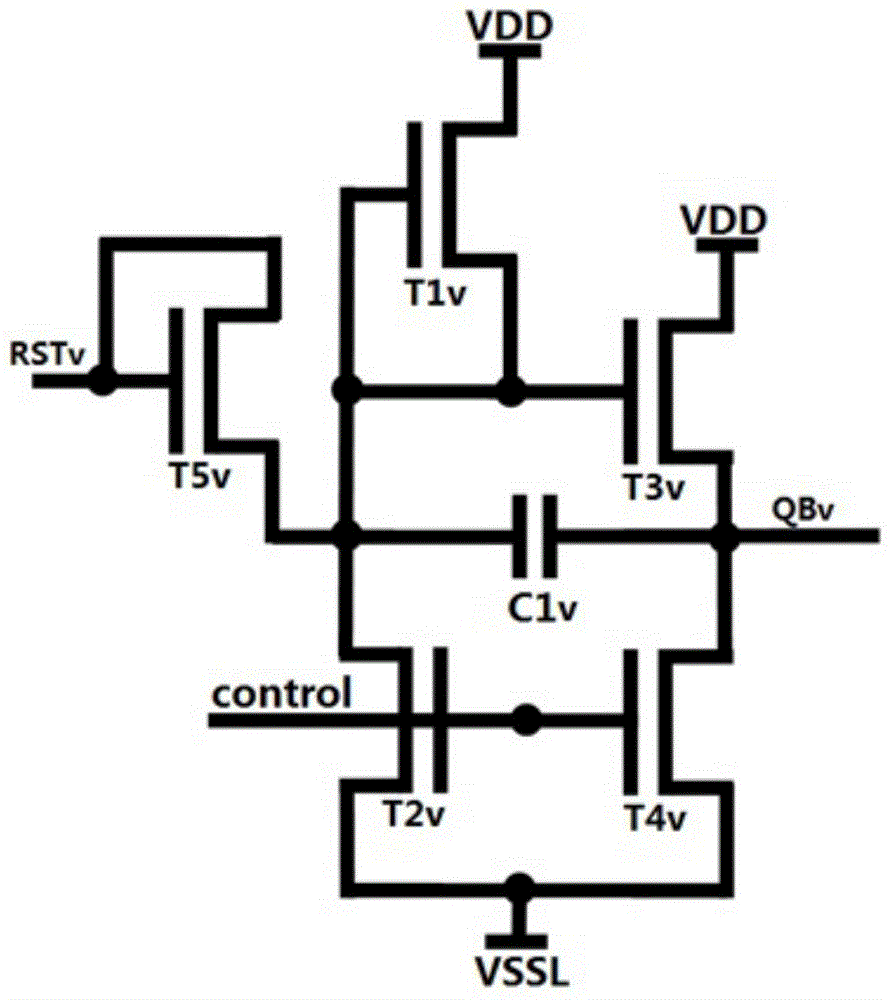

[0046] Such as figure 1 As shown, the inverter of the gate integrated drive circuit of this embodiment includes transistors T1v, T2v, T3v, T4v, T5v and coupling capacitor C1v, the drain of transistor T1v and the drain of T3v are connected to positive level VDD, The gate and source of the transistor T1v are connected to the drain of the transistor T2v, the gate of the transistor T3v, the source of the transistor T5v and one end of the capacitor C1v; the gate of the transistor T2v and the gate of the transistor T4v are connected to the control signal control, and the transistor T5v The gate and drain of the transistor are connected to the feedback signal RSTv, the source of the transistor T2v and the source of the transistor T4v are connected to the first negative level VSSL, and the drains of the transistors T3v and T4v are connected to the other end of the capacitor C1v to form an inverter output node QBv .

[0047] The transistors are all N-type depletion thin film transisto...

Embodiment 2

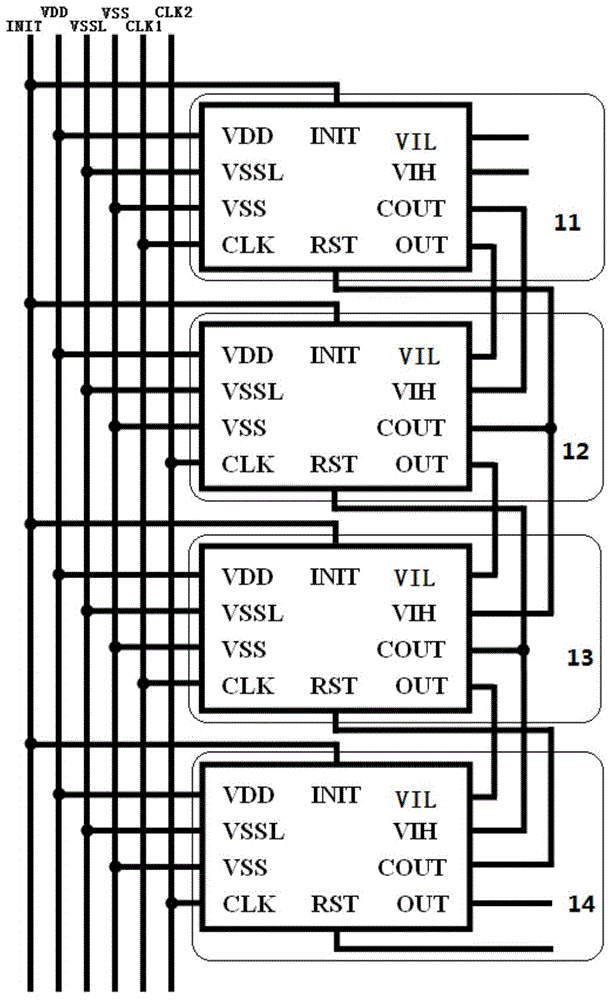

[0051] Such as figure 2 As shown, the gate integrated driver of this embodiment includes multi-level gate drive circuit units: a first-level gate drive circuit unit 11, a second-level gate drive circuit unit 12, and a third-level gate drive circuit unit 13 , the gate drive circuit unit 14 of the fourth stage, the gate drive circuit unit of each stage includes two input terminals VINH and VINL, three power supply terminals VDD, VSSL and VSS, wherein the voltage of VSSL is more negative than VSS, and a clock signal The input terminal CLK, the highest level of the clock signal is VDD, the lowest level is VSSL, two output terminals COUT and OUT, an initialization terminal INIT and a feedback terminal RST.

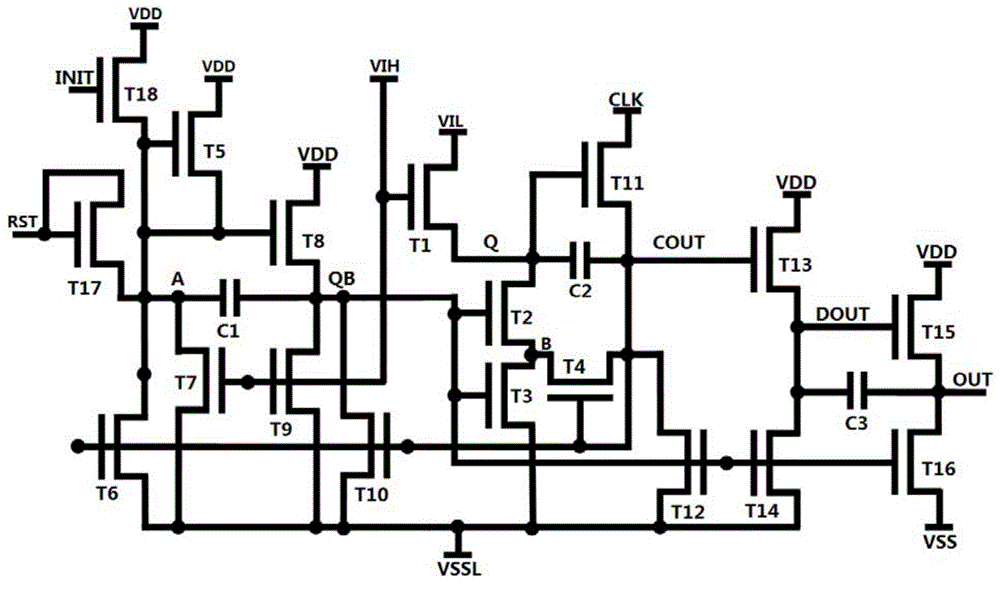

[0052] Such as image 3 As shown, each gate drive circuit unit includes transistors T1~T18 and coupling capacitors C1~C3, an input control signal VIH, an input signal VIL, a clock signal CLK, a feedback signal RST, an initialization signal INIT, the first The output signal C...

Embodiment 3

[0068] Compared with the embodiment 2, the integrated gate driving circuit of this embodiment removes the eighteenth transistor and omits the initialization process. Due to the new inverter module circuit used in the gate drive circuit, the QB point can automatically maintain a stable voltage slightly lower than VDD even if there is no initialization process. Therefore, the output signal of the circuit can still be maintained in the absence of input. stable low level.

[0069] Such as Figure 5 As shown, the integrated gate drive circuit of this embodiment includes multi-stage gate drive circuit units; the first output signal COUT of the gate drive circuit unit of this stage is used as the input control signal VIH and the upper gate drive circuit unit of the next stage. The feedback signal RST of the first-stage gate drive circuit unit, the second output signal OUT is used as the drive signal of the scanning line and the input signal VIL of the next-stage gate drive circuit u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More