Successive-approximation type digital-analog converter with feedback advanced setting, and corresponding Delta-Sigma ADC configuration

A digital-to-analog converter, successive approximation technology, applied in analog conversion, analog/digital conversion, code conversion, etc., can solve the problems of excessive conversion time, underutilization of low power consumption of SAR, affecting conversion rate, etc. The effect of building difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

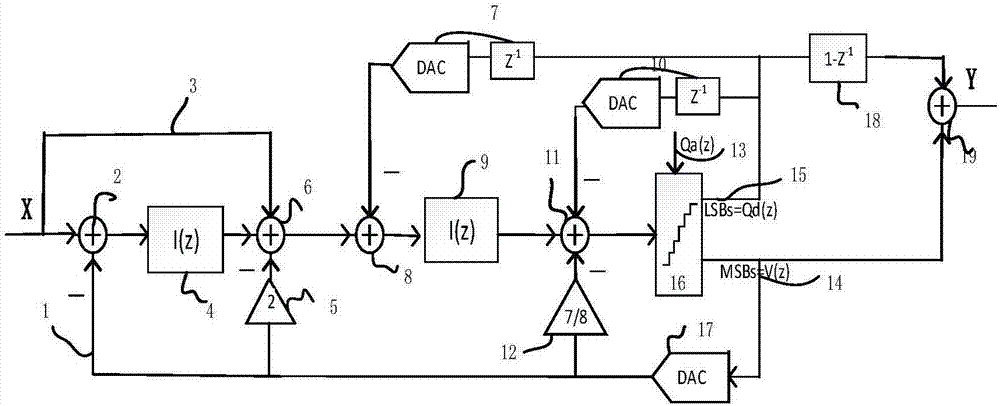

[0027]Embodiments of the present invention provide a novel continuous-time Delta-Sigma ADC architecture, such as figure 1 As shown, it mainly includes: the first summation node (2), the first stage integrator (4), the 2 times amplifier (5), the second summation node (6), the first summation node composed of the delay unit and DAC A delay and digital-to-analog conversion module (7), a third summing node (8), a first-stage integrator (9), a second de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More