Patents

Literature

130results about How to "Fast programming" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

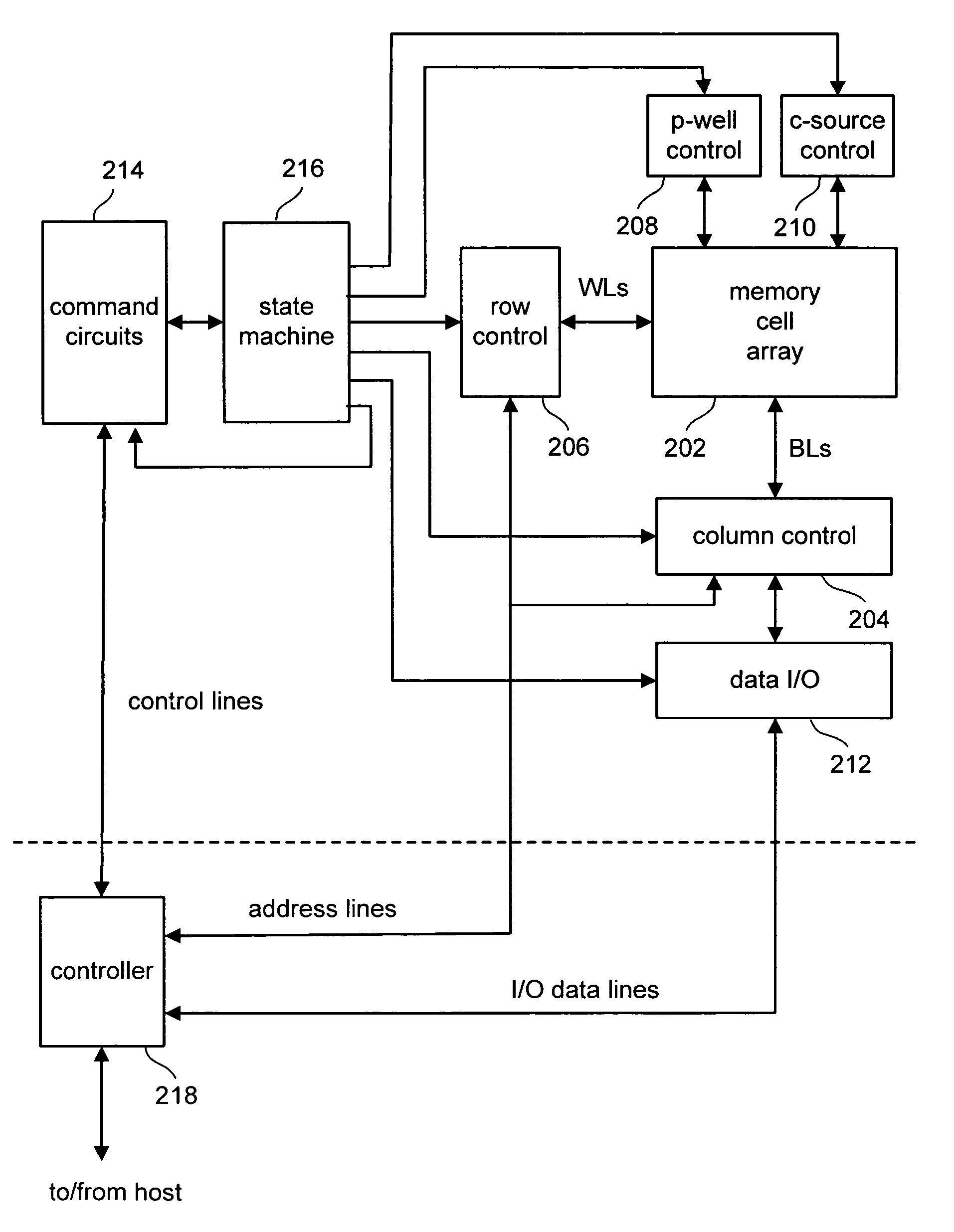

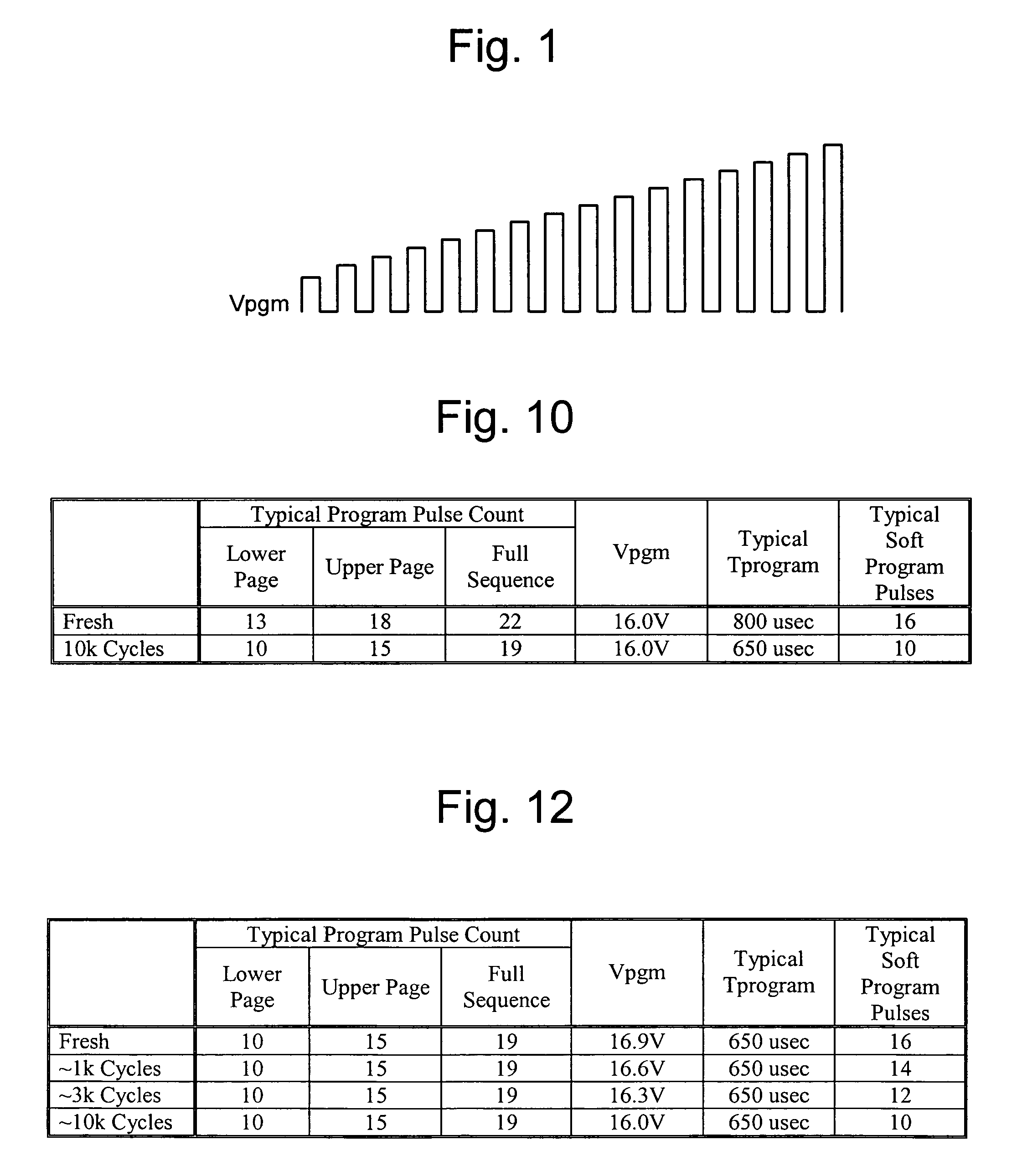

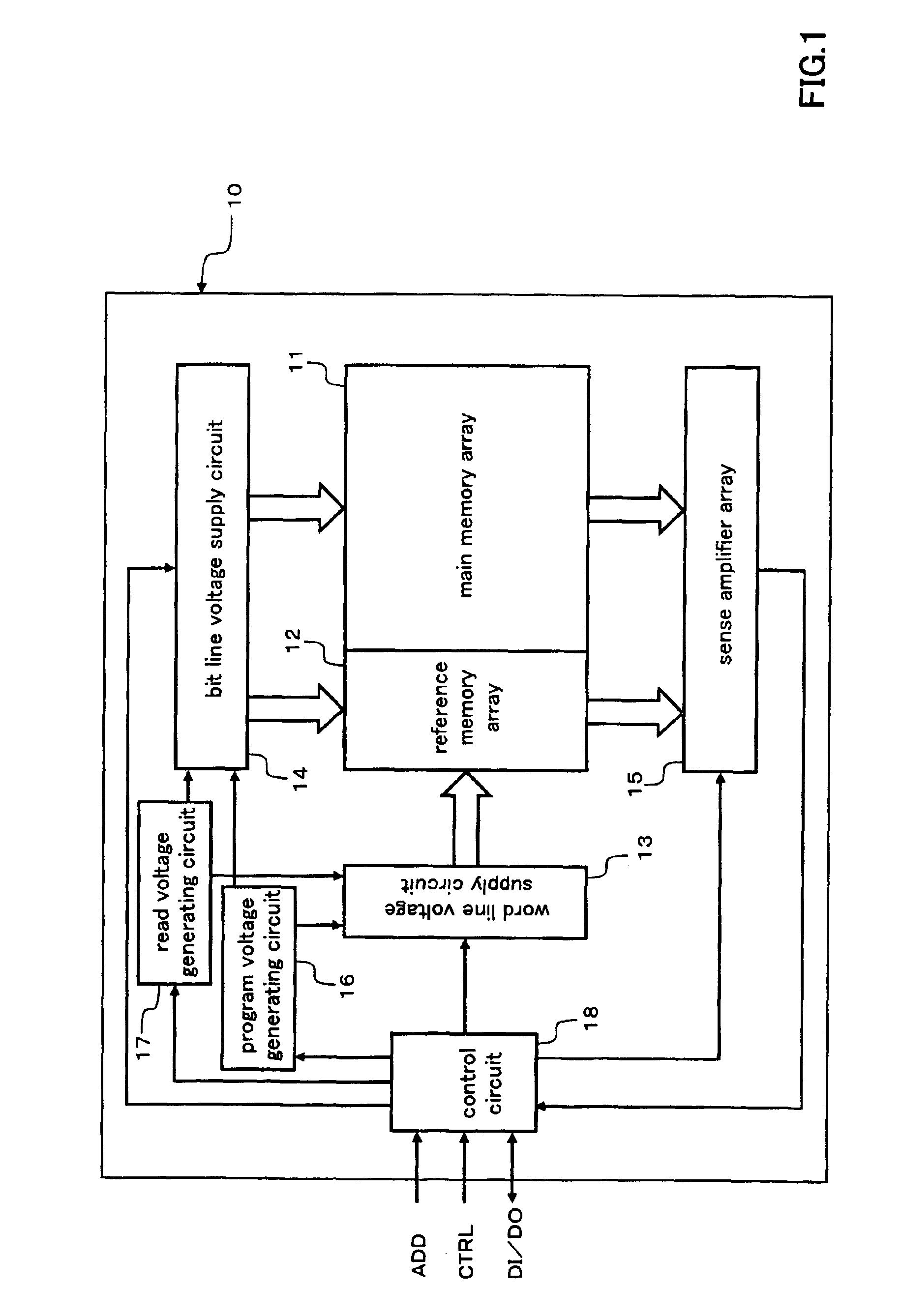

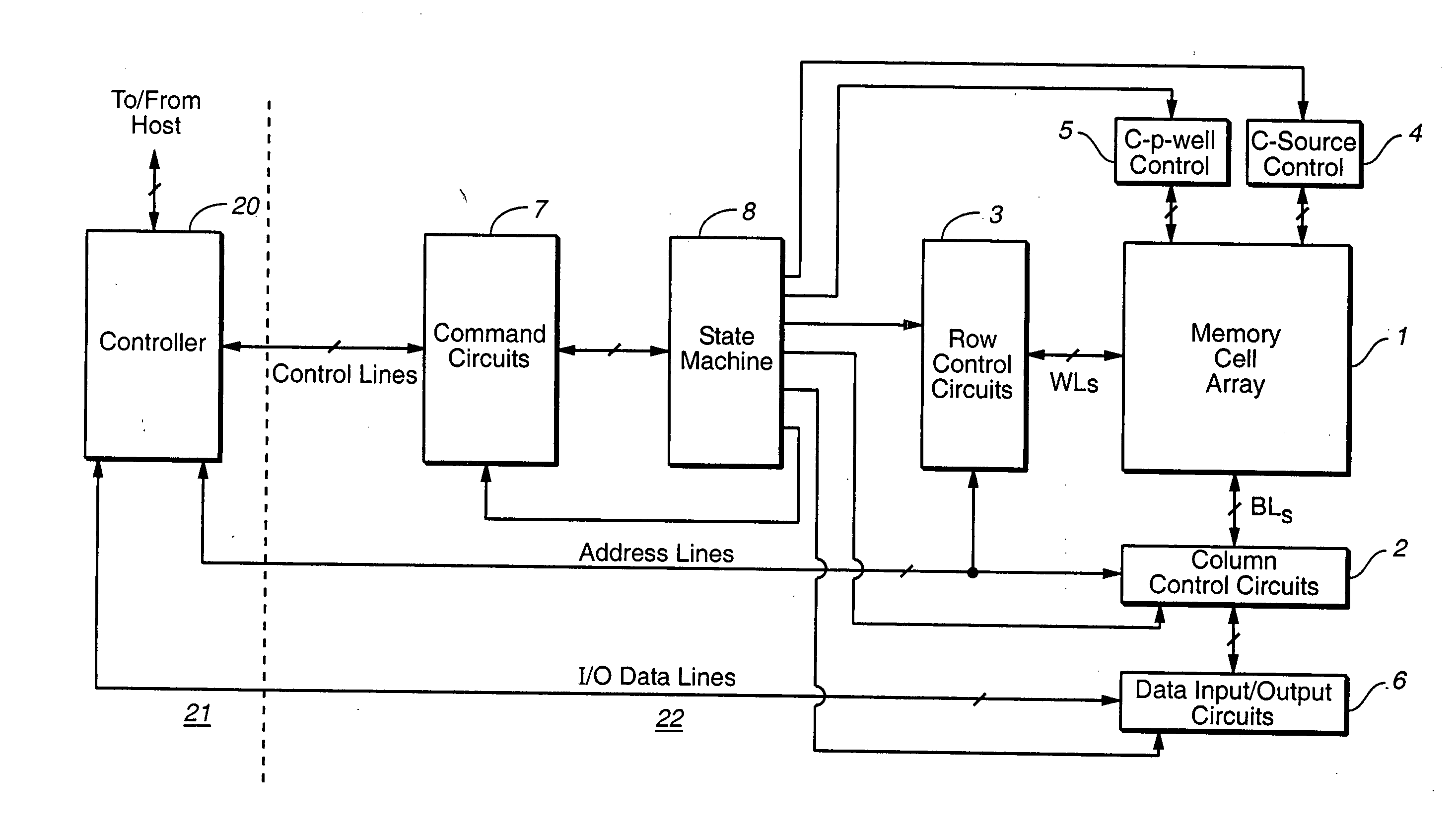

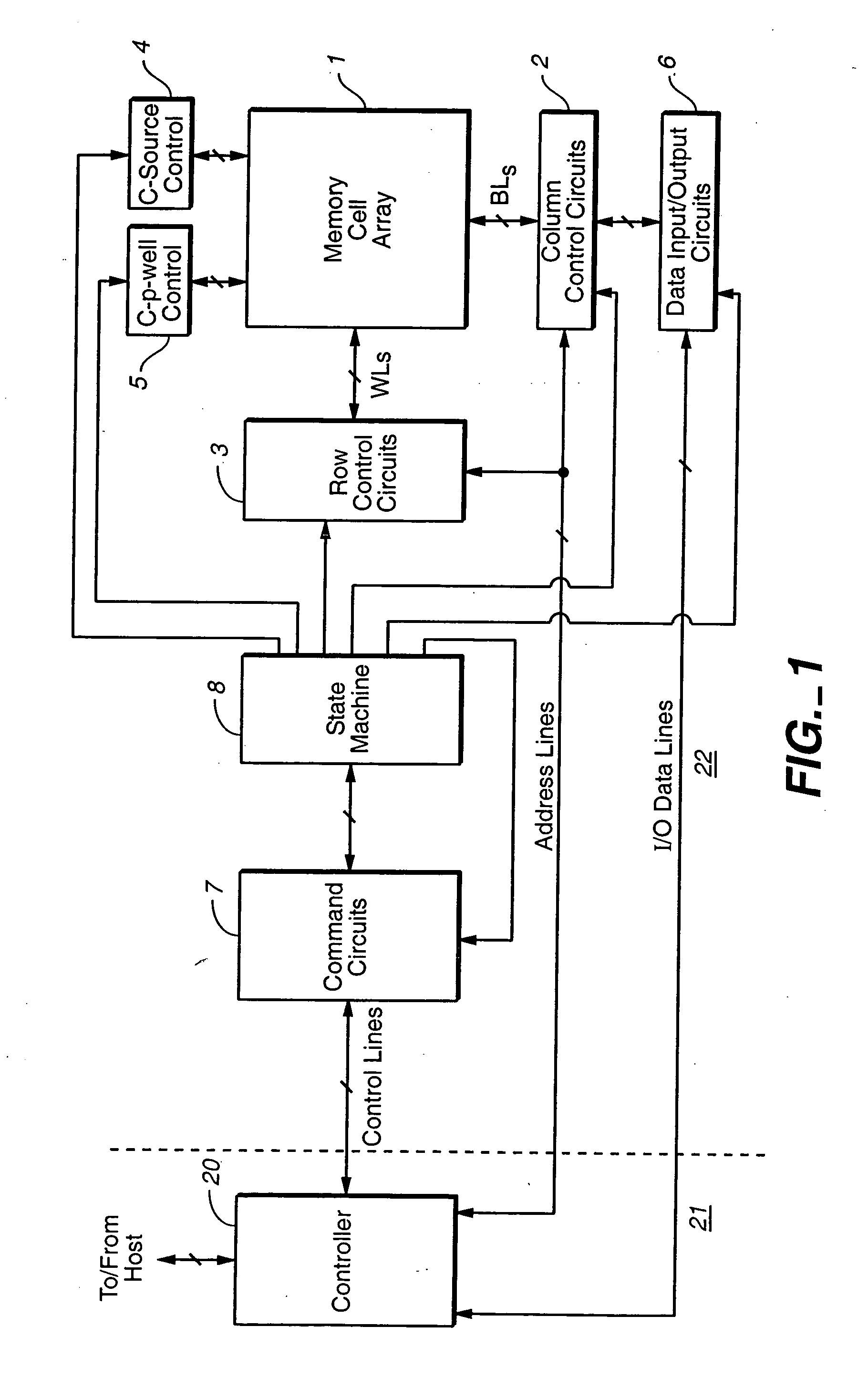

Starting program voltage shift with cycling of non-volatile memory

A system is disclosed for programming non-volatile storage that improves performance by setting the starting programming voltage to a first level for fresh parts and adjusting the starting programming voltage as the memory is cycled. For example, the system programs a set of non-volatile storage elements during a first period using an increasing program signal with a first initial value and subsequently programs the set of non-volatile storage elements during a second period using an increasing program signal with a second initial value, where the second period is subsequent to the first period and the second initial value is different than the first initial value.

Owner:SANDISK TECH LLC

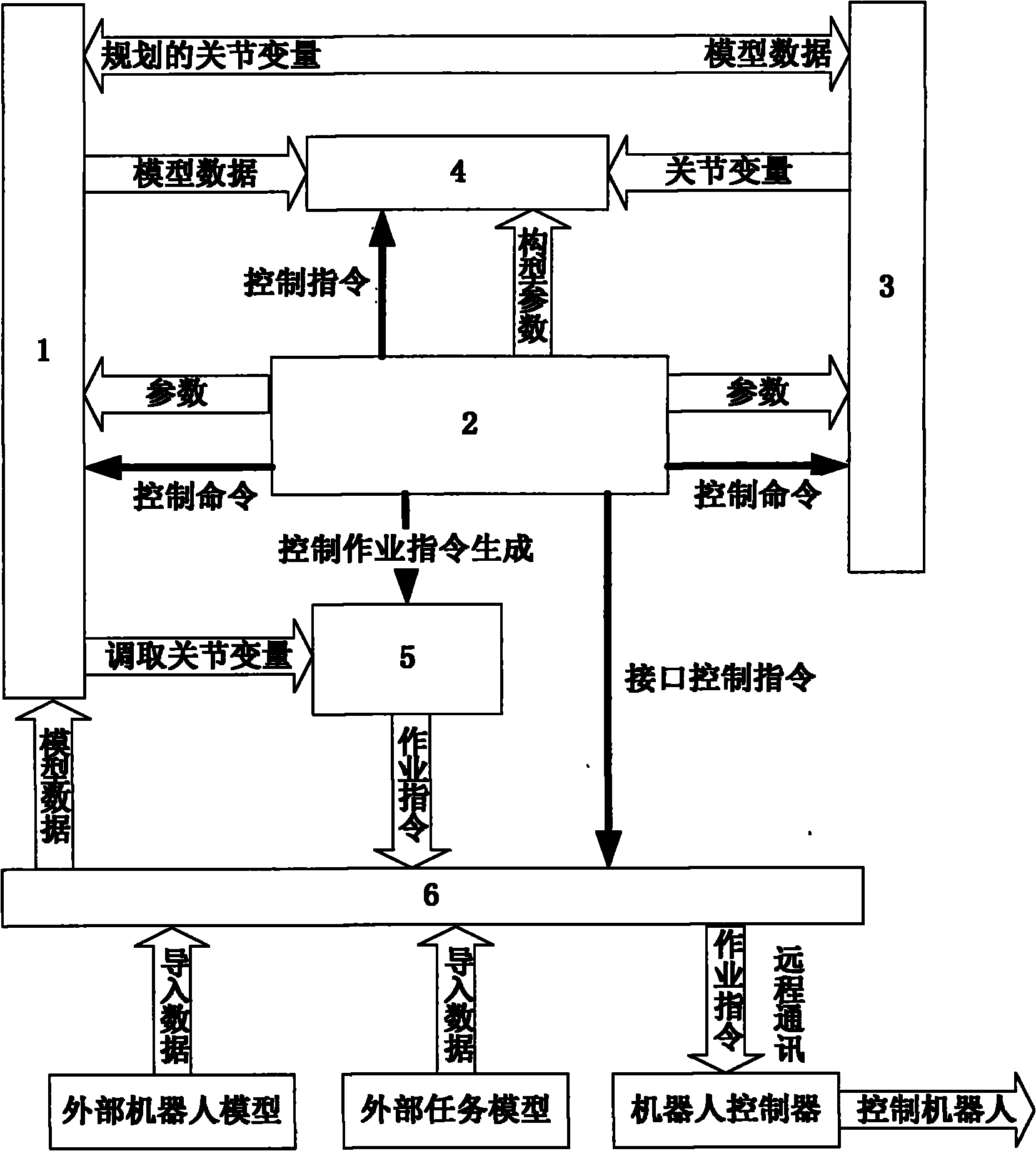

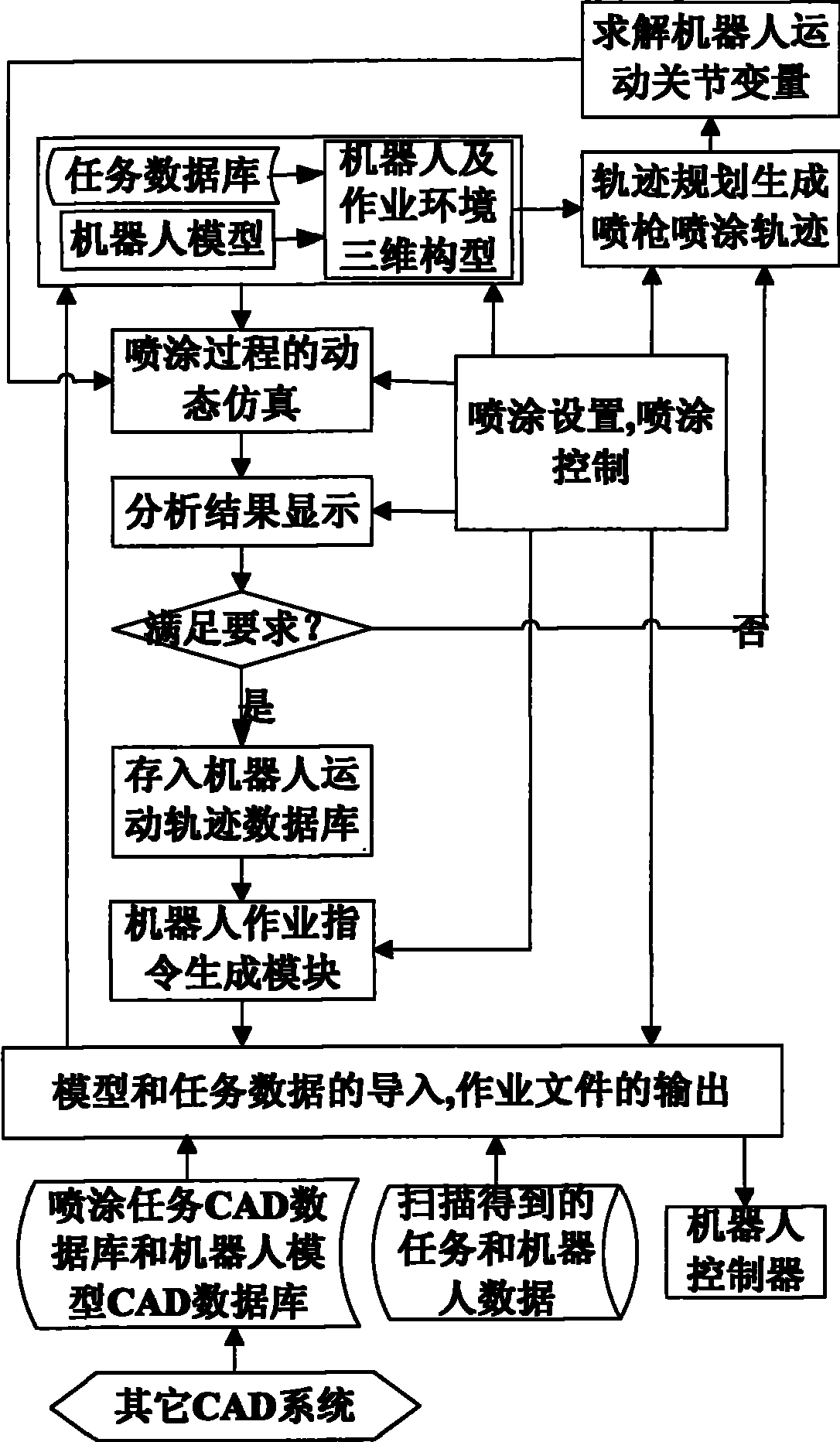

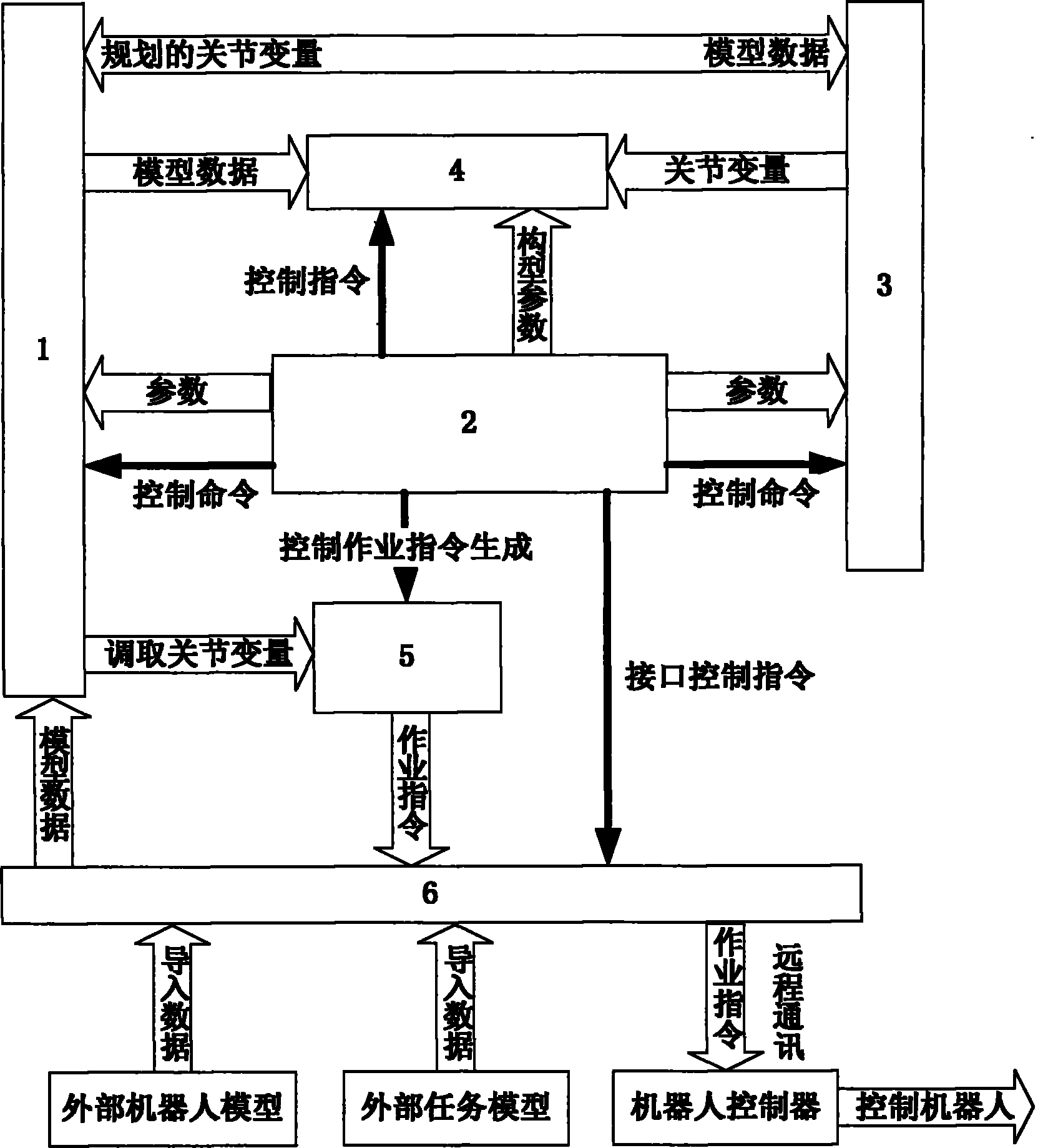

Industrial robot motion planning and performance testing system and implementation method thereof

InactiveCN101791801AFast programmingImprove accuracyManipulatorJoint variableHuman system interaction

The invention relates to an industrial robot motion planning and performance testing system and an implementation method thereof. The system comprises a database module, a man-machine interaction module, a spray gun track planning module, an analysis and display module, a robot job instruction generation module and a communication and interface module, wherein the database module realizes storage of the spray gun track and the joint variable of the spraying robot as well as the spraying tasks; the man-machine interaction module realizes parameter input and control on other modules; the spray gun track planning module is used for planning a spray gun track for optimizing the spraying effect and working out the joint variable corresponding to the track on the premise of meeting all the limits; the analysis and display module simulates and analyzes the spraying process of the spraying robot; the robot job instruction generation module realizes the function of generating spraying robot job files; and the communication and interface module is used for importing spraying task data, and uploading and downloading job files. The invention has the advantages of high programming speed, high accuracy, complete functions and strong versatility, and can be used for scientific research in various types of robots and control on the actual spraying operating system.

Owner:GUANGDONG UNIV OF TECH

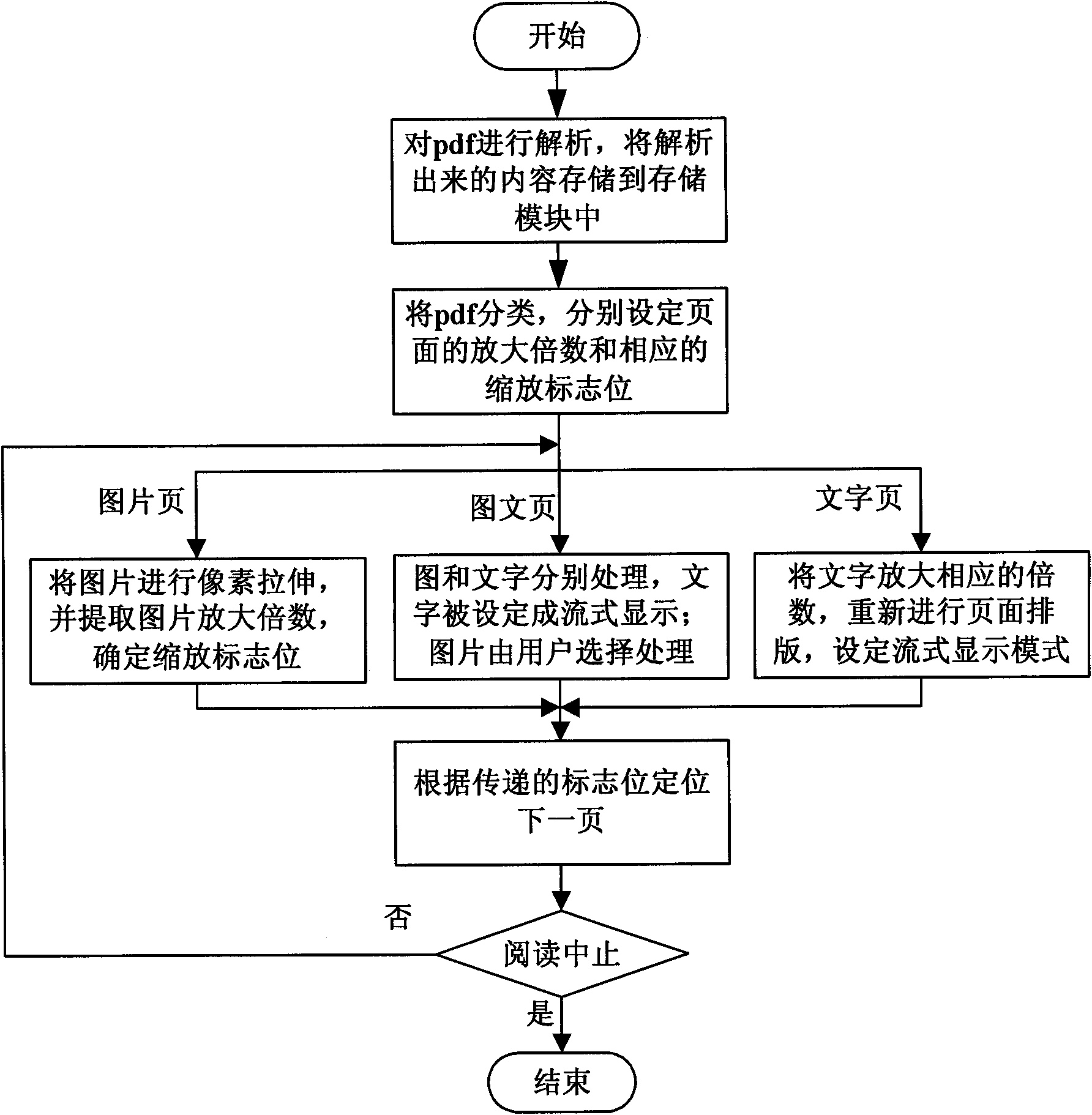

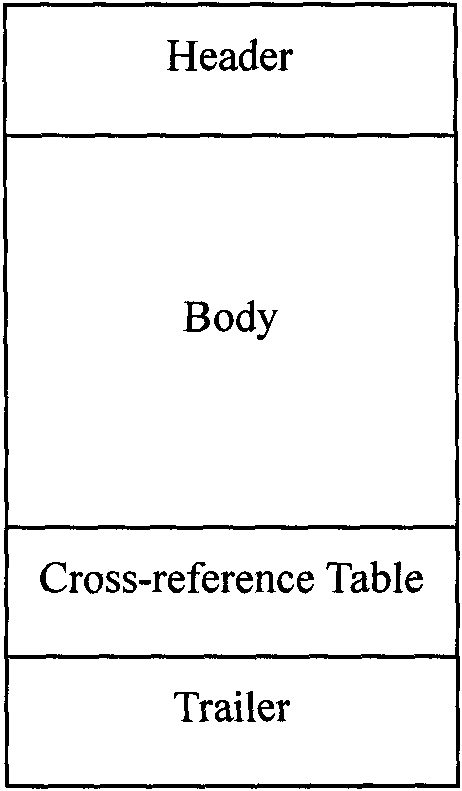

Method for realizing display of electronic document

ActiveCN101923723AEasy to switchFast programmingNatural language data processingSpecial data processing applicationsElectronic documentDocument preparation

The invention discloses a method for realizing the display of an electronic document, which belongs to the field of information display and comprises the following steps: S1, parsing the electronic document according to the format, and storing contents obtained by parsing into a storage module; and S2, classifying the document according to the contents in the storage module, setting a zoom flag in a page in the document after classifying, and displaying the parsed contents. When the page is an image page, pixel stretching is carried out on an image, and the zoom flag is further determined; when the page is a test page, the page is re-typeset and the stream display mode is set and saved; when the page is an image and text page, the image and text are respectively processed. The method can position the page through the flag, form the steam display page in different zoom-in scales, realize the function of utilizing a plurality of modes to respectively process the image and the text, further realize the convenient switching between the pages and have the function of carrying out fast arranging on the format mode and the steam mode of the page.

Owner:HANVON CORP

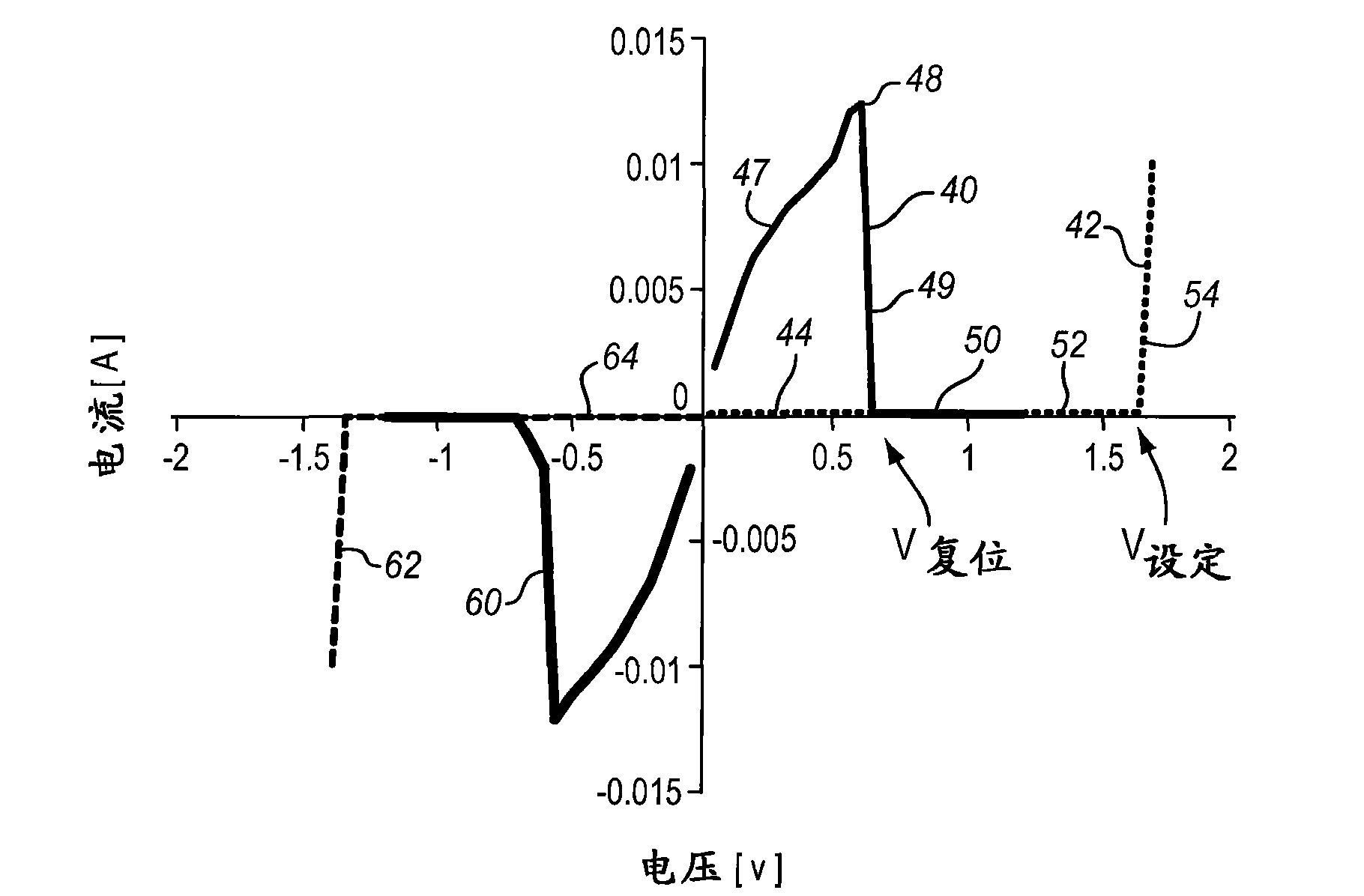

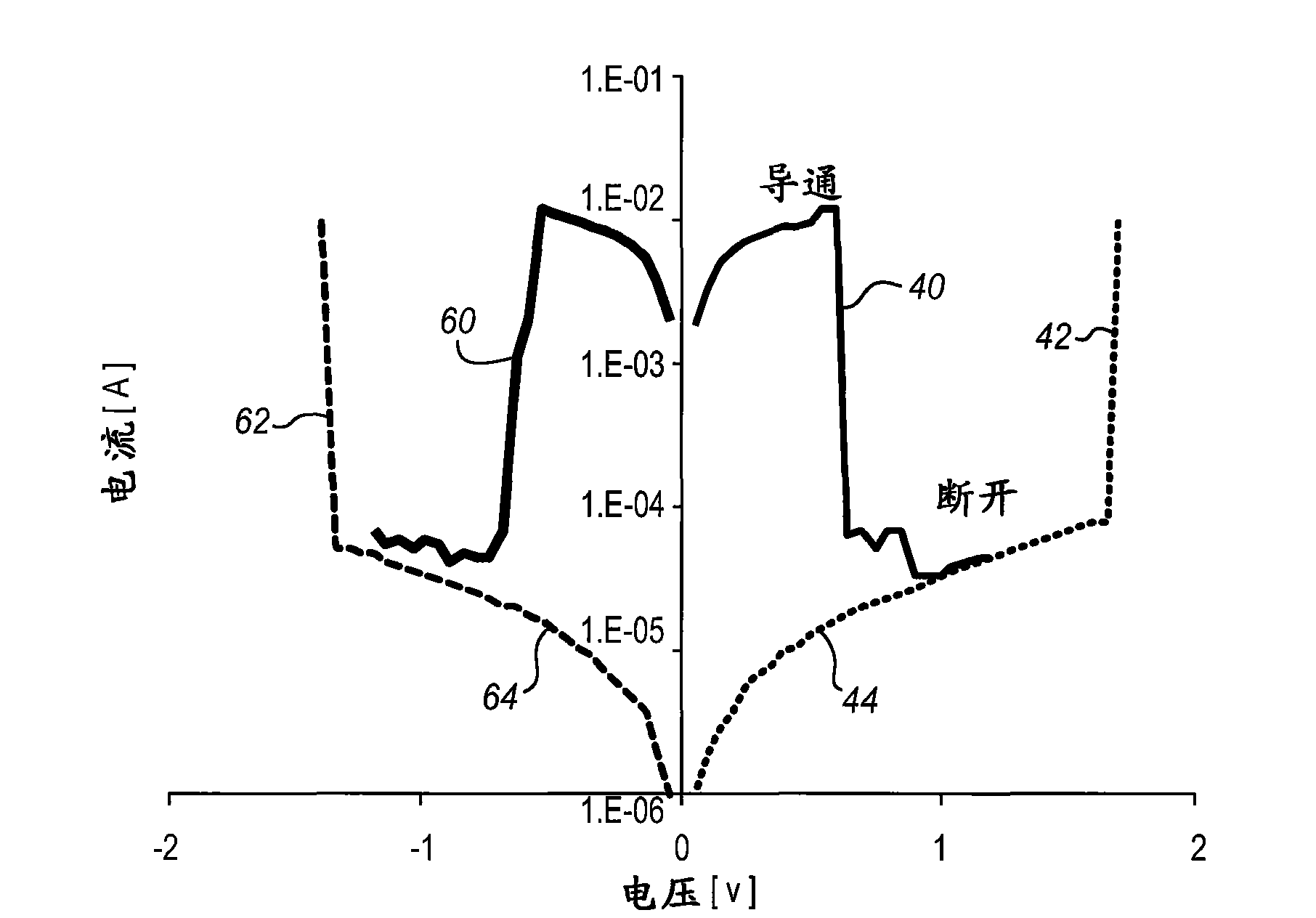

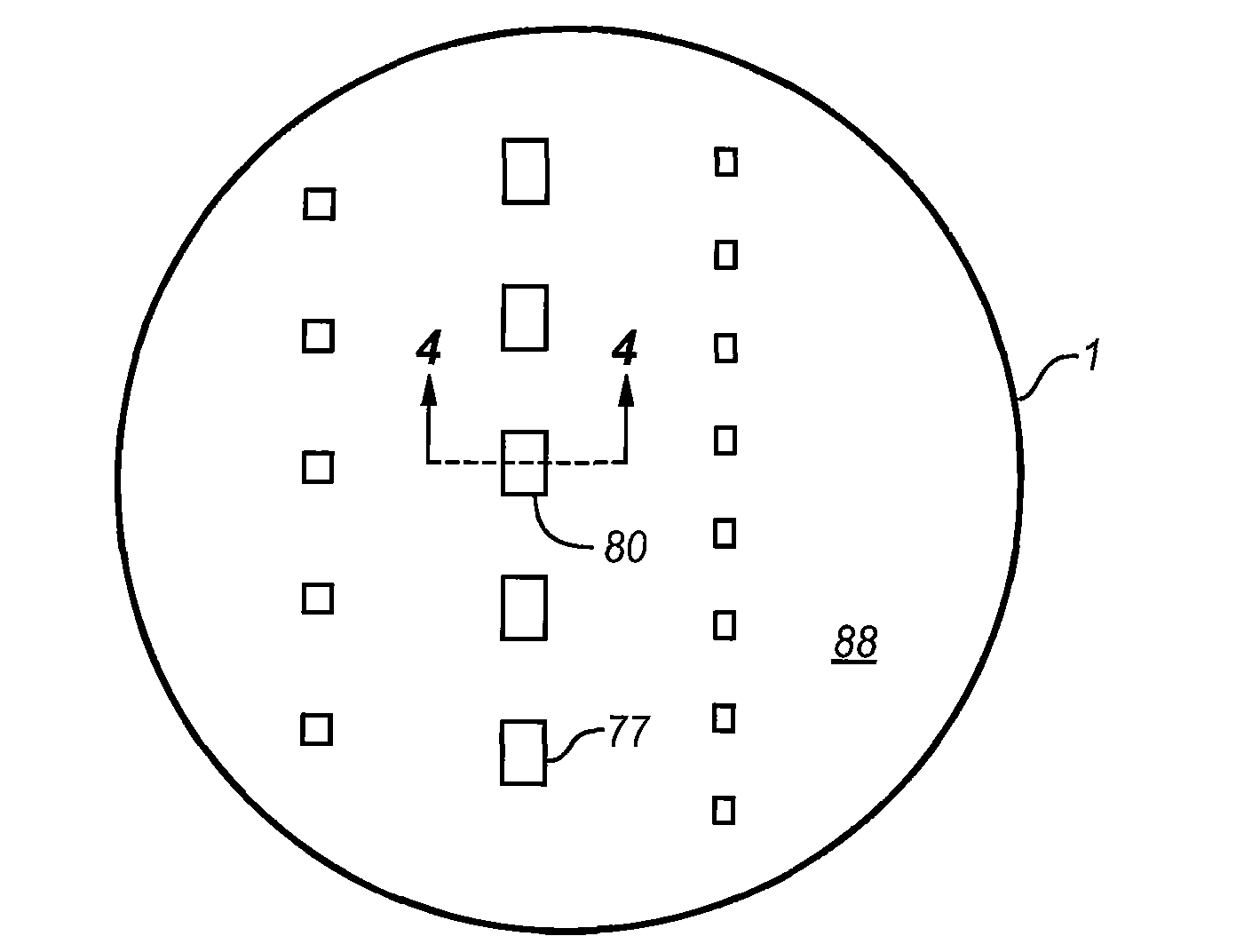

Correlated electron memory

ActiveCN101681911AEliminate injected dependenciesEliminate breakdownSolid-state devicesDigital storageMott transitionElectron

A non-volatile resistive switching memory that includes a material which changes between the insulative and conductive states due to correlations between electrons, particularly via a Mott transition.The material is crystallized into the conductive state and does not require electroforming.

Owner:思美存储器有限公司

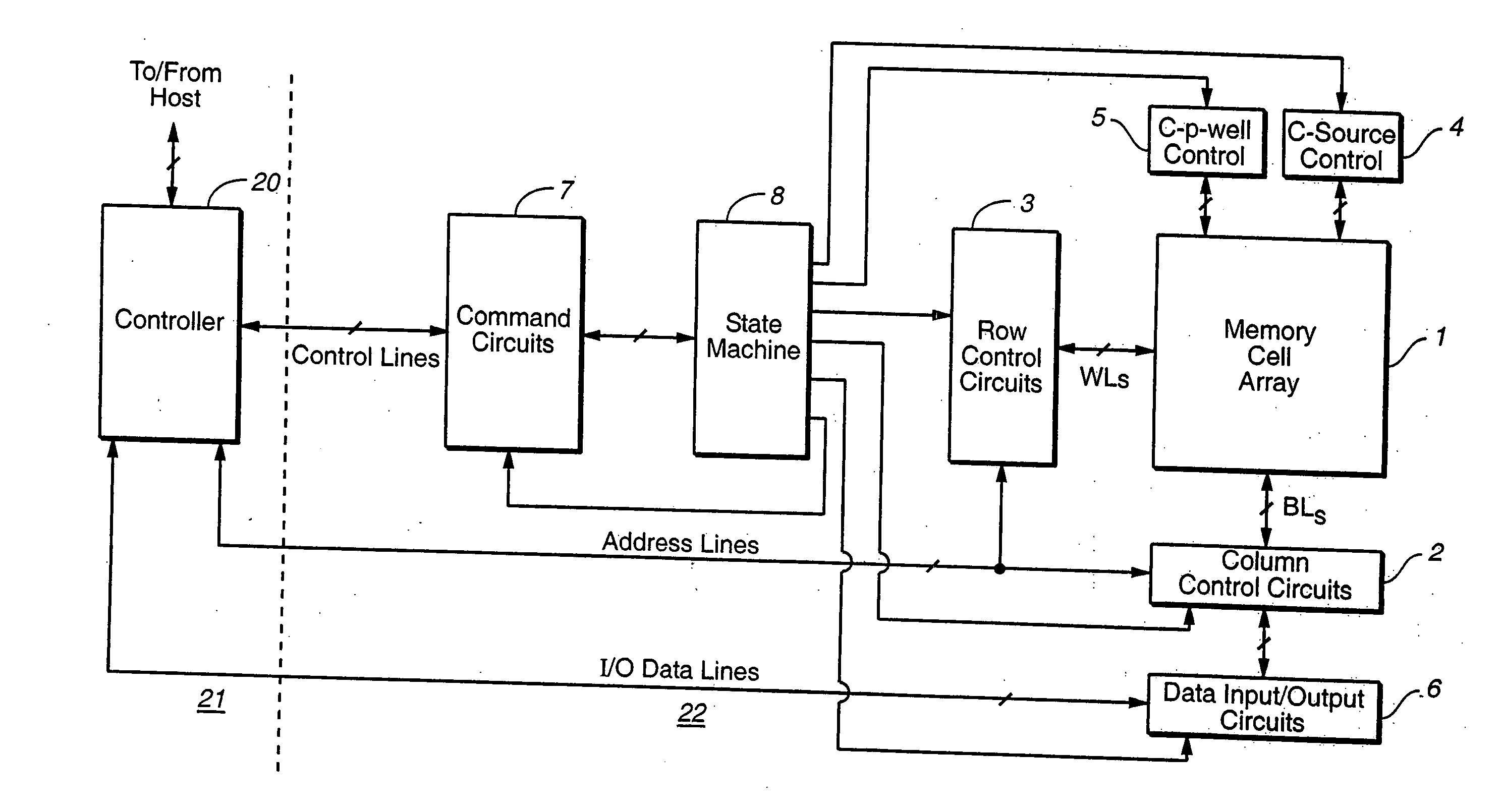

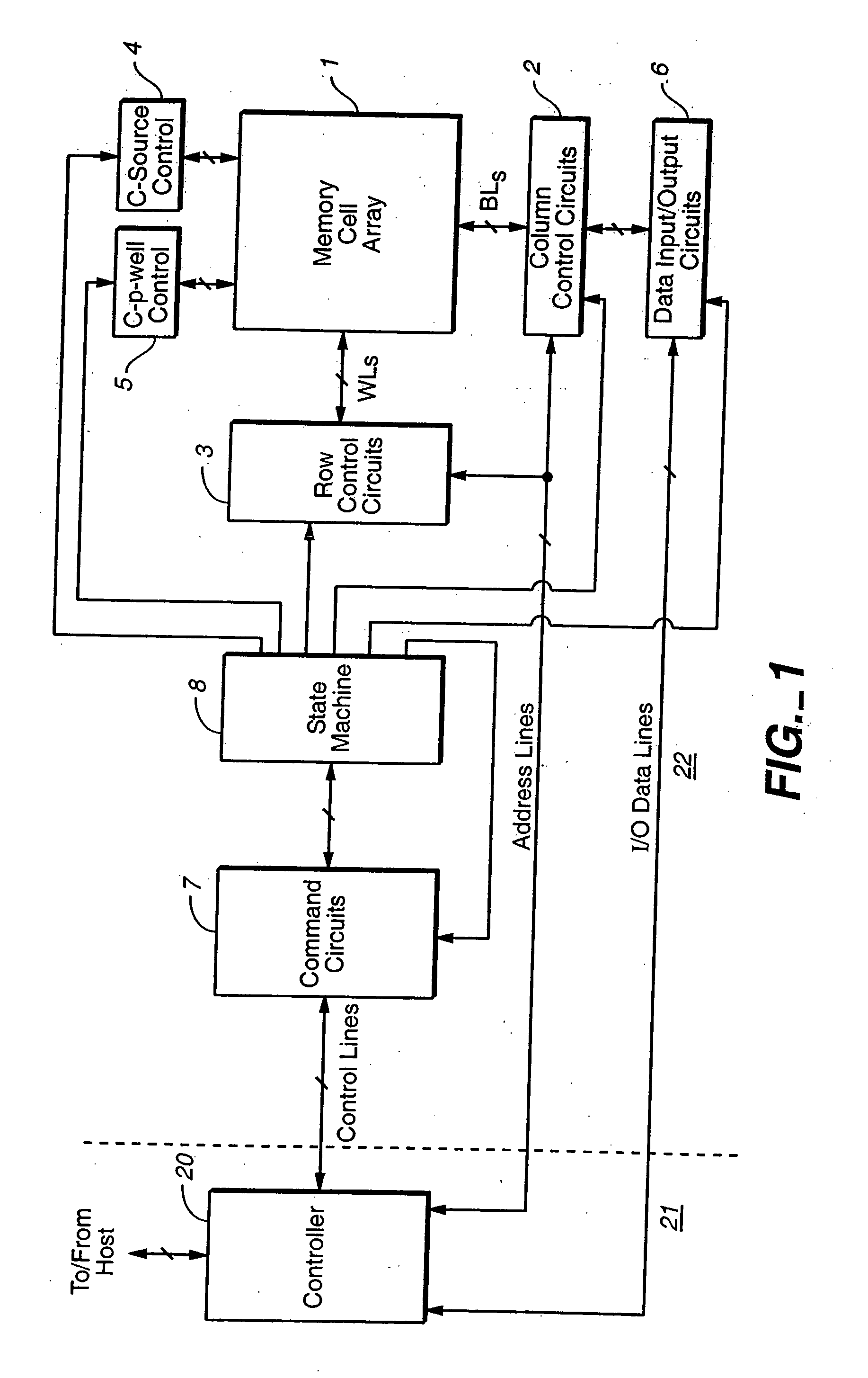

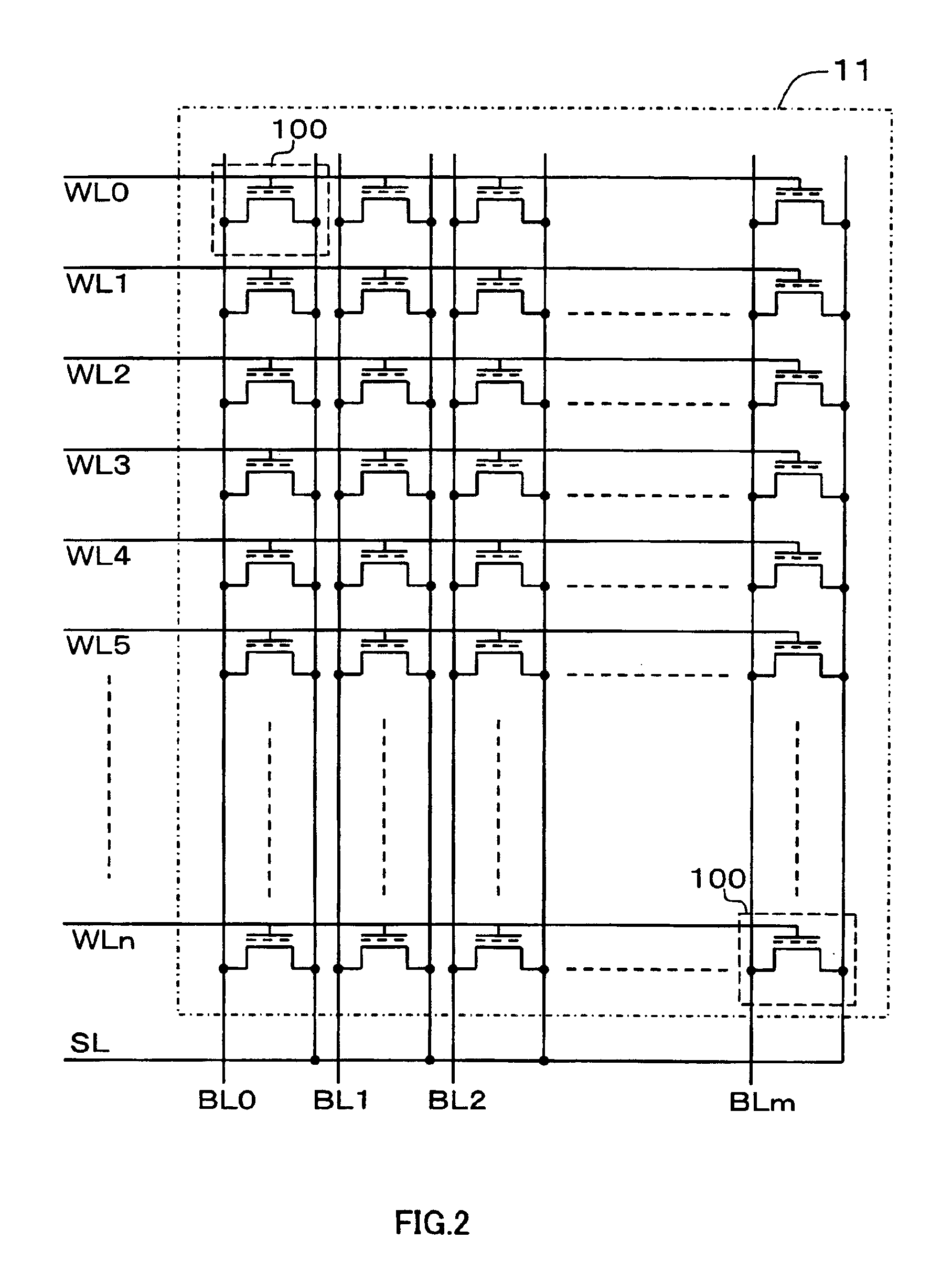

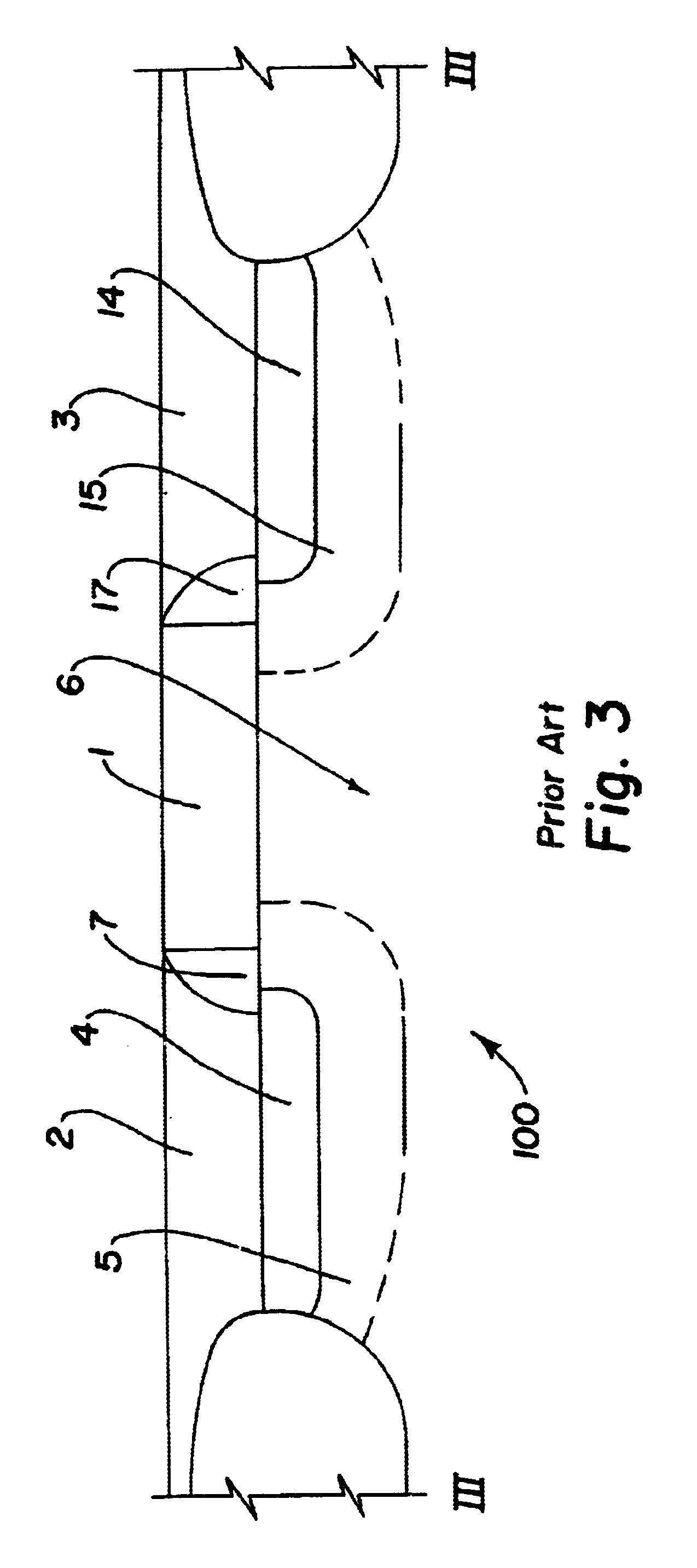

Operating techniques for reducing effects of coupling between storage elements of a non-volatile memory operated in multiple data states

InactiveUS20050276101A1Compensation effectAccurate readingTransistorSolid-state devicesProgrammable read-only memoryComputer science

Owner:TOSHIBA MEMORY CORP +1

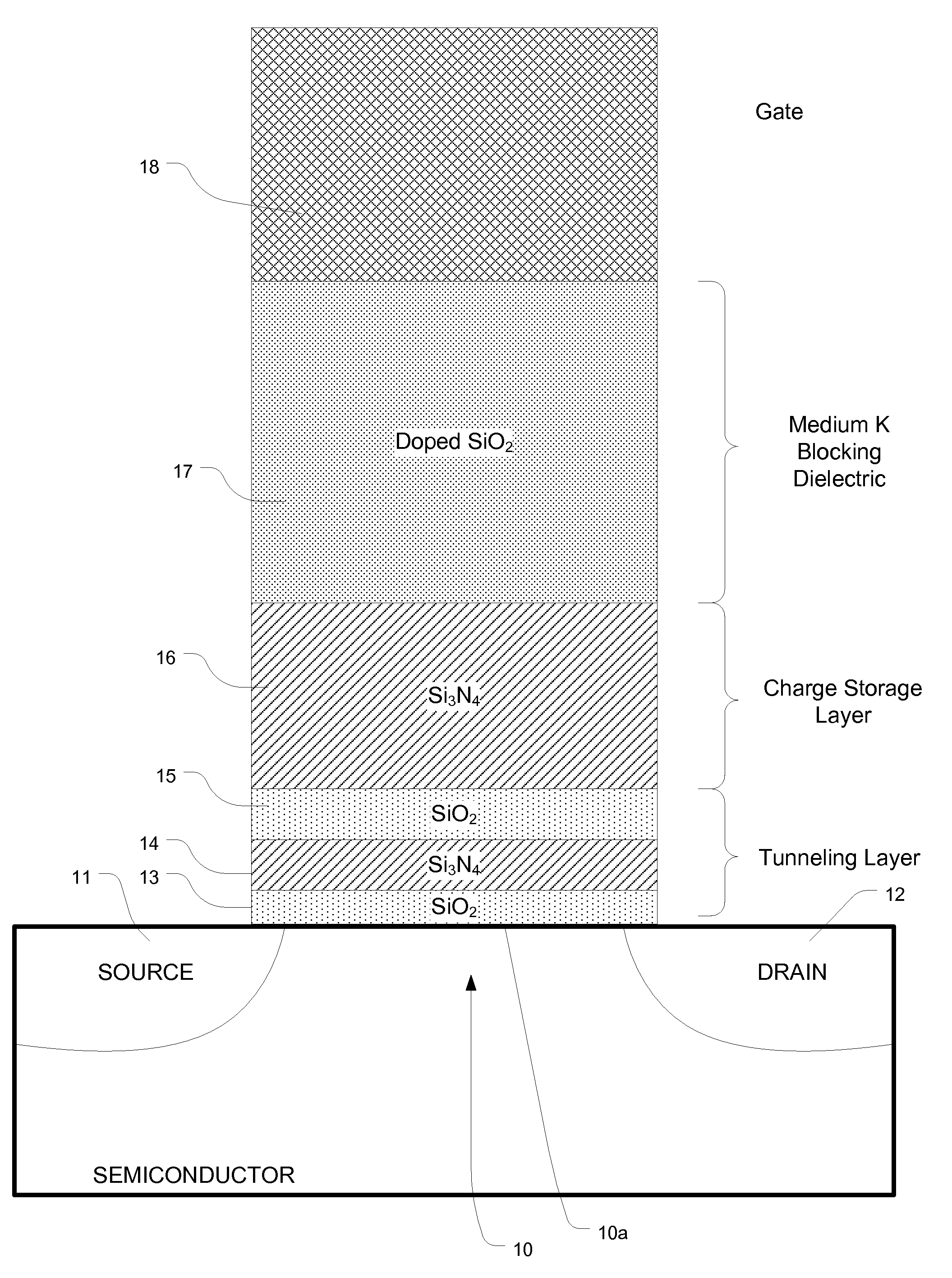

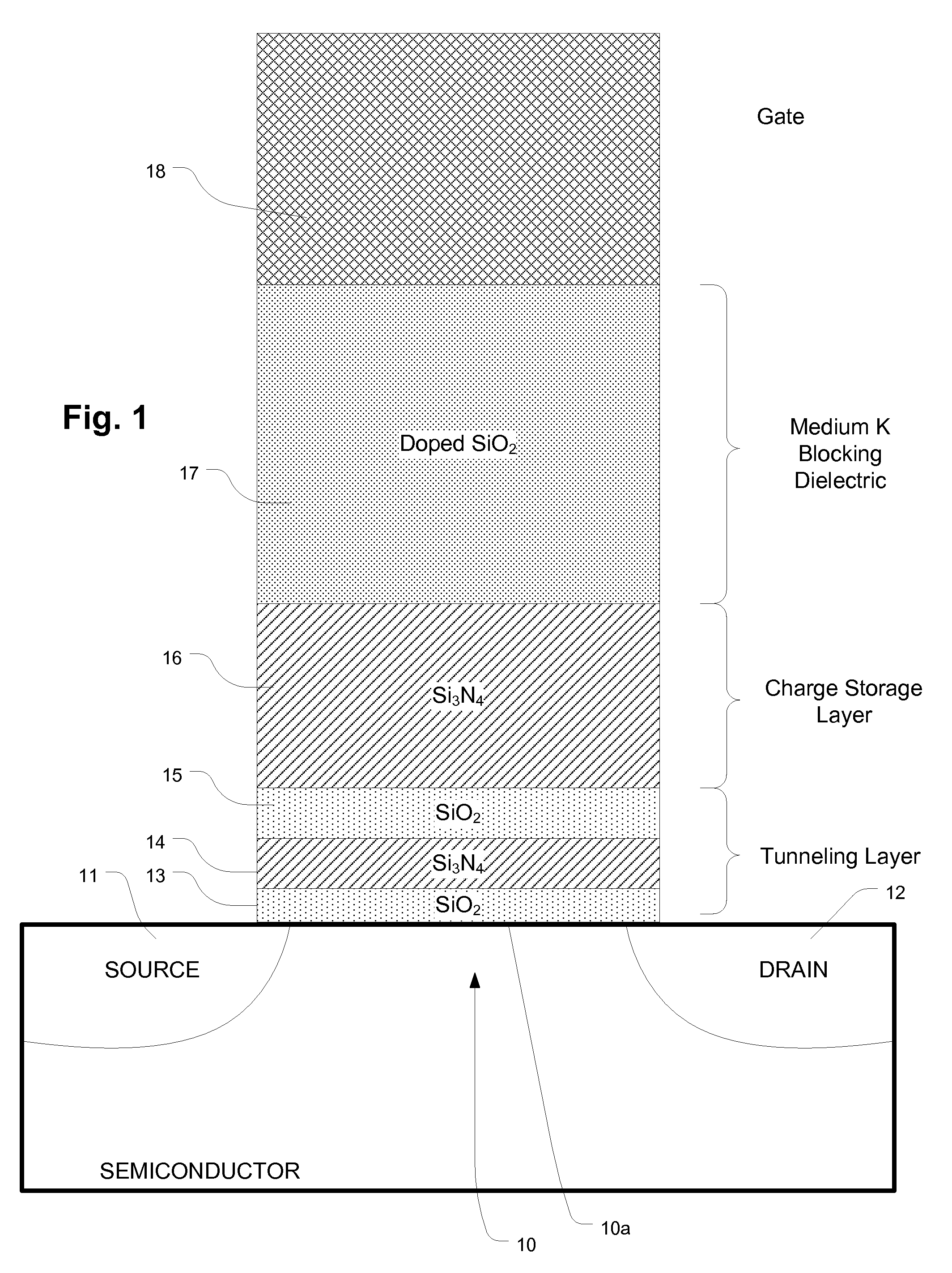

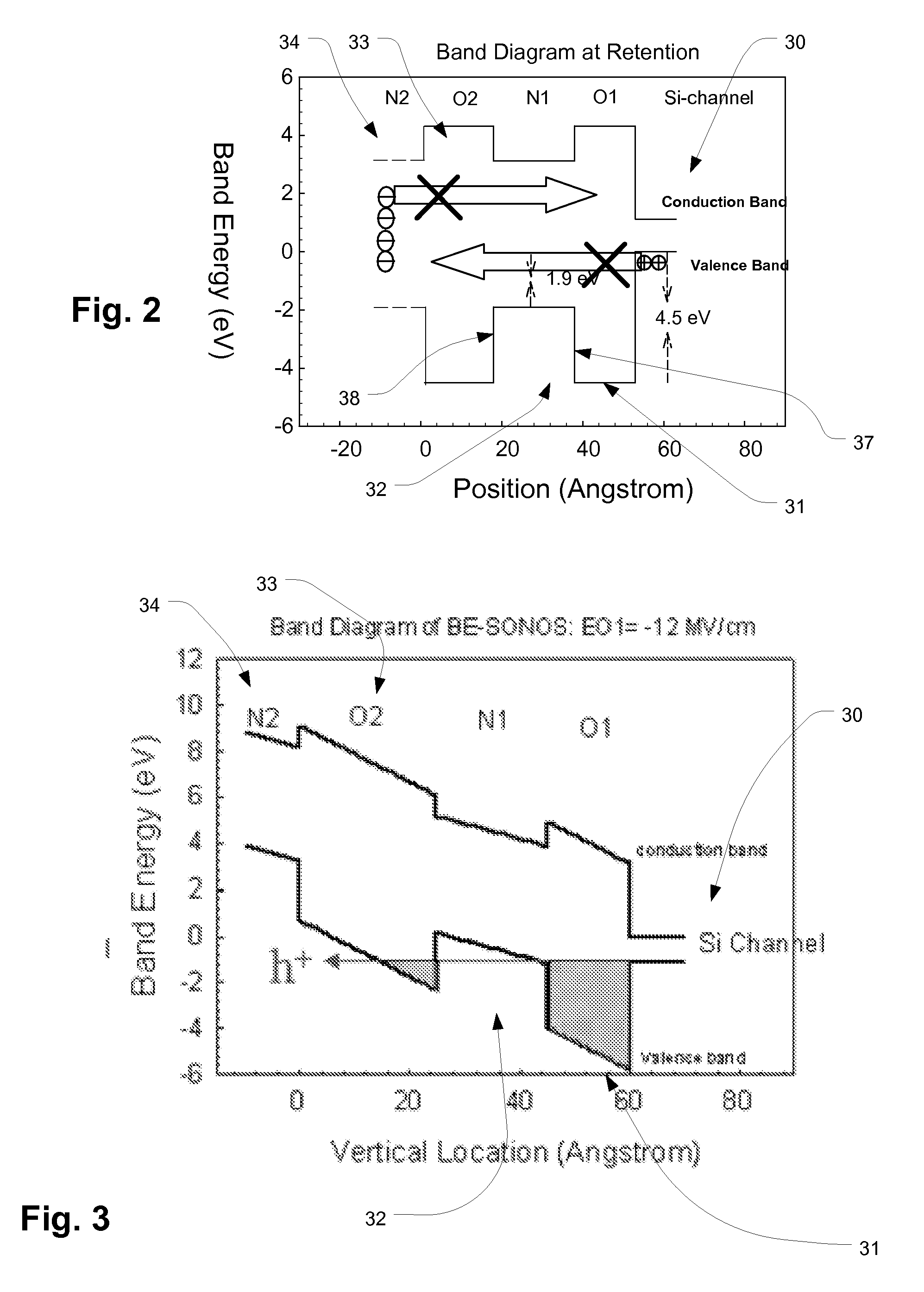

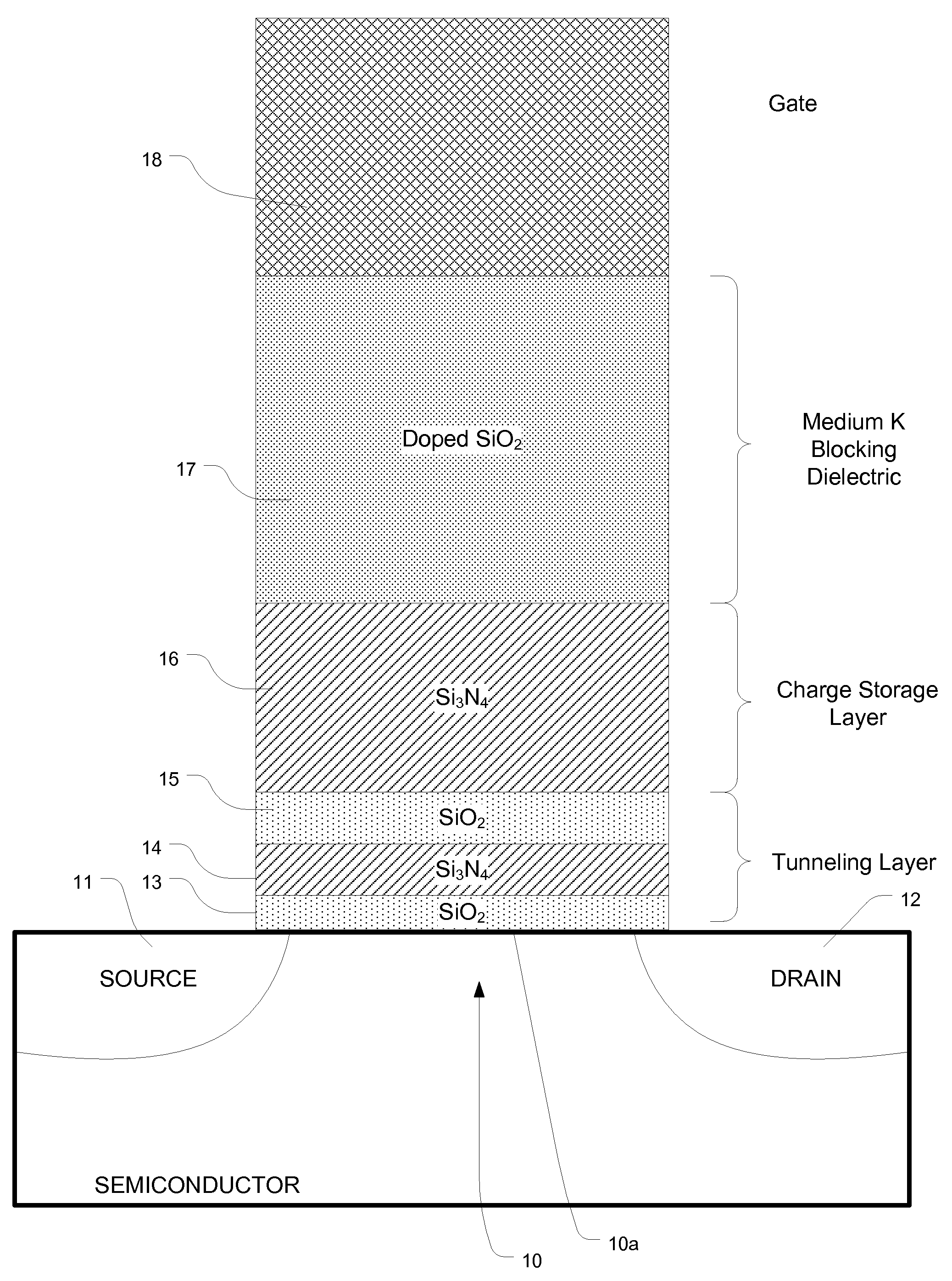

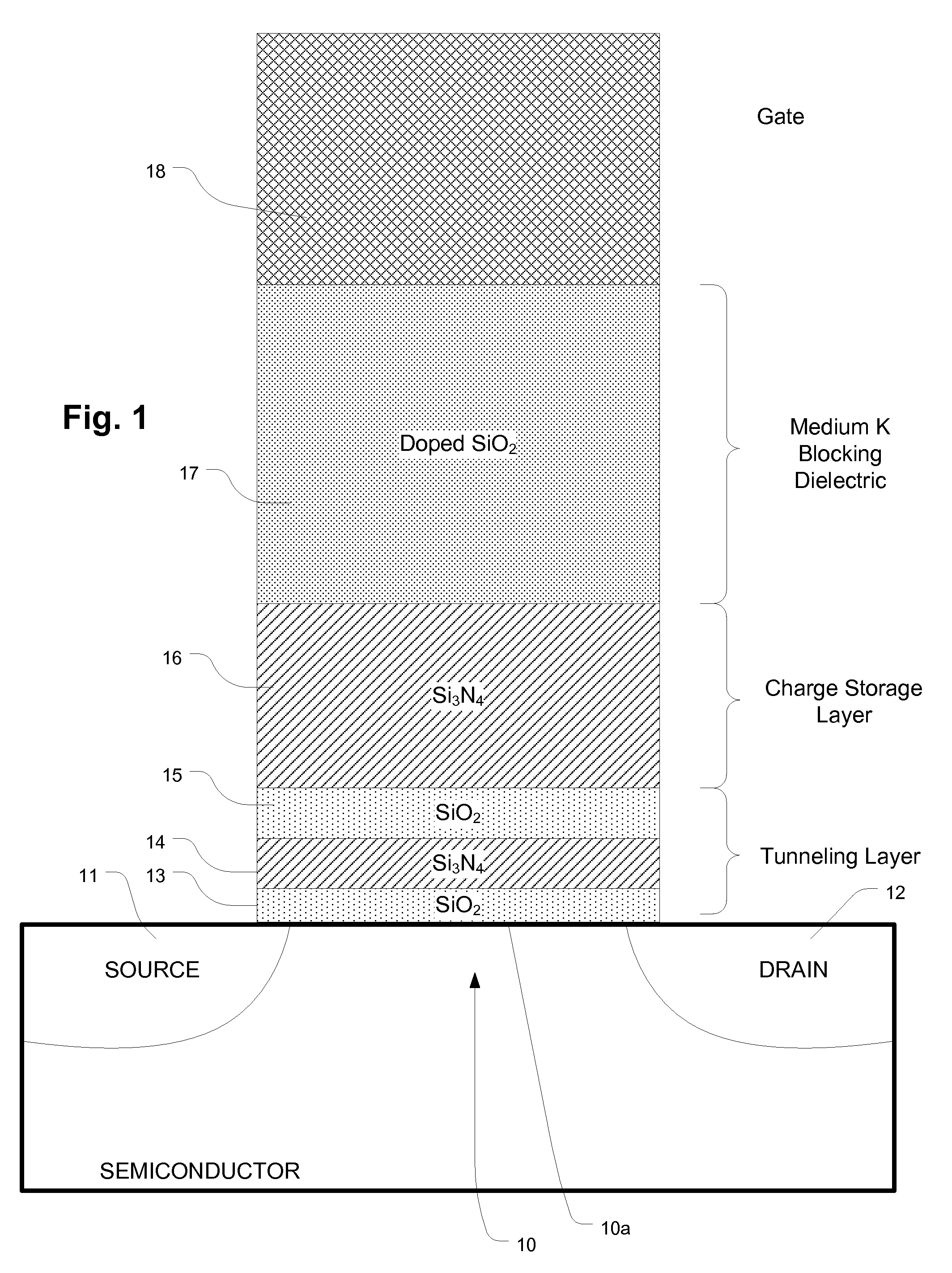

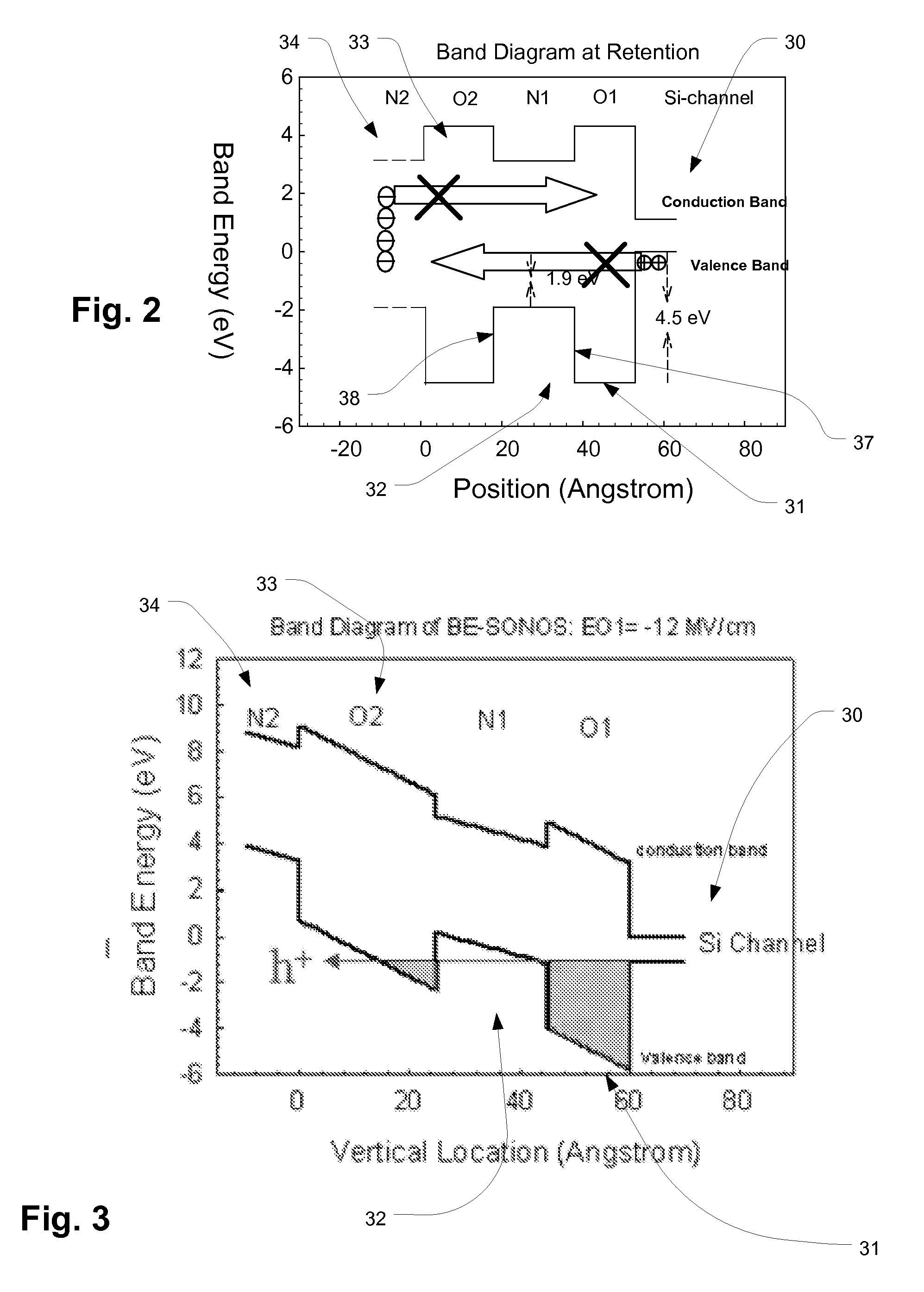

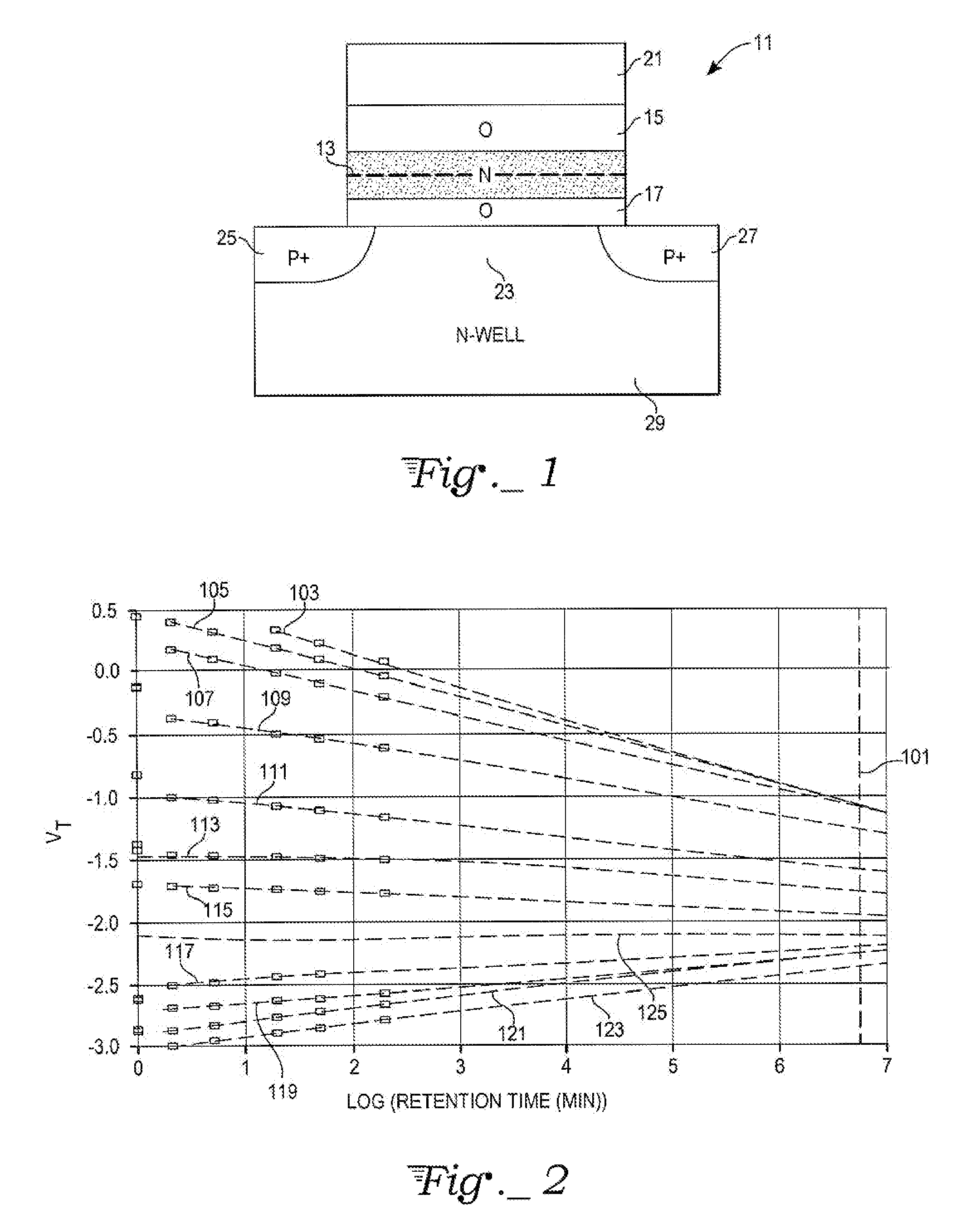

Blocking dielectric engineered charge trapping memory cell with high speed erase

ActiveUS7737488B2High barrier heightFast programmingSolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking layer of metal doped silicon oxide material having a medium dielectric constant, such as aluminum doped silicon oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric.

Owner:MACRONIX INT CO LTD

Blocking dielectric engineered charge trapping memory cell with high speed erase

ActiveUS20090039416A1Fast programmingImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking layer of metal doped silicon oxide material having a medium dielectric constant, such as aluminum doped silicon oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric.

Owner:MACRONIX INT CO LTD

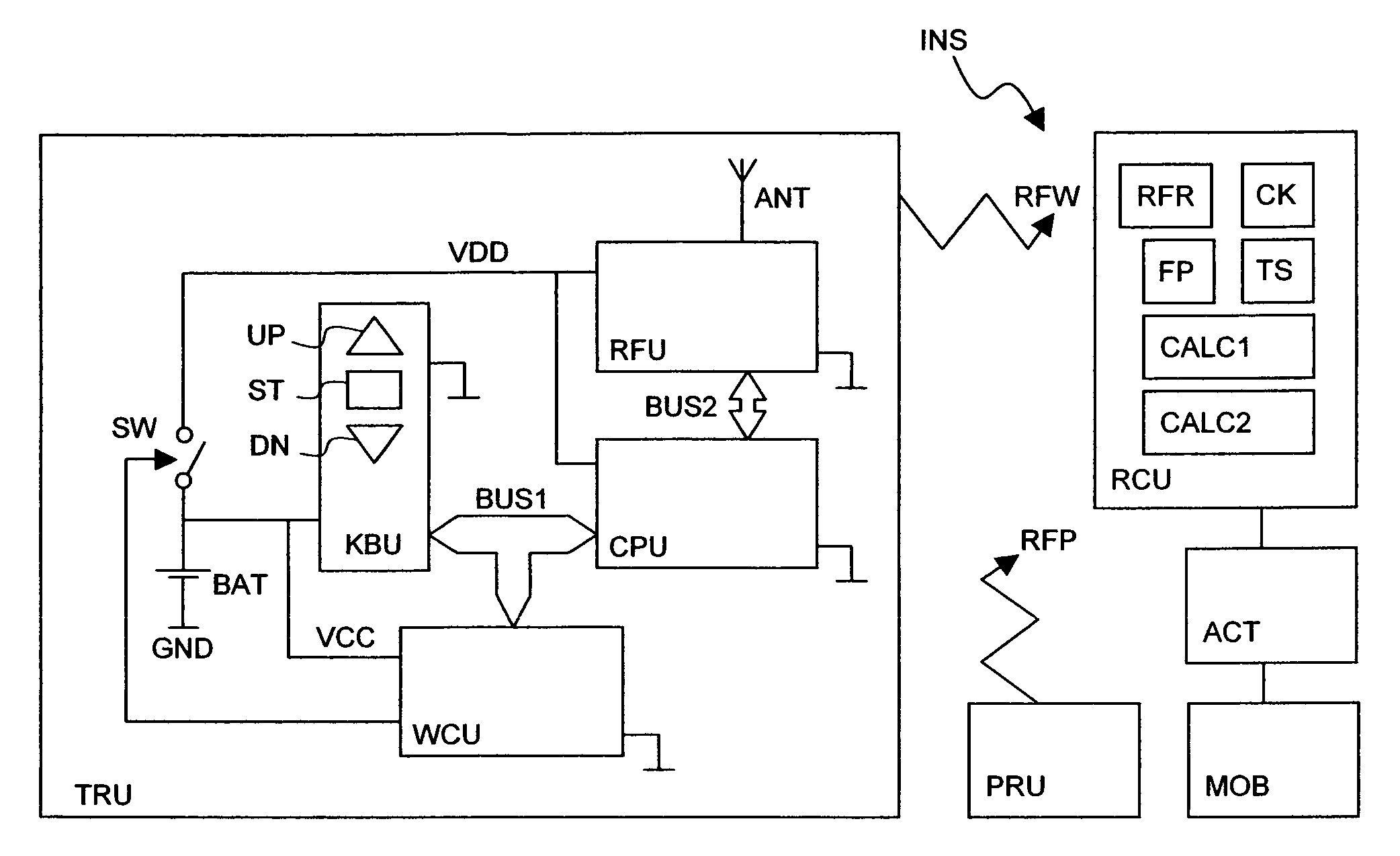

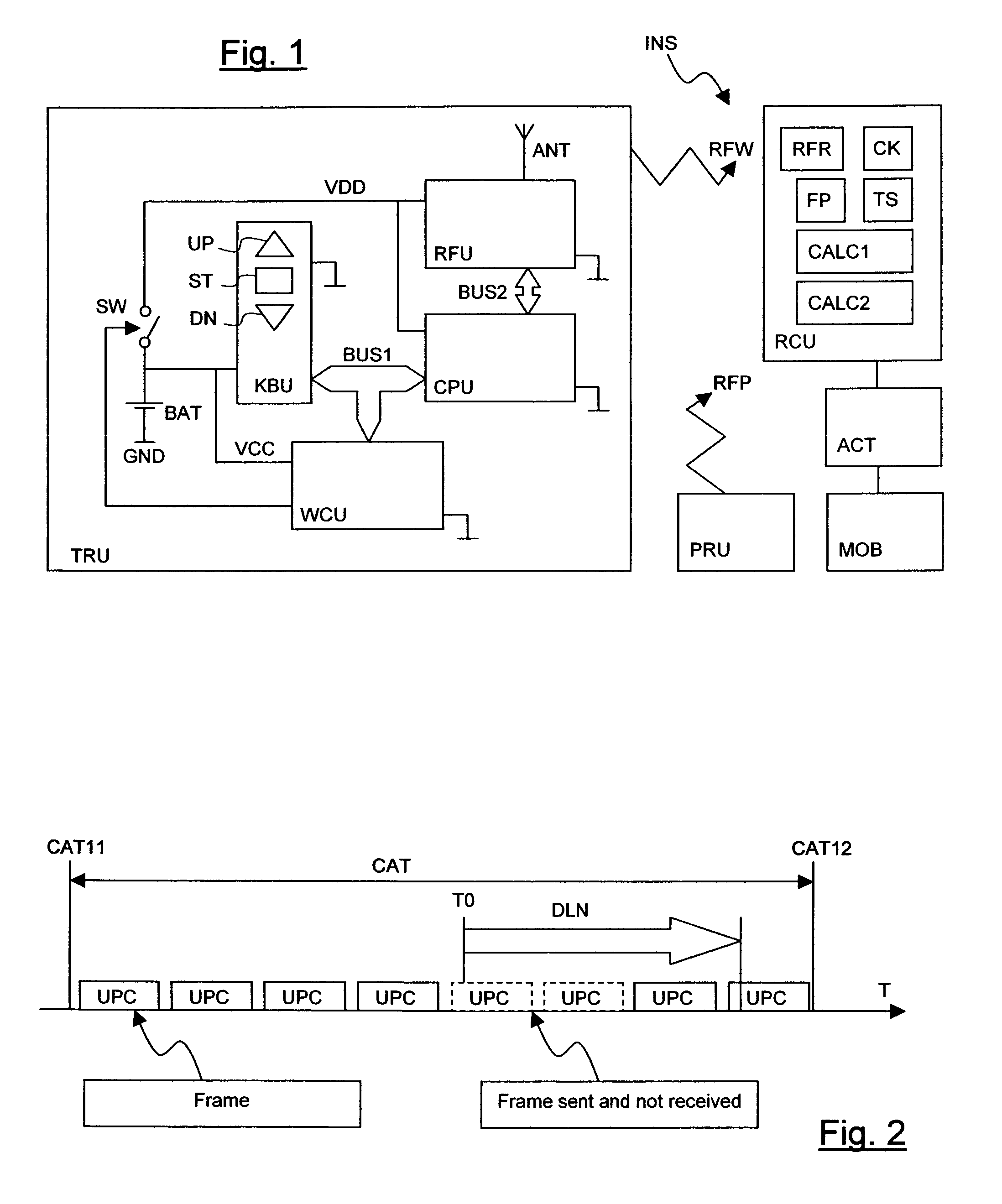

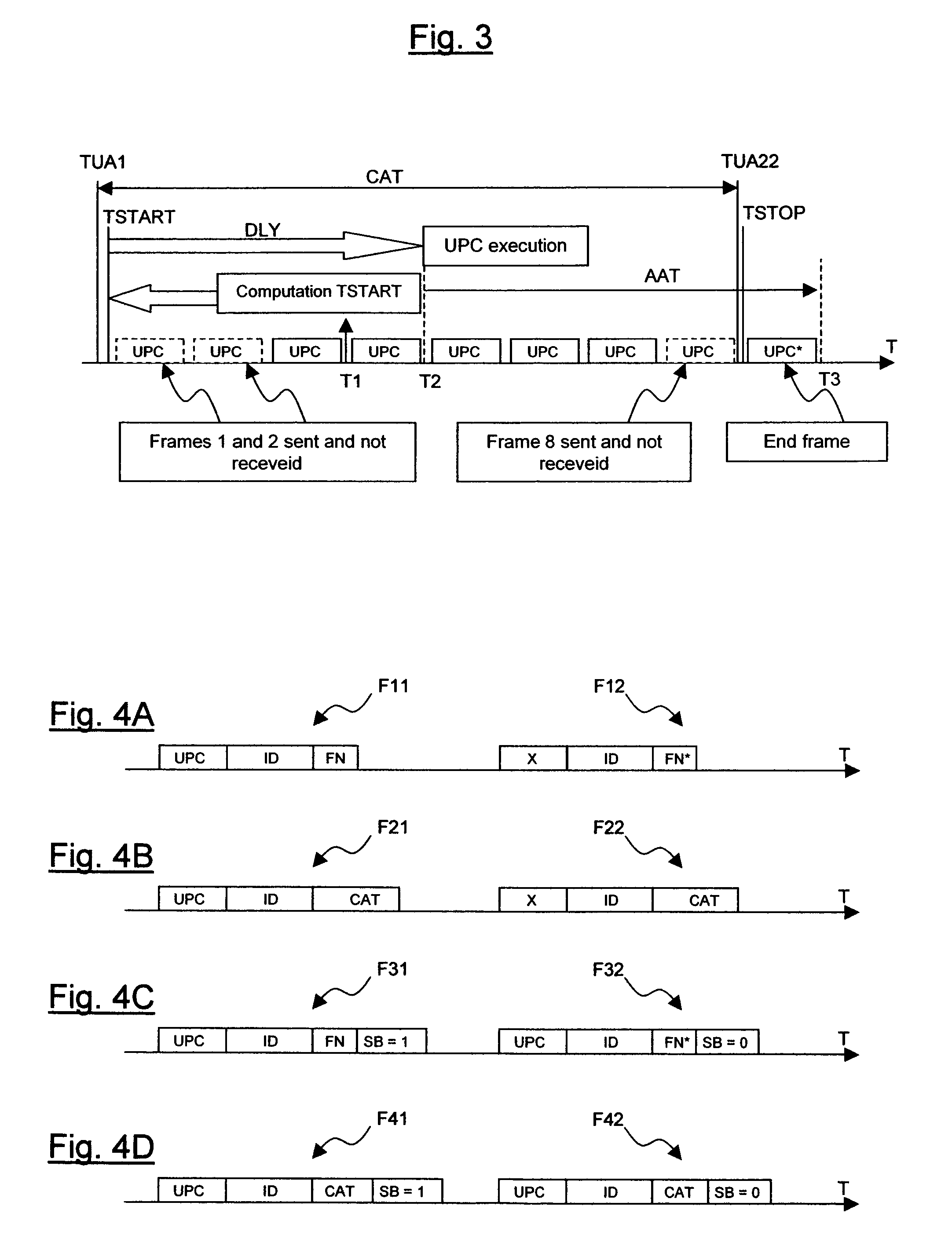

Actuator control method

ActiveUS7852765B2Quick installationFast programmingError preventionTransmission systemsTime informationSynchronous control

A synchronized control method for actuators driving a moving device includes the sending of a signal repeating a frame including the code of the control to be executed, inserting into the frame sent a time information item representative of the control generation duration, extracting the time information item and computing at least one of the application start and the application end instant of control, and the reception of the signal for application of the control to the actuator as long as the generation of the control signal lasts.

Owner:SOMFY ACTIVITES SA

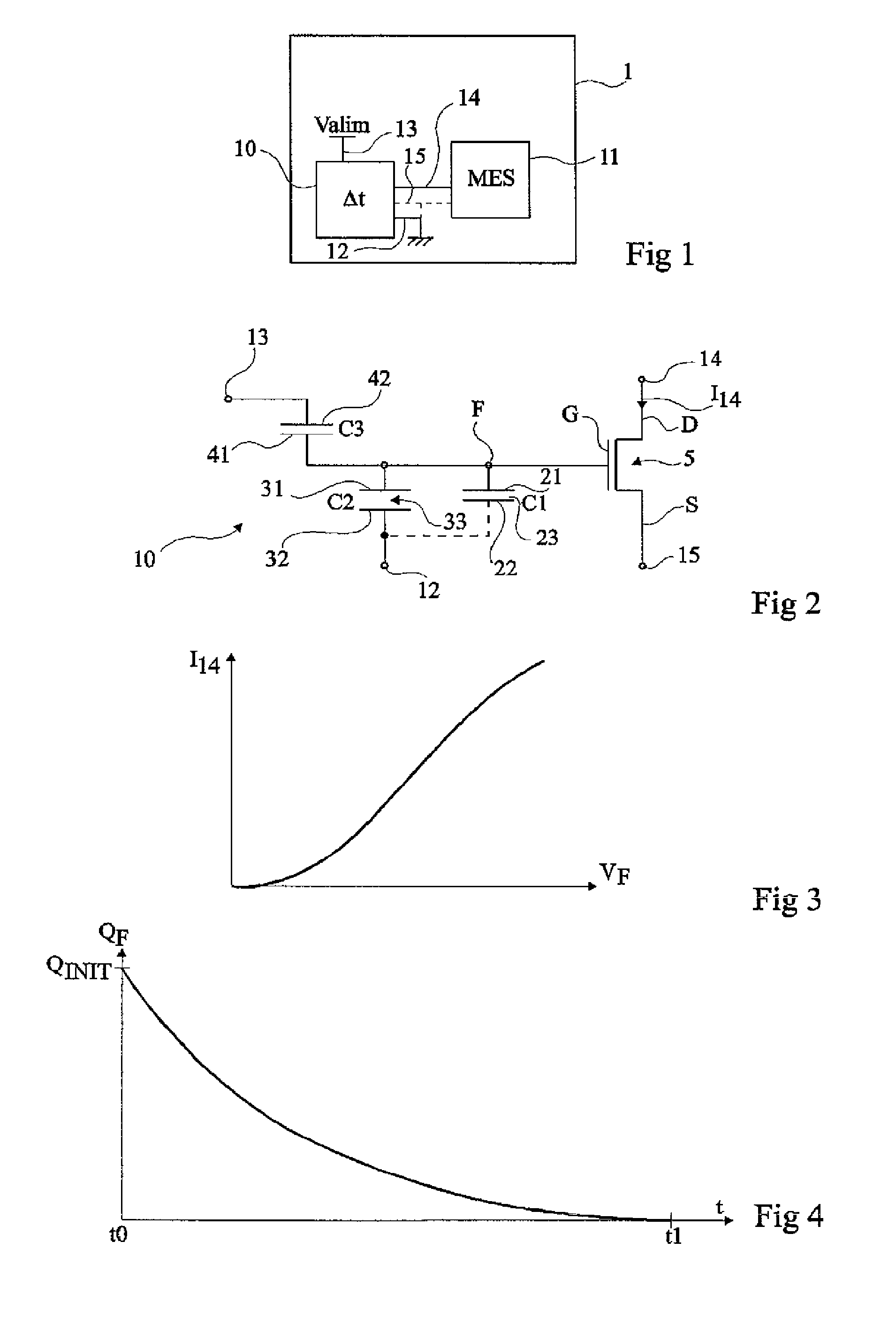

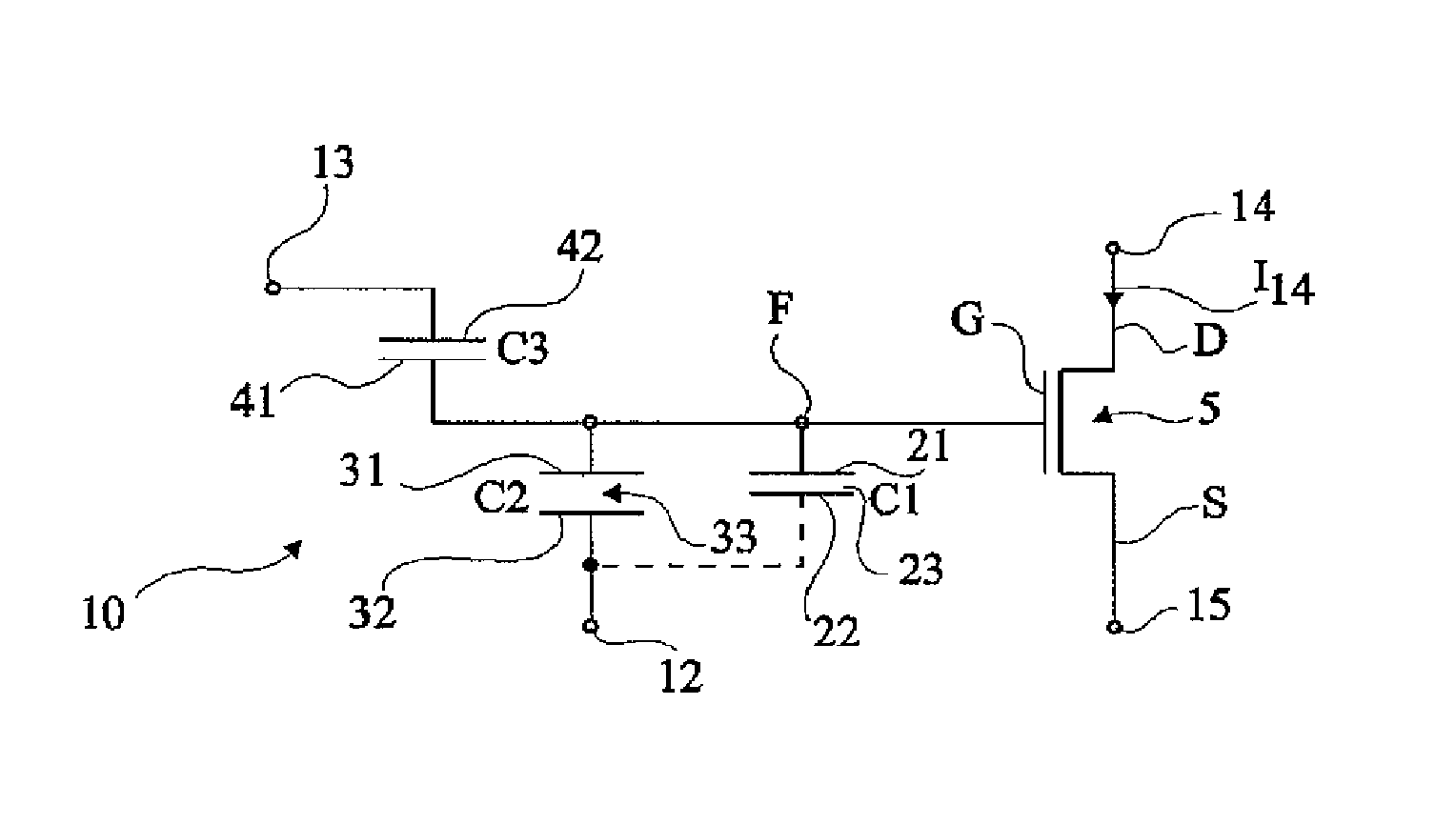

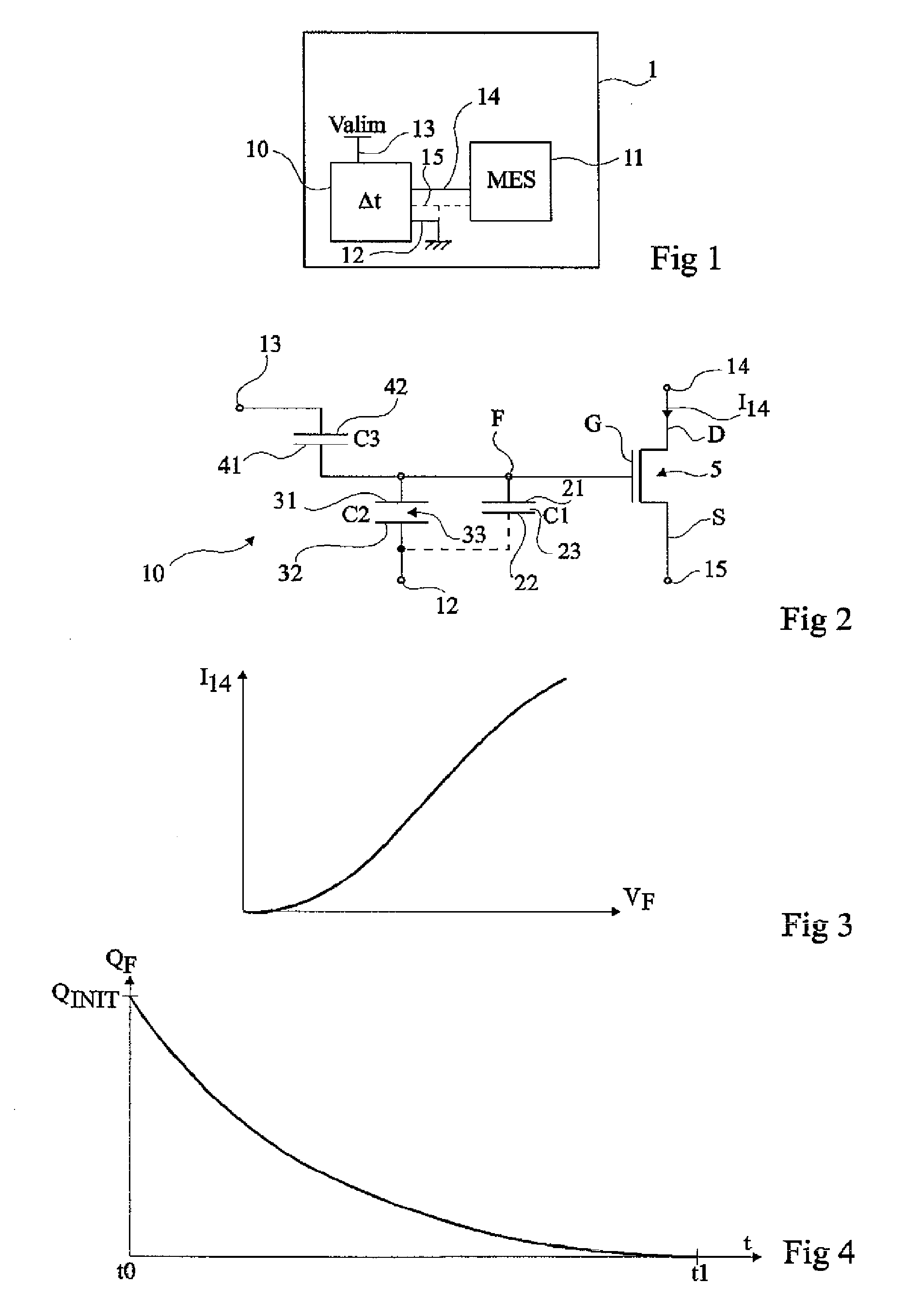

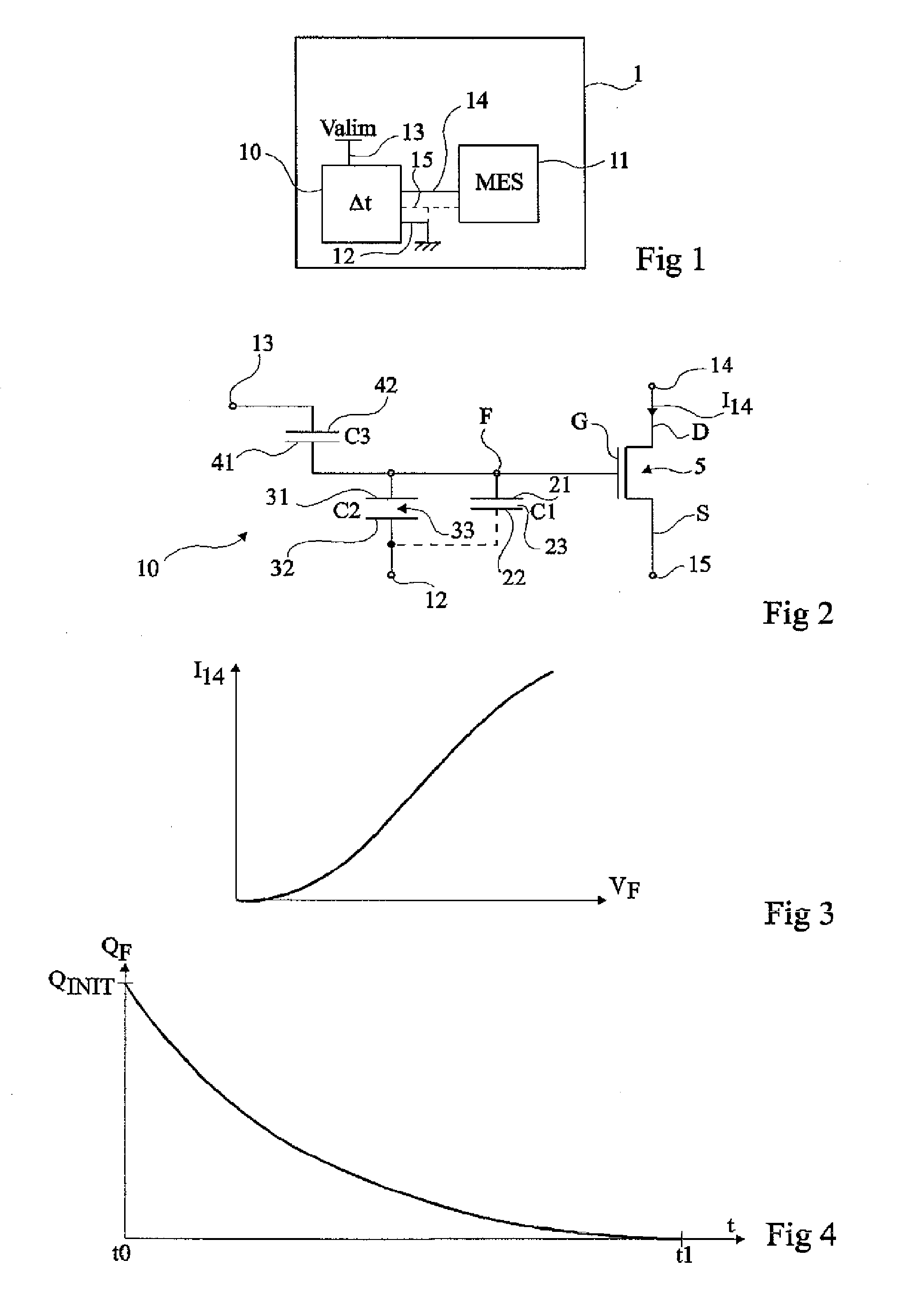

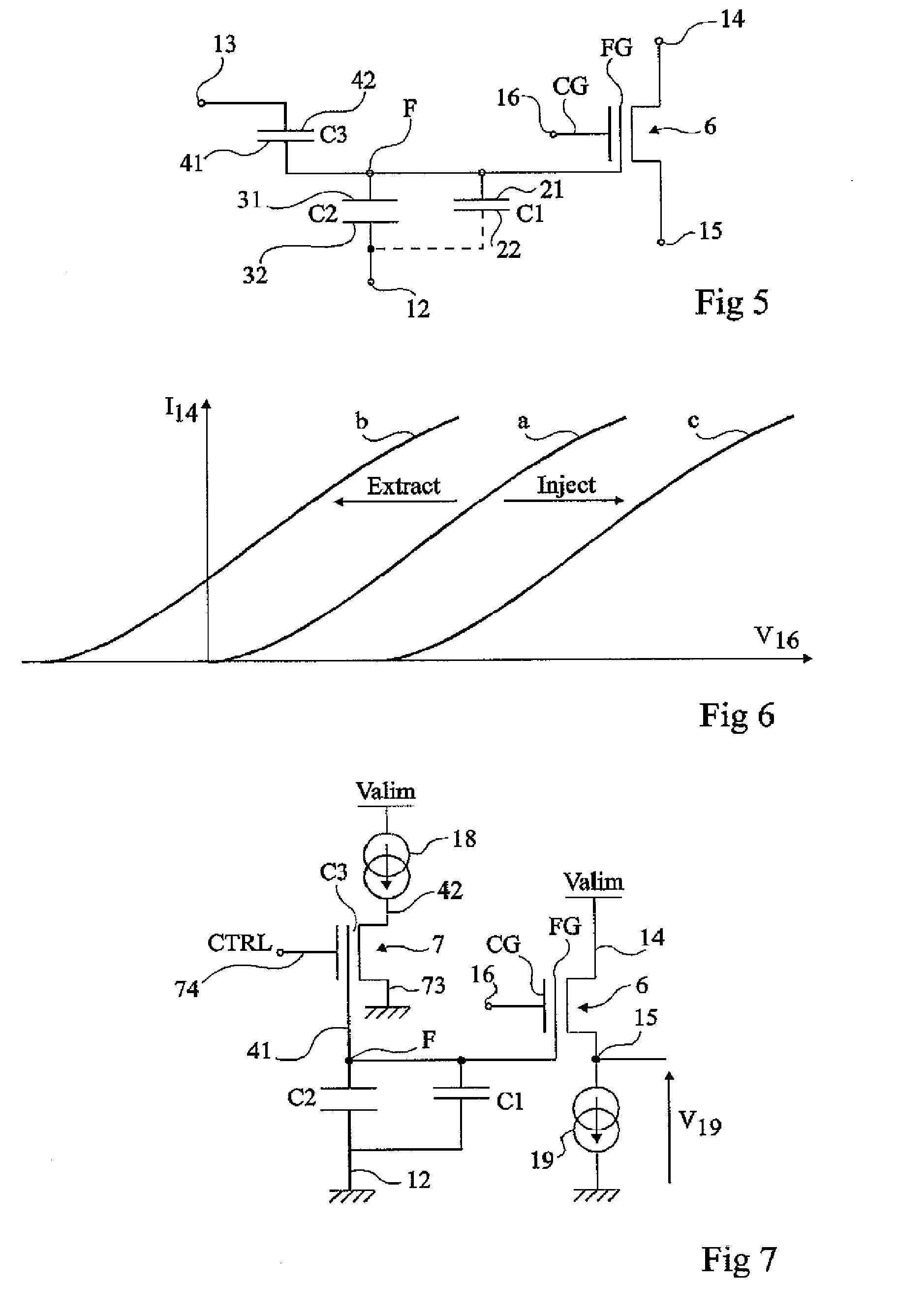

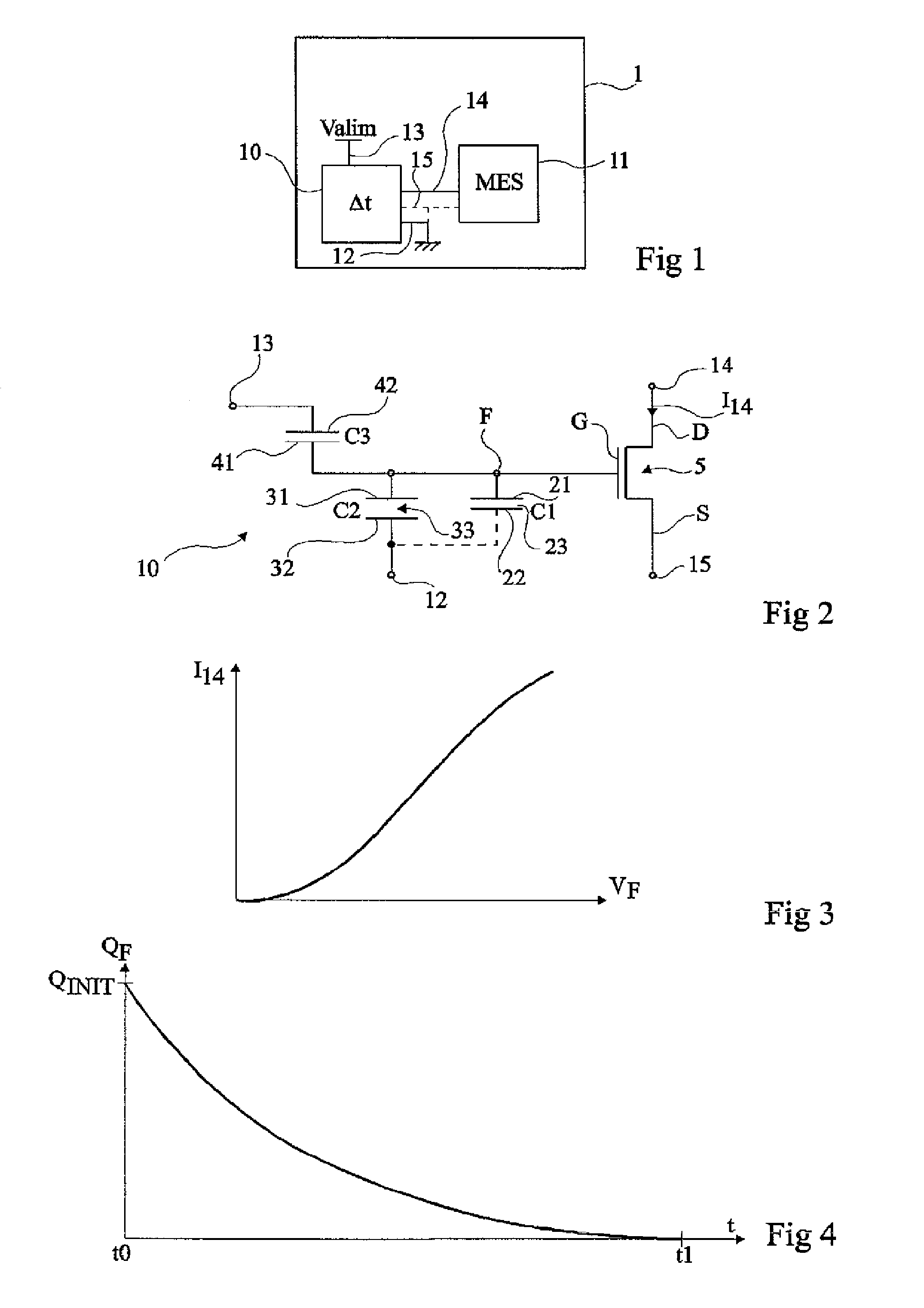

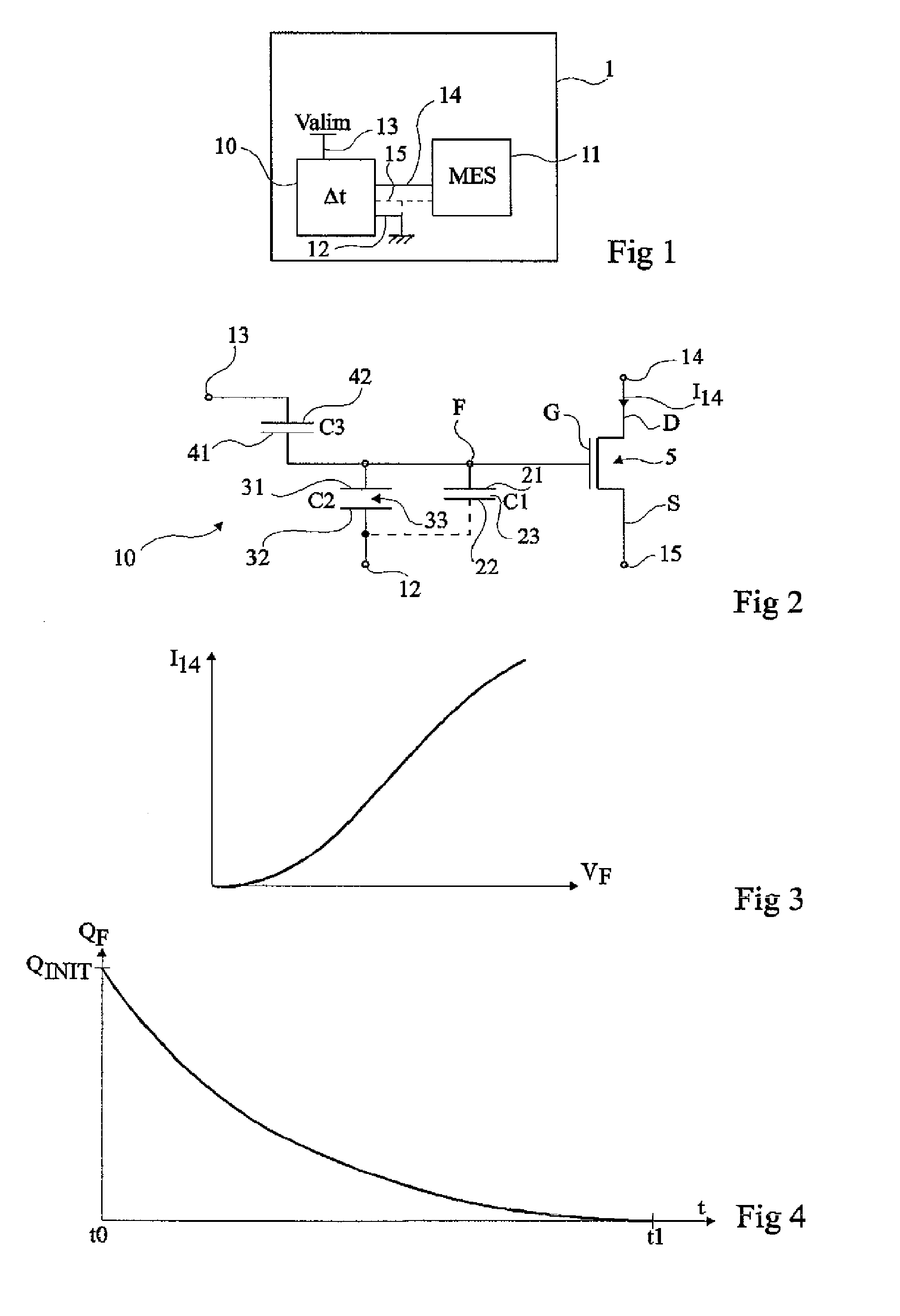

Charge retention circuit for a time measurement

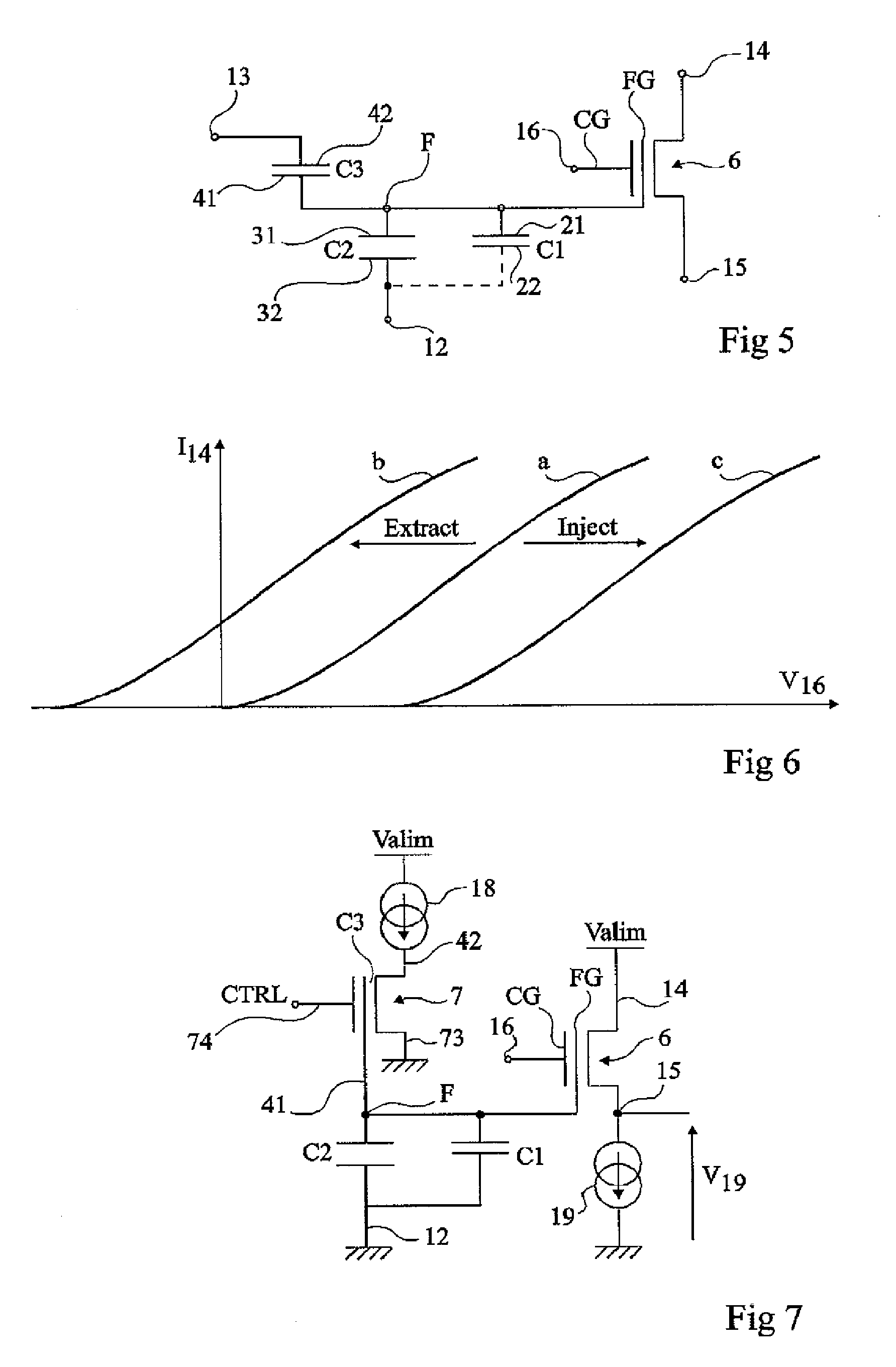

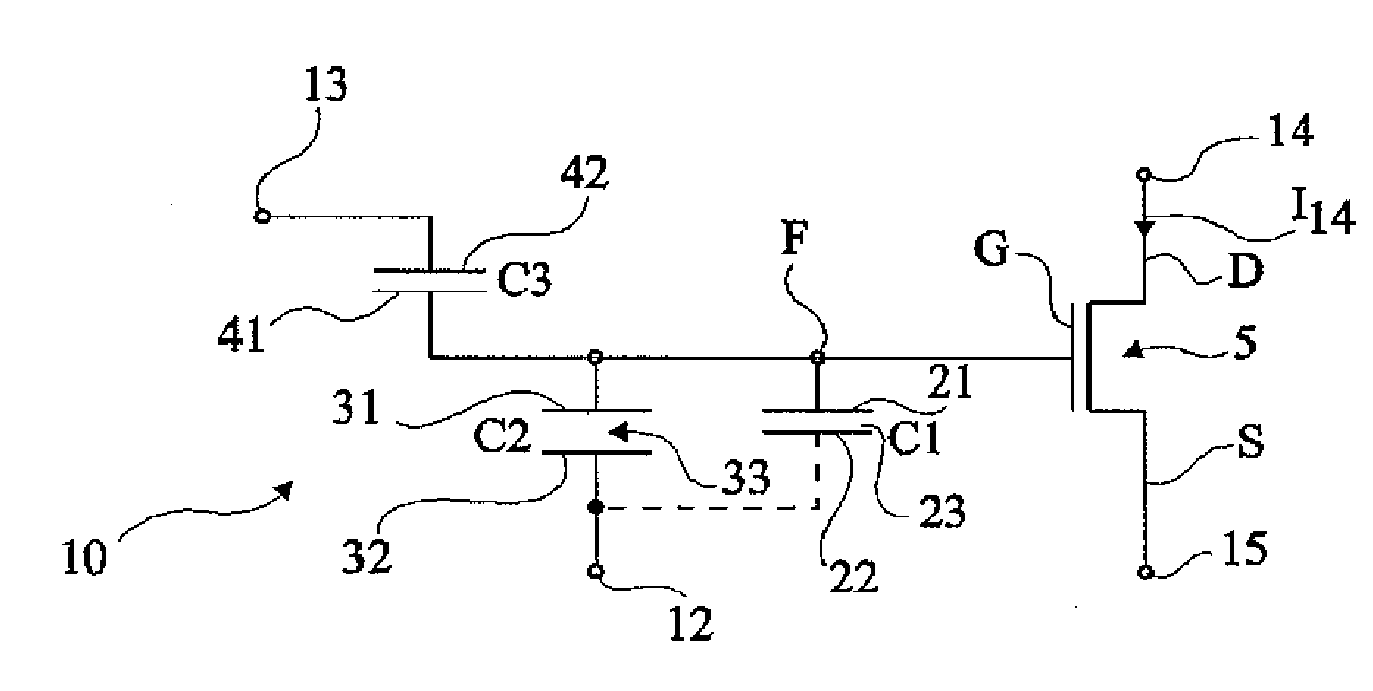

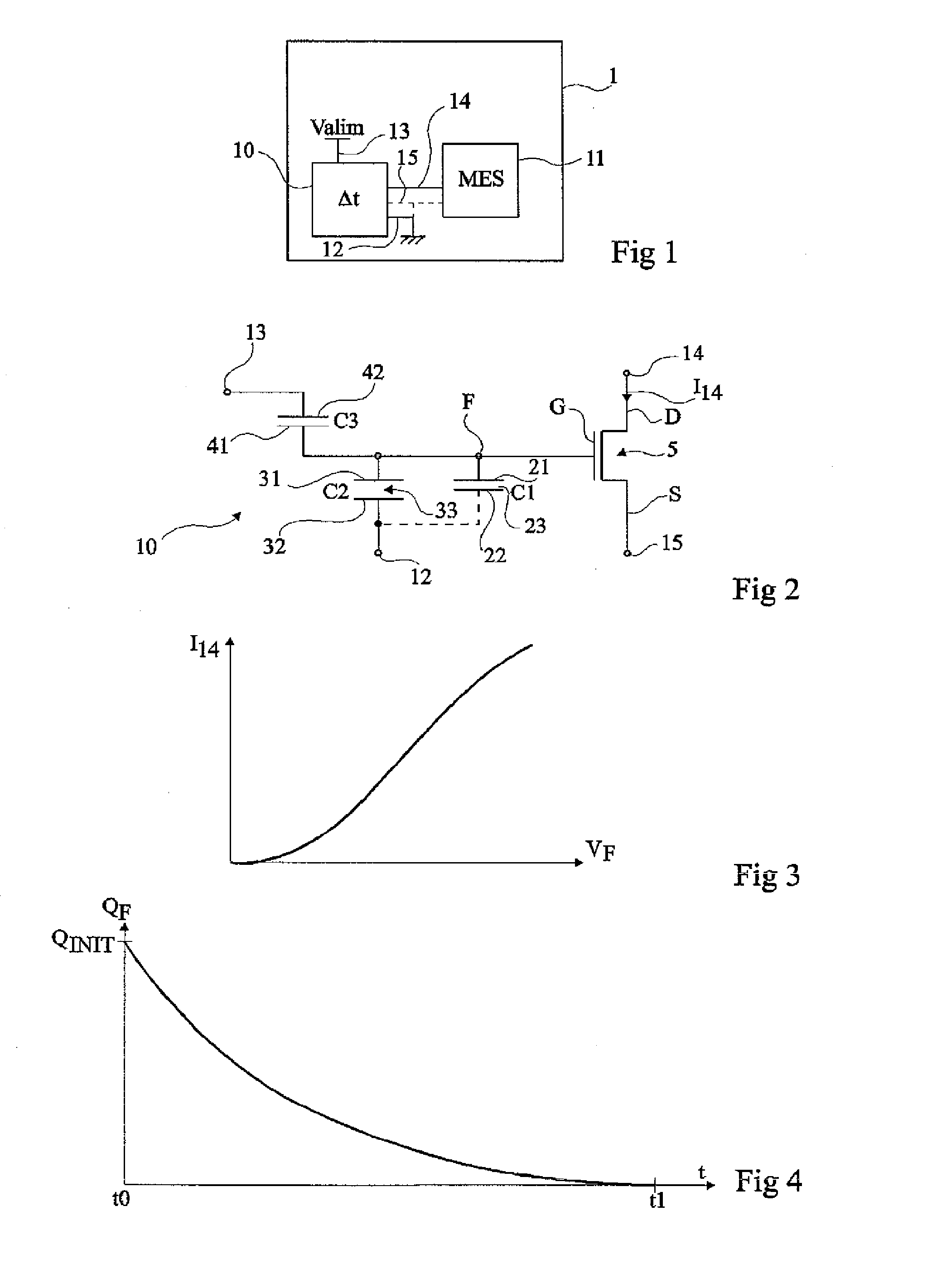

ActiveUS20100020648A1Fast programmingResistance/reactance/impedenceElectric analogue storesCapacitanceElectricity

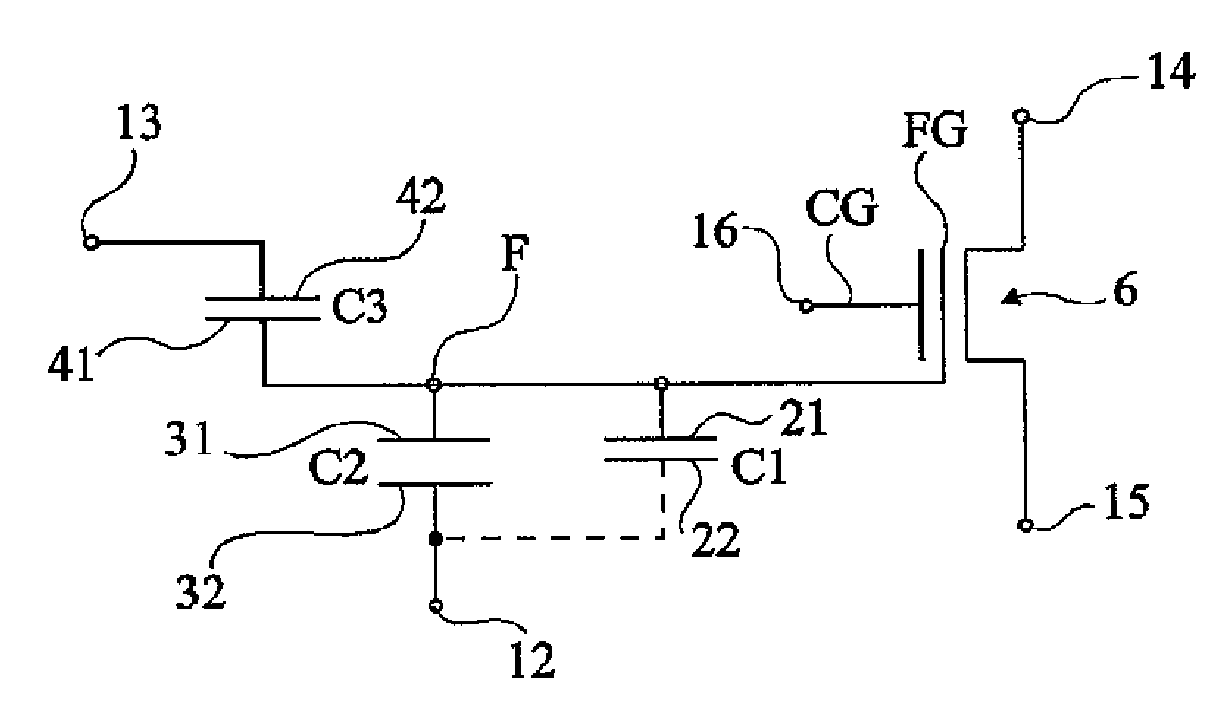

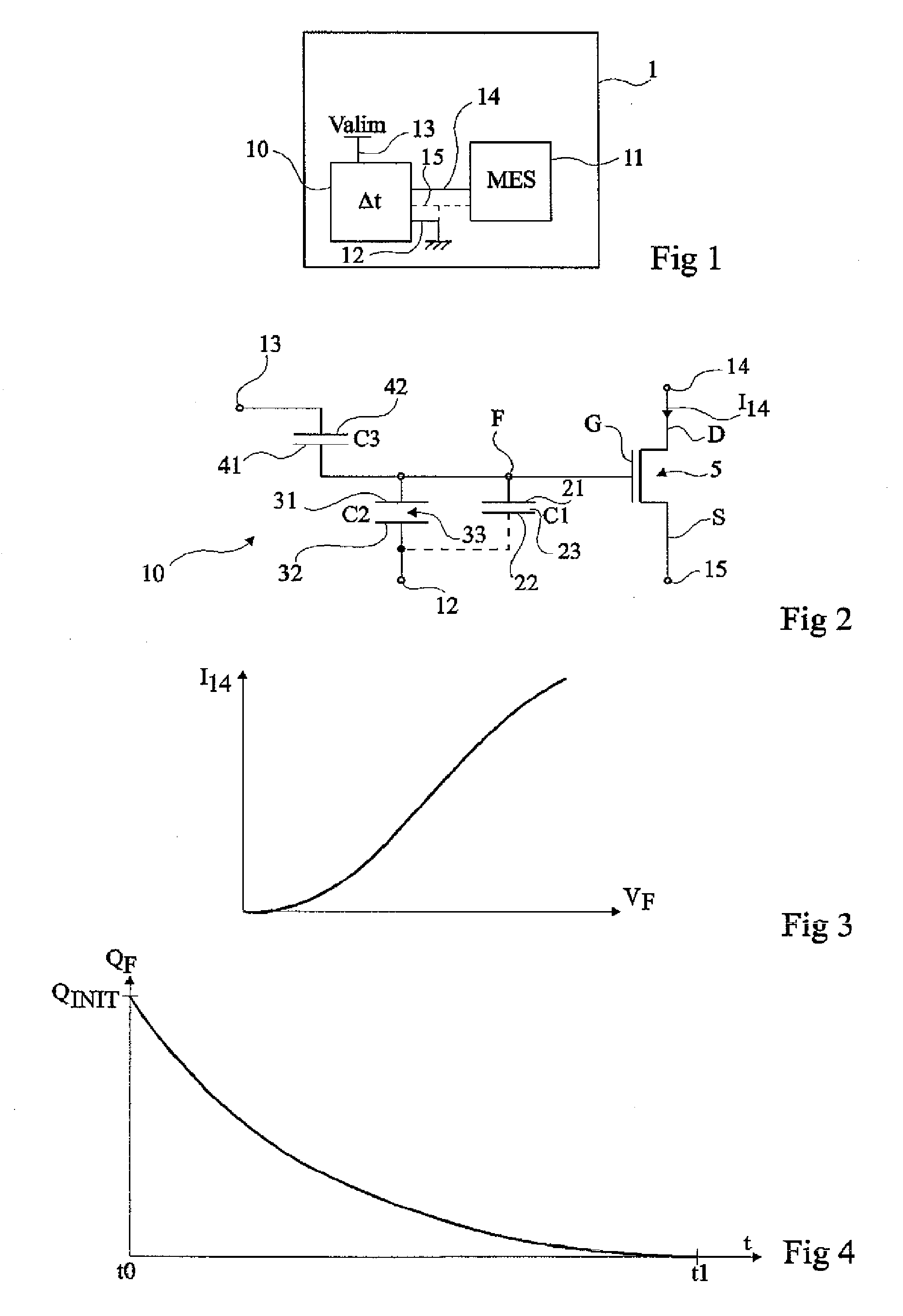

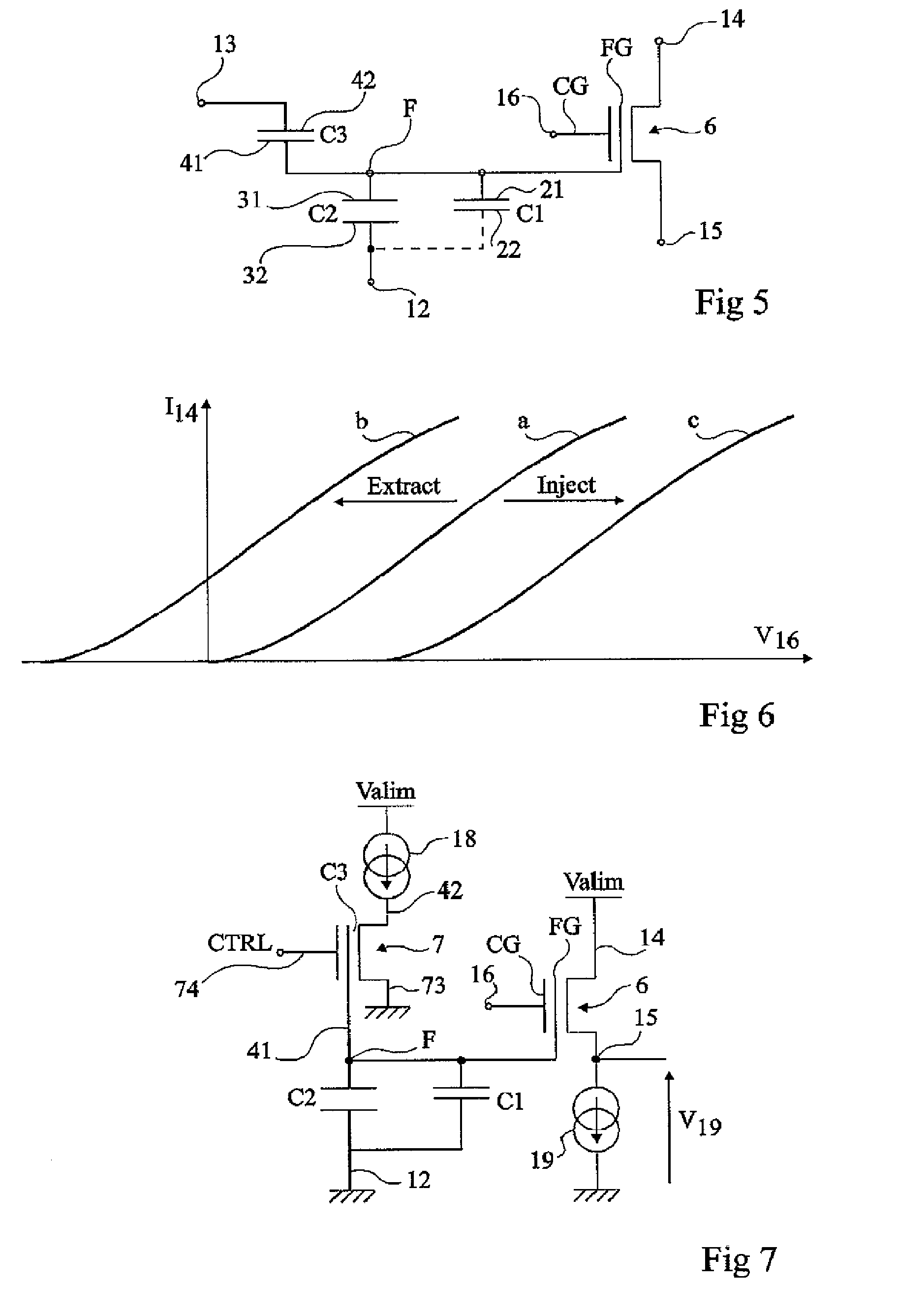

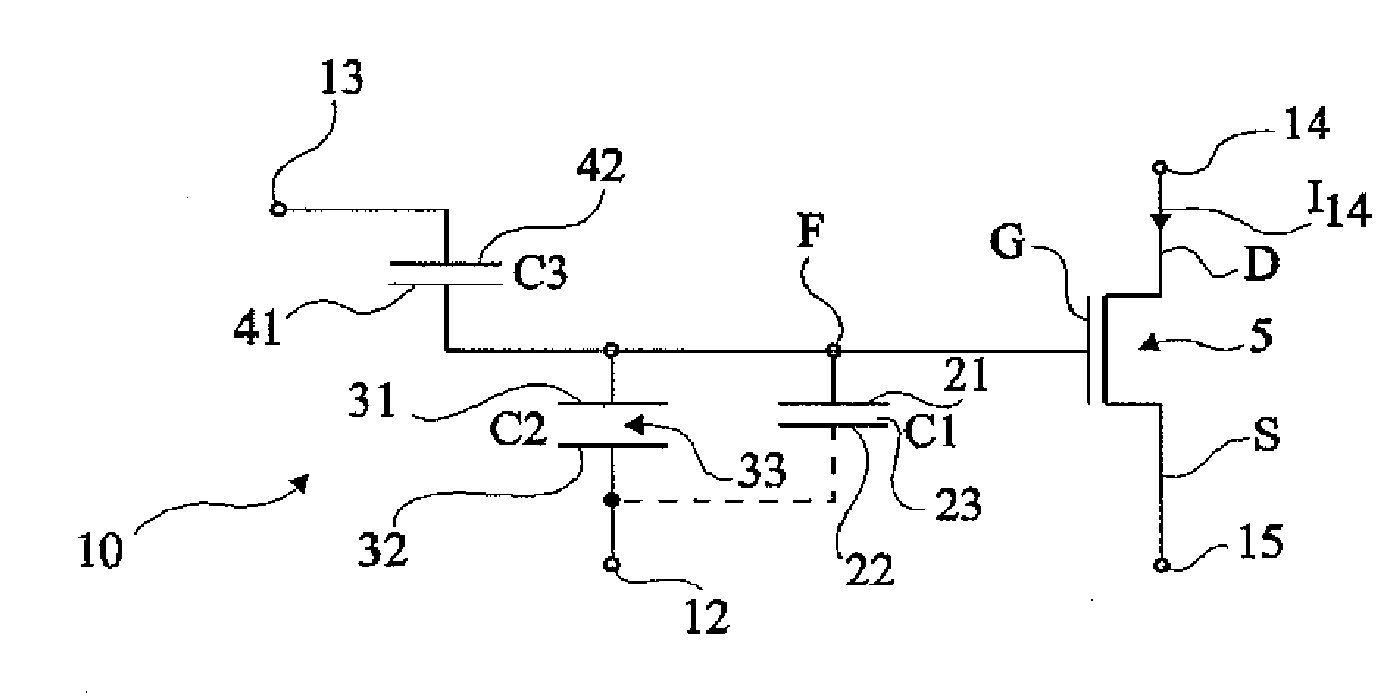

An electronic charge retention circuit for time measurement, including: at least a first capacitive element, a first electrode of which is connected to a floating node (F); at least a second capacitive element, a first electrode of which is connected to the floating node, the first capacitive element having a leakage through its dielectric space and the second capacitive element having a capacitance greater than the first; and at least a first transistor having an isolated control terminal connected to the floating node.

Owner:STMICROELECTRONICS SRL

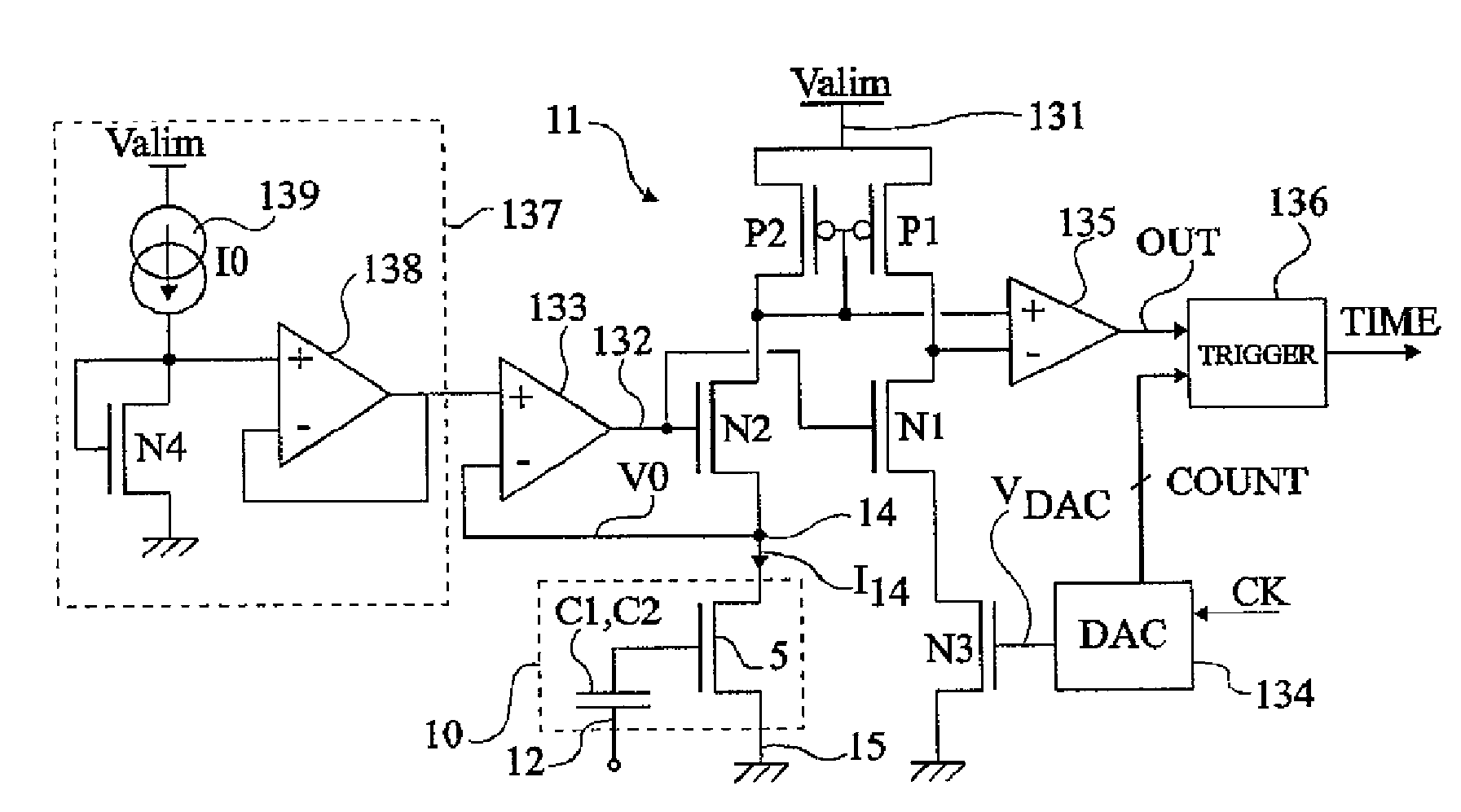

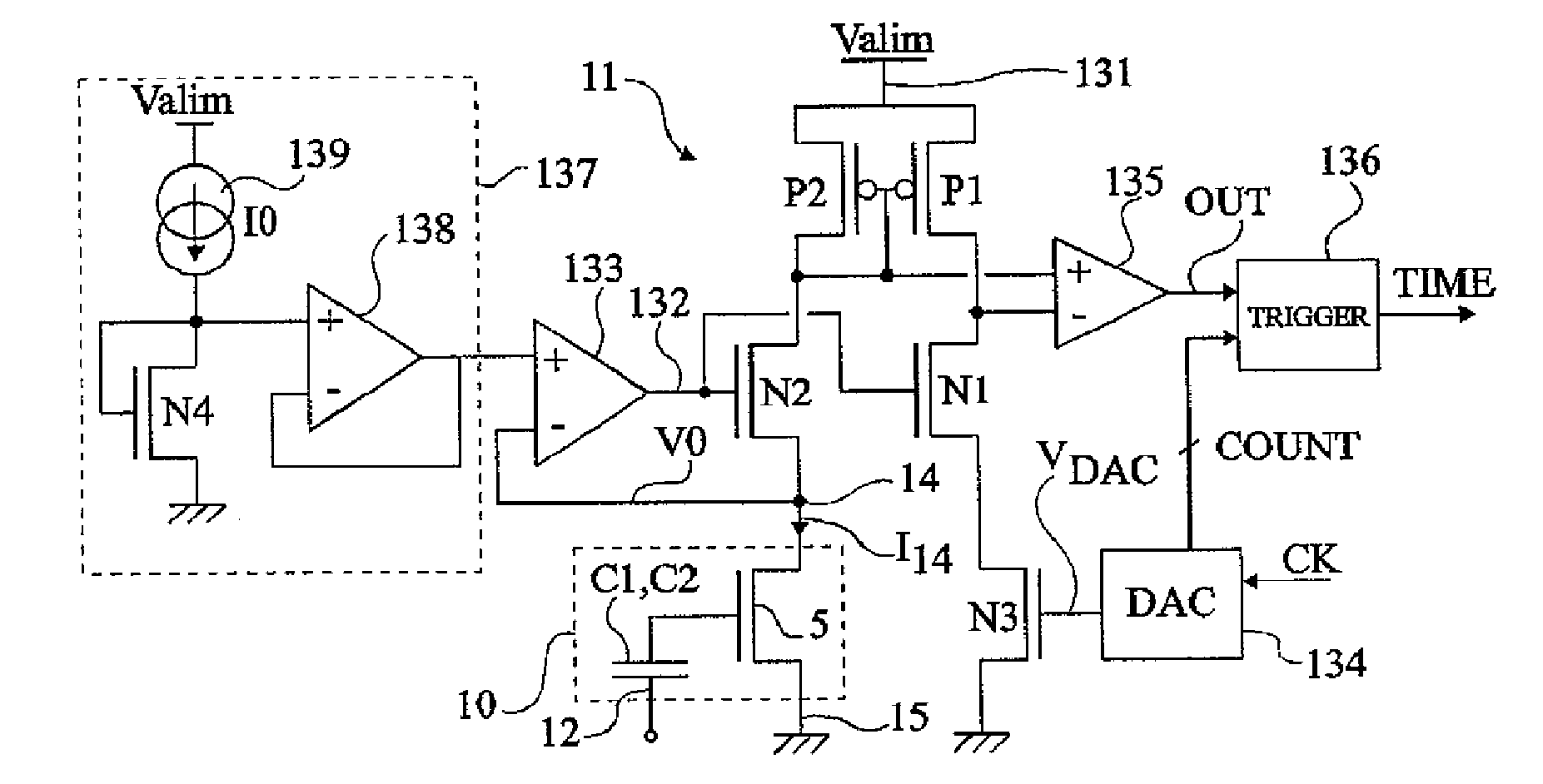

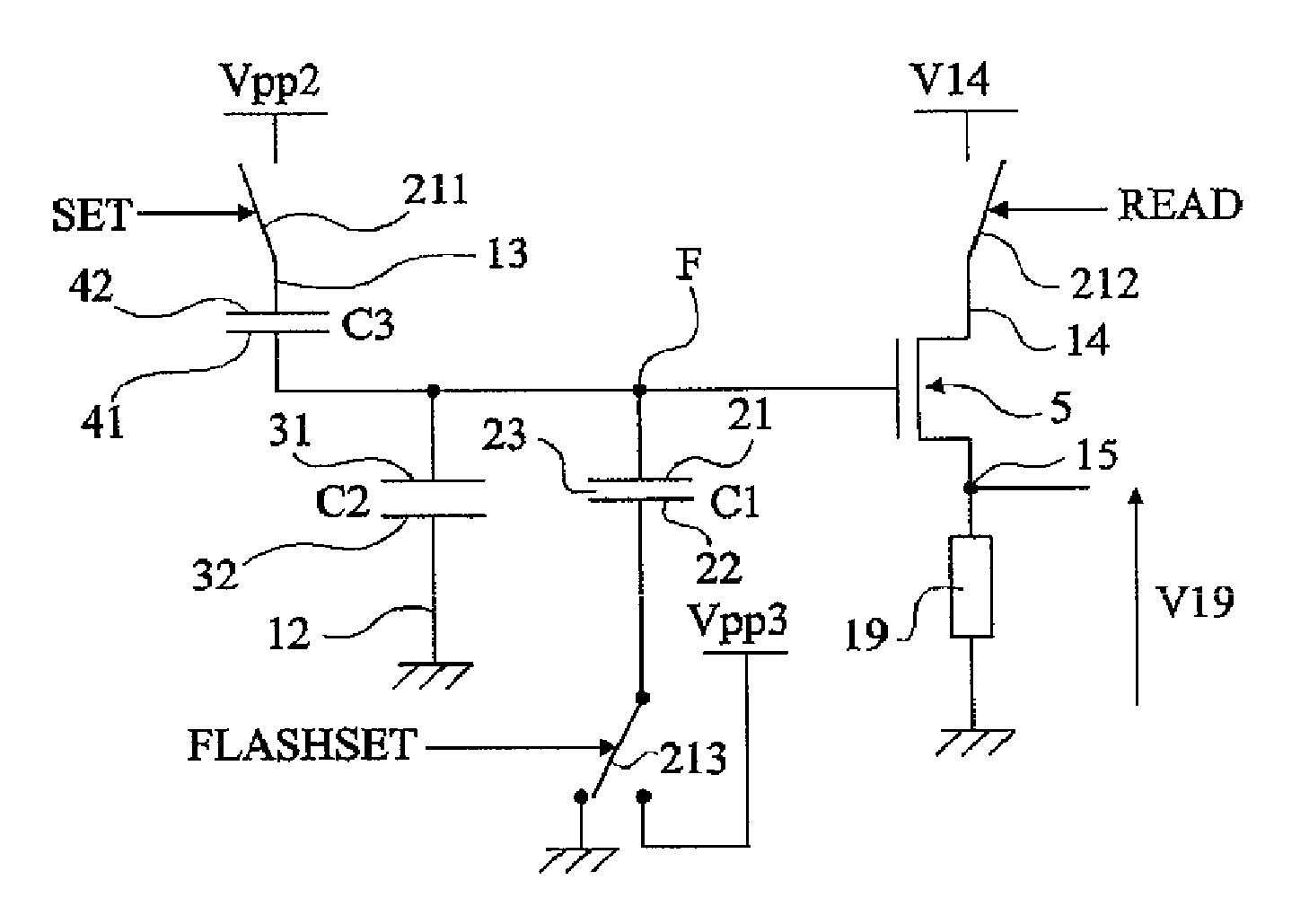

Circuit for reading a charge retention element for a time measurement

ActiveUS8036020B2Fast programmingDigital storageMeasurement by measuring electric/magnetic quantity changeCapacitanceCharge retention

A method and a circuit for reading an electronic charge retention element for a temporal measurement, of the type including at least one capacitive element whose dielectric exhibits a leakage and a transistor with insulated control terminal for reading the residual charges, the reading circuit including; two parallel branches between two supply terminals, each branch including at least one transistor of a first type and one transistor of a second type, the transistor of the second type of one of the branches consisting of that of the element to be read and the transistor of the second type of the other branch receiving, on its control terminal, a staircase signal, the respective drains of the transistors of the first type being connected to the respective inputs of a comparator whose output provides an indication of the residual voltage in the charge retention element.

Owner:STMICROELECTRONICS SRL

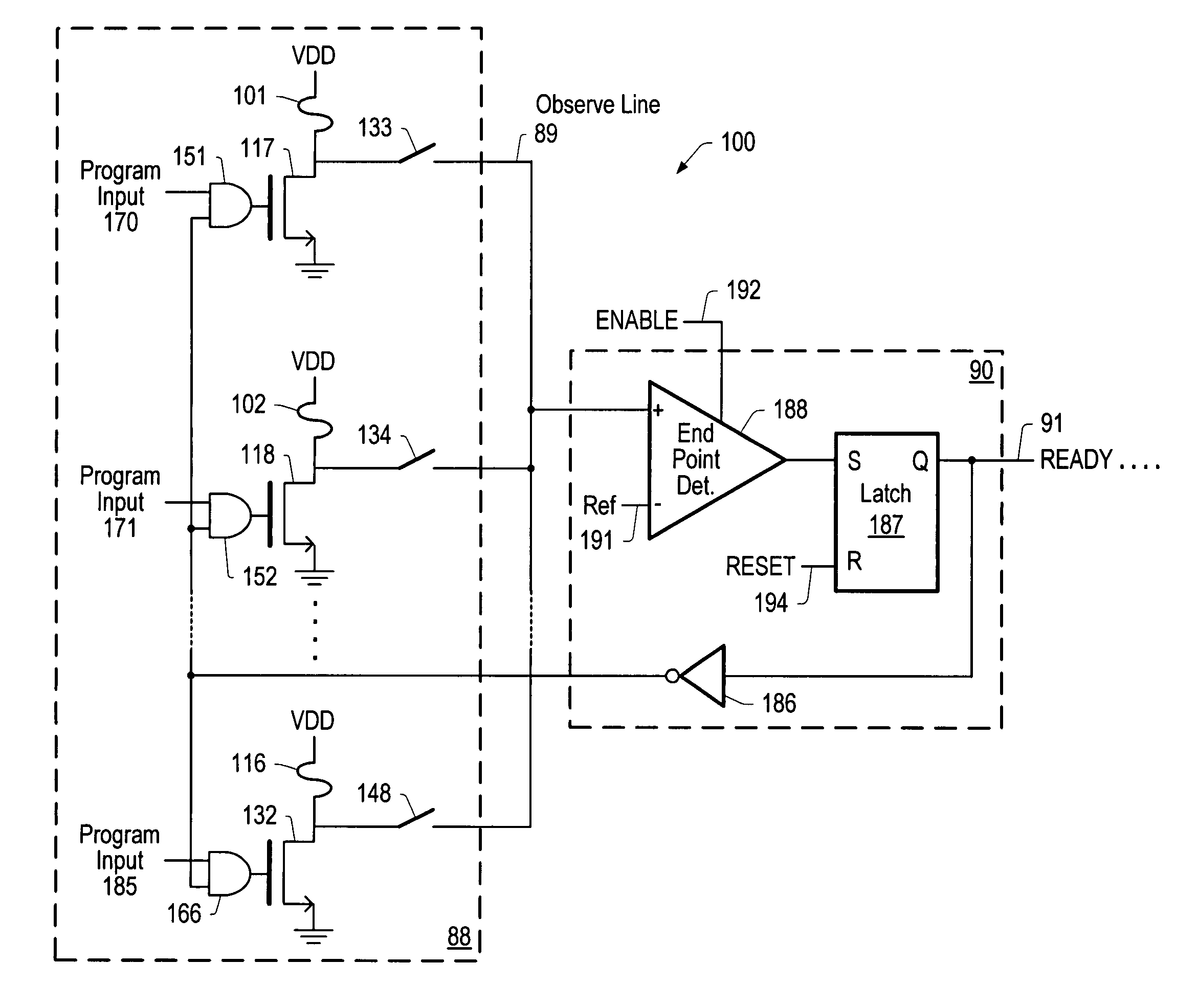

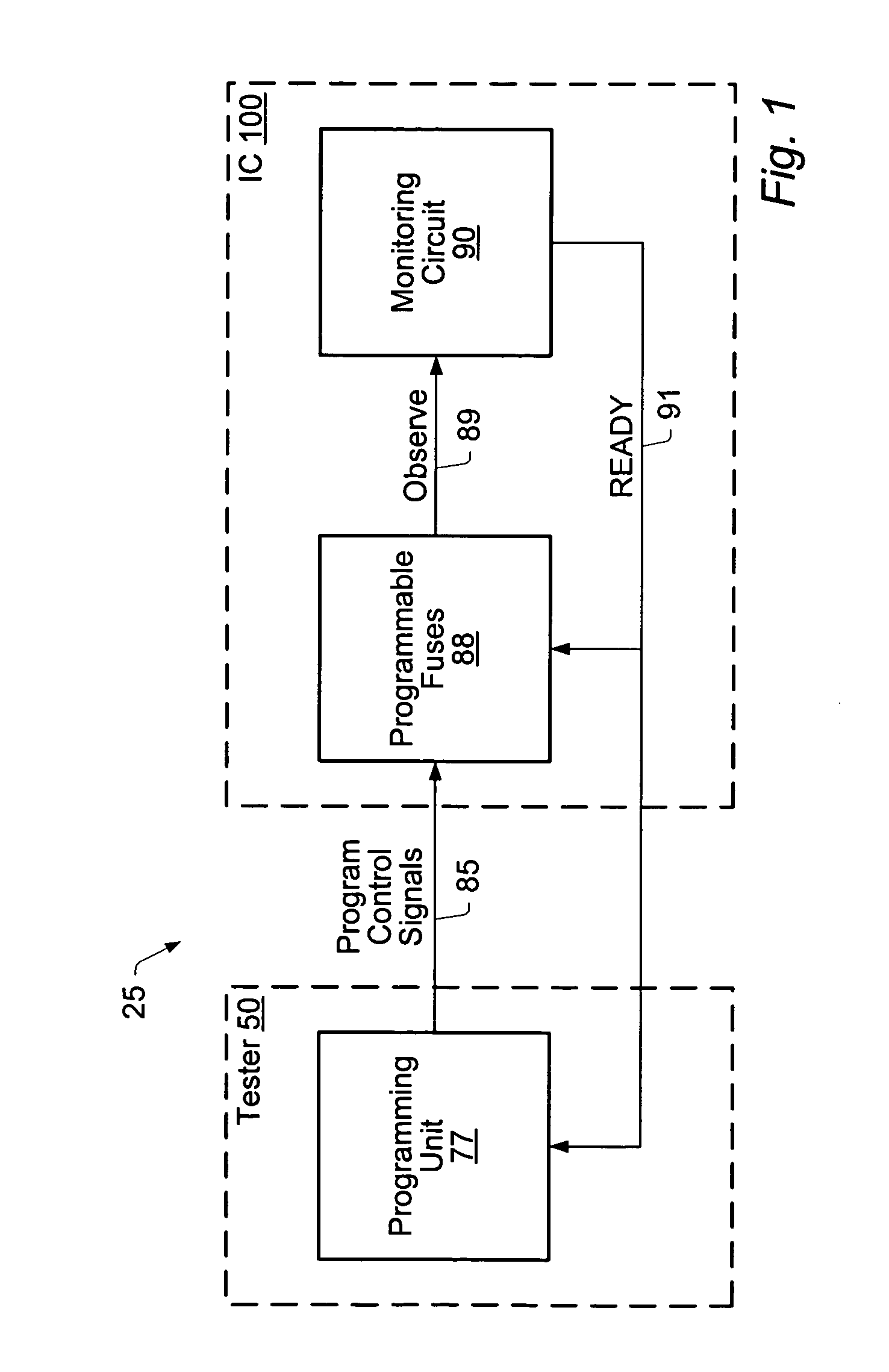

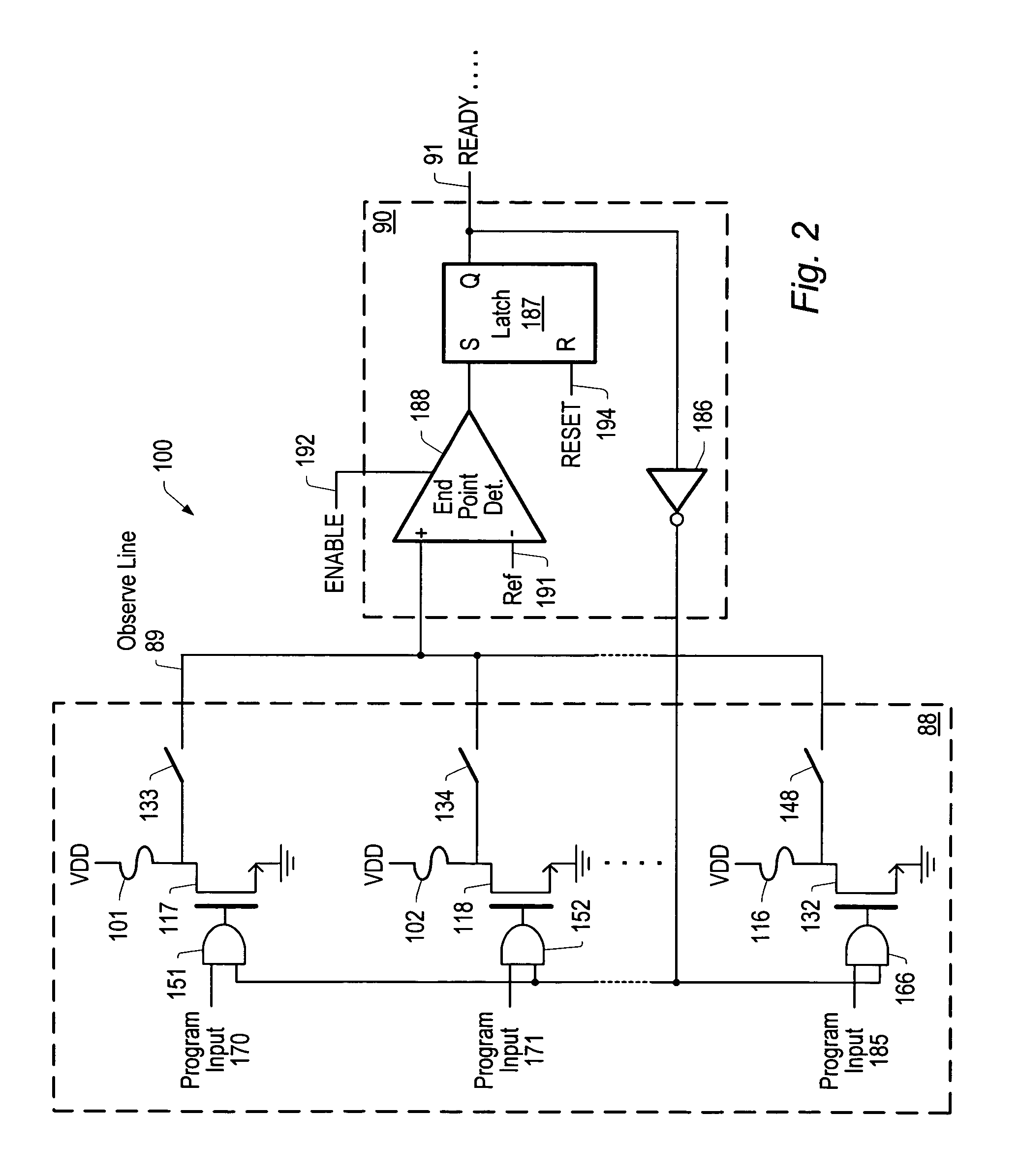

Method and circuit for fuse programming and endpoint detection

ActiveUS7009443B2Improve the immunityAvoid damageRead-only memoriesHeating/cooling contact switchesControl signalEngineering

In one embodiment, a system comprises a programming unit coupled to at least one programmable fuse and configured to program the programmable fuse. In addition, the system comprises a monitoring circuit coupled to the programmable fuse and configured to monitor electrical characteristics associated with the programmable fuse while the programmable fuse is being programmed. In one embodiment, the monitoring circuit is configured to detect a voltage associated with the programmable fuse. Furthermore, the monitoring circuit is configured to compare the detected voltage associated with the programmable fuse with a predetermined voltage value (i.e., endpoint detection). If the detected voltage is equal to or less than the predetermined voltage value, the monitoring circuit is configured to change a state of a control signal to stop the programming of the programmable fuse. Otherwise, the programming unit continues to program the programmable fuse.

Owner:MICROCHIP TECH INC

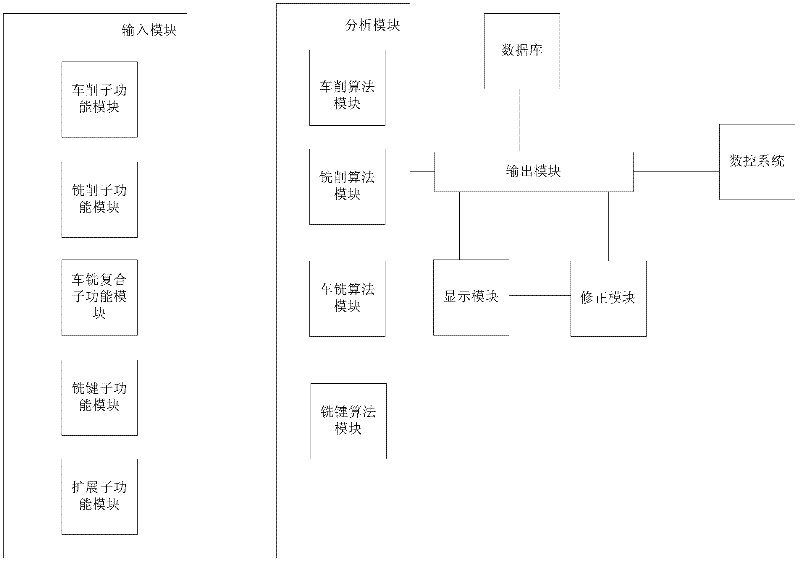

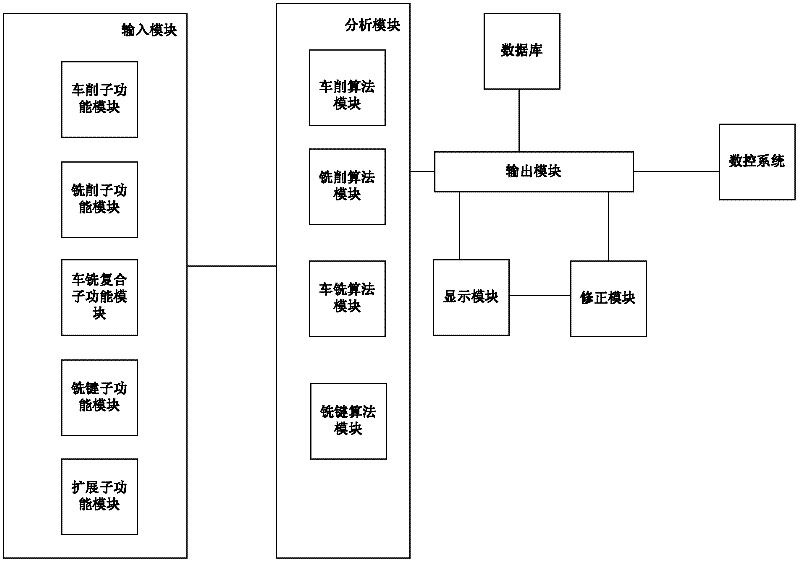

A System for Automatically Generating NC Machining Codes

ActiveCN102298360AChanging the State of CNC ProgrammingAvoid negligenceProgramme controlComputer controlEmbedded systemNumerical control system

The invention discloses an automatic numerical control machining code generating system, which comprises an input module, an analysis module, a database, an output module, a display module and a correction module, wherein the input module is connected with the analysis module, the analysis module is connected with the output module, and the output module is respectively connected with the database, the display module, the correction module and a numerical control system; and the display module is connected with the correction module. Firstly, submodules in the input module are manually selected according to parts to be machined, parameters are input into the selected submodules and then the input parameters are transmitted to corresponding algorithm modules in the analysis module; and theanalysis module selects the corresponding algorithm modules according to the received parameters and conducts analysis to generate numerical control codes which are transmitted to the numerical control system through the output module. Since standard numerical control code frames which are preset in the algorithm modules in the analysis module are necessary for the numerical control system, the format of the automatically generated numerical control codes is consistent with the numerical control system.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Charge retention circuit for a time measurement

ActiveUS8331203B2Fast programmingResistance/reactance/impedenceElectric analogue storesElectricityCapacitance

An electronic charge retention circuit for time measurement, including: at least a first capacitive element, a first electrode of which is connected to a floating node (F); at least a second capacitive element, a first electrode of which is connected to the floating node, the first capacitive element having a leakage through its dielectric space and the second capacitive element having a capacitance greater than the first; and at least a first transistor having an isolated control terminal connected to the floating node.

Owner:STMICROELECTRONICS SRL

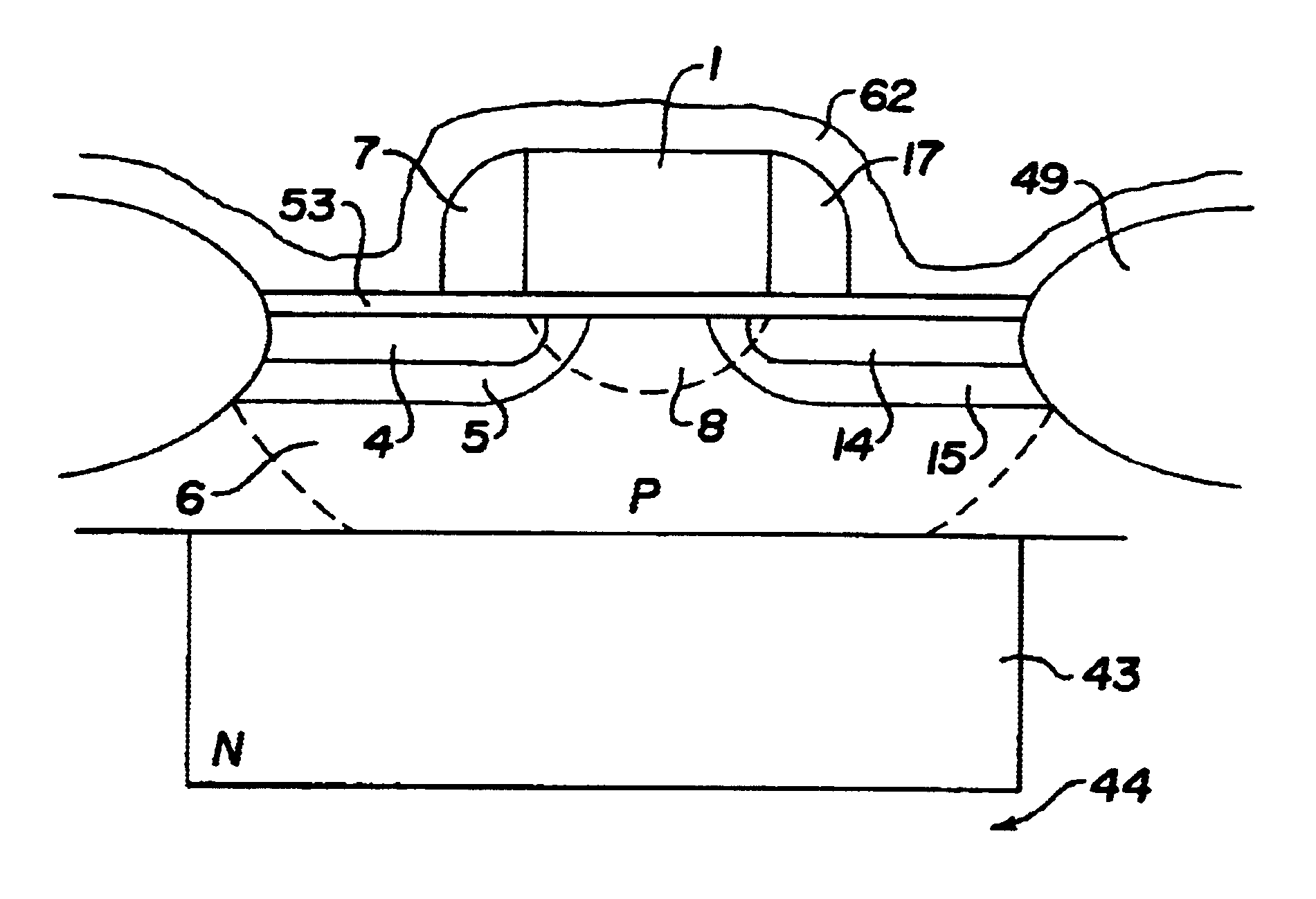

Enhanced EPROM structures with accentuated hot electron generation regions

An EPROM structure includes a NMOS transistor integrated with a capacitor. The terminal names of the NMOS transistor follow the conventional nomenclature: drain, source, body and gate. The gate of the NMOS transistor is connected directly and exclusively to one of the capacitor plates. In this configuration, the gate is now referred to as the "floating gate". The remaining side of the capacitor is referred to as the "control gate".

Owner:INTERSIL INC

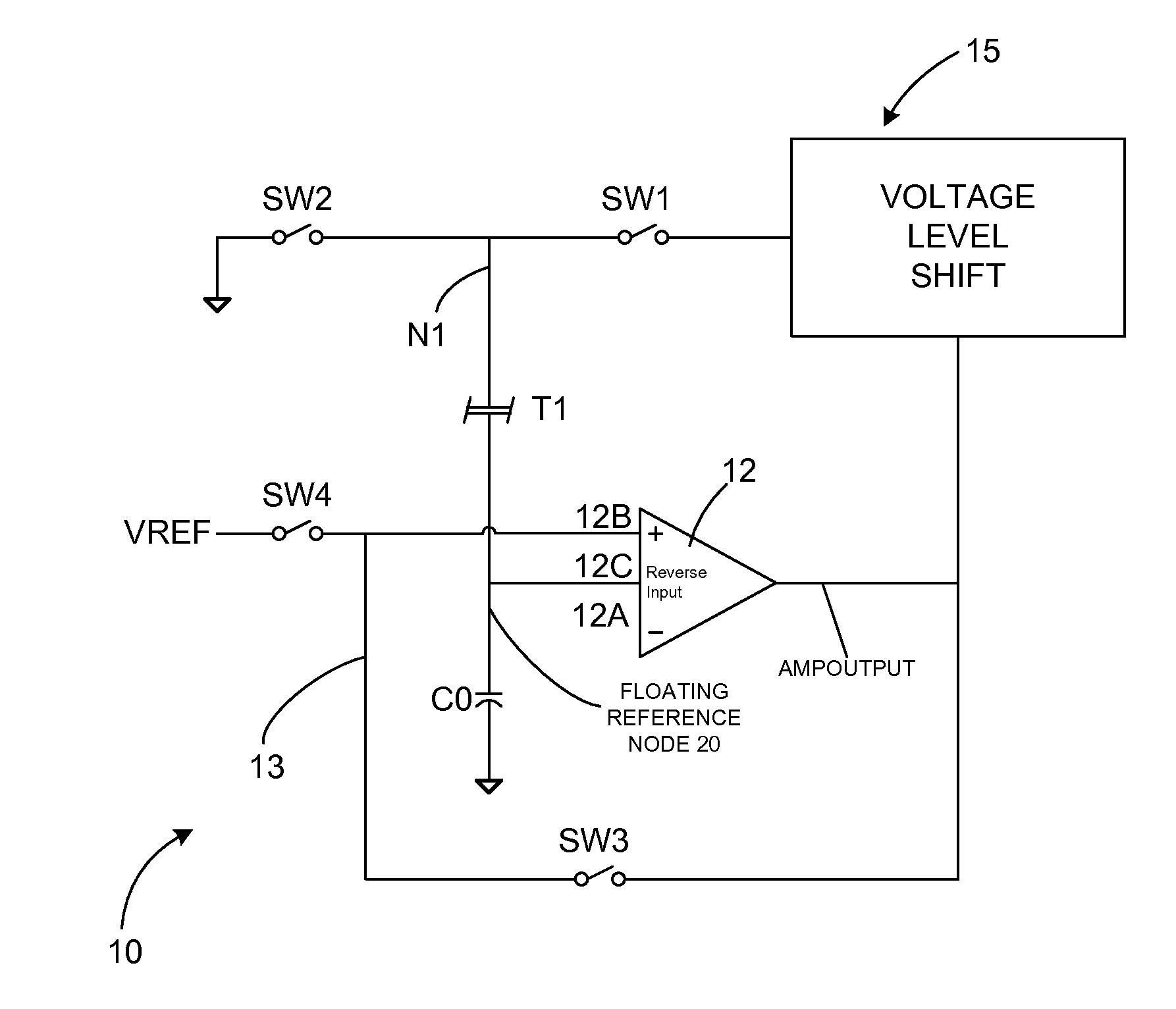

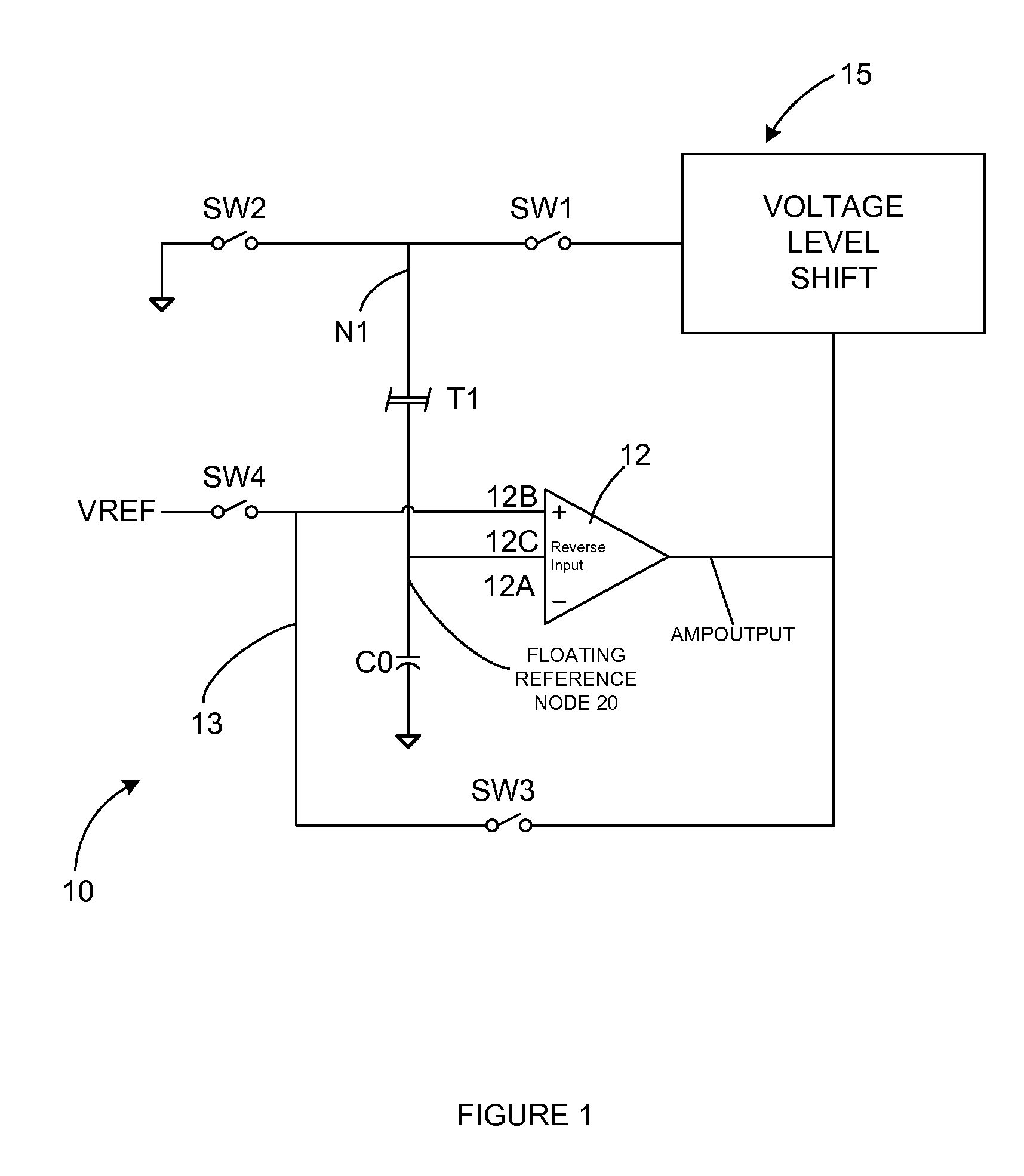

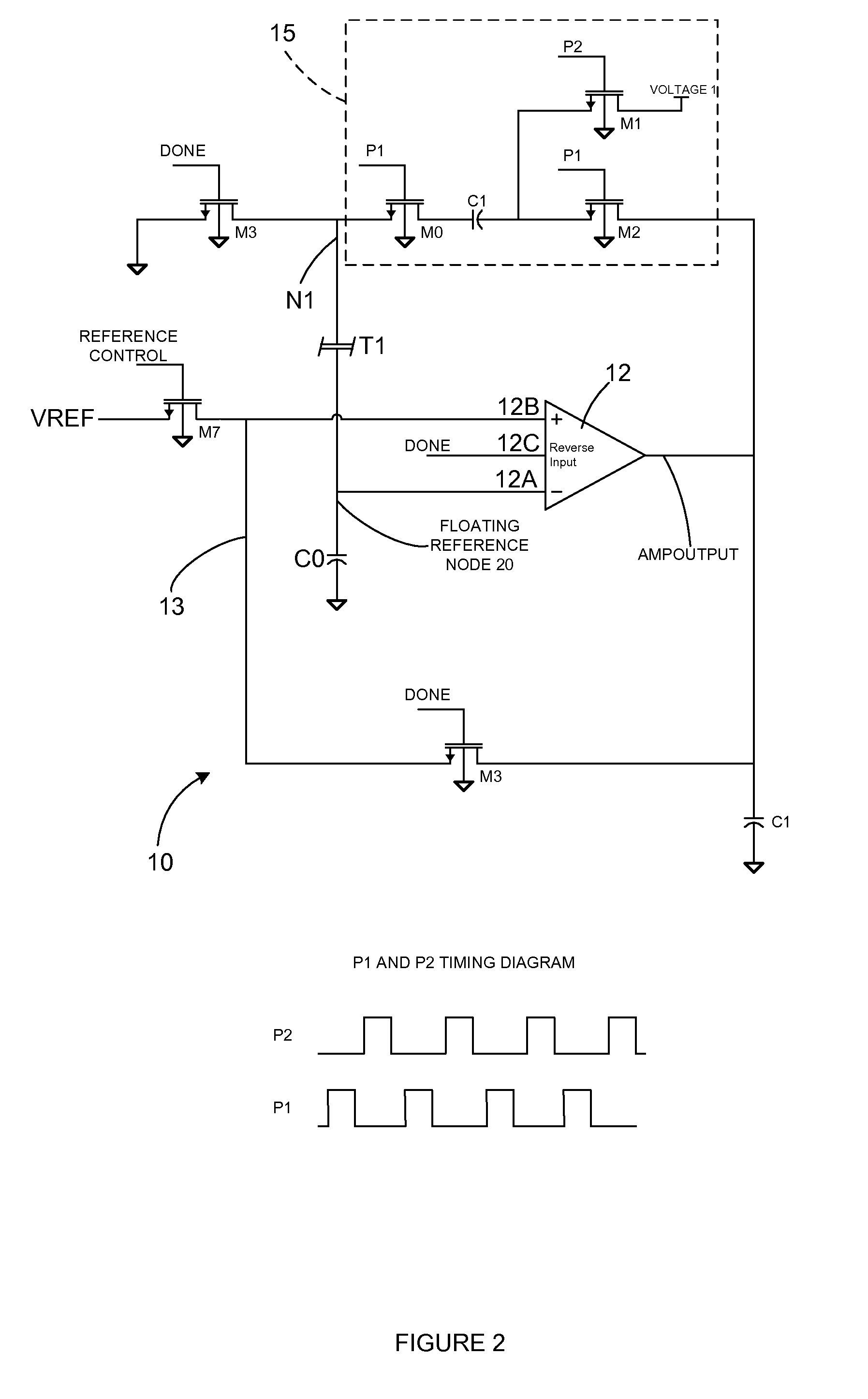

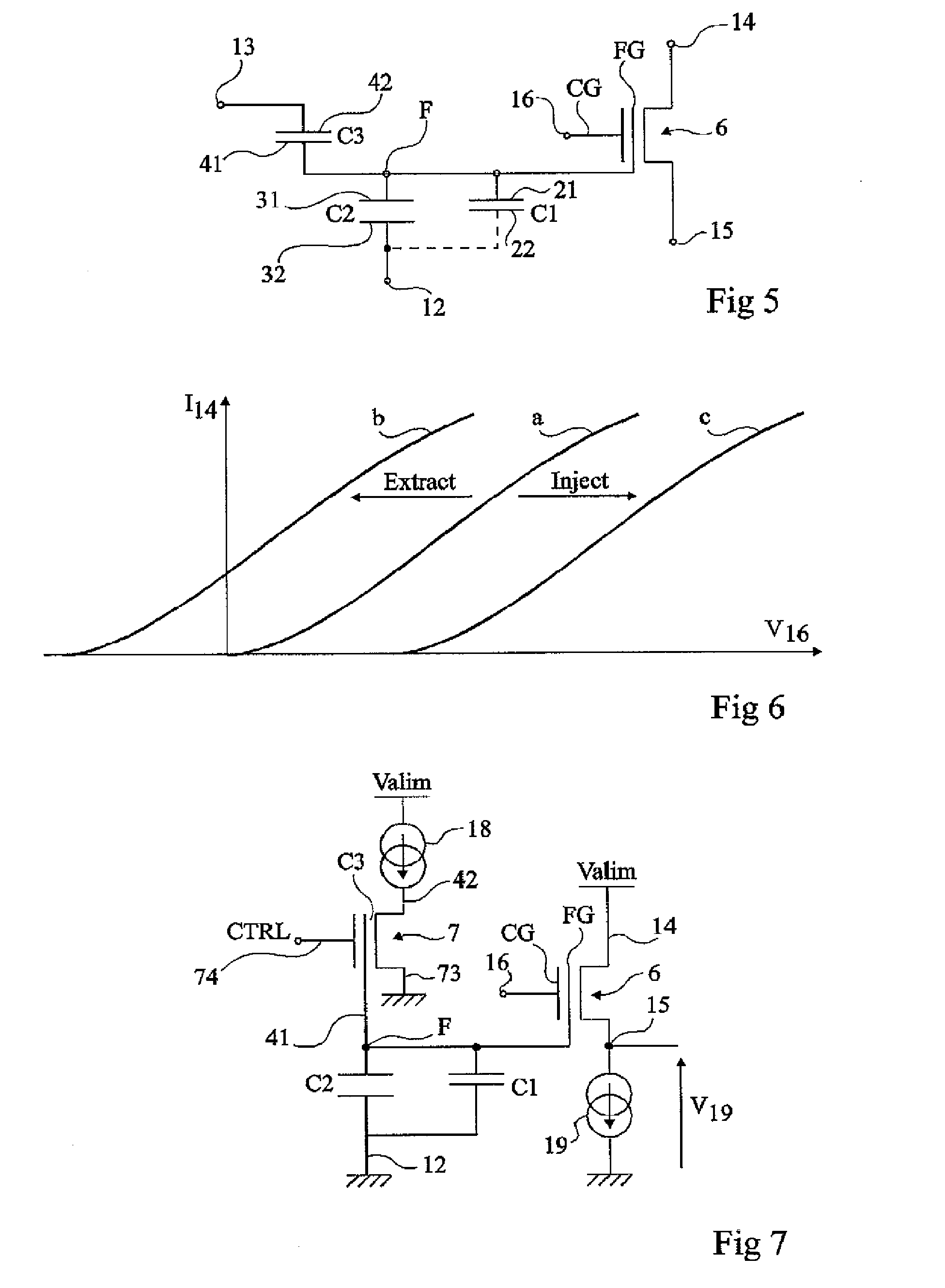

Circuit and system for programming a floating gate

ActiveUS7859911B2Improve accuracyImprove stabilityElectric analogue storesRead-only memoriesHemt circuitsElectrical and Electronics engineering

The invention provides circuits and systems for programming a floating gate. A floating gate tunneling device is used with an analog comparing device in a circuit having a floating reference node and an offset-mitigating feedback loop for iteratively programming a floating gate, or multiple floating gates.

Owner:TRIUNE IP

Eeprom charge retention circuit for time measurement

An electronic charge retention circuit for time measurement, implanted in an array of EEPROM memory cells, each including a selection transistor in series with a floating-gate transistor, the circuit including, on any one row of memory cells: a first subassembly of at least a first cell, the thickness of the dielectric of the tunnel window of the floating-gate transistor of which is less than that of the other cells; a second subassembly of at least a second cell, the drain and source of the floating-gate transistor of which are interconnected; a third subassembly of at least a third cell; and a fourth subassembly of at least a fourth cell, the tunnel window of which is omitted, the respective floating gates of the transistors of the cells of the four subassemblies being interconnected.

Owner:STMICROELECTRONICS SRL

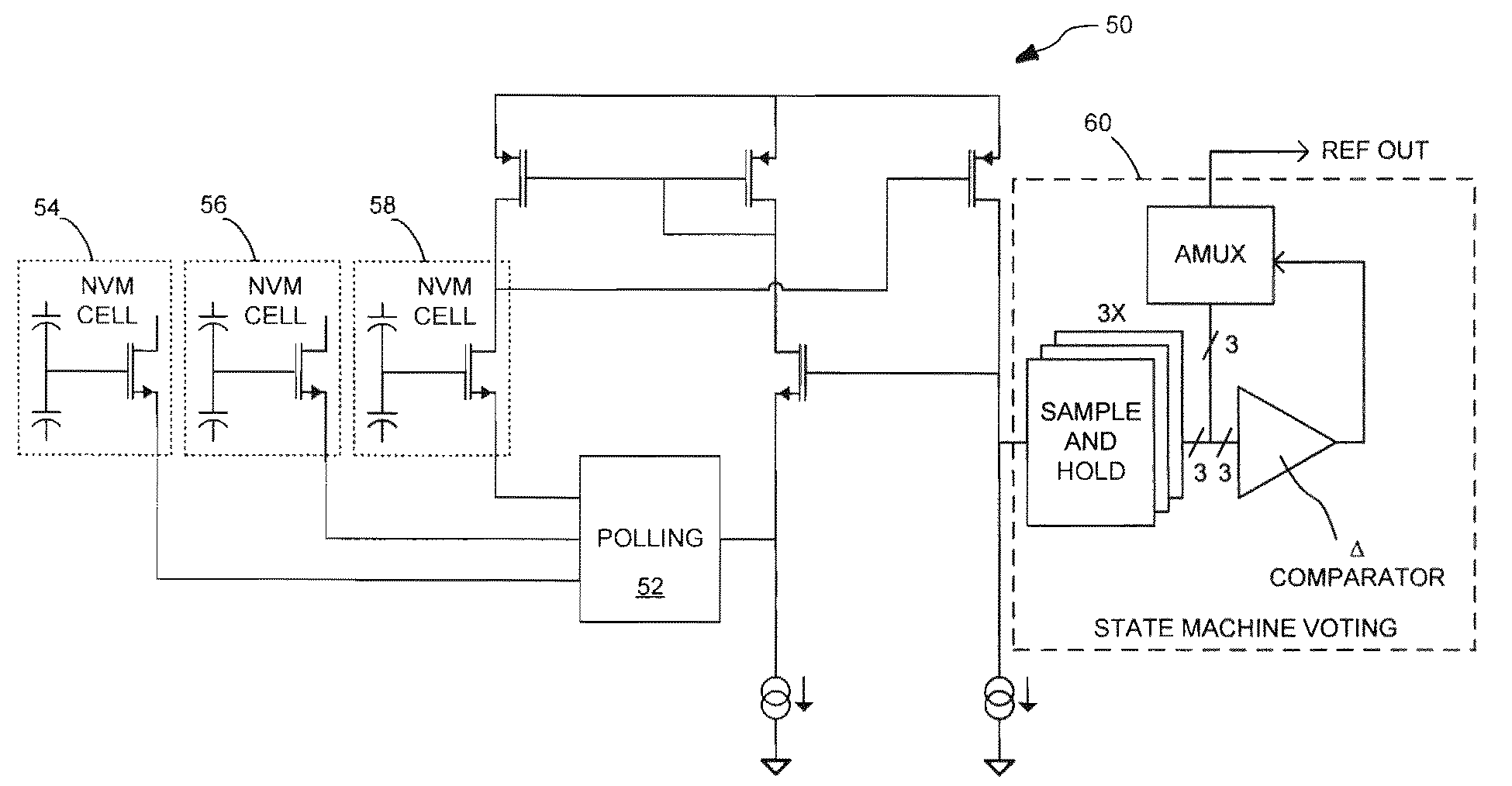

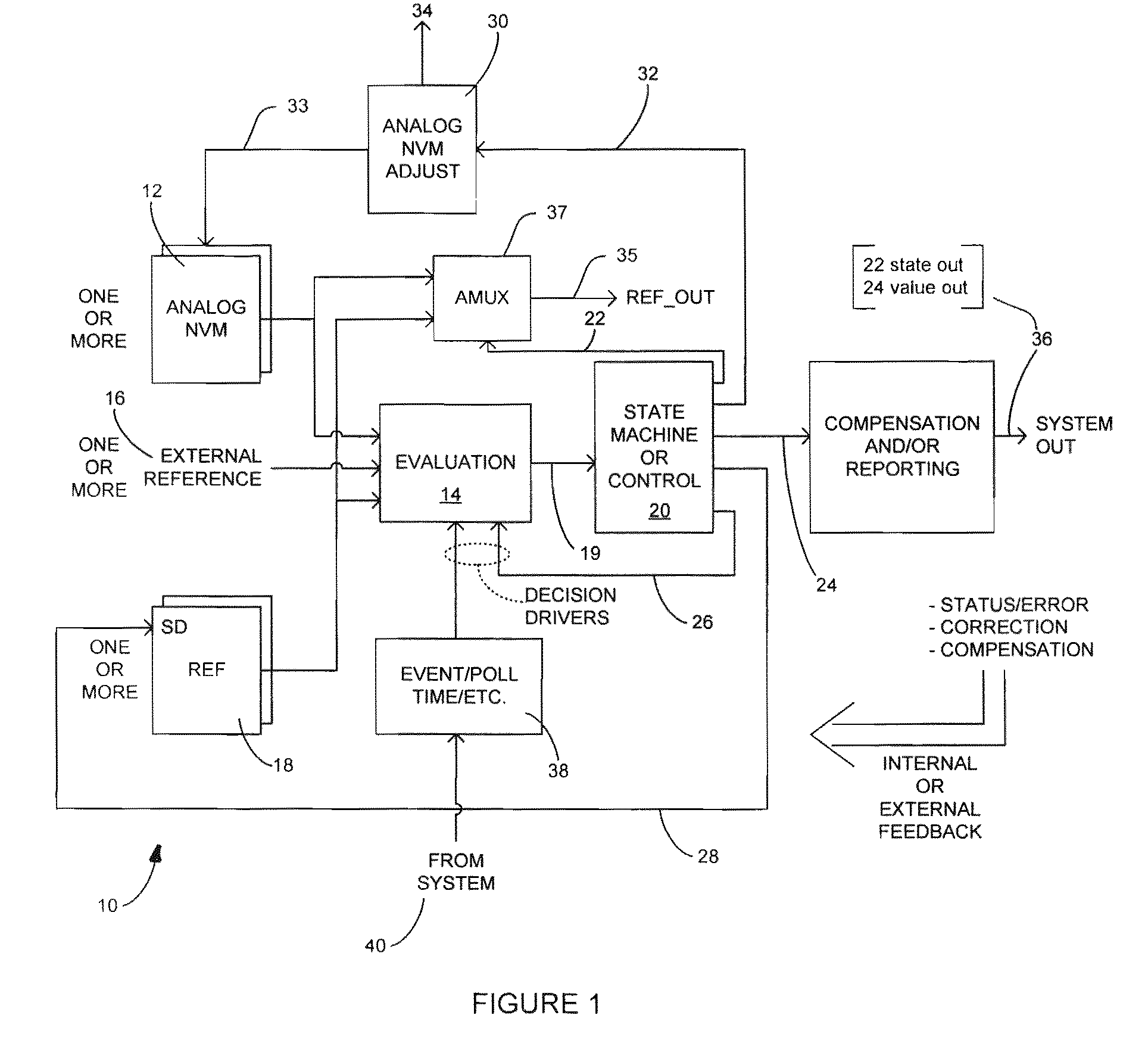

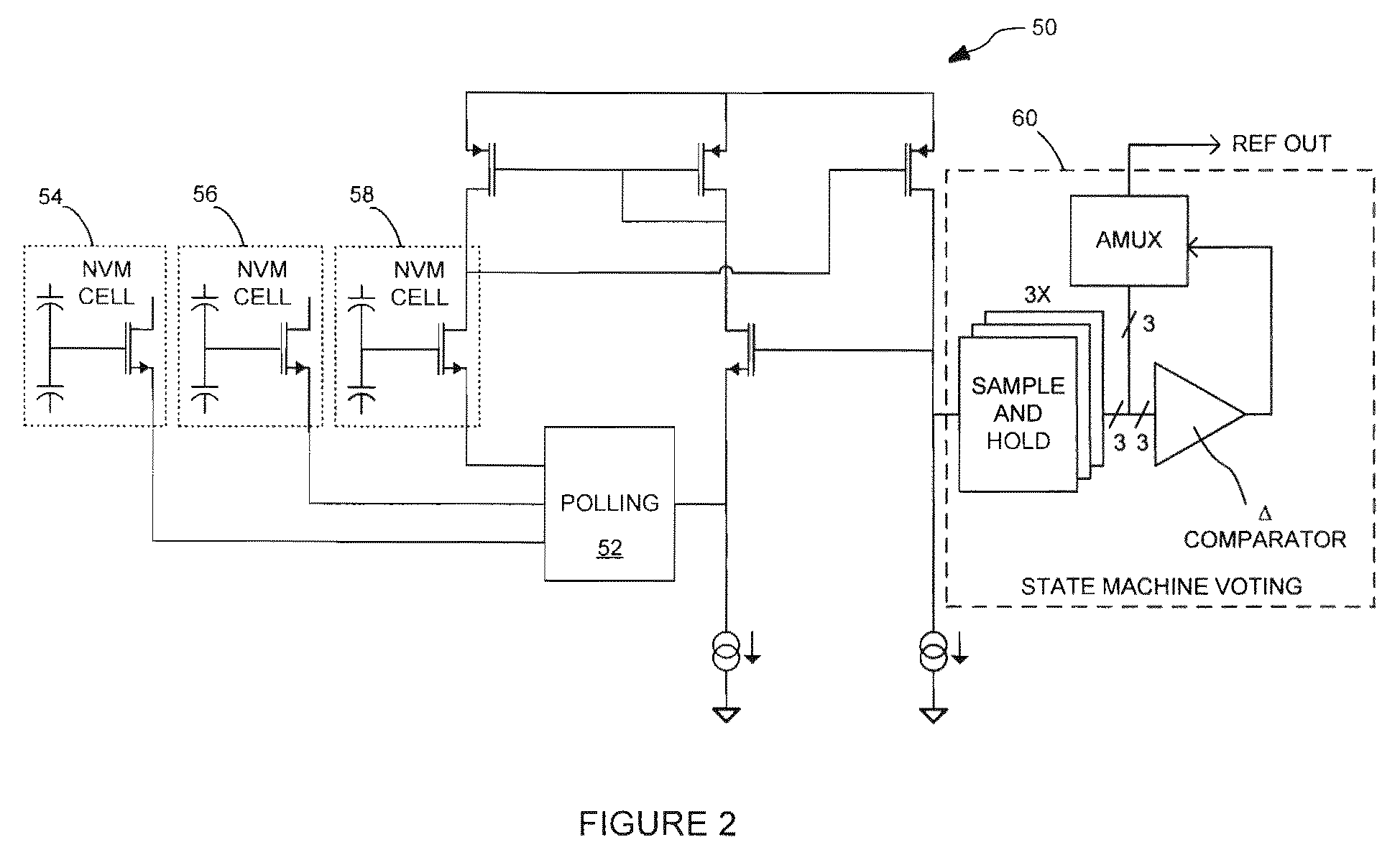

Non-volatile memory monitor

ActiveUS8102713B2Easy to operateImprove circuit accuracyRead-only memoriesDigital storageMonitoring systemComputer science

The invention provides circuits, systems, and methods for monitoring a non-volatile memory (NVM) cell, or an array of NVM cells. The monitor is capable of switching from a normal operating state to an evaluation state, monitoring for one or more particular characteristics, and returning to the normal operating state. Alternative embodiments of the invention are disclosed using various triggers and producing outputs capable of reporting or feeding back to influence the operation of the monitoring systems and methods, the NVM circuitry, or an external system. The invention includes an energy conservation feature, in that no power is consumed in the normal operating state, and low power in the evaluation state.

Owner:TRIUNE IP

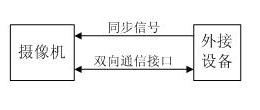

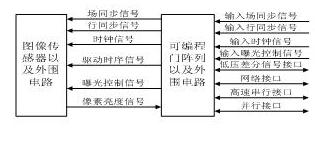

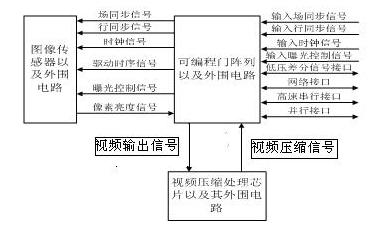

Design method capable of using external synchronous for cameral with various data output formats

ActiveCN102006420AFast programmingReduce running timeTelevision system detailsColor television detailsComputer architectureGate array

The design method capable of using external synchronous for a camera with various data output formats, relating to data output of the camera. A transformation between an external synchronizing signal and a CCD (charge coupled device) time sequence is carried out by utilizing a programmable gate array module, so as to realize two-way communication with the external synchronization. A synchronizing signal is transmitted by externally connecting an input line module, an input field module, an input clock module and an input exposure module on FPGA (filed programmable gate array), and the two-way communication with the external synchronization is realized by externally connecting a circumscribed high-speed serial interface, a parallel interface, a low-voltage differential signal interface and a network interface. Software control FPGA uses an external control signal firstly. The control signal can be one or two or three or four of an input field synchronizing signal, an input line synchronizing signal, an input clock signal and an input exposure control signal. The external device can be added with a video compression chip, or an embedded chip, or both the video compression chip and the embedded chip. The invention enables the exposure time to be synchronous with a specific event, and to be synchronous with an operation processing of the external device, enables the software to program fast, and enables program running time and memory using to be less.

Owner:WISESOFT CO LTD

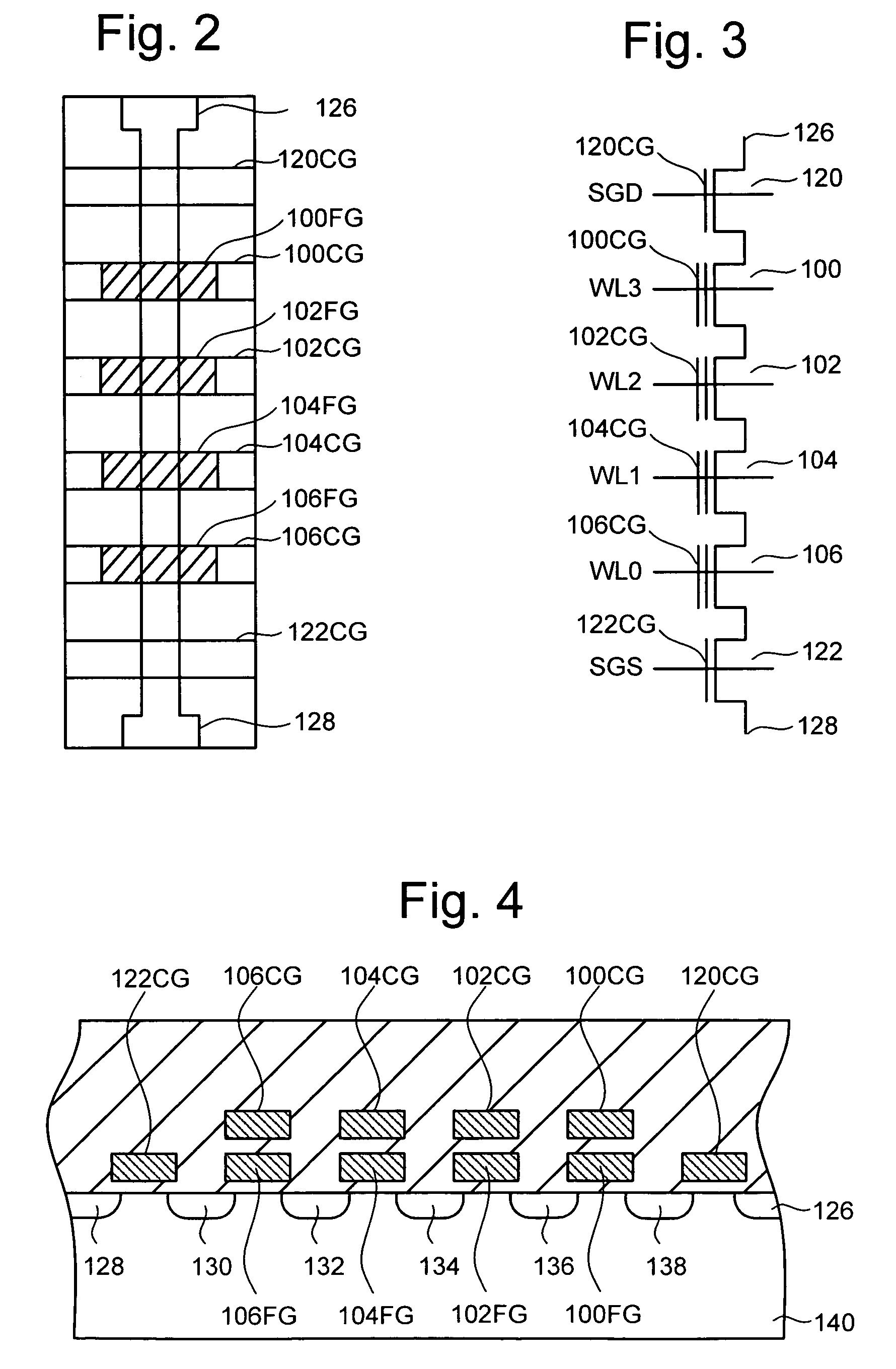

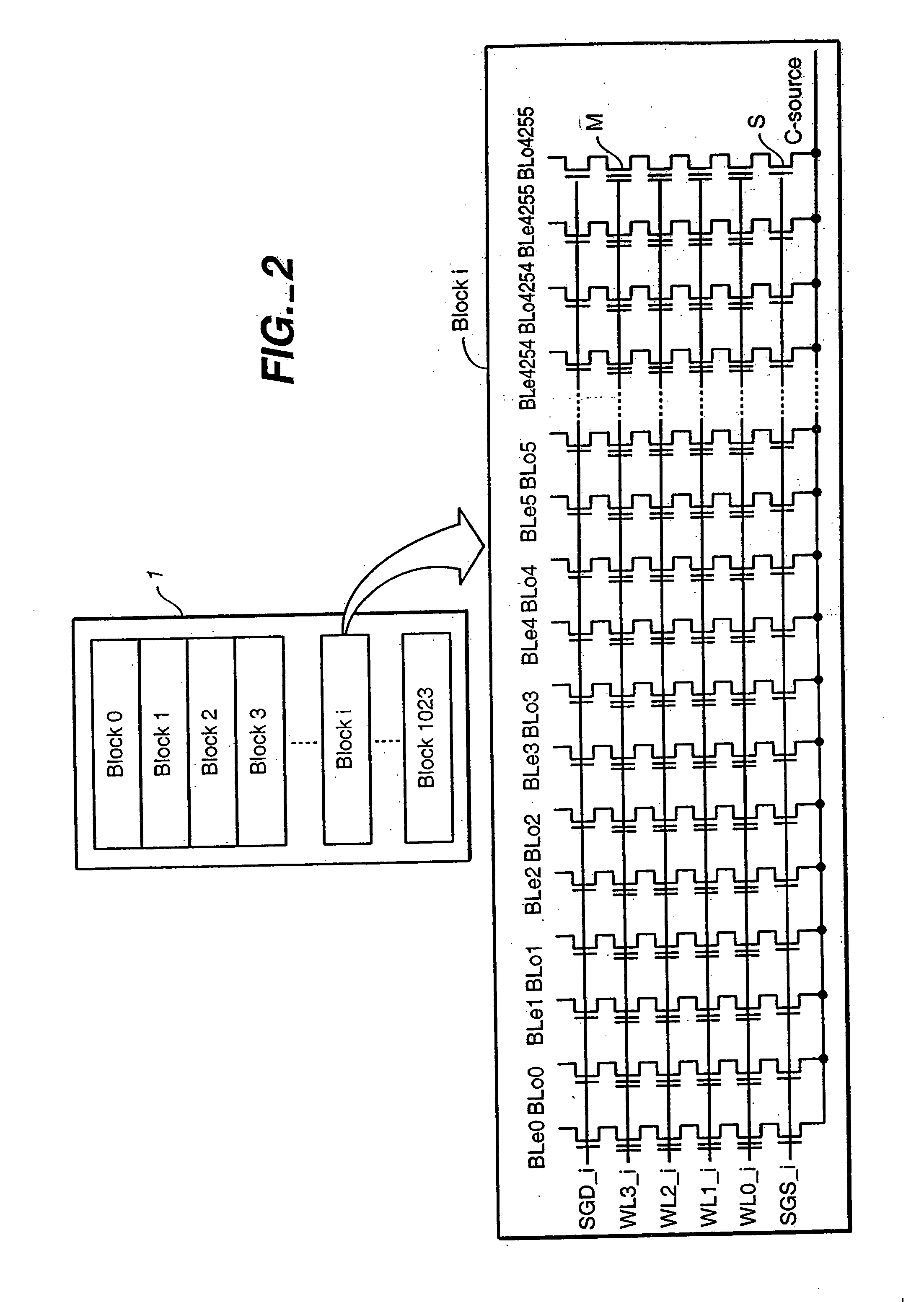

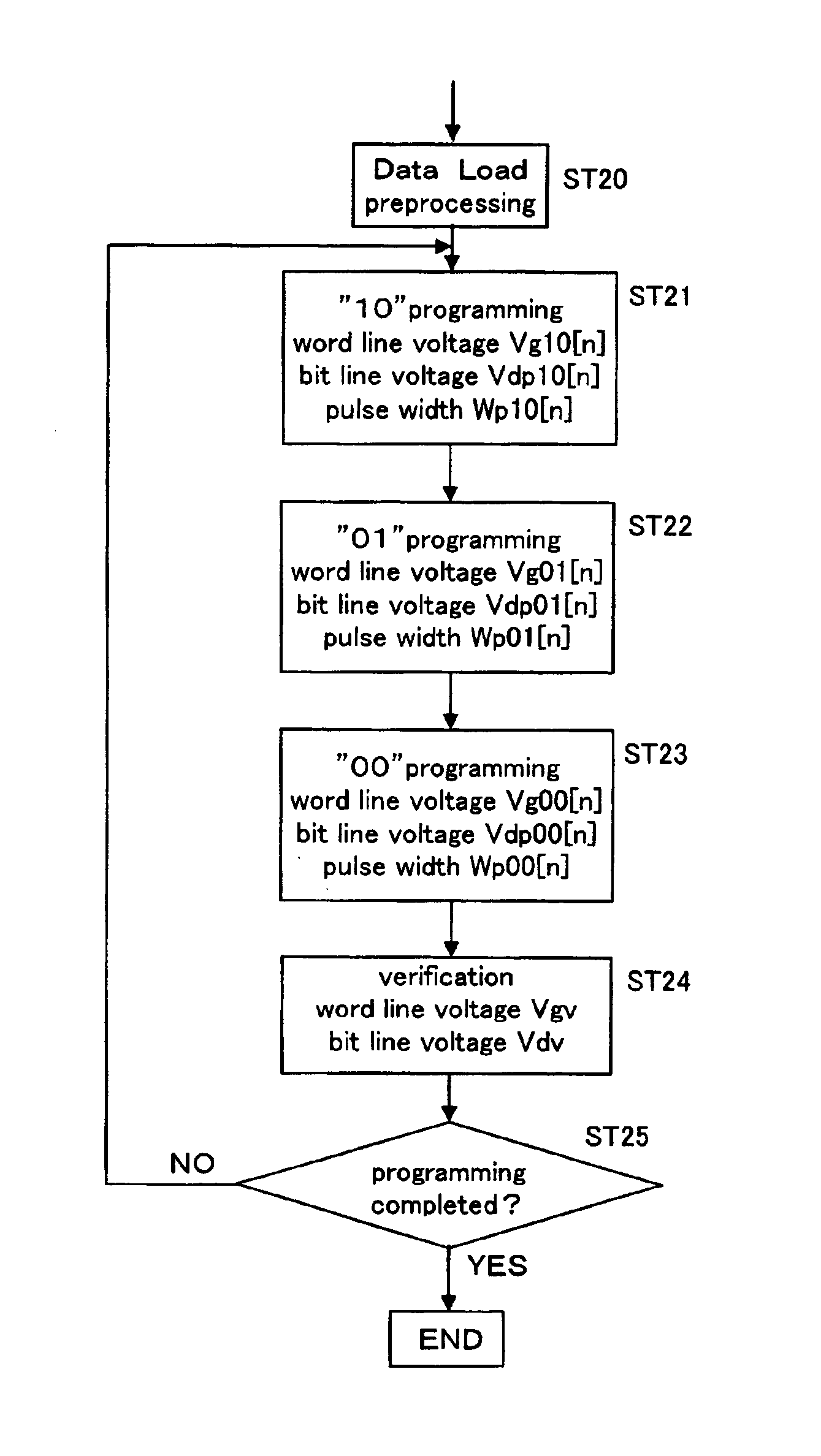

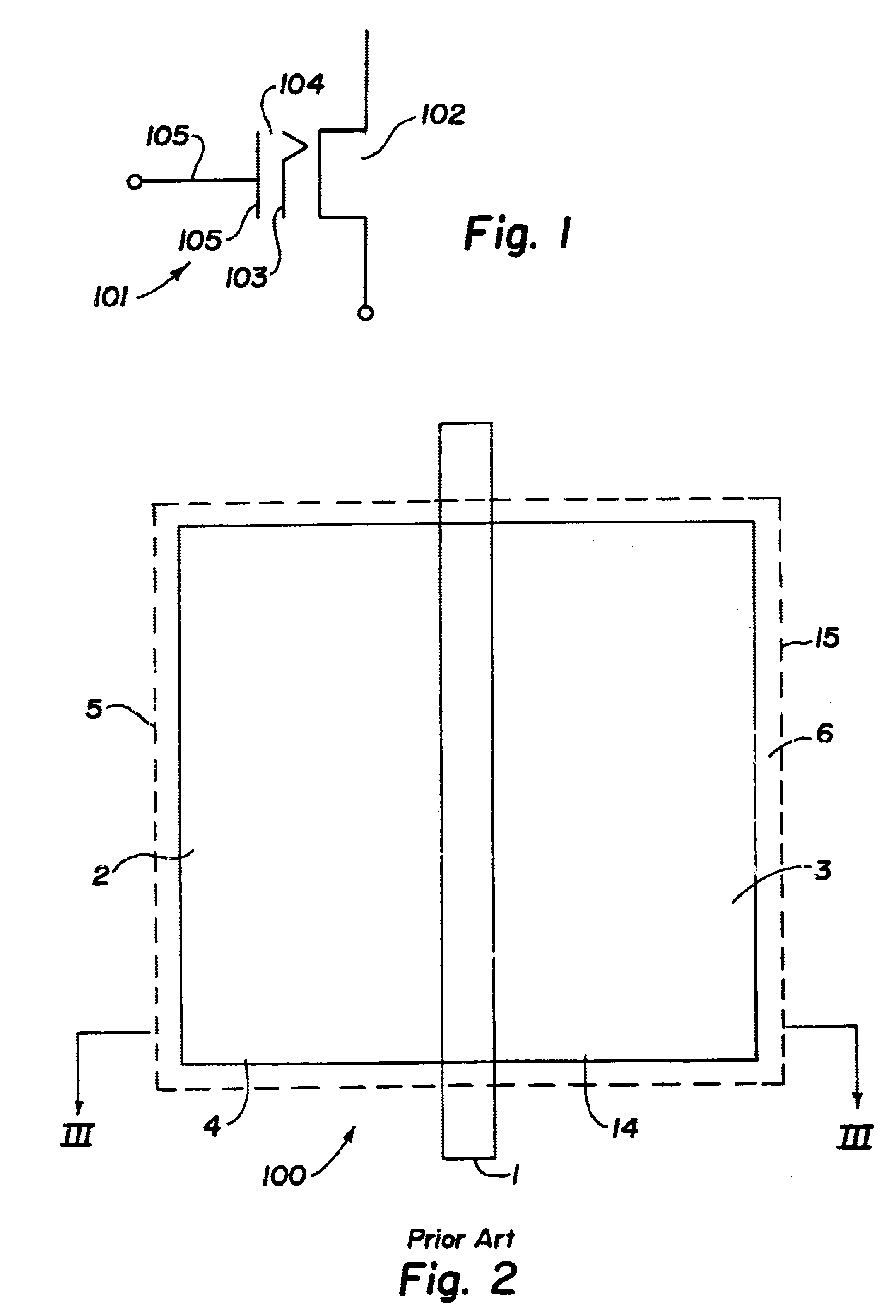

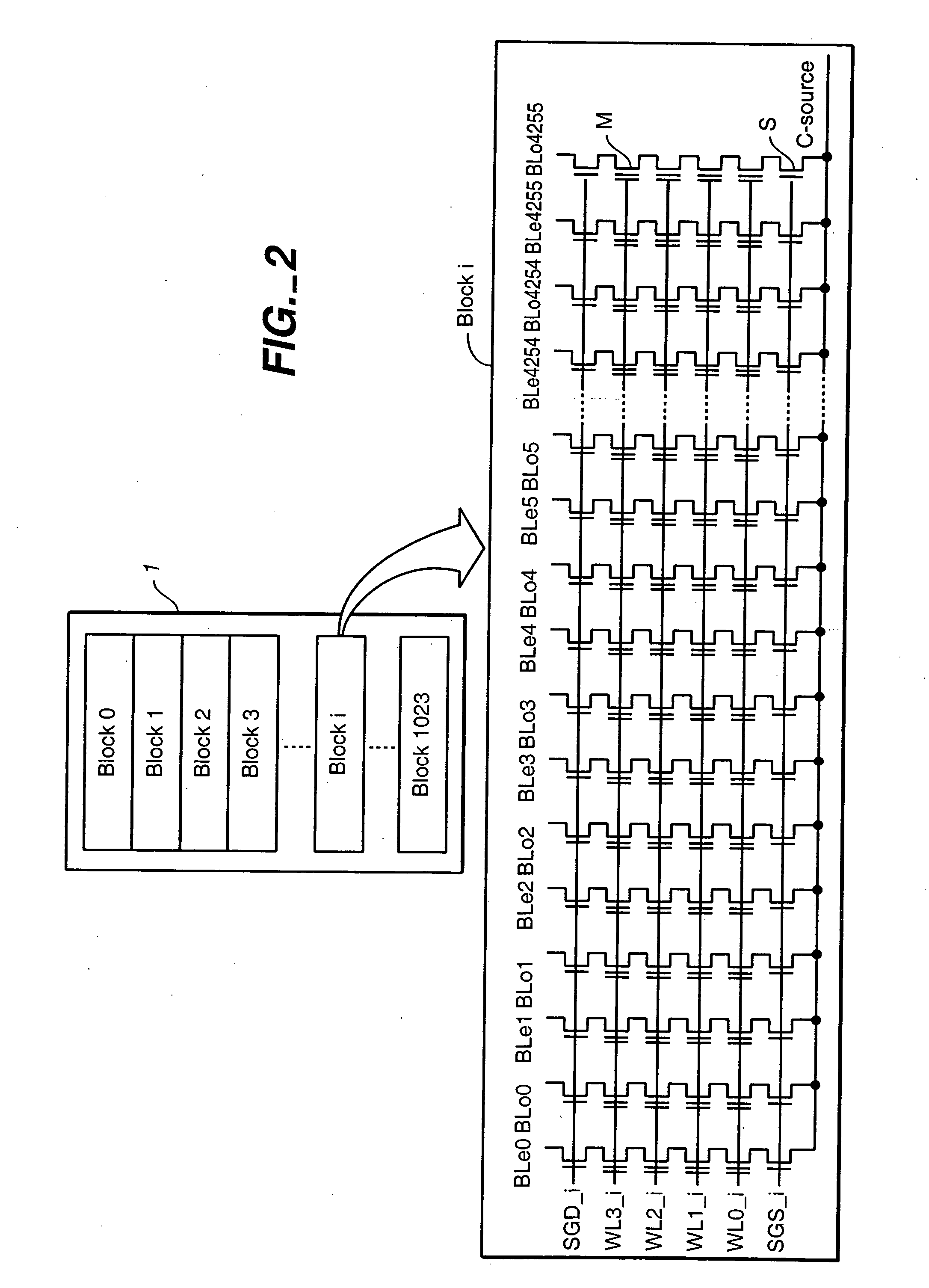

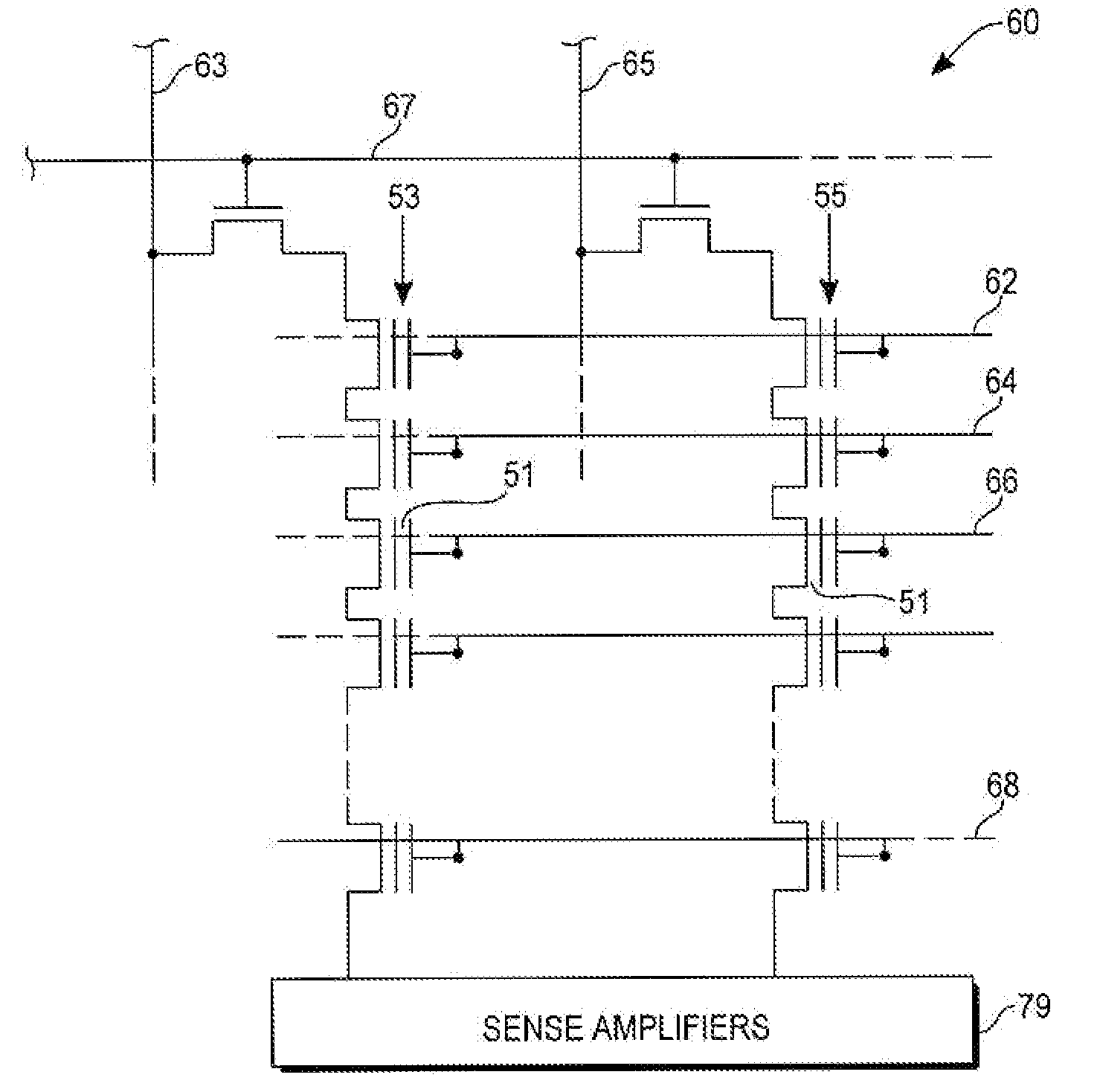

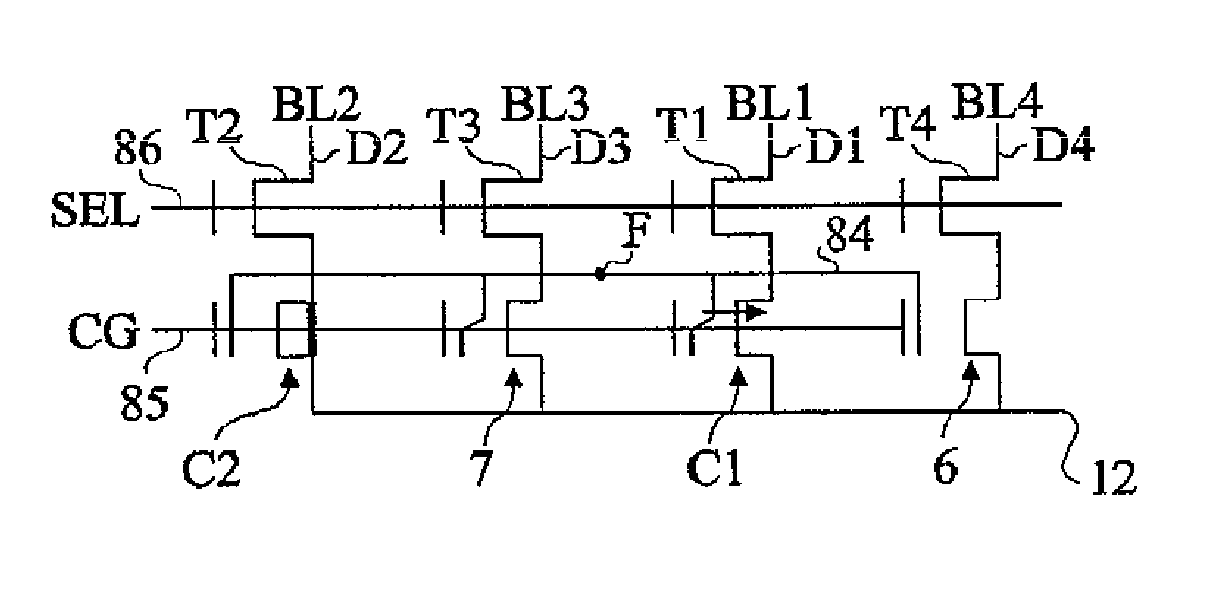

Operating techniques for reducing effects of coupling between storage elements of a non-volatile memory operated in multiple data states

InactiveUS20050047223A1Compensation effectAccurate readingTransistorSolid-state devicesCell memoryStorage cell

A non-volatile memory system having an array of memory cells with at least one storage element each is operated with a plurality of storage level ranges per storage element. A flash electrically erasable and programmable read only memory (EEPROM) is an example, wherein the storage elements are electrically floating gates. The memory is operated to minimize the effect of charge coupled between adjacent floating gates, by programming some cells a second time after adjacent cells have been programmed. The second programming step also compacts a distribution of charge levels within at least some of the programming states. This increases the separation between states and / or allows more states to be included within a given storage window. An implementation that is described is for a NAND type of flash EEPROM.

Owner:SANDISK TECH LLC +1

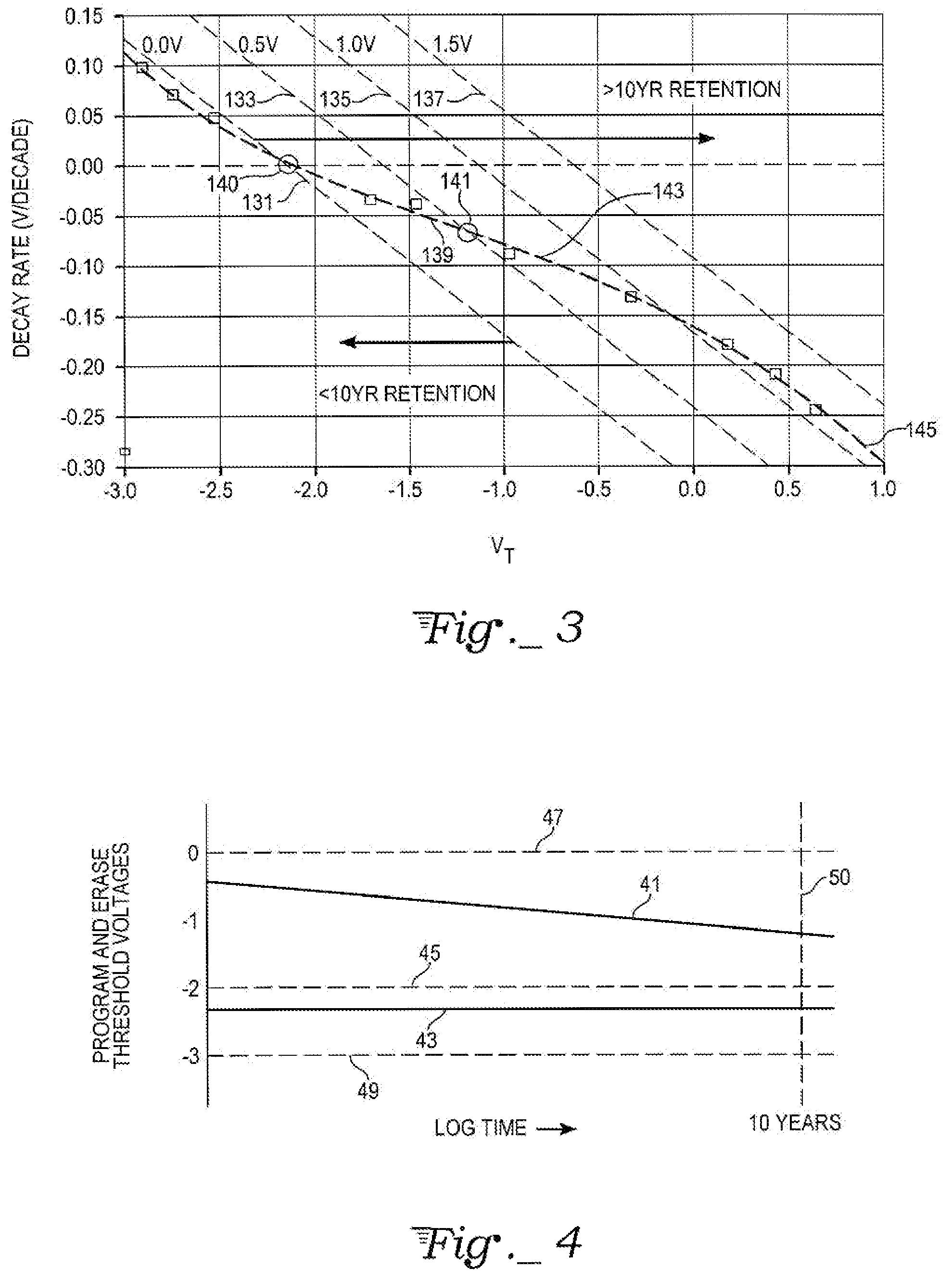

SONOS memory array with improved read disturb characteristic

ActiveUS7423912B2High voltageEffective massRead-only memoriesDigital storageCharge retentionEngineering

A PMOS non-volatile memory array using SONOS transistors having program and erase threshold voltages for representing digital logic states of zero and one and selected to optimize read disturb characteristics. The threshold voltages are linearly convergent and separated by at least 0.5 volts for a charge retention time of at least 10 years, with the threshold voltages defining a window wherein a read voltage for selected memory transistors can be held flat and not intersect the threshold voltages. The lower threshold is selected to be at a zero charge state for one of the two logic levels of the memory.

Owner:ATMEL CORP

EEPROM charge retention circuit for time measurement

An electronic charge retention circuit for time measurement, implanted in an array of EEPROM memory cells, each including a selection transistor in series with a floating-gate transistor, the circuit including, on any one row of memory cells: a first subassembly of at least a first cell, the thickness of the dielectric of the tunnel window of the floating-gate transistor of which is less than that of the other cells; a second subassembly of at least a second cell, the drain and source of the floating-gate transistor of which are interconnected; a third subassembly of at least a third cell; and a fourth subassembly of at least a fourth cell, the tunnel window of which is omitted, the respective floating gates of the transistors of the cells of the four subassemblies being interconnected.

Owner:STMICROELECTRONICS SRL

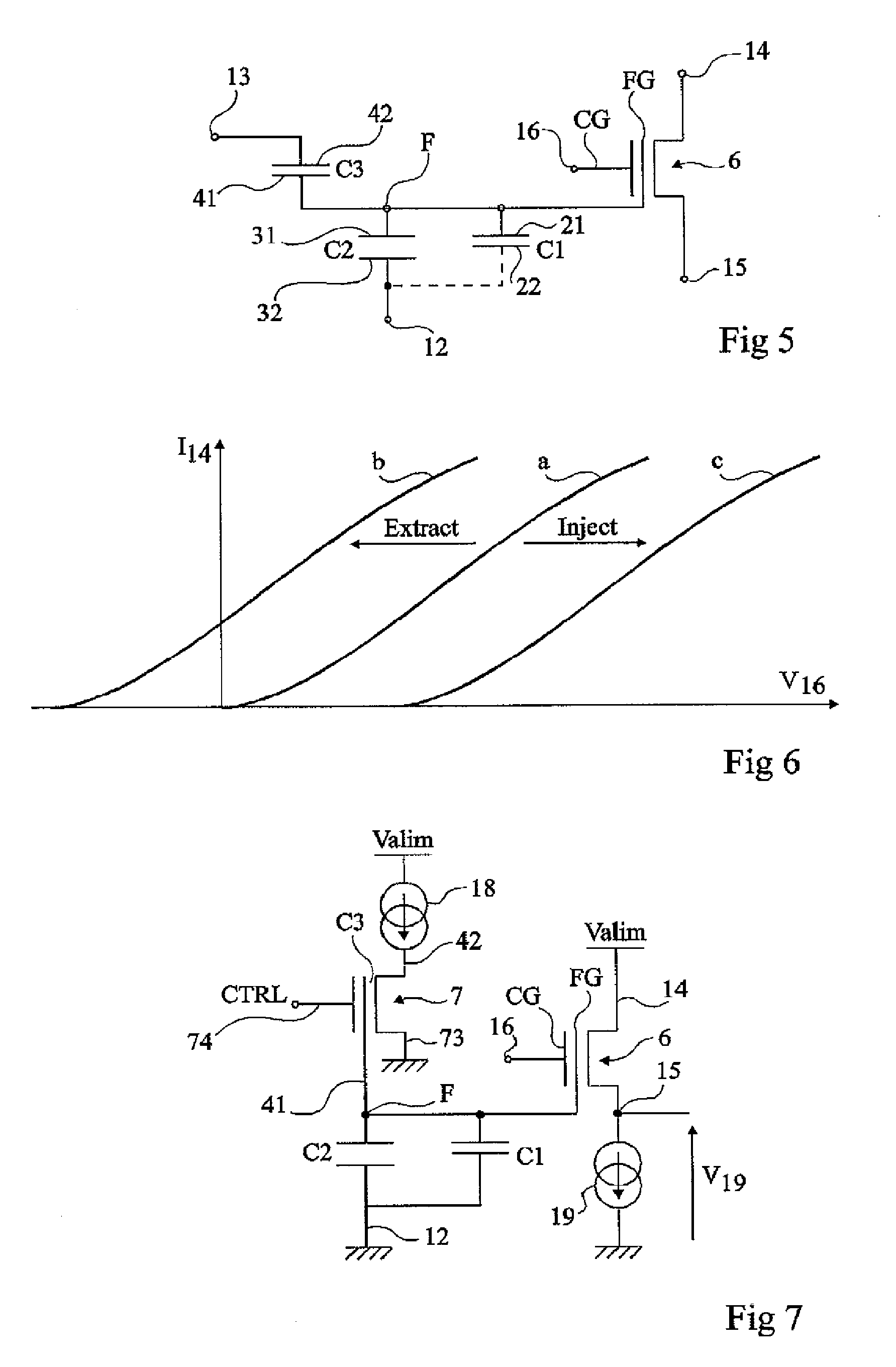

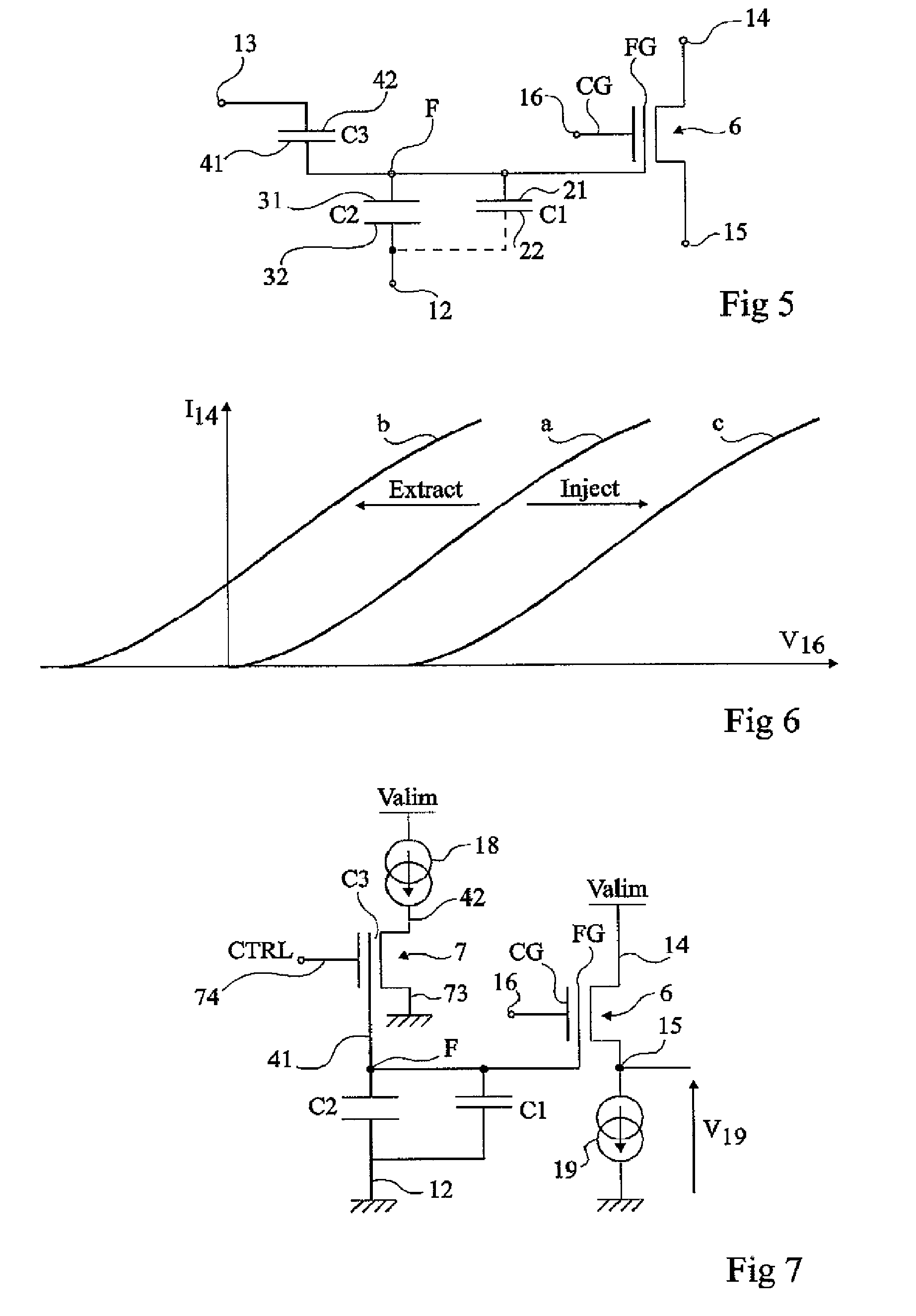

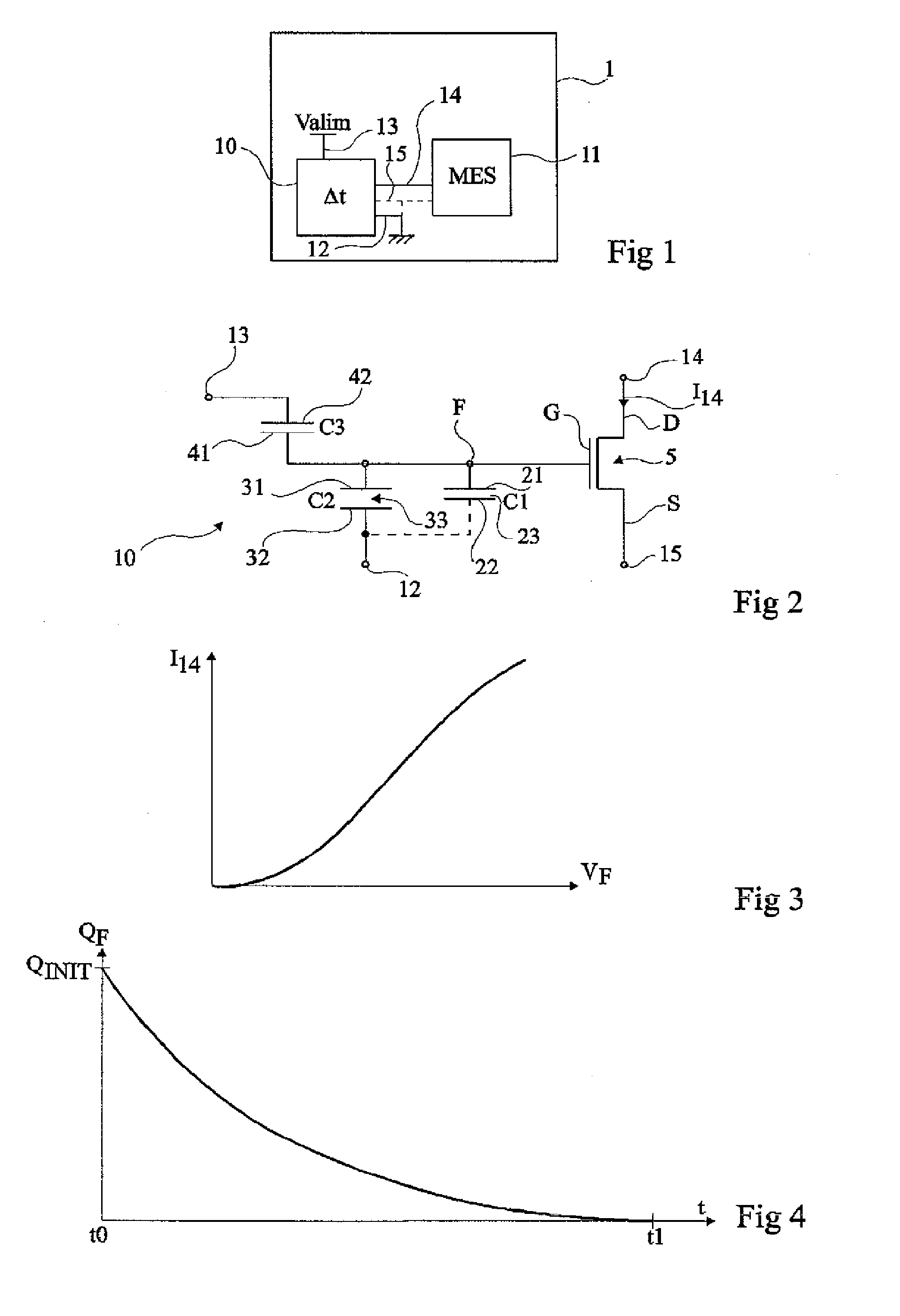

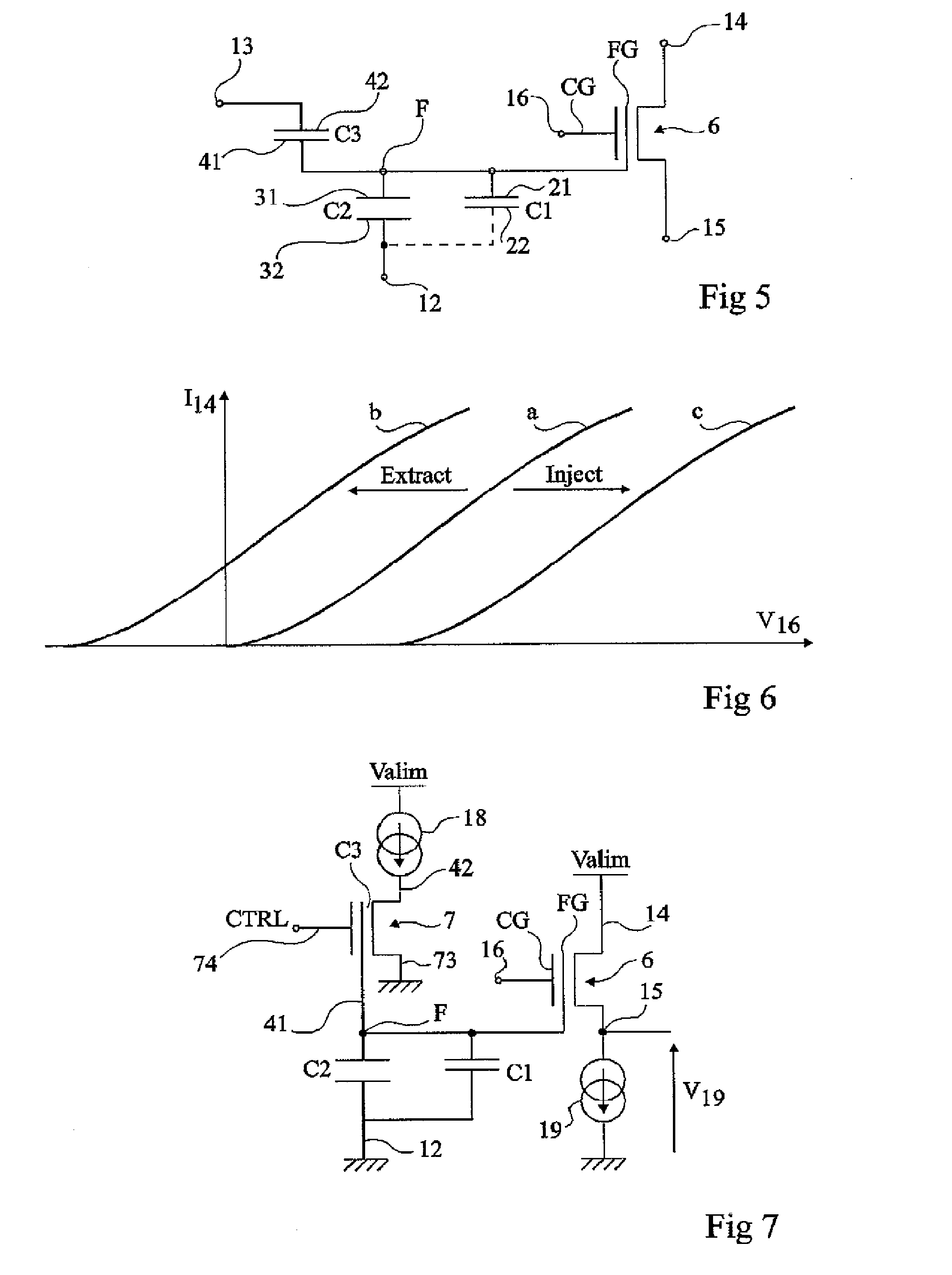

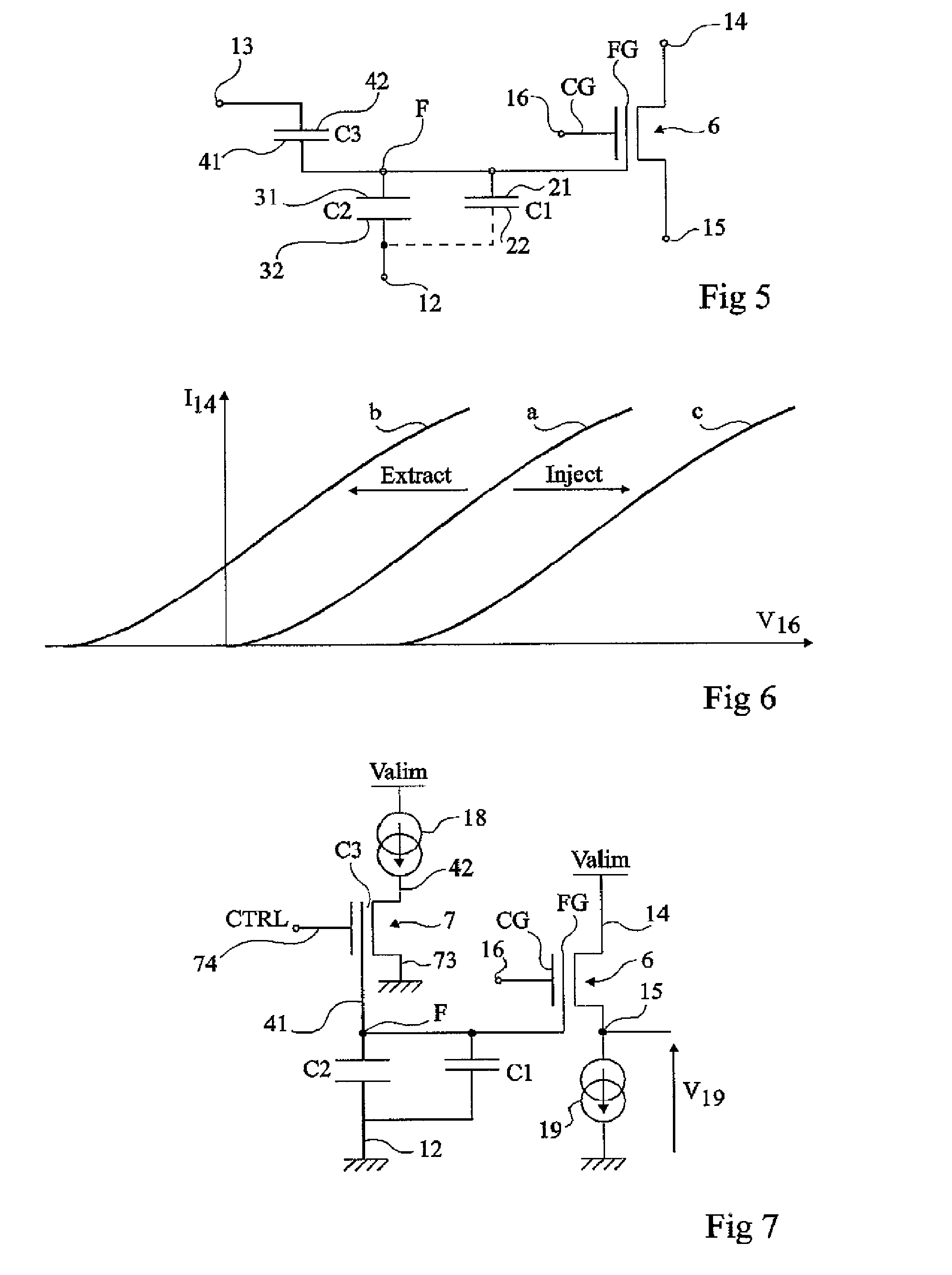

Programming of a charge retention circuit for a time measurement

ActiveUS20100054038A1Fast programmingElectric analogue storesRead-only memoriesElectricityCapacitance

A method of controlling an electronic charge retention circuit for time measurement, including at least a first capacitive element, the dielectric of which has a leakage, and at least a second capacitive element, the dielectric of which has a higher capacitance than the first, the two elements having a common electrode defining a floating node that can be connected to an element for measuring its residual charge, in which a charge retention period is programmed or initialized by injecting or extracting charges via the first element.

Owner:STMICROELECTRONICS SRL

Circuit for reading a charge retention element for a time measurement

A method and a circuit for reading an electronic charge retention element for a temporal measurement, of the type including at least one capacitive element whose dielectric exhibits a leakage and a transistor with insulated control terminal for reading the residual charges, the reading circuit including; two parallel branches between two supply terminals, each branch including at least one transistor of a first type and one transistor of a second type, the transistor of the second type of one of the branches consisting of that of the element to be read and the transistor of the second type of the other branch receiving, on its control terminal, a staircase signal, the respective drains of the transistors of the first type being connected to the respective inputs of a comparator whose output provides an indication of the residual voltage in the charge retention element.

Owner:STMICROELECTRONICS SRL

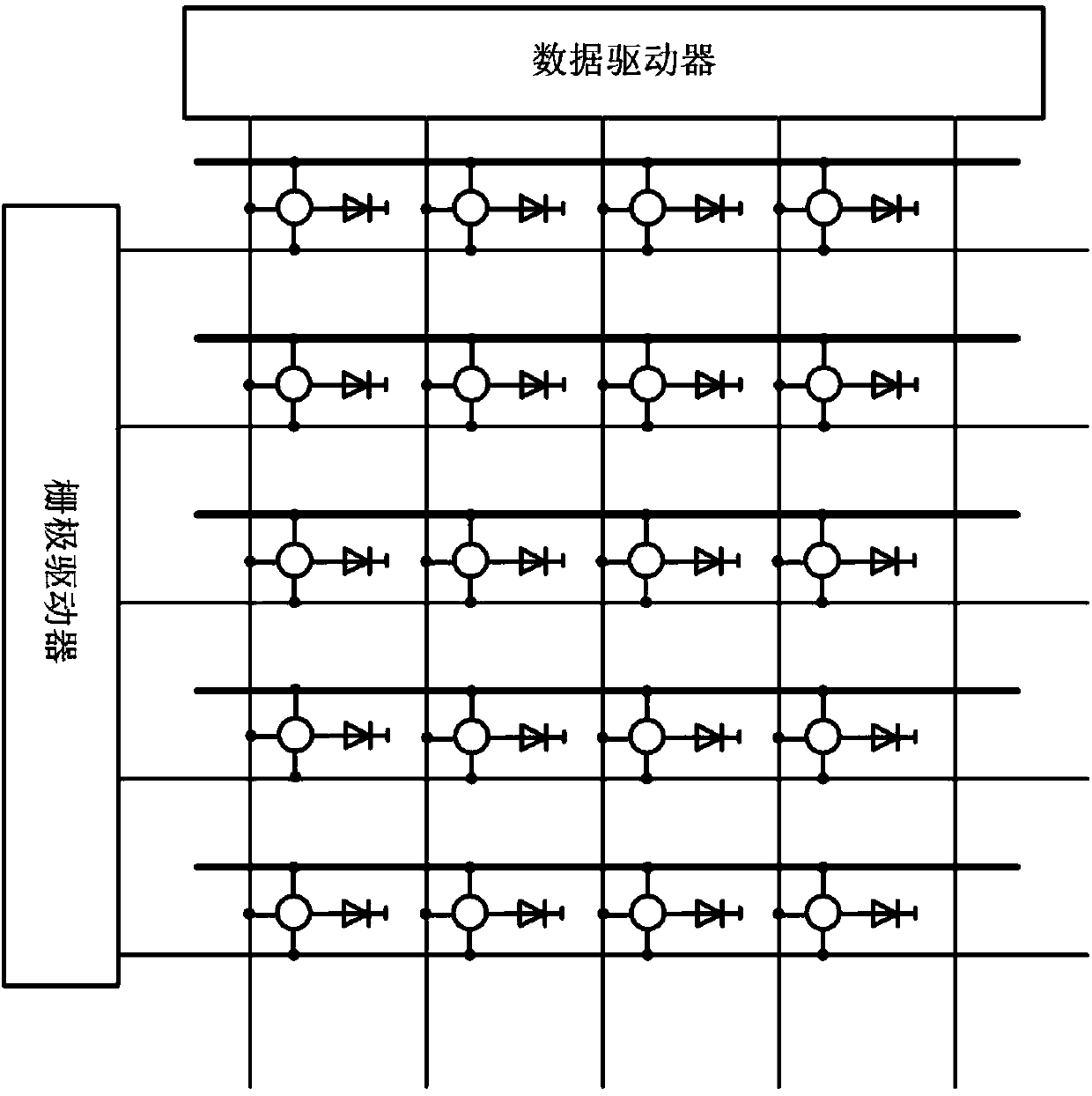

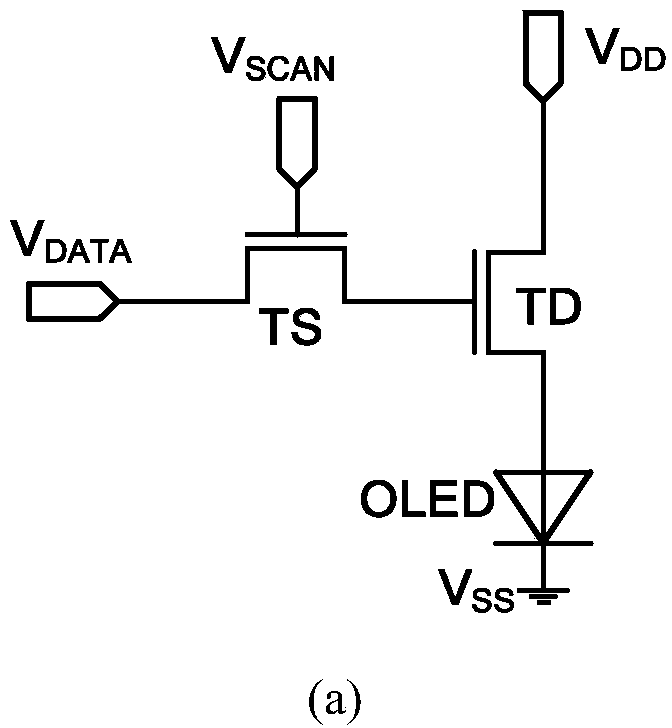

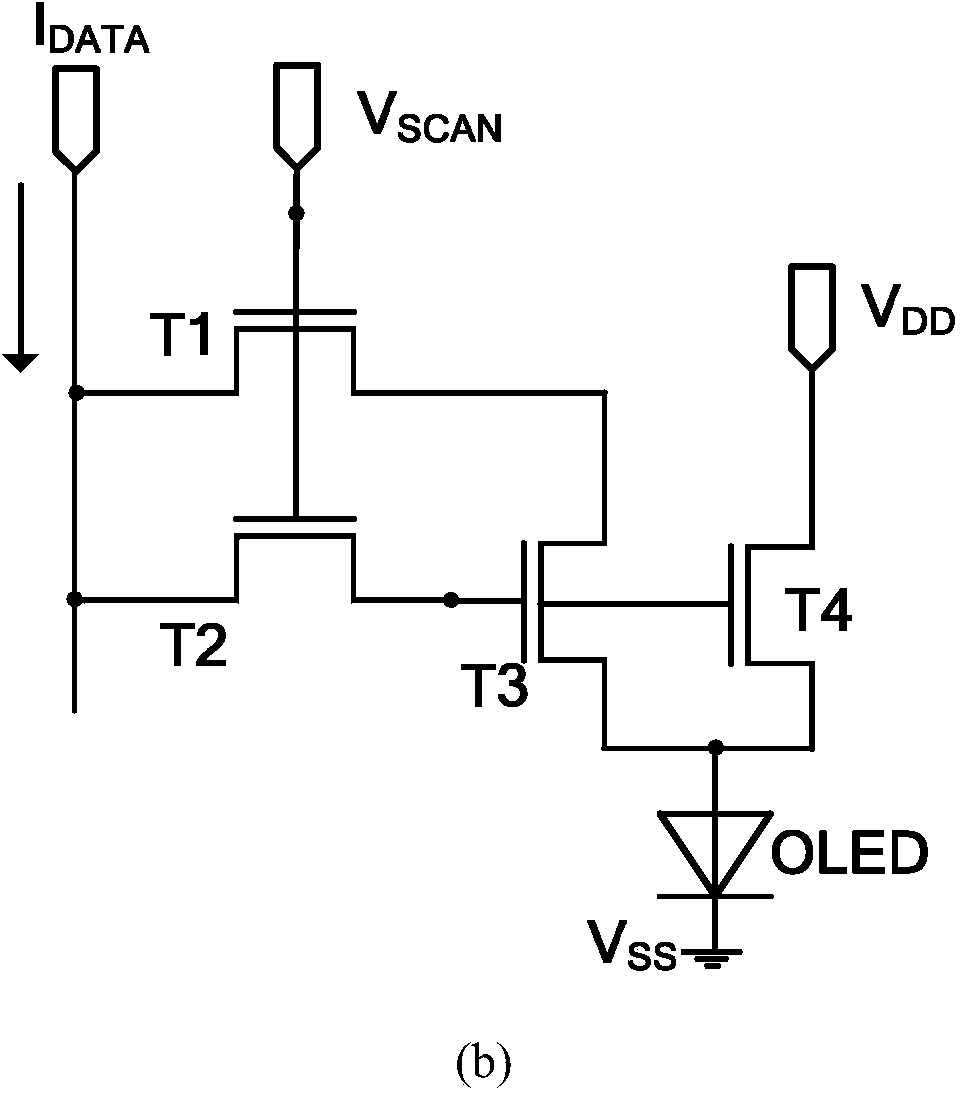

OLED data driving circuit, active TFT OLED panel based on OLED data driving circuit and driving method of active TFT OLED panel based on OLED data driving circuit

InactiveCN104050926AHigh speedFast programmingStatic indicating devicesAudio power amplifierData-driven

The invention discloses an OLED data driving circuit, an active TFT OLED panel based on the OLED data driving circuit and a driving method of the active TFT OLED panel based on the OLED data driving circuit. The current driving circuit is formed by the following parts including the current feed-forward part, the current feedback part, the comparison amplifier, the dynamic compensation part and the polarization power source. By means of the data driving circuit, current type TFT OLED pixels can be rapidly programmed with high accuracy. A gate driving line of the active TFT OLED panel based on the data driving circuit is two times that of a common panel, pixels in the direction of one gate driving line are divided into two different groups according to the parity of a dateline where the pixels are located, gate scanning time of two sets of pixels in the direction of the same line is respectively a half of the gate scanning time of the common panel, and two gate scanning lines are complemented and sequentially open the pixels in the direction of the same line.

Owner:贵州传曙科技有限公司

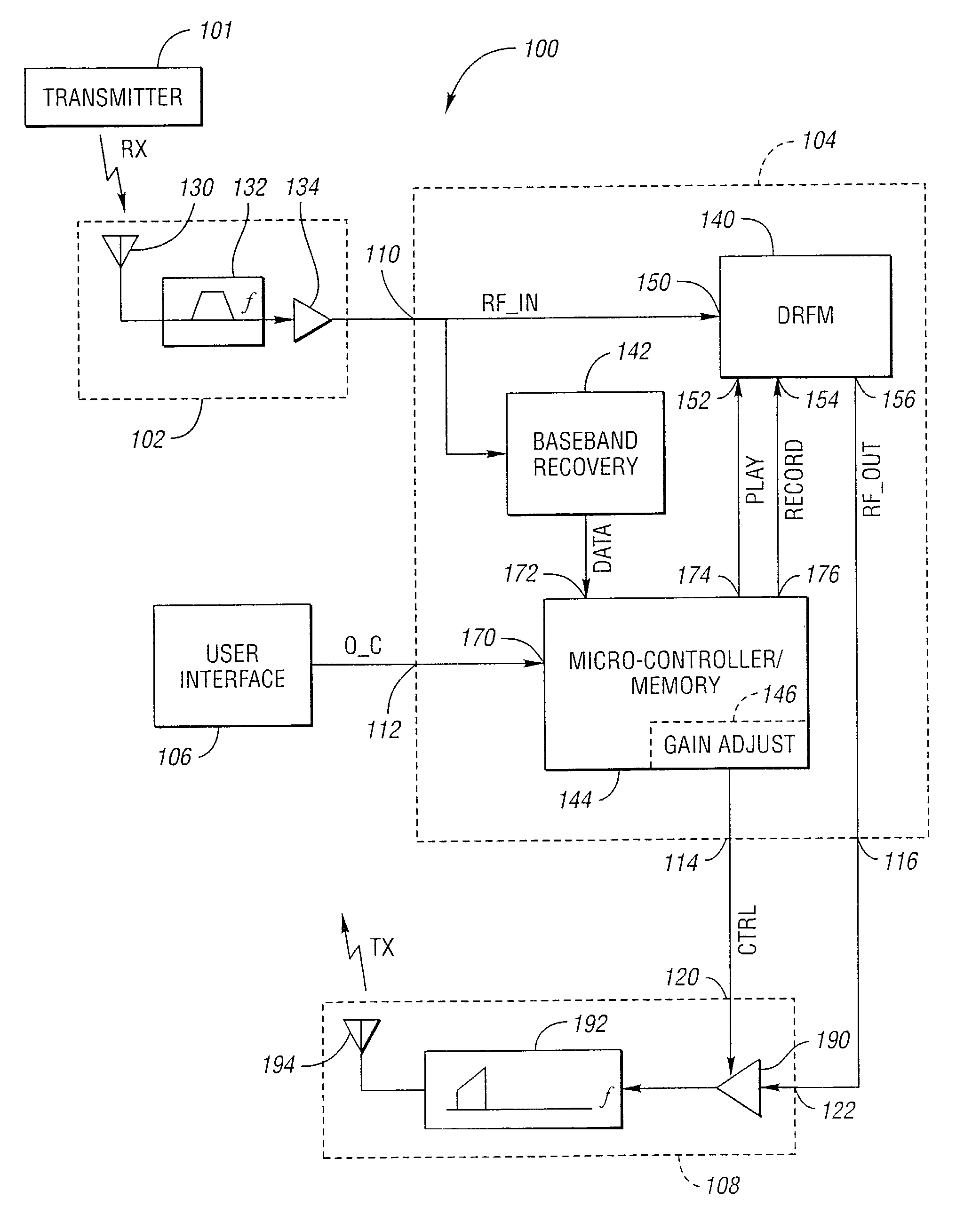

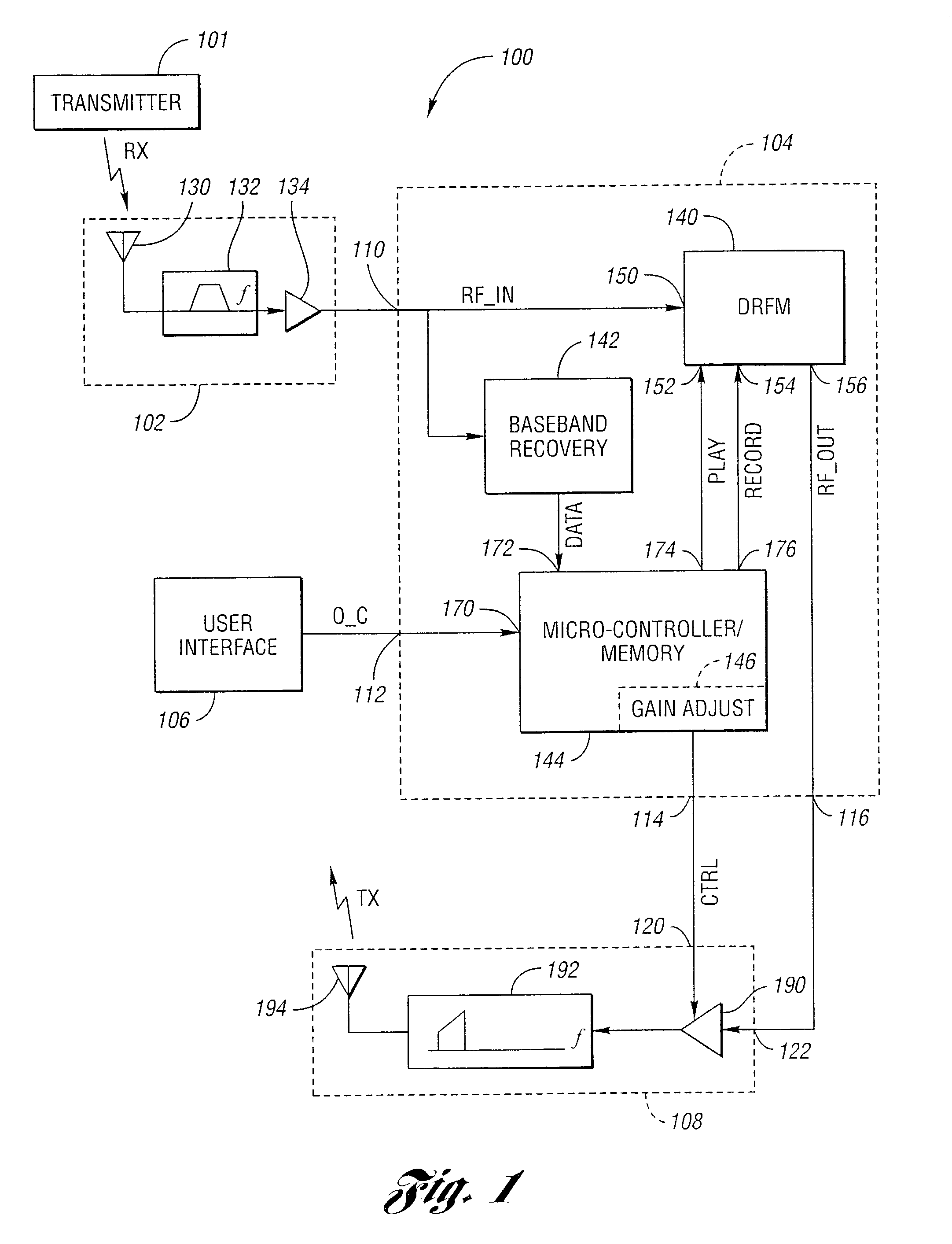

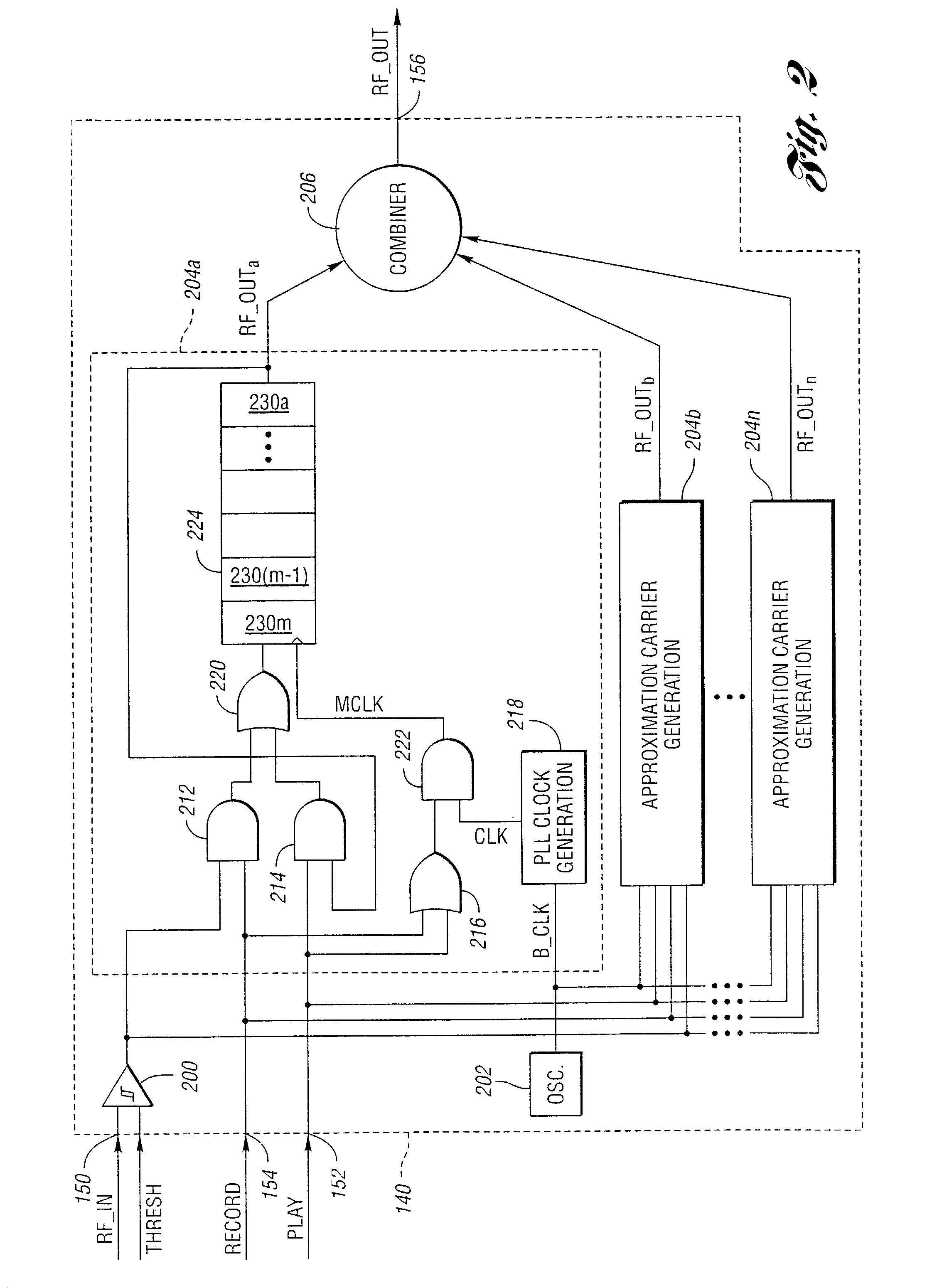

Programmable transmitter and receiver including digital radio frequency memory

InactiveUS7116242B2Reduced board areaFast programmingElectric signal transmission systemsMultiple keys/algorithms usageRadio frequencyDigital radio frequency memory

A vehicular programmable transceiver includes a digital radio frequency memory (DRFM) having at least one register configured to sample and hold a radio frequency input signal in response to a clock signal and to generate an output signal having a carrier frequency generated in response to the sampled and held input signal.

Owner:LEAR CORP

Programming of a charge retention circuit for a time measurement

A method of controlling an electronic charge retention circuit for time measurement, including at least a first capacitive element, the dielectric of which has a leakage, and at least a second capacitive element, the dielectric of which has a higher capacitance than the first, the two elements having a common electrode defining a floating node that can be connected to an element for measuring its residual charge, in which a charge retention period is programmed or initialized by injecting or extracting charges via the first element.

Owner:STMICROELECTRONICS SRL

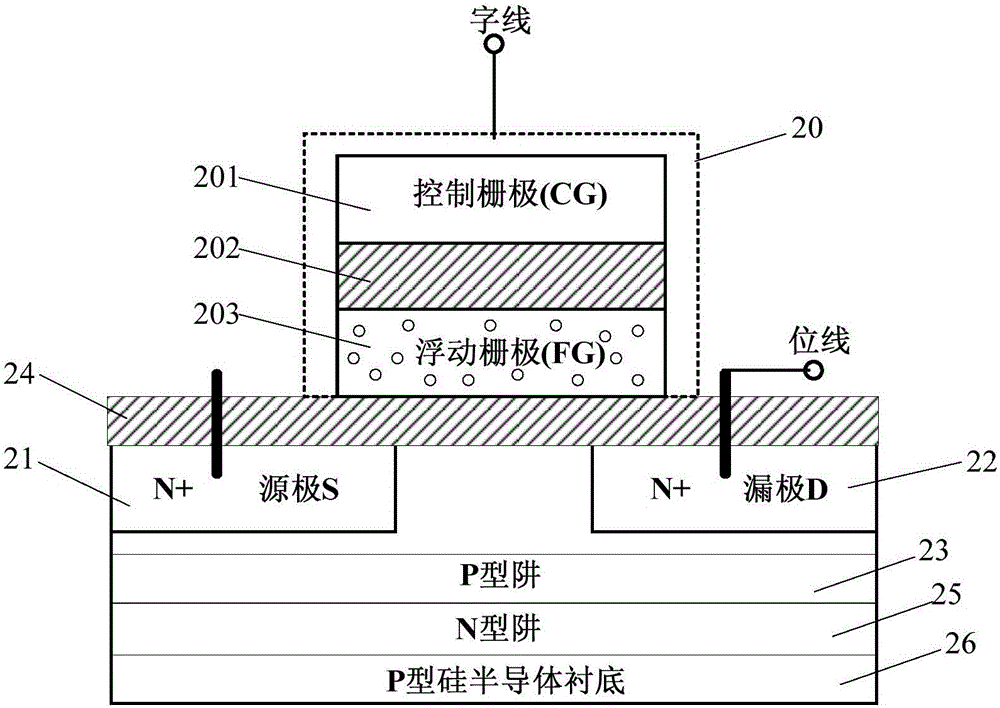

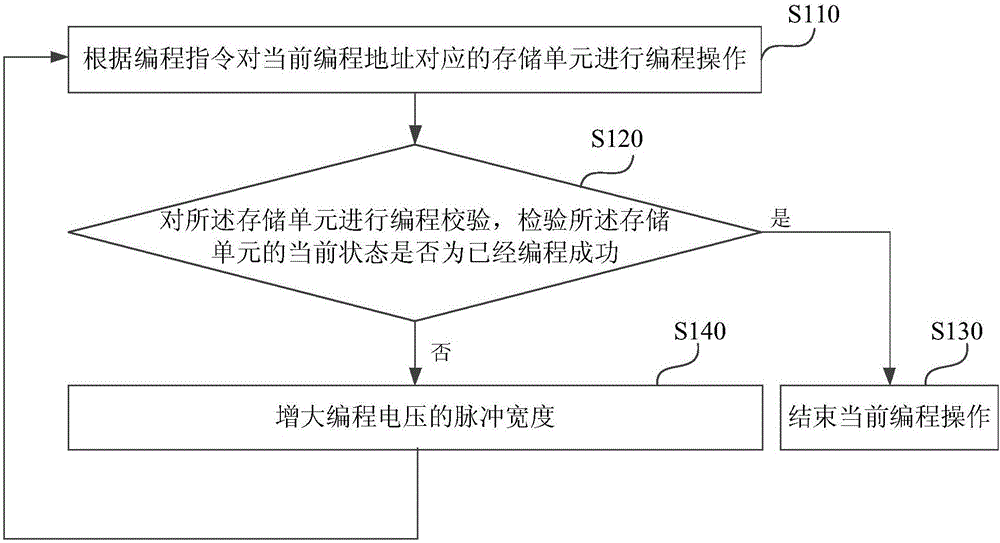

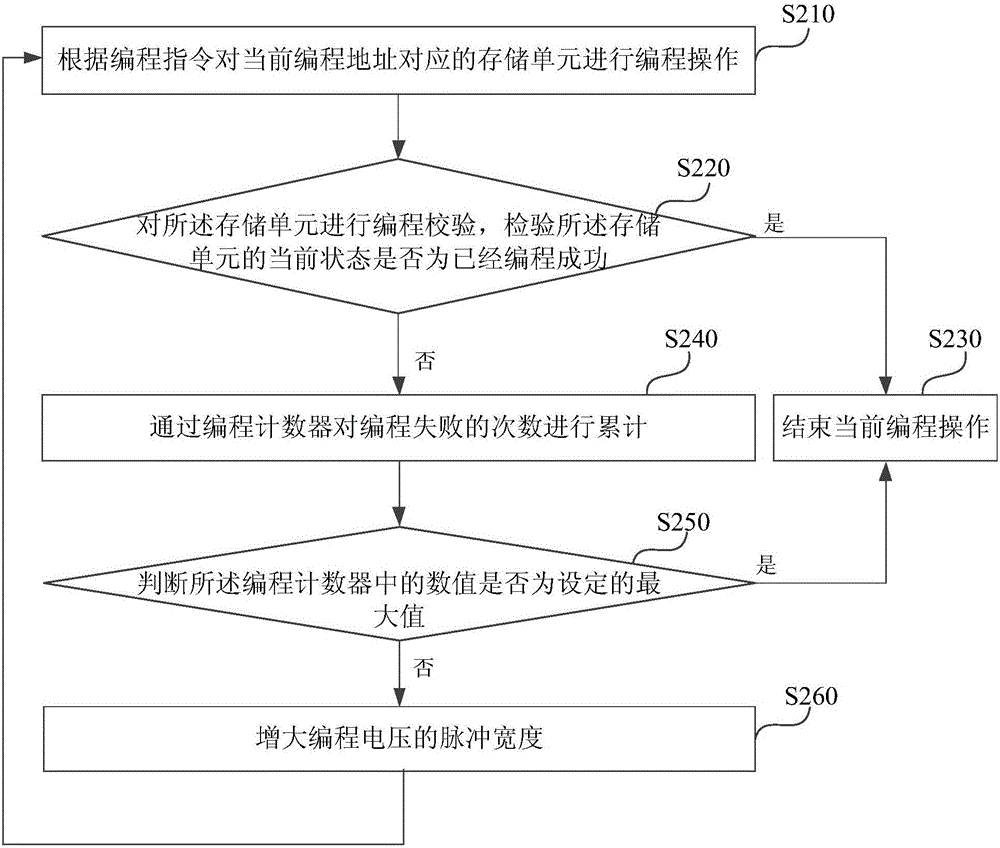

Programming method of storage unit

InactiveCN106205721AFast programmingIncrease the pulse widthRead-only memoriesEmbedded systemStorage cell

The invention discloses a programming method of a storage unit. The method includes the steps that programming operation is conducted on the storage unit corresponding to a current programming address according to a programming instruction; programming verification is conducted on the storage unit, whether the current state of the storage unit is a successfully programmed state or not is verified, if yes, current programming operation ends, and otherwise, pulse width of programming voltage is increased and the programming operation conducted on the storage unit corresponding to the current programming address is repeated till programming is successful. According to the programming method of the storage unit, when the storage unit is not successfully programmed through one time of programming operation, quick programming of the storage unit is achieved by continuously increasing the pulse width of programming voltage along with increase of the number of programming times when the storage unit is programmed, and programming speed is increased.

Owner:GIGADEVICE SEMICON (BEIJING) INC

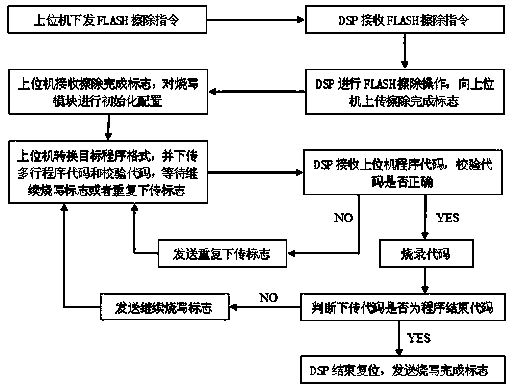

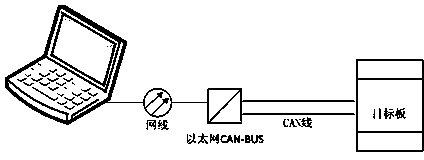

DSP (Digital Signal Processor) programming method based on CAN (Controller Area Network) bus

InactiveCN104216714AImprove programming speedImprove replacement efficiencySpecific program execution arrangementsArea networkData transmission

The invention discloses a DSP (Digital Signal Processor) programming method based on a CAN (Controller Area Network) bus. The DSP programming method comprises the following steps of (1) erasing a FLASH by an upper computer; (2) converting the format of a target program and downloading multi-row target program codes by the upper computer, and waiting for receiving a DSP uploading logo; (3) receiving and checking the codes by a DSP, outputting a checking result as a logo and uploading the logo to the upper computer; (4) carrying out code transmission and programming on the DSP by the upper computer according to the logo which is uploaded by the DSP. According to the DSP programming method based on the CAN bus, disclosed by the invention, the multi-row date transmission and programming in one time is adopted, measures for preventing line skipping and line leakage are adopted in a program, the purpose of quickly programming the program of a lower computer is achieved on the premise that correct programming is ensured, and the efficiency of carrying out program upgrading and debugging program replacing on a target board is greatly increased.

Owner:DONGFANG ELECTRIC CORPLESHAN NEW ENERGY EQUIP

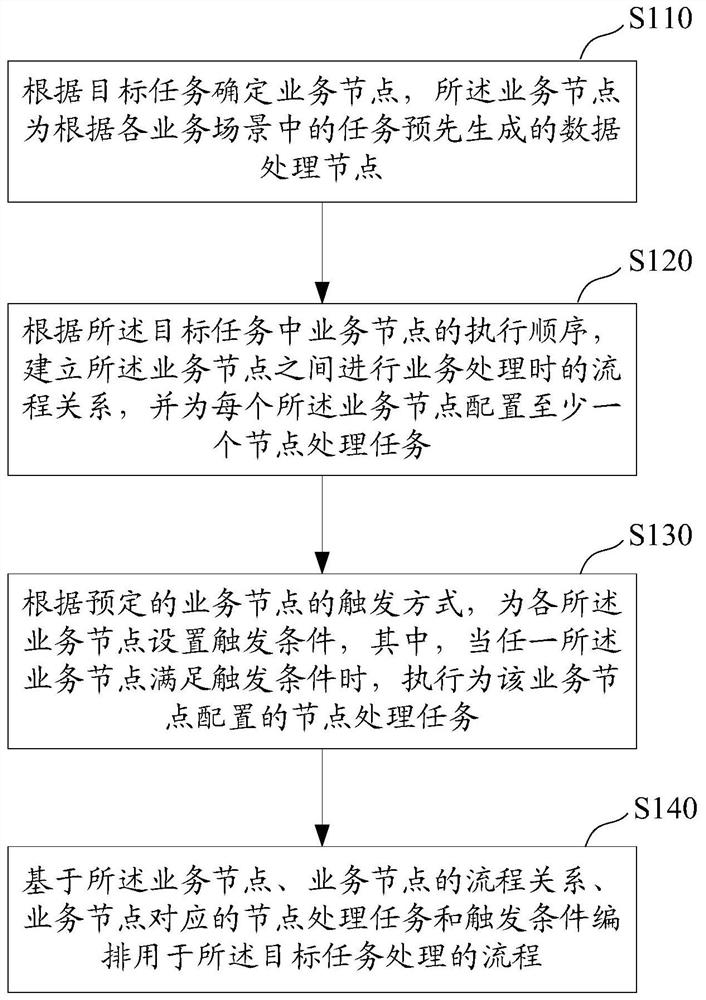

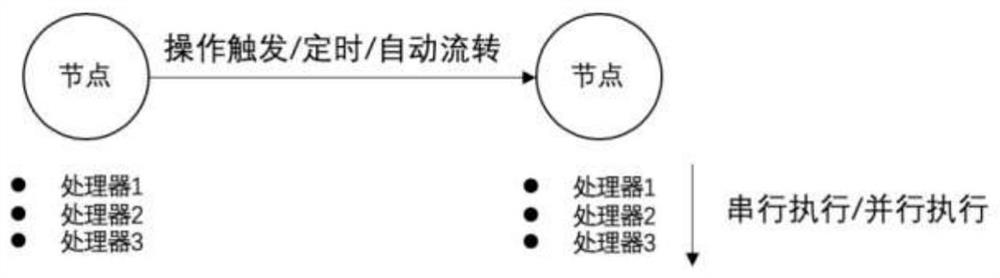

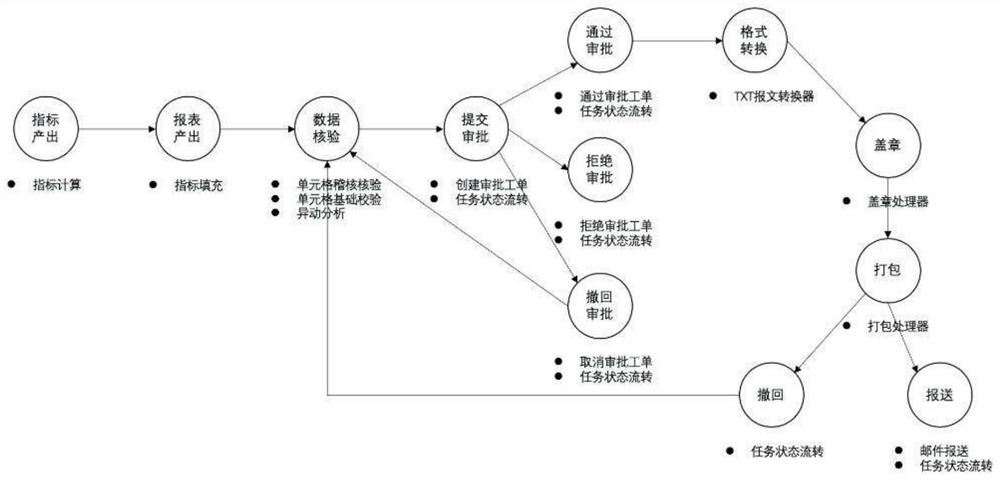

Task processing flow arrangement method and device and electronic equipment

The embodiment of the invention provides a task processing flow arrangement method and device and electronic equipment. The method comprises the following steps: determining service nodes according toa target task, establishing a flow relationship between the service nodes during service processing according to an execution sequence of the service nodes in the target task, and configuring at least one node processing task for each service node; triggering conditions are set for all the service nodes according to a preset triggering mode of the service nodes, wherein when any service node meets the triggering conditions, a node processing task configured for the service node is executed; and arranging a process for processing the target task based on the service node, the process relationship of the service node, the node processing task corresponding to the service node and the triggering condition. The technical scheme can be applied to the field of supervision, and arrangement of supervision disclosure task processing flows is realized.

Owner:ALIPAY (HANGZHOU) INFORMATION TECH CO LTD