Design method capable of using external synchronous for cameral with various data output formats

An output format and camera technology, applied in the direction of image communication, color TV parts, TV system parts, etc., can solve the problems of lack of output in multiple data formats, affecting the quality of original data, and single output signal, etc., to achieve The effect of easy interface of external equipment, less program running time, and quick programming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

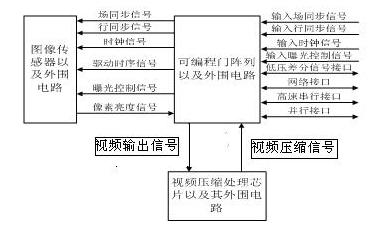

[0032] Embodiment 2, see attached image 3. On the basis of Embodiment 1, a video compression processing chip and its peripheral circuits are added. Adding a video compression processing chip can be a dedicated compression integrated circuit or a digital signal processing (DSP) chip. This example uses the TE3310 chip of TOKYO Company.

[0033] The programmable logic gate array receives the brightness signal of the pixels of the imaging plane output by the image sensor. Perform Bayer transformation to generate RGB format video signal, and then convert RGB format video signal to YUV format video signal. The programmable logic gate array outputs the video output signal (RGB signal or YUV signal) to the video compression processing chip, and the video compression processing chip completes M-JPEG compression or H264 compression, and sends the compressed data to the programmable logic gate array FPGA.

Embodiment 3

[0034] Embodiment 3, see attached Figure 4 . On the basis of Embodiment 1, an embedded processing chip and a peripheral circuit interface module are added. The added embedded processing chip can be an ARM chip or a POWER PC chip. What this example uses is the AR91RM9200 chip of Atmel Company. The high-speed serial interface, parallel interface, and low-voltage differential signal interface in the external communication interface are connected to the programmable gate array module, and the two-way communication of the above-mentioned interfaces is realized by the programmable gate array module FPGA. The network interface is connected to the embedded chip, and the embedded chip completes the network communication. The communication between the embedded chip and the programmable gate array module FPGA is completed through the parallel interface on the board. The programmable logic gate array receives the brightness signal of the pixels of the imaging plane output by the imag...

Embodiment 4

[0035] Embodiment 4, see attached Figure 5 . On the basis of Embodiment 1, a video compression processing chip and its peripheral circuits, an embedded processing chip and a peripheral circuit interface module are added. Like Embodiment 3, the high-speed serial interface, parallel interface, and low-voltage differential signal interface in the external communication interface are connected to the programmable gate array module, and the bidirectional communication of the above-mentioned interfaces is realized by the programmable gate array module FPGA. The network interface is connected to the embedded chip, and the embedded chip completes the network communication. The communication between the embedded chip and the programmable gate array module FPGA is completed through the parallel interface on the board.

[0036] The programmable logic gate array receives the brightness signal of the pixels of the imaging plane output by the image sensor. Perform Bayer transformation t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More