Method for reducing area of digital logic circuit

A technology of digital logic circuits and areas, applied in the direction of logic circuits using basic logic circuit components, logic circuits using specific components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

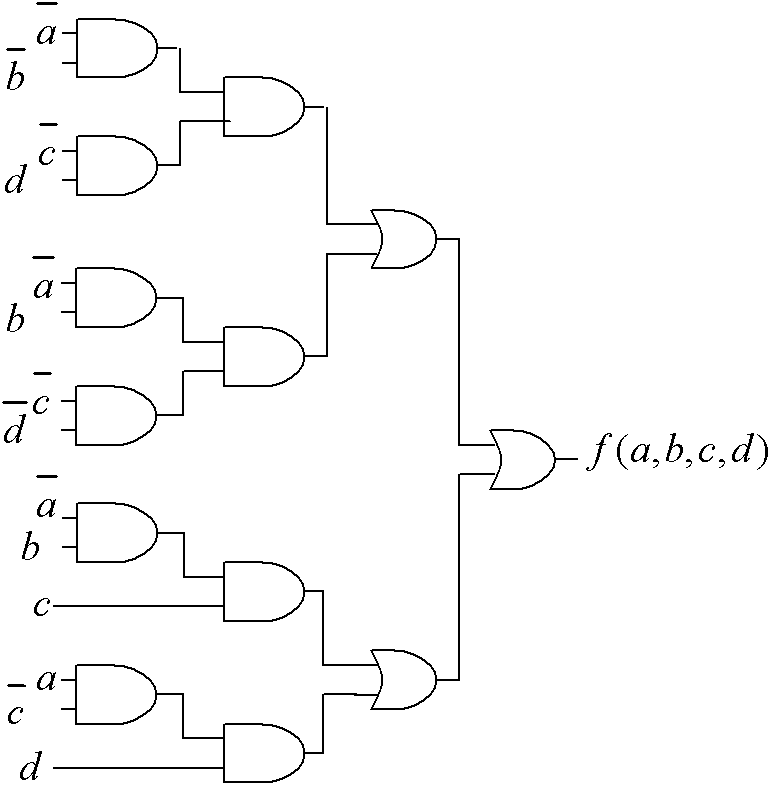

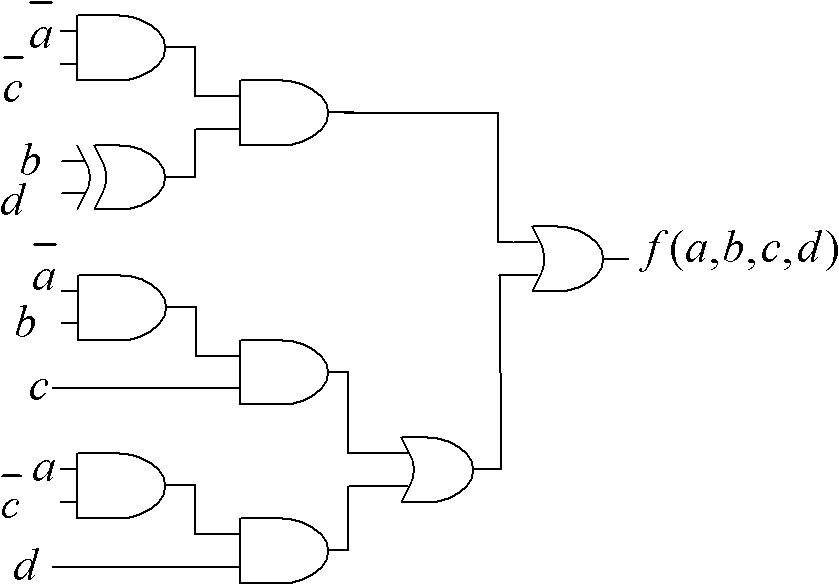

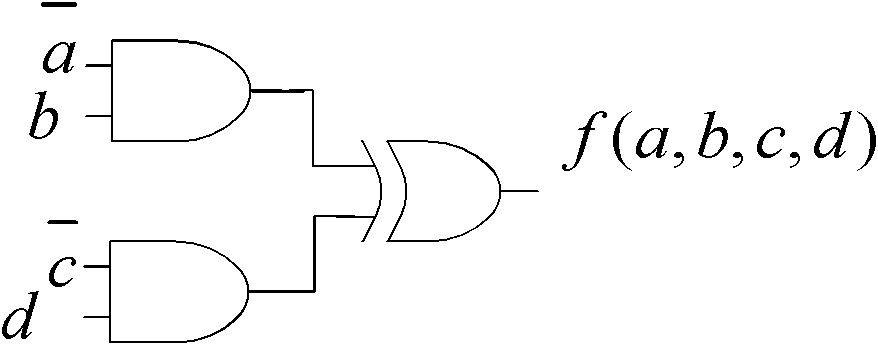

Image

Examples

Embodiment

[0033] A method to reduce the area of digital logic circuits, the logic function to be optimized is defined as f , f The optimized function is defined as f op ; f The set of product terms of is defined as S p ;like S p contains w product terms, any one of which is defined as p i ; D pi represents the product term p i The dimensionality of , that is, for a n function of variables, if the logistic function f a product of p i contain m variables, m≤n ,but p i The dimension of D pi =( n-m ); and order f op The initial value of is "0" and the specific steps are:

[0034] step a. Define the generalized Hamming distance: for a given n logistic function of variables f , and any two product terms of it are ,in i and j None greater than w; the product term p i and p j The generalized Hamming distance between p i and p j The difference between the values; the generalized Hamming distance is equal to the number of variables that meet the follo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More