Self-correction precursor 0/1 predicting unit for floating-point adder

A prediction unit and adder technology, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of counting error, leading 0 prediction unit inaccuracy, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0085] The present invention will be described in further detail below in conjunction with the accompanying drawings.

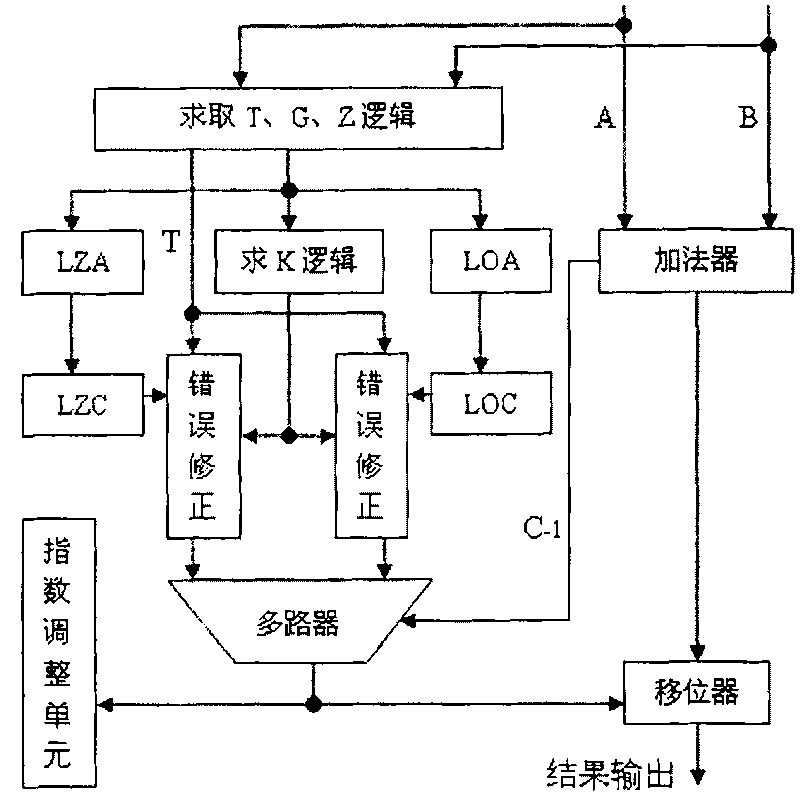

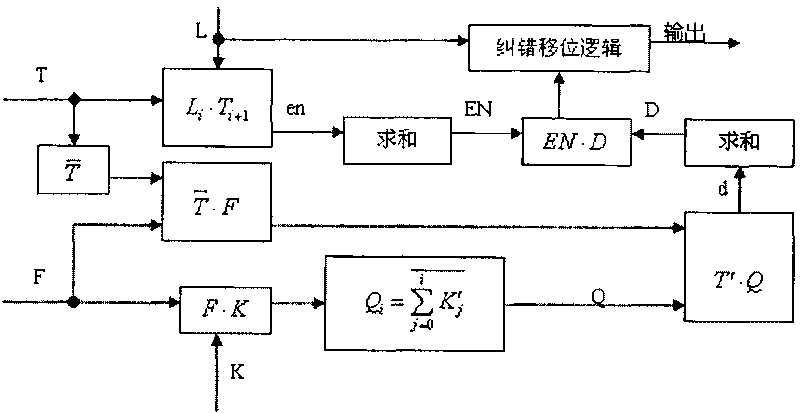

[0086] see figure 1, used for the self-correcting leading 0 / 1 prediction unit of the floating-point adder, for the addition operation of two specific numbers, the T, G, Z signals can be obtained by bitwise processing, and then T, G, The leading 0, 1 prediction can be realized by processing the Z three signals. Due to the combination of leading 0 and 1 prediction units, the hardware structure will inevitably be complicated, and the critical path will become longer, which is not conducive to improving the speed. Therefore, in the design of the present invention, the method of separating the leading 0 prediction unit and the leading 1 prediction unit is adopted, and the following two formulas are respectively used to calculate f i :

[0087] f i =T i ·Z i+1 , i≥0 (15)

[0088] f i =T i ·G i+1 , i≥0 (16)

[0089] Among them, formula (15) is the calcula...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More