Mode-based multiply-add processor for denormal operands

An anti-standard, processor technology, applied in the direction of electrical digital data processing, calculation using digital representation, digital data processing components, etc., can solve the problem of reducing the maximum operating frequency, increasing the minimum cycle time, increasing the silicon area, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

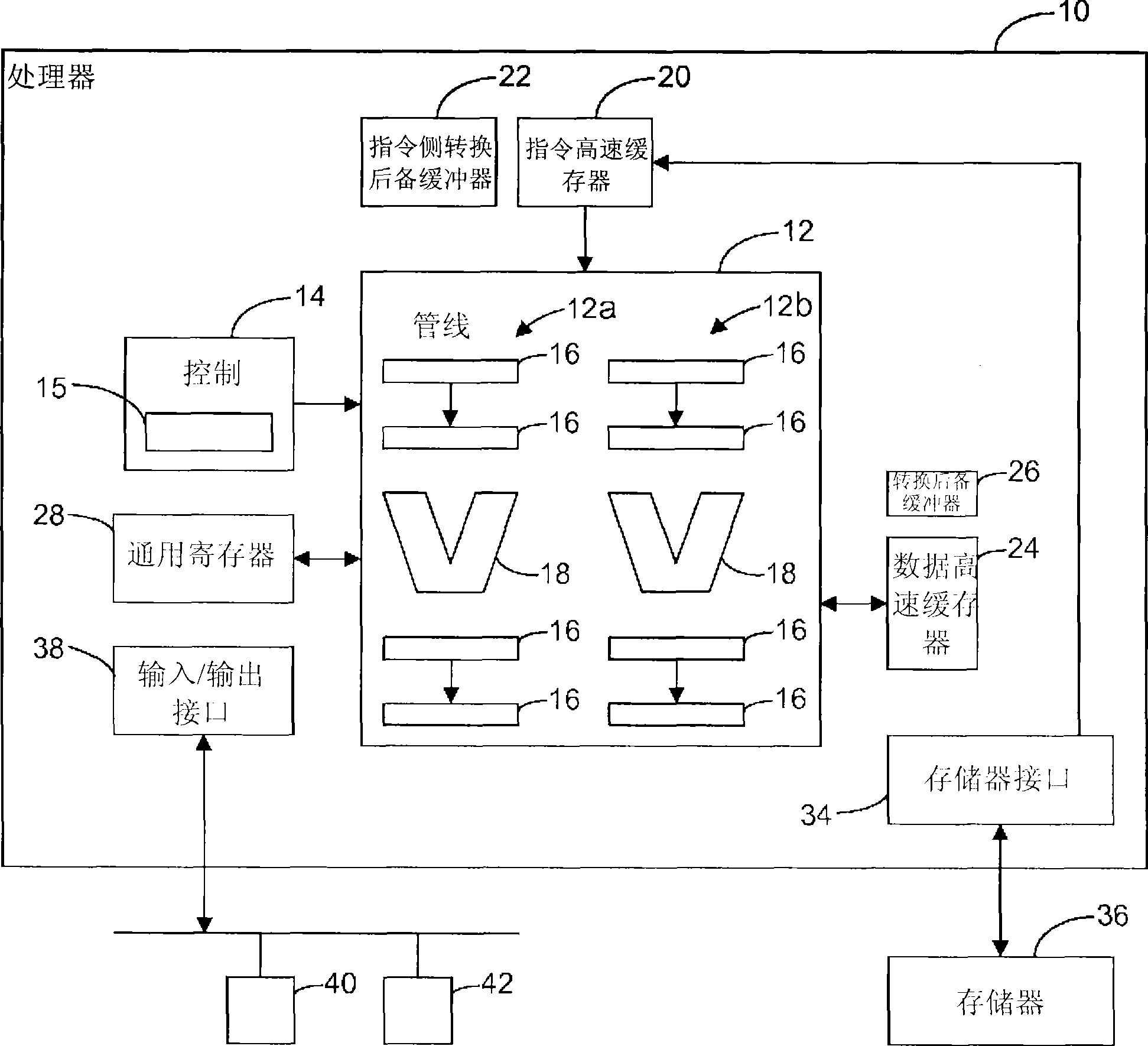

[0018] figure 1 A functional block diagram of processor 10 is depicted. Processor 10 executes instructions in instruction execution pipeline 12 according to control logic 14 . Control logic 14 includes one or more registers, such as status register 15 , that define various modes of operation. Pipeline 12 may be a superscalar design with multiple parallel pipelines (eg, 12a and 12b). Each pipeline 12a, 12b includes various registers or latches 16 organized into pipeline stages, and one or more arithmetic logic units (ALUs) 18 . Pipeline stage registers or latches 16 and ALU 18 may read operands from and / or write results to registers in general register file 18 .

[0019] The pipelines 12a, 12b fetch instructions from an instruction cache (I-cache or I$) 20 where memory addressing and permission are managed by an instruction-side translation lookaside buffer (ITLB) 22 . Data is accessed from a data cache (D-cache or D$) 24 where memory addressing and permissions are managed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More