Multiplication rounding implementation method and device

An implementation method and a rounding technology, which are applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems affecting the performance of floating-point processing units and low calculation efficiency, and achieve the goal of improving performance and improving execution efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

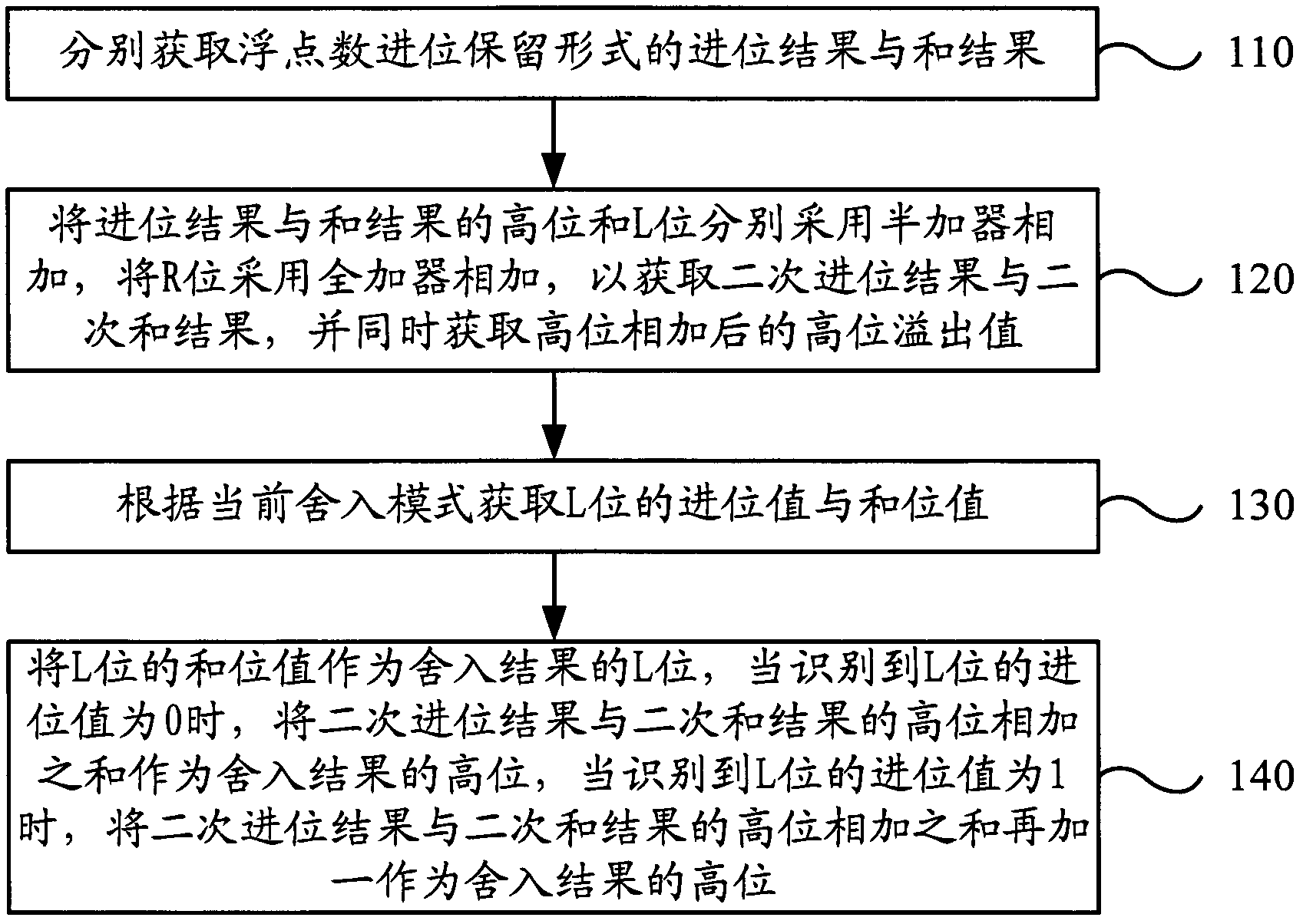

[0033] figure 1 It is a flow chart of the implementation method of multiplication and rounding provided by Embodiment 1 of the present invention. The method of this embodiment specifically includes the following steps:

[0034] Step 110. Obtain the carry result and sum result of the carry-reserved form of the floating-point number respectively. As mentioned above, the floating-point number is divided into high bit, L bit, R bit and sticky bit, the L bit is the lowest bit of the reserved part, and the high bit is the reserved part For the remaining part except the L position, the R position is the highest position of the truncated part, and the sticky position is the remaining part of the truncated part except the R position;

[0035] Step 120, add the high bit and L bit of the carry result and the sum result respectively using a half adder, and add the R bit using a full adder to obtain the secondary carry result and the secondary sum result, and simultaneously obtain the high...

Embodiment 2

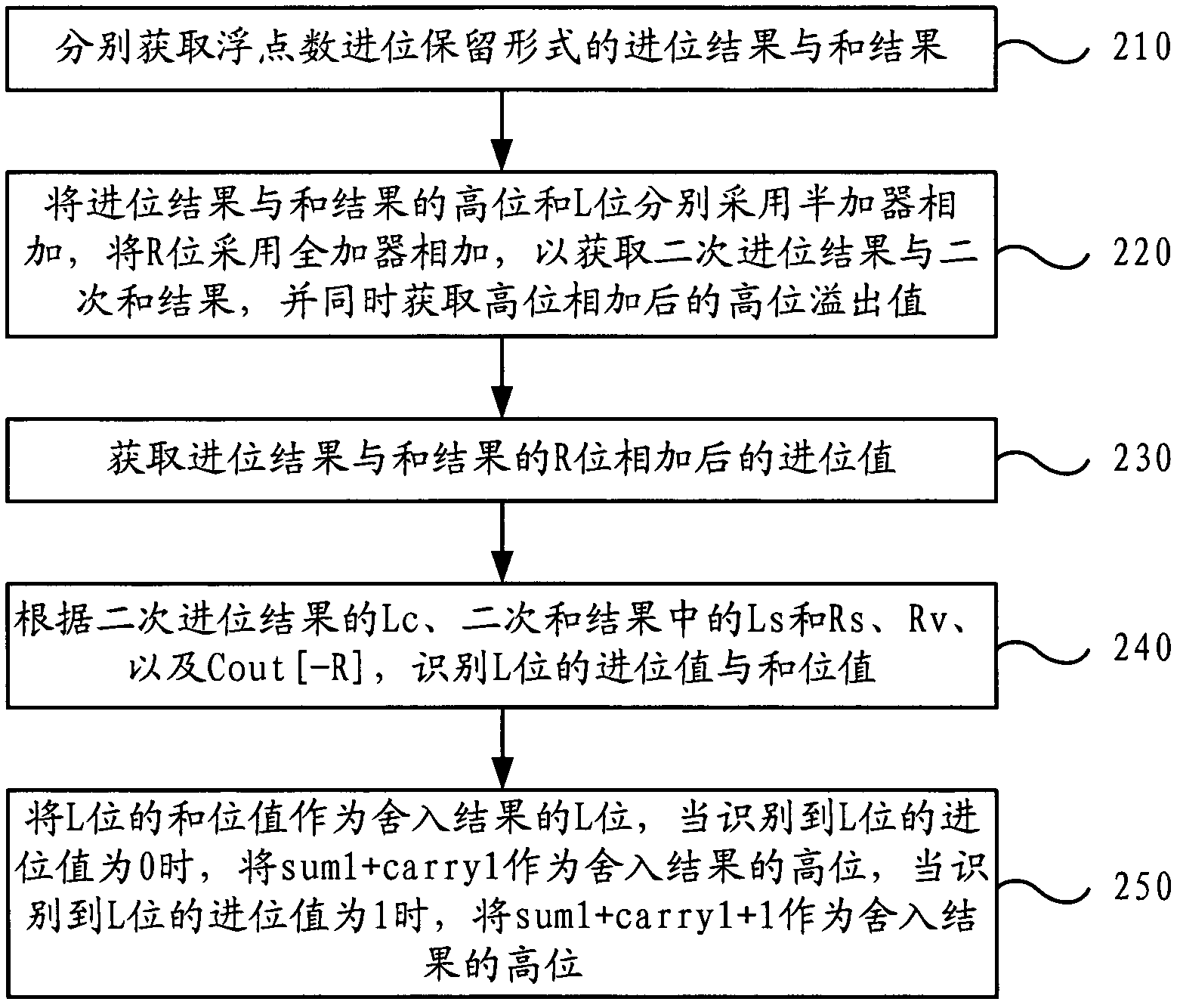

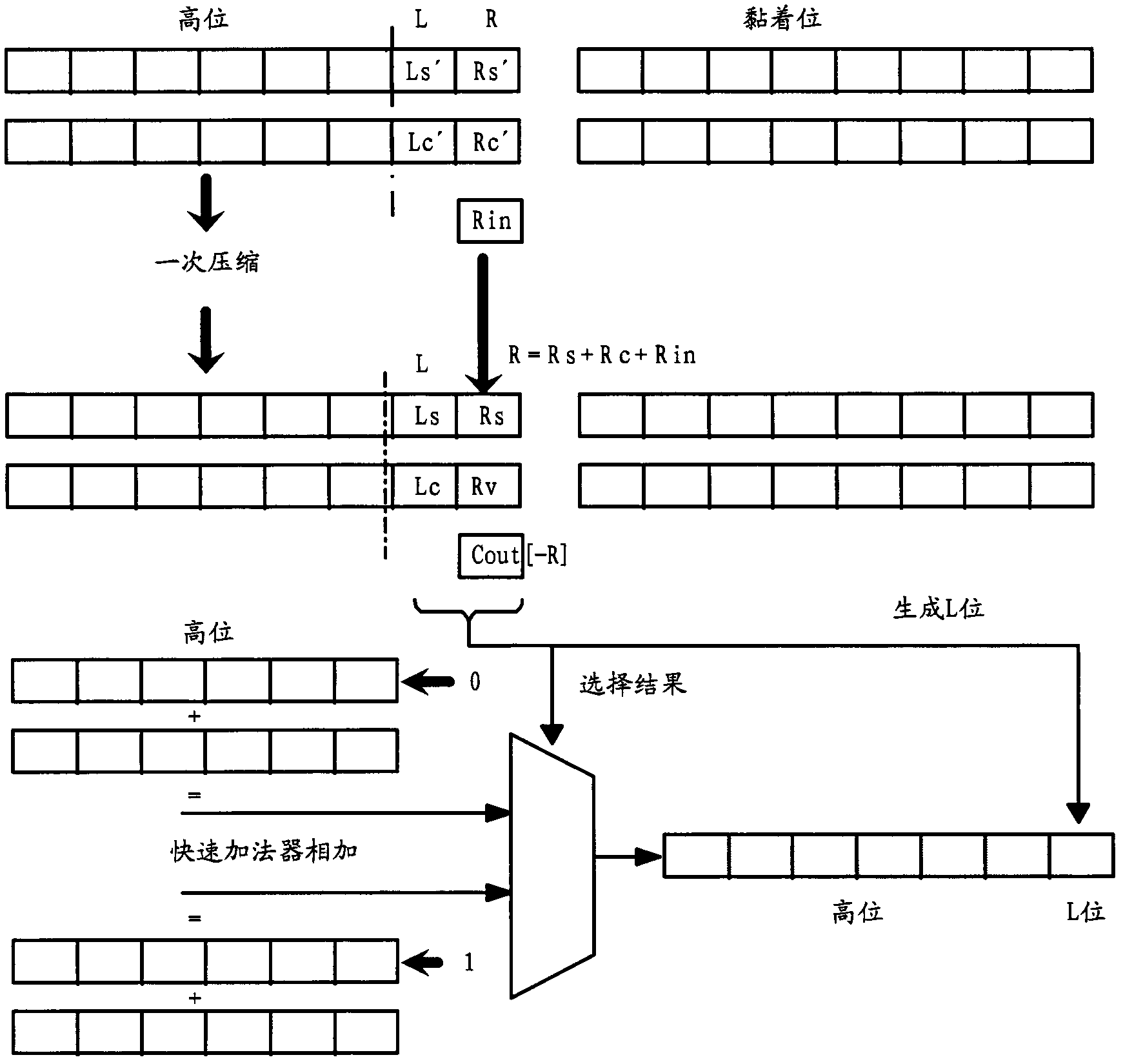

[0045] figure 2 It is a flowchart of a method for implementing multiplicative rounding provided by Embodiment 2 of the present invention. This embodiment is specifically a method for rounding floating-point numbers according to the round-to-nearest mode. Rounding to the nearest can be achieved by rounding to the nearest upper limit (Round to Nearest Up, RNU for short) and then correcting the L bit. For the correction of the L bit, according to the inventor's research in the process of implementing the present invention, it is found that rounding to the nearest can be done by adding 1 to the R bit of the rounded result, and when the sticky bits of the rounded result are all 0, the rounded The L position of the result is 0 to get. For the two cases of overflow and non-overflow, when there is no overflow, 1 should be added to the R bit of the rounded result; when overflow, 1 should be added to the L bit, that is, the upper bit of the R bit, which is equivalent to the R bit Add...

Embodiment 3

[0065] Figure 4 It is a flow chart for judging a tie situation in the implementation method of multiplication and rounding provided by Embodiment 3 of the present invention. This embodiment is based on Embodiment 2 and further considers the tie situation in the round-to-nearest mode. The so-called tie situation means that the value represented by the truncated part in the result to be rounded is the average value of the upper limit and the lower limit of the numerical value of the equivalent length. At this time, the result to be rounded is in the middle of the two nearest values. If binary 110.1000 is rounded to an integer, 1000 is equal to one-half of (0+1111). The IEEE754 standard specifies rounding to the nearest even number in this case.

[0066] Since the rounding to the nearest provided by Embodiment 2 is realized by rounding to the nearest upper limit, when a tie occurs, it is only necessary to set the L position of the rounding result obtained by rounding to the ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More