Floating point multiplier-adder

A floating-point multiplier and adder technology, which is applied in the fields of instrumentation, calculation, and electrical digital data processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The technical solutions of the present invention are described in detail below, but the protection scope of the present invention is not limited to the embodiments.

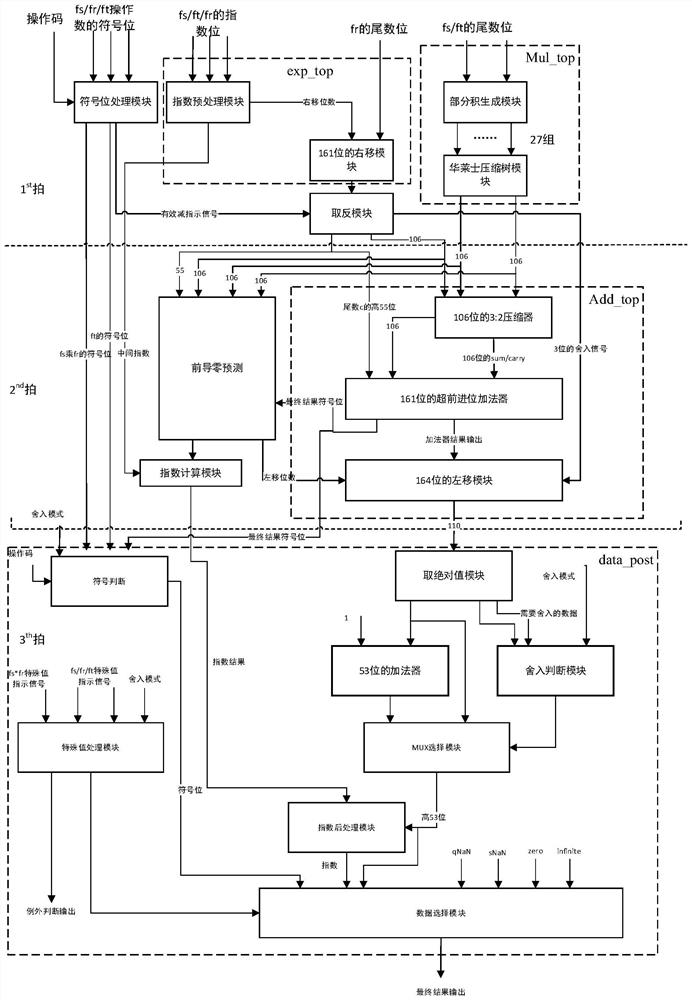

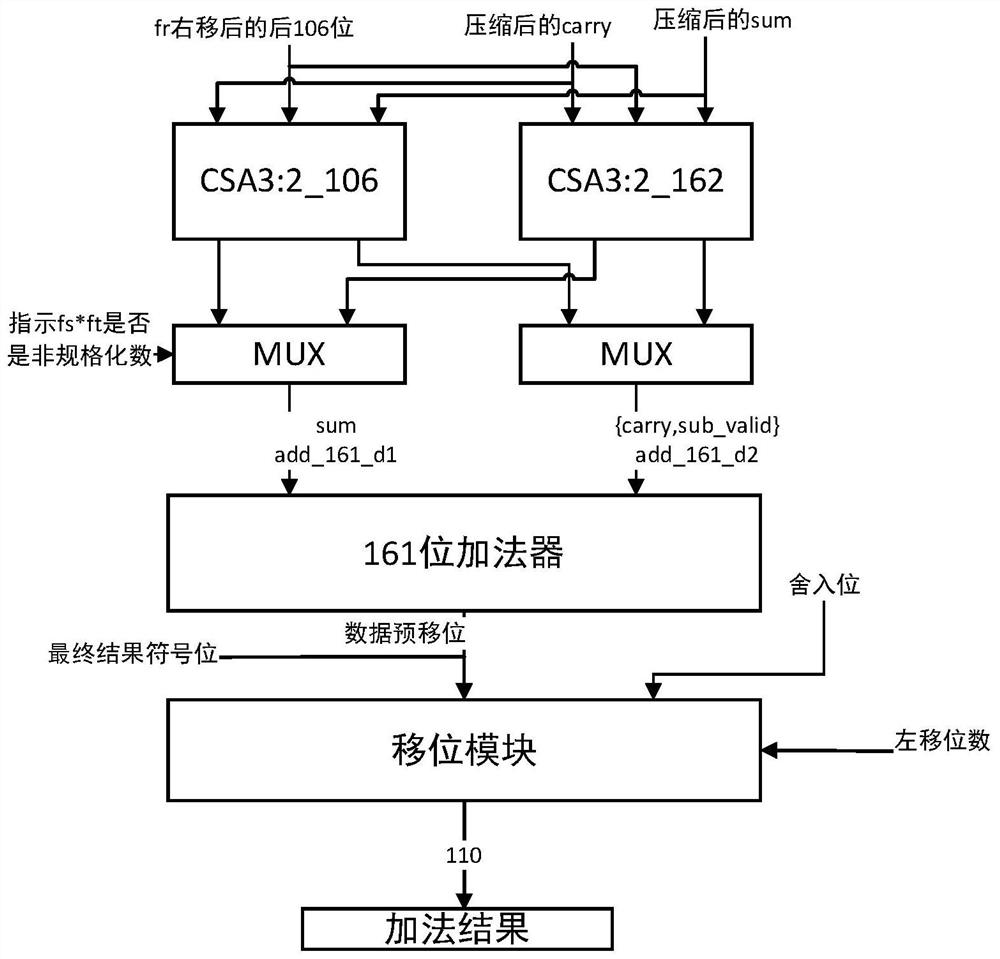

[0038] In order to make the content of the present invention more obvious and easy to understand, the following is combined with the appendix figure 1 -Attached Figure 5 and specific implementations for further description.

[0039] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

[0040] like figure 1 As shown, a floating-point multiplier-adder proposed by the present invention realizes the floating-point multiply-add operation in the form of A*B+C. The floating-point m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More