Scheduling method for directed acyclic graph tasks in heterogeneous multi-core processor system

A multi-core processor and directed acyclic graph technology, applied in the field of computer systems, can solve the problems of not considering the impact and low processor utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

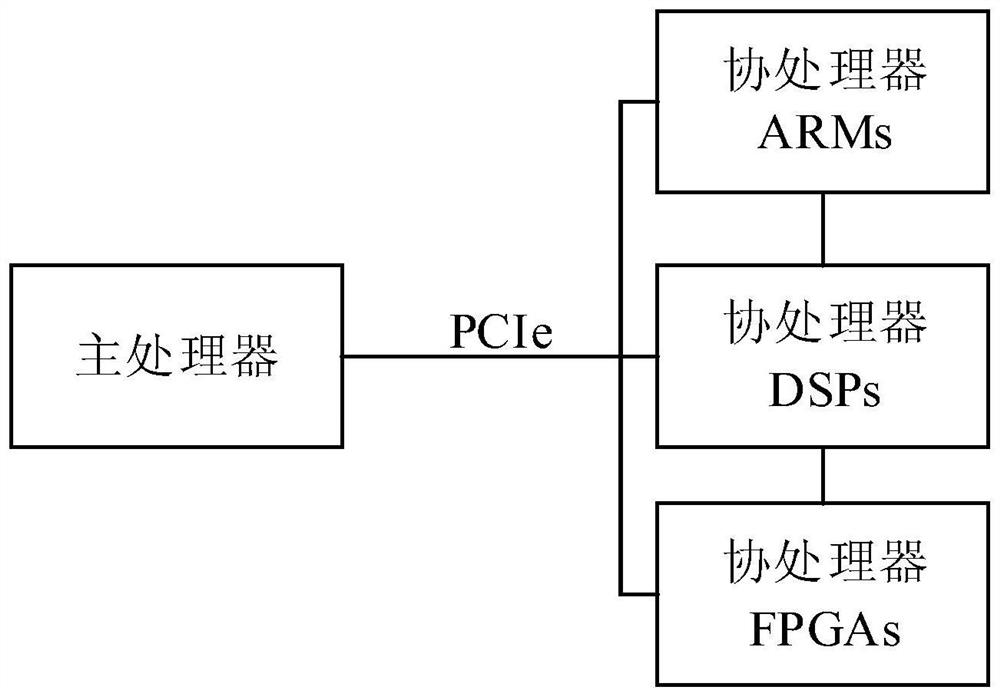

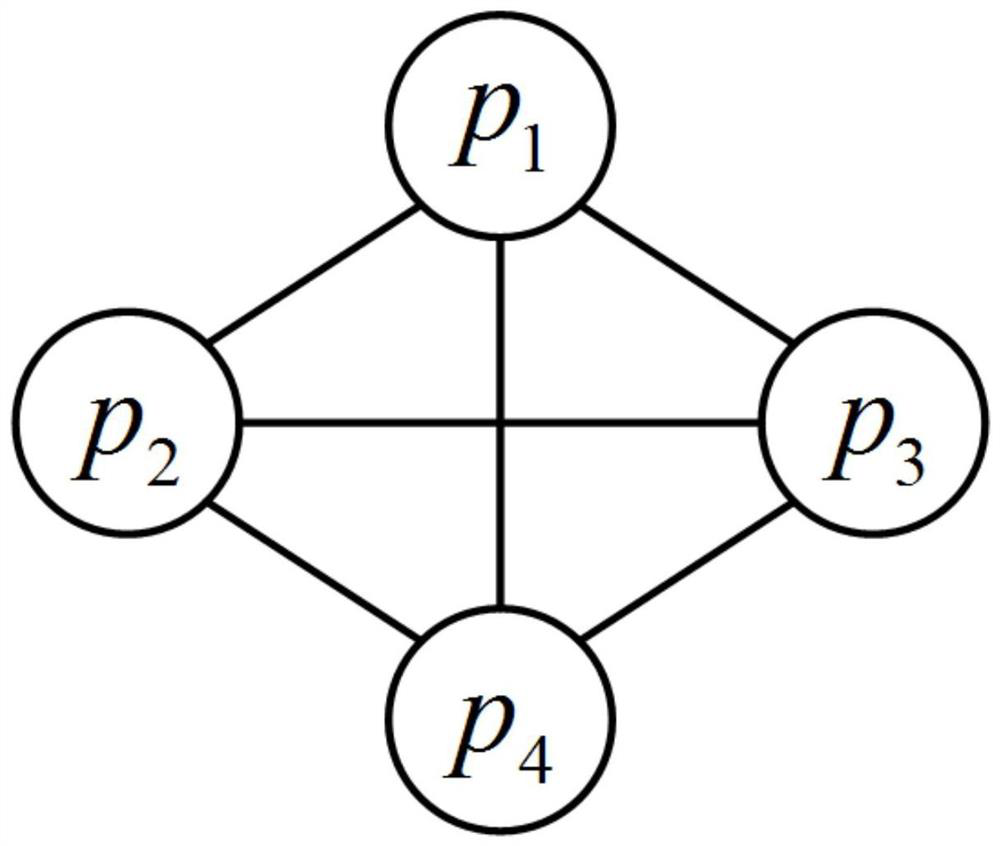

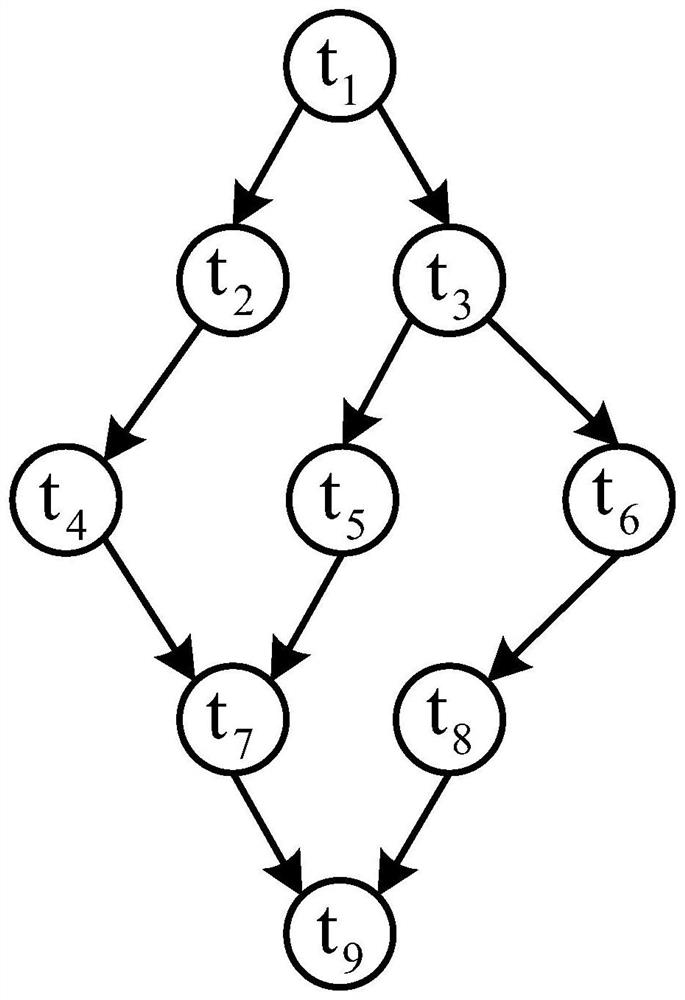

[0035] A method for scheduling directed acyclic graph tasks in a heterogeneous multi-core processor system. The heterogeneous multi-core processor system used by the method is as follows: figure 1 shown. The system consists of a main processor and M heterogeneous coprocessors such as ARM, DSP, and FPGA. The main processor is responsible for data input and collection of coprocessor processing results, and different types of heterogeneous processors are responsible for performing calculation tasks. The set of coprocessors is denoted as P={p 1 ,p 2 ,...,p M}, processor p m The calculation frequency is f m , which represents the number of bits of tasks that the processor can perform per second. Processor topology composed of all coprocessors figure 2 The fully connected undirected graph representation shown, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More