FPGA-based expandable sparse matrix vector multiplication processor

A sparse matrix and processor technology, which is used in electrical digital data processing, instruments, machine execution devices, etc., to achieve the effects of high-efficiency computing, good computing efficiency, and high data throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0023] In this embodiment, the sparse matrix in the scalable sparse matrix-vector multiplication processor adopts the CSC compressed storage format, that is, three different arrays are used to describe the positions of non-zero elements in the sparse matrix. The three arrays are: the data array that stores all non-zero element values in order from top left to bottom right, the row array that records the row number corresponding to each non-zero element, and records the first non-zero element in each column in the data array The ptr array of serial numbers. figure 1 Represents a sparse matrix of size 4*5 stored in a compressed storage format. In this embodiment, the sparse matrix in the scalable sparse matrix-vector multiplication processor adopts the CSC compression storage format as follows:

[0024]

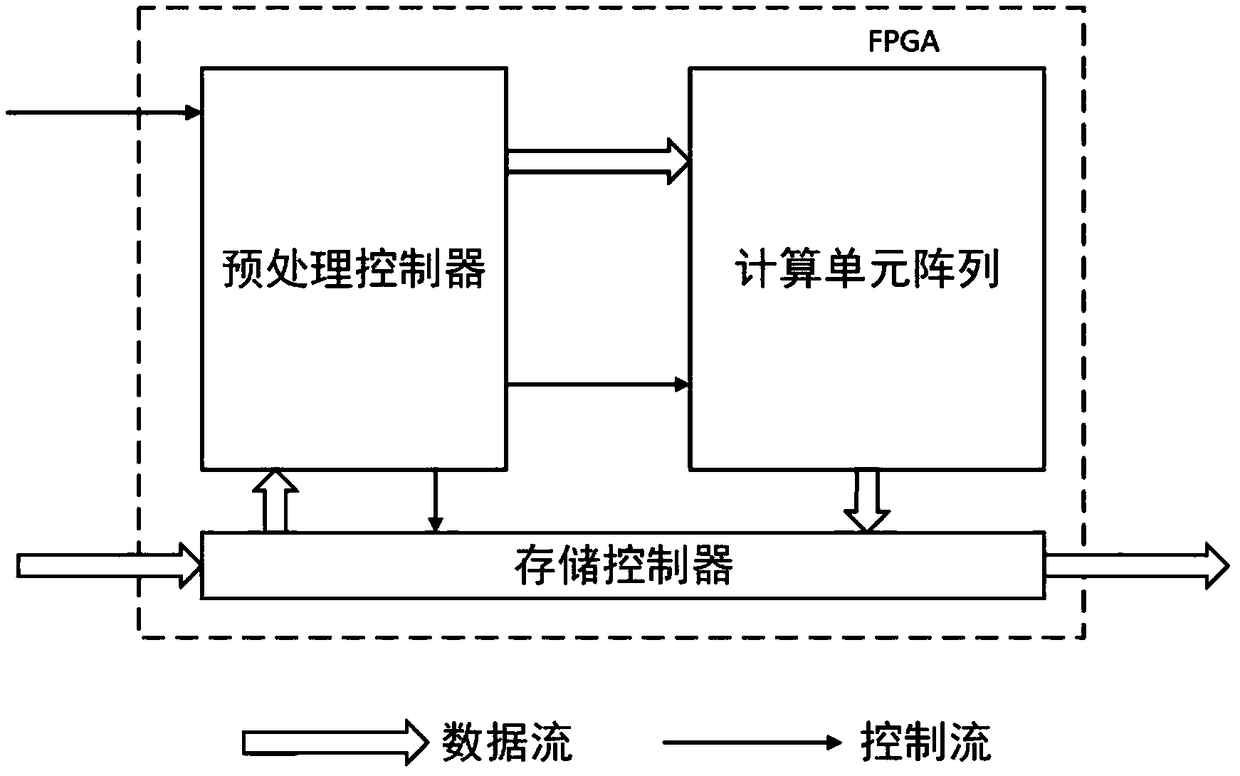

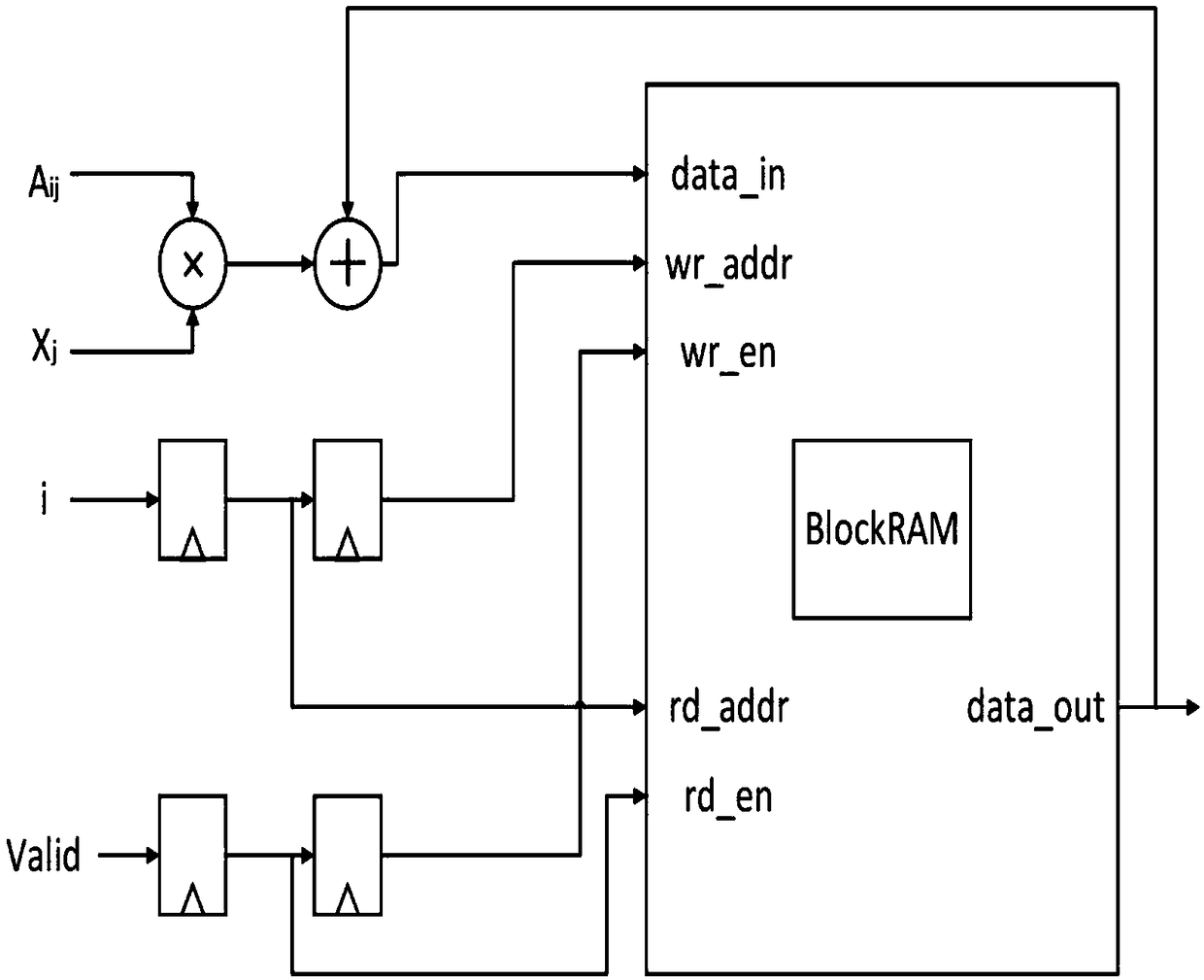

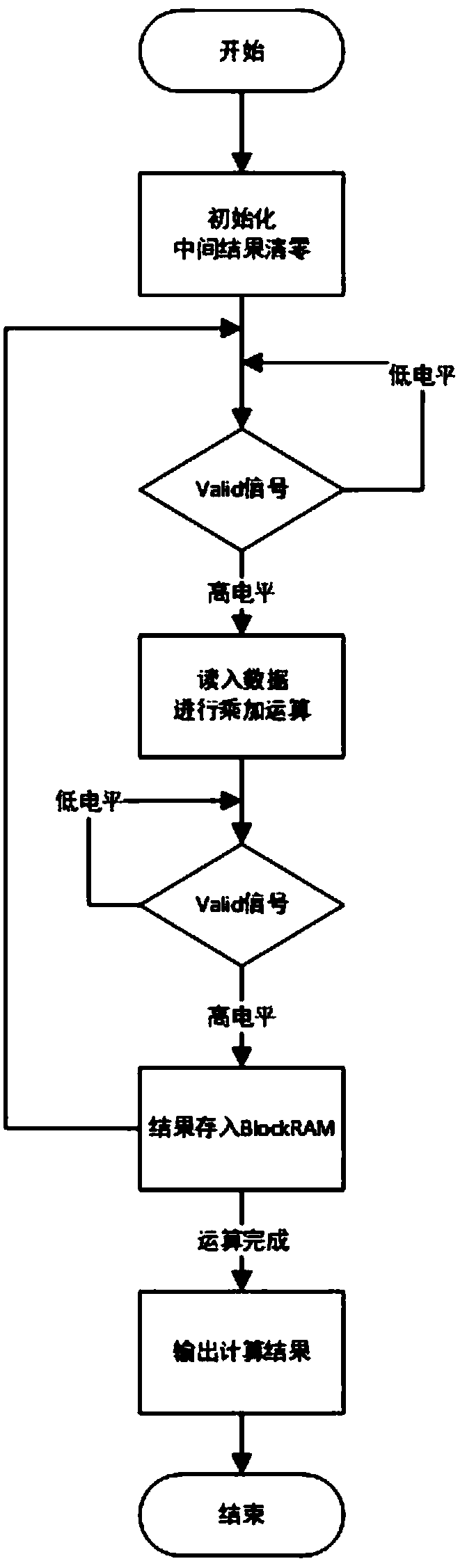

[0025] Such as figure 1 , the scalable sparse matrix-vec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More