Floating-point multiplicator and method of compatible double-prepcision and double-single precision computing

A floating-point multiplier and single-precision technology, which is applied to calculations using number system representations and calculations using non-contact manufacturing equipment, can solve problems such as reducing the execution time of double-precision operations and hardware waste

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0081] Example 1: Floating-point double-precision multiplication (expressed in hexadecimal) 0x3ff0000000000000×0x3fffffffffffffff.

[0082] 1. After the 53-bit mantissa passes through the first selector 2, it outputs 0x10000000000000.

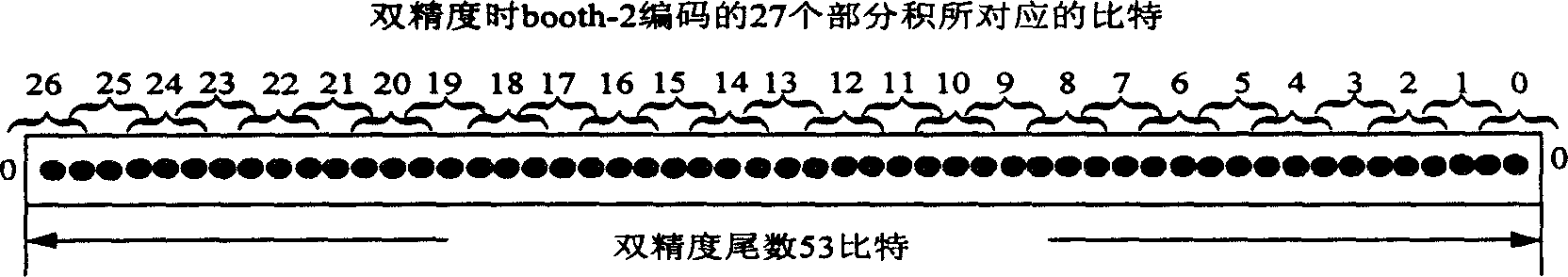

[0083] 2. First use the base-2 Potts encoder 3 to encode the 53-bit mantissa of the multiplier 0x3ff0000000000000 (implicit 1 is added in front of the 52 bits) 0x10000000000000 using the above encoding table to be encoded as {1, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0, -0 , -0, -0, -0, -0, -0, -0, -0}, and then multiply the encoded result with the mantissa 0x1fffffffffffff (53 bits) of the multiplicand 0x3fffffffffffffff to obtain 27 partial products, 0 ~26 partial products are all 0, and the 27th partial product is 0x1fffffffffffff.

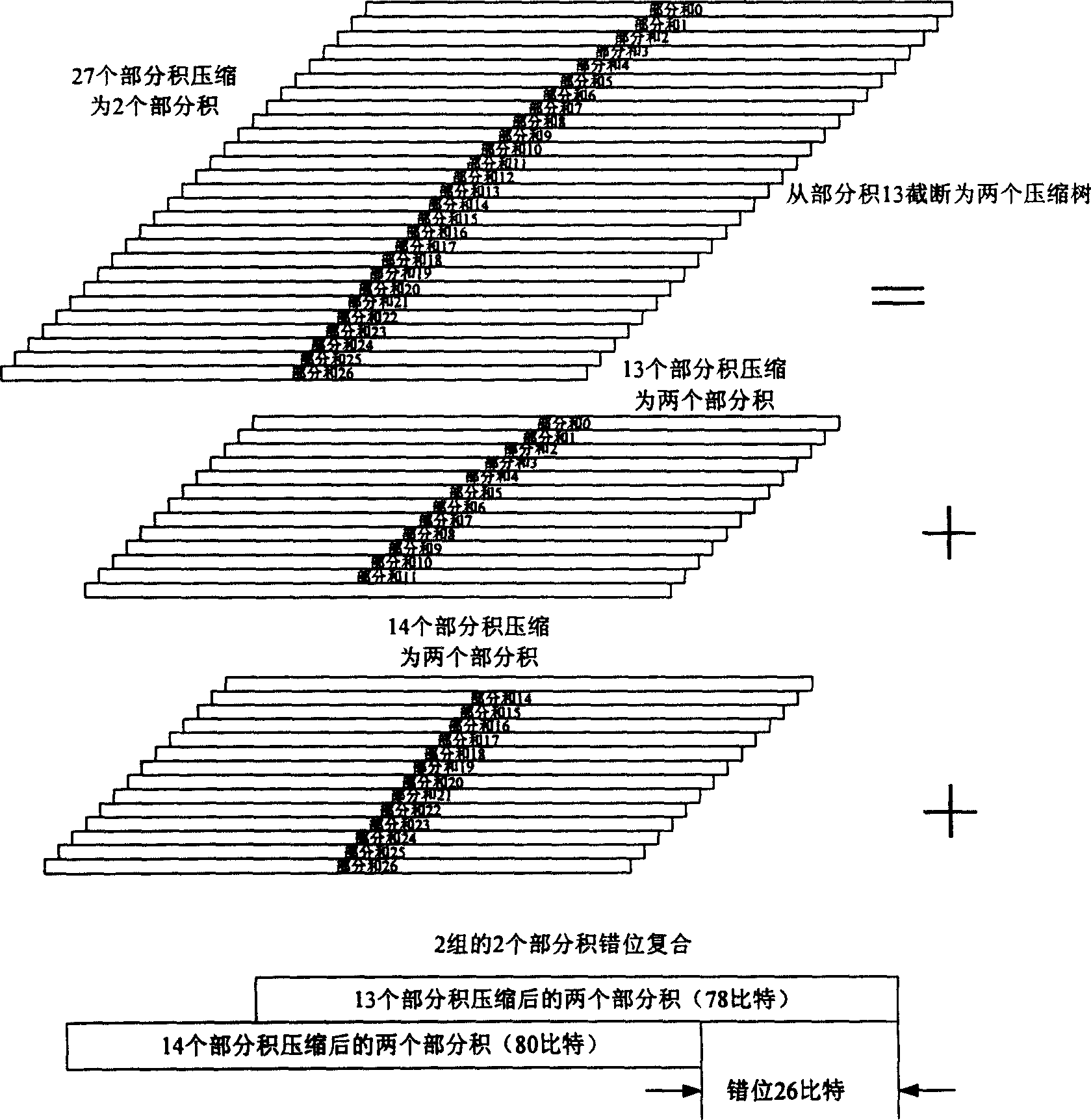

[0084] 3. The 0th to 12th partial products are sent to the 13:2 compression tree 4 for compression, the 13th to 26th partial products are sent to the 14:2 compression tree 5 f...

example 2

[0090] Example 2: Floating-point double-single-precision multiplication (expressed in hexadecimal) 0x3f8000003f800000×0x3fffffff3fffffff.

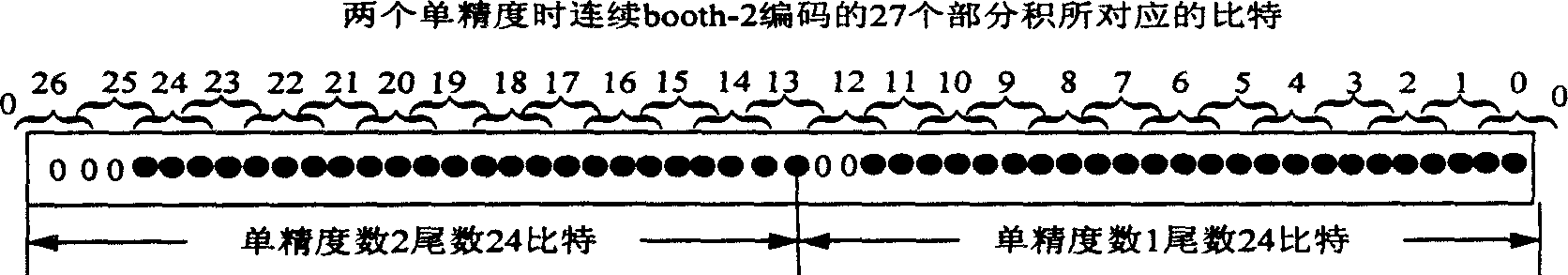

[0091] 1. The mantissa of the double-single-precision multiplier 0x3f8000003f800000 is filled into 53 bits 0x02000000800000 through the double-single-precision continuous encoding filling unit 1 .

[0092] 2. Through the first selector 2, select and output 53 bits 0x02000000800000.

[0093] 3. Using base 2 Potts encoder 3, the encoding becomes {0, 1, -2, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, -2, 0 ,0,0,0,0,0,0,0,0,0,0}. Multiply the coded result with the two mantissas of the multiplicand 0x3fffffff 3fffffff to get 27 partial products, the 0th to 12th partial products are the multiplication results of the first single precision, and the 13th to 27th are the second single precision the result of the multiplication.

[0094] 4. For the first single precision, send 0 to 12 partial products to the 13:2 compression tree 4 for compression to obt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More