Patents

Literature

38 results about "Sign extension" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Sign extension is the operation, in computer arithmetic, of increasing the number of bits of a binary number while preserving the number's sign (positive/negative) and value. This is done by appending digits to the most significant side of the number, following a procedure dependent on the particular signed number representation used.

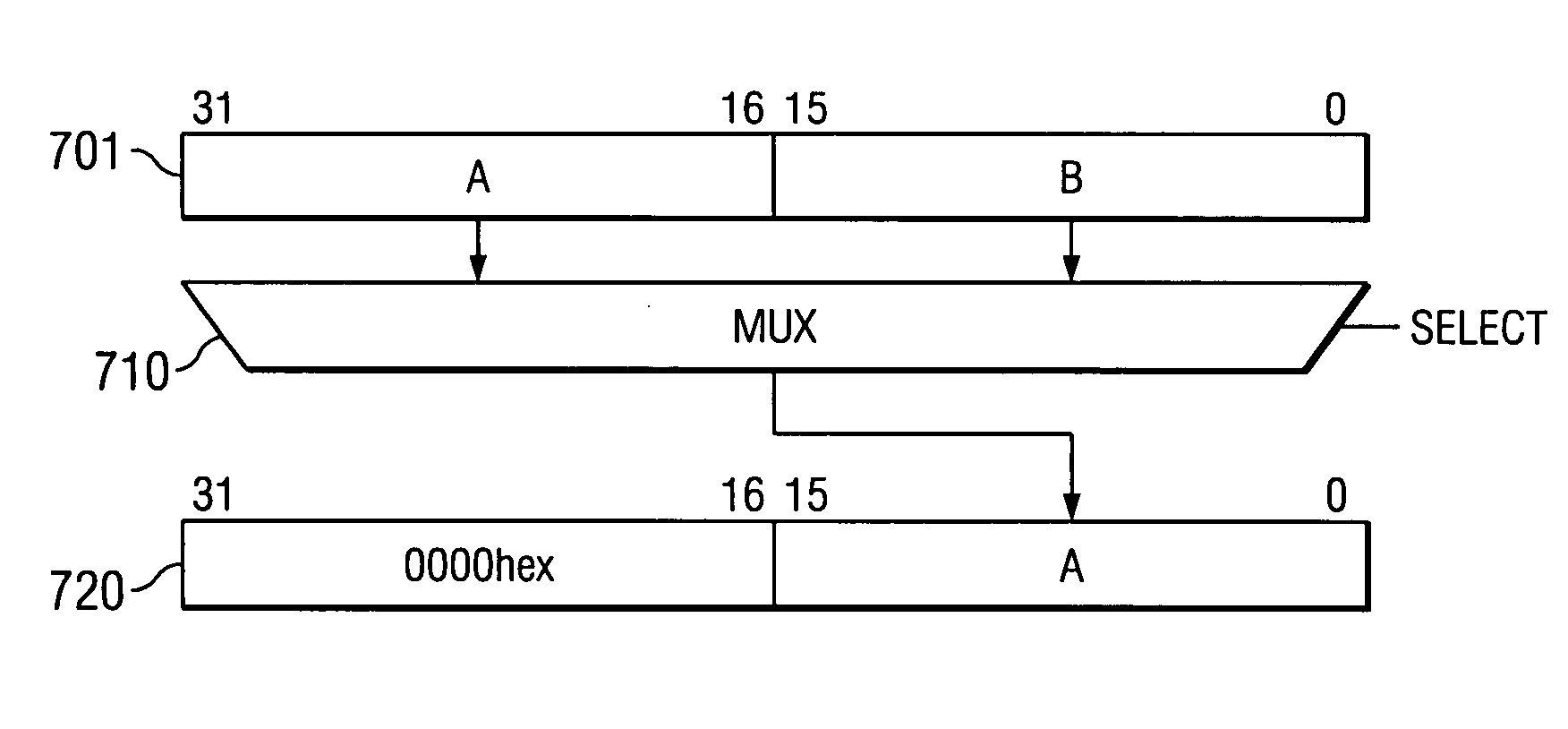

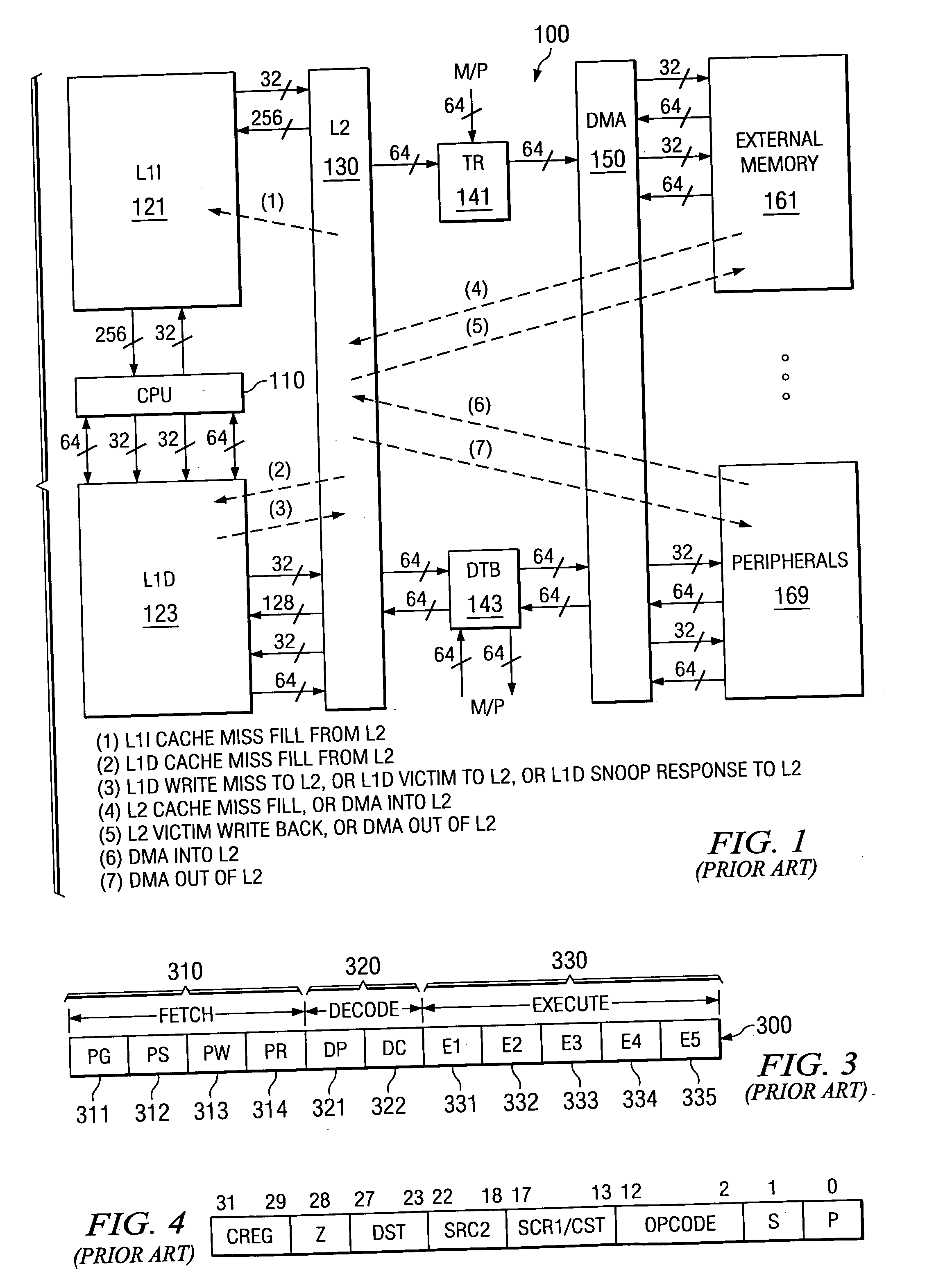

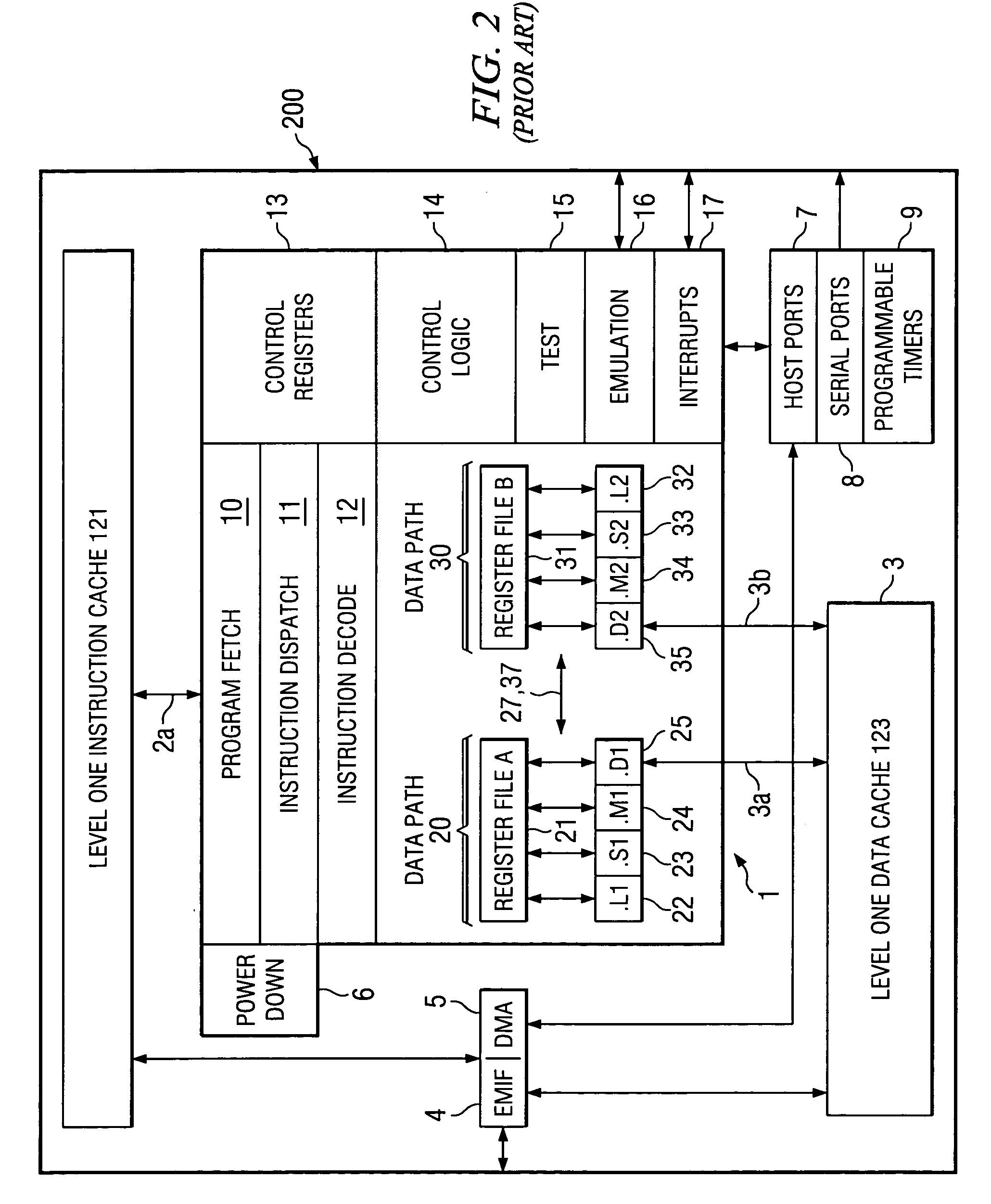

Register move instruction for section select of source operand

ActiveUS20050203928A1Reduces and eliminates time lostSpeed rateGeneral purpose stored program computerMemory systemsMultiplexerExecution unit

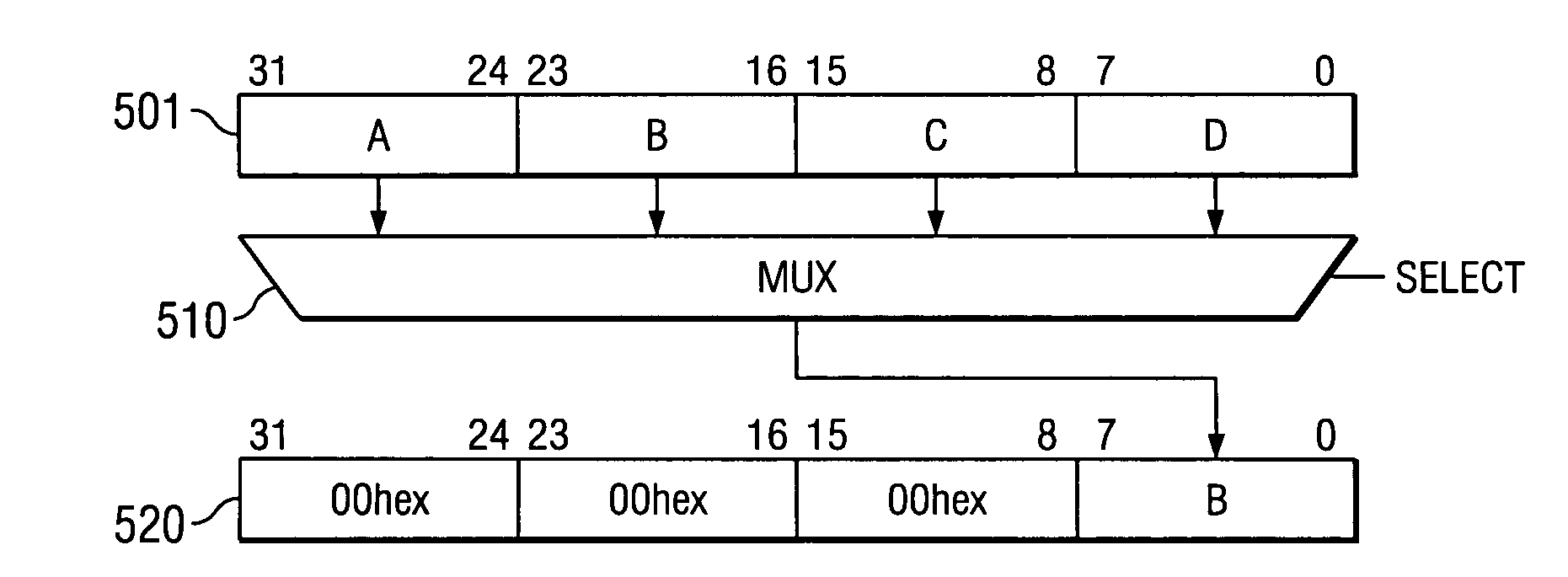

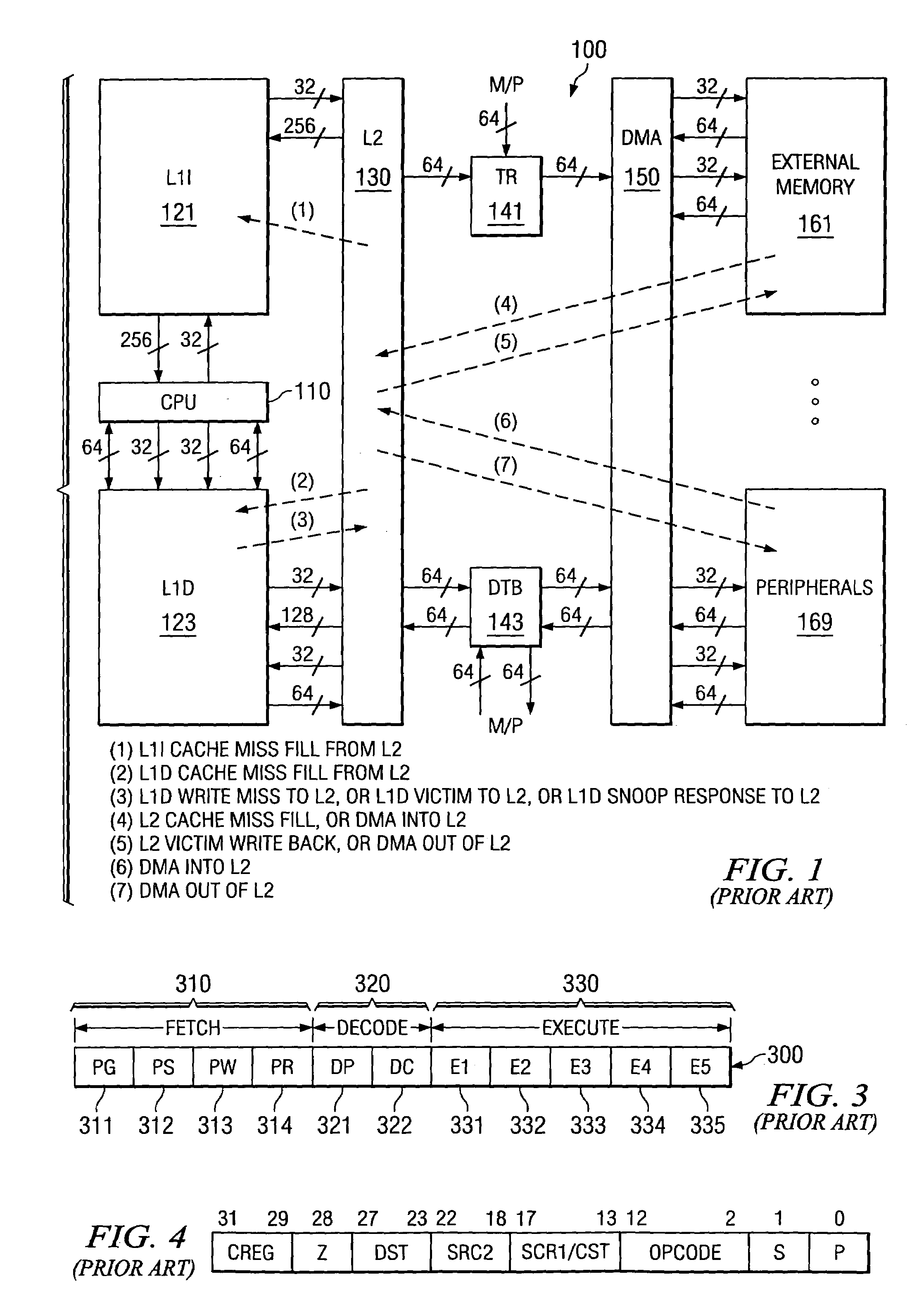

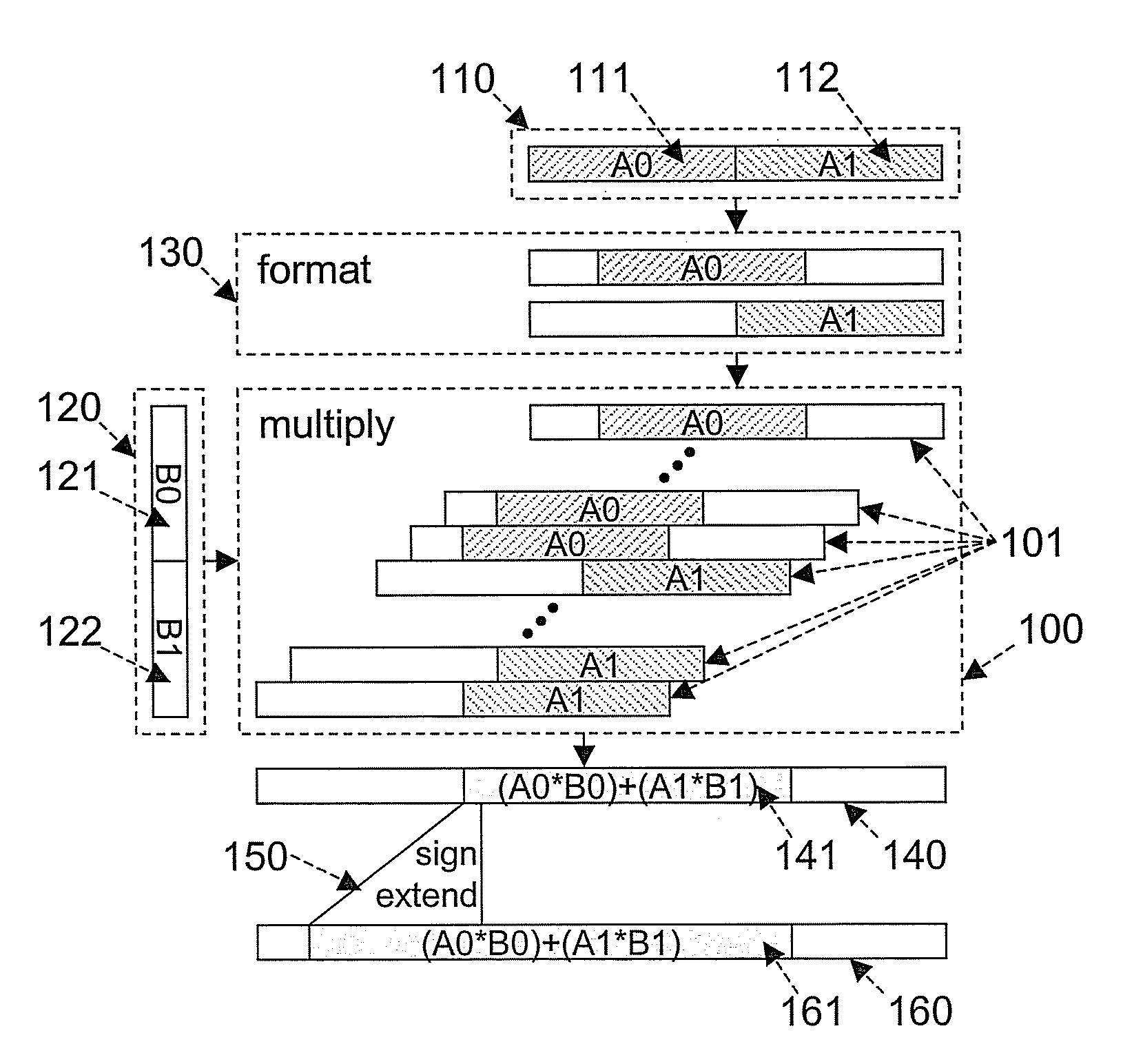

A data processing apparatus execution unit includes a multiplexer having inputs receiving data from sections of a source data register or registers. The multiplexer selects data from one section to store in a destination data register. The execution unit may zero extend or sign extend the remaining most significant bits of the destination data. In an alternative embodiment, the execution unit includes plural multiplexers, one for each section of the destination data. Each multiplexer received data from each section of the source data register or registers. Special codes in the sections of the second source data register may select 0 fill, 1 fill or sign extension from the next most significant section for each multiplexer.

Owner:TEXAS INSTR INC

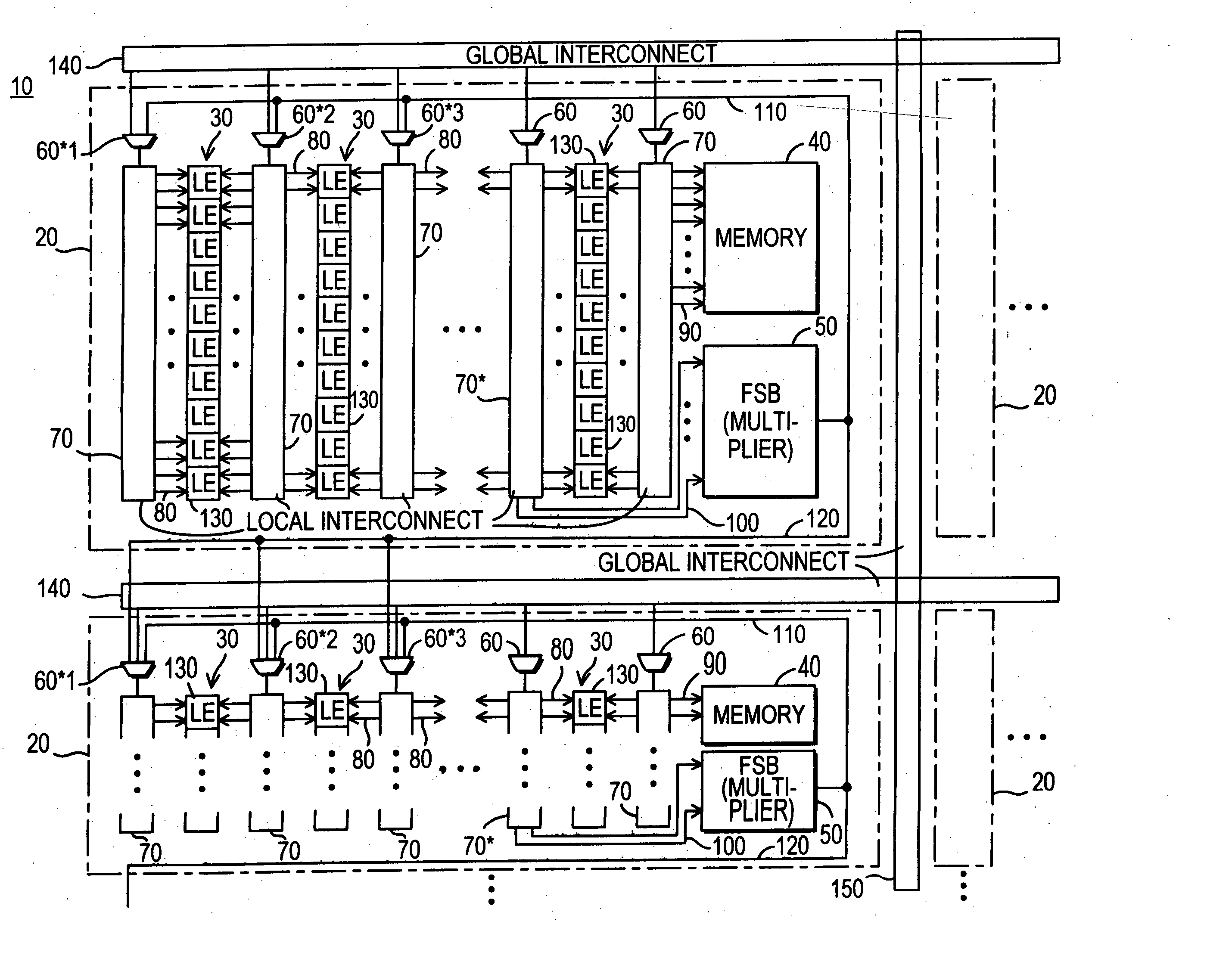

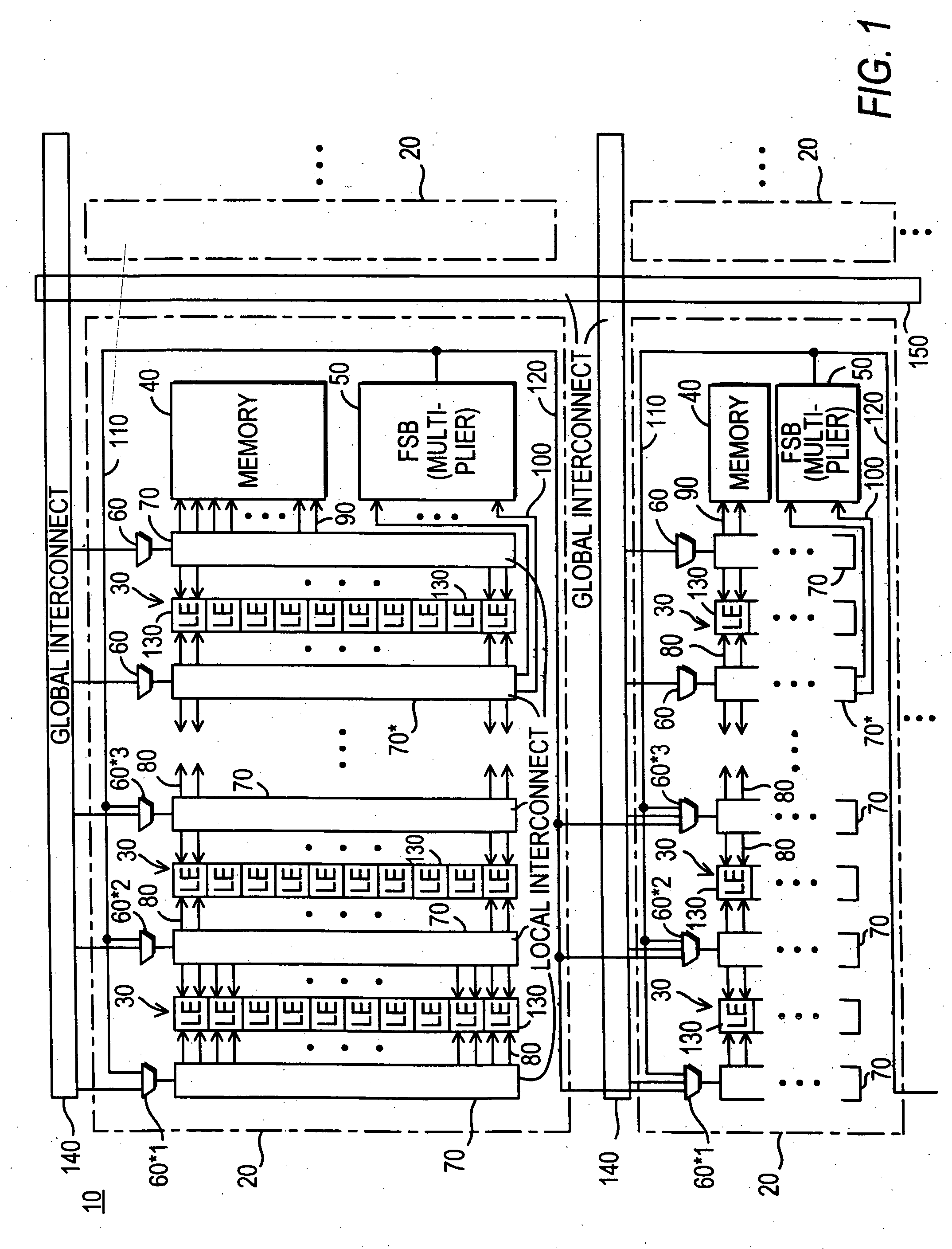

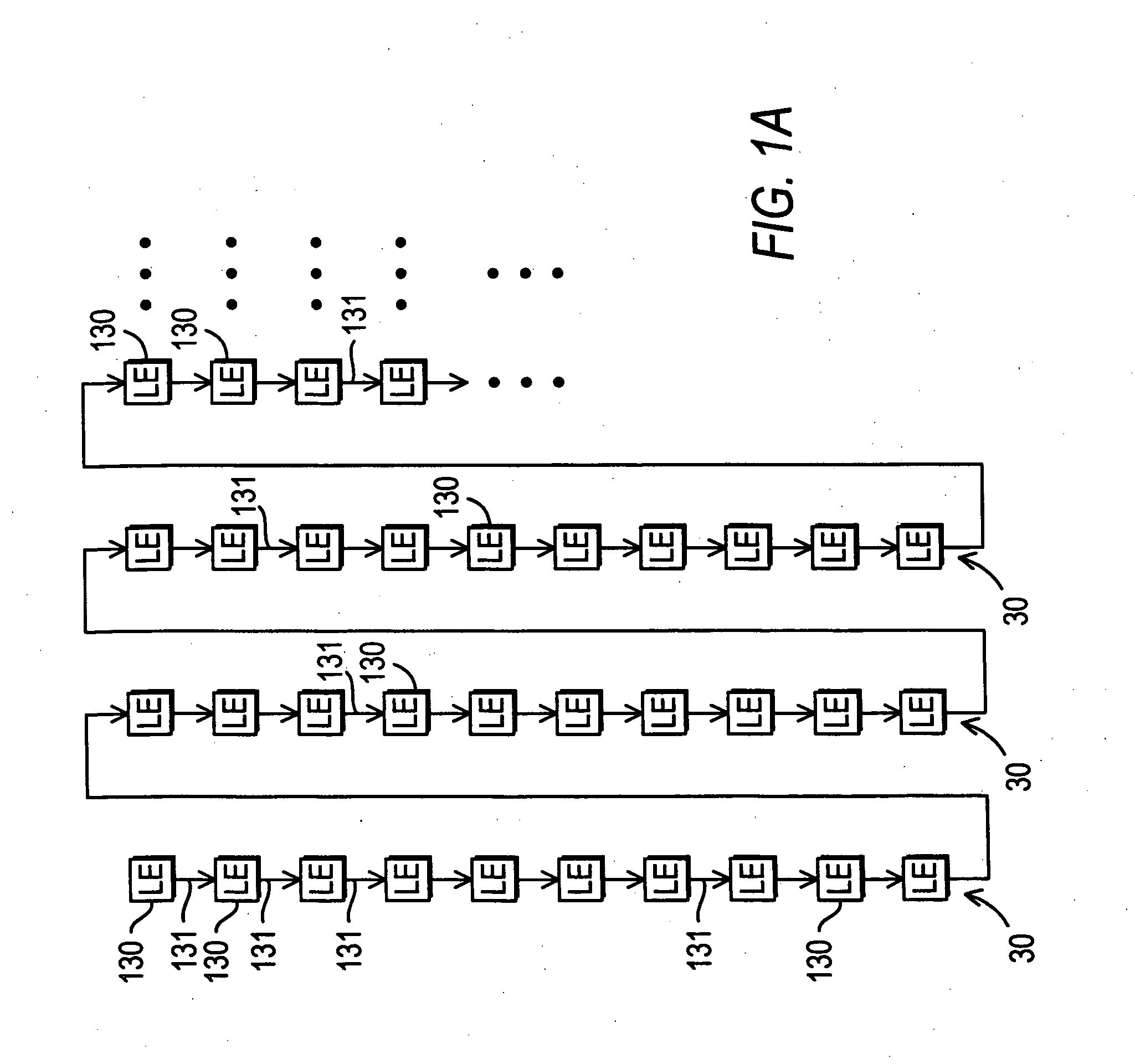

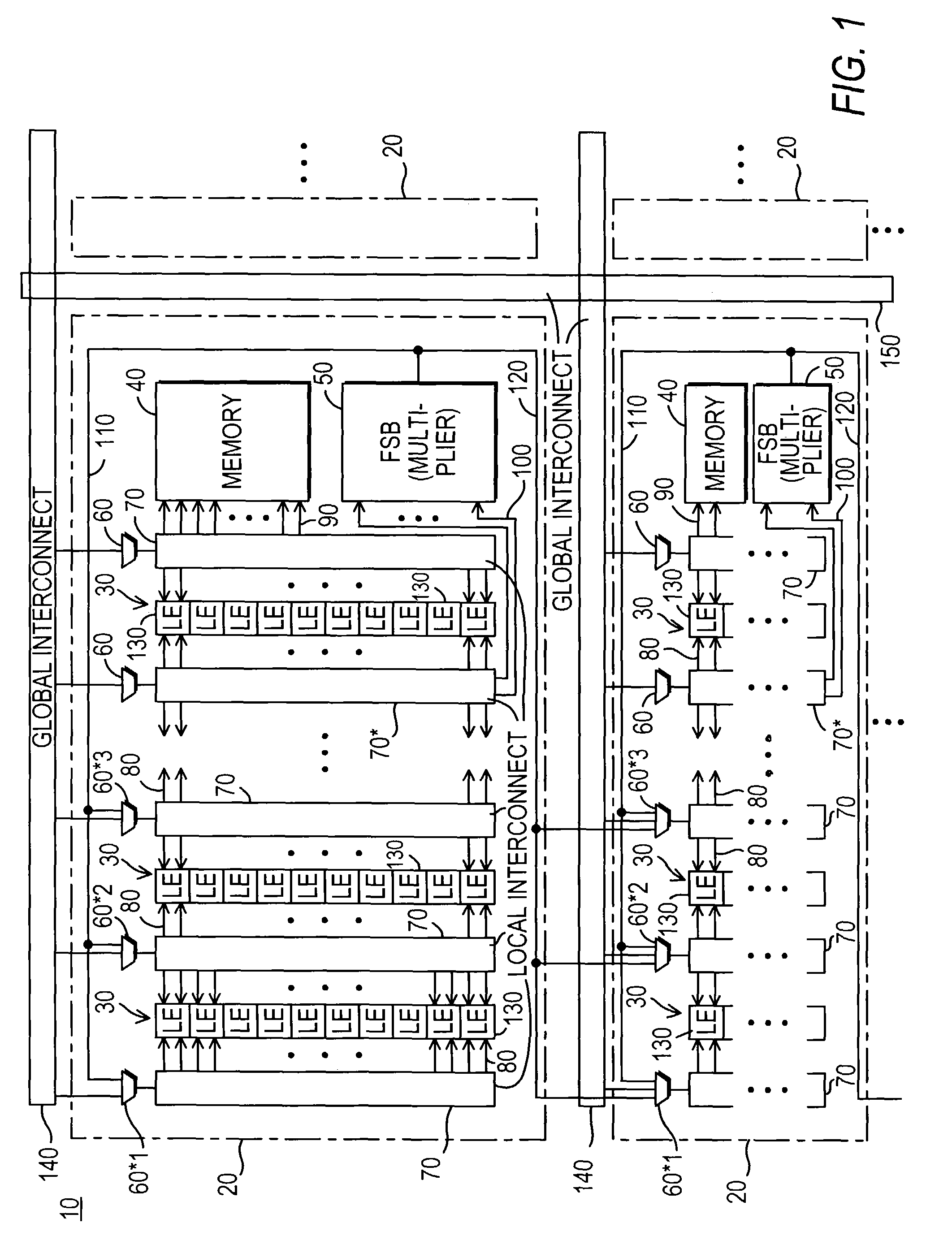

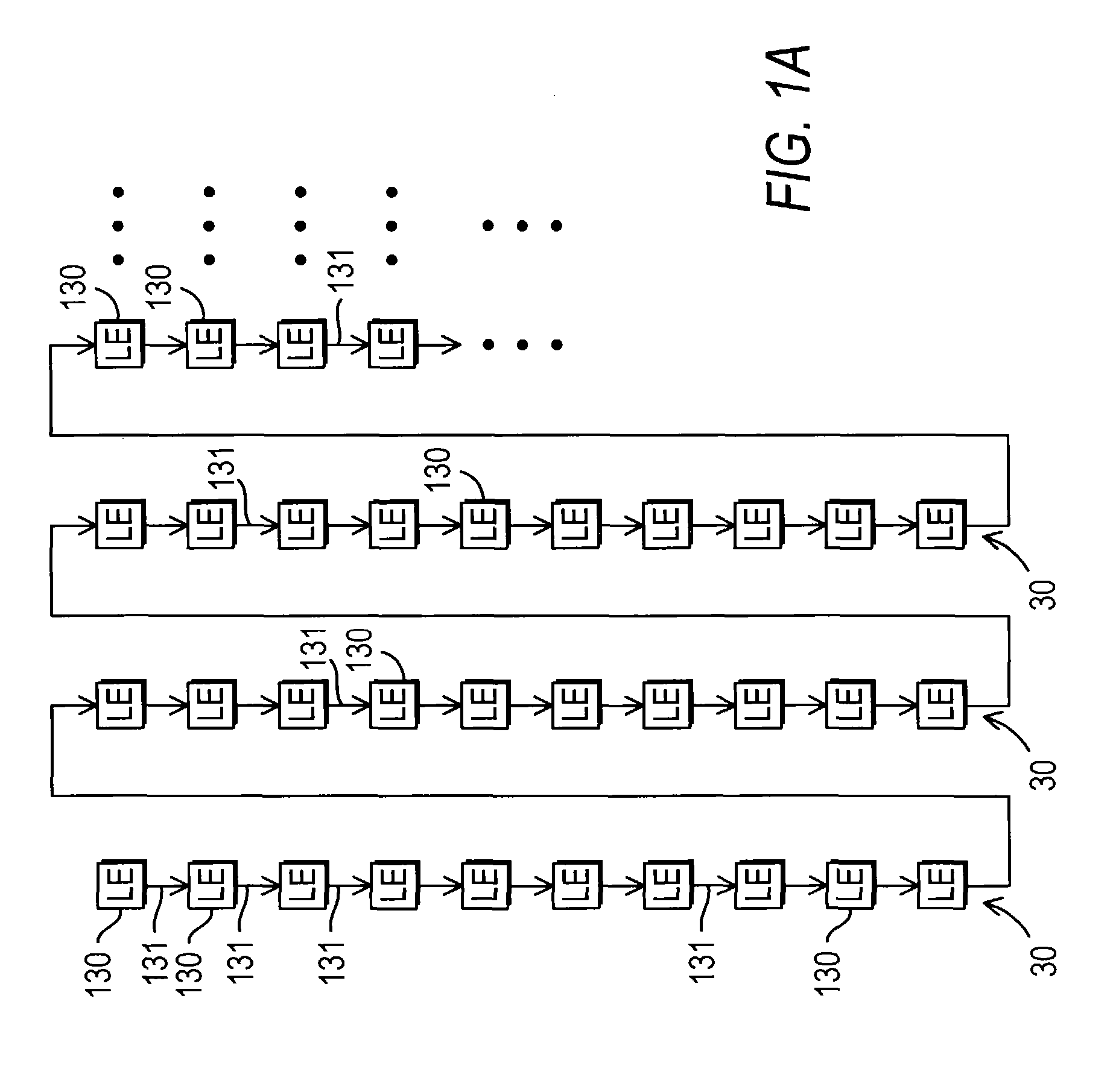

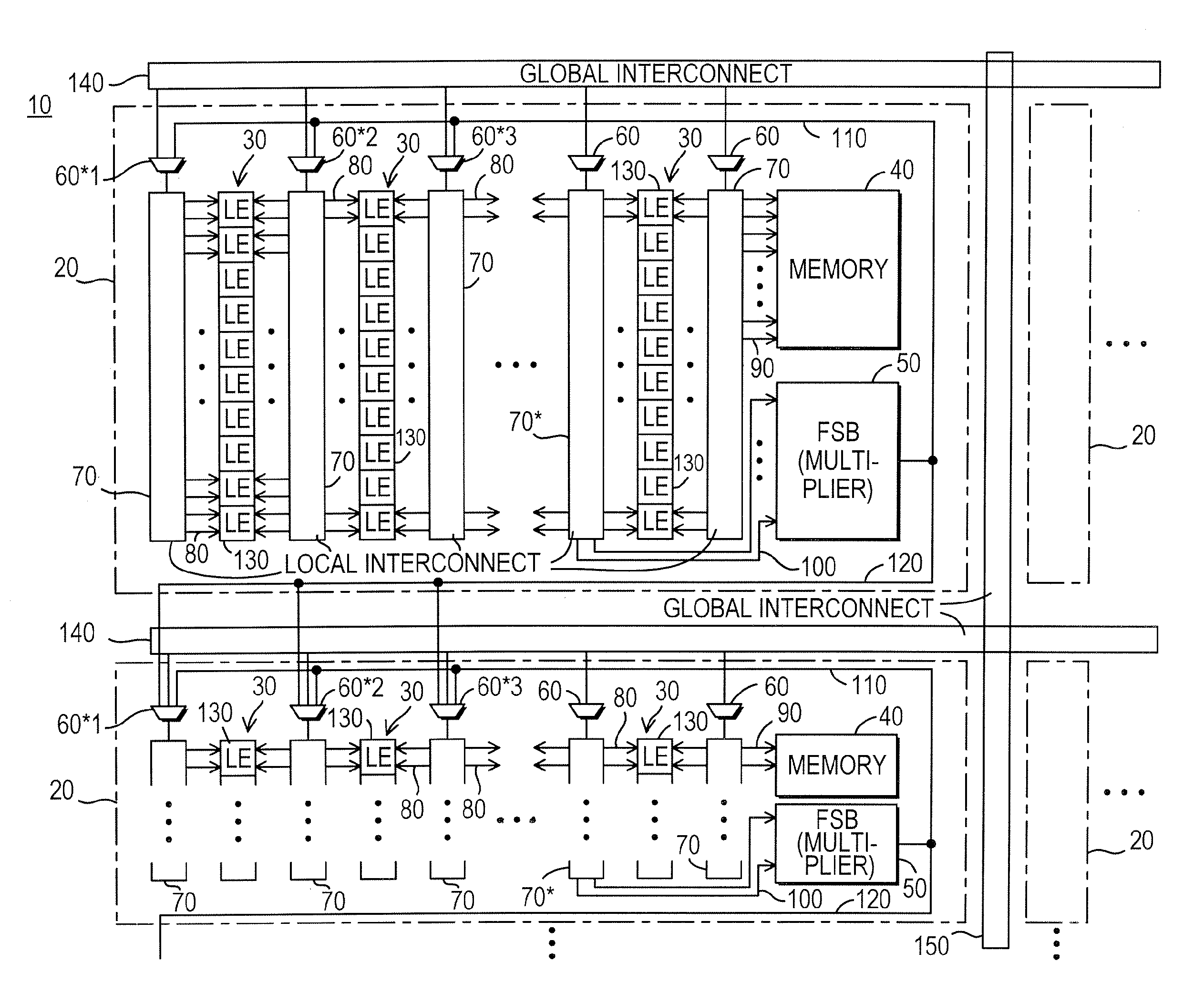

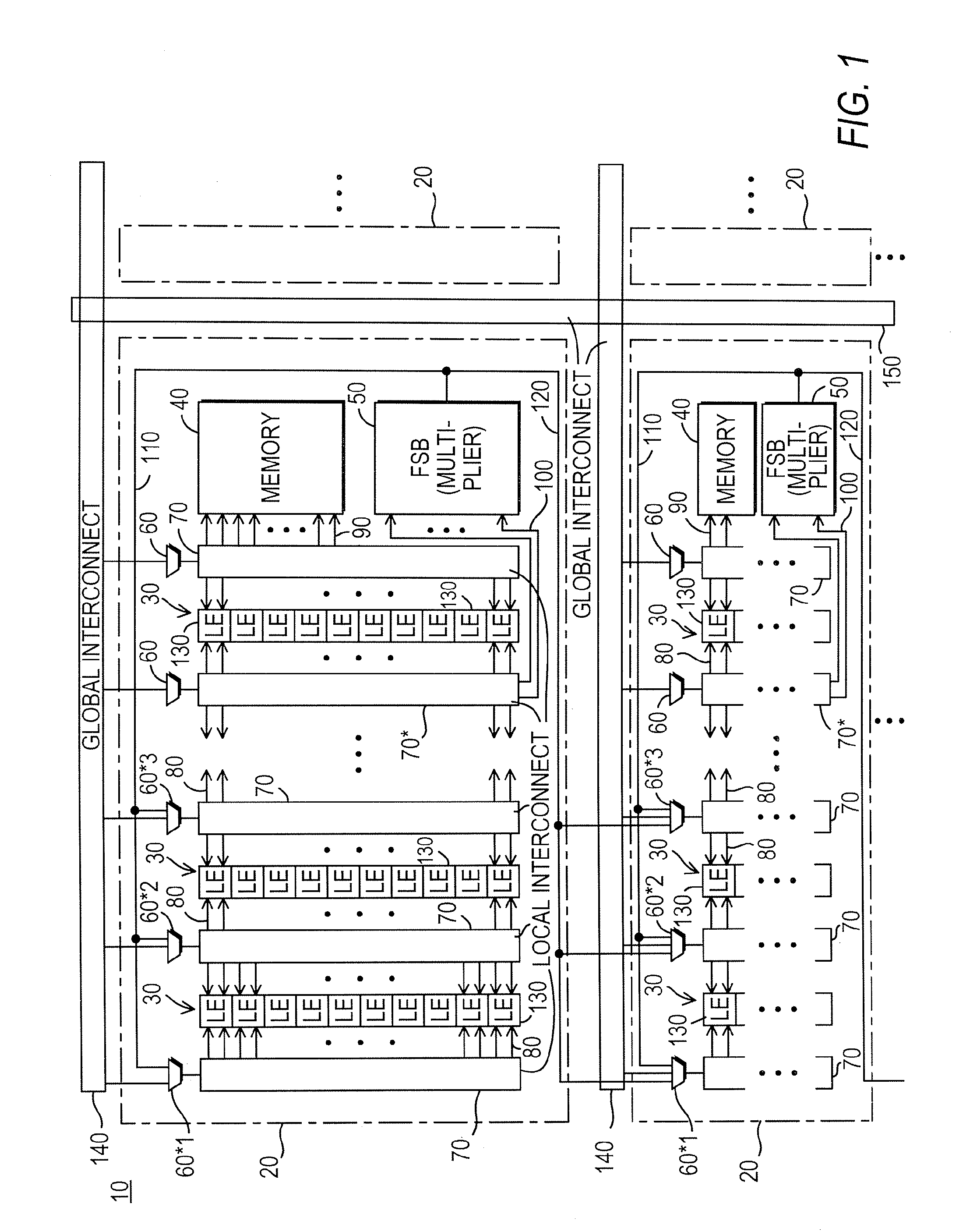

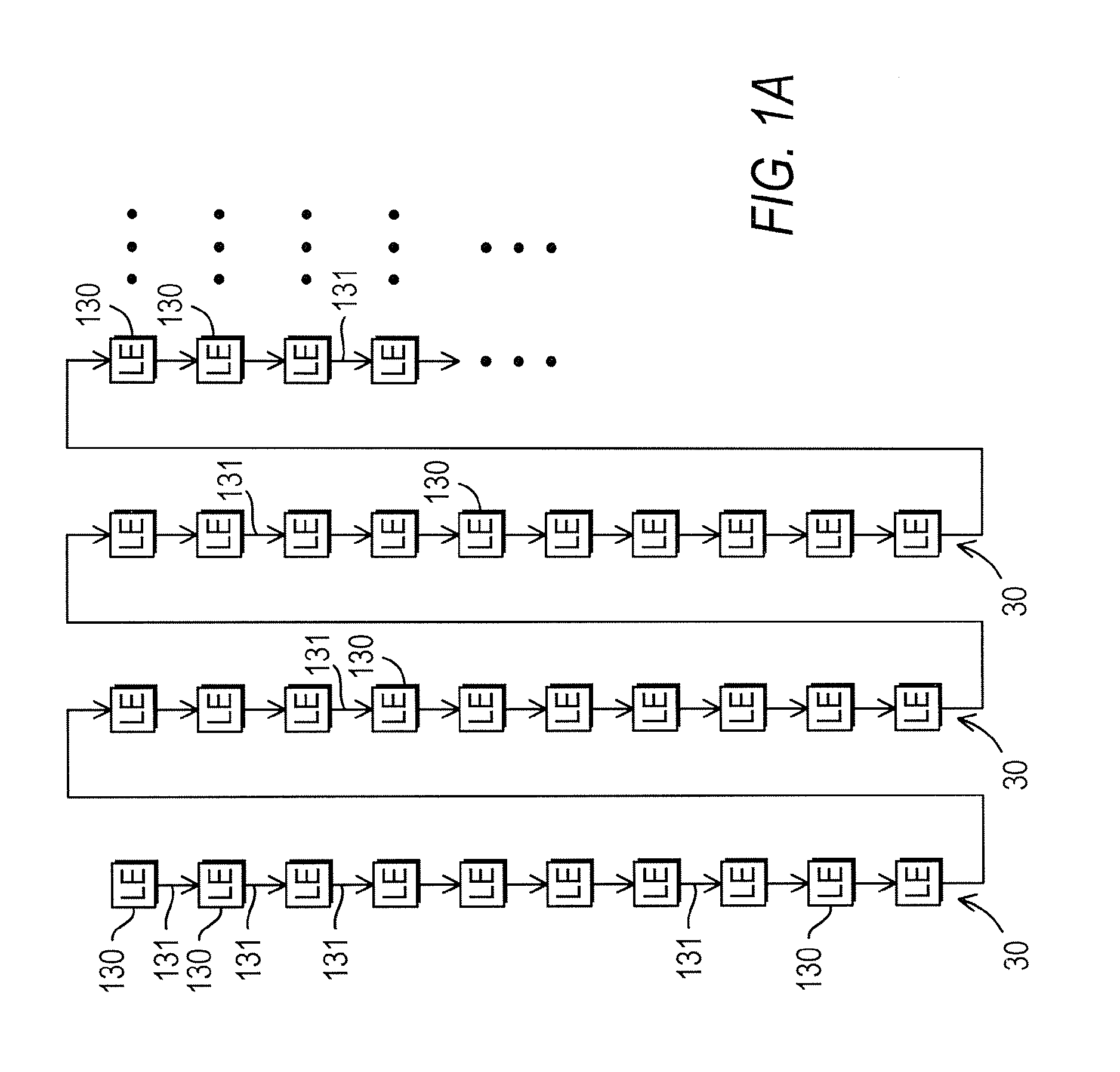

Programmable logic devices with function-specific blocks

InactiveUS20060218216A1Input reduce and evenReduce and even usabilityComputation using non-contact making devicesSemiconductor/solid-state device manufacturingGeneral purposeElectricity

Owner:LANGHAMMER MARTIN +1

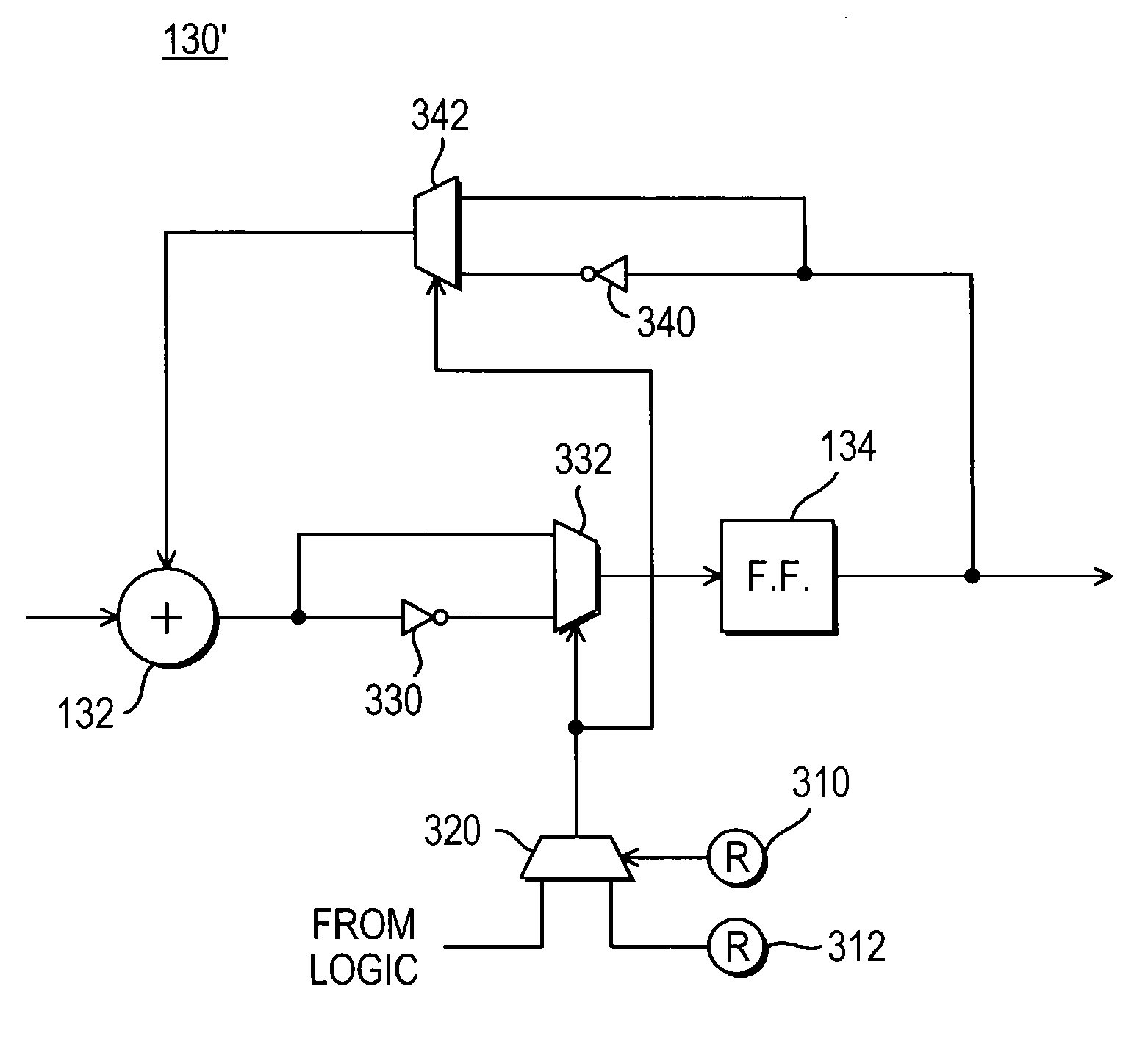

Circuitry for arithmetically accumulating a succession of arithmetic values

InactiveUS7024446B2Reduce the impactInput reduce and evenComputation using non-contact making devicesSemiconductor/solid-state device manufacturingGeneral purposeElectricity

A programmable logic integrated circuit device has at least one function-specific circuit block (e.g., a parallel multiplier, a parallel barrel shifter, a parallel arithmetic logic unit, etc.) in addition to the usual multiple regions of programmable logic and the usual programmable interconnection circuit resources. To reduce the impact of use of the function-specific block (“FSB”) on the general purpose interconnection resources of the device, inputs and / or outputs of the FSB may be coupled relatively directly to a subset of the logic regions. In addition to conserving general purpose interconnect, resources of the logic regions to which the FSB are connected can be used by the FSB to reduce the amount of circuitry that must be dedicated to the FSB. If the FSB is a multiplier, additional features include facilitating accumulation of successive multiplier outputs (using either addition or subtraction and with sign extension if desired) and / or arithmetically combining the outputs of multiple multipliers.

Owner:ALTERA CORP

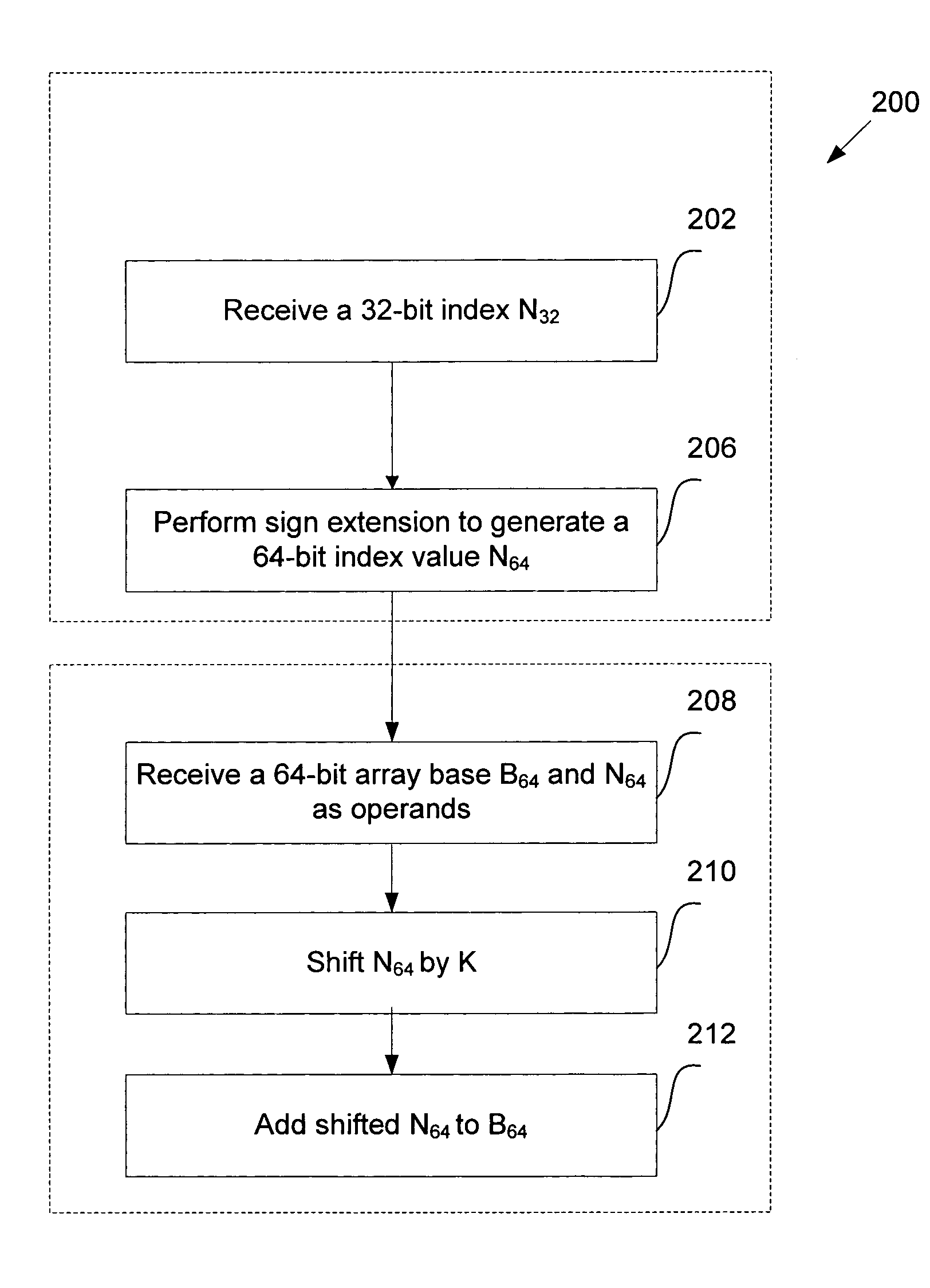

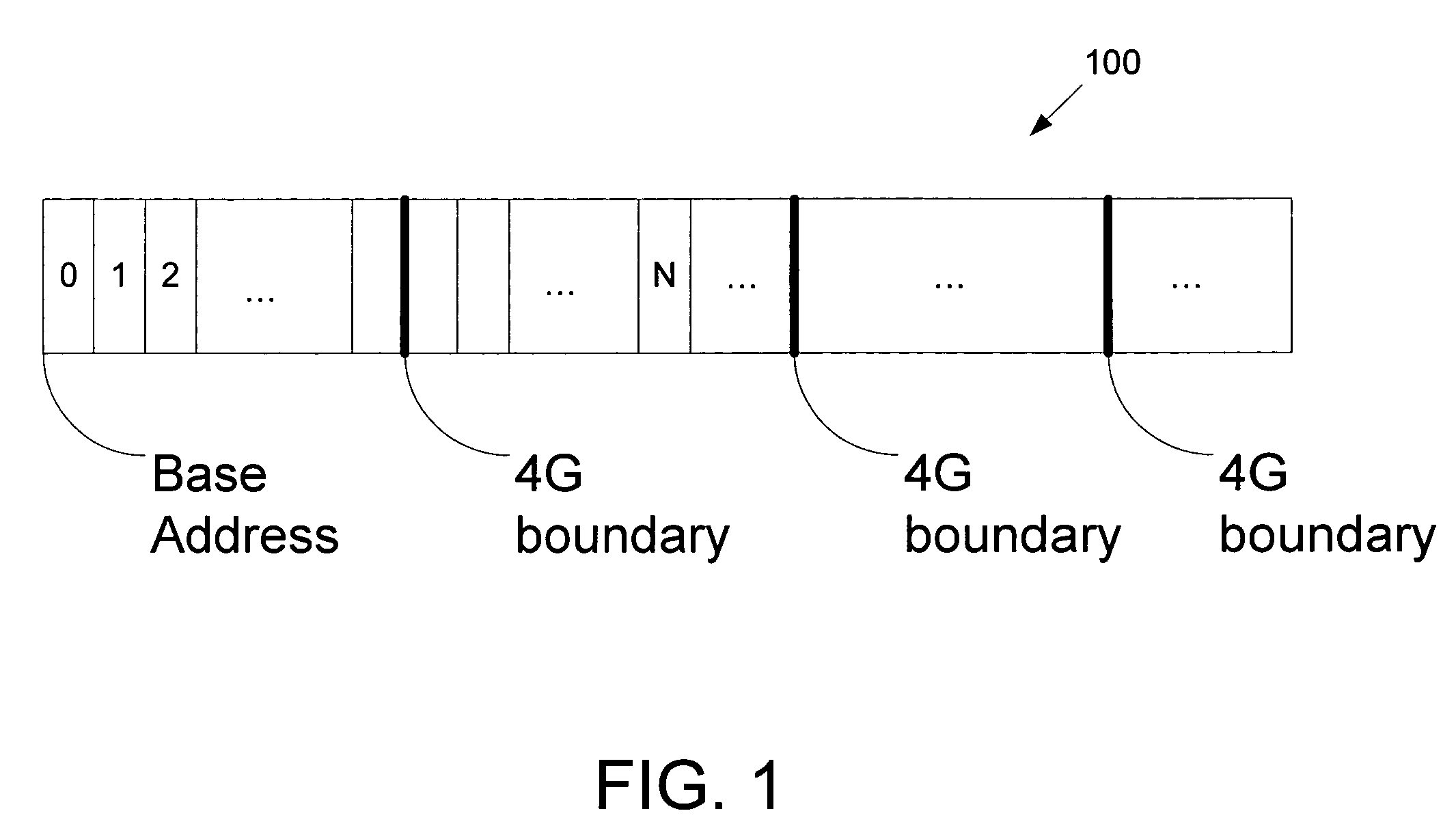

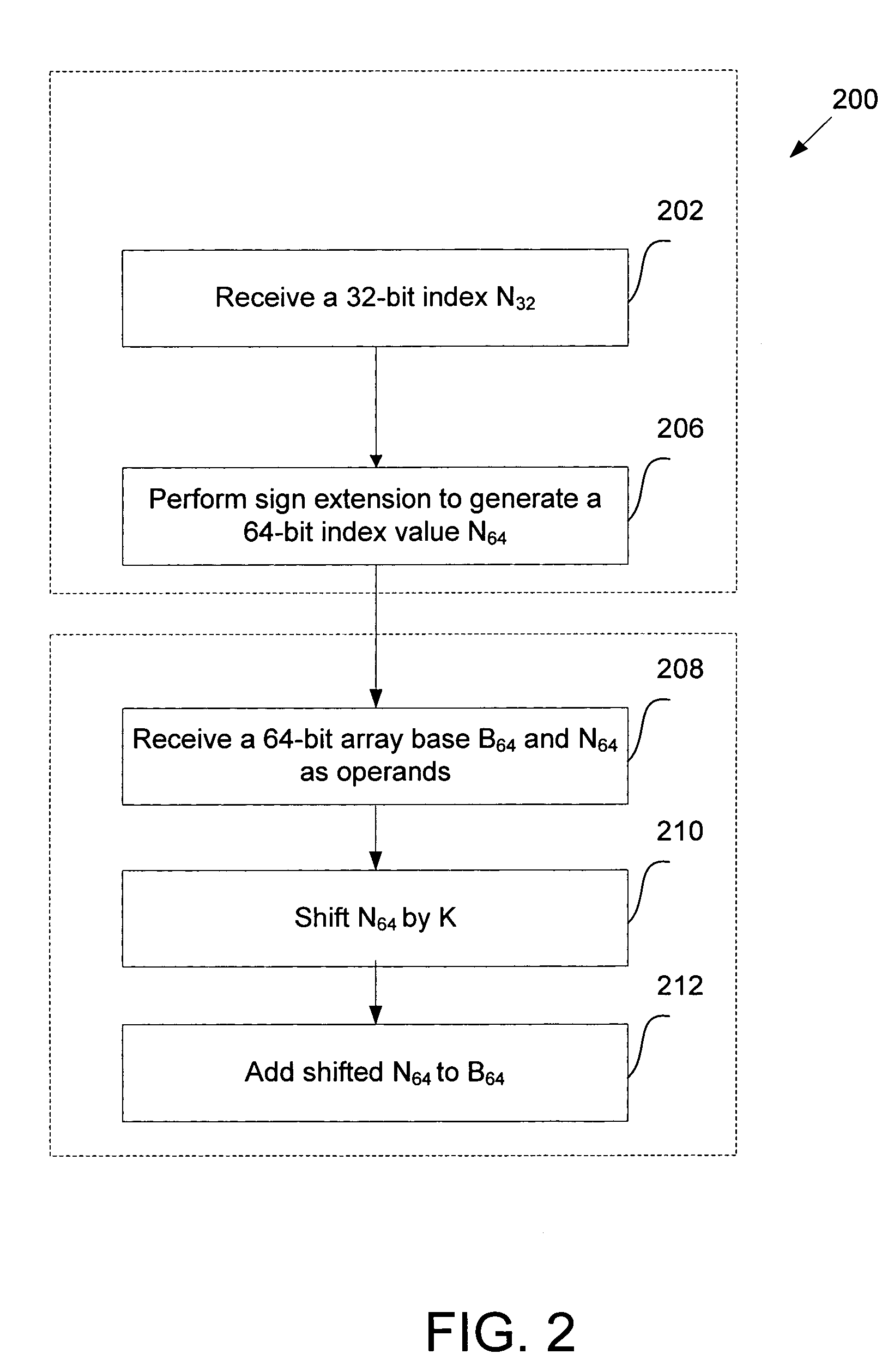

Memory addressing

Addressing memory includes receiving a first operand to a memory addressing operator, receiving a second operand to the memory addressing operator, performing sign extension on the first operand to provide a sign-extended operand, shifting the sign-extended operand to provide a shifted, sign-extended operand, and adding the shifted, sign-extended operand to the second operand. The second operand has a different bit length than the first operand.

Owner:AZUL SYSTEMS

Register move instruction for section select of source operand

ActiveUS7376813B2Reduces and eliminates time lostSpeed rateGeneral purpose stored program computerLogic circuits using elementary logic circuit componentsProcessor registerMultiplexer

Owner:TEXAS INSTR INC

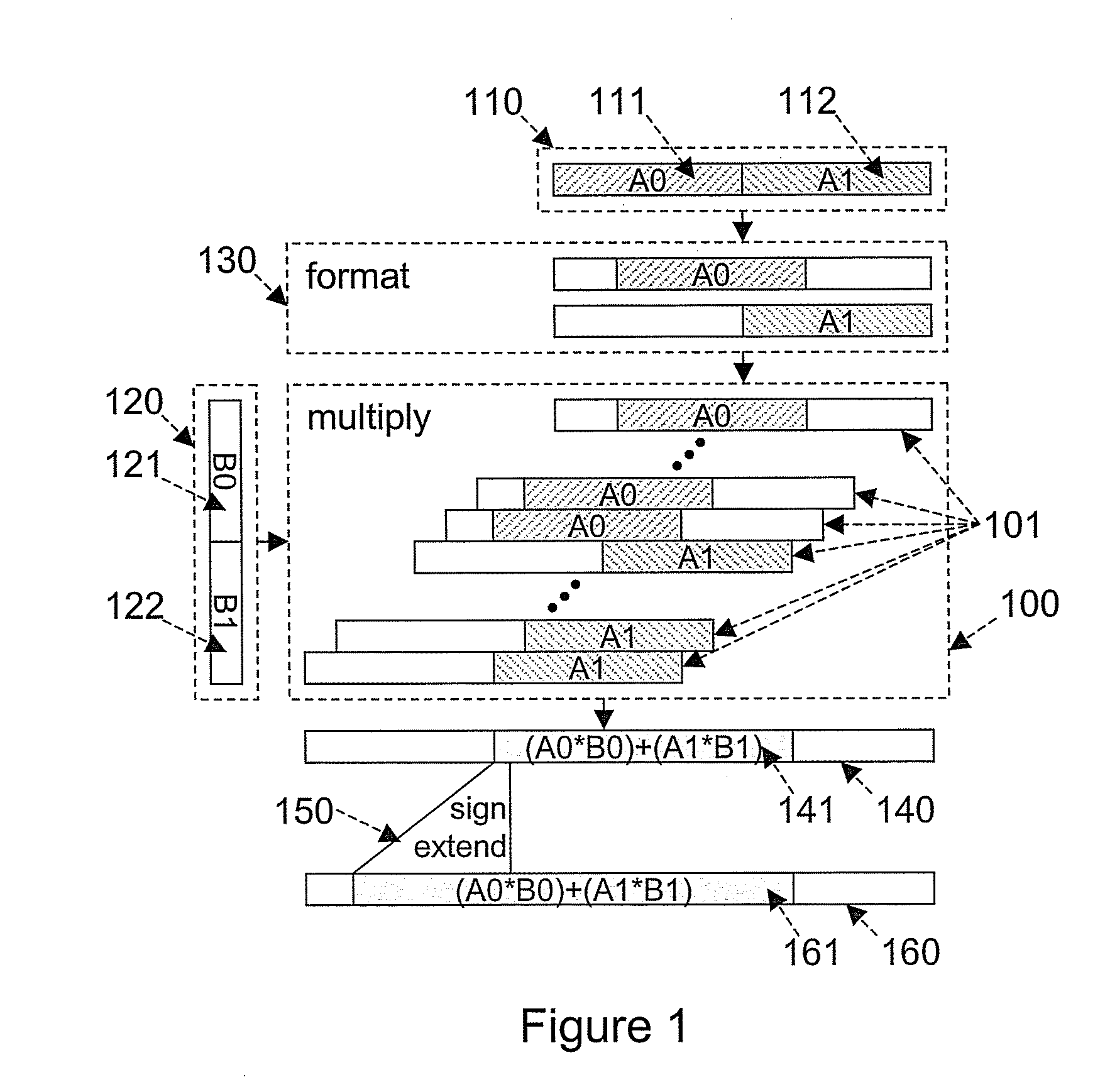

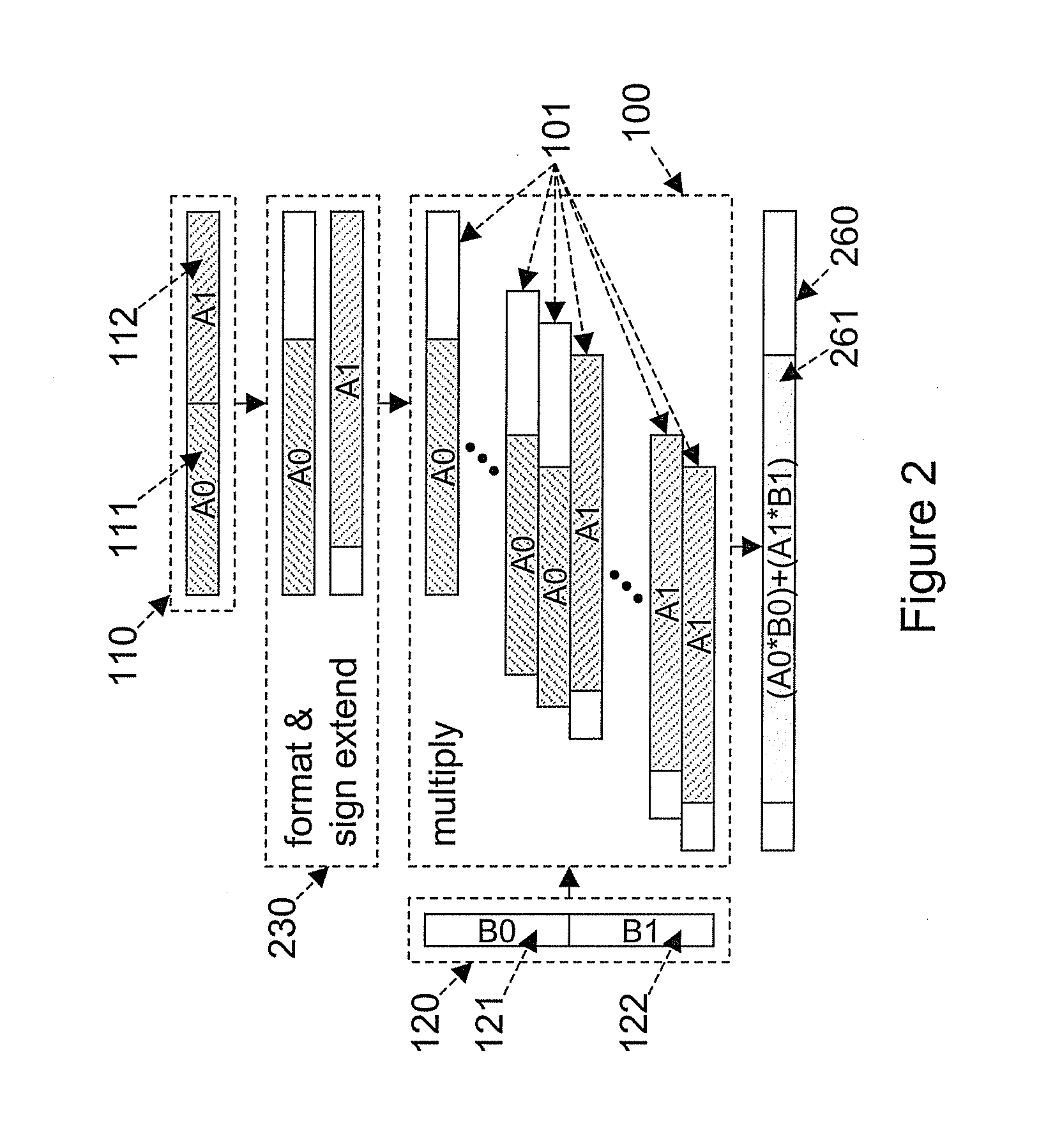

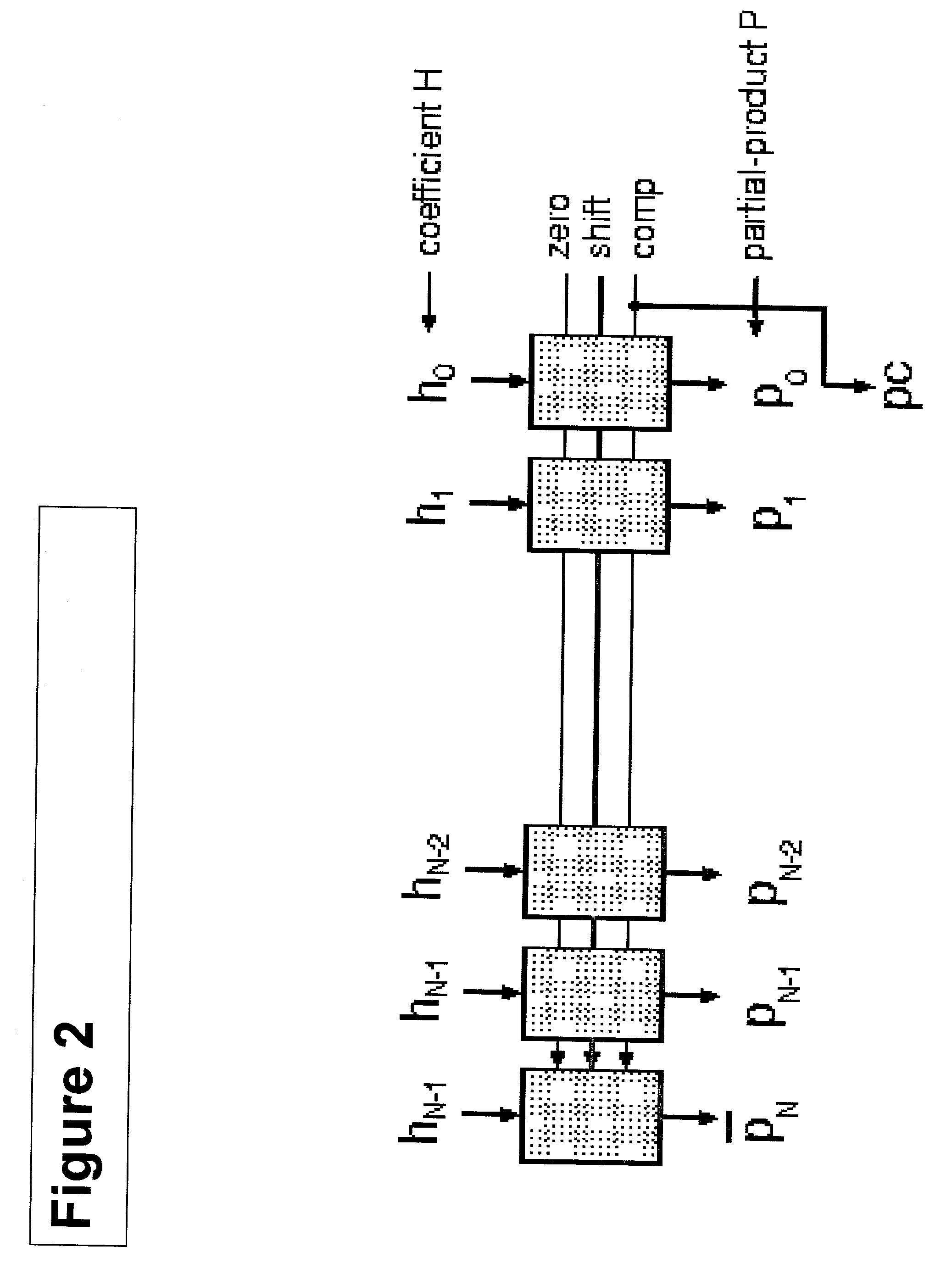

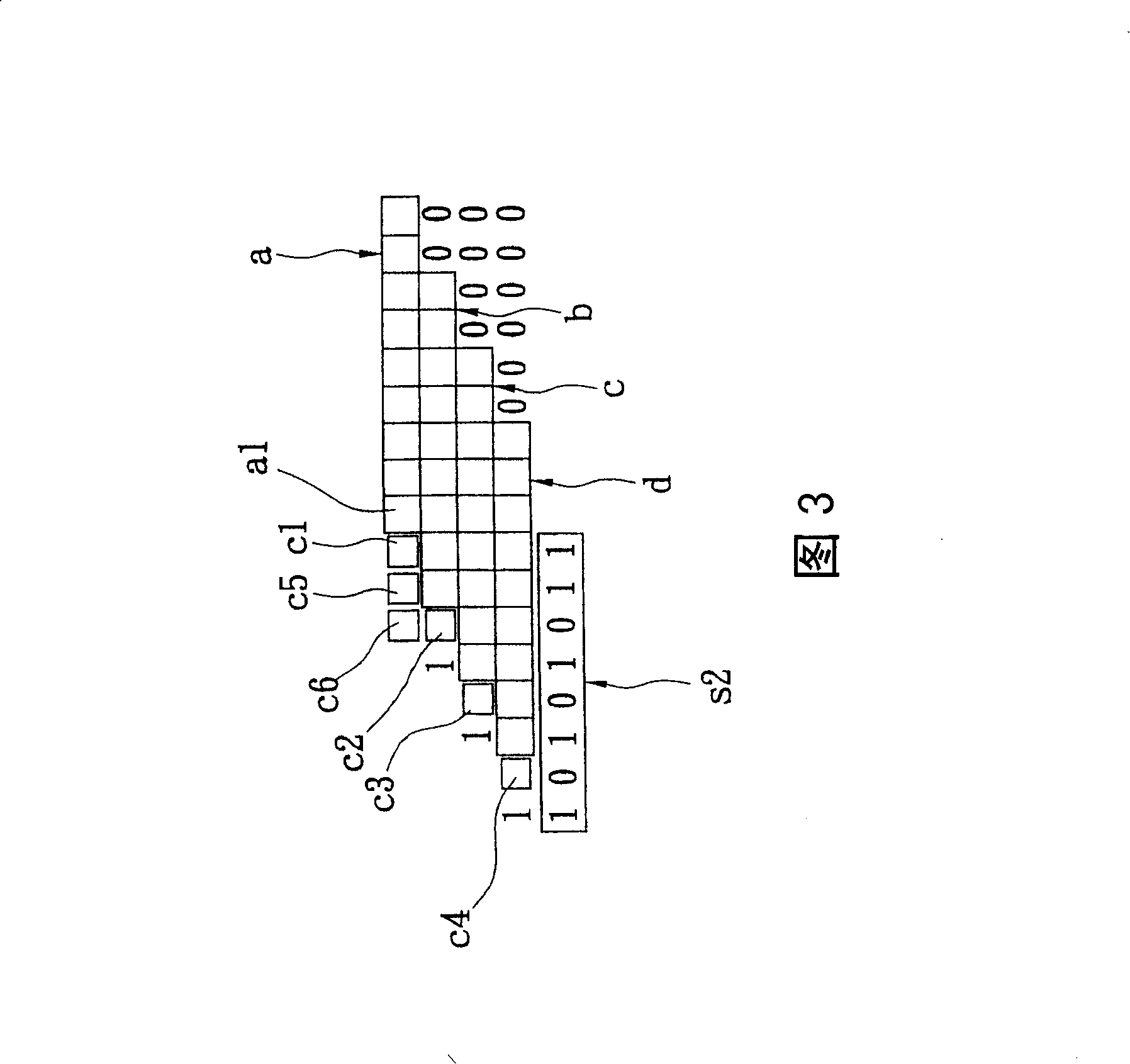

Method for sign-extension in a multi-precision multiplier

InactiveUS20090198758A1Computation using non-contact making devicesBinary multiplierPartial product reduction

A method for implementing sign extension within a multi-precision multiplier is described. The method includes receiving a first input within a multiplier core of the multiplier, receiving a second input within the multiplier core, and creating partial products in the multiplier core using the first and second inputs. The method also includes summing up the partial products in a partial product reduction tree in the multiplier core. The method also includes performing sign extension within the partial product reduction tree of the multiplier core by adding a value to a partial product of the partial product reduction tree. The method further includes computing an output from the partial product reduction tree, the output including a final product of the first and second inputs signed extended to a desired width.

Owner:IBM CORP

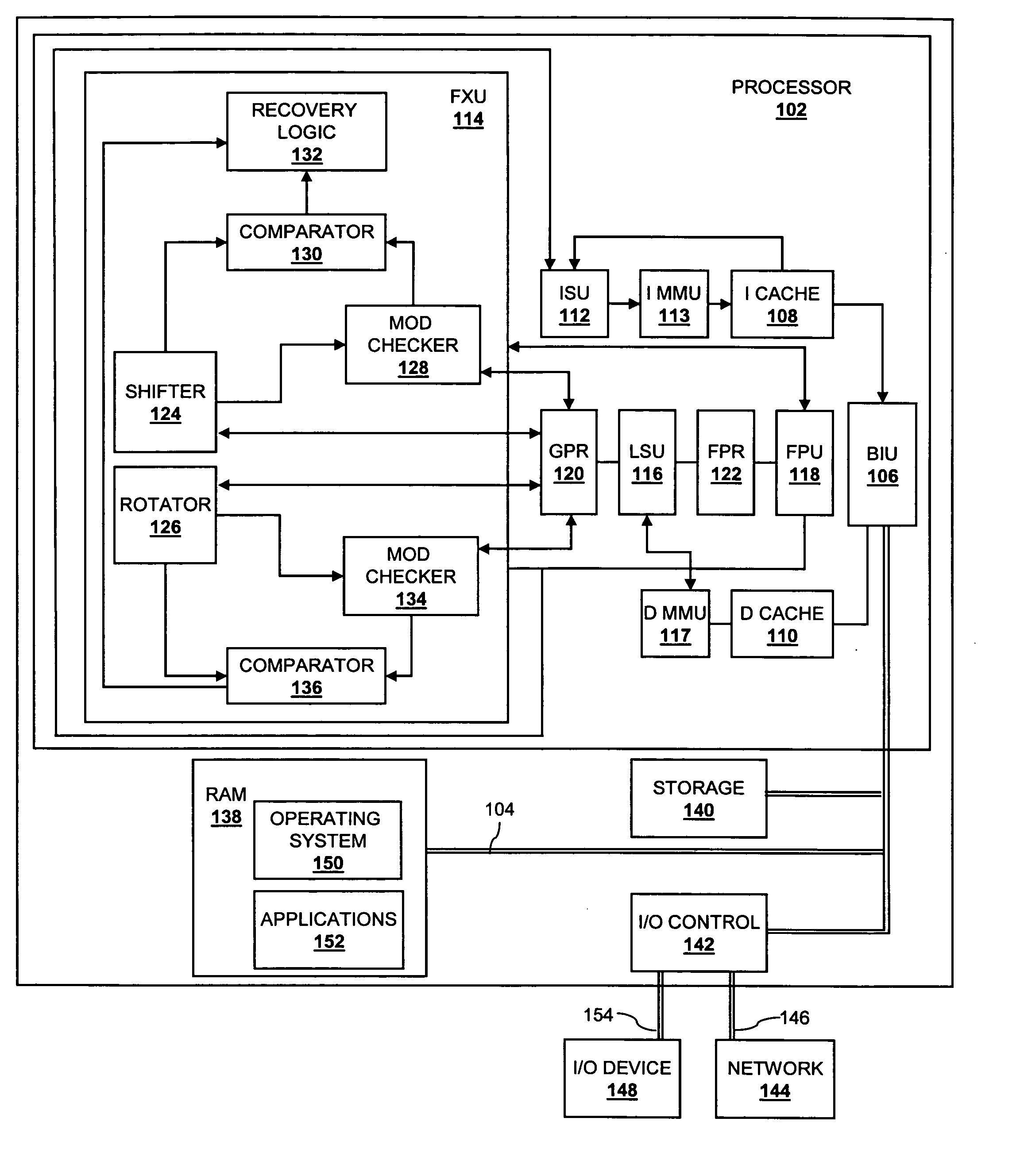

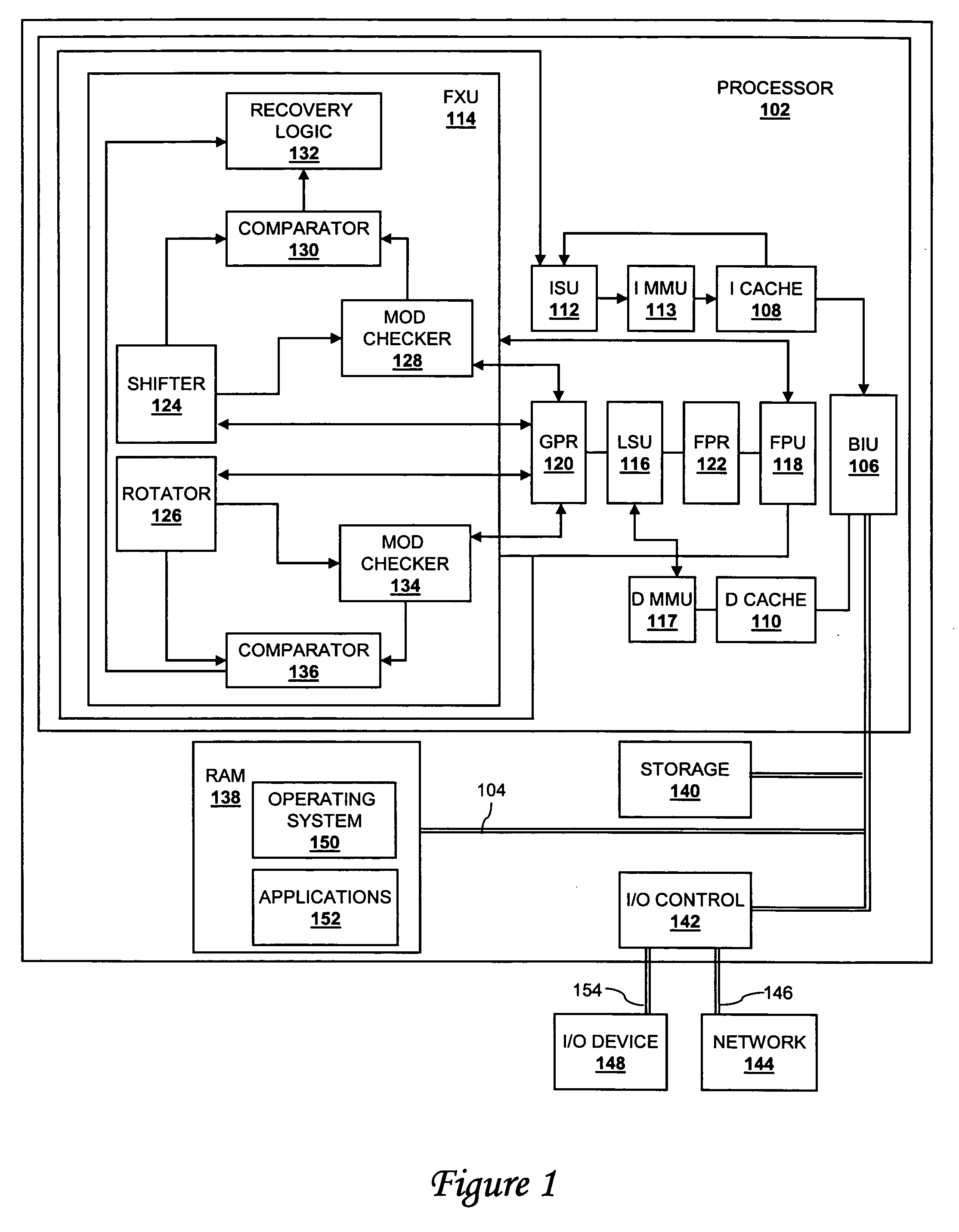

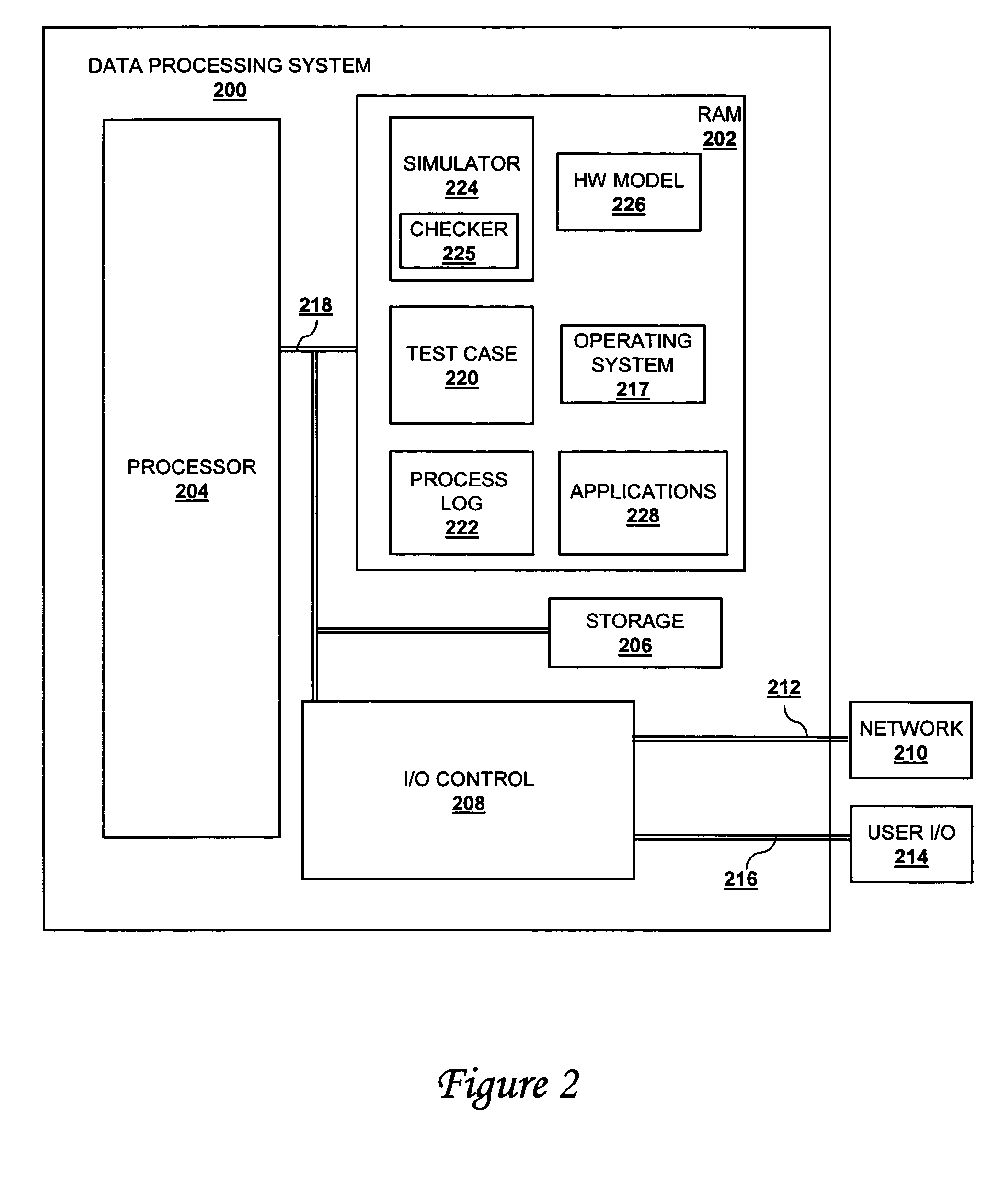

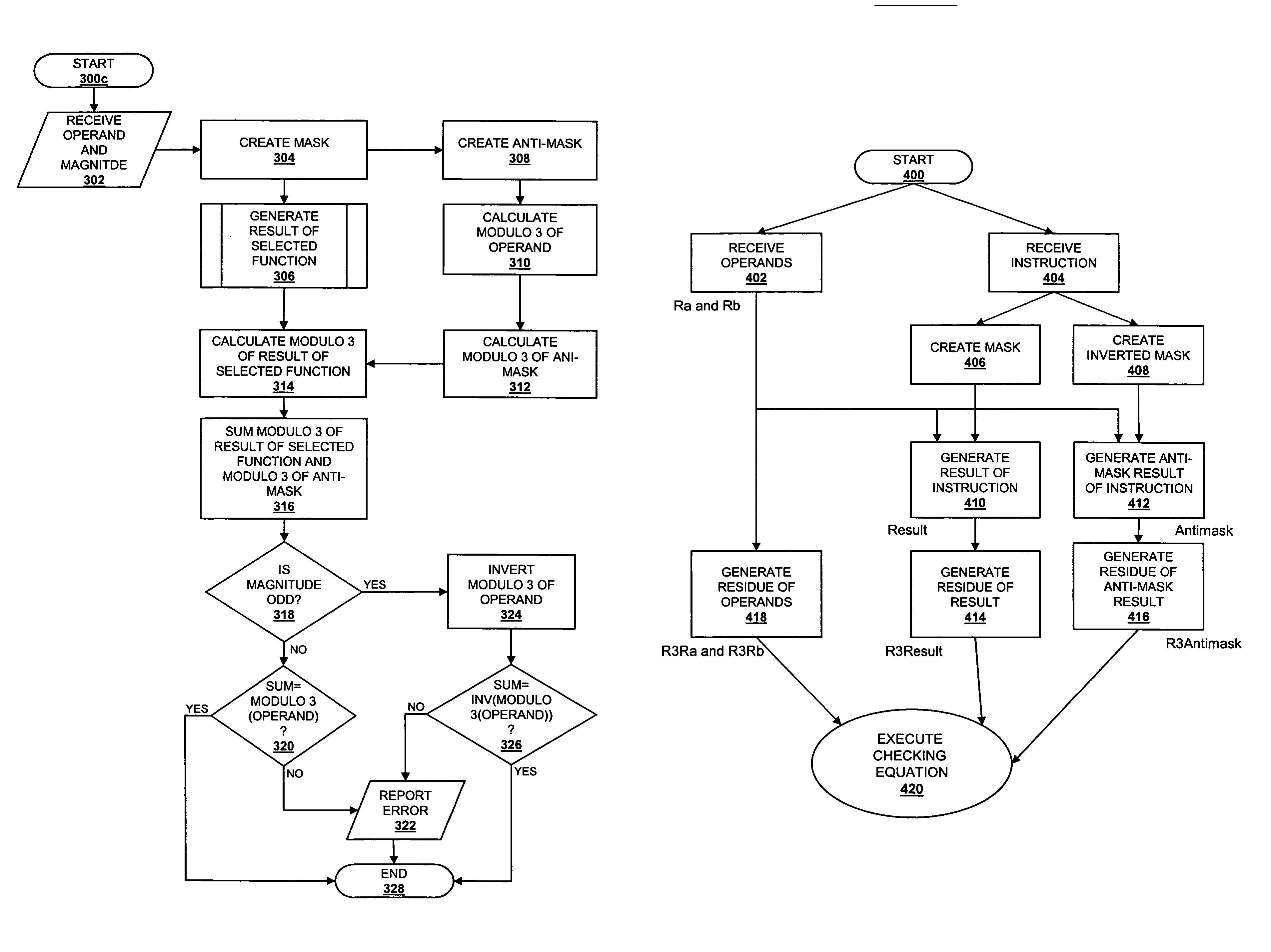

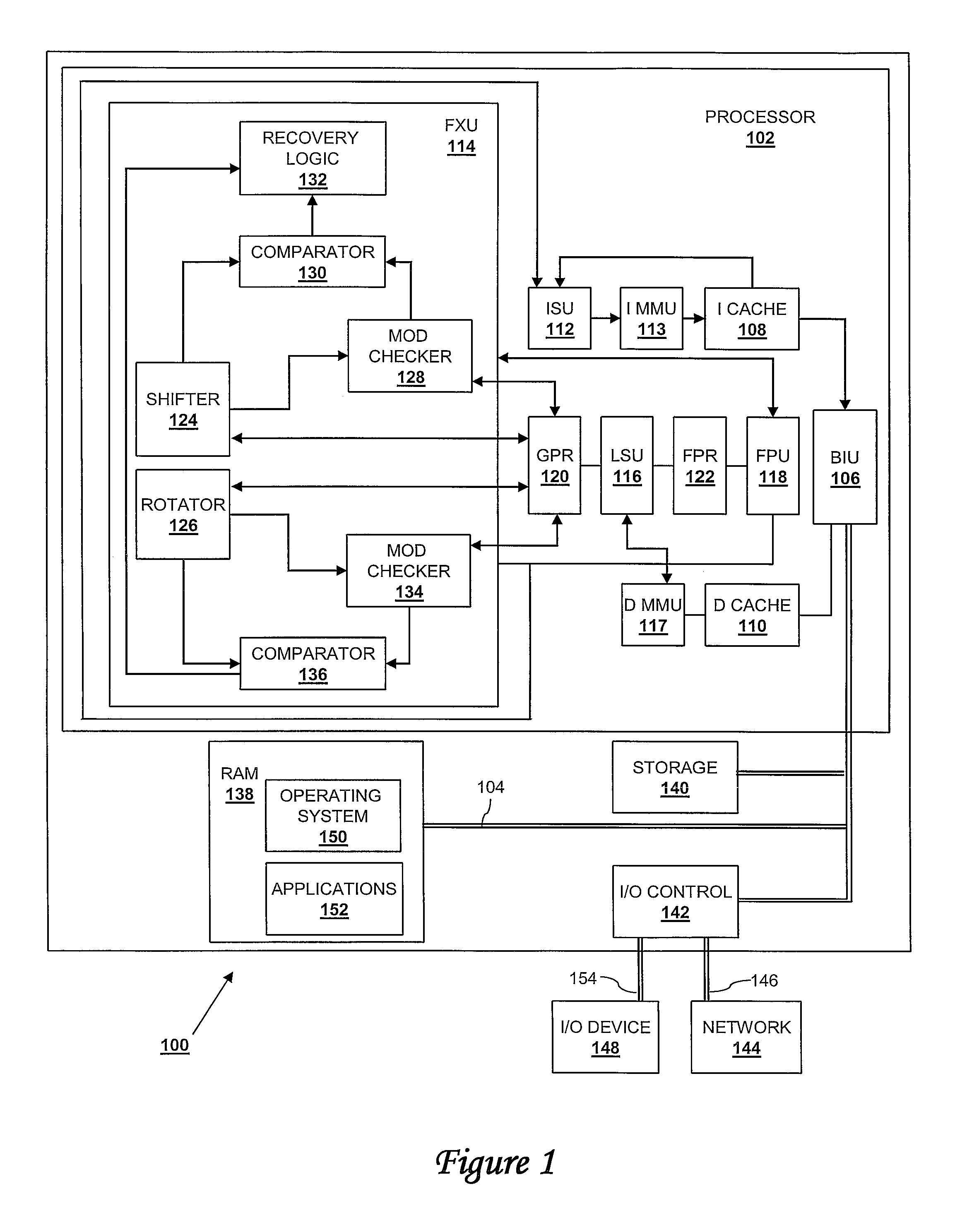

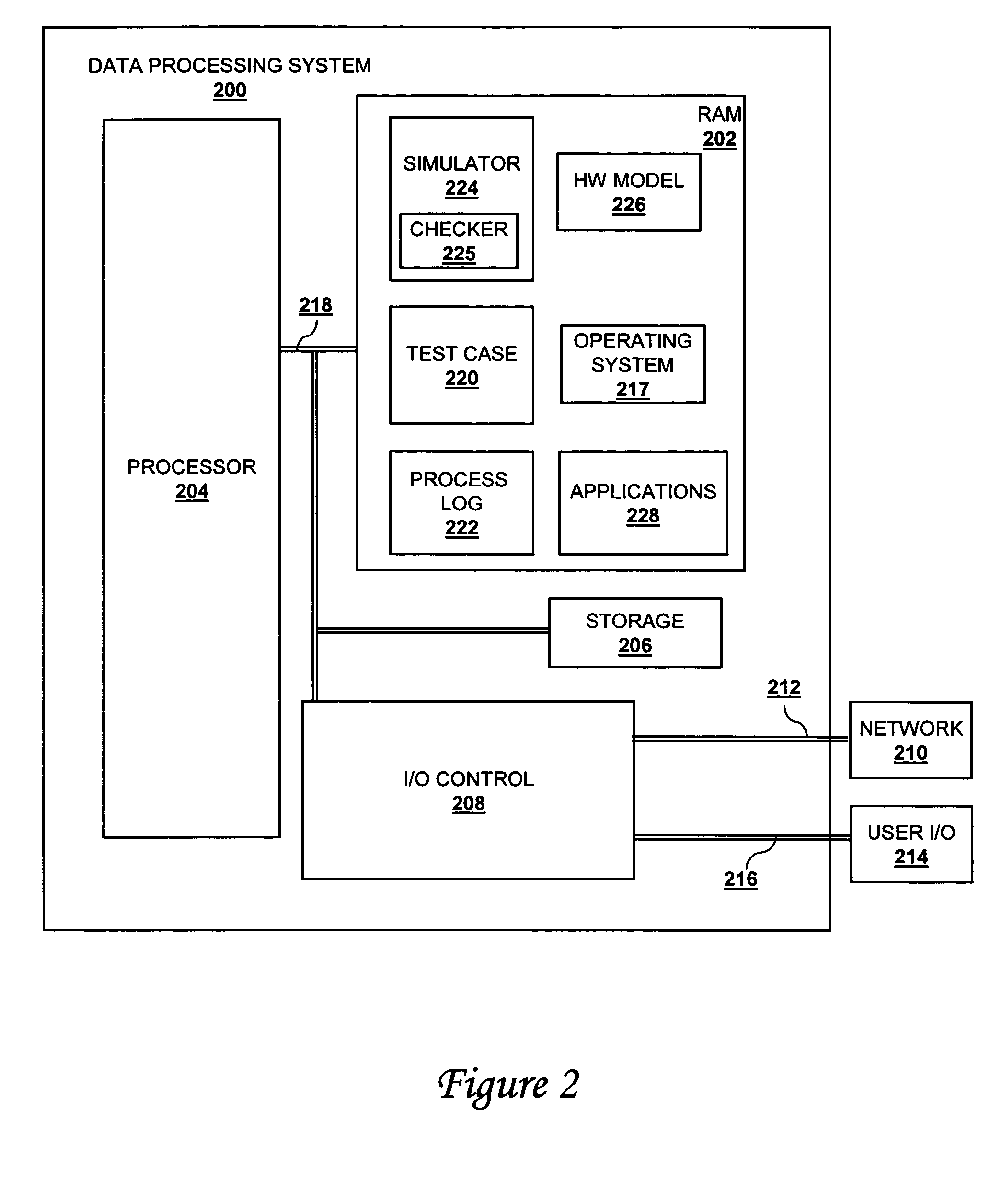

Method and system for checking rotate, shift and sign extension functions using a modulo function

InactiveUS20050278572A1Detecting faulty computer hardwareCode conversionComputer scienceSign extension

A method of discovering a fault in a circuit is disclosed. The method comprises generating a first result of a selected function by performing the selected function on an operand, wherein the selected function employs a mask. Once the function is performed, an antimask of the mask is created, and the modulo of the antimask is calculated. A modulo function of the first result of the selected function is calculated to obtain a third result. A modulo of the operand is then calculated to obtain a fourth result, and a second function is then performed on the second result and the third result to obtain a fifth result. In response to comparing the fifth result to the fourth result, a signal is propagated to indicate a fault in the circuit.

Owner:IBM CORP

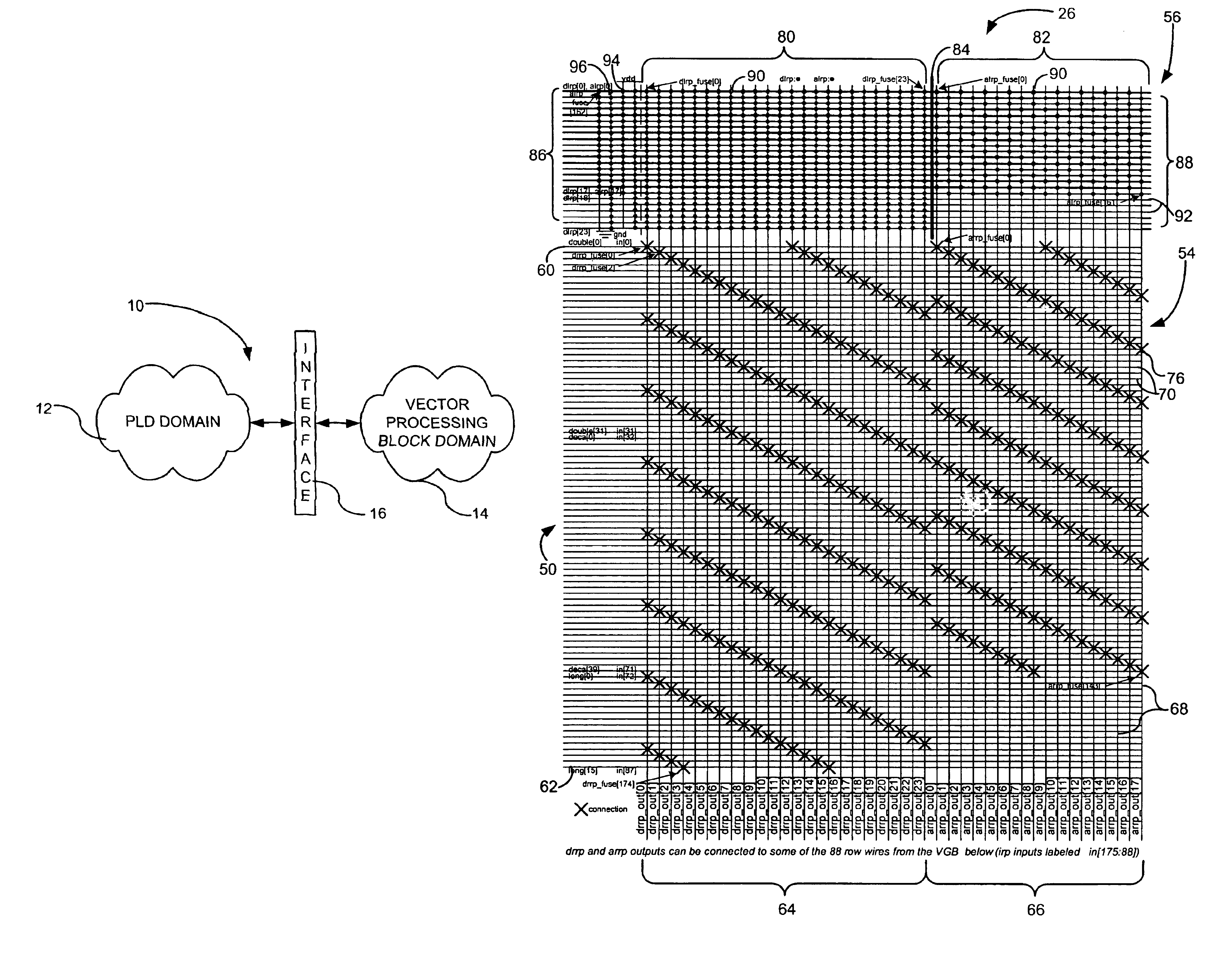

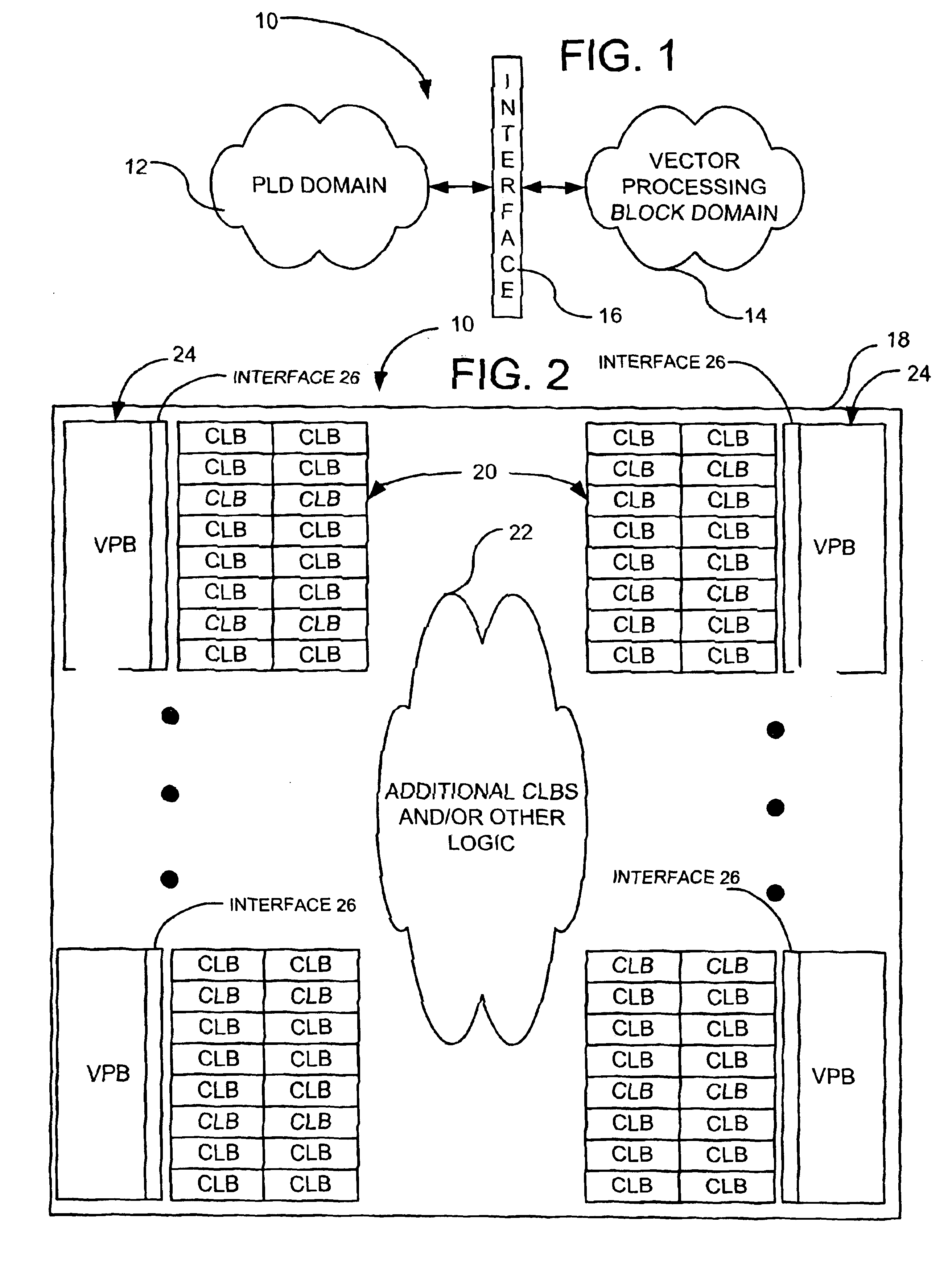

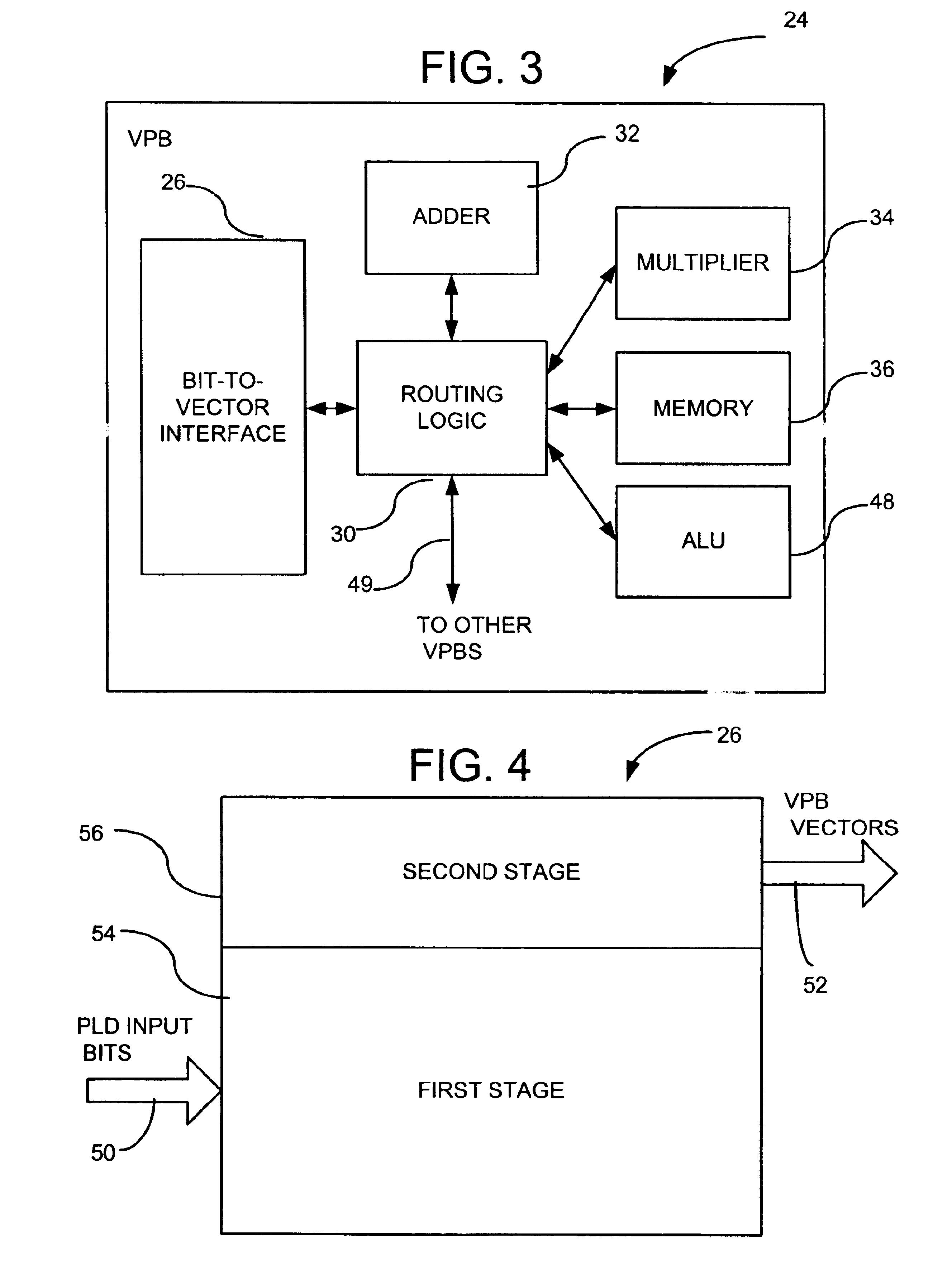

Converting bits to vectors in a programmable logic device

InactiveUS6844757B2Abundant resourcesResource can be very expensiveSolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic device16-bit

A circuit is disclosed for a programmable logic device (PLD) environment that converts unordered bits in a PLD domain to fixed-width vectors in a vector domain. The fixed-width vectors may be used within a vector processing block (VPB) that operates on data in vector format. The PLD includes multiple programmable logic blocks that are configurable by a user. The logic blocks operate on data at a bit level resulting in unordered bits of information in a PLD domain. However, a vector processing block operates on data on a vector level (e.g., 8 bits, 16 bits, 32 bits, 64 bits, etc.). Thus, an interface is coupled between the programmable logic blocks and the vector processing block that converts at least a portion of the unordered bits of information from the PLD domain to one or more fixed-width vectors for use in the vector processing block. The interface may also perform scaling and / or sign extension on the unordered bits, to further free up expensive resources in the PLD domain.

Owner:LATTICE SEMICON CORP

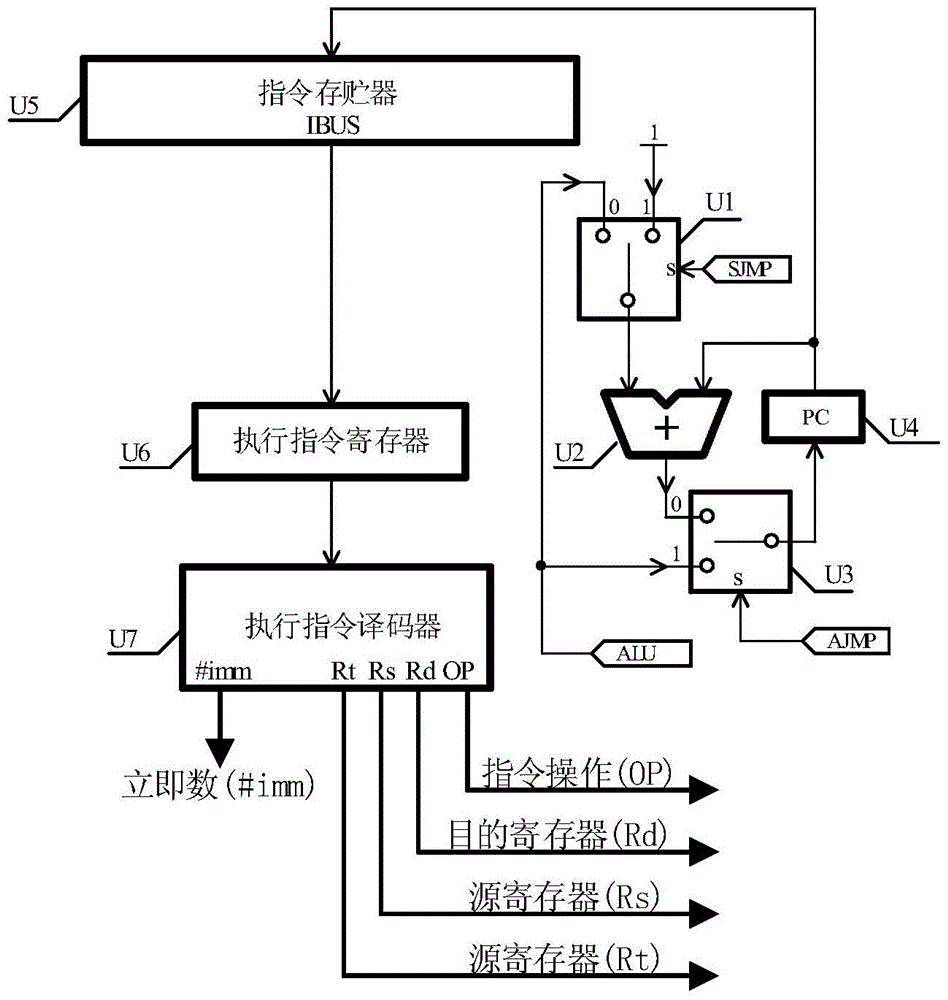

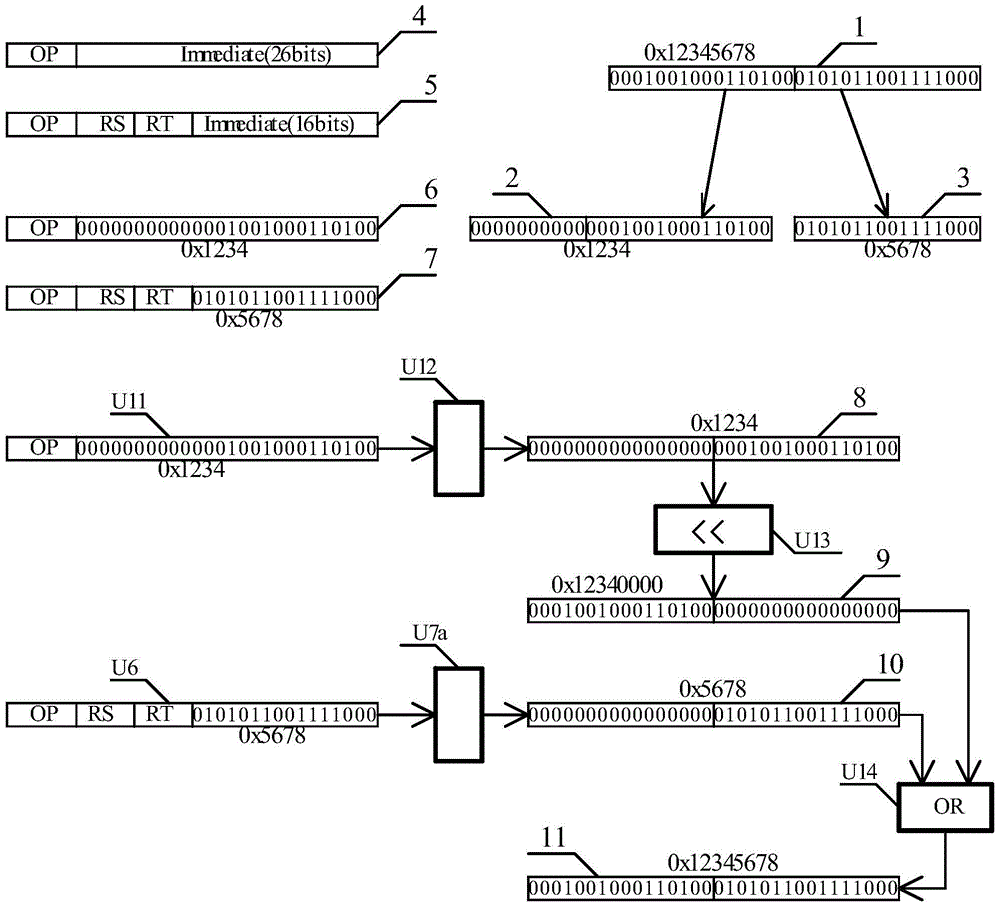

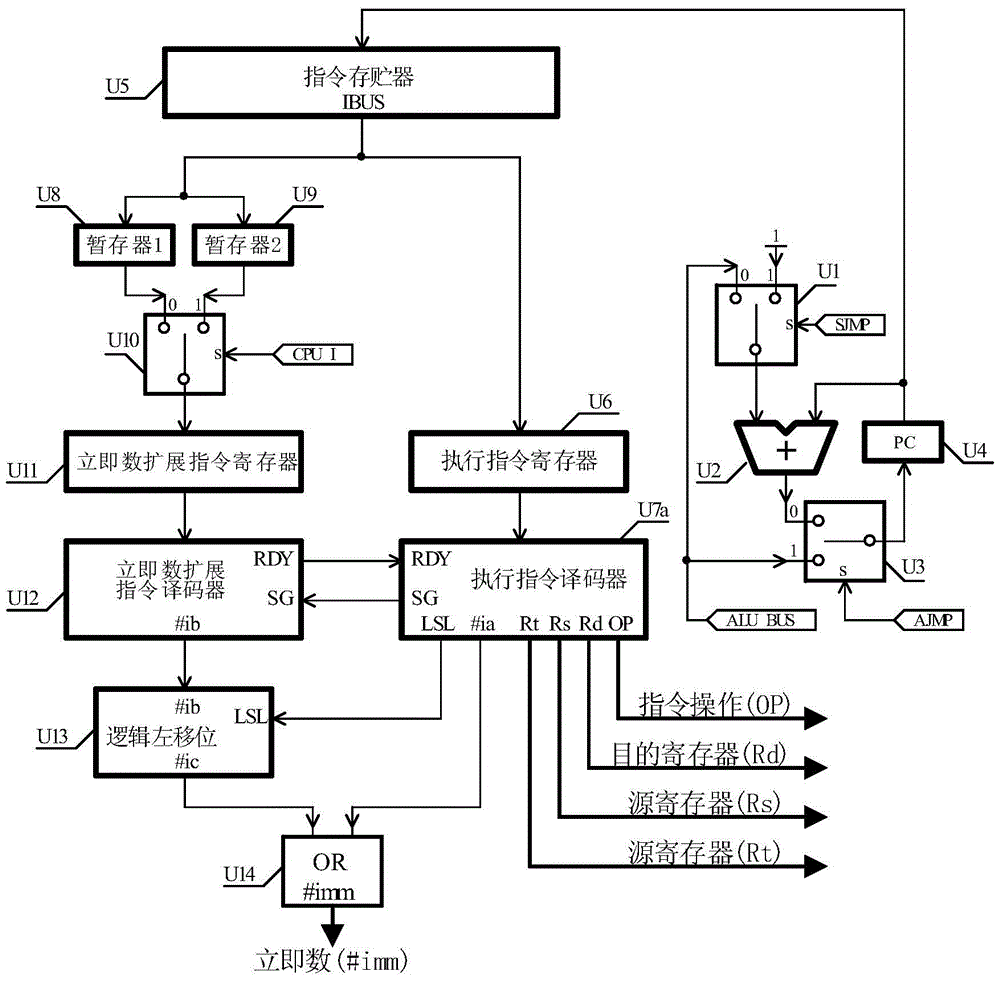

Method and device for extending immediate operand in computer instruction

ActiveCN105677298AOptimize execution efficiencyShorten the timeMachine execution arrangementsProgramming processLeft shifting

The invention discloses a method and device for extending an immediate operand in a computer instruction. At least one immediate operand extending instruction is newly increased in an RISC instruction system, during the programming process, an immediate operand the digit number of which is larger than the length of an immediate operand domain of an execution instruction is divided into a high-order immediate operand field and a low-order immediate operand field, the high-order immediate operand field is subjected to signed extension or unsigned extension and then is stored in the immediate operand domain of the immediate operand extending instruction, and the low-order immediate operand field just fills up the immediate operand domain of the execution instruction; during the instruction fetching process, the newly-increased immediate operand extending instruction and the execution instruction following closely are sent into respective decoders synchronously to carry out decoding; during the decoding process, the immediate operand output by the immediate operand extending instruction decoder is subjected to logical left shift and then is merged with the immediate operand output by the execution instruction decoder, after the merging process, the immediate operand the digit number of which is larger than the length of the immediate operand domain of the execution instruction is obtained. By employing the method for extending the immediate operand in the computer instruction, the program execution efficiency can be greatly improved, and time and space are saved.

Owner:李朝波

Method and system for checking rotate, shift and sign extension functions using a modulo function

A method of discovering a fault in a circuit is disclosed. The method comprises generating a first result of a selected function by performing the selected function on an operand, wherein the selected function employs a mask. Once the function is performed, an antimask of the mask is created, and the modulo of the antimask is calculated. A modulo function of the first result of the selected function is calculated to obtain a third result. A modulo of the operand is then calculated to obtain a fourth result, and a second function is then performed on the second result and the third result to obtain a fifth result. In response to comparing the fifth result to the fourth result, a signal is propagated to indicate a fault in the circuit.

Owner:INT BUSINESS MASCH CORP

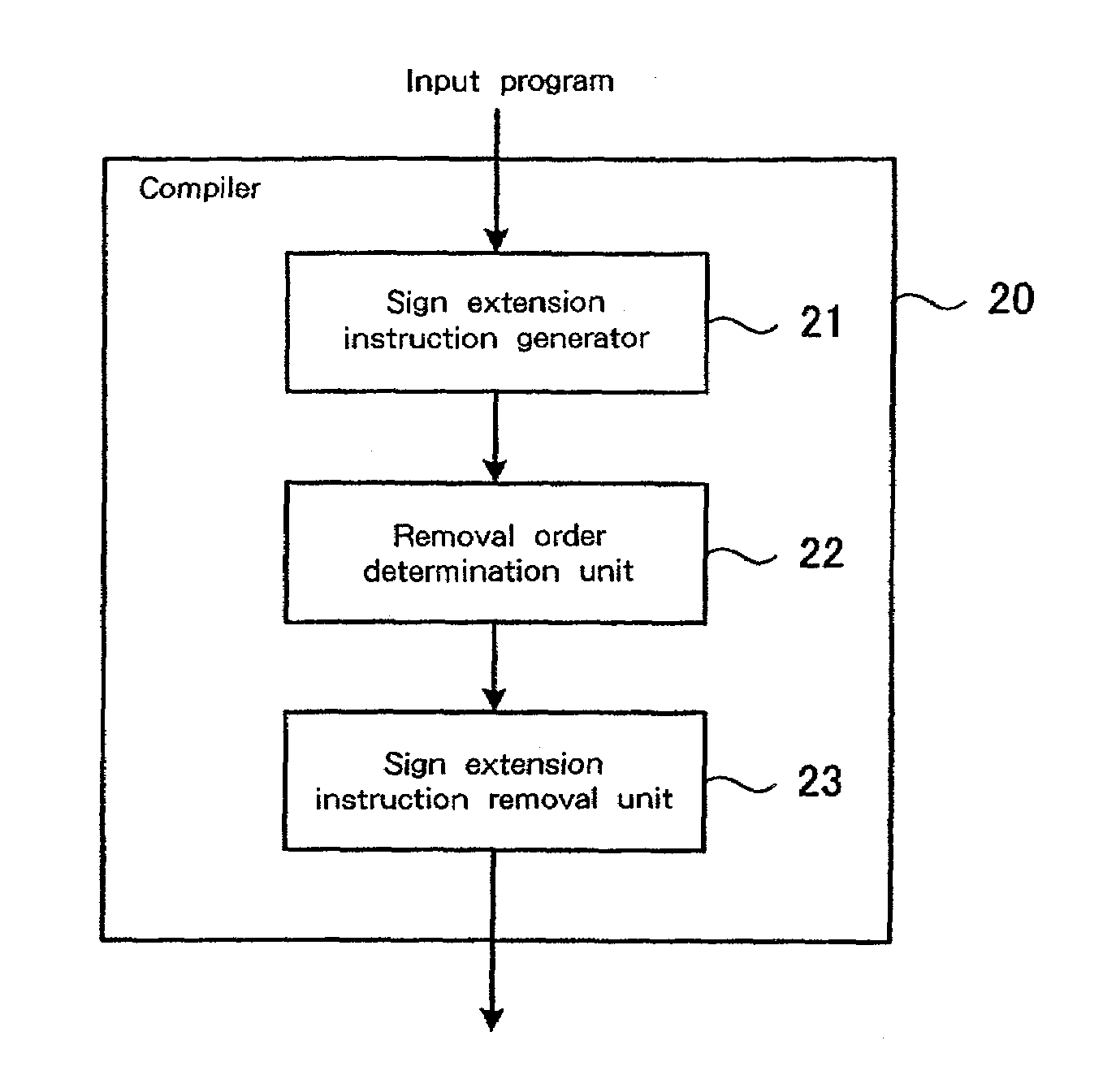

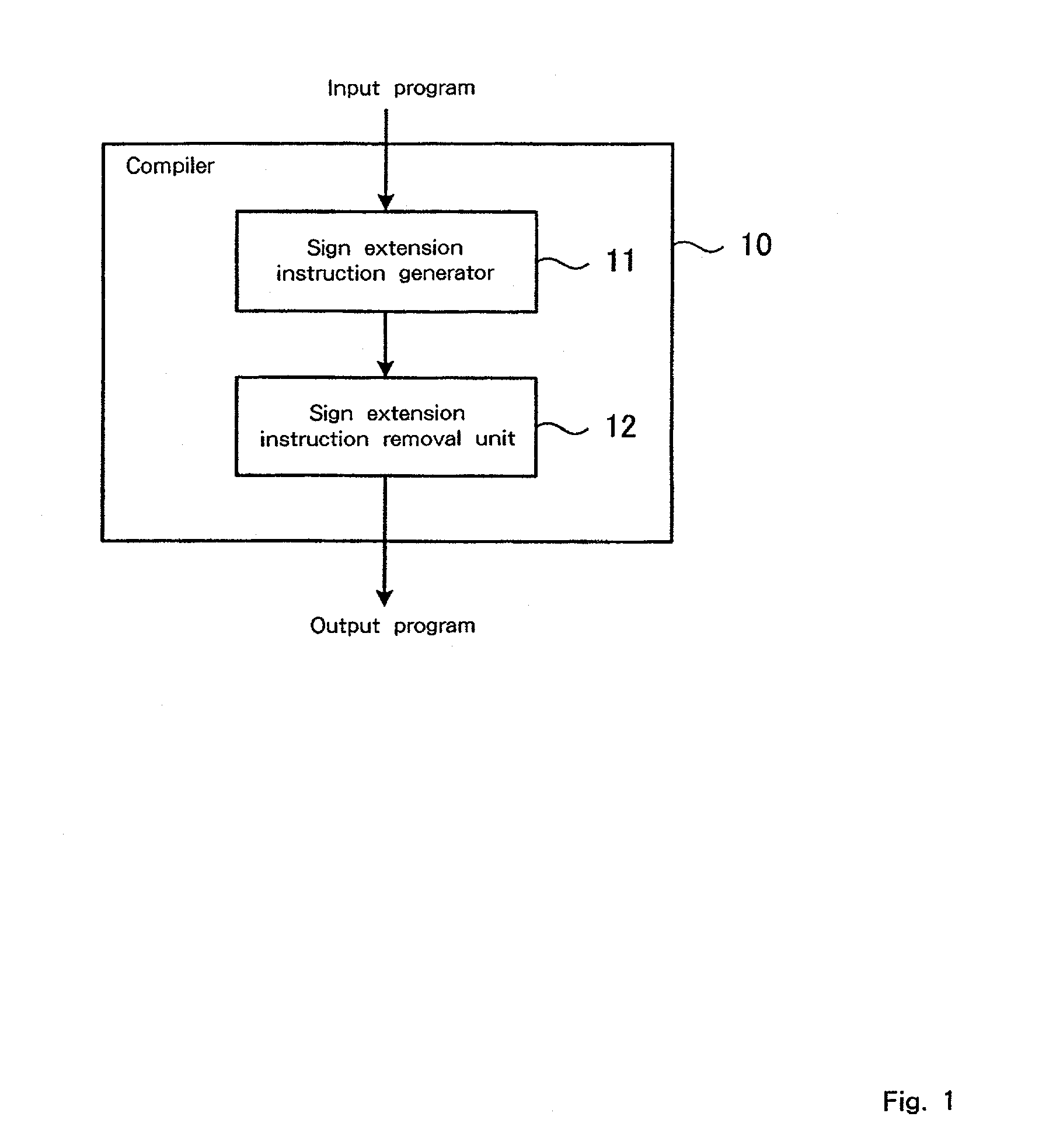

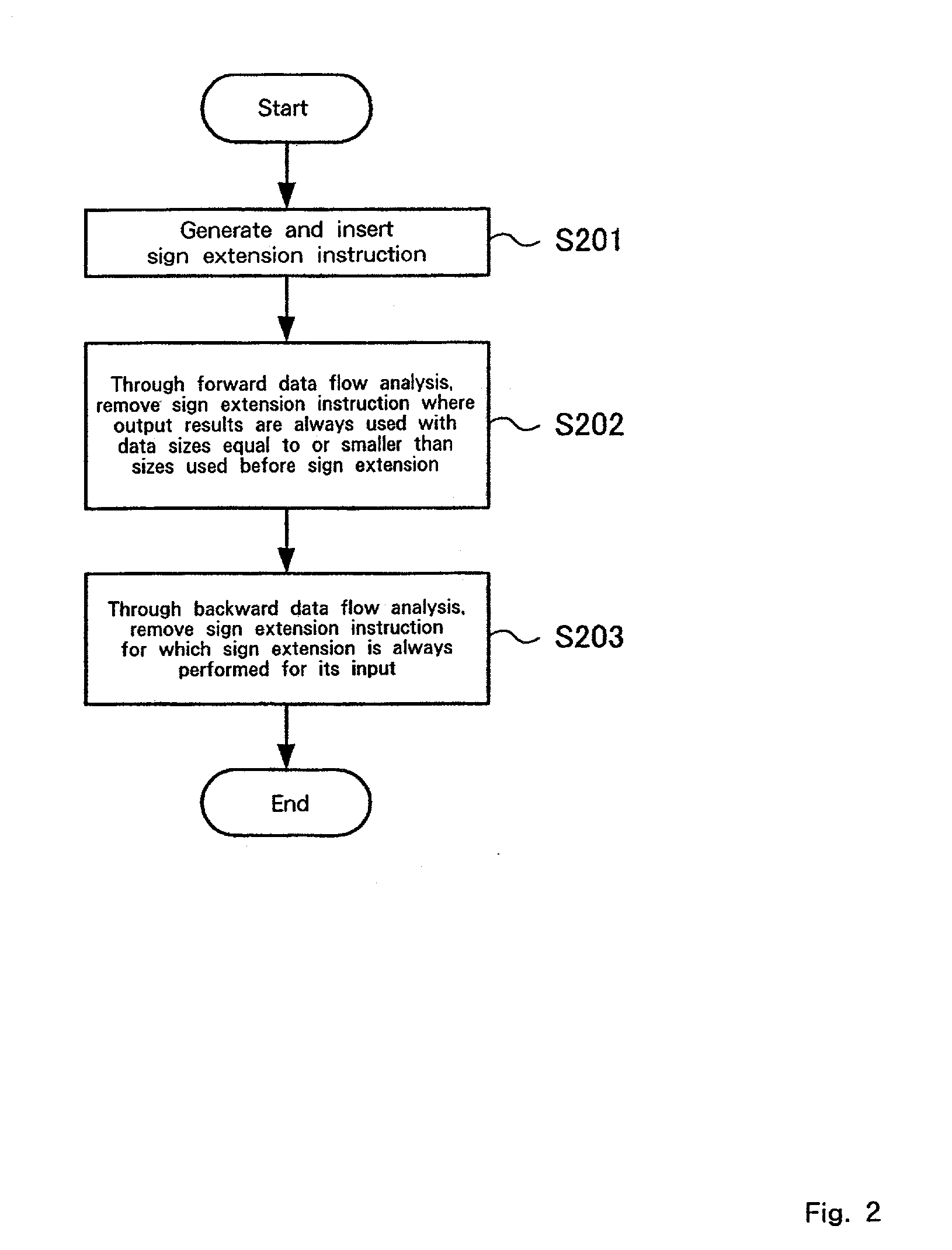

Computer program conversion and compilation

InactiveUS7278138B2Execution efficiency is improvedExecution efficiency is highSoftware engineeringDigital computer detailsComputer programSign extension

The present invention provides methods, apparatus, and systems to remove a redundant, sign extension instruction from a program and to improve the execution efficiency of the program. In an example embodiment, a conversion program for controlling a computer for the conversion of an execution program, especially a compiler, permits the computer to perform: a function for analyzing a sign extension instruction issued in order to perform the sign extension of a value defined in the execution program; and a function for, in accordance with analysis results, removing a predetermined sign extension instruction from those included in the execution program.

Owner:GOOGLE LLC

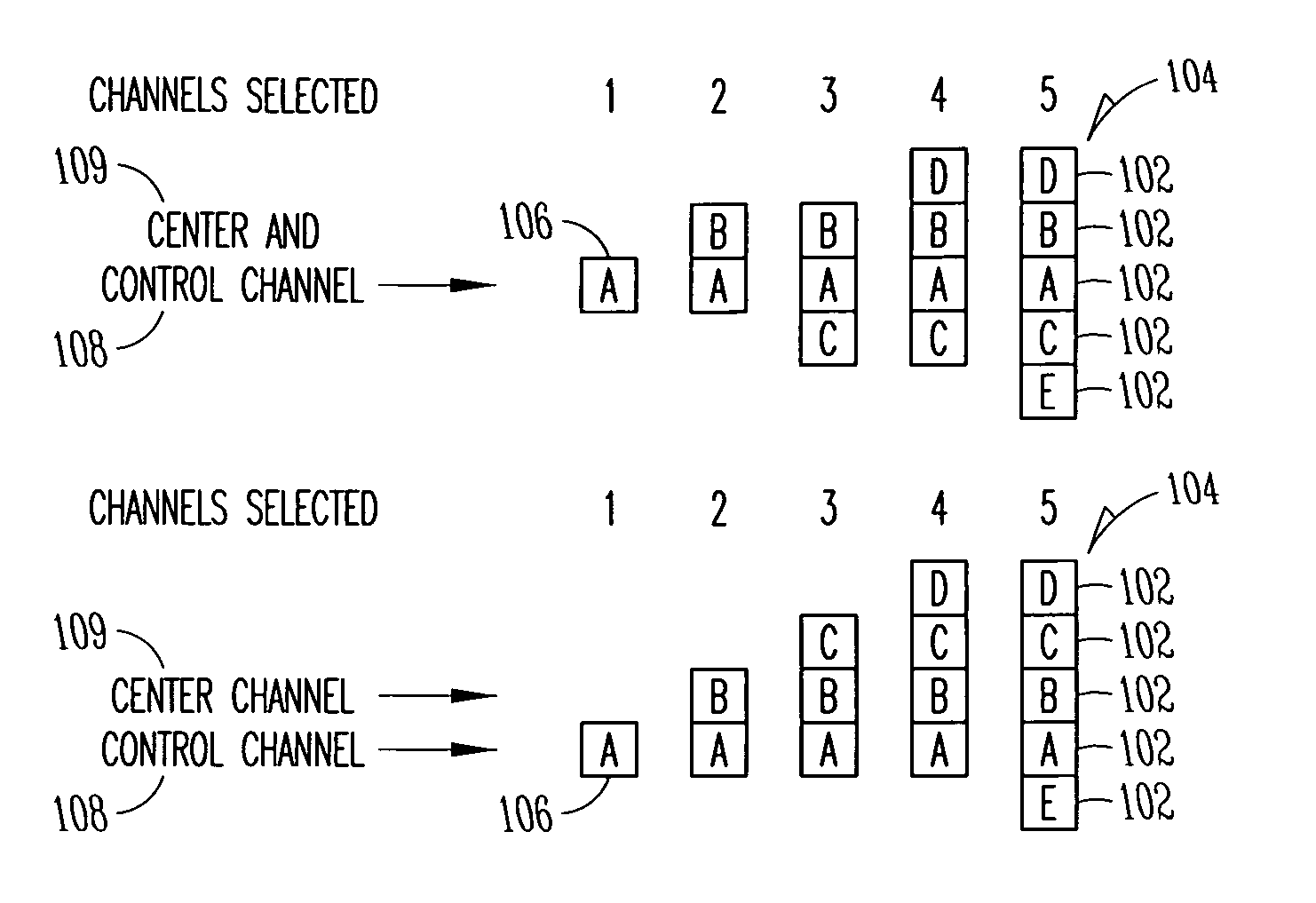

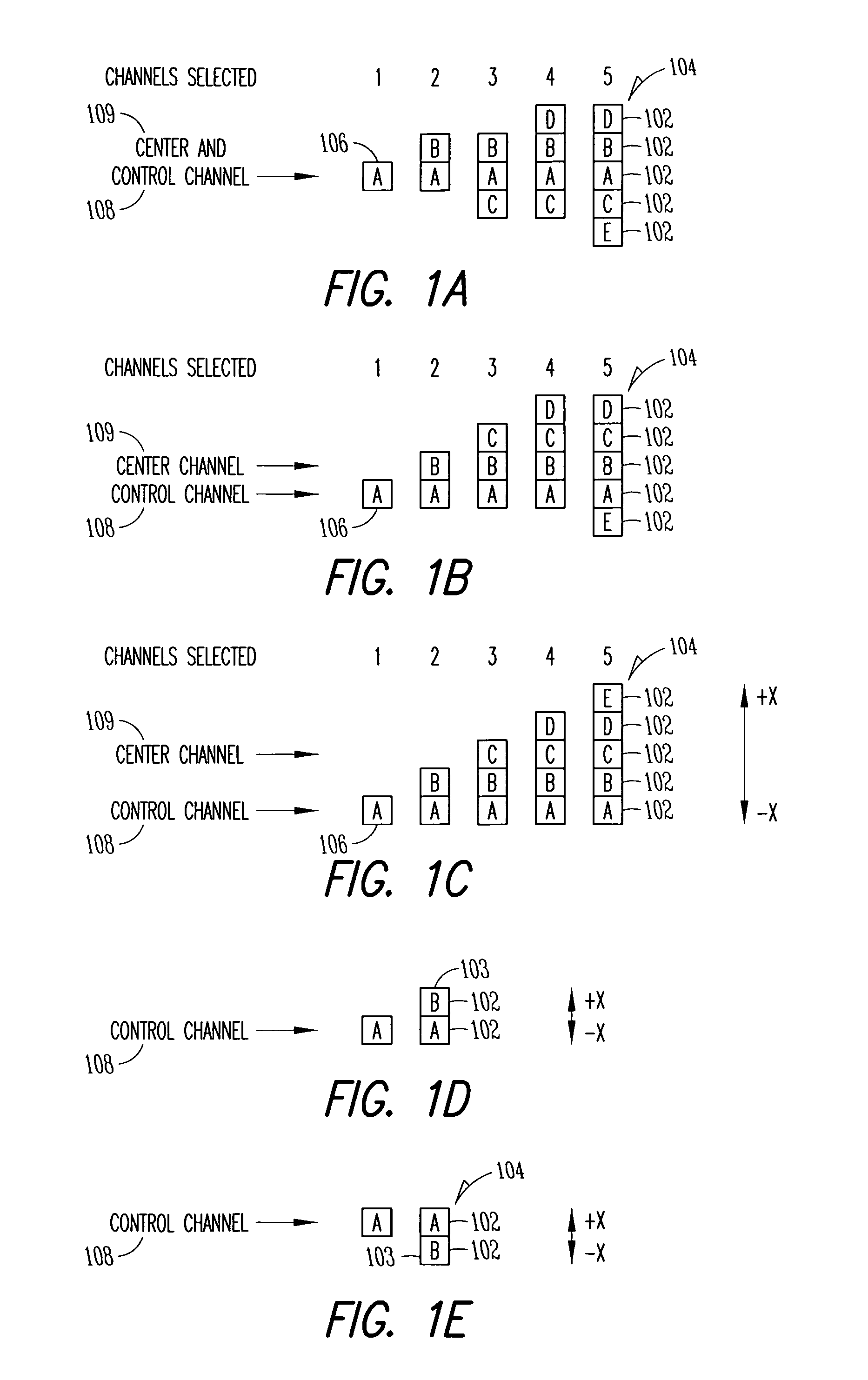

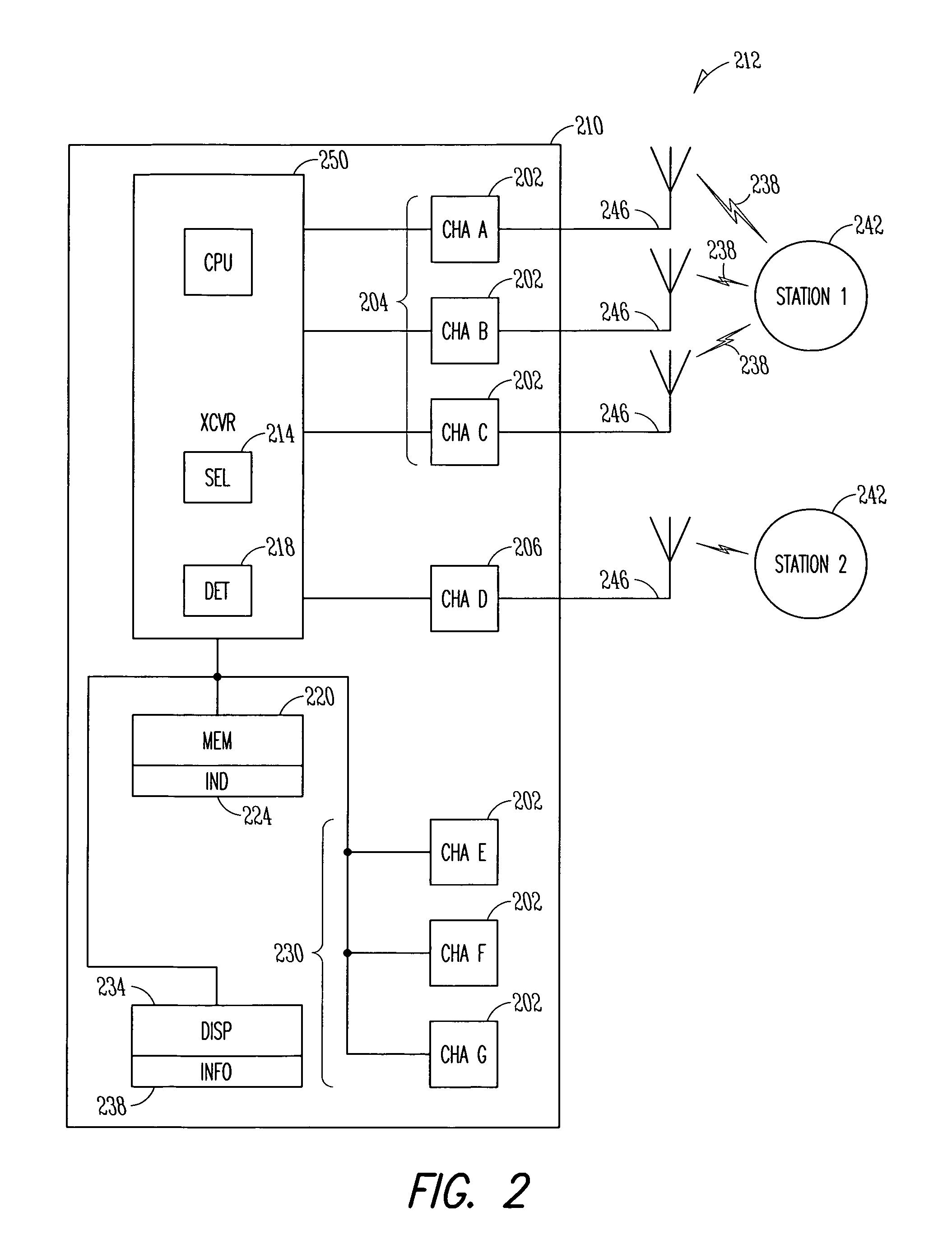

Channel specification apparatus, systems, and methods

ActiveUS7440423B2Network traffic/resource managementTime-division multiplexControl channelEngineering

An apparatus and a system, as well as a method and article, may operate to select a group of contiguous communications channels having a specified number of channels, a center channel, and a control channel. Some embodiments may operate to select a group of contiguous communications channels having a specified control channel and a signed extension channel offset.

Owner:APPLE INC

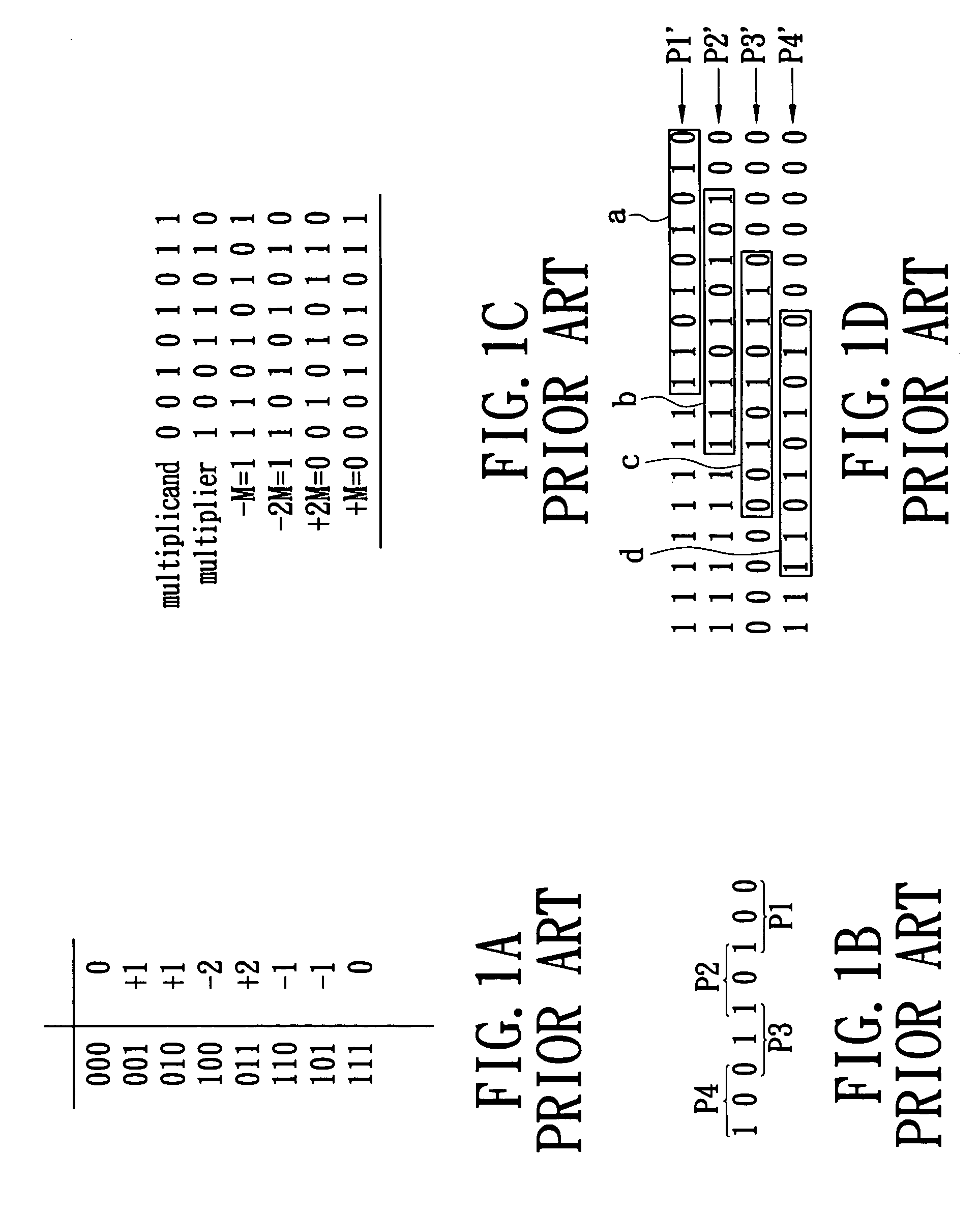

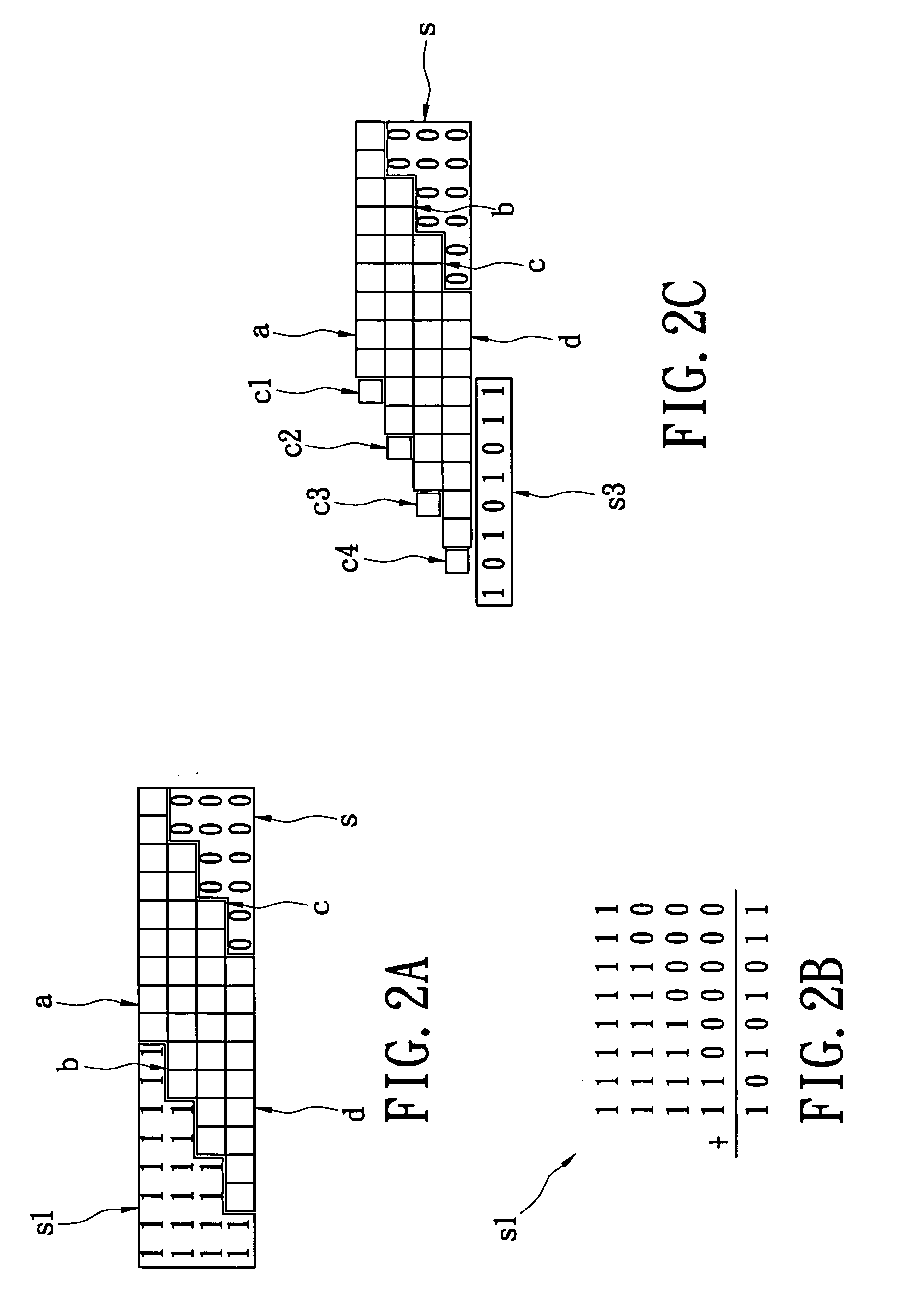

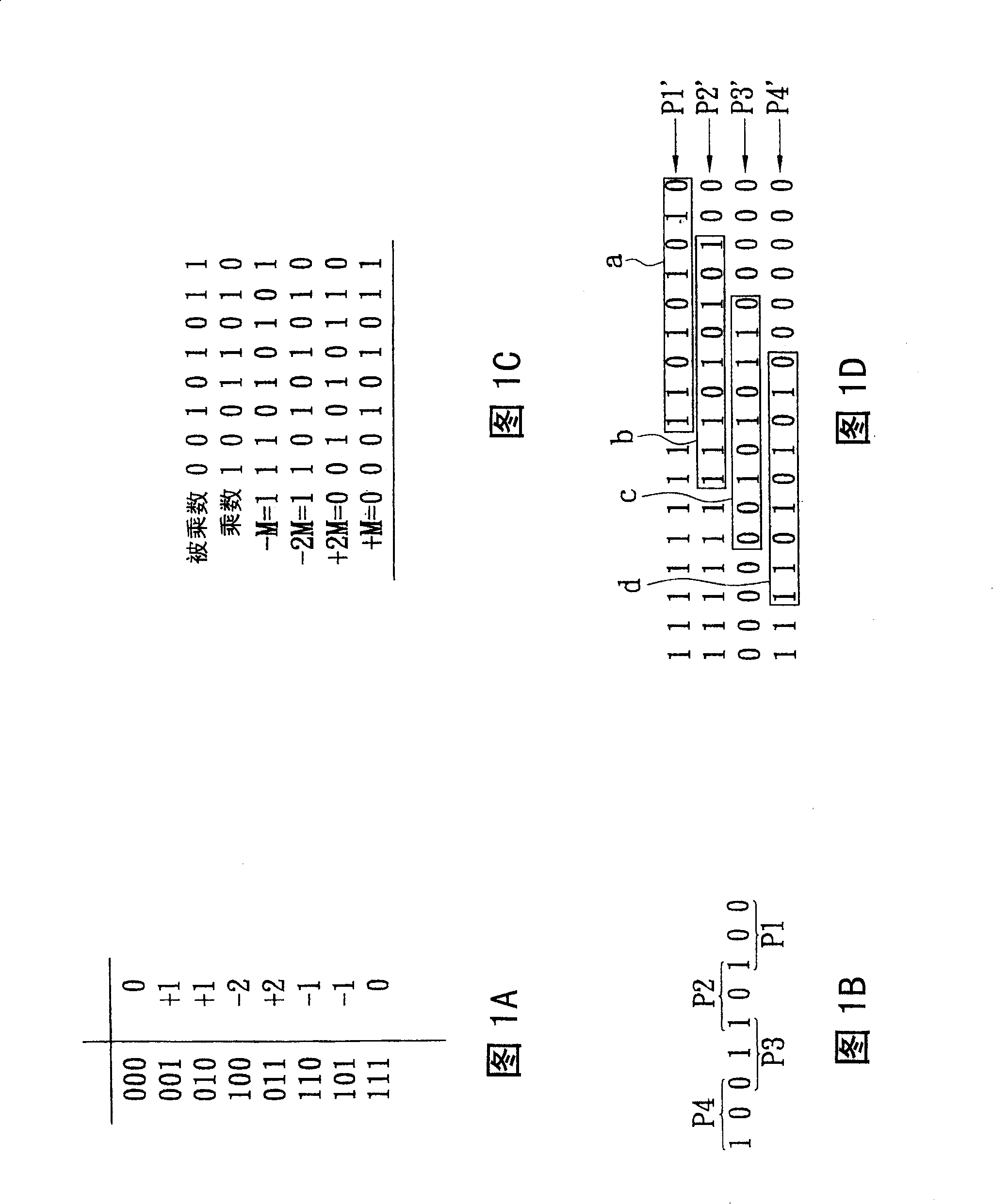

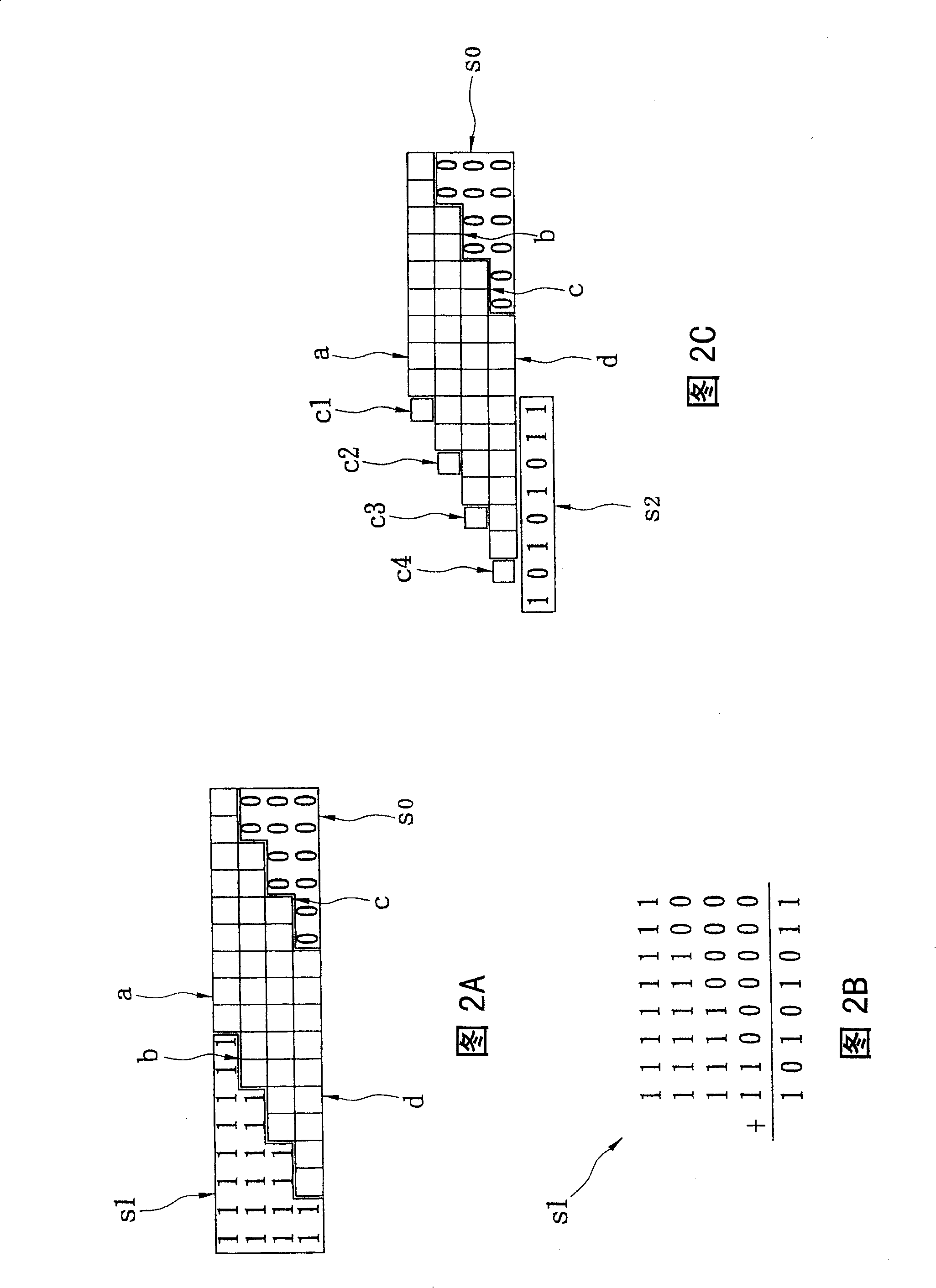

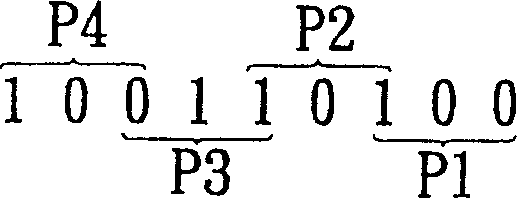

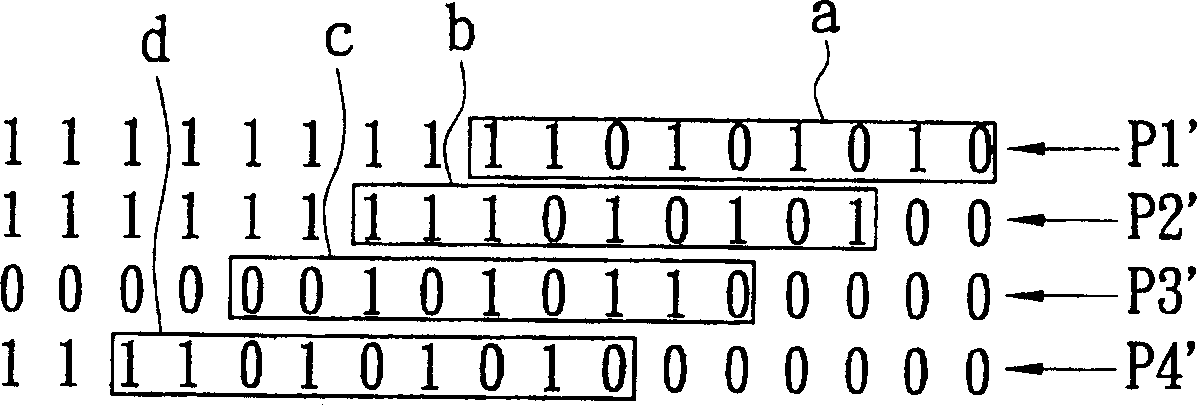

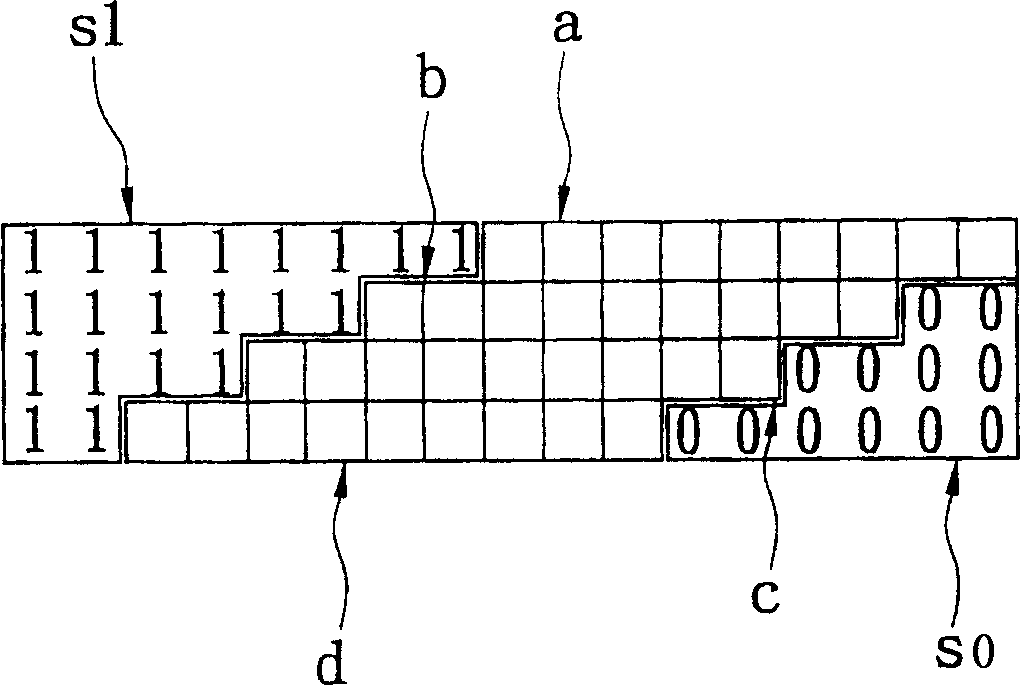

Multiplier sign extension method and architecture

InactiveUS20050223054A1Reduce wasteMade smallComputation using non-contact making devicesBinary multiplierPartial product

A multiplier sign extension method and architecture are used for encoding operations of a multiplier of a digital signal processor. The multiplier sign extension method comprises the steps of: determining the width of the multiplier to obtain a sign extension bit total value; encoding a multiplier by means of the modified Booth algorithm; calculating out a plurality of layers of partial product terms by multiplying a multiplicand by the encoded multiplier to form a first stepwise bit table; setting a plurality of complementary bits, a first correction bit and a second correction bit to form a second stepwise bit table; and summing up the plurality of layers of the second stepwise bit table. Without increasing critical paths, a plurality of complementary bits is provided for encoding of sign extension to reduce waste of chip area and make the multiplier smaller.

Owner:ALICORP

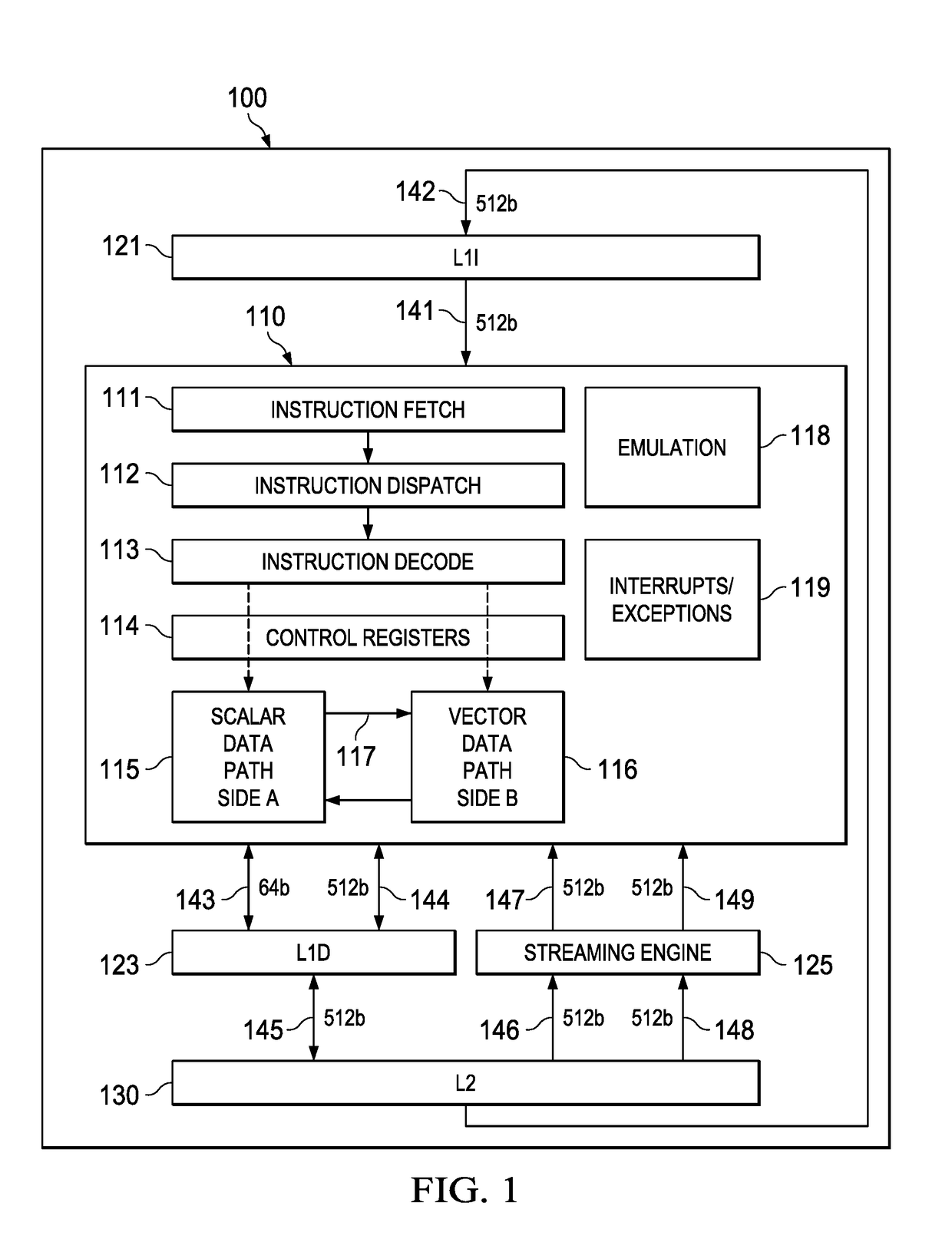

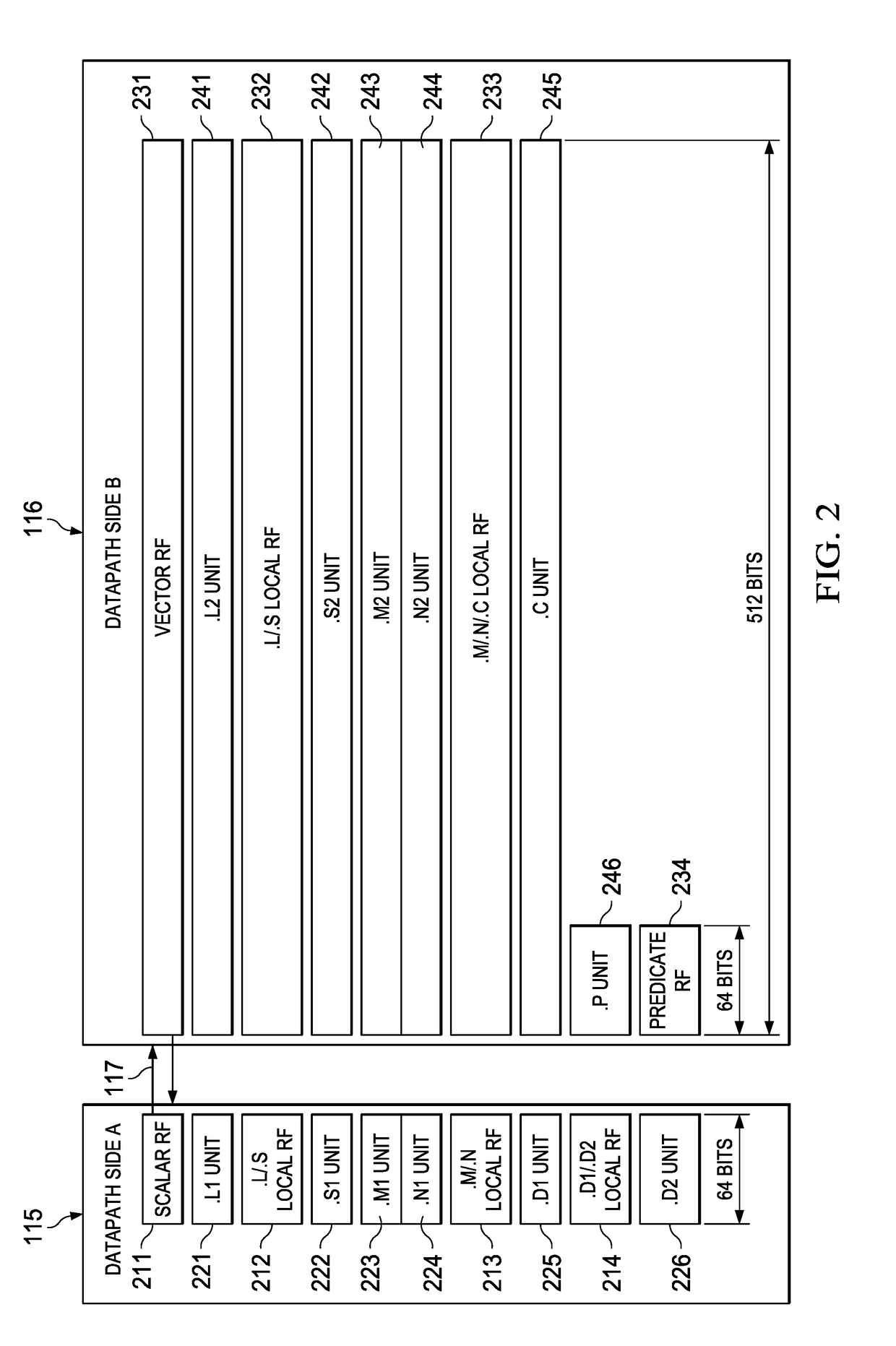

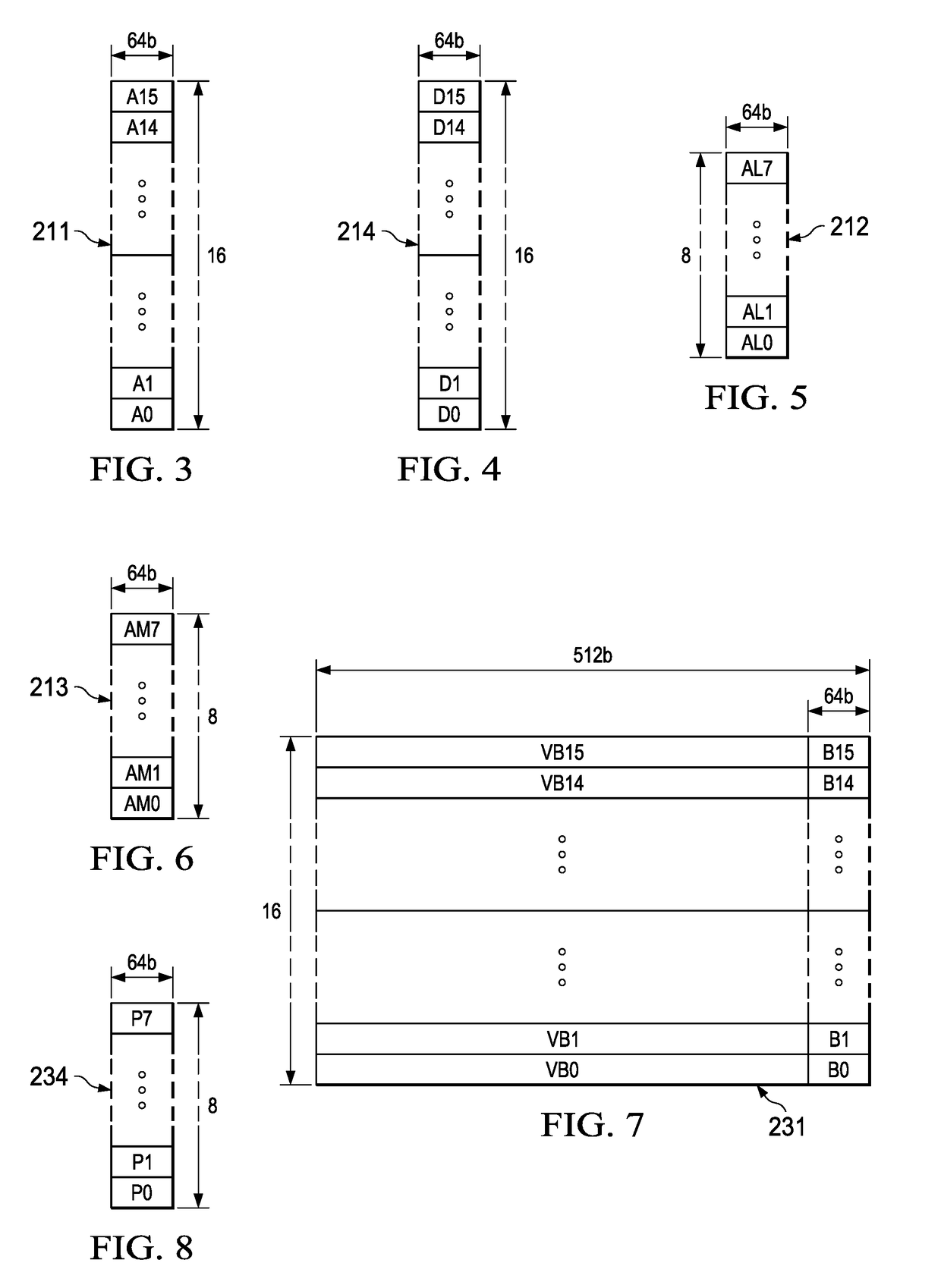

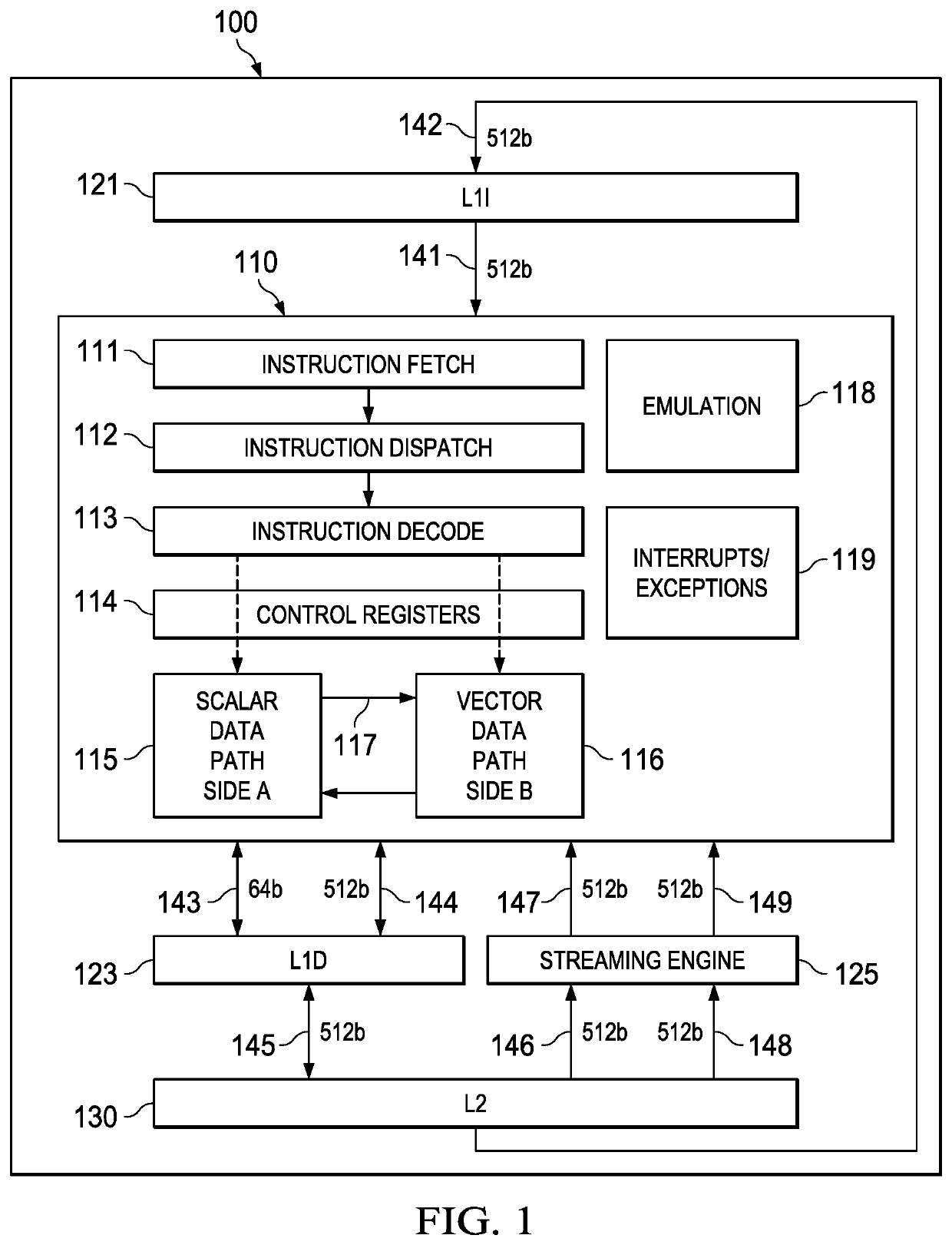

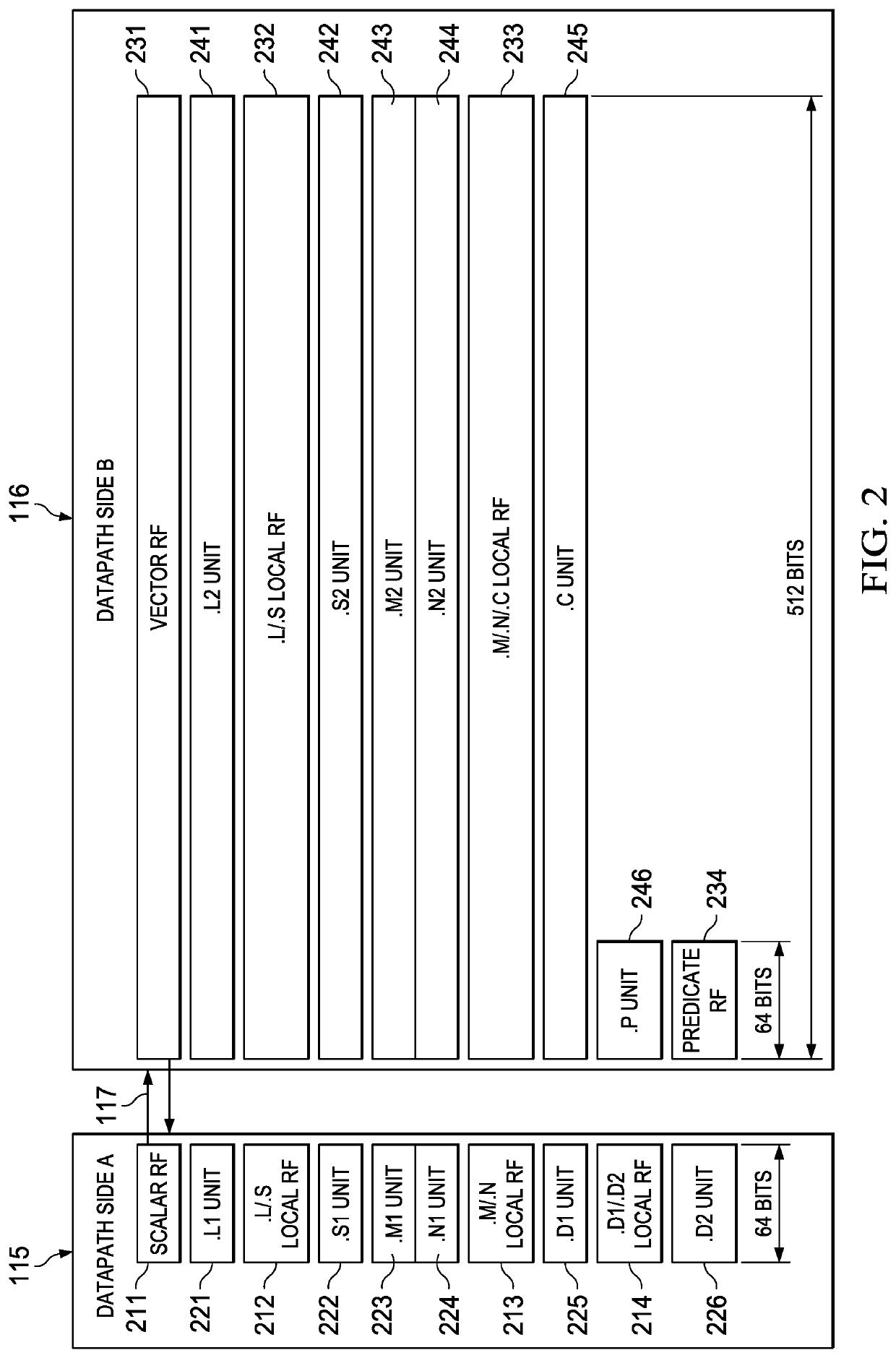

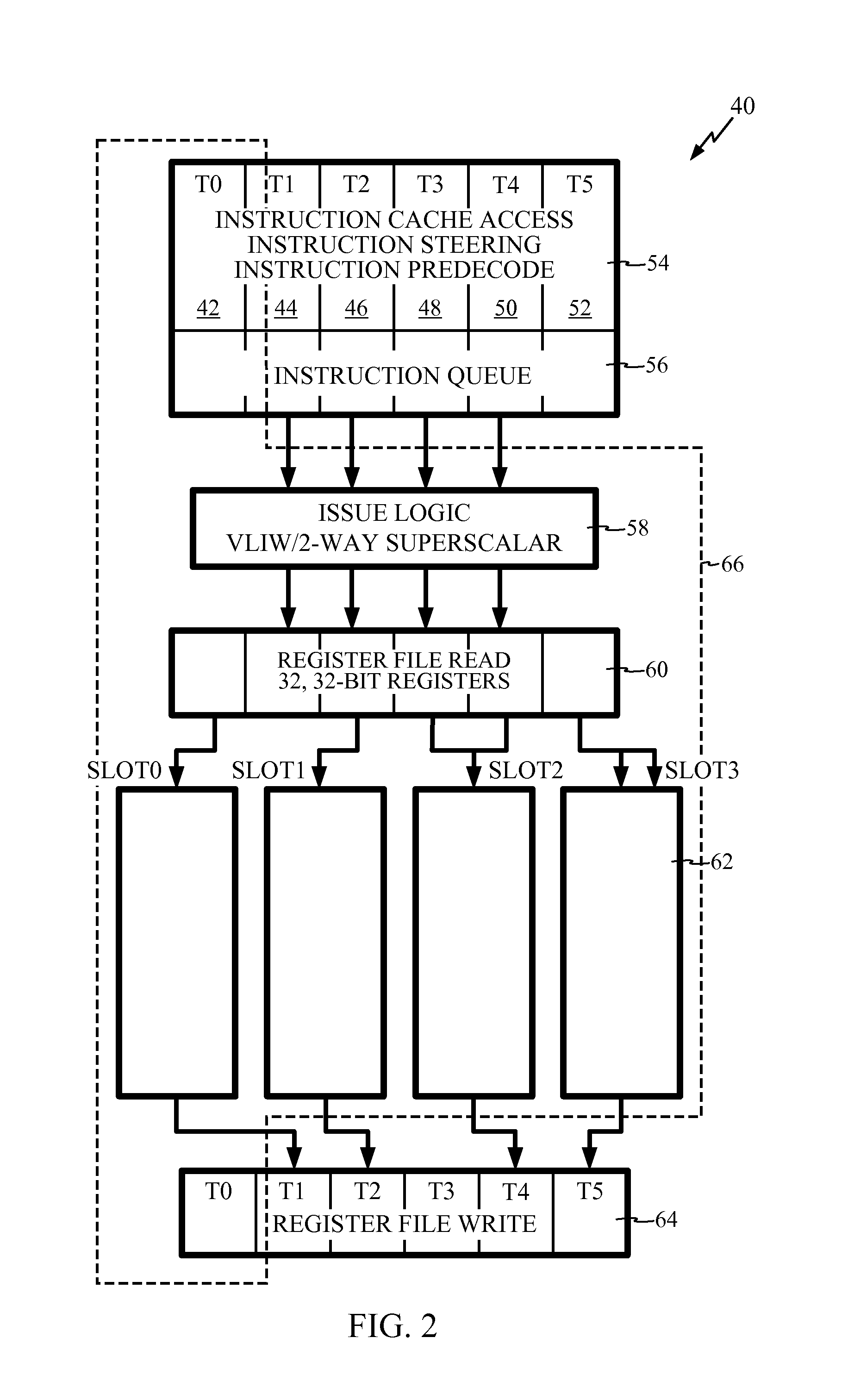

Streaming engine with short cut start instructions

A streaming engine employed in a digital data processor specifies a fixed read only data stream recalled memory. Streams are started by one of two types of stream start instructions. A stream start ordinary instruction specifies a register storing a stream start address and a register of storing a stream definition template which specifies stream parameters. A stream start short-cut instruction specifies a register storing a stream start address and an implied stream definition template. A functional unit is responsive to a stream operand instruction to receive at least one operand from a stream head register. The stream template supports plural nested loops with short-cut start instructions limited to a single loop. The stream template supports data element promotion to larger data element size with sign extension or zero extension. A set of allowed stream short-cut start instructions includes various data sizes and promotion factors.

Owner:TEXAS INSTR INC

Low power vector summation method and apparatus

InactiveUS7085794B2High switching activity is avoidedReduce power consumptionDigital technique networkDigital computer detailsConstant errorMaximum magnitude

Owner:INTEL CORP

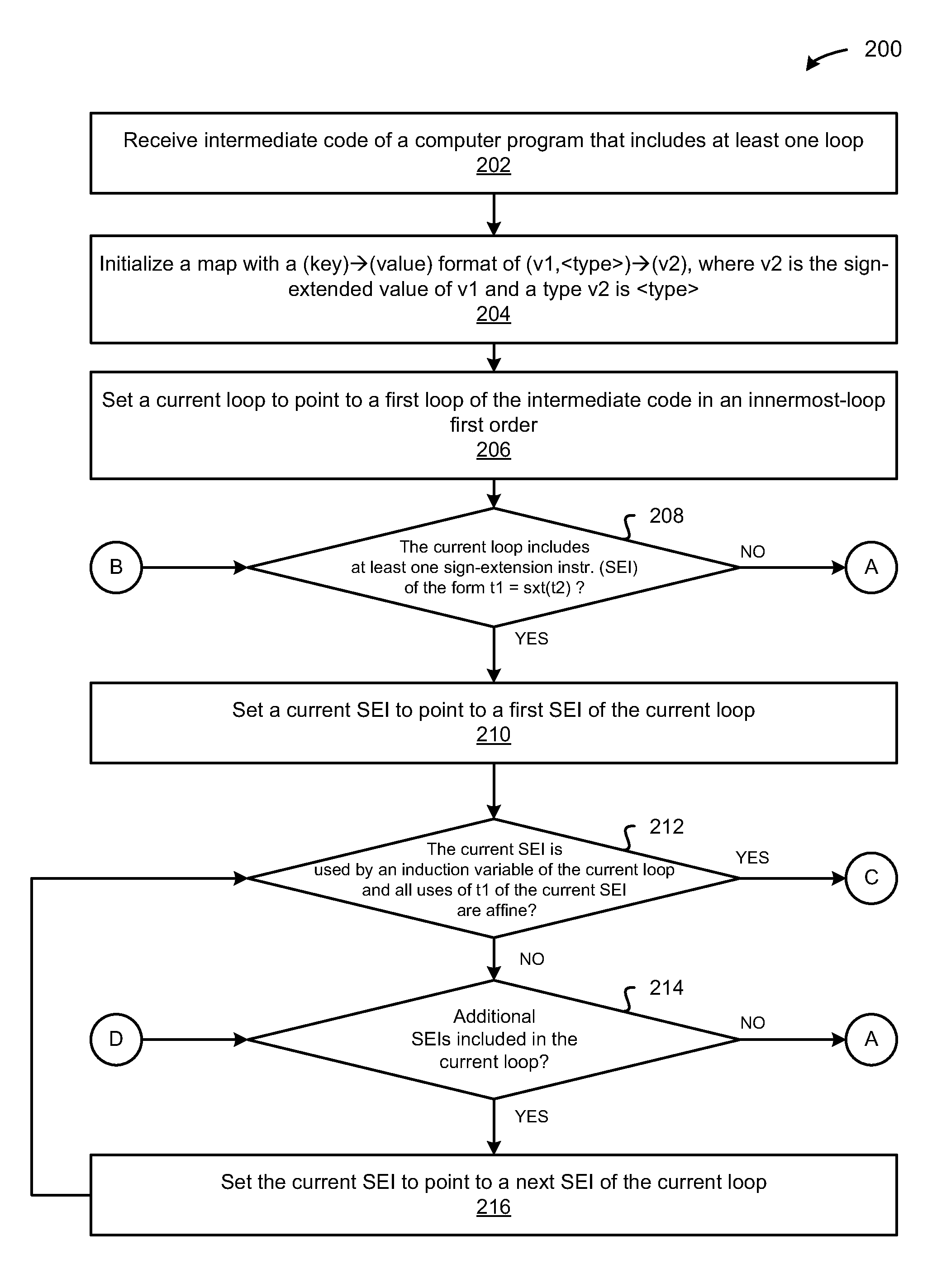

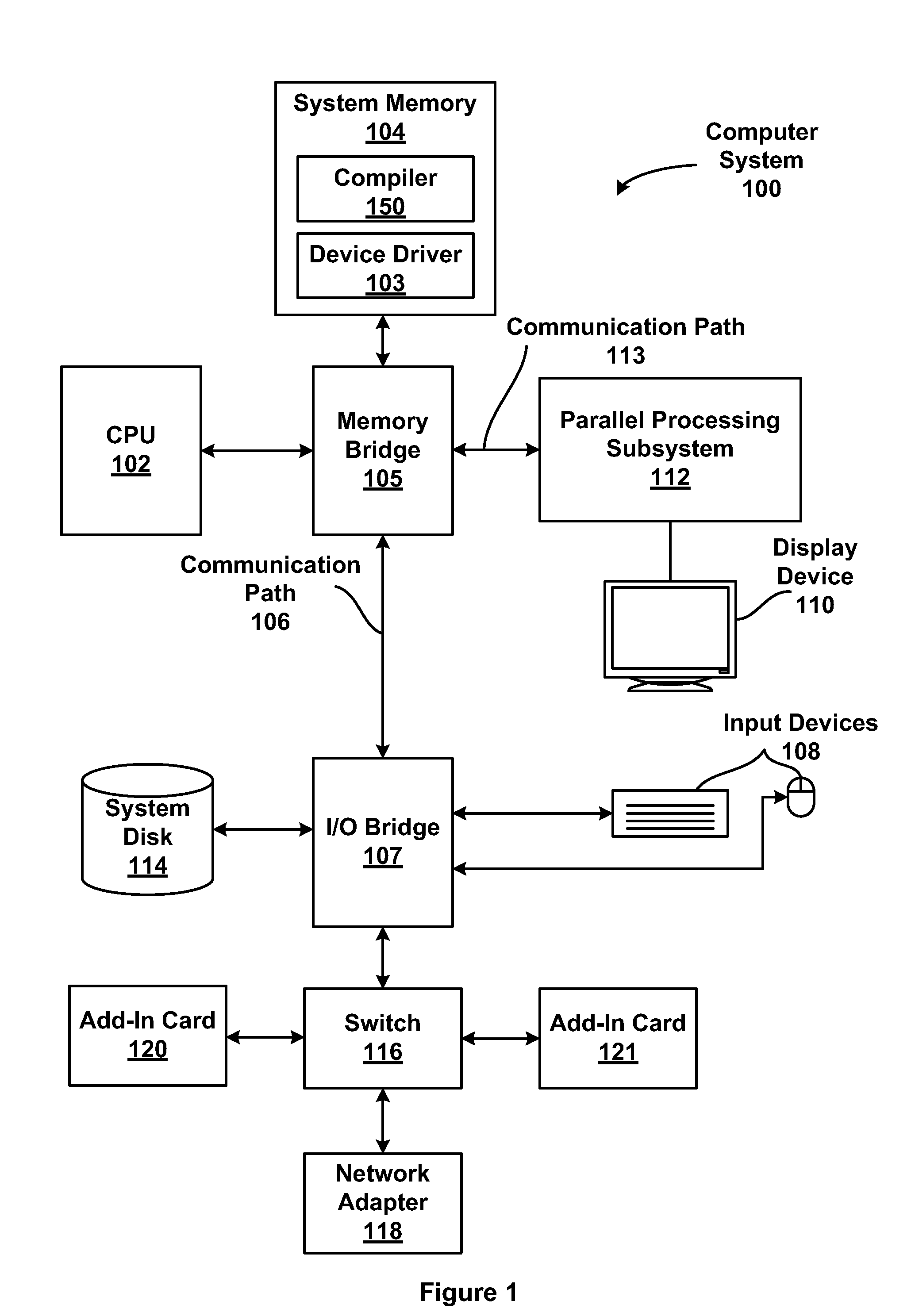

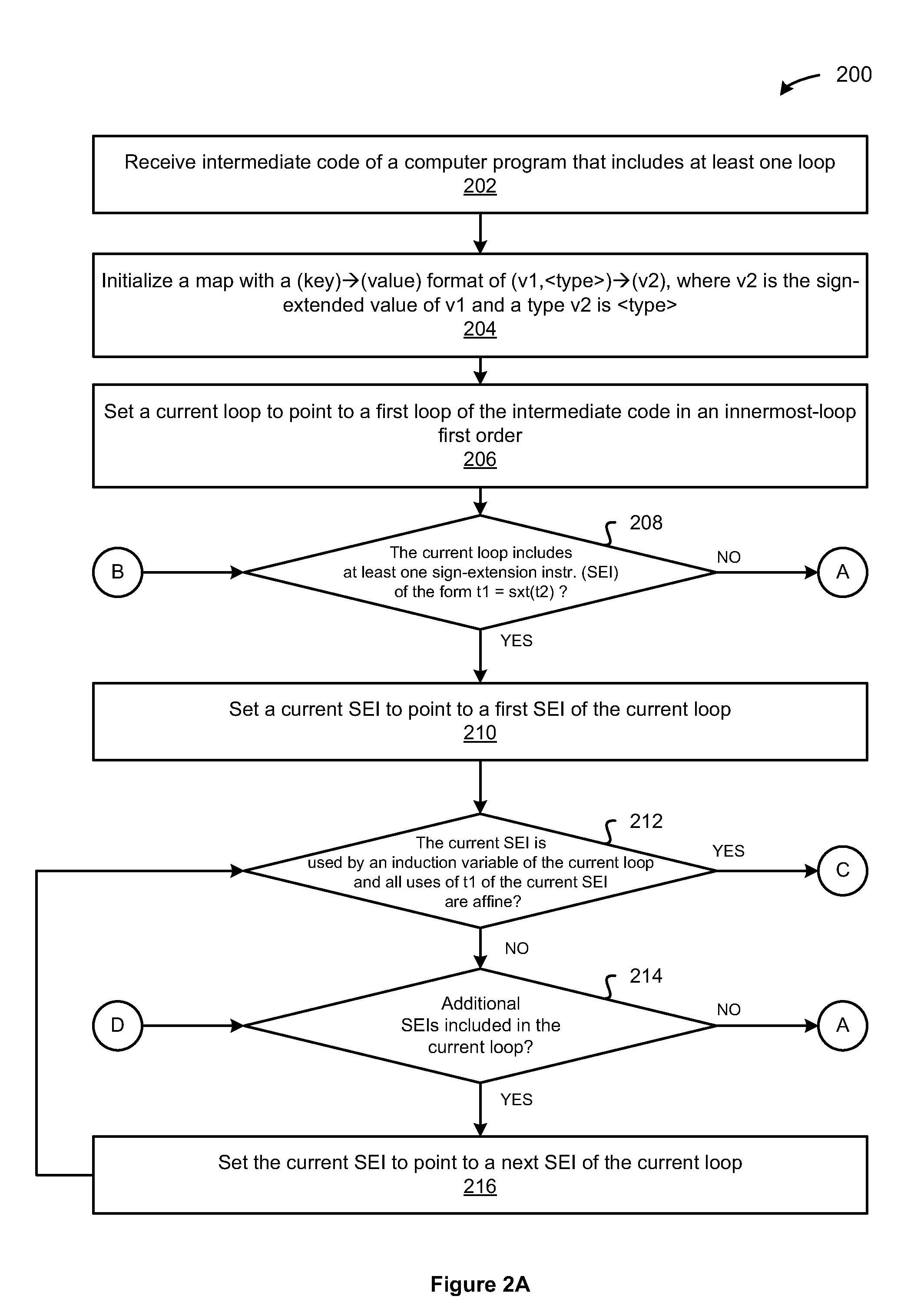

Demand-driven algorithm to reduce sign-extension instructions included in loops of a 64-bit computer program

ActiveUS20130117737A1Correctness of the computer program remains intactReduce in quantityProgram controlMemory systemsParallel computingIntermediate code

One embodiment of the present invention sets forth a technique for reducing sign-extension instructions (SEIs) included in a computer program, the technique involves receiving intermediate code that is associated with the computer program and includes a first SEI that is included in a loop structure within the computer program, determining that the first SEI is eligible to be moved outside of the loop structure, inserting into a preheader of the loop a second SEI that, when executed by a processor, promotes an original value targeted by the first SEI from a smaller type to a larger type, and replacing the first SEI with one or more intermediate instructions that are eligible for additional compiler optimizations.

Owner:NVIDIA CORP

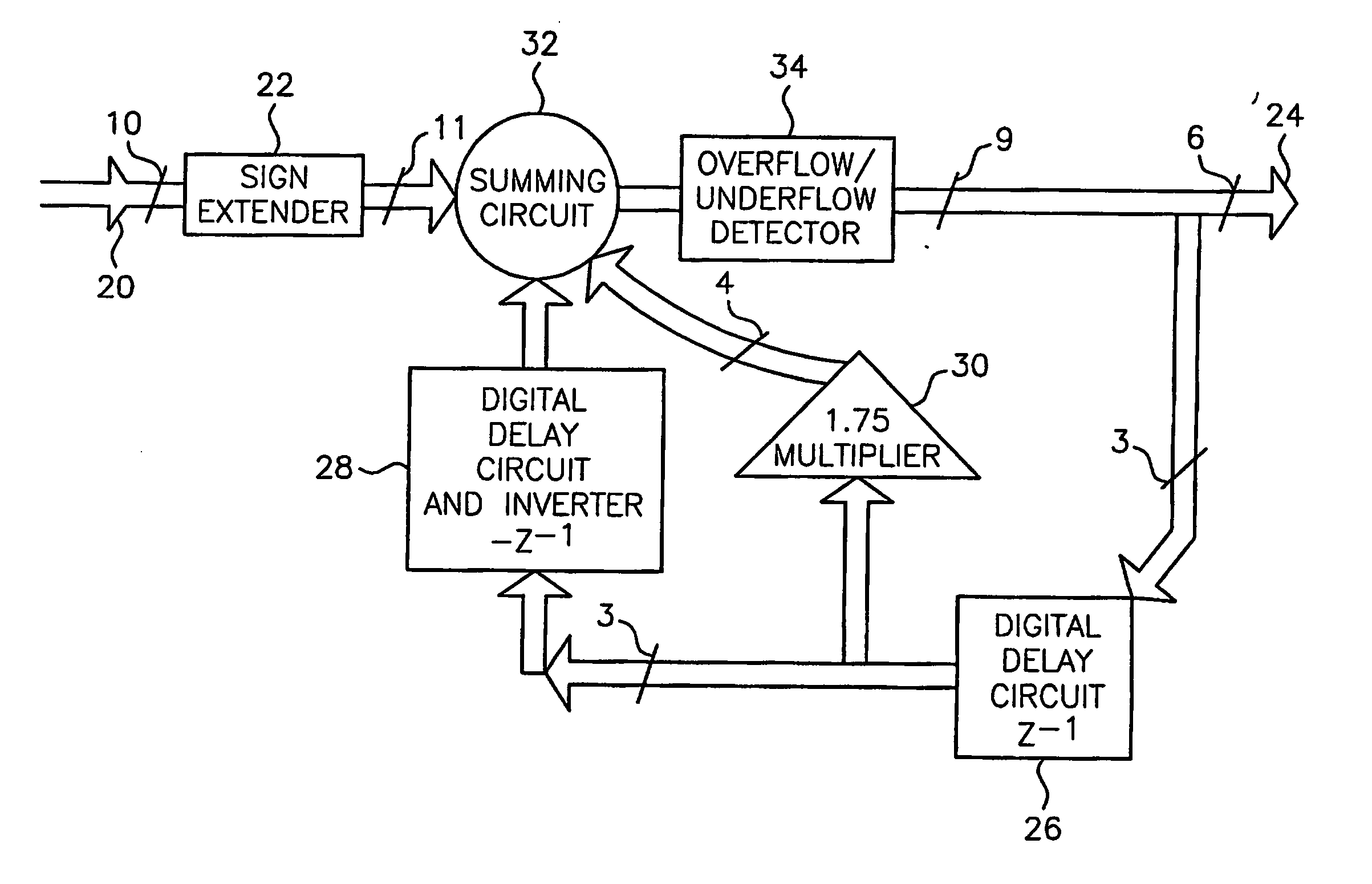

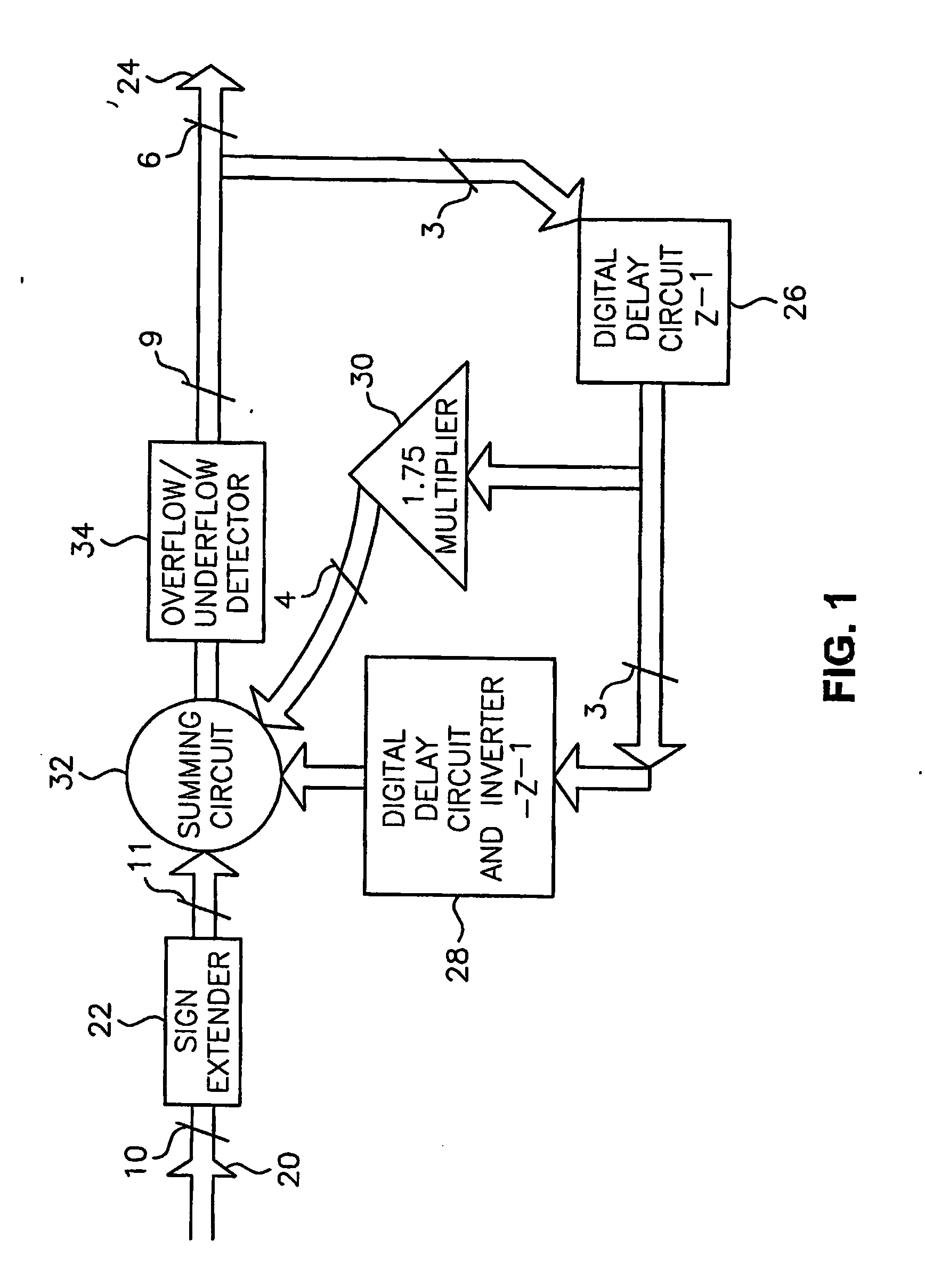

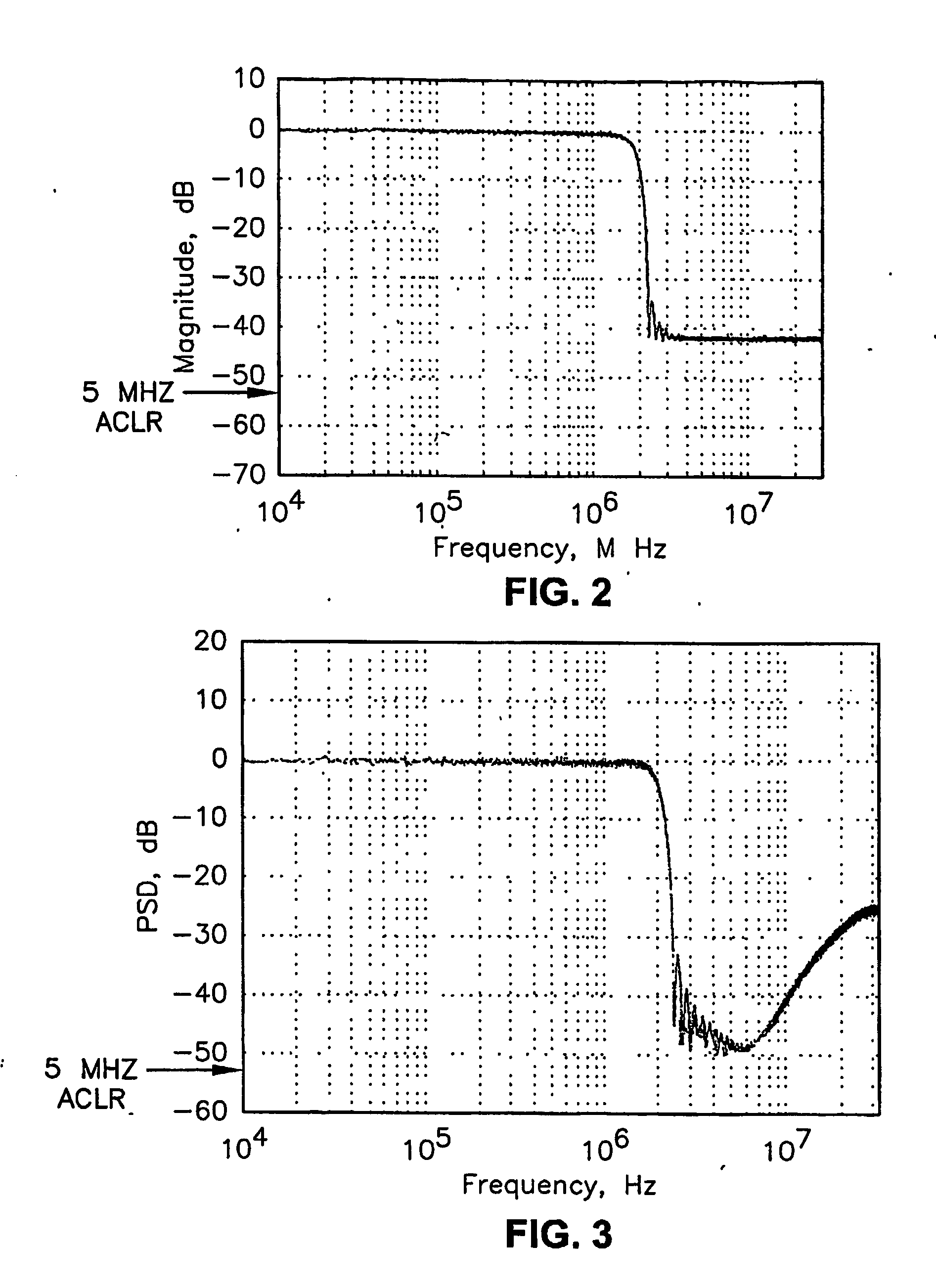

Bandpass delta sigma truncator and method of truncating a multi-bit digital signal

A bandpass delta sigma truncator that truncates multi-bit digital input signals to digital output signals (24) having a selected number of the most significant data bits of the digital input signals and a method of truncating multi-bit digital signals. The remaining least significant data bits (3) of the input signals are (a) time delayed (26) by a period of time equal to the time between successive input signals and multiplied by a number (30) related to the ratio of a selected frequency to the frequency of the input signals and the results of the multiplication are added (32) to signs extensions (11) of the input signals, and (b) time delayed by a period of time equal to twice the time between successive input signals and after inversion (28) are added (32) to the sign extensions of the input signals.

Owner:IBM CORP

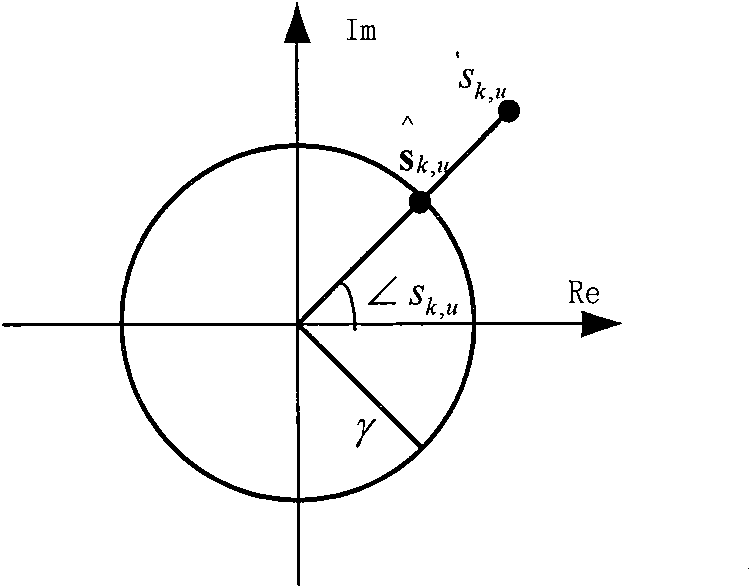

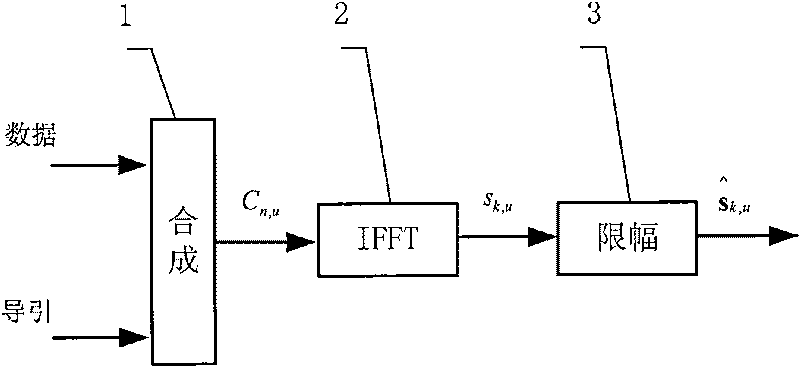

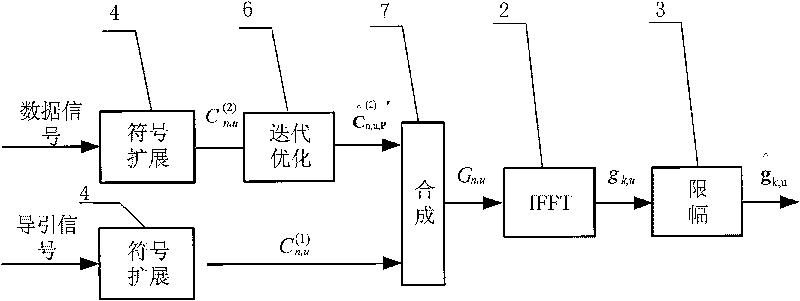

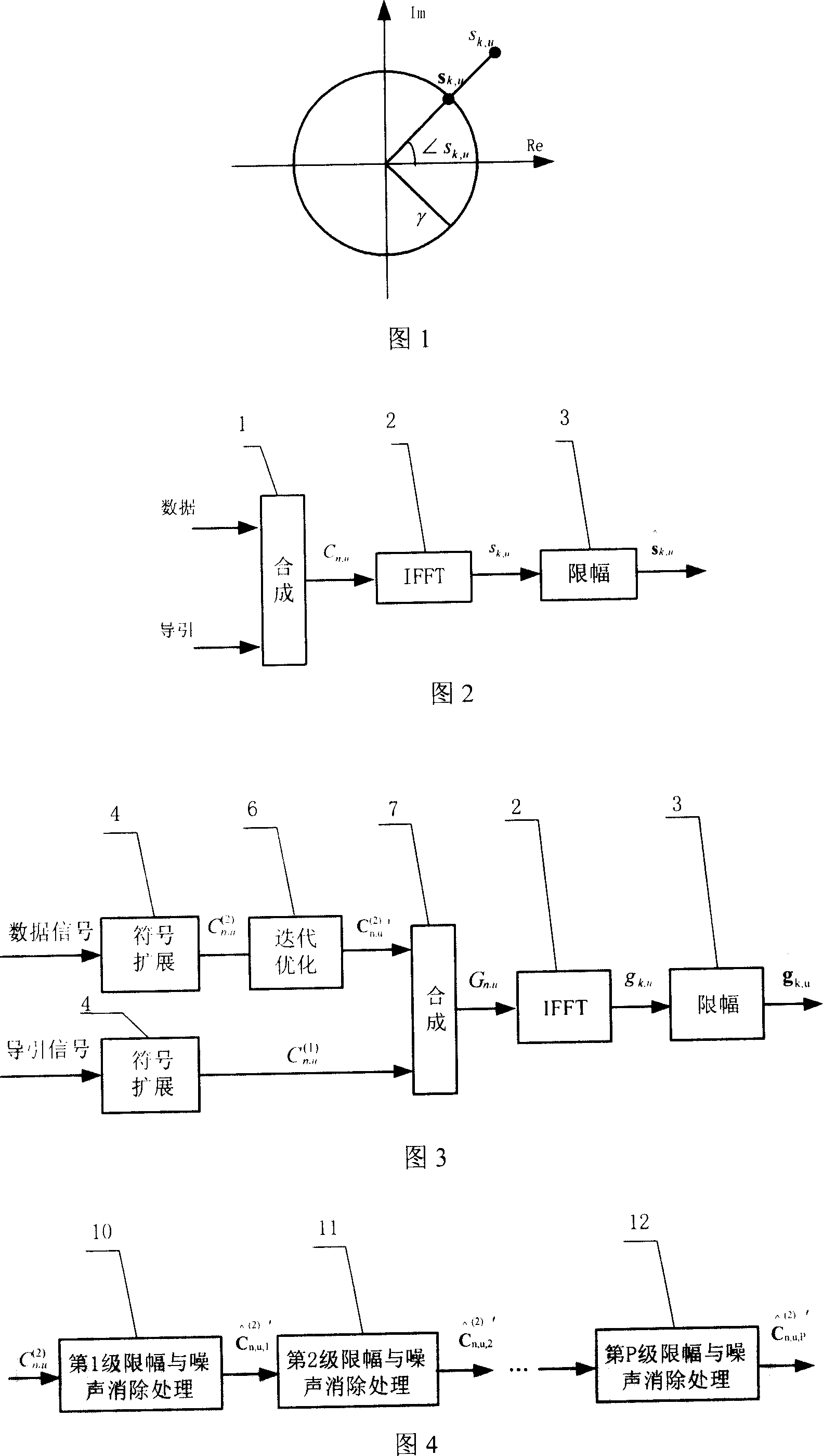

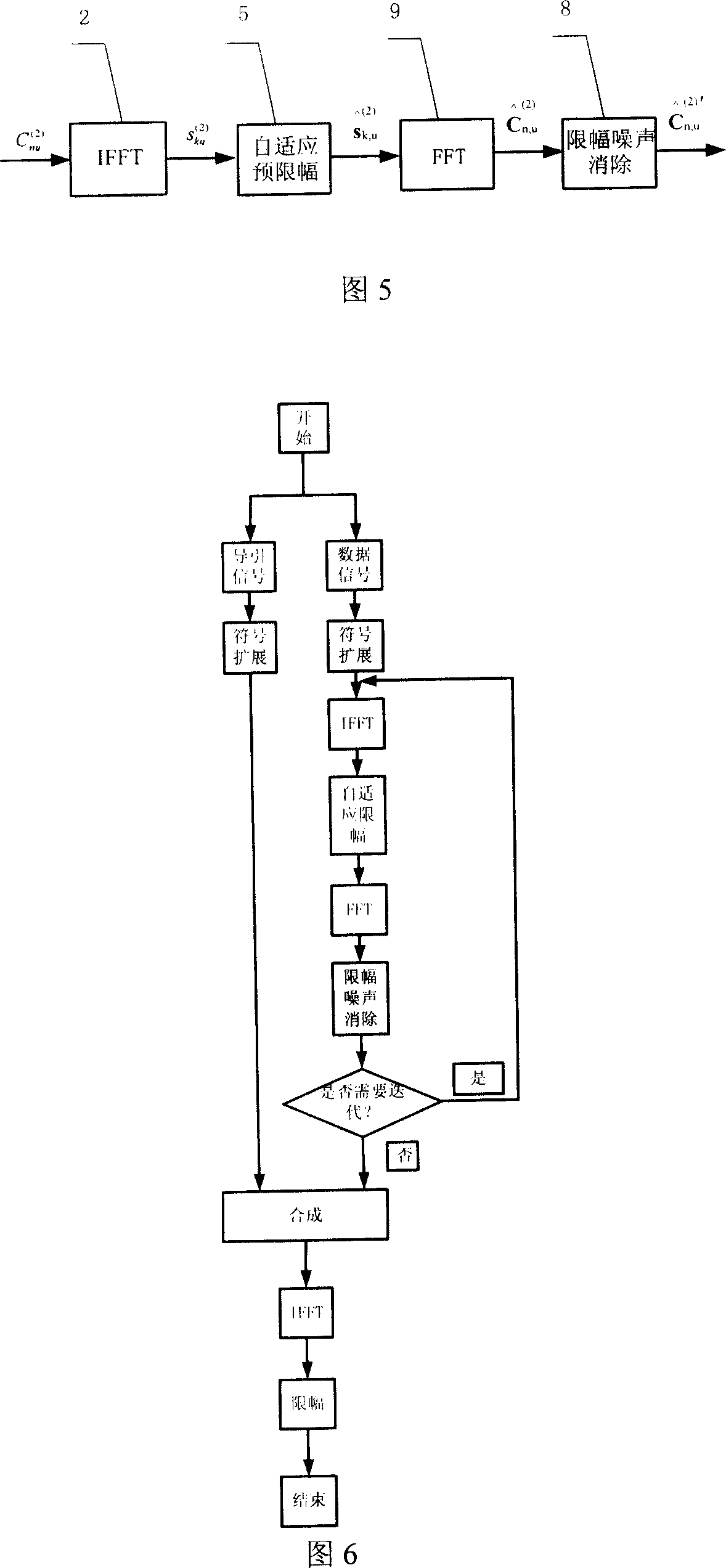

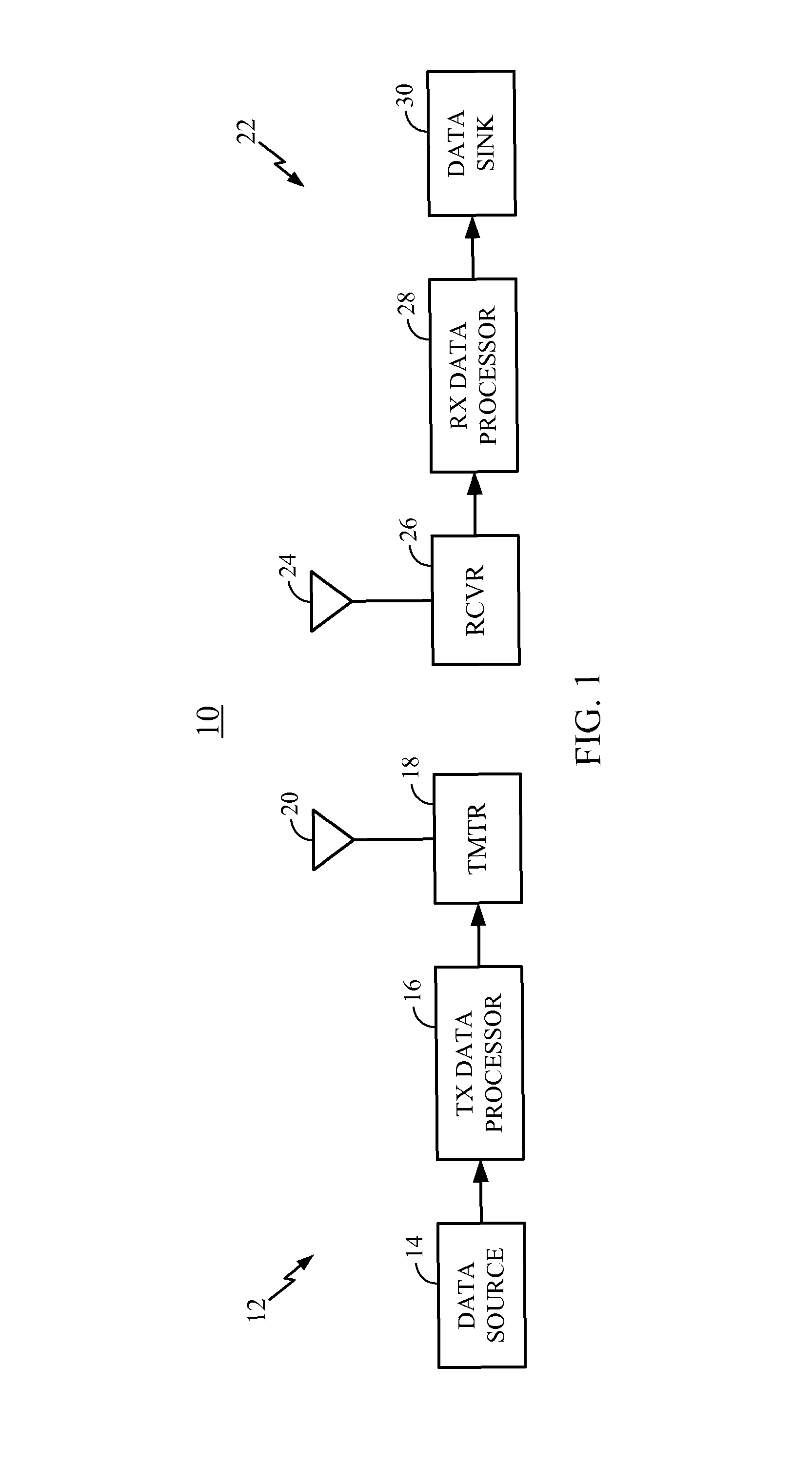

Channel estimation optimizing method for amplitude-limiting OFDM system

The disclosed optimization method separates data signal from pilot signal, which pass through sign extension portion and IFFT portion respectively. The data portion passes through clipping module then. Optimizing process module carries out optimizing process for data signal. The purpose of the optimizing process is to eliminate influence on the pilot signal by the clipping operation. FFT is carried out for data after self-adapting amplitude limiting in advance so as to convert signal in time domain into signal in frequency domain. Afterwards, the signal in frequency domain passes through module for limiting and eliminating amplitude of noise. Finally, the method superposes the portion of optimizing processed data signal with the portion of pilot signal, and outputs the superposed signal. Through iterative algorithm, the invention reduces influence on the pilot signal caused by amplitude-limited noise, raises precision for estimating channel so as to raise transmission performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Programmable logic devices with function-specific blocks

InactiveUS20100007379A1Input reduce and evenReduce and even usabilityComputation using non-contact making devicesSolid-state devicesGeneral purposeArithmetic logic unit

A programmable logic integrated circuit device has at least one function-specific circuit block (e.g., a parallel multiplier, a parallel barrel shifter, a parallel arithmetic logic unit, etc.) in addition to the usual multiple regions of programmable logic and the usual programmable interconnection circuit resources. To reduce the impact of use of the function-specific block (“FSB”) on the general purpose interconnection resources of the device, inputs and / or outputs of the FSB may be coupled relatively directly to a subset of the logic regions. In addition to conserving general purpose interconnect, resources of the logic regions to which the FSB are connected can be used by the FSB to reduce the amount of circuitry that must be dedicated to the FSB. If the FSB is a multiplier, additional features include facilitating accumulation of successive multiplier outputs (using either addition or subtraction and with sign extension if desired) and / or arithmetically combining the outputs of multiple multipliers.

Owner:ALTERA CORP

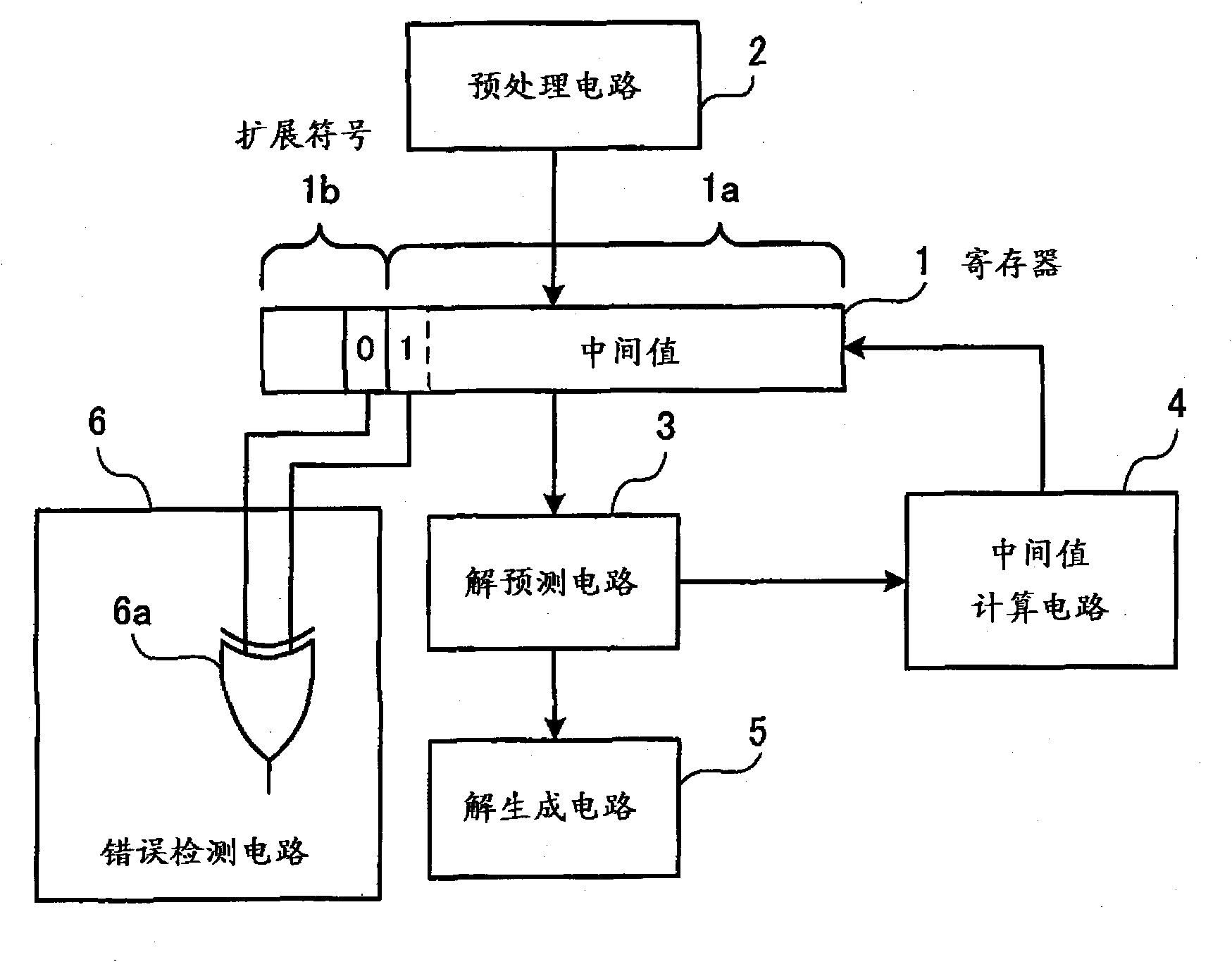

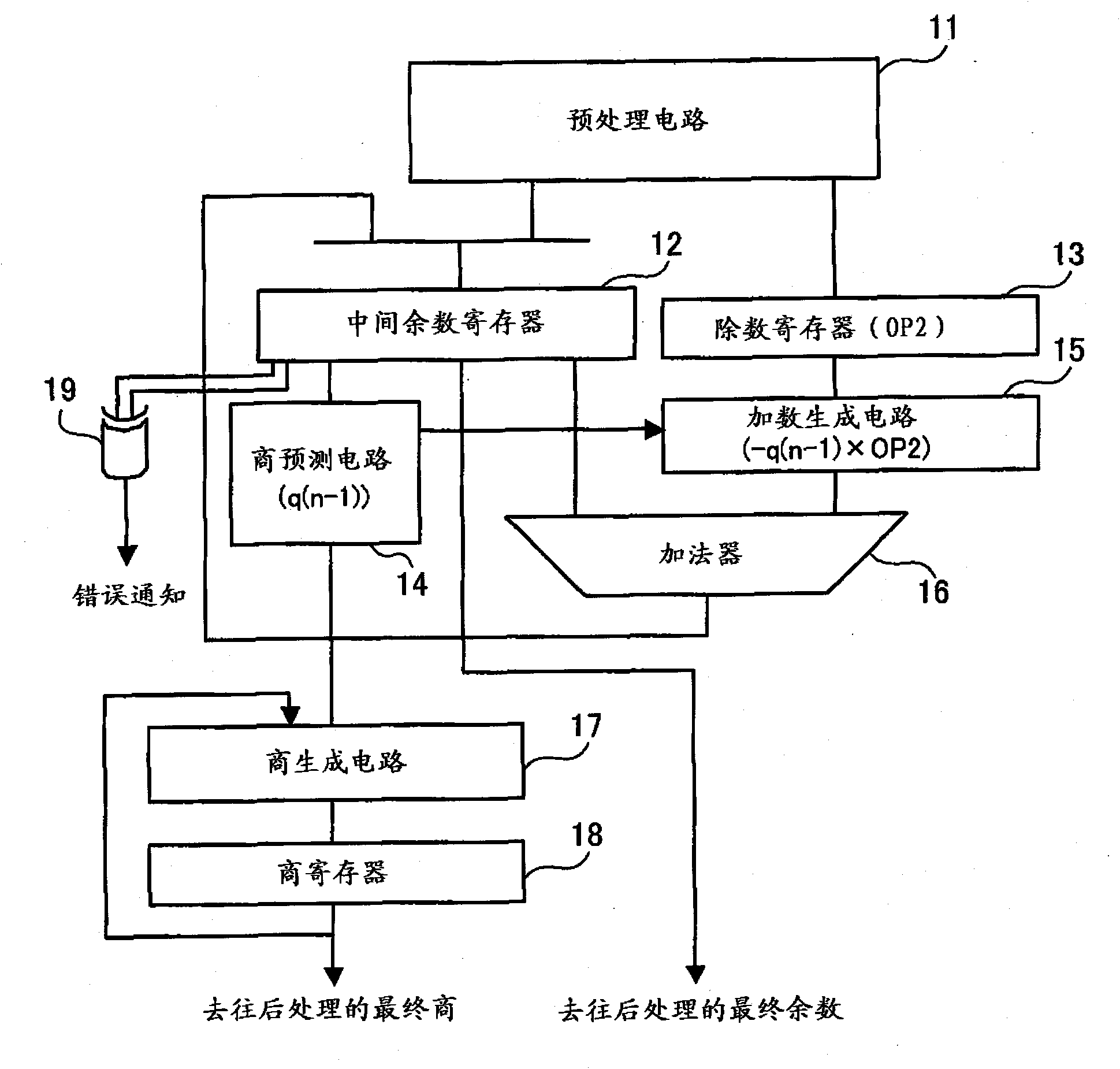

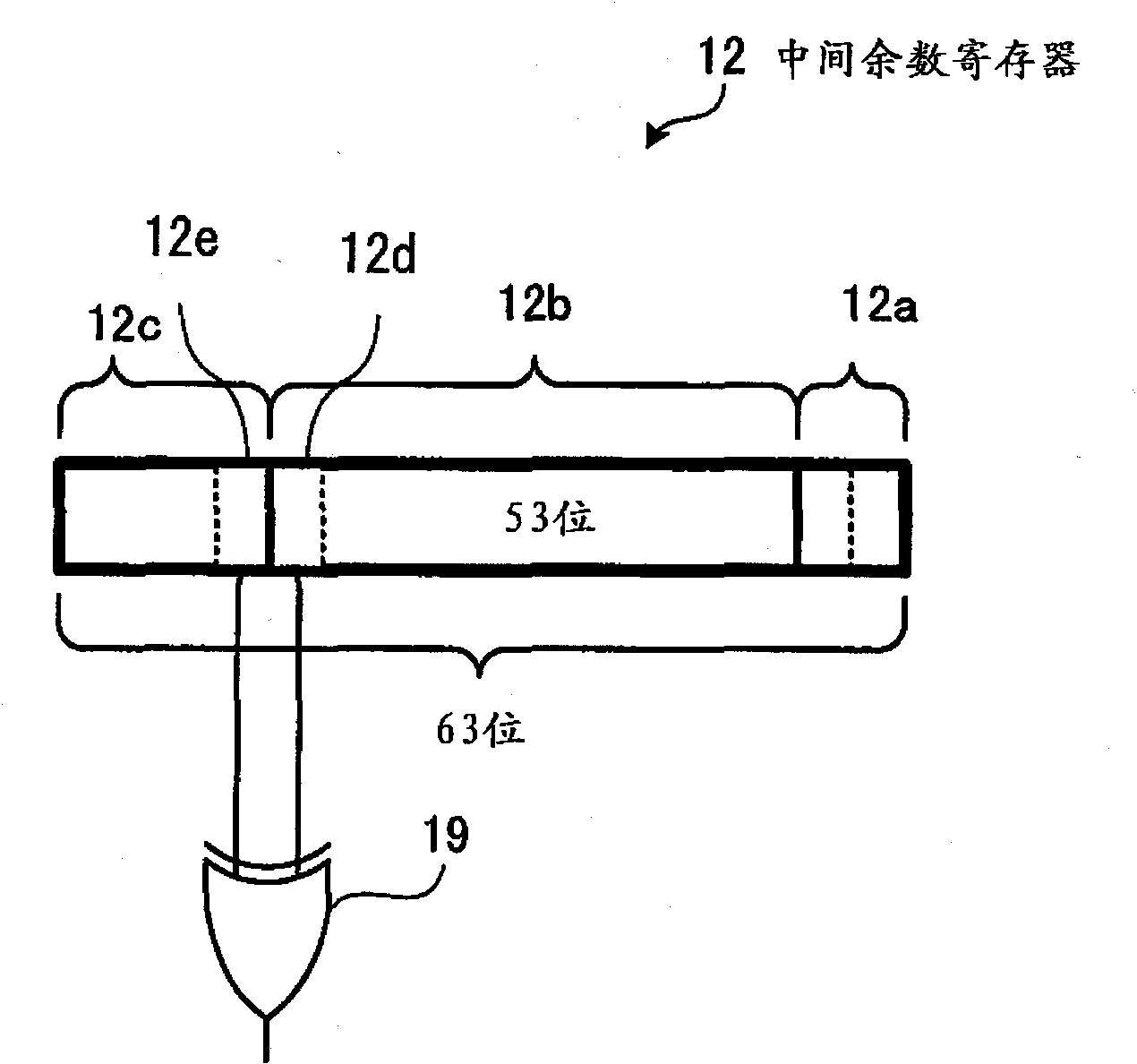

Arithmetic circuit, arithmetic processing device, and arithmetic processing method

InactiveCN101937379ADigital data processing detailsRedundant hardware error correctionComputer hardwareSign bit

In an arithmetic circuit, every time a numerical value is stored in a register, a partial solution is predicted on the basis of the numerical value, an intermediate value is generated by a predetermined calculation using one or more predicted partial solutions, an extended sign bit is appended to the intermediate value by sign extension, and the intermediate value to which the extended sign bit is appended is stored in the register. In addition, the solution is generated on the basis of the one or more partial solutions. A value of a sign bit constituting the intermediate value stored in the register is compared with a value of the extended sign bit stored in the register, and an error signal is outputted when the value of the sign bit is different from the value of the extended sign bit.

Owner:FUJITSU LTD

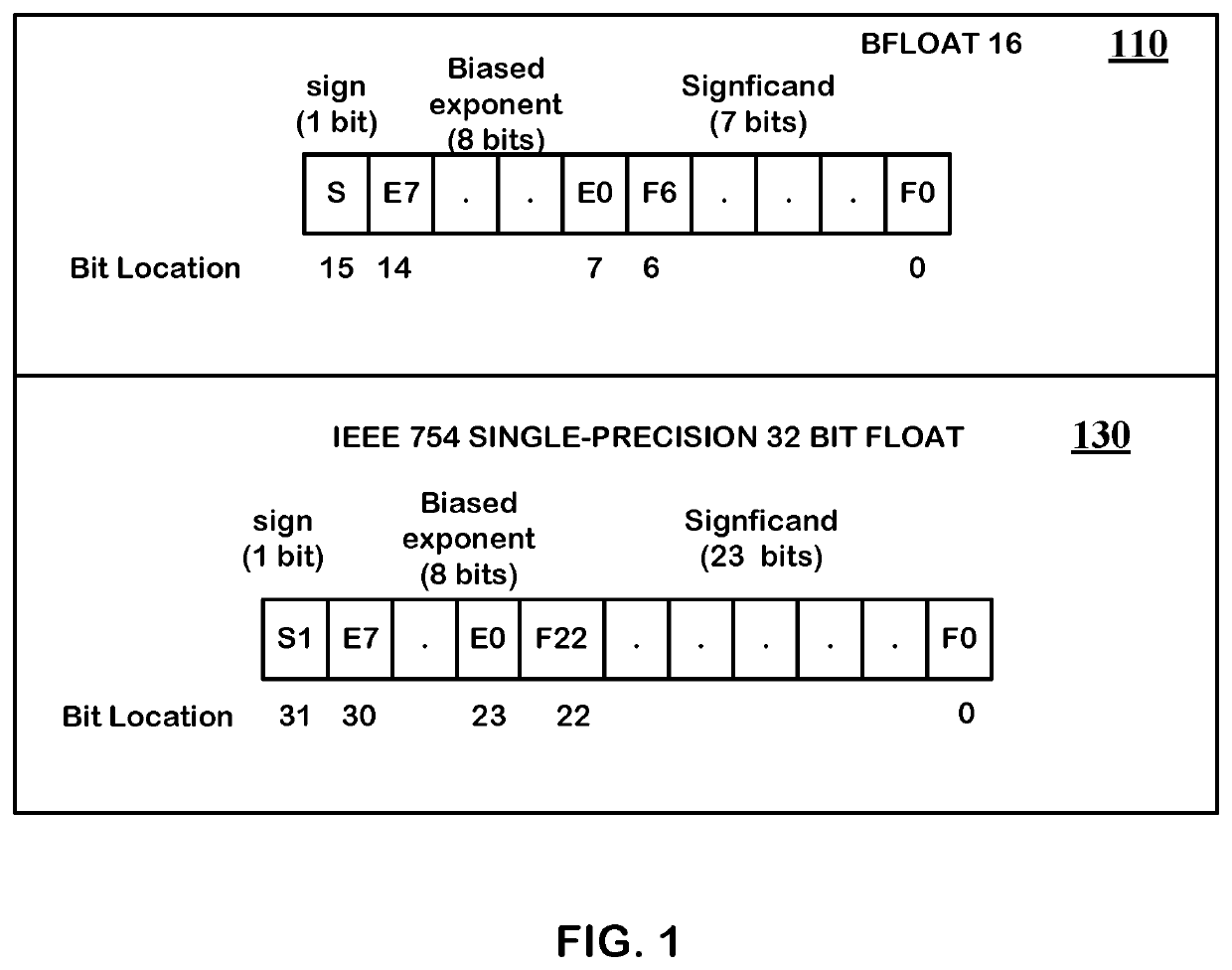

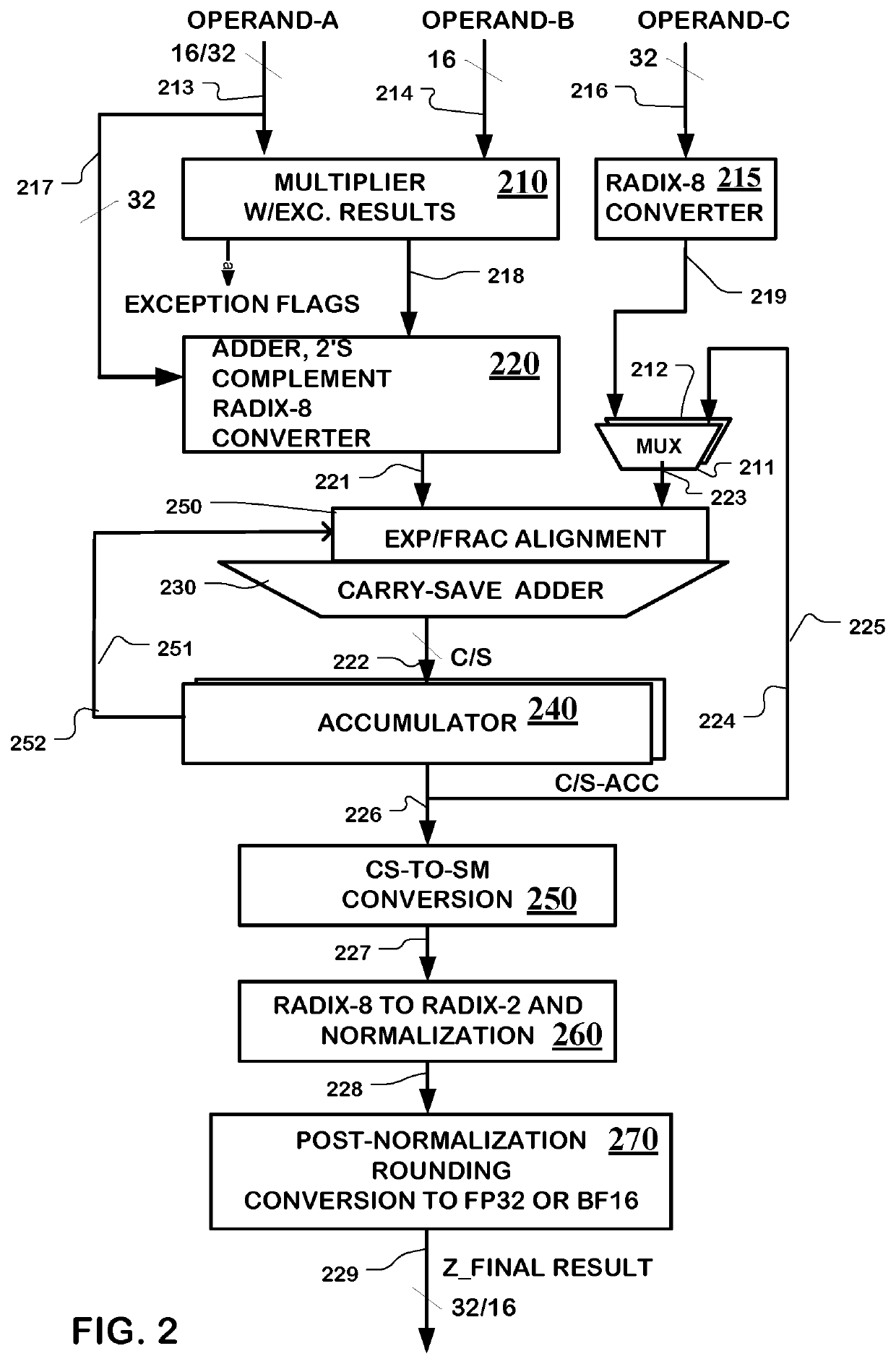

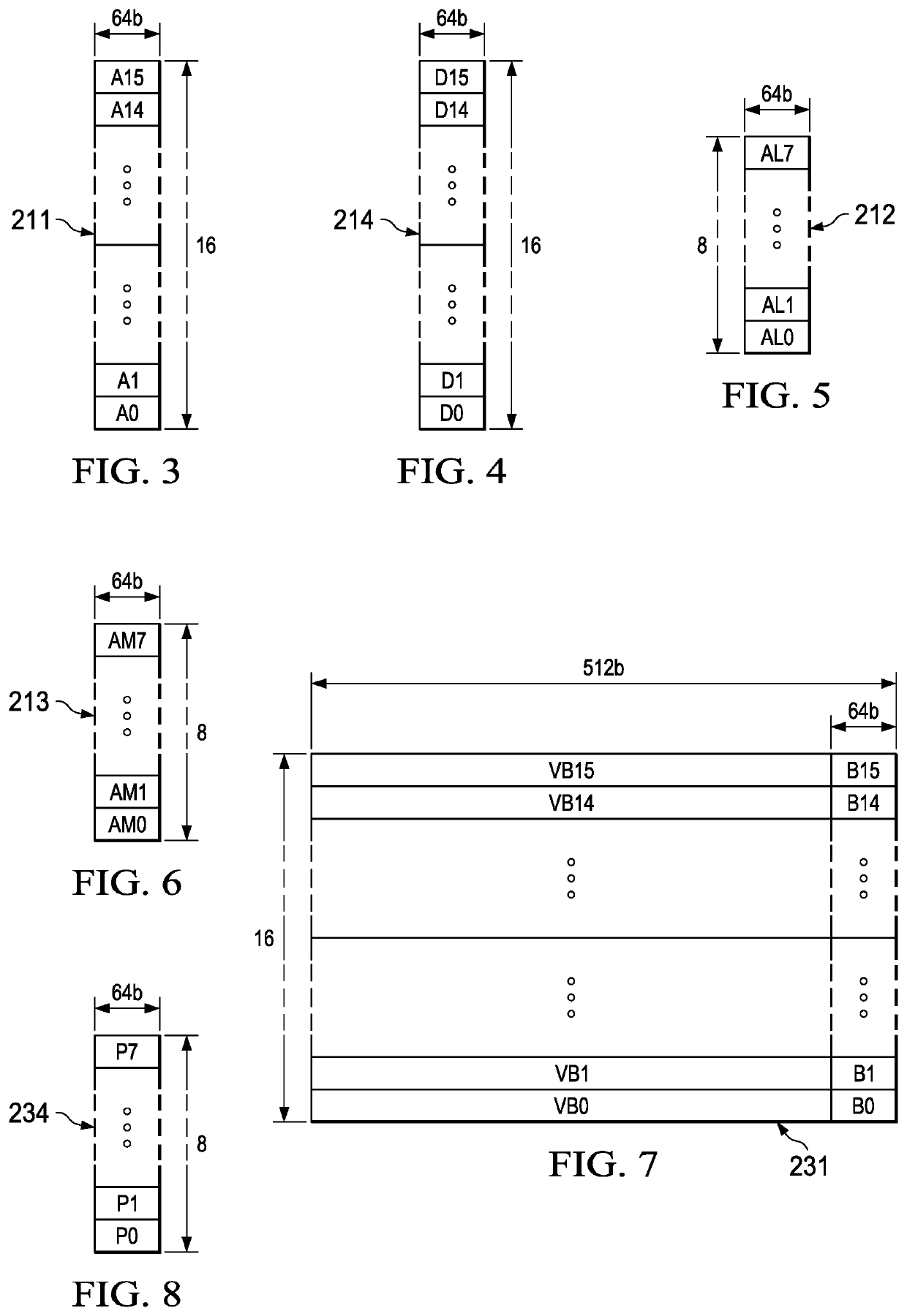

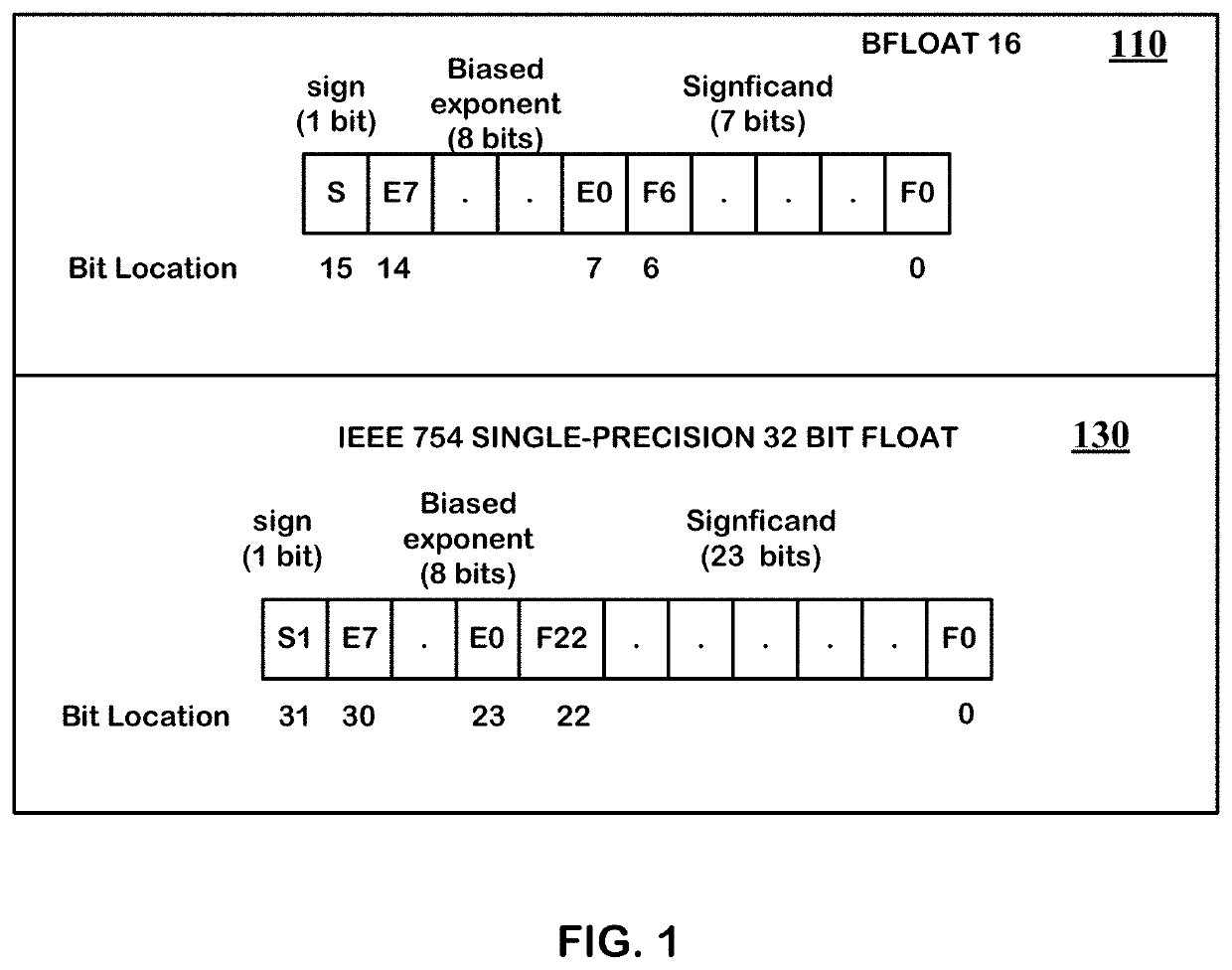

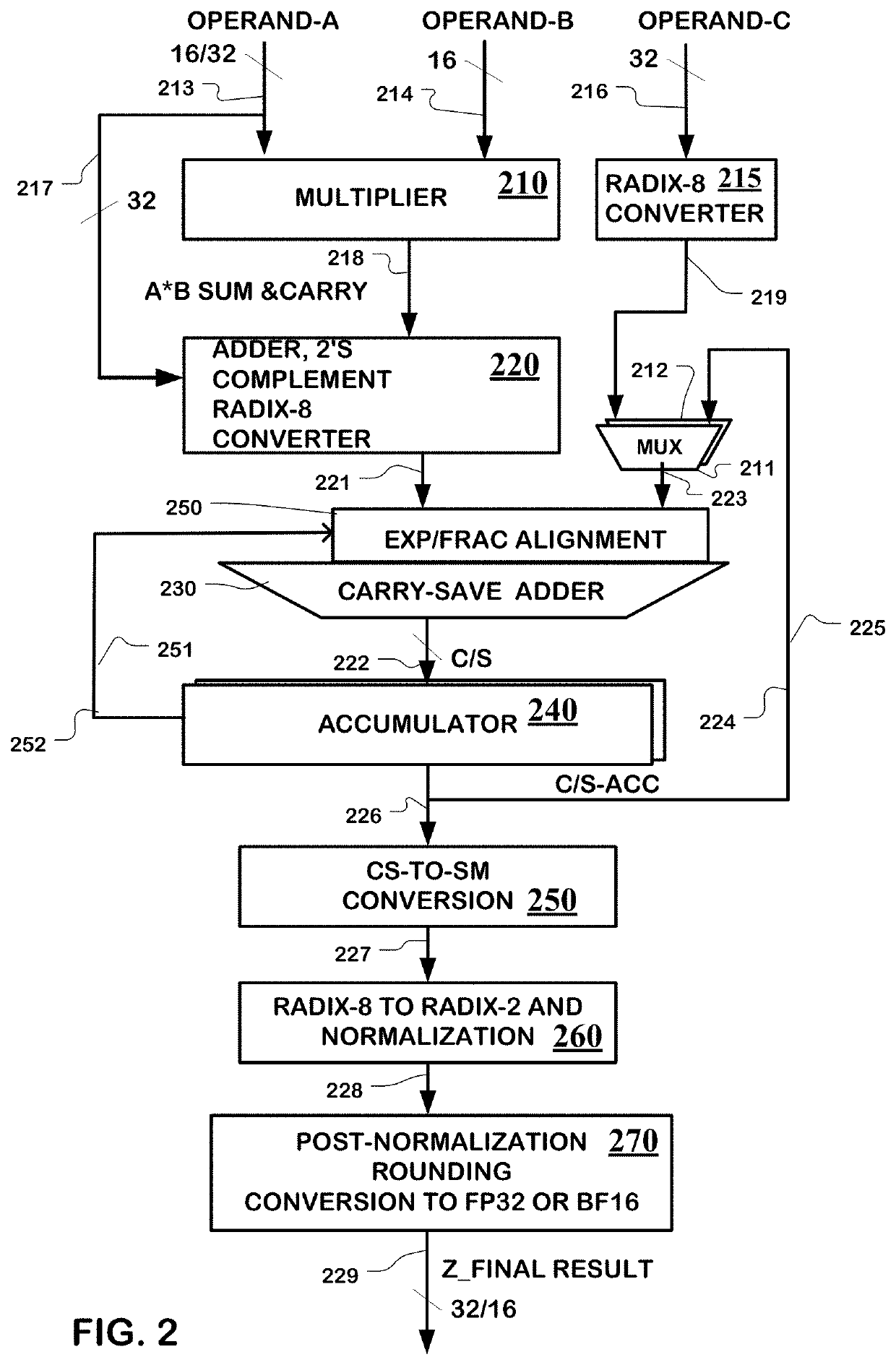

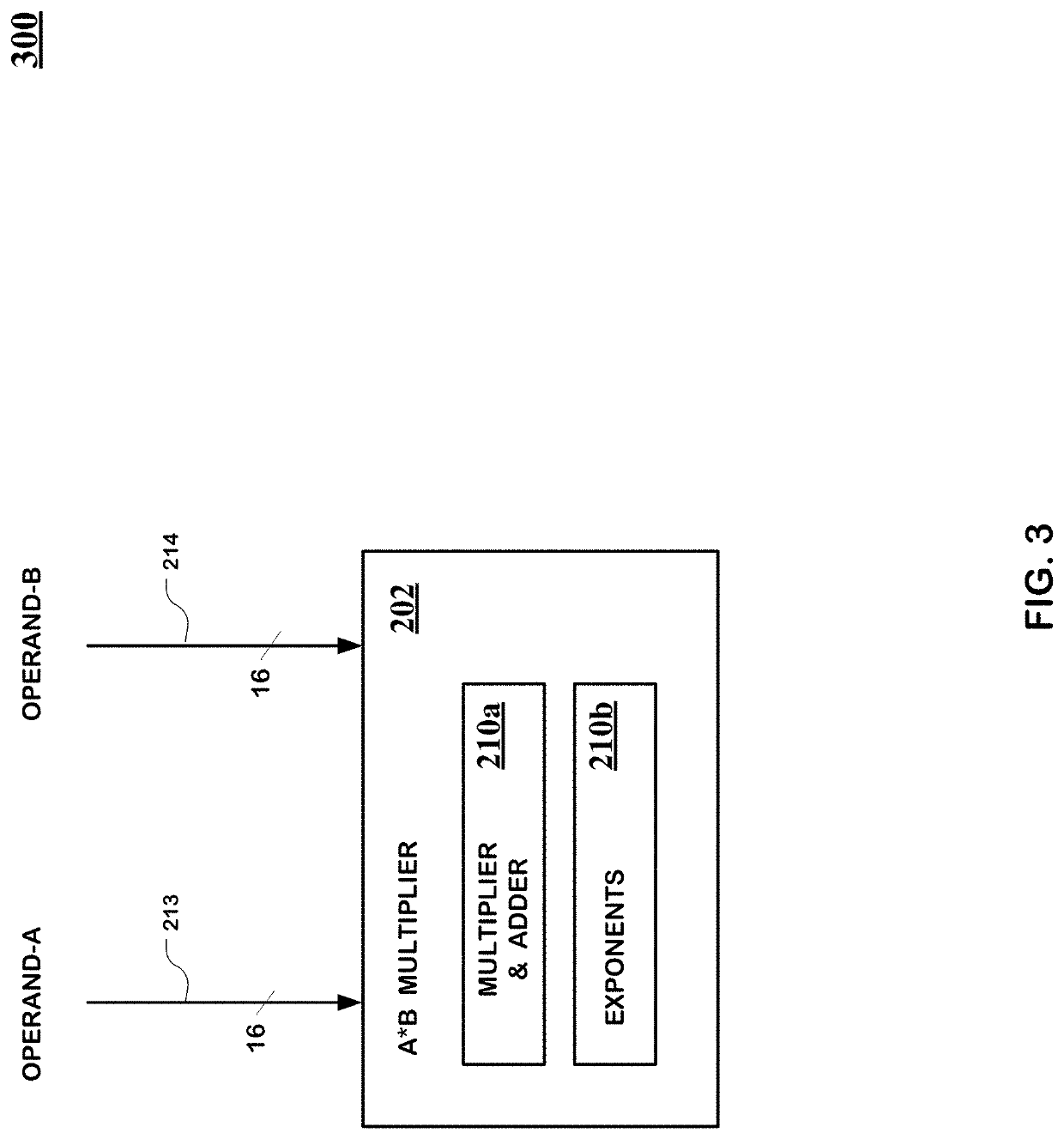

Floating point multiply-add, accumulate unit with exception processing

A Floating point Multiply-Add, Accumulate Unit, supporting BF16 format for Multiply-Accumulate operations, and FP32 Single-Precision Addition complying with the IEEE 754 Standard is described with exception handling. Operations including exception handling in a way that does not interfere with execution of data flow operations, overflow detection, zero detection and sign extension are adopted for 2's complement and Carry-Save format.

Owner:SAMBANOVA SYST INC

Streaming engine with short cut start instructions

ActiveUS11182200B2Program initiation/switchingError detection/correctionDigital dataParallel computing

A streaming engine employed in a digital data processor specifies a fixed read only data stream recalled memory. Streams are started by one of two types of stream start instructions. A stream start ordinary instruction specifies a register storing a stream start address and a register of storing a stream definition template which specifies stream parameters. A stream start short-cut instruction specifies a register storing a stream start address and an implied stream definition template. A functional unit is responsive to a stream operand instruction to receive at least one operand from a stream head register. The stream template supports plural nested loops with short-cut start instructions limited to a single loop. The stream template supports data element promotion to larger data element size with sign extension or zero extension. A set of allowed stream short-cut start instructions includes various data sizes and promotion factors.

Owner:TEXAS INSTR INC

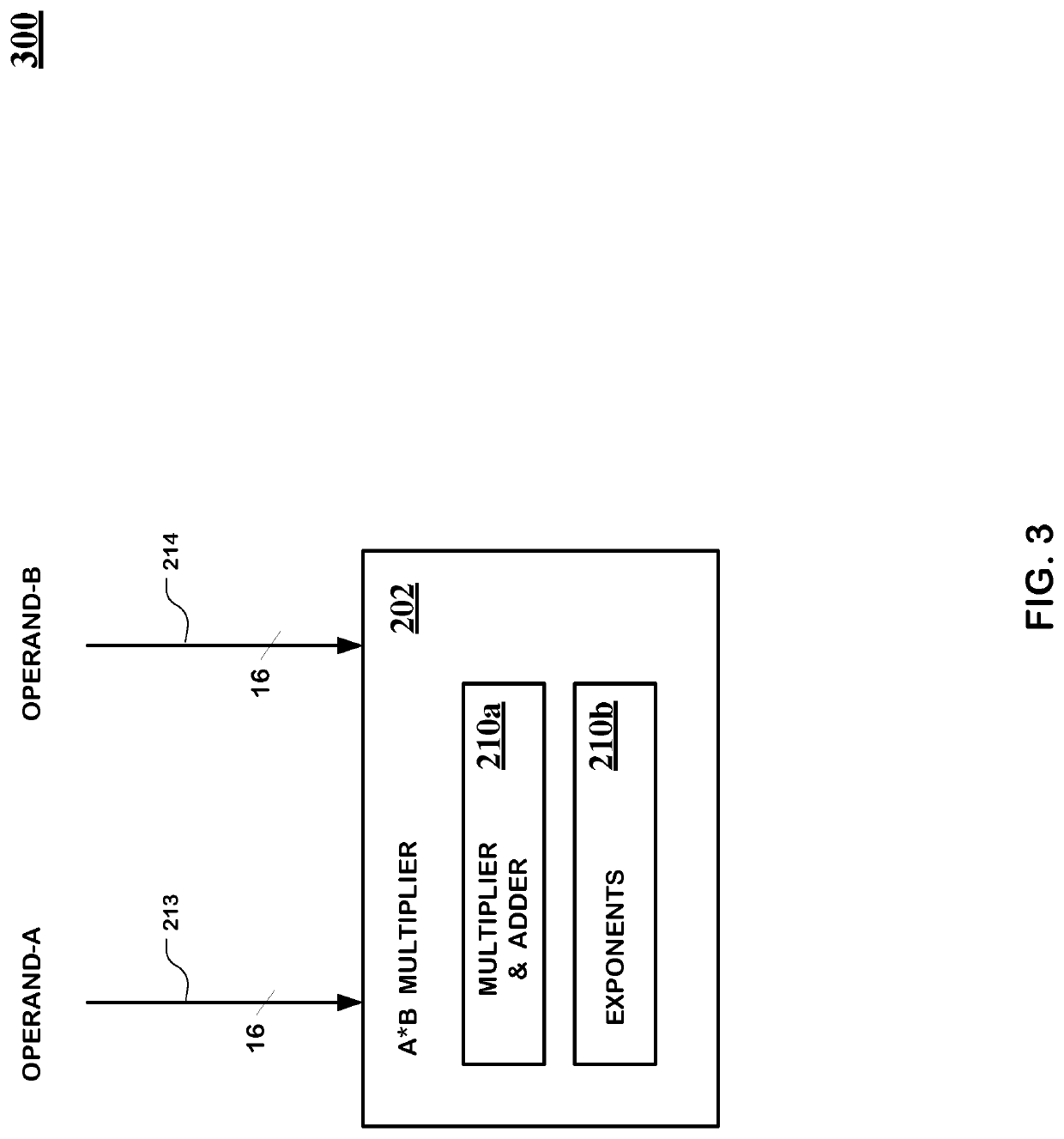

Floating point multiply-add, accumulate unit with combined alignment circuits

Floating point Multiply-Add, Accumulate Unit, supporting BF16 format for Multiply-Accumulate operations, and FP32 Single-Precision Addition complying with the IEEE 754 Standard. The Multiply-Accumulate unit uses higher radix and longer internal 2's complement significand representation to facilitate precision as well as comparison and operation with negative numbers. The addition can be performed using Carry-Save format to avoid long carry propagation and speed up the operation. The circuit uses early exponent comparison to shorten the accumulate pipeline stage. Operations including overflow detection, zero detection and sign extension are adopted for 2s complement and Carry-Save format.

Owner:SAMBANOVA SYST INC

Channel estimation optimizing method for amplitude-limiting OFDM system

The disclosed optimization method separates data signal from pilot signal, which pass through sign extension portion and IFFT portion respectively. The data portion passes through clipping module then. Optimizing process module carries out optimizing process for data signal. The purpose of the optimizing process is to eliminate influence on the pilot signal by the clipping operation. FFT is carried out for data after self-adapting amplitude limiting in advance so as to convert signal in time domain into signal in frequency domain. Afterwards, the signal in frequency domain passes through module for limiting and eliminating amplitude of noise. Finally, the method superposes the portion of optimizing processed data signal with the portion of pilot signal, and outputs the superposed signal. Through iterative algorithm, the invention reduces influence on the pilot signal caused by amplitude-limited noise, raises precision for estimating channel so as to raise transmission performance.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

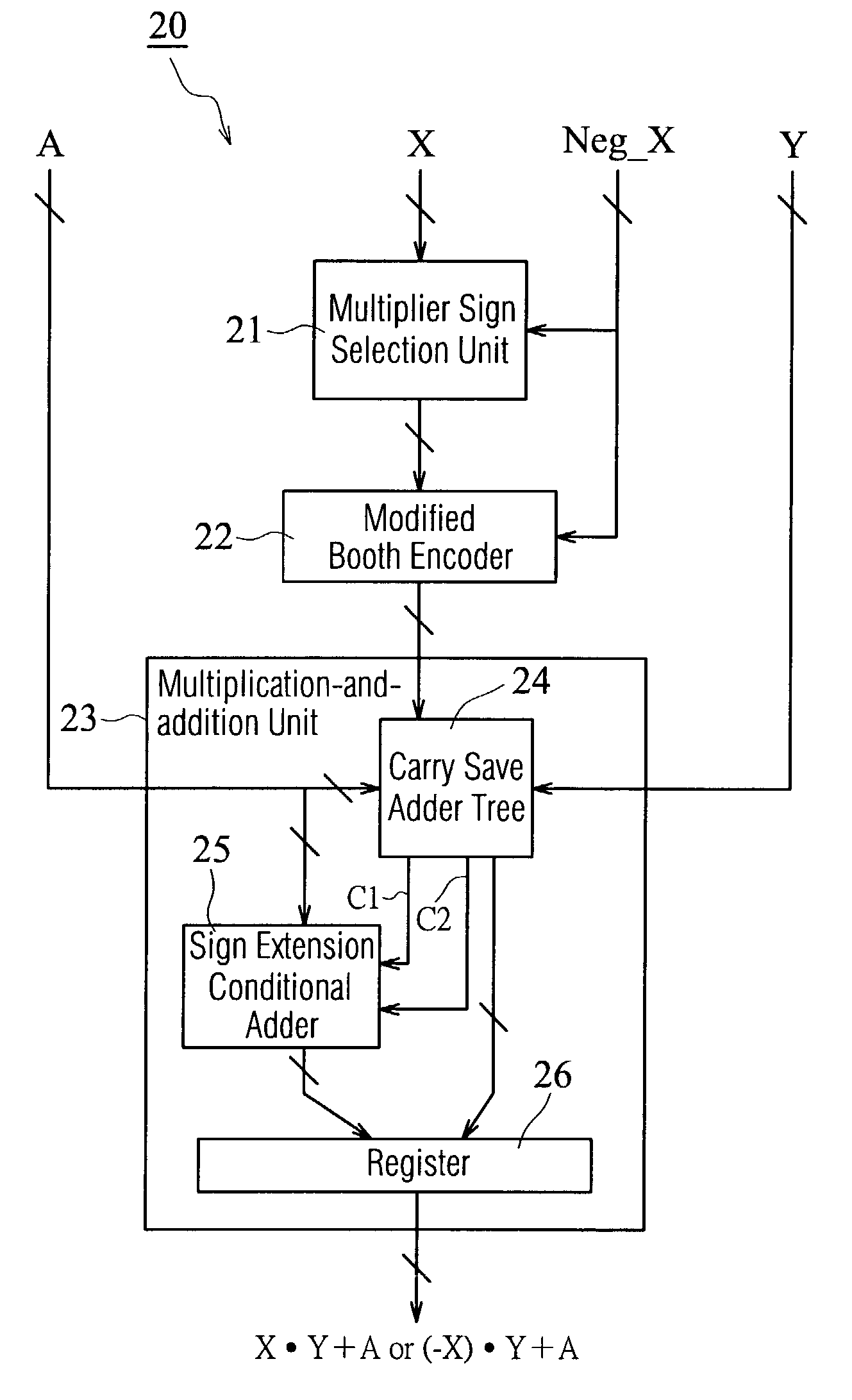

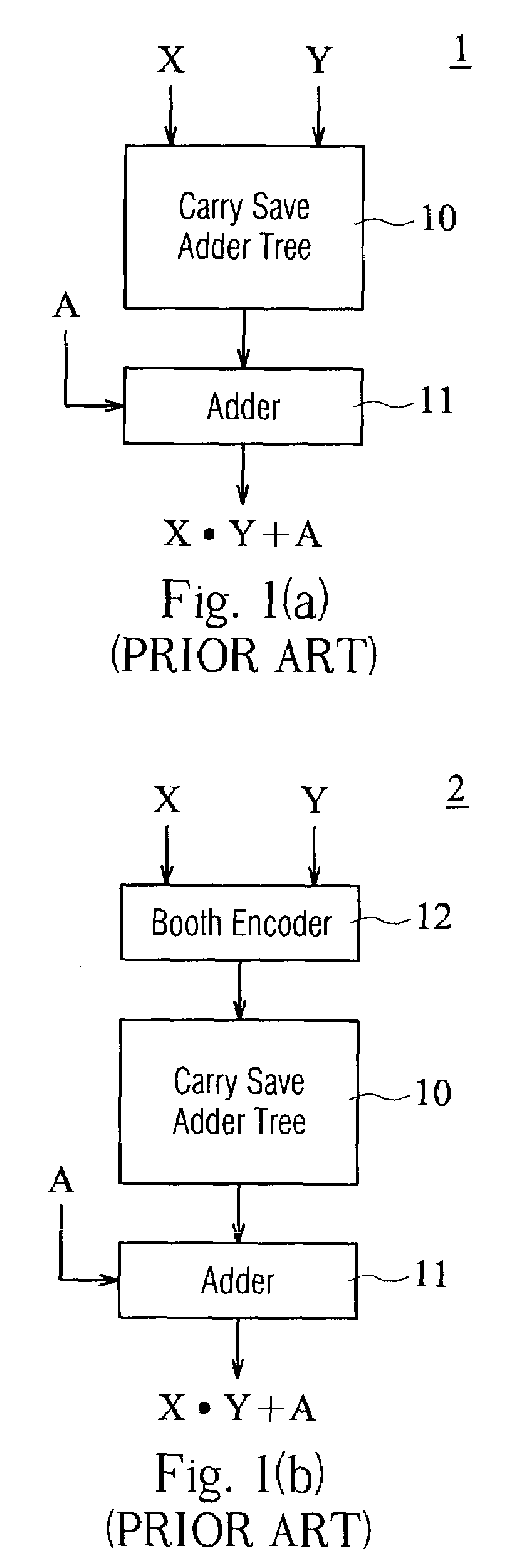

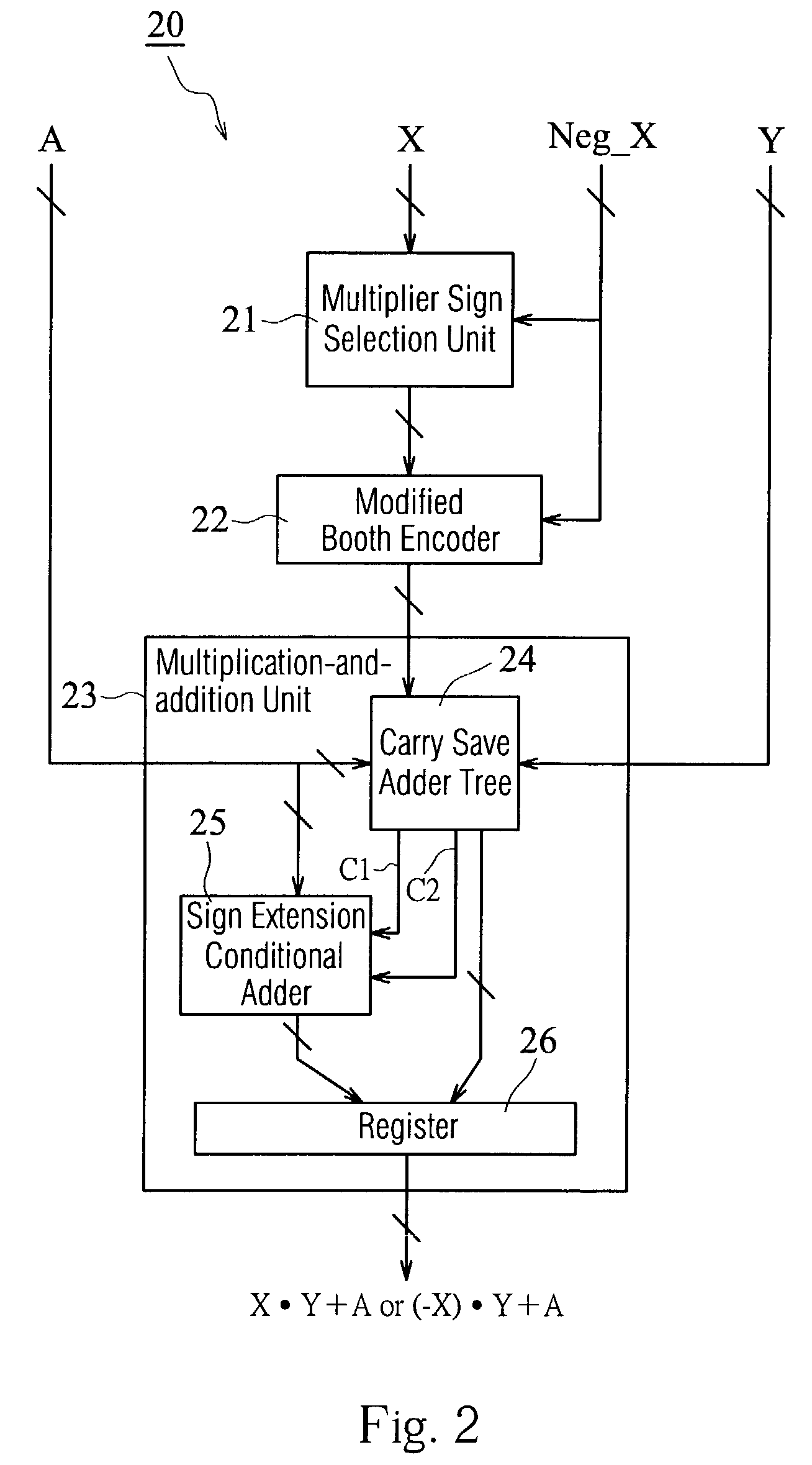

Multiply accumulator for two N bit multipliers and an M bit addend

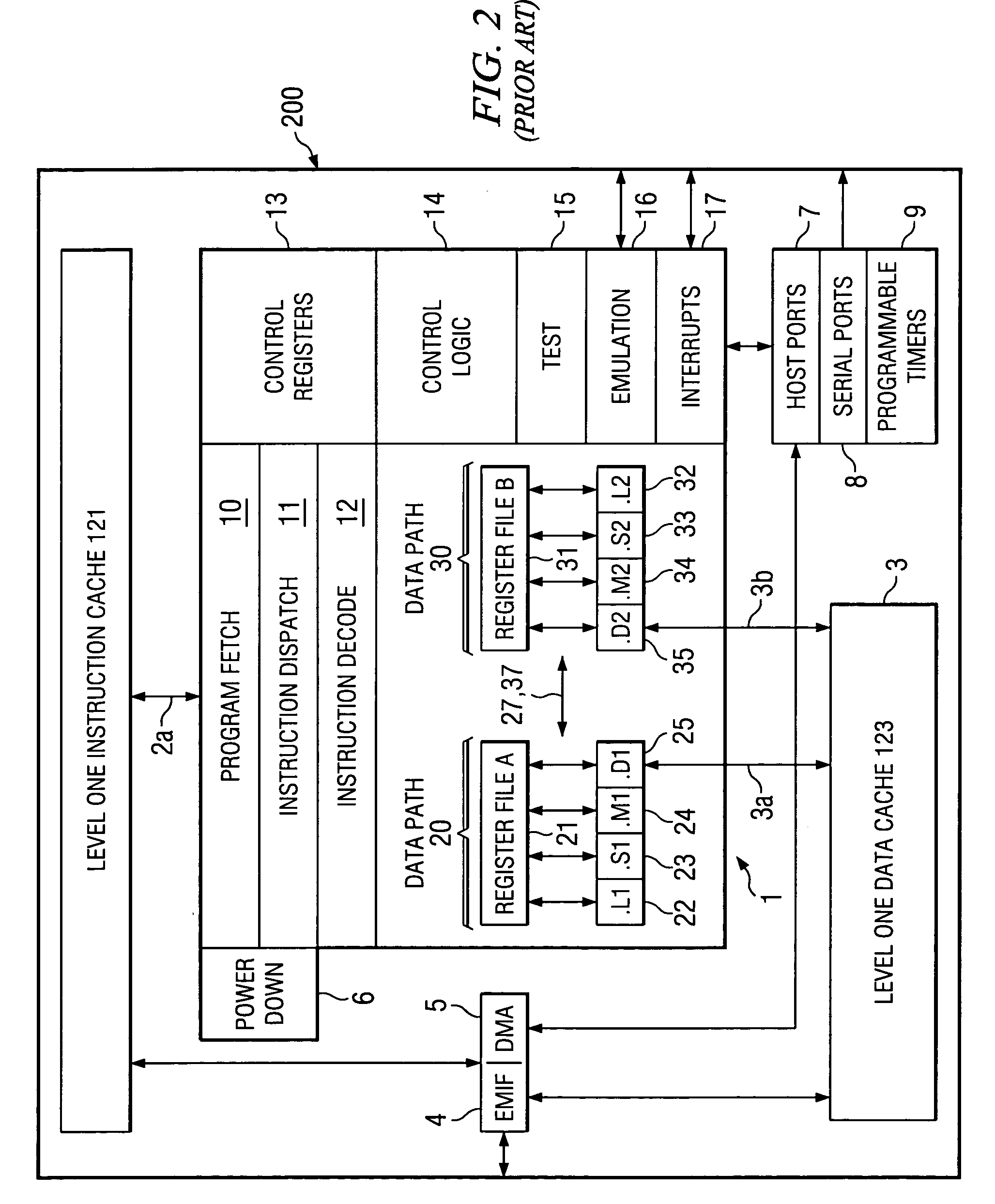

InactiveUS7043517B2Guaranteed high speed operationComputation using non-contact making devicesDigital computer detailsBinary multiplierBooth encoding

A multiply accumulator performs a multiplication-and-addition operation for a first multiplier with N bits, a second multiplier with N bits, and an addend with M bits, wherein M is larger than 2N. The multiply accumulator includes a modified Booth encoder and a multiplication-and-addition unit. The modified Booth encoder performs a Booth encoding to either the first multiplier or its bit inversion by supplementing a multiplier sign bit behind a least significant bit of either the first multiplier or its bit inversion. The multiplication-and-addition unit includes a carry save adder tree and a sign extension adder and achieves a high speed of the multiplication-and-addition operation by simultaneously performing the multiplication and addition.

Owner:FARADAY TECH CORP

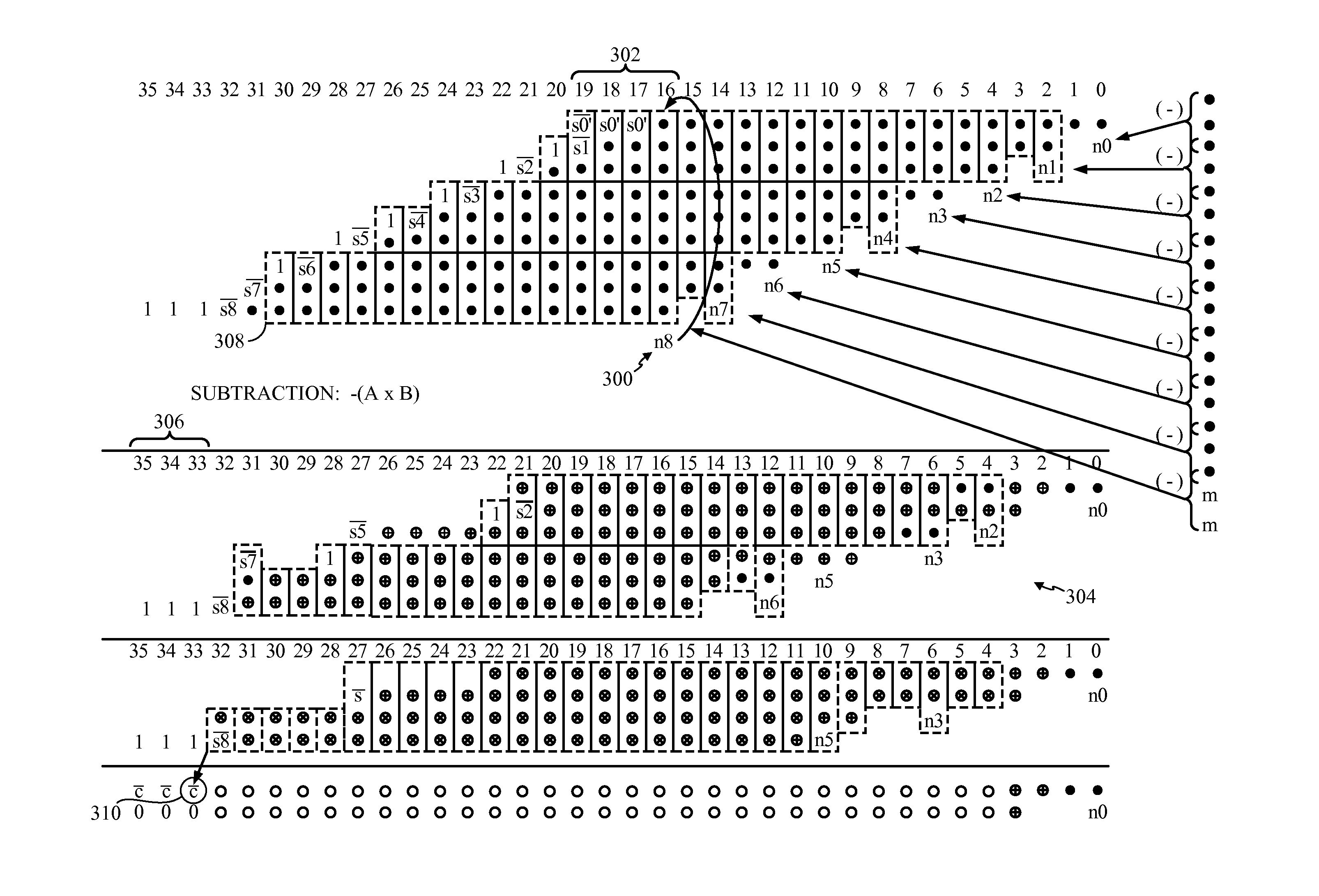

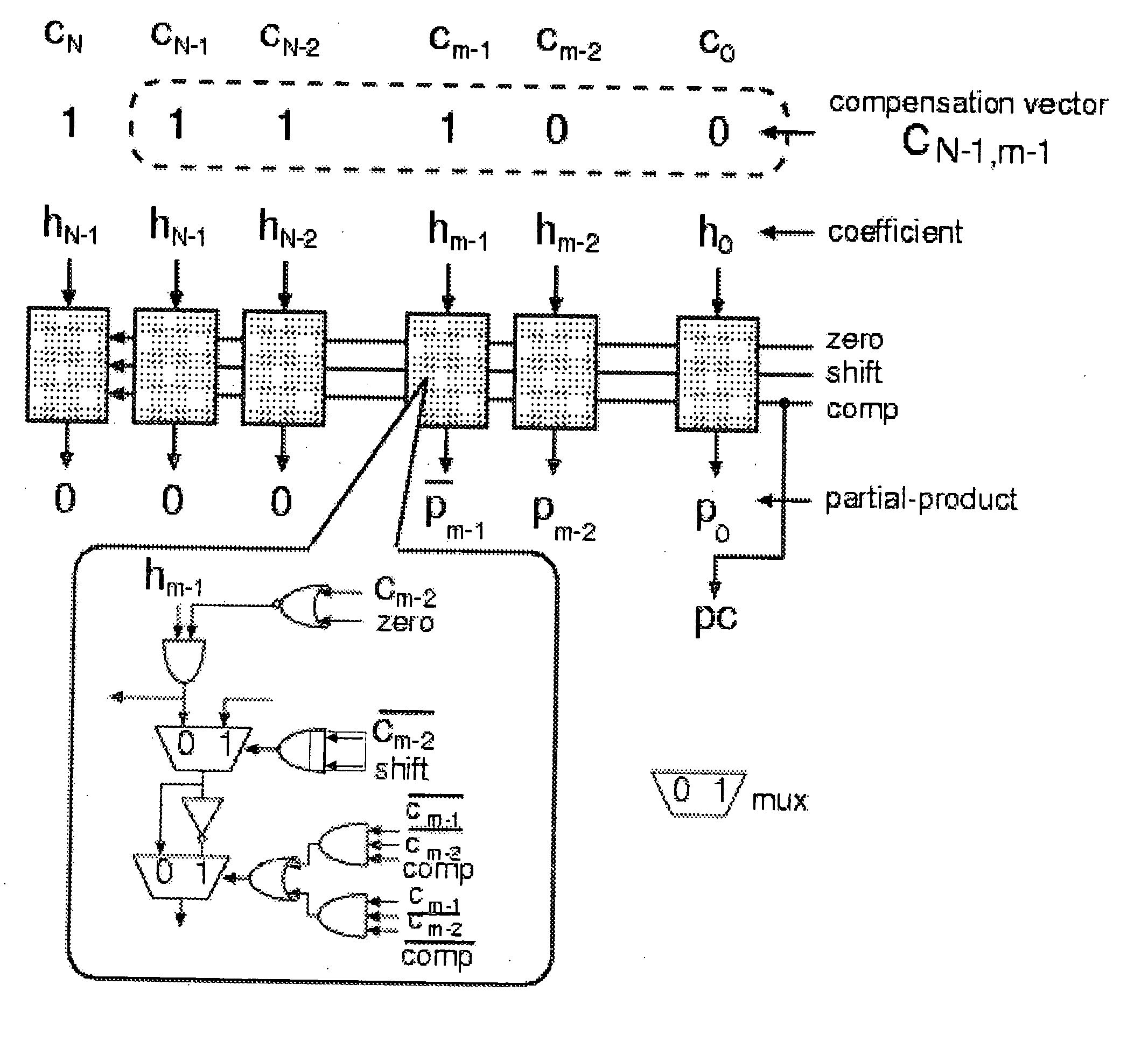

Power-efficient sign extension for booth multiplication methods and systems

InactiveUS7797366B2Improve operationIncrease usageComputation using non-contact making devicesPower efficientSign bit

Techniques for the design and use of a digital signal processor, including processing transmissions in a communications (e.g., code division multiple access) system. Power-efficient sign extension for Booth multiplication processes involves applying a sign bit in a Booth multiplication tree. The sign bit allows the Booth multiplication process to perform a sign extension step. This further involves one-extending a predetermined partial product row of the Booth multiplication tree using a sign bit for preserving the correct sign of the predetermined partial product row. The process and system resolve the signal value of the sign bit by generating a sign-extension bit in the Booth multiplication tree. The sign-extension bit is positioned in a carry-out column to extend the product of the Booth multiplication process. Then, the method and system form a final product from the Booth multiplication tree by adding the carry-out value to the sign bit positioned at least a predetermined column of the Booth multiplication tree. The result is to effectively extend the sum component of the final product with the sign and zero-extending the carry component of the final product.

Owner:QUALCOMM INC

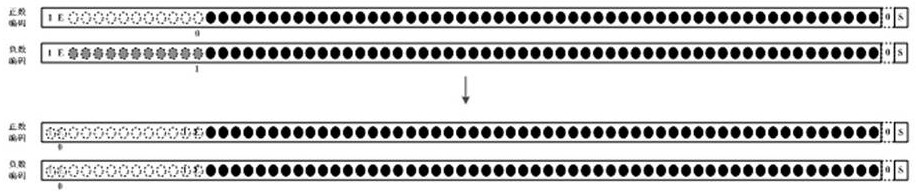

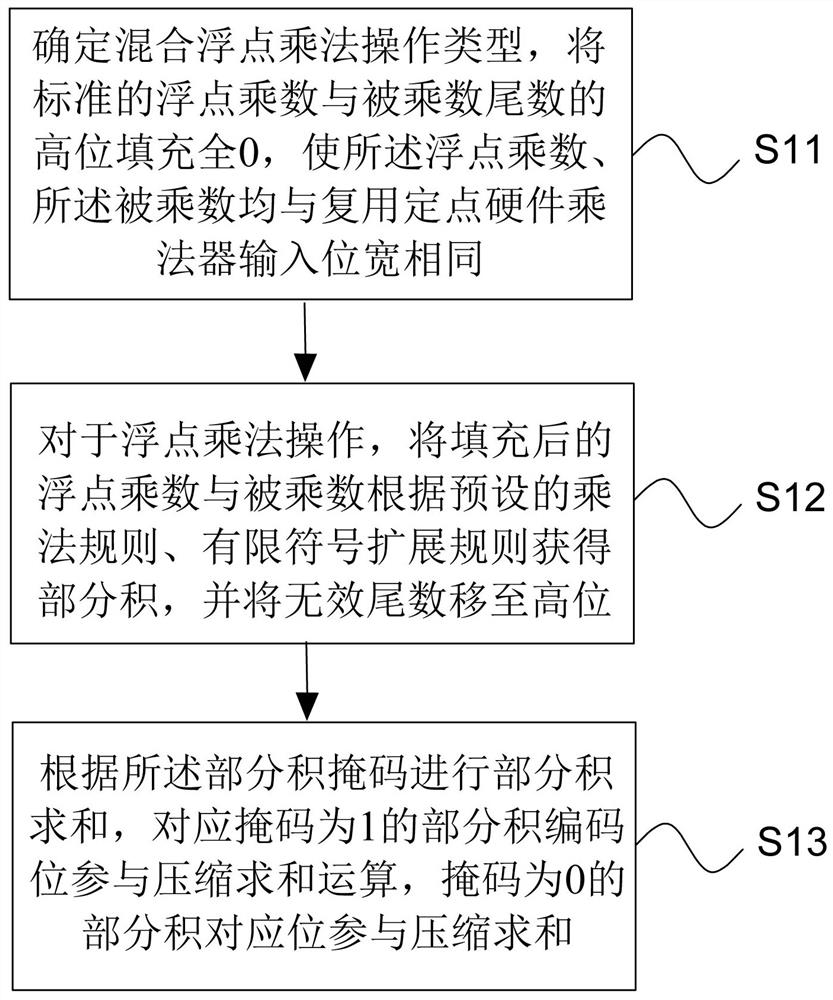

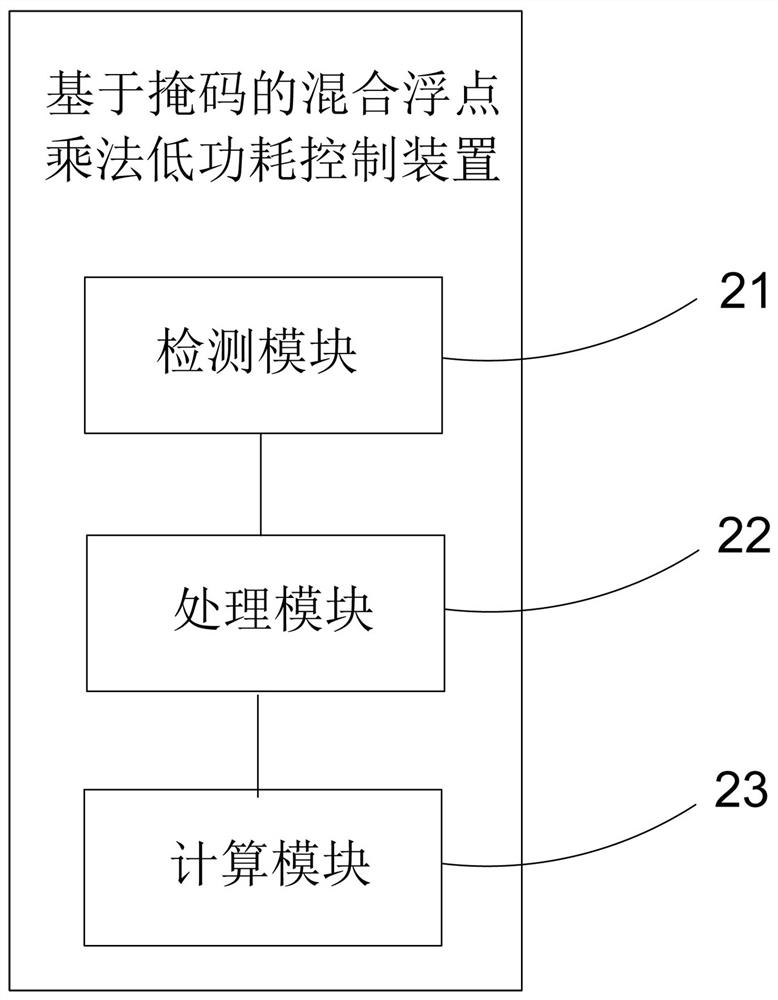

A mask-based hybrid floating-point multiplication low-power control method and device

ActiveCN110727412BReduce overheadSimple implementation logicDigital data processing detailsBinary multiplierFloating point multiplication

The invention discloses a mask-based mixed floating point multiplication low power consumption control method. Including the hardware to automatically determine the mixed floating-point multiplication operation type, and fill the high bits of the standard floating-point multiplier and the multiplicand mantissa with all 0s, so that the floating-point multiplier and the multiplicand can be combined with the multiplexed fixed-point hardware multiplier The input bit width is the same; for the floating-point multiplication operation, the filled floating-point multiplier and the multiplicand are obtained according to the preset multiplication coding rules and sign extension rules to obtain partial products, and the invalid mantissa is moved to the high bit, and the mask control is used The invalid mantissa does not participate in the partial product compression sum operation to save logic power consumption. The invention also discloses a mask-based mixed floating-point multiplication low-power control device. The invention supports the multiplexing of fixed-point multiplication hardware to realize the low power consumption control of floating-point multiplication, the hardware automatically detects floating-point multiplication operations, and controls the high-order expansion bit coding based on the mask, which has the advantages of low hardware overhead, easy logic implementation, and simple power consumption control. .

Owner:JIANGNAN INST OF COMPUTING TECH

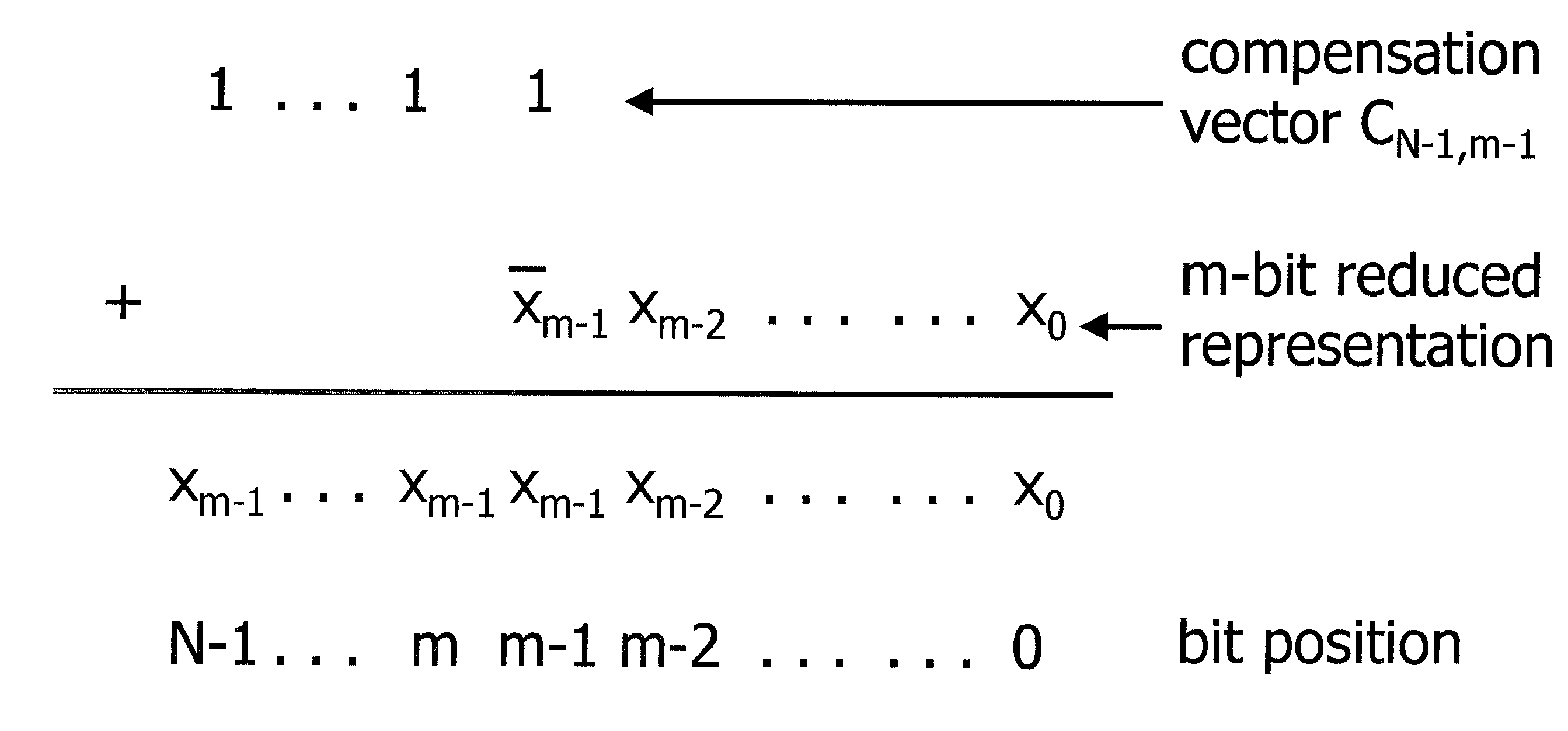

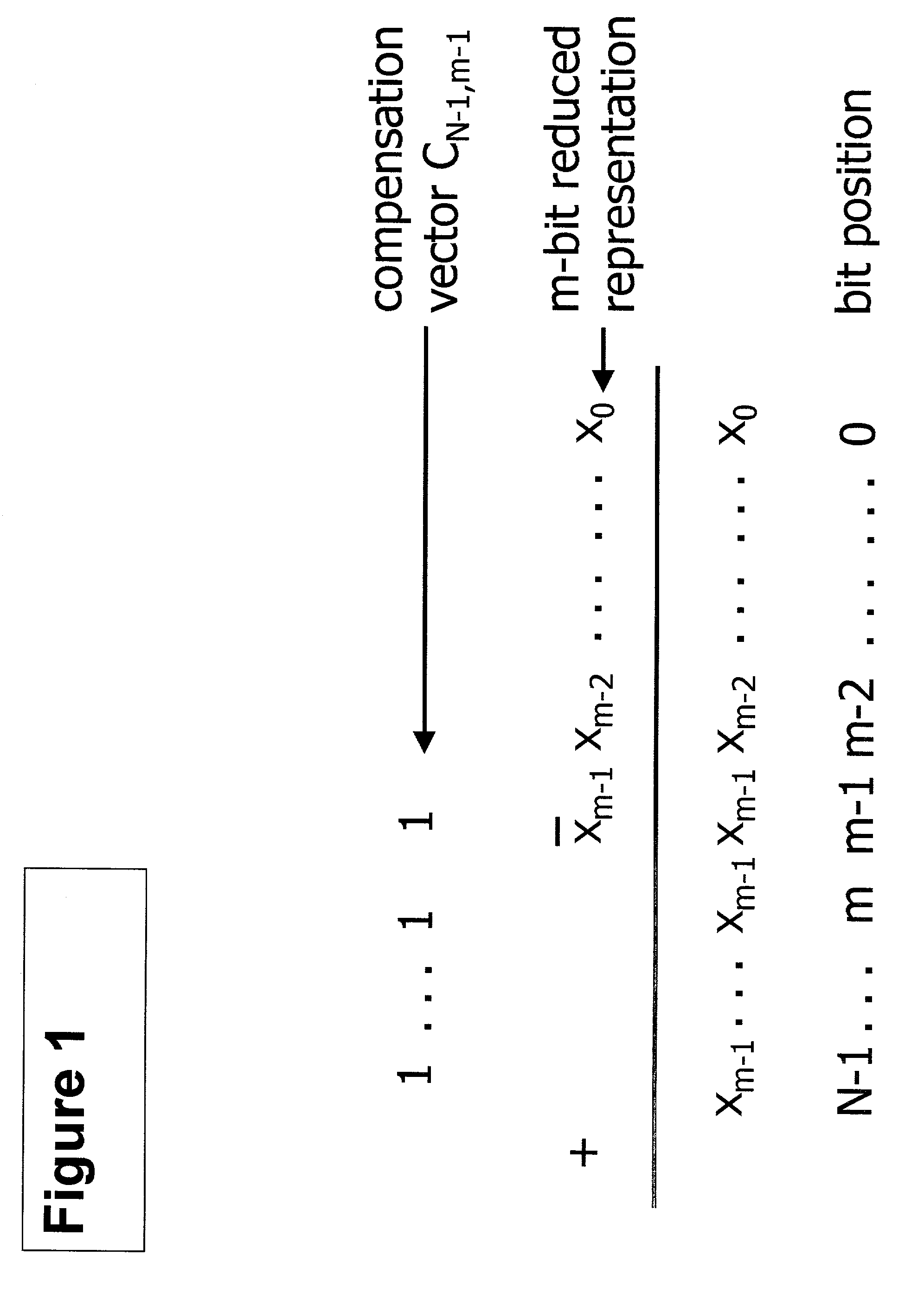

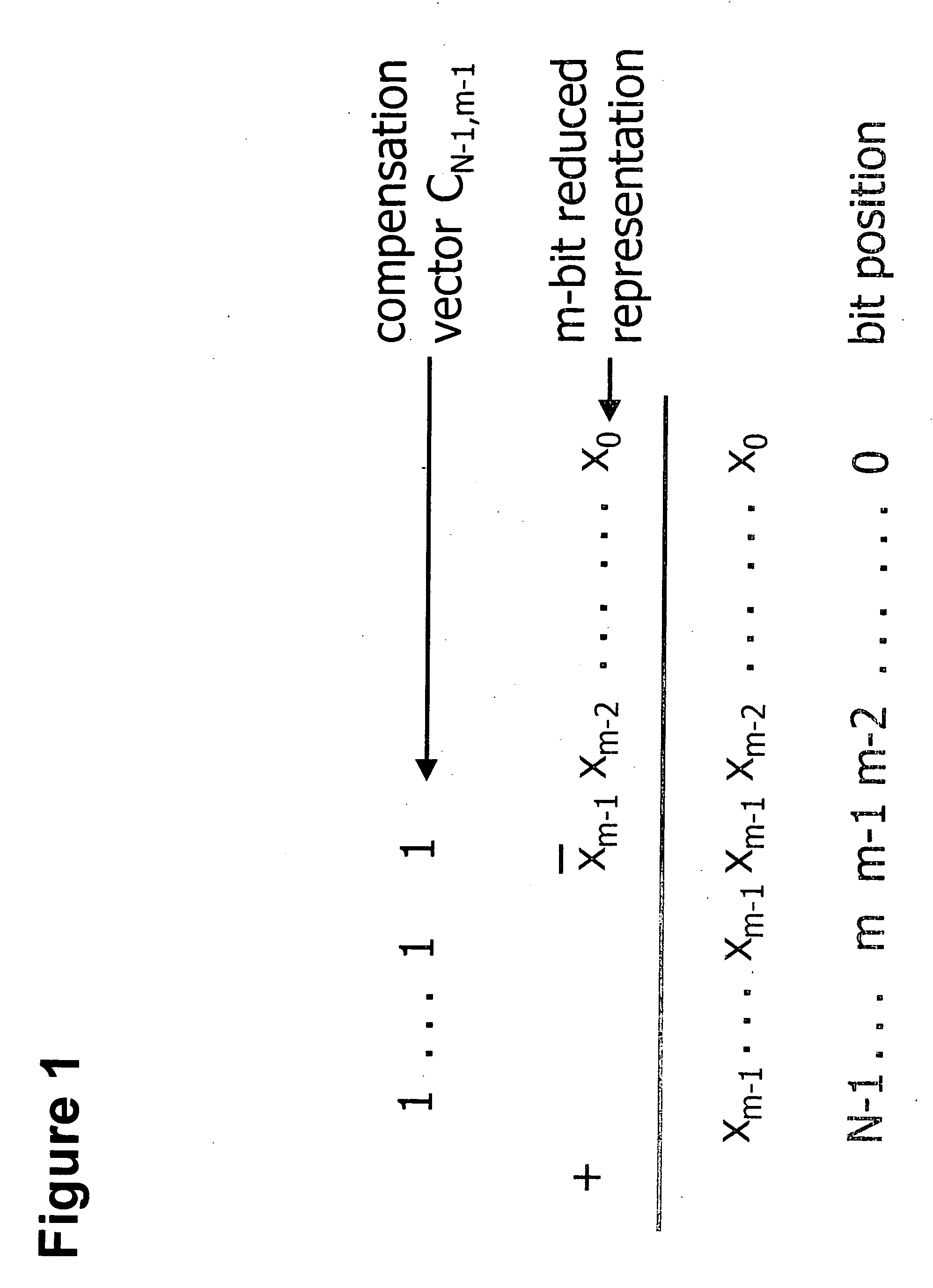

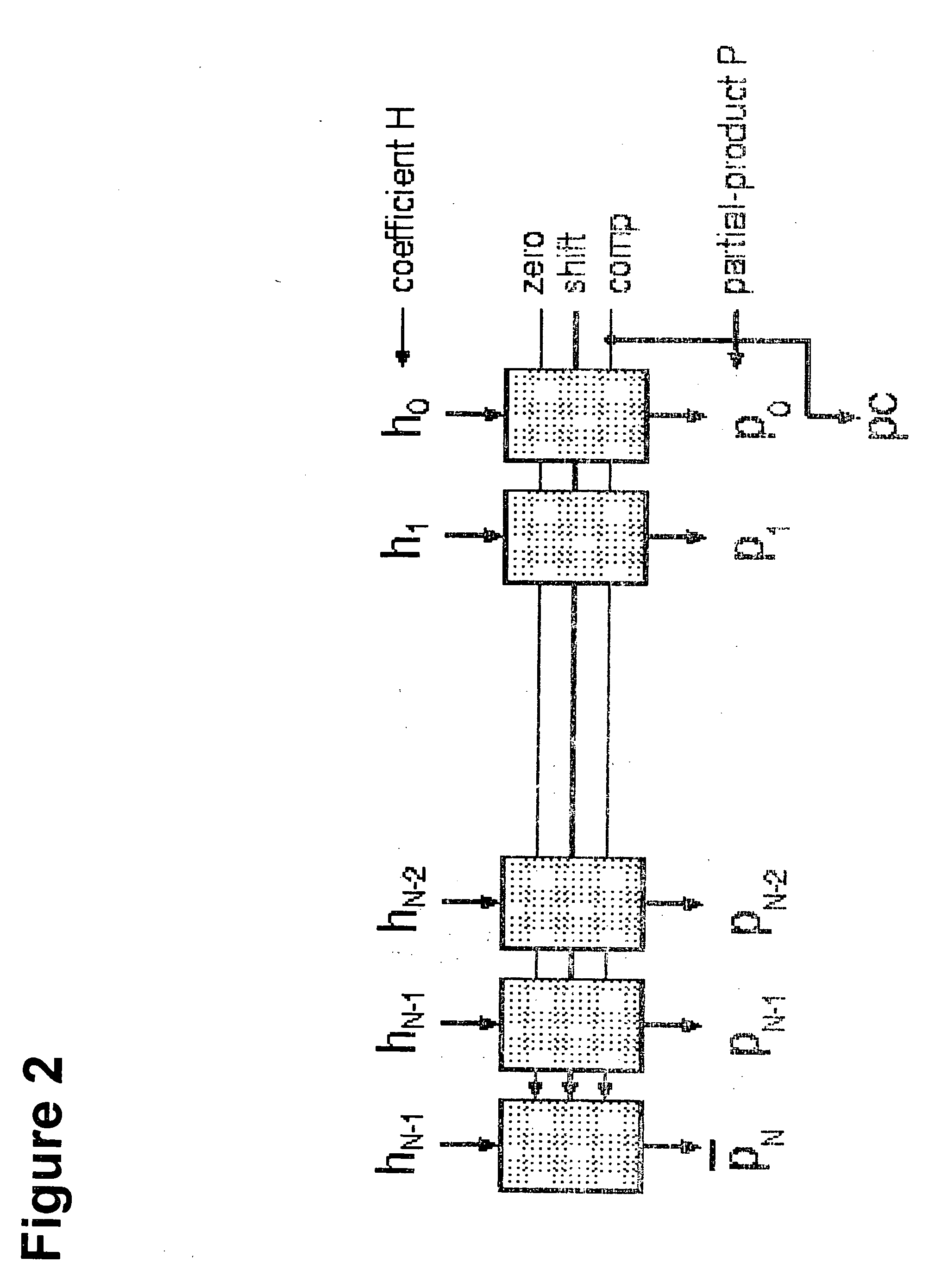

Low power vector summation method and apparatus

InactiveUS20060143259A1Reduce power consumptionHigh switching activity is avoidedDigital technique networkDigital computer detailsConstant errorMaximum magnitude

An arrangement is provided for using 2's complement arithmetic without the high switching activity of the prior art. In particular, the invention operates to exploit the sign-extension property of a 2's complement number. A reduced representation for 2's complement numbers is provided to avoid sign-extension and the switching of sign-extension bits. The maximum magnitude of a 2's complement number is detected and its reduced representation is dynamically generated to represent the signal. A constant error introduced by the reduced representation is also dynamically compensated.

Owner:INTEL CORP

Symbol extension method and structure of multipliers

ActiveCN100405288CNo critical path addedComputation using non-contact making devicesBinary multiplierComputer architecture

This invention discloses a sign extension method and a structure of a multiplier, which designs multiple complement bits in the codes of sign extension during the code operation used in a multiplier of a DSP without increasing critical paths to reach the aim of reducing the waste to the chip area and reducing the size of the multiplier.

Owner:ALICORP

Symbol extension method and structure of multipliers

ActiveCN1704898ANo critical path addedComputation using non-contact making devicesBinary multiplierComputer architecture

This invention discloses a sign extension method and a structure of a multiplier, which designs multiple complement bits in the codes of sign extension during the code operation used in a multiplier of a DSP without increasing critical paths to reach the aim of reducing the waste to the chip area and reducing the size of the multiplier.

Owner:ALICORP