Symbol extension method and structure of multipliers

A multiplier and symbol technology, applied in the field of multiplier symbol extension method and structure, can solve the problems of affecting performance and increasing key paths

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

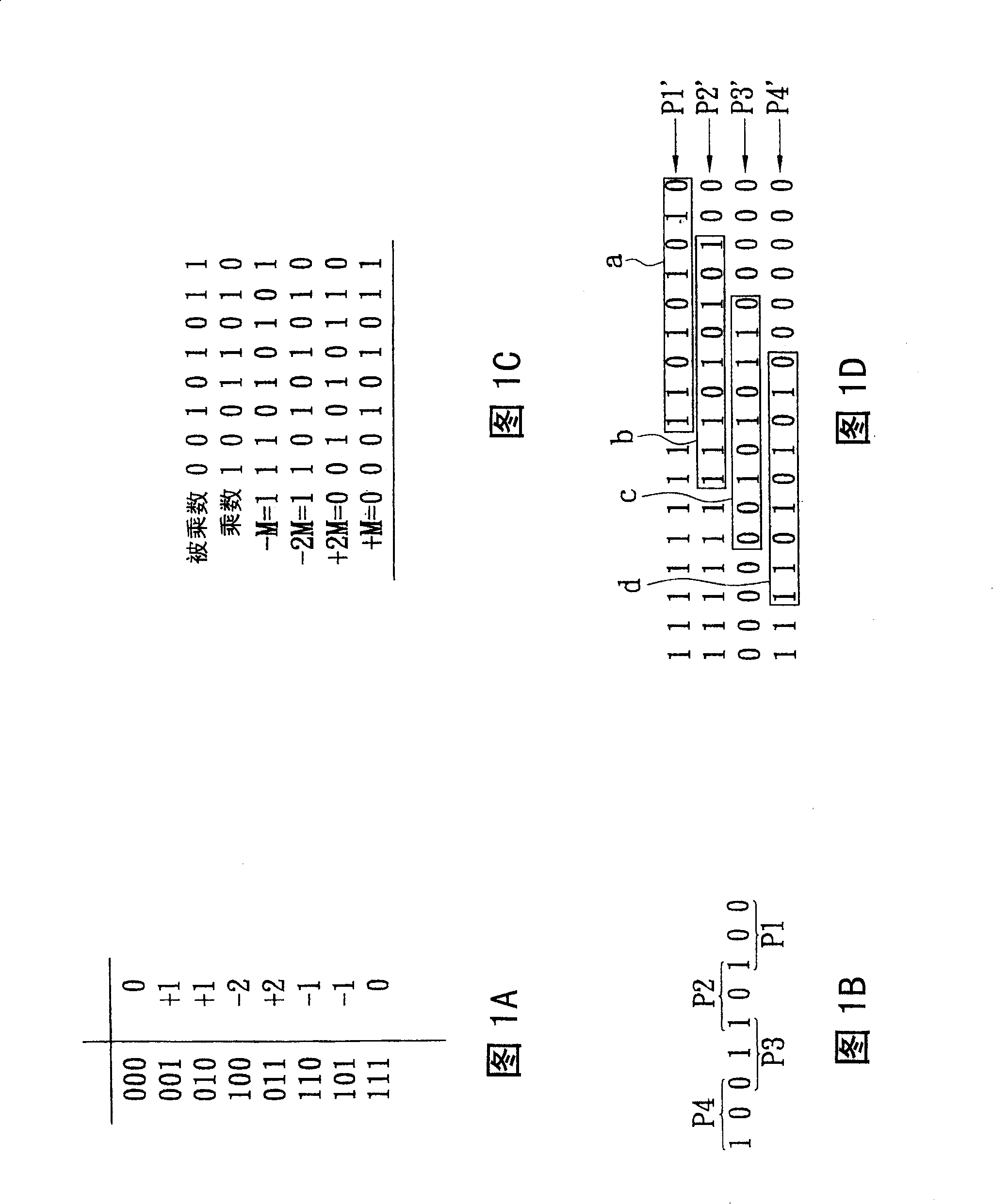

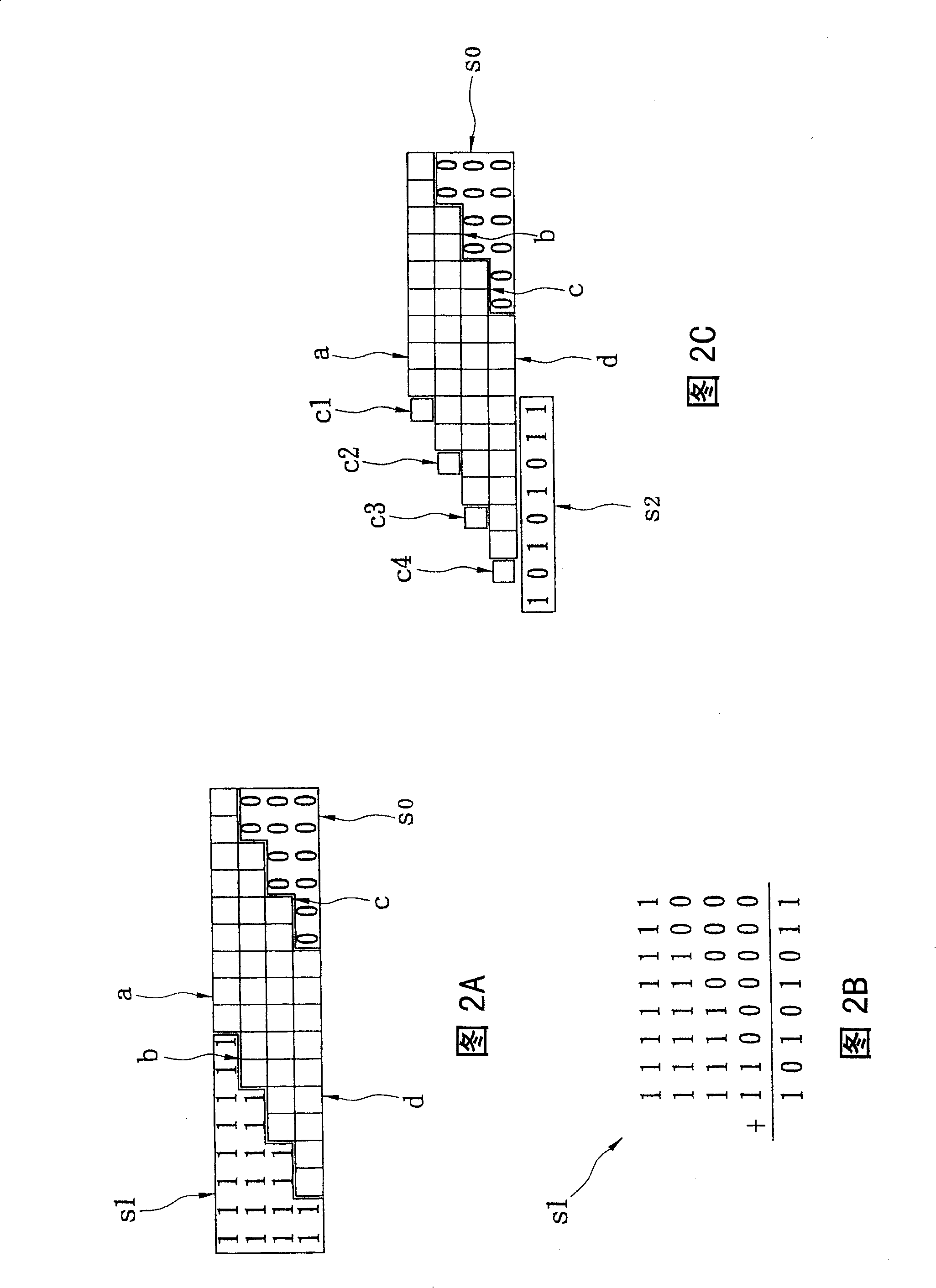

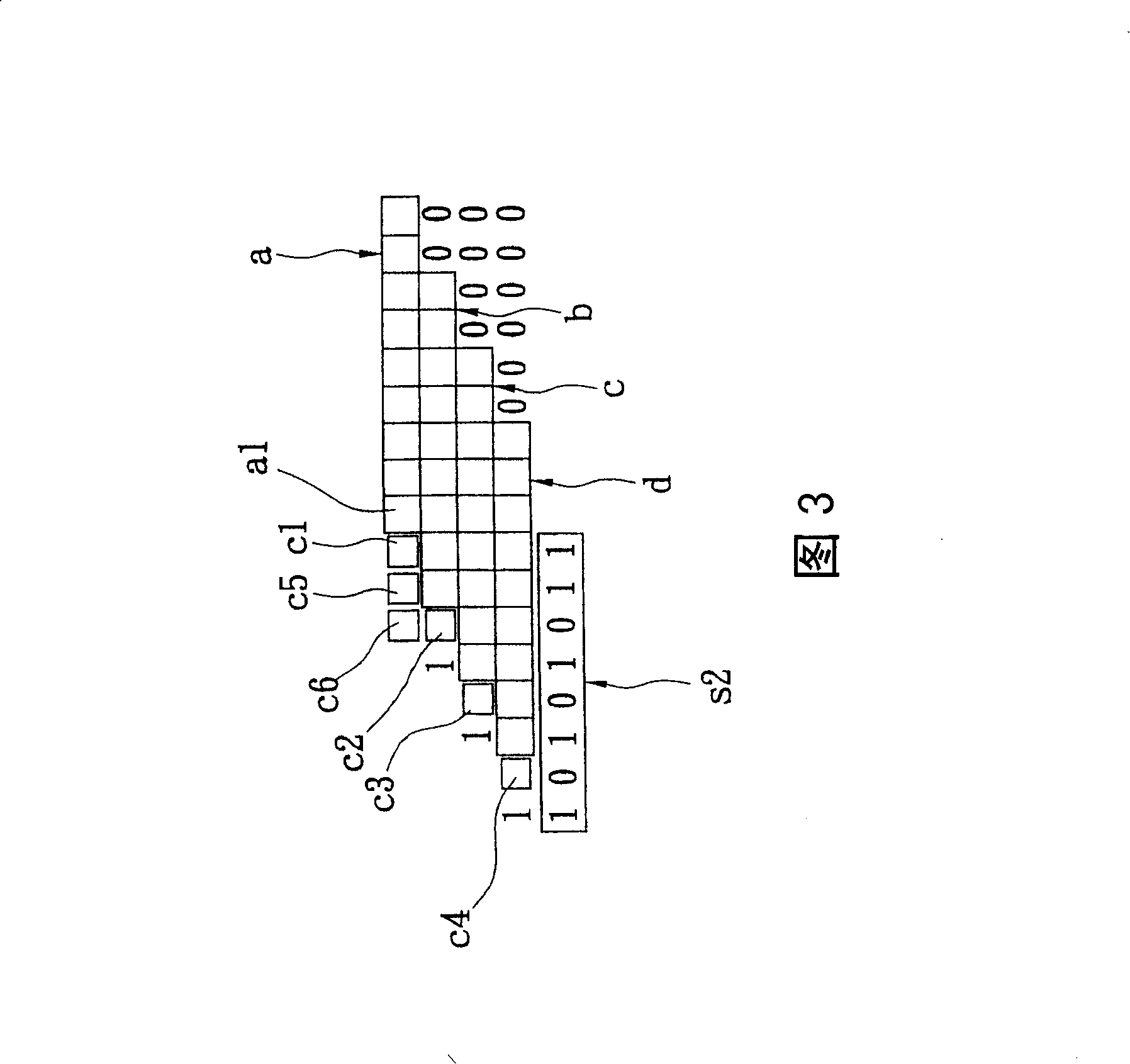

[0038]In the operation of the multiplier (multiplier) in the digital signal processor (DSP), the present invention provides a sign extension method and structure of the multiplier so that the area of the sign extension bit (sign extension bit) of the digital signal processor chip does not increase , but also to maintain performance, but also to make the Wallace Tree ladder table less, and thereby reduce the critical path (critical path).

[0039] In the present invention, the sign extension bits generated by the partial product terms in the modified Booth algorithm are all set to 1 (one-extension), and the fixed values can be summed up first in the calculation , and then judge whether there is a need for compensation, please refer to the schematic diagram of the symbol extension in Figure 2A, in which there are four groups of partial product terms, namely a, b, c, d, etc., in the improved Booth The first ladder-type bit table is formed in the algorithm, and the right side ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More