Floating point multiply-add, accumulate unit with exception processing

a technology of multiplying and accumulating units and logic circuits, applied in the field of implementation of arithmetic logic circuits, can solve problems such as system failures or other problems in performance, algorithms to stall or fail, and relatively complicated logic circuits,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

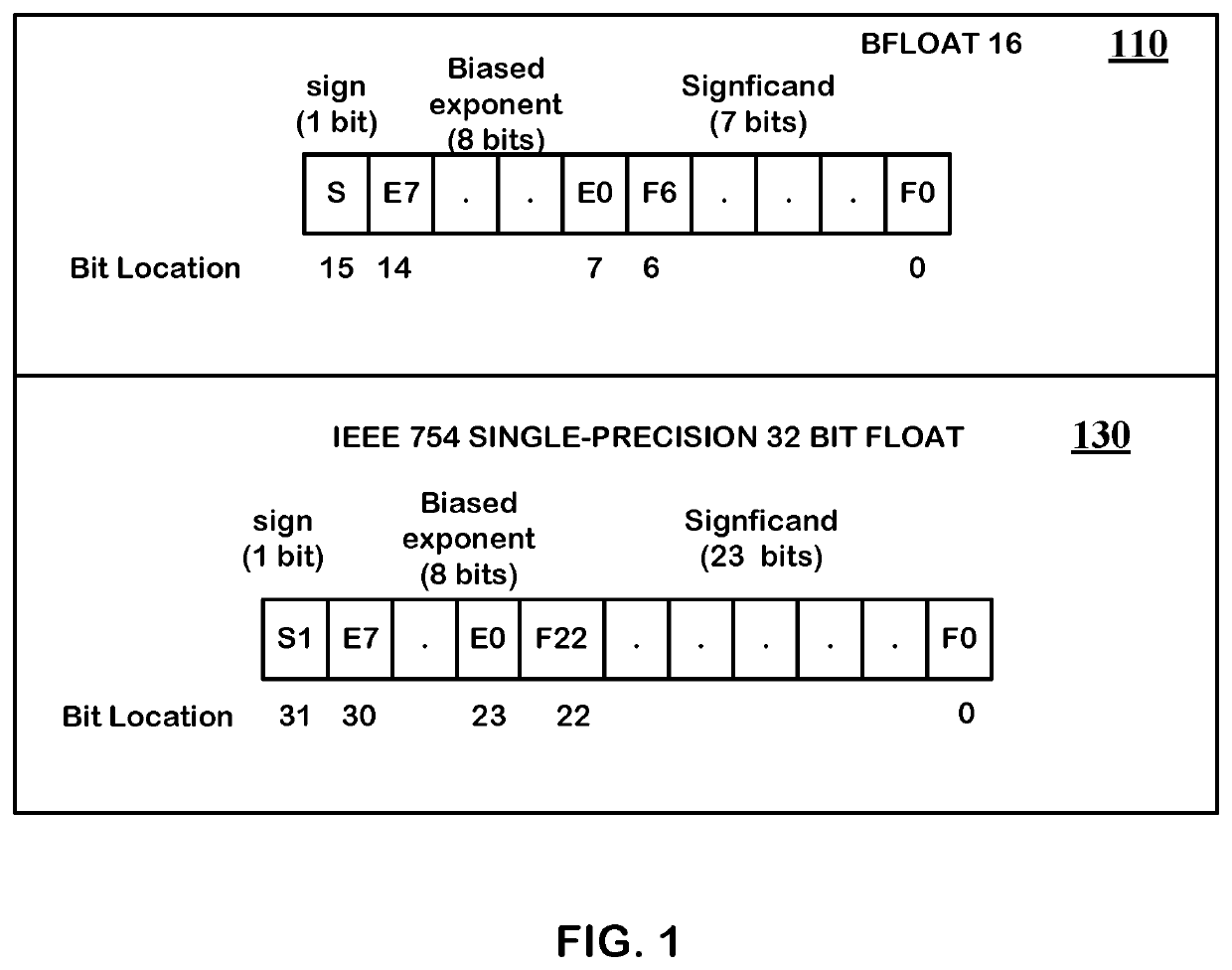

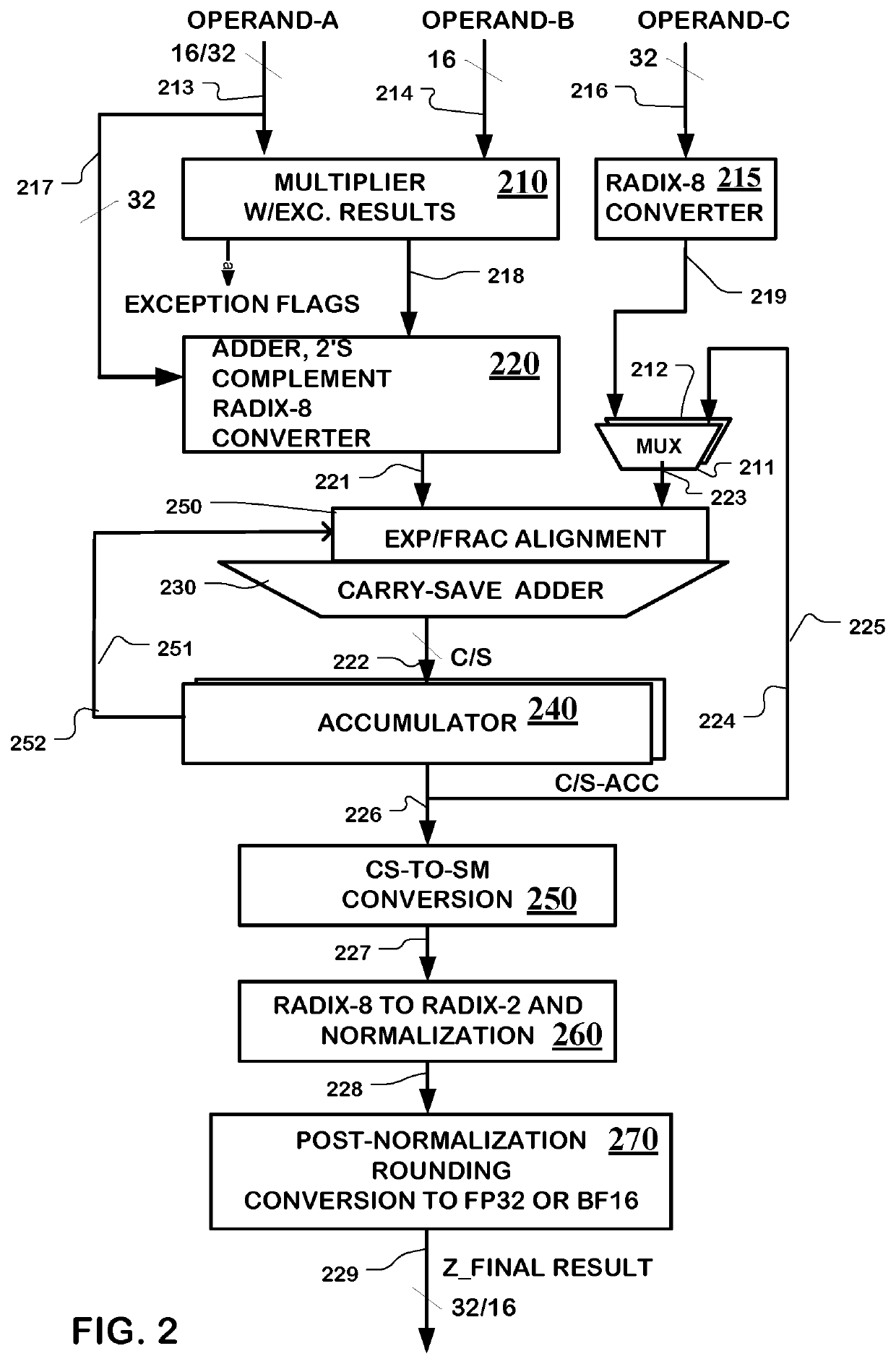

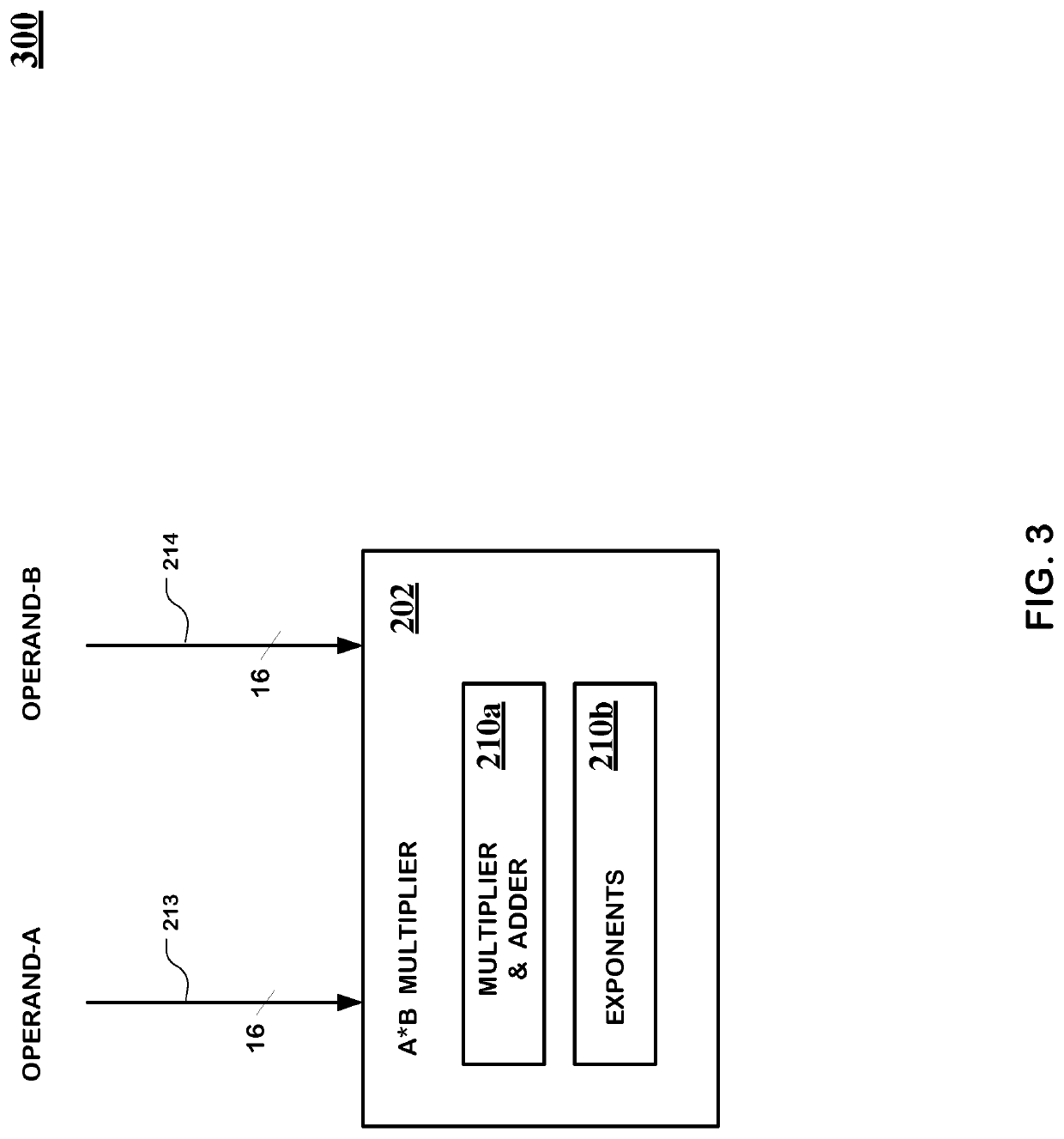

[0050]A detailed description of a technology implementing an arithmetic unit for a configurable, and reconfigurable, data flow architecture with exception handling is provided. An example reconfigurable data flow architecture is described in U.S. Pat. No. 10,831,507, by Shah et al., issued Nov. 10, 2020, which is incorporated by reference as if fully set forth herein. The arithmetic unit can execute a plurality of floating point arithmetic operations using input operands and generating at least one output operand, where the source of the input operands, the destination of the output operand and the operation are configurable, and reconfigurable by configuration data that can be static during a data flow operation.

[0051]In the execution of at least one of the floating point arithmetic operations, exceptions related to illegal operations and to generation of results not normally represented in the floating point encoding format utilized are detected, and results of the operation are s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More