Patents

Literature

32results about How to "Execution efficiency is improved" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

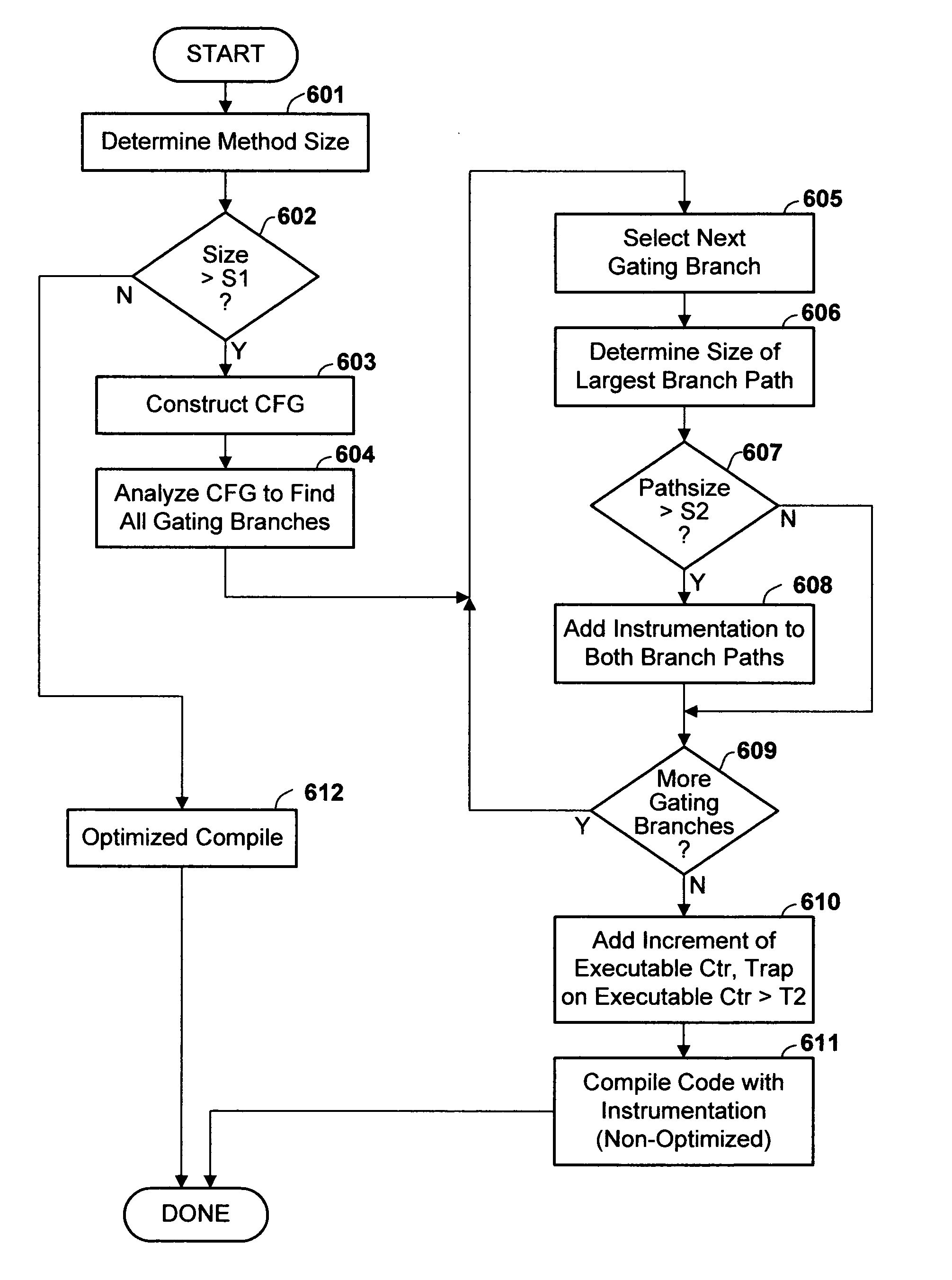

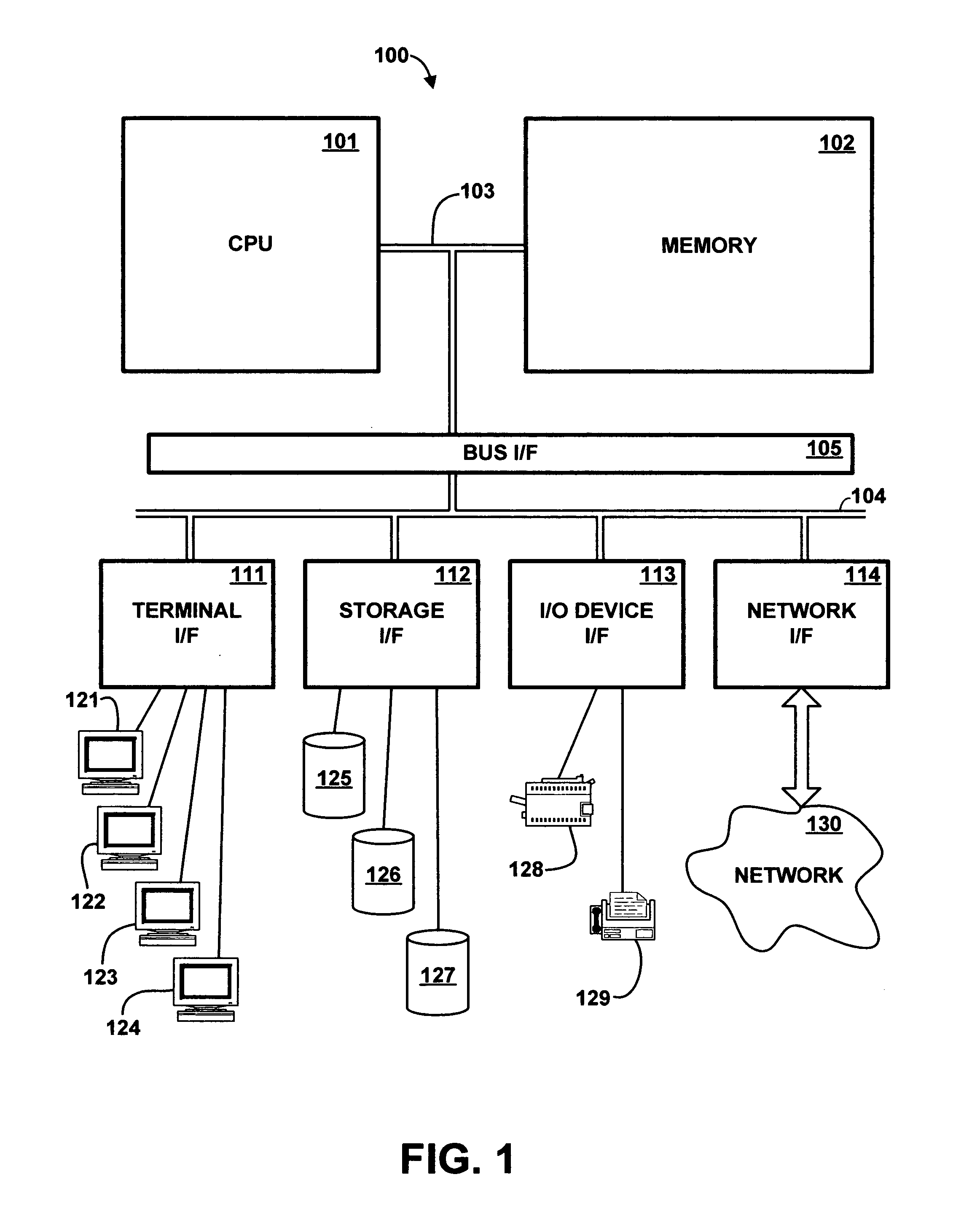

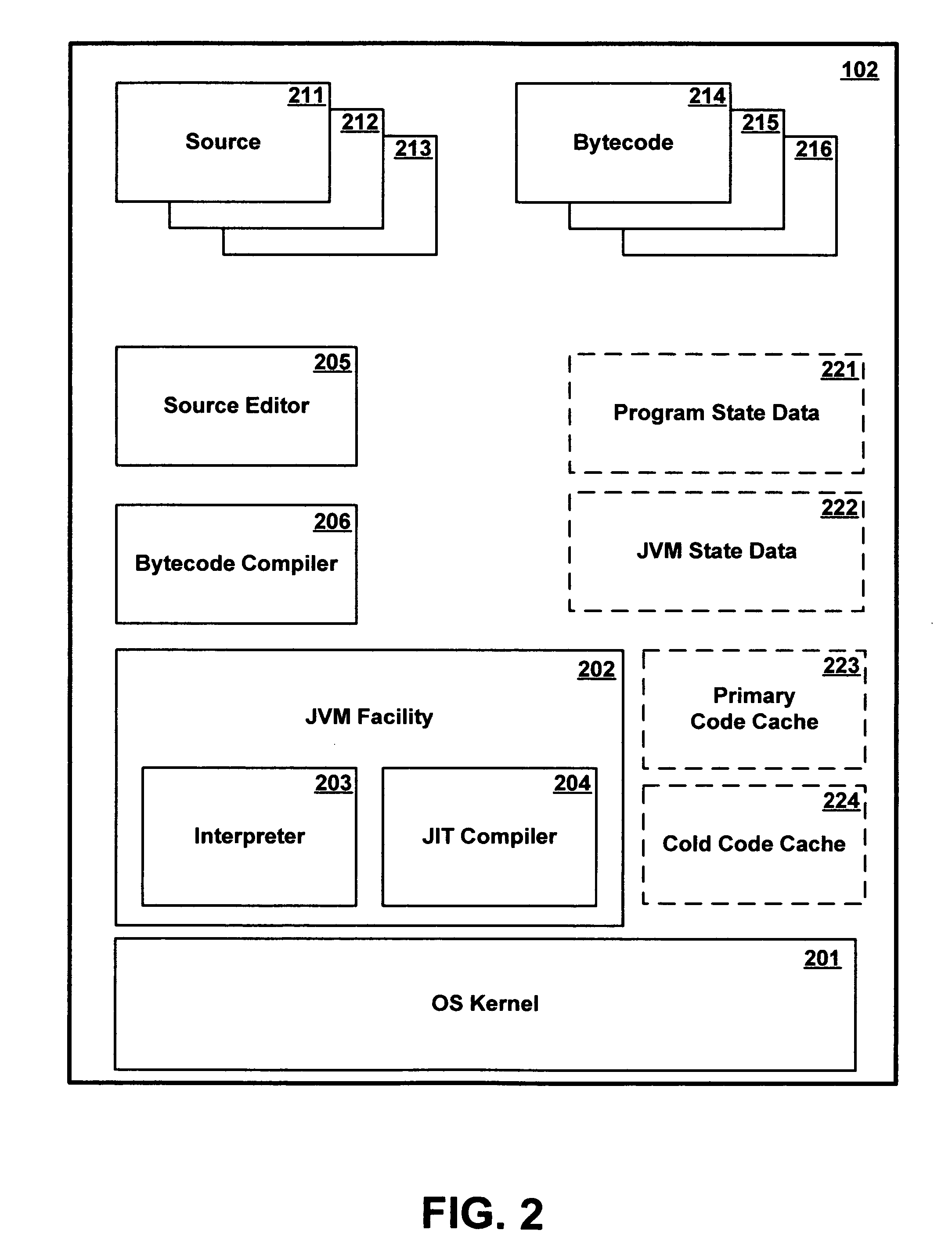

Method and apparatus for dynamic compilation of selective code blocks of computer programming code to different memory locations

InactiveUS20060048114A1Reduce in quantitySimplifies dynamic analysisProgram controlMemory systemsCoding blockDynamic compilation

A dynamic compiler analyzes the frequency of execution of selective code paths within a program procedure, and selectively compiles code paths to different memory locations based on the observed frequency of execution. Preferably, code is dynamically compiled in two stages. In a first compilation stage, the compiler instruments selective code paths to count the number of times each path is taken. A second stage compilation is thereafter triggered when the procedure has been called some threshold number of times. In the second stage, the compiler selectively re-compiles the more frequently executed code paths to a primary location, and re-compiles the remaining code paths to an alternate location. Placing infrequently executed code in an alternate location reduces the size of the primary code area, improving execution efficiency.

Owner:IBM CORP

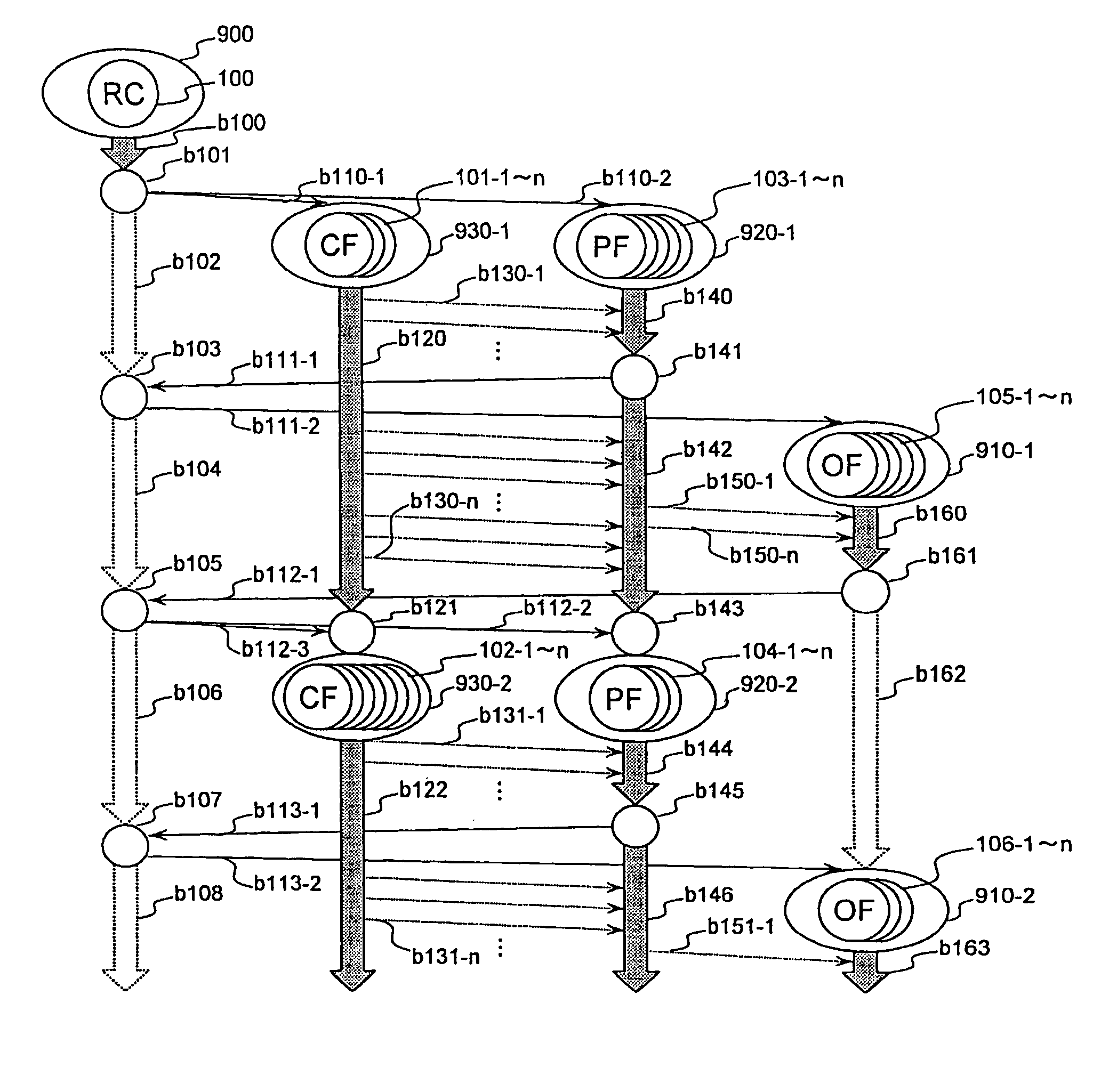

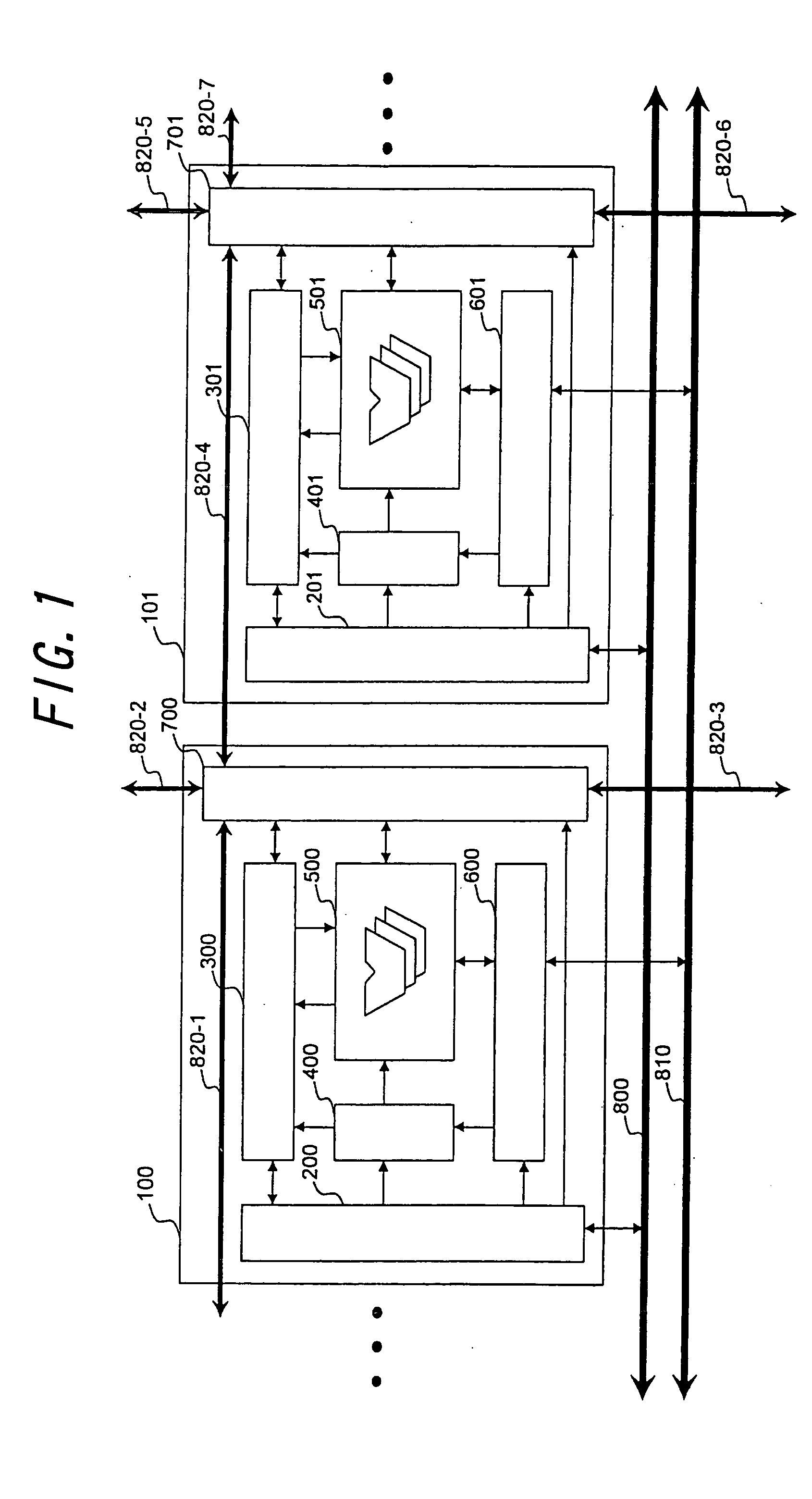

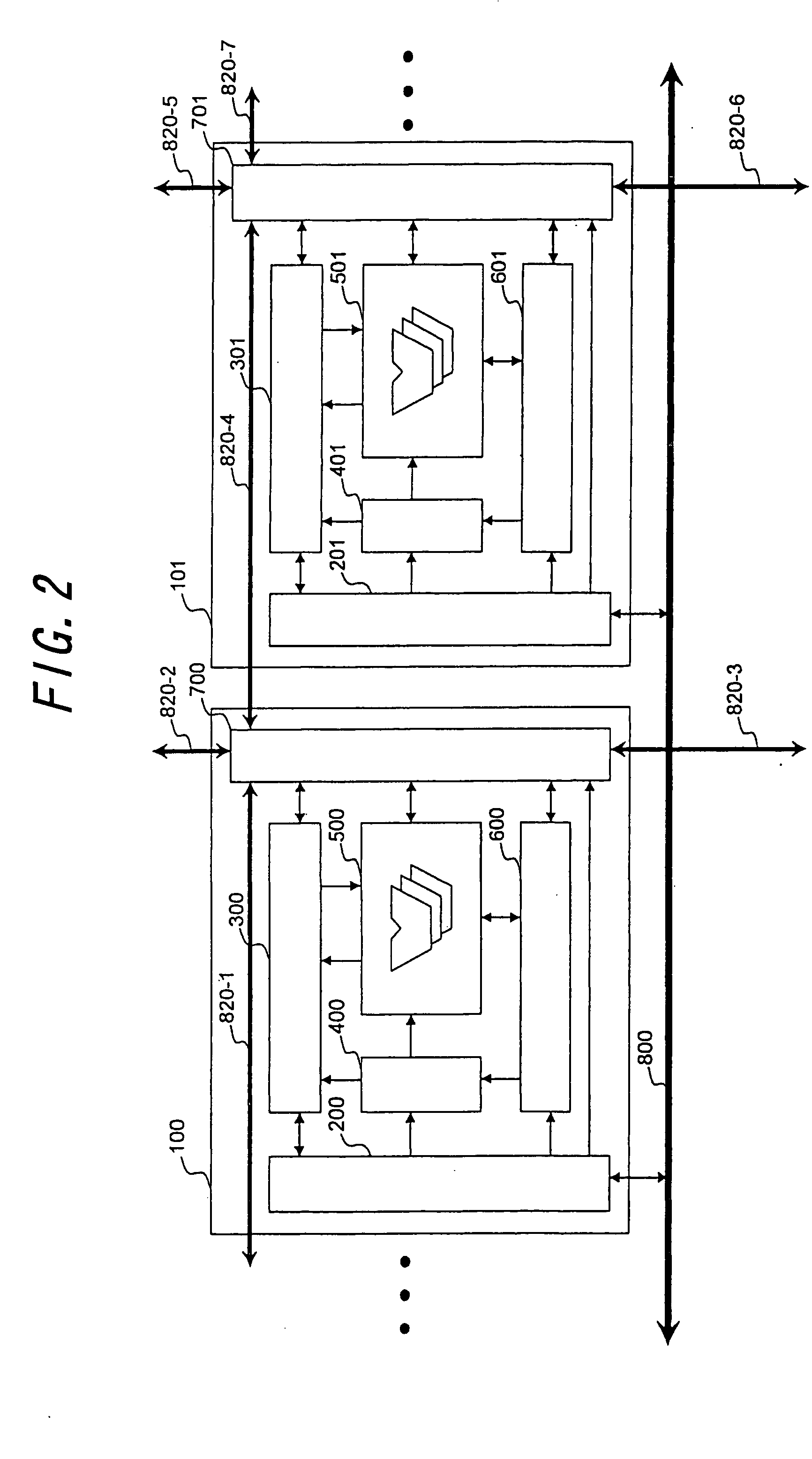

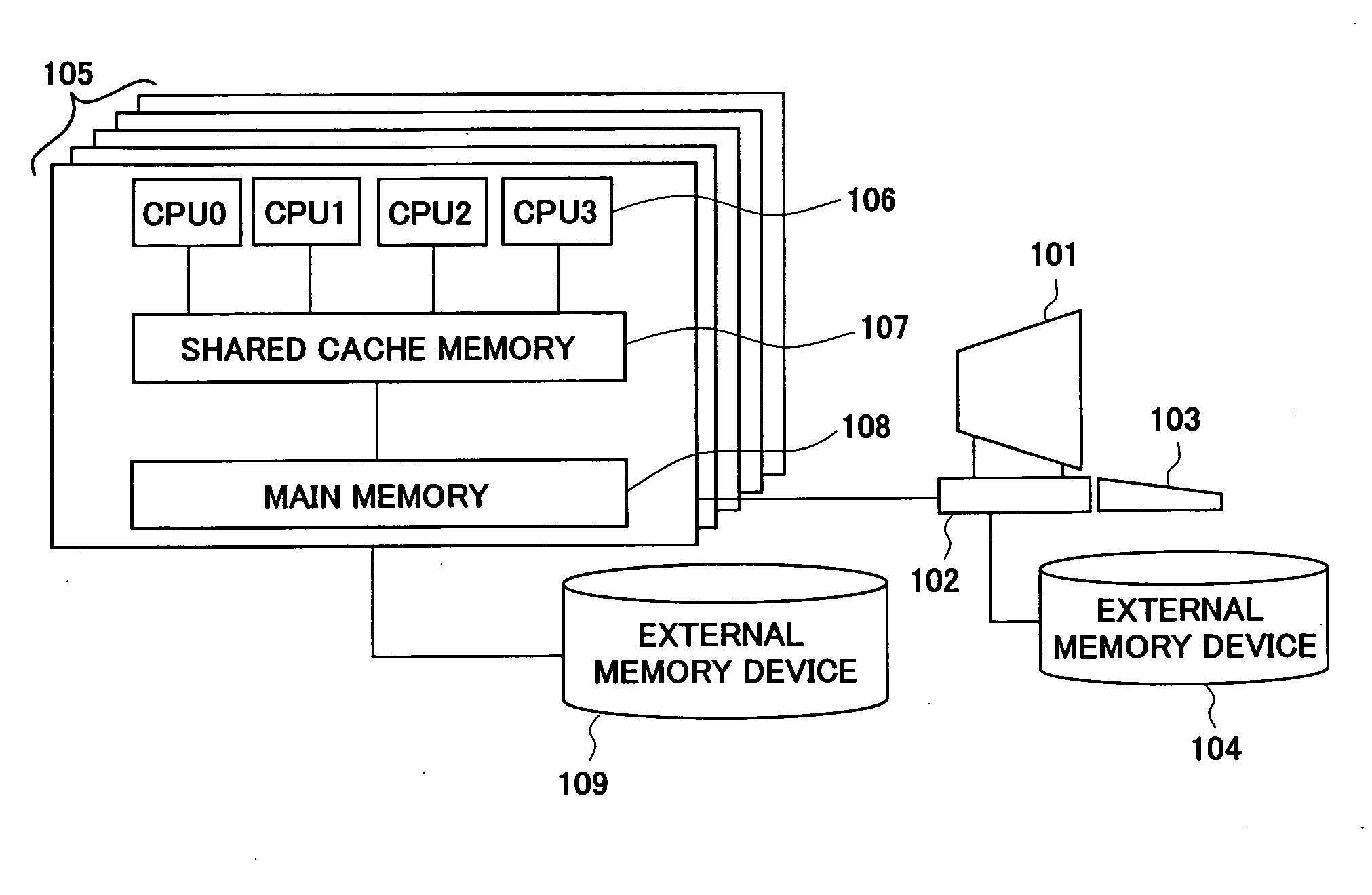

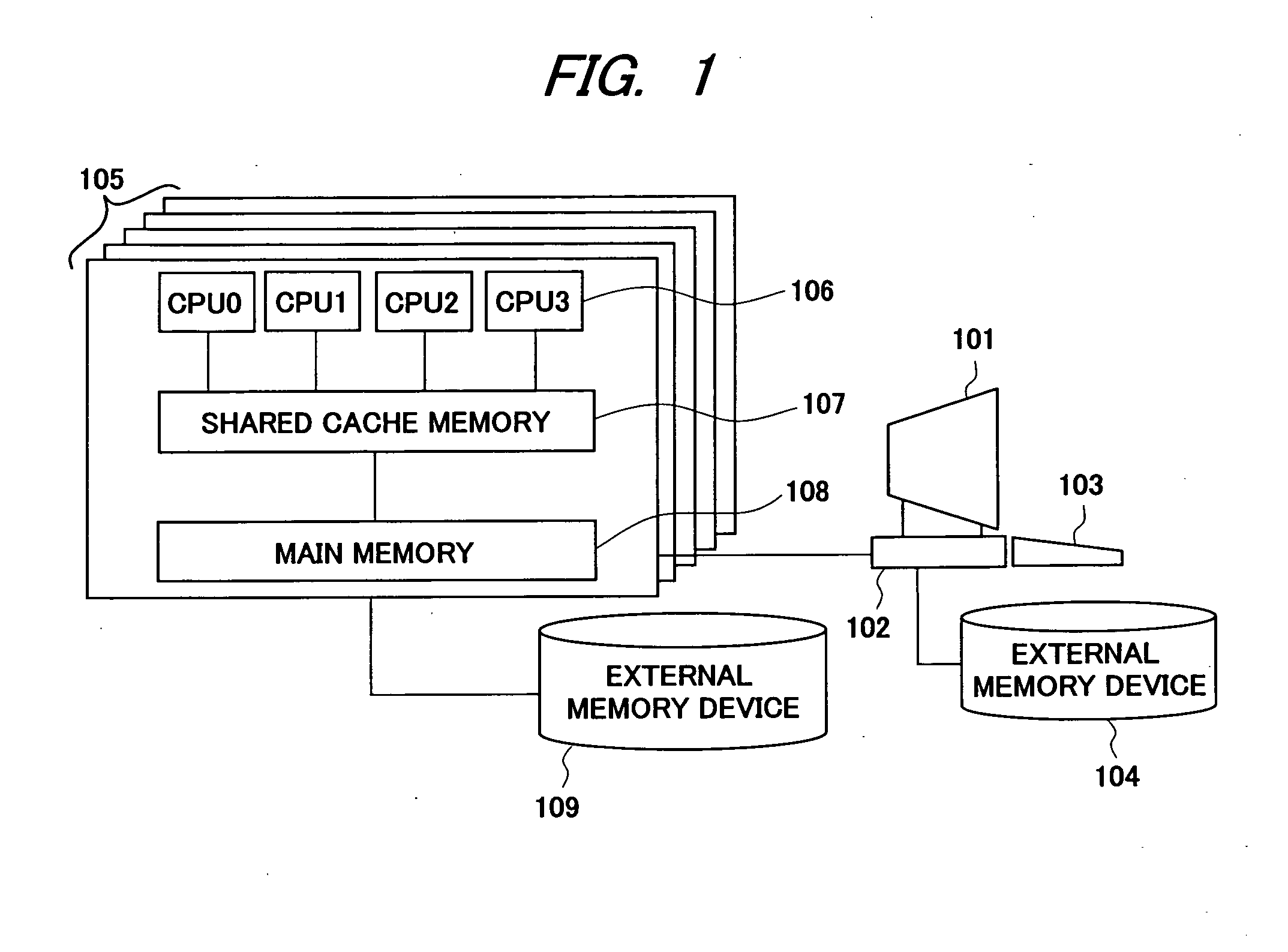

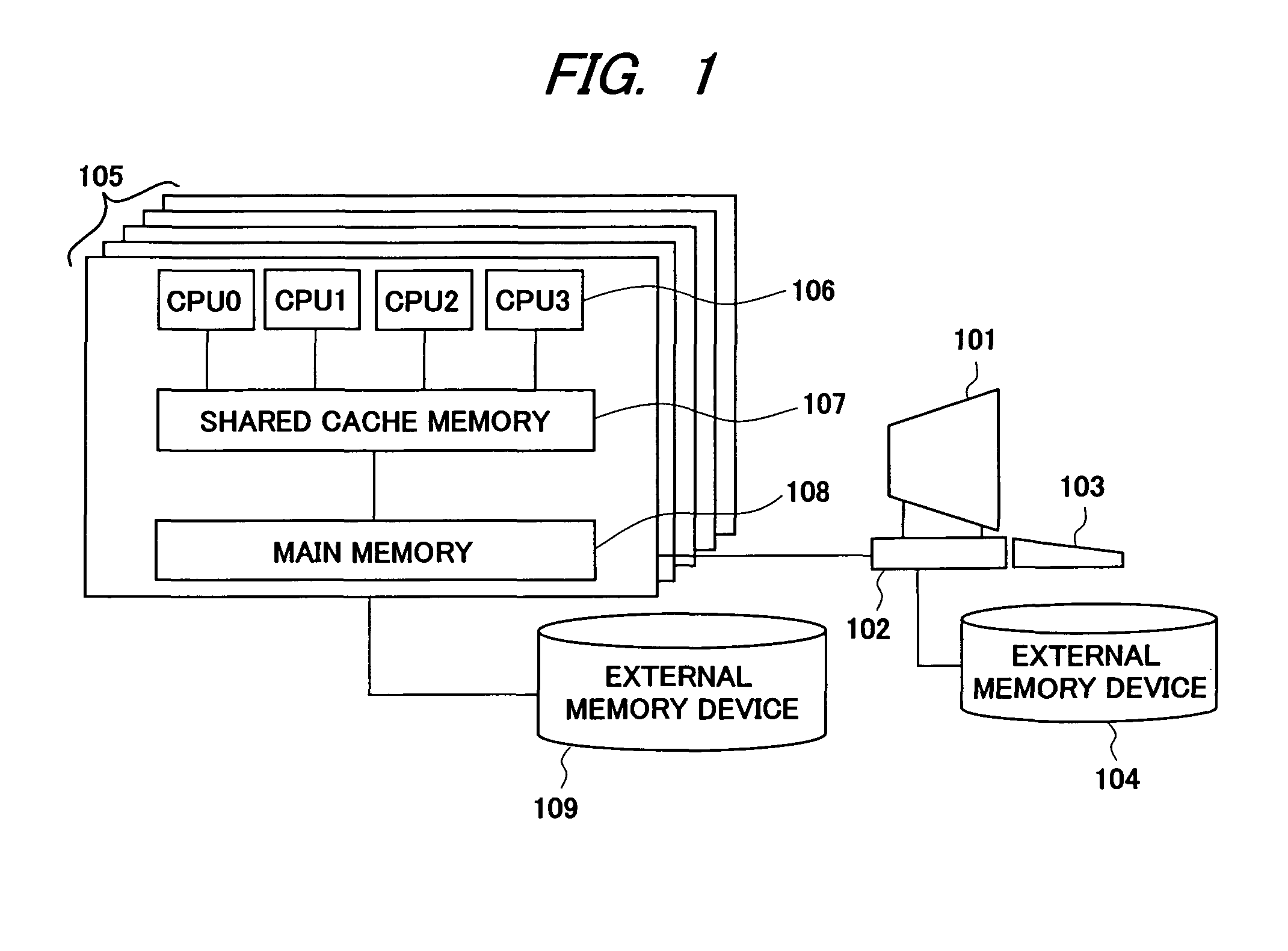

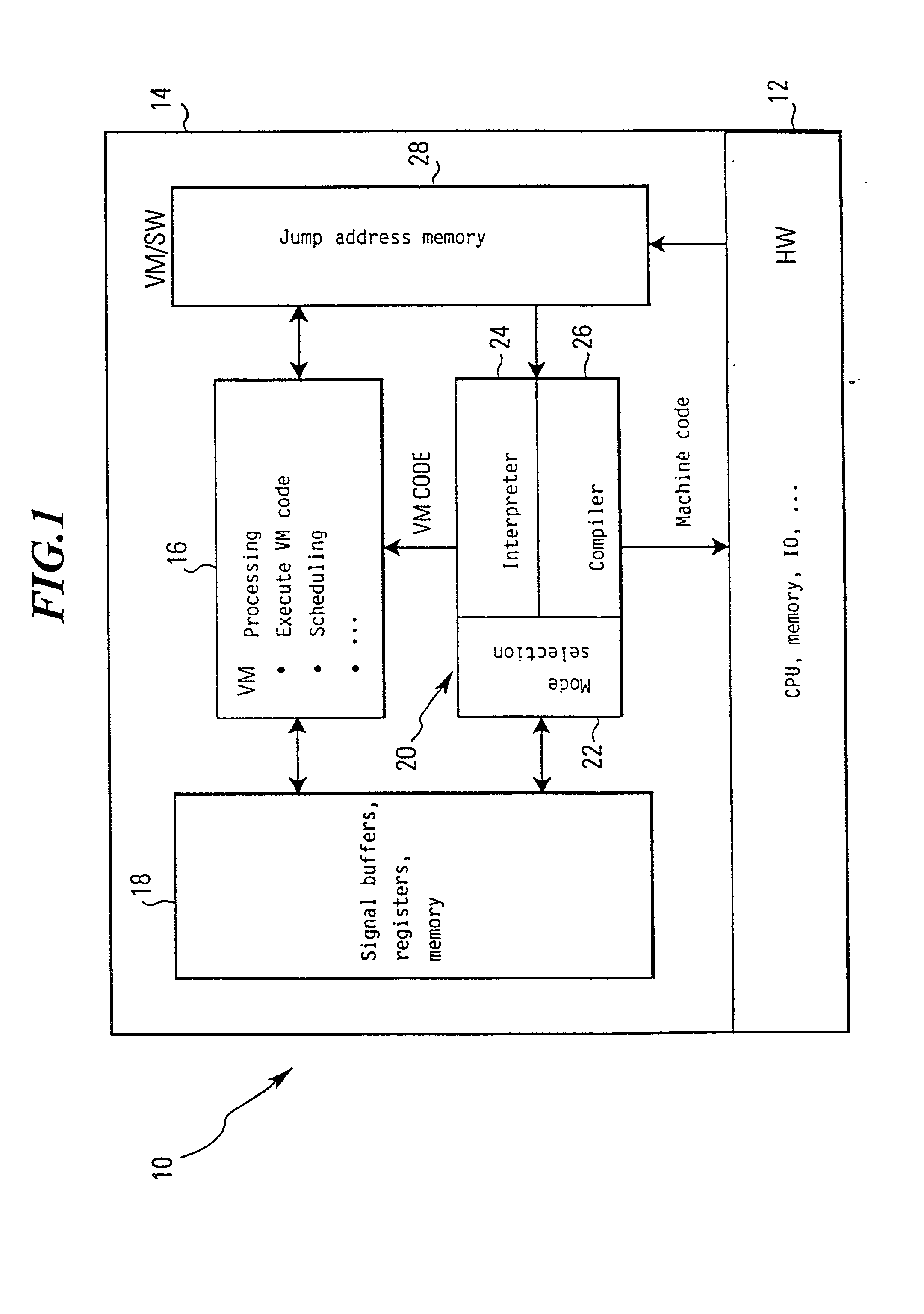

Self-optimizing computer system

InactiveUS20050166207A1Execution efficiency is improvedReduce optimization timeResource allocationConcurrent instruction executionDynamical optimizationManagement process

Provided is a self-optimizing computer system that can achieve ultimate optimization (improvement in the speed) by preparing a mechanism that can observe the behavior of the program execution in the self-optimizing computer system and optimize dynamically depending on the execution behavior of program. The self-optimizing computer system comprising multiple processing units, characterized in that each of the processing units operates as at least one of an operation processing unit for executing a program, an observation processing unit for observing the behavior of the program under execution, an optimization processing unit for performing an optimization process according to the observation result of the observation processing unit, and a resource management processing unit for performing a resource management process of whole of the system such as a change of the contents of execution.

Owner:NATIONAL UNIVERSITY

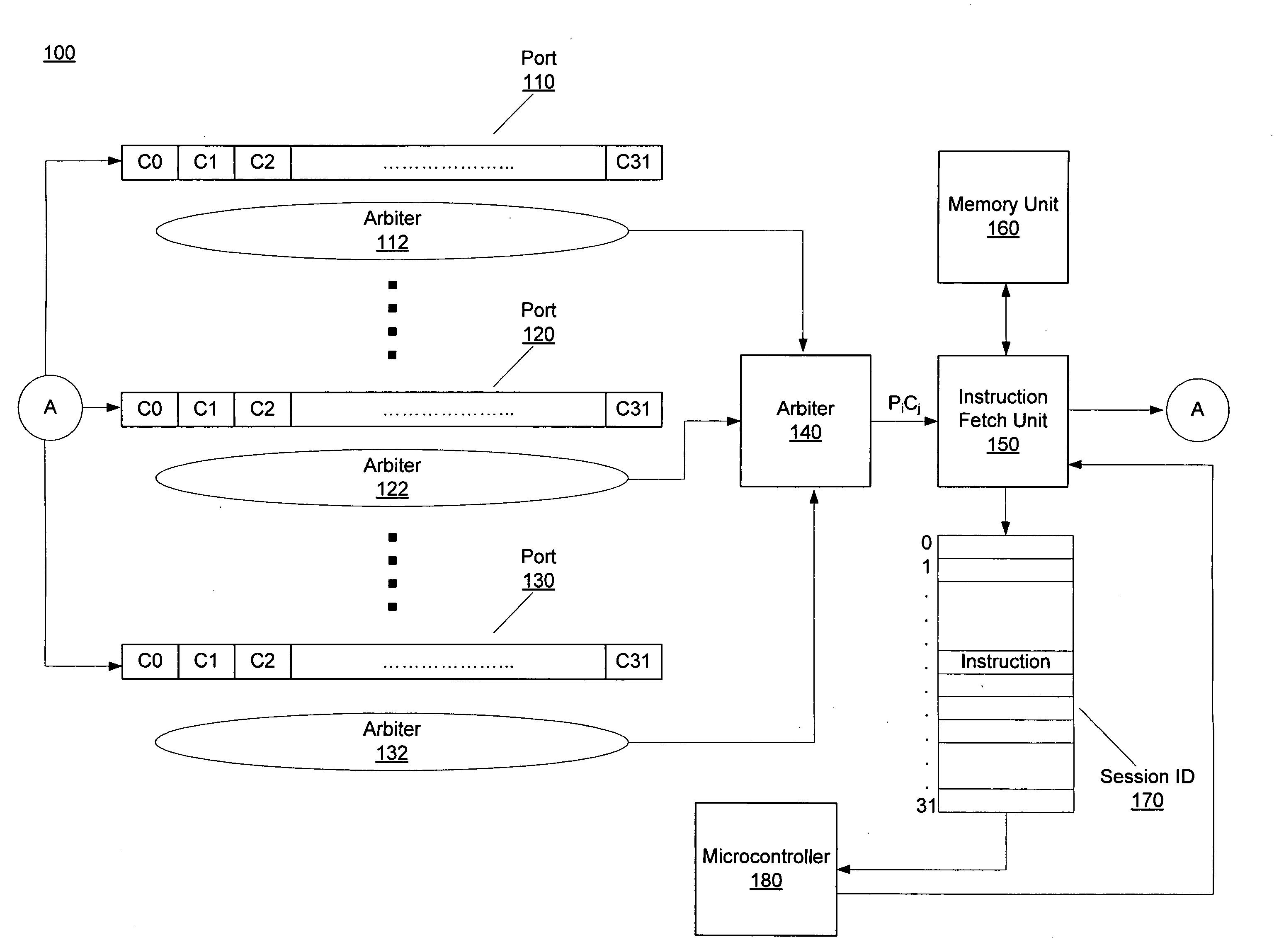

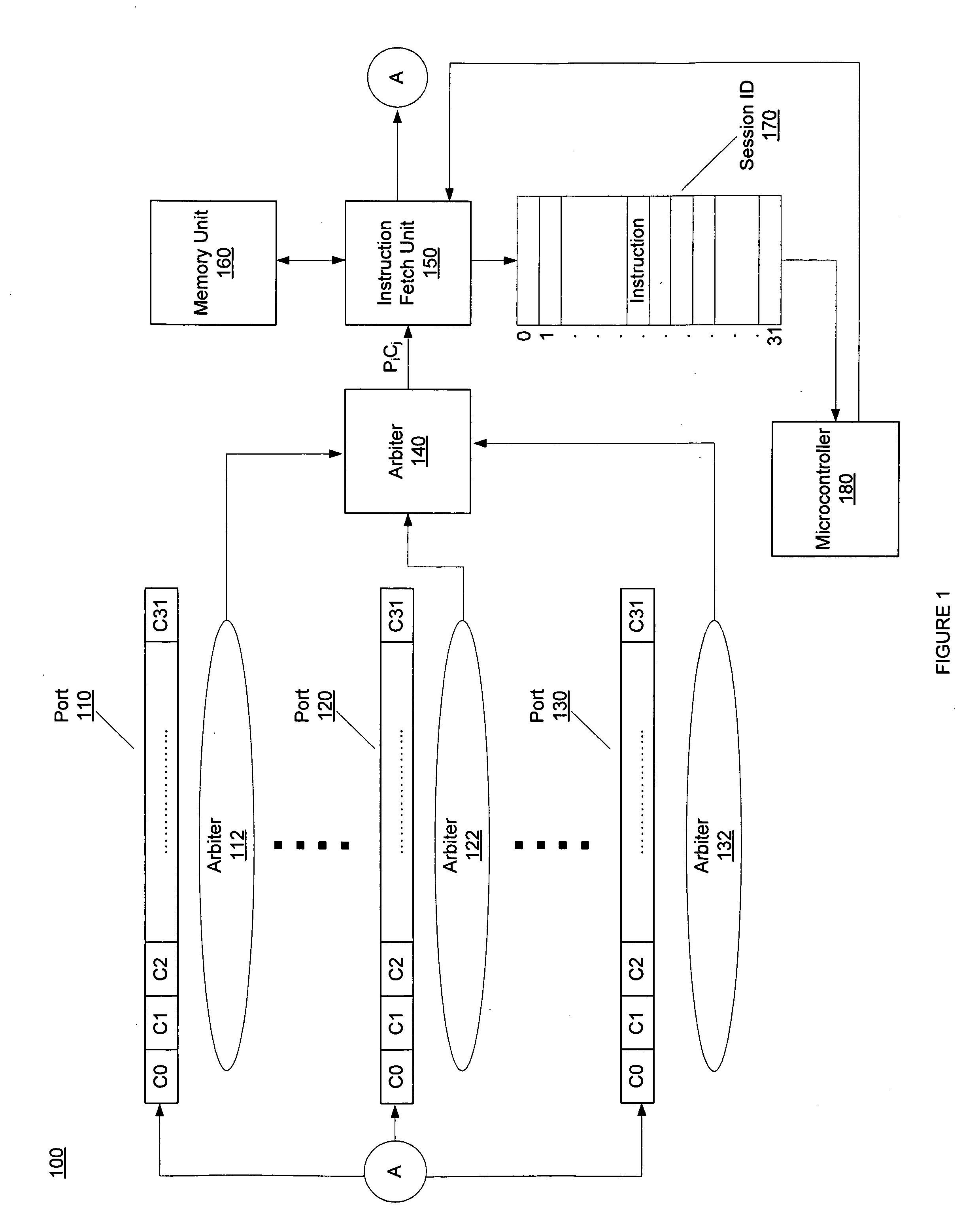

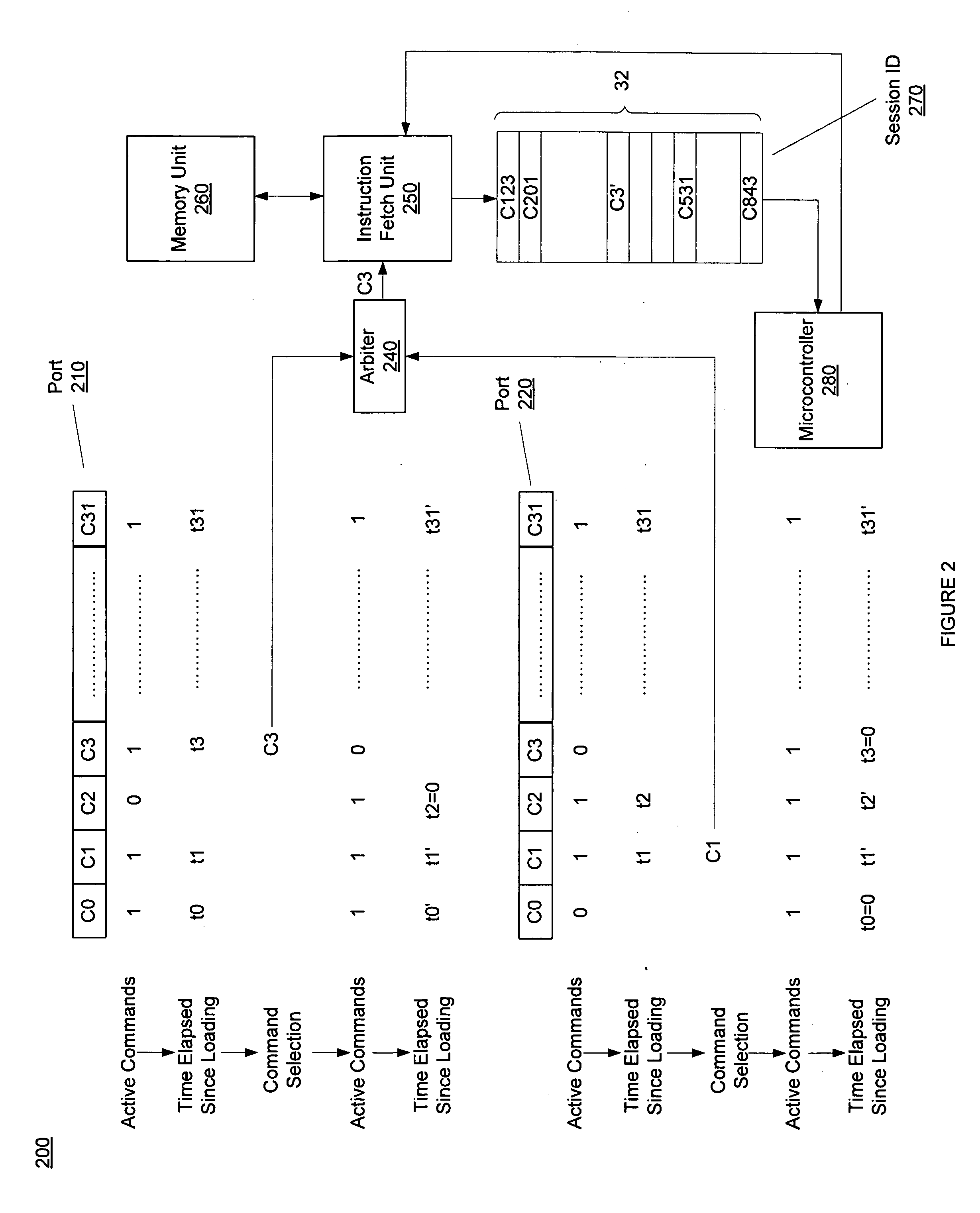

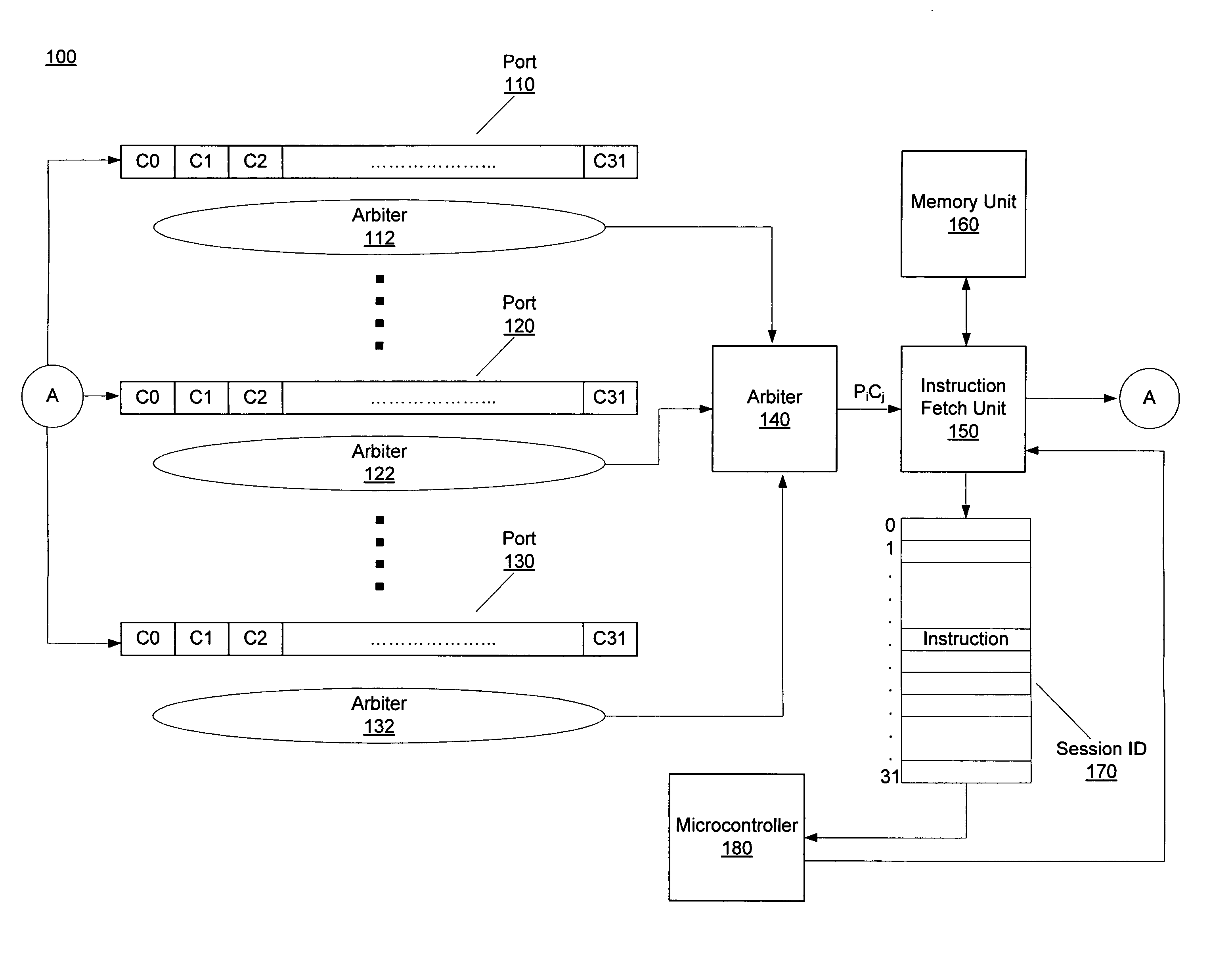

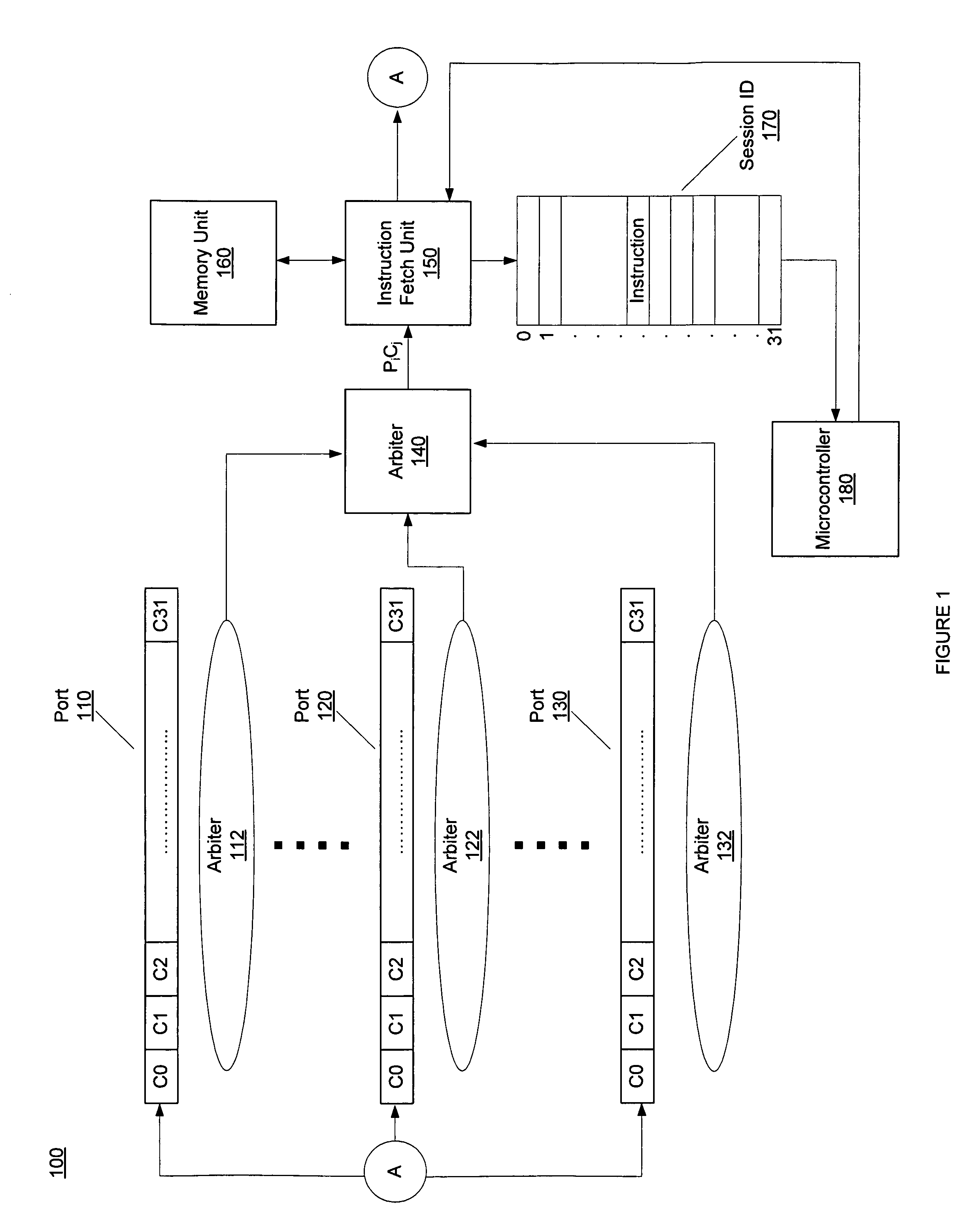

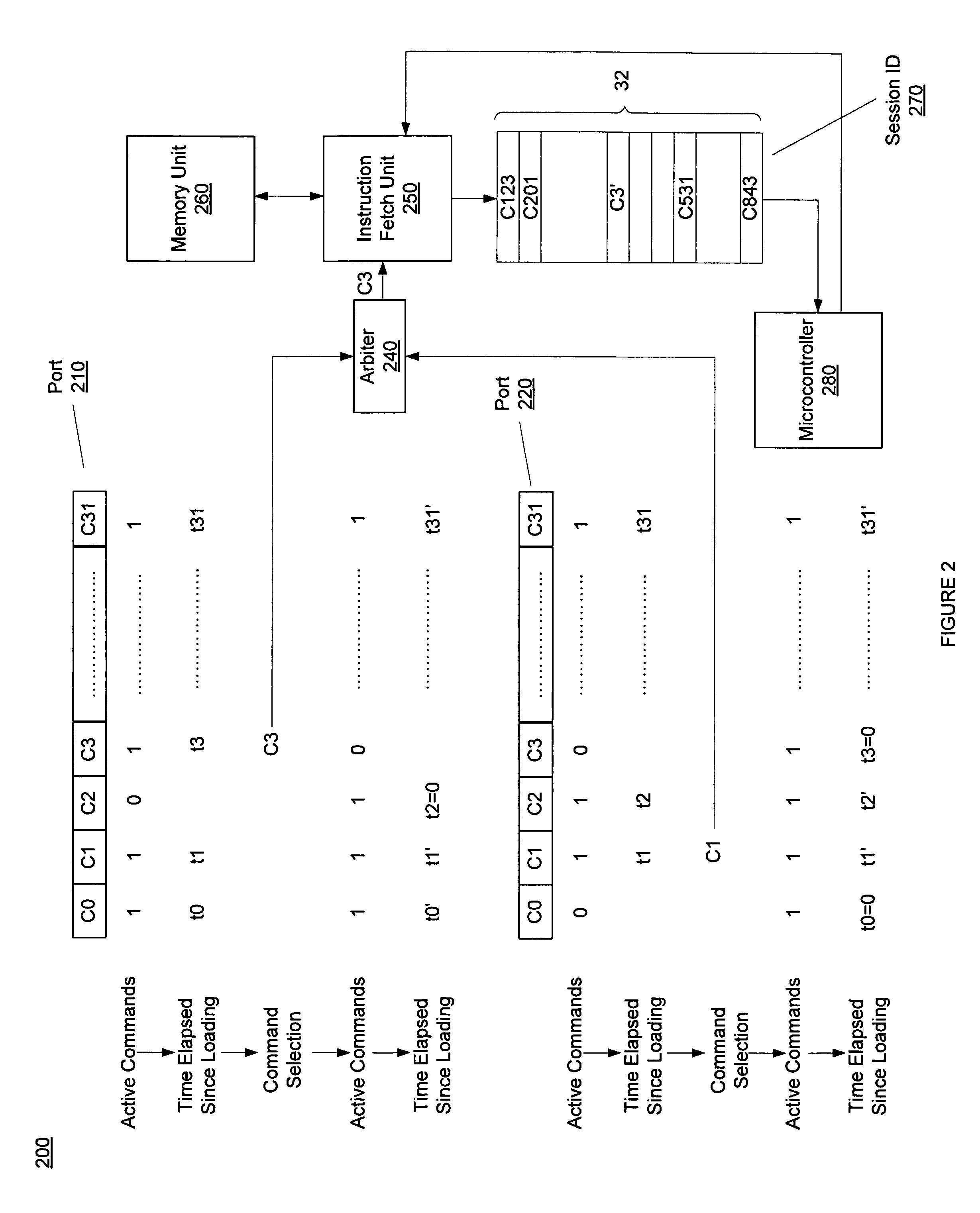

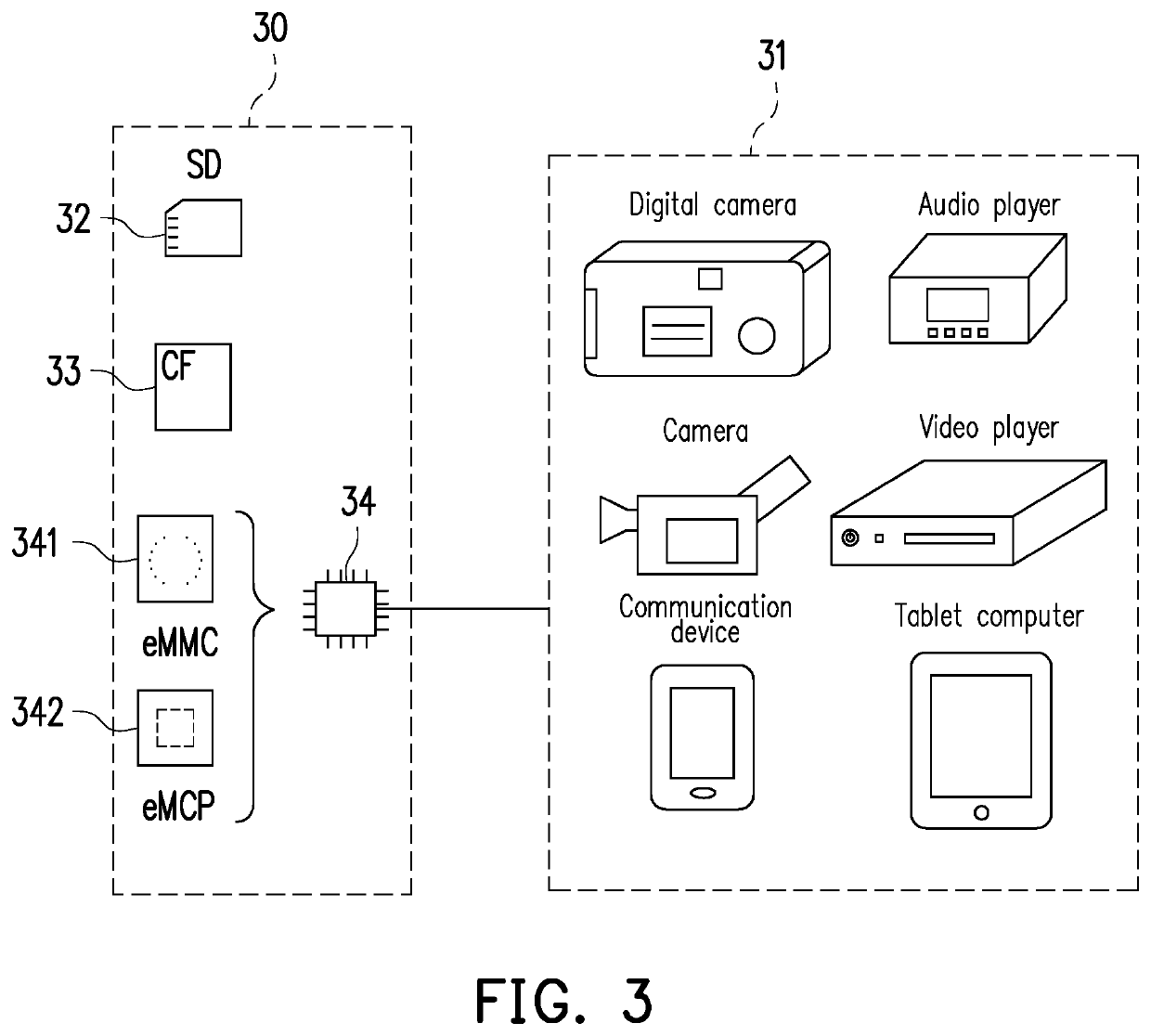

Method and system for improved flash controller commands selection

ActiveUS20100161941A1Execution efficiency is improvedImprove system efficiencyMemory adressing/allocation/relocationDigital computer detailsMicrocontrollerFlash memory controller

A system for selecting a subset of issued flash storage commands to improve processing time for command execution. A plurality of ports stores a first plurality of command identifiers and are associated with the plurality of ports. Each of the first plurality of arbiters selects an oldest command identifier among command identifiers within each corresponding port resulting in a second plurality of command identifiers. A second arbiter makes a plurality of selections from the second plurality of command identifiers based on command identifier age and the priority of the port. A session identifier queue stores commands associated with the plurality of selections among other commands forming a third plurality of commands. A microcontroller selects an executable command from the third plurality of commands for execution based on an execution optimization heuristic. After execution of the command, the command identifier in the port is cleared.

Owner:NVIDIA CORP

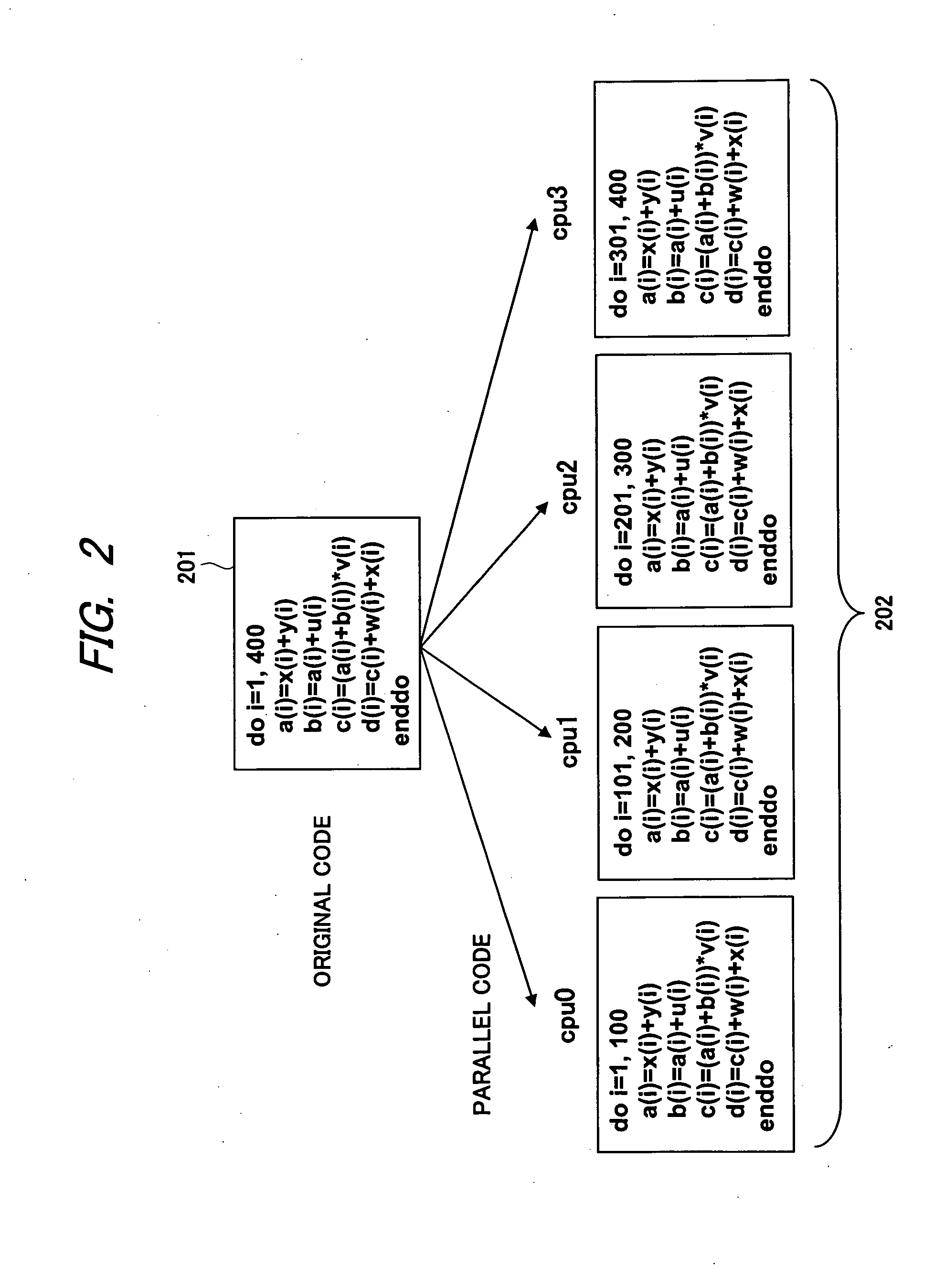

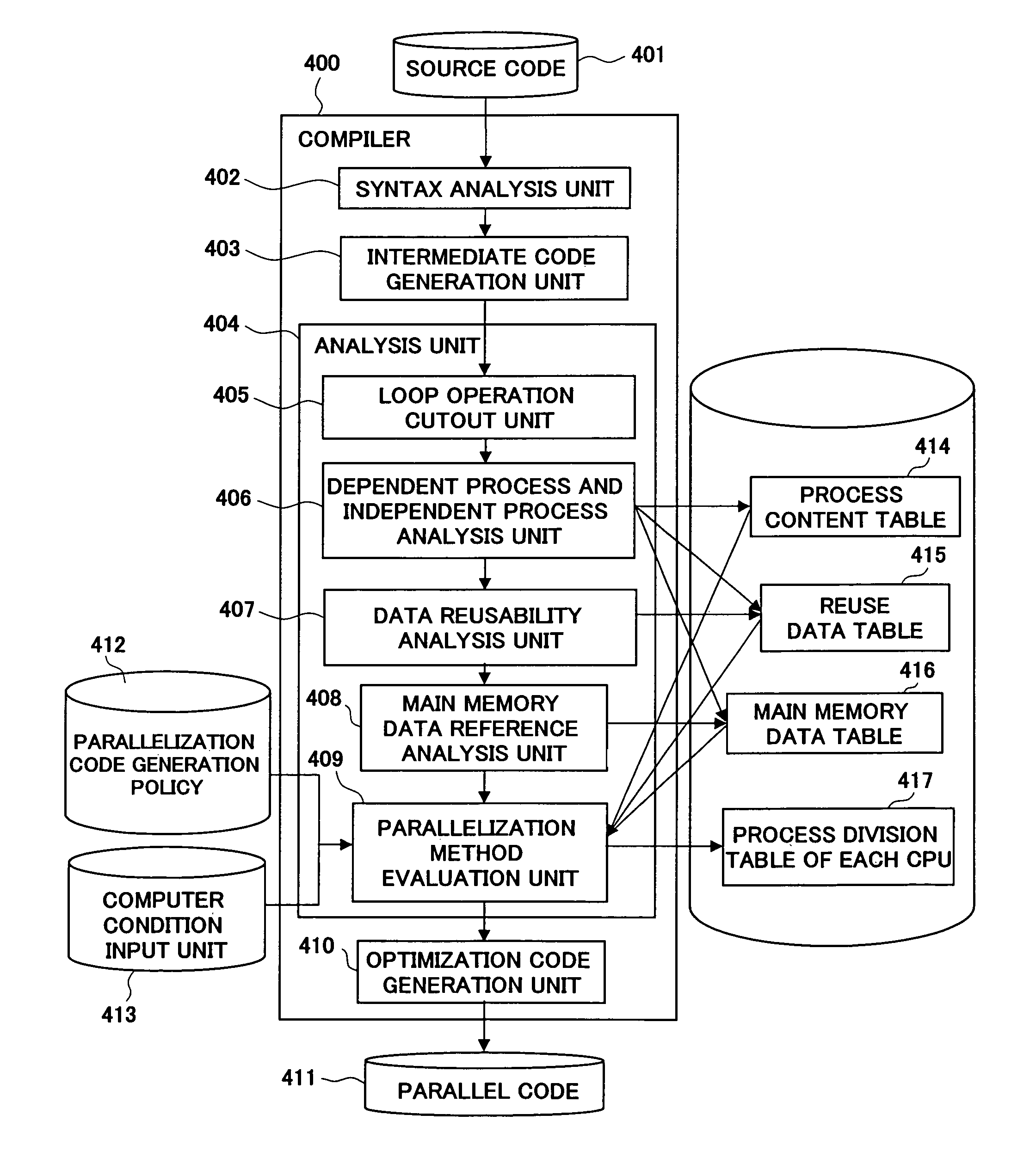

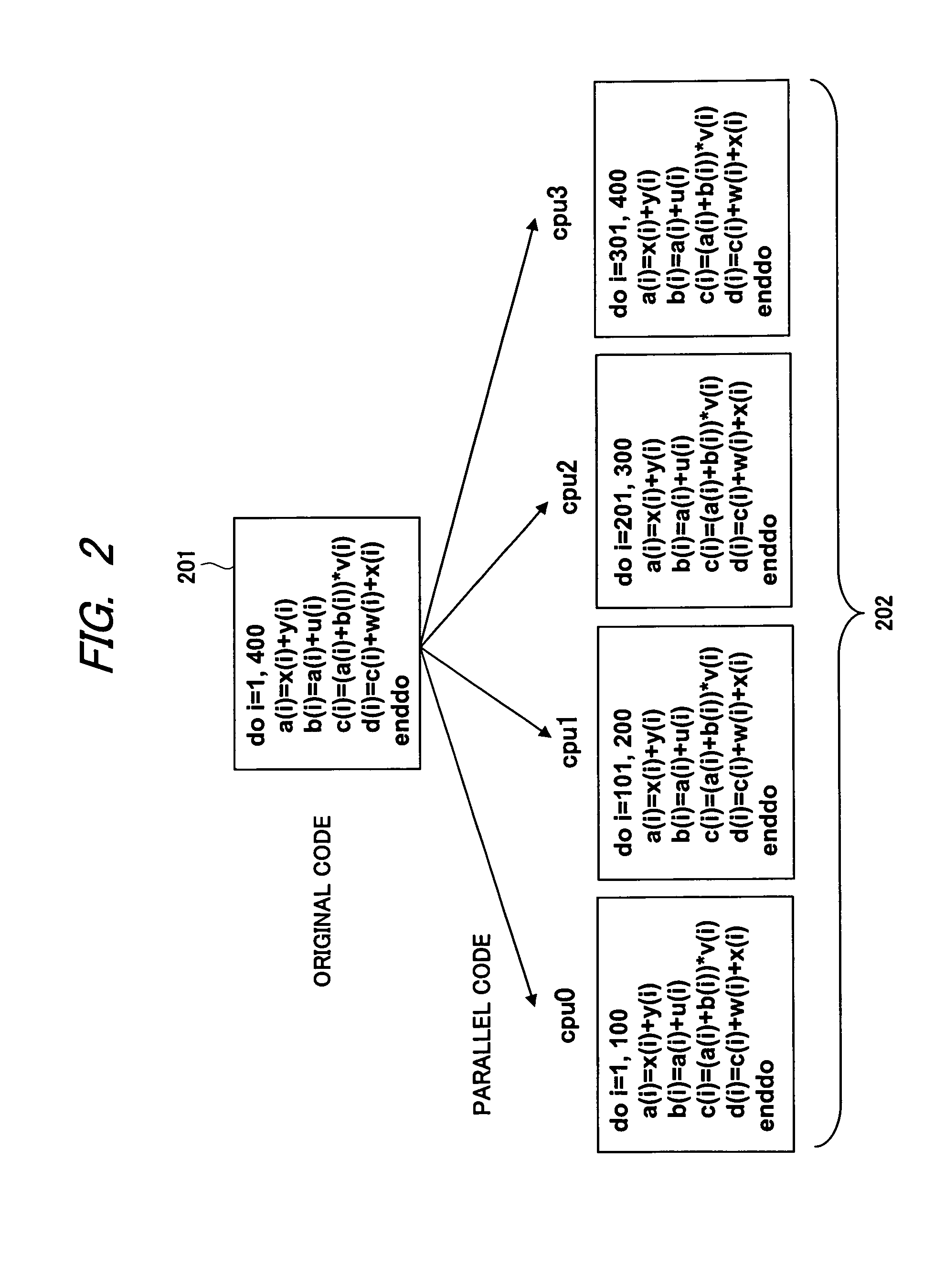

Optimum code generation method and compiler device for multiprocessor

ActiveUS20090113404A1Execution efficiency is improvedReduce the amount of data transferredSoftware engineeringProgram controlMulti processorUser input

A method of generating optimum parallel codes from a source code for a computer system configured of plural processors that share a cache memory or a main memory is provided. A preset code is read and operation amounts and process contents are analyzed while distinguishing dependence and independence among processes from the code. Then, the amount of data to be reused among processes is analyzed, and the amount of data that accesses the main memory is analyzed. Further, upon the reception of a parallel code generation policy inputted by a user, the processes of the code are divided, and while estimating an execution cycle from the operation amount and process contents thereof, the cache use of the reuse data, and the main memory access data amount, a parallelization method with which the execution cycle becomes shortest is executed.

Owner:HITACHI LTD

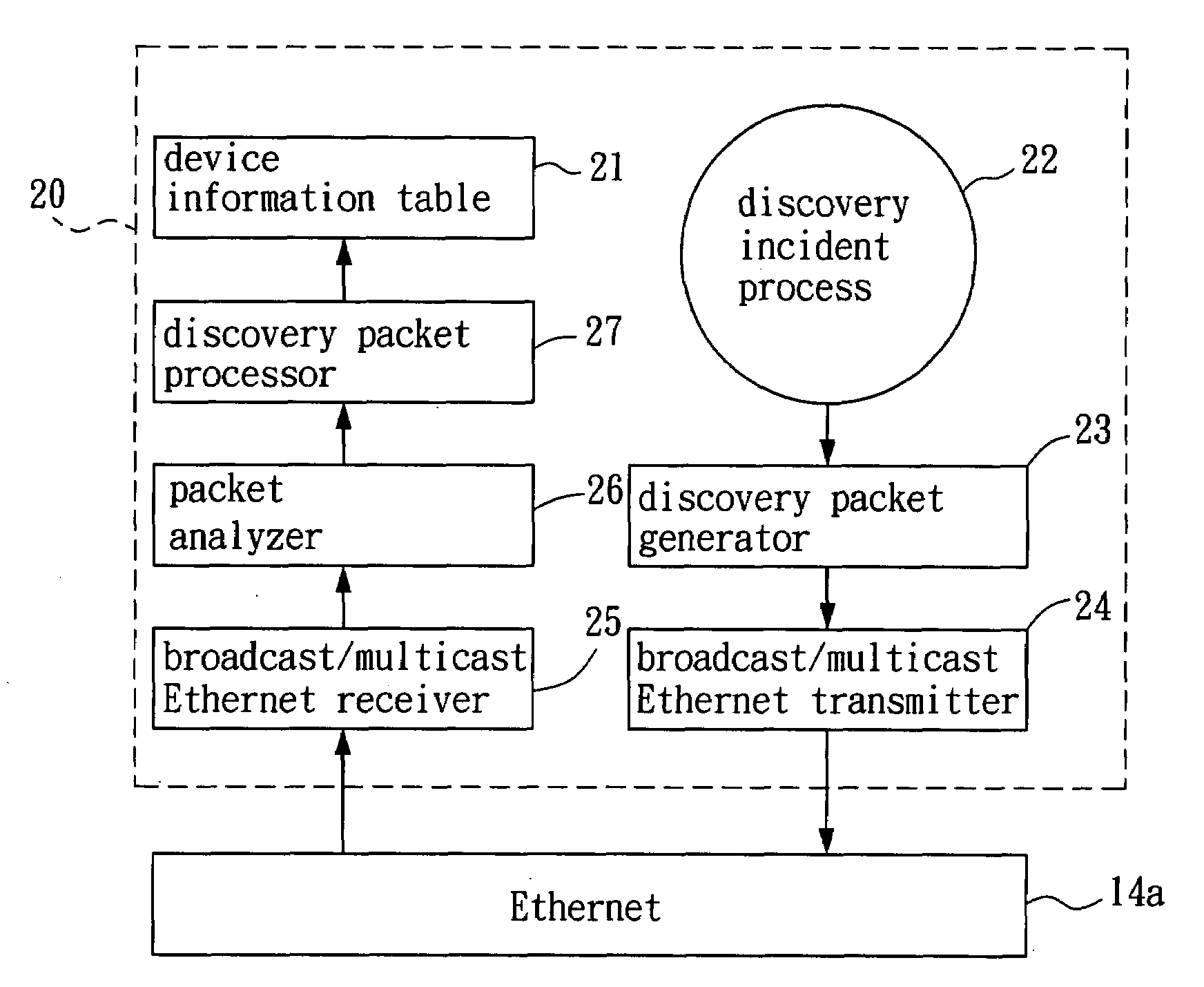

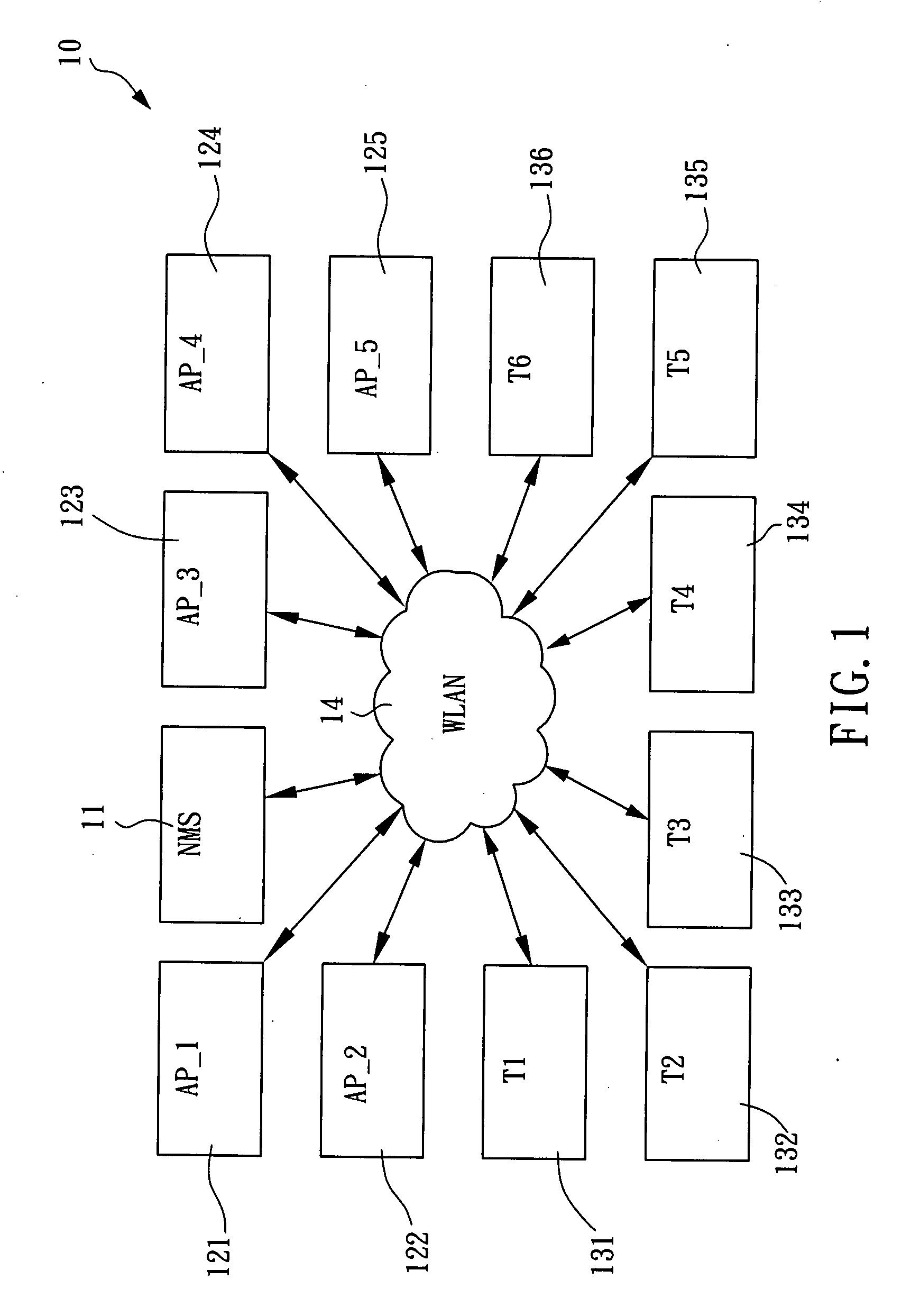

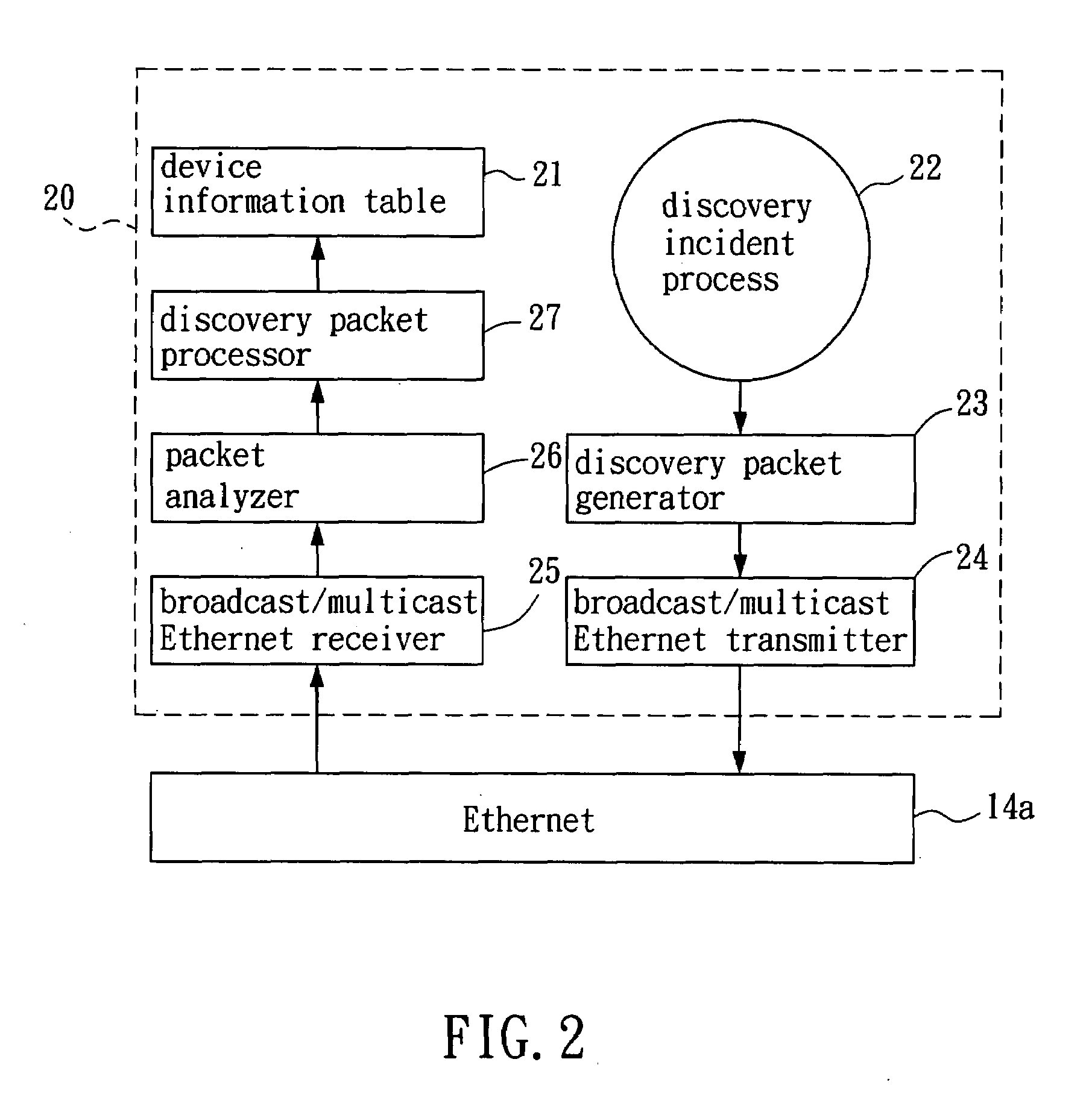

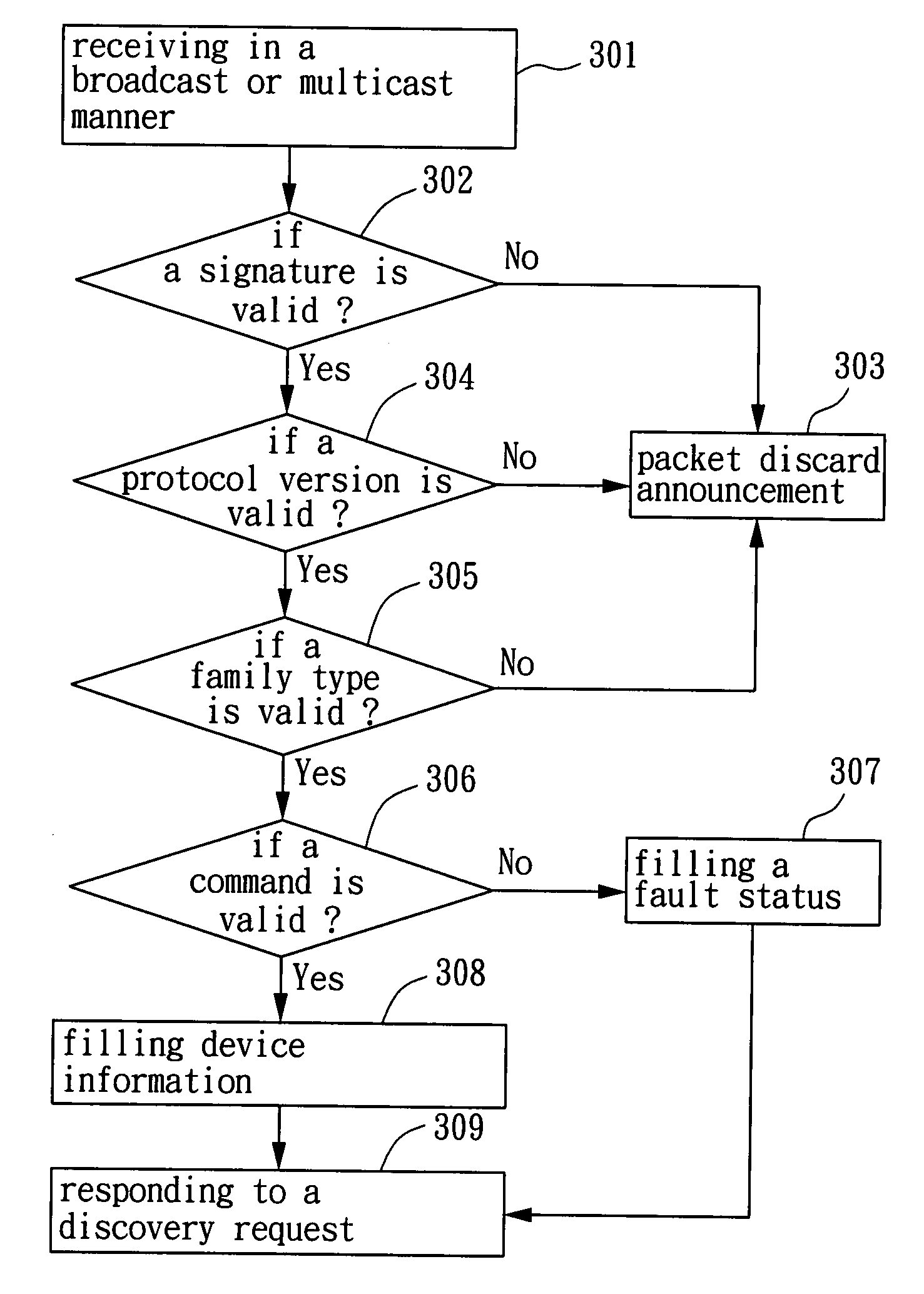

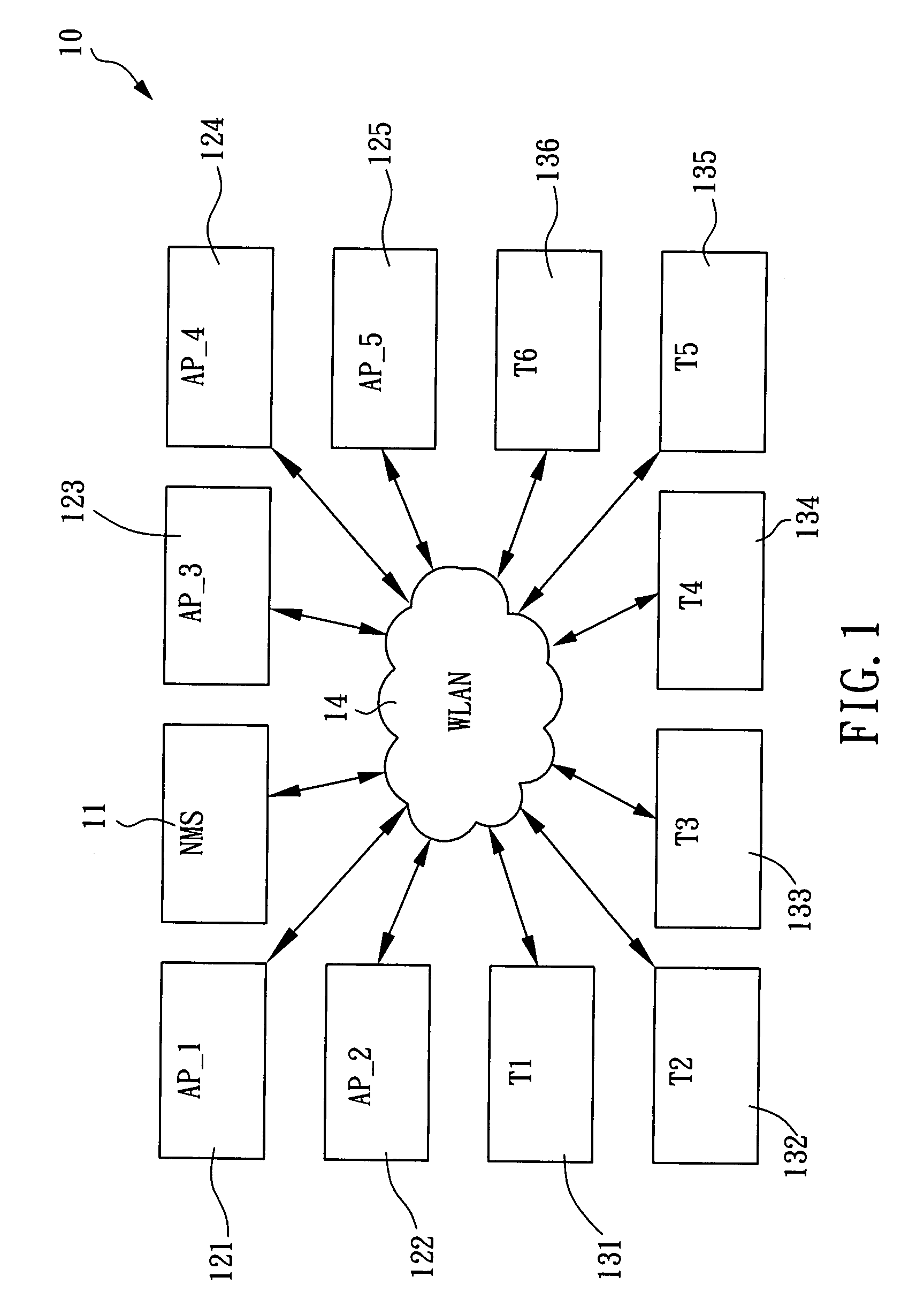

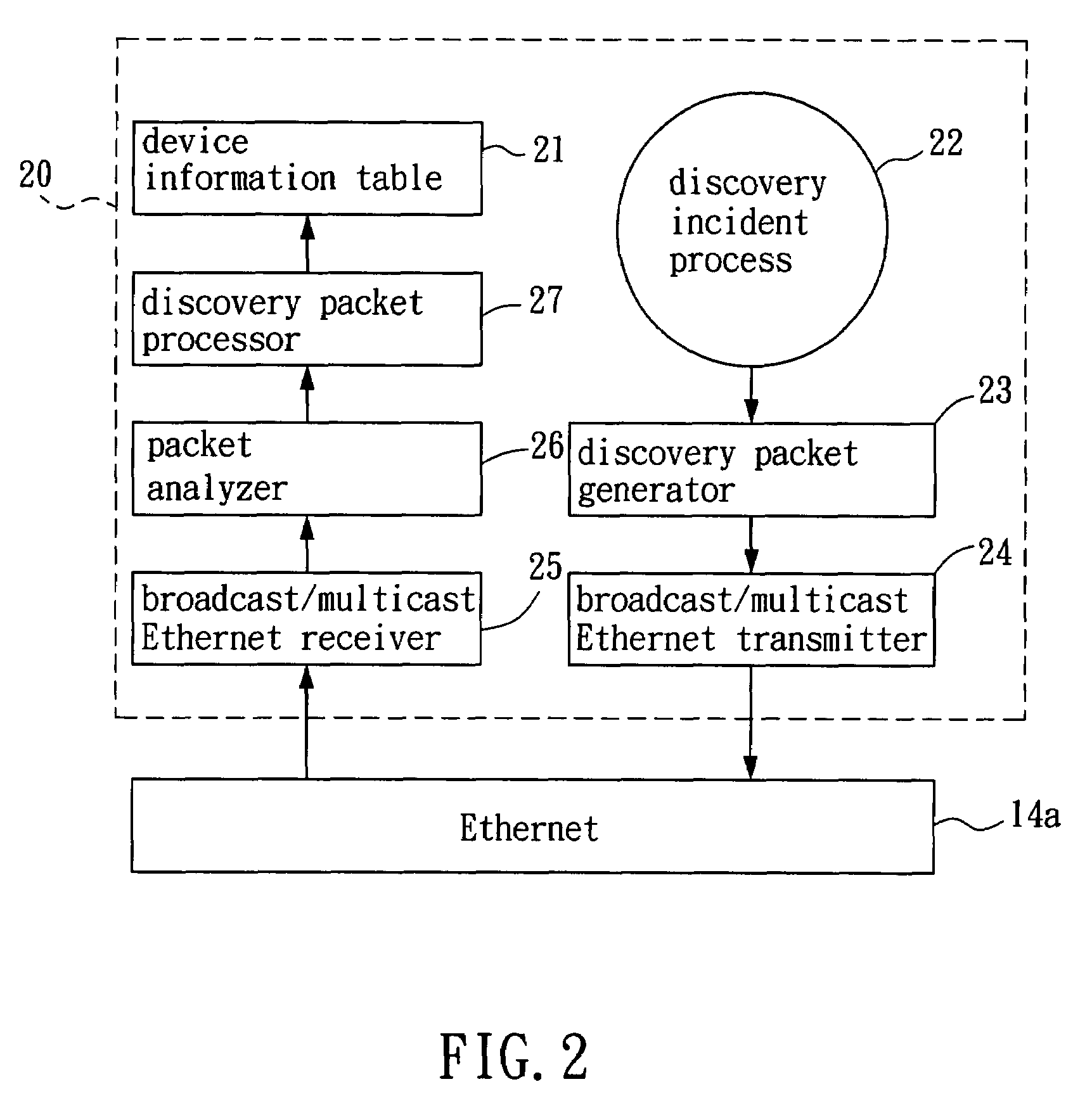

Method for discovering network device

ActiveUS20080089244A1Low hardware and software costExecution efficiency is improvedData switching by path configurationMedia access controlIp address

A method for discovering a network device is disclosed for executing a discovery procedure of the network device in a Data Link Layer (i.e. Layer 2 of OSI 7 Layers Model) via a Network Management Server (NMS) within a Local Area Network (LAN) system to discover other network devices within the LAN. Firstly, sending a discovery packet from a Network Management Server (NMS), wherein the discovery packet comprises a command for requesting the network device to send back a corresponding Media Access Control (MAC) address. Then, receiving the discovery packet by at least one of the network device, and generating a response packet corresponding to the discovery packet for sending the response packet, wherein the response packet comprises the Media Access Control (MAC) address of the network device. Then, receiving the response packet from the NMS for collecting the MAC address while ignoring an IP address in the response packet, and updating a device information table according to the MAC address for identifying the network device.

Owner:CAMEO COMM

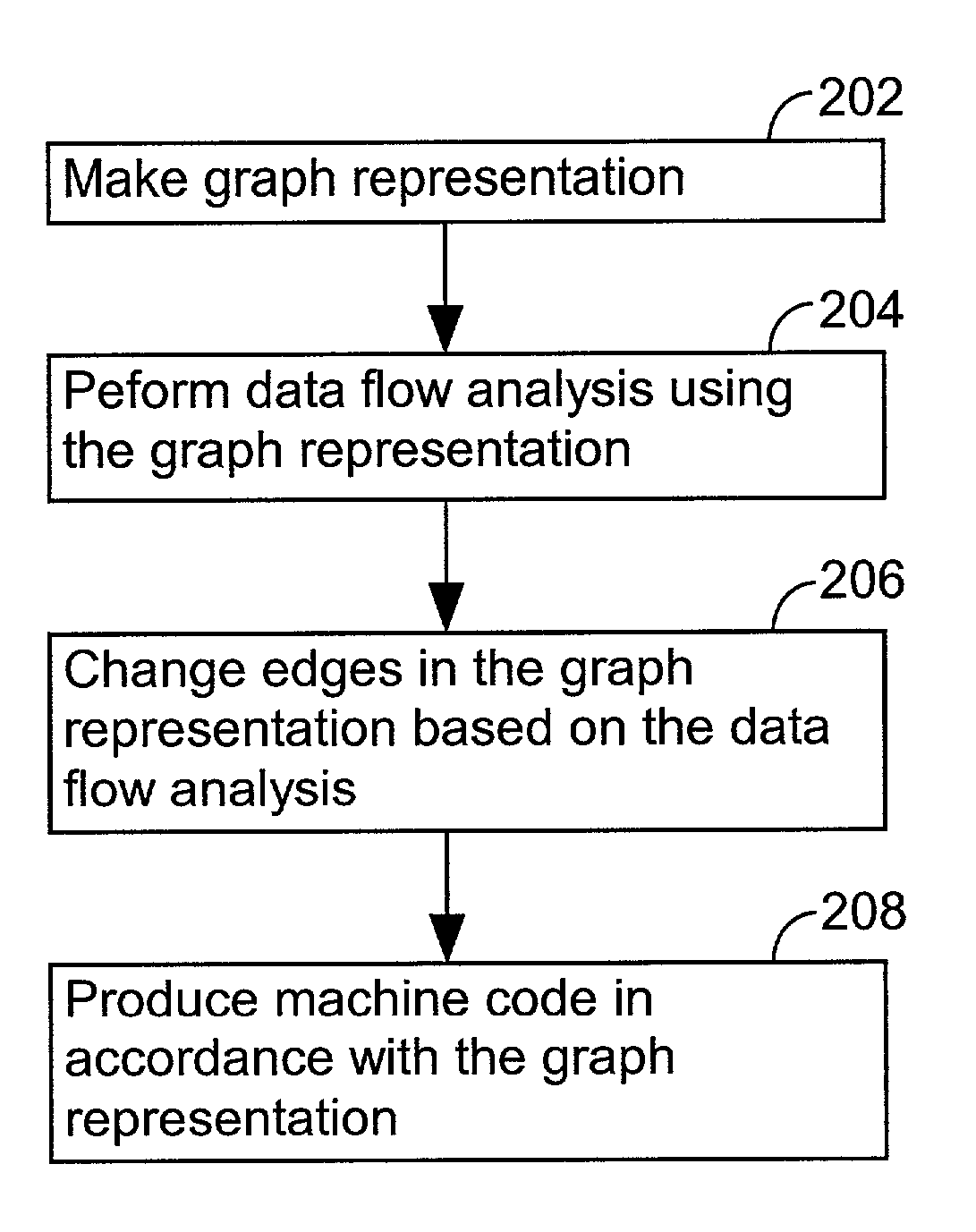

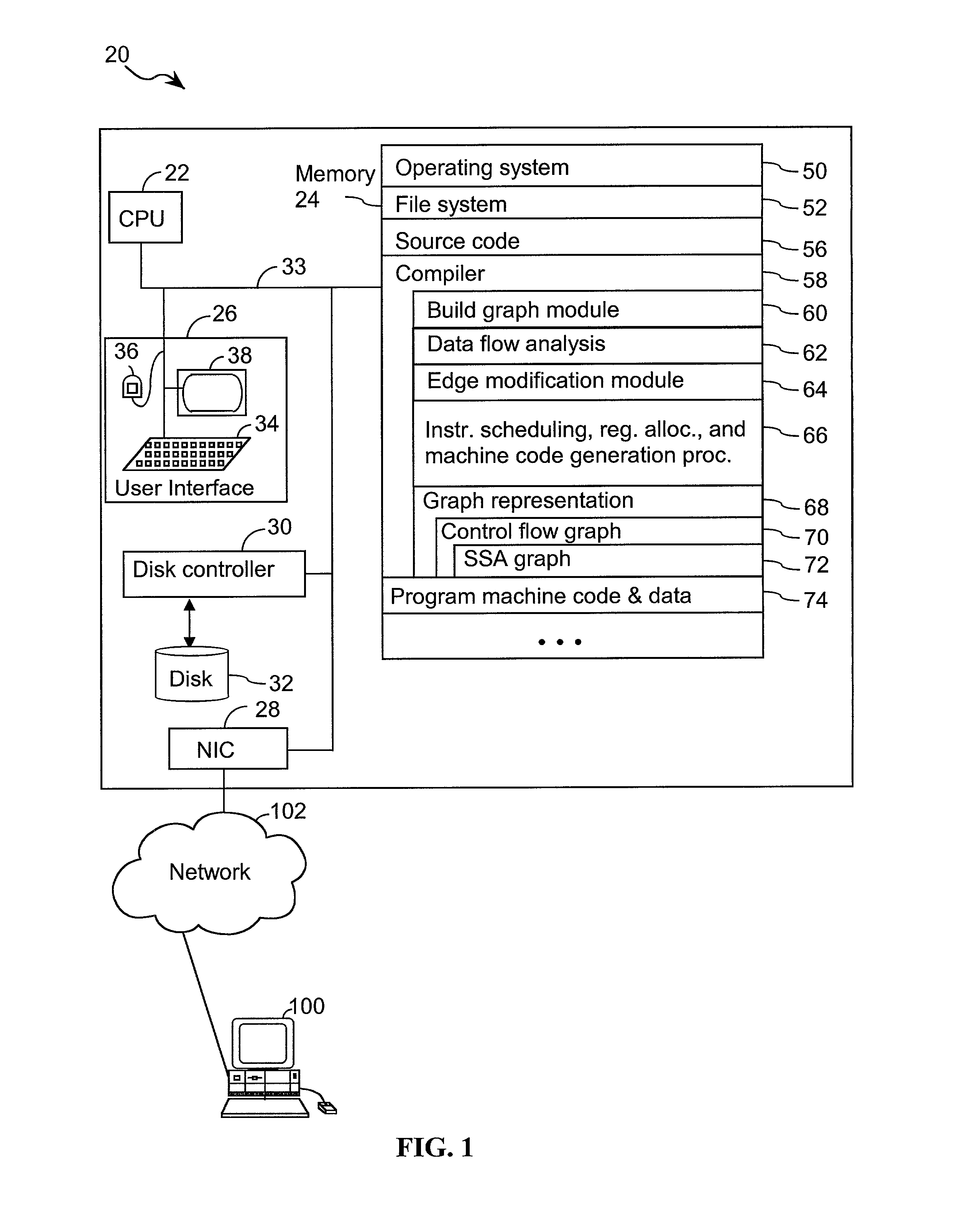

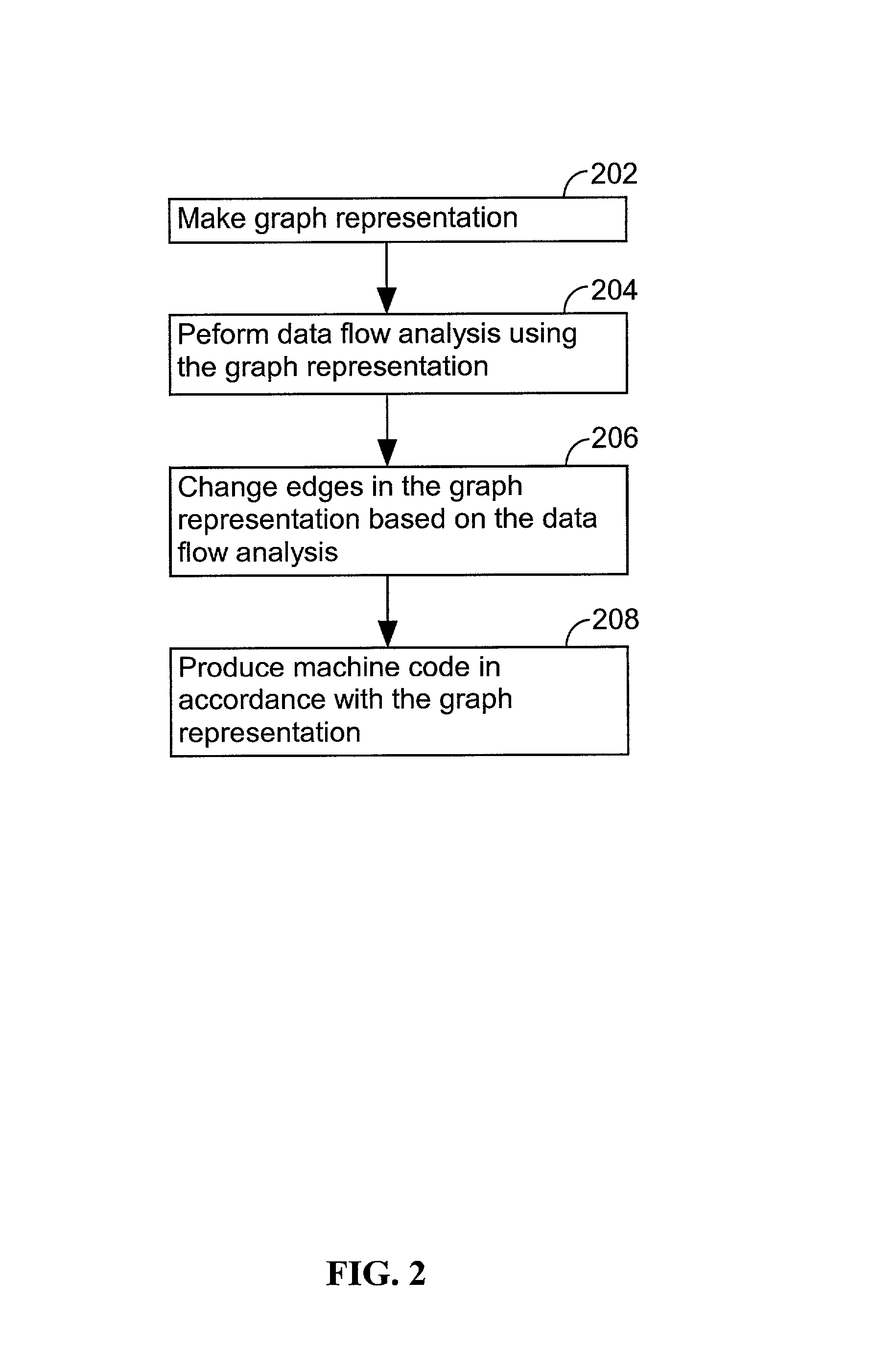

System and method for optimizing operations via dataflow analysis

InactiveUS7185327B2Increase speedGood flexibilitySoftware engineeringSpecific program execution arrangementsGraphicsIntermediate language

A method for modifying serial dependencies in a procedure includes a step of building a graph representation of the procedure. The graph representation has an origin as well as a unique position, relative to the origin, for each memory operation in the procedure. Each memory operation in the representation is designated with a location type. Each of these location types are based on one or more characteristics of the corresponding memory operation that are sufficient to notify the compiler that the memory operation accesses a distinct or disjoint memory location. Memory operations having the same location type as subsequent memory operations are identified. When the graph representation does not include additional memory operations of the same location type between pairs of such memory operations, the subsequent memory operation is moved to a position in the intermediate representation that is closer to the origin.

Owner:HEWLETT PACKARD DEV CO LP

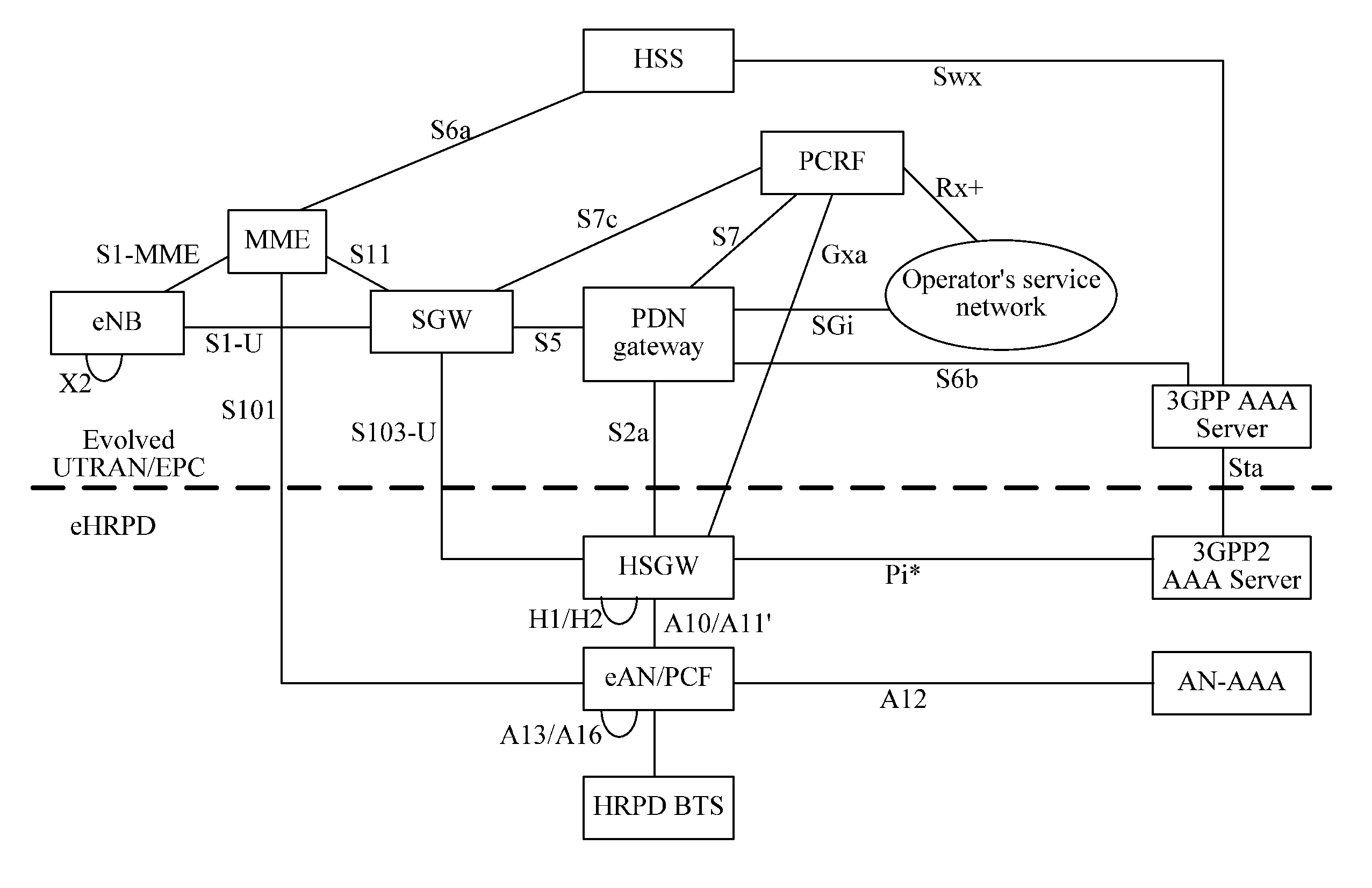

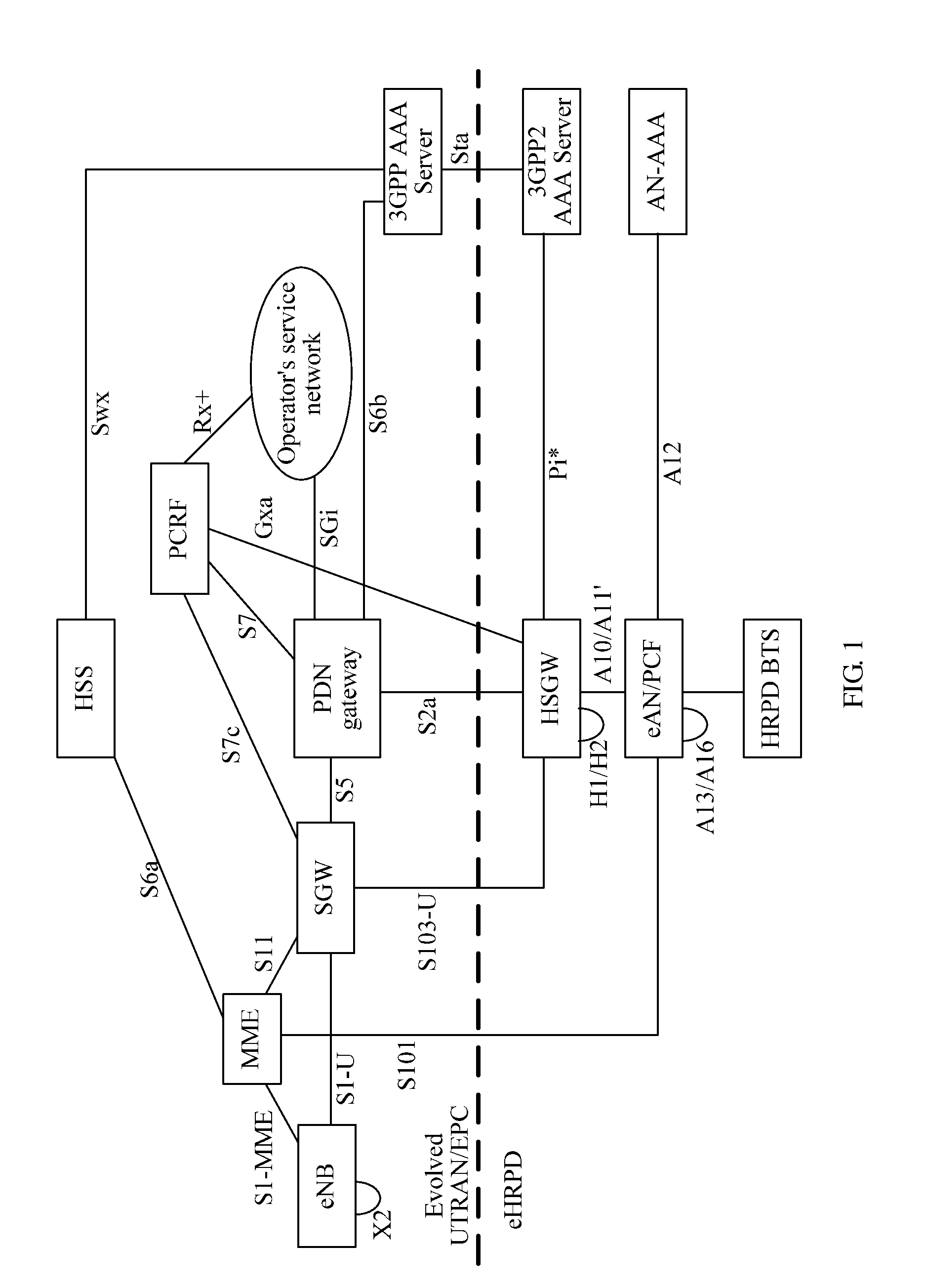

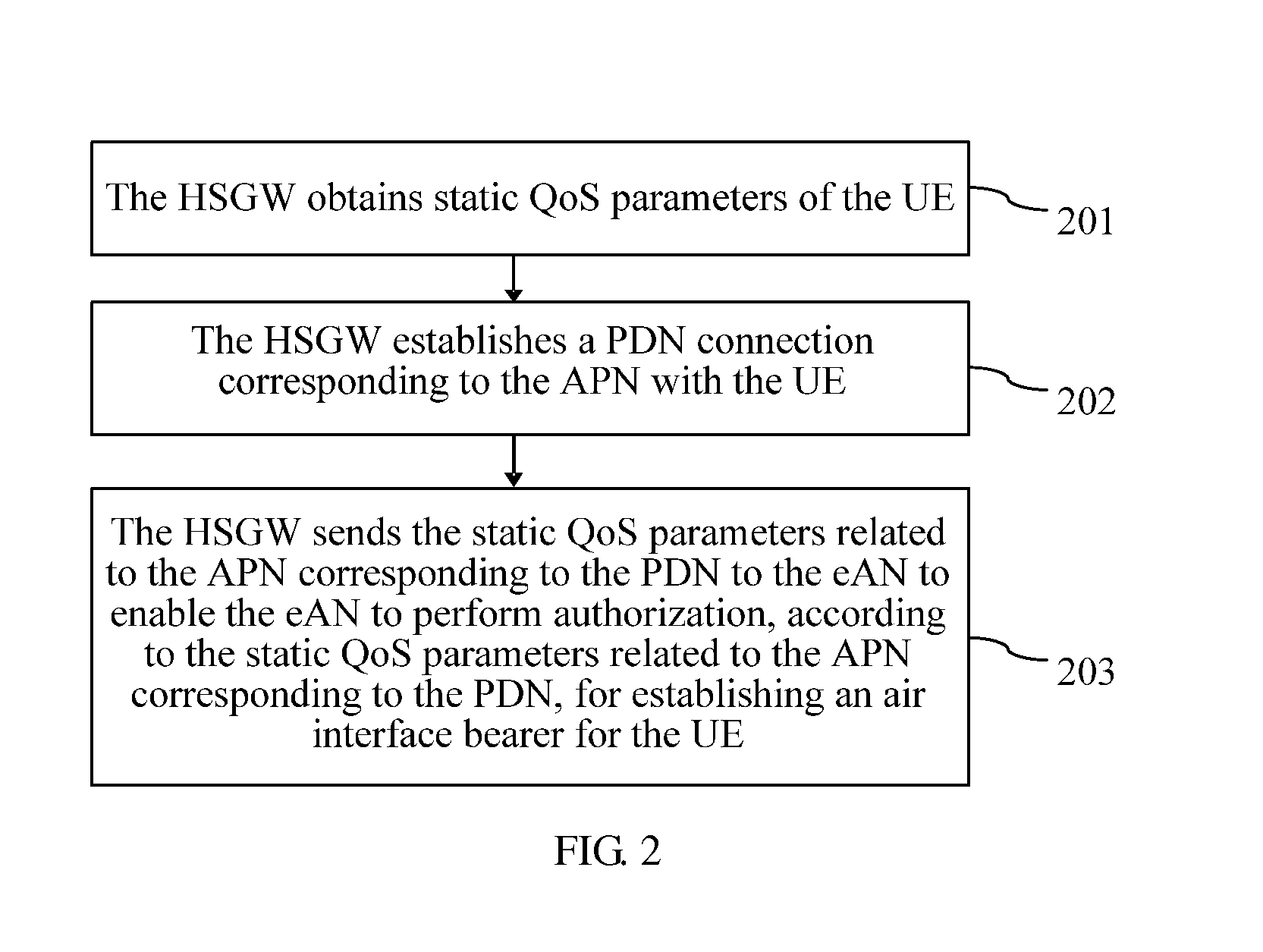

Method and Apparatus for Negotiation Control of Quality of Service Parameters

InactiveUS20120069763A1Reduce processing loadExecution efficiency is improvedError preventionFrequency-division multiplex detailsAccess networkQuality of service

A method and an apparatus for negotiation control of Quality of Service (QoS) parameters are provided. The method includes: obtaining, by a High Rate Packet Data (HRPD) Serving Gateway (HSGW), static QoS parameters of a User Equipment (UE), where the static QoS parameters include static QoS parameters related to an Access Point Name (APN); establishing, by the HSGW, a Packet Data Network (PDN) connection corresponding to the APN with the UE; and sending, by the HSGW, static QoS parameters related to the APN corresponding to the PDN to an access network to enable the access network to perform QoS authorization, according to the static QoS parameters related to the APN corresponding to the PDN, for establishing an air interface bearer for the UE.

Owner:HUAWEI TECH CO LTD

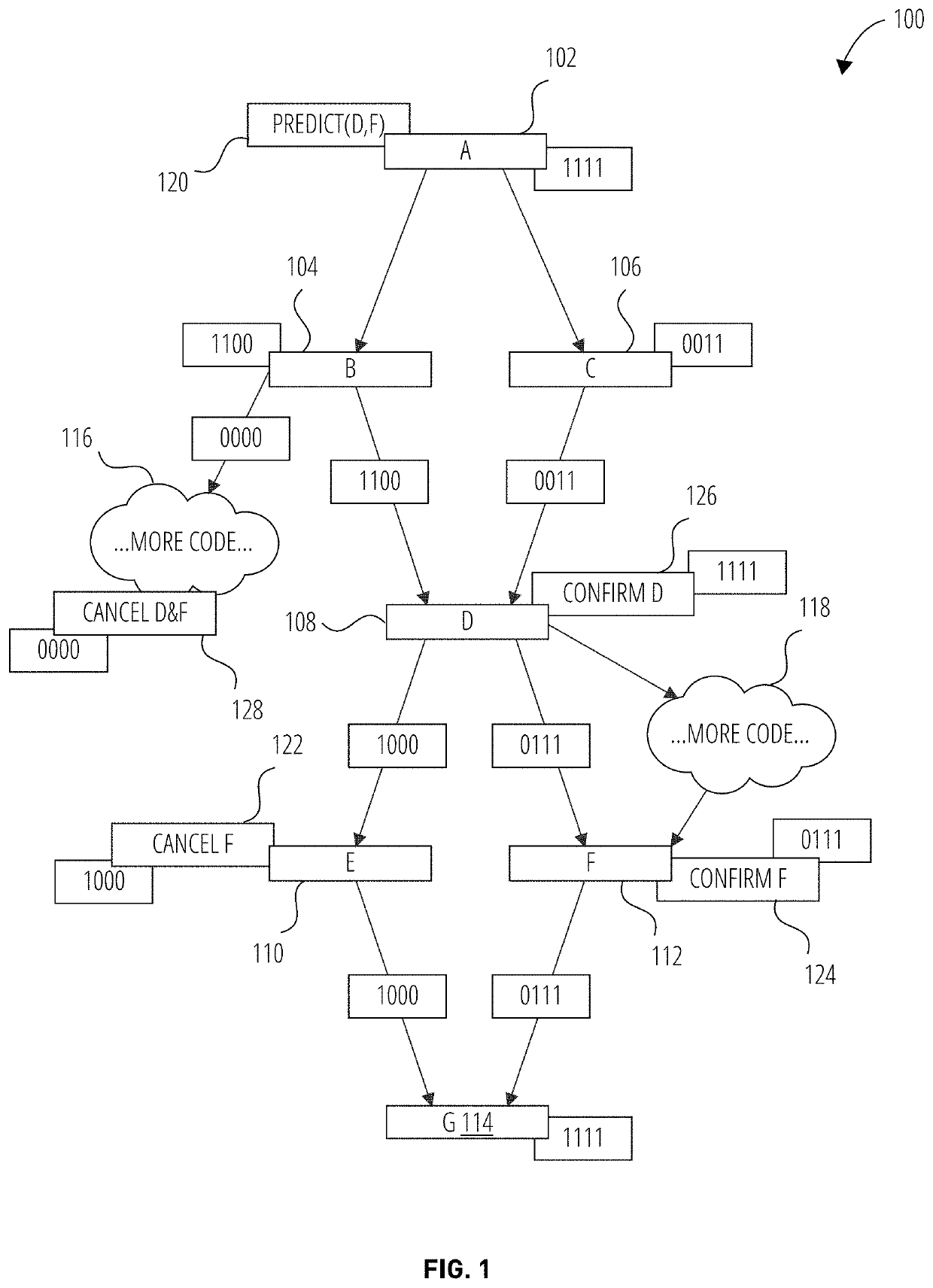

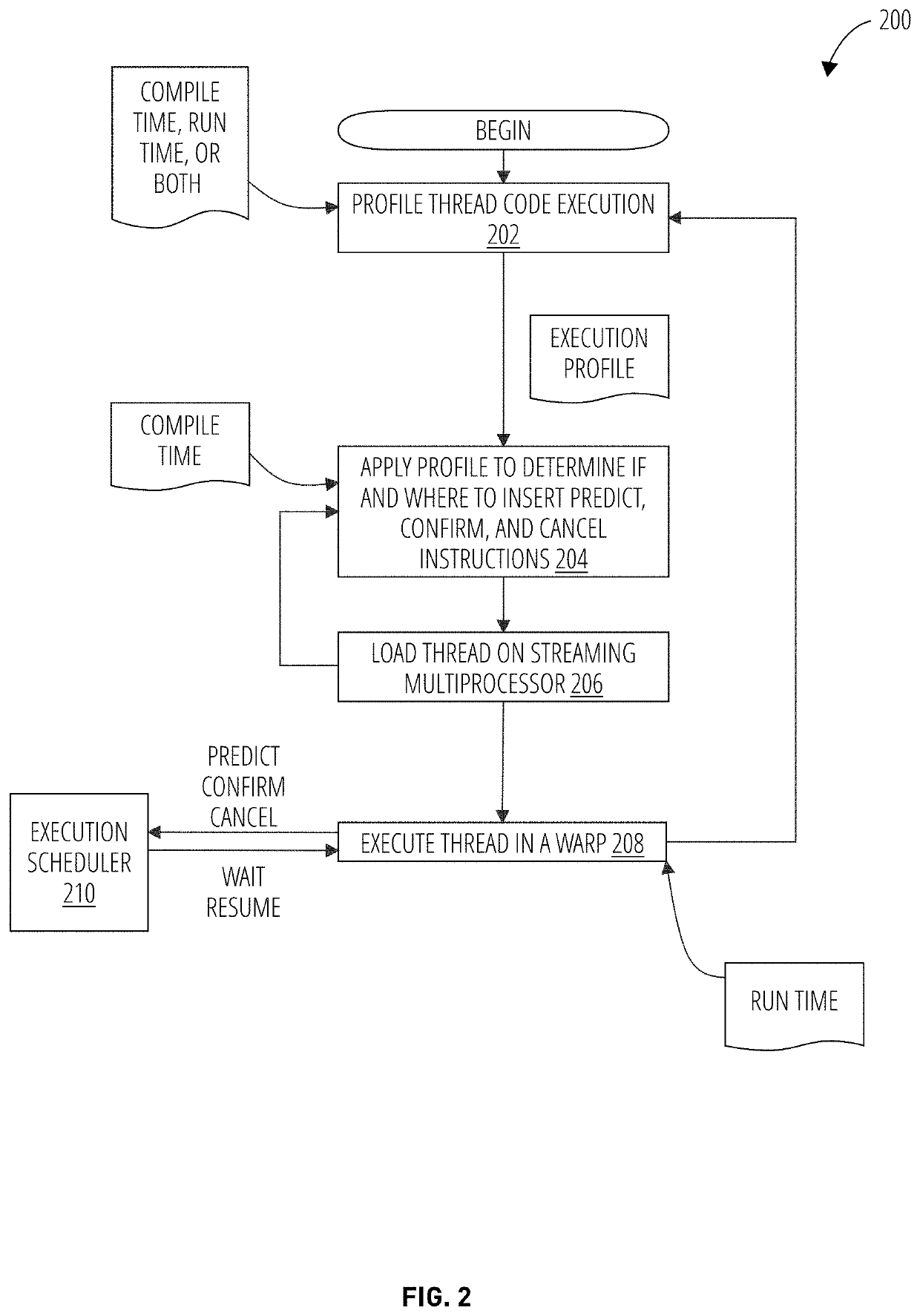

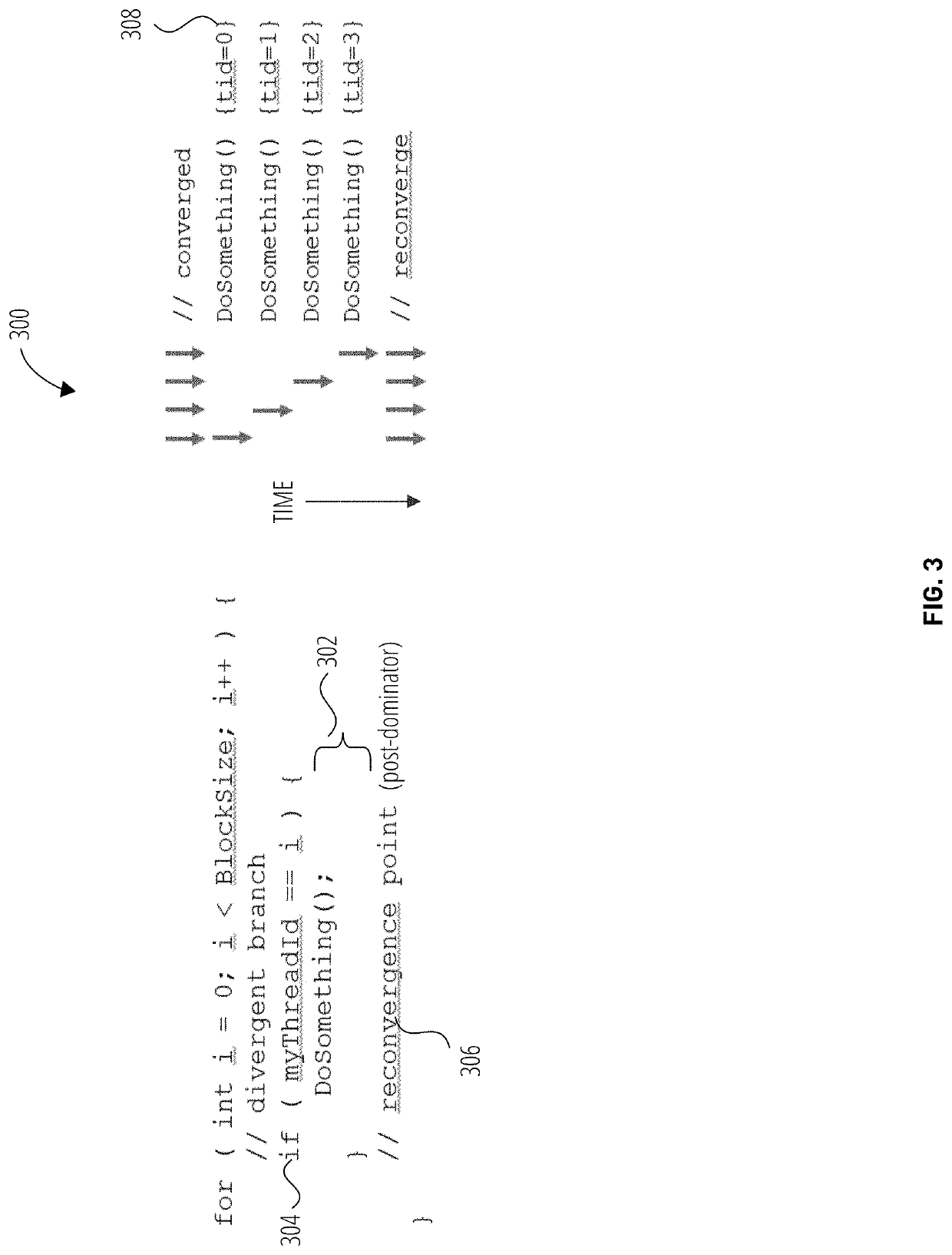

Convergence among concurrently executing threads

ActiveUS20200081748A1Execution efficiency is improvedPromoting thread convergenceProgram initiation/switchingProgram synchronisationComputer architectureThread scheduling

Convergence of threads executing common code sections is facilitated using instructions inserted at strategic locations in computer code sections. The inserted instructions enable the threads in a warp or other group to cooperate with a thread scheduler to promote thread convergence.

Owner:NVIDIA CORP

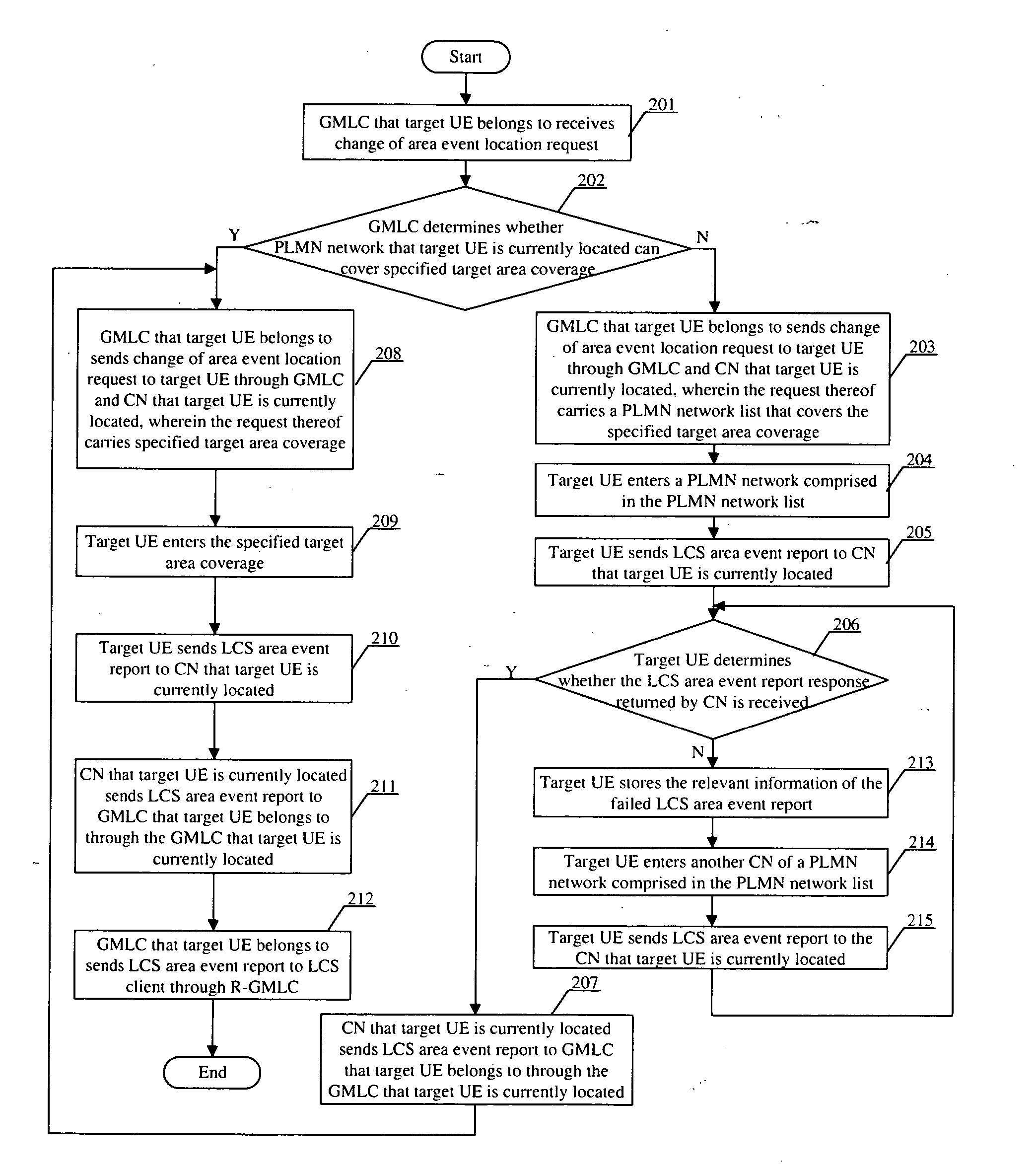

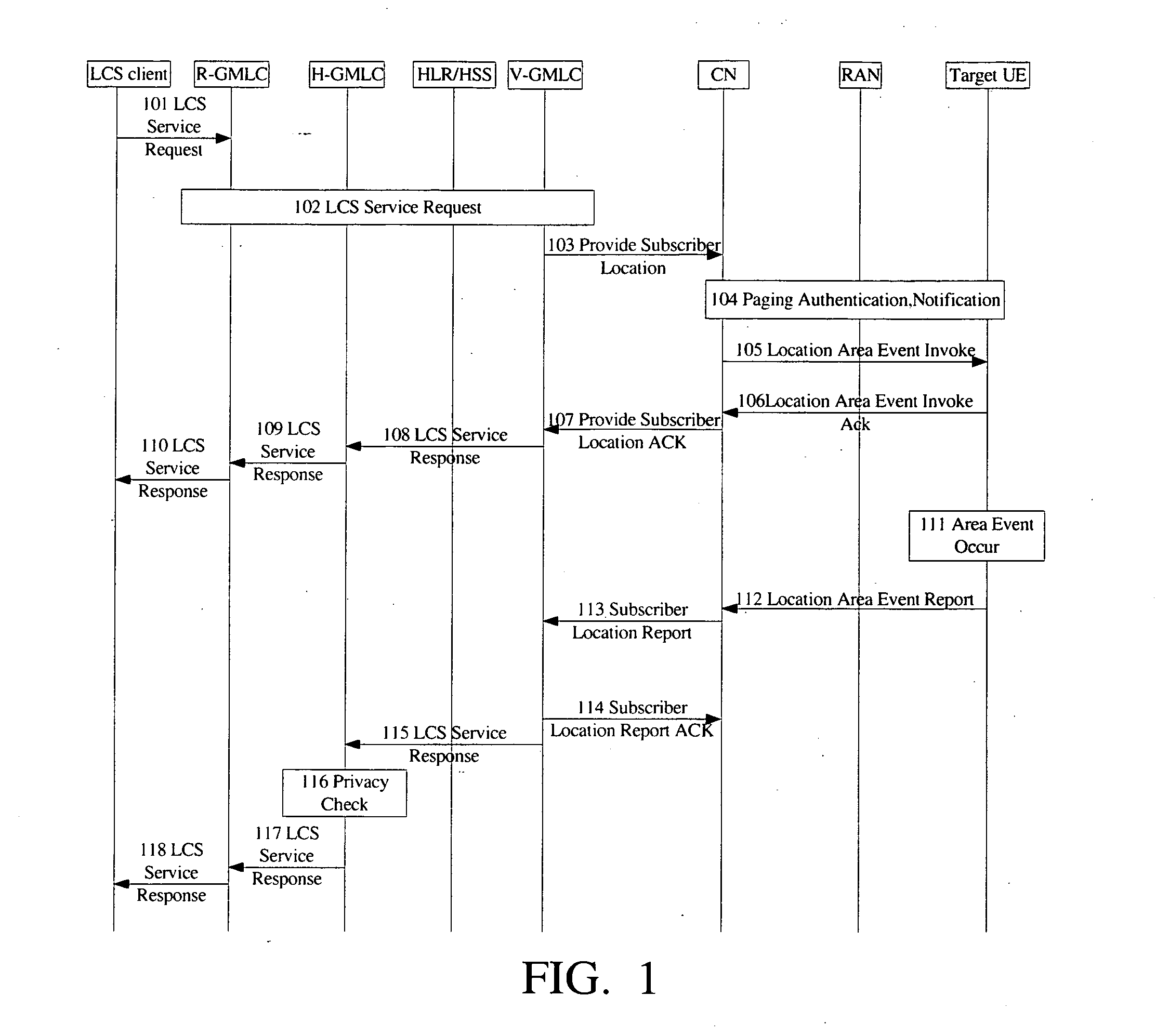

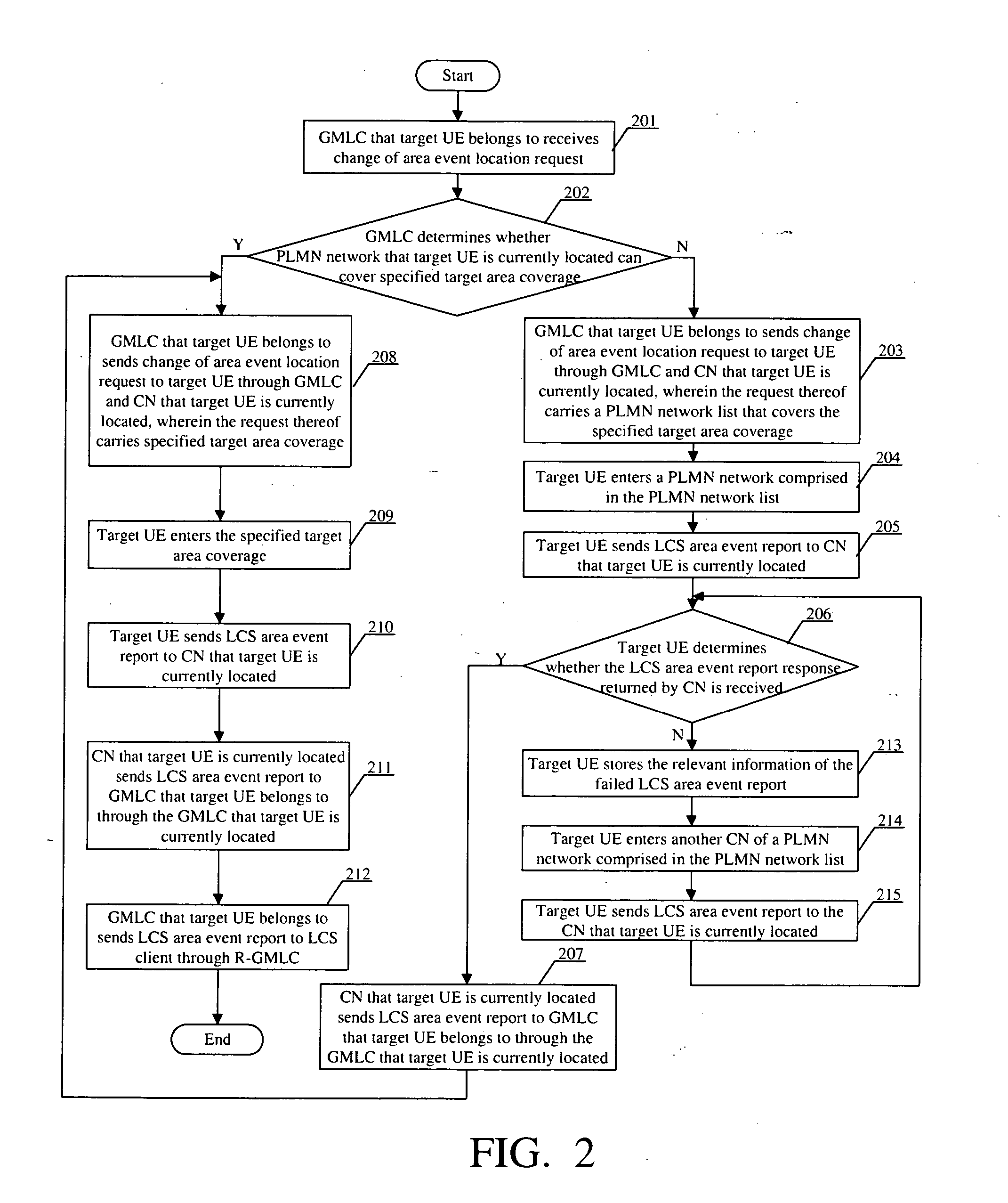

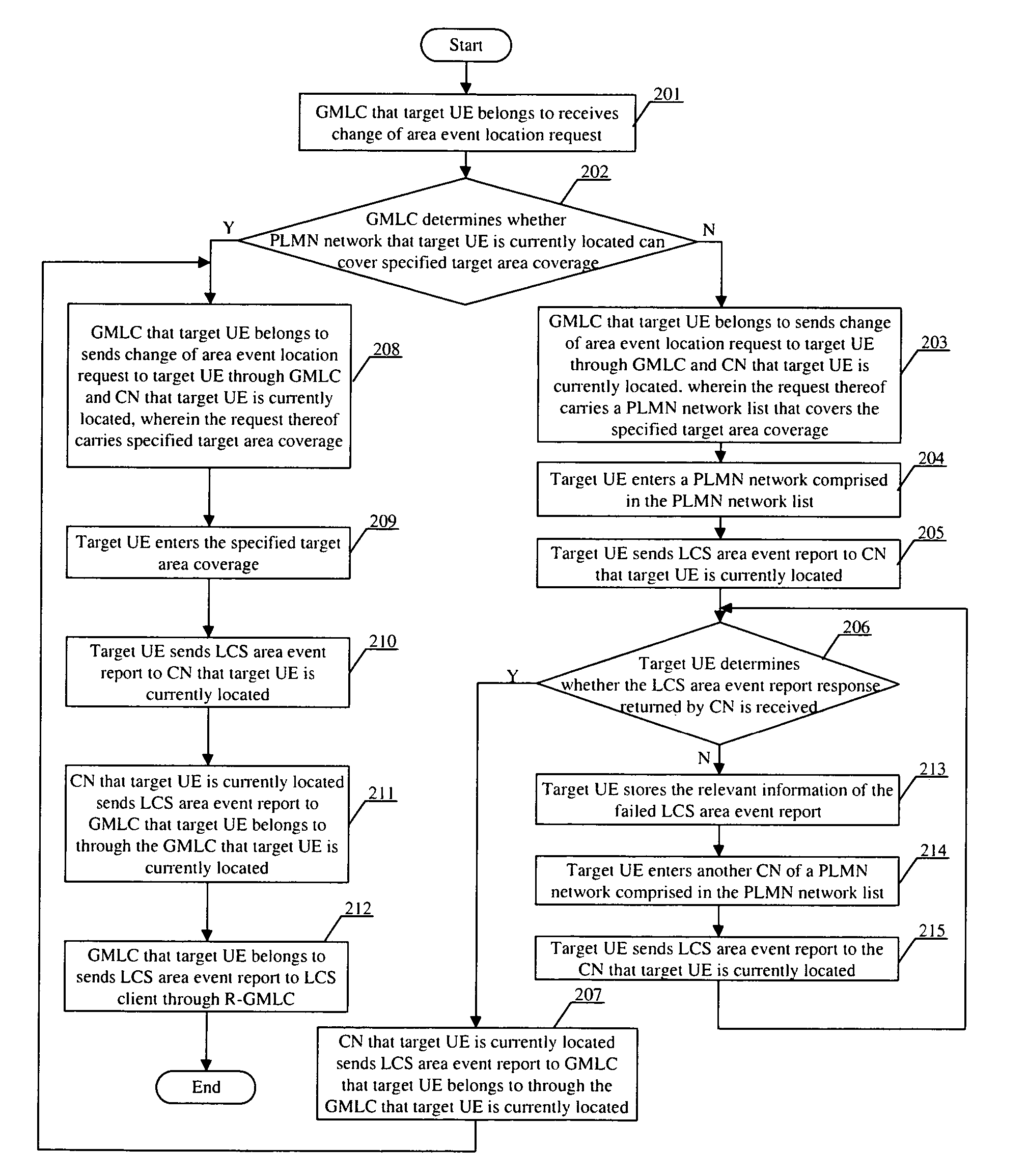

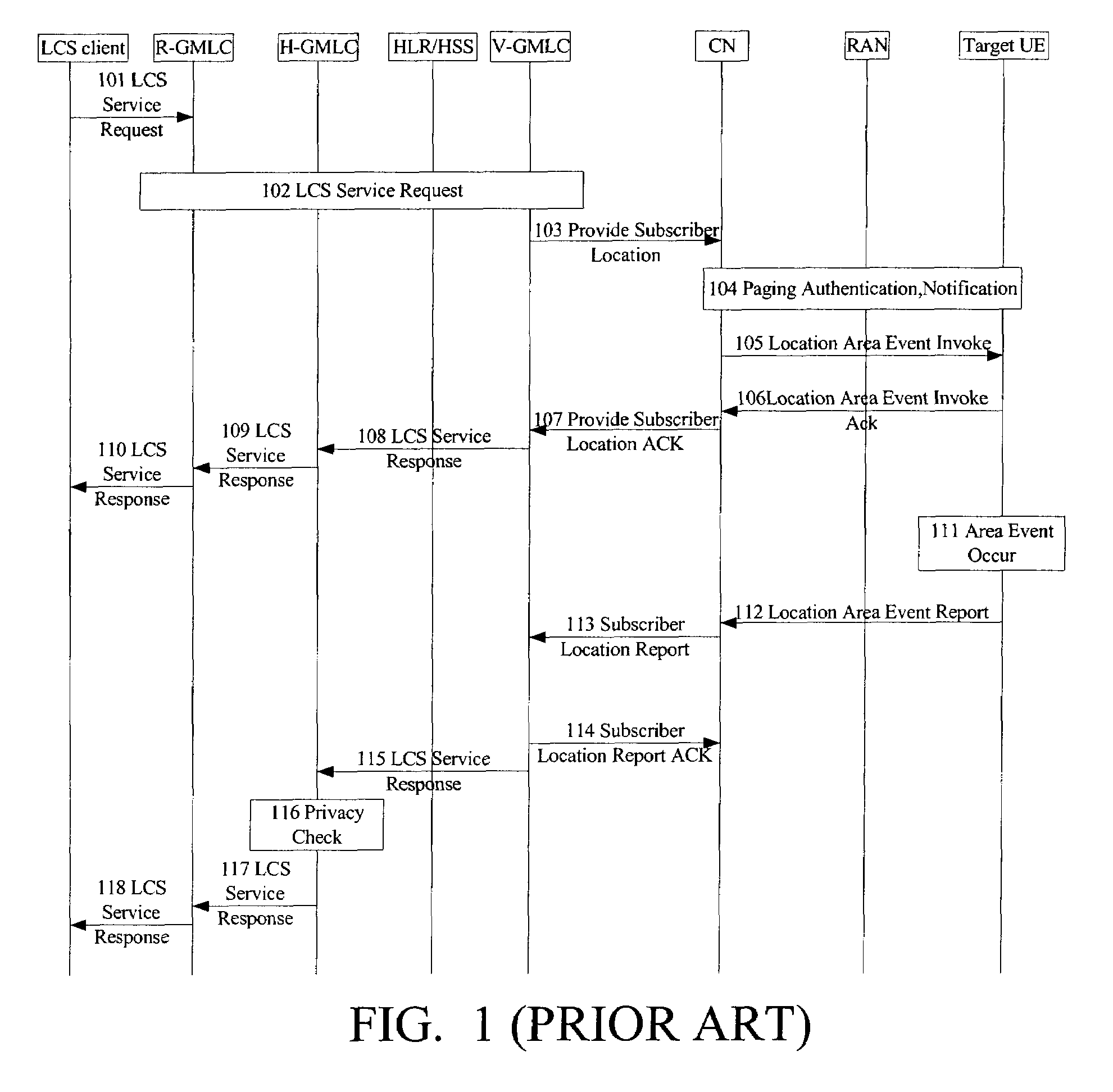

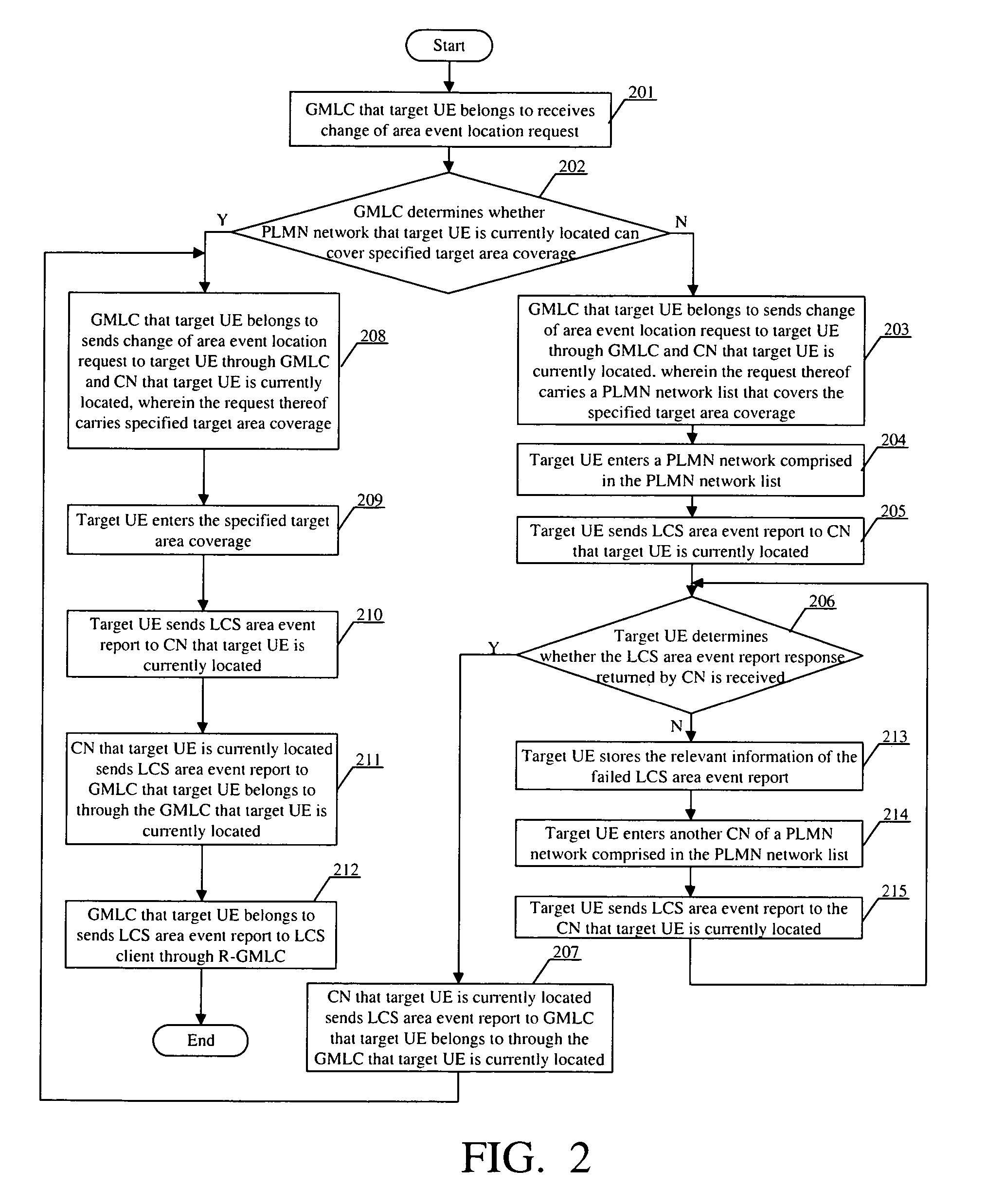

Method of sending a location report from target user equipment

ActiveUS20060105788A1Avoid wastingExecution efficiency is improvedServices signallingRadio/inductive link selection arrangementsUser equipmentMobile communication network

Disclosed herein is a method useful for target user equipment (UE) sending a location report. When the target UE is located in a first central network (CN) of a location service (LCS) system, the target UE reports the location report to the LCS system. If the target UE does not receive a location report response from the LCS system, when being located in a second CN of LCS system, target UE will continue to report the location report to LCS system. In accordance with one aspect of the disclosed method, the waste of location service system resource is avoided as well as the execution efficiency of location service is increased. In addition, during procedure of change of area event location request, the consequent processing of request thereof is guaranteed to be normal, so that execution efficiency of location service is increased. Moreover, message interaction between the function entities is saved for the exception cases. Accordingly, the waste of public land mobile communication network resource caused by generation of excessive useless messages is avoided.

Owner:HUAWEI TECH CO LTD

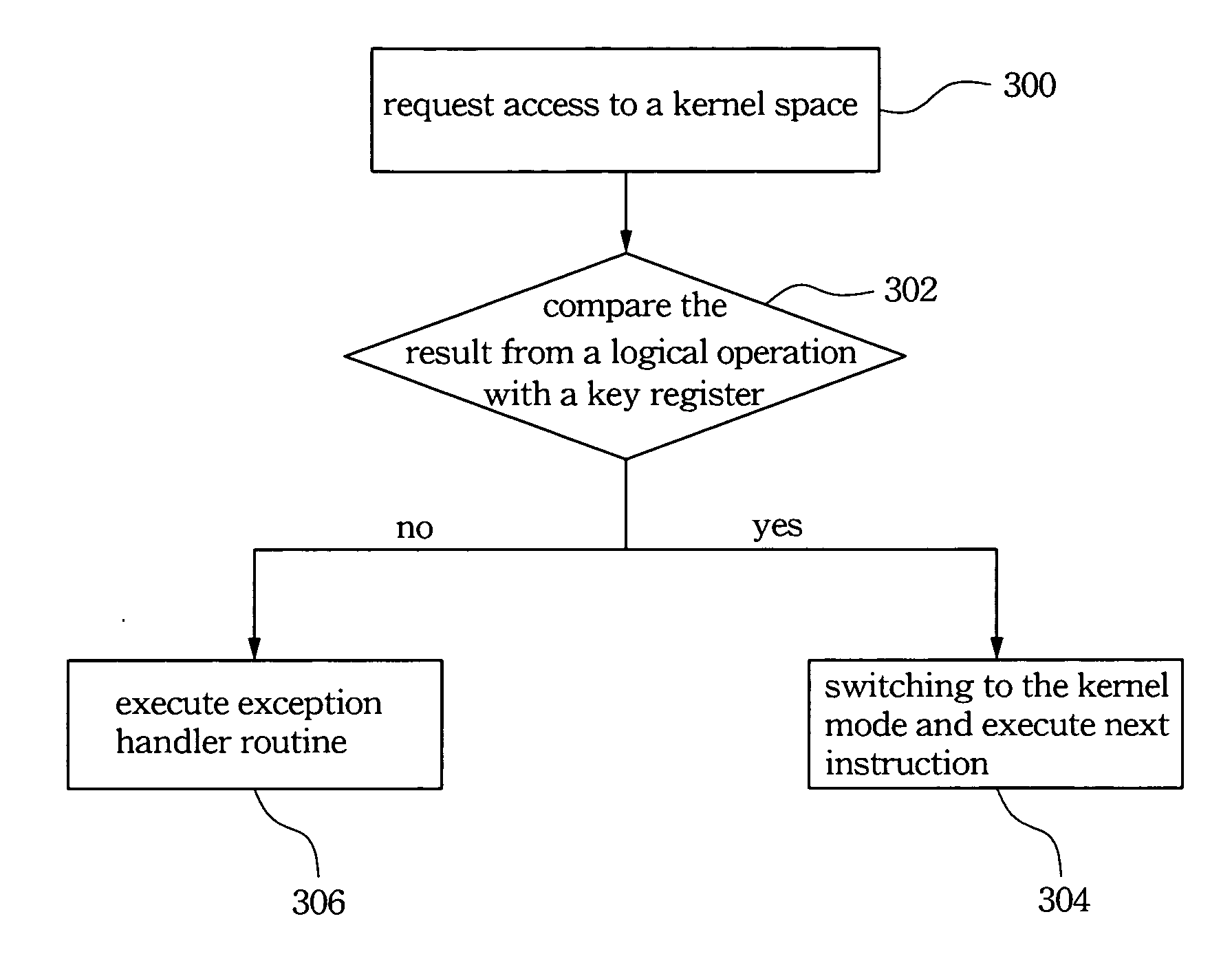

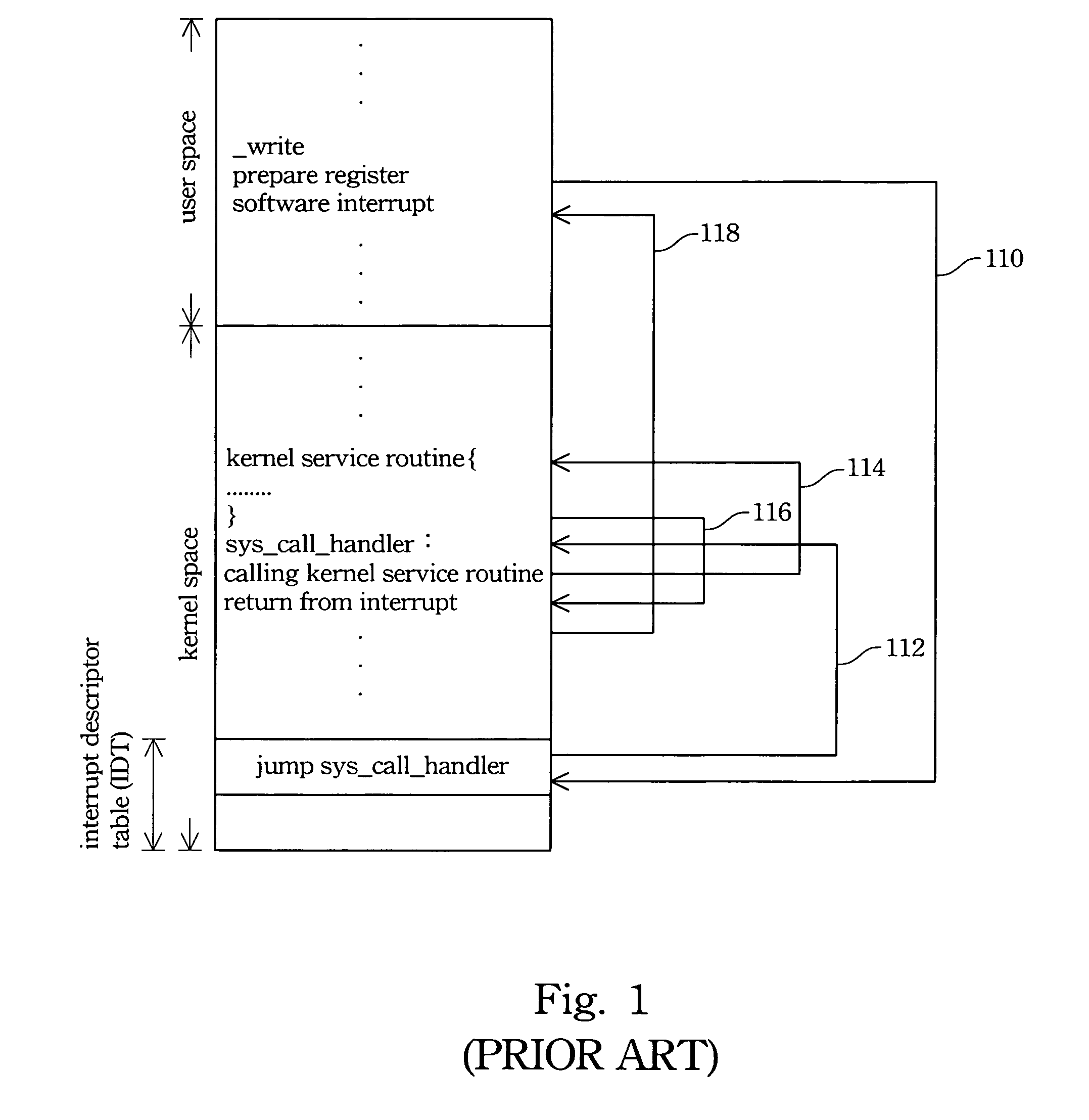

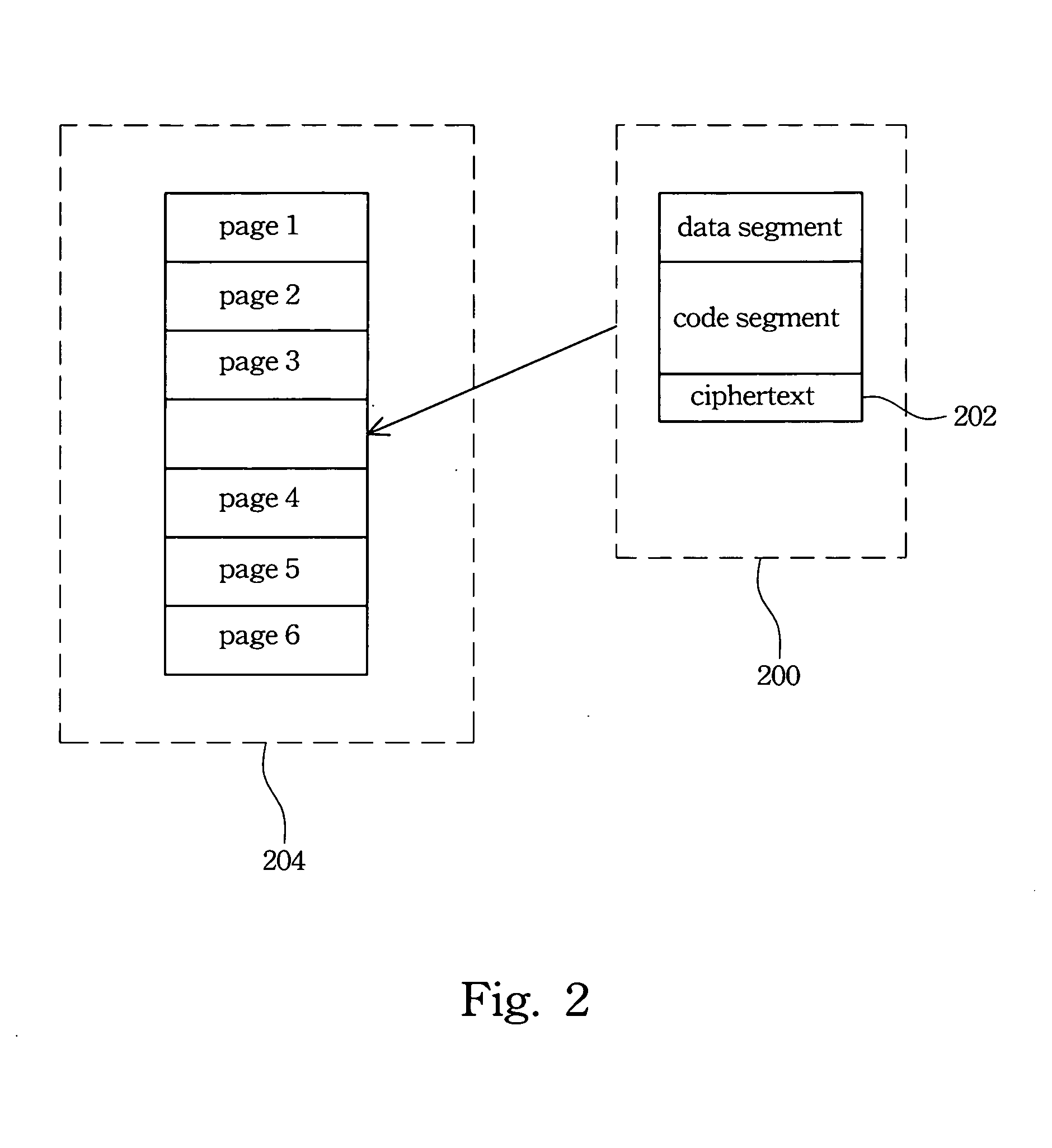

Fast system call method

ActiveUS20080046725A1Execution efficiency is improvedSimple and safe processUser identity/authority verificationUnauthorized memory use protectionRelevant informationOperational system

A method of a fast system call is provided. First, a logical operation to compute a kernel service routine is used. Then the logical operation result is compared with ciphertext from a key register. At least one input for the logical operation is from the relevant information of the required kernel service routine. For example, the start address of the kernel service routine or the content of the start address of the kernel service routine, or combinations thereof. If the logical operation result equals to the ciphertext of the key register, a switch from a user mode to a kernel mode to read the kernel service routine is allowed. Otherwise, the central processing system executes a corresponding exceptional handler routine. Then the operating system terminates the mode switch request and reports an error to the operating system.

Owner:NATIONAL CHUNG CHENG UNIV

Optimum code generation method and compiler device for multiprocessor

ActiveUS8296746B2Execution efficiency is improvedReduce the amount of data transferredSoftware engineeringProgram controlUser inputParallel computing

A method of generating optimum parallel codes from a source code for a computer system configured of plural processors that share a cache memory or a main memory is provided. A preset code is read and operation amounts and process contents are analyzed while distinguishing dependence and independence among processes from the code. Then, the amount of data to be reused among processes is analyzed, and the amount of data that accesses the main memory is analyzed. Further, upon the reception of a parallel code generation policy inputted by a user, the processes of the code are divided, and while estimating an execution cycle from the operation amount and process contents thereof, the cache use of the reuse data, and the main memory access data amount, a parallelization method with which the execution cycle becomes shortest is executed.

Owner:HITACHI LTD

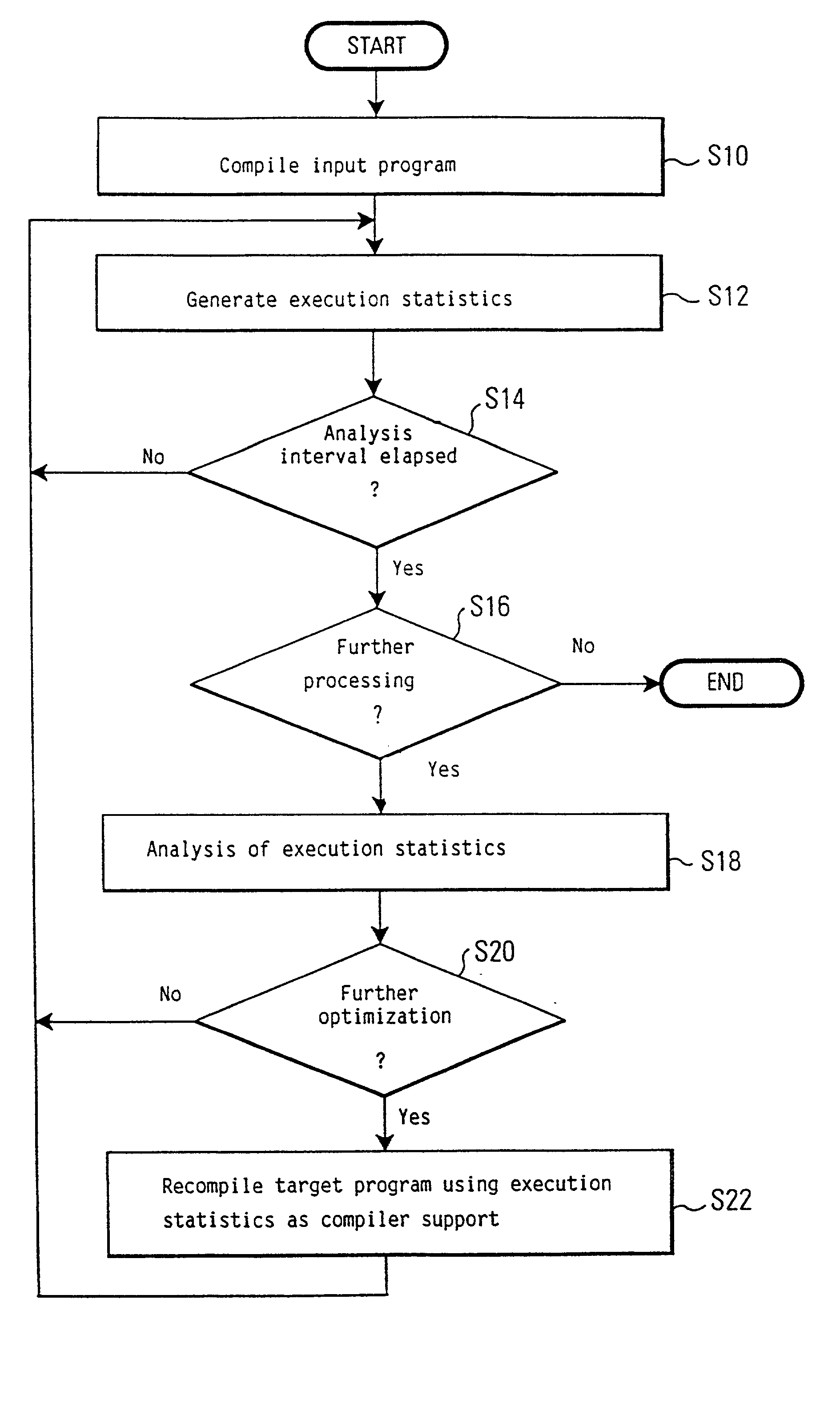

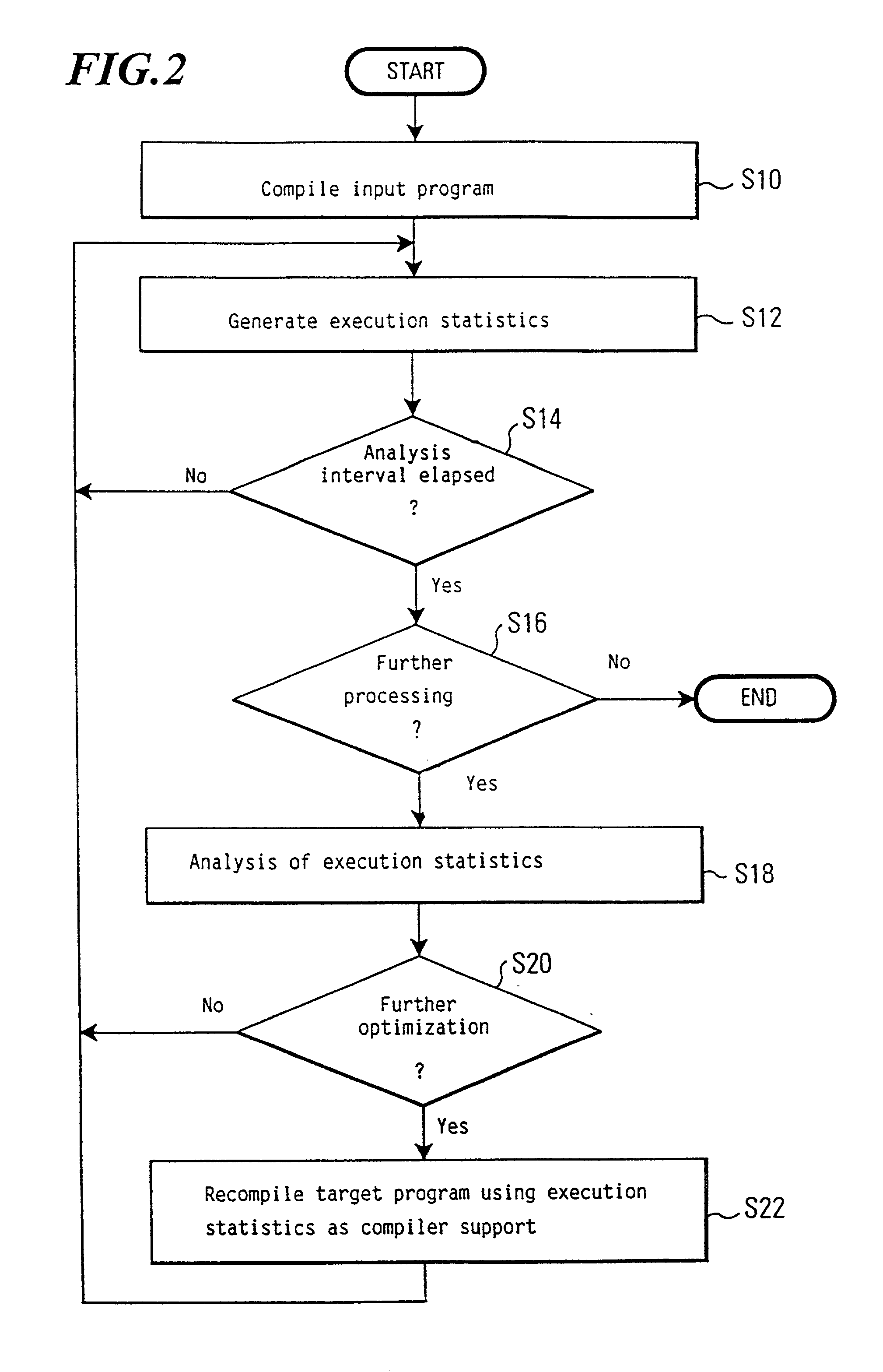

Program profiling

InactiveUS20020010913A1Execution efficiency is improvedHardware monitoringProgram controlParallel computingProgram analysis

To improve the overall execution efficiency for the execution of a program submitted to a virtual machine, there is proposed a program profiling method for a virtual machine starting with a compilation of a submitted program to generate a target program (S10). Then, the target program is executed to generate execution statistics (S12) being stored in a jump memory (28). Finally, the target program is recompiled (S22) using the execution statistics stored in the jump memory (28) as compiler support.

Owner:TELEFON AB LM ERICSSON (PUBL)

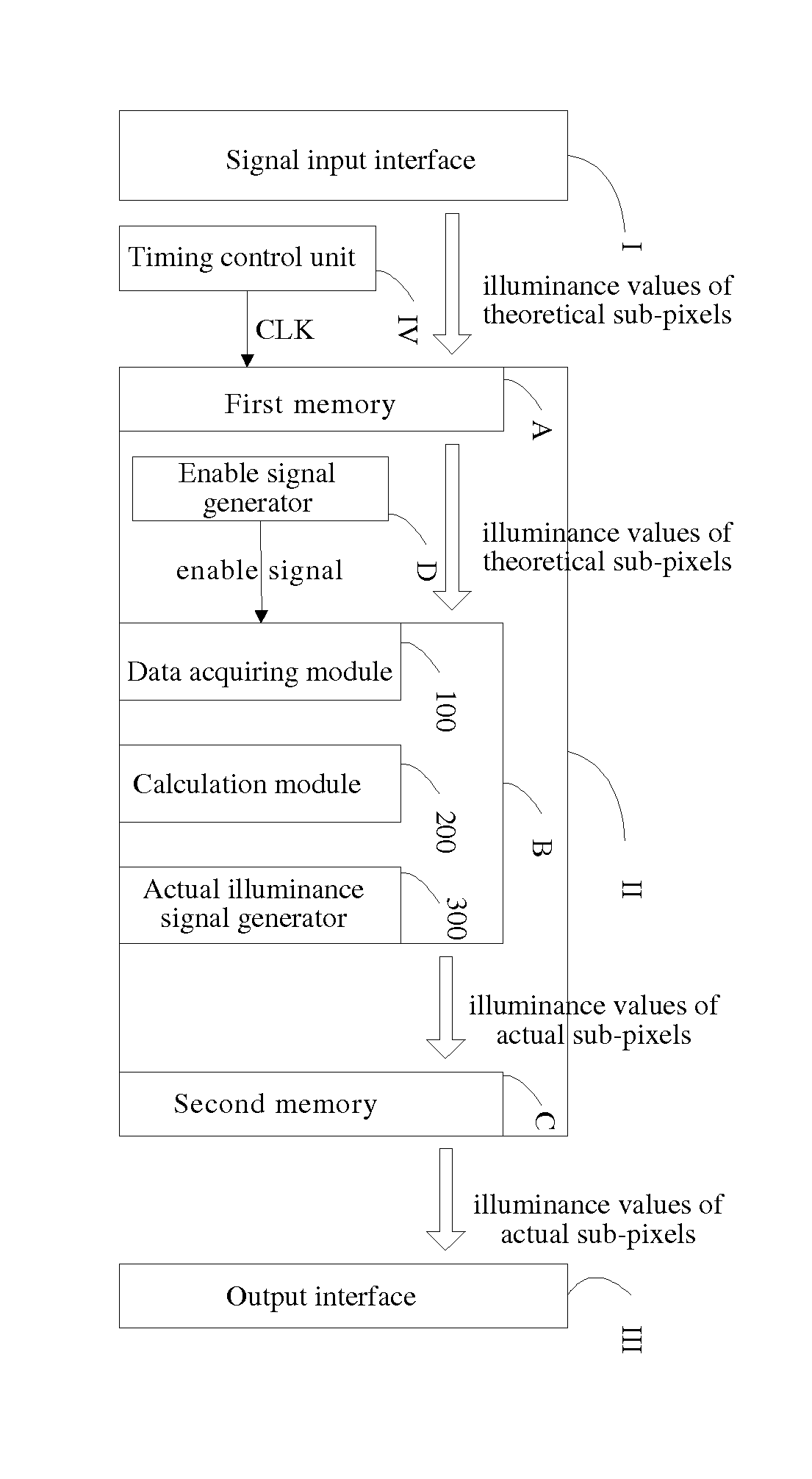

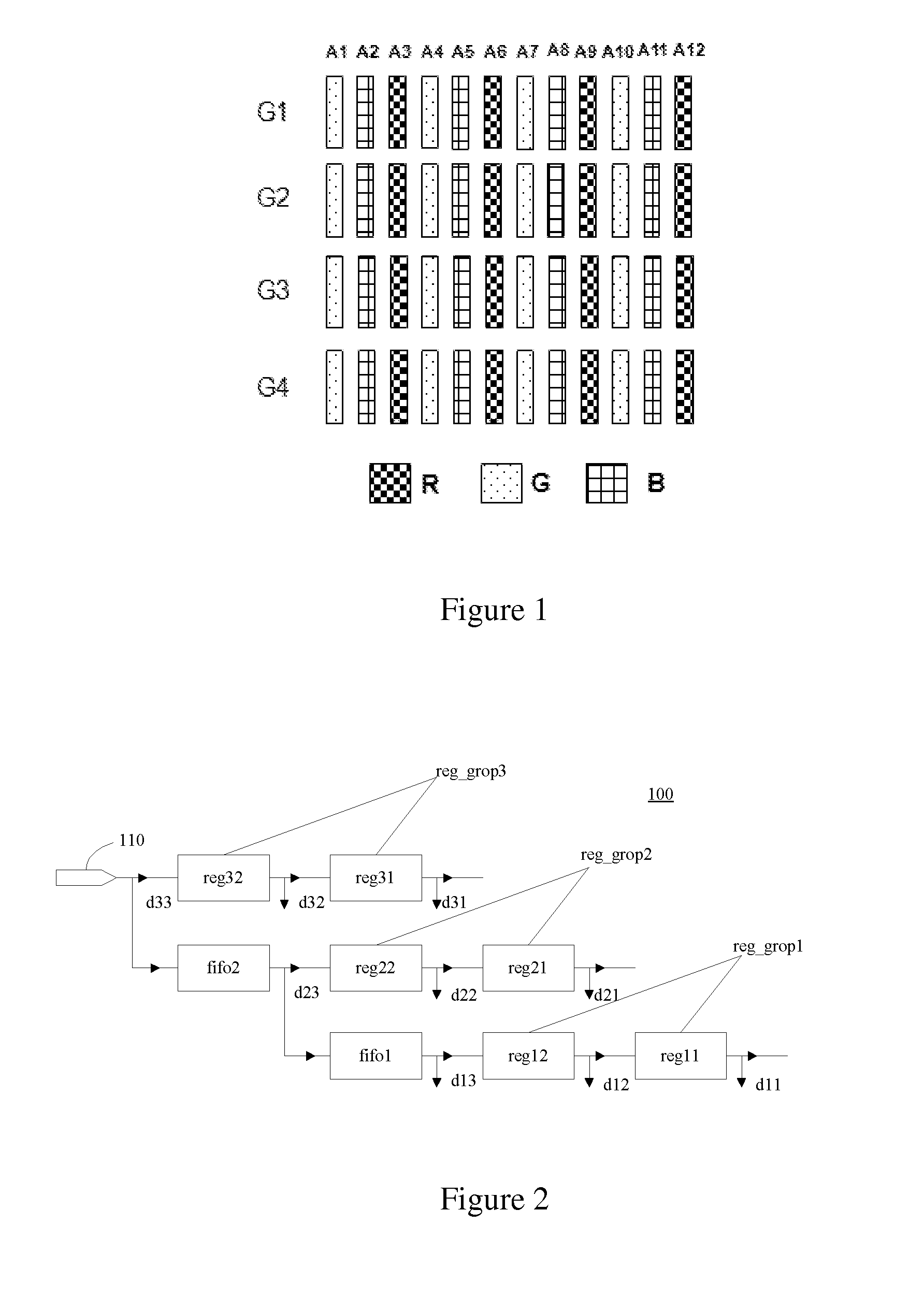

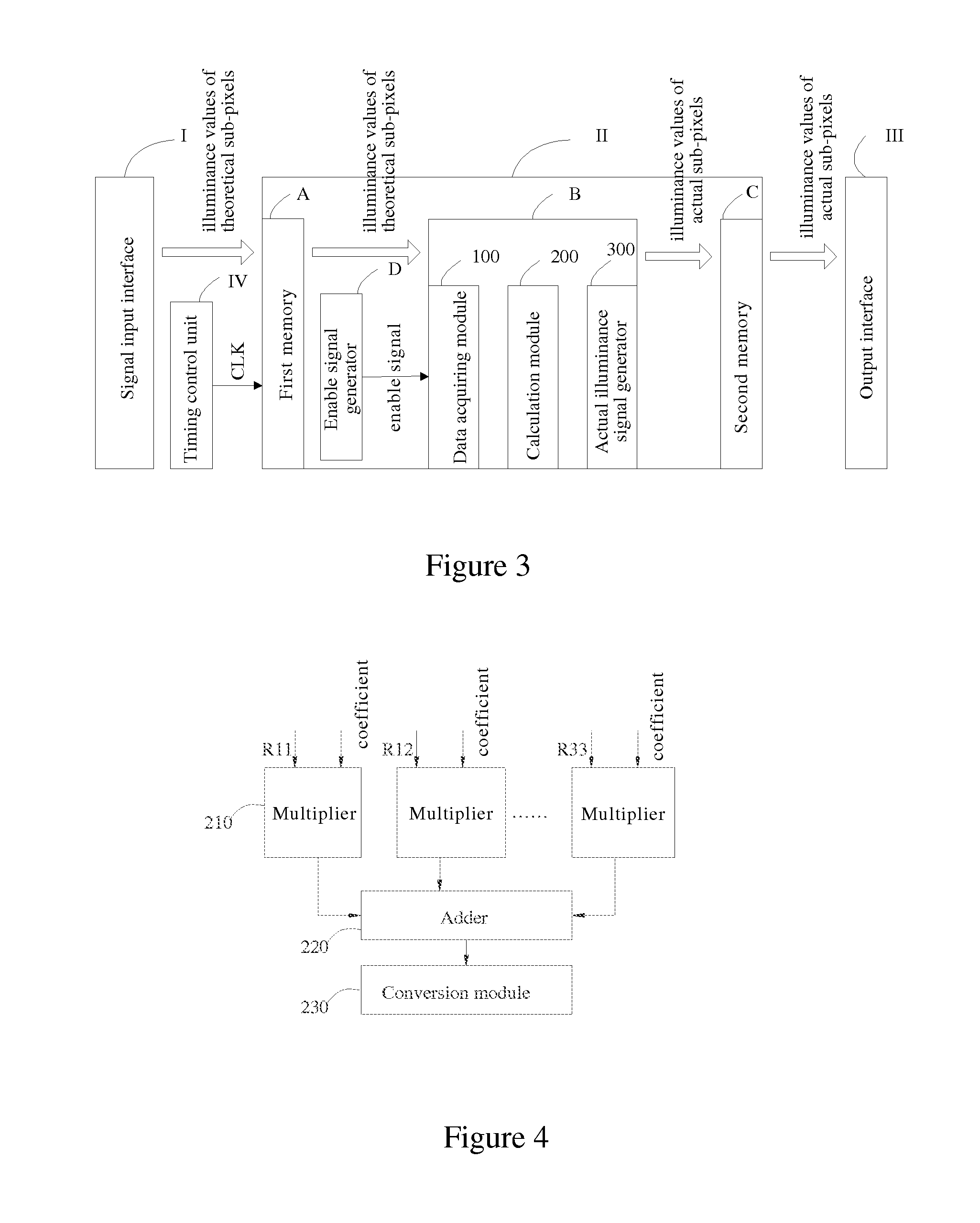

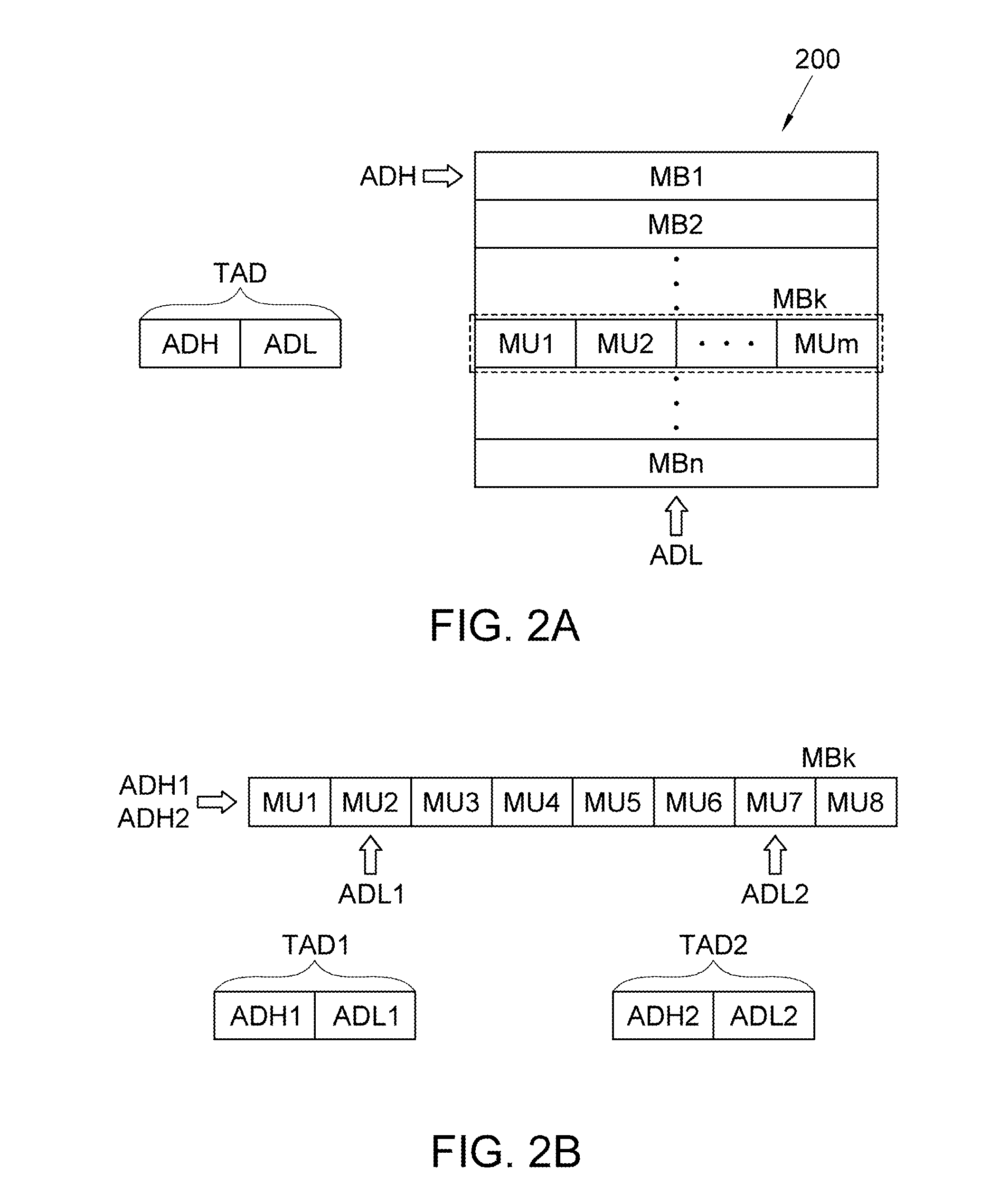

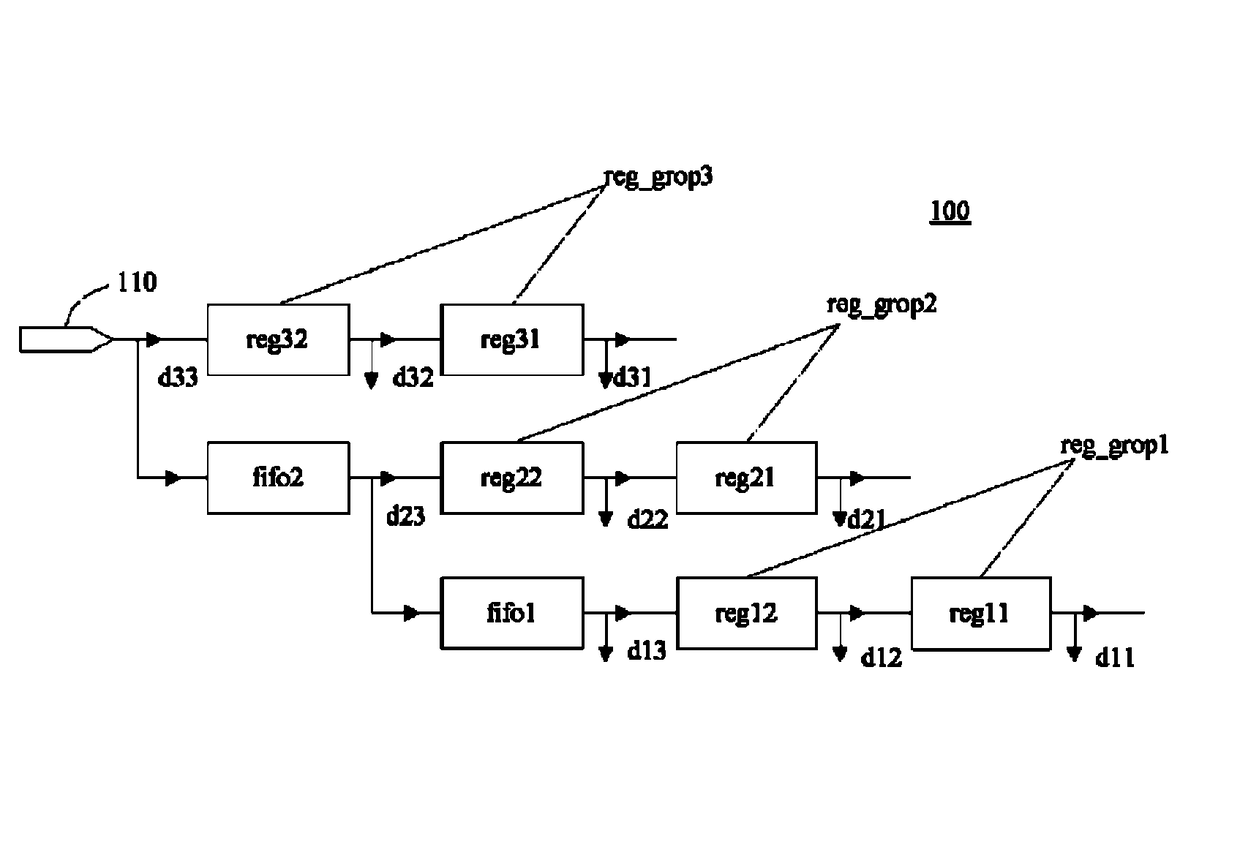

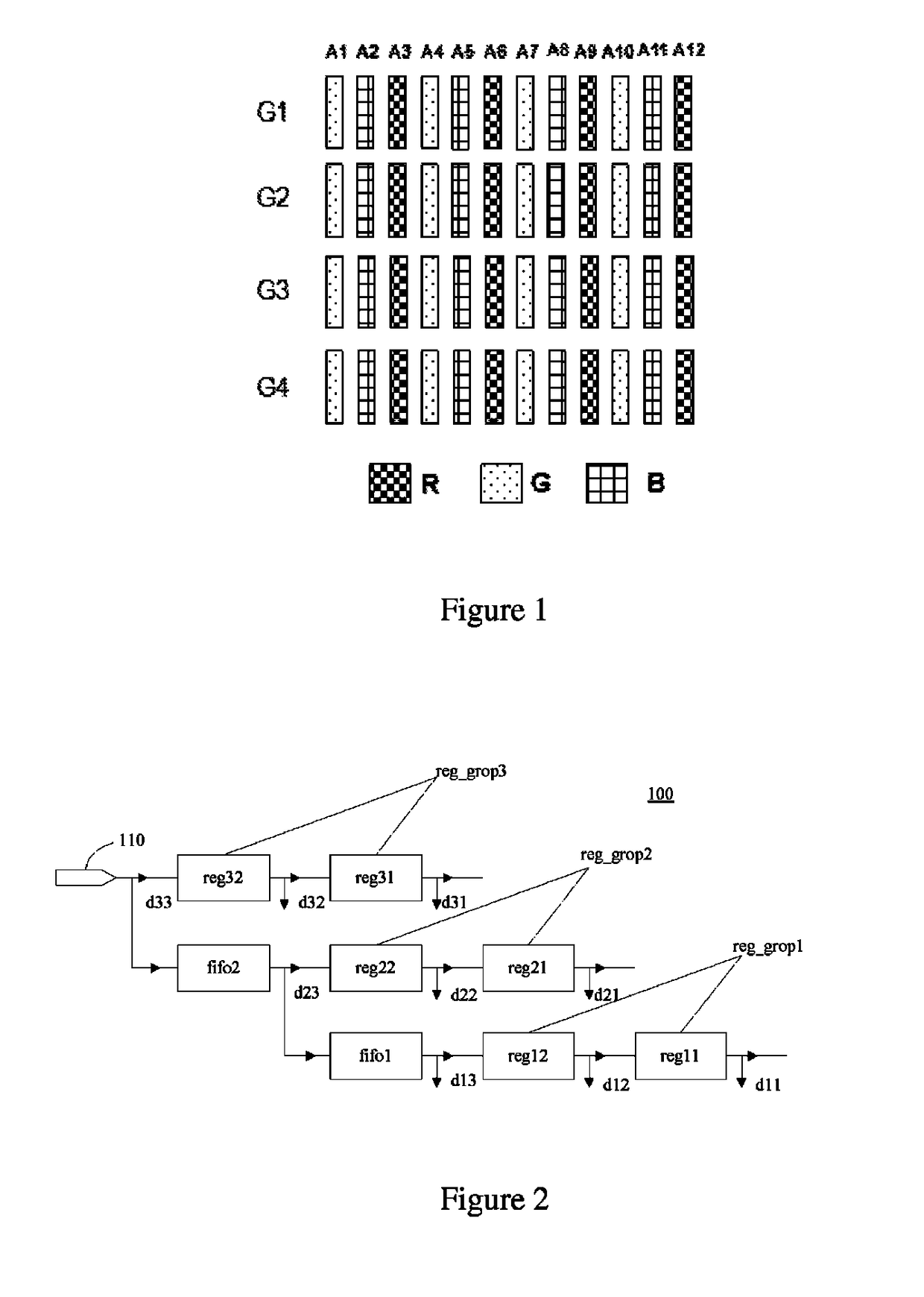

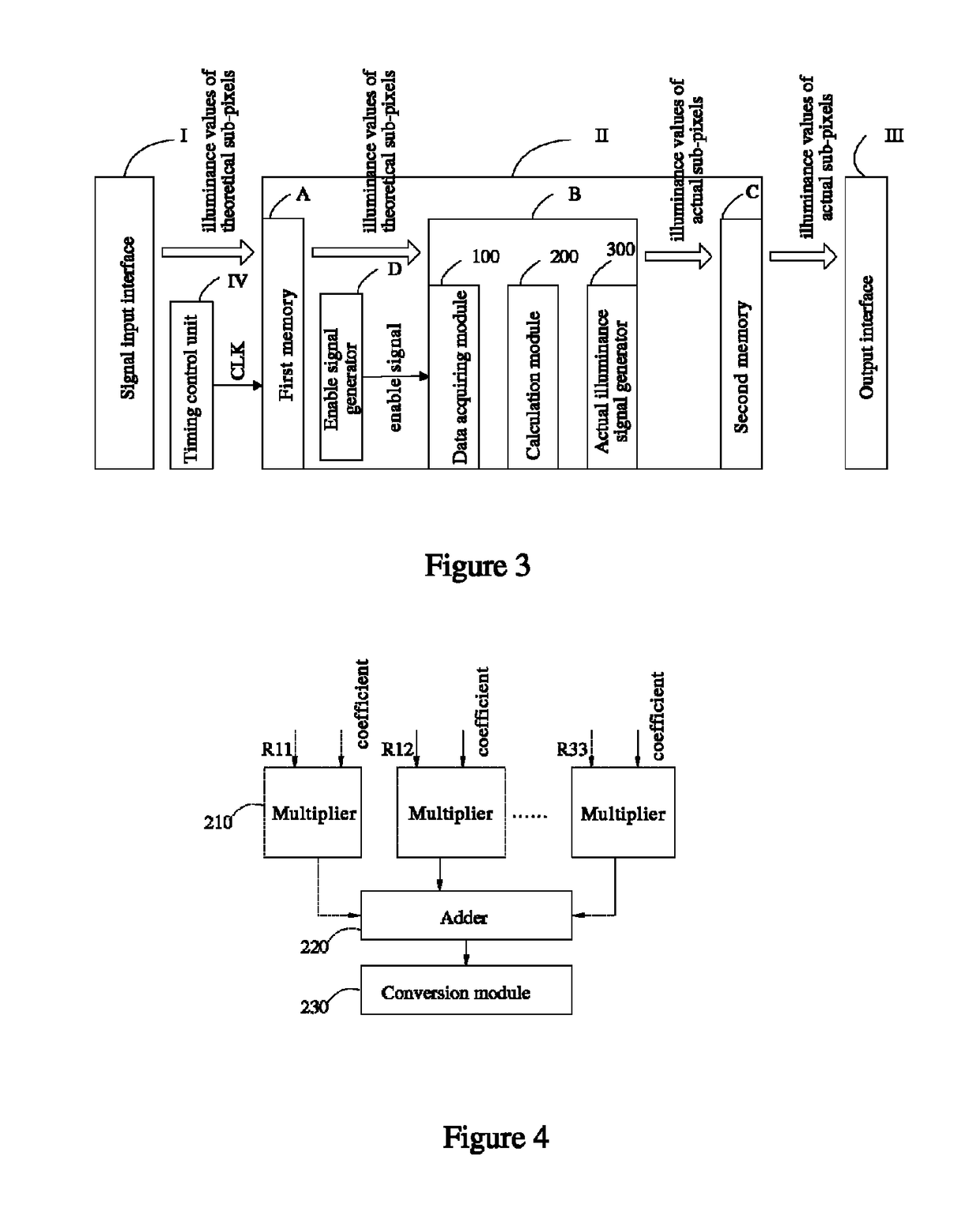

Data acquisition module and method, data processing unit, driver and display device

ActiveUS20160358536A1Execution efficiency is improvedFast dataCathode-ray tube indicatorsDigital storageShift registerDisplay device

The present invention provides a data acquiring module, comprising: a data input and output terminal, through which date enter into the data acquiring module, and which can output data independently; a shift register groups, each of which comprises (b−1) serially connected shift registers, and an output terminal of each shift register being able to output data independently, wherein a and b are integers greater than 1; and (a−1) serially connected first-in first-out memories connected to (a−1) shift register groups respectively, and the output terminal of each first-in first-out memory being able to output data independently, an input terminal of the last shift register in the shift register group without a corresponding first-in first-out memory in the a shift register groups, and the input terminal of the last first-in first-out memory of the serially connected first-in first-out memories being connected to the data input and output terminal. The present invention also provides a data processing unit, a driver and a display device.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

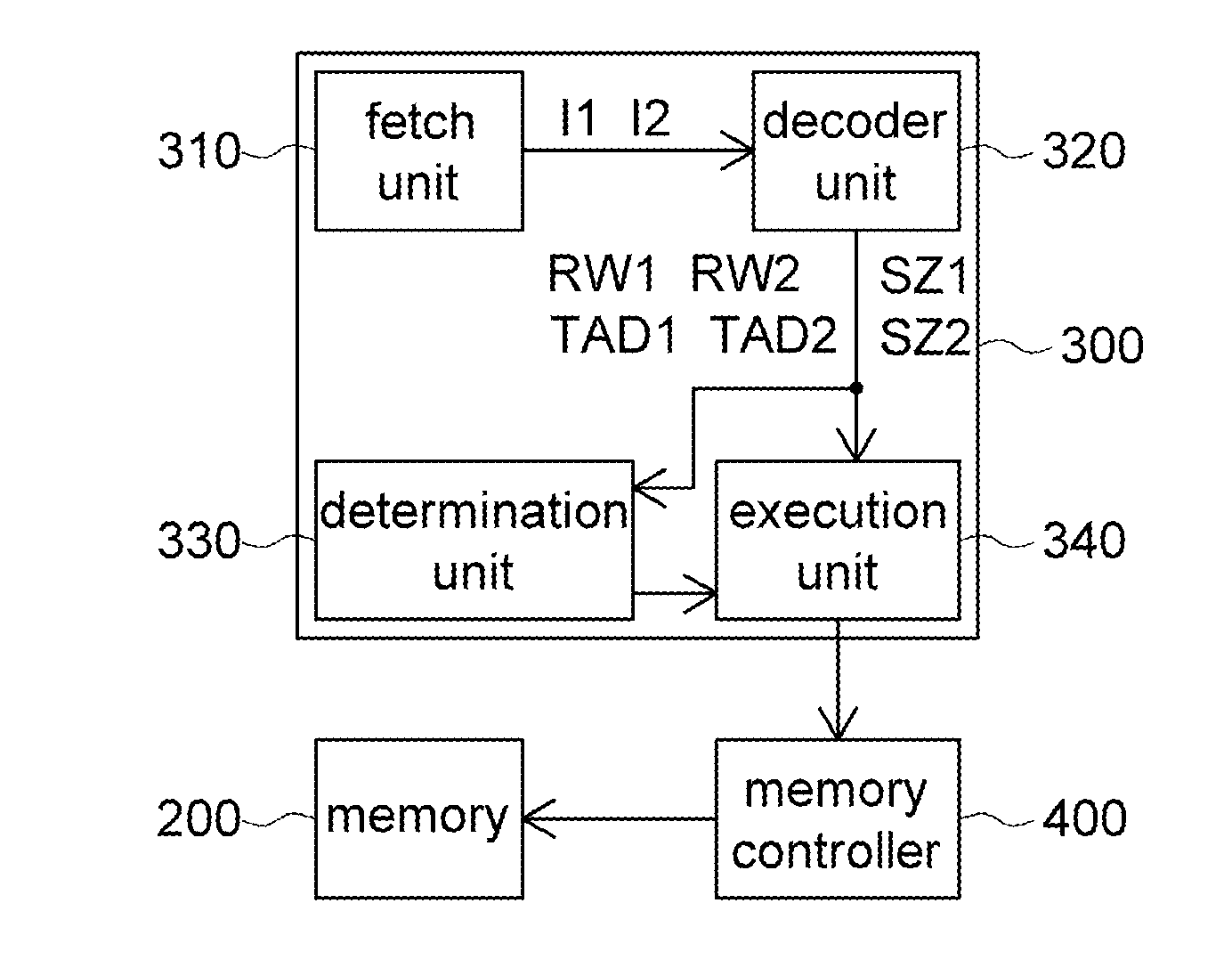

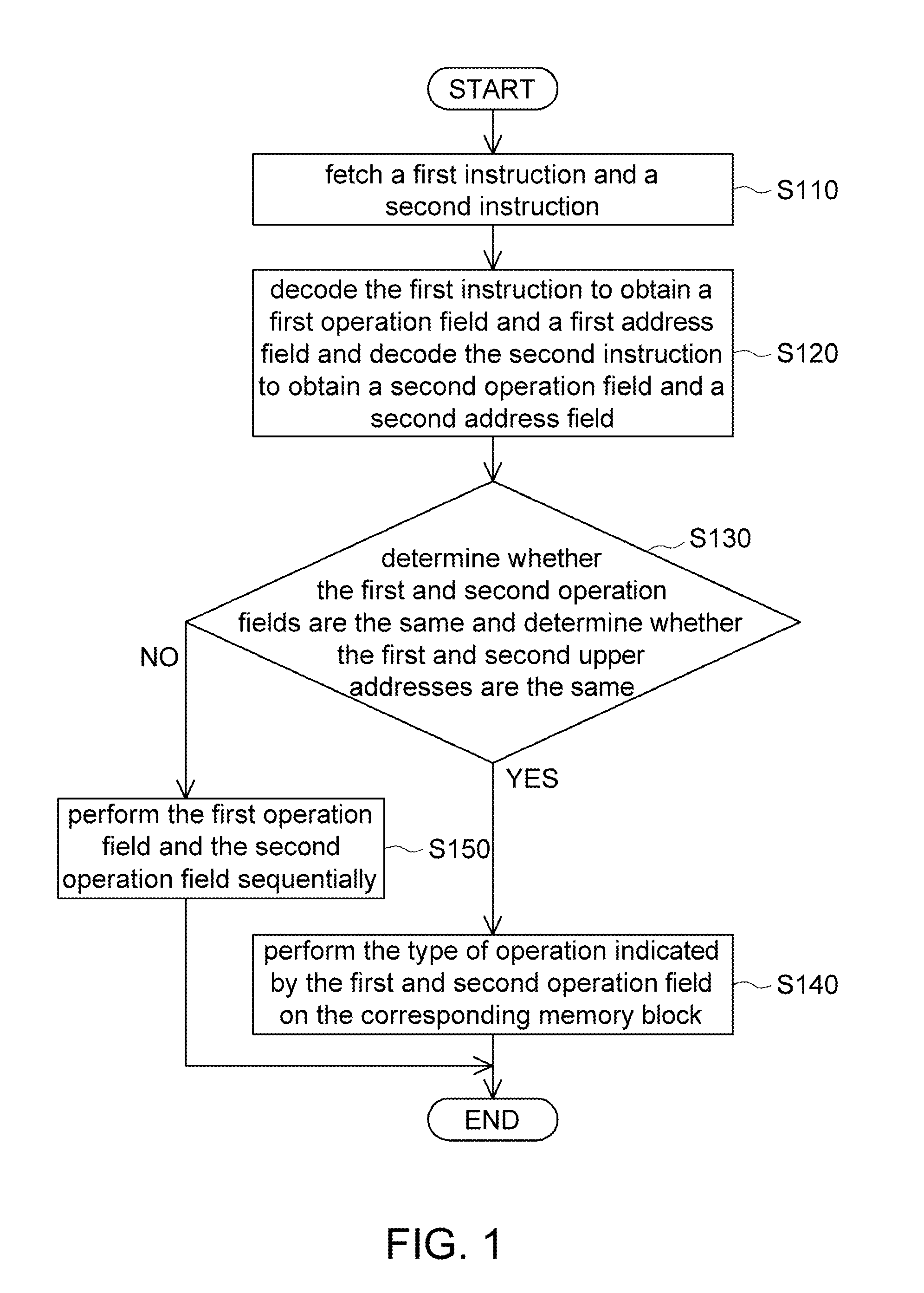

Methods and Devices for Accessing a Memory and a Central Processing Unit Using the Same

ActiveUS20100262789A1Execution efficiency is improvedImprove executionDigital computer detailsSpecific program execution arrangementsAccess methodParallel computing

A memory accessing method including the following steps is provided. Firstly, two instructions are fetched. Next, the two instructions are respectively decoded to obtain two operation fields and two address fields. The two operation fields indicate the type of operation in accessing the memory. One of the address fields includes a first upper address corresponding to the first memory block and a first lower address corresponding to a first memory unit of the first memory block. The other one of the two address fields includes a second upper address corresponding to the second memory block and a second lower address corresponding to a second memory unit of the second memory block. Then, whether two instructions are performing the same type of operation on the same memory block is determined. If yes, the type of operation indicated by the two operation fields is performed on the corresponding memory block parallelly.

Owner:REALTEK SEMICON CORP

Data acquisition module and method, data processing unit, driver and display device

ActiveUS9734753B2Execution efficiency is improvedFast dataCathode-ray tube indicatorsDigital storageShift registerDisplay device

The present invention provides a data acquiring module, comprising: a data input and output terminal, through which data enter into the data acquiring module, and which can output data independently; a shift register groups, each of which comprises (b−1) serially connected shift registers, and an output terminal of each shift register being able to output data independently, wherein a and b are integers greater than 1; and (a−1) serially connected first-in first-out memories connected to (a−1) shift register groups respectively, and the output terminal of each first-in first-out memory being able to output data independently, an input terminal of the last shift register in the shift register group without a corresponding first-in first-out memory in the a shift register groups, and the input terminal of the last first-in first-out memory of the serially connected first-in first-out memories being connected to the data input and output terminal. The present invention also provides a data processing unit, a driver and a display device.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

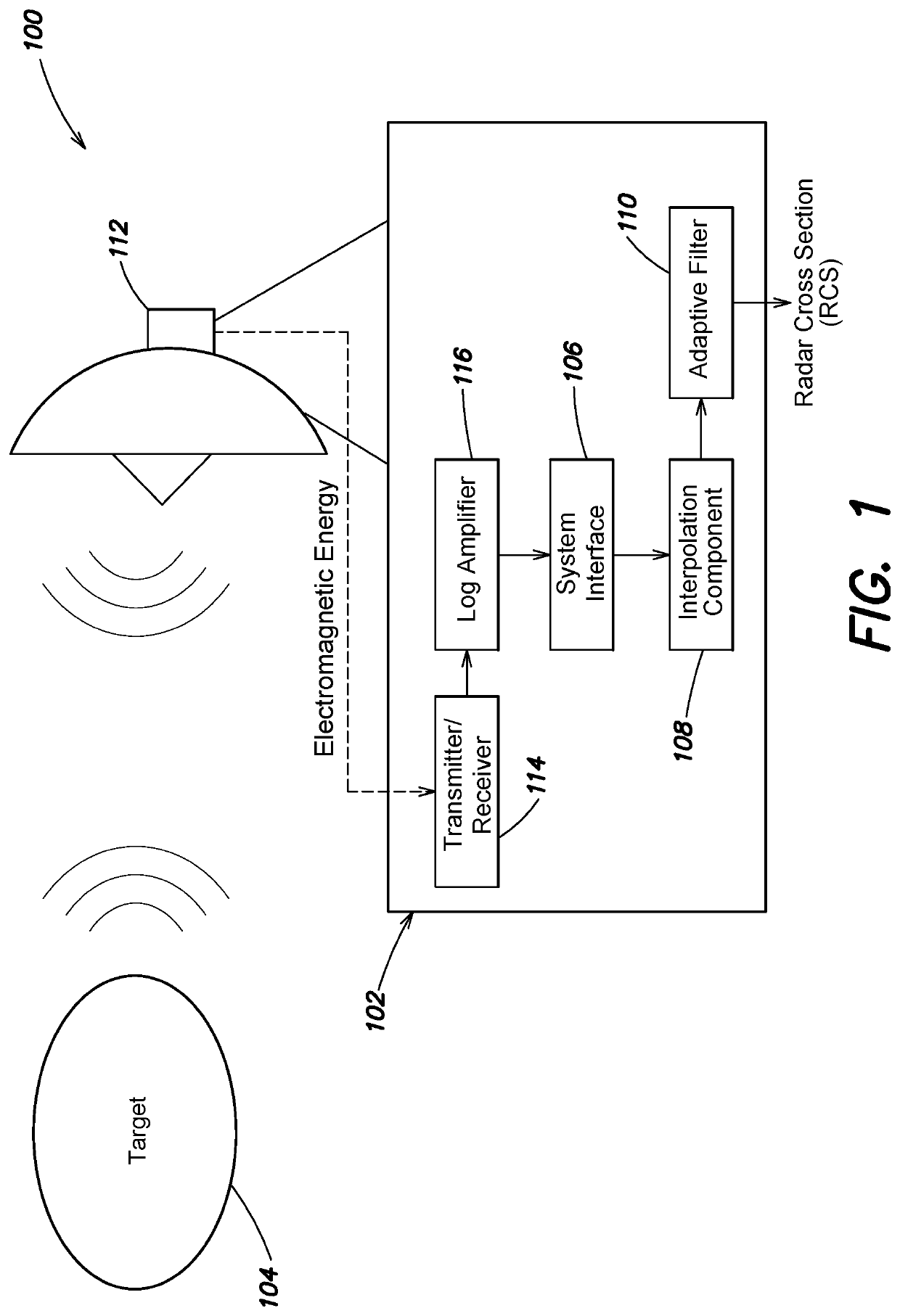

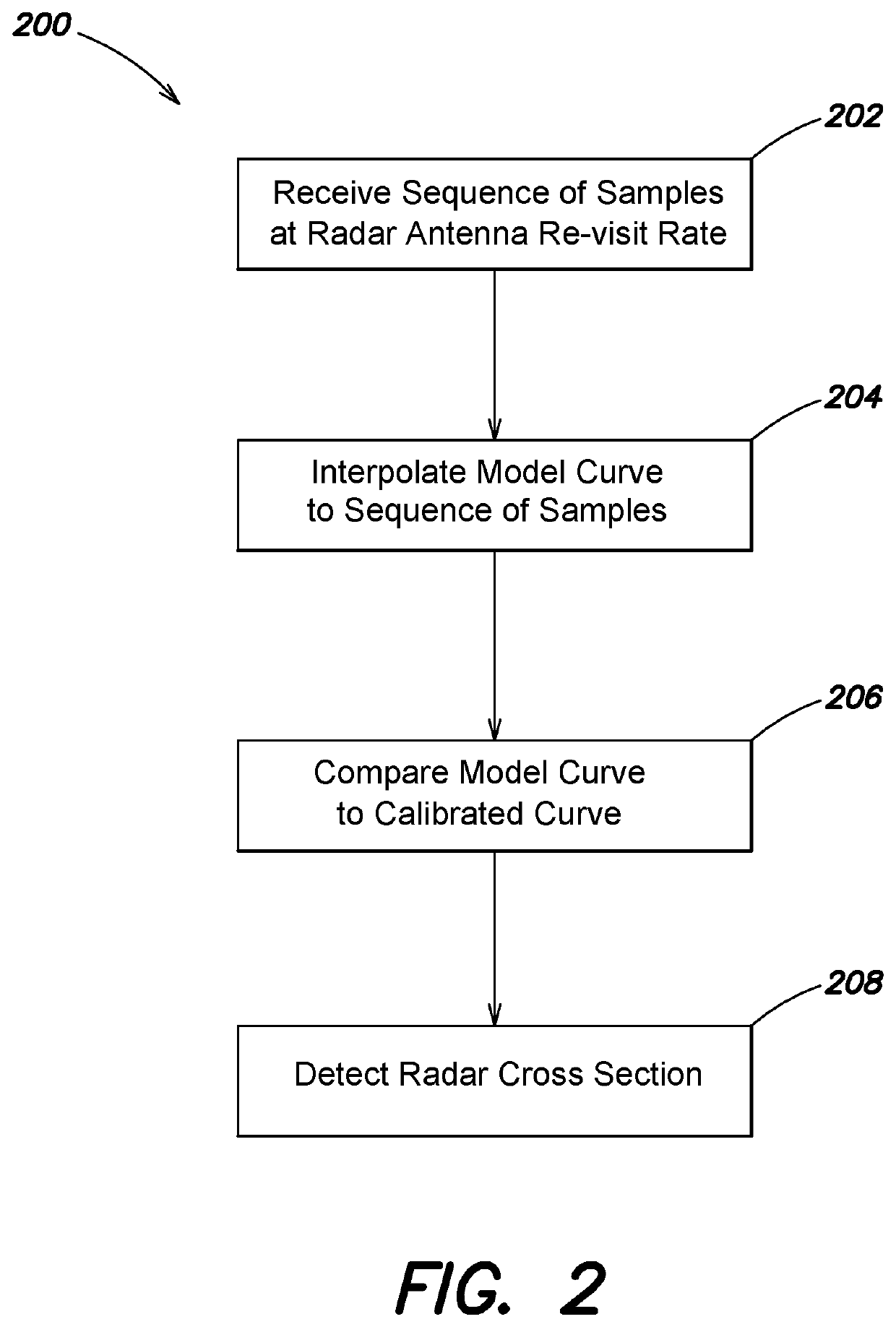

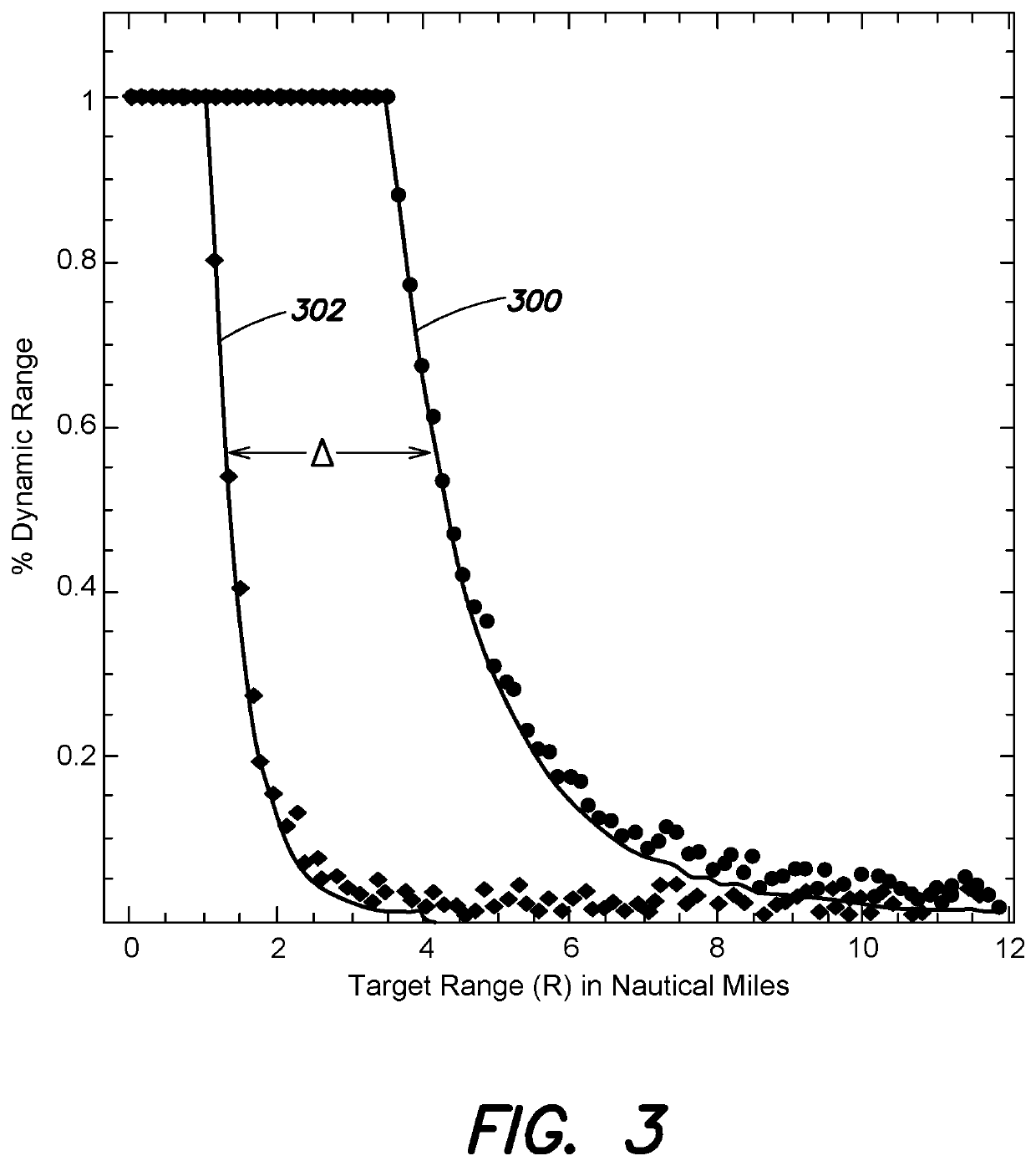

Systems and methods for interpolation in systems with non-linear quantization

PendingUS20190385746A1Execution efficiency is improvedFunction increaseMedical simulationMedical data miningCalibration curveVisit rate

Various aspects and examples are directed to methods and systems for interpolation in systems that execute non-linear quantization routines. Particular aspects of the methods described herein include a method of detecting a Radar Cross Section (RCS) and a method of detecting patient injuries. In one example, a method of detecting RCS includes receiving a sequence of samples at a re-visit rate of a radar antenna, the sequence of samples being based on electromagnetic energy reflected from a target, interpolating a model curve to the sequence of samples, where each sample of the sequence of samples geometrically increases in value relative to a previous sample of the sequence of samples, comparing the model curve to a calibrated curve and determining a shift between the model curve and the calibrated curve based on the comparison, and detecting a RCS based on the shift between the model curve and the calibrated curve.

Owner:RAYTHEON CO

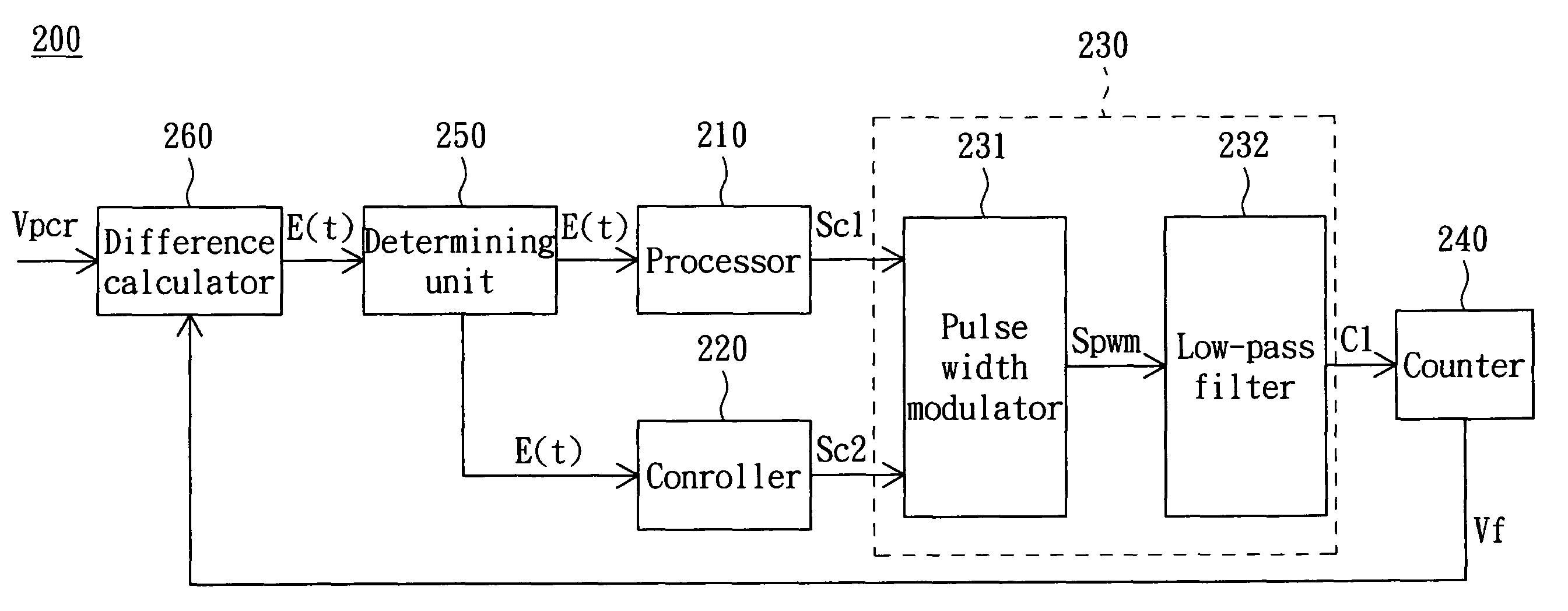

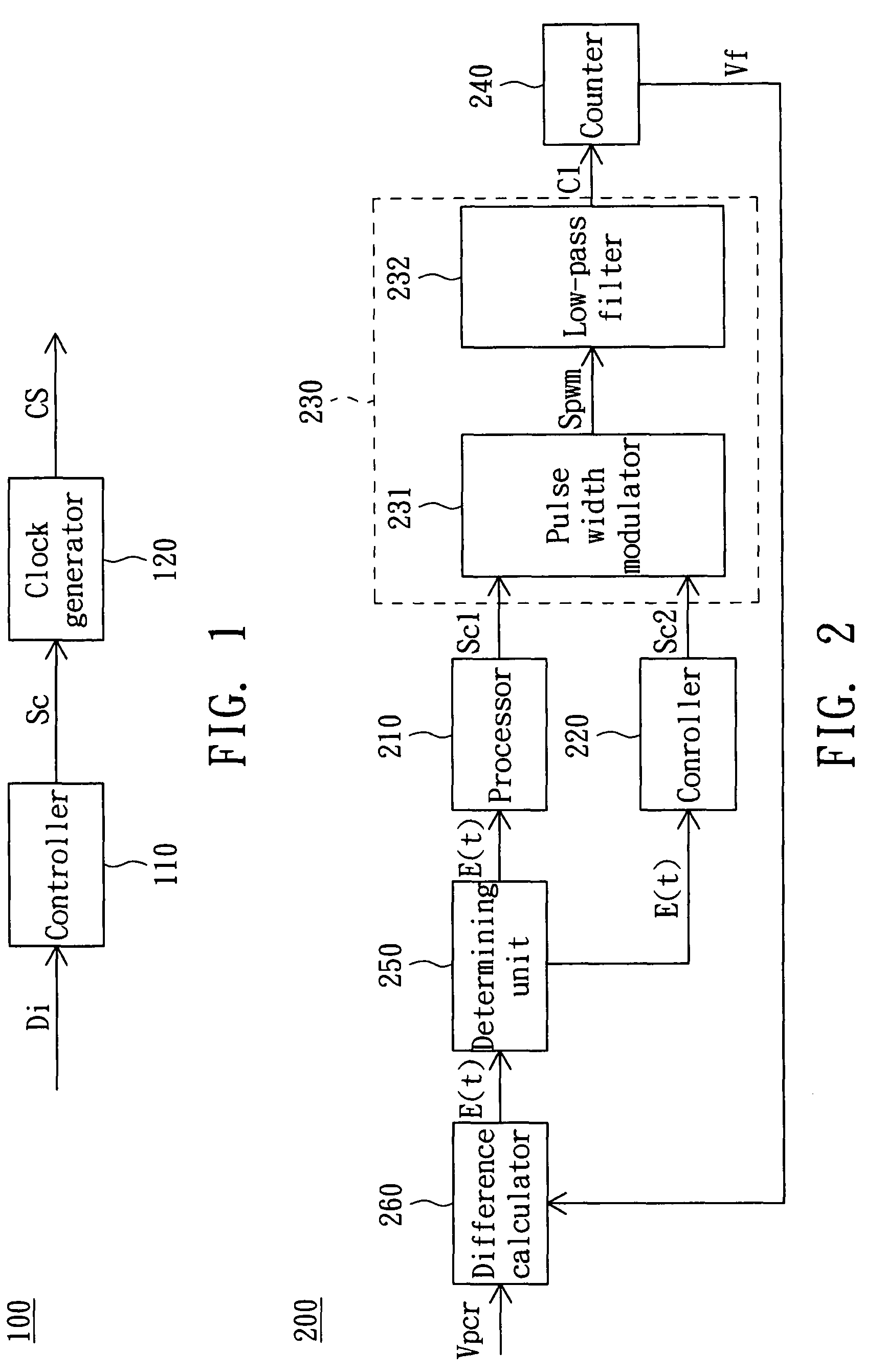

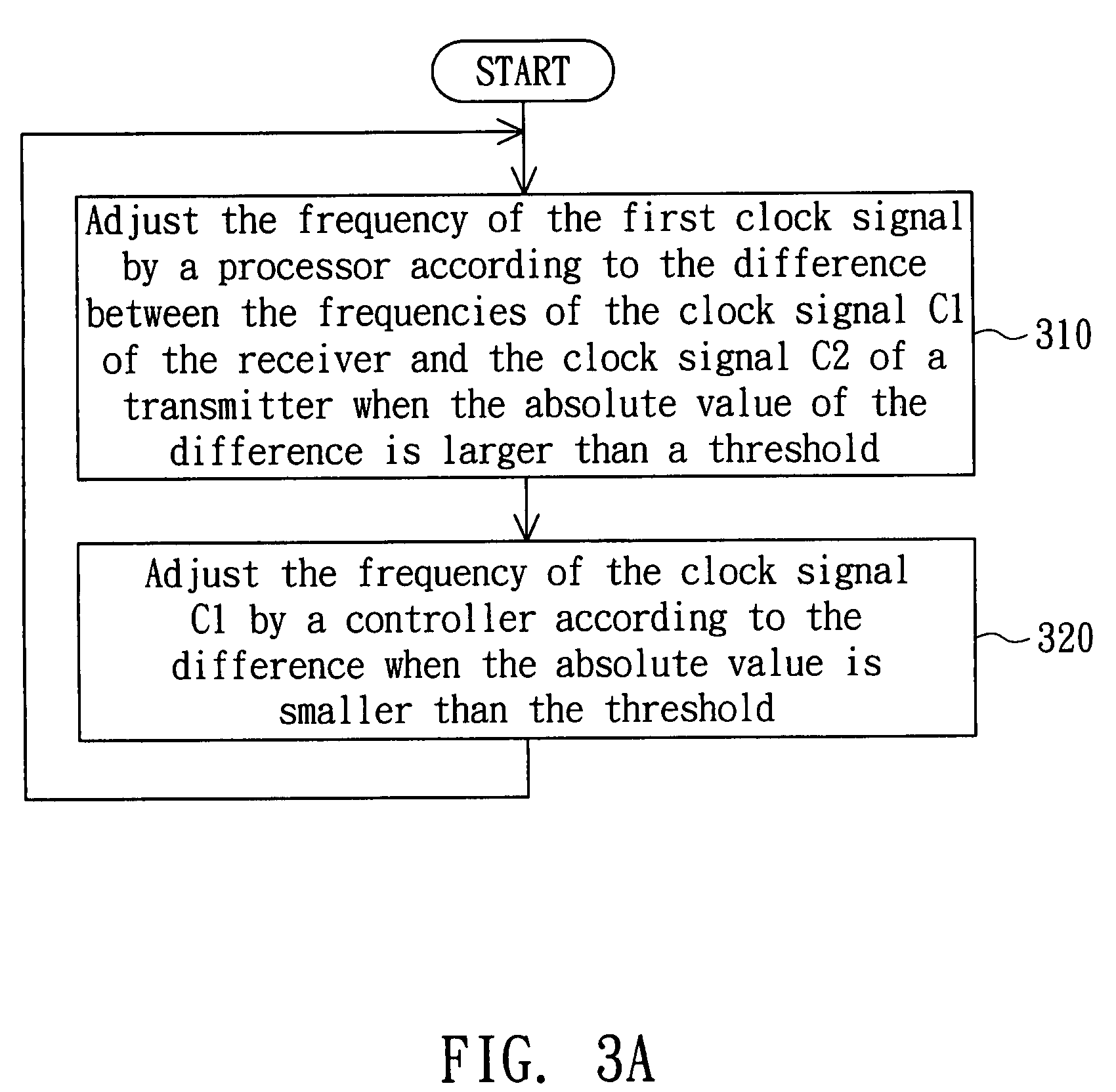

Receiver with the function of adjusting clock signal and an adjusting method therefor

InactiveUS7924964B2Reduce processor loadExecution efficiency is improvedTelevision system detailsTransmissionControl signalEngineering

Owner:HIMAX TECH LTD

Method of sending a location report from target user equipment

ActiveUS7509132B2Avoid wastingExecution efficiency is improvedSpecial service for subscribersServices signallingTelecommunicationsDuring procedure

Disclosed herein is a method useful for target user equipment (UE) sending a location report. When the target UE is located in a first central network (CN) of a location service (LCS) system, the target UE reports the location report to the LCS system. If the target UE does not receive a location report response from the LCS system, when being located in a second CN of LCS system, target UE will continue to report the location report to LCS system. In accordance with one aspect of the disclosed method, the waste of location service system resource is avoided as well as the execution efficiency of location service is increased. In addition, during procedure of change of area event location request, the consequent processing of request thereof is guaranteed to be normal, so that execution efficiency of location service is increased. Moreover, message interaction between the function entities is saved for the exception cases. Accordingly, the waste of public land mobile communication network resource caused by generation of excessive useless messages is avoided.

Owner:HUAWEI TECH CO LTD

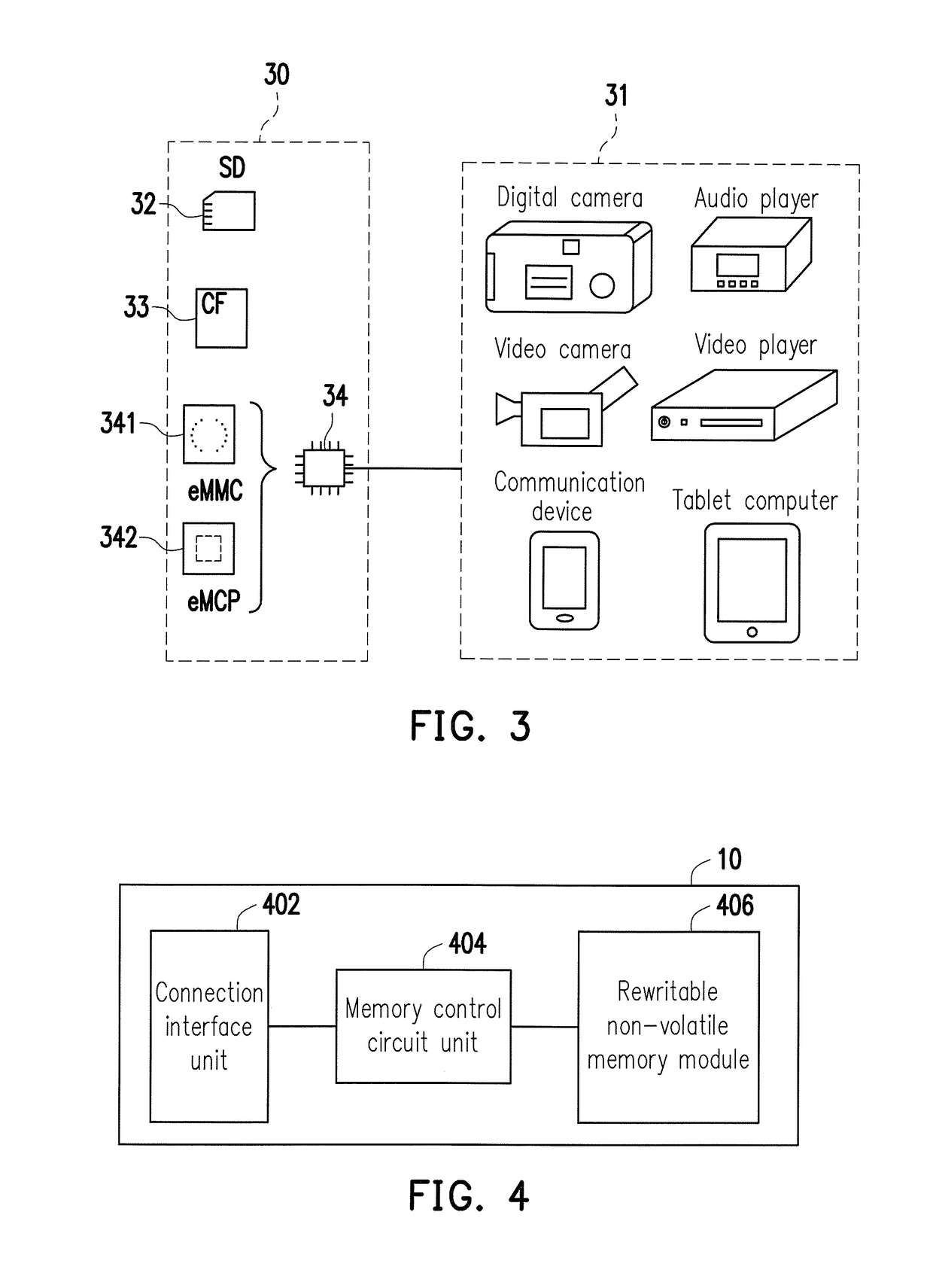

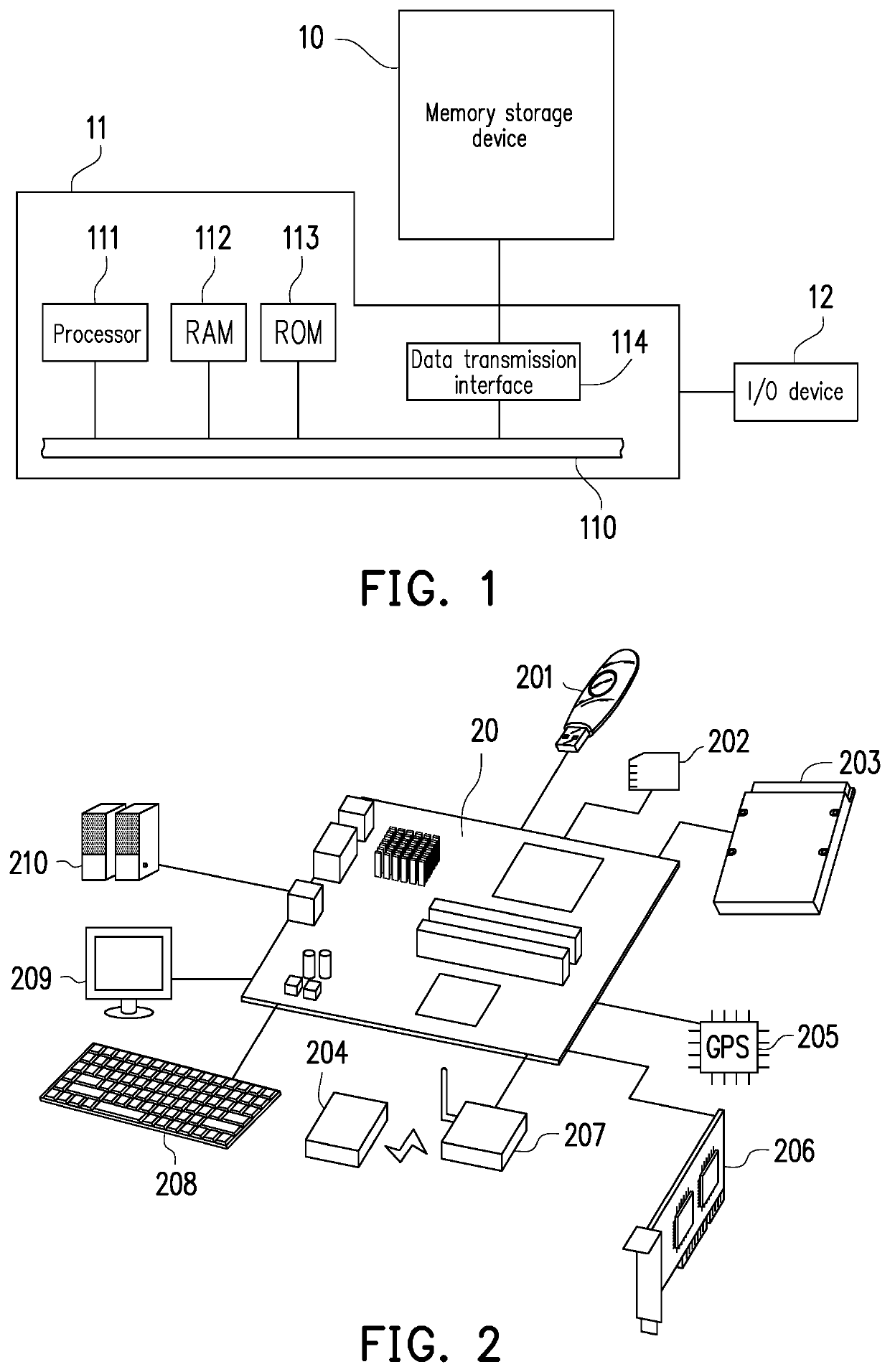

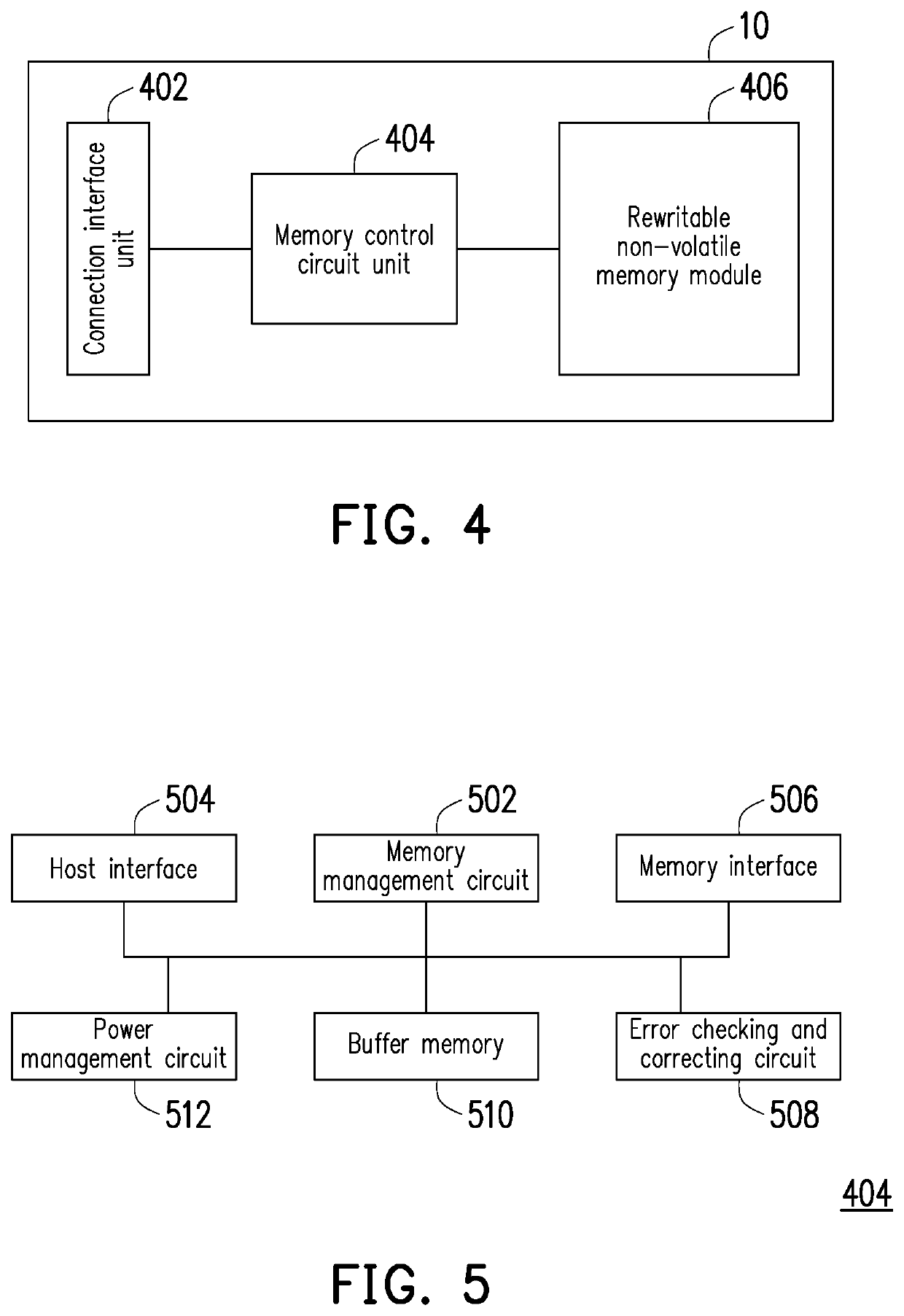

Decoding method, memory storage device and memory control circuit unit

InactiveUS20170134049A1Reduce in quantityExecution efficiency is improvedRead-only memoriesError correction/detection using multiple parity bitsDecoding methodsData set

A decoding method, a memory storage device and a memory control circuit unit are provided. The method includes: determining an offset threshold value and a corresponding check matrix; receiving response data from a rewritable non-volatile memory module and performing an iterative decoding process. The check matrix includes at least one sub-matrix group, each sub-matrix of the sub-matrix group has a default dimension, and the offset threshold value is less than a default dimension value corresponding to the default dimension In the iterative decoding process, several default groups in a data set are shifted, so as to obtain first shift groups, while an offset of each first shift group with respect to a corresponding group among the default groups is not over the default threshold value. Therefore, decoding reference data used in the iterative decoding process may be generated more efficiently.

Owner:EPOSTAR ELECTRONICS CORP

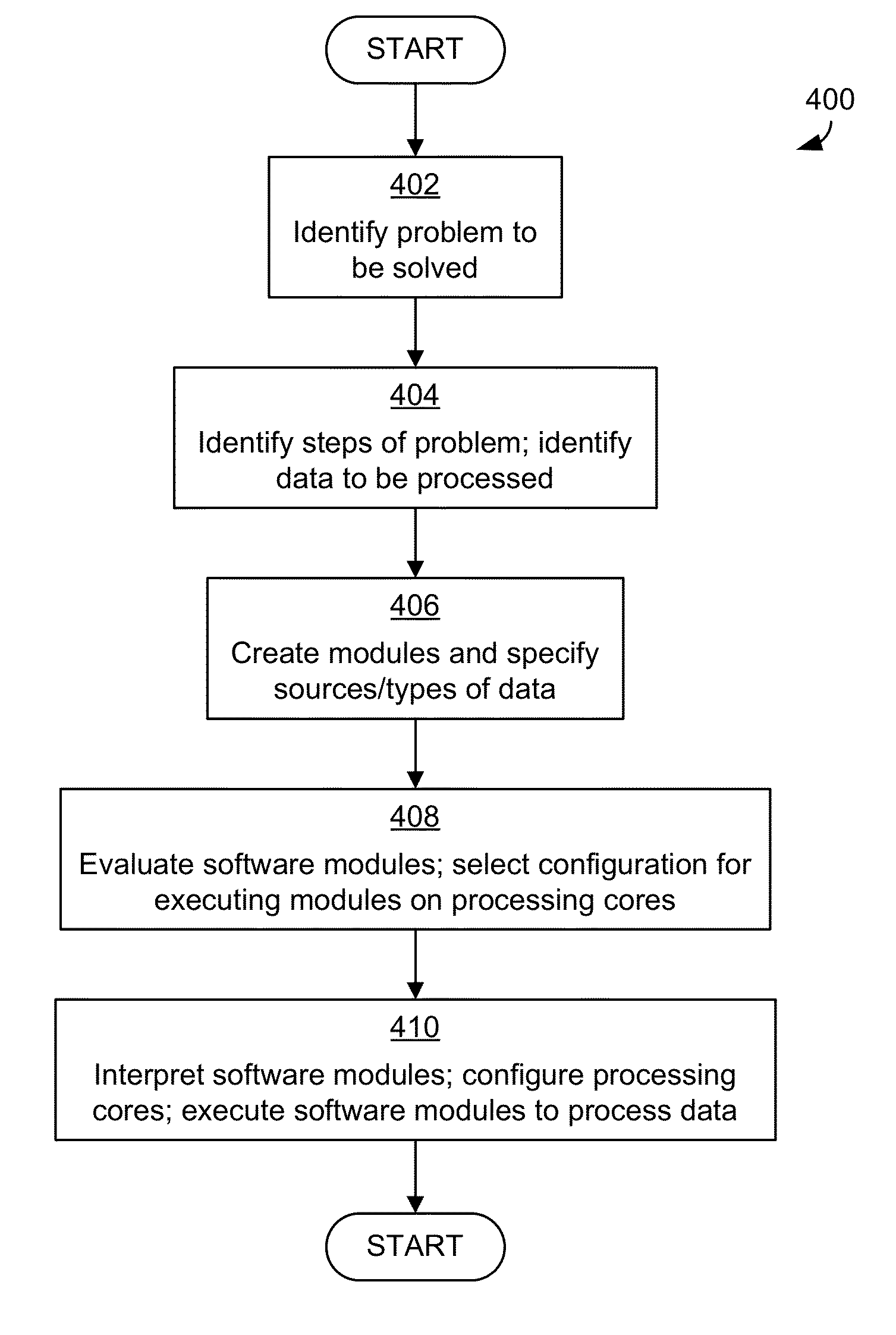

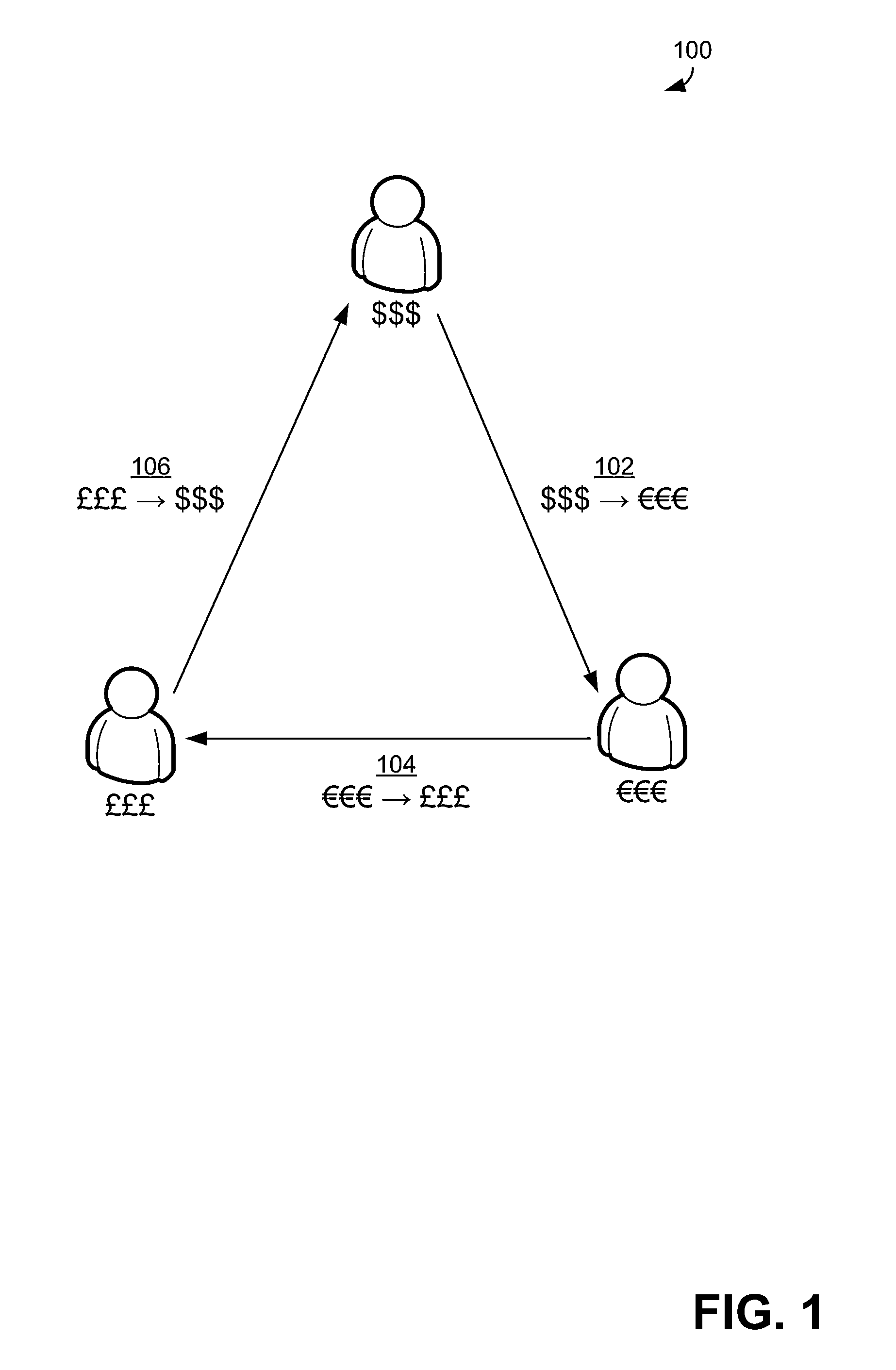

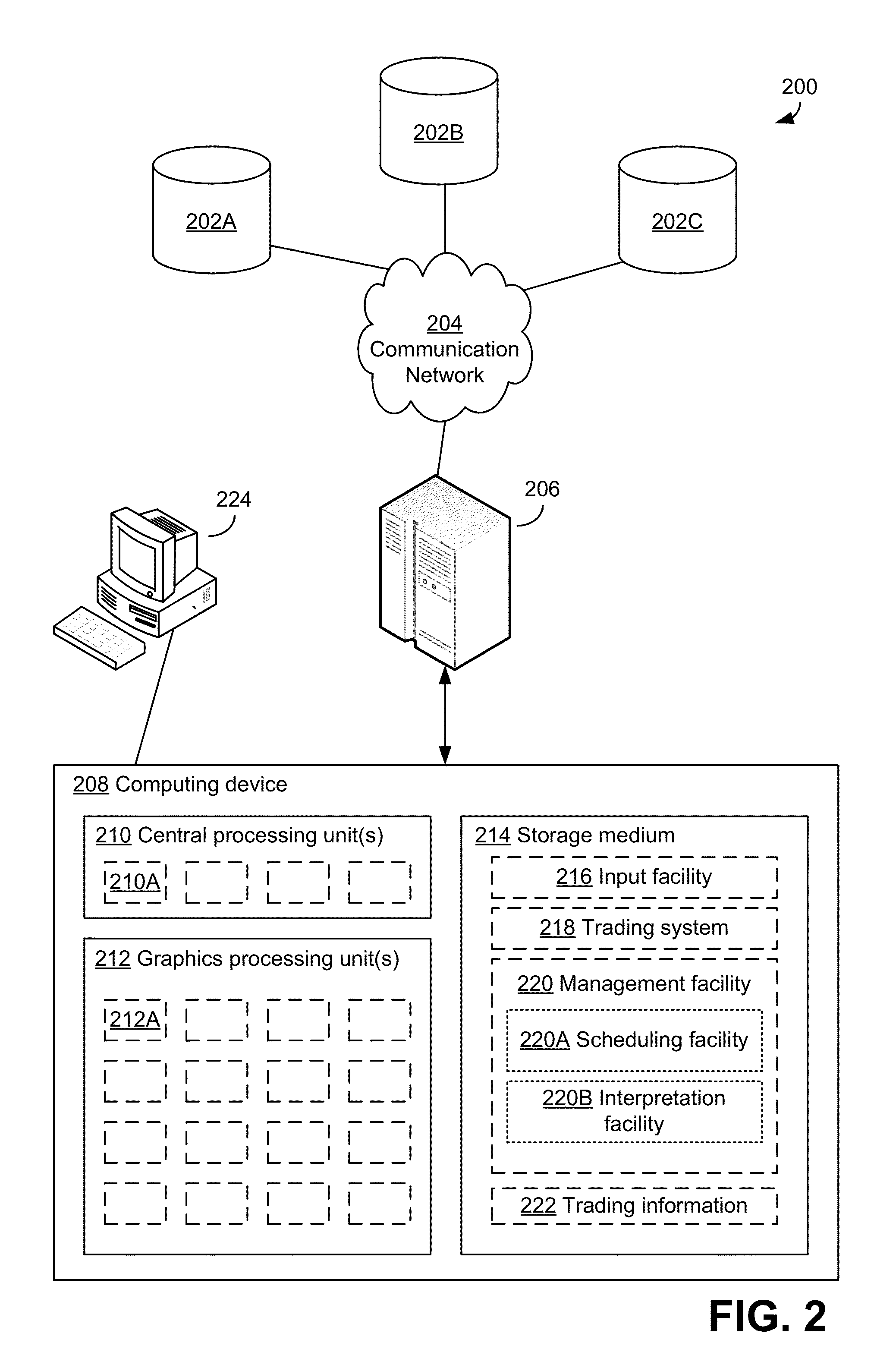

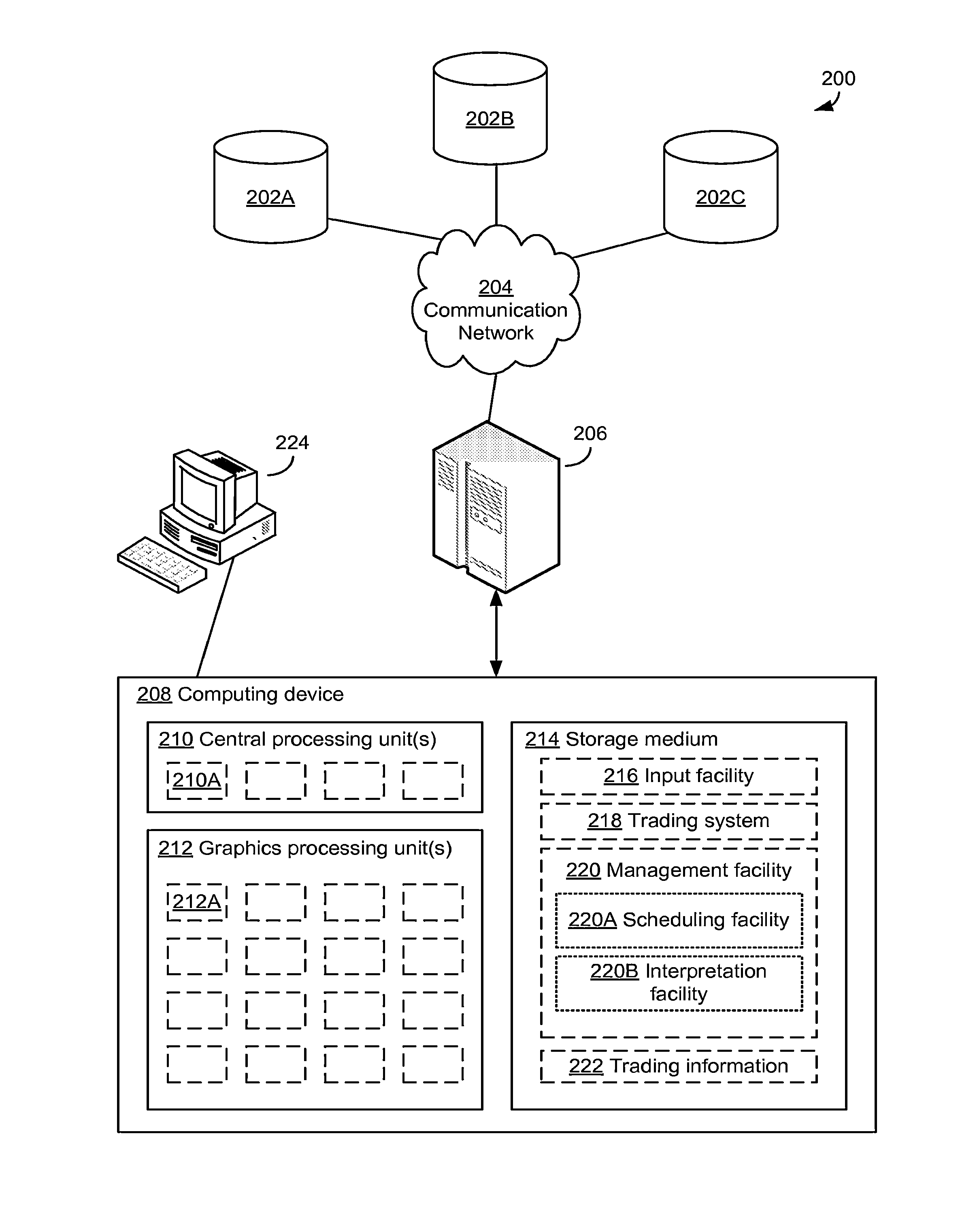

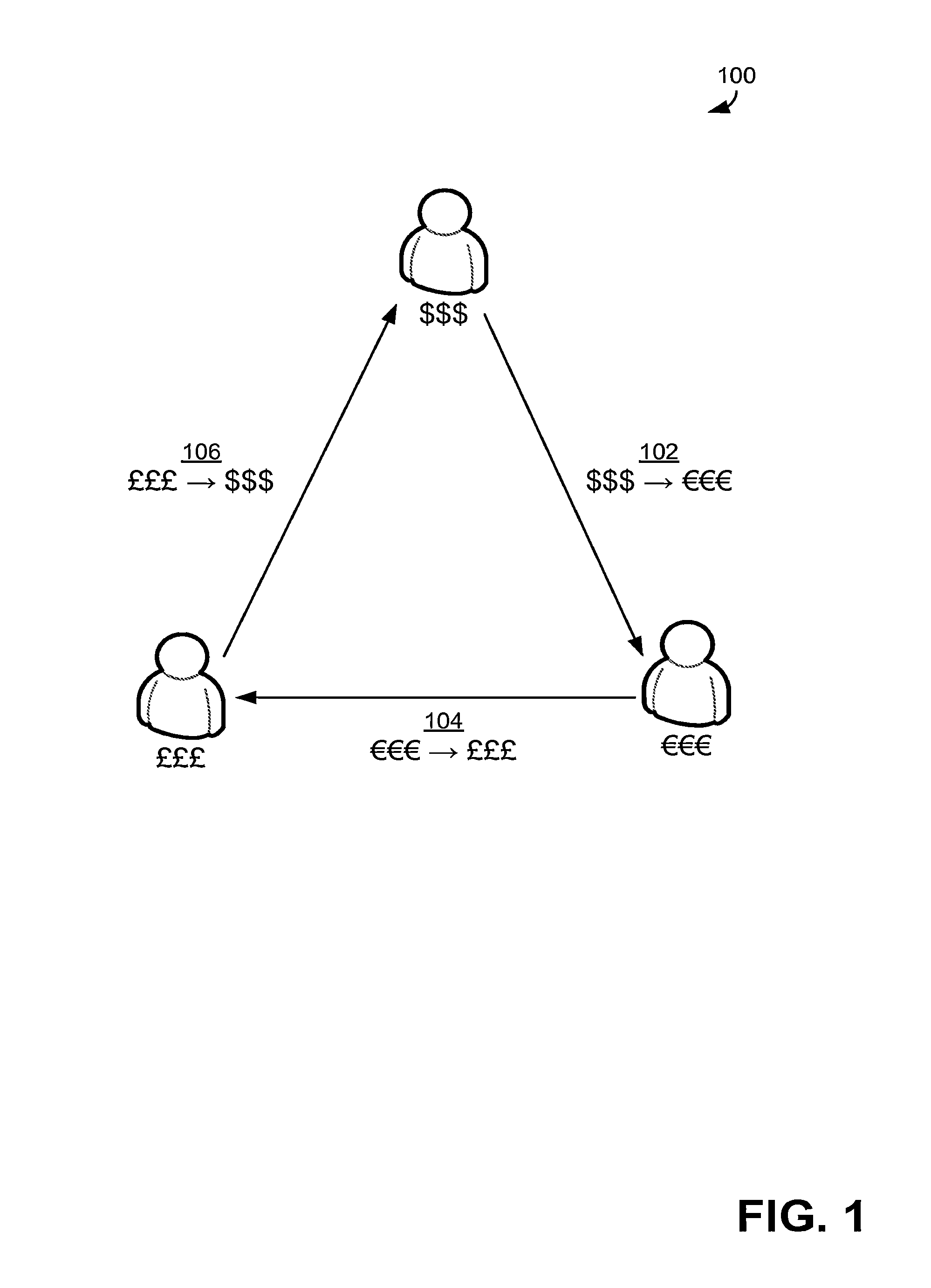

Parallel processing system

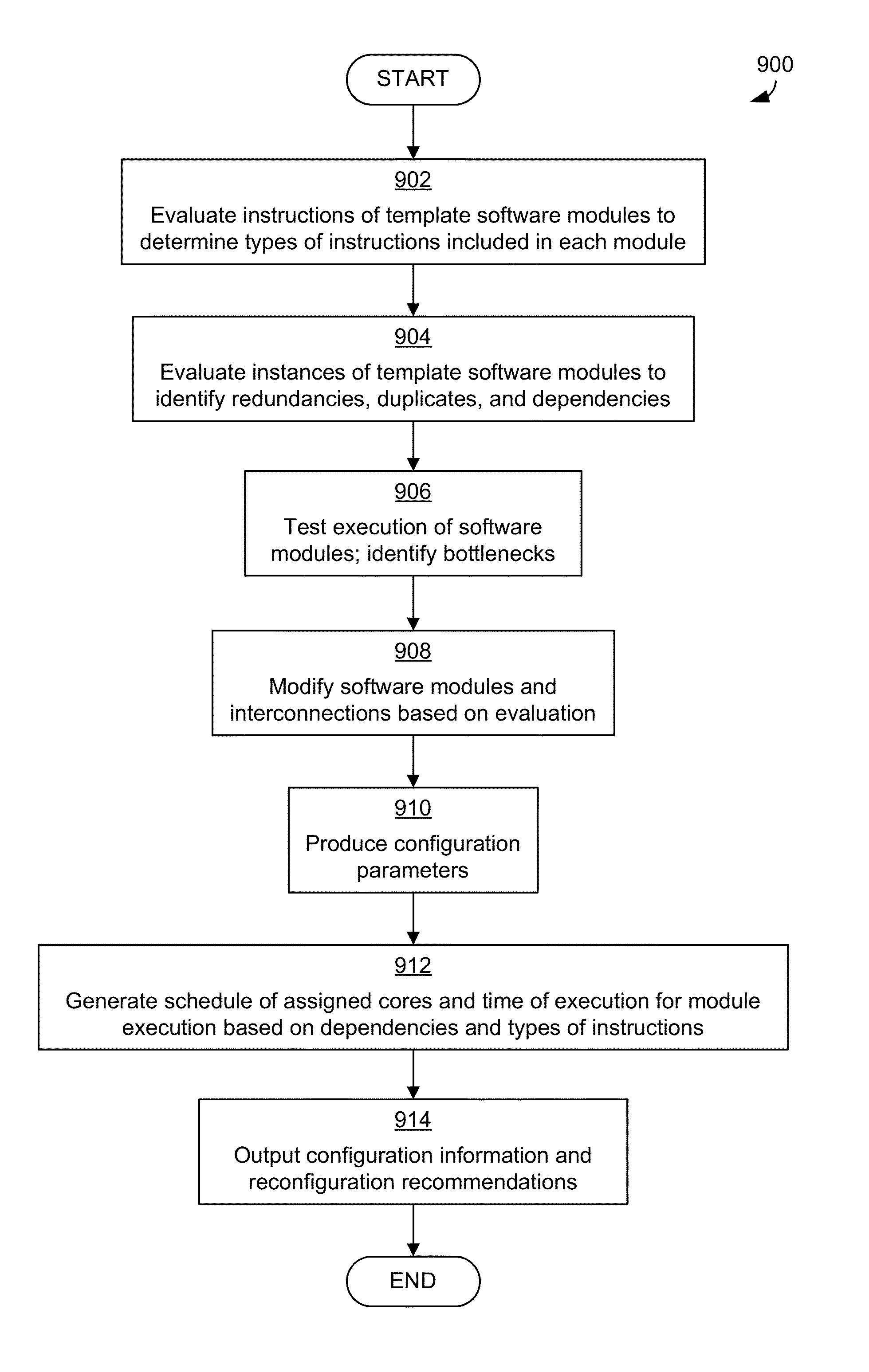

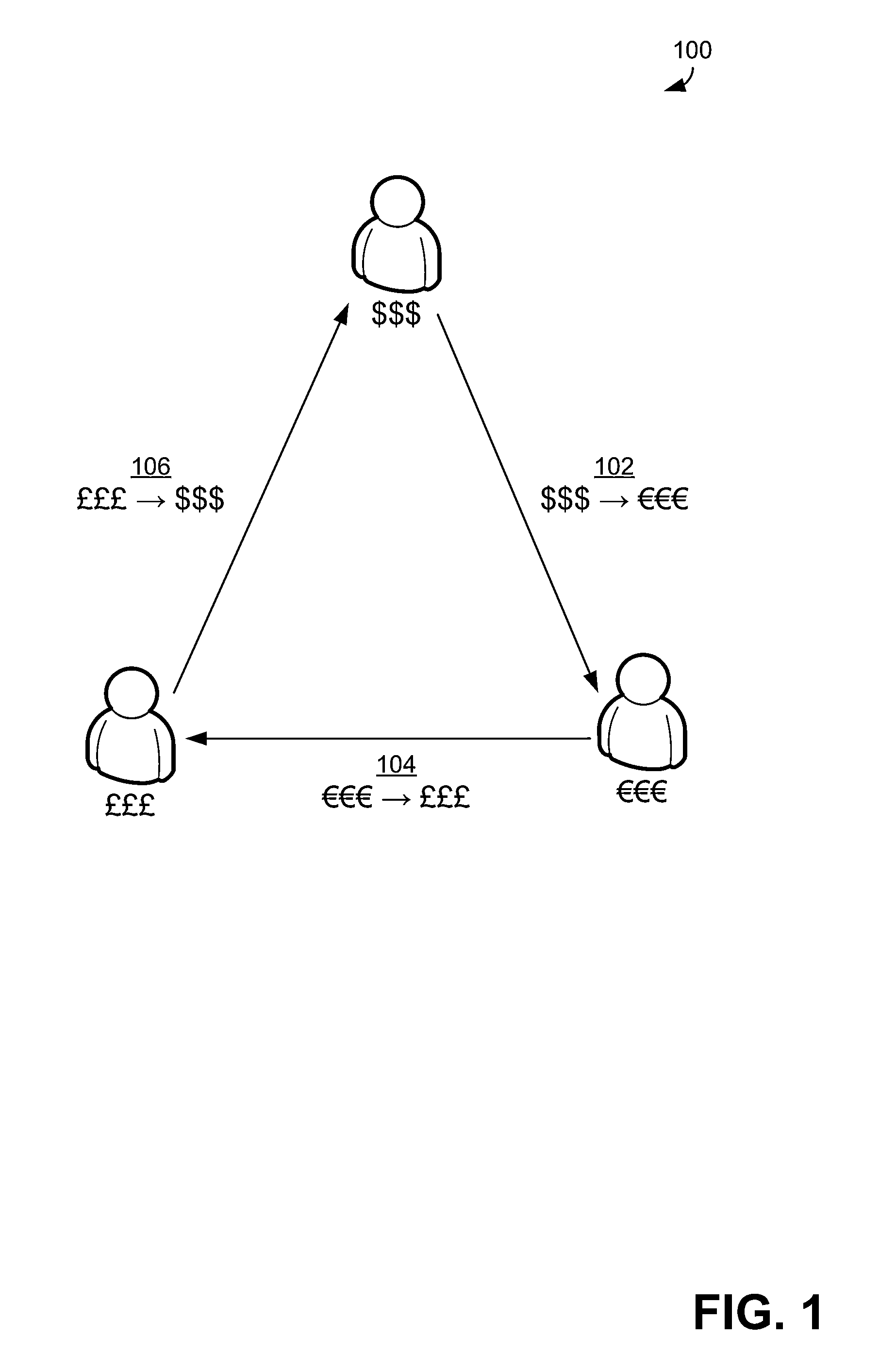

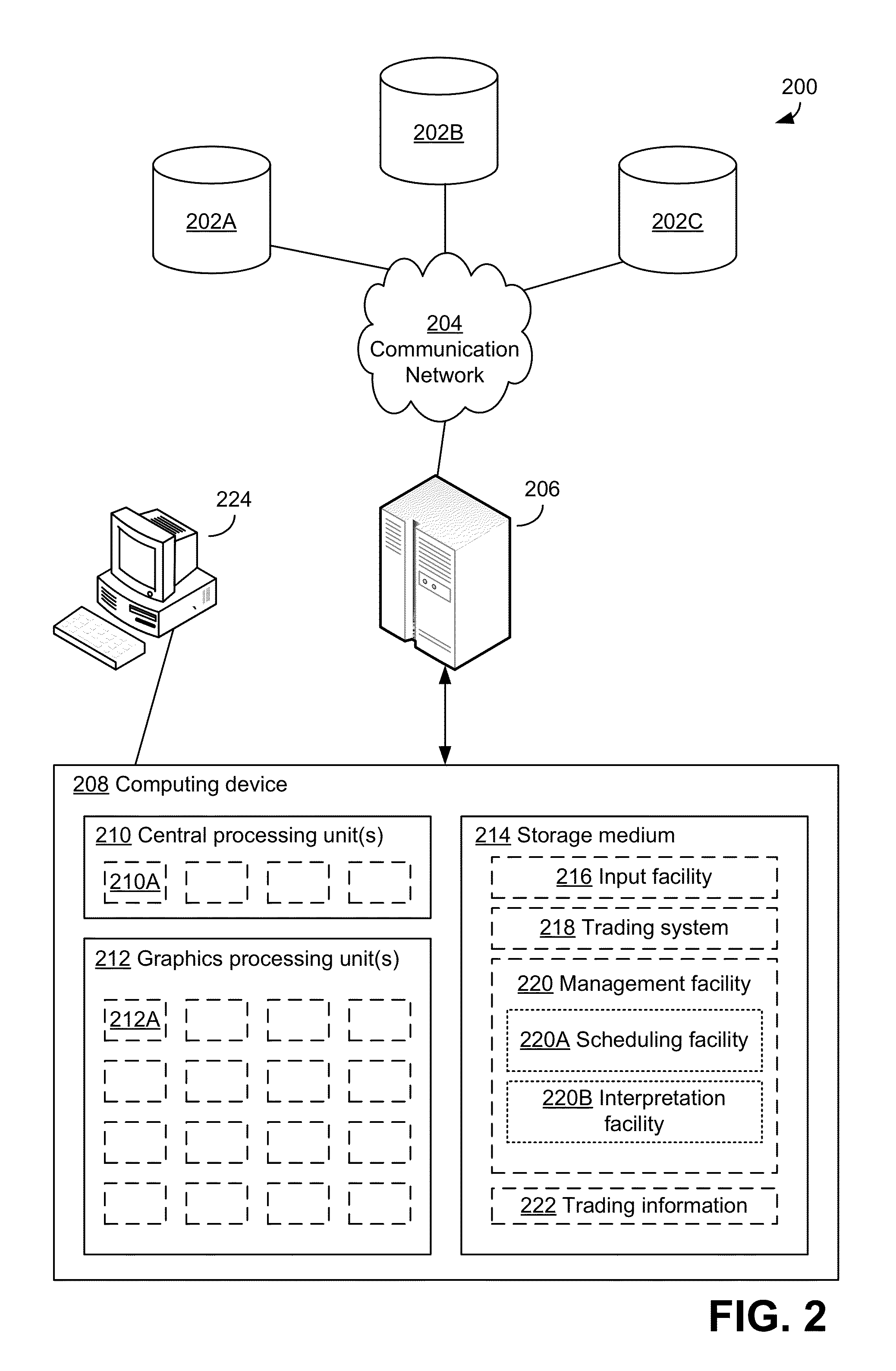

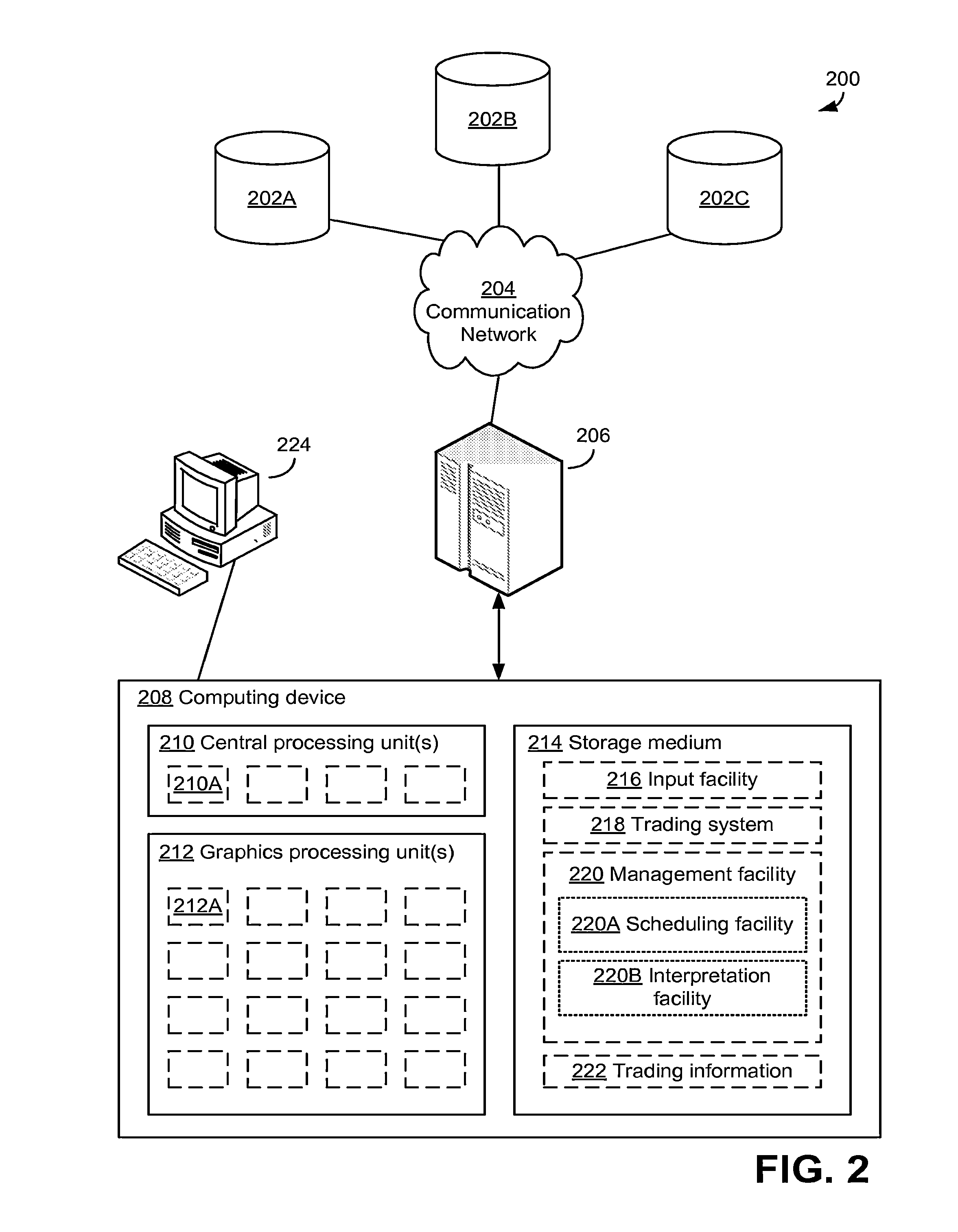

ActiveUS20140026150A1Improve executionEfficient executionFinanceProgram synchronisationComputer architectureEngineering

Software development tools and techniques for configuring parallel processing systems to execute software modules implementing processes for solving complex problems, including over-the-counter trading processes and foreign exchange trading processes, to execute quickly and efficiently. The parallel processing system may include low-cost, consumer-grade multicore processing units. A process for solving a complex problem may be divided into software modules, including by evaluating the process to determine discrete processing steps that produce an intermediate result on which later steps of the process depend. The software modules created for a process may form a template processing chain describing multiple processing chains of the process that are to be executed. A software development tool for producing configuration information for multicore processing units may evaluate the software modules and the processing chains to determine whether the modules will execute quickly and efficiently on the multicore processing units of the parallel processing system.

Owner:ONEZERO FINANCIAL SYST

Receiver with the function of adjusting clock signal and an adjusting method therefor

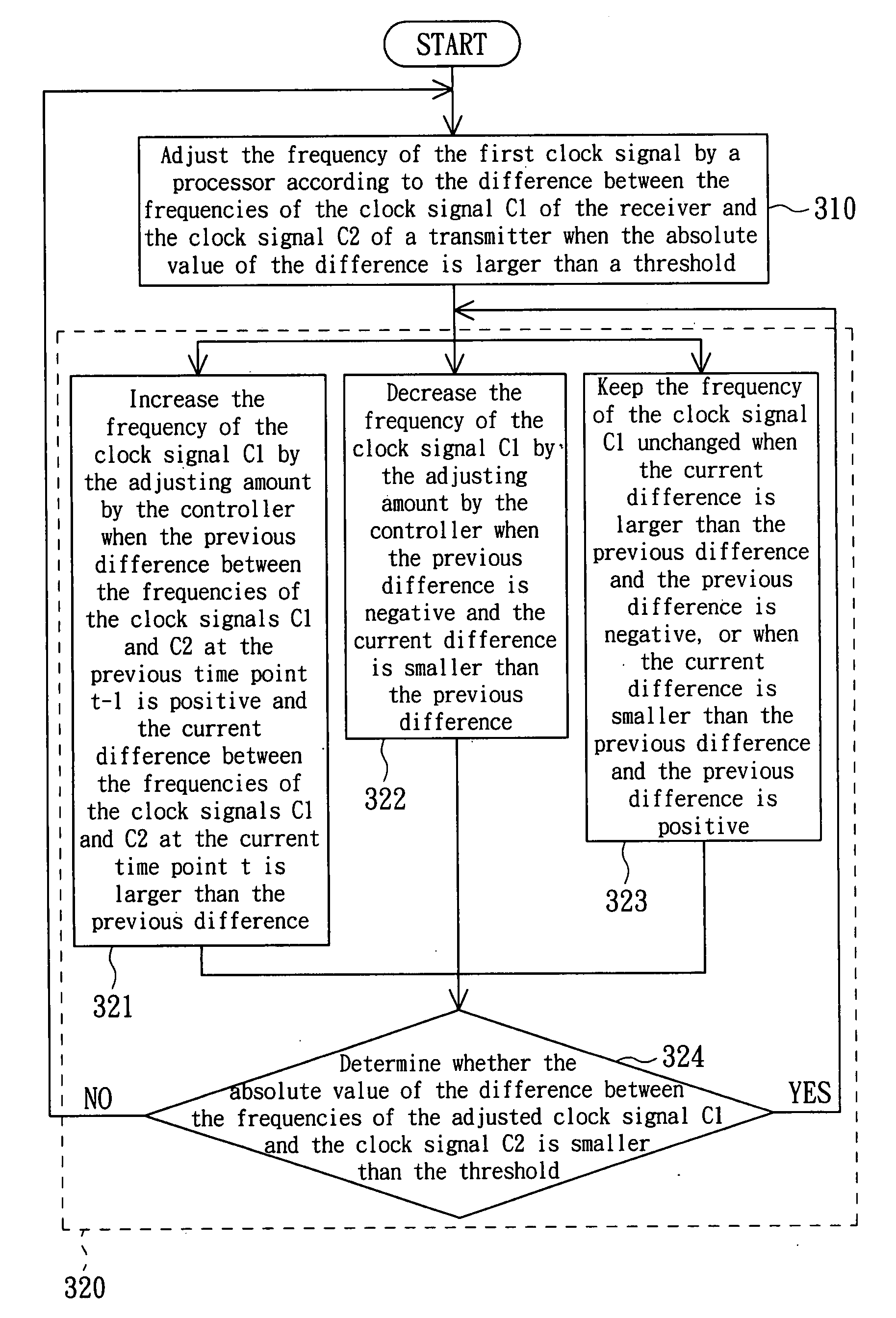

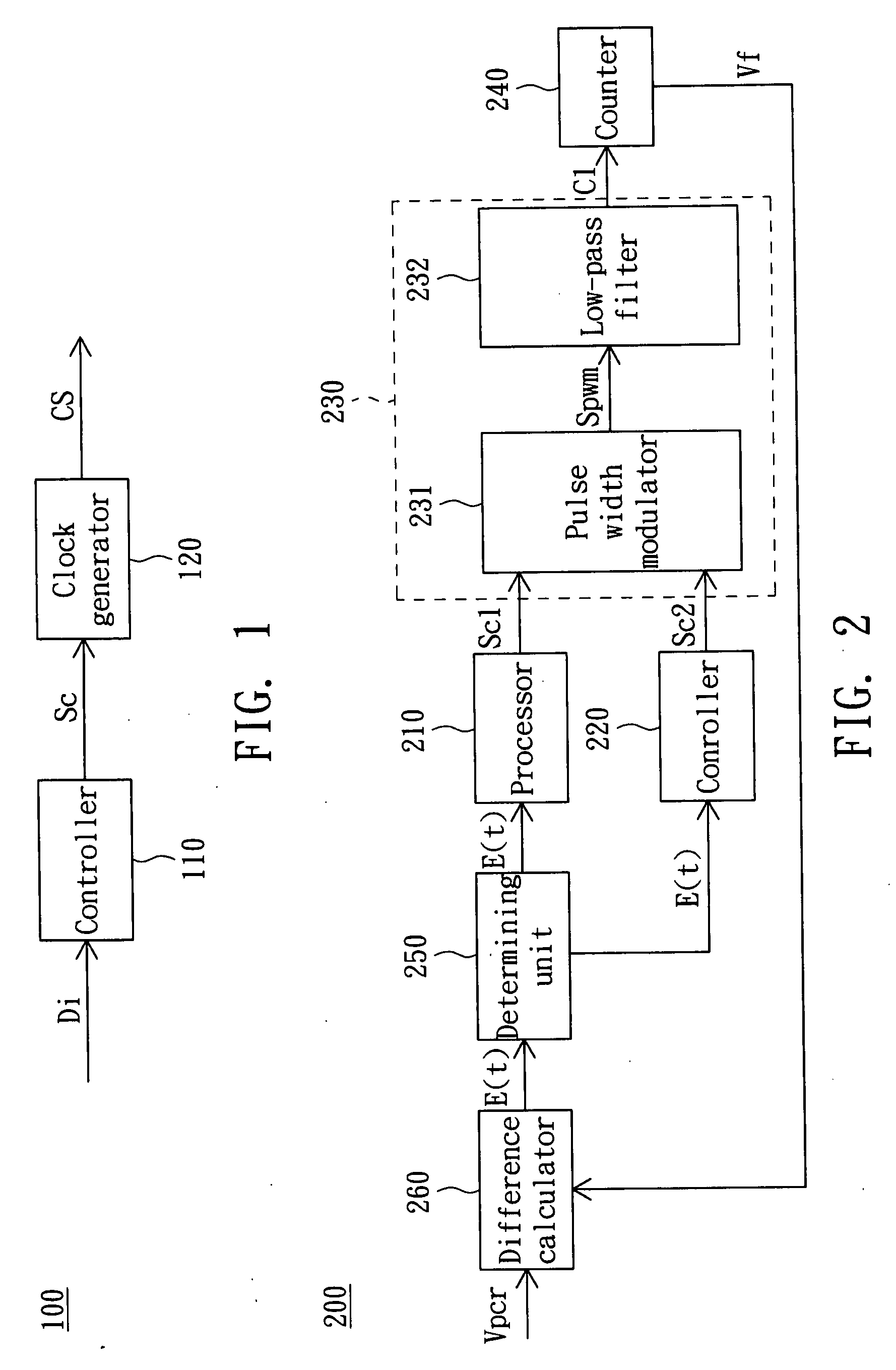

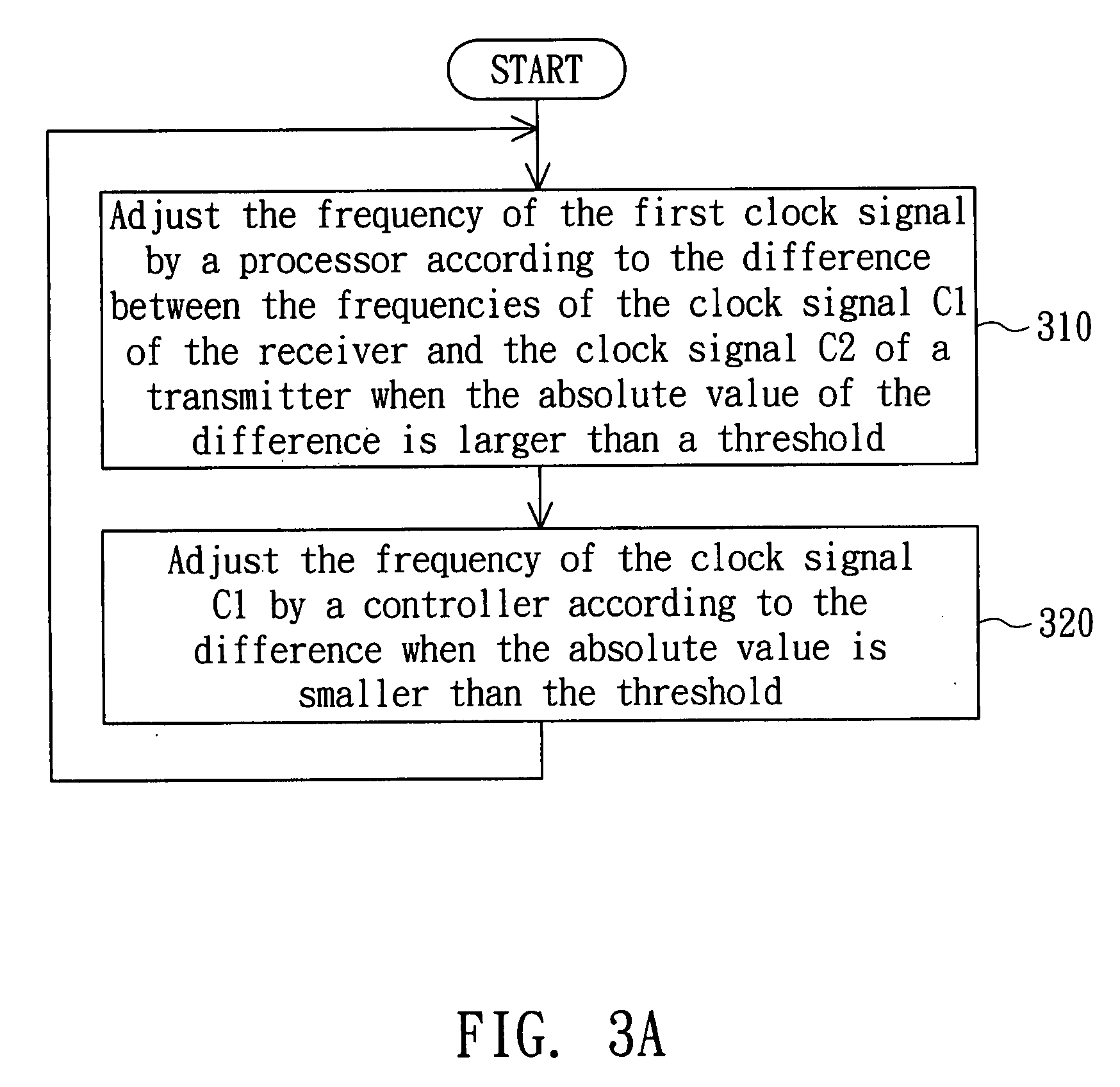

InactiveUS20090041091A1Reduce processor loadExecution efficiency is improvedTelevision system detailsTransmissionClock generatorCurrent time

A receiver having a first clock signal is provided. The first frequency of the first clock signal is adjusted to be close to a second frequency of a second clock signal of a transmitter. The receiver includes a clock generator, a processor and a controller. The clock generator is for generating the first clock signal. The processor is for outputting a first control signal to control the clock generator to adjust the first frequency to be close to the second frequency when an absolute value of a current difference between the first and the second frequencies at a current time point is larger than a threshold. The controller is for outputting a second control signal to control the clock generator when the absolute value of the current difference is smaller than the threshold, so as to reduce the load of the processor.

Owner:HIMAX TECH LTD

Method for discovering network device

ActiveUS7729294B2Low costExecution efficiency is improvedData switching by path configurationIp addressNetwork management

A method for discovering a network device is disclosed for executing a discovery procedure of the network device in a Data Link Layer (i.e. Layer 2 of OSI 7 Layers Model) via a Network Management Server (NMS) within a Local Area Network (LAN) system to discover other network devices within the LAN. Firstly, sending a discovery packet from a Network Management Server (NMS), wherein the discovery packet comprises a command for requesting the network device to send back a corresponding Media Access Control (MAC) address. Then, receiving the discovery packet by at least one of the network device, and generating a response packet corresponding to the discovery packet for sending the response packet, wherein the response packet comprises the Media Access Control (MAC) address of the network device. Then, receiving the response packet from the NMS for collecting the MAC address while ignoring an IP address in the response packet, and updating a device information table according to the MAC address for identifying the network device.

Owner:CAMEO COMM

Parallel processing system

ActiveUS8910167B2Improve executionExecution efficiency is improvedFinanceProgram synchronisationComputer moduleSoftware development

Software development tools and techniques for configuring parallel processing systems to execute software modules implementing processes for solving complex problems, including over-the-counter trading processes and foreign exchange trading processes, to execute quickly and efficiently. The parallel processing system may include low-cost, consumer-grade multicore processing units. A process for solving a complex problem may be divided into software modules, including by evaluating the process to determine discrete processing steps that produce an intermediate result on which later steps of the process depend. The software modules created for a process may form a template processing chain describing multiple processing chains of the process that are to be executed. A software development tool for producing configuration information for multicore processing units may evaluate the software modules and the processing chains to determine whether the modules will execute quickly and efficiently on the multicore processing units of the parallel processing system.

Owner:ONEZERO FINANCIAL SYST

Method and system for improved flash controller commands selection

ActiveUS9208108B2Execution efficiency is improvedImprove system efficiencyDigital computer detailsConcurrent instruction executionMicrocontrollerFlash memory controller

A system for selecting a subset of issued flash storage commands to improve processing time for command execution. A plurality of ports stores a first plurality of command identifiers and are associated with the plurality of ports. Each of the first plurality of arbiters selects an oldest command identifier among command identifiers within each corresponding port resulting in a second plurality of command identifiers. A second arbiter makes a plurality of selections from the second plurality of command identifiers based on command identifier age and the priority of the port. A session identifier queue stores commands associated with the plurality of selections among other commands forming a third plurality of commands. A microcontroller selects an executable command from the third plurality of commands for execution based on an execution optimization heuristic. After execution of the command, the command identifier in the port is cleared.

Owner:NVIDIA CORP

Data merging method, control circuit unit and storage device for flash memory

ActiveUS20210223976A1Execution efficiency is improvedMemory architecture accessing/allocationInput/output to record carriersComputer architectureEngineering

A data merging method for flash memory, a flash memory control circuit unit and a flash memory storage device are provided. The disclosure is applicable to a flash memory, an embedded memory device or a solid state drive of 3D structure. The method includes: selecting at least one source physical erasing unit from at least one first physical erasing unit according to a valid data count of the at least one first physical erasing unit and a valid data count of each of a plurality of memory sub-modules; and copying valid data in the at least one source physical erasing unit to at least one destination physical erasing unit to perform a valid data merging operation.

Owner:HEFEI CORE STORAGE ELECTRONICS LTD

Memory control method, memory storage device and memory control circuit unit

PendingUS20210397375A1Improve memory performanceExecution efficiency is improvedMemory architecture accessing/allocationInput/output to record carriersEngineeringPhysical address

A memory control method for a rewritable non-volatile memory module is provided according to an exemplary embodiment of the disclosure. The method includes: collecting valid data from a source unit; copying a first logical to physical mapping table corresponding to the source unit to generate a second logical to physical mapping table; updating the second logical to physical mapping table according to a physical address of a recycling unit expected to be written, and the second logical to physical mapping table is recorded with mapping information corresponding to the recycling unit; copying the valid data from the source unit into the recycling unit; and updating first management information according to the second logical to physical mapping table.

Owner:PHISON ELECTRONICS

Parallel processing system

InactiveUS20150052538A1Improve executionExecution efficiency is improvedFinanceProgram synchronisationComputer architectureEngineering

Software development tools and techniques for configuring parallel processing systems to execute software modules implementing processes for solving complex problems, including over-the-counter trading processes and foreign exchange trading processes, to execute quickly and efficiently. The parallel processing system may include low-cost, consumer-grade multicore processing units. A process for solving a complex problem may be divided into software modules, including by evaluating the process to determine discrete processing steps that produce an intermediate result on which later steps of the process depend. The software modules created for a process may form a template processing chain describing multiple processing chains of the process that are to be executed. A software development tool for producing configuration information for multicore processing units may evaluate the software modules and the processing chains to determine whether the modules will execute quickly and efficiently on the multicore processing units of the parallel processing system.

Owner:ONEZERO FINANCIAL SYST

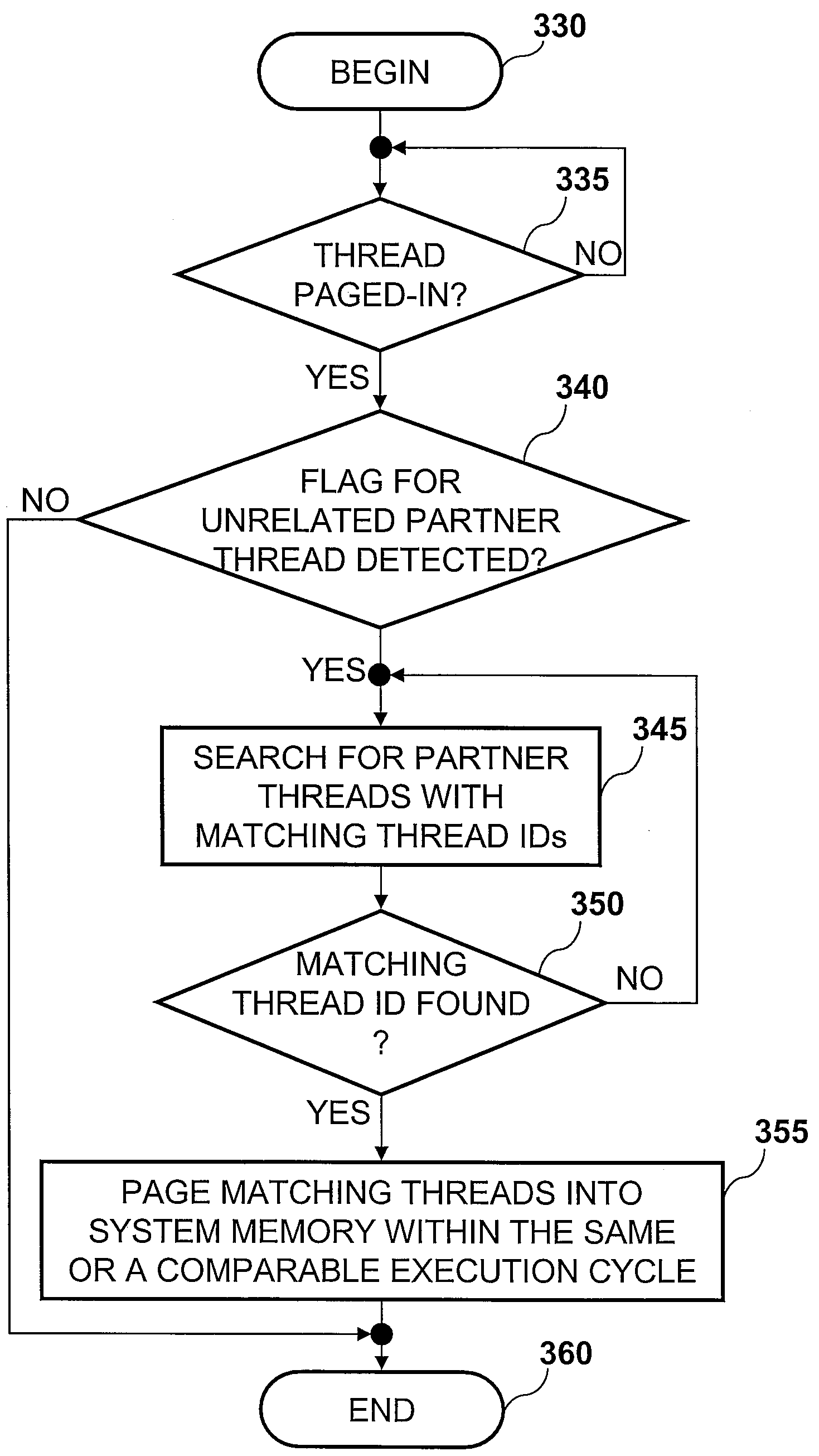

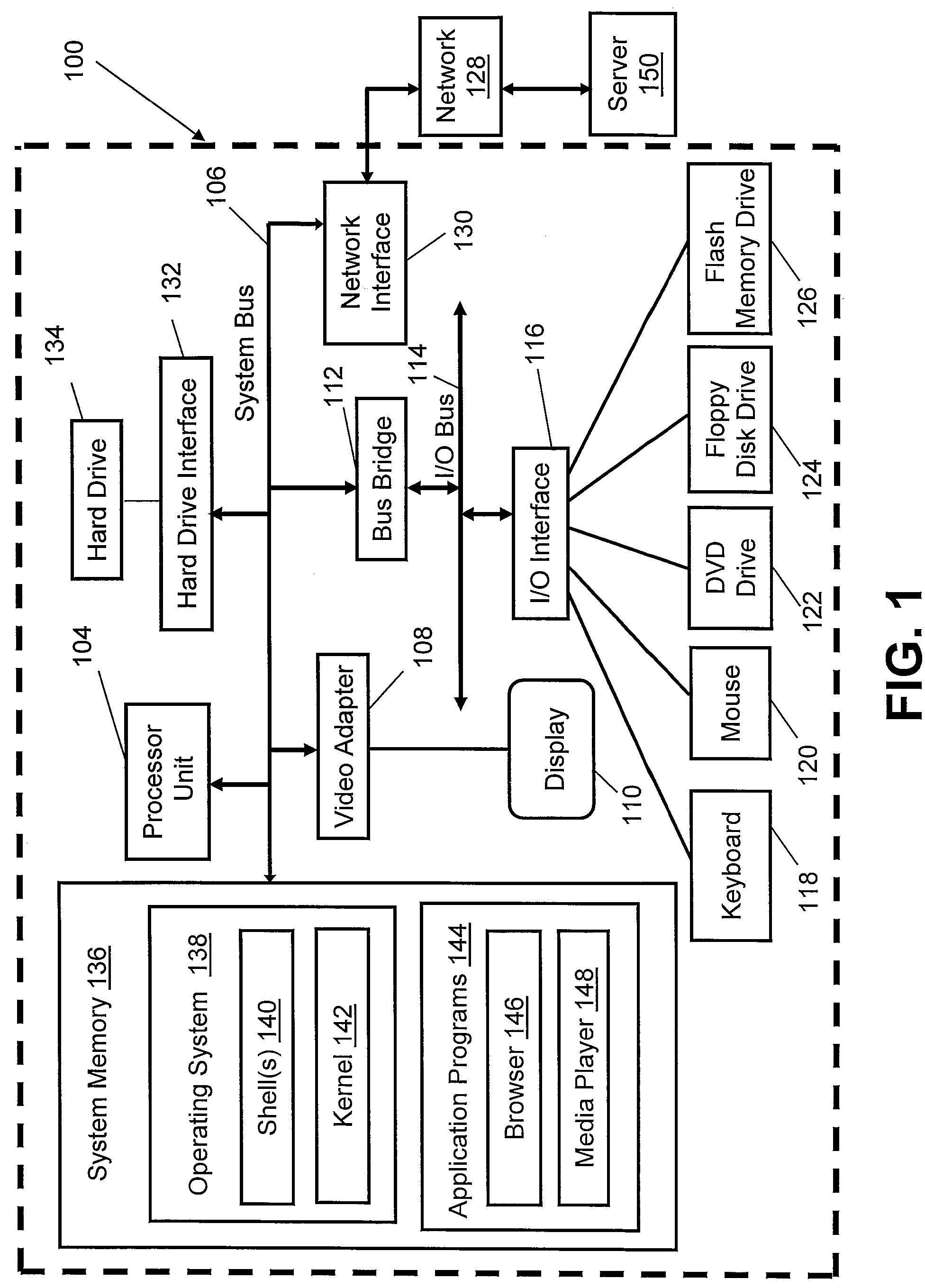

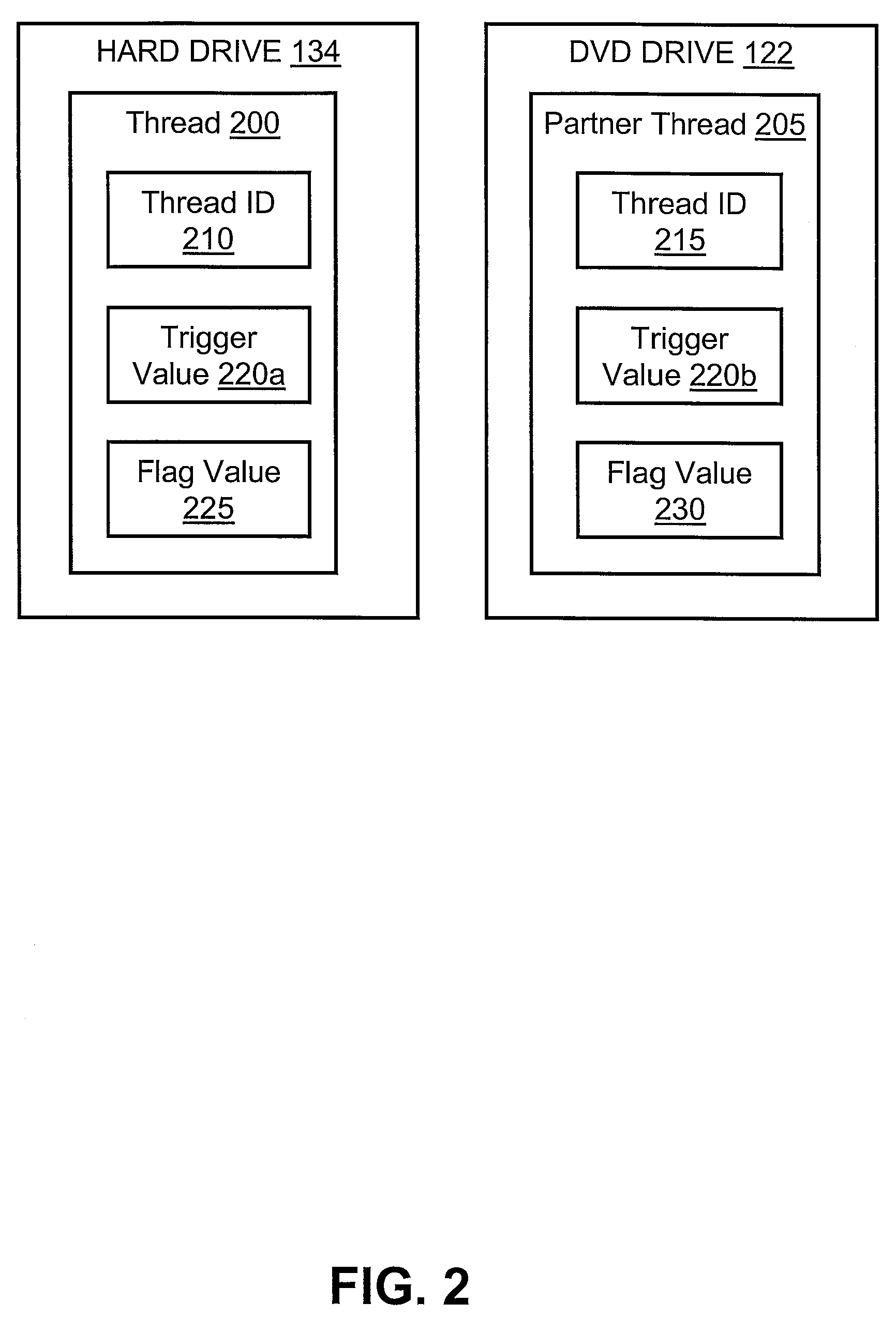

Method, system and program product for associating threads within non-related processes based on memory paging behaviors

InactiveUS7596668B2Eliminate delaysExecution efficiency is improvedMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemUser input

A method of tying related process threads within non-related applications together in terms of memory paging behavior. In a data processing system, a first process thread is related to one or more “partner” threads within separate high latency storage locations. The kernel analyzes the memory “page-in” patterns of multiple threads and identifies one or more partner threads of the first thread based on user input, observed memory page-in patterns, and / or pre-defined identification information within the thread data structures. The kernel marks the first thread and its corresponding related partner threads with a unique thread identifier. When the first thread is subsequently paged into a lower latency memory, the kernel also pages-in the related partner threads that are marked with the unique thread identifier in lockstep. Tying related threads from non-related applications together in terms of memory paging behavior thus eliminates memory management delays.

Owner:IBM CORP

Data merging method, control circuit unit and storage device for flash memory

ActiveUS11175847B2Execution efficiency is improvedMemory architecture accessing/allocationInput/output to record carriersComputer architectureEngineering

Owner:HEFEI CORE STORAGE ELECTRONICS LTD

Memory control method, memory storage device and memory control circuit unit

ActiveUS11144245B2Execution efficiency is improvedImprove executionInput/output to record carriersControl circuitData scatter

A memory control method is disclosed. The method includes: determining a mode for reading first data in a first management unit as a first mode or a second mode according to a data dispersion degree of the first data; reading the first data from the first management unit according to a physical distribution of the first data if the mode for reading the first data is determined as the first mode; and reading the first data from the first management unit according to a logical distribution of the first data if the mode for reading the first data is determined as the second mode. Furthermore, a memory storage device and a memory control circuit unit are also disclosed.

Owner:PHISON ELECTRONICS