Arithmetic circuit, arithmetic processing device, and arithmetic processing method

A technology for computing circuits and circuits, which is applied in the field of arithmetic circuits, and can solve the problems of arithmetic circuit logic quality limitations, difficult subtraction and shift-type arithmetic circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

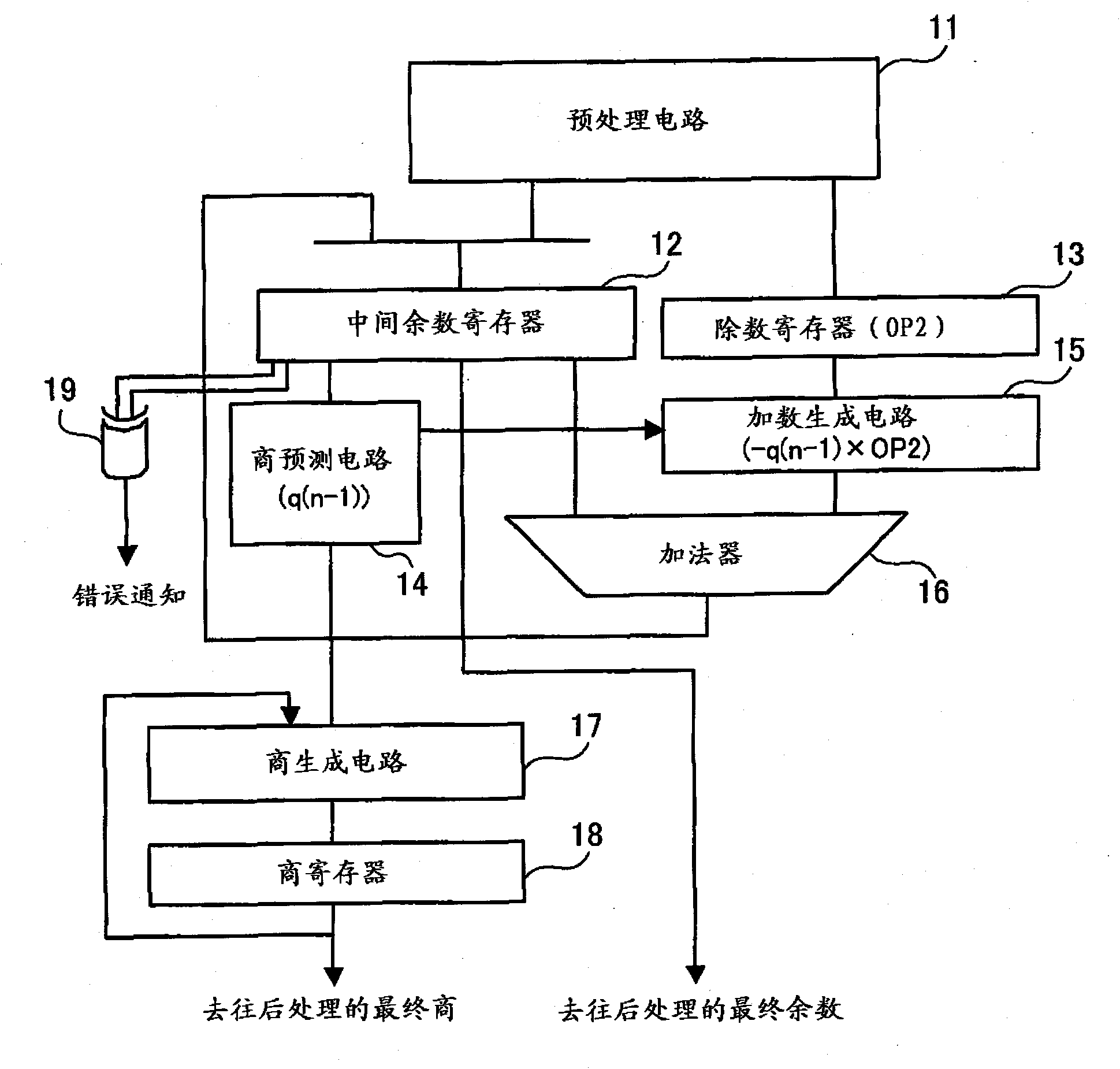

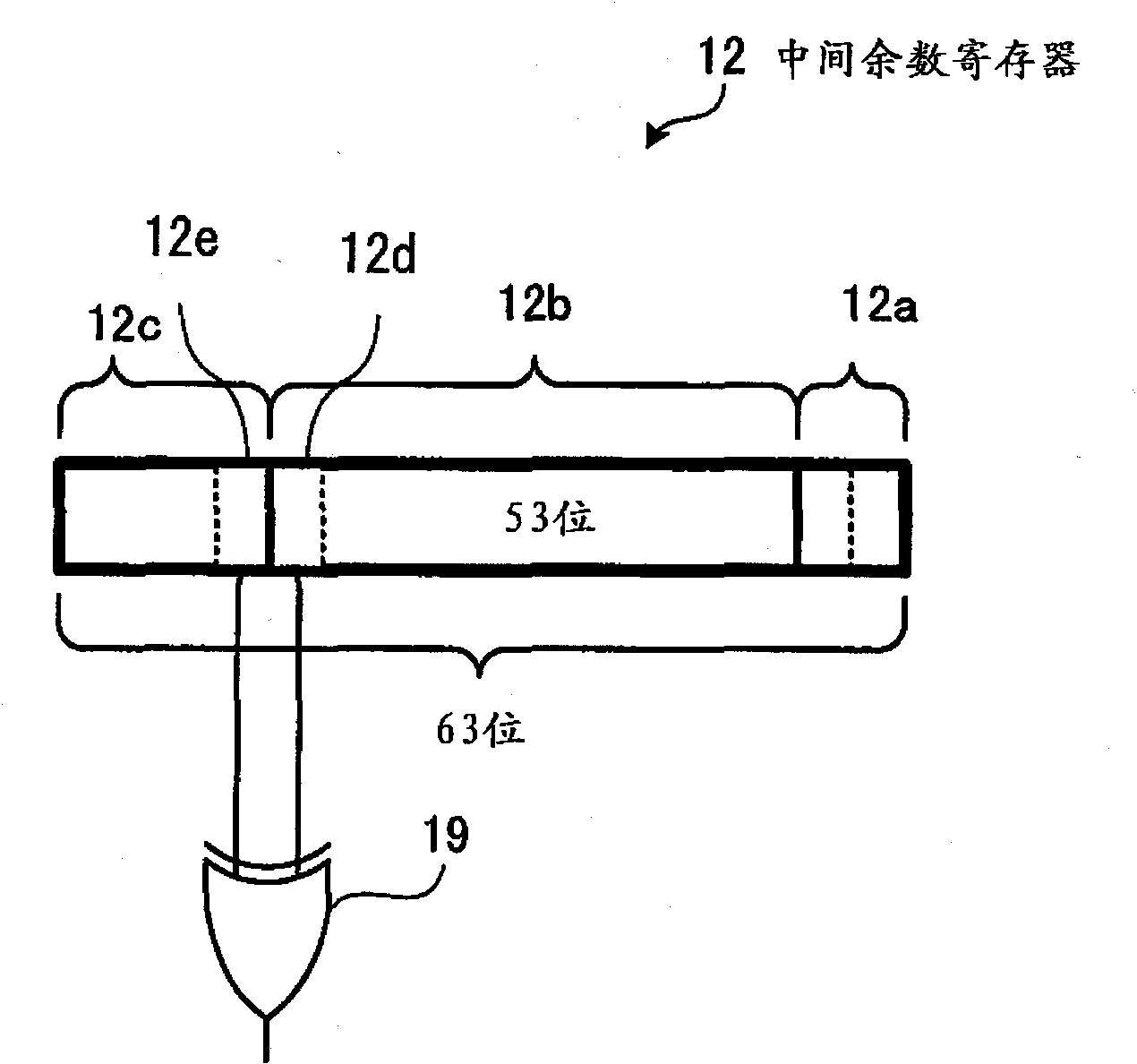

[0022] Embodiments are described below with reference to the drawings, wherein like numerals refer to like elements throughout.

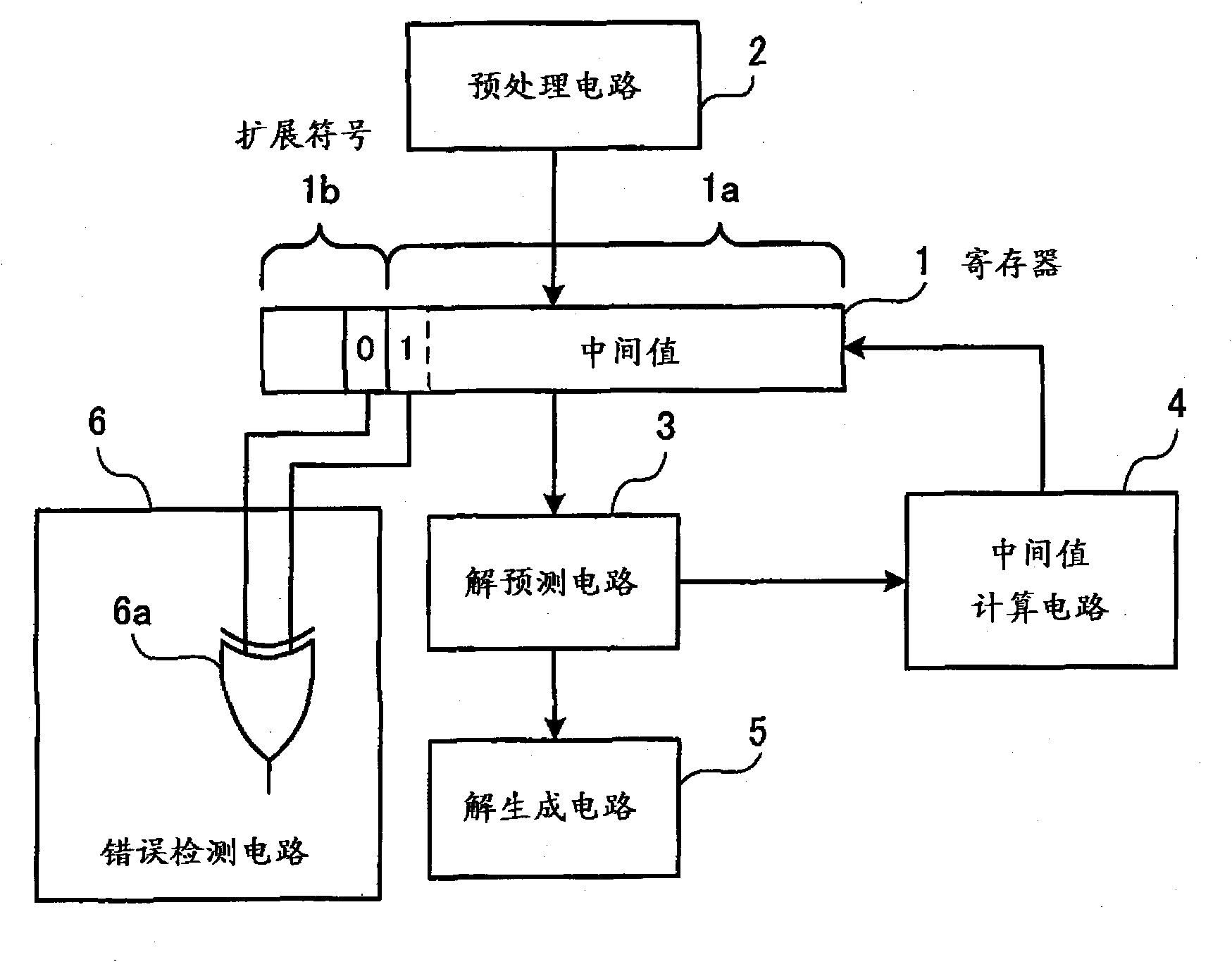

[0023] figure 1 An arithmetic circuit according to the first embodiment is illustrated. figure 1 The arithmetic circuit includes a register 1 , a preprocessing circuit 2 , a solution prediction circuit 3 , an intermediate value calculation circuit 4 , a solution generation circuit 5 and an error detection circuit 6 .

[0024] figure 1 Register 1 in represents one or more registers. The register 1 stores an intermediate value 1a generated by the intermediate value calculation circuit 4 and an extension sign 1b added to the intermediate value 1a by sign extension of the intermediate value 1a.

[0025] The processing circuit 2 stores in the register 1 one or more values on which an arithmetic operation is to be performed. For example, the preprocessing circuit 2 stores the dividend in the register 1 when the register 1 performs division or stores...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More