Patents

Literature

107 results about "Barrel shifter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

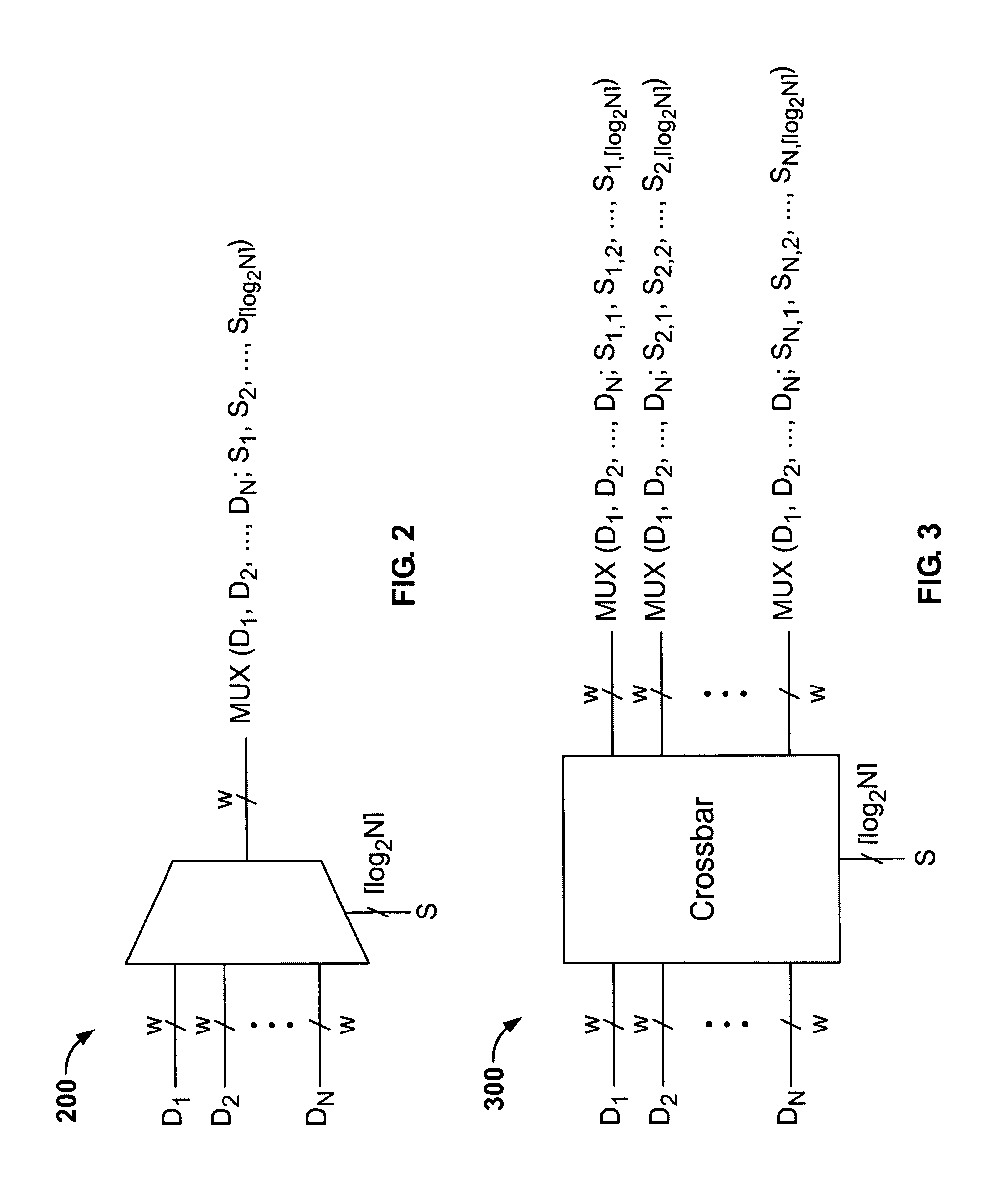

A barrel shifter is a digital circuit that can shift a data word by a specified number of bits without the use of any sequential logic, only pure combinational logic. One way to implement it is as a sequence of multiplexers where the output of one multiplexer is connected to the input of the next multiplexer in a way that depends on the shift distance. A barrel shifter is often used to shift and rotate n-bits in modern microprocessors, typically within a single clock cycle.

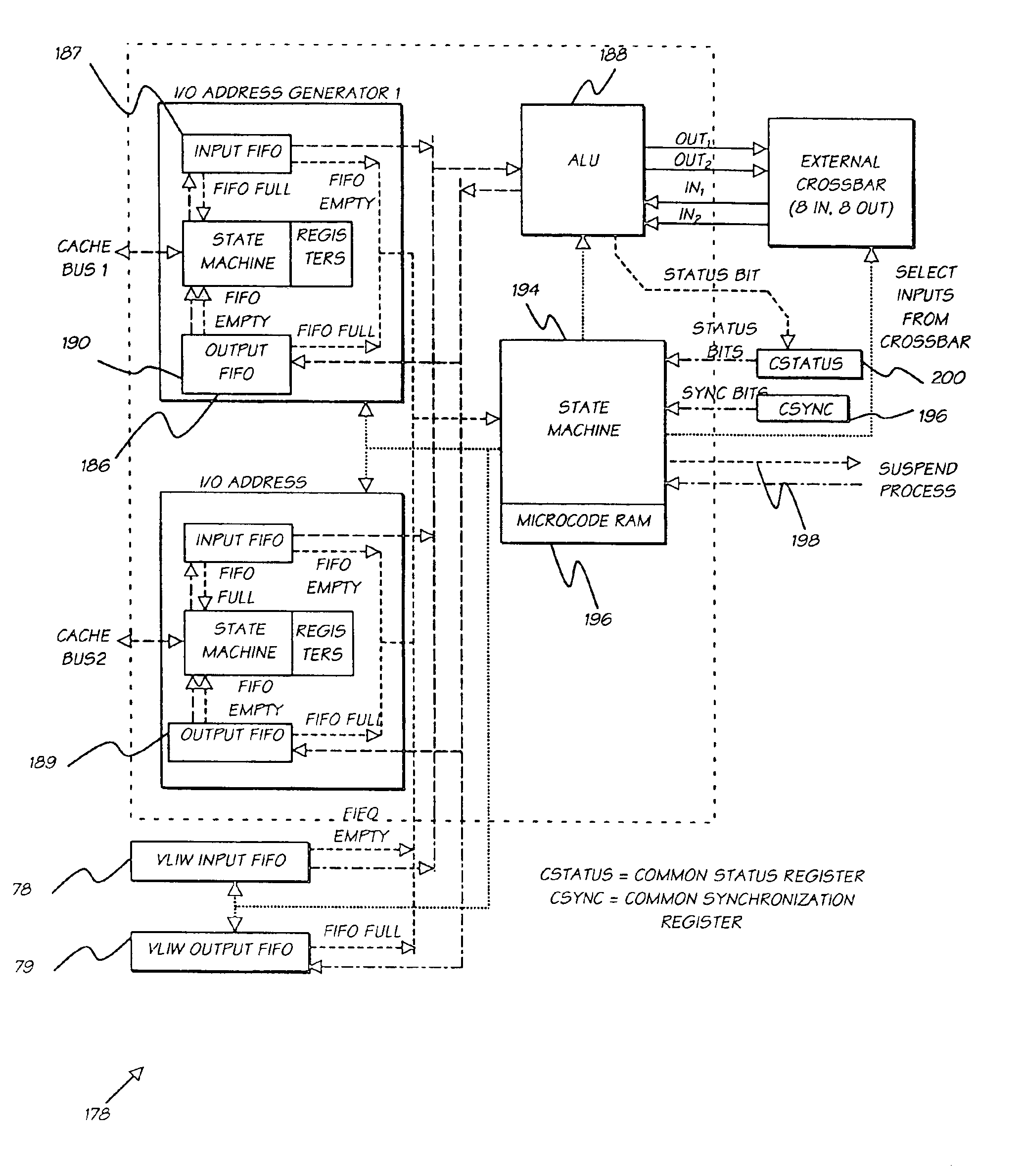

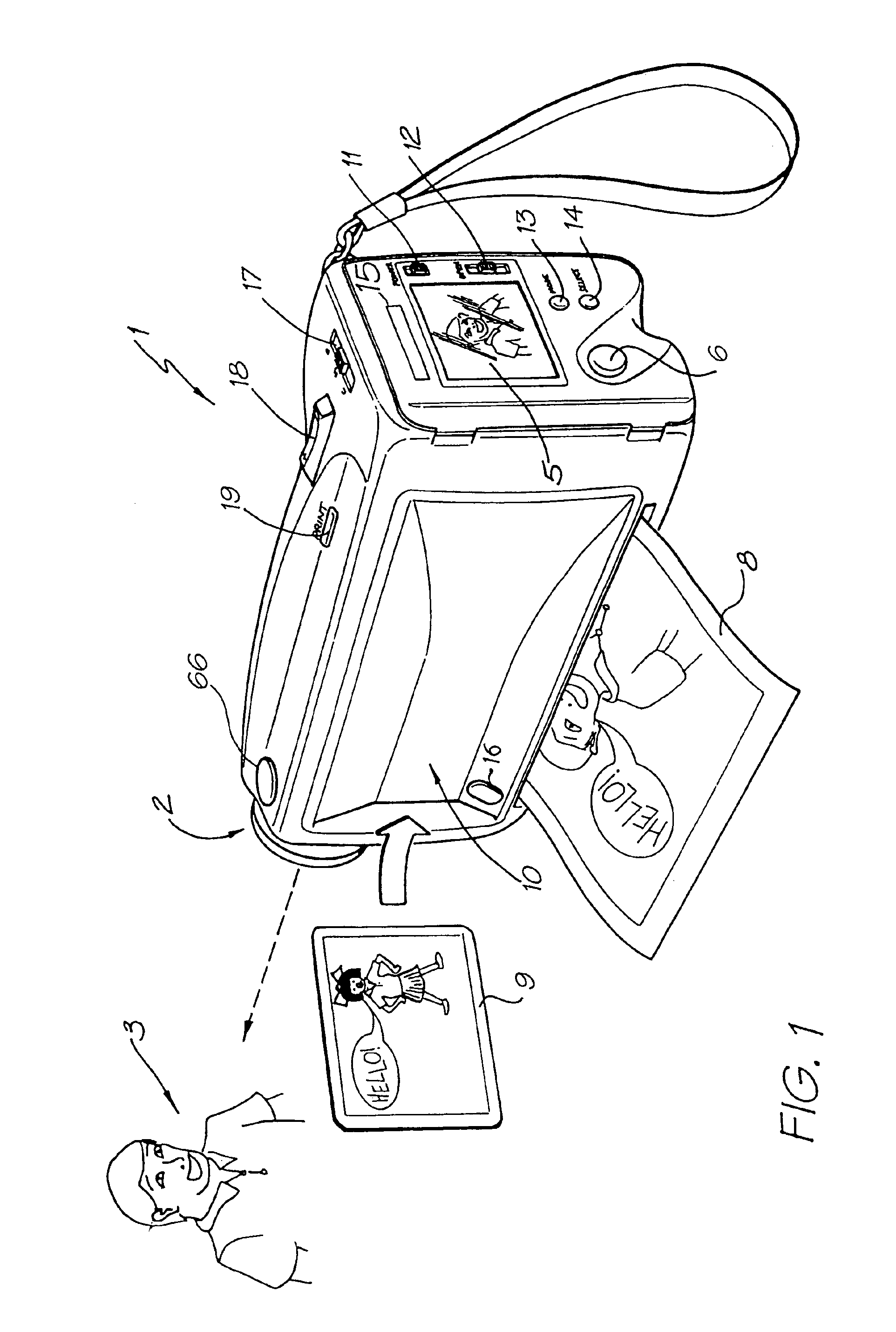

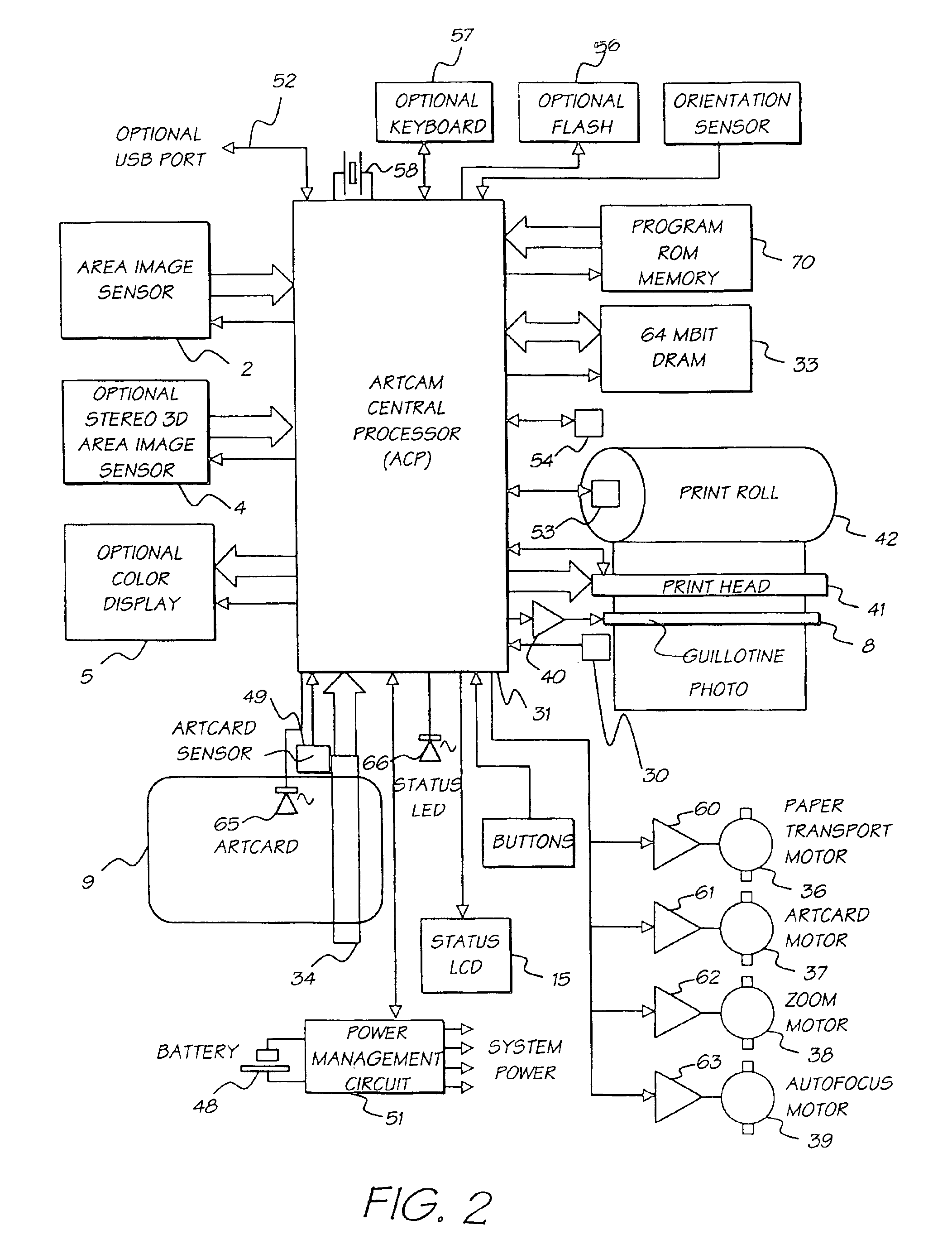

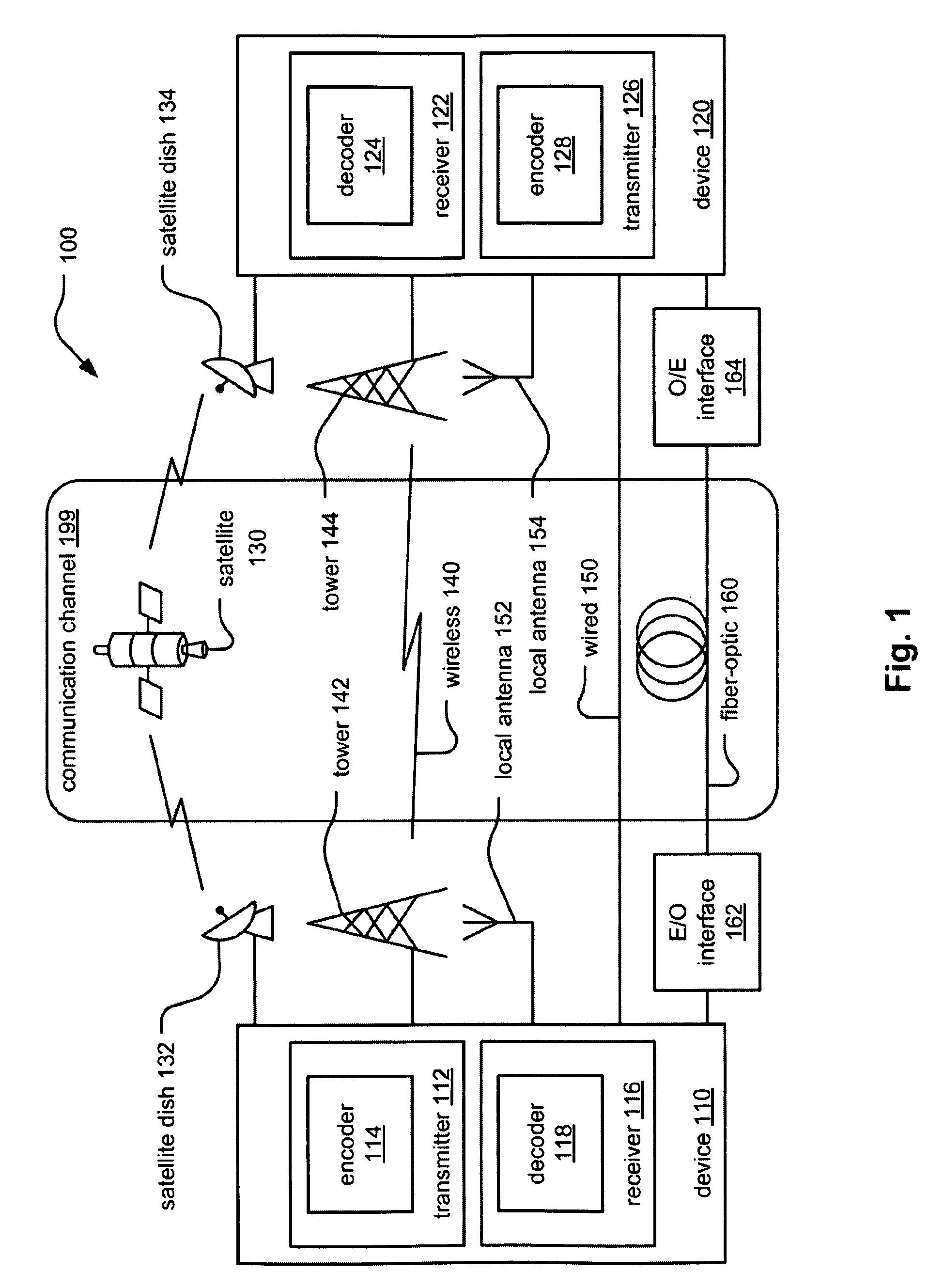

Digital camera system containing a VLIW vector processor

InactiveUS6879341B1Material nanotechnologyTelevision system detailsCrossbar switchArithmetic logic unit

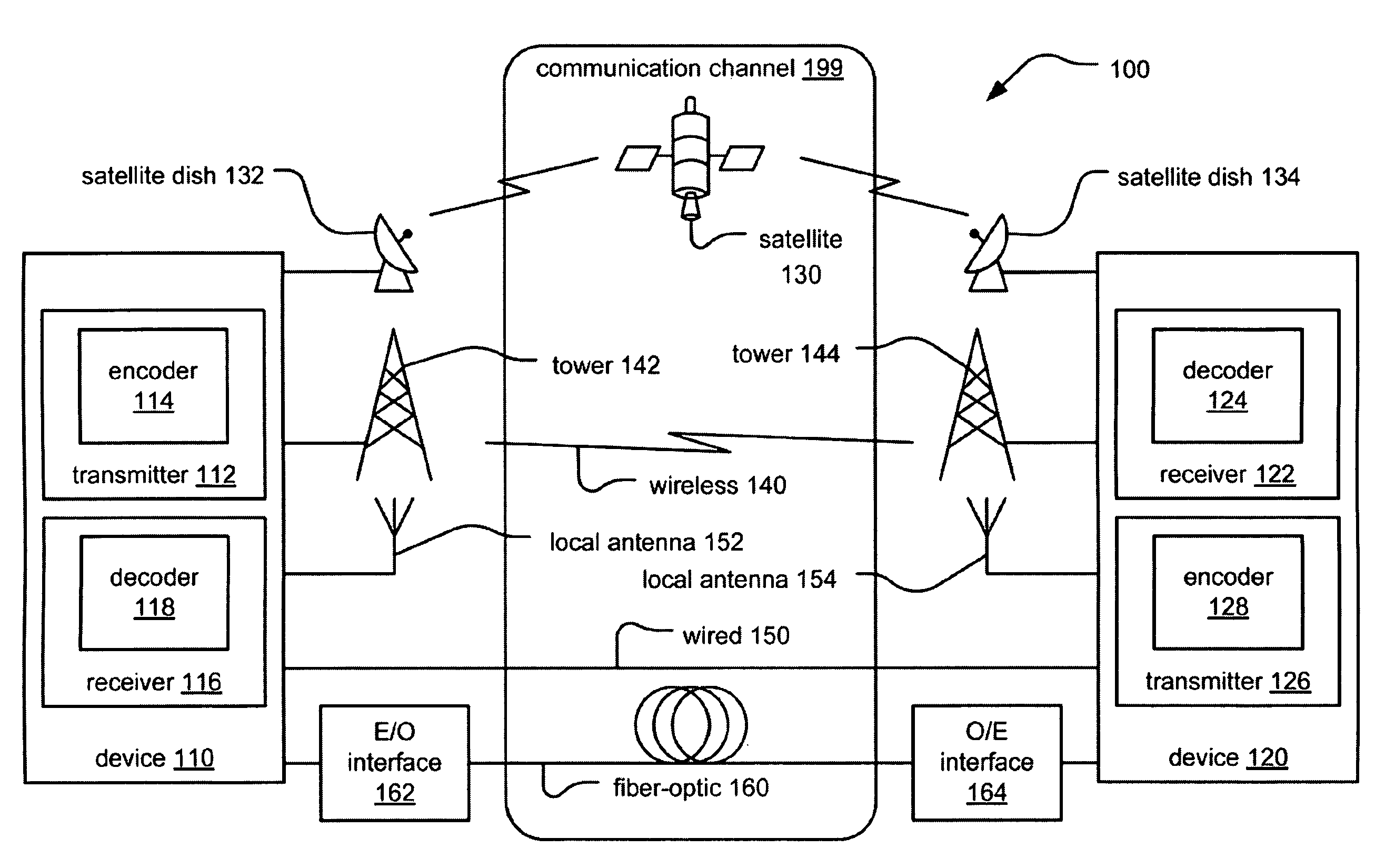

A digital camera has a sensor for sensing an image, a processor for modifying the sensed image in accordance with instructions input into the camera and an output for outputting the modified image where the processor includes a series of processing elements arranged around a central crossbar switch. The processing elements include an Arithmetic Logic Unit (ALU) acting under the control of a writeable microcode store, an internal input and output FIFO for storing pixel data to be processed by the processing elements and the processor is interconnected to a read and write FIFO for reading and writing pixel data of images to the processor. Each of the processing elements can be arranged in a ring and each element is also separately connected to its nearest neighbors. The ALU receives a series of inputs interconnected via an internal crossbar switch to a series of core processing units within the ALU and includes a number of internal registers for the storage of temporary data. The core processing units can include at least one of a multiplier, an adder and a barrel shifter. The processing elements are further connected to a common data bus for the transfer of a pixel data to the processing elements and the data bus is interconnected to a data cache which acts as an intermediate cache between the processing elements and a memory store for storing the images.

Owner:GOOGLE LLC

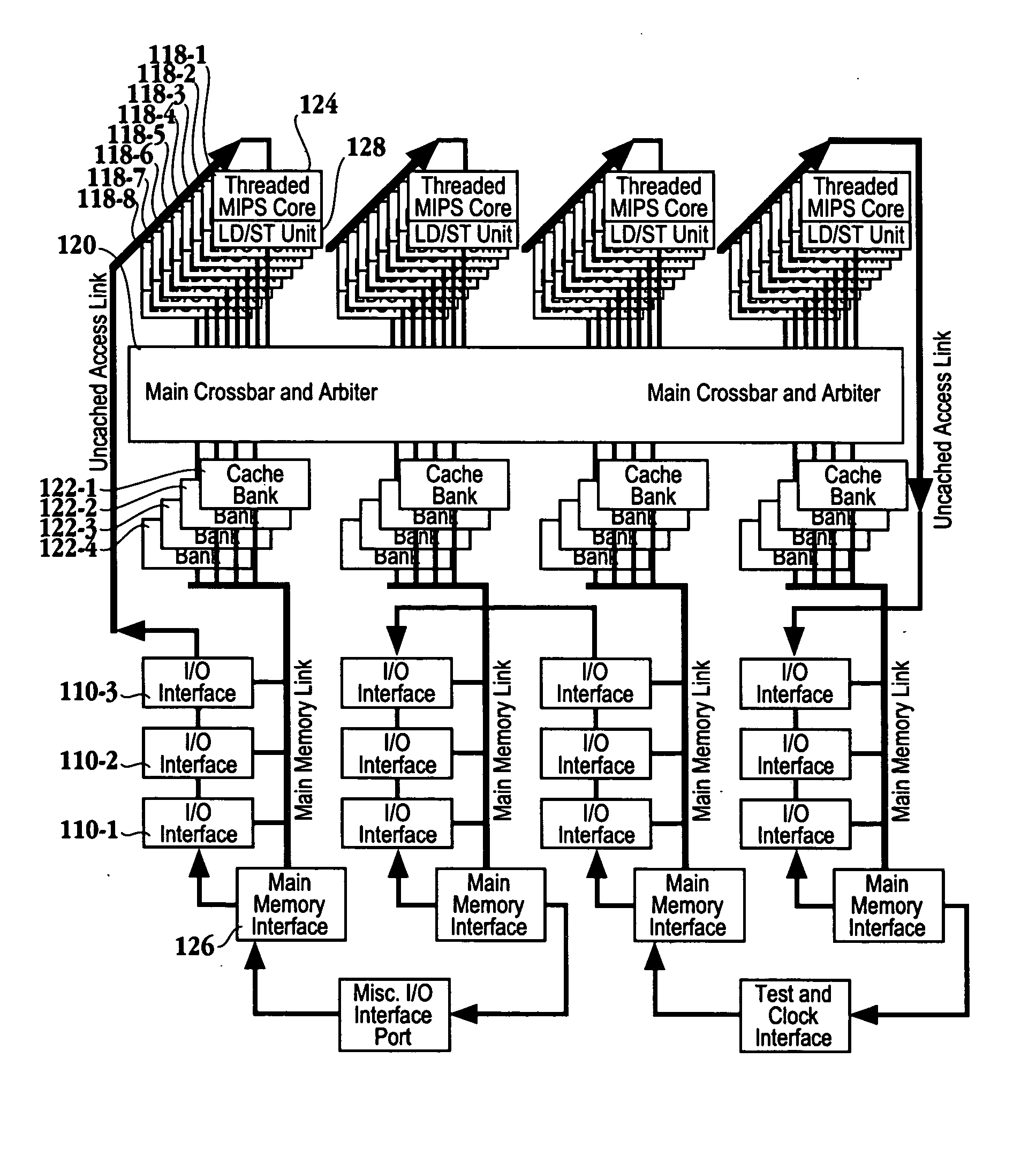

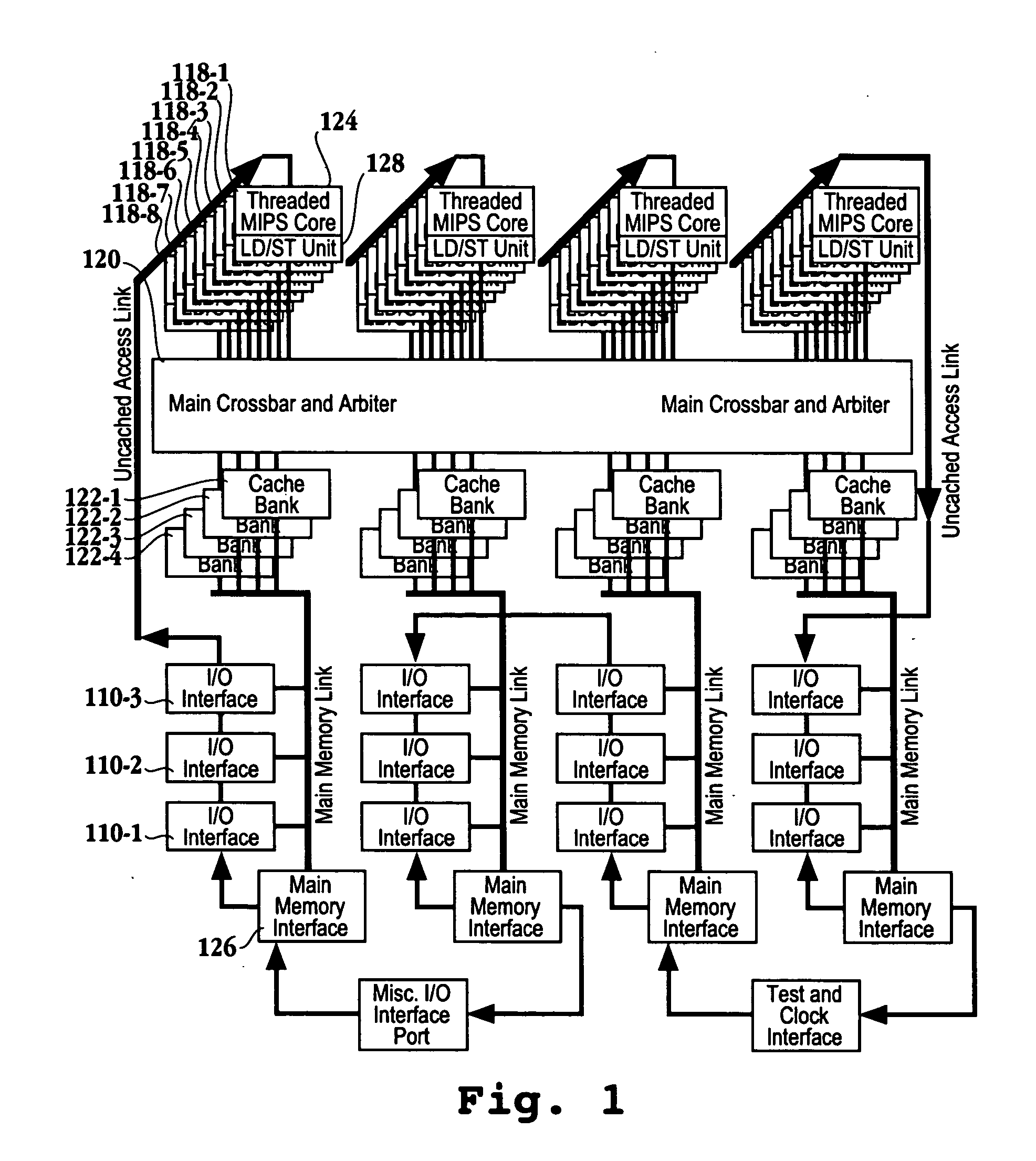

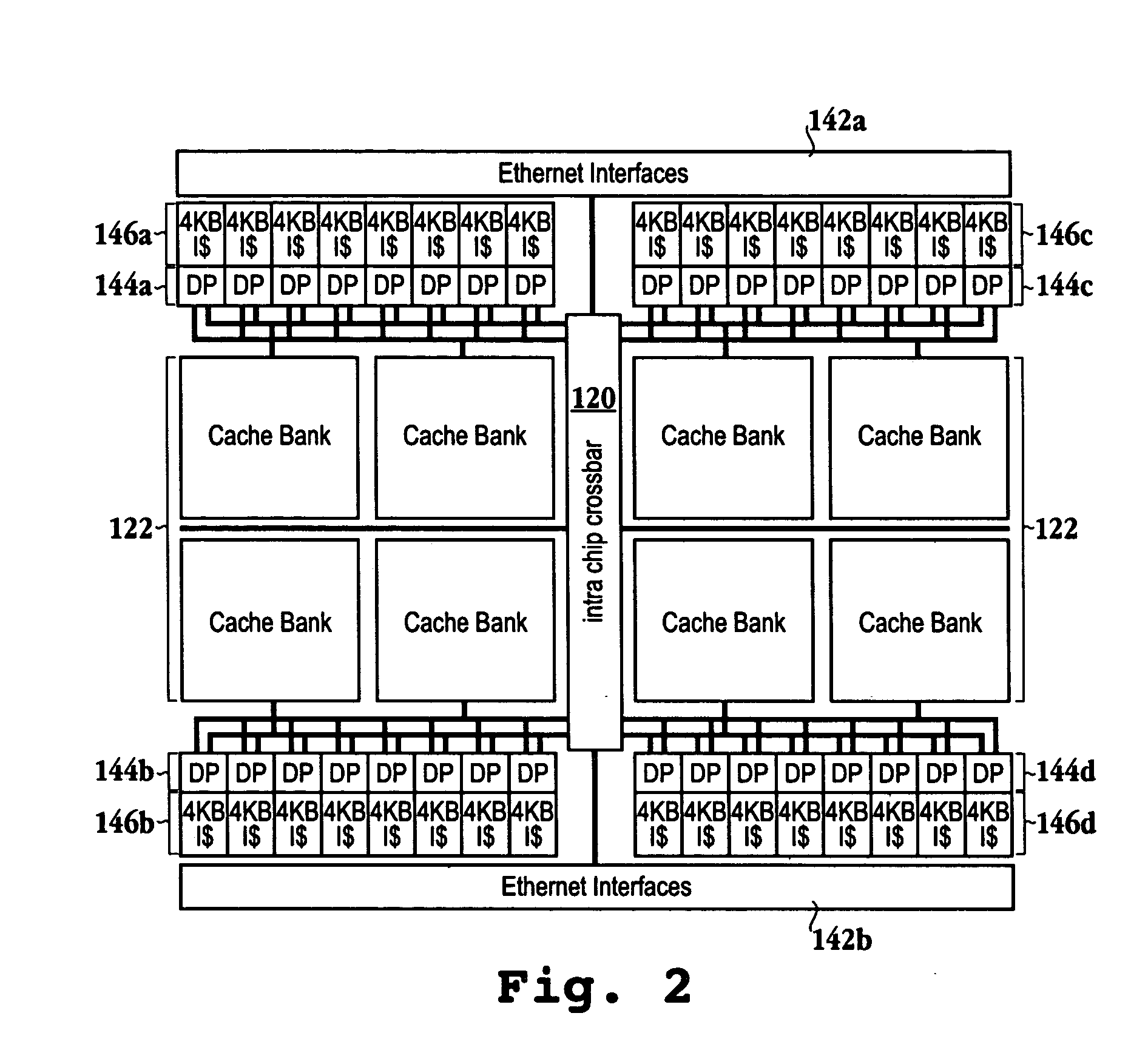

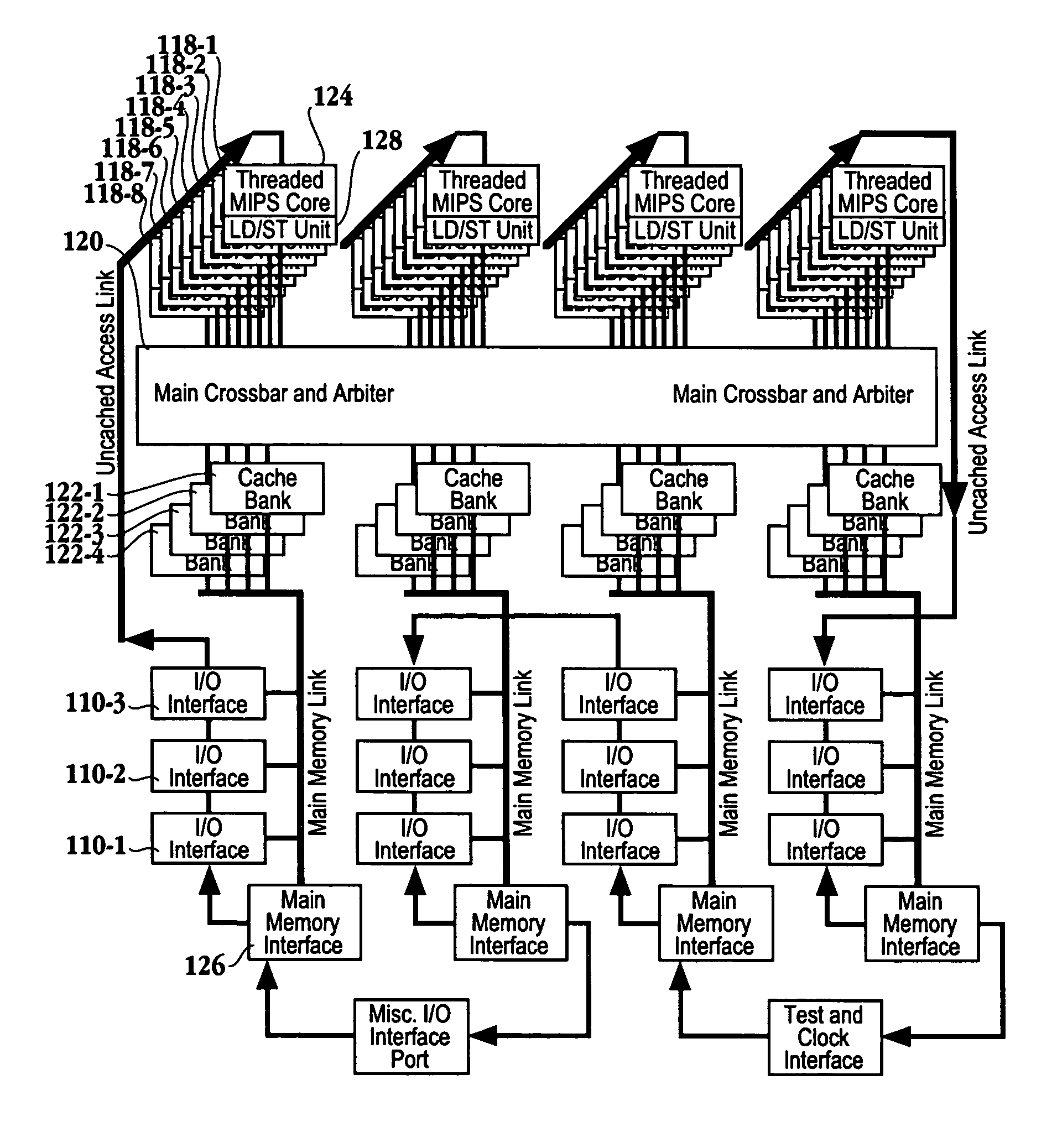

Cache crossbar arbitration

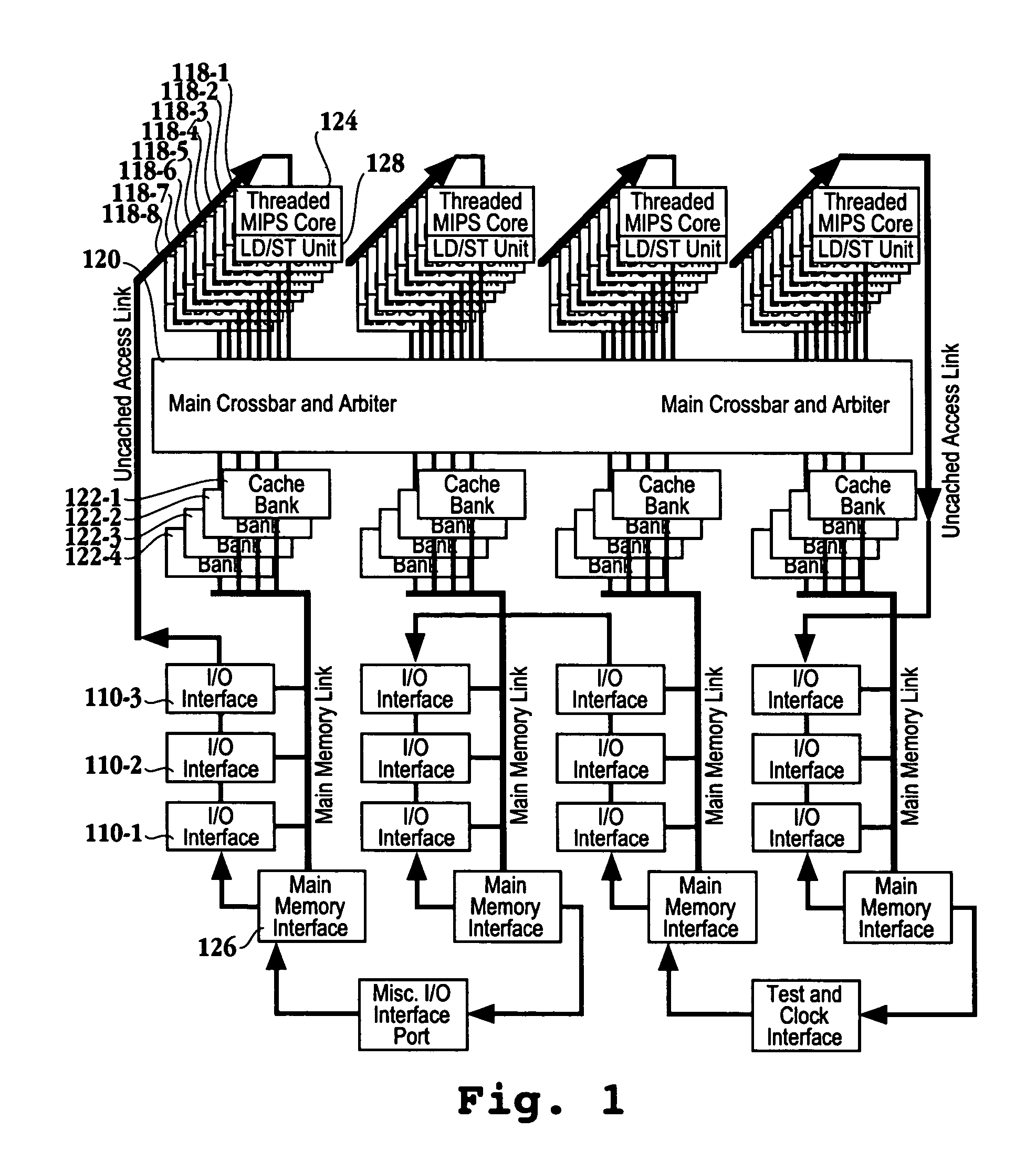

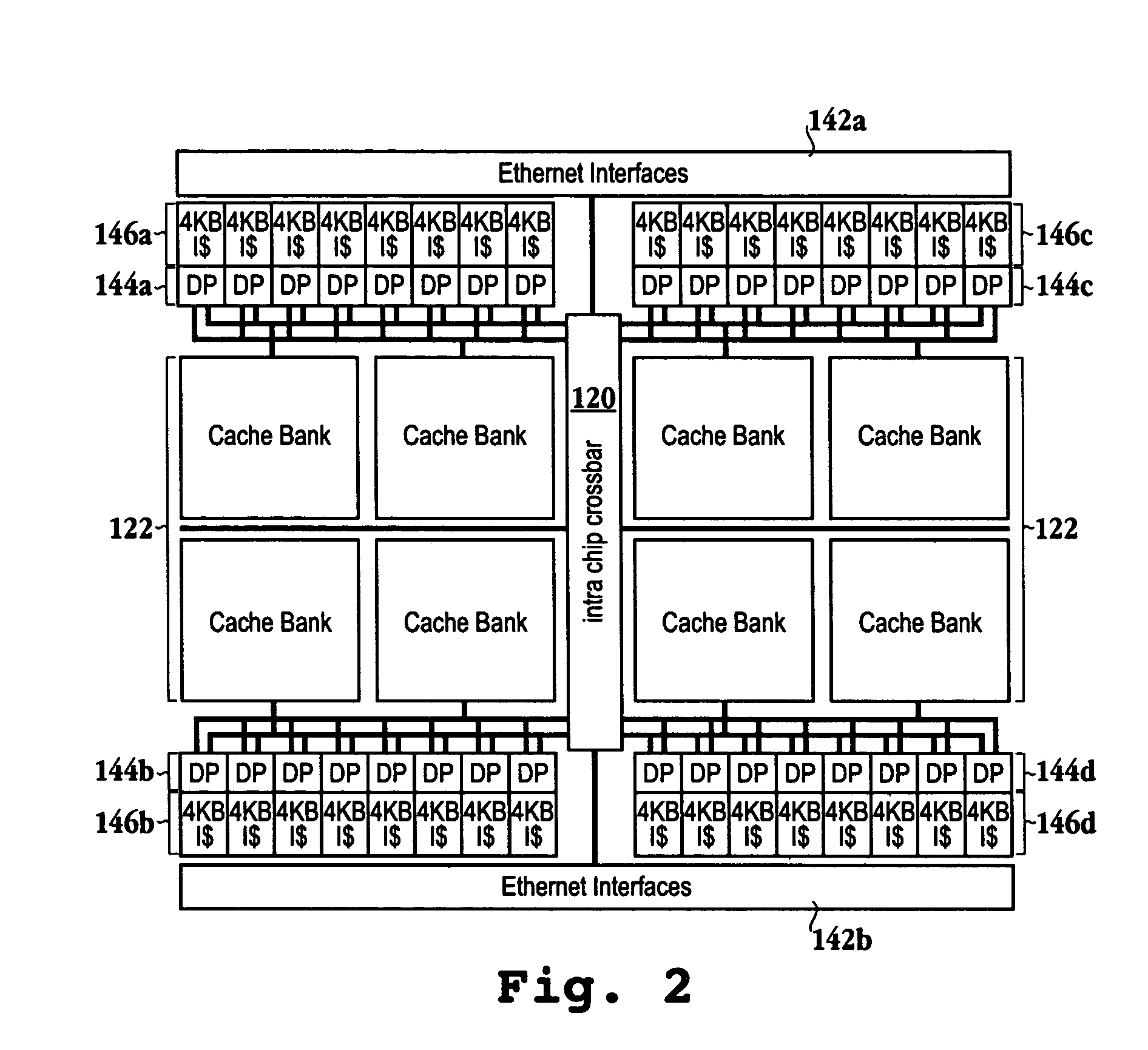

ActiveUS20050060457A1Efficient processingMemory adressing/allocation/relocationConcurrent instruction executionProcessing coreParallel computing

A processor chip is provided. The processor chip includes a plurality of processing cores, where each of the processing cores are multi-threaded. The plurality of processing cores are located in a center region of the processor chip. A plurality of cache bank memories are included. A crossbar enabling communication between the plurality of processing cores and the plurality of cache bank memories is provided. The crossbar includes an arbiter configured to arbitrate multiple requests received from the plurality of processing cores with available outputs. The arbiter includes a barrel shifter configured to rotate the multiple requests for dynamic prioritization, and priority encoders associated with each of the available outputs. Each of the priority encoders have logic gates configured to disable priority encoder outputs. A method for arbitrating requests within a multi-core multi-thread processor is included.

Owner:ORACLE INT CORP

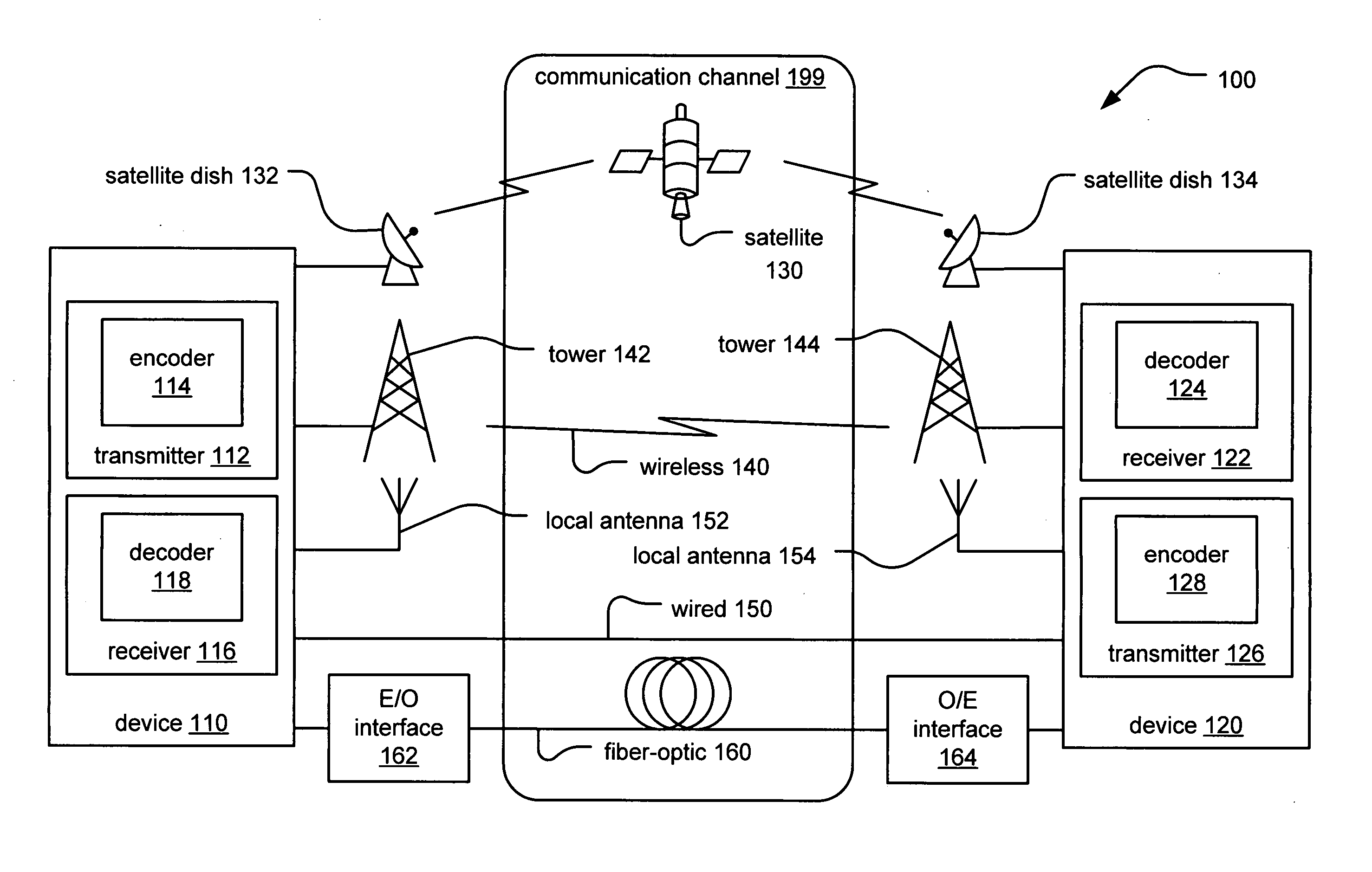

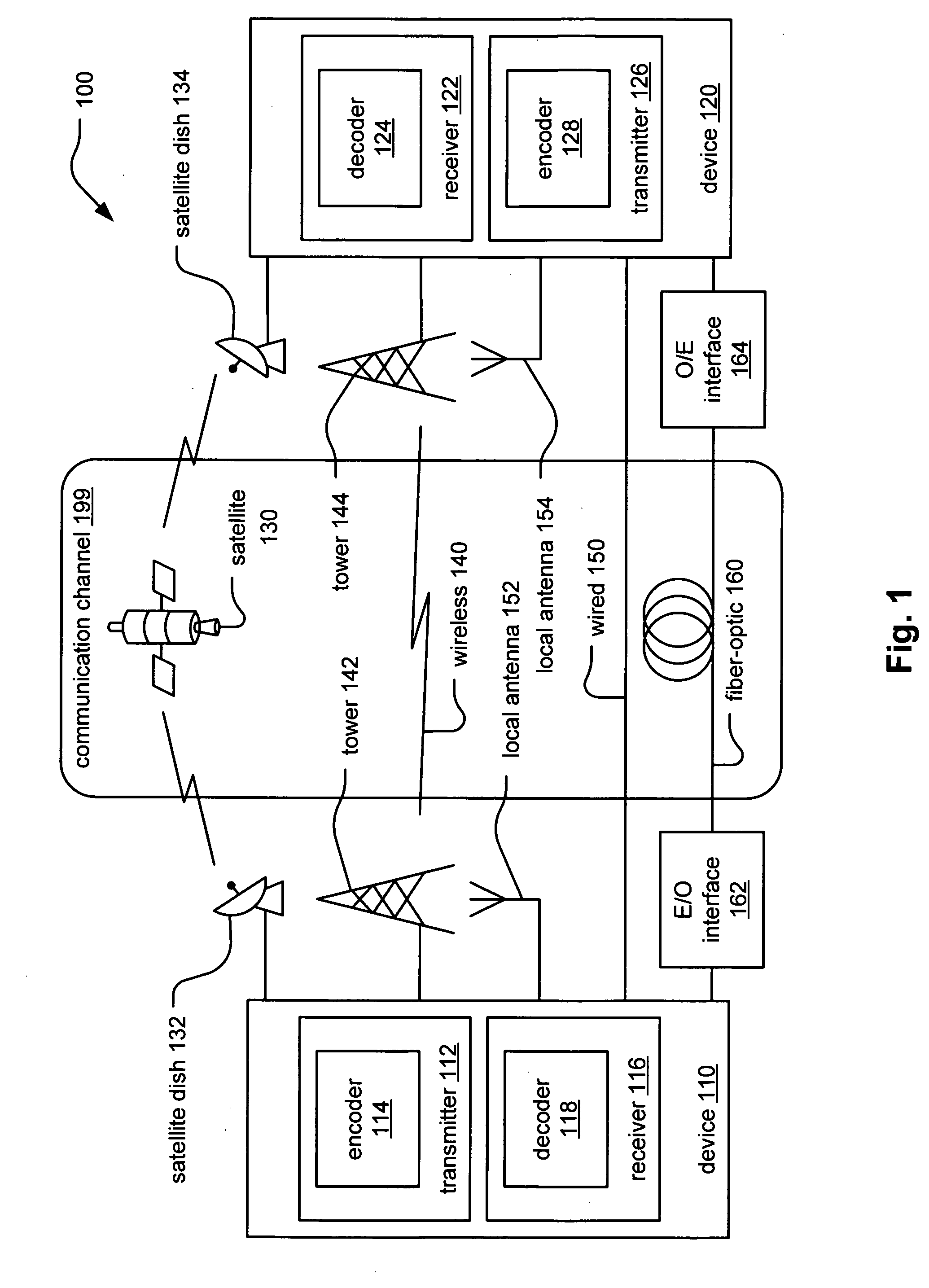

Message passing memory and barrel shifter arrangement in LDPC (Low Density Parity Check) decoder supporting multiple LDPC codes

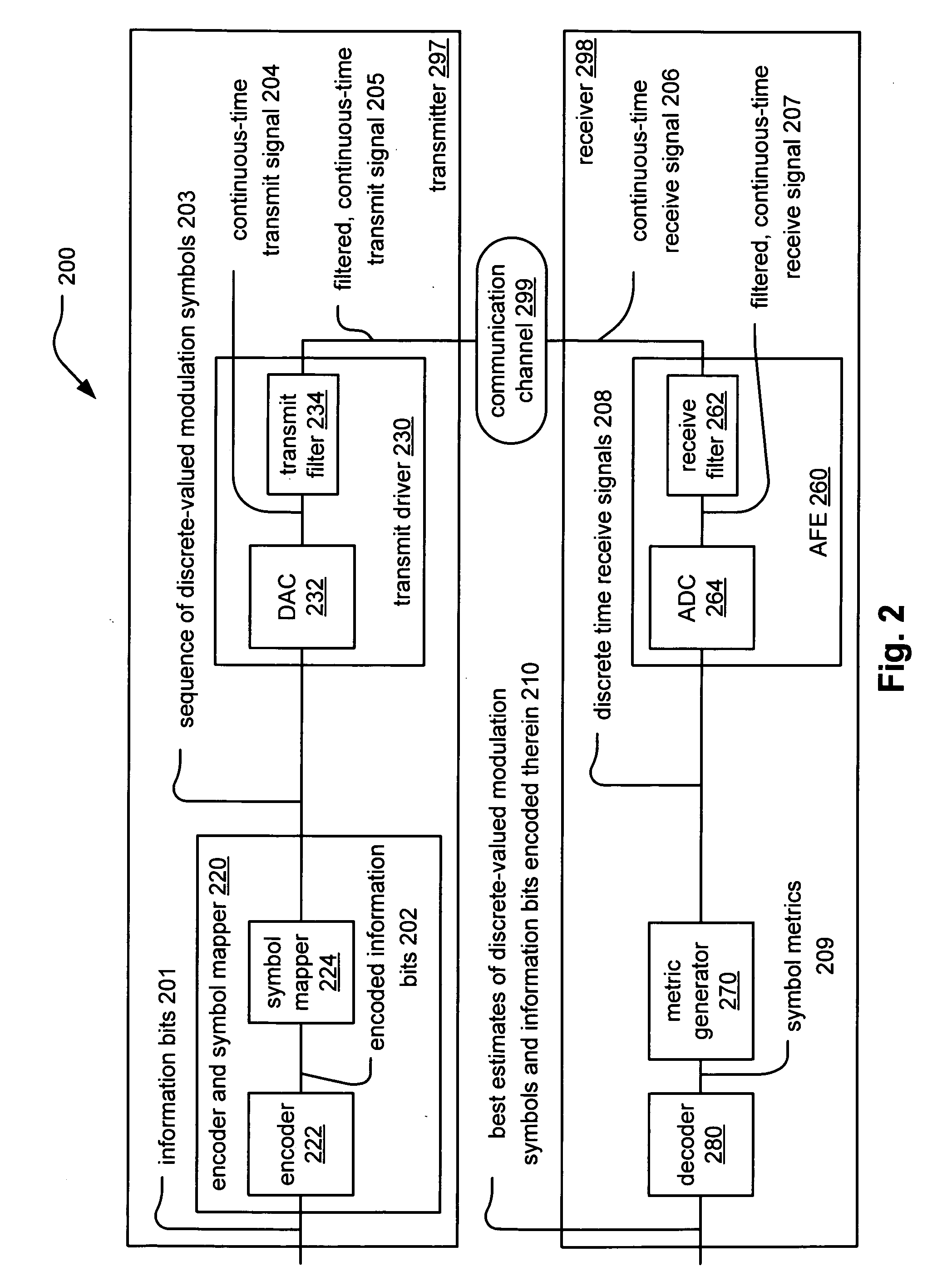

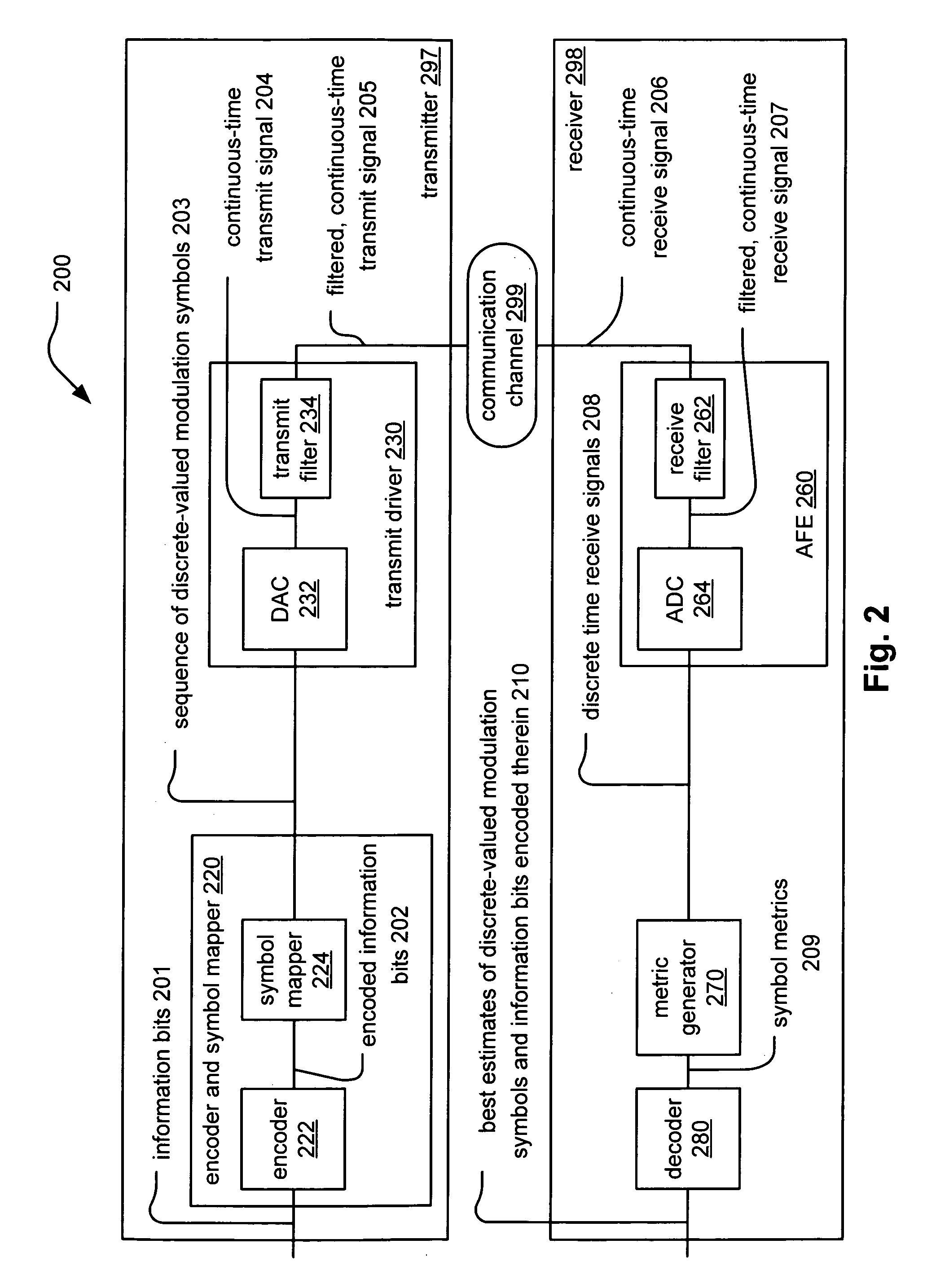

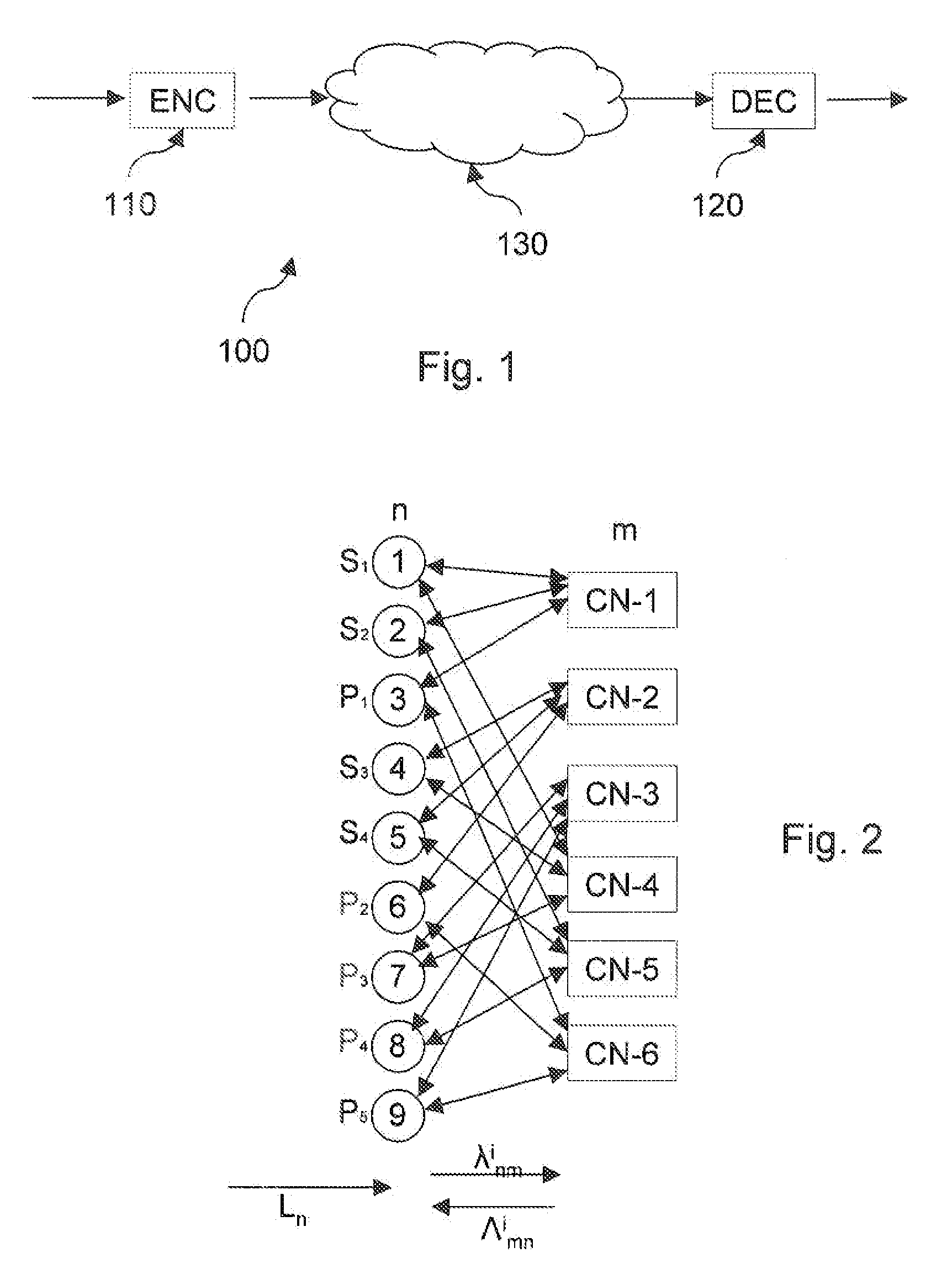

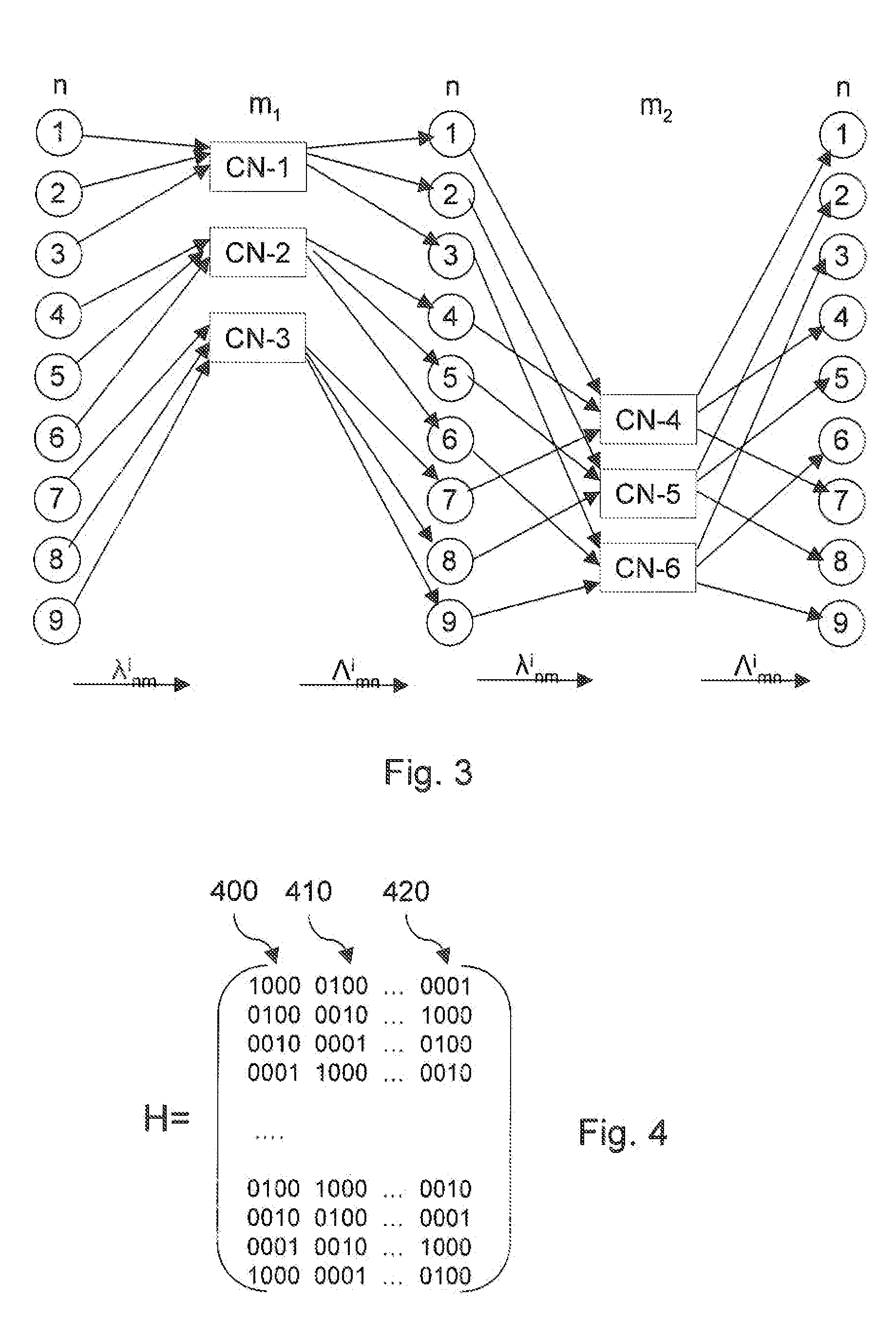

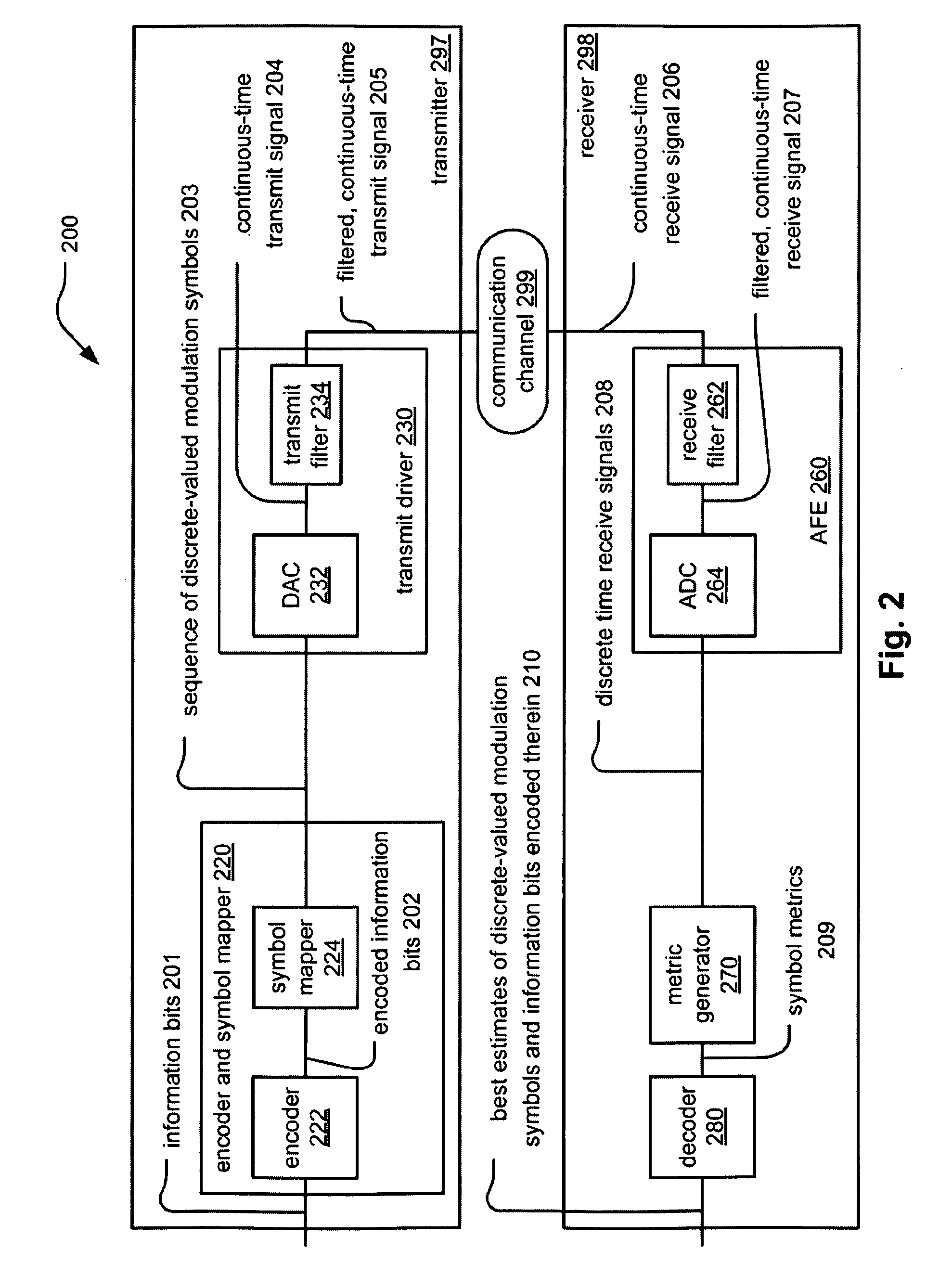

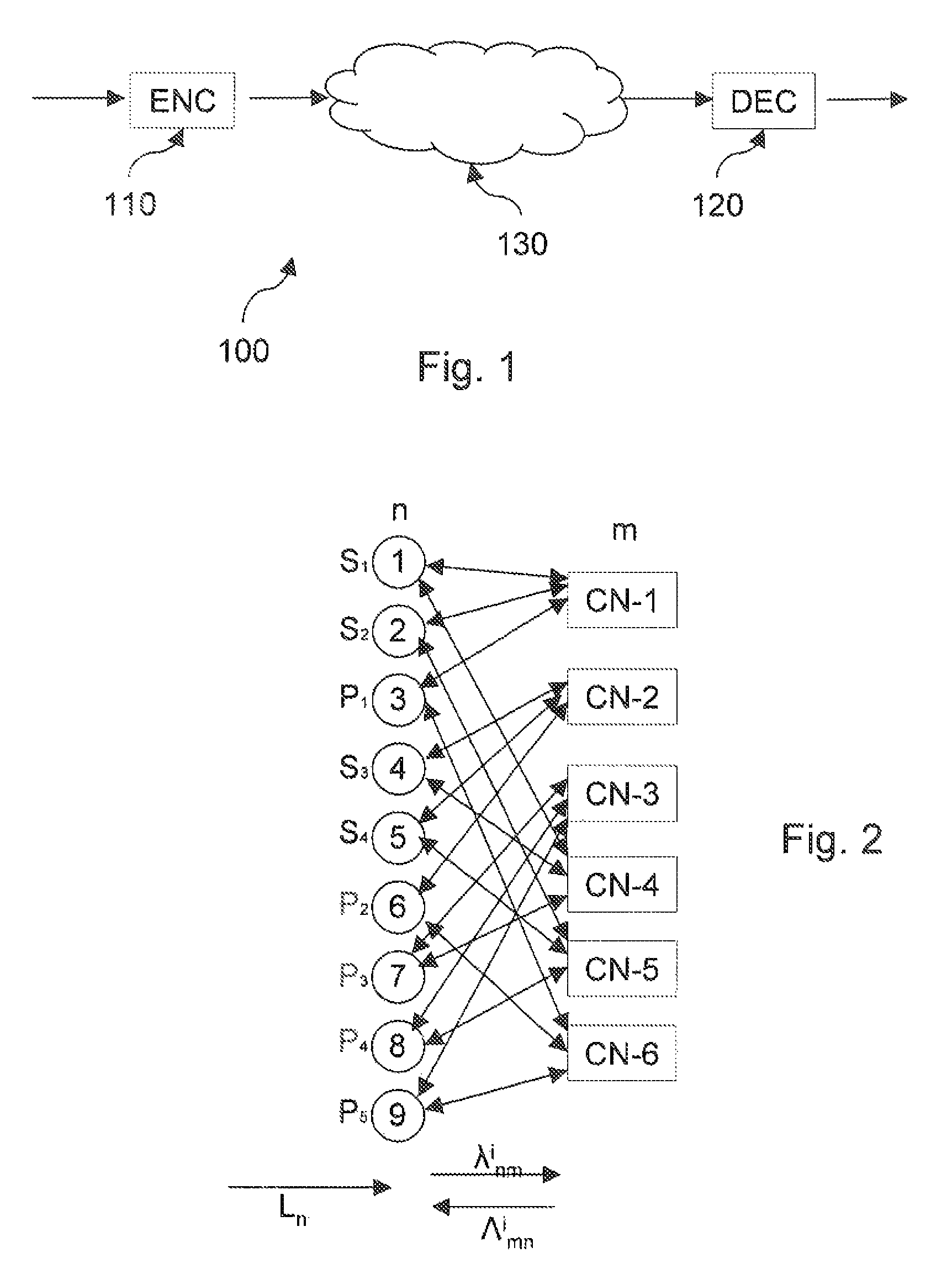

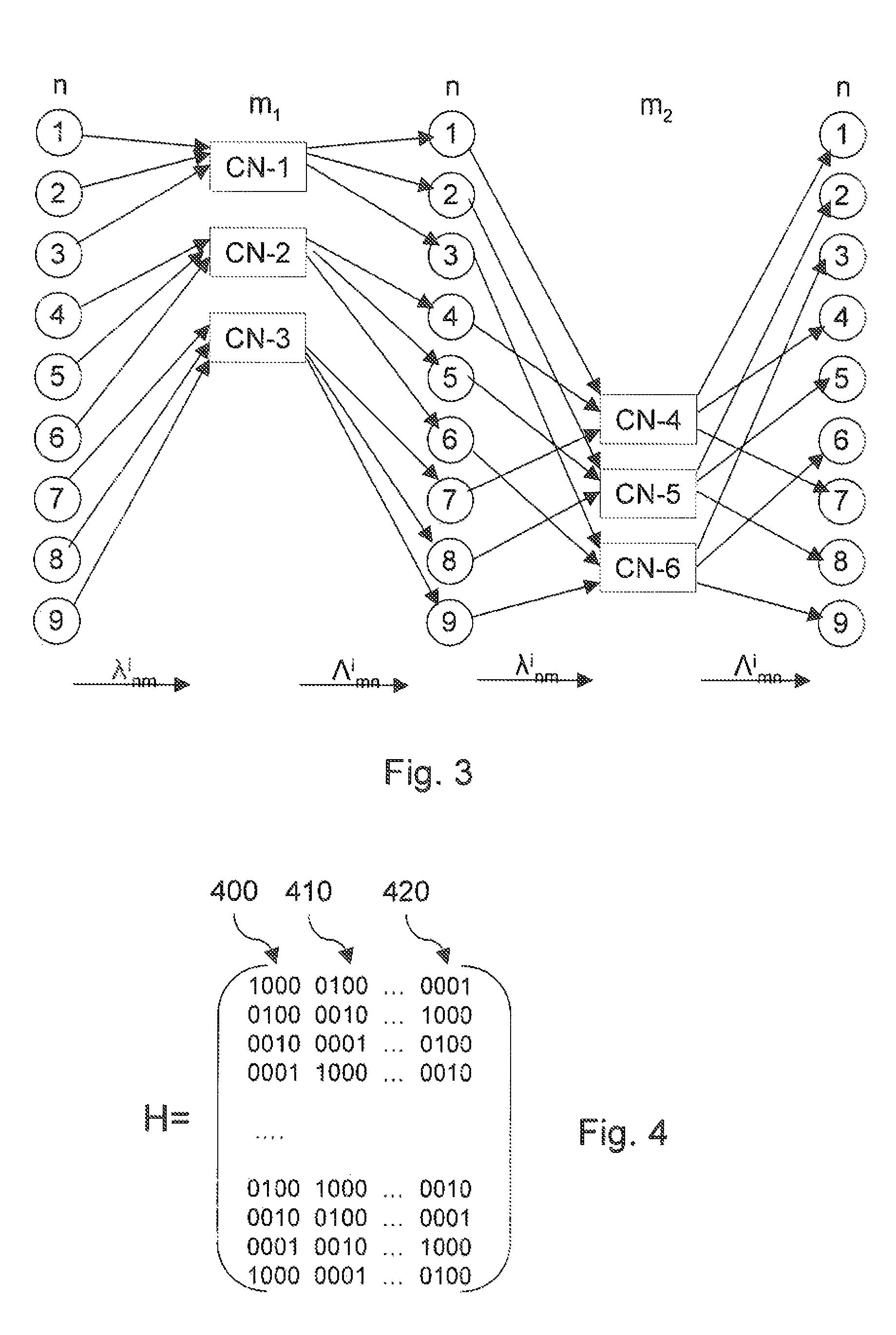

Message passing memory and barrel shifter arrangement in LDPC (Low Density Parity Check) decoder supporting multiple LDPC codes. A novel approach is presented by which a barrel shifter may be implemented in conjunction with a single message passing memory within an LDPC decoder. This arrangement also allows for a single bit / check processor to be employed that is operable to perform updating of edge messages with respect to check nodes as well as updating of edge messages with respect to bit nodes. There are a variety of embodiments by which the barrel shifter and the message passing memory may be implemented. By using this approach, a common architecture and design may operate to decode various types of LDPC coded signals including those whose code rate and / or modulation (including constellation shape and mapping) may vary as frequently as on a frame by frame basis or even on a block by block basis.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Efficient design to implement LDPC (Low Density Parity Check) decoder

ActiveUS20050262424A1Error detection/correctionError correction/detection using LDPC codesIntelligent designCombined use

Efficient design to implement LDPC decoder. The efficient design presented herein provides for a solution that is much easier, smaller, and has less complexity than other possible solutions. The use of a ping-pong memory structure (or pseudo-dual port memory structure) in conjunction with a metric generator near the decoder's front end allows parallel bit / check node processing. An intelligently operating barrel shifter operates with a message passing memory that is operable to store updated edges messages with respect to check nodes as well as updated edges messages with respect to bit nodes. Using an efficient addressing scheme allows the same memory structure to store the two types of edges messages with respect to bit nodes: (1) corresponding to information bits and (2) corresponding to parity bits. In addition, an intelligently designed hardware macro block may be instantiated a number of times into the decoder design to support ever greater design efficiency.

Owner:AVAGO TECH INT SALES PTE LTD

Shuffled LDPC decoding

InactiveUS20100251059A1Low costSimple structureCode conversionError correction/detection using block codesParity-check matrixTheoretical computer science

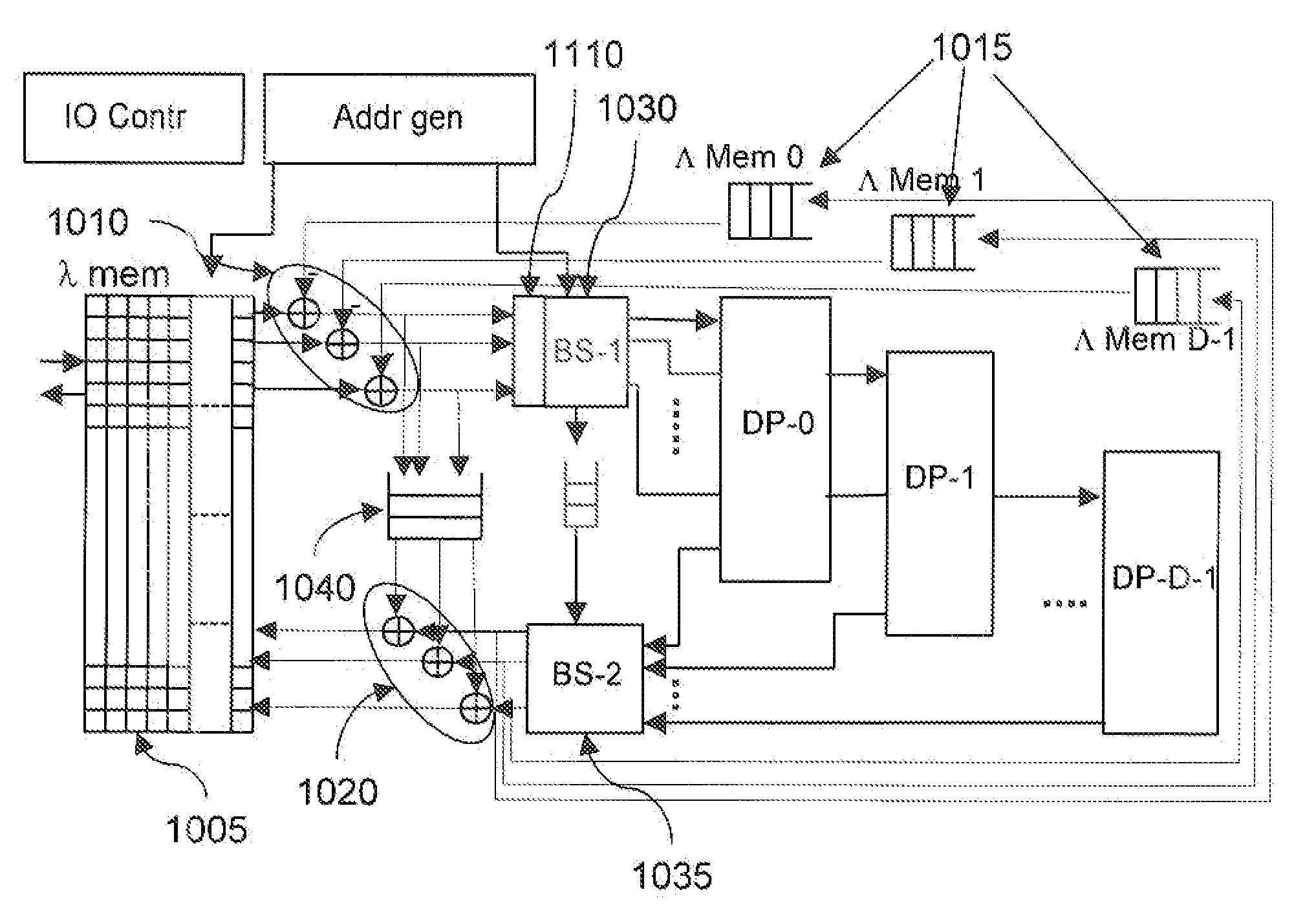

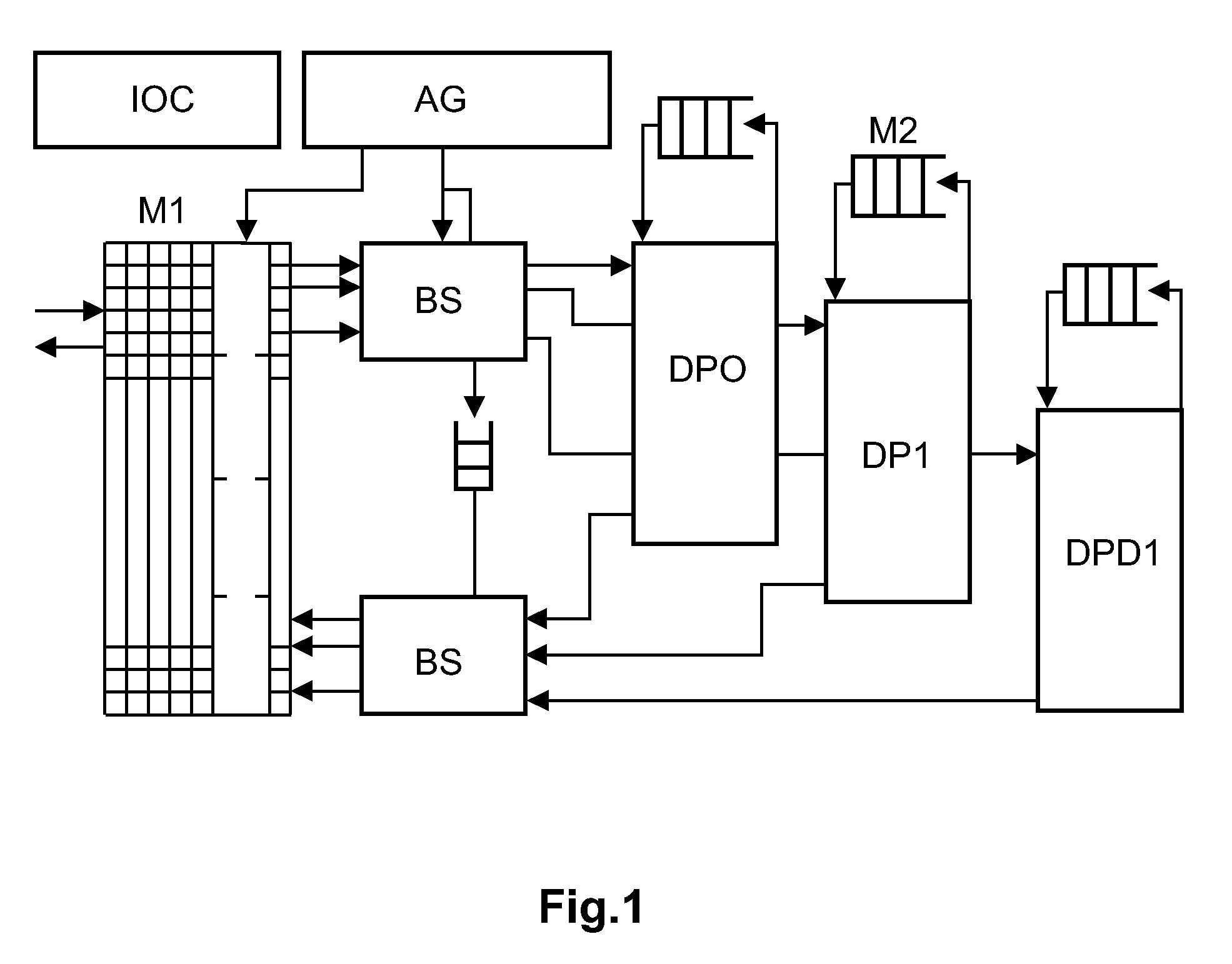

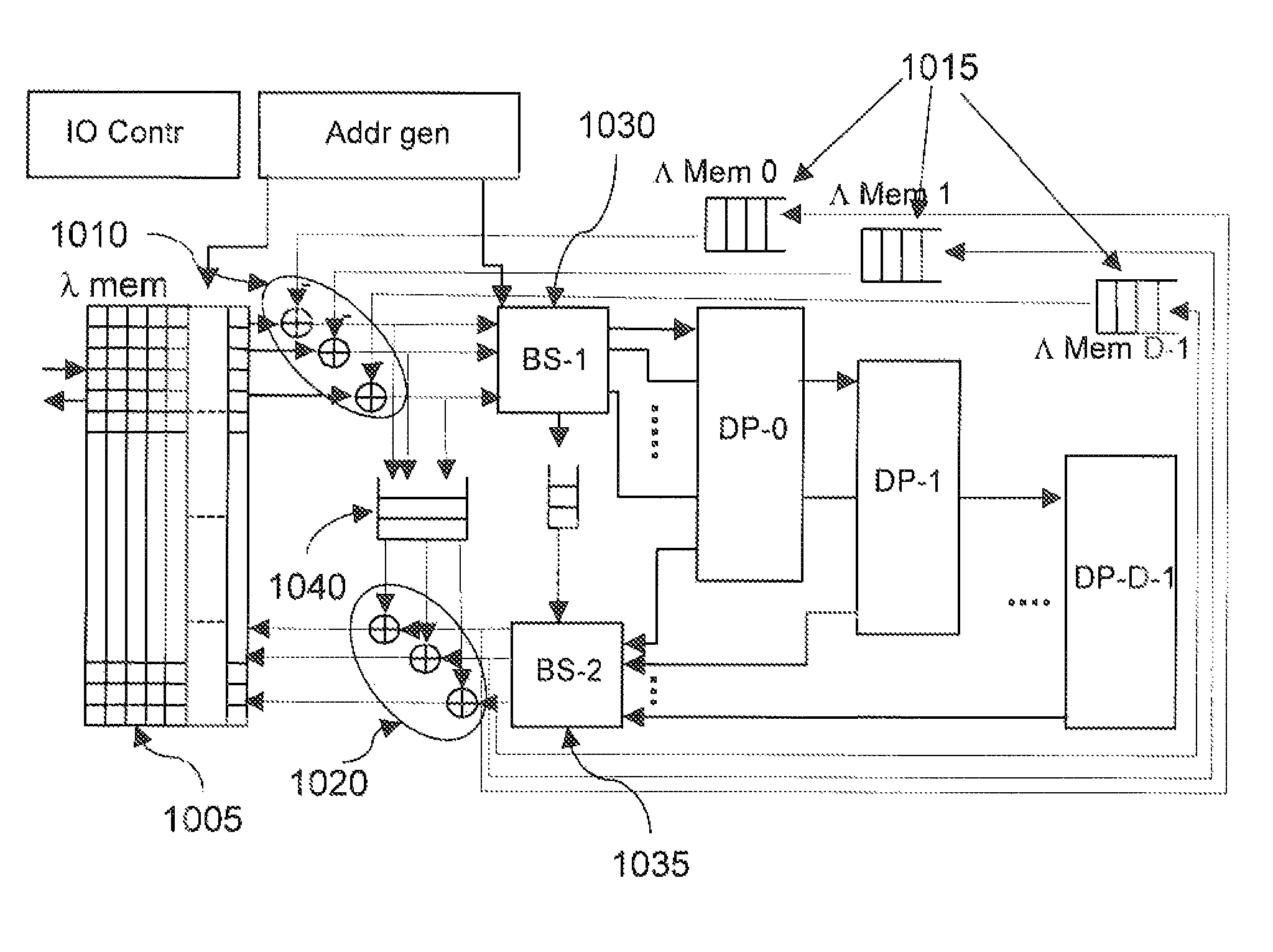

An LDPC decoder iteratively decodes an LDPC code represented by a parity check matrix H consisting of a plurality of circulants based on a Log-Likelihood Ratio Belief-Propagation algorithm. First computation means (1010) compute for a next iteration symbol messages λκm from a representation of a corresponding symbol value stored in a first memory 1005 and from check node messages Λmn from a previous iteration. A shuffler (1030) changes a sequence of the symbol message received from the first computation means (1010) in dependence on a position of the non-zero elements in a corresponding sub-matrix. Second computation N means (DP-O, DP-I, DP-D-I) compute the check node messages in dependence on symbol messages received from the barrel shifter and store a representation of the computed check node message in a second memory (1015). Third computation means (1020) update the representation of the symbol values in the first memory in dependence on output of the first and second computing means. The principle of “staggered” or “shuffled” LDPC decoding is used. One embodiment is designed for multi-diagonal circulants.

Owner:ST ERICSSON SA

Distributed processing LDPC (low density parity check) decoder

ActiveUS20090013237A1Error correction/detection using multiple parity bitsCode conversionCommunication deviceThroughput

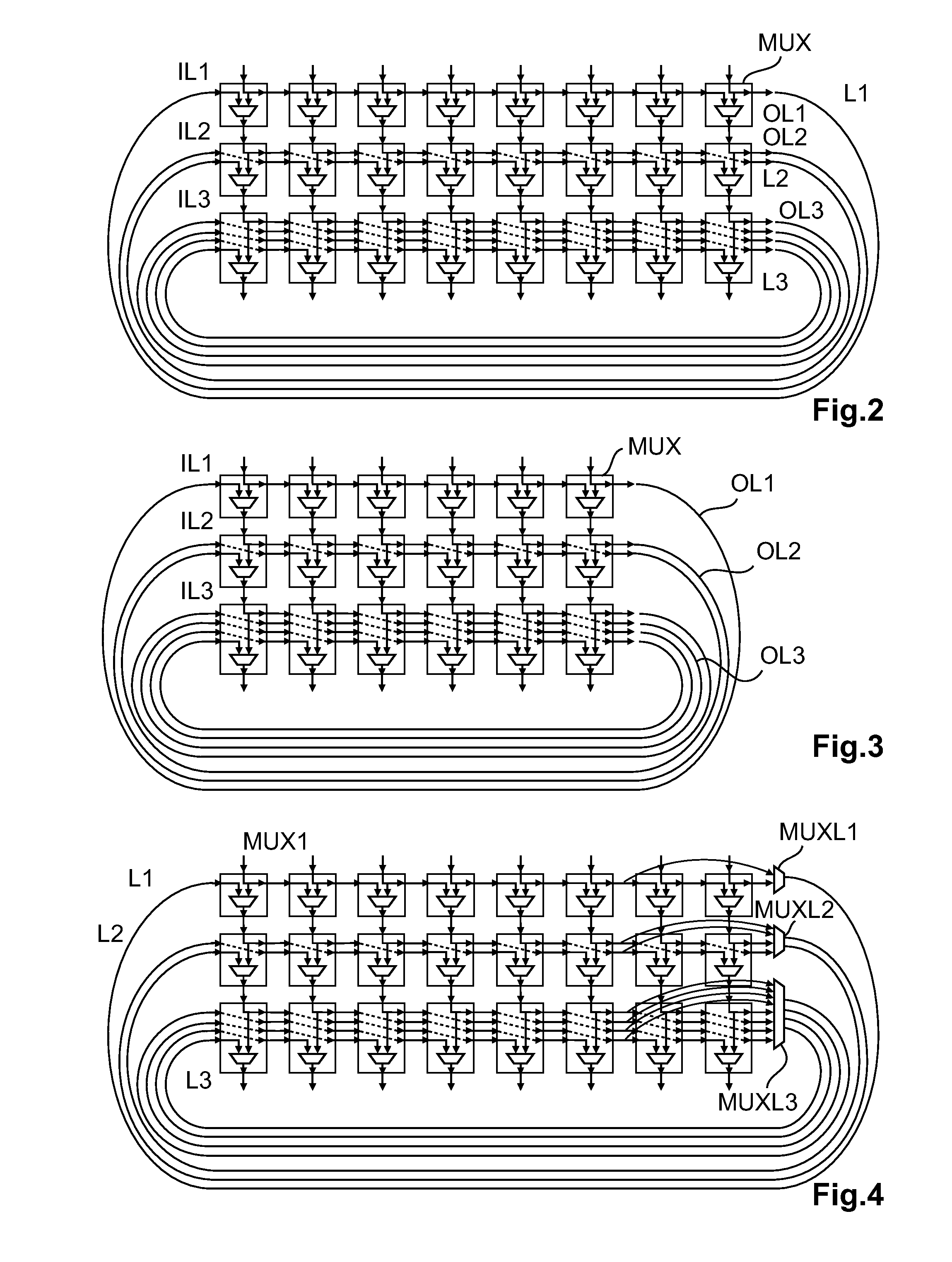

Distributed processing LDPC (Low Density Parity Check) decoder. A means is presented herein that includes an LDPC decoding architecture leveraging a distributed processing technique (e.g., daisy chain) to increase data throughput and reduce memory storage requirements. Routing congestion and critical path latency are also improved thereby. Each daisy chain includes a number of registers, and a number of localized MUXs (e.g., MUXs having merely 2 inputs each). The means presented herein also does not contain any barrel shifters, high fan-in multiplexers, or interconnection networks; therefore, the critical path is relatively short and it can also be pipelined to further increase data throughput. If desired, a communication device can include multiple configurations of such daisy chains to accommodate the decoding of various LDPC coded signals (e.g., such as for an application and / or communication device that must decoded LDPC codes using different low density parity check matrices).

Owner:AVAGO TECH INT SALES PTE LTD

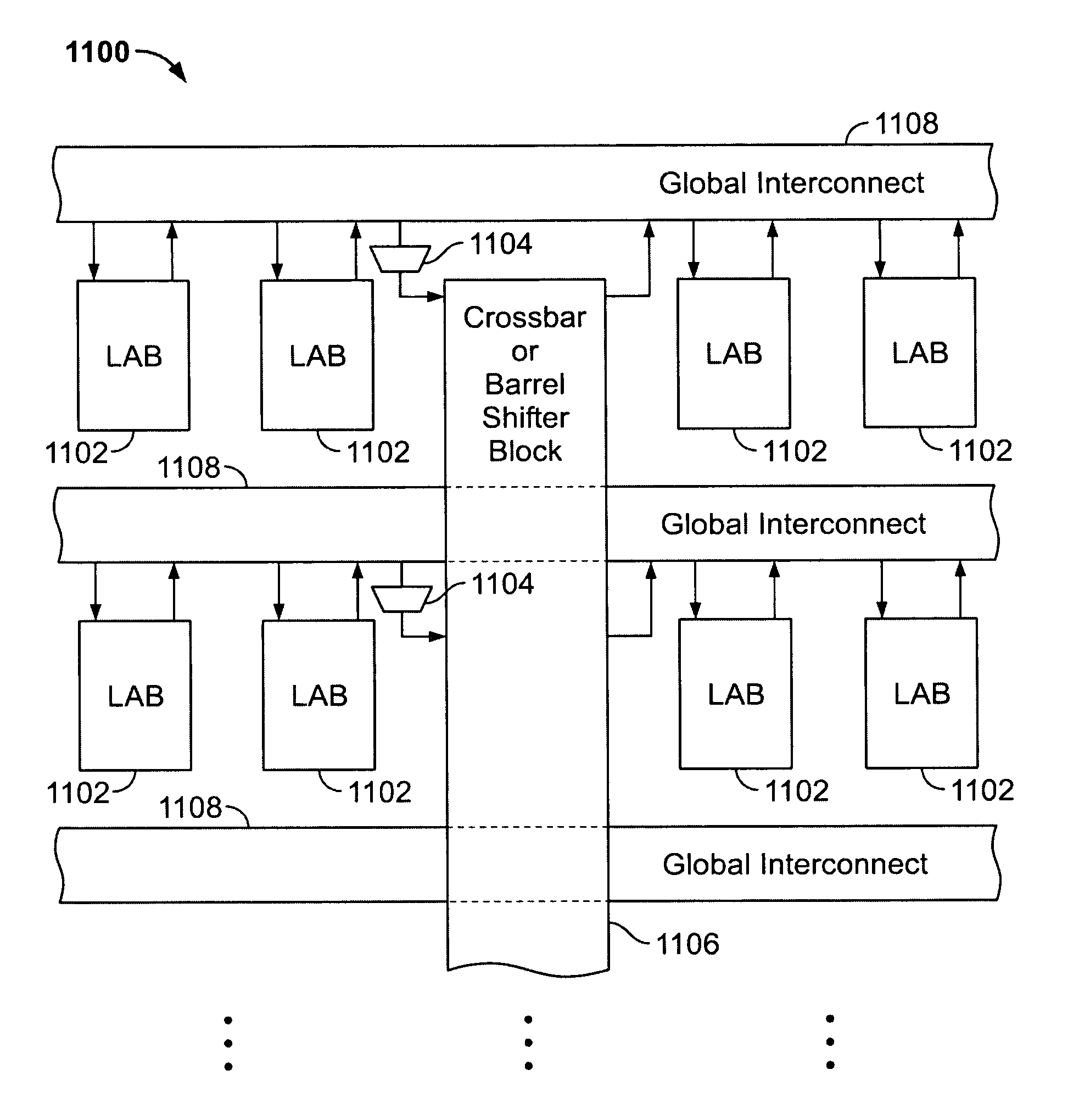

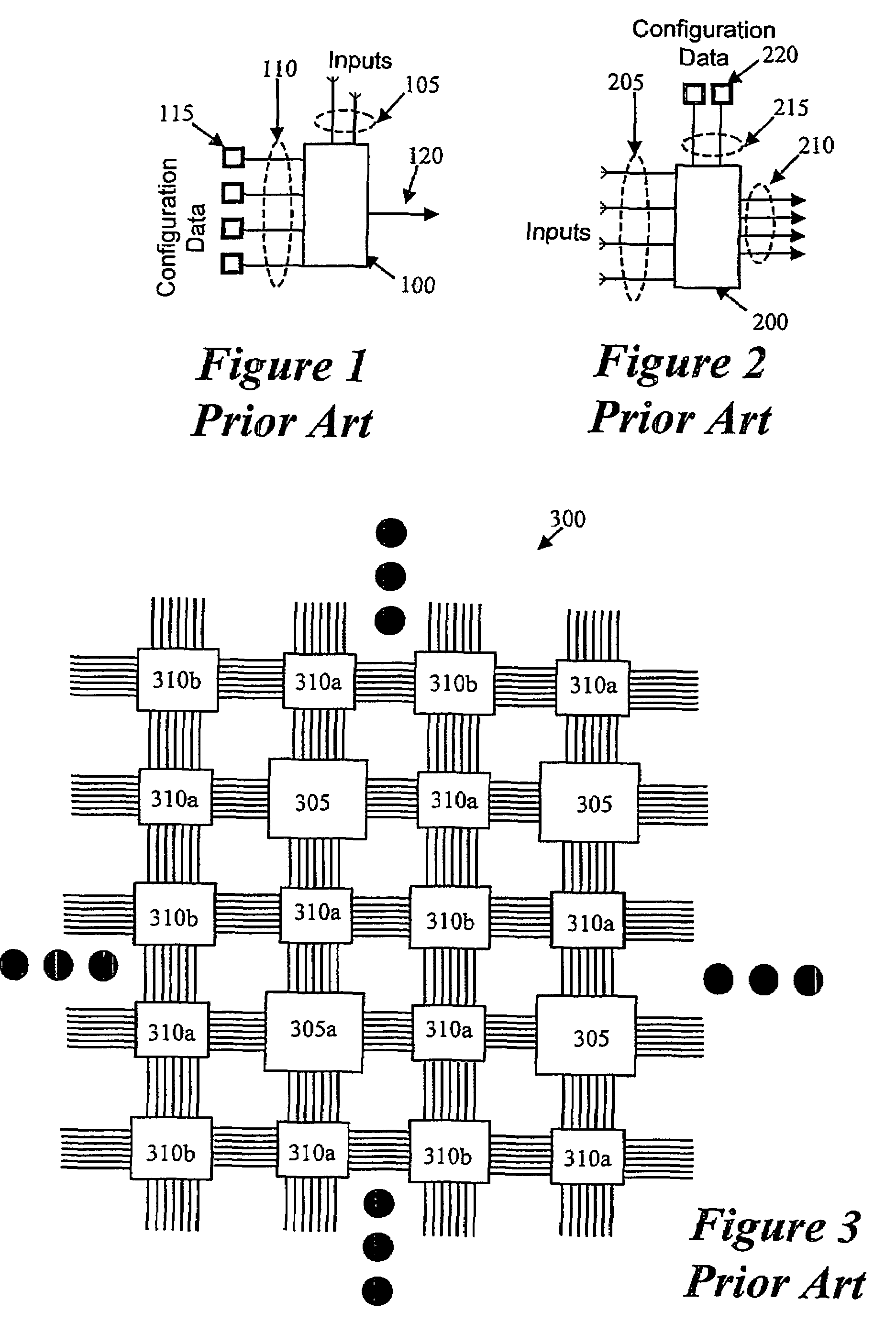

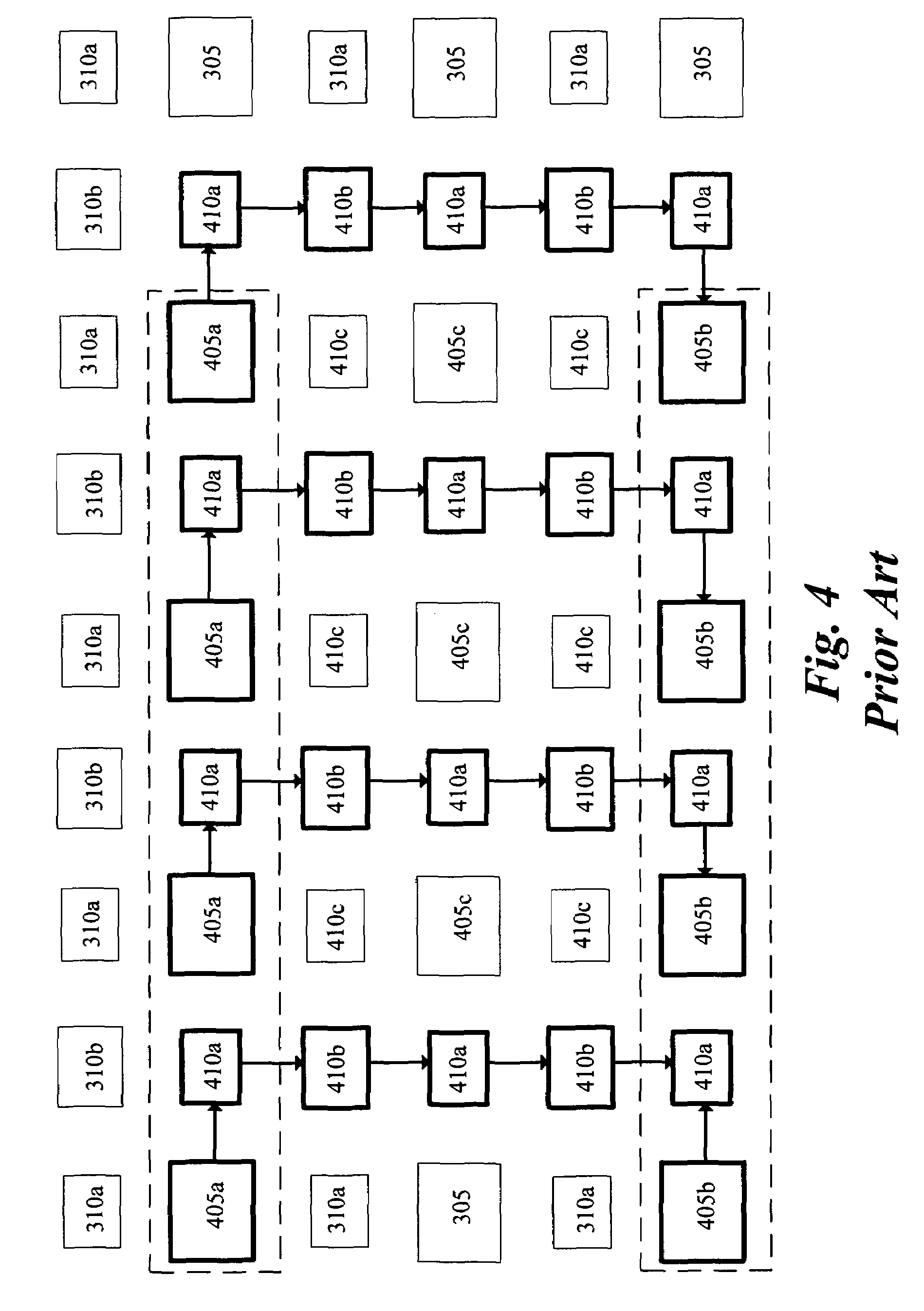

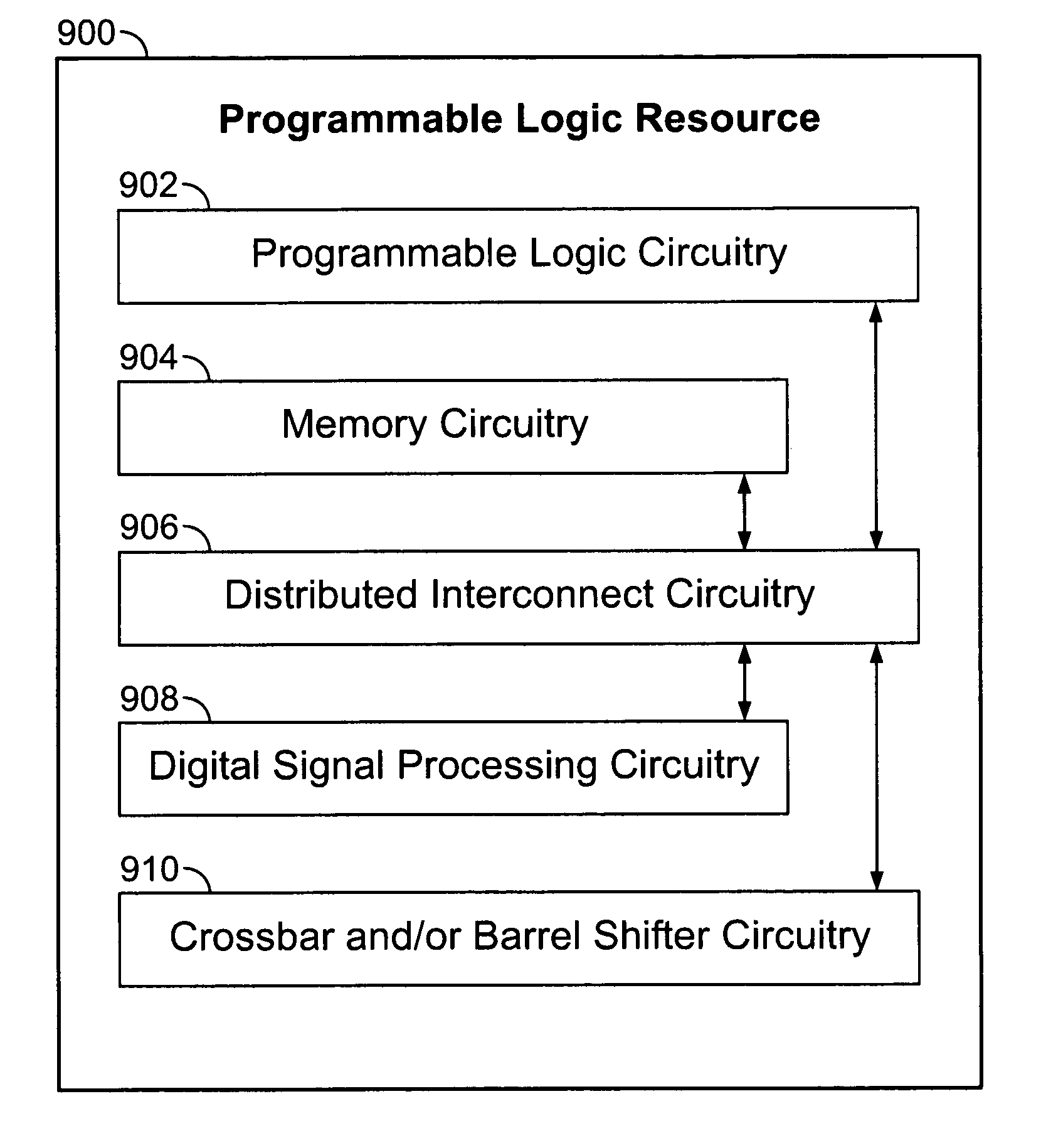

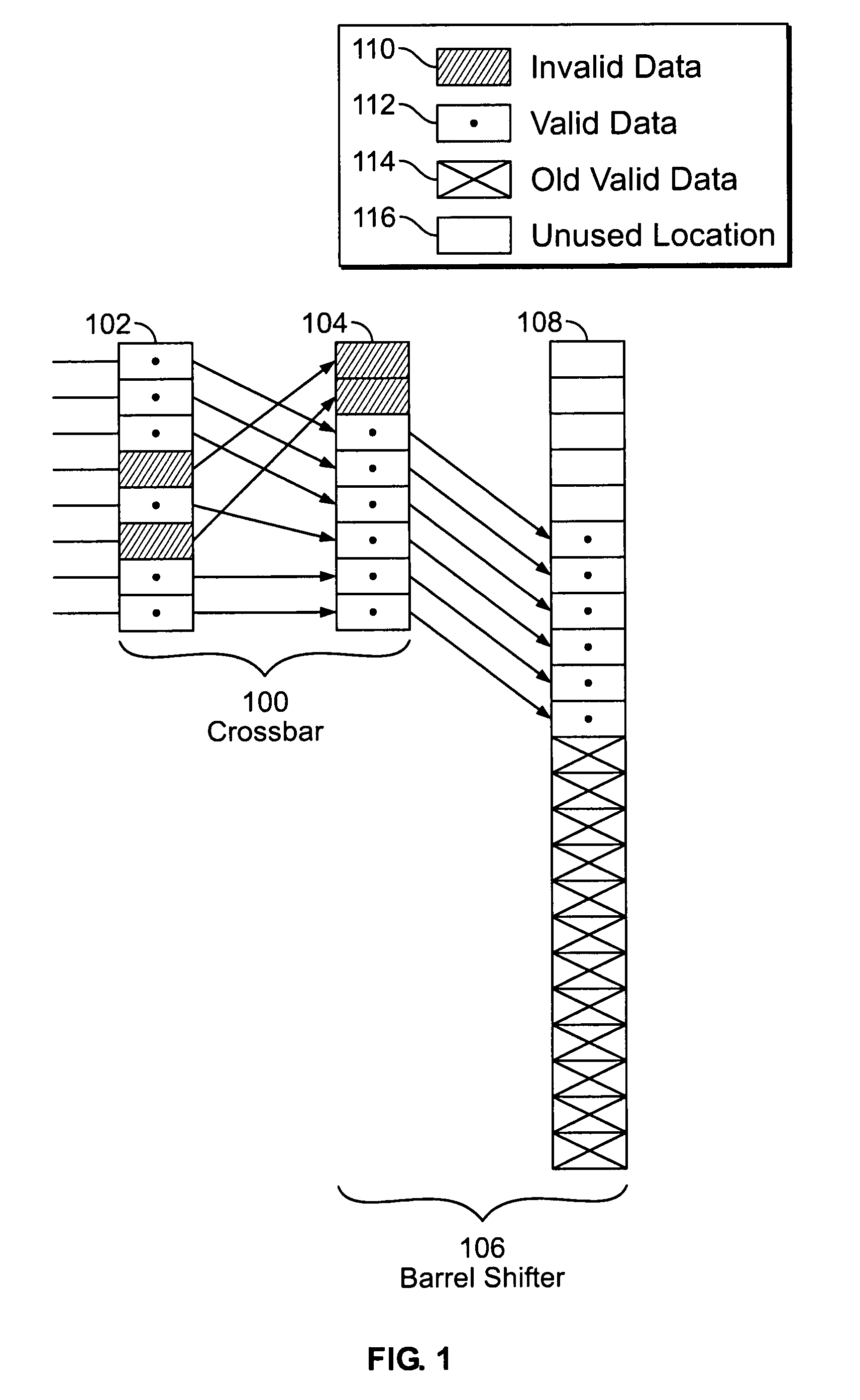

Dedicated crossbar and barrel shifter block on programmable logic resources

InactiveUS7042248B1Reduce in quantityHardware savingSolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceBarrel shifter

A dedicated hardware block is provided for implementing crossbars and / or barrel shifters in programmable logic resources. Crossbar and / or barrel shifter circuitry may replace one or more rows, one or more columns, one or more rectangles, or any combination thereof of programmable logic regions on a programmable logic resource. The functionality of the crossbar and / or barrel shifter circuitry can further be improved by implementing time-multiplexing.

Owner:ALTERA CORP

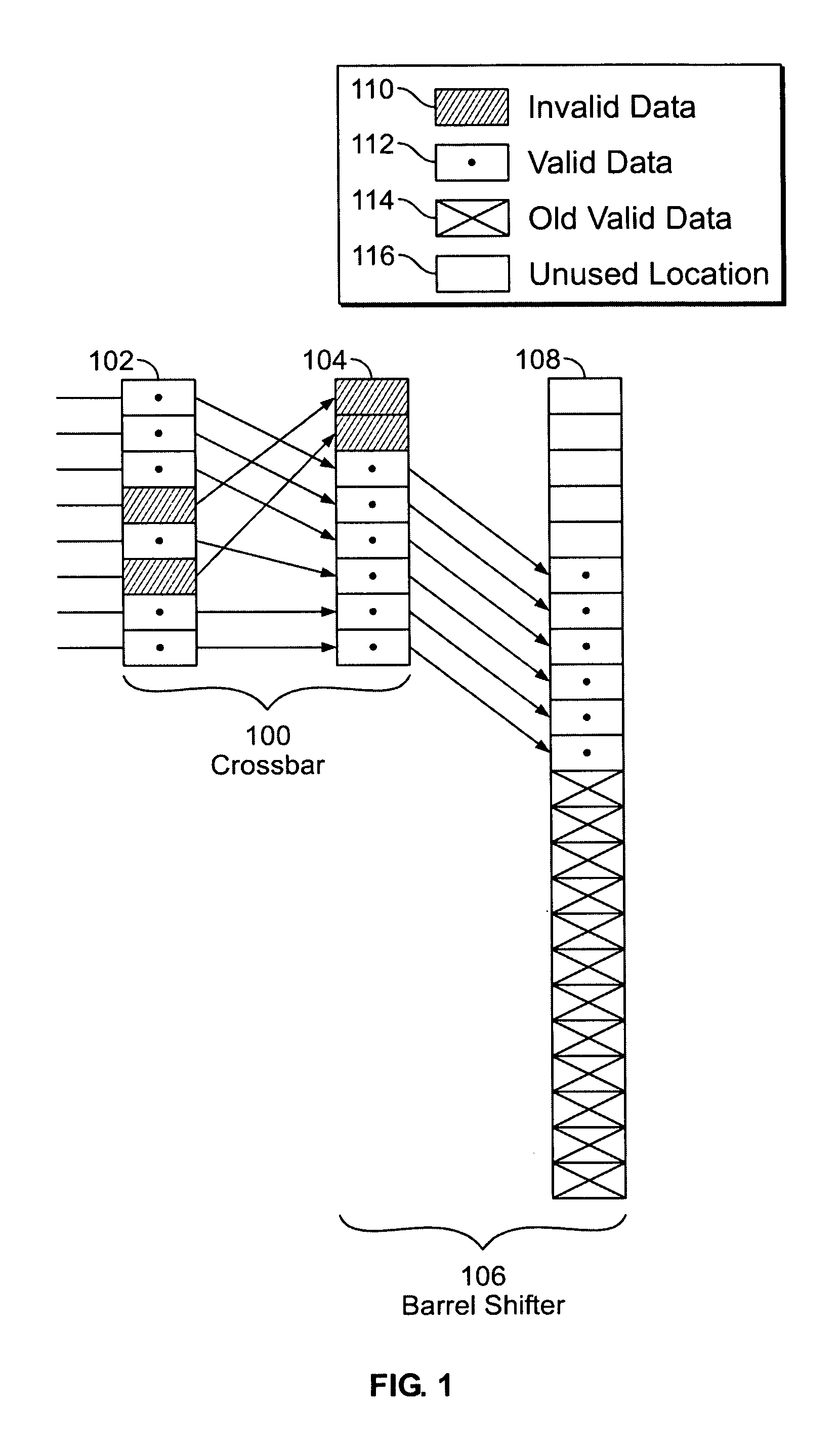

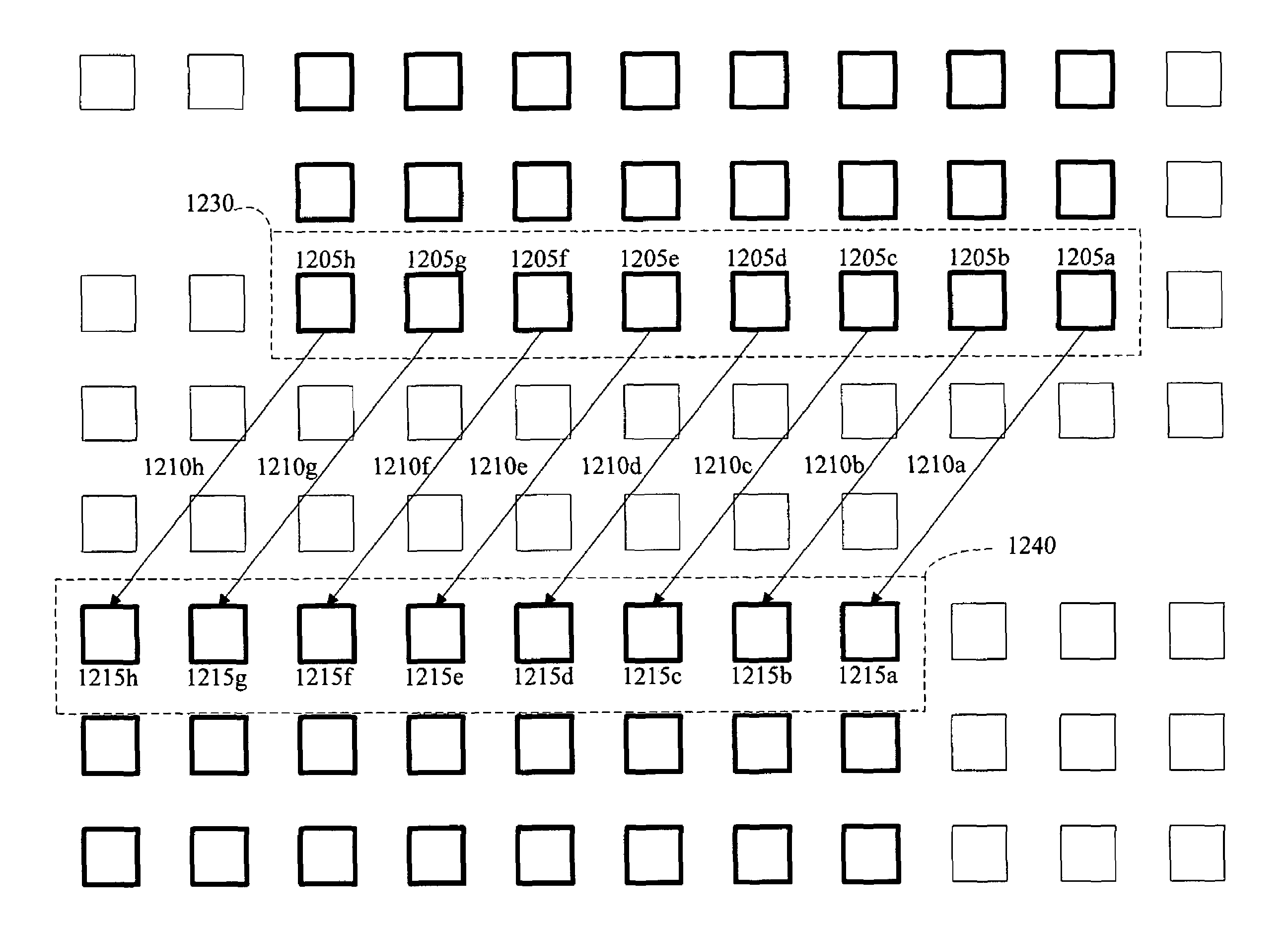

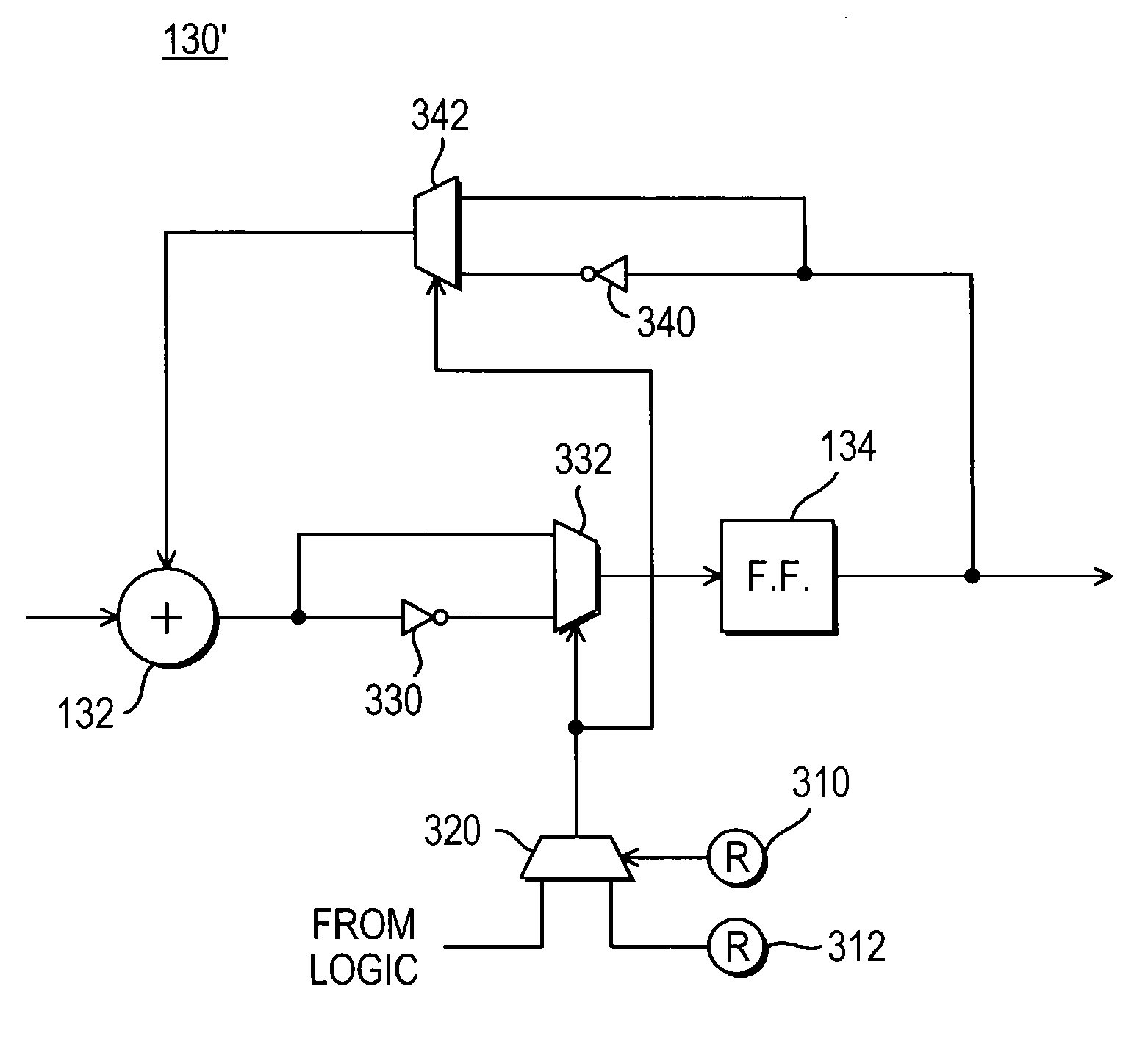

Barrel shifter implemented on a configurable integrated circuit

InactiveUS7518400B1Excessive levelSolid-state devicesLogic circuits using elementary logic circuit componentsEngineeringBarrel shifter

Some embodiments provide a barrel shifter on a configurable integrated circuit (IC). The barrel shifter has a first set of tiles and a second set of tiles with configurable circuits. The barrel shifter also has a first set of non-neighboring offset connections (NNOCs) connecting at least one of the tiles in the first set to at least one of the tiles in the second set.

Owner:ALTERA CORP

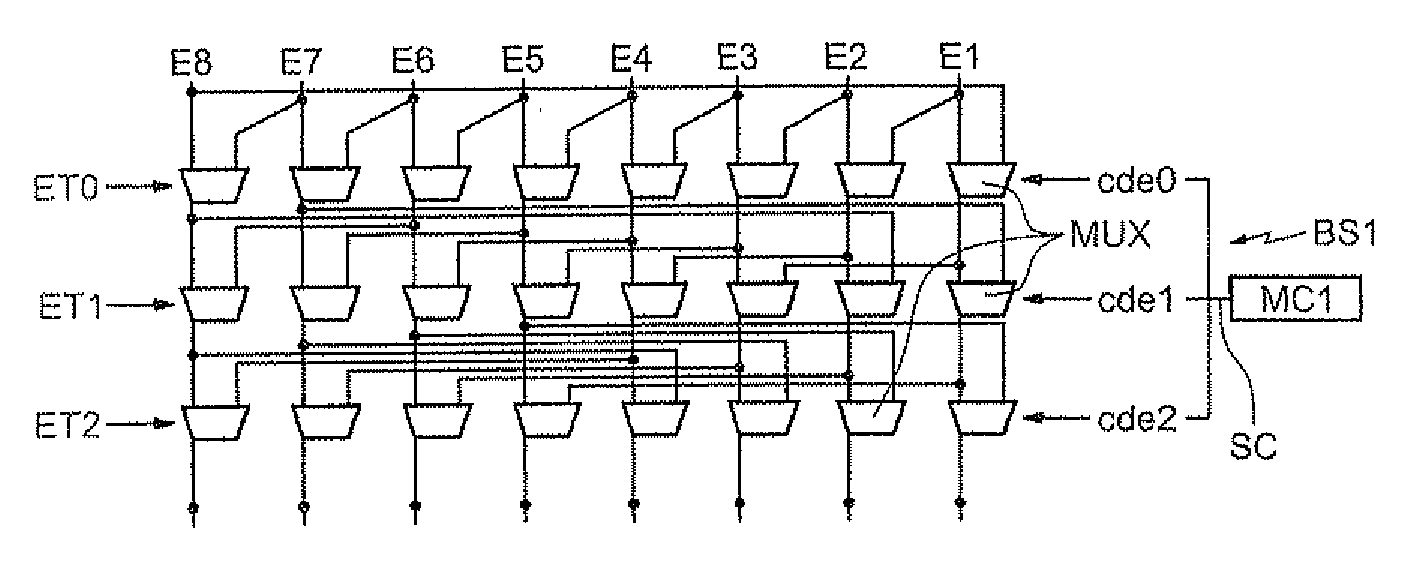

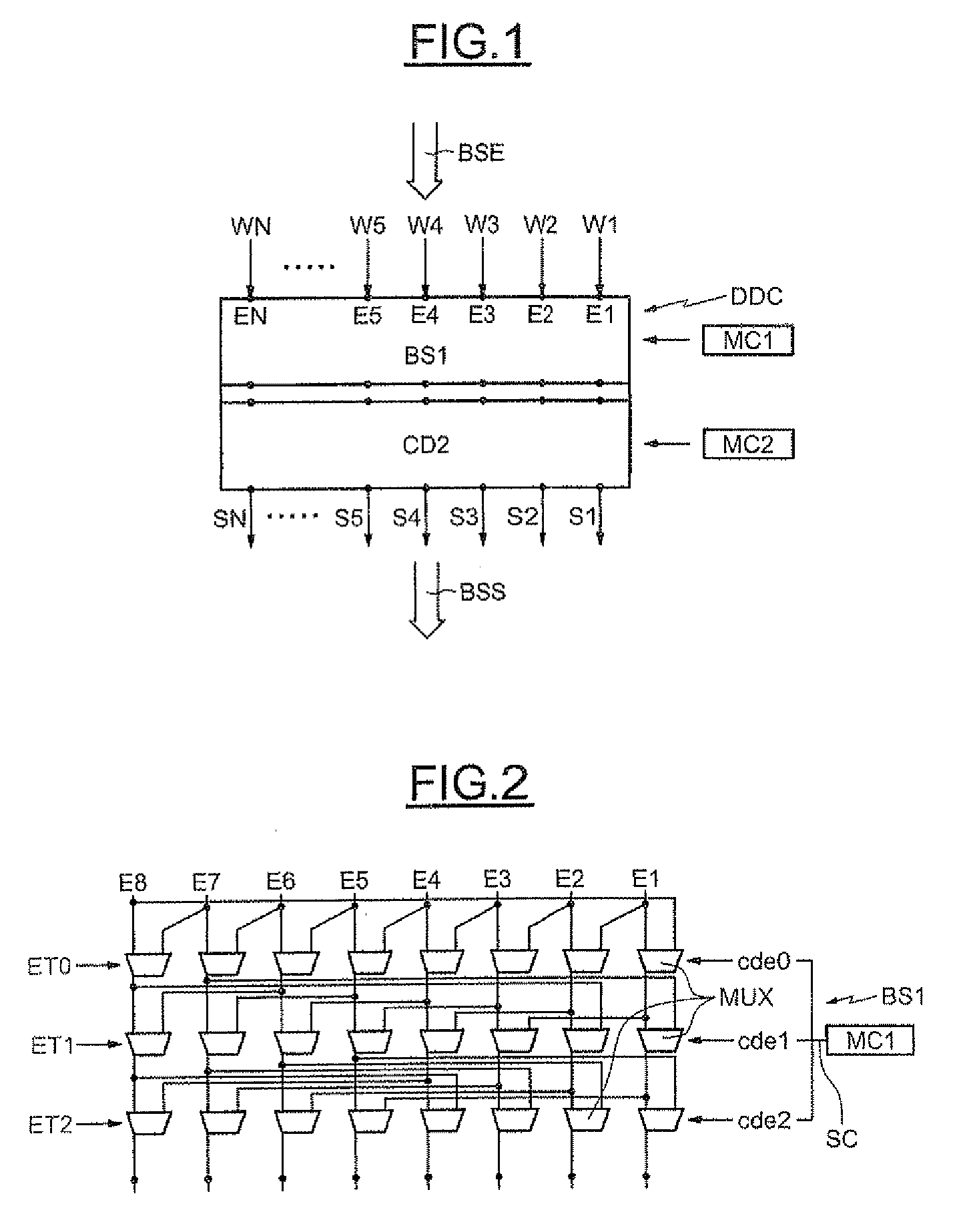

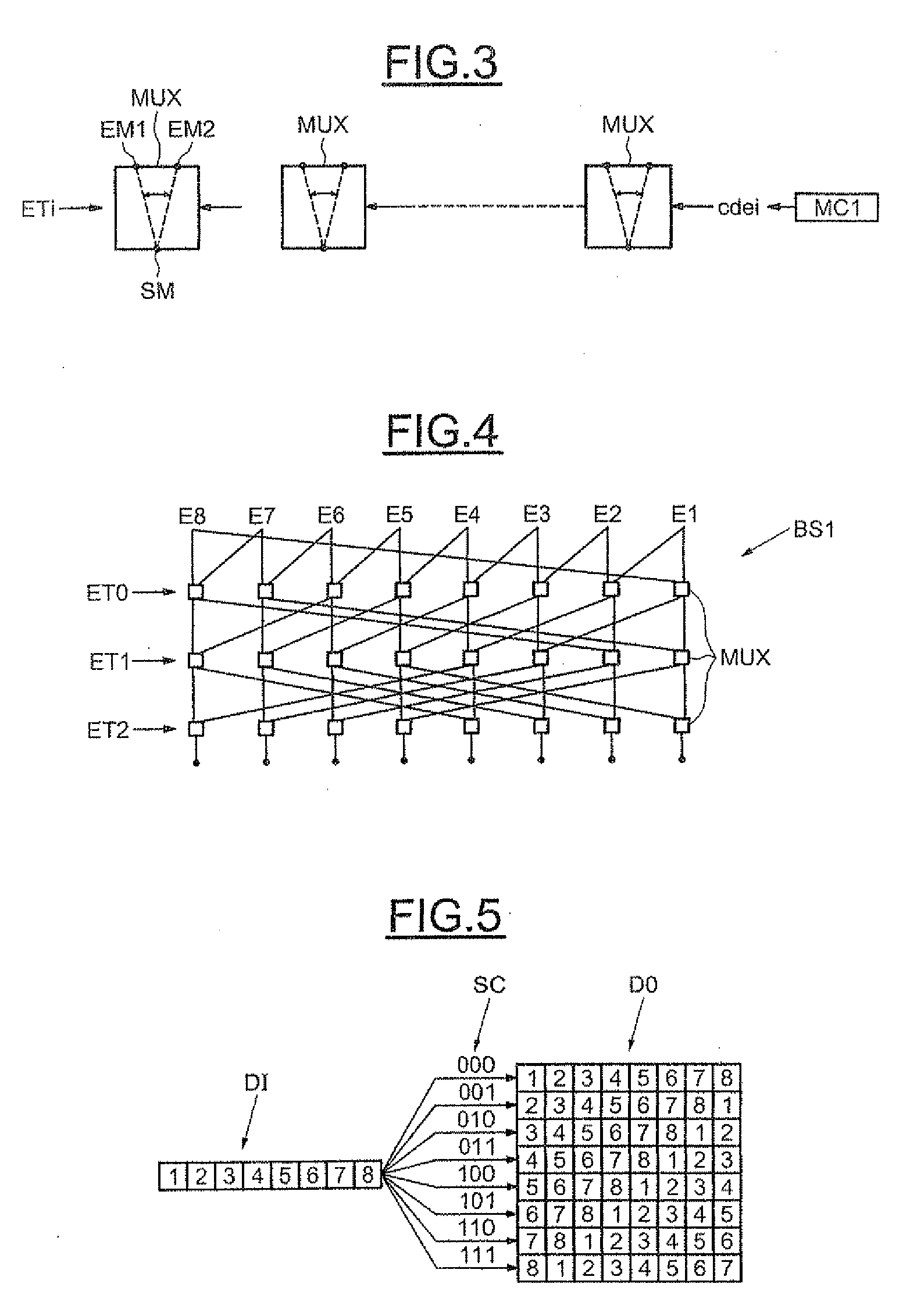

Electronic device, barrel shifter unit and method of barrel shifting

InactiveUS8270558B2Reduce complexityDigital data processing detailsDigital computer detailsMultiplexerEngineering

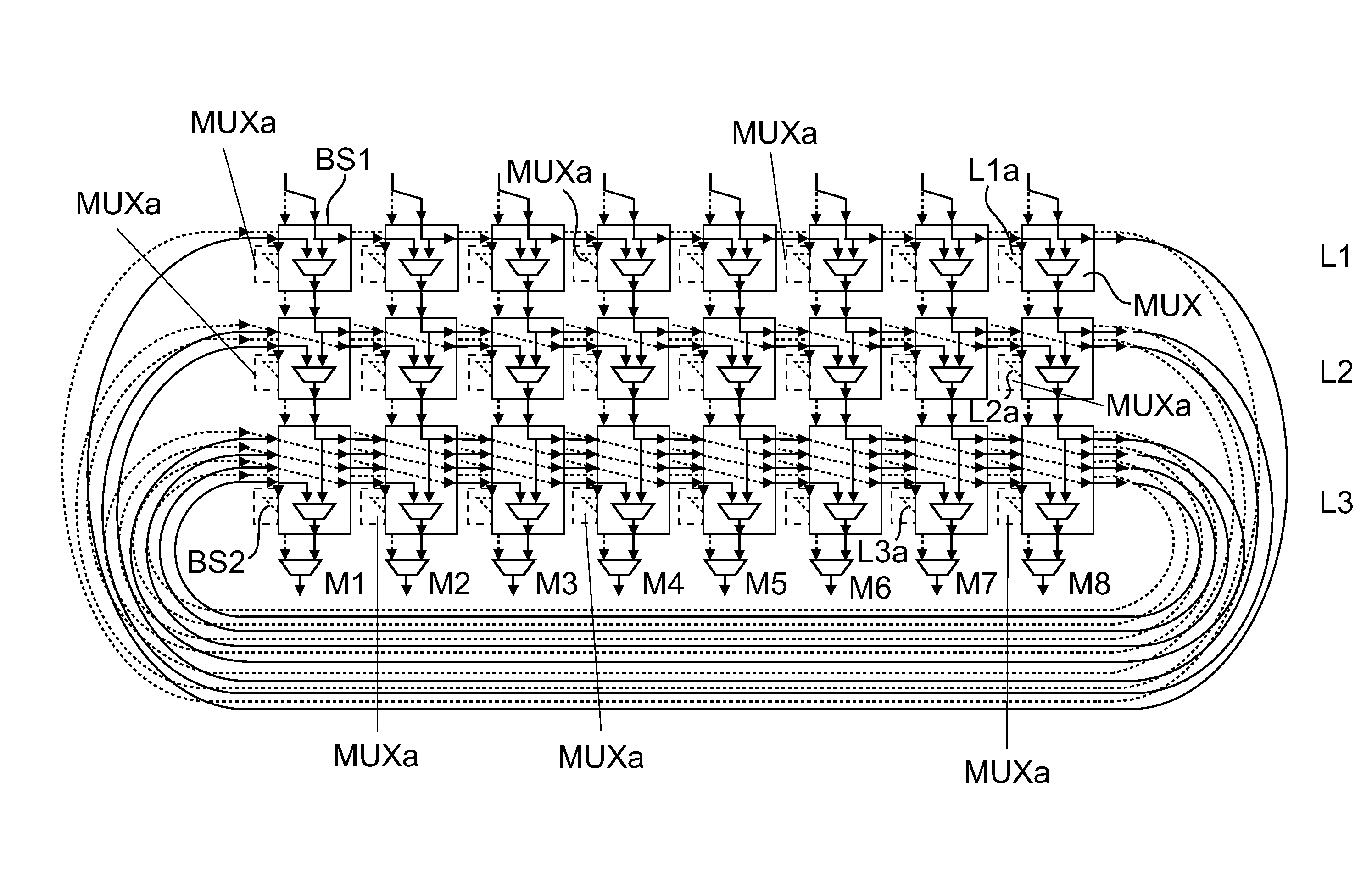

An electronic device is provided which comprises a barrel shifter unit (BS) for performing a rotation of an input. The barrel shifter unit comprises a first and second barrel shifter (BS1, BS2). The electronic device furthermore comprises a selection unit for selecting a first set of elements (a) for the second barrel shifter (BS2) and a second set of elements for the first barrel shifter (BS1). The electronic device furthermore comprises a plurality of second multiplexers (M1 M8) for receiving the input of the second barrel shifter as first input and the output of the first barrel shifter as second input.

Owner:ST ERICSSON SA

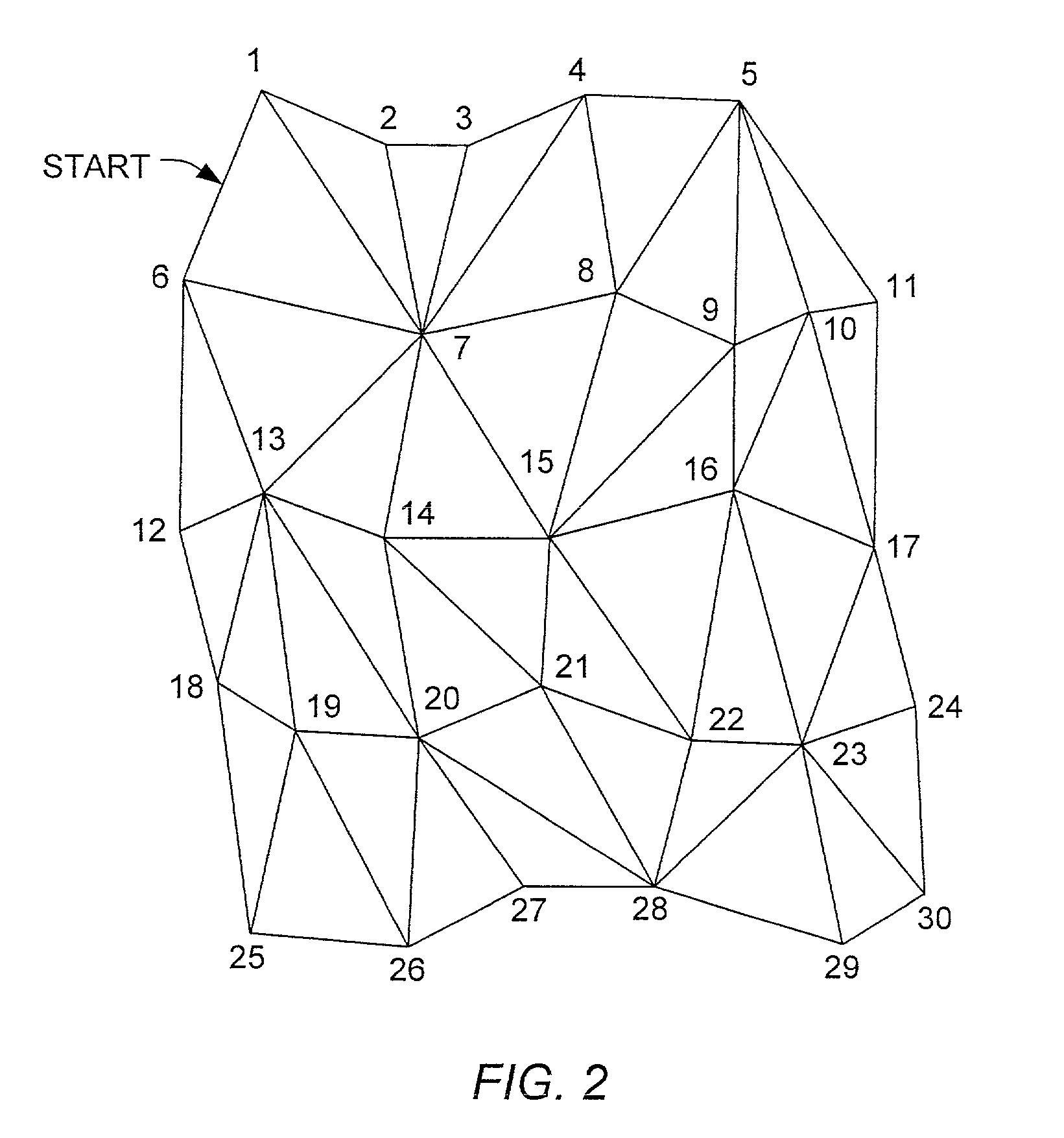

Decompression of variable-length encoded compressed three-dimensional graphics data

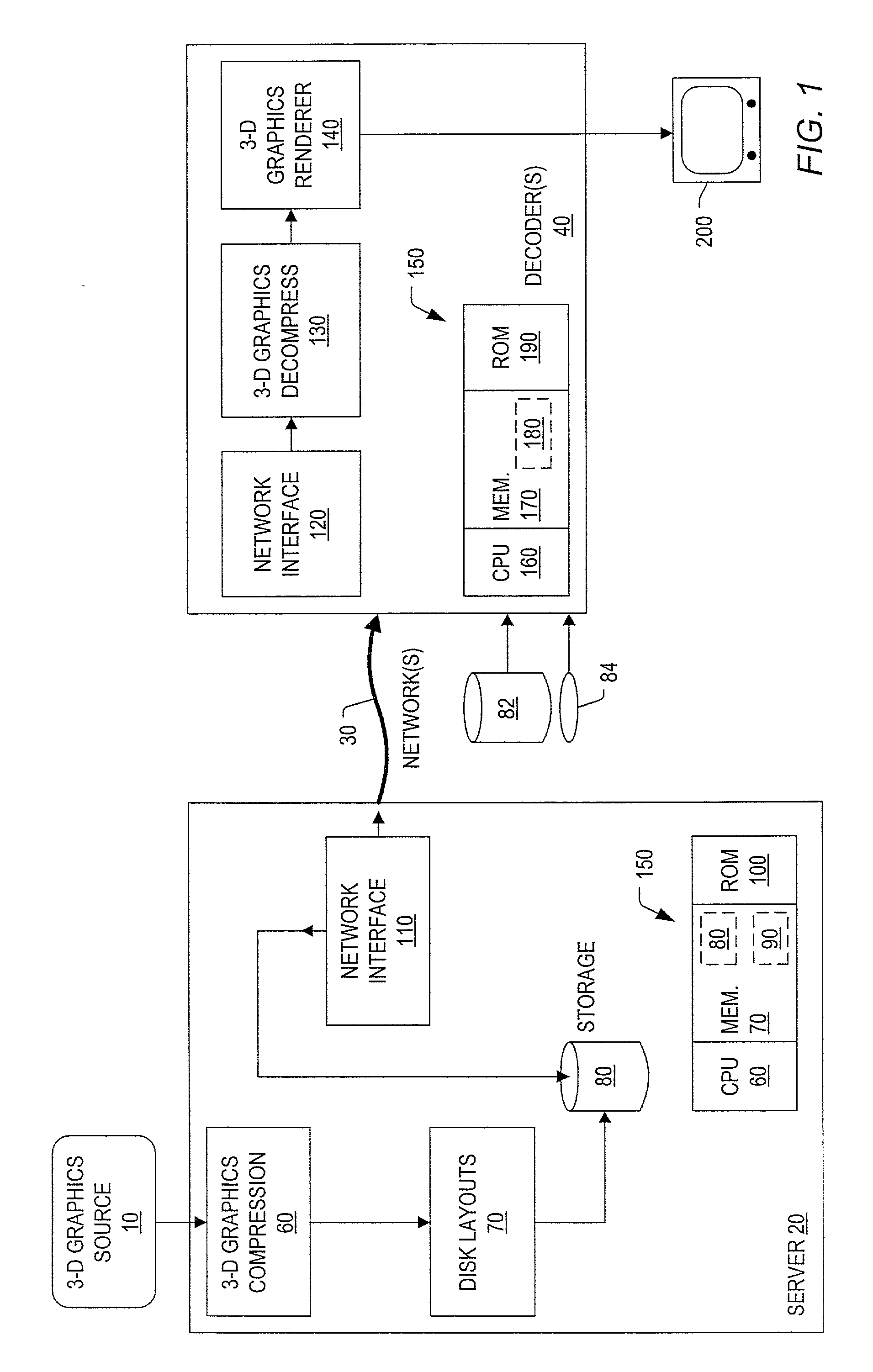

Three-dimensional compressed geometry is decompressed with a unit having an input FIFO receiving compressed data bits and outputting to an input block state machine and an input block, whose outputs are coupled to a barrel shifter unit. Input block output also is input to Huffman tables that output to the state machine. The state machine output also is coupled to a data path controller whose output is coupled to a tag decoder, and to a normal processor receiving output from the barrel shifter unit. The decompressor unit also includes a position / color processor that receives output from the barrel shifter unit. Outputs from the normal processor and position / color processor are multiplexed to a format converter. For instructions in the data stream that generate output to the format converter, the decompression unit generates a tag sent to the tag decoder in parallel with bits for normals that are sent to the format converter. The decompressed stream of triangle data may then be passed to a traditional rendering pipeline, where it can be processed in full floating point accuracy, and thereafter displayed or otherwise used.

Owner:SUN MICROSYSTEMS INC

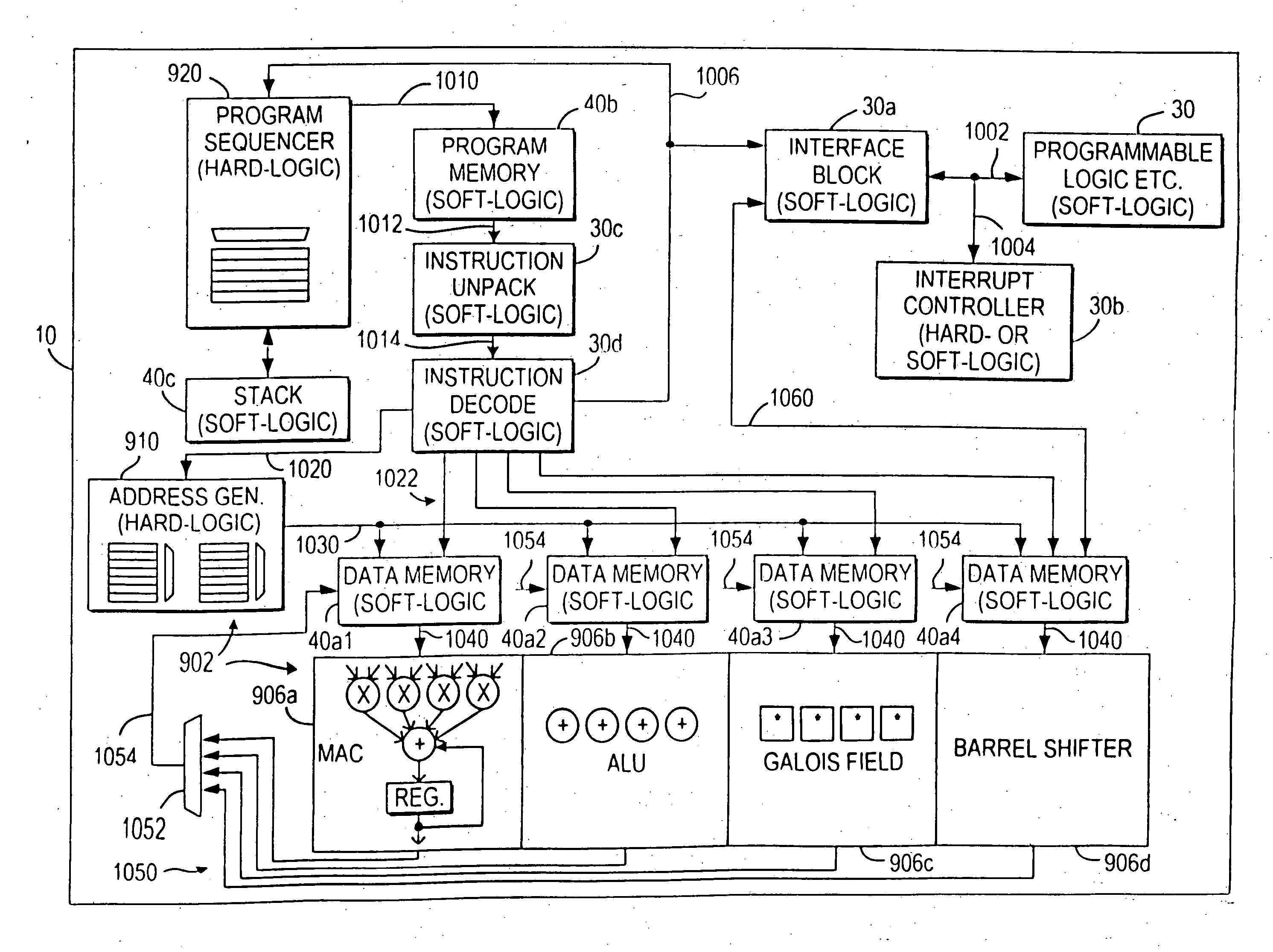

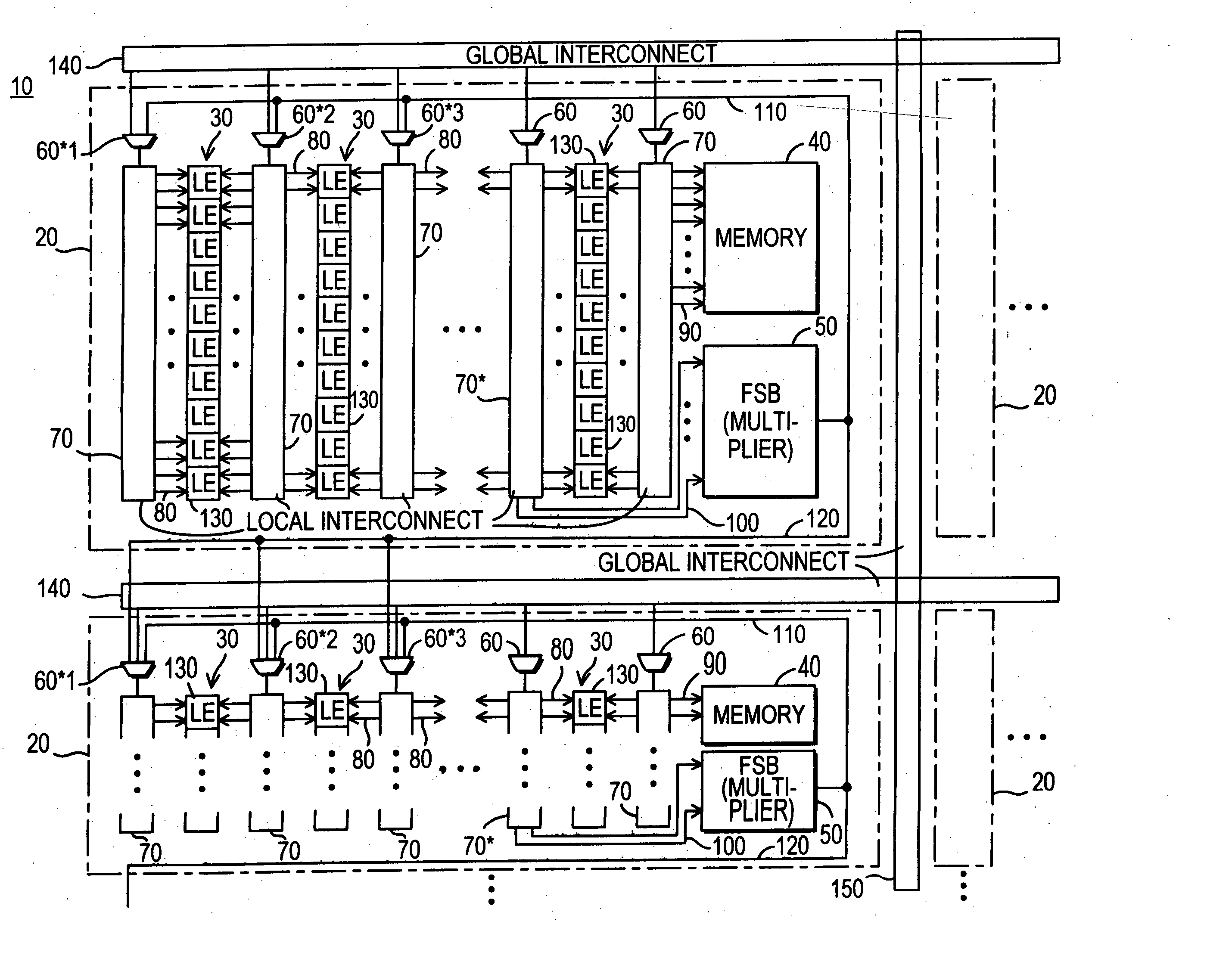

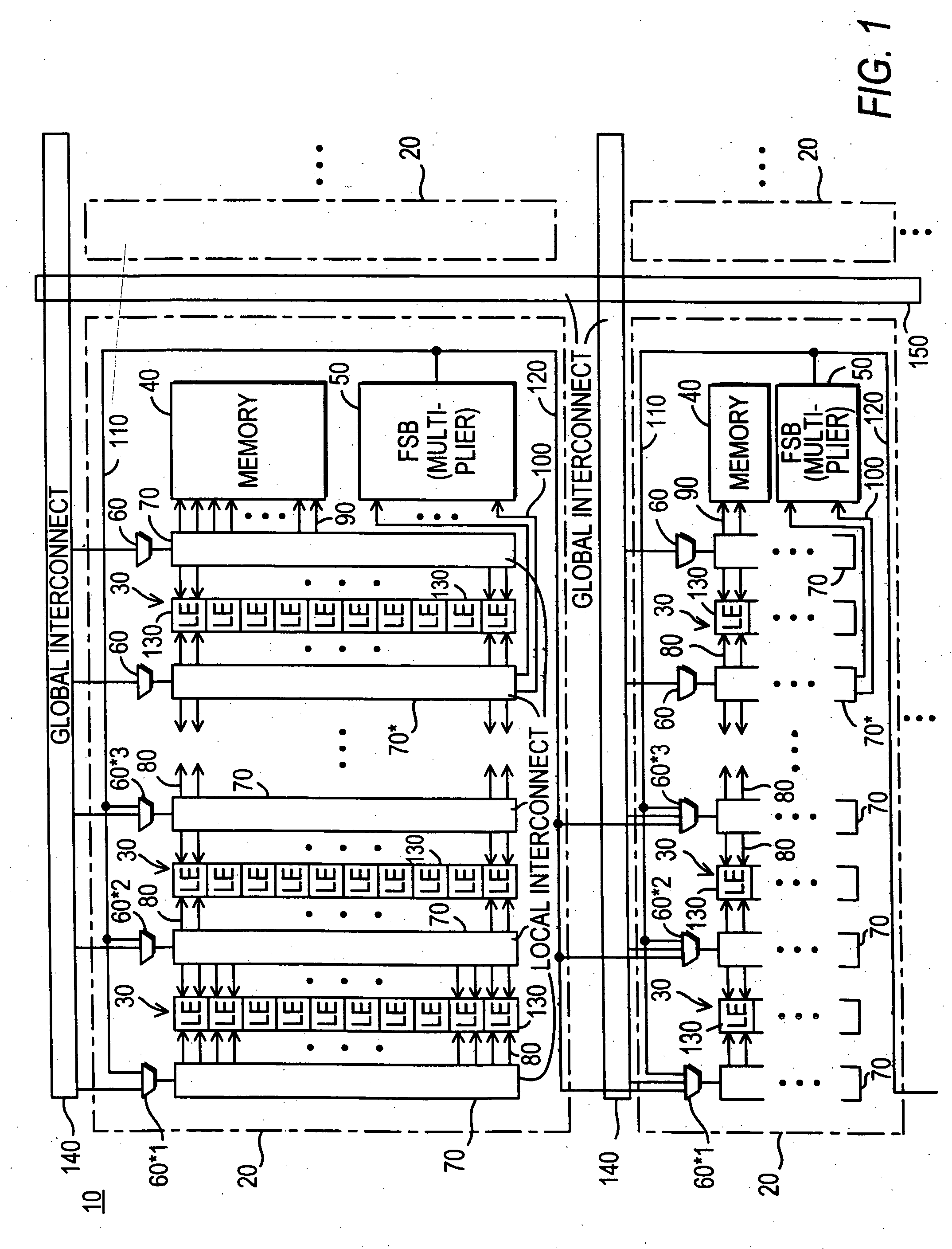

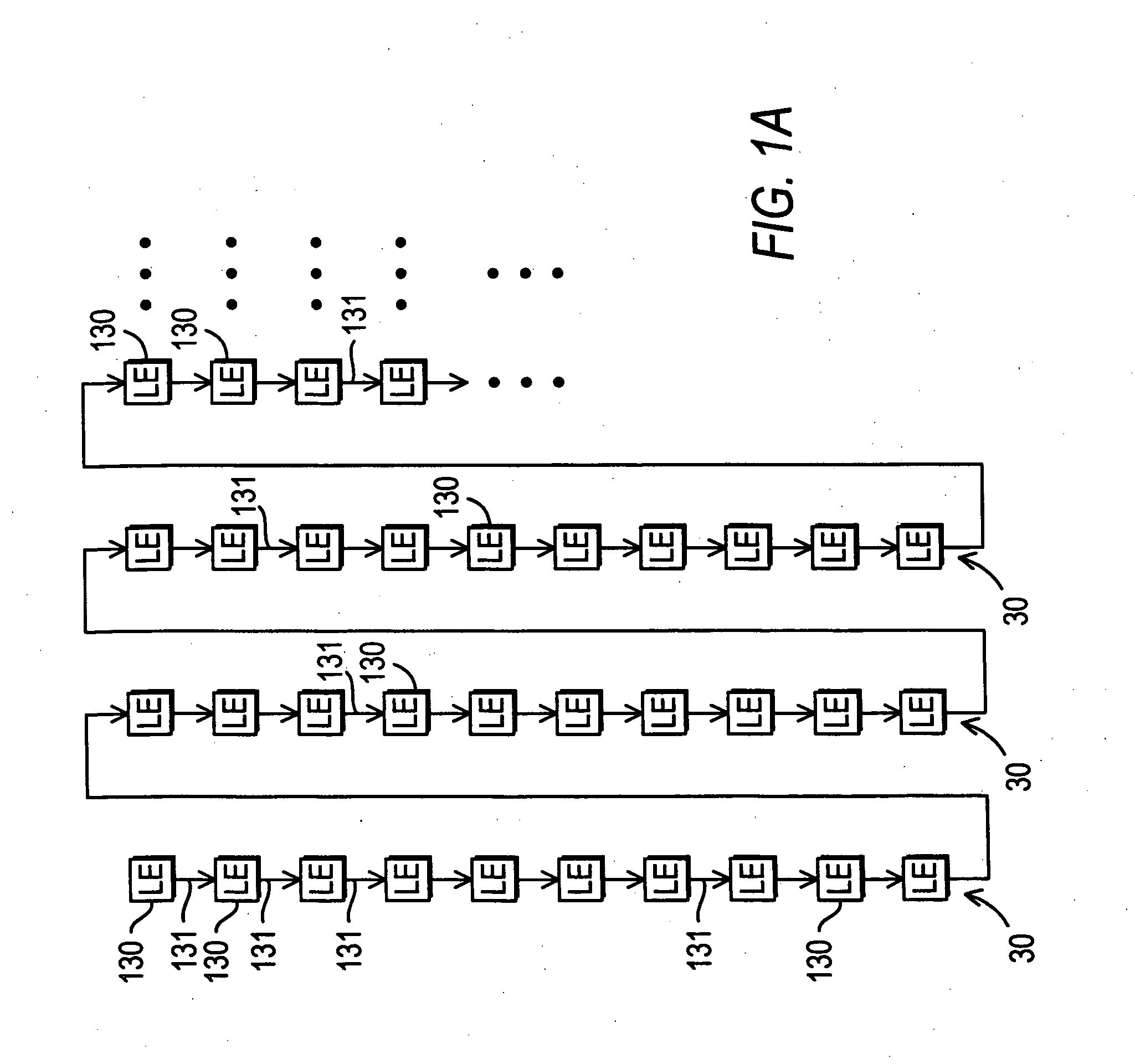

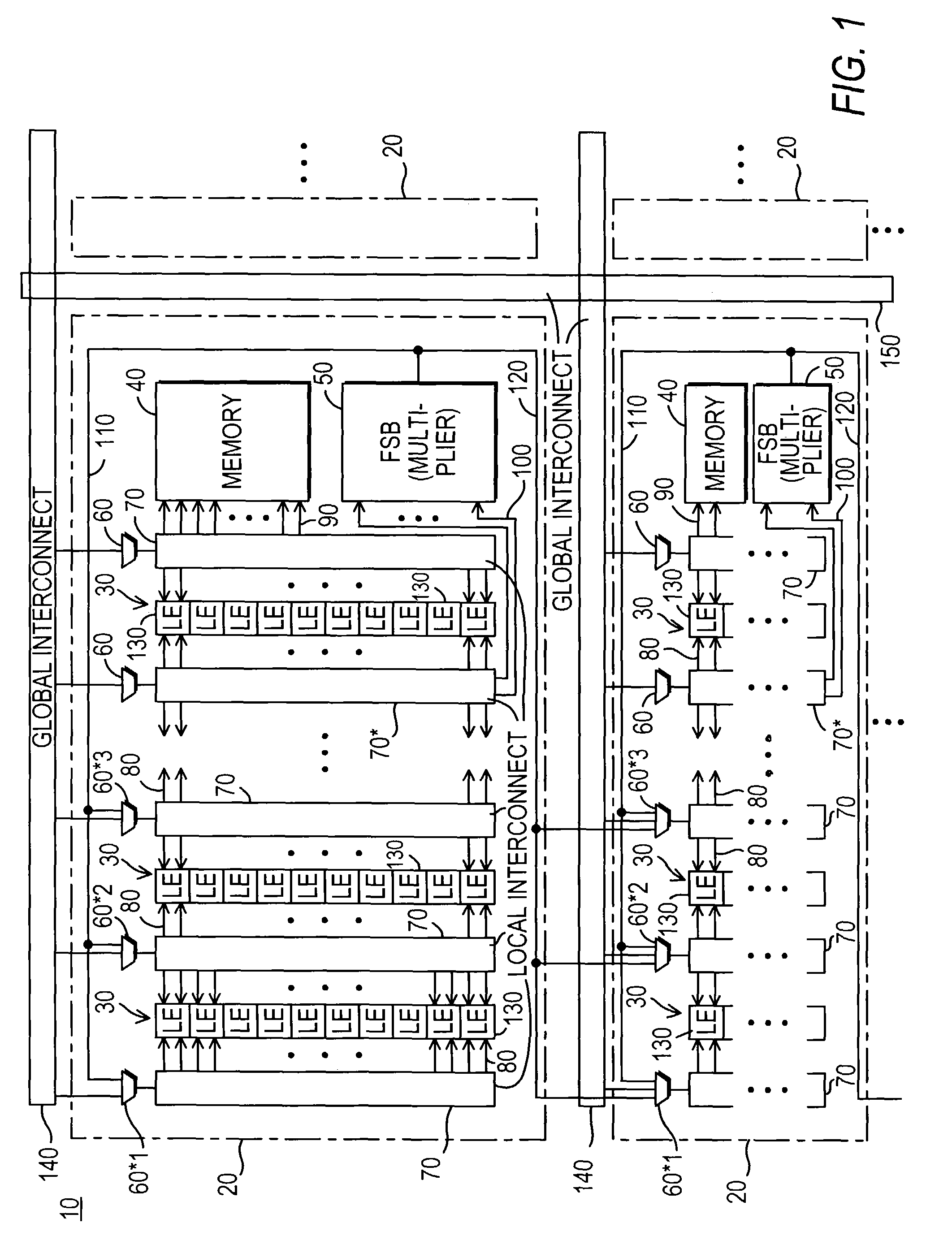

Programmable logic integrated circuit devices including dedicated processor components and hard-wired functional units

InactiveUS20050257030A1Function increaseFunctionalArchitecture with single central processing unitSpecific program execution arrangementsGeneral purposeArithmetic logic unit

A programmable logic integrated circuit device (“PLD”) includes programmable logic and a dedicated (i.e., at least partly hard-wired) processor object (or at least a high-functionality functional unit) for performing or at least helping to perform tasks that it is unduly inefficient to implement in the more general-purpose programmable logic and / or that, if implemented in the programmable logic, would operate unacceptably or at least undesirably slowly. The processor object includes an operating portion and a program sequencer that retrieves or at least helps to retrieve instructions for controlling or at least partly controlling the operating portion. The processor object may also include an address generator and / or a multi-ported register file for generating or at least helping to generate addresses of data on which the operating portion is to operate and / or destinations of data output by the operating portions. Examples of typical operating portions include multiplier-accumulators, arithmetic logic units, barrel shifters, and DSP circuitry of these or other kinds. The PLD may be provided with the capability to allow programs to be written for the device using local or “relative” addresses, and to automatically convert these addresses to actual or “absolute” addresses when the programs are actually performed by the device.

Owner:ALTERA CORP

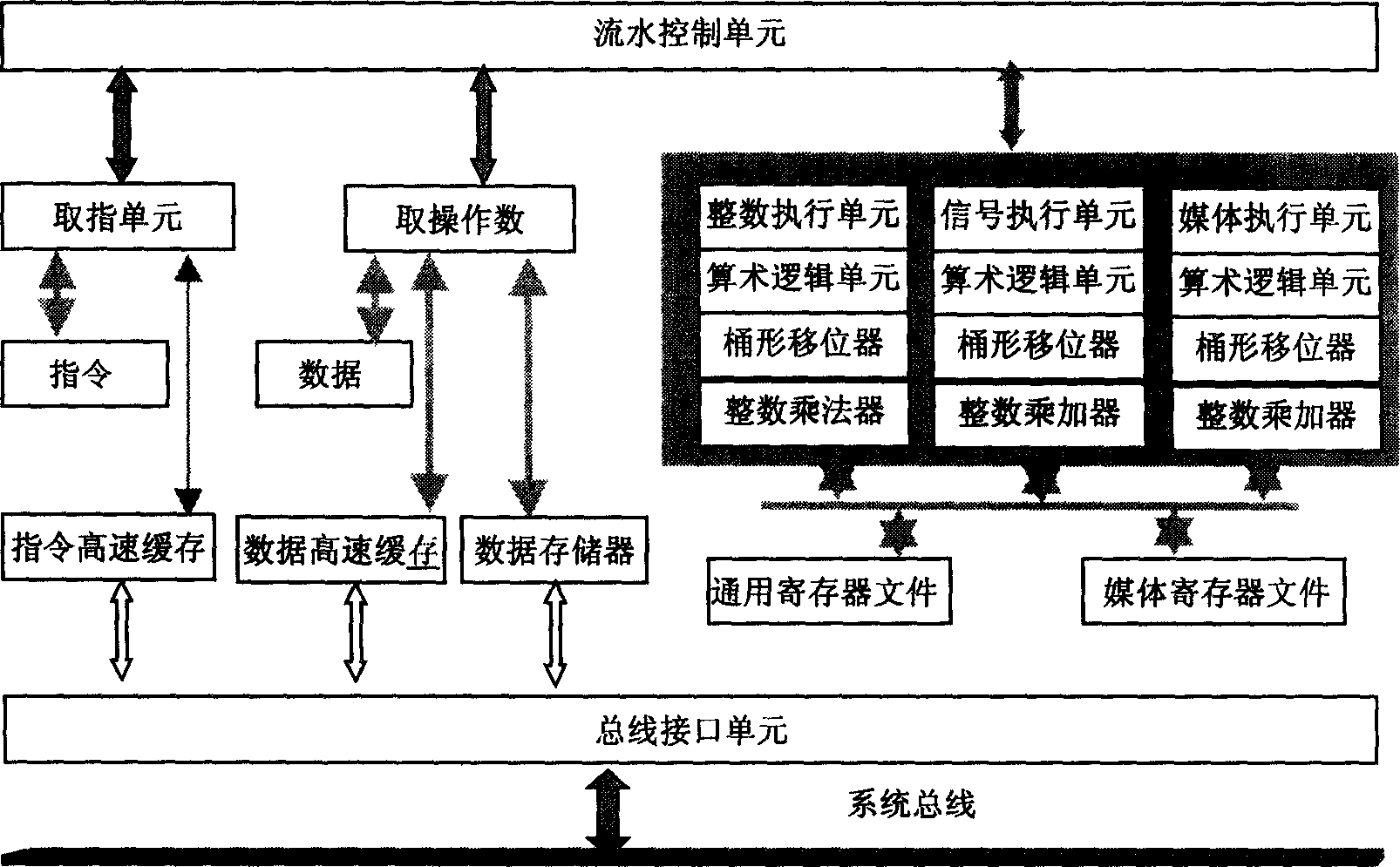

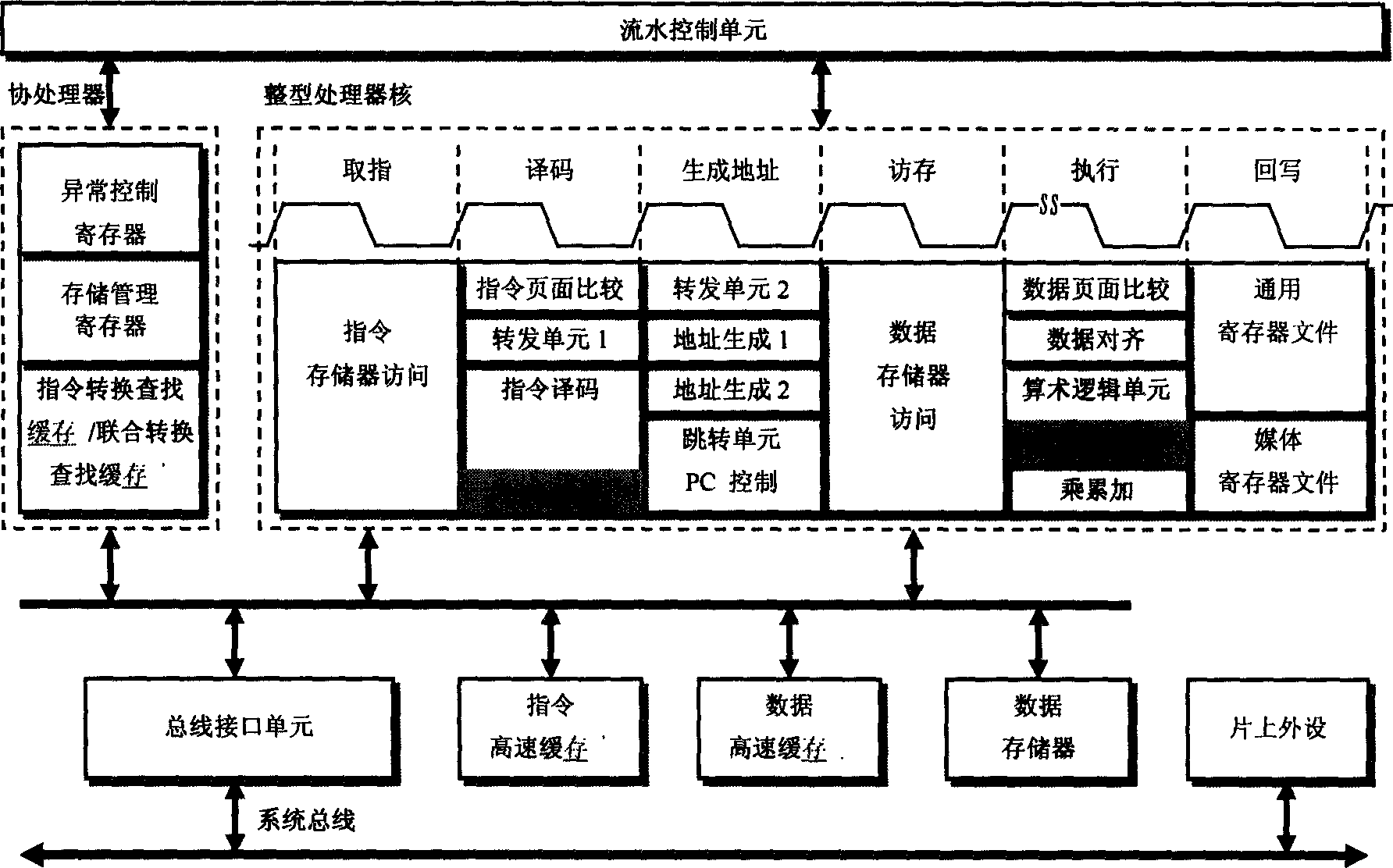

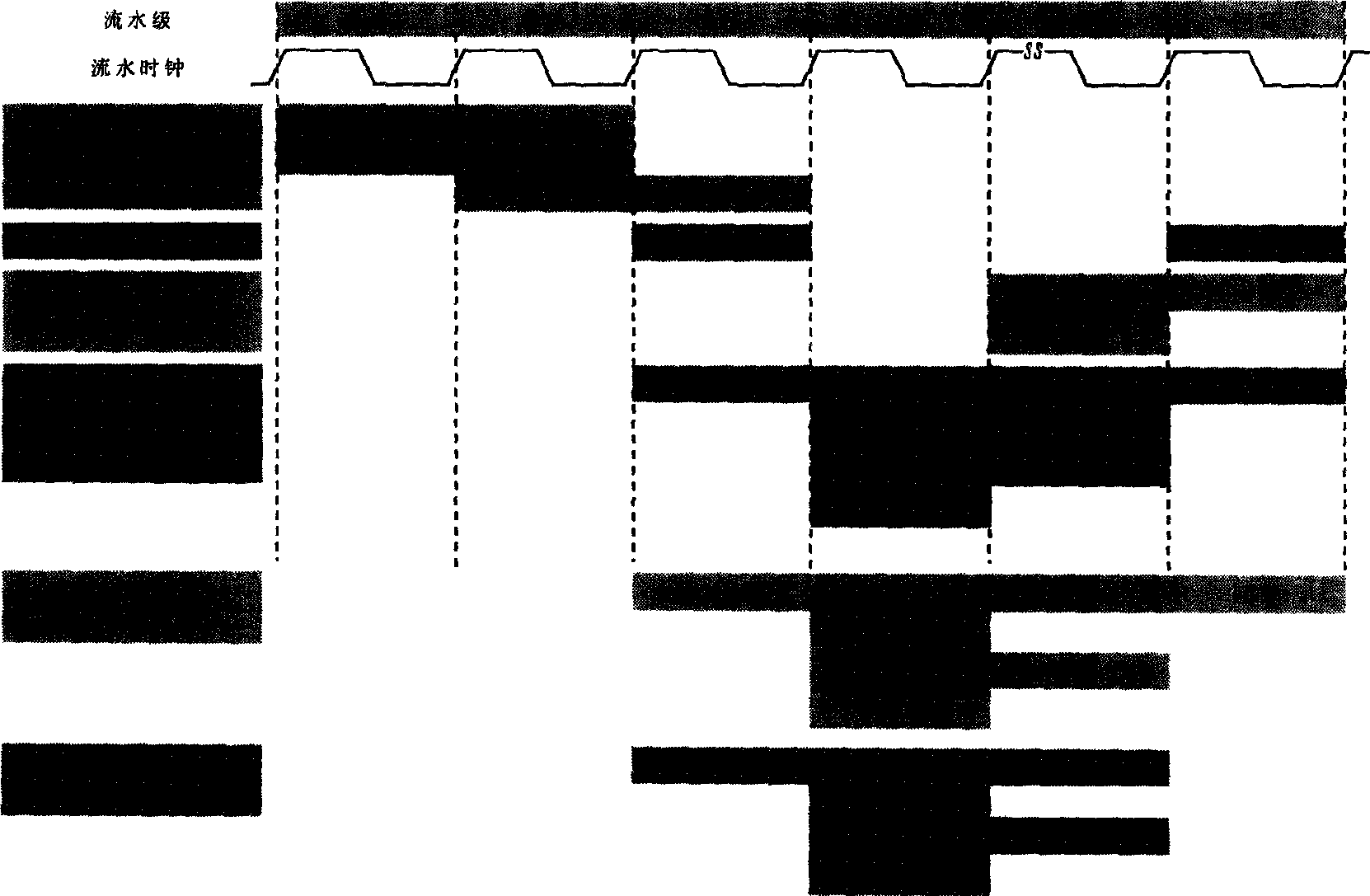

32-bit media digital signal processor

Owner:ZHEJIANG UNIV

Barrel shifter

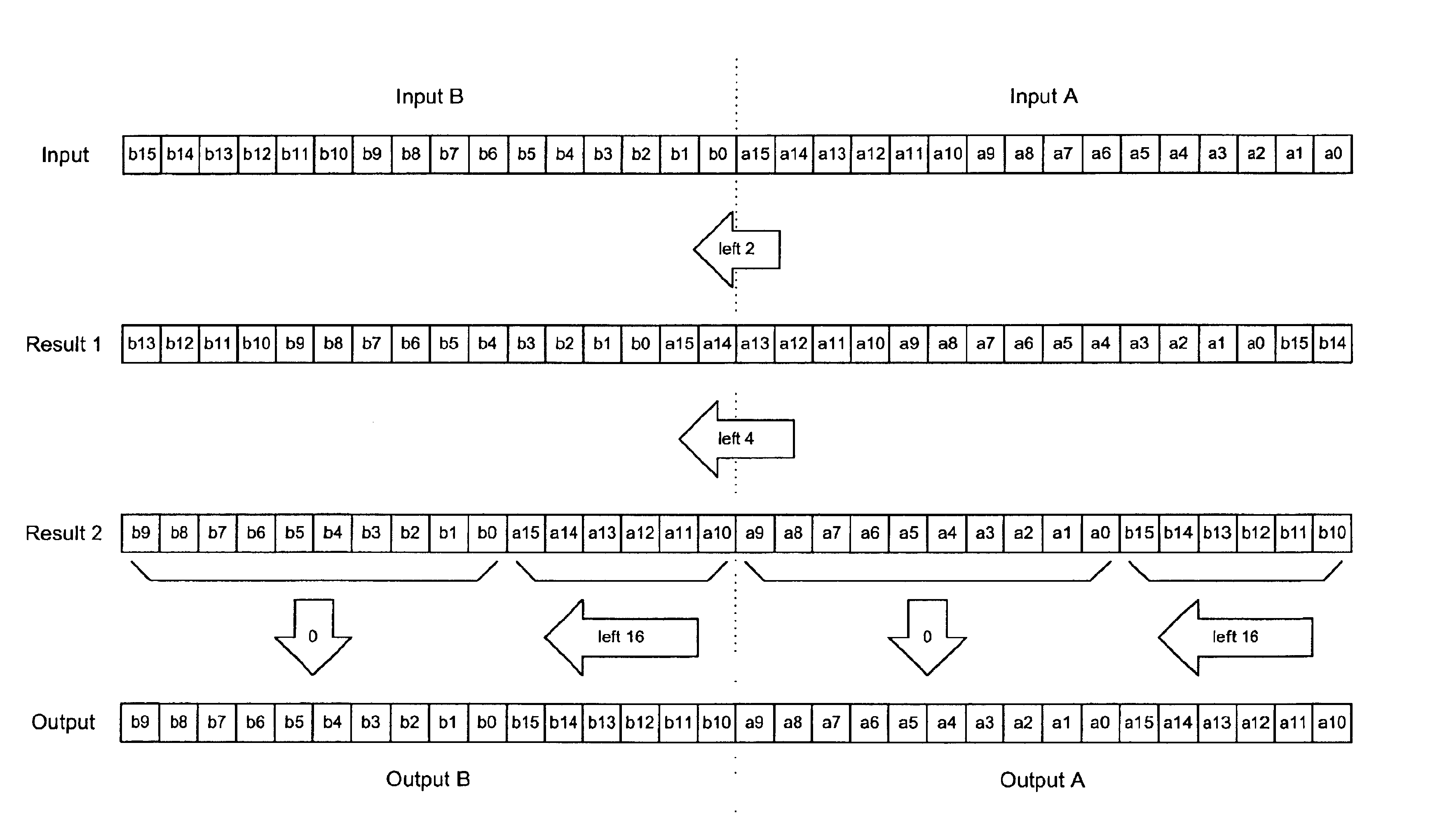

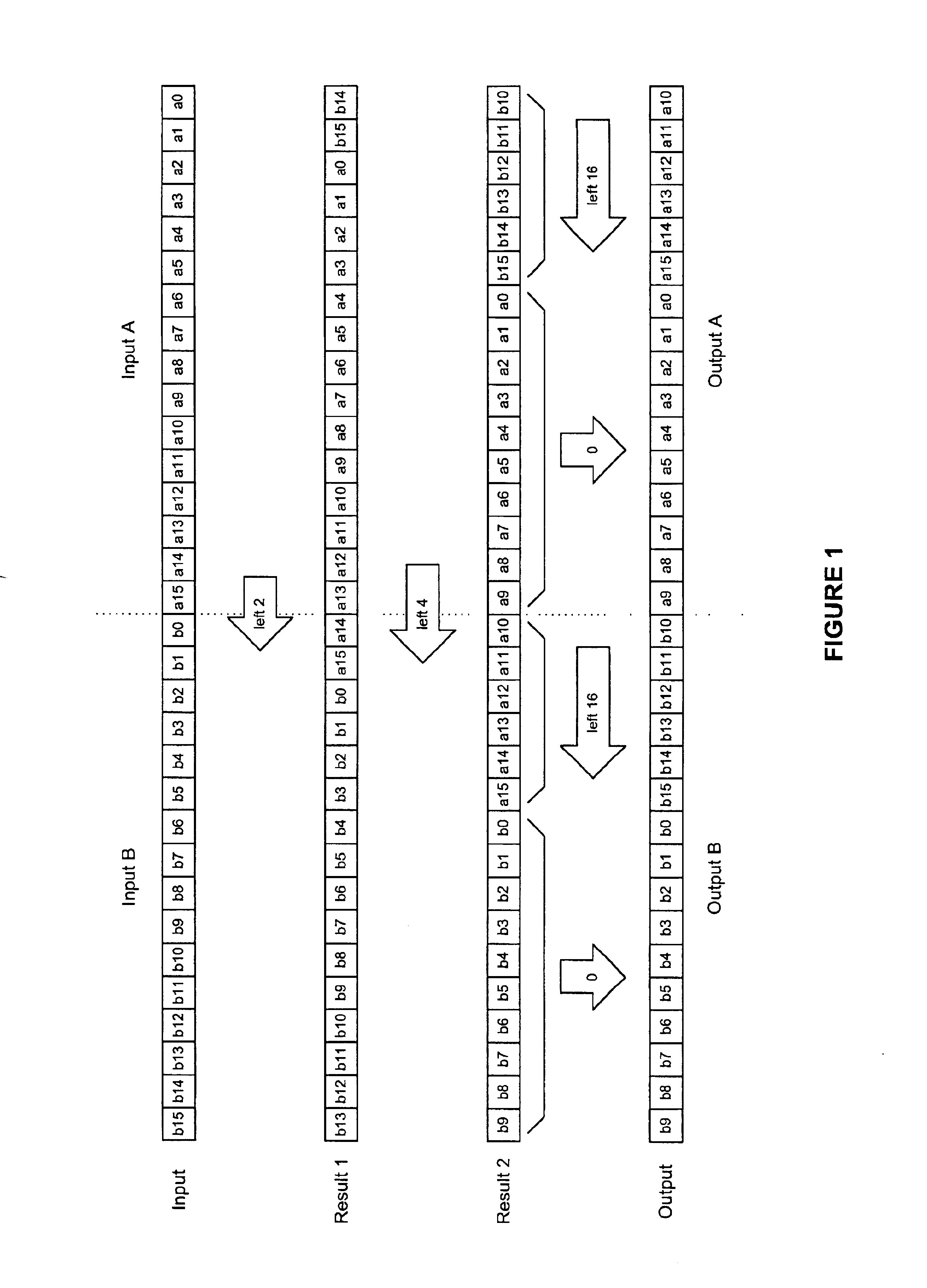

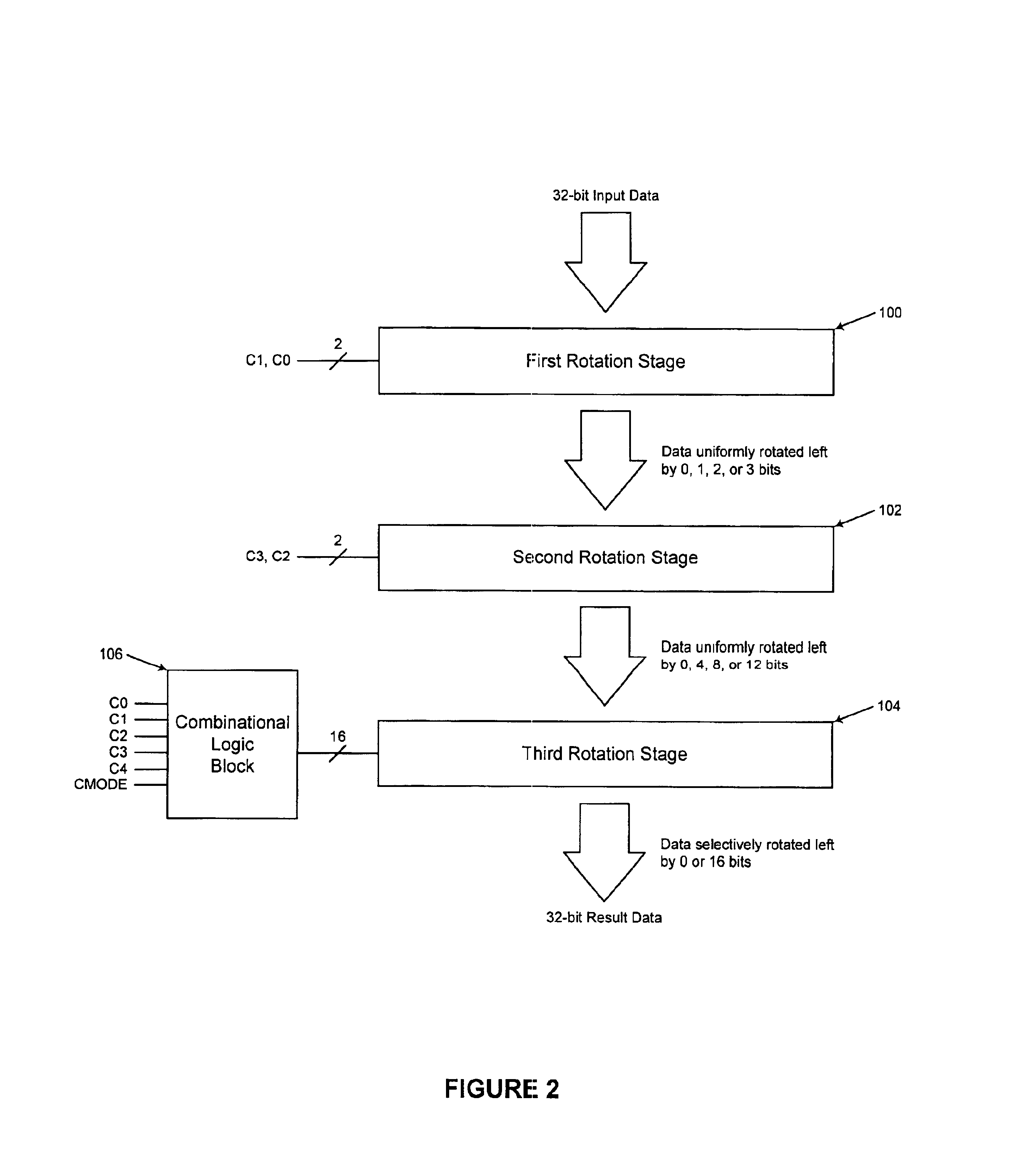

The present invention relates to a barrel shifter for manipulating bits within computer words. The barrel shifter includes multiple multiplexer stages for rotating single and multiple words. In several embodiments, it provides a half-word alignment in a 2n-bit barrel shifter, rotates a single 32-bit data word or two 16-bit data words, rotates a 2n-bit data word or two 2n−1-bit data half-words, a method of operating a 2n-bit barrel shifter to rotate two 2n−1-bit data words, multiplexer stages for rotating the bits to the left or right based on control signals, such that the stages do not require 2:1 multiplexers between the first and second stages.

Owner:SYNTEK INT HLDG

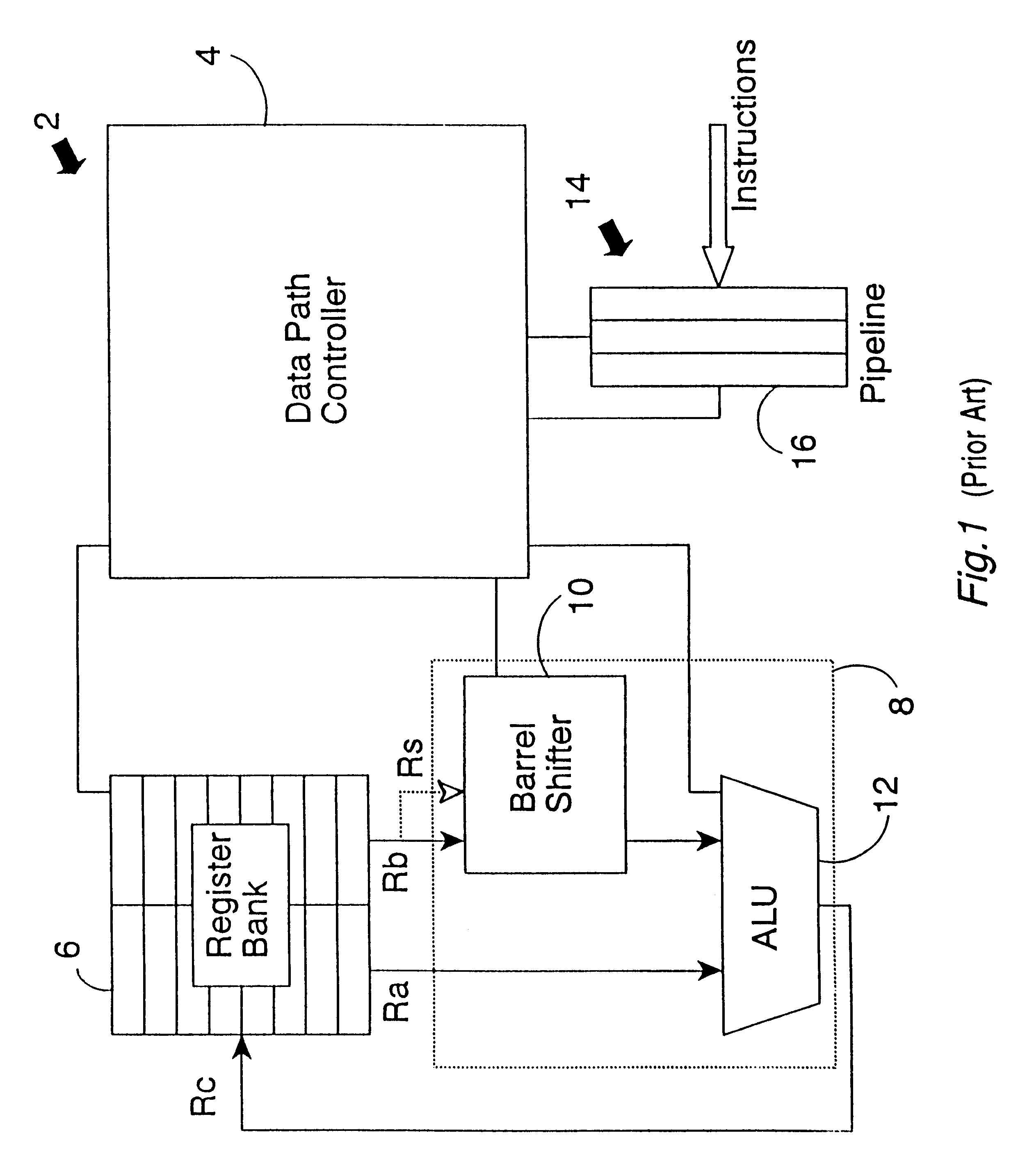

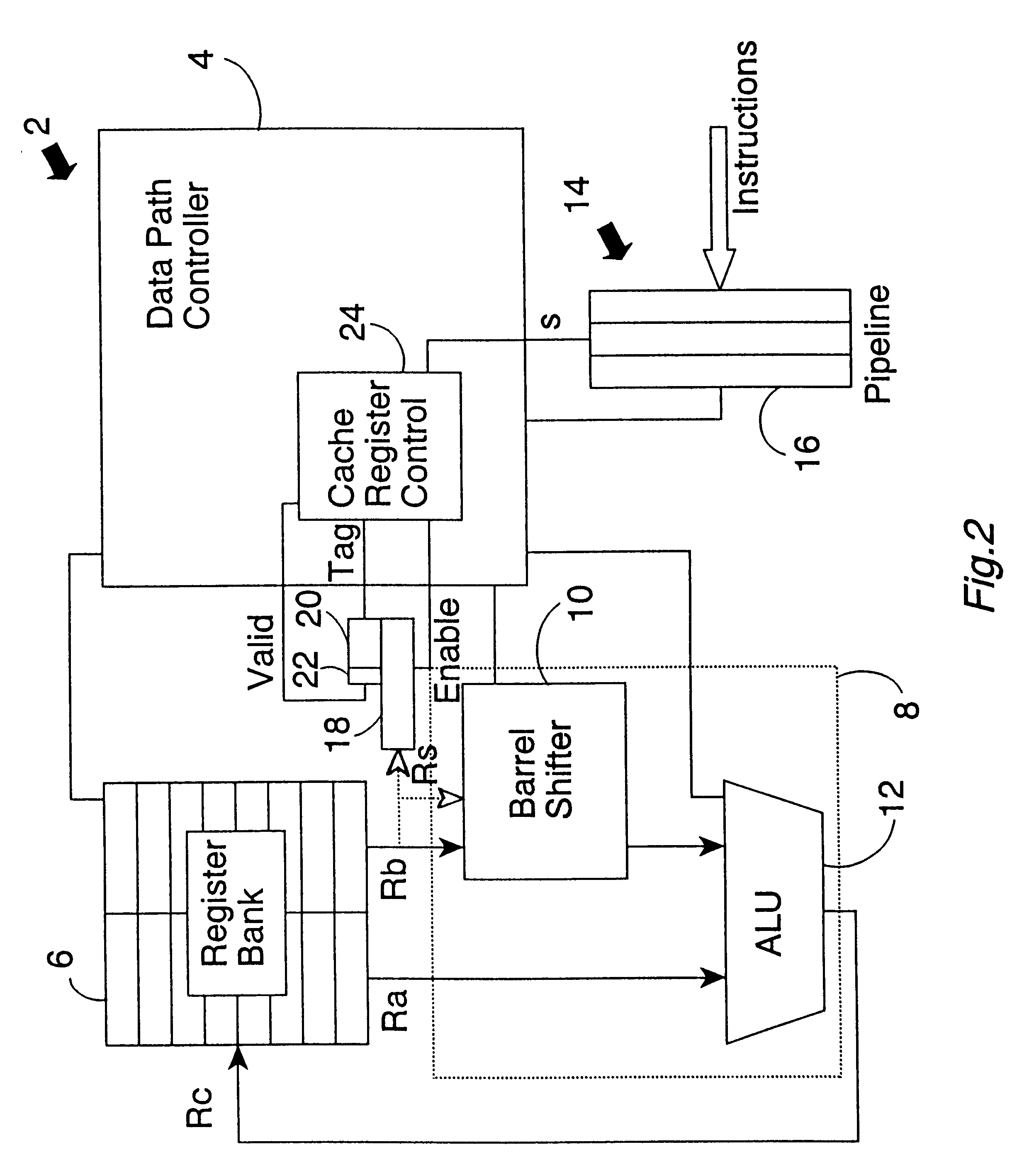

Operand supply to an execution unit

InactiveUS6289417B1Reduce in quantityMemory adressing/allocation/relocationConcurrent instruction executionProgram instructionProcessor register

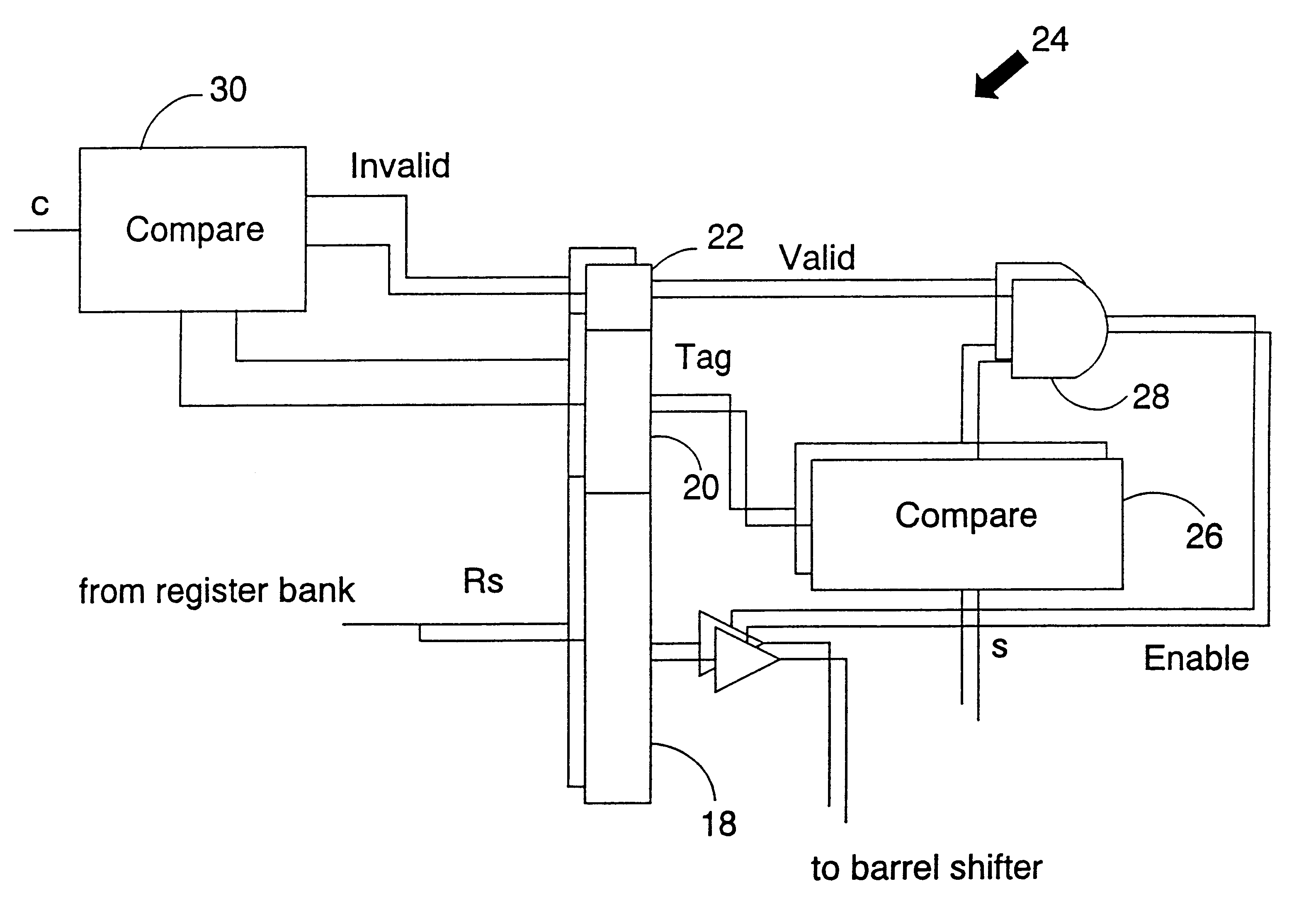

A microprocessor system comprising a register bank 6 and an execution unit 8 incorporating a barrel shifter 10 and an ALU 12 is provided. The register bank 6 has X read ports whilst at least some of the program instructions require Y input operands to be read from the register bank 6, where Y is greater than X. A cache register 18 is provided that caches previously read input operands for supply to the barrel shifter 10 and if it is detected that the same register is being read a second or subsequent time then this cached value is supplied to the barrel shifter 10 rather than requiring a further read from the register bank 6. A tag register 20 associated with each cache register 18 draws data indicating from which register within the register bank 6 the cached data value was copied. A valid flag 22 indicates that that cached data value is still current, i.e. at the corresponding register within the register bank 6 has not been overwritten.

Owner:ARM LTD

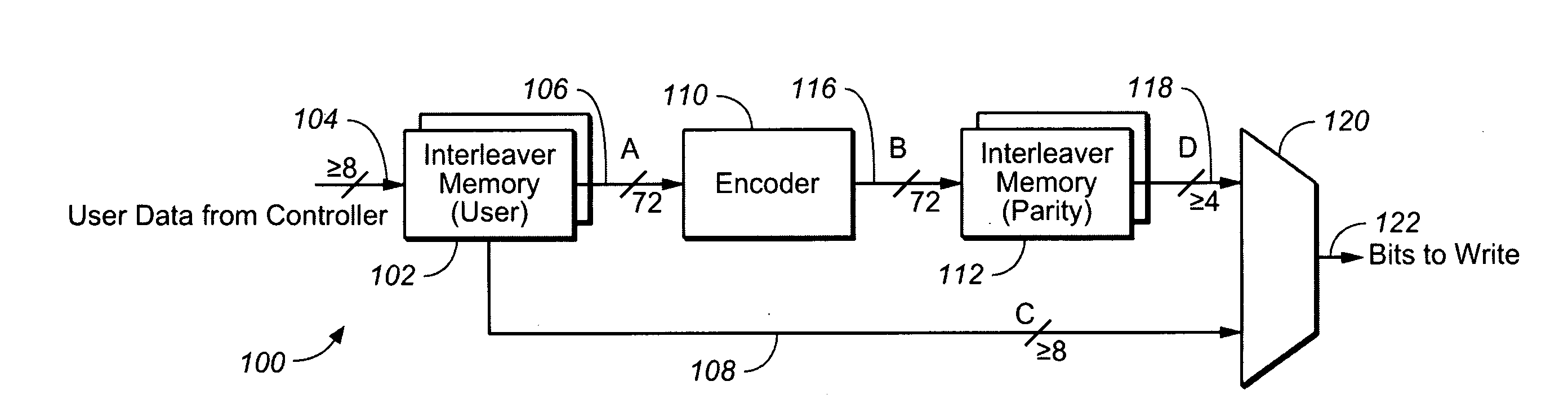

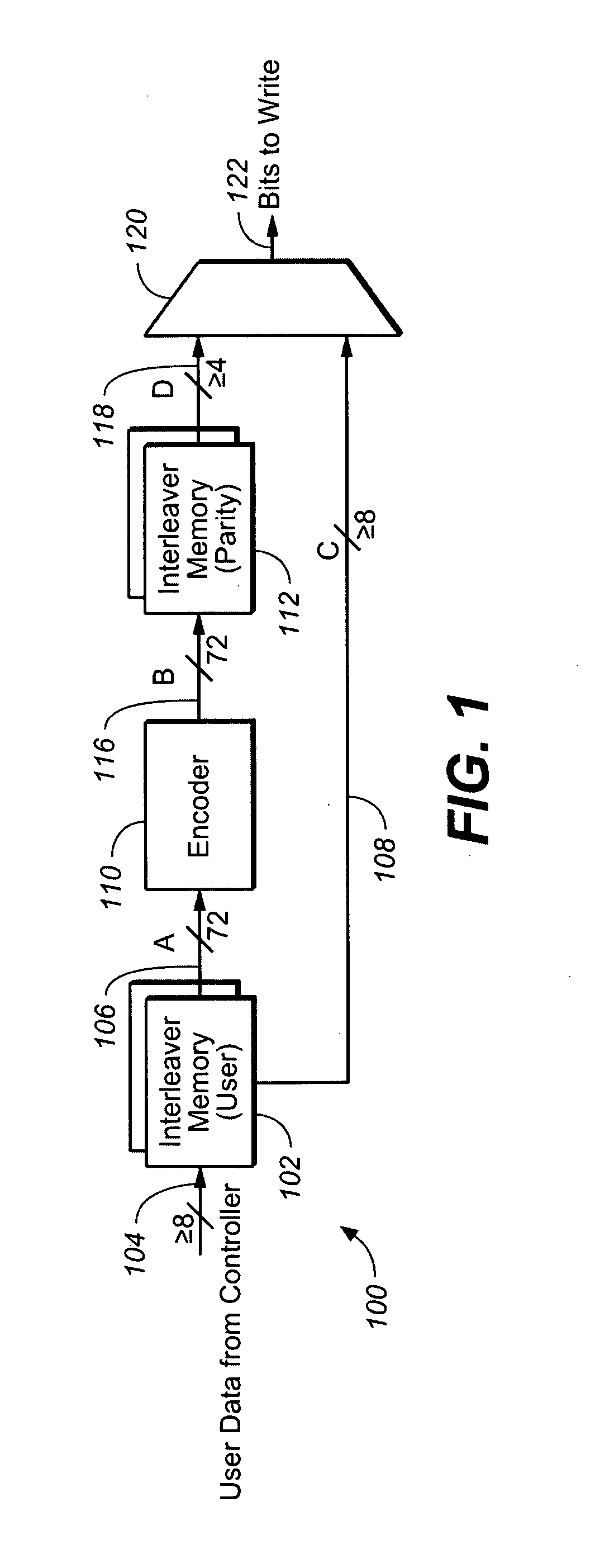

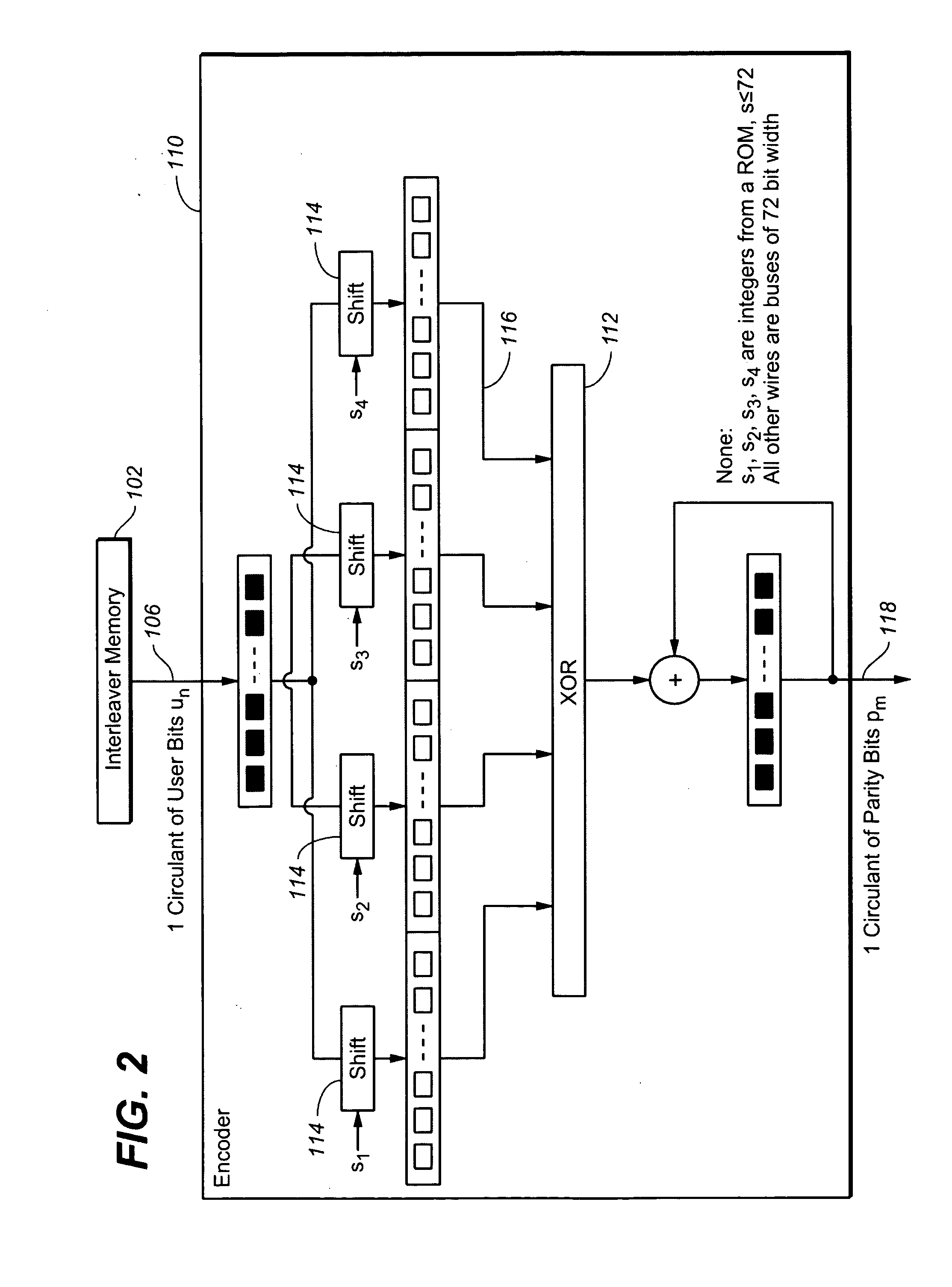

Programmable quasi-cyclic low-density parity check (QC LDPC) encoder for read channel

InactiveUS20100100788A1Code conversionError correction/detection using block codesMultiplexerEncoding algorithm

The present invention is a programmable QC LDPC encoder for encoding user data. The encoder may be configurable for implementation with a read channel. The encoder may include a plurality of barrel shifter circuits. The barrel shifter circuits are configured for generating a plurality of parity bits based on interleaved user bits received by the encoder. The barrel shifter circuits are further configured for outputting the parity bits. The encoder may further include an encoder interleaver memory. The encoder interleaver memory may be communicatively coupled with the barrel shifter circuits and may receive the parity bits output from the barrel shifter circuits. The encoder interleaver may be configured for interleaving the parity bits. Further, the encoder may be configured for outputting the interleaved parity bits to a multiplexer. The barrel shifter circuits may generate the plurality of parity bits via an encoding algorithm: p=u*GT.

Owner:BROADCOM INT PTE LTD

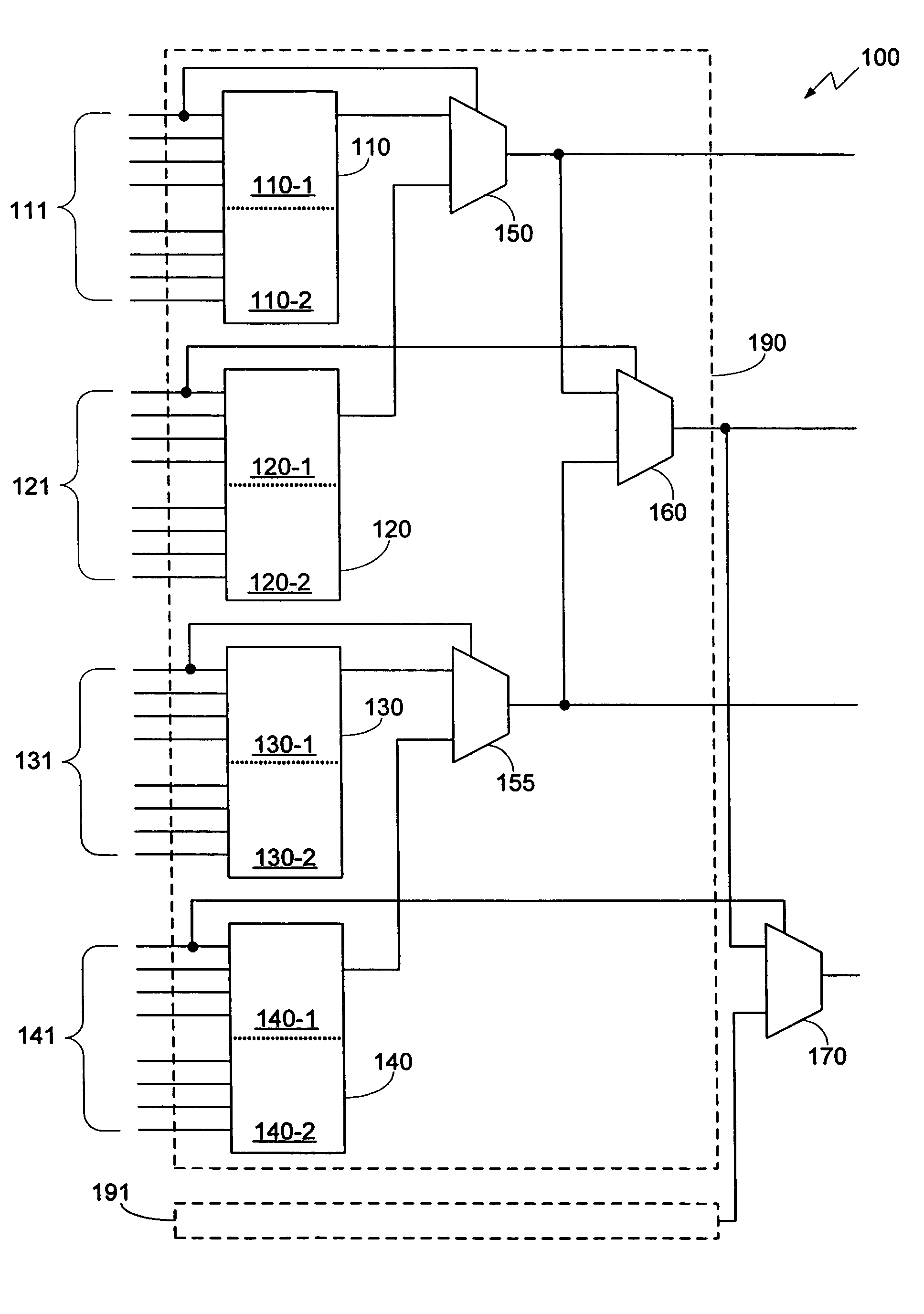

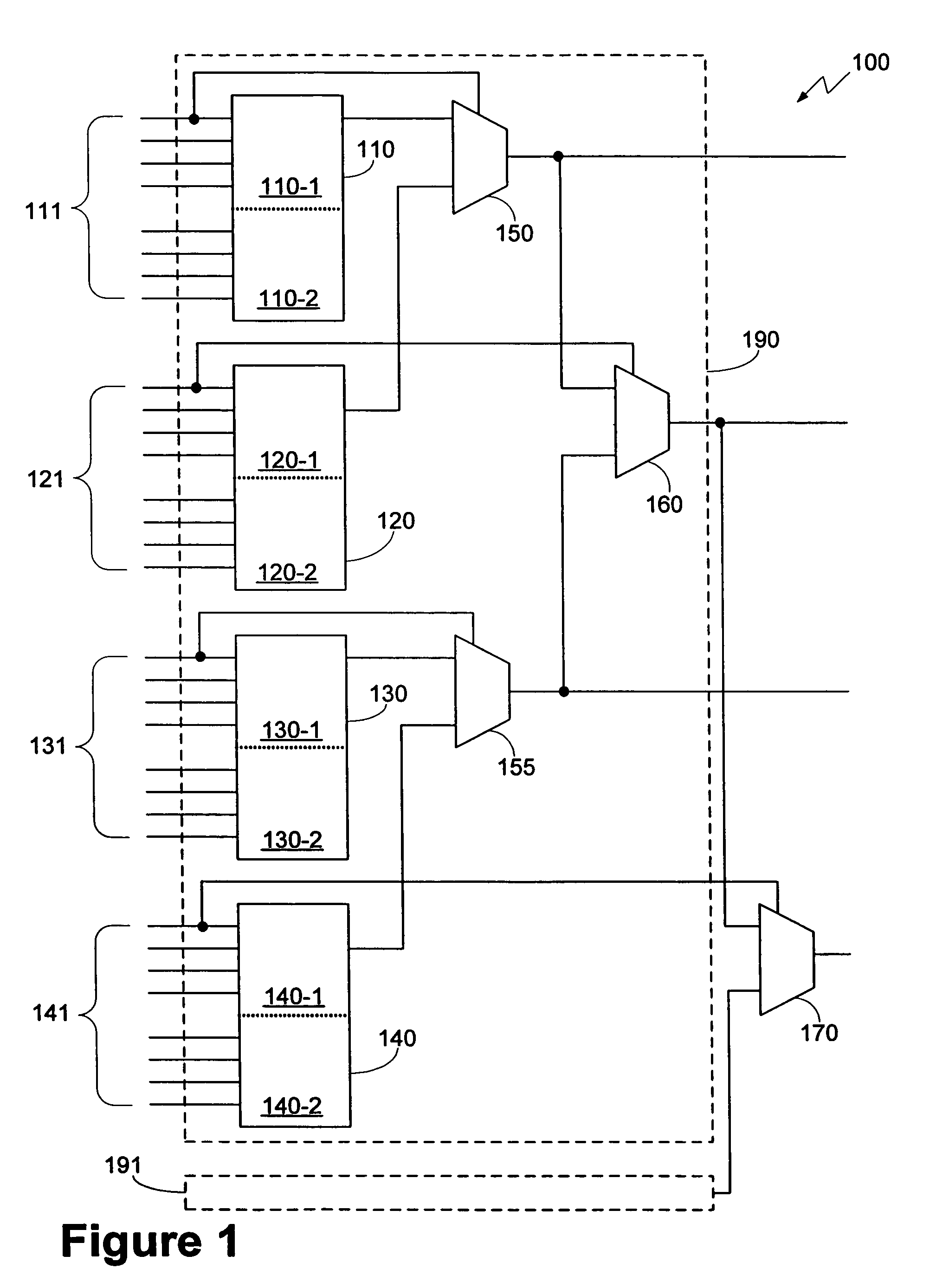

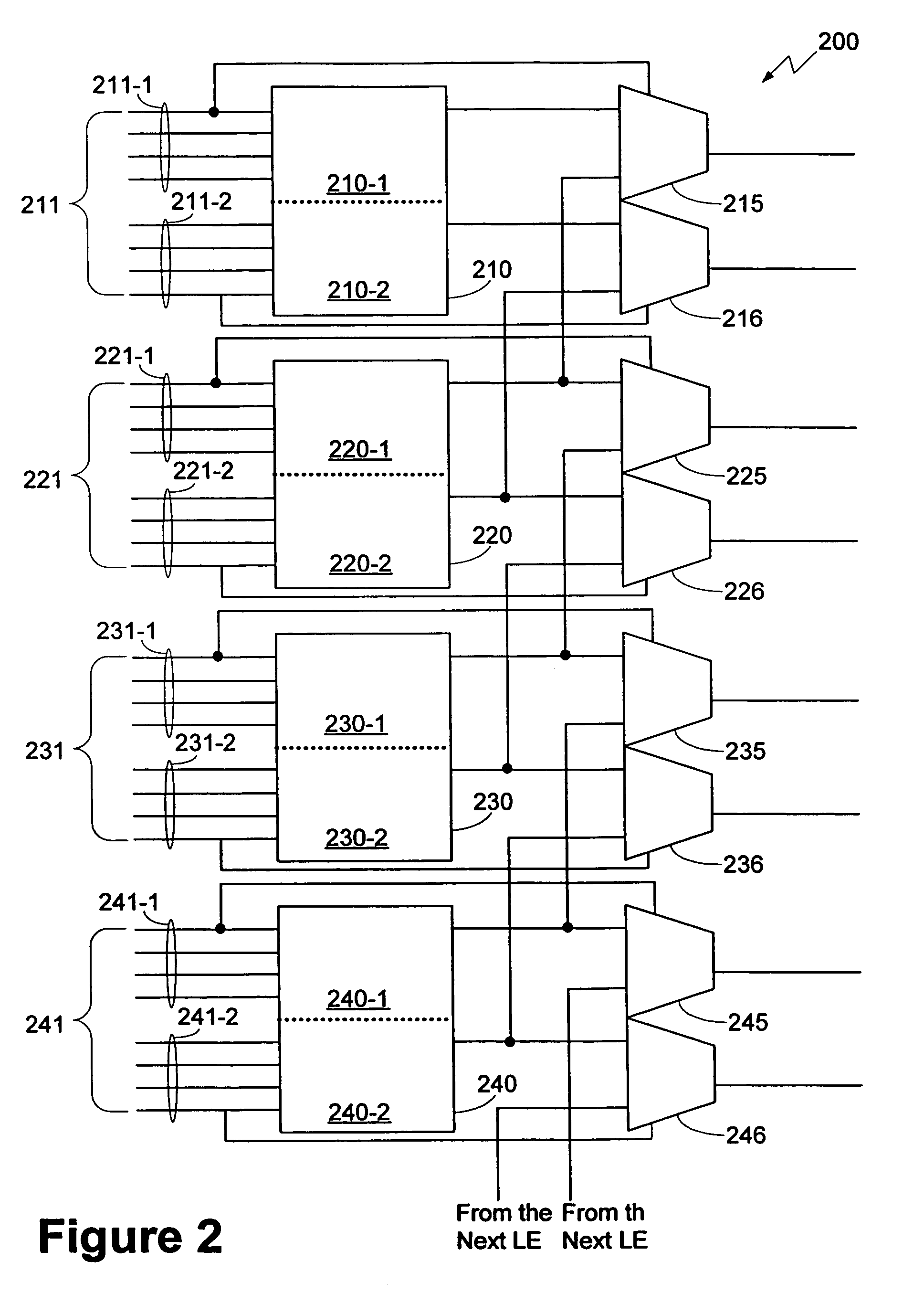

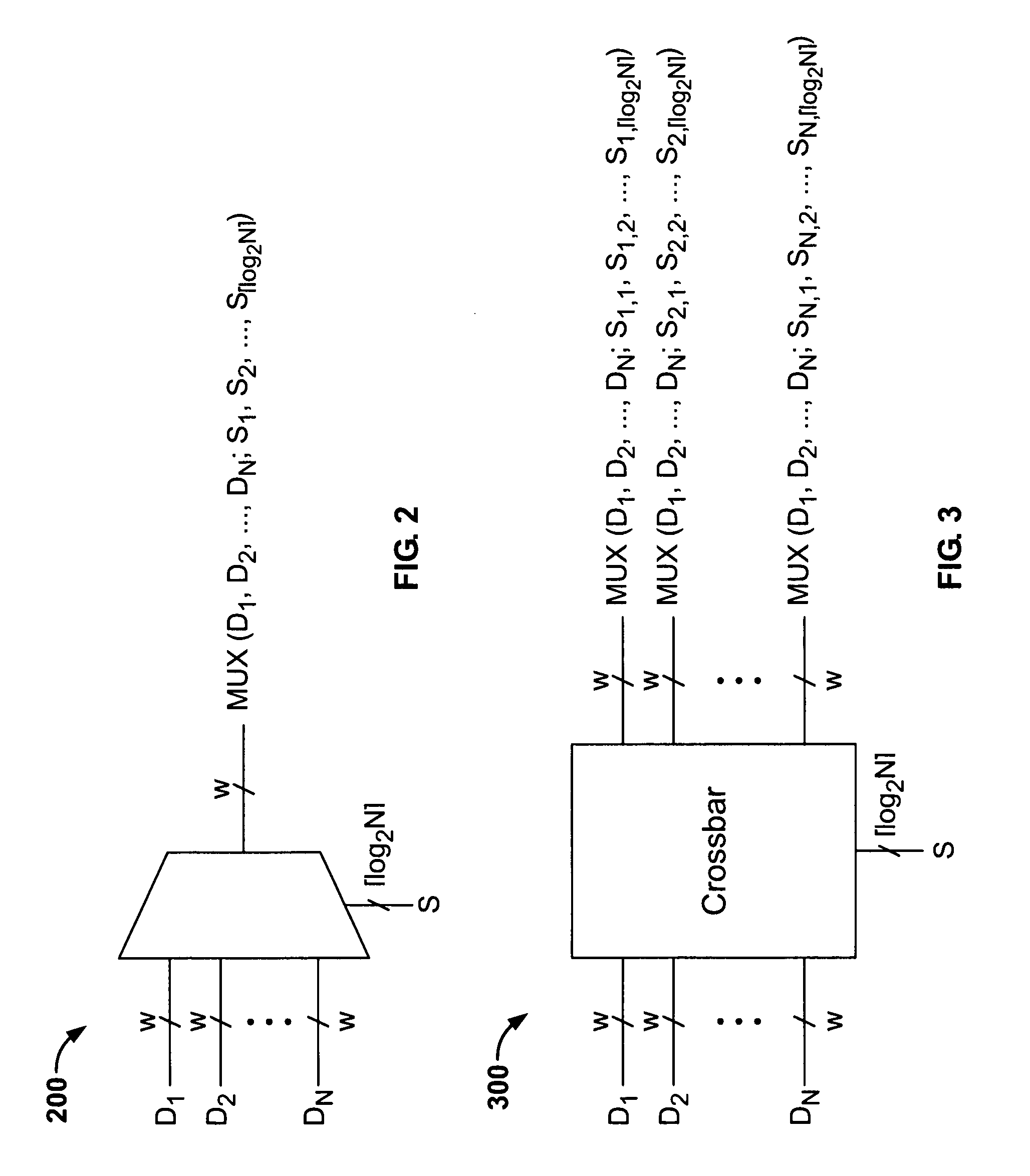

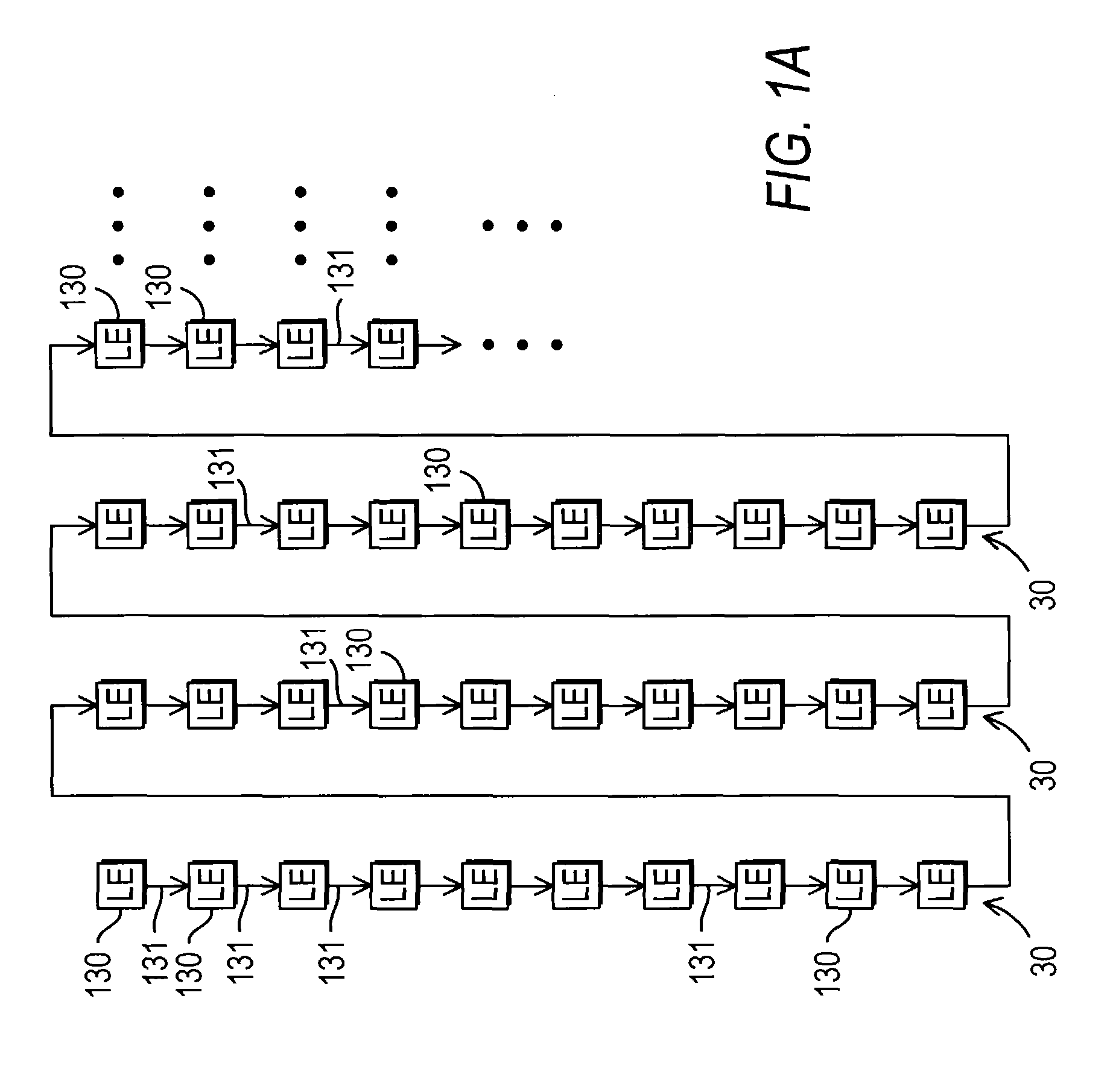

Logic cell with improved multiplexer, barrel shifter, and crossbarring efficiency

InactiveUS7119575B1Efficient multiplexingEfficient barrel shiftingSolid-state devicesLogic circuits using elementary logic circuit componentsLogic cellMultiplexer

Logic circuits that provide improved efficiency are described. In one general embodiment, this is accomplished by feeding outputs of LEs in the logic circuit to multiplexers that receive their select signals from input terminals of the LEs in the logic circuit. In one embodiment, each of the LEs provides one output signal. The first LE in the logic circuit provides an output signal to one multiplexer, while each of the remaining LEs in the logic circuit provides an output signal to two multiplexers. In another embodiment, each of the LEs provides two output signals. The first LE in the logic circuit provides two output signals to one multiplexer, while each of the remaining LEs in the logic circuit provides two output signals to four multiplexers.

Owner:ALTERA CORP

Method and apparatus for recovering a clock signal from an asynchronous data signal

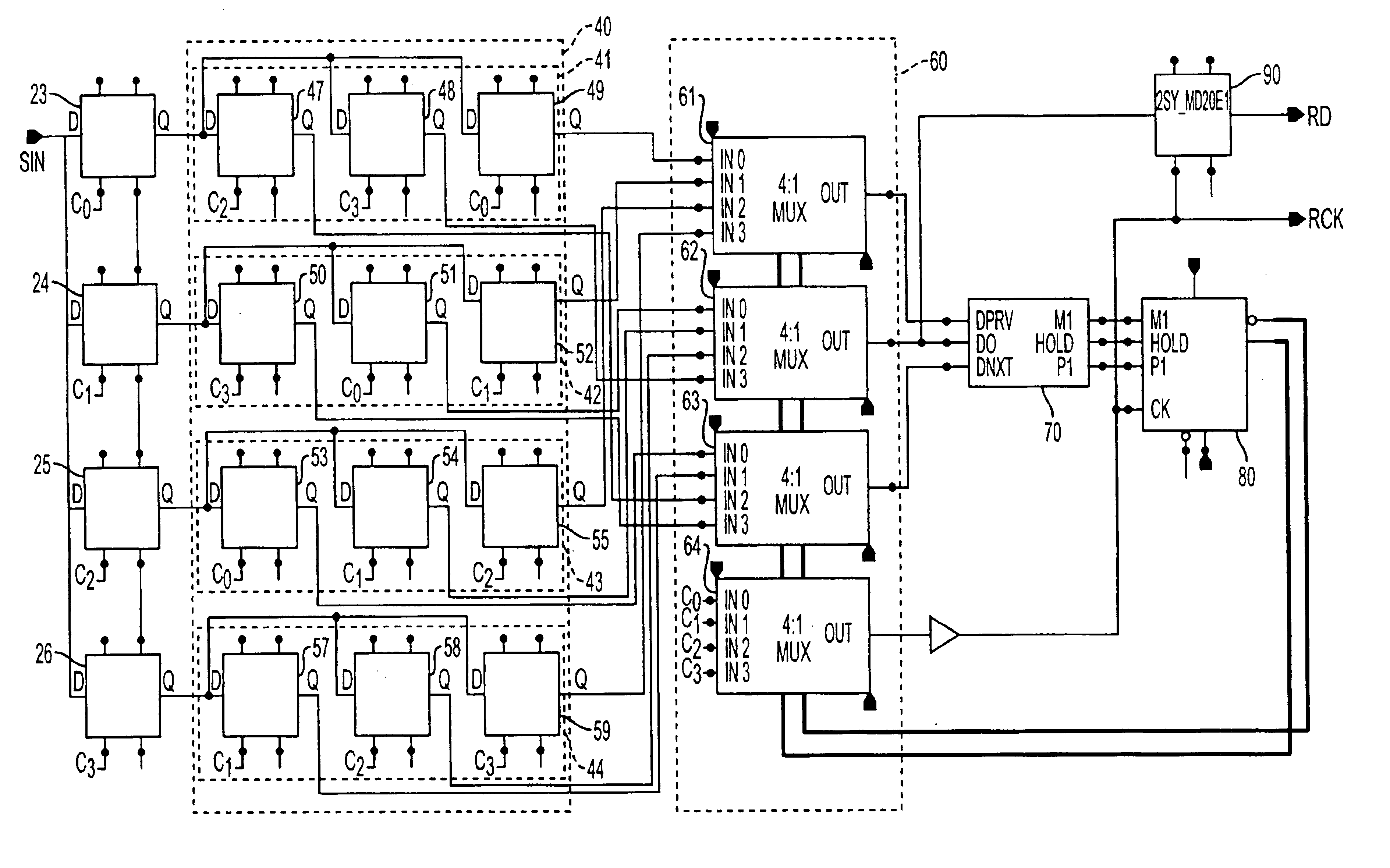

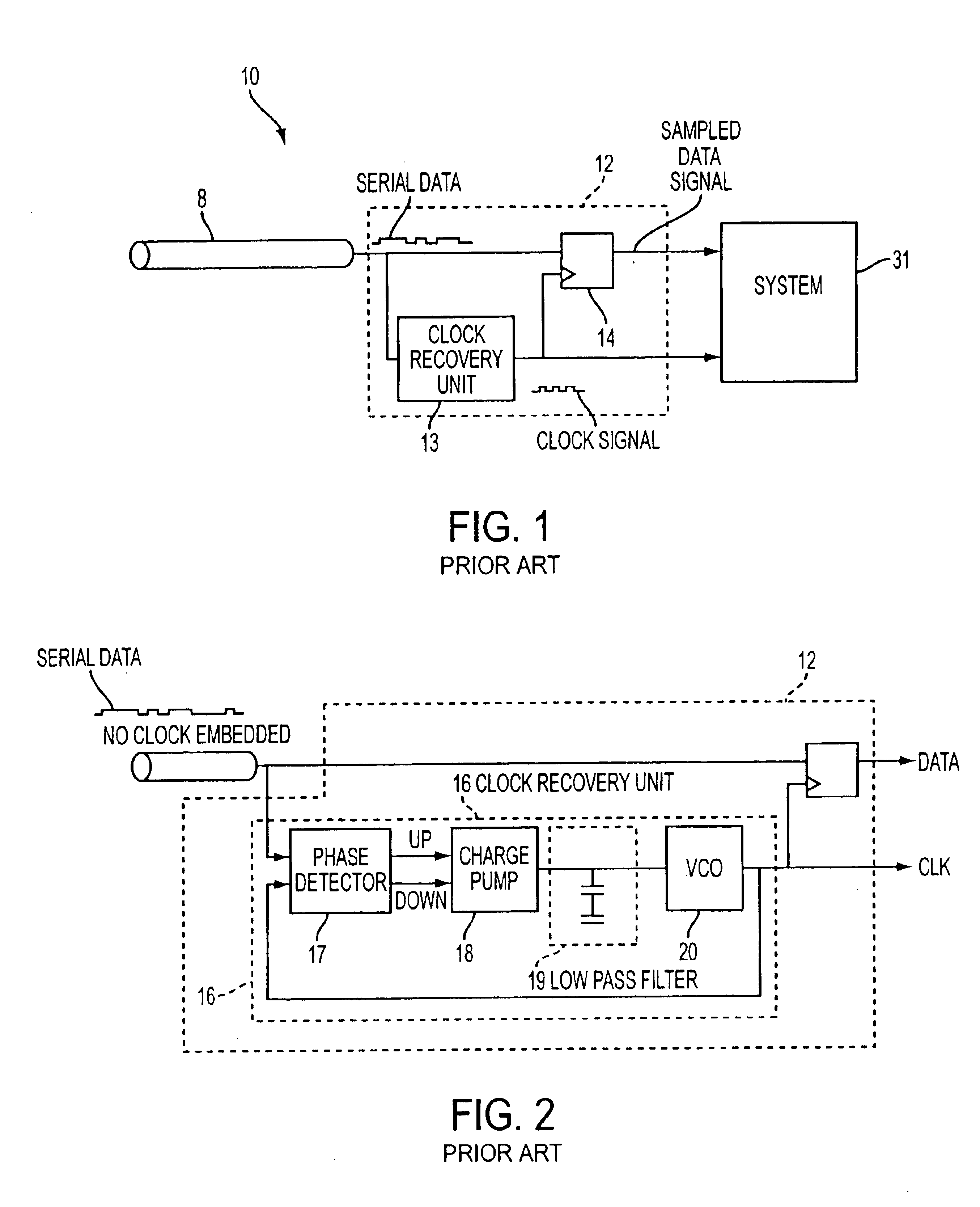

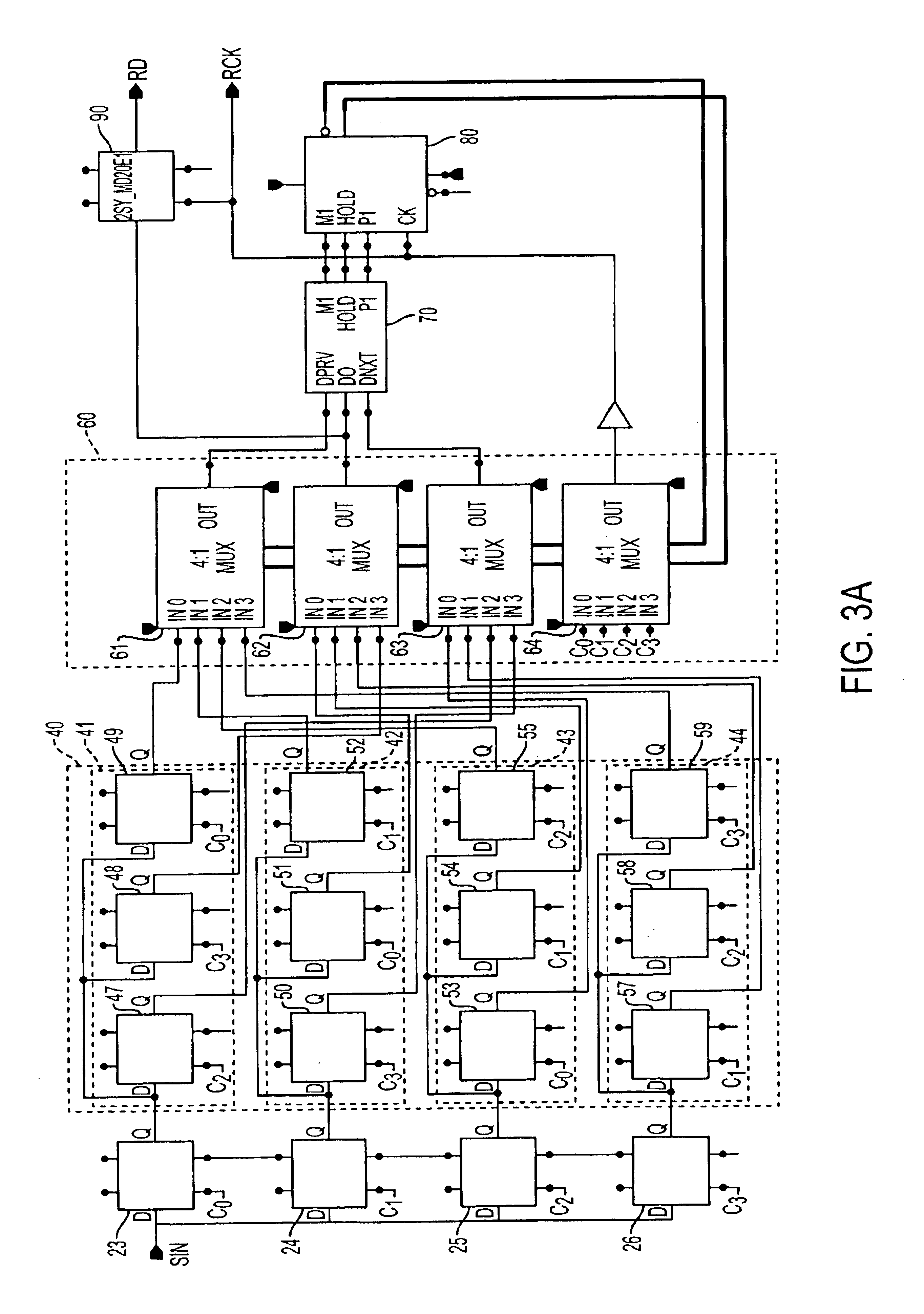

InactiveUS6868134B2Simple and cost-effectiveSimple and cost-effective designPulse automatic controlSynchronising arrangementMultiplexerClock recovery

A clock recovery unit for generating a clock signal corresponding to an asynchronous data signal. The clock recovery unit includes an input port for receiving an incoming data signal; a local oscillator circuit for generating a plurality of clock signals having the same frequency, where the plurality of clock signals are each shifted in phase relative to one another; a sampling unit having a plurality of latches, each of which is clocked by one of the plurality of clock signals generated by the local oscillator circuit, the sampling unit outputting a plurality data samples of the incoming data signal; a data phase alignment unit coupled to the sampling unit, the data phase alignment unit receiving the plurality of data samples as input signals and operative for shifting the phase of the plurality of data samples; a multiplexer circuit coupled to the data phase alignment unit, the multiplexer circuit having a first multiplexer operative for selecting a portion of the plurality of data samples, each of the data samples having a corresponding clock signal, which is one of the plurality of clock signals generated by the local oscillator circuit, the multiplexer circuit having a second multiplexer operative for selecting one of the plurality of clock signals generated by the local oscillator circuit; a phase decoder coupled to the multiplexer circuit, the phase decoder operative for receiving the portion of the plurality of data samples selected by the multiplexer and for generating an output signal indicative of the logic values of the portion of the plurality of the data samples selected by the first multiplexer; and a barrel shifter circuit coupled to the phase decoder, the barrel shifter operative for adjusting the data samples selected by the first multiplexer in accordance with the output signal of the phase decoder.

Owner:PANASONIC CORP

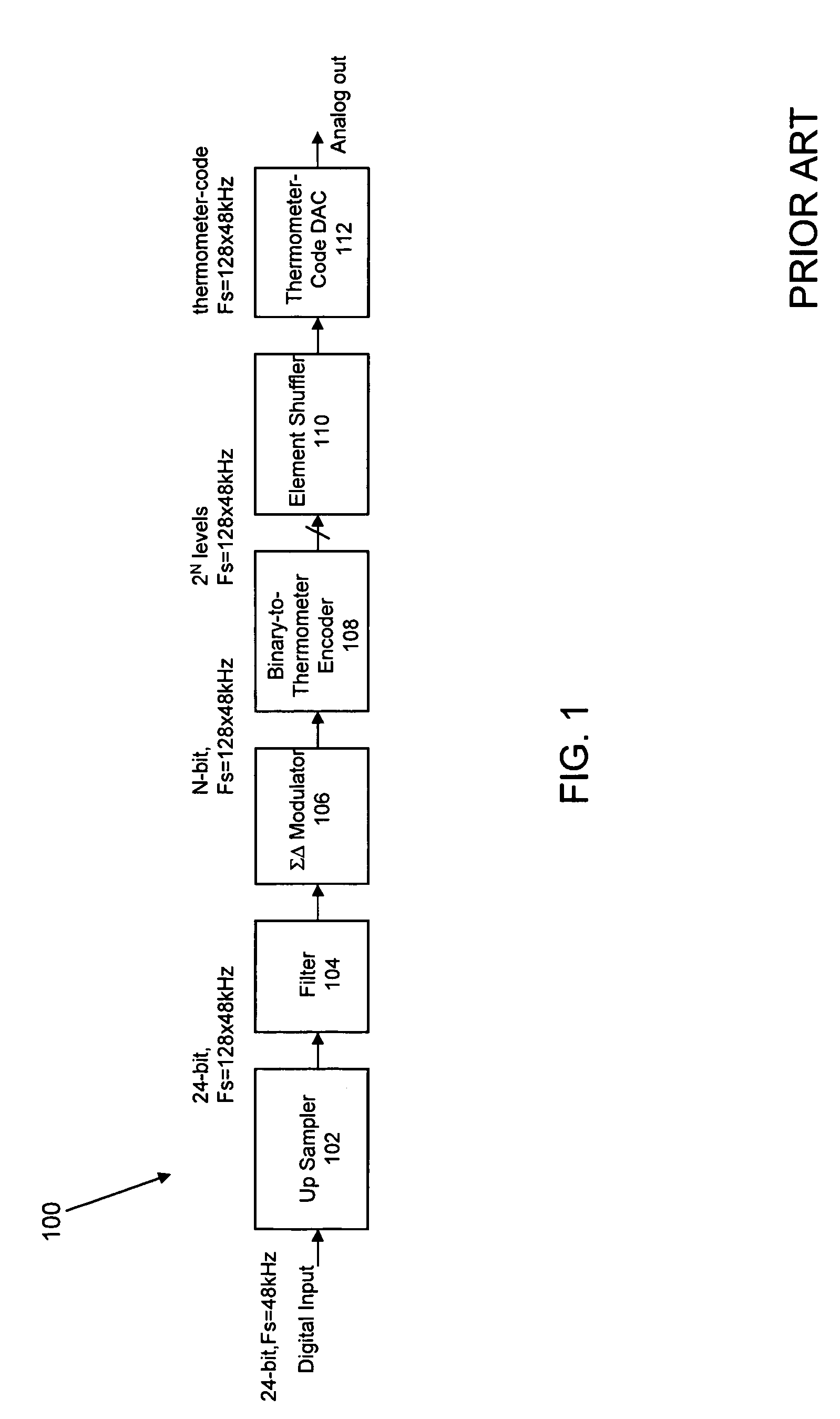

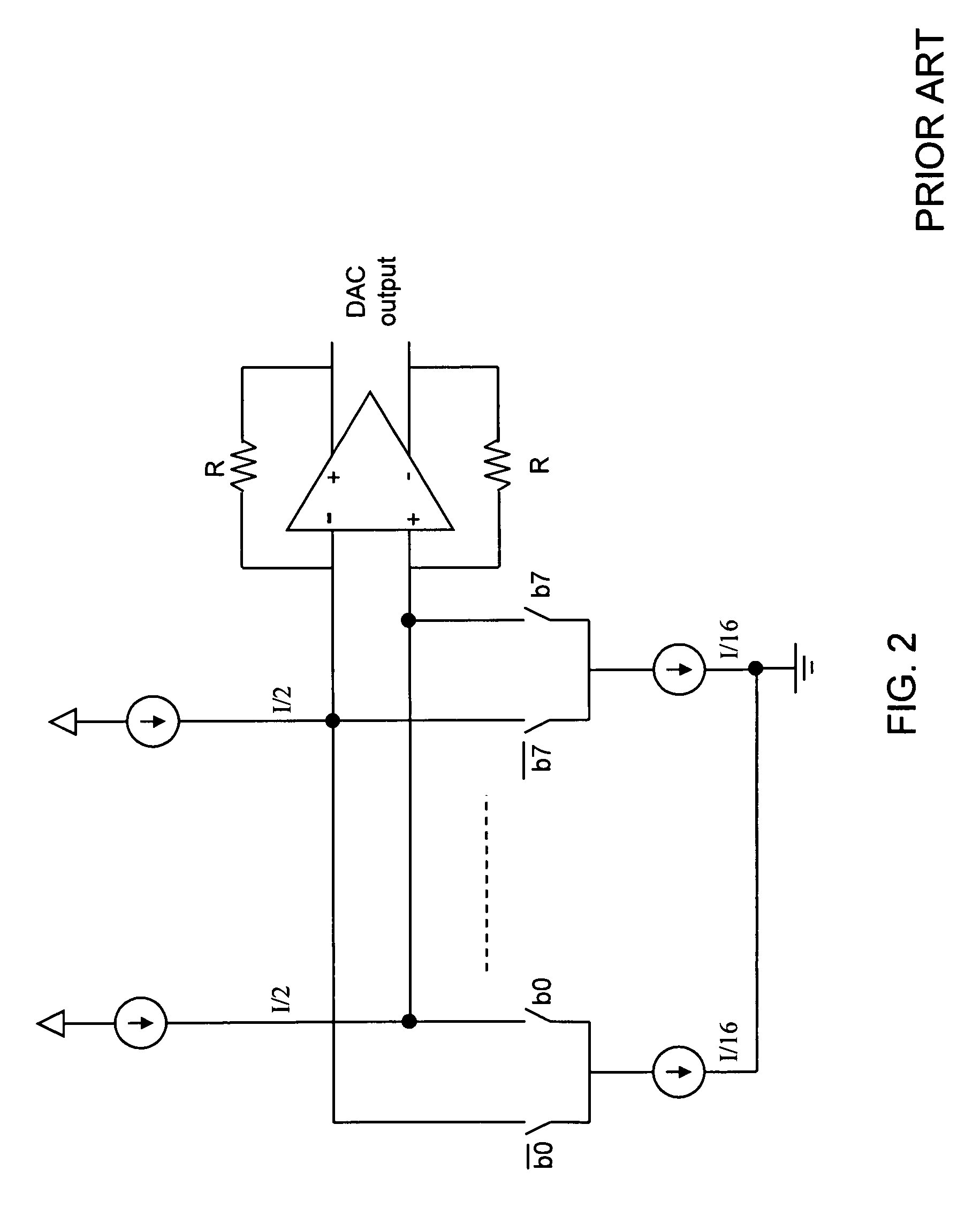

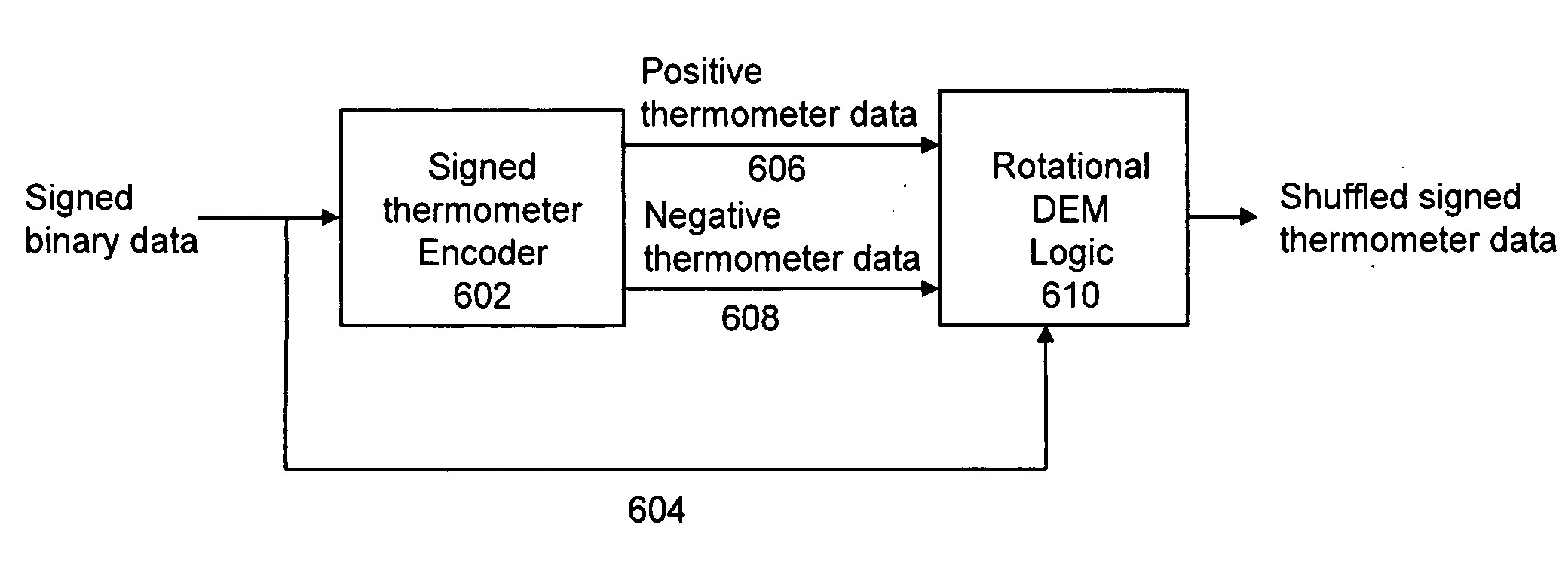

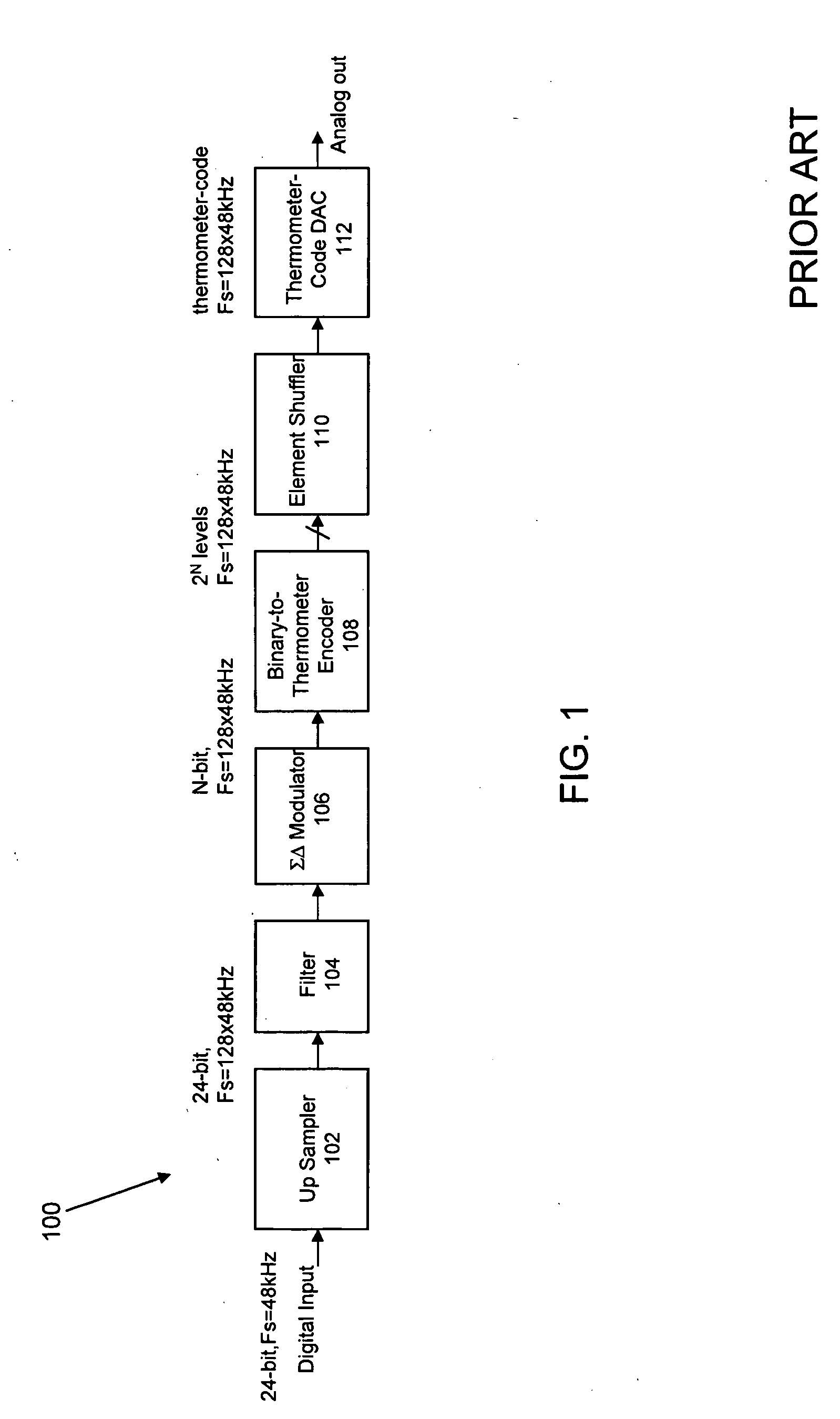

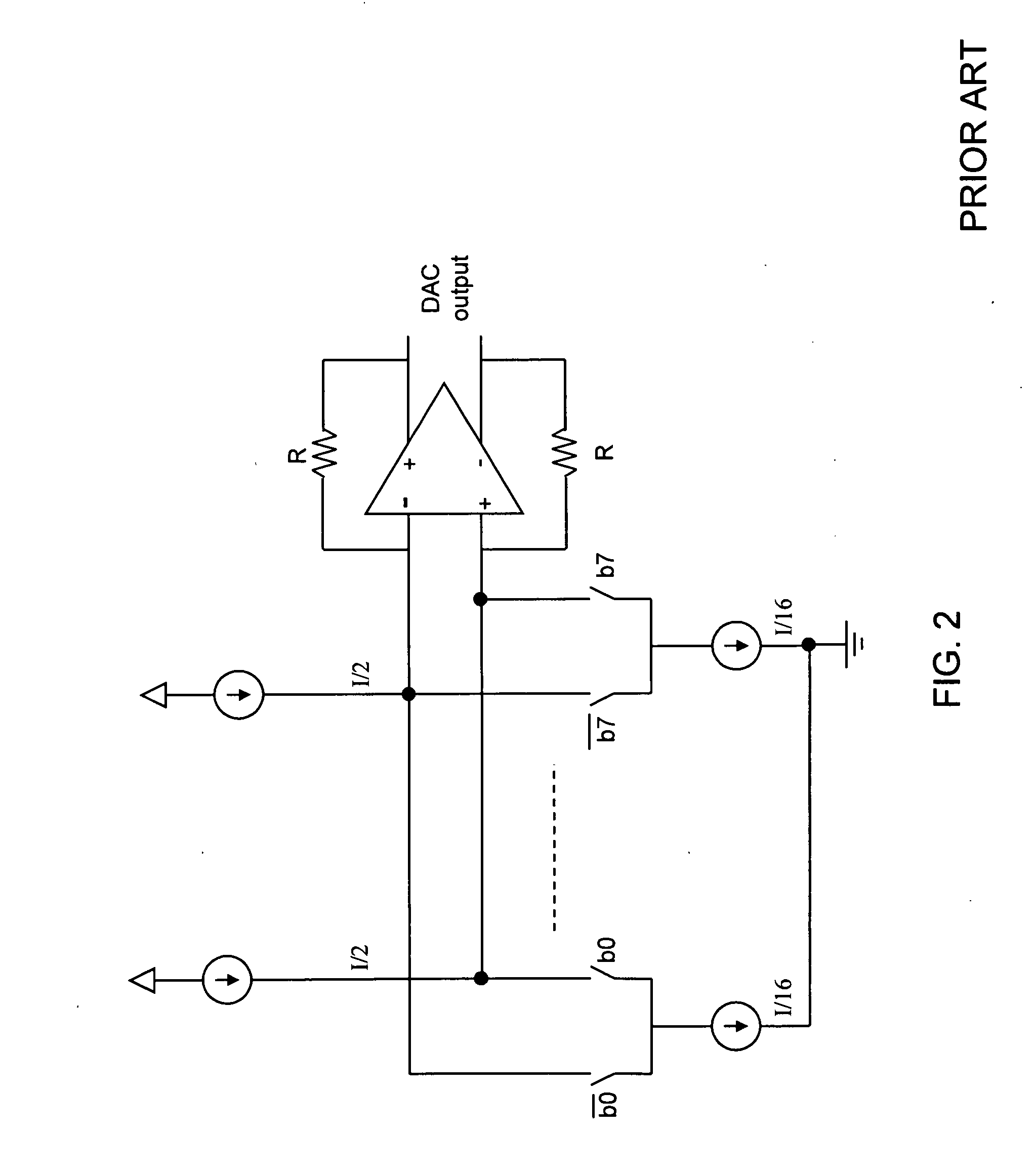

System and method for area-efficient three-level dynamic element matching

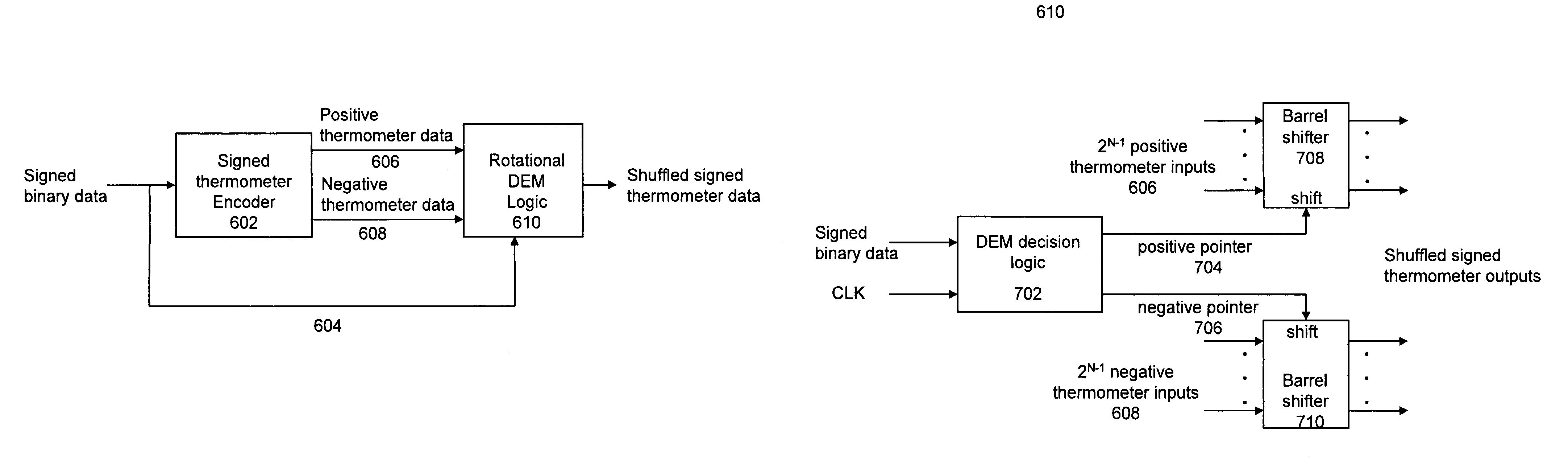

ActiveUS7777658B2Electric signal transmission systemsAnalogue conversionThree levelData transformation

A system for converting digital signals into analog signals using sigma-delta modulation and includes a signed thermometer encoder for converting a plurality of signed binary data received at the encoder into a plurality of signed thermometer data and a rotational dynamic element matching (DEM) arrangement for receiving the plurality of signed binary data and the plurality of signed thermometer data. The rotational DEM arrangement further includes a first barrel shifter for receiving a positive thermometer data at a cycle, the first barrel shifter having a first pointer indicating a starting position of next positive thermometer data, and a second barrel shifter for receiving a negative thermometer data at a cycle, the second shifter having a second pointer indicating a starting position of next negative thermometer data, wherein the first pointer is circularly shifted as a function of positive binary data and the second pointer is circularly shifted as a function of negative binary data.

Owner:ANALOG DEVICES INC

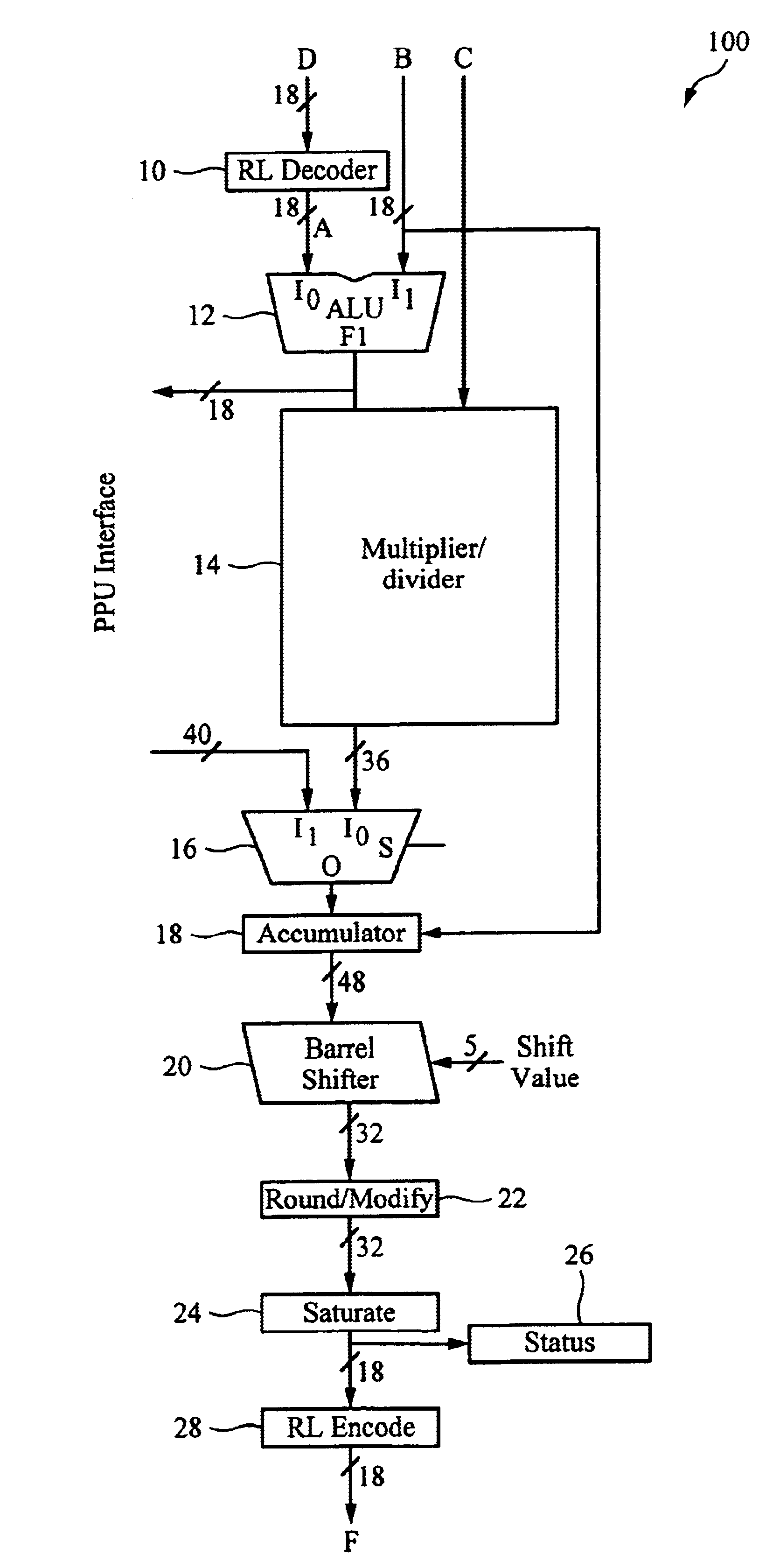

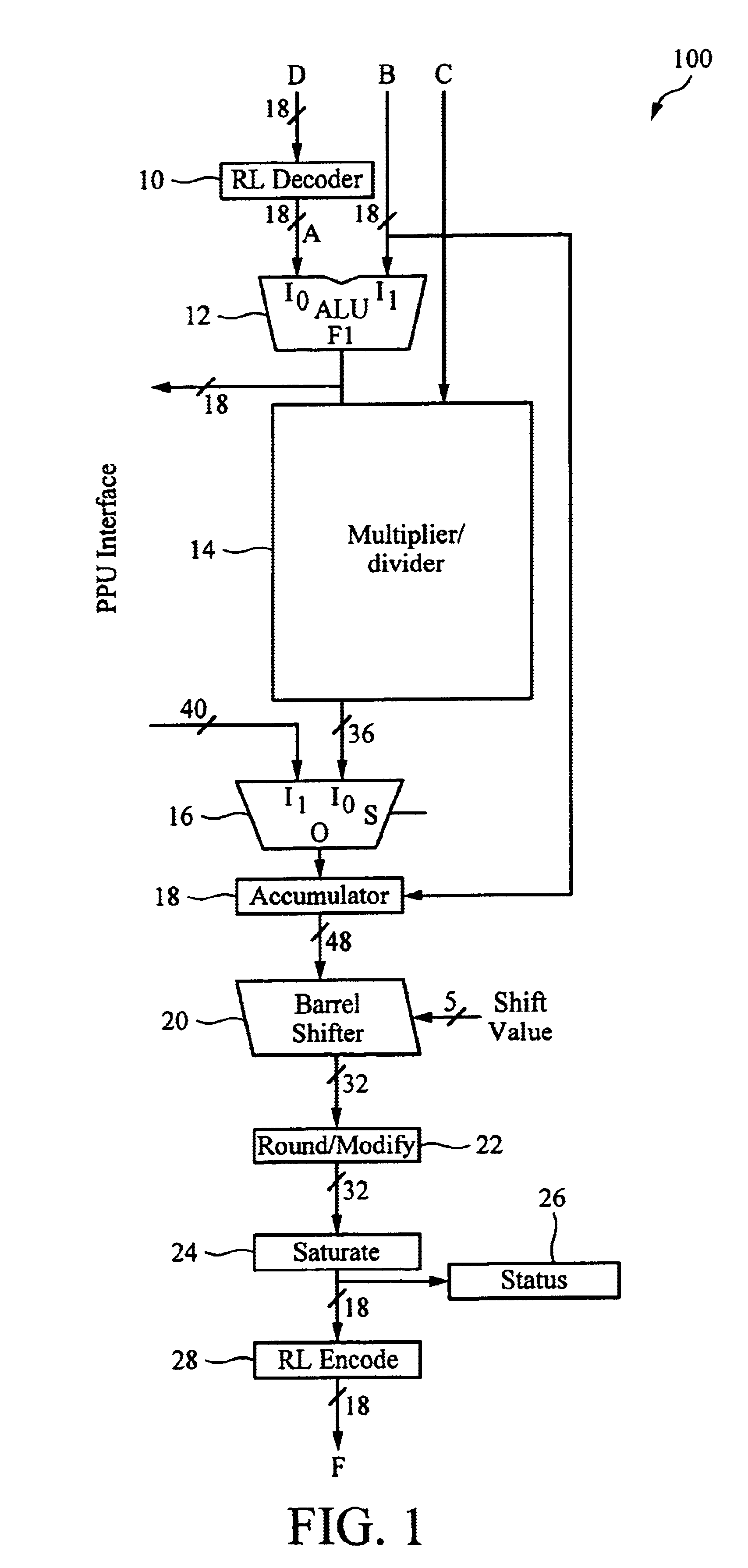

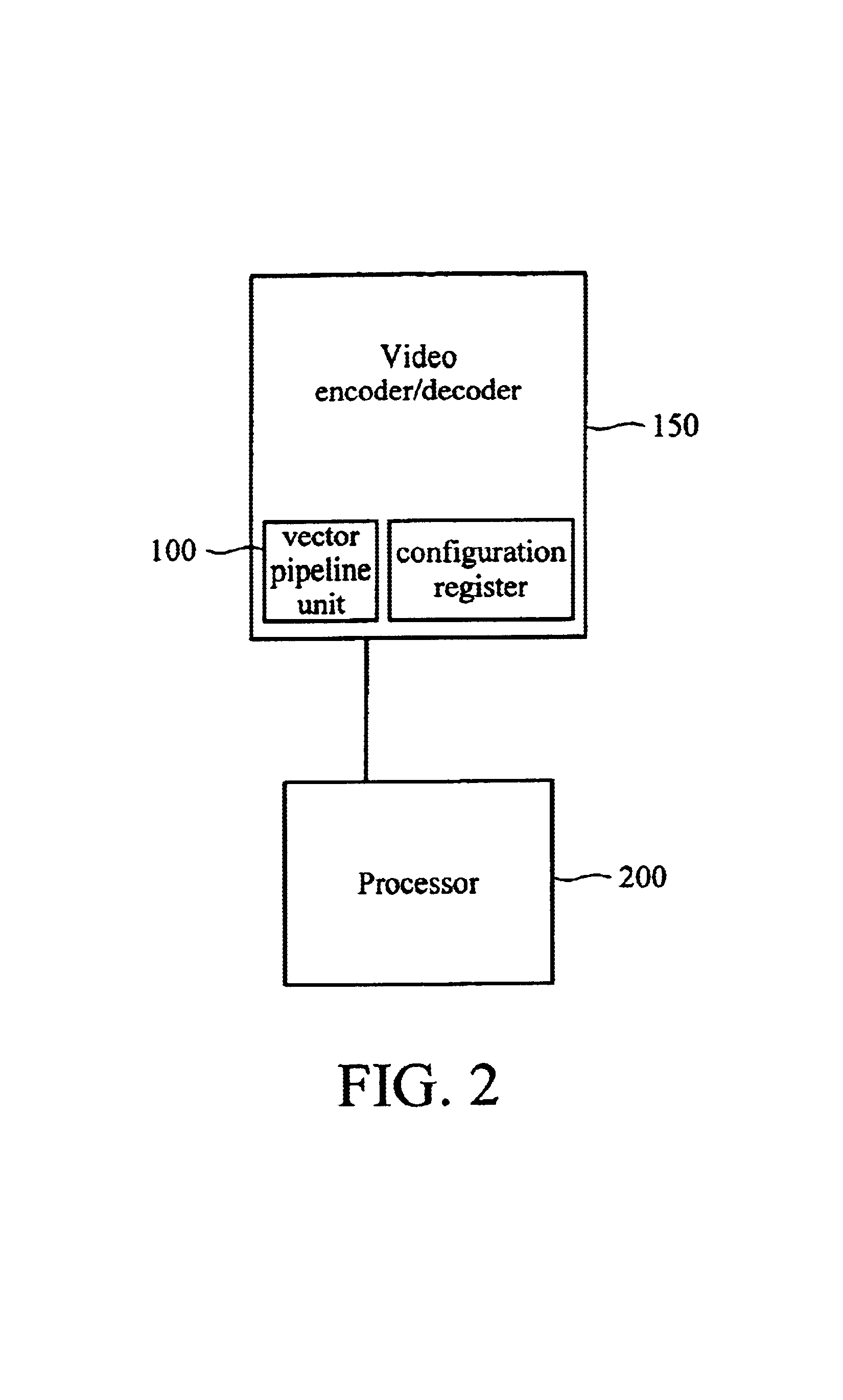

Processor architecture for compression and decompression of video and images

InactiveUS6909744B2Improve performanceReduce power consumptionColor television with pulse code modulationColor television with bandwidth reductionArithmetic logic unitBinary multiplier

A video encoder / decoder includes a vector pipeline unit and is configured only once by a processor to encode / decode data in accordance with any one of the JPEG, MPEG1, MPEG2 or MPEG4, H.261 or H.263 compression standards. The configuration data is stored in a configuration register of the video encoder / decoder. An optional ROM stores the configuration data for subsequent reading and loading—by the processor—into the configuration register. The vector pipeline unit includes: a run-length decoder, a binary arithmetic logic unit, a binary multiplier / divider, an accumulator, a barrel shifter, a round / modify unit, a saturate logic unit, a status register and a run-length encoder. Each component of the vector pipeline unit is optionally enabled or disabled. By disabling one or more components of the vector pipeline unit the power consumed by the encoder / decoder is reduced. The vector pipeline, after being configured continuously encodes / decodes vectors of data according to the configured standard, without requiring any additional configuration or software programming. The status register gathers statistical data on the saturated data and supplies the statistical data to the processor, thereby, further improving the performance of the video encode / decoder. The video encoder / decoder encodes / decodes data based on any other compression standard with additional configuration or software programming.

Owner:LUXXON CORP

Dedicated crossbar and barrel shifter block on programmable logic resources

ActiveUS8082526B2Reduce in quantityHardware savingDigital data processing detailsSolid-state devicesProgrammable logic deviceBarrel shifter

A dedicated hardware block is provided for implementing crossbars and / or barrel shifters in programmable logic resources. Crossbar and / or barrel shifter circuitry may replace one or more rows, one or more columns, one or more rectangles, or any combination thereof of programmable logic regions on a programmable logic resource. The functionality of the crossbar and / or barrel shifter circuitry can further be improved by implementing time-multiplexing.

Owner:ALTERA CORP

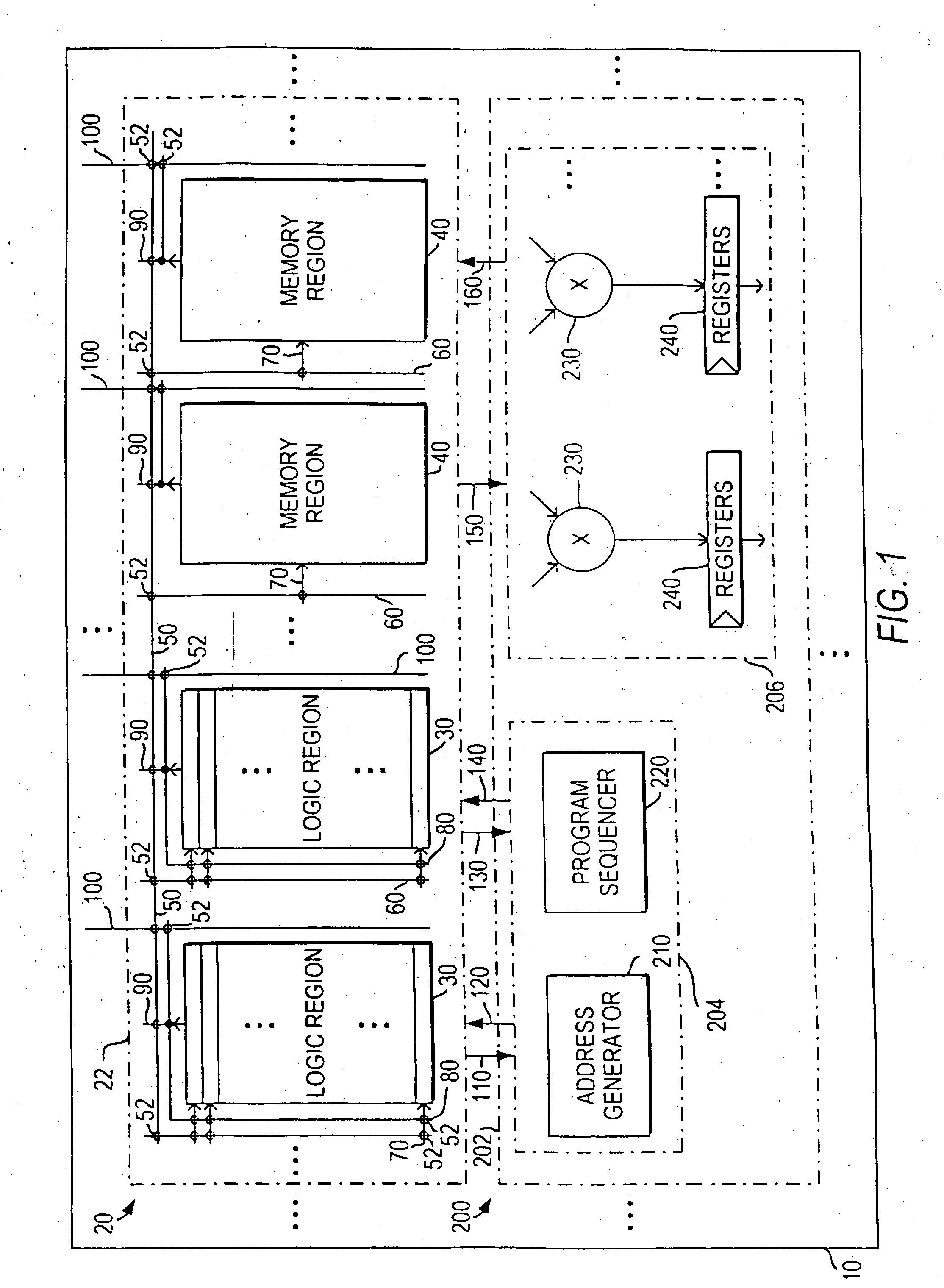

Programmable logic devices with function-specific blocks

InactiveUS20060218216A1Input reduce and evenReduce and even usabilityComputation using non-contact making devicesSemiconductor/solid-state device manufacturingGeneral purposeElectricity

Owner:LANGHAMMER MARTIN +1

System and method for area-efficient three-level dynamic element matching

ActiveUS20100149012A1Prominent effectEffective areaElectric signal transmission systemsDelta modulationThree levelData transformation

A system for converting digital signals into analog signals using sigma-delta modulation and includes a signed thermometer encoder for converting a plurality of signed binary data received at the encoder into a plurality of signed thermometer data and a rotational dynamic element matching (DEM) arrangement for receiving the plurality of signed binary data and the plurality of signed thermometer data. The rotational DEM arrangement further includes a first barrel shifter for receiving a positive thermometer data at a cycle, the first barrel shifter having a first pointer indicating a starting position of next positive thermometer data, and a second barrel shifter for receiving a negative thermometer data at a cycle, the second shifter having a second pointer indicating a starting position of next negative thermometer data, wherein the first pointer is circularly shifted as a function of positive binary data and the second pointer is circularly shifted as a function of negative binary data.

Owner:ANALOG DEVICES INC

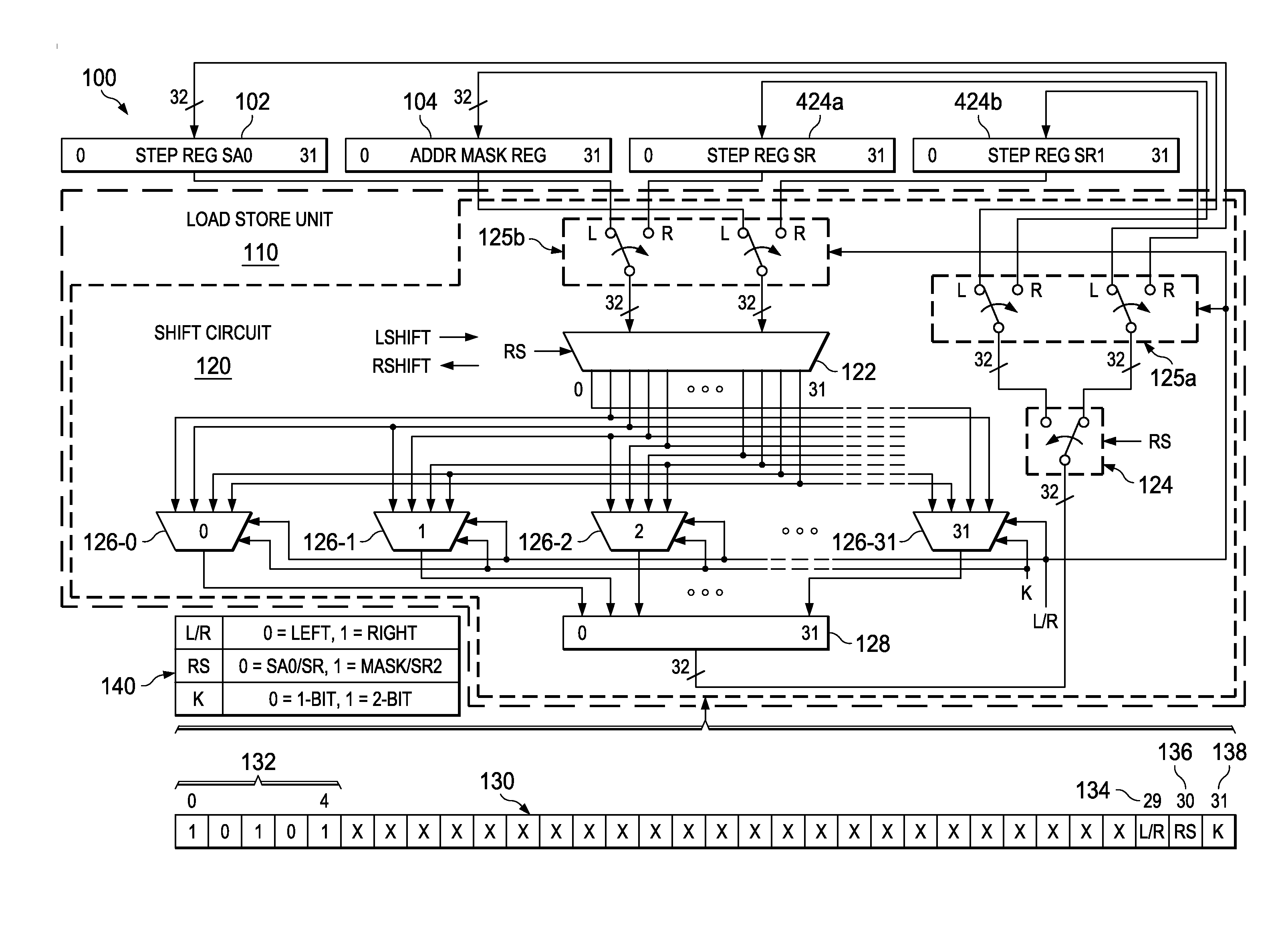

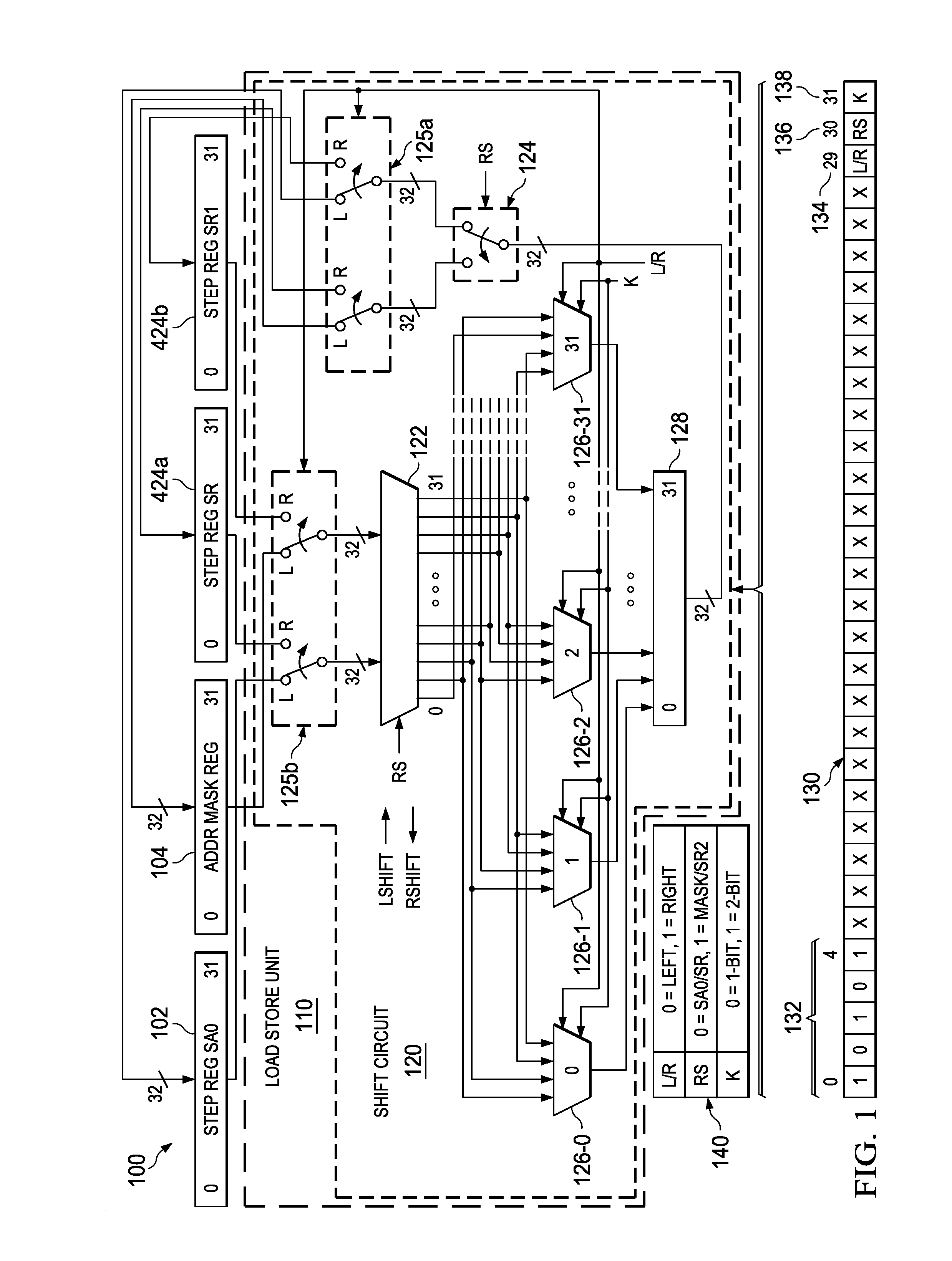

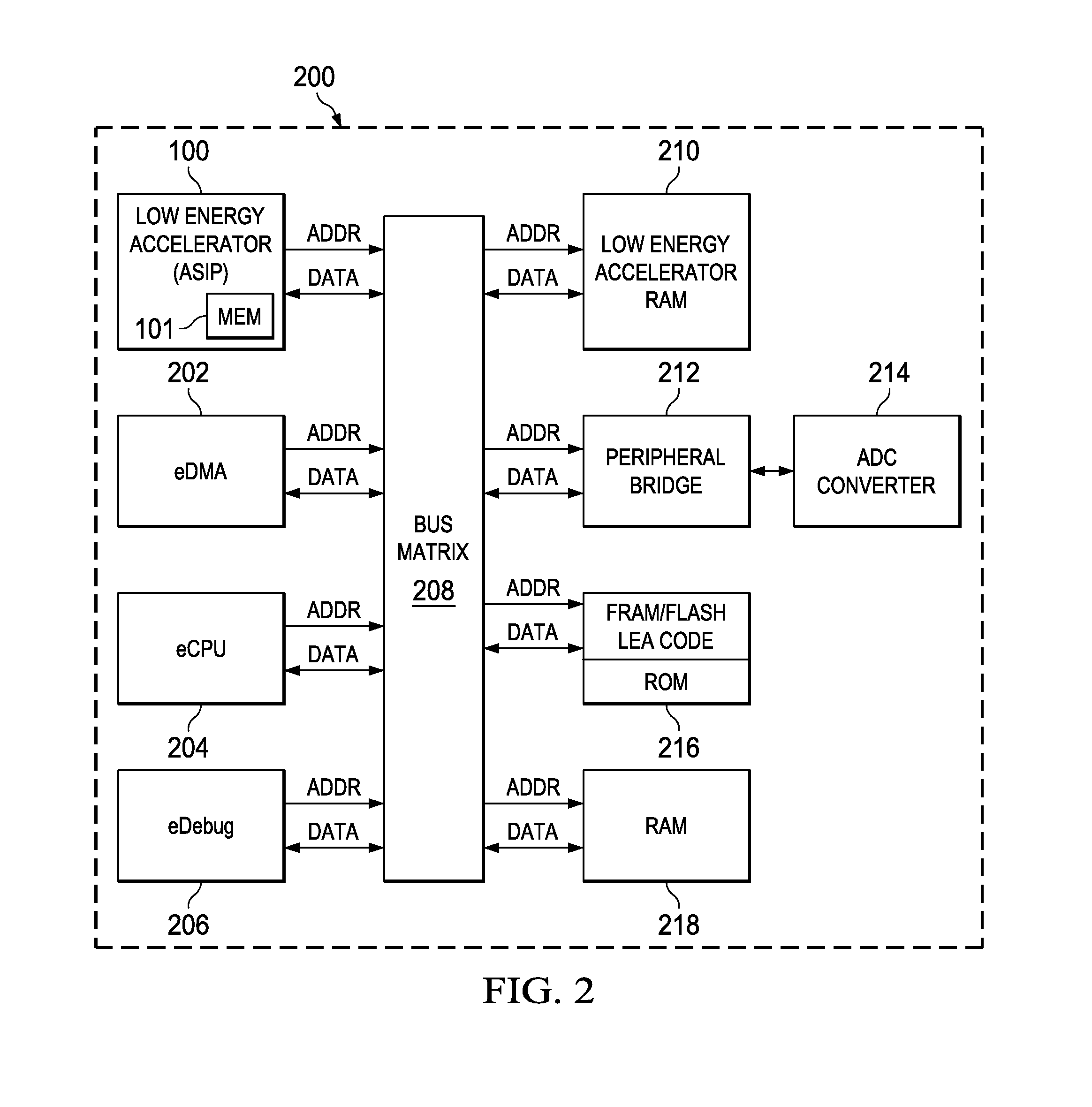

Load store circuit with dedicated single or dual bit shift circuit and opcodes for low power accelerator processor

PendingUS20170060586A1Without significant overheadEasy to operateRegister arrangementsEnergy efficient computingMicrocontrollerProcessor register

Described examples include integrated circuits such as microcontrollers with a low energy accelerator processor circuit or other application specific integrated processor circuit including a load store circuit operative to perform load and store operations associated with at least one register and a low gate count shift circuit to selectively shift the data of the register by only an integer number bits less than the register data width without using a barrel shifter for low power operation to support vector operations for FFT or filtering functions.

Owner:TEXAS INSTR INC

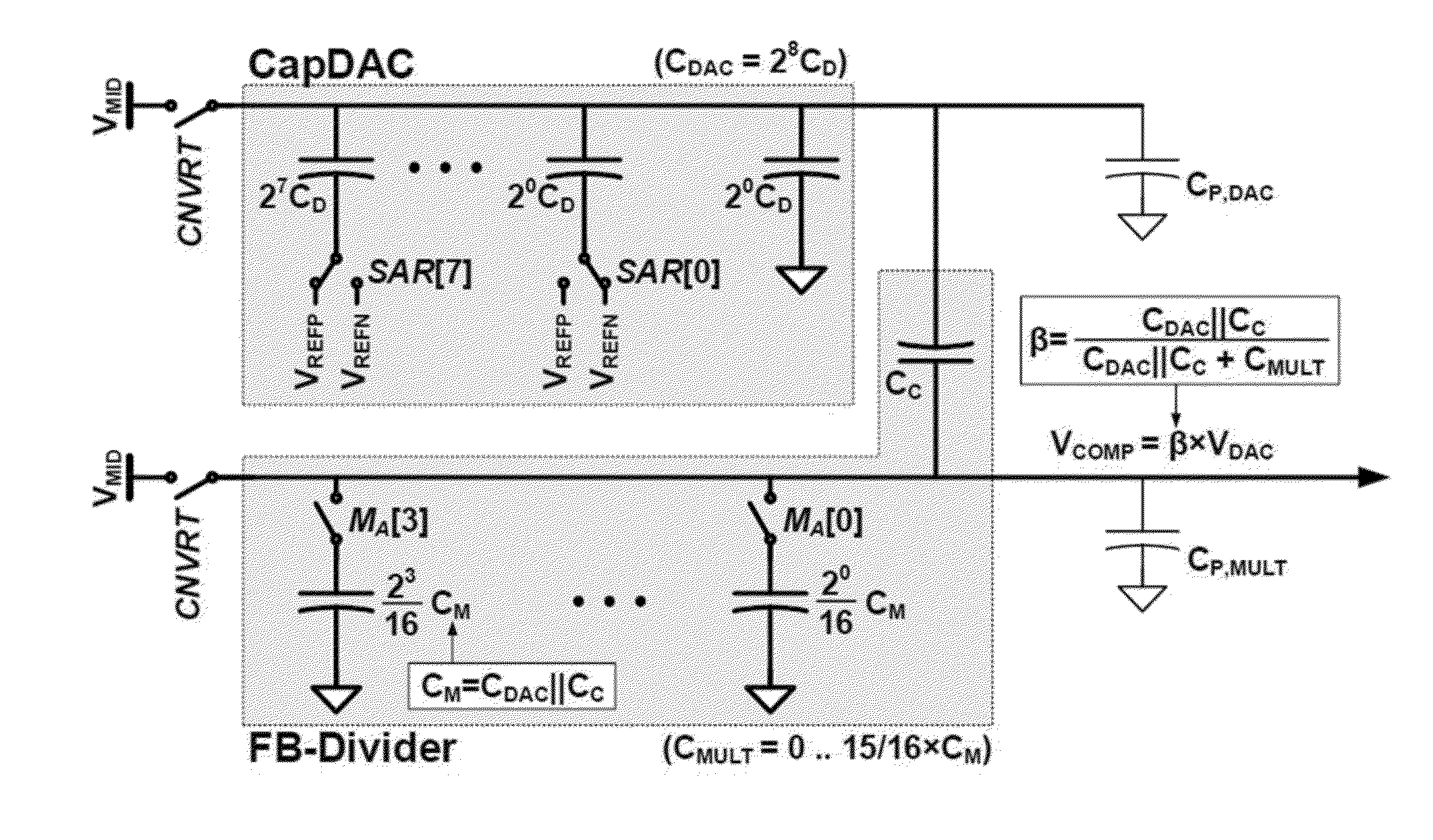

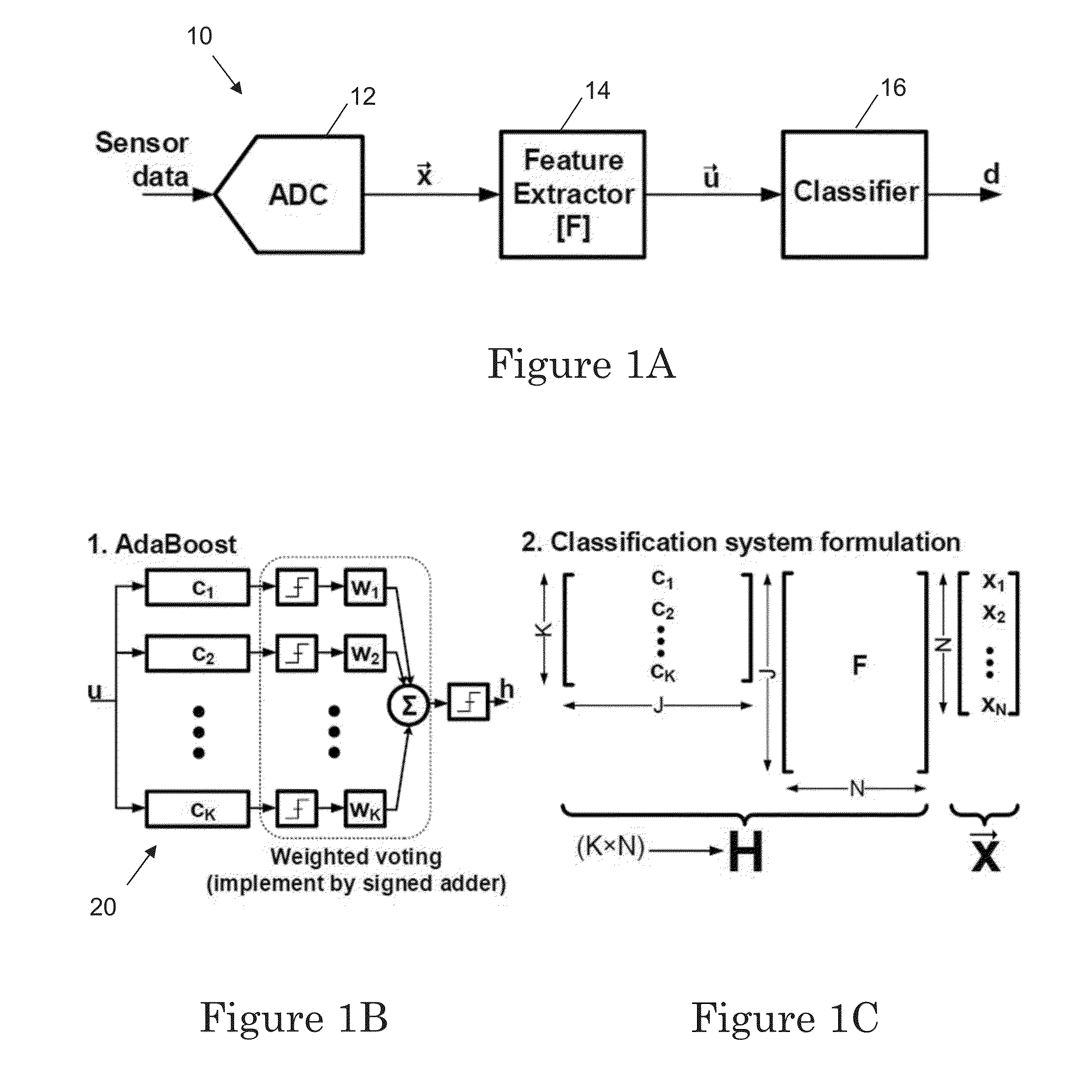

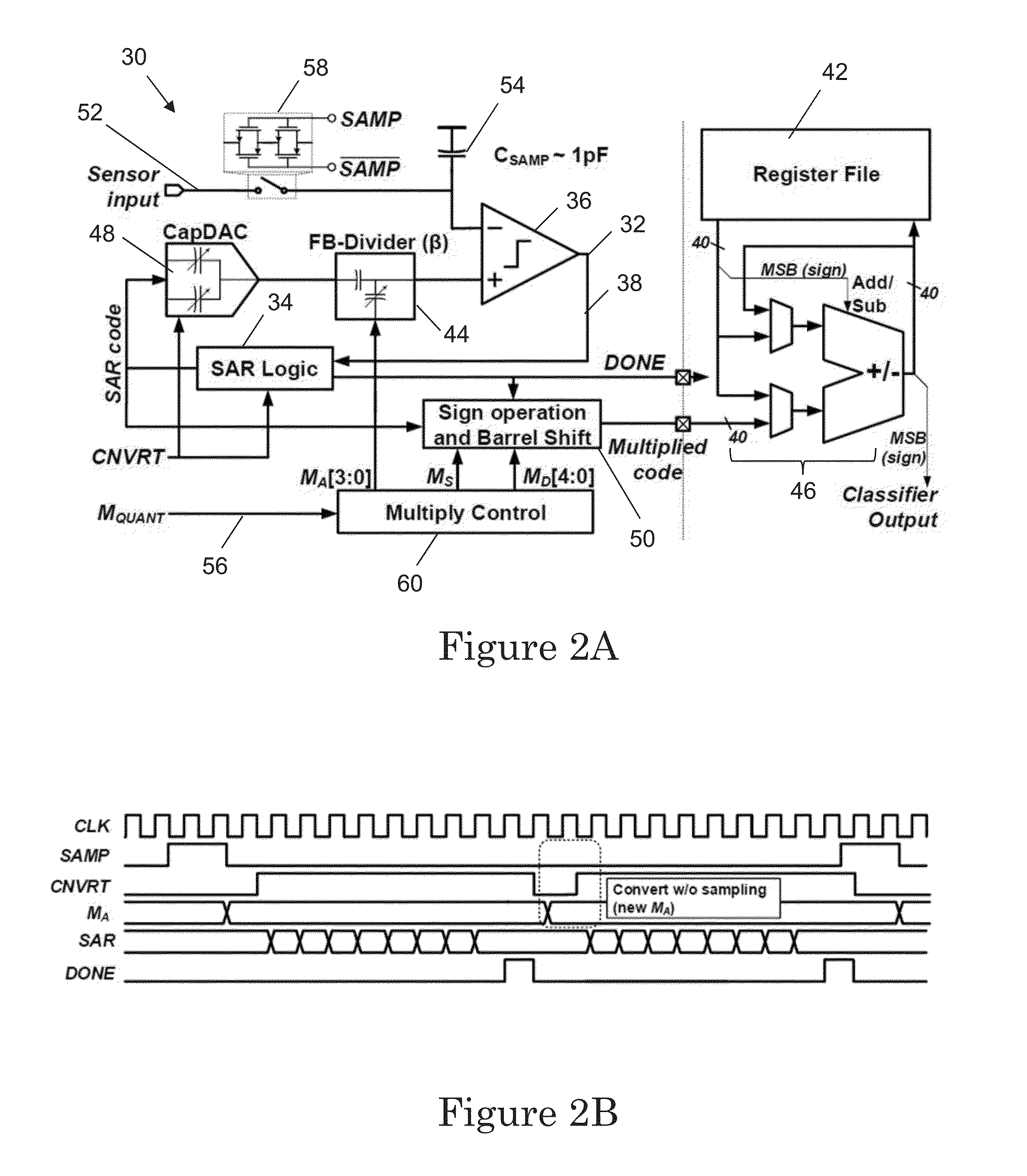

Multiplying analog to digital converter and method

ActiveUS20160248437A1Analogue/digital conversionElectric signal transmission systemsUltrasound attenuationCapacitive divider

A multiplying analog to digital converter (ADC) including a successive-approximation-register (SAR) analog to digital converter (ADC) having a sample input and a feedback input and an ADC output configured with a feedback path configured to couple the ADC output to a digital to analog converter. A feedback attenuator is disposed in the feedback path, the feedback attenuator being configured to attenuate a feedback signal coupled to the feedback input, the feedback attenuator being configured to provide analog multiplication observed at the ADC output. A barrel shifter is configured to provide digital multiplication of the ADC output. The feedback attenuator may be configured as a divider network. The feedback attenuator may be configured to provide attenuation using only passive components. The feedback attenuator may be configured as a capacitive divider network. The feedback attenuator may be configured to provide attenuation ranging between 1 and 0.5.

Owner:THE TRUSTEES FOR PRINCETON UNIV

Circuitry for arithmetically accumulating a succession of arithmetic values

InactiveUS7024446B2Reduce the impactInput reduce and evenComputation using non-contact making devicesSemiconductor/solid-state device manufacturingGeneral purposeElectricity

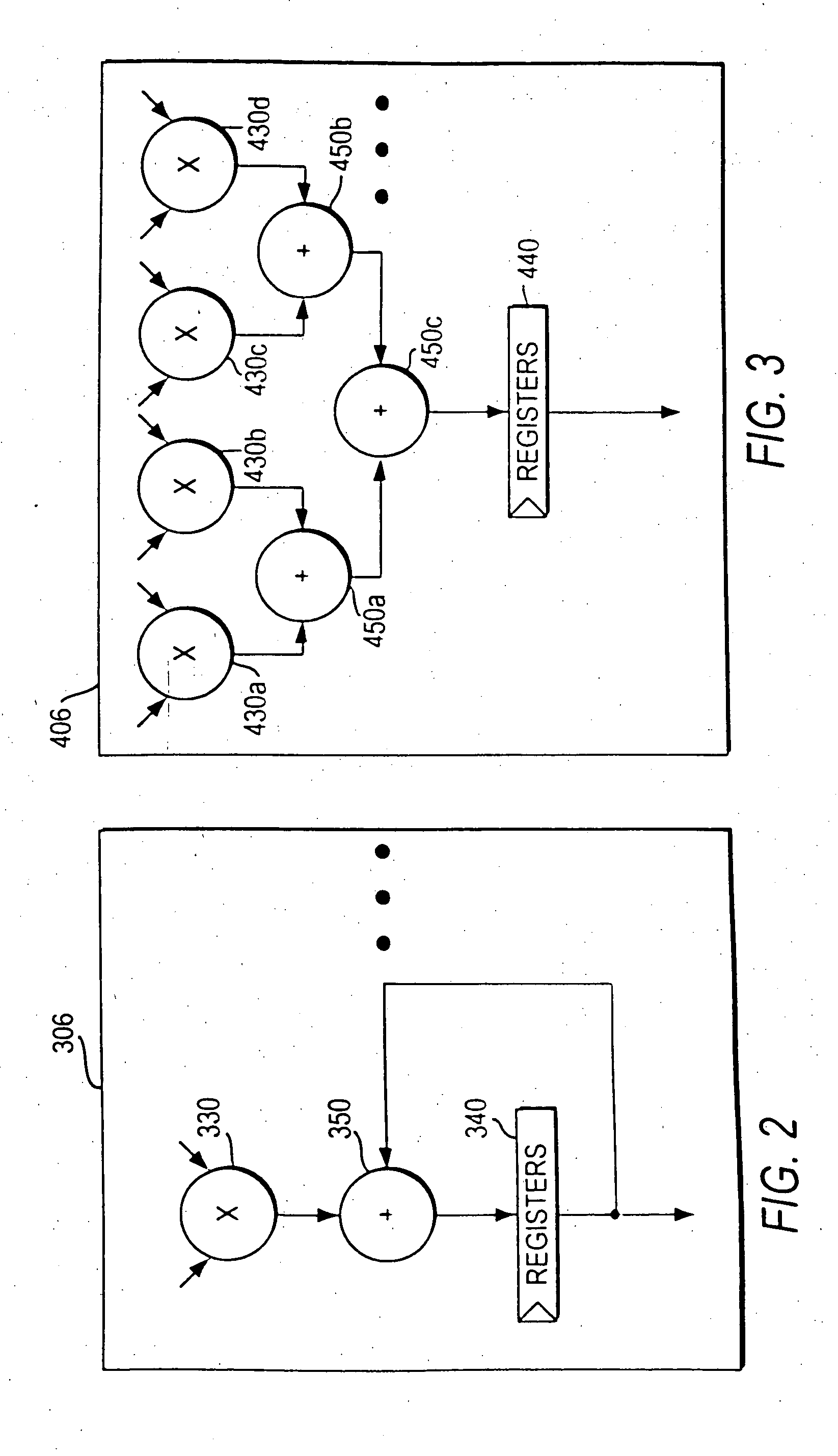

A programmable logic integrated circuit device has at least one function-specific circuit block (e.g., a parallel multiplier, a parallel barrel shifter, a parallel arithmetic logic unit, etc.) in addition to the usual multiple regions of programmable logic and the usual programmable interconnection circuit resources. To reduce the impact of use of the function-specific block (“FSB”) on the general purpose interconnection resources of the device, inputs and / or outputs of the FSB may be coupled relatively directly to a subset of the logic regions. In addition to conserving general purpose interconnect, resources of the logic regions to which the FSB are connected can be used by the FSB to reduce the amount of circuitry that must be dedicated to the FSB. If the FSB is a multiplier, additional features include facilitating accumulation of successive multiplier outputs (using either addition or subtraction and with sign extension if desired) and / or arithmetically combining the outputs of multiple multipliers.

Owner:ALTERA CORP

Request arbitration in multi-core processor

ActiveUS7133950B2Memory adressing/allocation/relocationConcurrent instruction executionProcessing coreLogic gate

Owner:ORACLE INT CORP

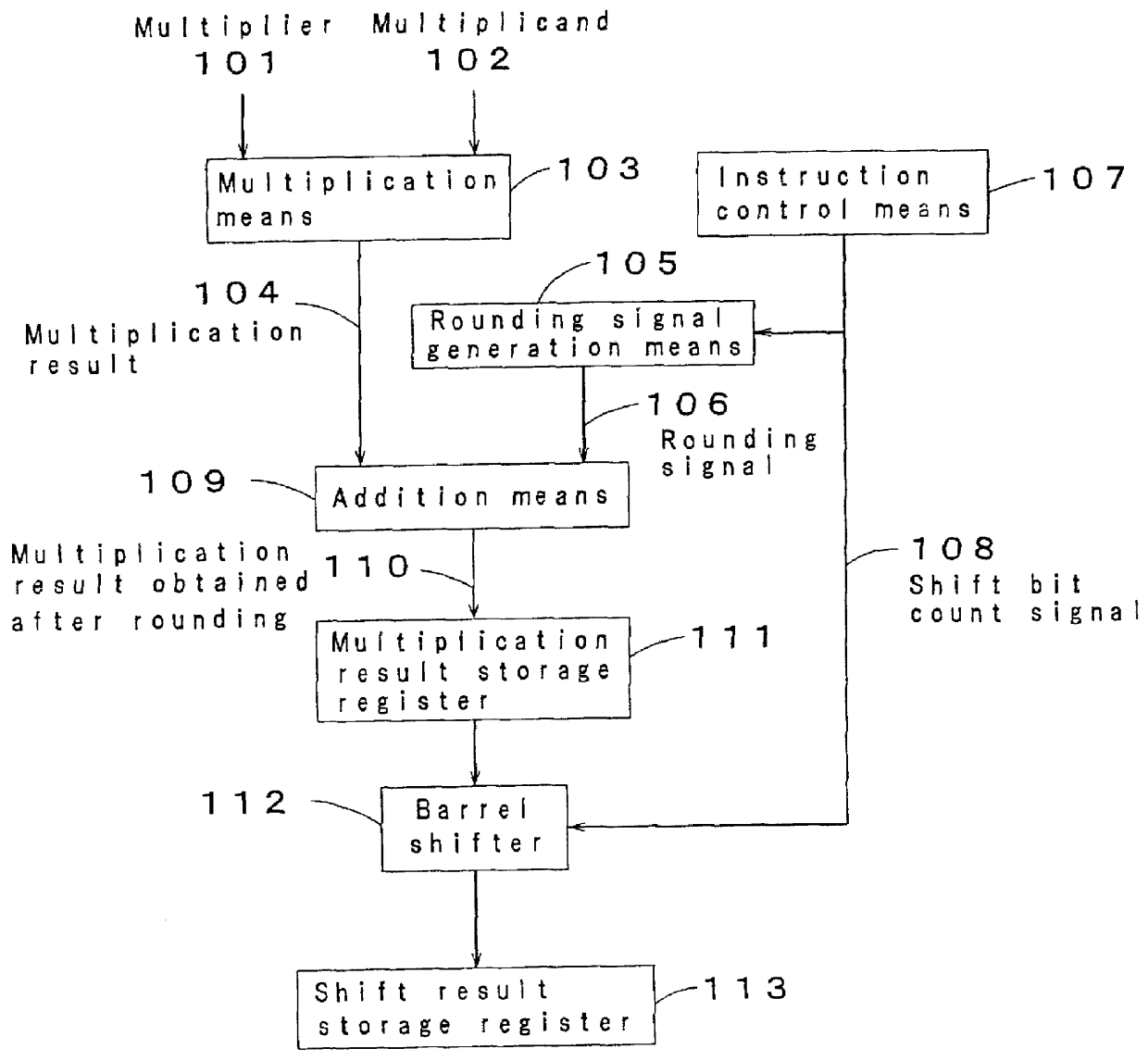

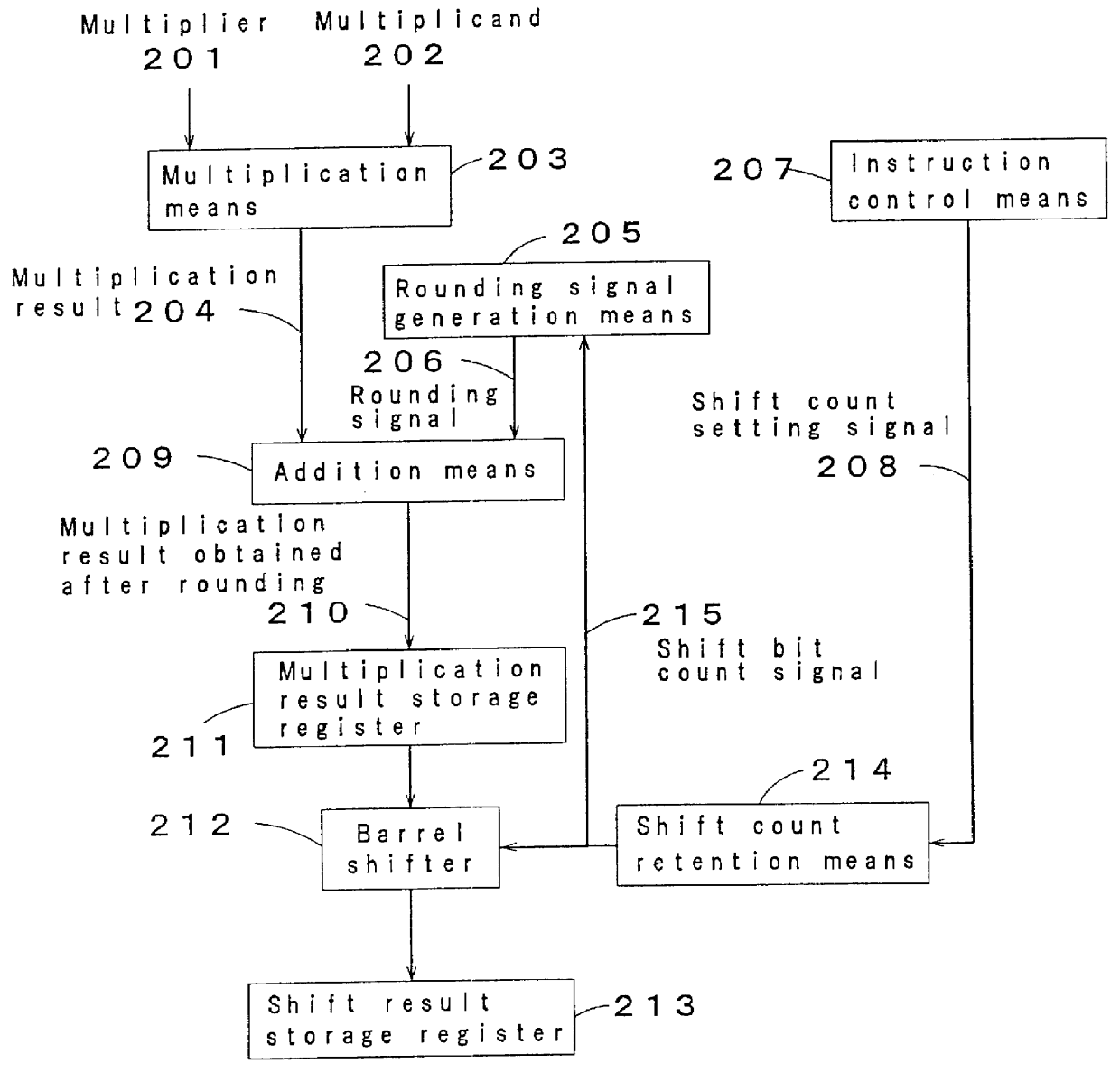

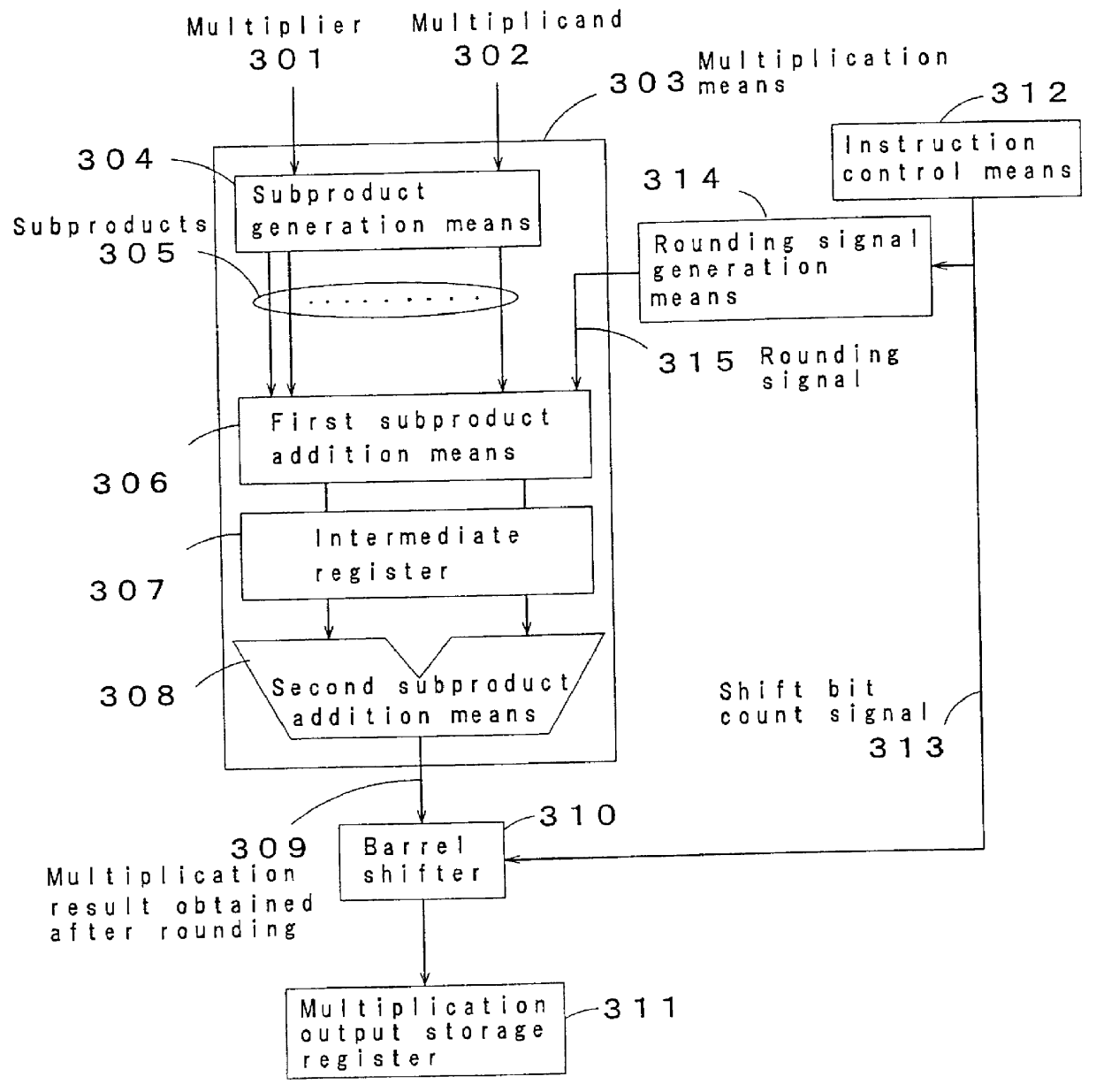

Multiplication method and multiplication circuit

InactiveUS6167419AAvoid throughputHigh speed machiningComputation using non-contact making devicesData conversionGeneration processProcessor register

A multiplication method and a multiplication circuit, wherein a multiplicand is multiplied by a multiplier using a multiplication process, the result of the multiplication is added by an addition process to a rounding signal to be output from a rounding signal generation process, and the result of the addition, i.e., a multiplication result obtained after rounding, is stored in a register. By a barrel shifter, the multiplication result obtained after rounding stored in the register is shifted by a bit count indicated by a shift bit count signal. The shift bit count signal output from an instruction control process is input to the barrel shifter and a rounding signal generation process. The rounding signal generation process generates a rounding signal on the basis of the shift bit count signal indicating the bit count used to shift the multiplication result after rounding. By carrying out a rounding process in the addition process by using the rounding signal, the rounding process can be carried out at an appropriate position desired by the user without increasing instruction code or storage.

Owner:PANASONIC CORP

Electronic data shift device, in particular for coding/decoding with an LDPC code

The electronic shift device includes N inputs and N outputs, a configurable barrel shifter connected between the N inputs and the N outputs. A second shifter is arranged and connected between some of the outputs of the barrel shifter and some of the N outputs according to different predetermined organizations of data that can be received simultaneously on at least some of the N inputs. The second shifter is configurable so that, for a relevant organization and regardless of the desired shift value compatible with the organization, the corresponding input data are delivered to predetermined outputs. A first controller is able to configure the barrel shifter according to the desired shift value and a second controller is able to configure the second shifter according to the organization of the data that can actually be received and according to the desired shift value.

Owner:STMICROELECTRONICS SRL

Shuffled LDPC decoding

An LDPC decoder iteratively decodes an LDPC code represented by a parity check matrix H consisting of a plurality of circulants based on a Log-Likelihood Ratio Belief-Propagation algorithm. First computation means (1010) compute for a next iteration symbol messages λκm from a representation of a corresponding symbol value stored in a first memory 1005 and from check node messages Λmn from a previous iteration. A shuffler (1030) changes a sequence of the symbol message received from the first computation means (1010) in dependence on a position of the non-zero elements in a corresponding sub-matrix. Second computation means (DP-O, DP-I, DP-D-I) compute the check node messages in dependence on symbol messages received from the barrel shifter and store a representation of the computed check node message in a second memory (1015). Third computation means (1020) update the representation of the symbol values in the first memory in dependence on output of the first and second computing means. The principle of “staggered” or “shuffled” LDPC decoding is used. One embodiment is designed for multi-diagonal circulants.

Owner:ST ERICSSON SA

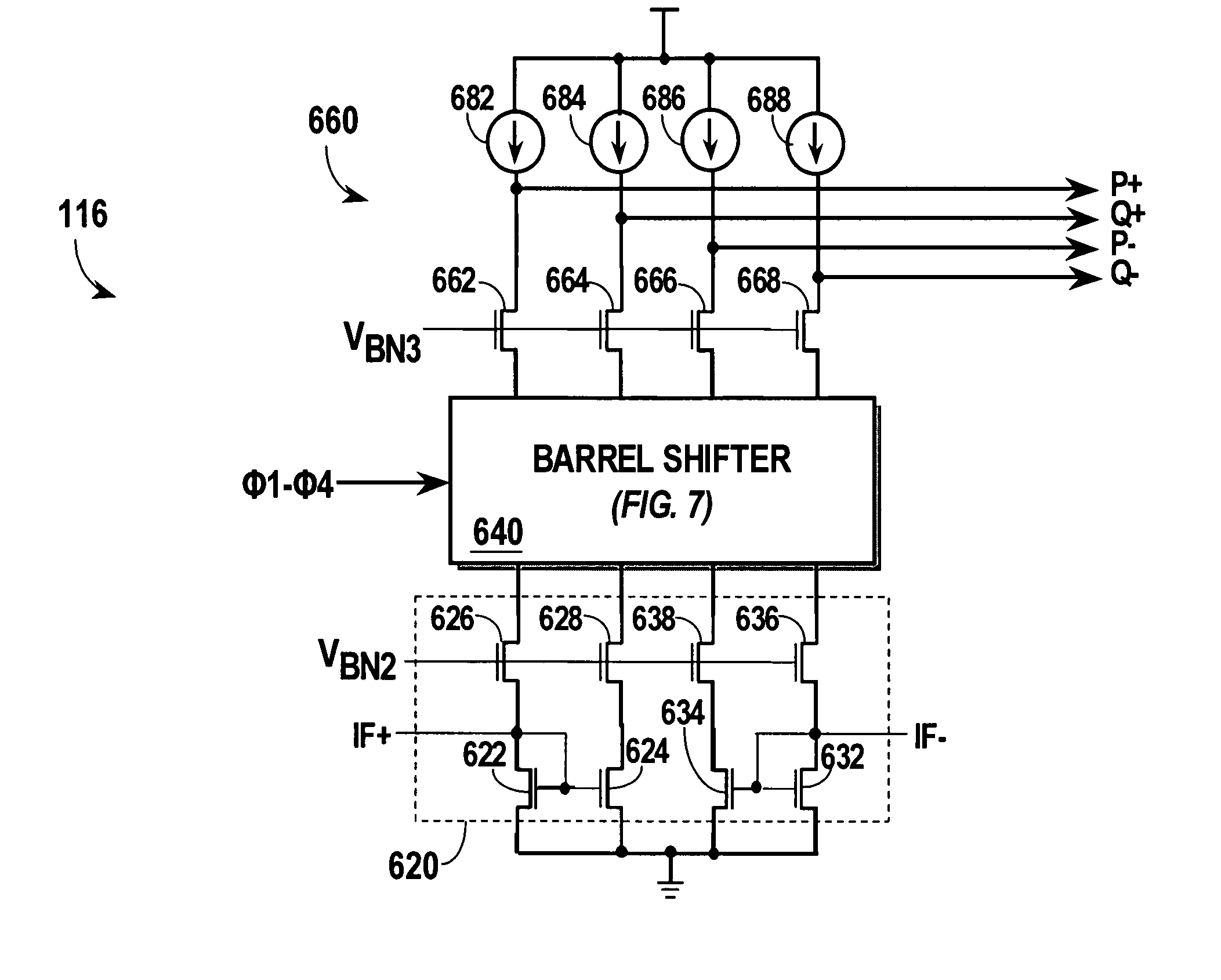

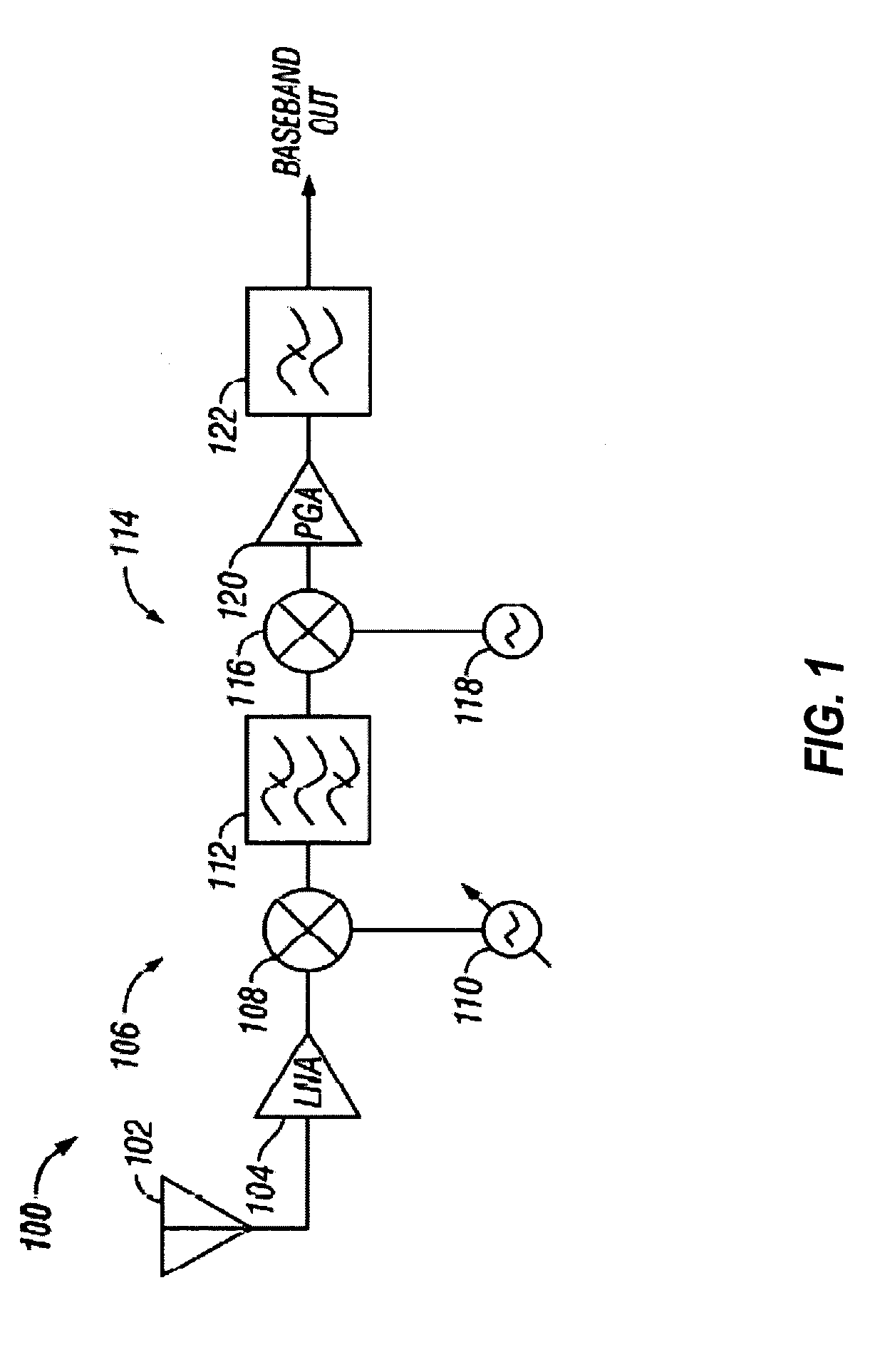

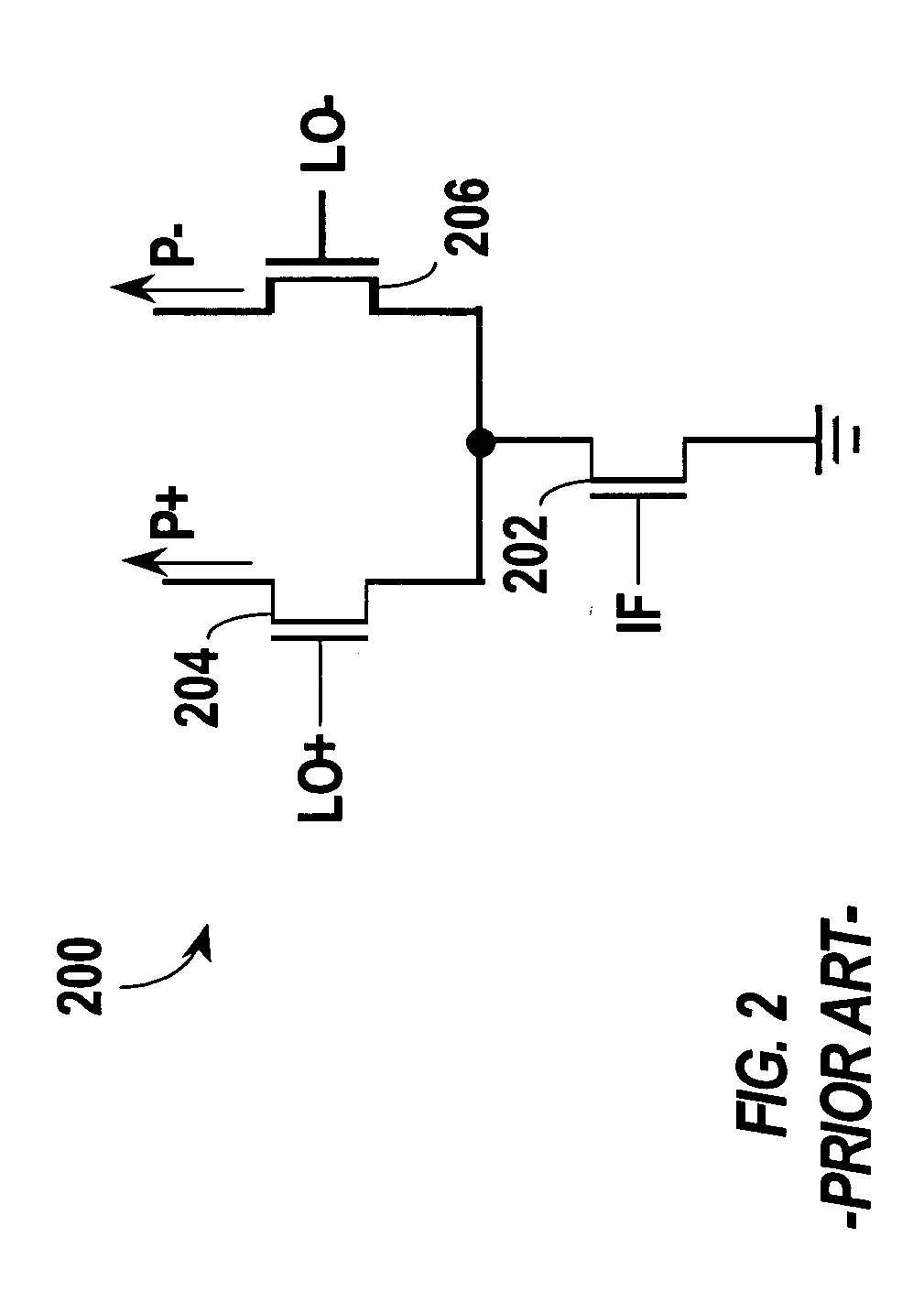

Low distortion quadrature mixer and method therefor

ActiveUS20050266821A1Modulation transference balanced arrangementsTransmissionAudio power amplifierLow distortion

A mixer (114) includes an input amplifier (620) and a barrel shifter (640). The input amplifier (620) has an input for receiving an input signal, and first through fourth output terminals respectively providing first through fourth current signals. The barrel shifter (640) has first through fourth input terminals for respectively receiving the first through fourth current signals, first through fourth control terminals for respectively receiving first through fourth clock signals, and first through fourth output terminals for respectively providing positive and negative in-phase output signals and positive and negative quadrature output signals.

Owner:XENOGENIC DEV LLC