Load store circuit with dedicated single or dual bit shift circuit and opcodes for low power accelerator processor

a storage circuit and accelerator processor technology, applied in the field of electronic processor circuits, can solve problems such as limiting computational performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013]In the drawings, like reference numerals refer to like elements throughout, and the various features are not necessarily drawn to scale. In the following discussion and in the claims, the terms “including”, “includes”, “having”, “has”, “with”, or variants thereof are intended to be inclusive in a manner similar to the term “comprising”, and thus should be interpreted to mean “including, but not limited to . . . ” Also, the term “couple” or “couples” is intended to include indirect or direct electrical connection or combinations thereof. For example, if a first device couples to or is coupled with a second device, that connection may be through a direct electrical connection, or through an indirect electrical connection via one or more intervening devices and connections.

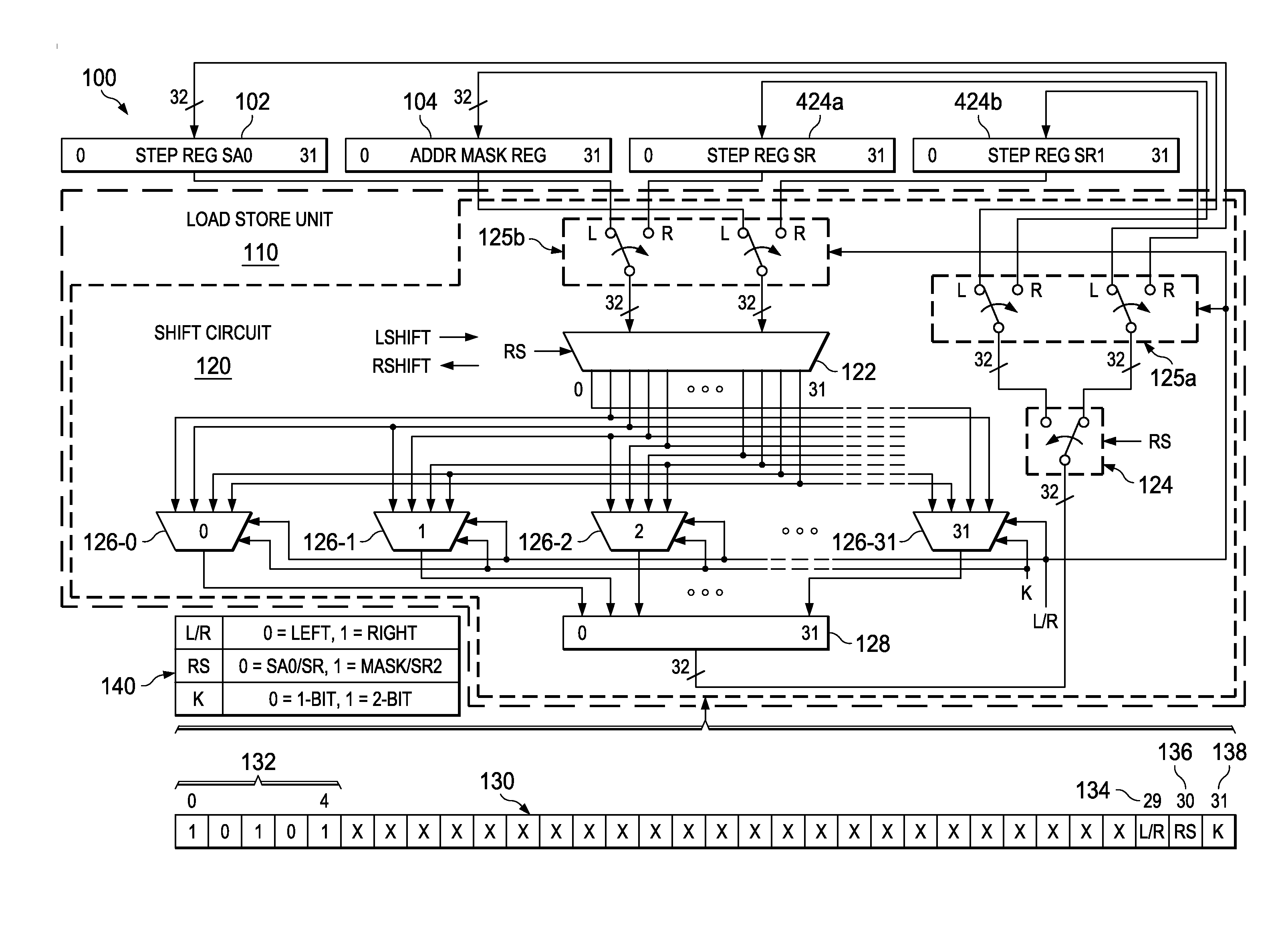

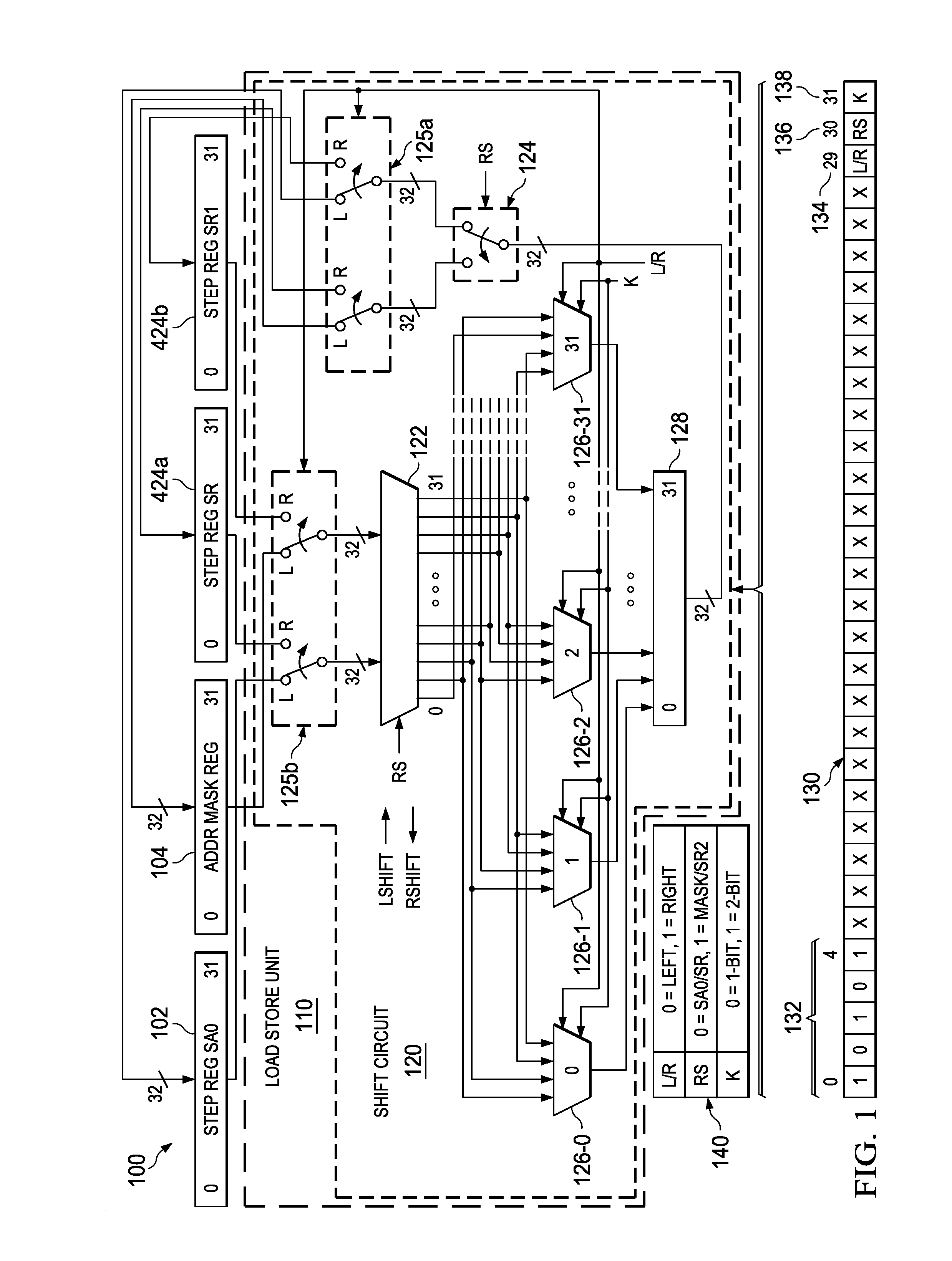

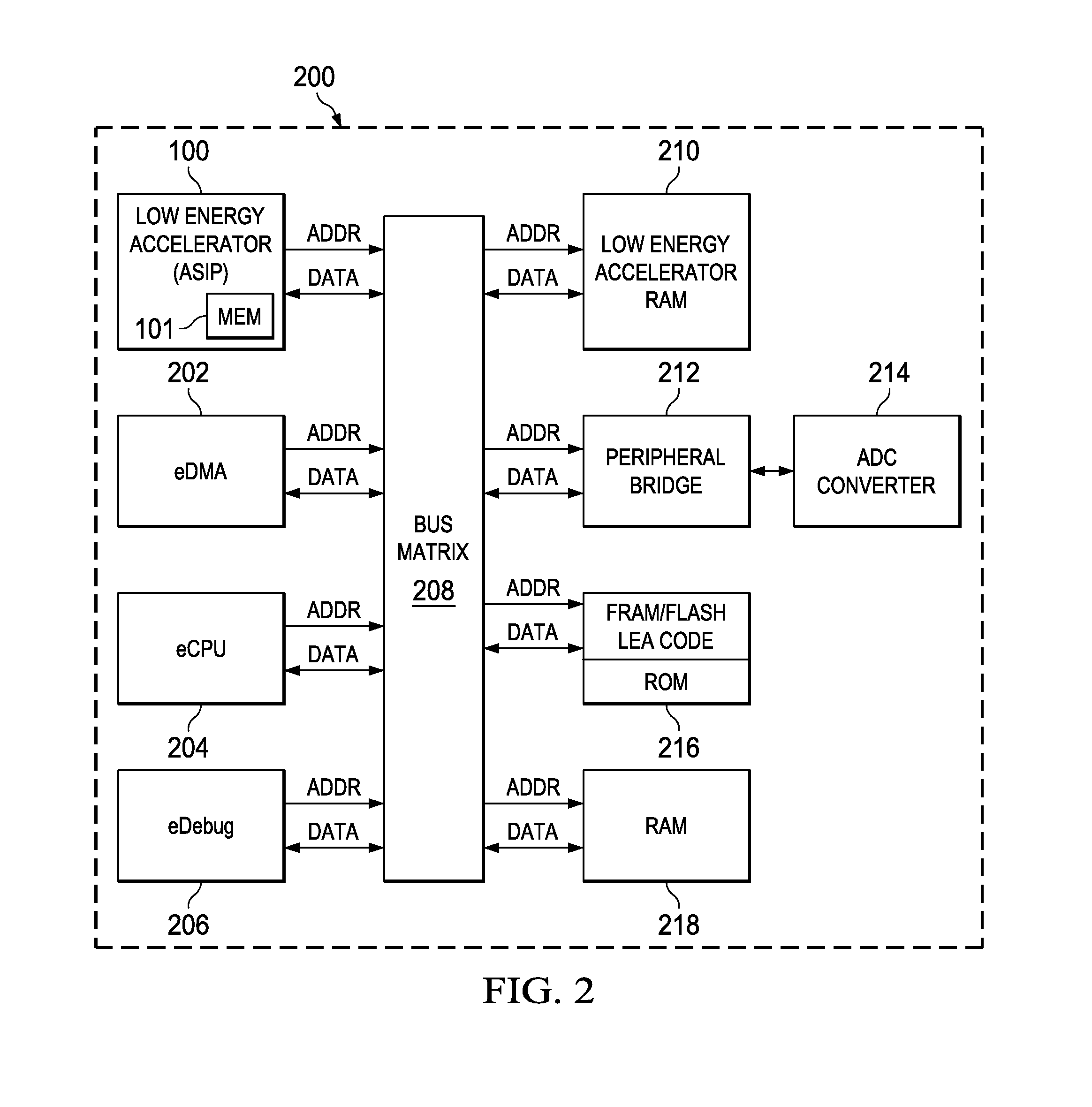

[0014]FIGS. 1 and 2 show a microcontroller unit (MCU) 200 which can be a single integrated circuit (IC) 200 in one example. Certain example implementations include analog interface circuitry such as analog to d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More