Patents

Literature

107 results about "Registered memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

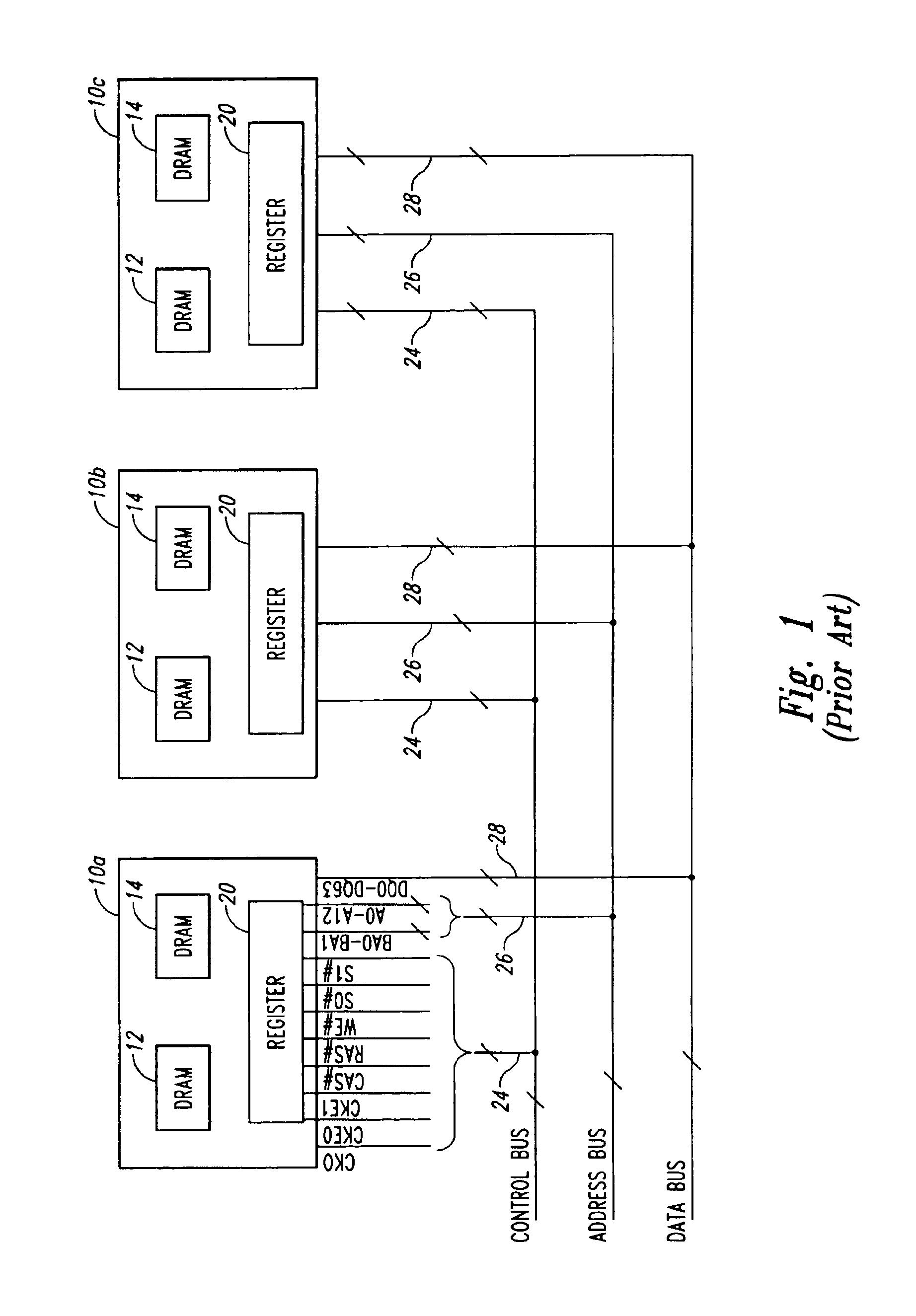

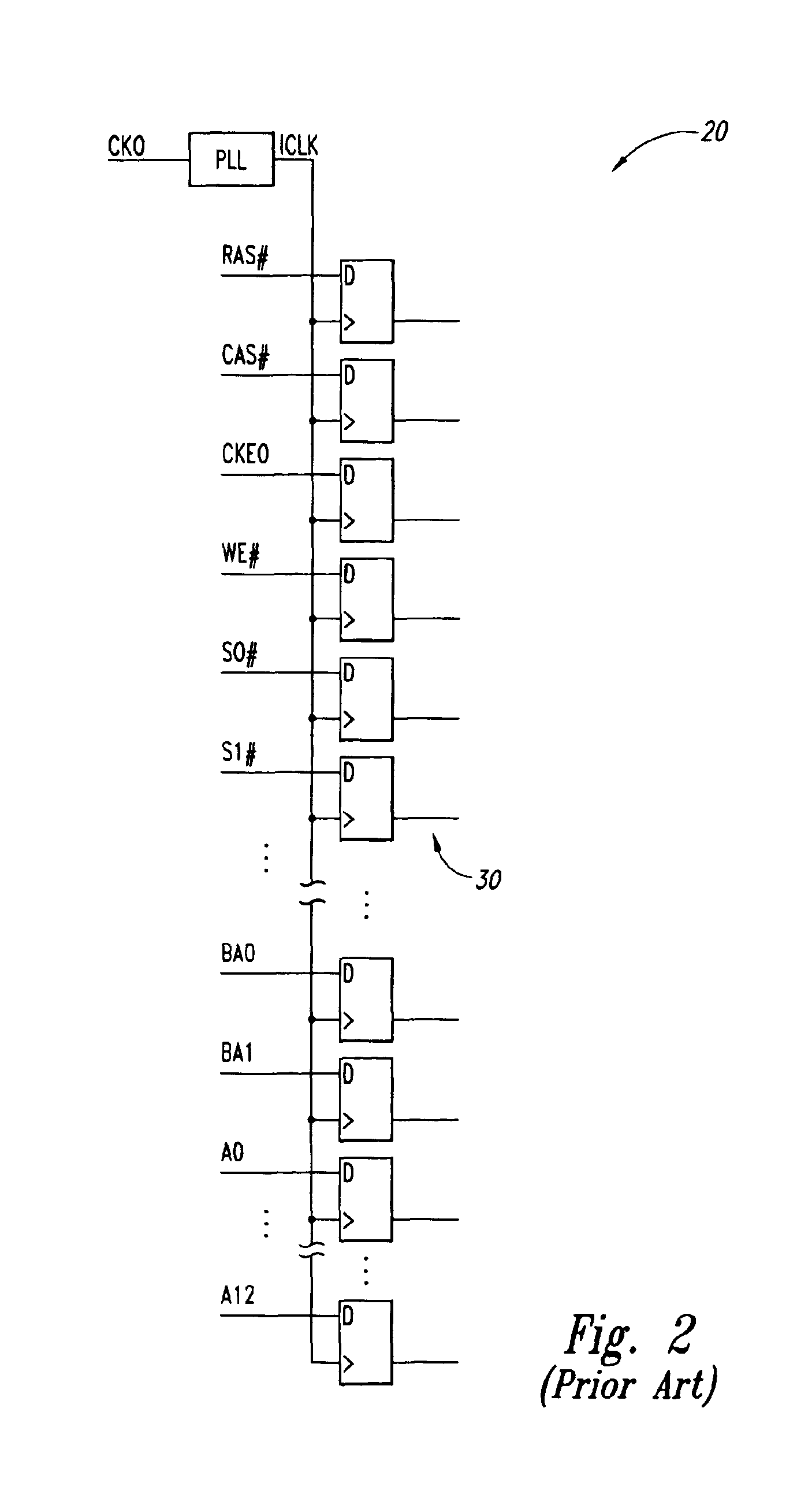

Registered (also called buffered) memory modules have a register between the DRAM modules and the system's memory controller. They place less electrical load on the memory controller and allow single systems to remain stable with more memory modules than they would have otherwise. When compared with registered memory, conventional memory is usually referred to as unbuffered memory or unregistered memory. When manufactured as a dual in-line memory module (DIMM), a registered memory module is called an RDIMM, while unregistered memory is called UDIMM or simply DIMM.

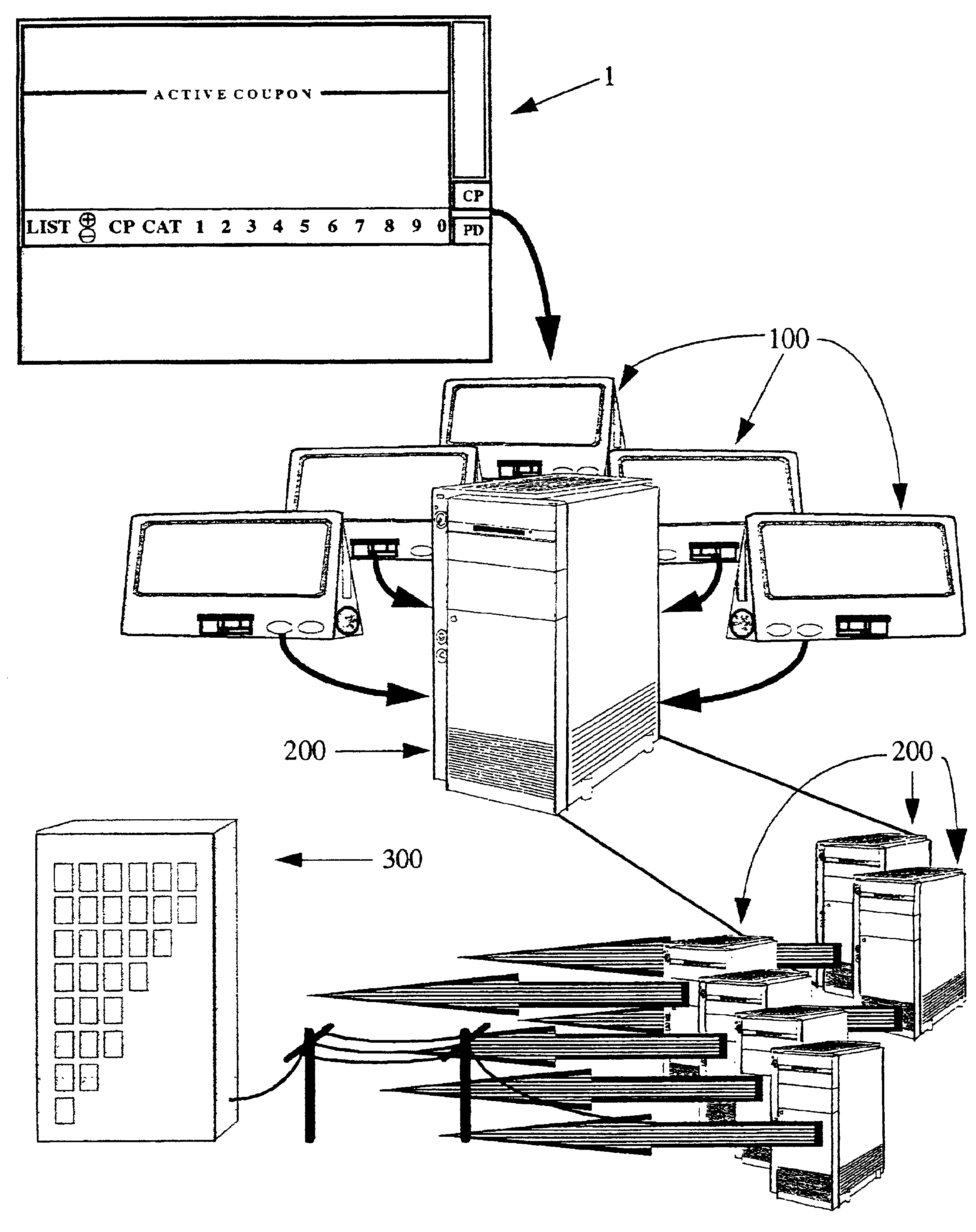

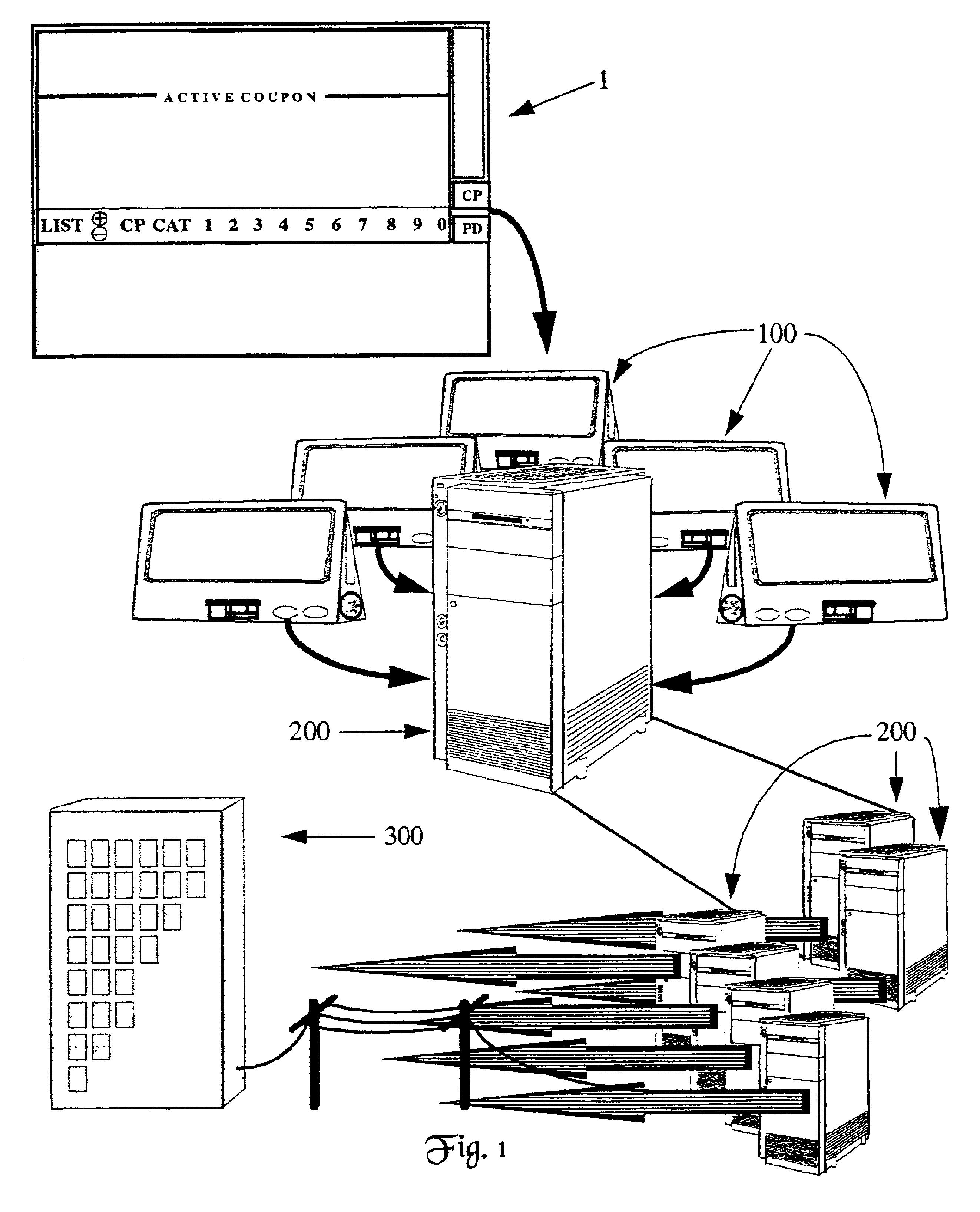

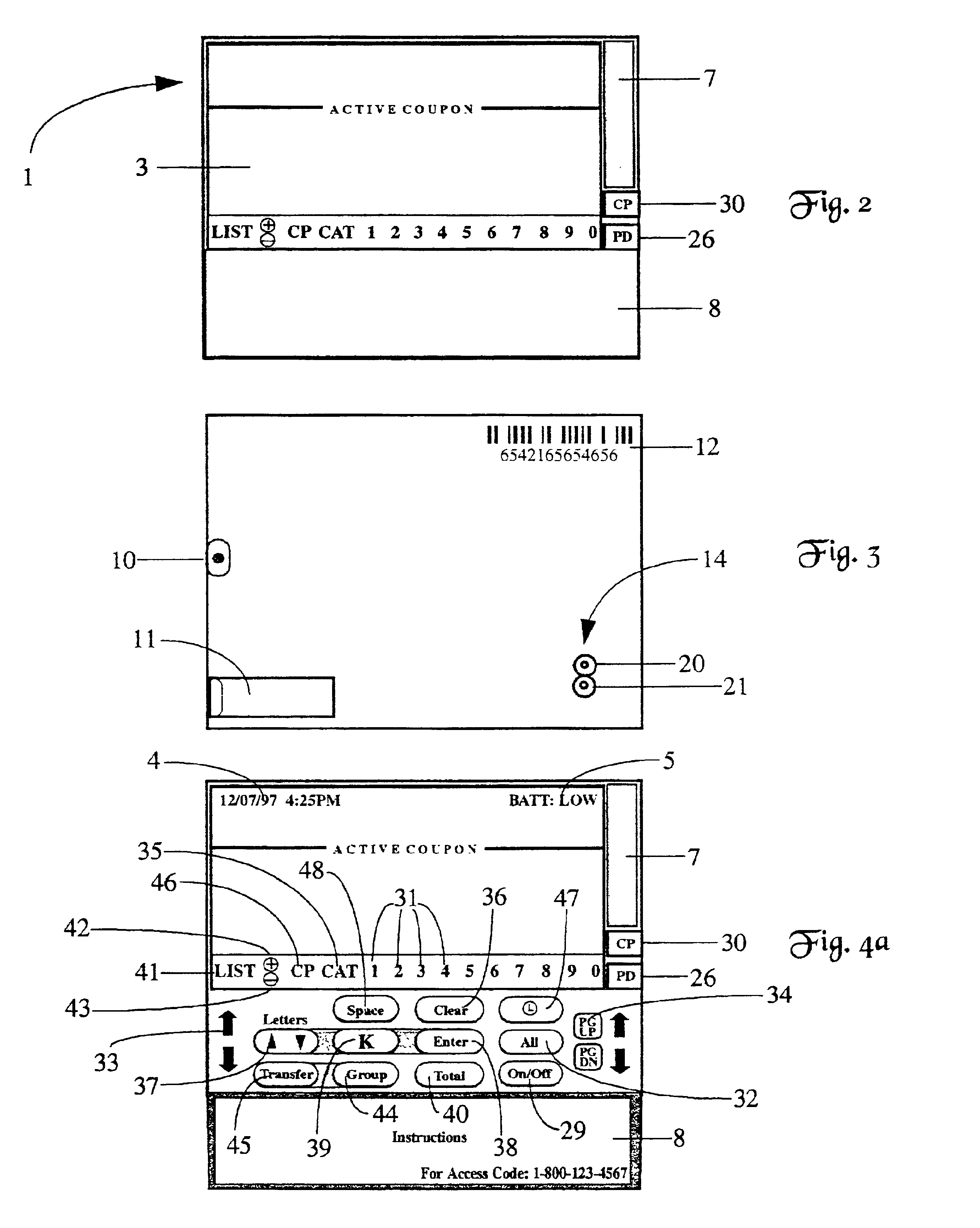

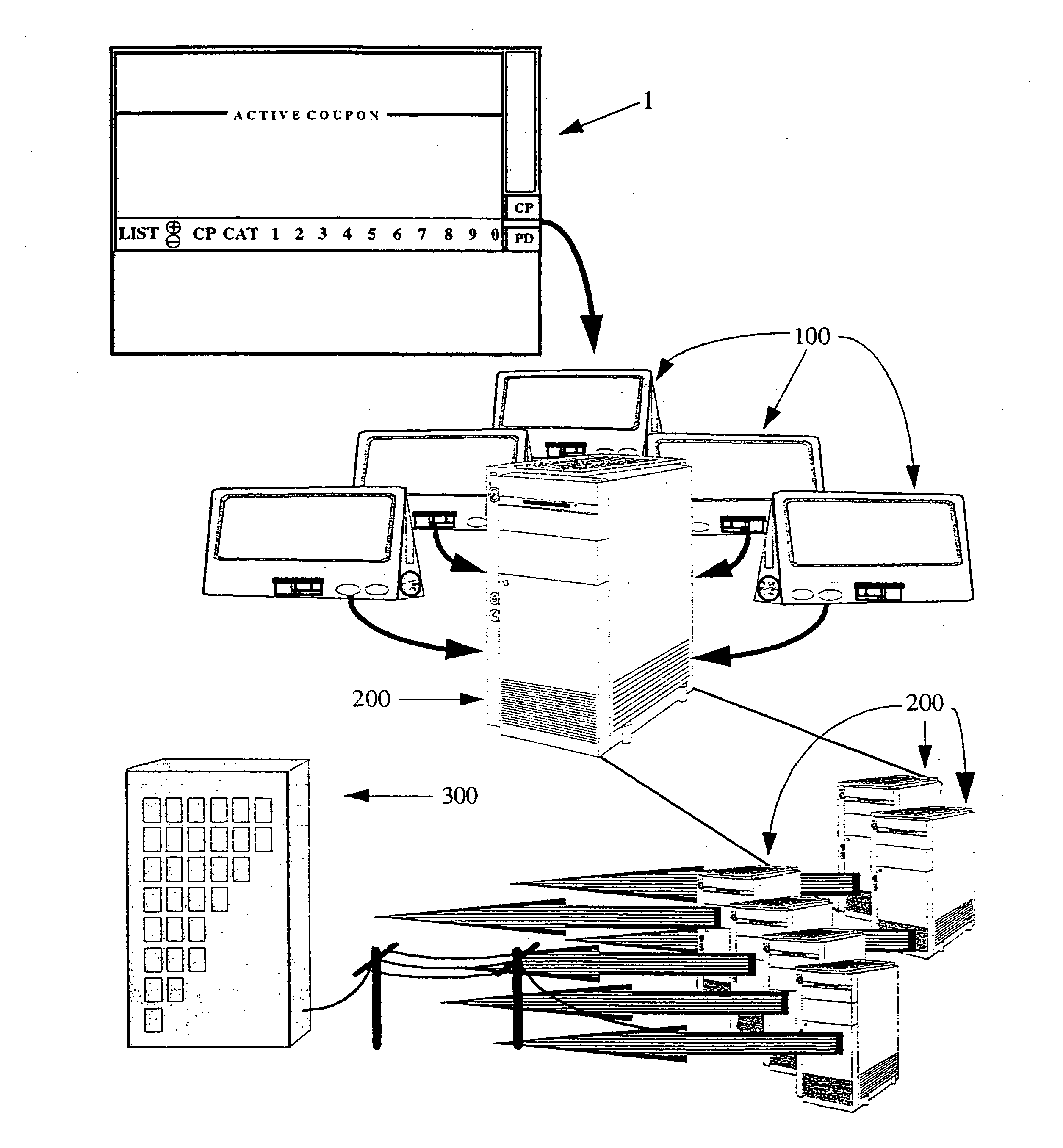

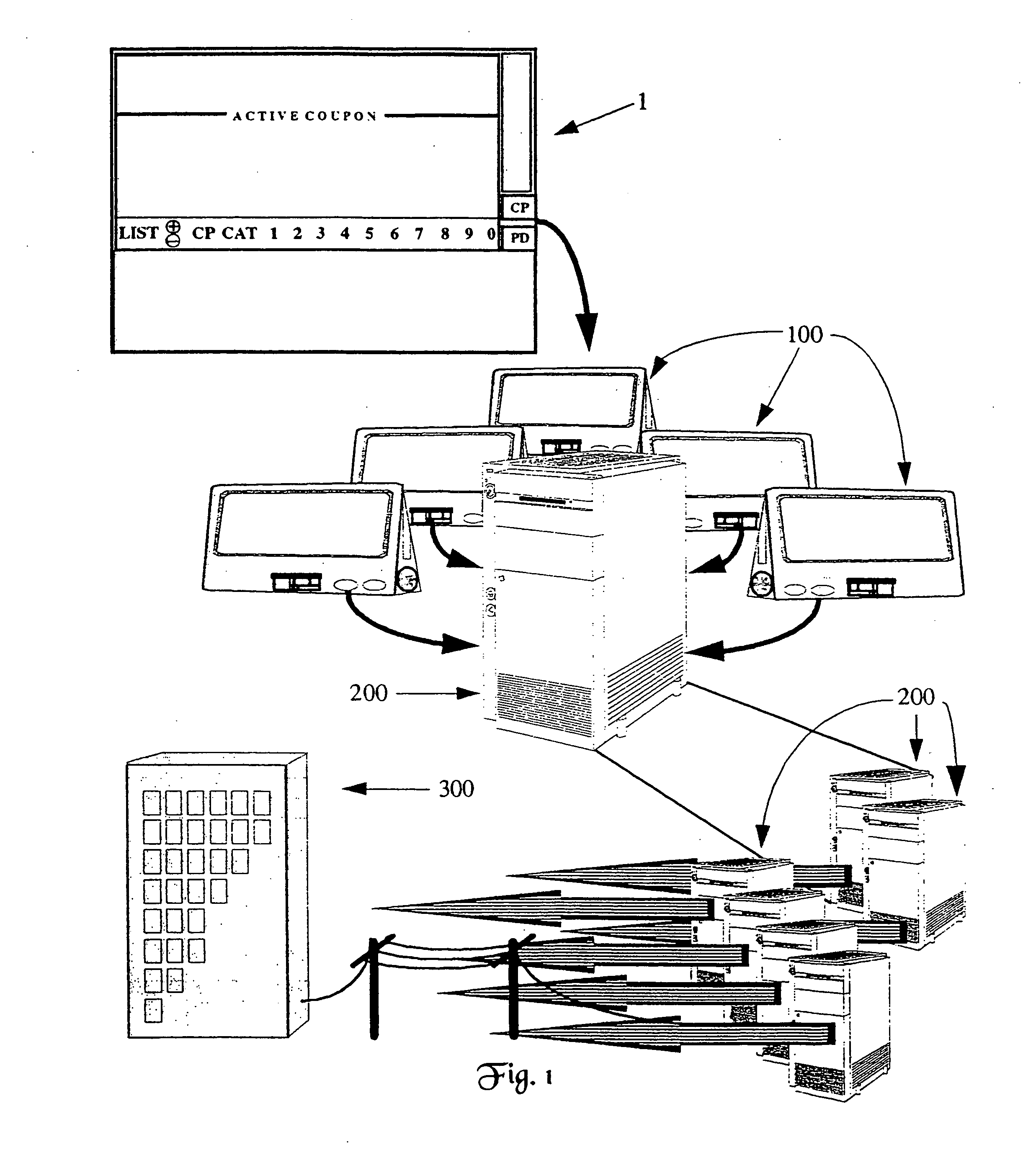

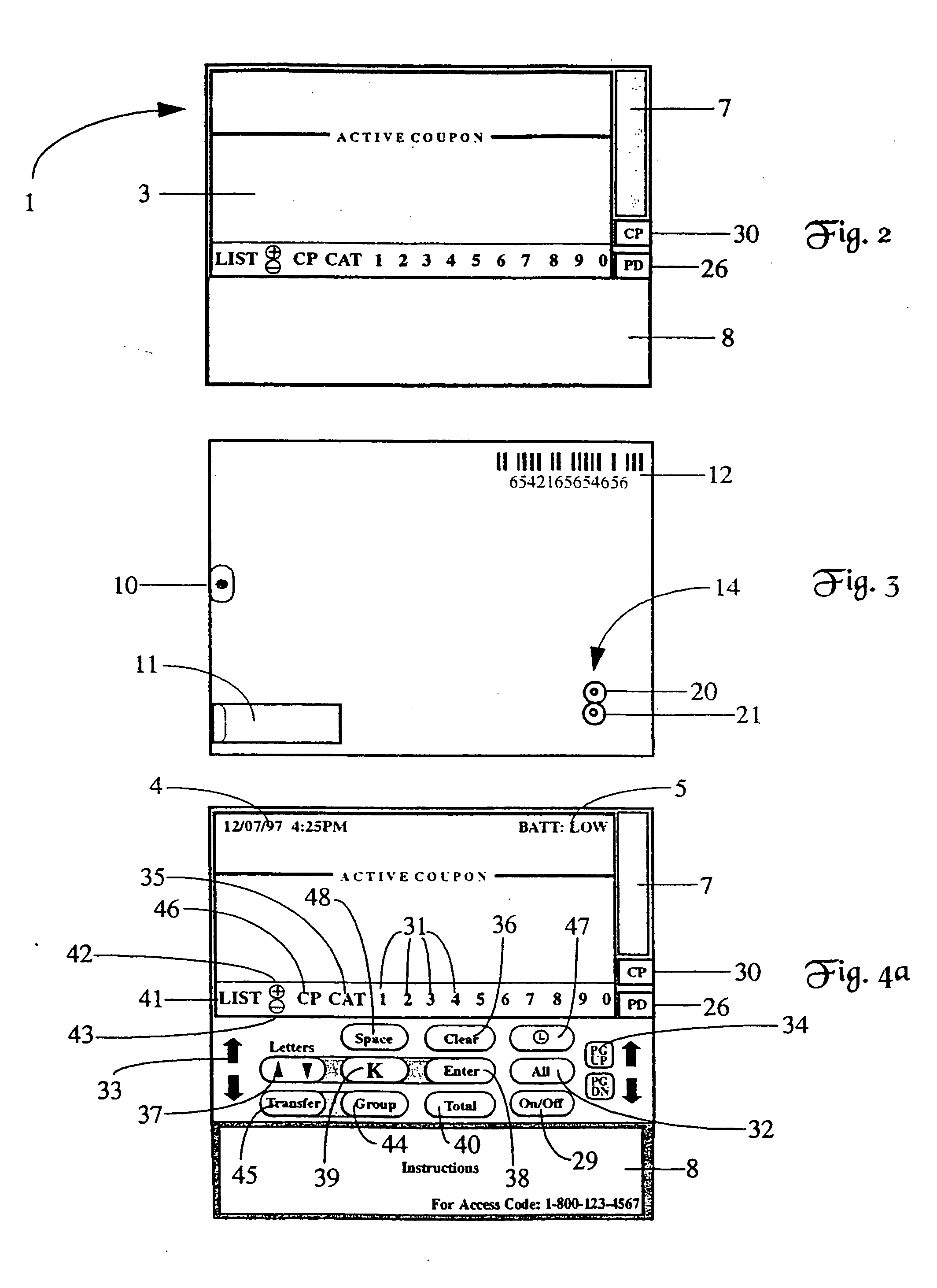

Method and apparatus for coupon management and redemption

InactiveUS6932270B1Eliminate disadvantagesIncrease speedCoin-freed apparatus detailsCash registersRandom access memoryBarcode

The present invention provides a system for the electronic management and redemption of coupons. The system incudes an integrated coupon card comprising a microprocessor, a random access memory means, a scanner, and a communications port. The coupon card is capable of scanning coupon bar codes from paper coupons and receiving redemption requirement data from a periphery device. The coupon card will allow bar codes and redemption requirement data to be transferred to a periphery device and will store what bar codes were redeemed because they corresponded to purchase data received from a cash register memory. The system further incudes one or more periphery devices having a microprocessor, a first communications port for communicating with said coupon card, and a second communications port for communicating with a cash register. The periphery devices receive purchase data from a cash register memory and compare said purchase data to coupon bar codes received from a coupon card in order to determine which coupons are redeemable. The system also incudes a server computer which win be connected to the periphery devices. The server computer will collect redeemed coupon information from the periphery devices and also provide the periphery devices with information such redemption requirement data or coupons which may be loaded onto a coupon card. A clearing house will collect coupon redemption information from all servers in the system to create redemption reports. The clearing house allows redemption requirement data and other information to be transferred through the servers to individual periphery devices and / or coupon cards.

Owner:WAY AHEAD IP

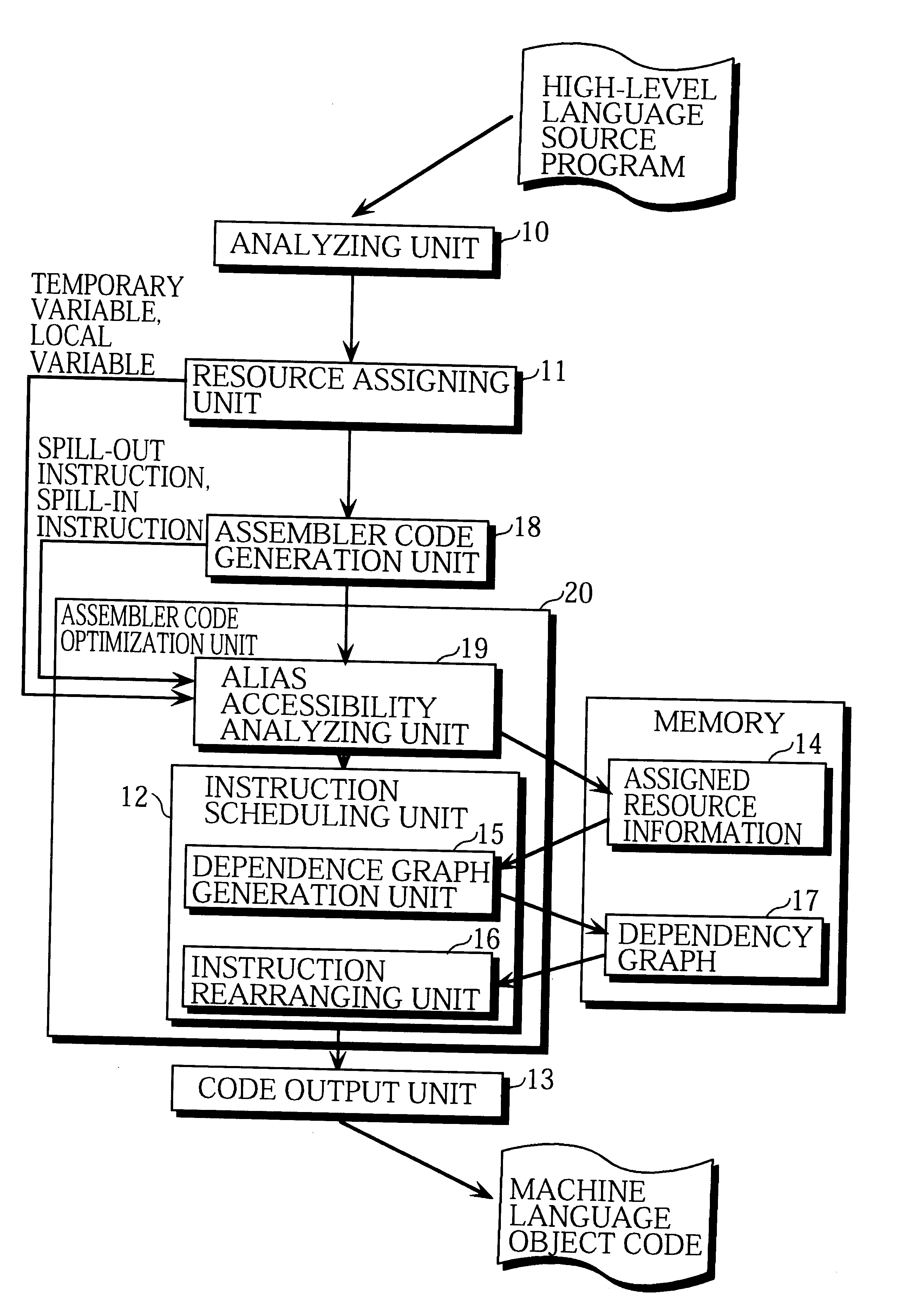

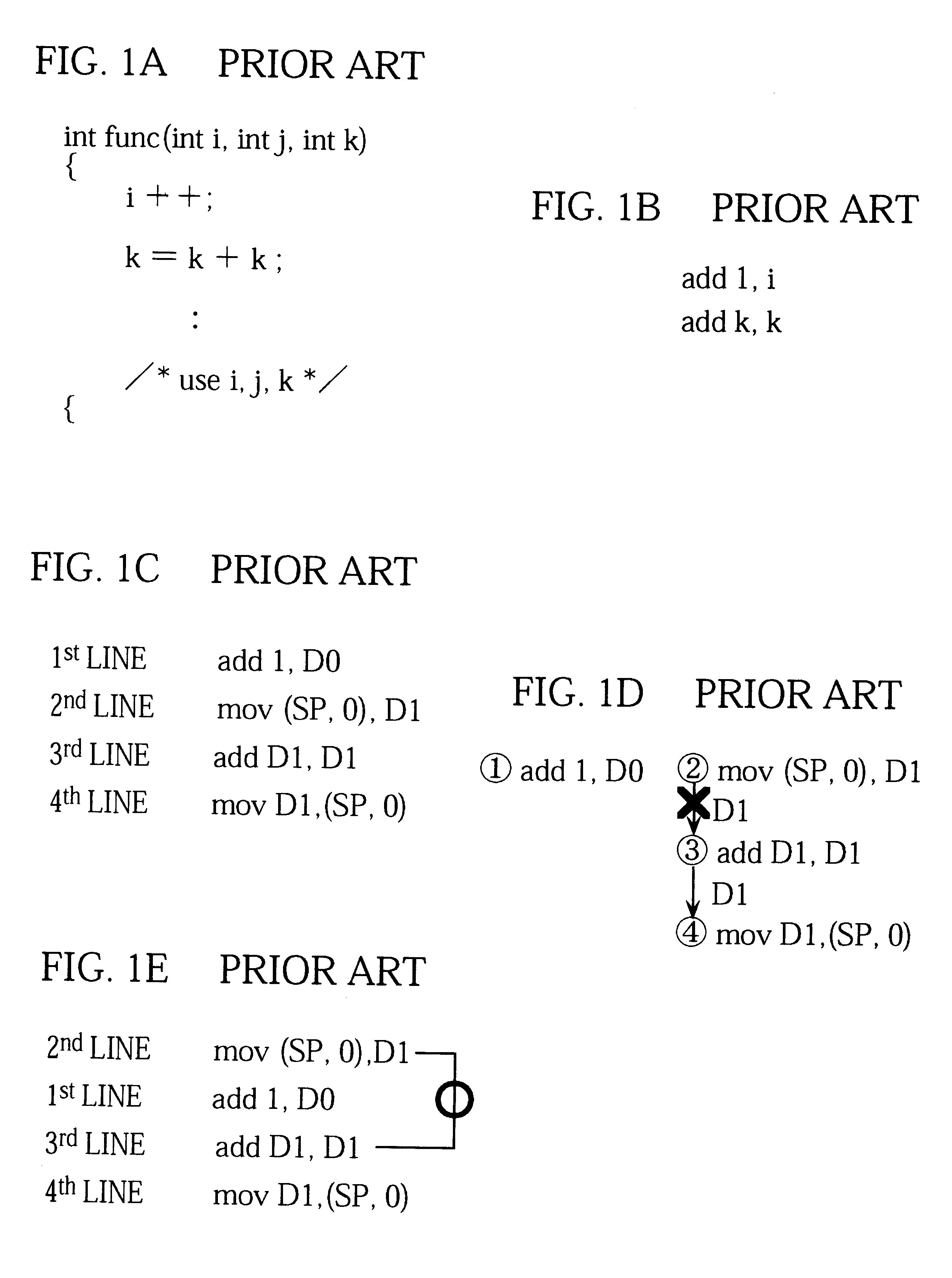

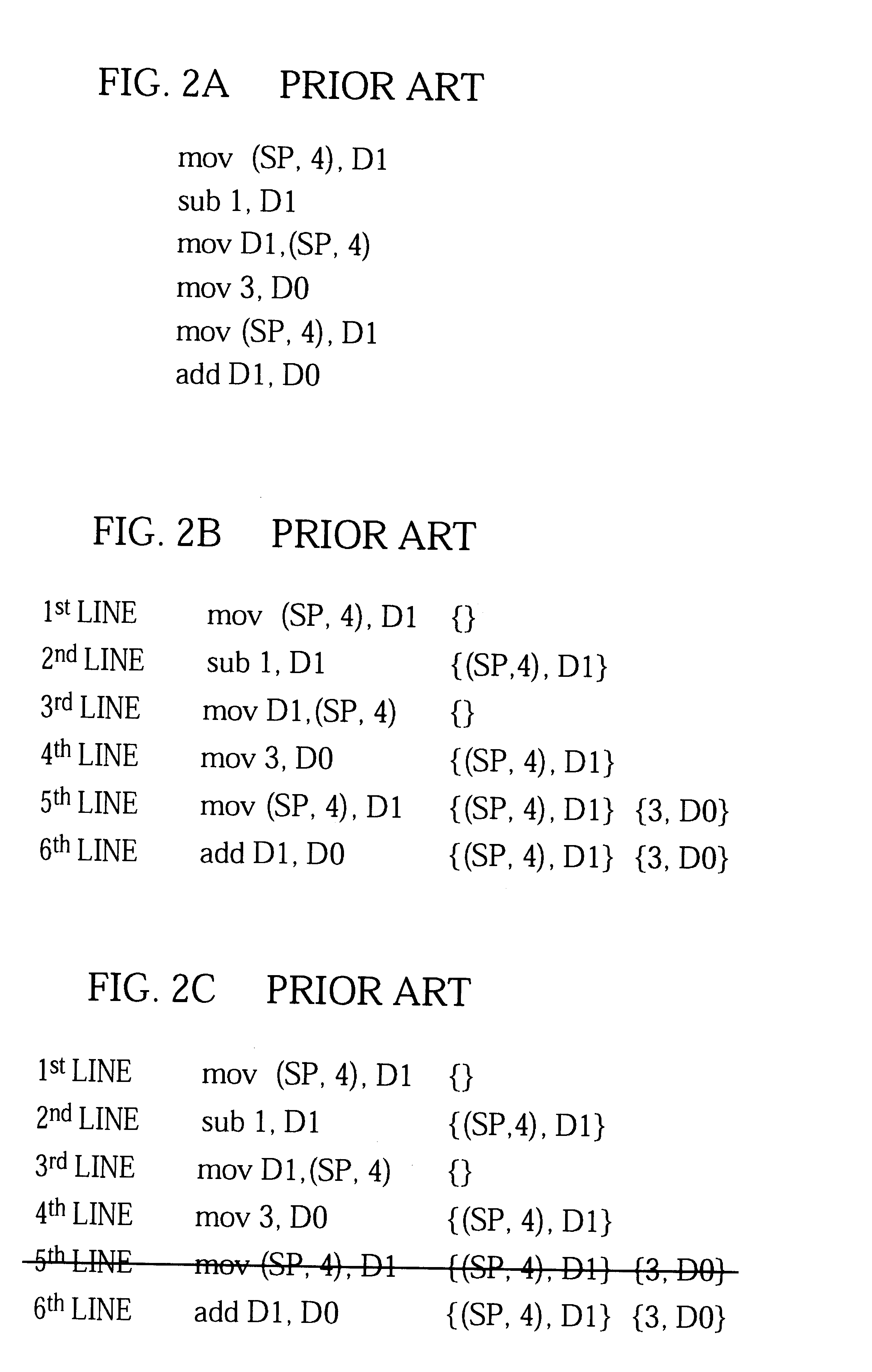

Compiler for optimizing memory instruction sequences by marking instructions not having multiple memory address paths

Internal variables generated by a compiler are assigned to machine resources such as registers and memory by the resource assigning unit 11, and when the assembler code generation unit 18 has outputted an instruction sequence, the alias accessibility analyzing unit 19 registers memory access instructions in the instruction sequence in the assigned resource information 14 according to whether the instructions have a possibility of access by alias. The assembler code optimization unit 20 refers to the assigned resource information 14 and performs optimization at assembler level, thereby reducing the program size and execution time of the instruction sequence.

Owner:SOCIONEXT INC

Method and apparatus for coupon management and redemption

InactiveUS20050230473A1Eliminate disadvantagesIncrease speedCoin-freed apparatus detailsCash registersRandom access memoryBarcode

The present invention provides a system for the electronic management and redemption of coupons. The system incudes an integrated coupon card comprising a microprocessor, a random access memory means, a scanner, and a communications port. The coupon card is capable of scanning coupon bar codes from paper coupons and receiving redemption requirement data from a periphery device. The coupon card will allow bar codes and redemption requirement data to be transferred to a periphery device and will store what bar codes were redeemed because they corresponded to purchase data received from a cash register memory. The system further incudes one or more periphery devices having a microprocessor, a first communications port for communicating with said coupon card, and a second communications port for communicating with a cash register. The periphery devices receive purchase data from a cash register memory and compare said purchase data to coupon bar codes received from a coupon card in order to determine which coupons are redeemable. The system also incudes a server computer which will be connected to the periphery devices. The server computer will collect redeemed coupon information from the periphery devices and also provide the periphery devices with information such redemption requirement data or coupons which may be loaded onto a coupon card. A clearing house will collect coupon redemption information from all servers in the system to create redemption reports. The clearing house allows redemption requirement data and other information to be transferred through the servers to individual periphery devices and / or coupon cards.

Owner:FAJKOWSKI PETER W

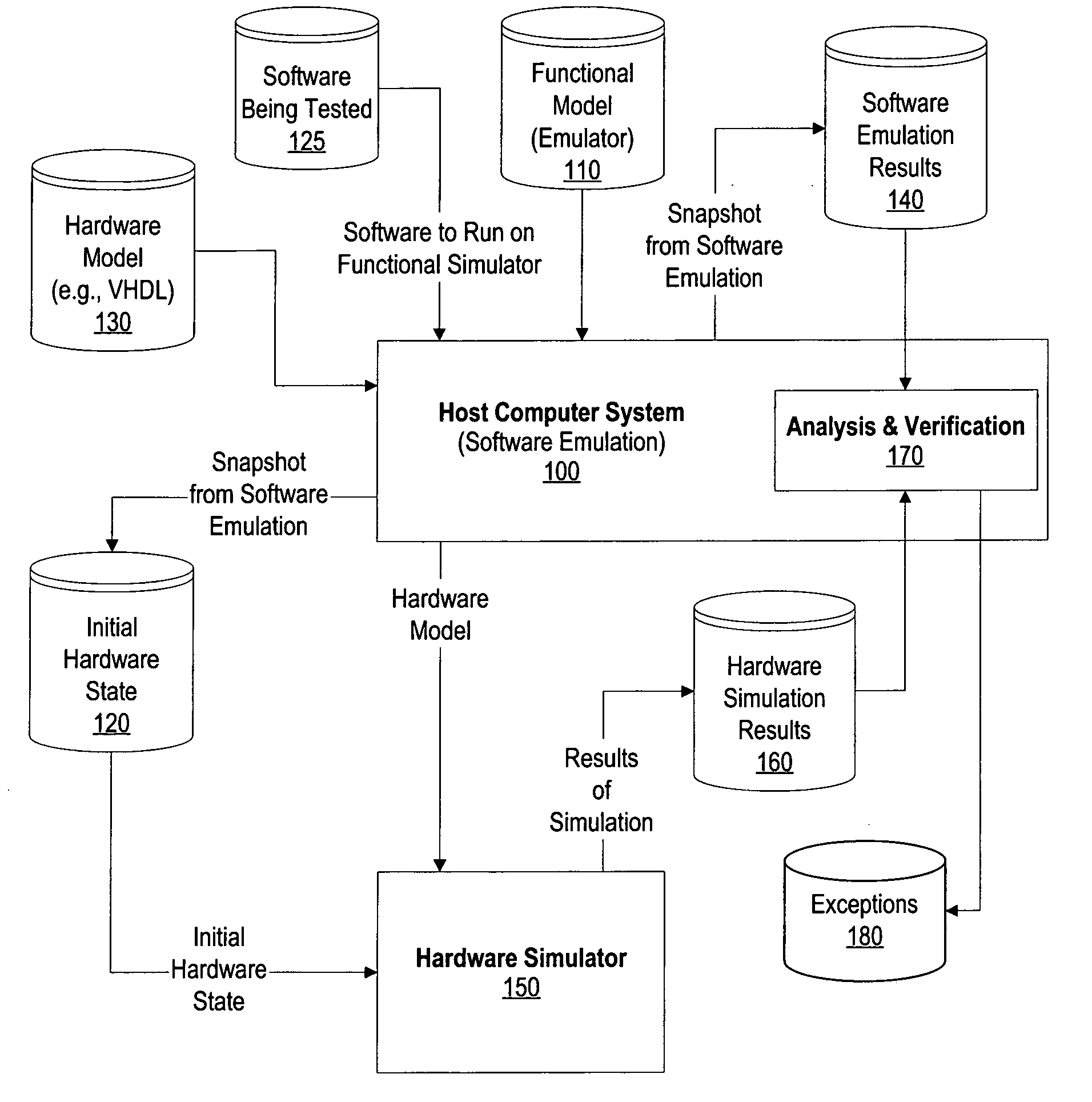

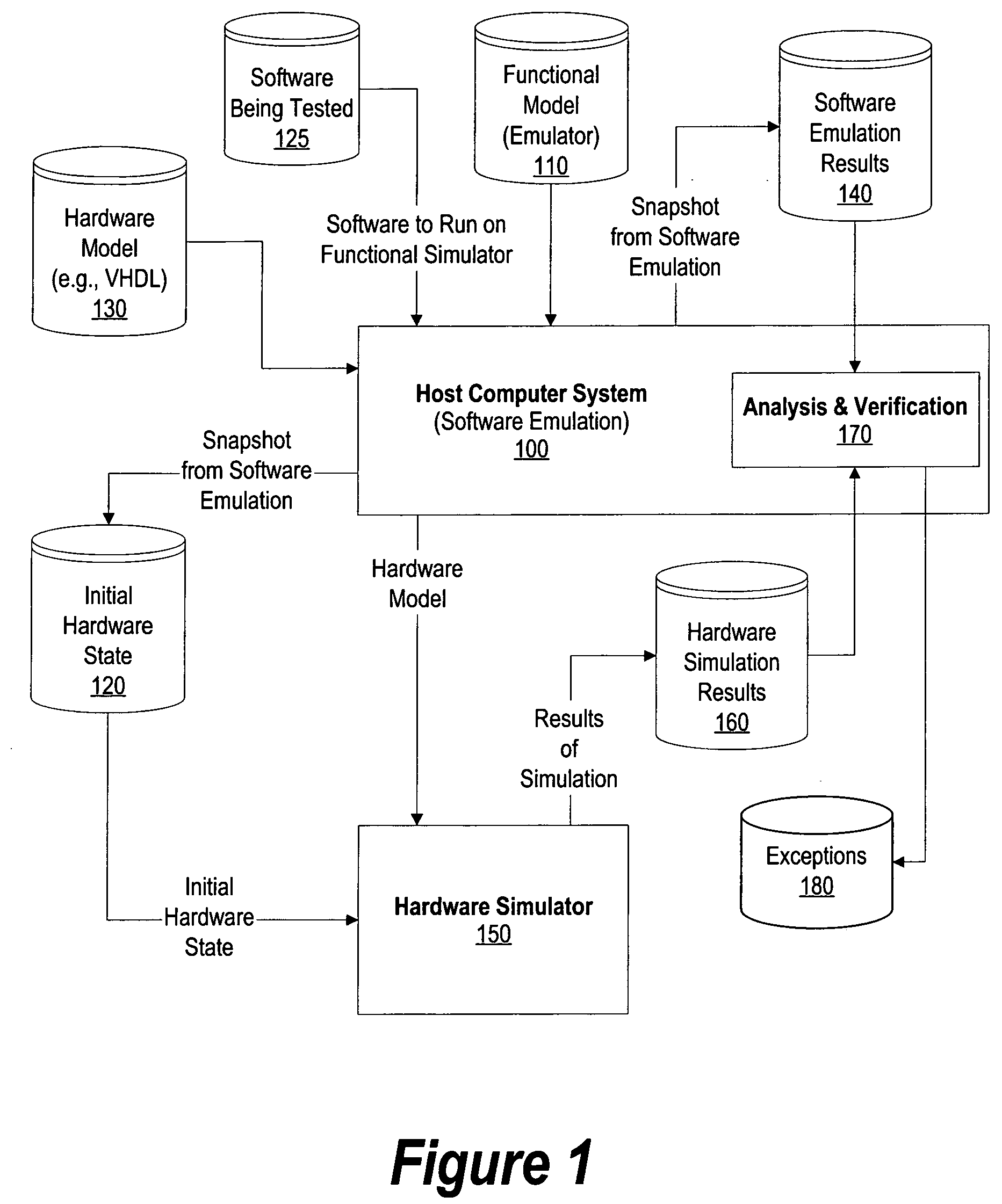

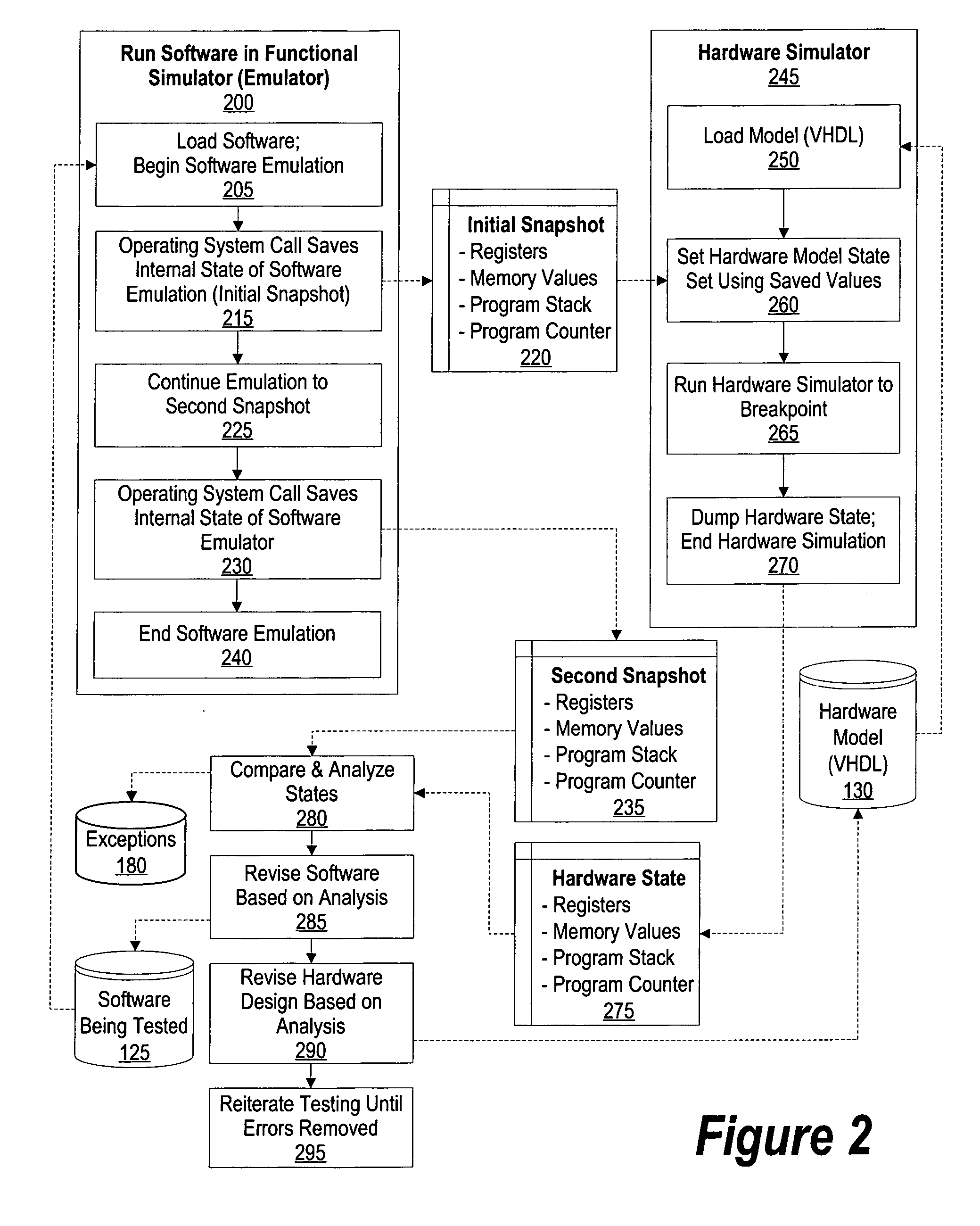

System and method for improved software simulation using a plurality of simulator checkpoints

InactiveUS20060155525A1CAD circuit designSoftware simulation/interpretation/emulationSoftware emulationParallel computing

A system and method is provided to improve software simulation. A software emulator is used in conjunction with a hardware simulator. A special snapshot instruction is included in the software code that is emulated. When the snapshot instruction is encountered, values such as register, memory, and program stack values, are stored creating an initial snapshot. Code continues to be emulated and, when the next snapshot instruction is encountered, the values are written to create a second snapshot. The initial values are used to set an initial state in a hardware model that is simulated on a hardware simulator. The results of the hardware simulation are compared to the second snapshot to uncover software errors and / or hardware errors so that the software can be modified or the hardware design can be modified. Multiple sets of snapshots can be taken to analyze multiple sections of the software program.

Owner:IBM CORP

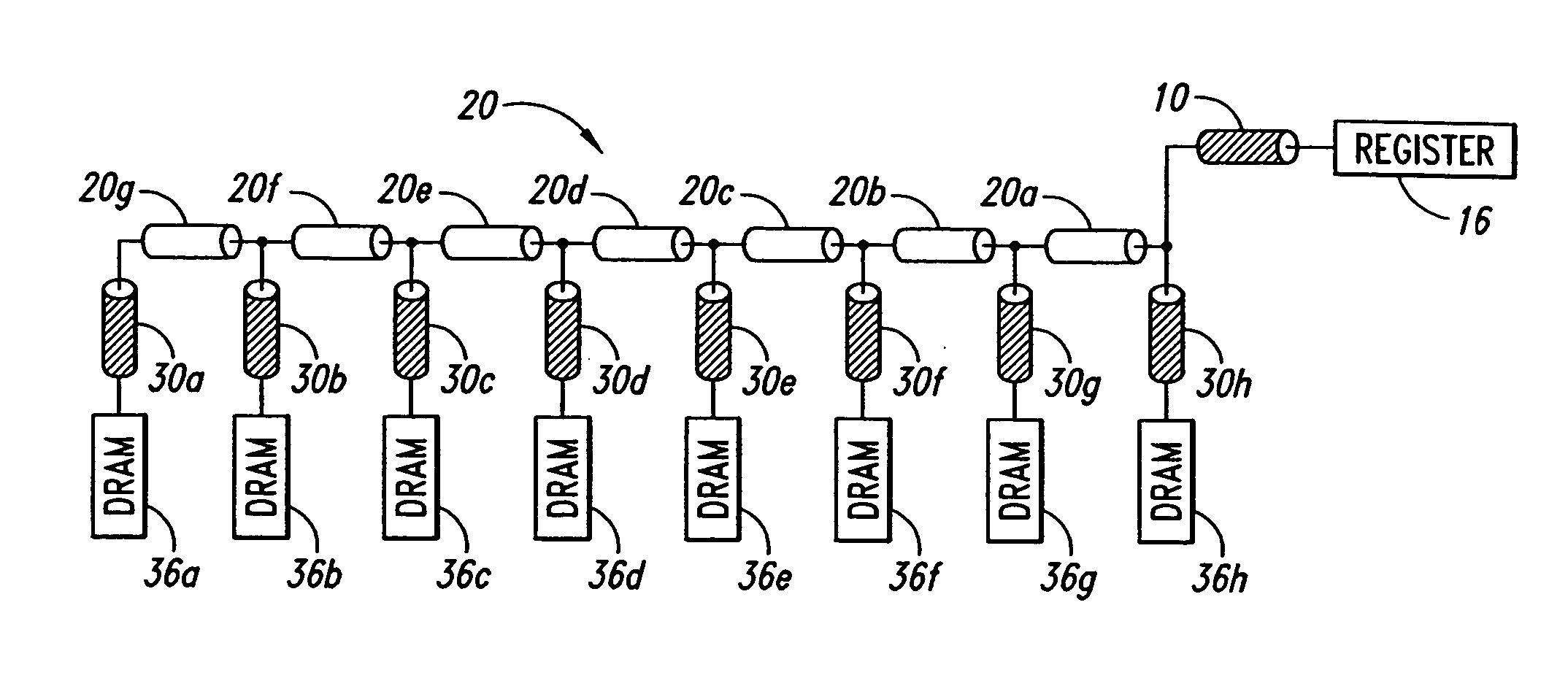

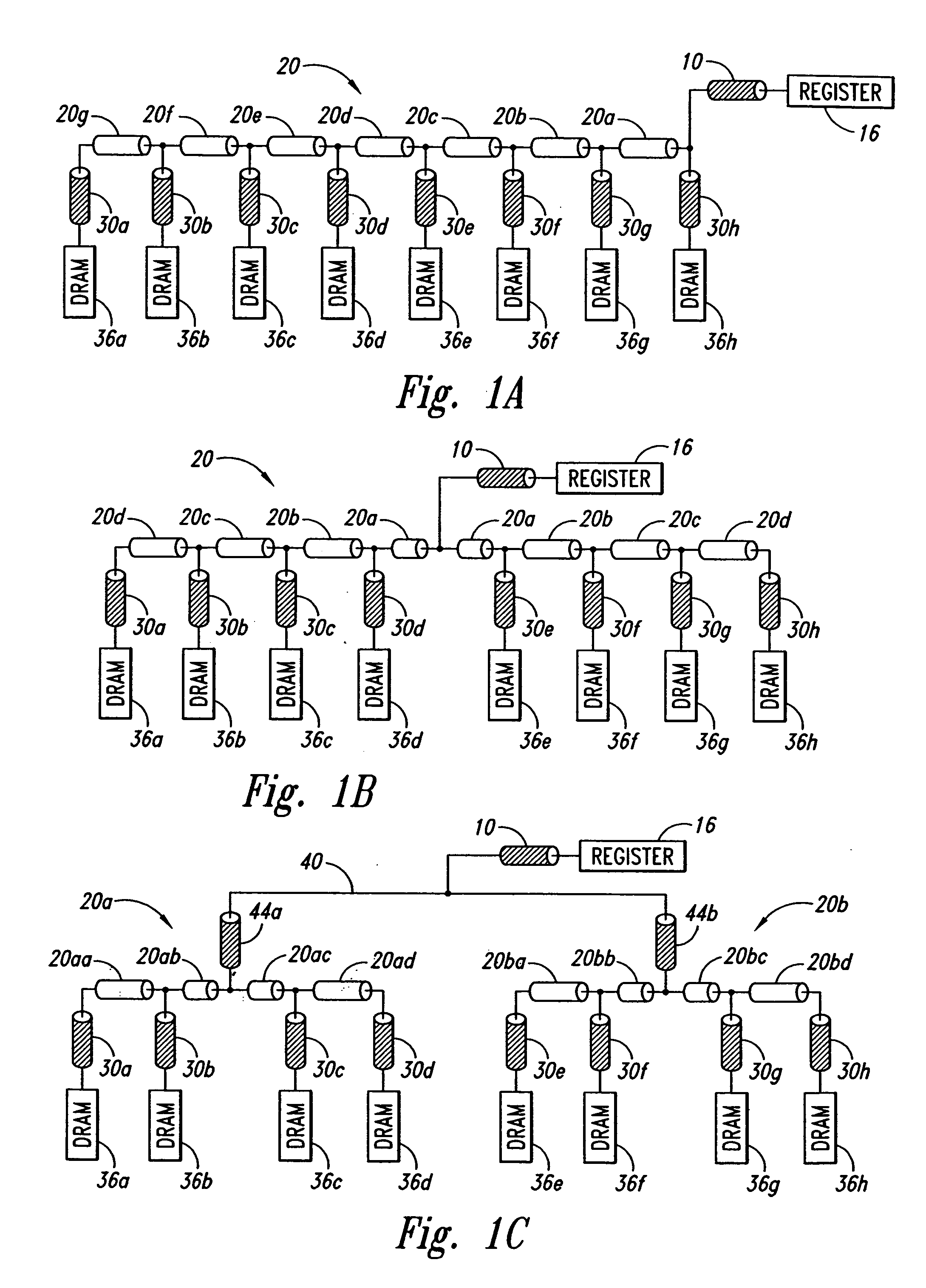

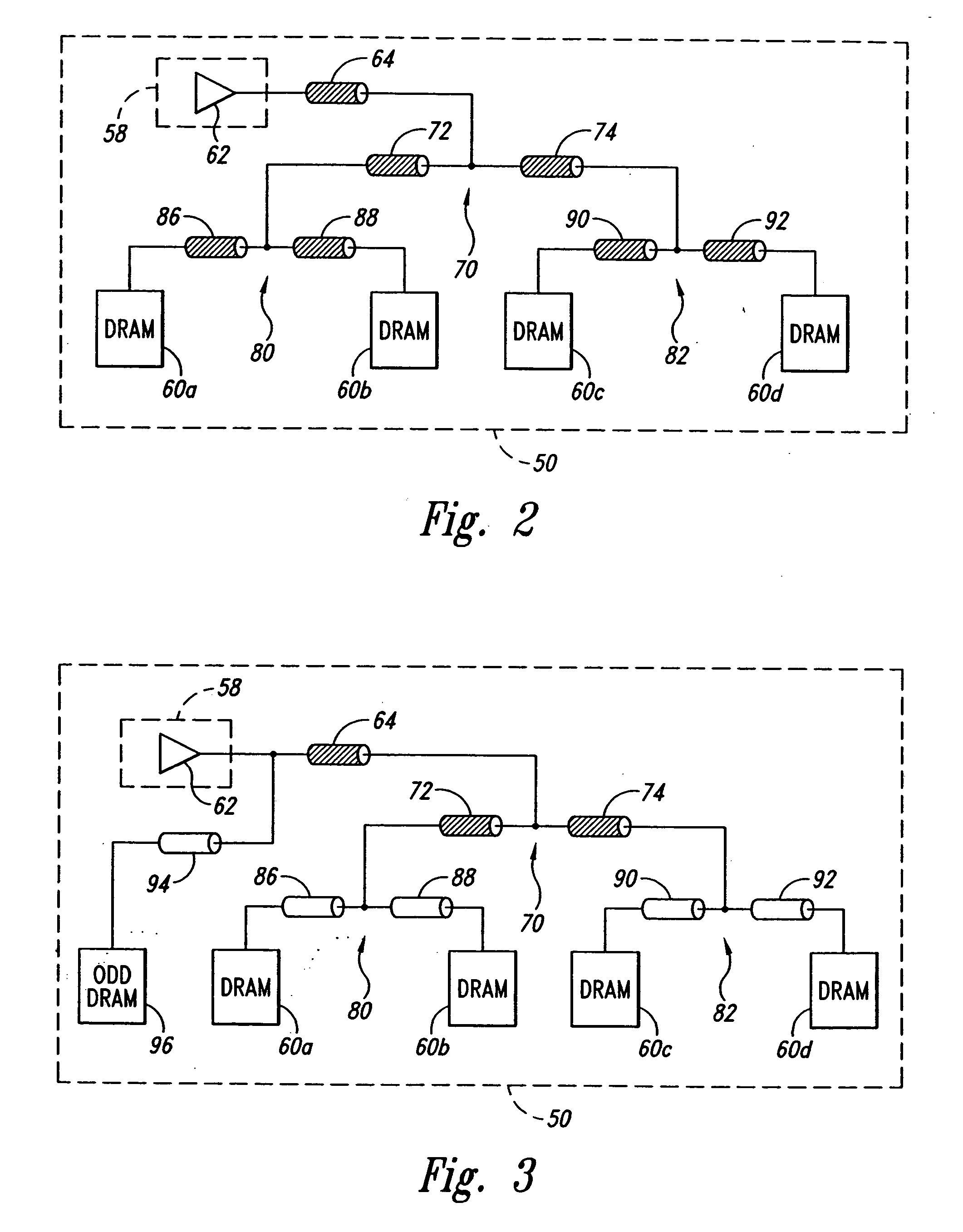

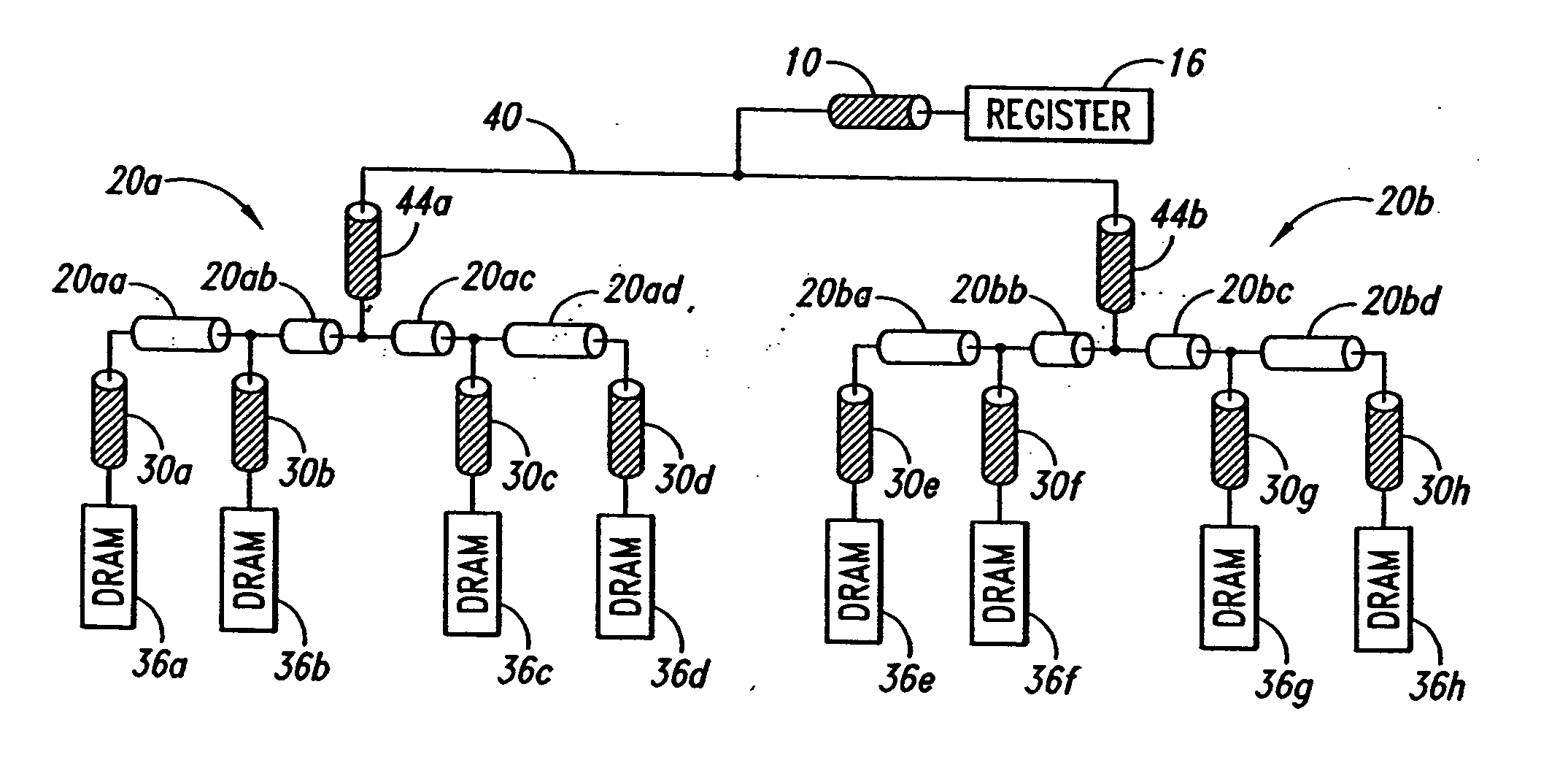

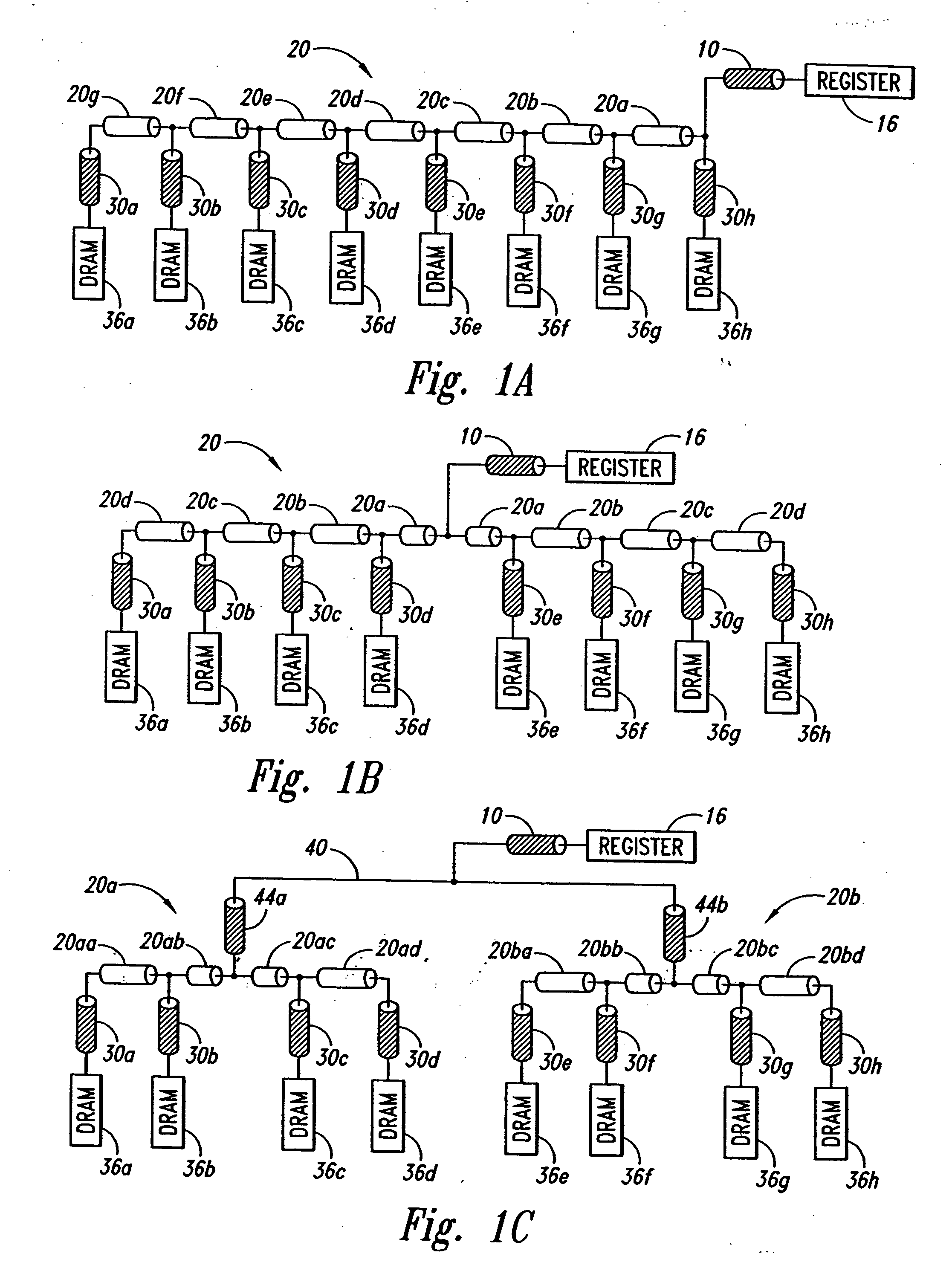

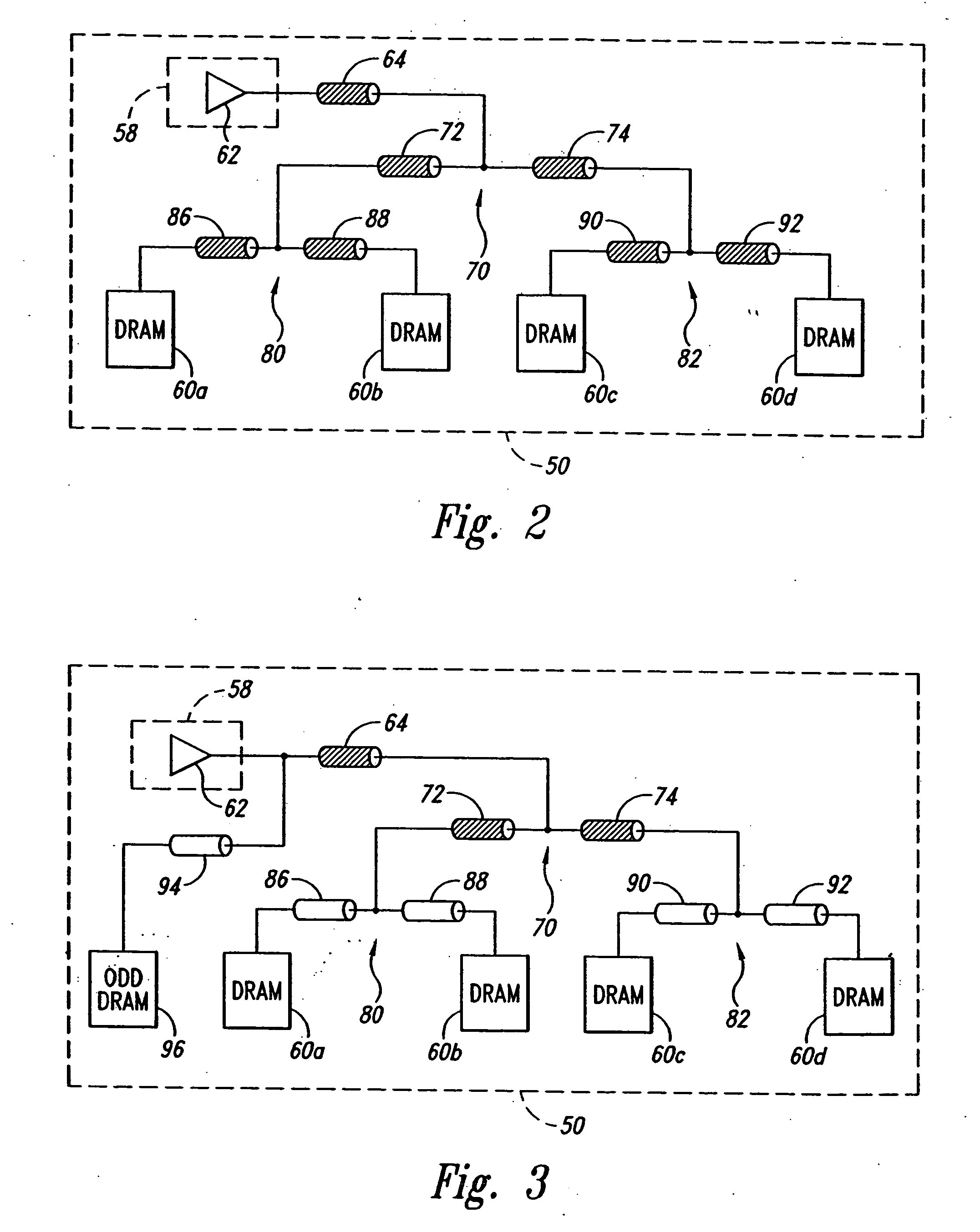

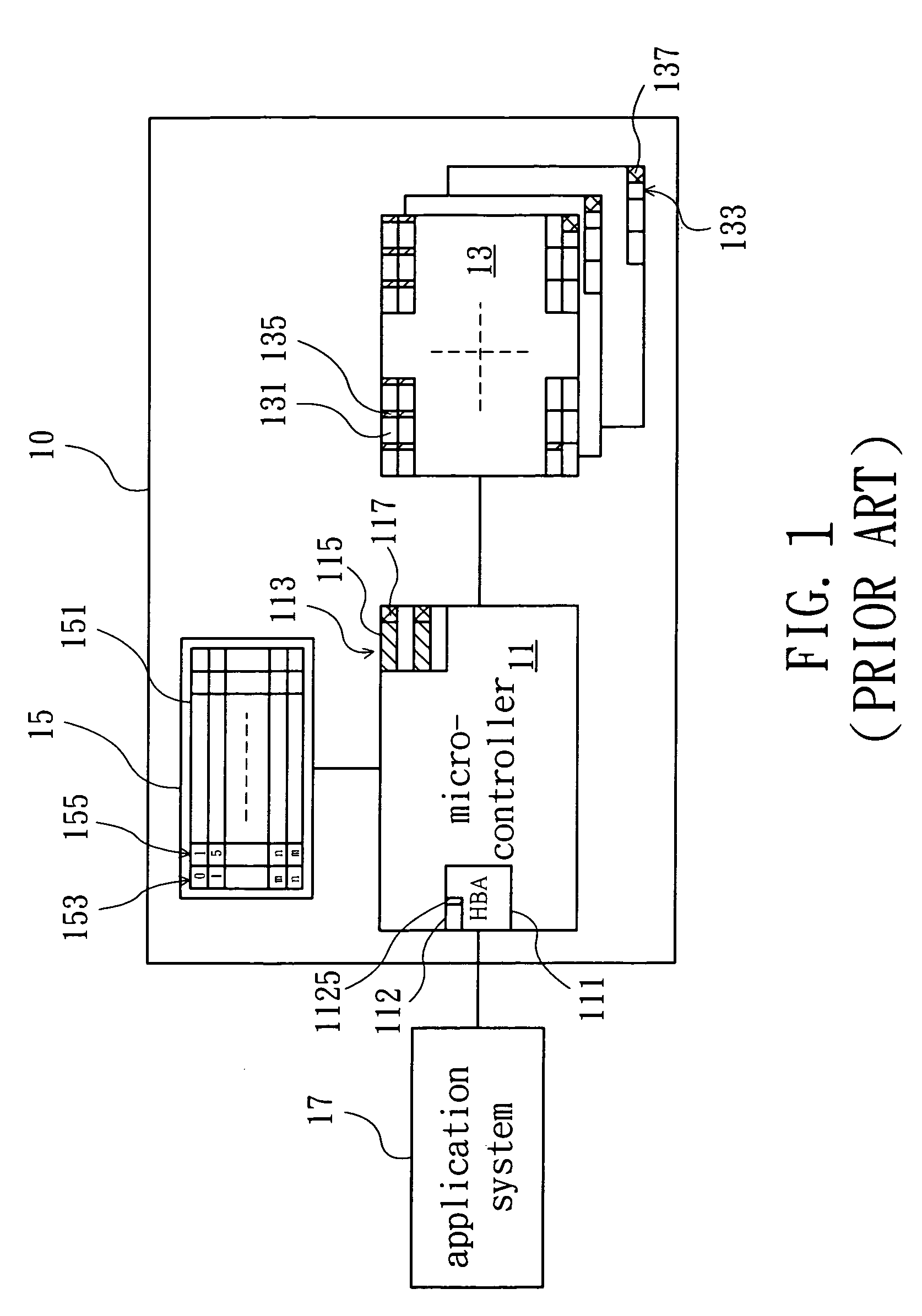

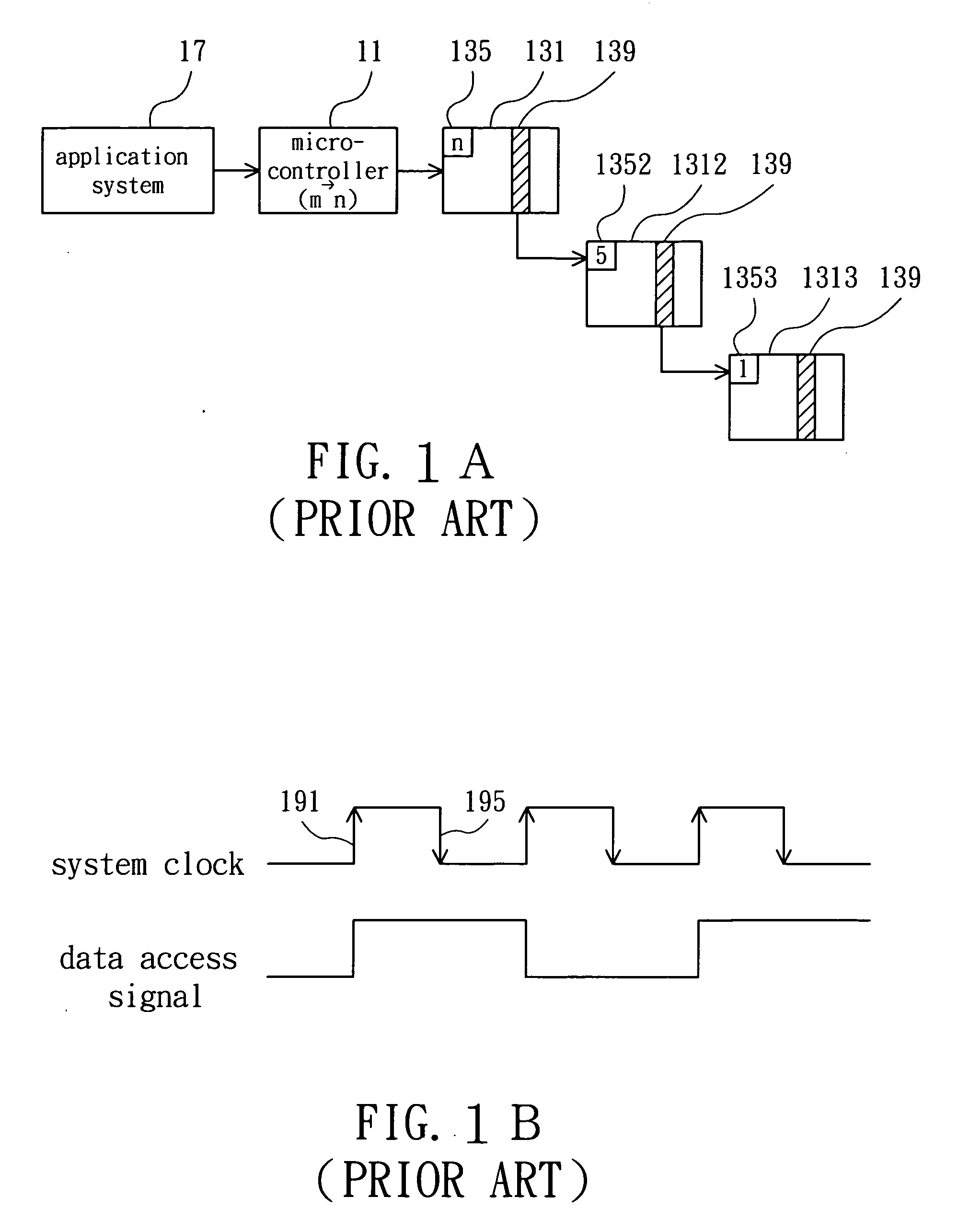

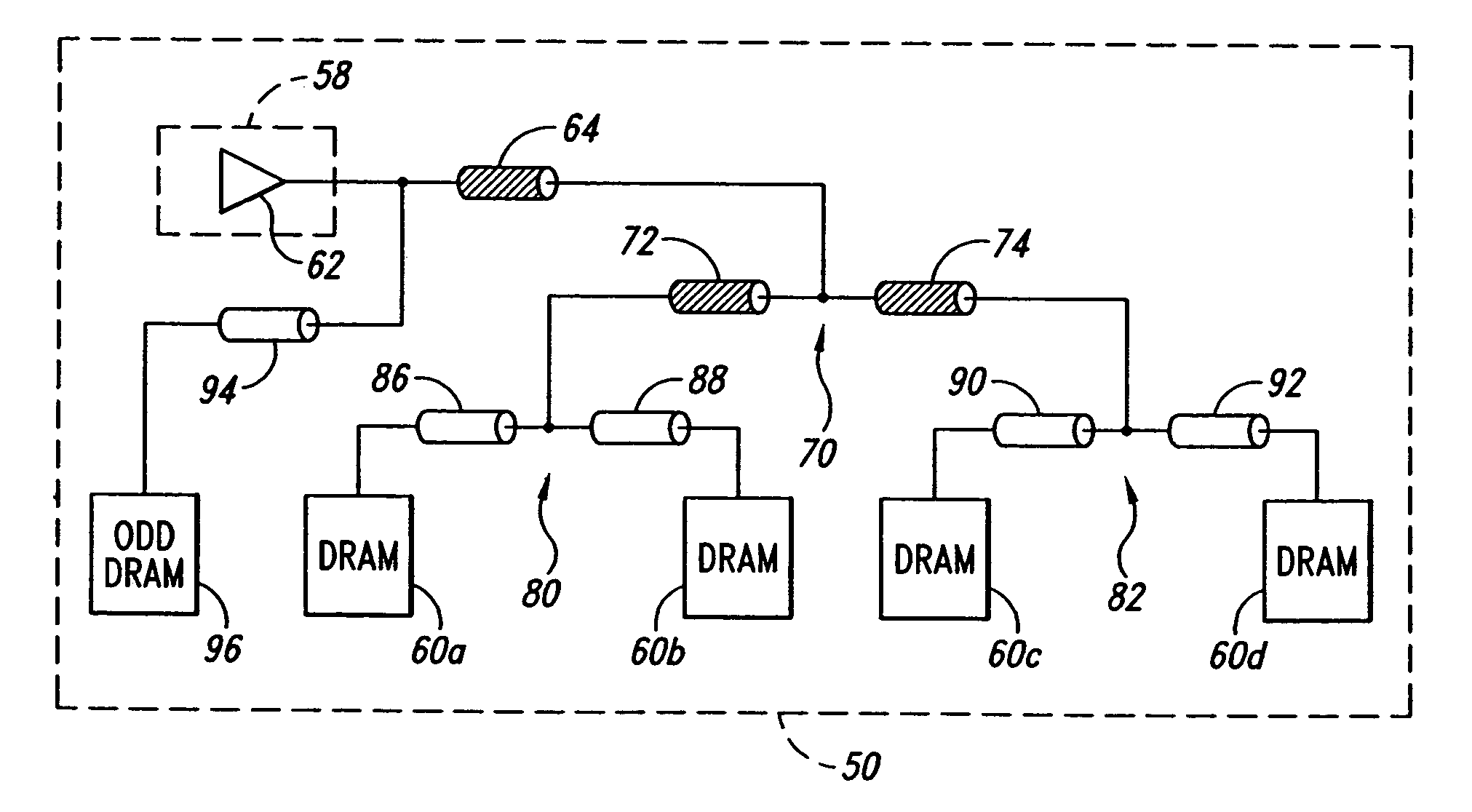

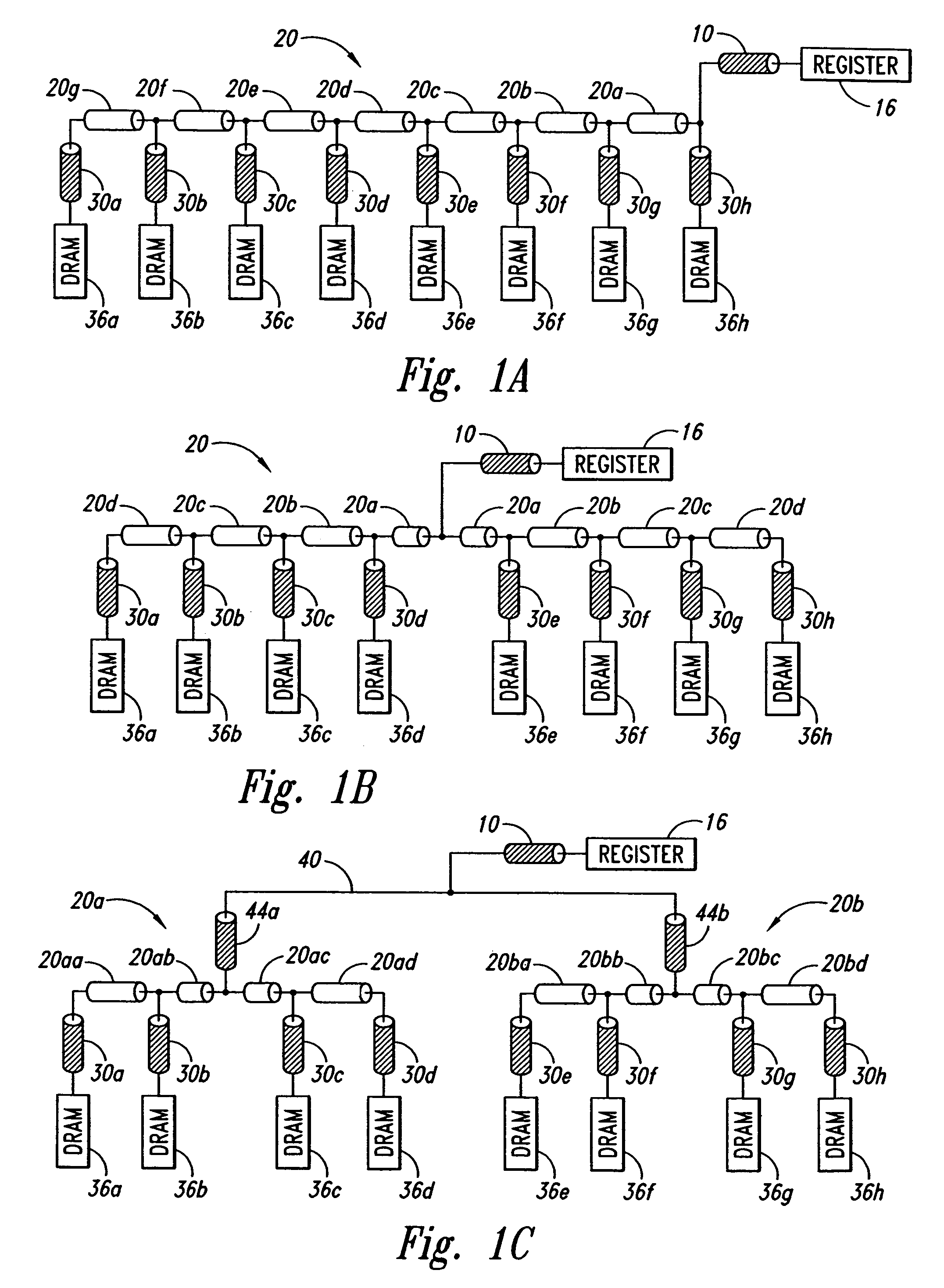

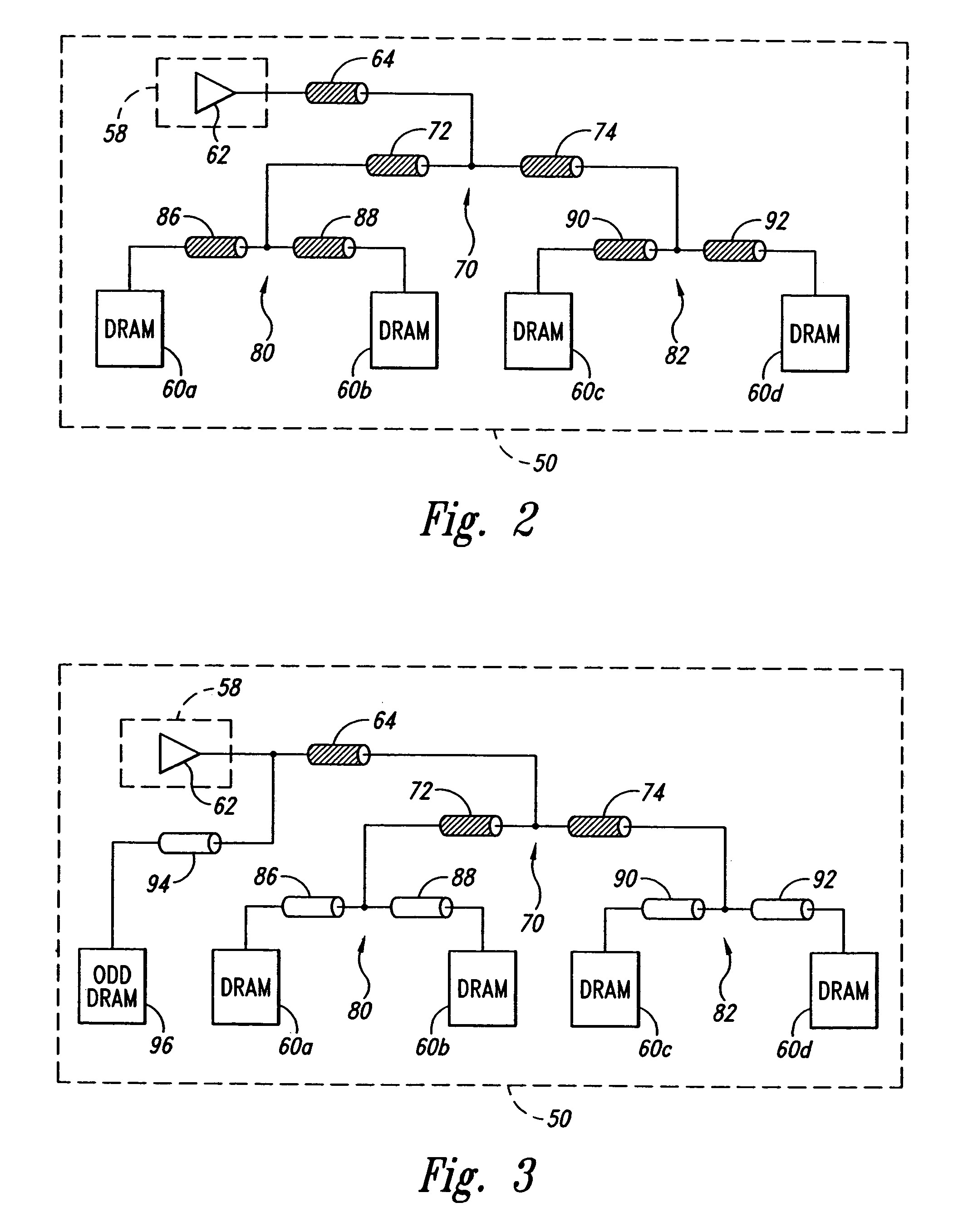

Memory module and method having improved signal routing topology

InactiveUS20050030797A1Reliability increasing modificationsFinal product manufactureError checkSignal routing

A registered memory module includes several memory devices coupled to a register through a plurality of transmission lines forming a symmetrical tree topology. The tree includes several branches each of which includes two transmission lines coupled only at its ends to either another transmission line or one of the memory devices. The branches are arranged in several layers of hierarchy, with the transmission lines in branches having the same hierarchy having the same length. Each transmission line preferably has a characteristic impedance that is half the characteristic impedance of any pair of downstream transmission lines to which it is coupled to provide impedance matching. A dedicated transmission line is used to couple an additional memory device, which may or may not be an error checking memory device, to the register.

Owner:ROUND ROCK RES LLC

Memory module and method having improved signal routing topology

InactiveUS20060023528A1Reliability increasing modificationsFinal product manufactureError checkSignal routing

A registered memory module includes several memory devices coupled to a register through a plurality of transmission lines forming a symmetrical tree topology. The tree includes several branches each of which includes two transmission lines coupled only at its ends to either another transmission line or one of the memory devices. The branches are arranged in several layers of hierarchy, with the transmission lines in branches having the same hierarchy having the same length. Each transmission line preferably has a characteristic impedance that is half the characteristic impedance of any pair of downstream transmission lines to which it is coupled to provide impedance matching. A dedicated transmission line is used to couple an additional memory device, which may or may not be an error checking memory device, to the register.

Owner:ROUND ROCK RES LLC

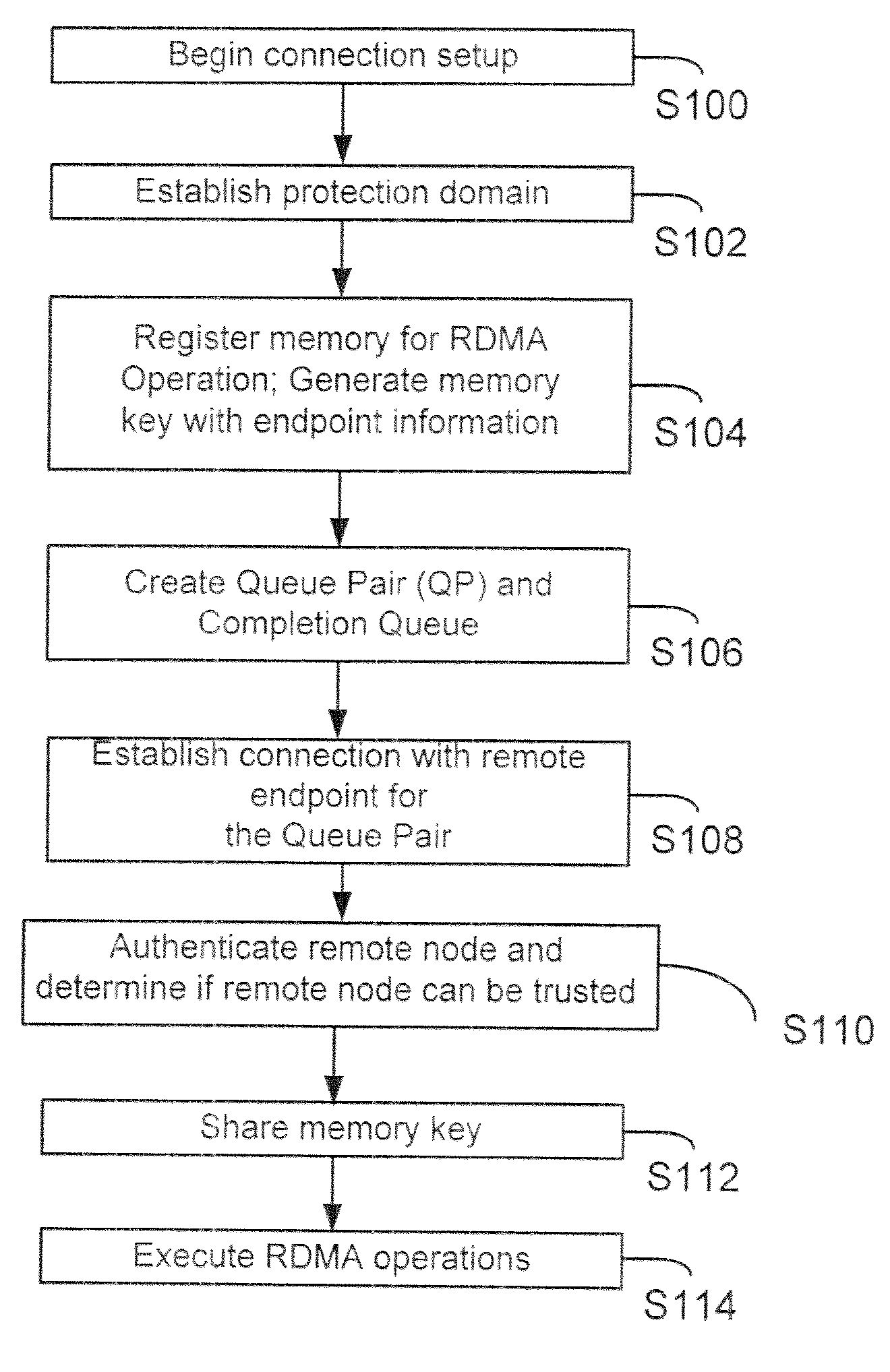

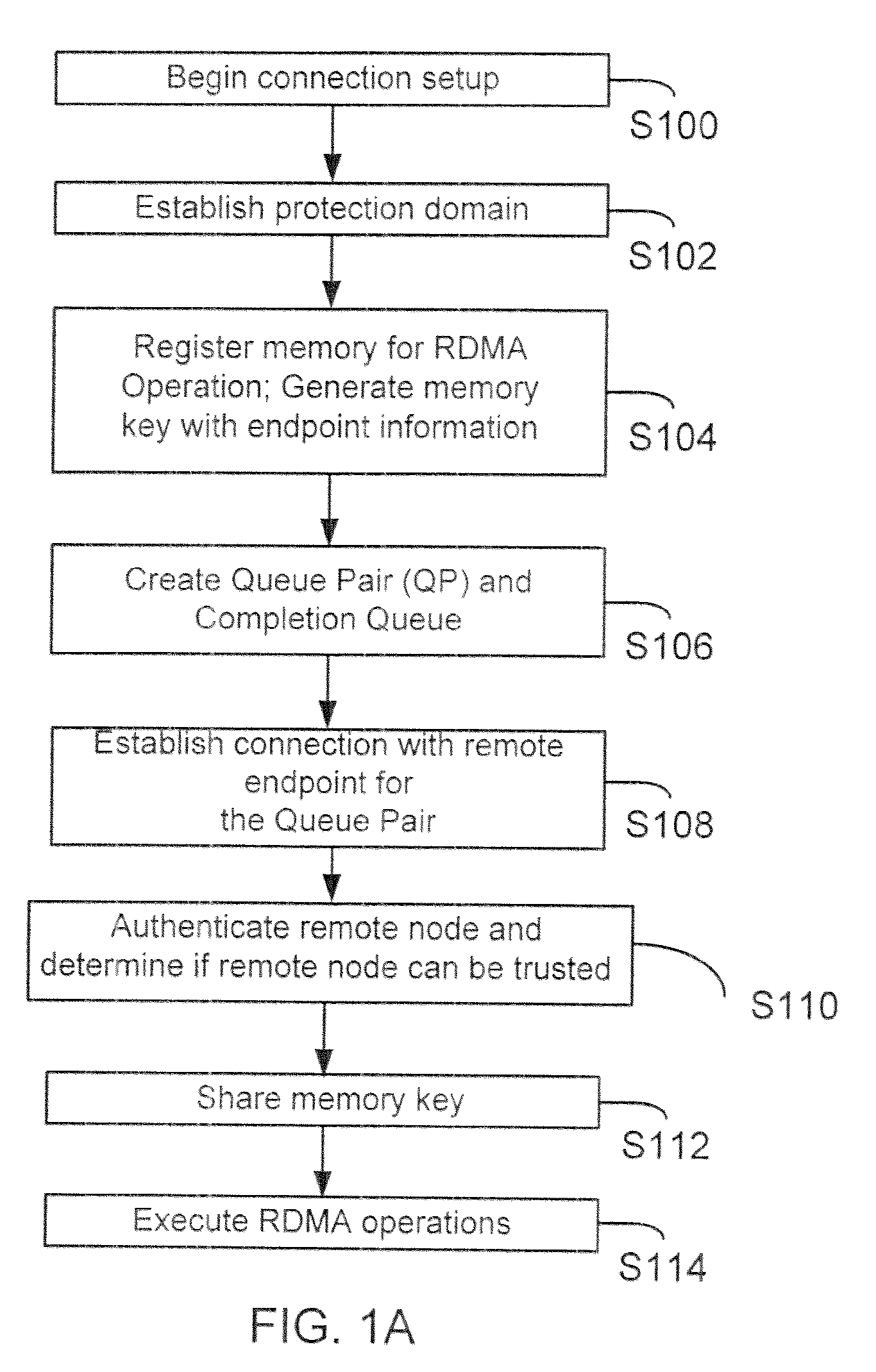

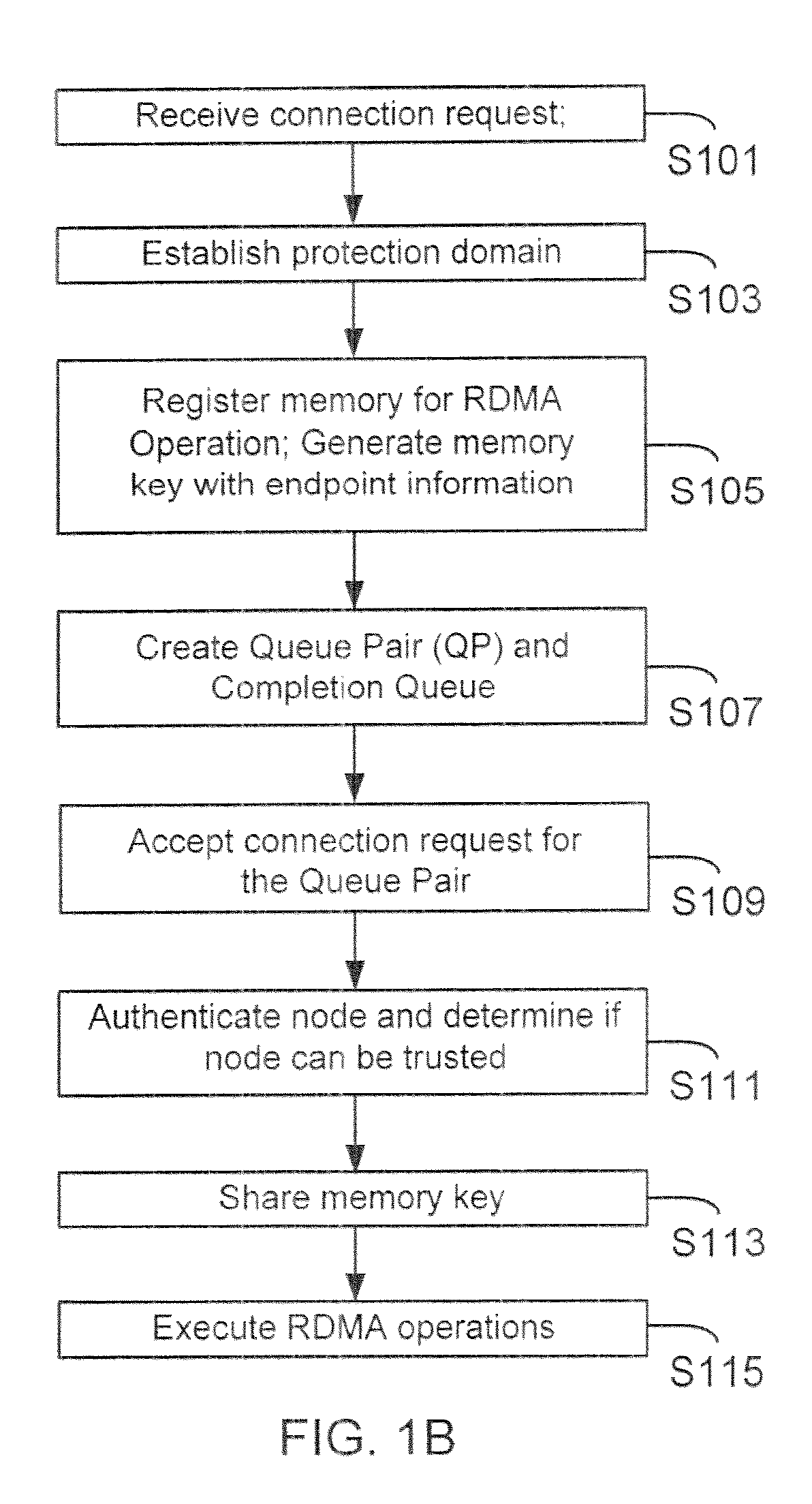

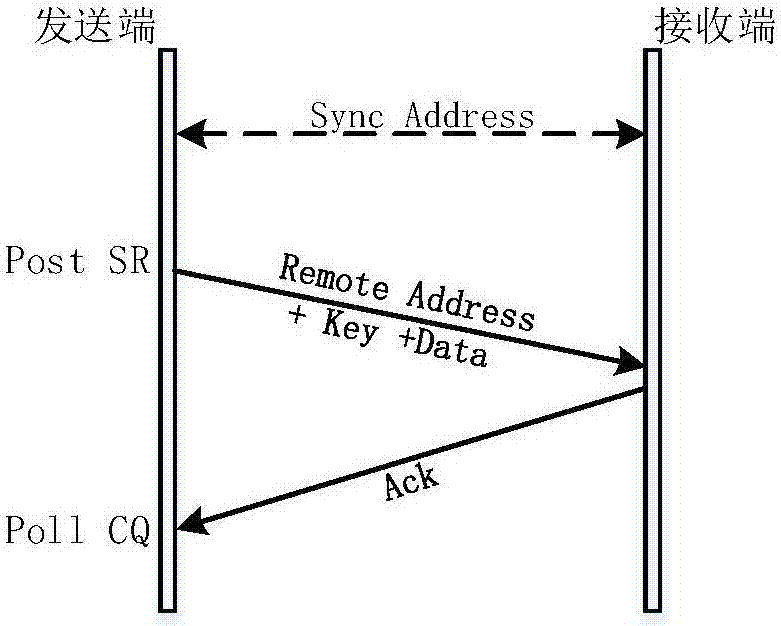

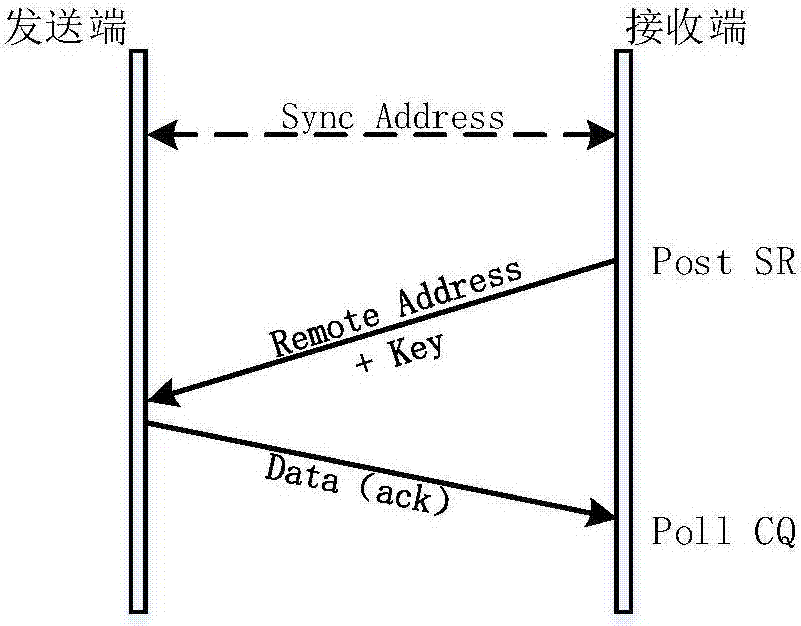

Method and system for secure remote direct memory access

ActiveUS7971236B1Prevent easy accessEasy accessDigital data processing detailsMultiple digital computer combinationsNetwork addressingRemote direct memory access

Method and system are provided where a memory key structure is used for authenticating access to a memory location that is registered for a remote direct memory access (RDMA) operation. The memory key structure not only includes a standard memory key that is expected by an RDMA enabled network interface card (RNIC), but also includes an endpoint network address identifier and a transport identifier. The endpoint network address identifier and the transport identifier are verified before an entity is granted access to the registered memory location.

Owner:NETWORK APPLIANCE INC

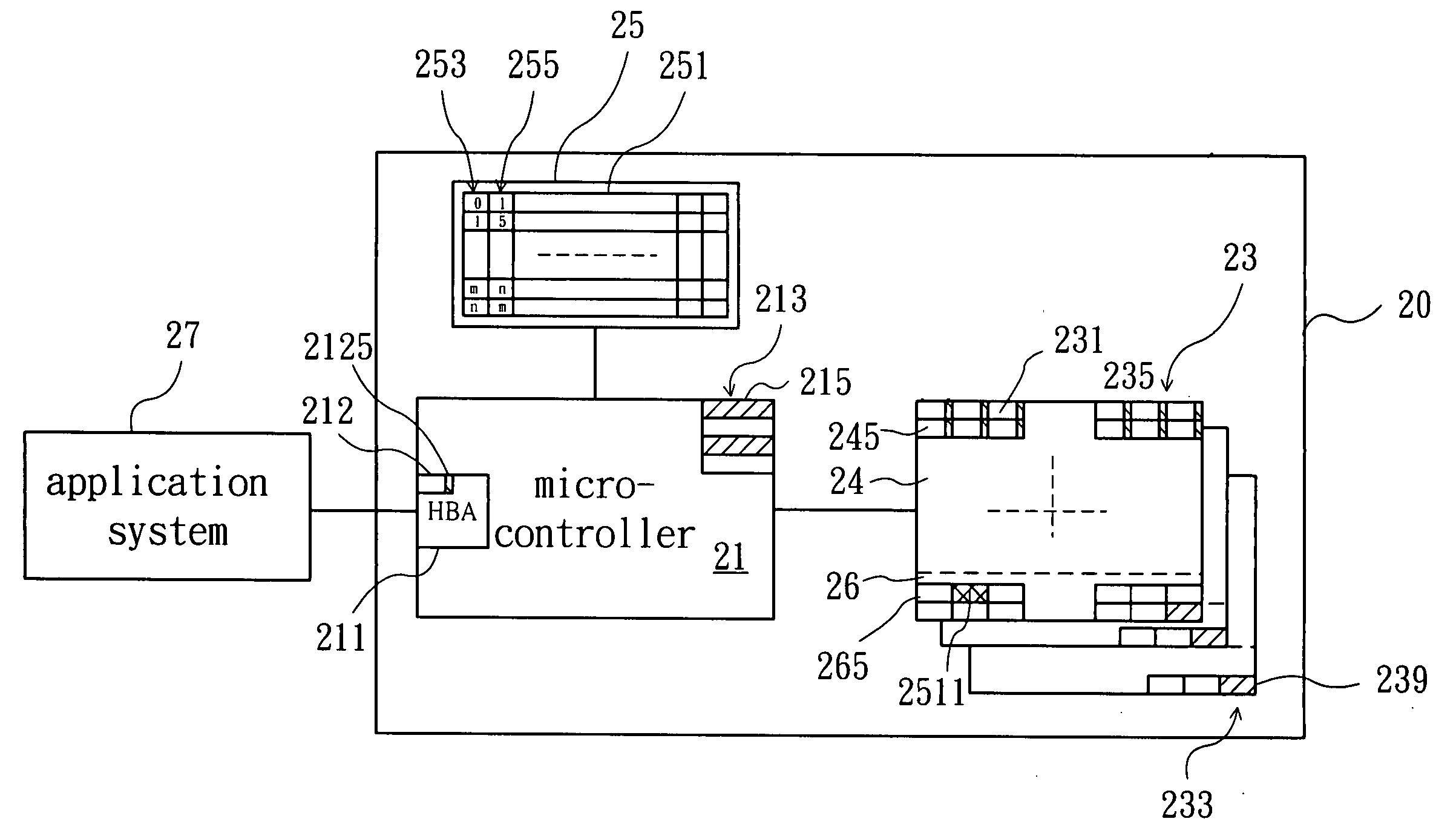

Flash storage

InactiveUS20060271727A1Safety and reliability in data access can be ensuredMemory loss protectionMicro-instruction address formationData accessTerm memory

A flash storage comprises a flash memory, including a plurality of physical memory blocks, each of physical memory blocks comprising a plurality of memory segments, and a plurality of physical sectors, and each of physical sectors being further provided therein with at least a user data column and a logical address pointer column. When physical data is written into the user data column, writing logical address pointer data into the logical address pointer column of the same physical sector may be performed together by the control of a micro-controller. Furthermore, the logical address pointer data in the same memory segment are arranged to be a backup memory segment address mapping table and then stored in one physical memory block. The backup memory segment address mapping table may be loaded directly and stored into a registered memory by the micro-controller when the system boots. Thus, not only shortening the startup duration of the flash storage, but also saving the memory capacity of the registered memory and securing data access may be obtained.

Owner:PROLIFIC TECH INC

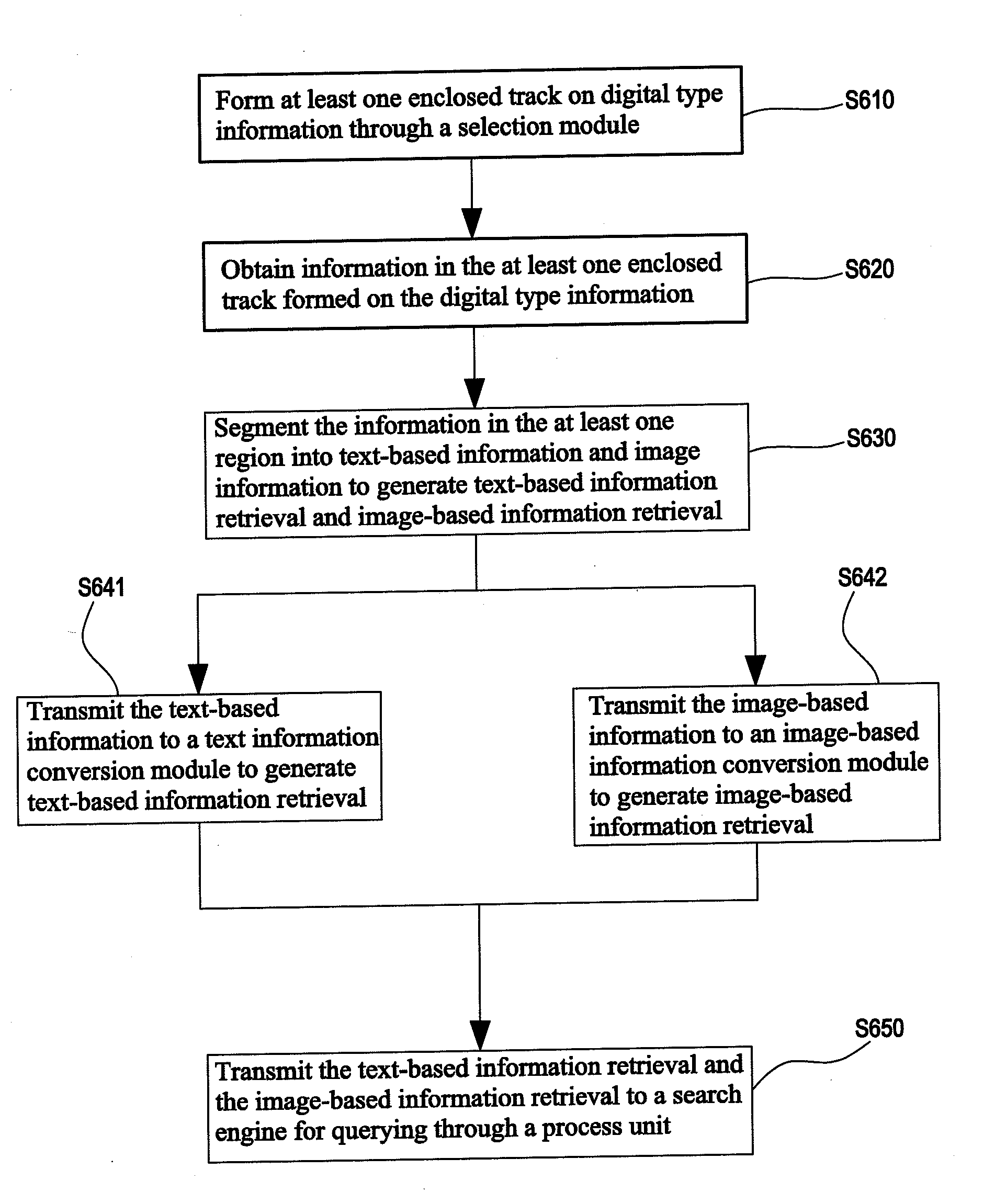

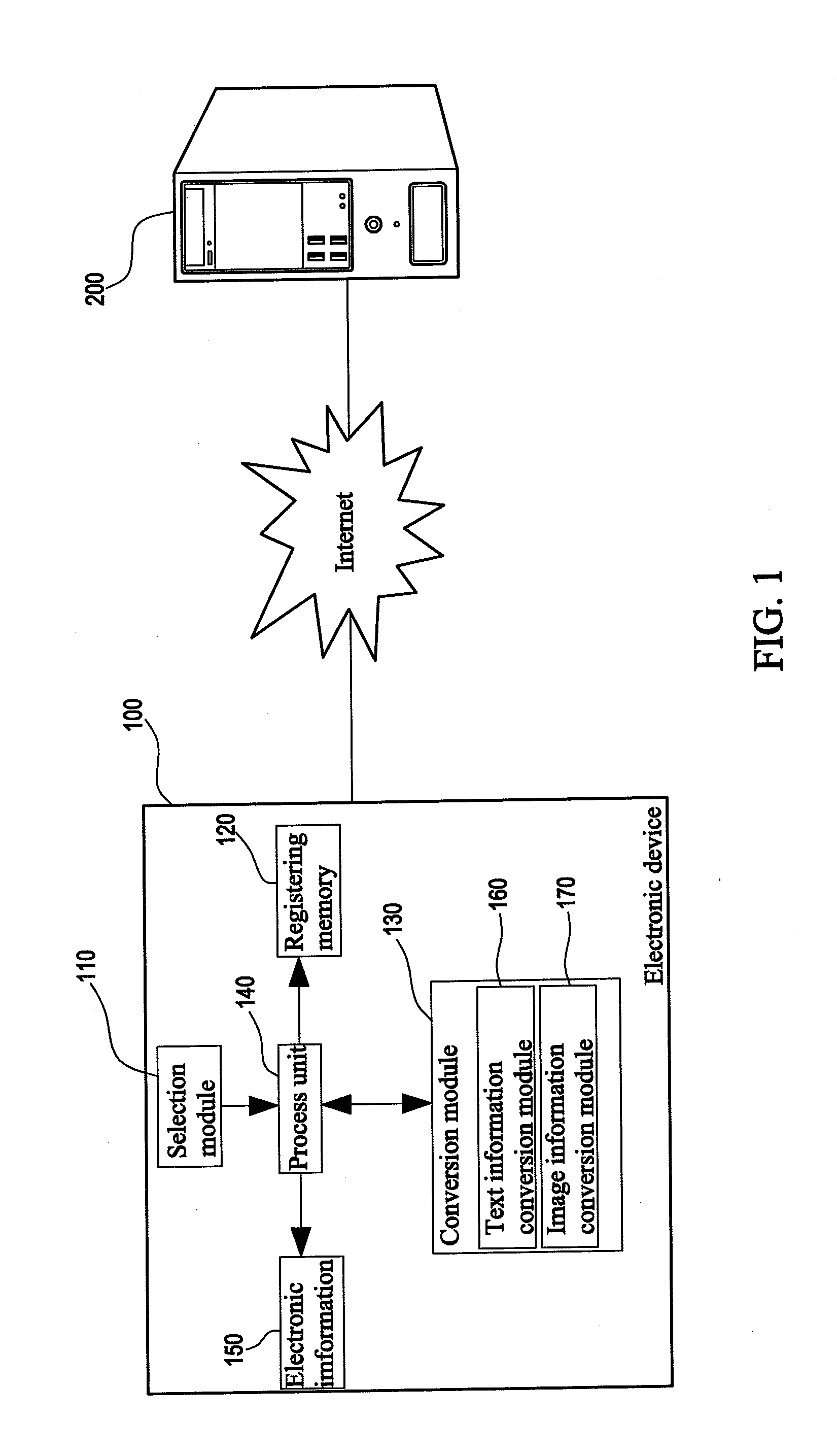

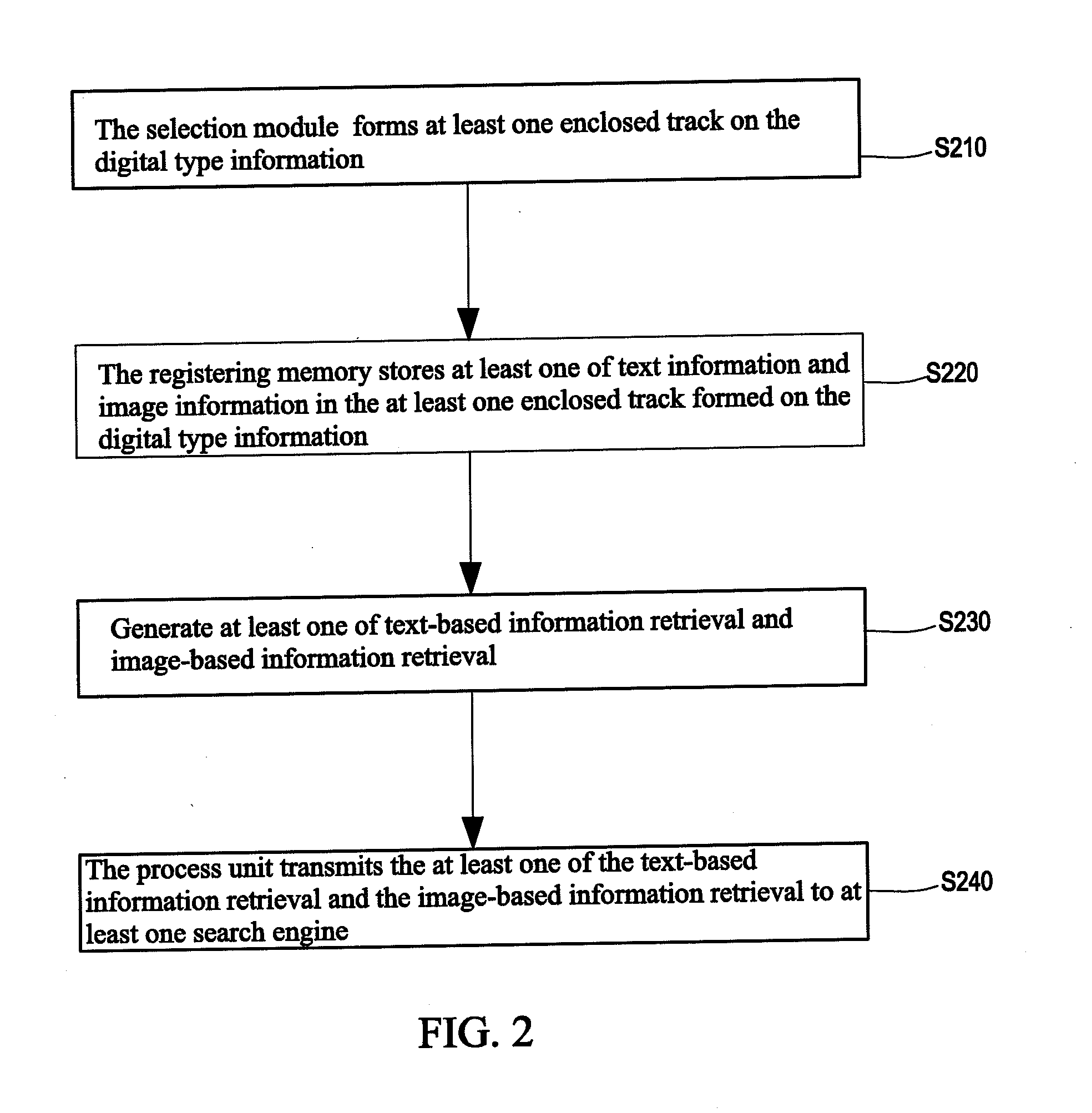

Input method for querying by using a region formed by an enclosed track and system using the same

InactiveUS20130132361A1Improve convenienceStill image data retrievalDigital data processing detailsInformation retrievalRegistered memory

An input method and a system for querying by using at least one region formed by at least one enclosed track are provided. The method mainly includes: forming at least one region on digital type information; storing at least one of text information and image information in the track into a registering memory; generating at least one of text-based information retrieval and image-based information retrieval according to the at least one of the text information and the image information; and finally, transmitting the at least one of the text-based information retrieval and the image-based information retrieval to at least one search engine for querying.

Owner:INSTITUTE FOR INFORMATION INDUSTRY

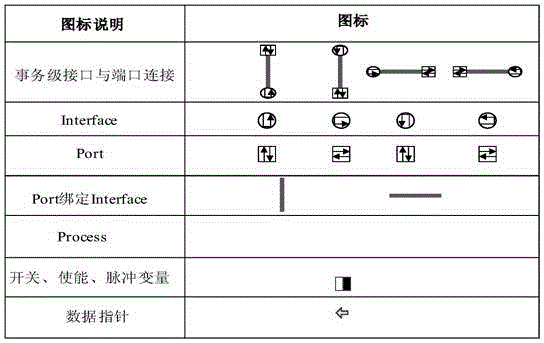

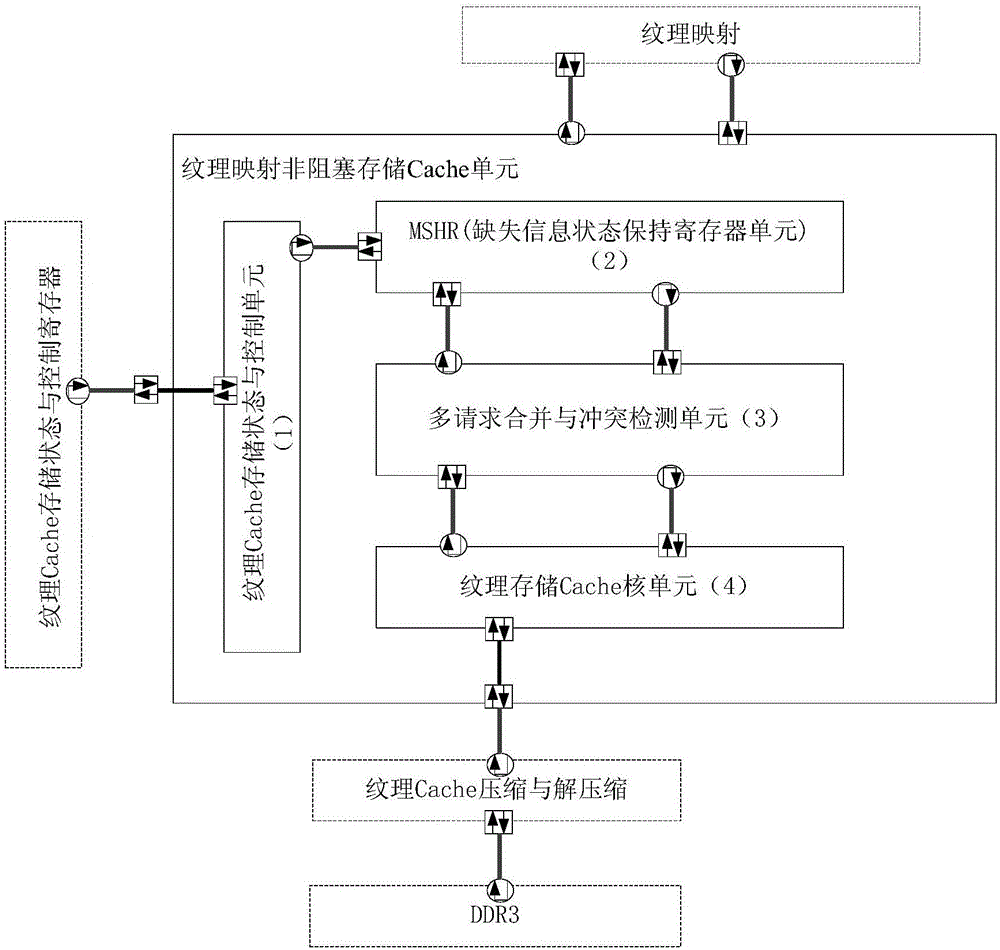

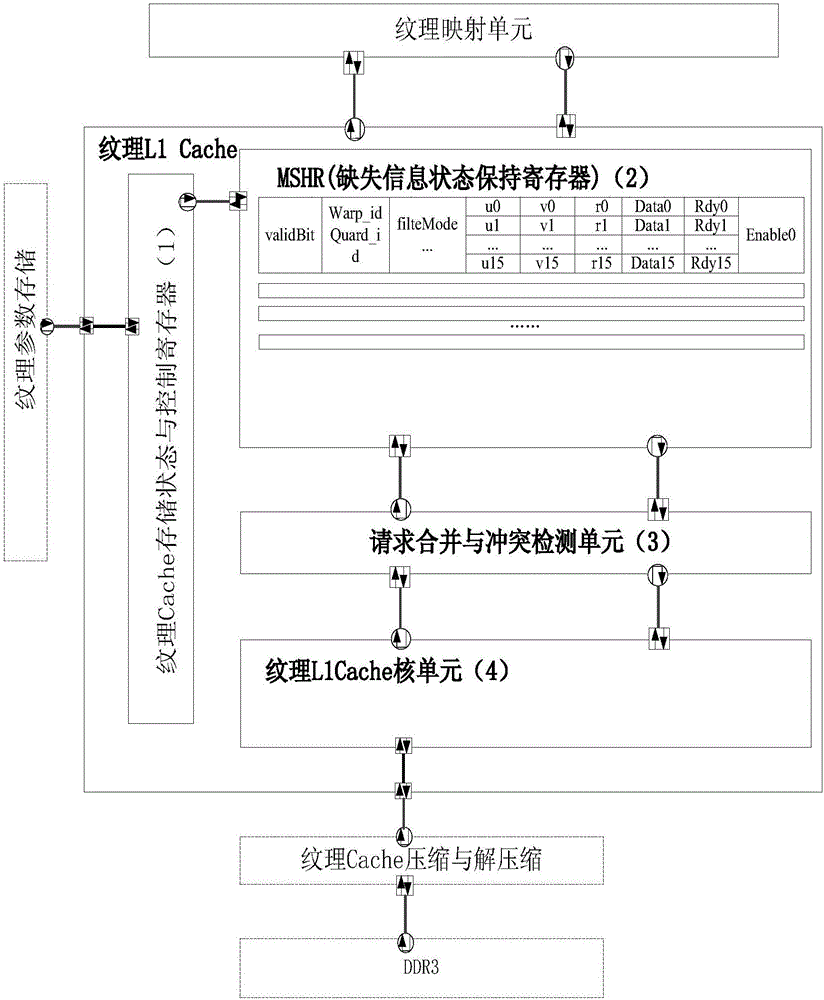

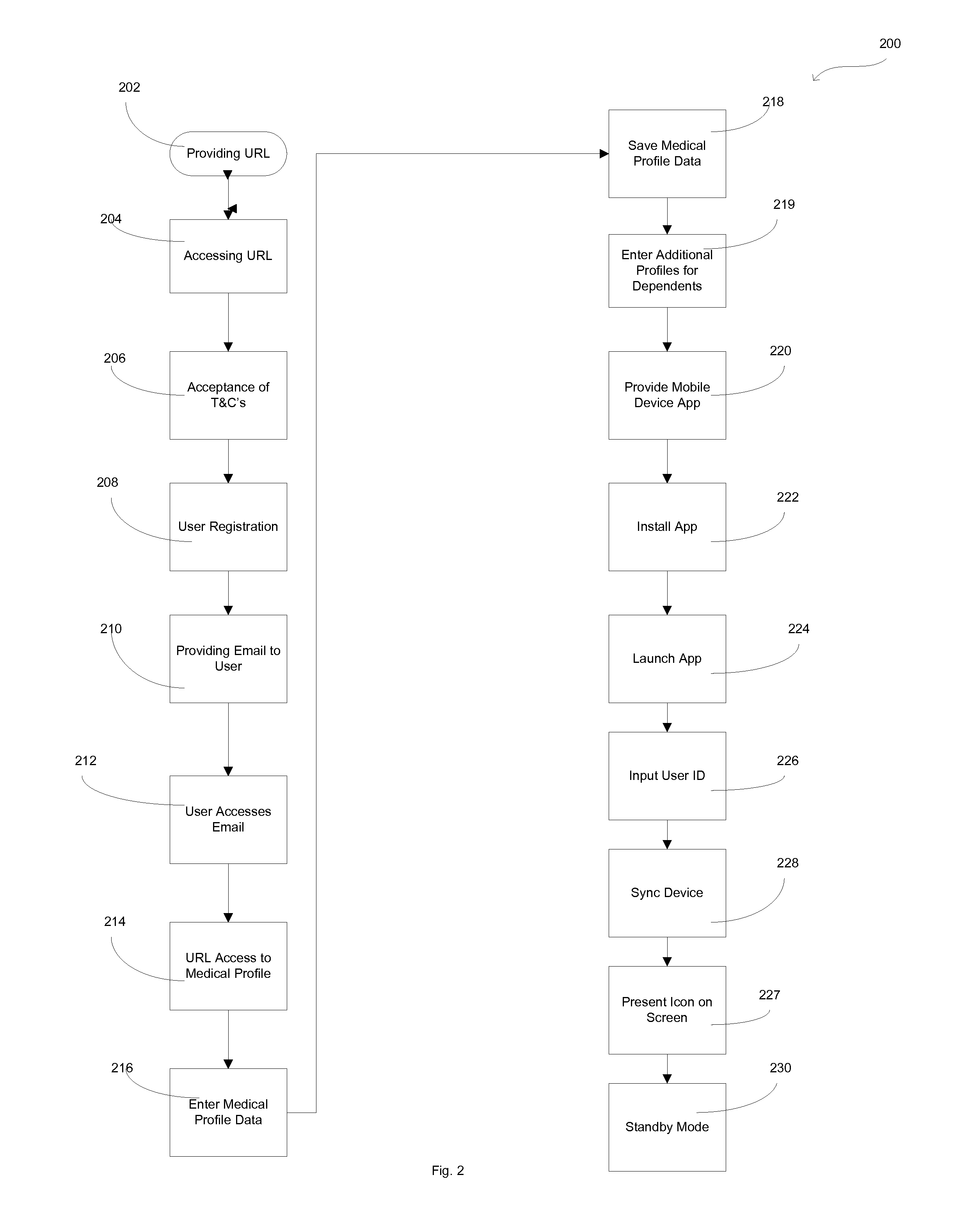

Modeling structure of GPU texture mapping non-blocking memory Cache

ActiveCN106683158AAchieving massive parallelismRealize requirementsImage memory managementProcessor architectures/configurationCollision detectionSignal design

The invention belongs to the field of computer figures, and provides a modeling structure of a GPU texture mapping non-blocking memory Cache. The modeling structure comprises a texture Cache storage status and control unit (1), a missing information status handling register memory cell (MSHR) (2), a multi-request combination and collision detection unit (3), and a texture memory Cache core unit (4). Hardware modeling with accurate periods is conducted on a texture memory Cache access process, parallel processing of texture access request data is realized through a multi-process mode including input request collision detection, request combination and division, multiple ports, multiple Banks and non-blocking flowing, and large-scale parallelism and high throughput demands of texture access data are met effectively. Moreover, the modeling structure effectively avoids configuration of complex circuit signal design and rapid assessment large-scale hardware system, is suitable for system level design and development of circuits in an early age, and provides effective reference for products and functions of the same kind.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

Retaining an Association Between a Virtual Address Based Buffer and a User Space Application that Owns the Buffer

InactiveUS20090276605A1Memory adressing/allocation/relocationMicro-instruction address formationOperational systemApplication software

Registering memory space for an application is performed. One or more open calls are received from an application to access one or more input / output (I / O) devices. Responsive to receiving the one or more open calls, one or more I / O map and pin calls are sent in order to register memory space for the one or more I / O devices within at least one storage area that will be accessed by the application. A verification is made as to whether the memory space to be registered is associated with the application. Responsive to the memory space being associated with the application, at least one virtual I / O bus address is received for each registered memory space of the one or more I / O devices. At least one I / O command is executed using the at least one virtual I / O bus address without intervention by an operating system or operating system image.

Owner:IBM CORP

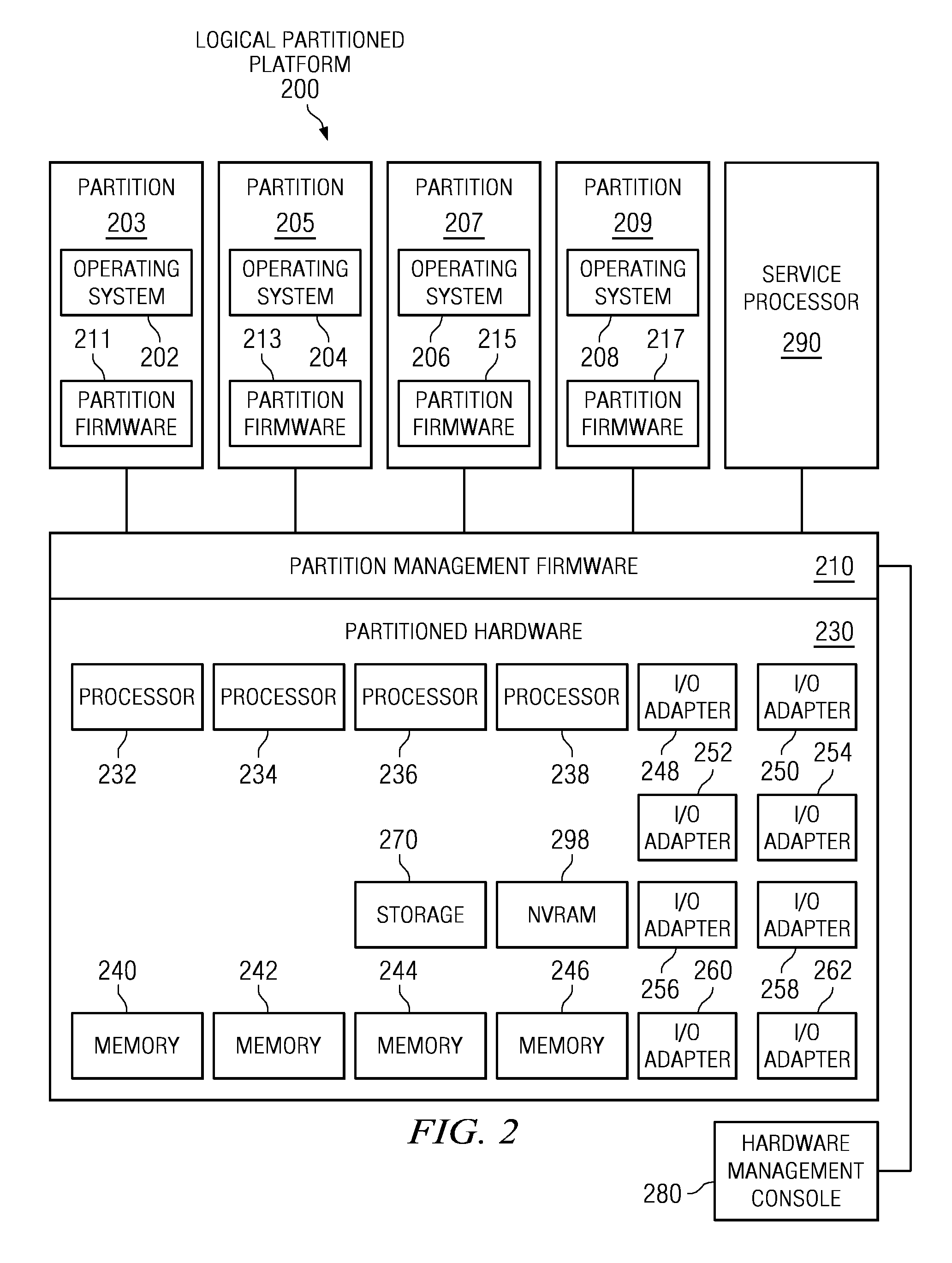

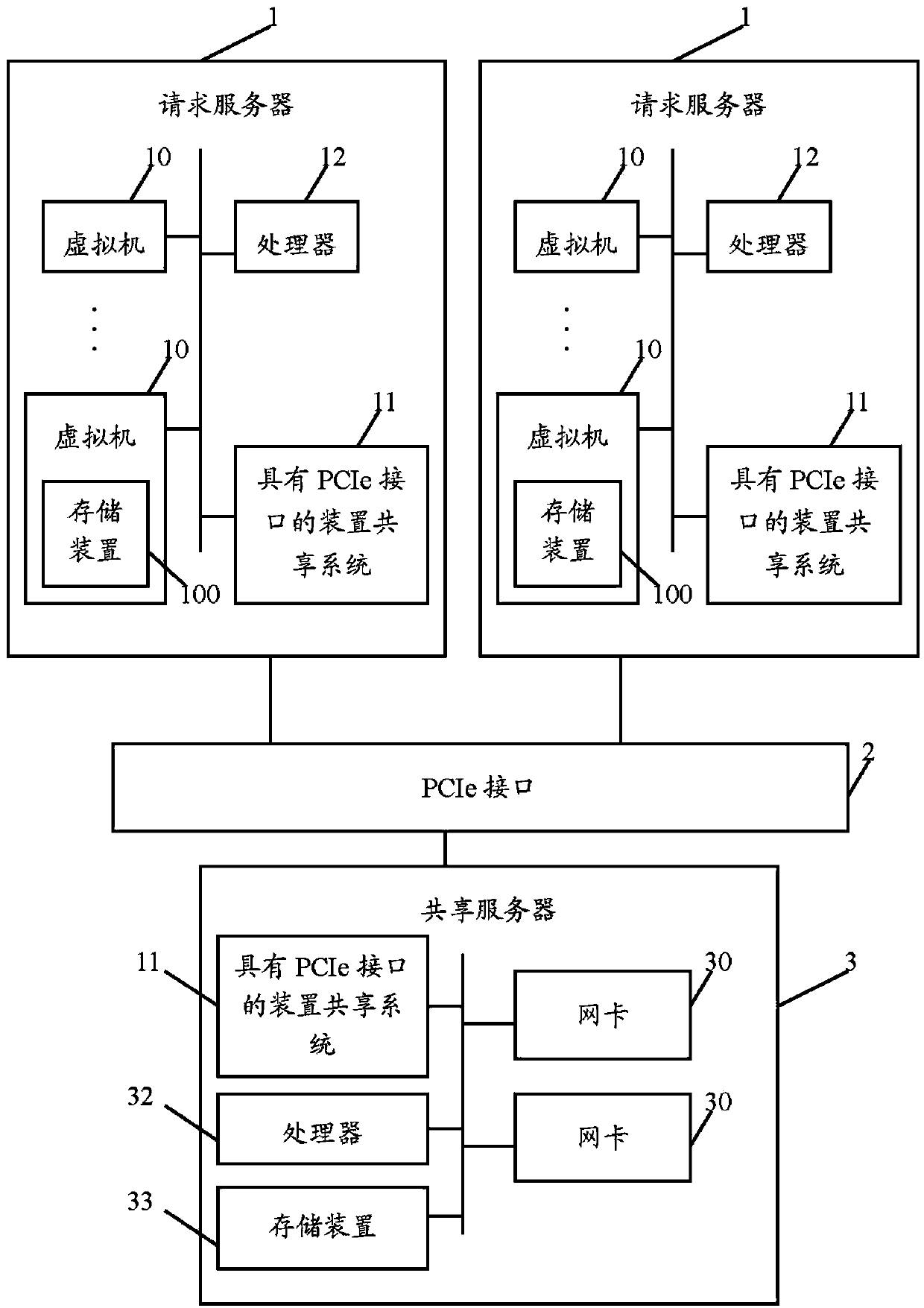

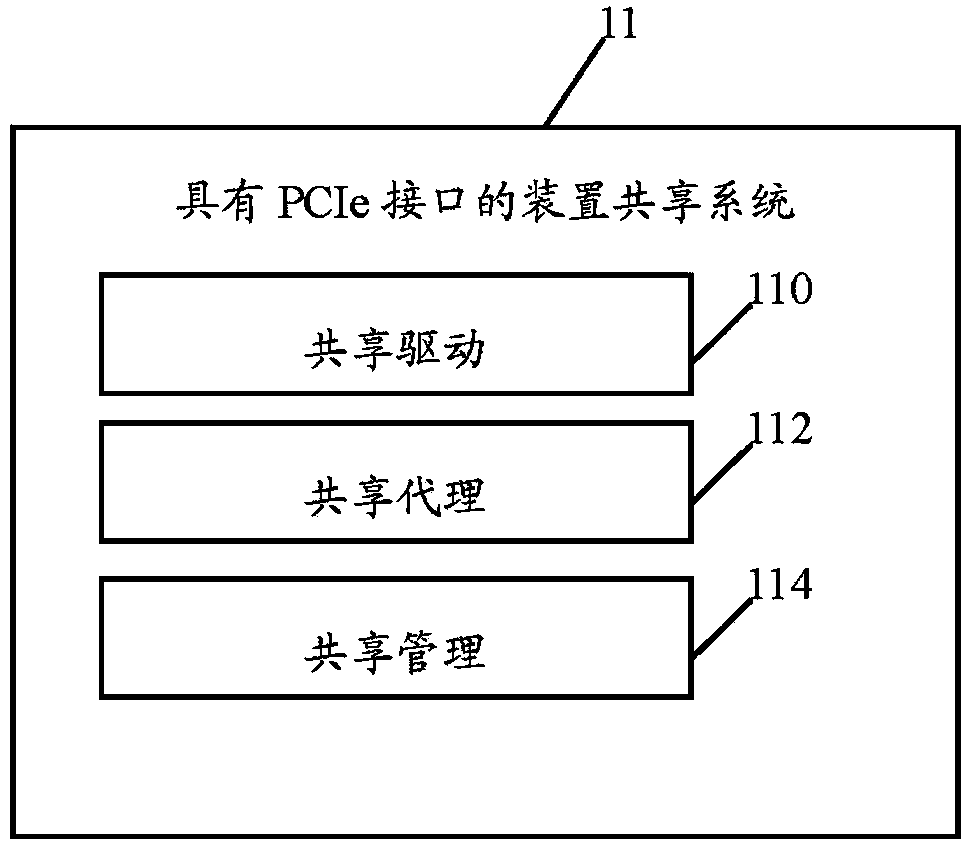

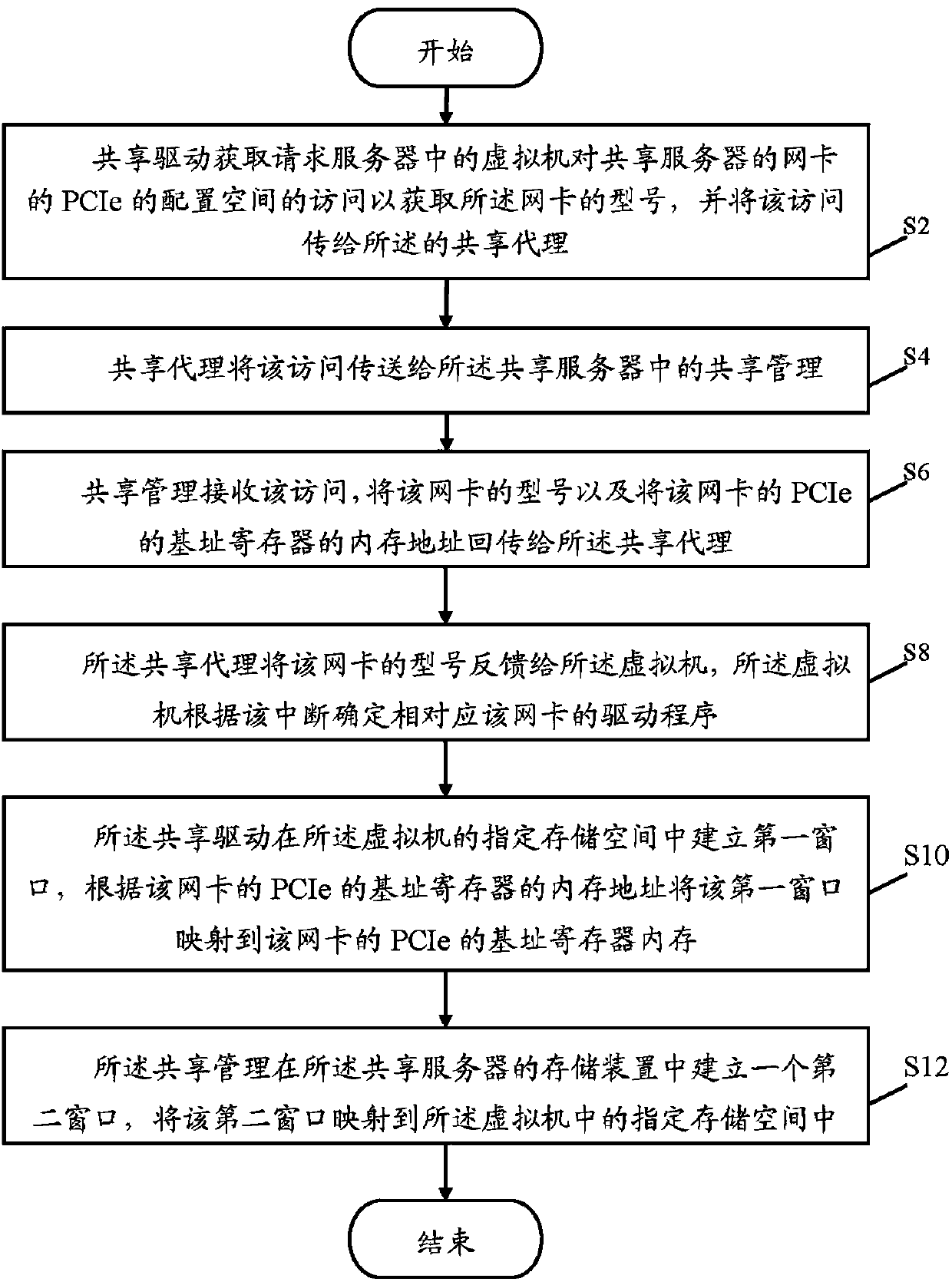

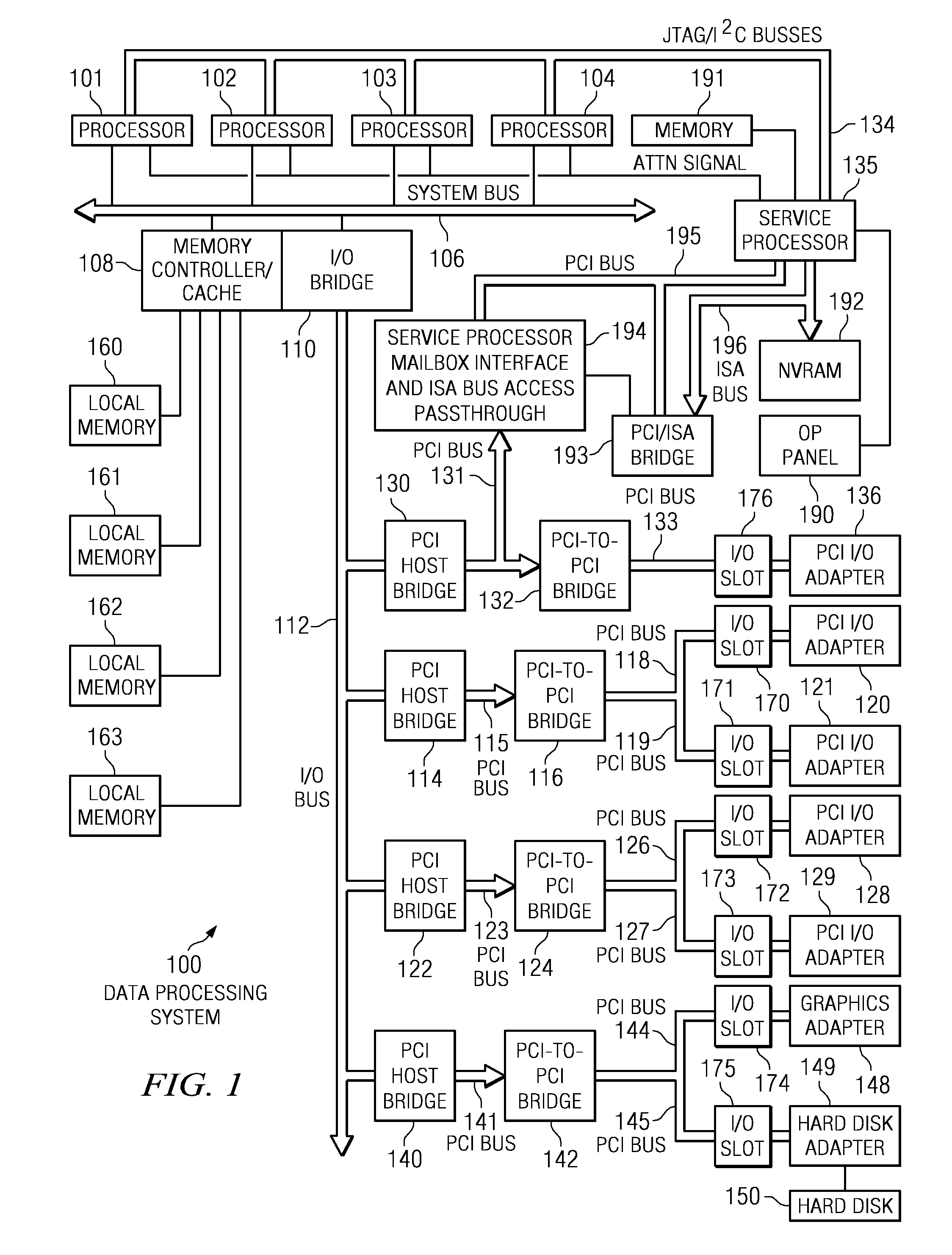

Device sharing system with PCIe interface and device sharing method with PCIe interface

InactiveCN103873489AAchieve sharingNo need to modify the driverTransmissionSoftware simulation/interpretation/emulationMemory addressProcessor register

A device sharing system with a PCIe interface runs in a request server and a shared server which provides a PCIe interface device as a to-be-shared device. A shared drive acquires the access of a virtual machine in the request server to the to-be-shared device, and a shared manager returns the model of the to-be-shared device and the memory address of a base register of a PCIe of the to-be-shared device to a shared agent according to the access. The shared drive establishes a first window in a specified storage space of the virtual machine and maps the first window to the memory of the base register of the PCIe of the to-be-shared device. The shared manager establishes a second window in a storage device of the shared server and maps the second window to the specified storage space of the virtual machine. The invention further provides a device sharing method with a PCIe interface. By adopting the device sharing system and the device sharing method of the invention, device sharing with a PCIe interface among a plurality of servers can be realized.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

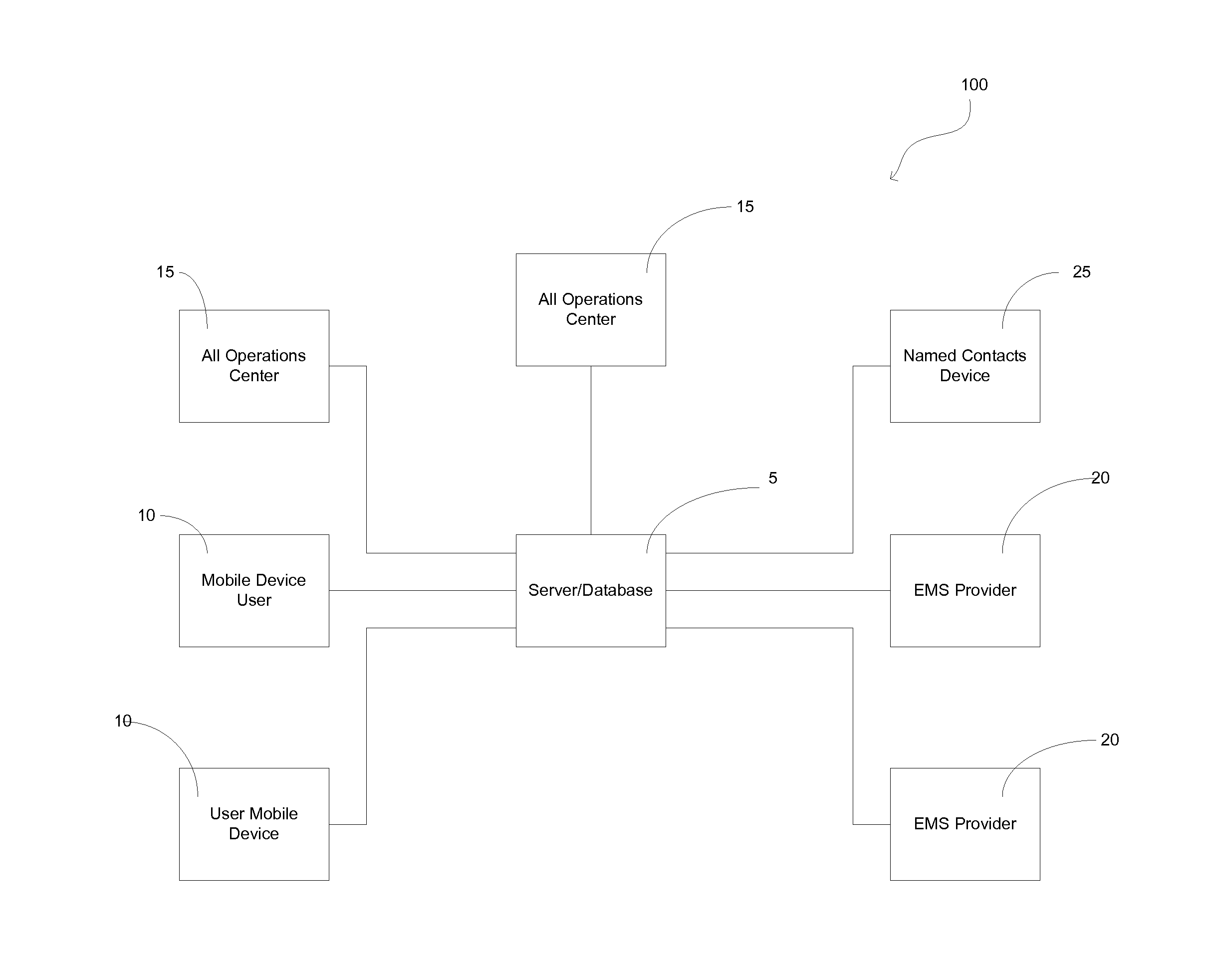

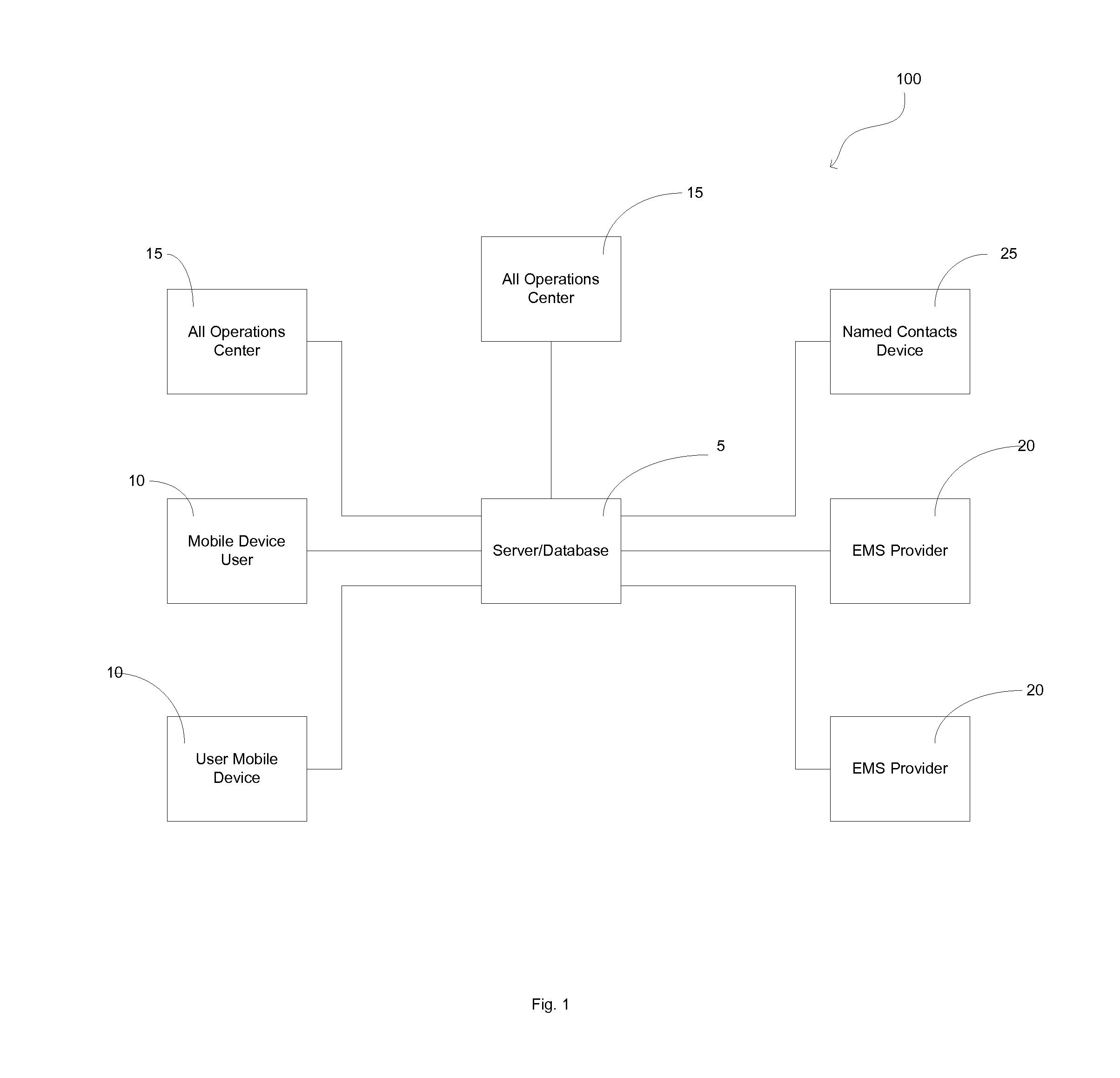

Emergency Notification System

InactiveUS20160014584A1Real-Time VisibilityGood dispersionEmergency connection handlingTelephonic communicationEmergency medical servicesApplication software

An emergency notification system and method that is operable to provide a technique for a user to transmit an emergency signal request wherein the emergency signal request is transmitted to a 911 operations center, registered EMS providers, and at least one named contact identified by the user transmitting the emergency signal request simultaneously. The emergency notification system includes a server database having control software and further includes a software application for mobile devices. The emergency notification system is operable to receive and store relevant medical data for each of the registered users of the system wherein the medical data is transmitted to emergency medical service providers during the transmission of the emergency signal request. A customized notification message is additionally sent to a predefined list of contacts during the emergency signal request. The customized notification message further includes the geographic coordinates of the user transmitting the emergency signal request.

Owner:WEBB GRANT LEWIS

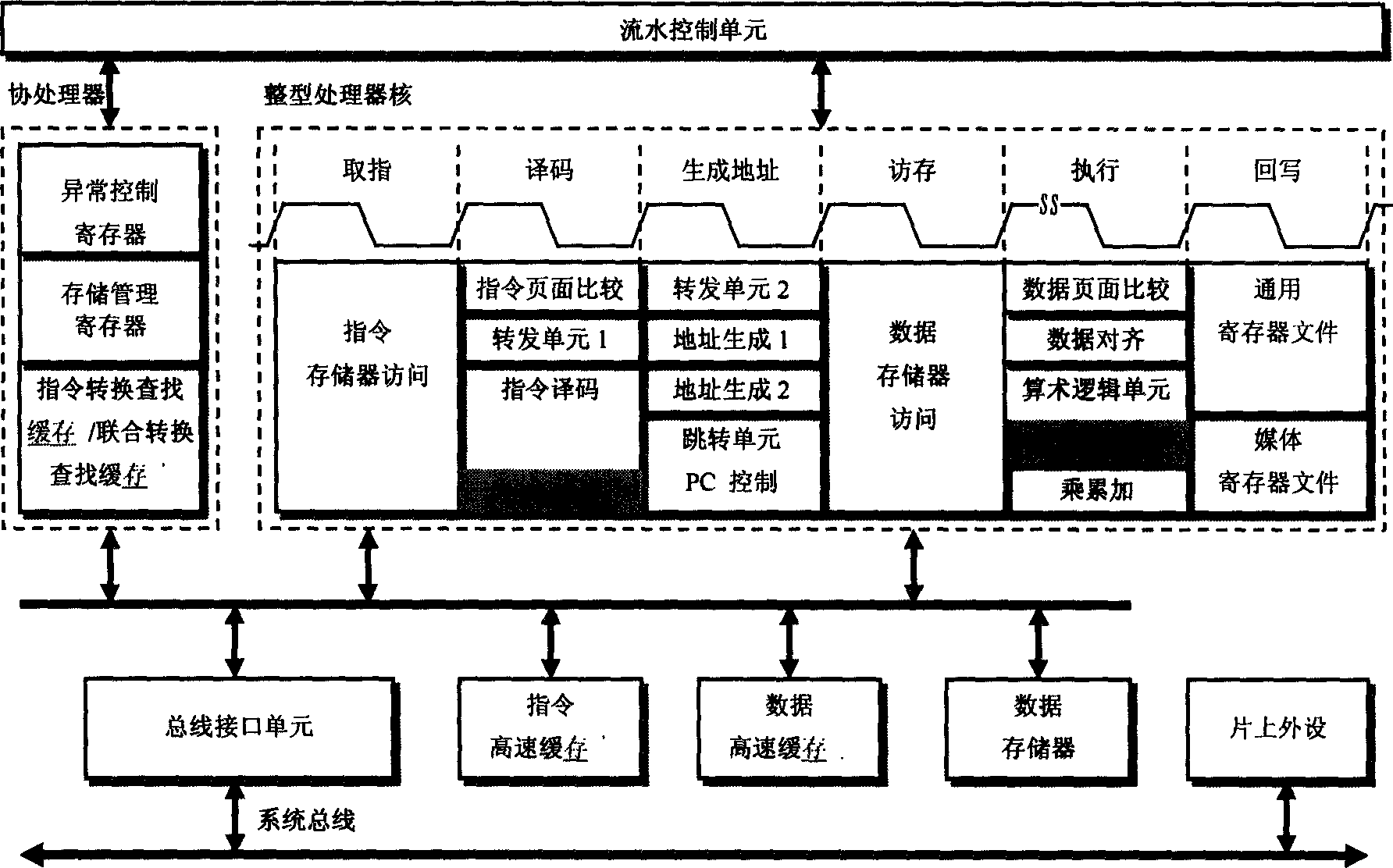

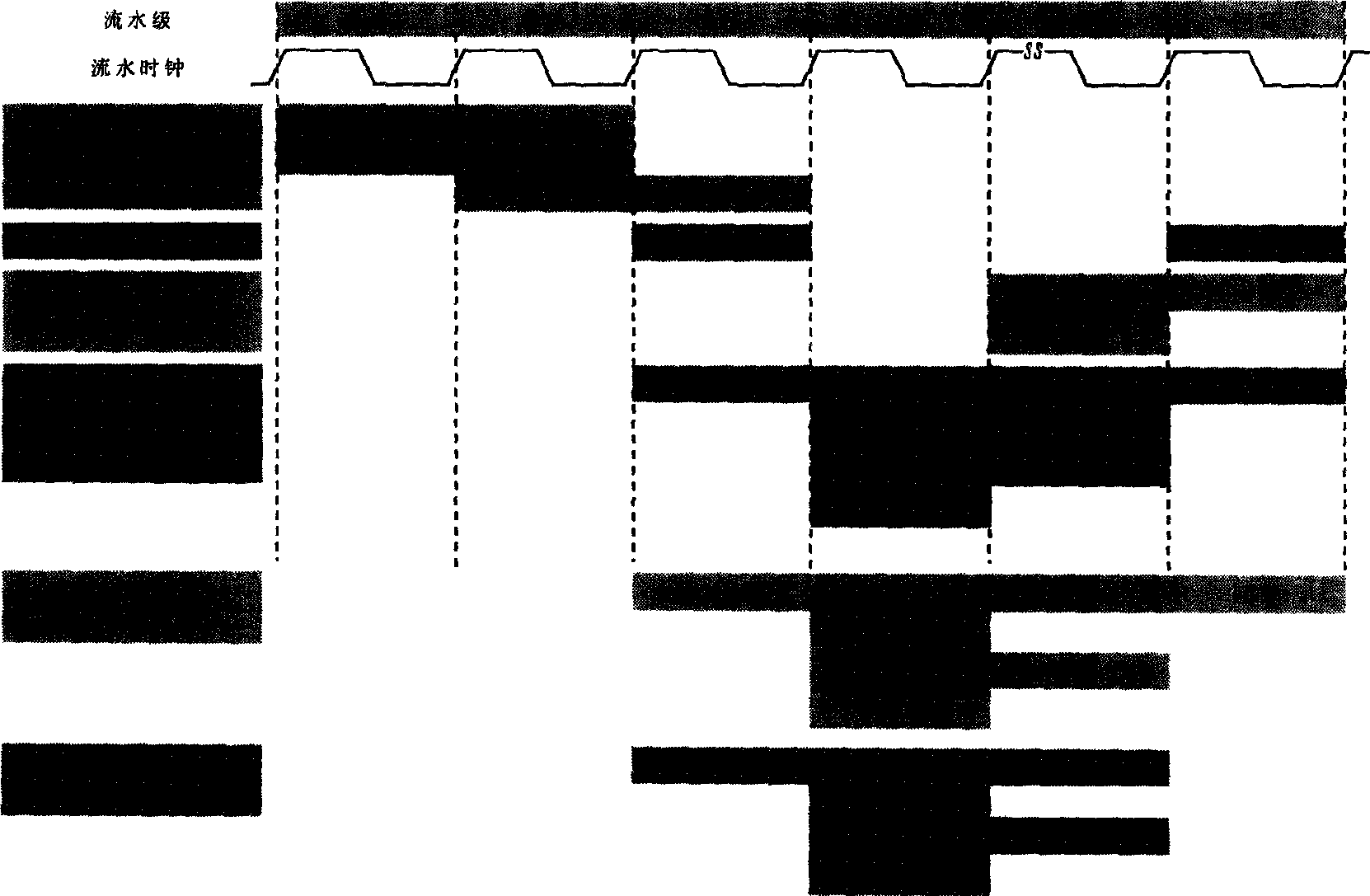

32-bit media digital signal processor

Owner:ZHEJIANG UNIV

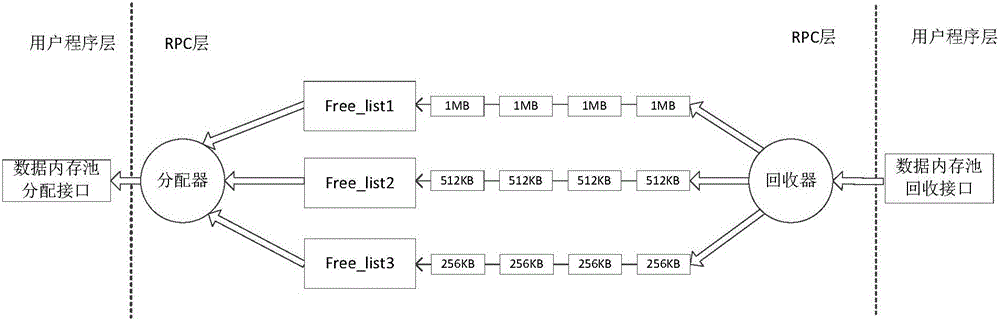

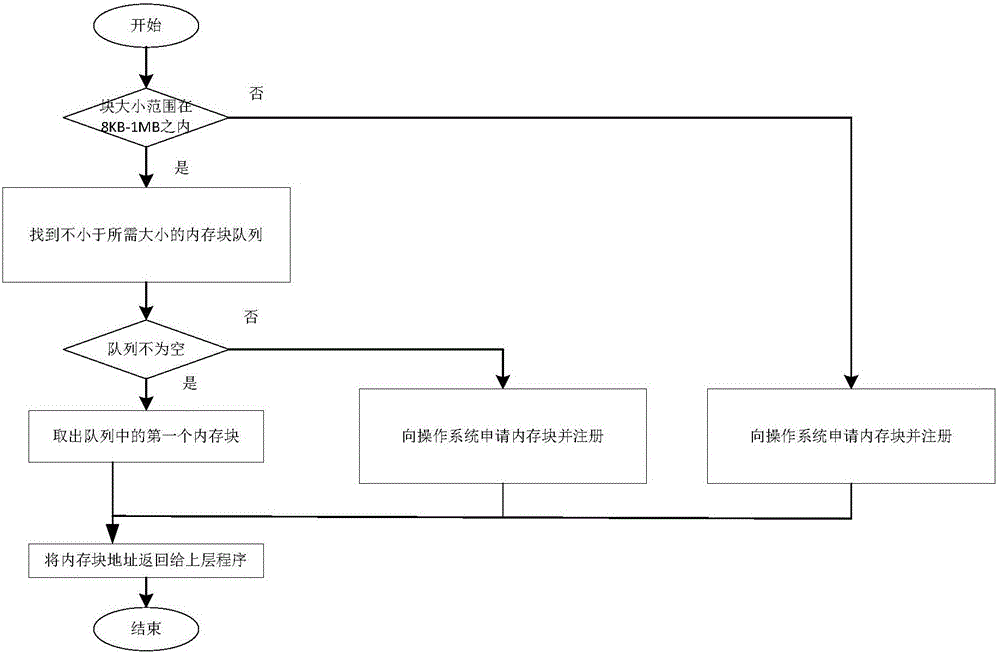

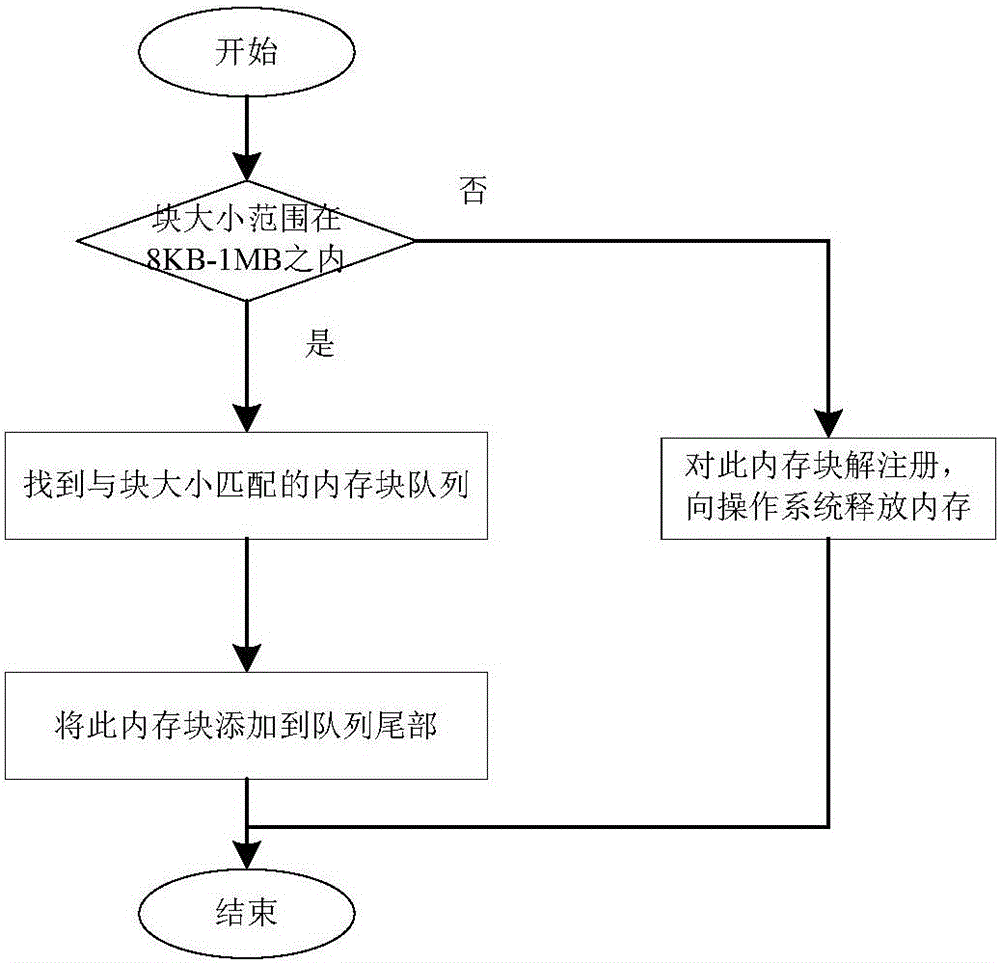

Memory management method of user-state RPC over RDMA

ActiveCN105978985AReduce registration overheadReduce the number of memory registrationsInterprogram communicationDigital computer detailsMemory management unitCopying

The invention discloses a memory management method of a user-state RPC over RDMA. A registered memory pool for storing registered memory blocks is arranged in a RPC layer, and the memory blocks are used repeatedly in transmission to achieve a goal of avoiding a registered memory; meanwhile, a memory management interface is added, so that an upper-layer user can directly use the registered memory blocks managed by the RPC layer, and memory copying between the upper-layer user and a RPC component is accordingly avoided. The memory blocks managed in the registered memory pool are fixed in size, and the scope of the block size can be configured based on the actual use. The memory management method of the user-state RPC over RDMA can efficiently reduce the memory registration number when the RPC component adopts the RDMA way for transmission, and has an effect of reducing the memory registration expense.

Owner:HUAZHONG UNIV OF SCI & TECH

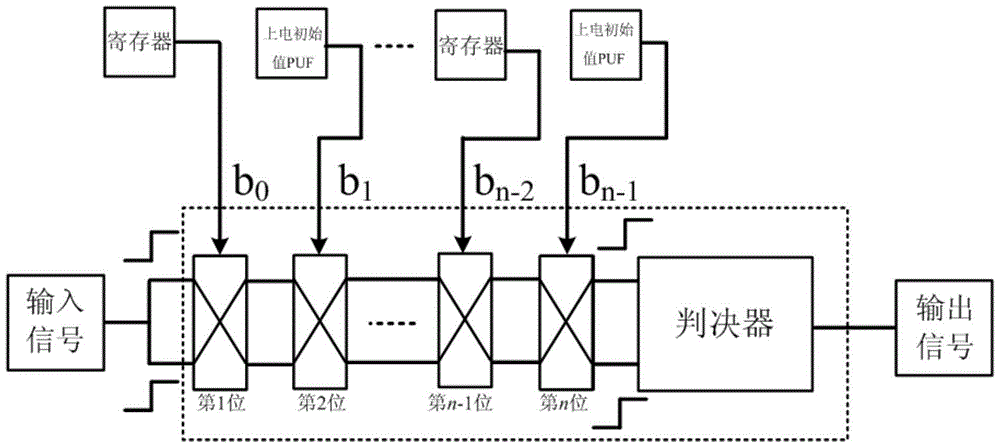

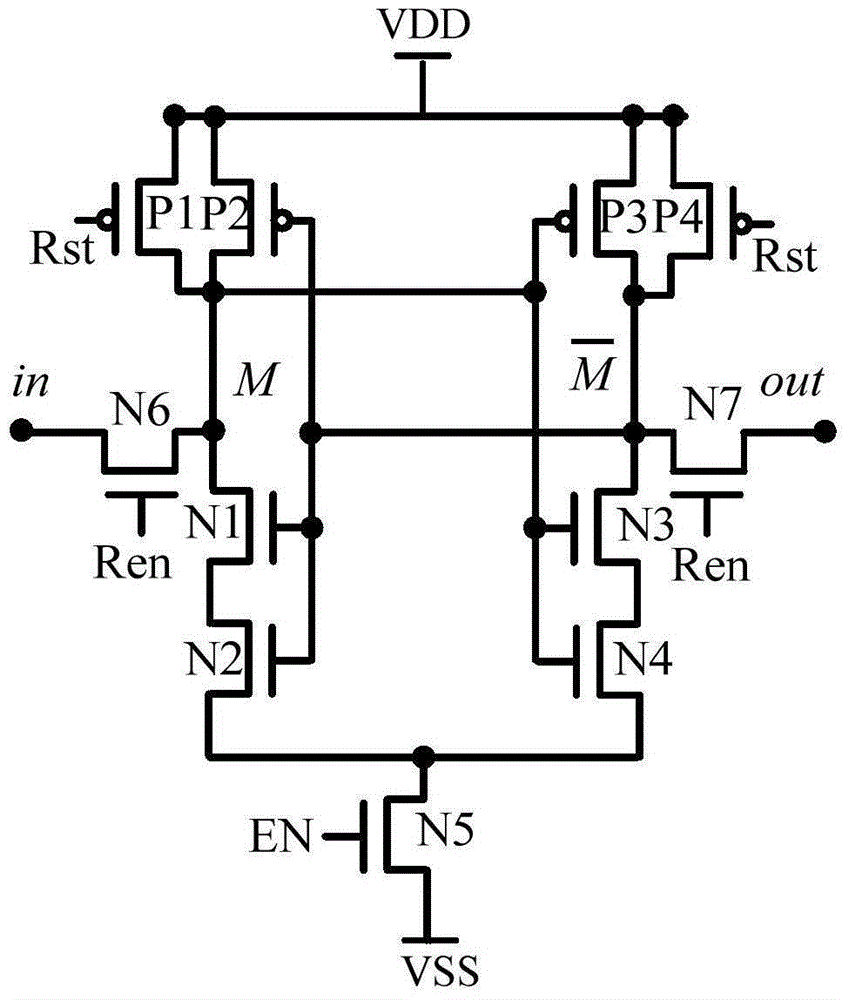

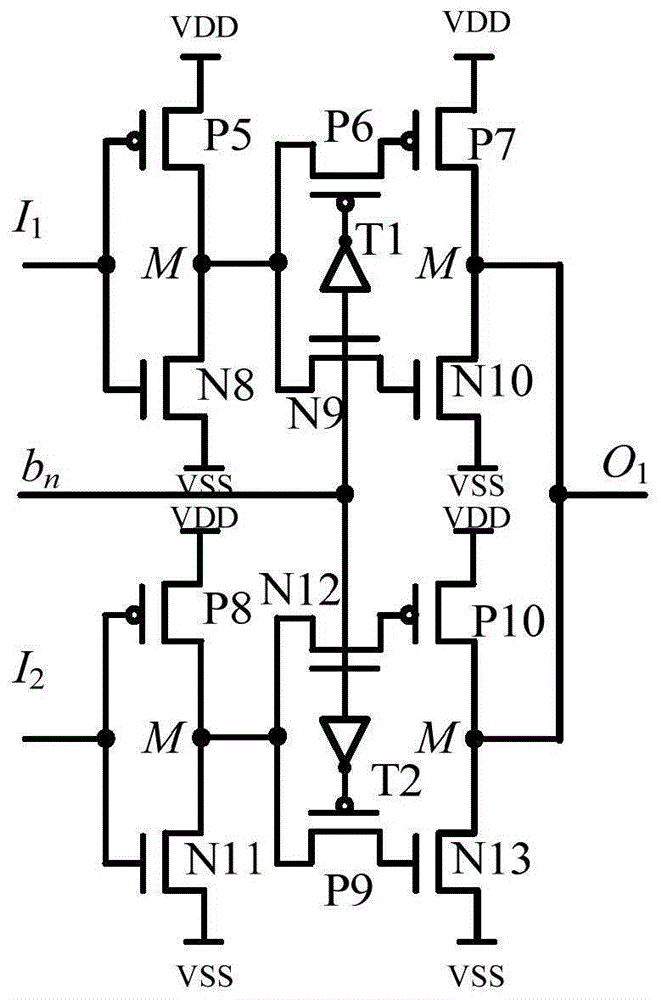

Hybrid PUF circuit

ActiveCN105227176AImprove reliabilityIncrease randomnessLogic circuitsControl signalExcitation signal

The invention discloses a hybrid PUF circuit, comprising a basic PUF circuit and a control PUF circuit, wherein a decision type PUF circuit achieves the basic PUF circuit, a register and an initial electrification value PUF circuit are alternately arranged to achieve the control PUF circuit, a control signal stored in the register and a signal generated by the initial electrification value PUF circuit are spliced to form n bits of excitation signals to serve as enabling signals of the basic PUF circuit, each bit of excitation signal needs to pass through two different delay paths composed of a first delay circuit unit and a second delay circuit unit in the basic PUF circuit, the output data of the basic PUF circuit are generated by a delay difference between the two delay paths, in the two delay paths, each delay circuit unit completes an on-off operation according to the corresponding excitation signal, determines to propagate a rising edge signal linearly or crosswise and finally generates a PUF output signal through a decision device; and the hybrid PUF circuit has the advantages of higher reliability and randomness and stronger model attack and machine learning attack resistance.

Owner:NINGBO UNIV

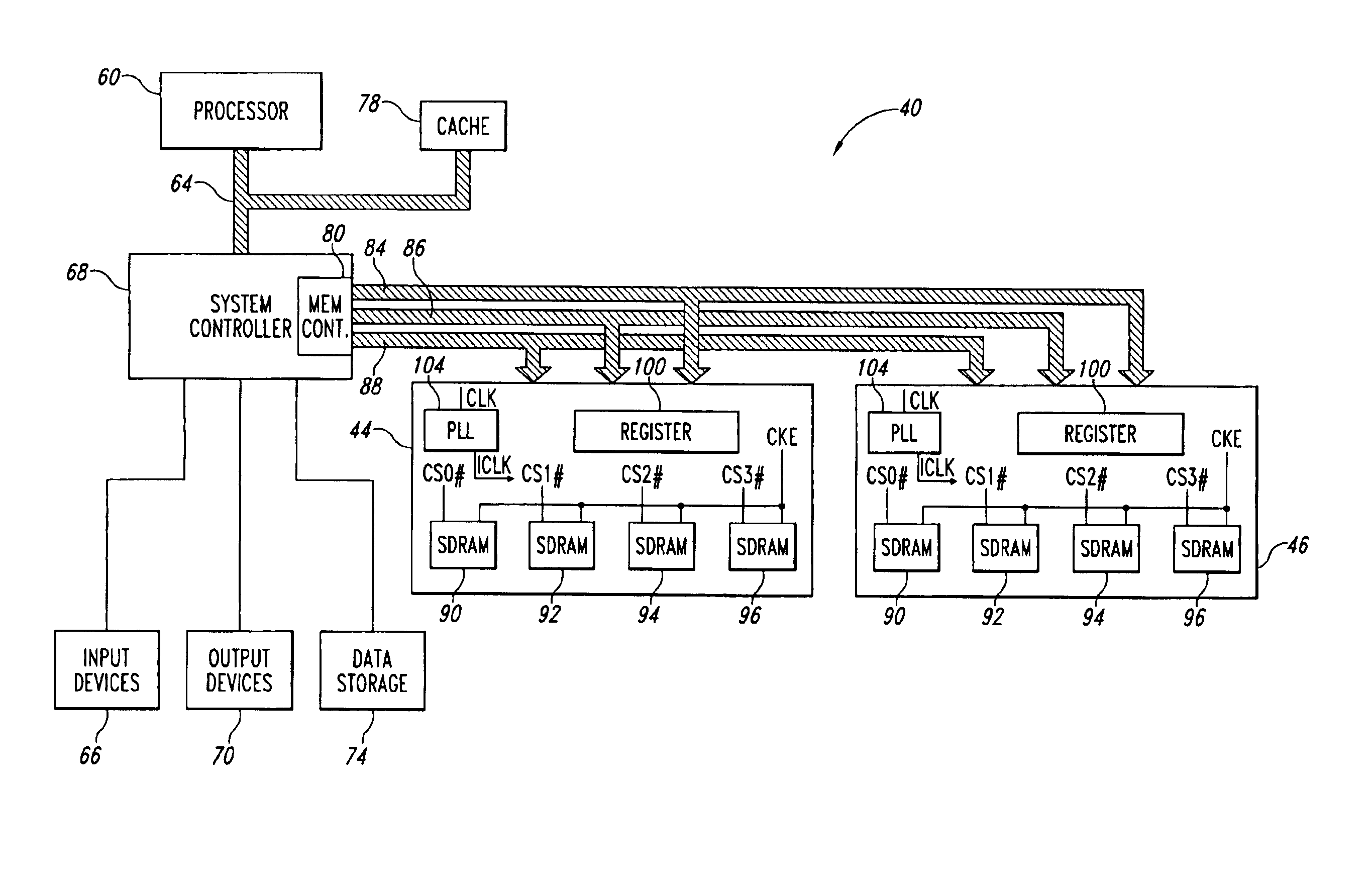

Reduced power registered memory module and method

A registered memory module includes a plurality of flip-flops having respective data terminals, respective clock terminals receiving a clock signal and output terminals coupled to a plurality of SDRAM devices in the module. A logic gate decodes respective chip select signals for selecting the SDRAM devices. The logic gate generates an enable signal if a memory access is being directed to any of the SDRAM devices in the module. In one embodiment, the flip-flops include an enable input coupled to receive the enable signal from the logic gate. In another embodiment, the input signals are coupled to the data inputs of the flip-flops through logic gates that are selectively enabled by the enable signal from the logic gate. As a result, the input signals are not latched by transitions of the clock signal when a memory access is not directed to any of the SDRAM devices in the module.

Owner:ROUND ROCK RES LLC

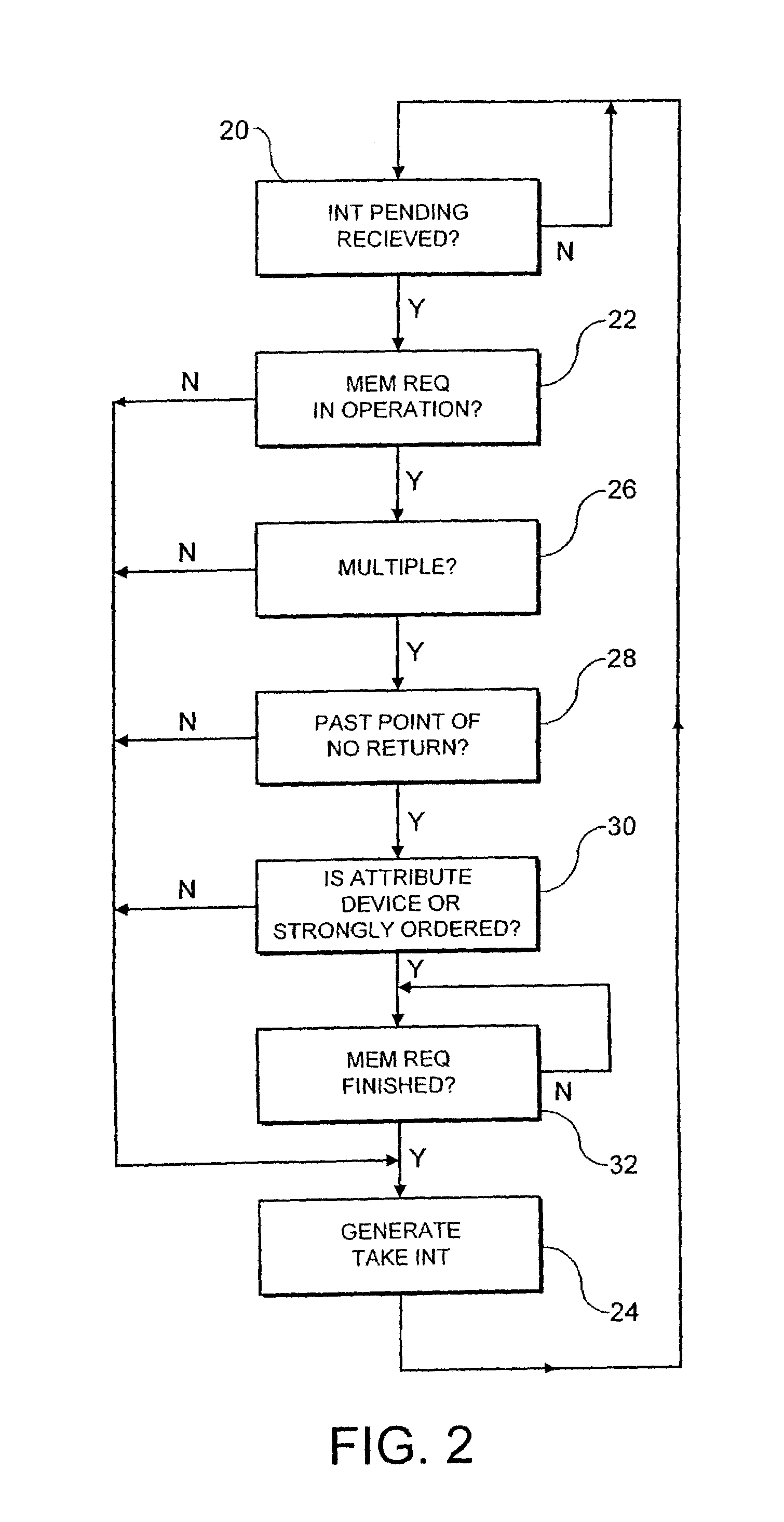

Handling interrupts during multiple access program instructions

ActiveUS7047401B2Increase code densityEfficient reuseProgram initiation/switchingDigital computer detailsData valueProgram instruction

A data processing apparatus 2 supports multiple memory access program instructions LDM, STM which serve to load data values from multiple program registers 16 to respective memory locations or to store data values from multiple memory locations to respective program registers. A memory management unit 8 within the system stores device or strongly ordered memory attribute values which control whether or not a multiple memory access instruction involving such a memory location may be early terminated when an interrupt is received during its operation. Early termination is permitted in those circumstances where the multiple memory access instruction may be safely restarted and rerun in its entirety, whereas early termination is not permitted and the operation completes before the interrupt is taken in those circumstances where the memory locations are subject to a guaranteed number of memory accesses as this appears within the controlling program instructions.

Owner:ARM LTD

Memory module and method having improved signal routing topology

InactiveUS7242213B2Reliability increasing modificationsFinal product manufactureError checkSignal routing

A registered memory module includes several memory devices coupled to a register through a plurality of transmission lines forming a symmetrical tree topology. The tree includes several branches each of which includes two transmission lines coupled only at its ends to either another transmission line or one of the memory devices. The branches are arranged in several layers of hierarchy, with the transmission lines in branches having the same hierarchy having the same length. Each transmission line preferably has a characteristic impedance that is half the characteristic impedance of any pair of downstream transmission lines to which it is coupled to provide impedance matching. A dedicated transmission line is used to couple an additional memory device, which may or may not be an error checking memory device, to the register.

Owner:ROUND ROCK RES LLC

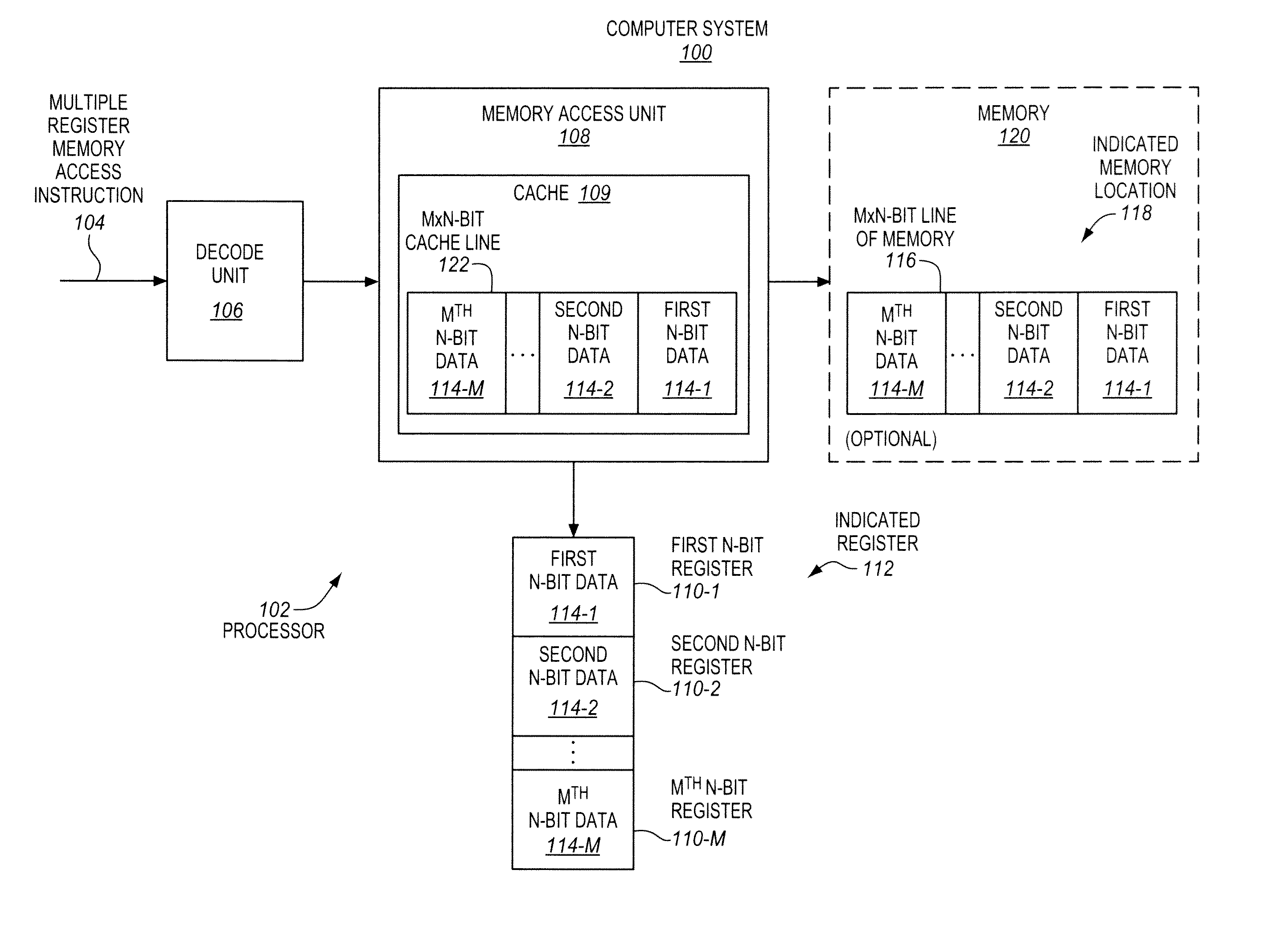

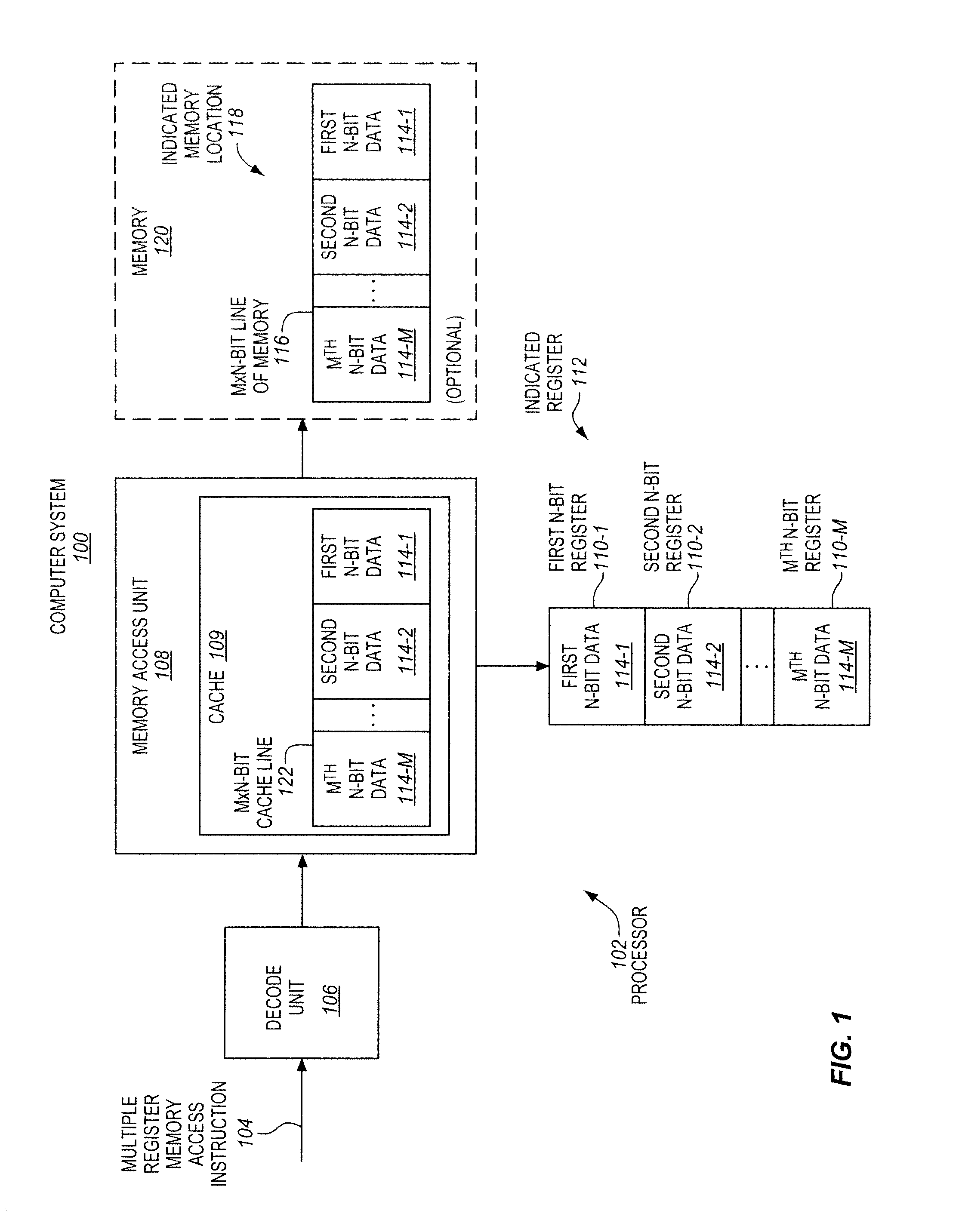

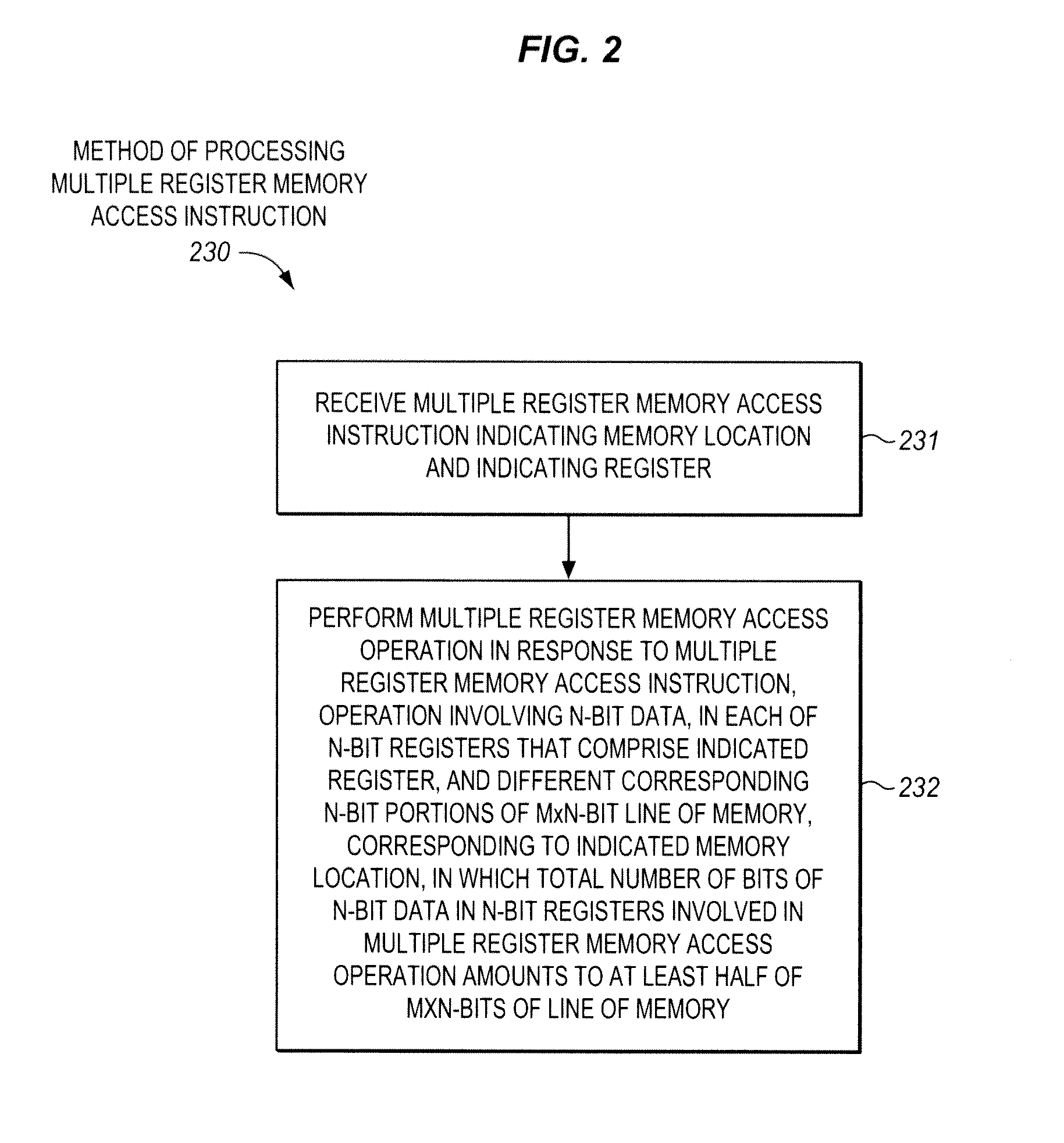

Multiple register memory access instructions, processors, methods, and systems

ActiveUS20150006848A1General purpose stored program computerDigital storageBit lineParallel computing

A processor includes N-bit registers and a decode unit to receive a multiple register memory access instruction. The multiple register memory access instruction is to indicate a memory location and a register. The processor includes a memory access unit coupled with the decode unit and with the N-bit registers. The memory access unit is to perform a multiple register memory access operation in response to the multiple register memory access instruction. The operation is to involve N-bit data, in each of the N-bit registers comprising the indicated register. The operation is also to involve different corresponding N-bit portions of an M×N-bit line of memory corresponding to the indicated memory location. A total number of bits of the N-bit data in the N-bit registers to be involved in the multiple register memory access operation is to amount to at least half of the M×N-bits of the line of memory.

Owner:INTEL CORP

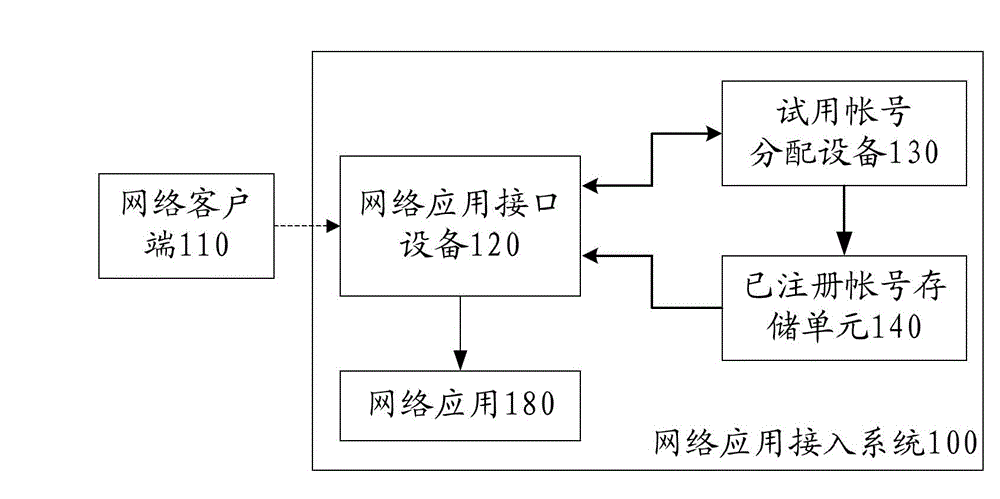

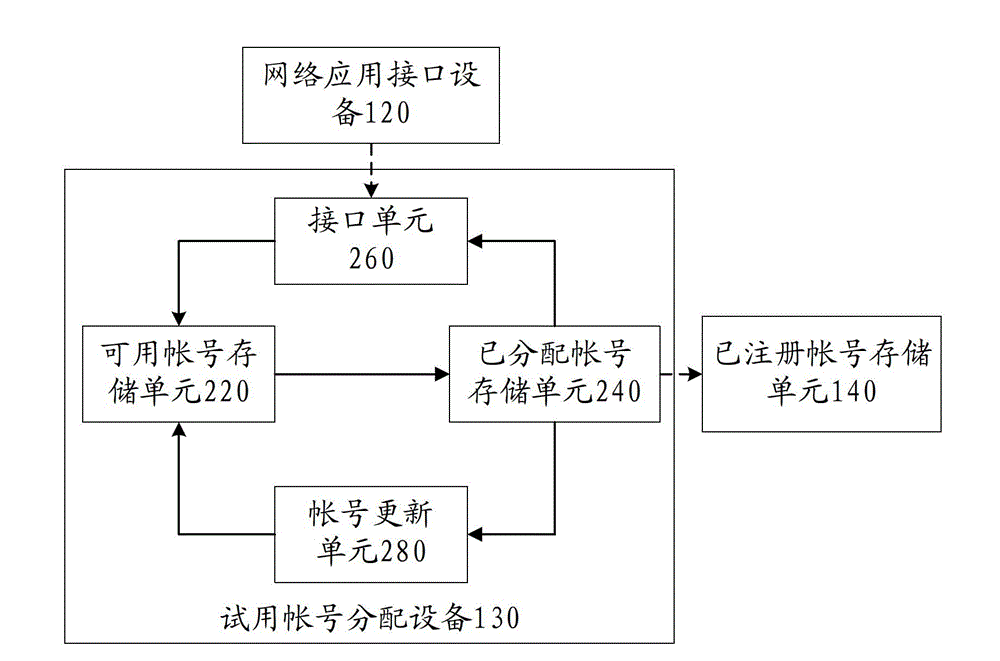

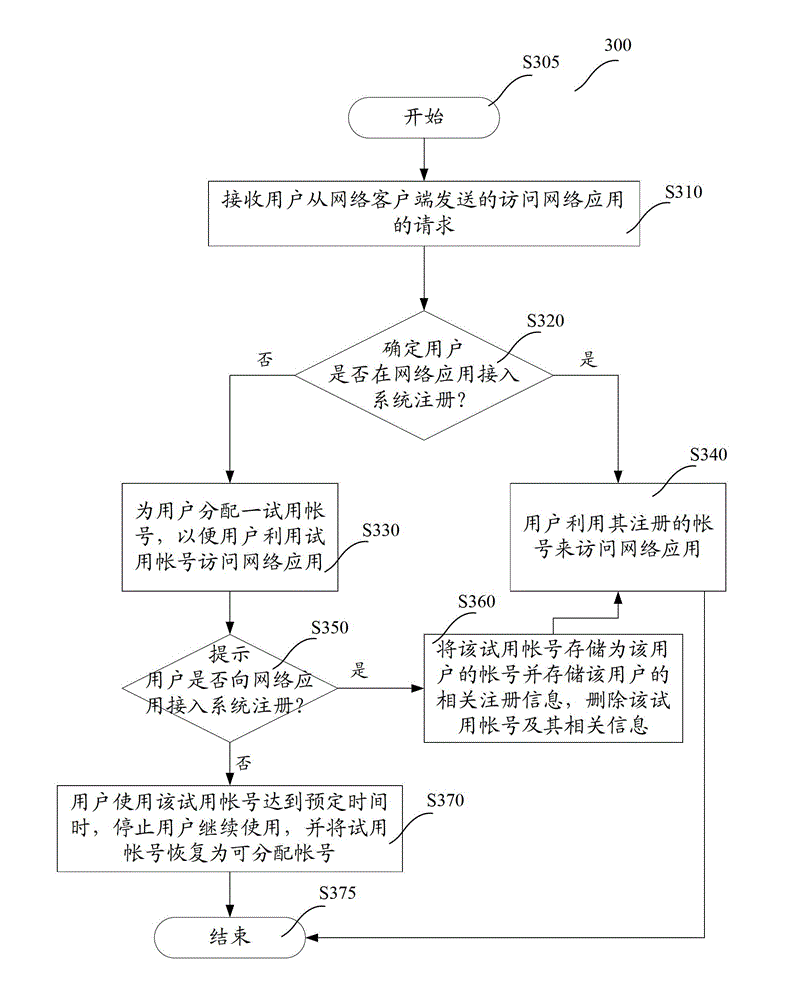

Network application access method and system

The invention discloses a network application access method used for accessing to one or more of network applications through a network application access system, wherein the network application access method comprises: receiving a request of accessing network application sent by a user from a network client, and determining whether the user is registered; distributing a trial account number to the user to enable the user to access to the network application through the trial account number if the user is a non-registered user; the user accesses to the network application through the registered account number if the user is a registered user, wherein the step of determining whether the user is registered comprises: determining the user as a non-registered user if the account number of the user is not contained in the access request, or if the contained account number is nonexistent or is null value; and determining the user as a registered user if the account number of the user contained in the access request exists. Furthermore, the invention further provides a network application access system. The network application access method and system provided by the invention can be used for shortening the route of the non-registered user entering the corresponding network application on a webpage application platform and reducing the user loss caused by complex procedures.

Owner:BEIJING QIHOO TECH CO LTD +1

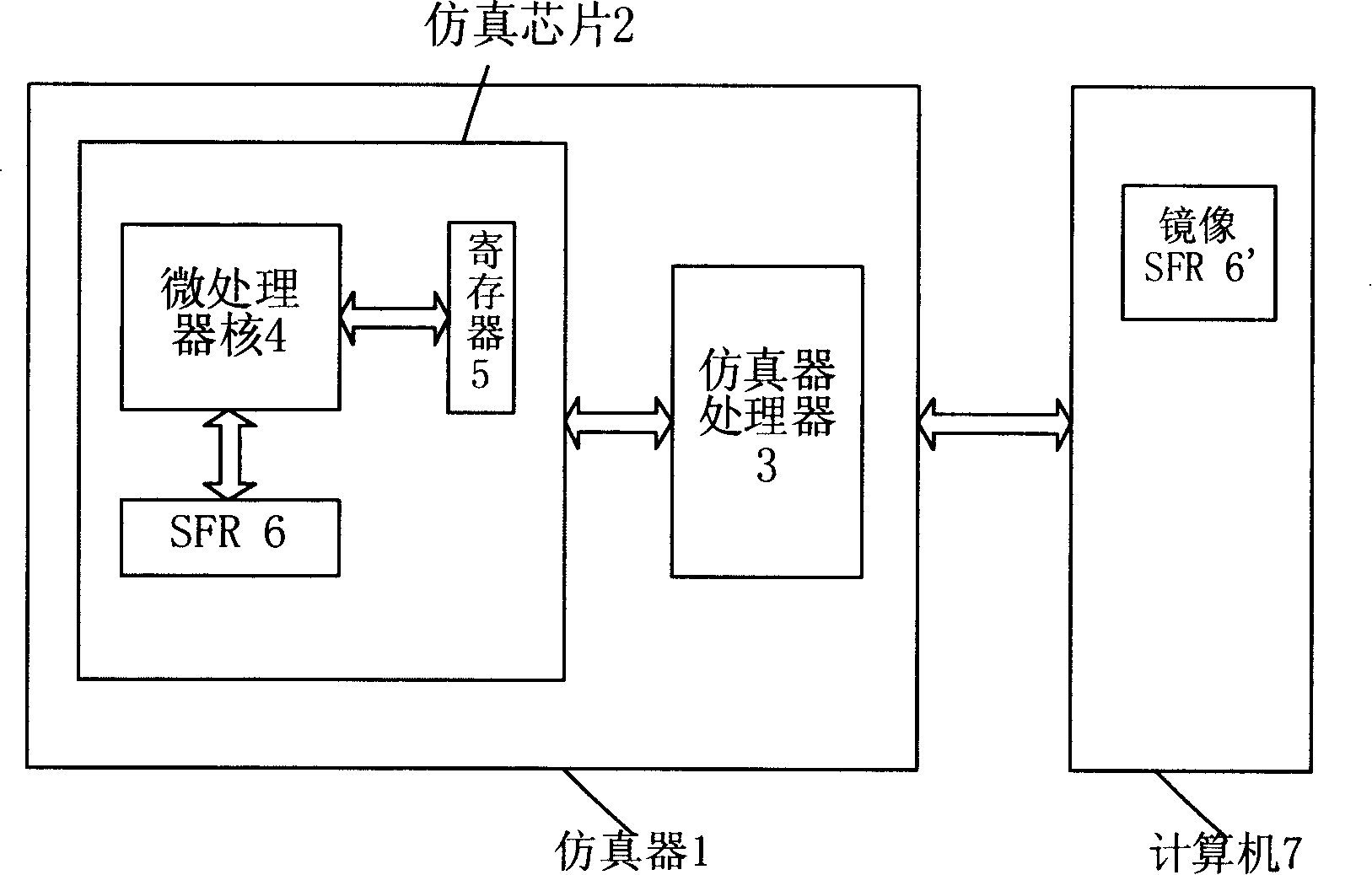

Simulator for simulating register with specific function

InactiveCN101206614AWill not affect operationImprove debugging efficiencySoftware testing/debuggingMonitoring statusSpecial function register

The present invention discloses a simulator simulating special function register, comprising a simulation chip and a simulator processor. A general register is arranged inside the simulation chip, and when the simulator is in monitoring state, a microprocessor core of the simulation chip can automatically store a current reading / writing operation FIFO count pointer value of a SFR realized in the FIFO mode into the register. After the microprocessor core of the simulation chip executes reading / writing operation to the SFR, the microprocessor core can automatically update the value in the register. The simulator processor can automatically read the value stored in the register. The simulator processor can send commands or commands and data to the simulation chip, and the microprocessor core carries out reading / writing operation to the SFR. The present invention provides reliable and convenient means for debugging the SFR of the type, and can effectively improve the debugging efficiency of user programs.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

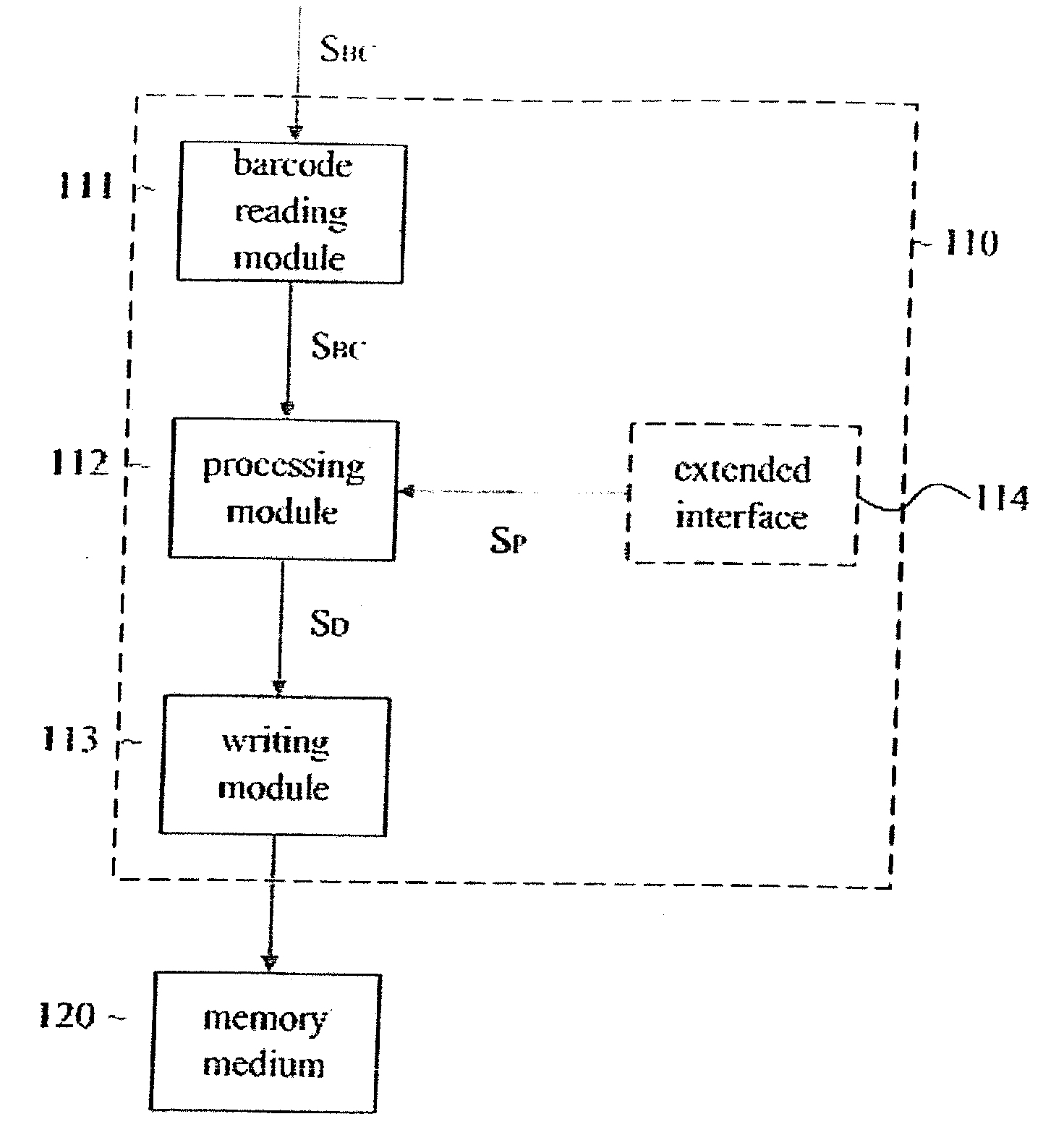

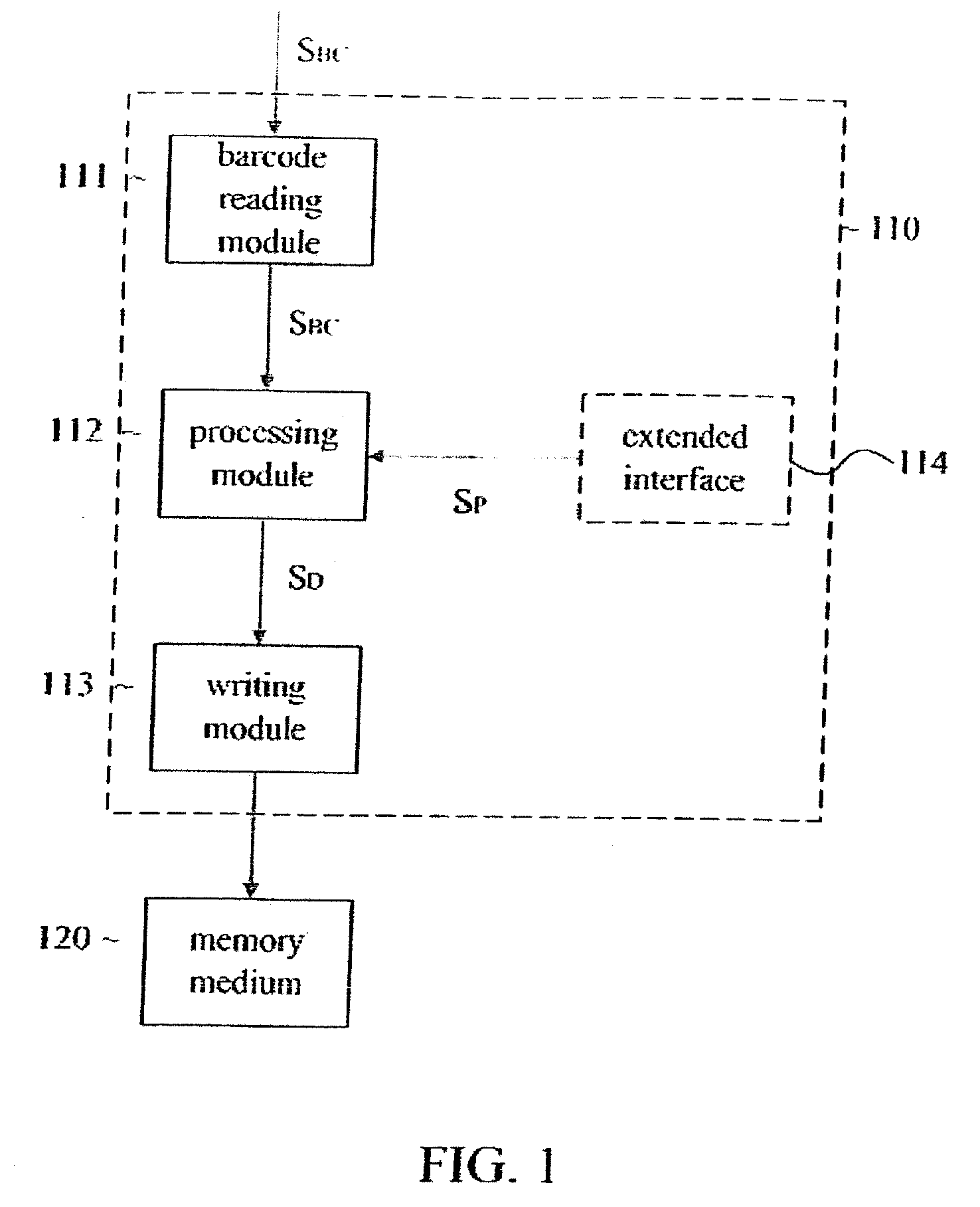

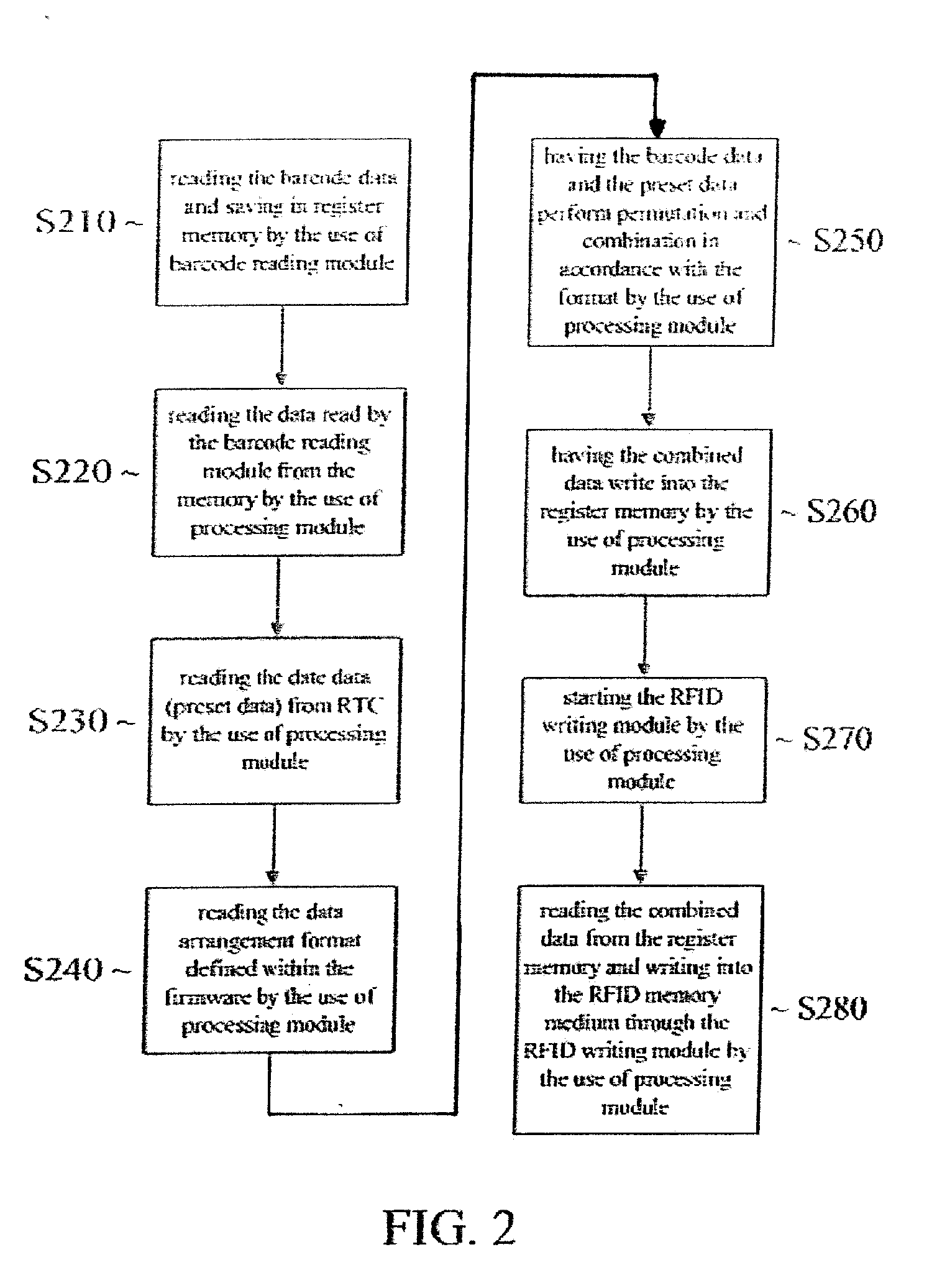

Data converter and its converting method

InactiveUS20100038428A1More convenientMore secureCharacter and pattern recognitionHybrid readersReal-time clockProcessor register

A data converter and its converting method having both the functions of barcode technology and RFID technology, and conforming with related regulations of international civil aviation are disclosed. The data converter includes a barcode reading module, a processing module, and a reading module. The converting method includes the following steps: (1) Reading an external barcode data SBC by the barcode reading module; (2) Reading the external barcode data SBC read by the barcode reading module by the barcode reading module from a memory; (3) Reading the date data (preset data SP) from the RTC (Real Time Clock) by the processing module; (4) Reading the data arrangement format defined within the firmware by the processing module; (5) Combining the external barcode data SBC and the preset data SP in accordance with the arranged format by the processing module; (6) Writing the combined data into a register memory by the processing module; (7) Starting the RFID module by the processing module; (8) Reading the combined data from the register memory by the processing module and writing into the RFID medium memory through the RFID module.

Owner:INST OF TRANSPORTATION MIN OF TRANSPORTATION & COMM TAIWAN R O C

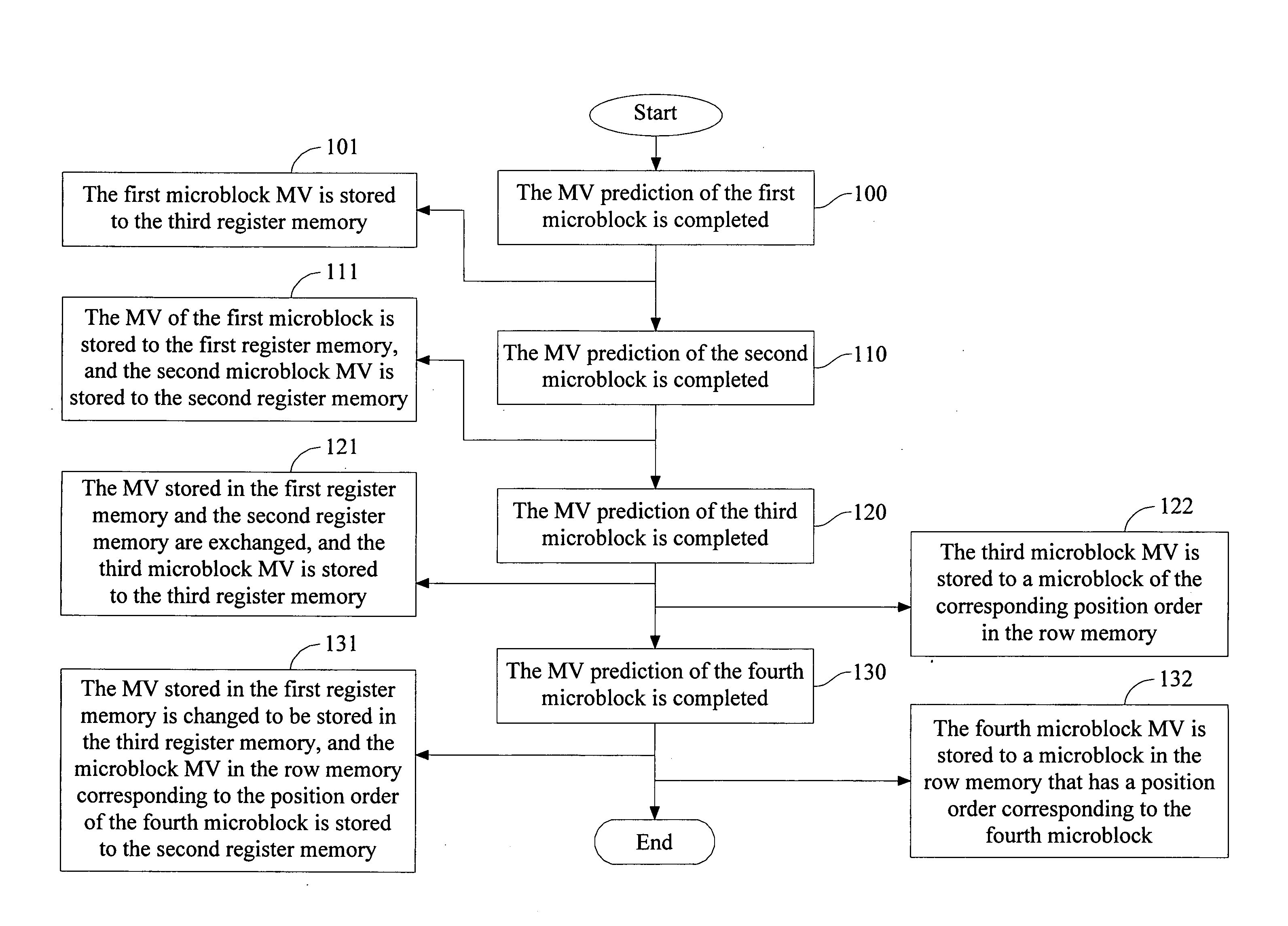

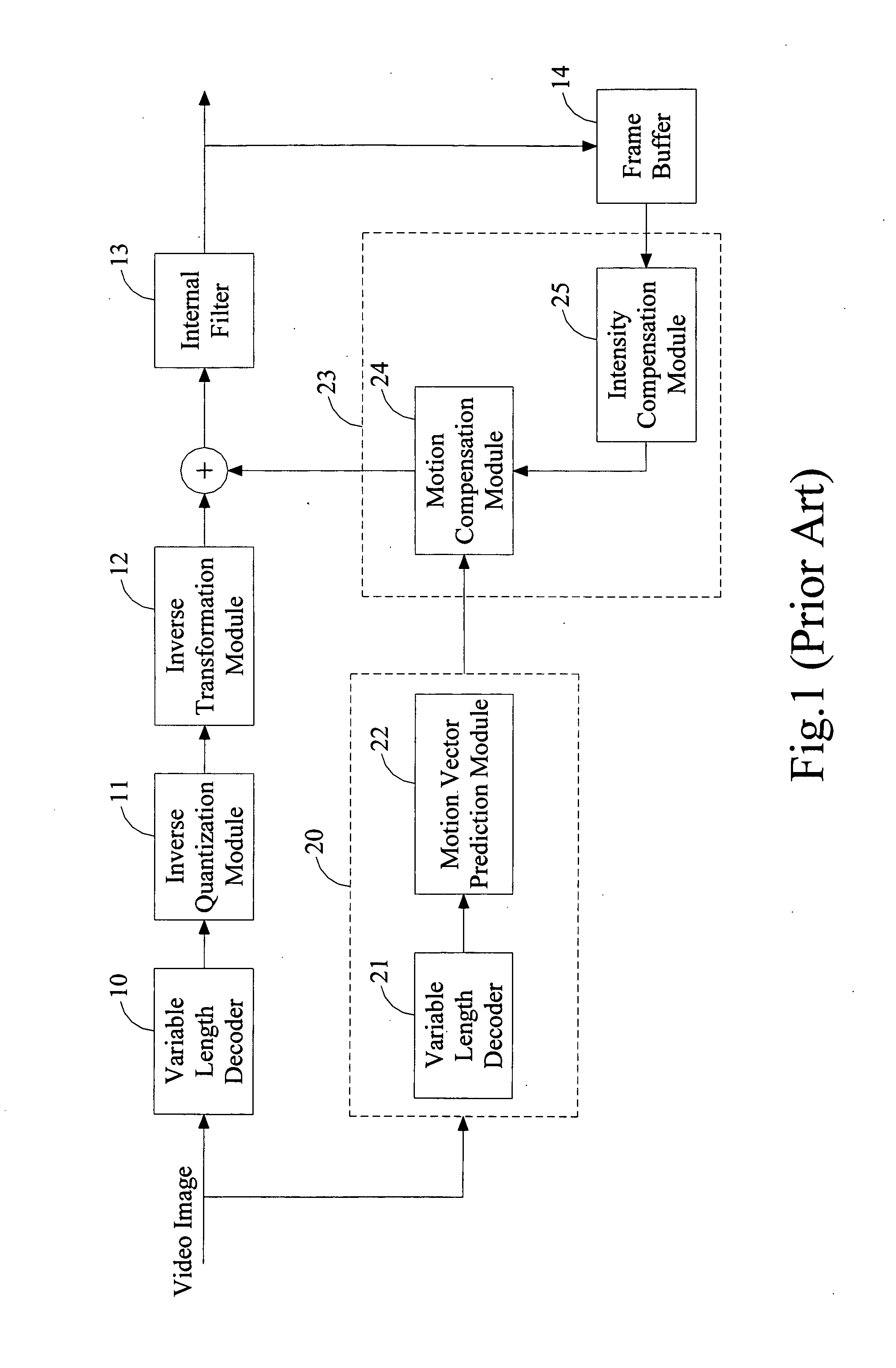

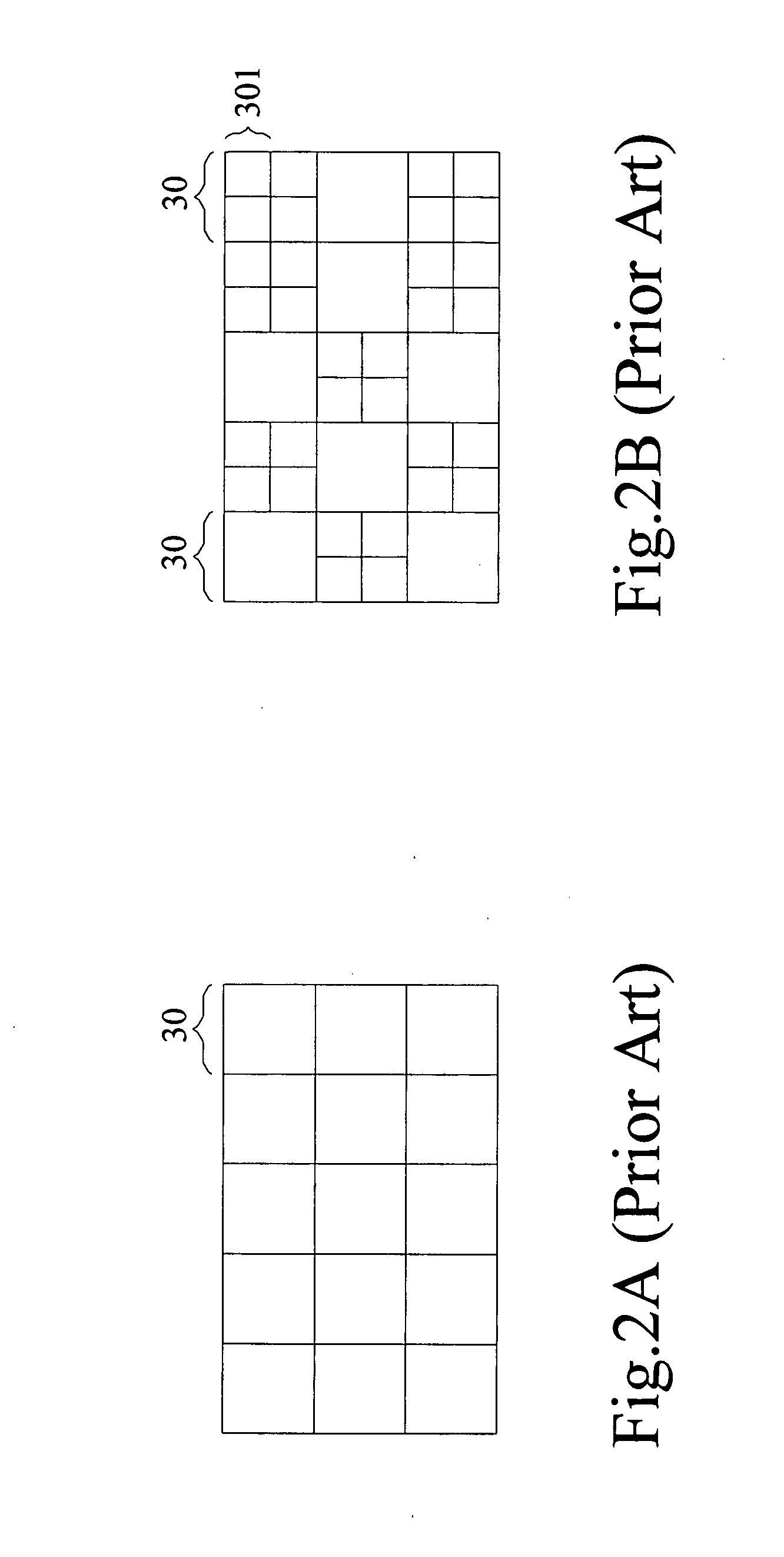

Motion vector prediction method and prediction apparatus thereof

InactiveUS20080159402A1Save memory spaceImprove efficiencyColor television with pulse code modulationColor television with bandwidth reductionMotion vectorProcessor register

A motion vector (MV) prediction method and a prediction apparatus thereof are applicable for a video image encoder / decoder to predict an MV of a video image. Firstly, segment a macroblock in the video image into microblocks. Then, configure a row memory and three register memories to register the MV required for prediction. Finally, the MV stored in the row memory or the register memories at a position corresponding to the current microblock to be predicted is used to predict the MV of the current microblock to be predicted in the current macroblock to be predicted. After the prediction is completed and moved to another macroblock or microblock, the MV stored in the row memory or the register memories is updated according to a predetermined storage updating condition.

Owner:IND TECH RES INST

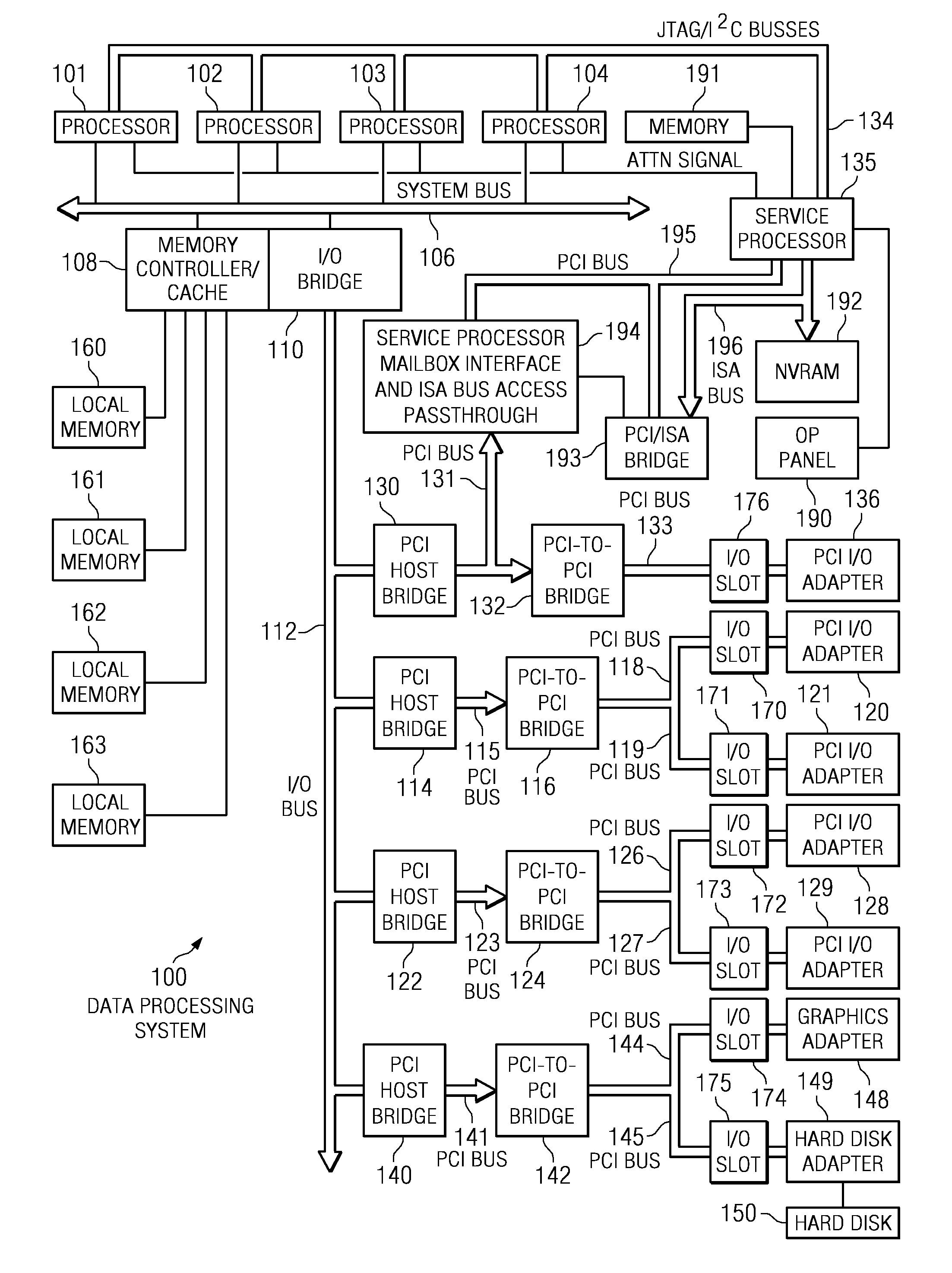

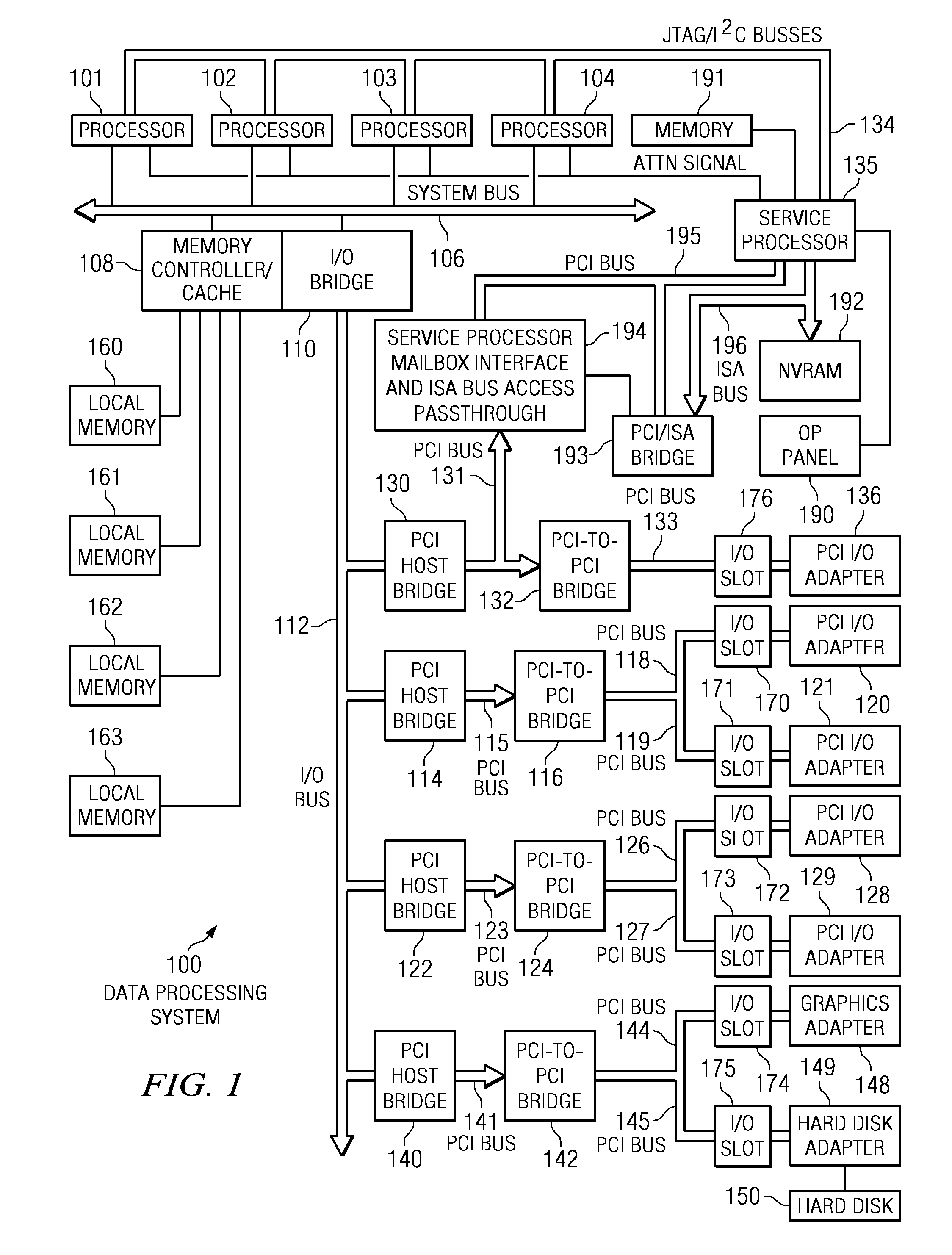

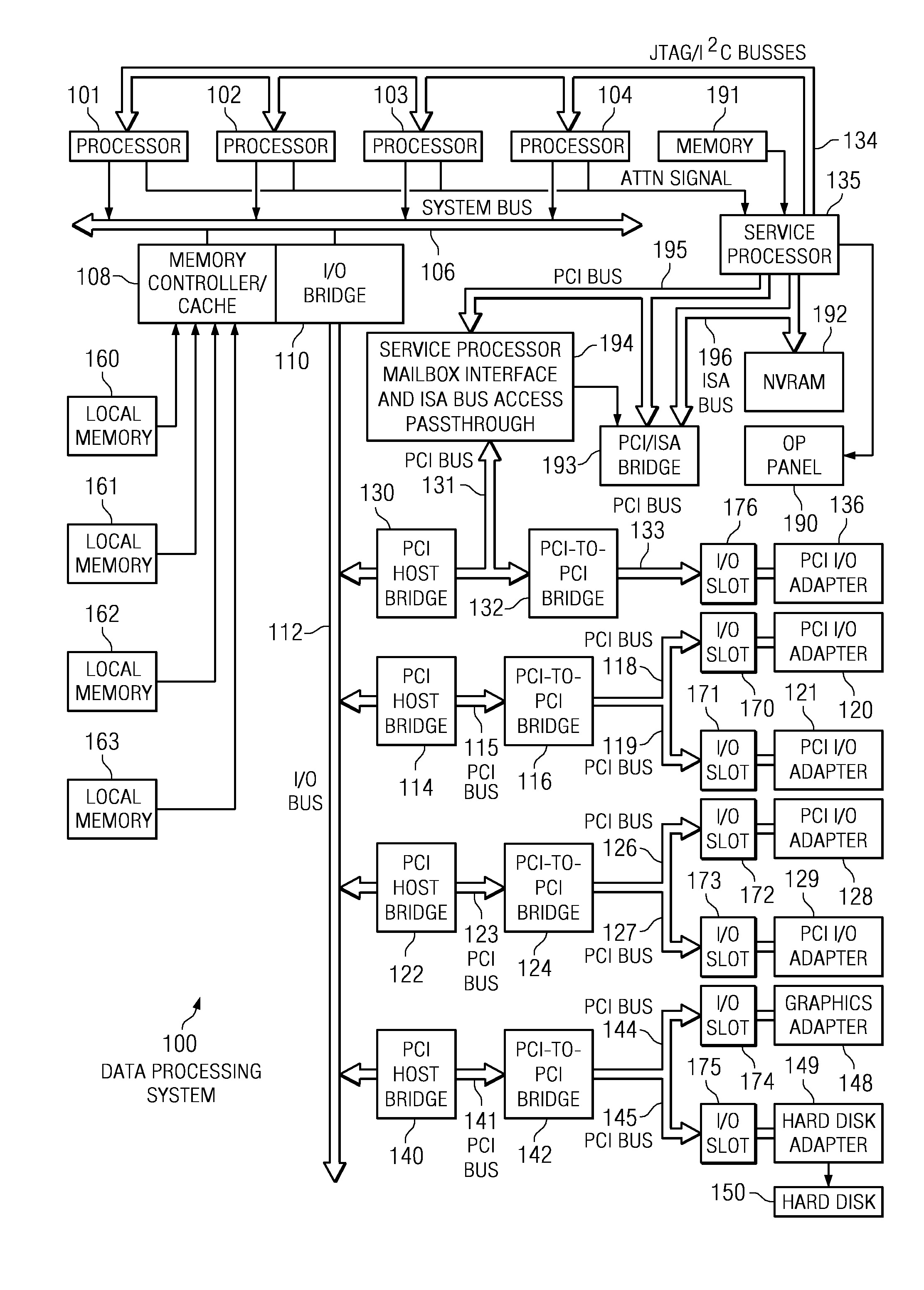

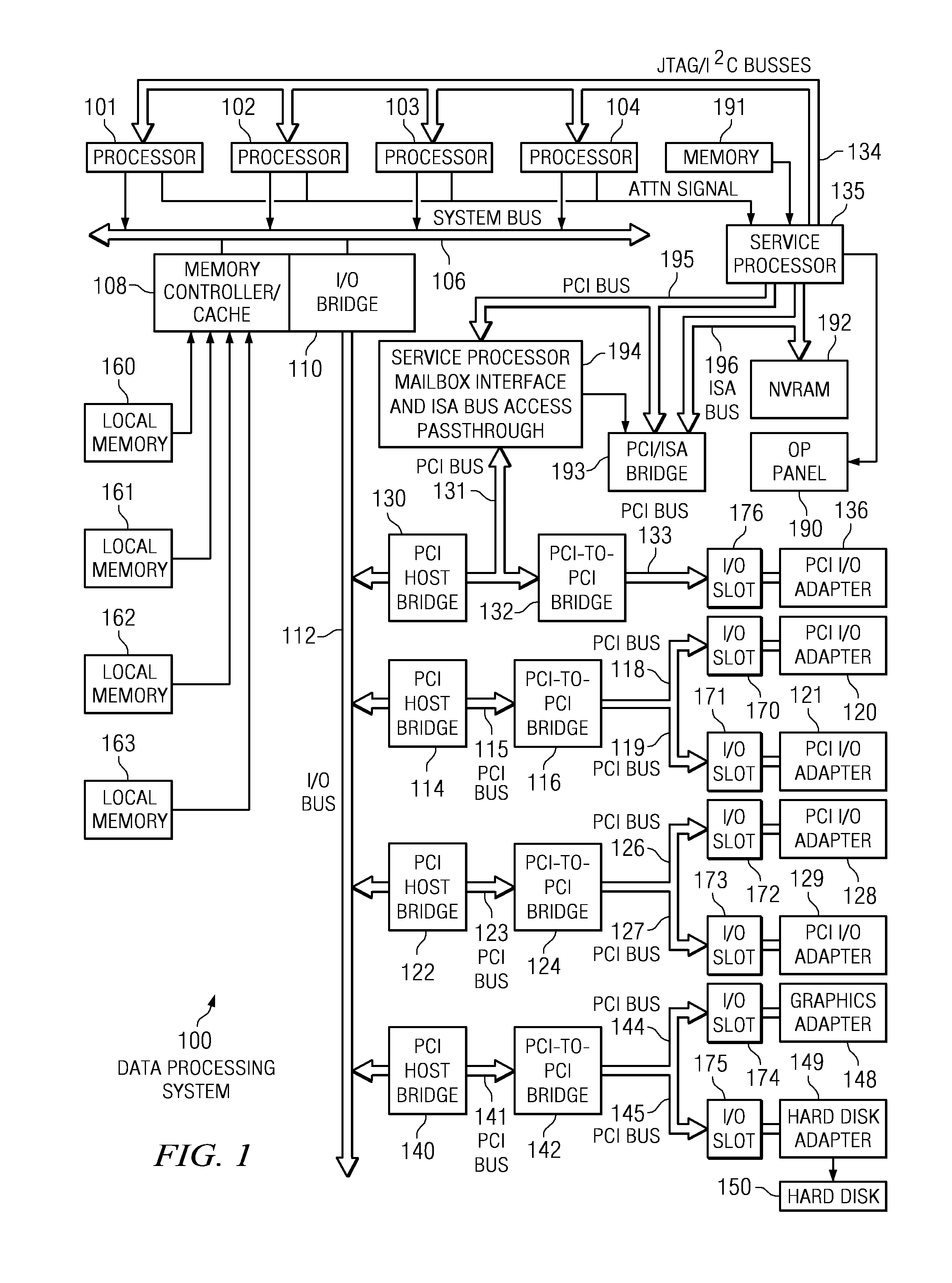

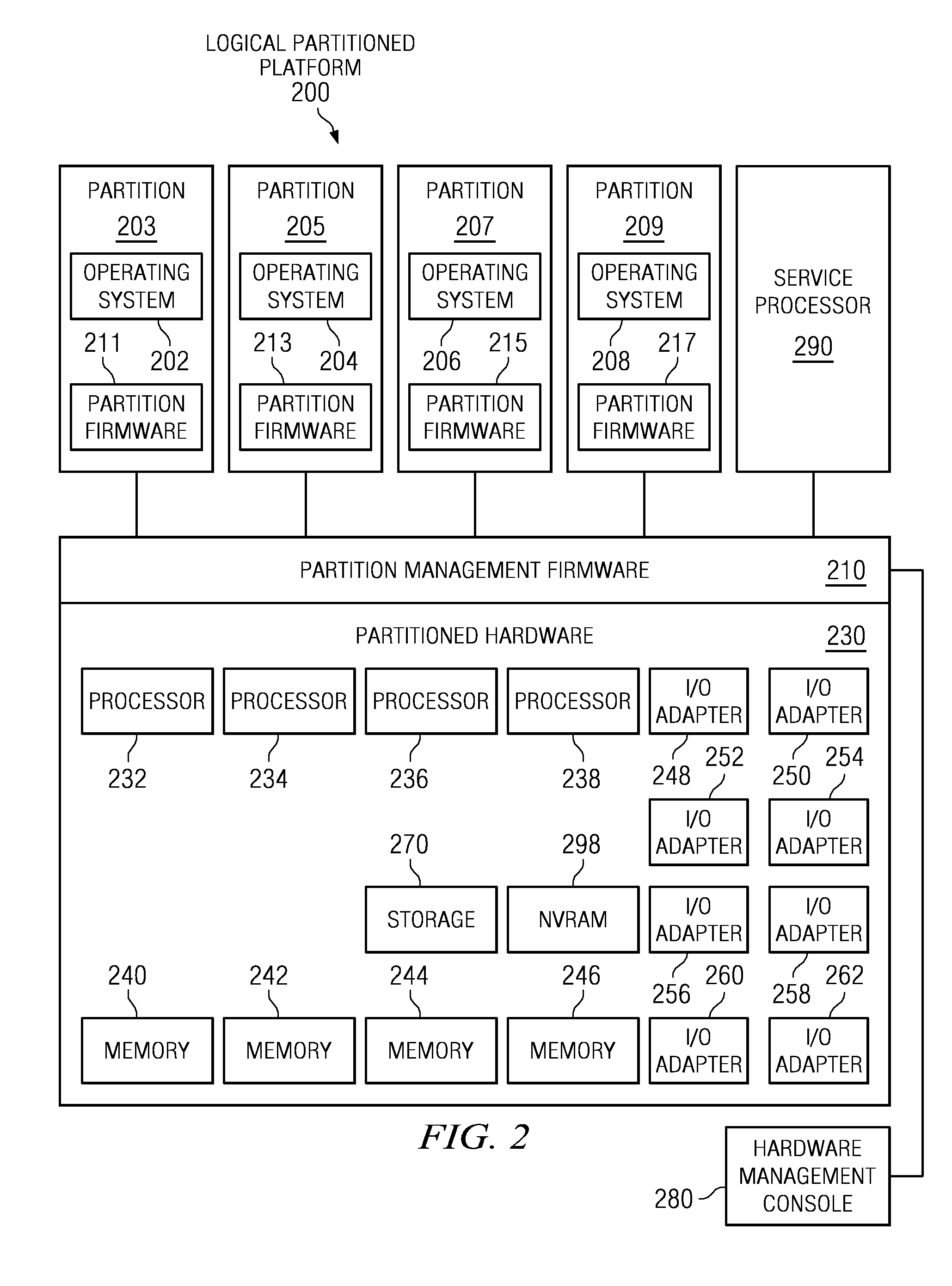

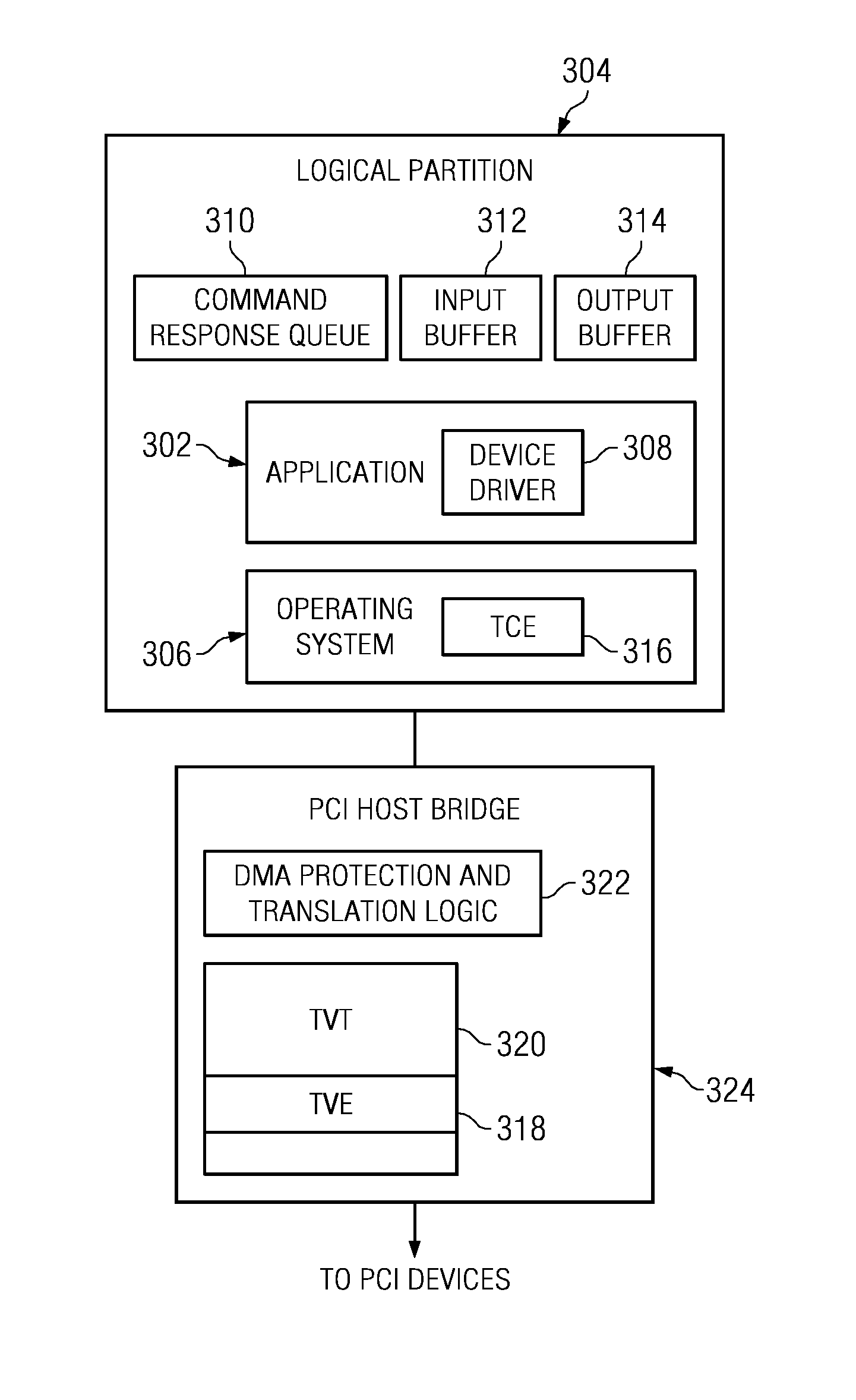

Mapping a Virtual Address to PCI Bus Address

InactiveUS20090276544A1Memory systemsInput/output processes for data processingData processing systemData treatment

Registering memory space within a data processing system is performed. One or more open calls are received from an application to access one or more input / output (I / O) devices. Responsive to receiving the one or more open calls, one or more I / O map and pin calls are sent in order to register memory space for the one or more I / O devices within at least one storage area that will be accessed by the application. At least one virtual I / O bus address is received for each registered memory space of the one or more I / O devices. At least one I / O command is executed using the at least one virtual I / O bus address without intervention by an operating system or operating system image.

Owner:IBM CORP

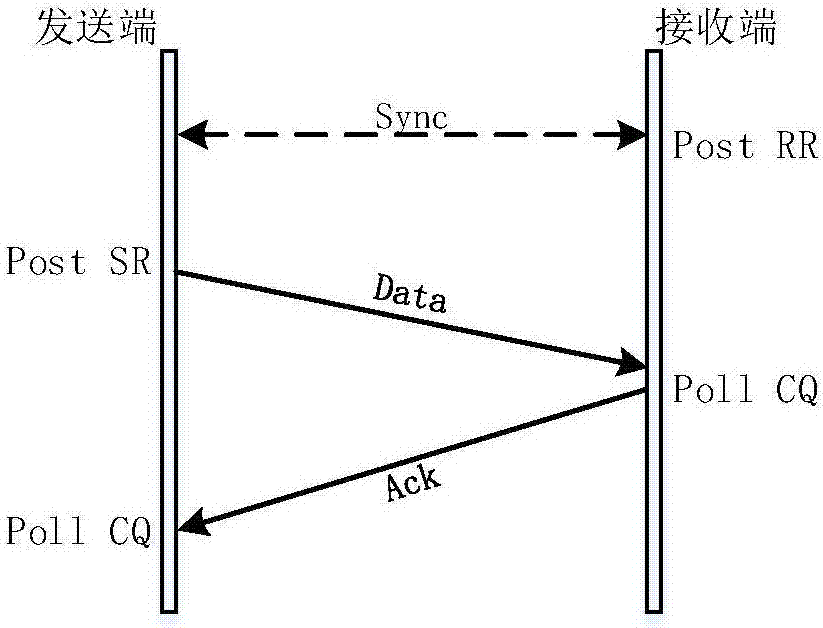

Method for message communication based on RDMA protocol

InactiveCN107147590AImprove efficiencySave resourcesInterprogram communicationData switching networksByteRegistered memory

The invention discloses a method for message communication based on an RDMA protocol. The method comprises the following steps of dividing a shared cache into a first preset number of memory blocks and registering a second preset number of memory blocks; judging whether the byte length of communication data is greater than the sum of the second preset number of memory blocks; if yes, registering a third preset number of memory blocks; storing the communication data into the registered memory blocks; and sending the communication data in the memory blocks to a receiving end. According to the method, the efficiency of sending the communication data is improved and the system resources are effectively saved; the invention also discloses a system for message communication based on the RDMA protocol, and the system has the beneficial effects.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

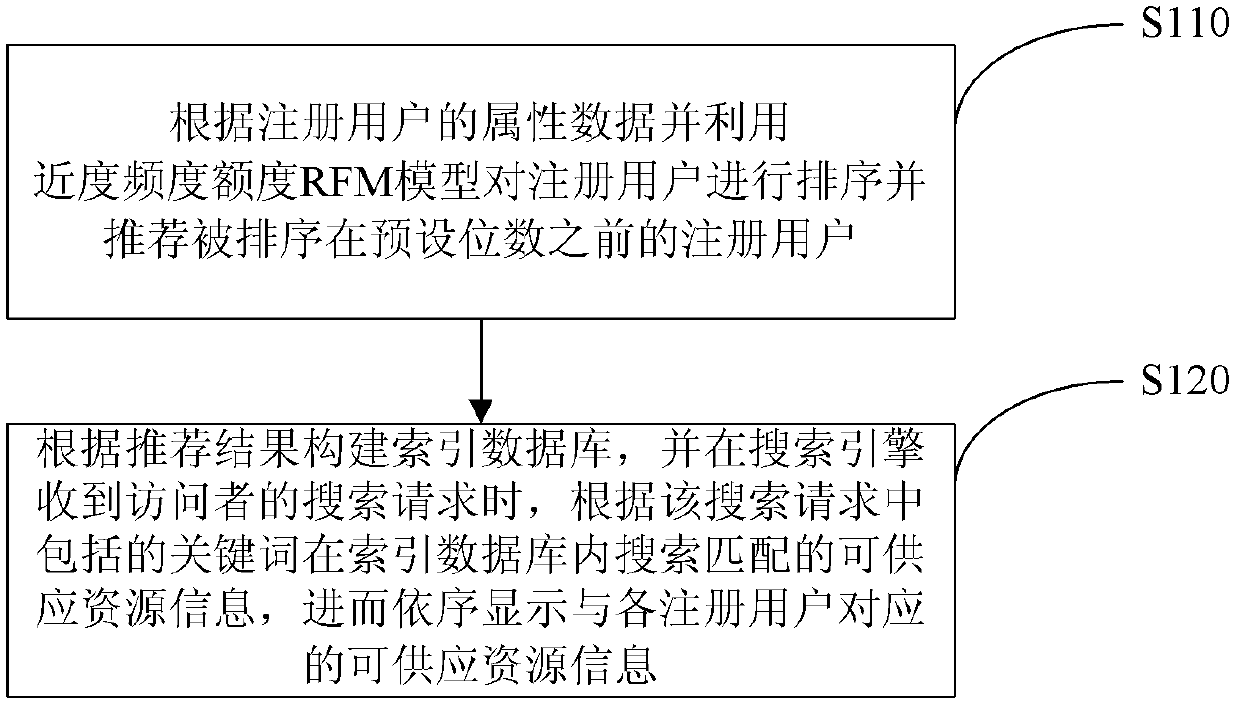

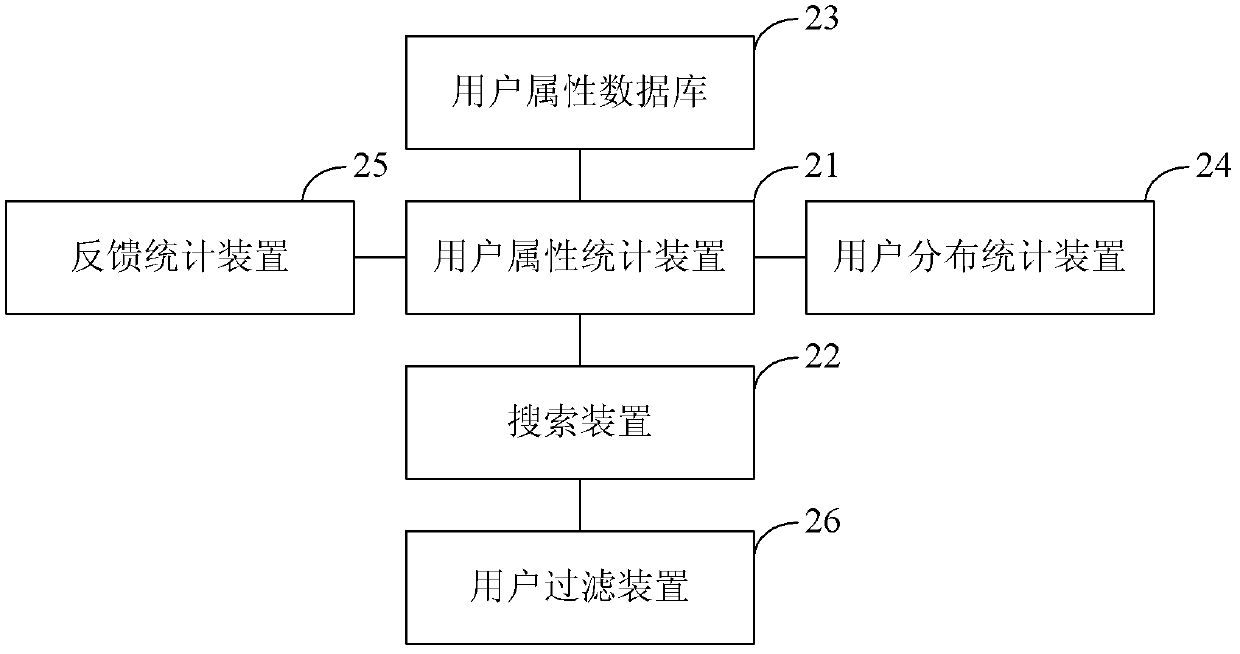

User attribute-based search realization method and system

ActiveCN103309894ALong calculation timeSpecial data processing applicationsResource informationData mining

The invention discloses a user attribute-based search realization method. The method comprises the following steps: S1, ordering registered users and recommending registered users which are ordered in front of a preset place according to attribute data of the registered users by utilizing a close frequency model (RFM); S2, constructing an index database according to the recommended result, searching matched available resource information in the index database according to key words in a search request when a search engines receives the search request of an accessor, and then displaying the available resource information corresponding to each registered user in turn. Correspondingly, the invention also discloses a user attribute-based search realization system. By the search realization method and the search realization system provided by the embodiment of the invention, the user attributes of the registered users can be embodied in the searched results of the available resource information, and the increment of search engine calculation time and the display delay of the results can be avoided.

Owner:ALIBABA GRP HLDG LTD

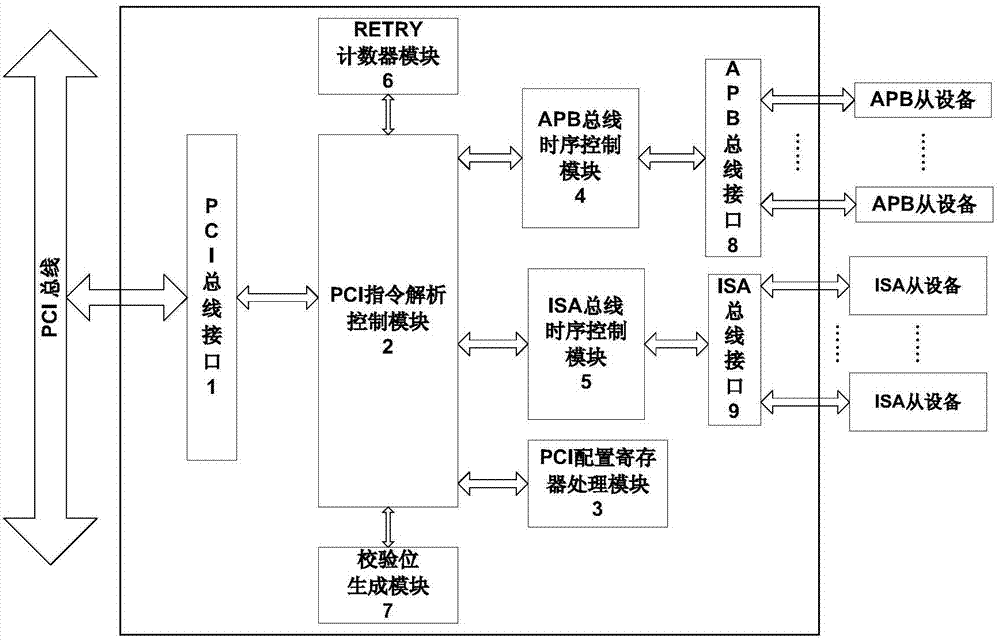

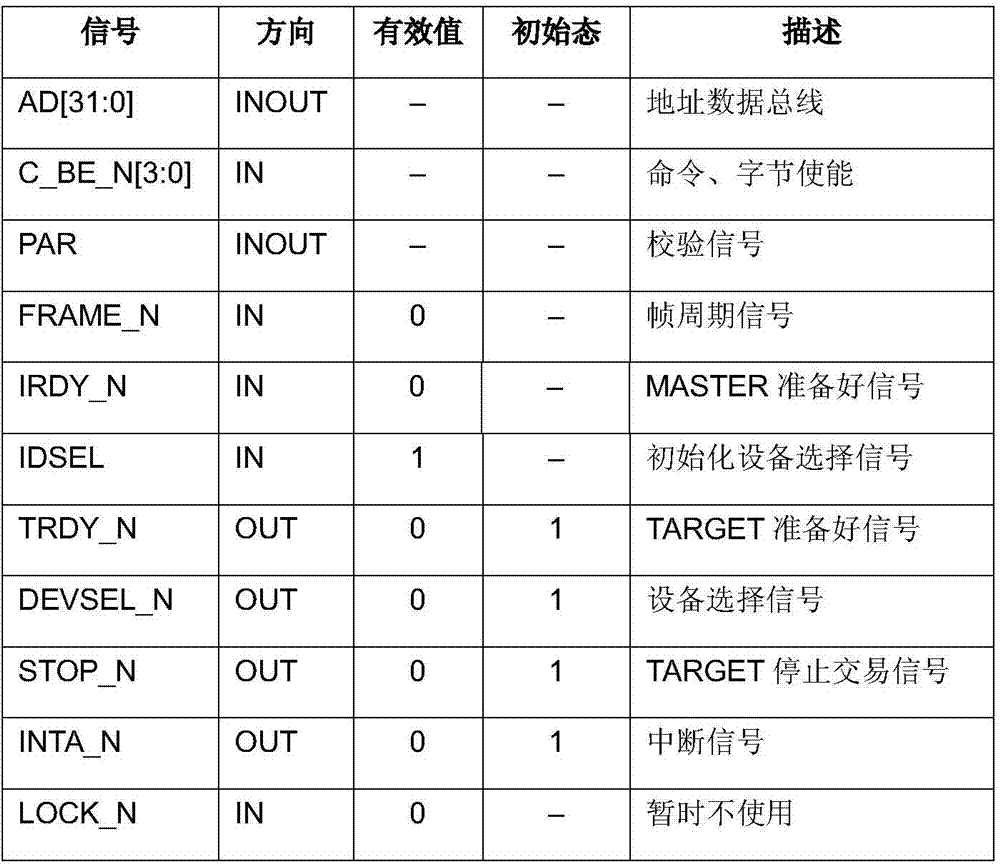

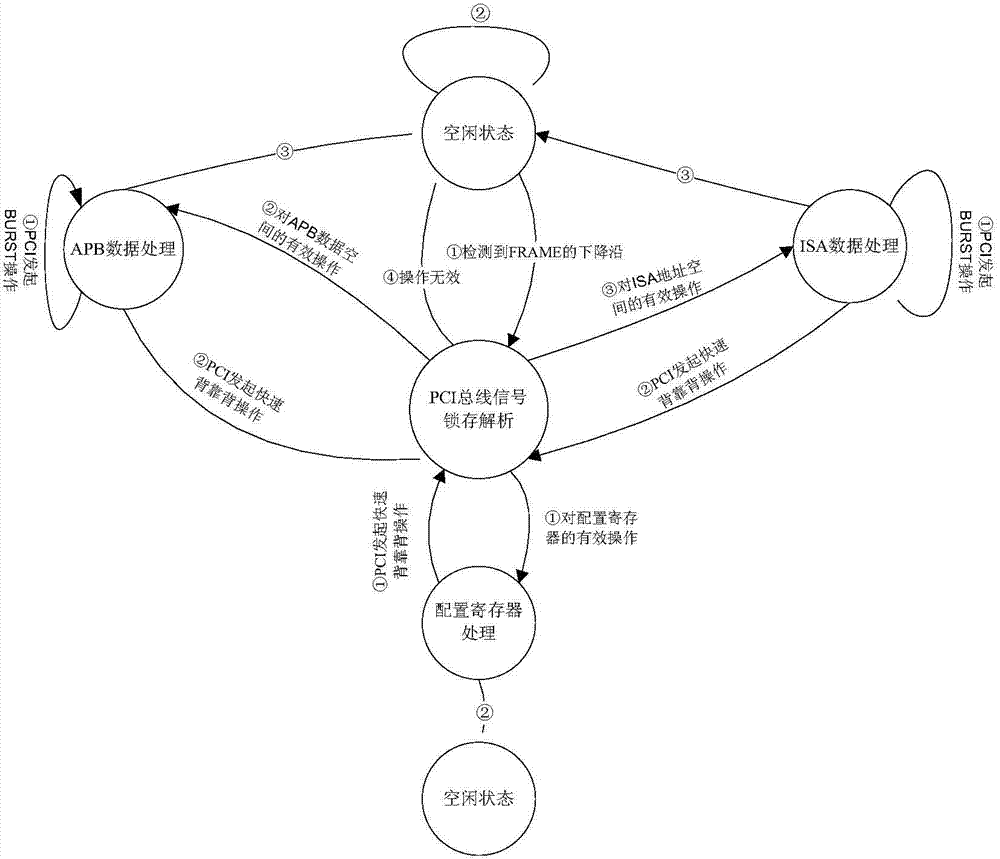

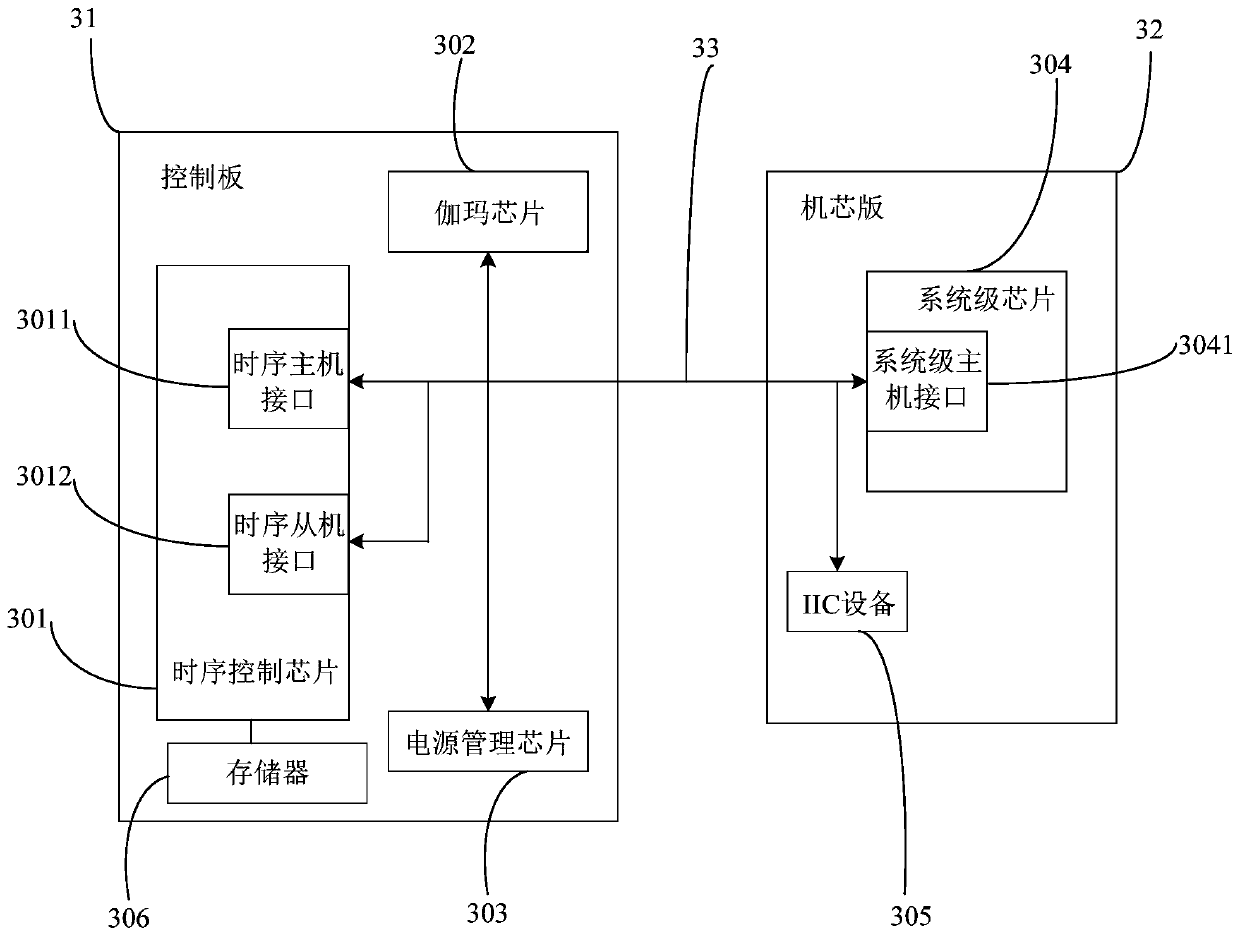

Design method for converting PCI bus into ISA bus or APB bus

ActiveCN104714907AHighly integrated designImprove adaptabilityElectric digital data processingProcessor registerComputerized system

The invention provides a design method for converting a PCI bus into an ISA bus or an APB bus. The design method solves the problem that in the prior art, a processor in an embedded type computer system cannot have access to devices meeting the ISA parallel bus protocol at the same time. According to the technical scheme, the design method comprises the steps that a PCI bus interface 1 receives a PCI bus configuration instruction of the PCI bus and sends the PCI bus configuration instruction to a PCI instruction analysis controlling module 2; the PCI instruction analysis controlling module 2 analyzes out a register address and a register memory address from the bus configuration instruction and sends the register address and the register memory address to a PCI bus configuration register module 3; the PCI bus configuration register module 3 writes the register address into a PCI control register which is located in the PCI bus configuration register module 3 and corresponds to the register address.

Owner:FLIGHT AUTOMATIC CONTROL RES INST

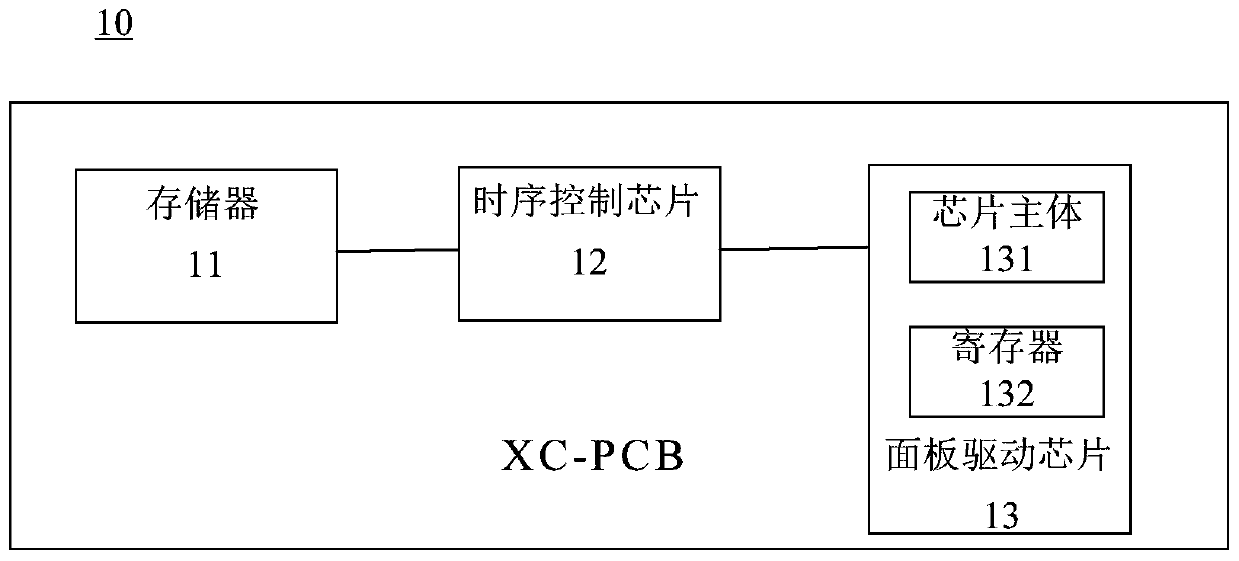

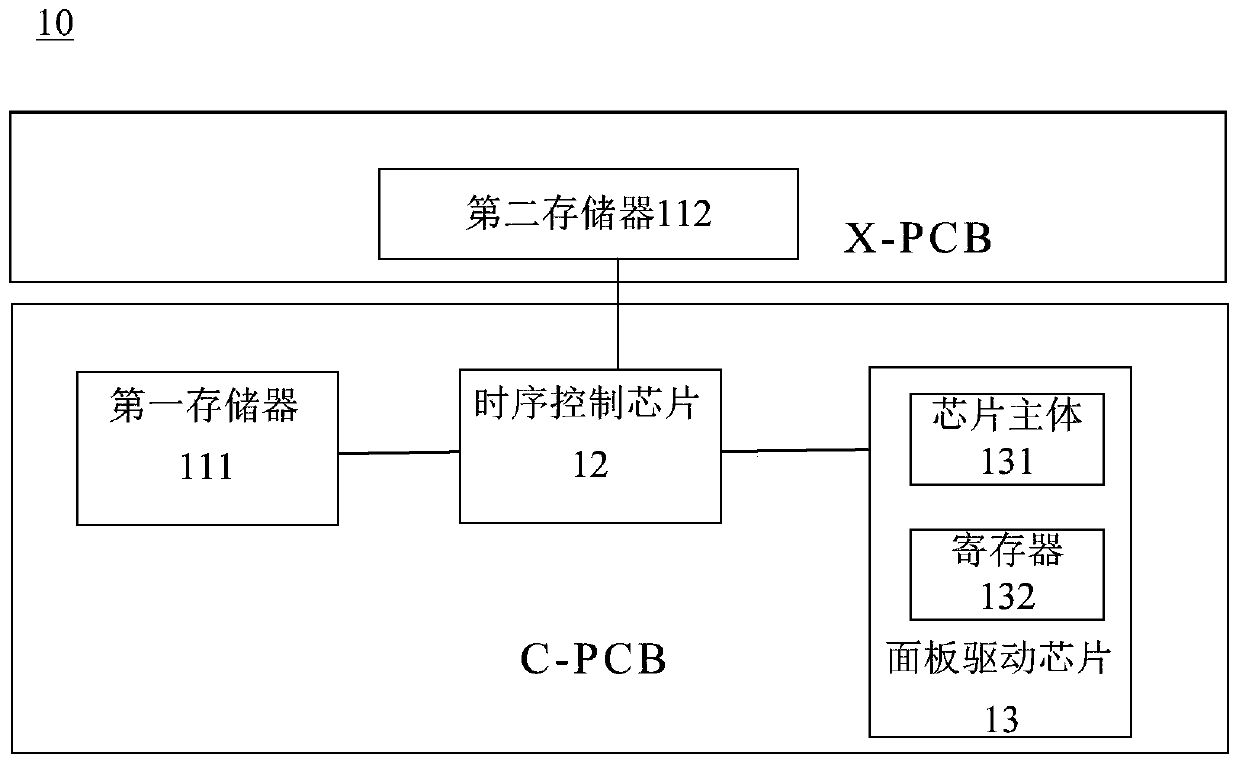

Display panel driving system

InactiveCN110890076ATroubleshoot technical issues that require setting up memoryLow costStatic indicating devicesData-drivenData storing

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Retaining an association between a virtual address based buffer and a user space application that owns the buffer

InactiveUS7908457B2Memory adressing/allocation/relocationMicro-instruction address formationVirtual address spaceSystem image

Registering memory space for an application is performed. One or more open calls are received from an application to access one or more input / output (I / O) devices. Responsive to receiving the one or more open calls, one or more I / O map and pin calls are sent in order to register memory space for the one or more I / O devices within at least one storage area that will be accessed by the application. A verification is made as to whether the memory space to be registered is associated with the application. Responsive to the memory space being associated with the application, at least one virtual I / O bus address is received for each registered memory space of the one or more I / O devices. At least one I / O command is executed using the at least one virtual I / O bus address without intervention by an operating system or operating system image.

Owner:INT BUSINESS MASCH CORP